## 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

概要

高効率DC-DCステップダウンスイッチングレギュレータのMAX8952は、最大2.5Aの出力電流を供給します。このデバイスは、2.5V～5.5Vの入力電圧範囲で動作するため、ハンドセットで一般に使用されるバッテリ技術をサポートしています。出力電圧は、0.77V～1.40Vの範囲でI<sup>2</sup>Cプログラム可能です。完全差動リモート検出が、負荷において高精度DCレギュレーションを確保しています。総出力誤差は、全負荷、ライン、および温度範囲で±1.5%以下となります。

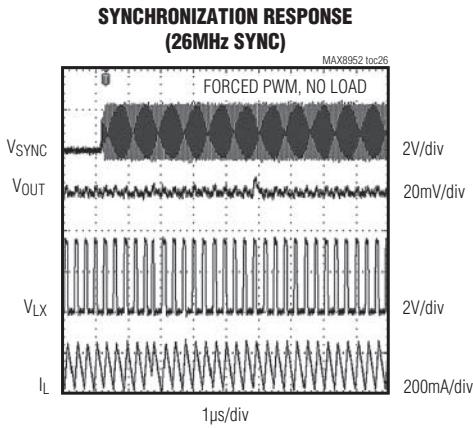

このICは、3.25MHzの固定周波数で動作します。この高い動作周波数によって、外付け部品のサイズが最小化されています。コンバータのスイッチング周波数は、アプリケーションのマスタークロックに同期可能です。外部クロックに同期させる場合、このICは、外部クロックの周波数を測定して、スイッチング周波数を外部クロック周波数に切り替える前に、クロックが安定状態にあることを確保します。

内蔵DACは、10mVステップで出力電圧の調整が可能です。出力電圧はI<sup>2</sup>Cインターフェースから直接プログラム可能であり、また内部レジスタセットをプリロードし、2つのVIDロジック信号を使用して適切なレジスタを選択してプログラムすることもできます。その他の機能には、突入電流を低減する内部ソフトスタート制御回路、出力過電圧保護、過電流保護、および温度過昇保護があります。

## アプリケーション

携帯電話およびスマートフォン

PDAおよびMP3プレーヤ

タブレットPC

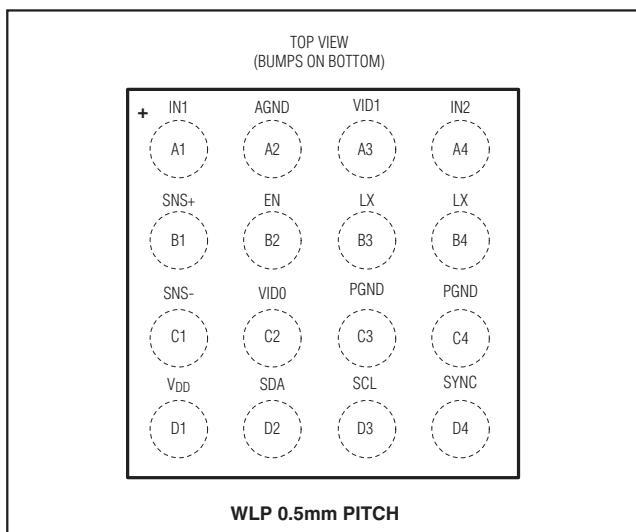

## ピン配置

## 特長

- ◆ 保証出力電流 : 2.5A

- ◆ I<sup>2</sup>Cプログラム可能なV<sub>OUT</sub> : 770mV~1.40V (10mVステップ)

- ◆ 初期精度 :  $\pm 0.5\%$  (1.40V出力の場合)

- ◆ 出力精度 :  $\pm 1.5\%$  (全負荷、ライン、および温度範囲、DCRが38.5mΩ以下の場合)

- ◆ 省電力モードによって軽負荷時の効率が向上

- ◆ 固定PWMスイッチング周波数 : 3.25MHz

- ◆ 小型1.0μHインダクタ

- ◆ 13MHz/19.2MHz/26MHzシステムクロックに同期可能

- ◆ 過電圧および過電流保護

- ◆ 入力動作電源 : 2.5V~5.5V

- ◆ サーマルシャットダウン保護

- ◆ FETおよび同期整流器内蔵

- ◆ 400kHz I<sup>2</sup>Cインターフェース

- ◆ シャットダウン電流 : 1μA以下

- ◆ 2mm x 2mmの16ピンWLPパッケージ

## 刑番

| PART         | TEMP RANGE     | PIN-PACKAGE                  |

|--------------|----------------|------------------------------|

| MAX8952EWE+T | -40°C to +85°C | 16 Bump WLP<br>(0.5mm pitch) |

+は鉛(Pb)フリー/RoHS準拠パッケージを表します。

T = テープ&リール

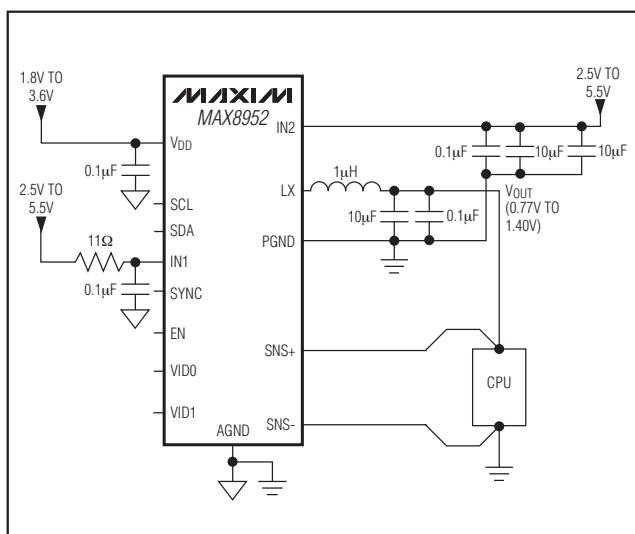

## 標準動作回路

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

## ABSOLUTE MAXIMUM RATINGS

|                                                           |                                    |

|-----------------------------------------------------------|------------------------------------|

| IN1, IN2 to AGND                                          | -0.3V to +6.0V                     |

| V <sub>DD</sub> to AGND                                   | -0.3V to +4.0V                     |

| LX, SNS+, VID0, VID1, EN to AGND                          | -0.3V to (V <sub>IN1</sub> + 0.3V) |

| SCL, SDA, SYNC to AGND                                    | -0.3V to (V <sub>DD</sub> + 0.3V)  |

| PGND, SNS- to AGND                                        | -0.3V to +0.3V                     |

| RMS LX Current                                            | 2500mA                             |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)     |                                    |

| 16-Bump WLP 0.5mm Pitch<br>(derate 20.4mW/°C above +70°C) | 1632mW                             |

|                                                                   |                 |

|-------------------------------------------------------------------|-----------------|

| Operating Temperature Range                                       | -40°C to +85°C  |

| Junction to Ambient Thermal Resistance ( $\theta_{JA}$ ) (Note 1) | 49°C/W          |

| Junction Temperature                                              | +150°C          |

| Storage Temperature Range                                         | -65°C to +150°C |

| Soldering Temperature (reflow)                                    | +260°C          |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to [japan.maxim-ic.com/thermal-tutorial](http://japan.maxim-ic.com/thermal-tutorial).

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

(V<sub>IN1</sub> = V<sub>IN2</sub> = 3.6V, V<sub>AGND</sub> = V<sub>PGND</sub> = 0V, V<sub>DD</sub> = 1.8V, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 2)

| PARAMETER                                             | CONDITIONS                                                                                                                          | MIN                              | TYP                          | MAX  | UNITS |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------------------|------|-------|

| IN1, IN2 Operating Range                              |                                                                                                                                     | 2.5                              | 5.5                          |      | V     |

| V <sub>DD</sub> Operating Range                       |                                                                                                                                     | 1.8                              | 3.6                          |      | V     |

| V <sub>DD</sub> Undervoltage Lockout (UVLO) Threshold | V <sub>DD</sub> falling                                                                                                             | 0.54                             | 0.865                        | 1.35 | V     |

| V <sub>DD</sub> UVLO Hysteresis                       |                                                                                                                                     |                                  | 50                           |      | mV    |

| IN_ Undervoltage Lockout (UVLO) Threshold             | V <sub>IN</sub> _ falling                                                                                                           | 2.10                             | 2.15                         | 2.20 | V     |

| IN_ UVLO Hysteresis                                   |                                                                                                                                     |                                  | 70                           |      | mV    |

| V <sub>DD</sub> Shutdown Supply Current               | V <sub>IN1</sub> = V <sub>IN2</sub> = 5.5V,<br>EN = V <sub>DD</sub> = AGND                                                          | TA = +25°C                       | 0.01                         | 1    | μA    |

|                                                       |                                                                                                                                     | TA = +85°C                       | 0.01                         |      |       |

| IN1, IN2 Shutdown Supply Current                      | V <sub>IN1</sub> = V <sub>IN2</sub> = 5.5V,<br>EN = V <sub>DD</sub> = AGND                                                          | TA = +25°C                       | 0.25                         | 1    | μA    |

|                                                       |                                                                                                                                     | TA = +85°C                       | 0.25                         |      |       |

| IN1, IN2 Standby Supply Current                       | V <sub>IN1</sub> = V <sub>IN2</sub> = 5.5V, SCL = SDA = V <sub>DD</sub> , EN = AGND, I <sup>2</sup> C ready                         | TA = +25°C                       | 0.35                         | 1    | μA    |

|                                                       |                                                                                                                                     | TA = +85°C                       | 0.35                         |      |       |

| V <sub>DD</sub> Standby Supply Current                | V <sub>IN1</sub> = V <sub>IN2</sub> = V <sub>DD</sub> = 3.6V,<br>SCL = SDA = V <sub>DD</sub> , EN = AGND,<br>I <sup>2</sup> C ready | TA = +25°C                       | 0.02                         | 1    | μA    |

|                                                       |                                                                                                                                     | TA = +85°C                       | 0.02                         |      |       |

| LOGIC INTERFACE                                       |                                                                                                                                     |                                  |                              |      |       |

| Logic Input High Voltage (V <sub>IH</sub> )           | V <sub>IN1</sub> = V <sub>IN2</sub> = 2.5V to 5.5V,<br>V <sub>DD</sub> = 1.8V to 3.6V                                               | EN, VID0, VID1<br>SYNC, SCL, SDA | 1.4<br>0.7 x V <sub>DD</sub> |      | V     |

| Logic Input Low Voltage (V <sub>IL</sub> )            | V <sub>IN1</sub> = V <sub>IN2</sub> = 2.5V to 5.5V,<br>V <sub>DD</sub> = 1.8V to 3.6V                                               | EN, VID0, VID1<br>SYNC, SCL, SDA | 0.4<br>0.3 x V <sub>DD</sub> |      | V     |

| SDA, SCL, SYNC Logic Input Current                    | V <sub>IL</sub> = 0V or V <sub>IH</sub> = 3.6V,<br>EN = AGND                                                                        | TA = +25°C<br>TA = +85°C         | -1<br>0.01<br>+1<br>0.01     |      | μA    |

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{IN1} = V_{IN2} = 3.6V$ ,  $V_{AGND} = V_{PGND} = 0V$ ,  $V_{DD} = 1.8V$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                                         | CONDITIONS                                                                         | MIN   | TYP   | MAX   | UNITS |

|---------------------------------------------------|------------------------------------------------------------------------------------|-------|-------|-------|-------|

| VID0, VID1, EN Logic Input Pulldown Resistor      | Controlled by I <sup>2</sup> C command:<br>VID0_PD = 1<br>VID1_PD = 1<br>EN_PD = 1 | 200   | 320   | 450   | kΩ    |

| <b>I<sup>2</sup>C INTERFACE</b>                   |                                                                                    |       |       |       |       |

| SDA Output Low Voltage                            | $I_{SDA} = 3mA$                                                                    |       | 0.03  | 0.4   | V     |

| I <sup>2</sup> C Clock Frequency                  |                                                                                    |       |       | 400   | kHz   |

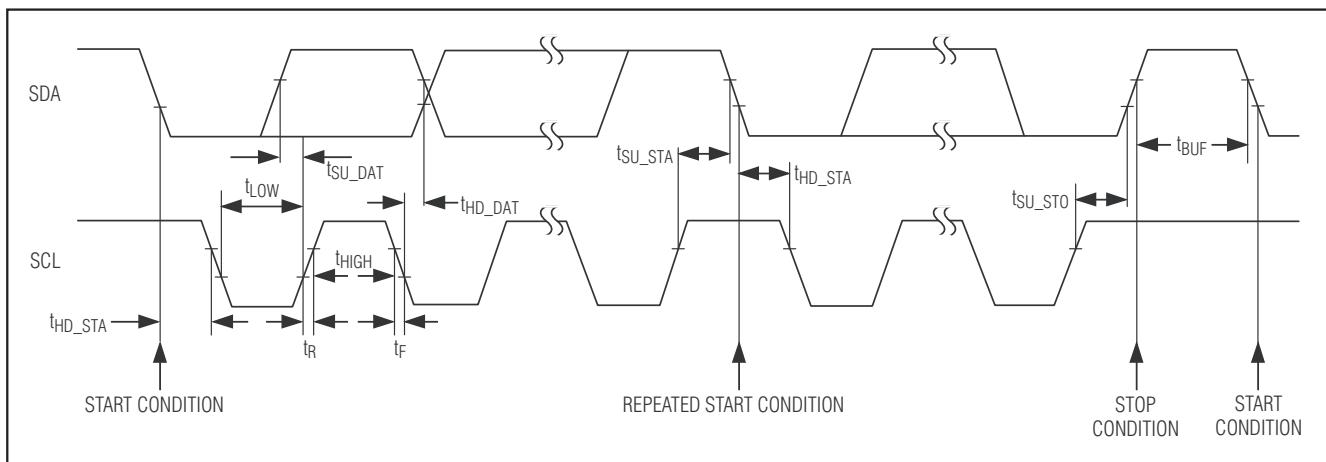

| Bus-Free Time Between START and STOP              | $t_{BUF}$                                                                          |       | 1.3   |       | μs    |

| Hold Time REPEATED START Condition                | $t_{HD\_STA}$                                                                      | 0.6   | 0.1   |       | μs    |

| SCL Low Period                                    | $t_{LOW}$                                                                          | 1.3   | 0.2   |       | μs    |

| SCL High Period                                   | $t_{HIGH}$                                                                         | 0.6   | 0.2   |       | μs    |

| Setup Time REPEATED START Condition               | $t_{SU\_STA}$                                                                      | 0.6   | 0.1   |       | μs    |

| SDA Hold Time                                     | $t_{HD\_DAT}$                                                                      | 0     | -0.01 |       | μs    |

| SDA Setup Time                                    | $t_{SU\_DAT}$                                                                      | 0.1   | 0.05  |       | μs    |

| Setup Time for STOP Condition                     | $t_{SU\_STO}$                                                                      | 0.6   | 0.1   |       | μs    |

| <b>STEP-DOWN DC-DC REGULATOR</b>                  |                                                                                    |       |       |       |       |

| IN1 + IN2 Supply Current                          | $V_{OUT} = 1.27V$ , no switching                                                   | 54    | 80    |       | μA    |

|                                                   | $V_{OUT} = 1.27V$ , $f_{sw} = 3.25MHz$                                             | 9     |       |       | mA    |

| Minimum Output Capacitance Required for Stability | $V_{OUT} = 0.77V$ to $1.40V$ ,<br>$I_{OUT} = 0$ to $2.5A$                          |       | 10    |       | μF    |

| OUT Voltage Range                                 | 10mV steps                                                                         | 0.770 |       | 1.400 | V     |

| Output Overvoltage Protection                     | Rising, 50mV hysteresis (typ)                                                      | 1.65  | 1.8   | 1.9   | V     |

MAX8952

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{IN1} = V_{IN2} = 3.6V$ ,  $V_{AGND} = V_{PGND} = 0V$ ,  $V_{DD} = 1.8V$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                                    | CONDITIONS                                                                  | MIN                  | TYP      | MAX          | UNITS |

|----------------------------------------------|-----------------------------------------------------------------------------|----------------------|----------|--------------|-------|

| OUT Voltage Accuracy                         | No load, $V_{IN\_} = 2.5V$ to $5.5V$ , $V_{OUT} = 1.27V$ , $FPWM\_EN\_ = 1$ | -0.5                 |          | +0.5         | %     |

|                                              | No load, $V_{IN\_} = 2.5V$ to $5.5V$ , $V_{OUT} = 0.77V$ , $FPWM\_EN\_ = 1$ | -1.0                 |          | +1.0         |       |

|                                              | No load, $V_{IN\_} = 2.5V$ to $5.5V$ , $V_{OUT} = 1.40V$ , $FPWM\_EN\_ = 1$ | -0.5                 |          | +0.5         |       |

| Load Regulation                              | $R_L$ is the resistance from LX to SNS+ (output)                            |                      | $R_L/25$ |              | V/A   |

| RAMP Timer                                   | $RAMP[2:0] = 000$                                                           |                      | 32.50    |              | mV/μs |

|                                              | $RAMP[2:0] = 001$                                                           |                      | 16.25    |              |       |

|                                              | $RAMP[2:0] = 010$                                                           |                      | 8.125    |              |       |

|                                              | $RAMP[2:0] = 011$                                                           |                      | 4.063    |              |       |

|                                              | $RAMP[2:0] = 100$                                                           |                      | 2.031    |              |       |

|                                              | $RAMP[2:0] = 101$                                                           |                      | 1.016    |              |       |

|                                              | $RAMP[2:0] = 110$                                                           |                      | 0.508    |              |       |

|                                              | $RAMP[2:0] = 111$                                                           |                      | 0.254    |              |       |

| Peak Current Limit<br>(p-Channel MOSFET)     |                                                                             | 3.45                 | 4.2      | 4.8          | A     |

| Valley Current Limit<br>(n-Channel MOSFET)   | Hysteretic mode                                                             | 2.7                  | 3.6      | 4.5          | A     |

| Negative Current Limit<br>(n-Channel MOSFET) | PWM mode                                                                    | 2.0                  | 2.5      | 3.0          | A     |

| n-Channel Zero-Crossing<br>Threshold         |                                                                             |                      | 50       |              | mA    |

| LX pFET On-Resistance                        | $IN2$ to LX, $I_{LX} = -200mA$                                              |                      | 0.08     | 0.16         | Ω     |

| LX nFET On-Resistance                        | $FPWM\_EN\_ = 0$ ,<br>LX to PGND, $I_{LX} = 200mA$                          |                      | 0.06     | 0.12         | Ω     |

| LX Leakage                                   | $V_{LX} = 5.5V$ or $0V$                                                     | $T_A = +25^{\circ}C$ | -1       | 0.03         | +1    |

|                                              |                                                                             | $T_A = +85^{\circ}C$ |          | 0.05         | μA    |

| Operating Frequency                          | Internal oscillator, PWM mode                                               |                      | 2.82     | 3.25         | 3.56  |

|                                              | Internal oscillator, power-save mode before entering<br>PWM mode            |                      | 2.43     | 3.25         | 4.06  |

|                                              | $13MHz = f_{SYNC}$ , $SYNC[1:0] = 01$                                       |                      |          | $f_{SYNC}/4$ | MHz   |

|                                              | $19.2MHz = f_{SYNC}$ , $SYNC[1:0] = 10$ or $11$                             |                      |          | $f_{SYNC}/6$ |       |

|                                              | $26MHz = f_{SYNC}$ , $SYNC[1:0] = 00$                                       |                      |          | $f_{SYNC}/8$ |       |

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

MAX8952

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{IN1} = V_{IN2} = 3.6V$ ,  $V_{AGND} = V_{PGND} = 0V$ ,  $V_{DD} = 1.8V$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                              | CONDITIONS                                                           | MIN  | TYP  | MAX  | UNITS      |

|----------------------------------------|----------------------------------------------------------------------|------|------|------|------------|

| Minimum Duty Cycle                     | Forced-PWM mode (FPWM_EN_ = 1), minimum duty cycle = 0%              |      |      | 16   | %          |

| Maximum Duty Cycle                     |                                                                      | 60   |      |      | %          |

| Minimum On- and Off-Time               |                                                                      | 30   | 40   | 50   | ns         |

| OUT Discharge Resistance               | During shutdown or UVLO, from SNS+ to PGND                           |      | 650  |      | $\Omega$   |

| SNS+, SNS- Input Impedance             |                                                                      | 400  | 600  | 850  | k $\Omega$ |

| Time Delay from PWM to Power-Save Mode | Time required for error amplifier to stabilize before switching mode |      | 70   |      | $\mu$ s    |

| Time Delay from Power-Save Mode to PWM | Time required for error amplifier to stabilize before switching mode |      | 140  |      | $\mu$ s    |

| <b>SYNCHRONIZATION (SYNC)</b>          |                                                                      |      |      |      |            |

| SYNC Capture Range                     | SYNC[1:0] = 00                                                       | 18.9 | 26.0 | 38.0 | MHz        |

|                                        | SYNC[1:0] = 1X                                                       | 14.2 | 19.2 | 28.5 |            |

|                                        | SYNC[1:0] = 01                                                       | 9.5  | 13.0 | 19.0 |            |

| SYNC Pulse Width                       |                                                                      |      | 13   |      | ns         |

| <b>PROTECTION CIRCUITS</b>             |                                                                      |      |      |      |            |

| Thermal-Shutdown Hysteresis            |                                                                      |      | 20   |      | °C         |

| Thermal Shutdown                       |                                                                      |      | +160 |      | °C         |

**Note 2:** All devices are 100% production tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range are guaranteed by design.

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

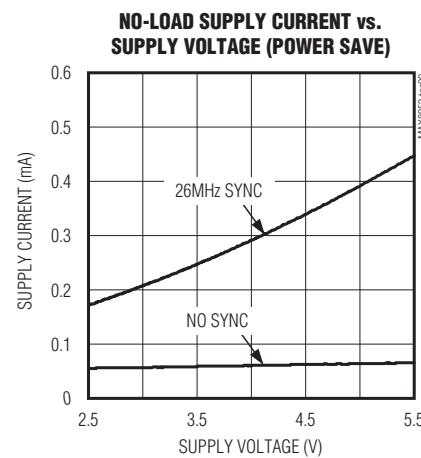

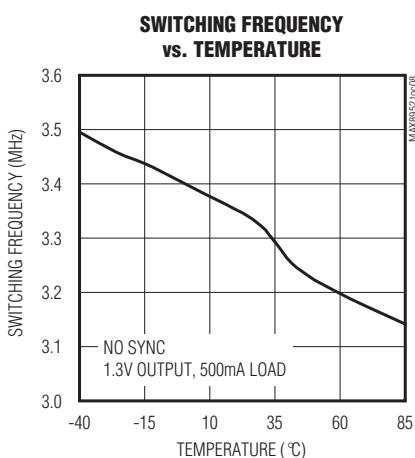

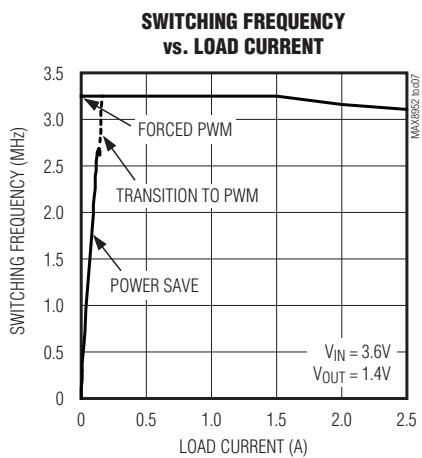

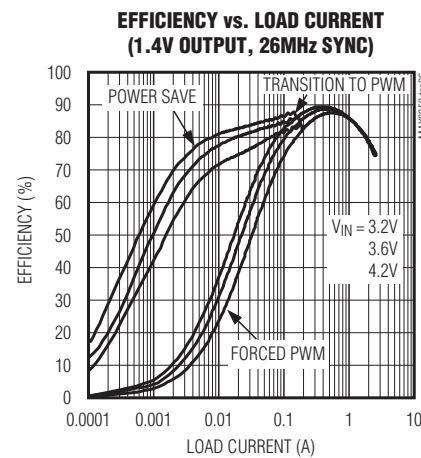

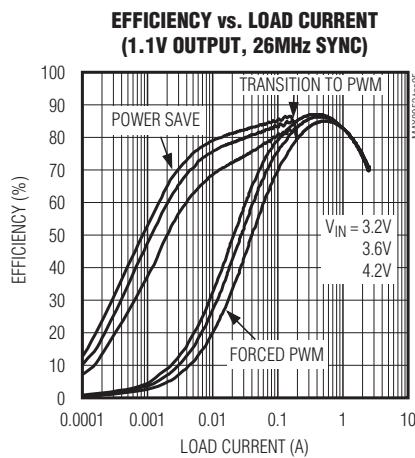

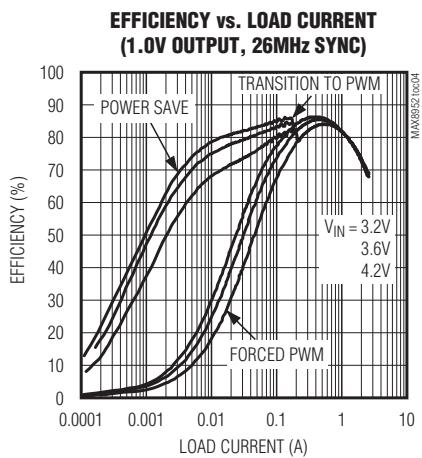

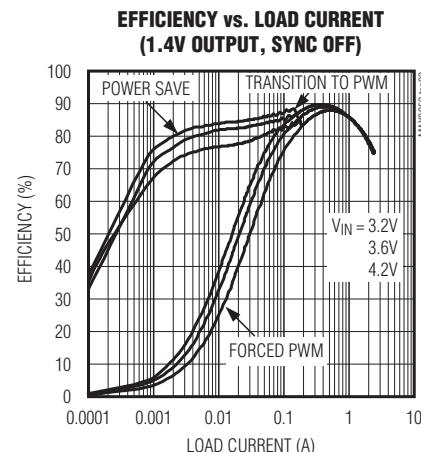

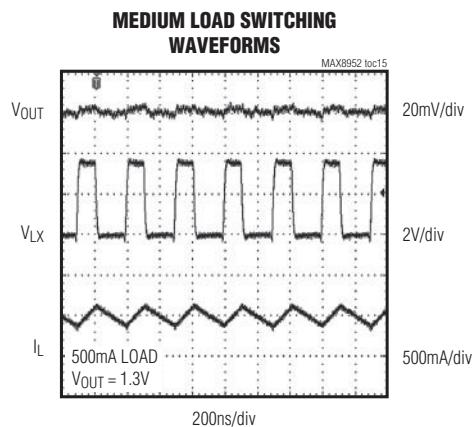

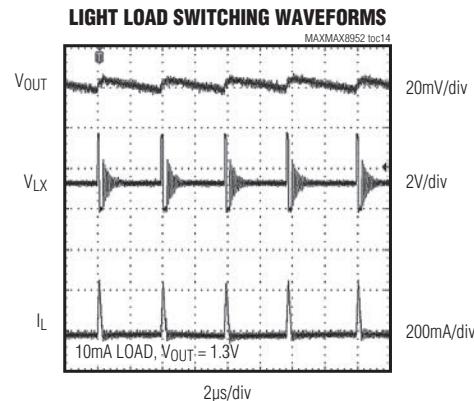

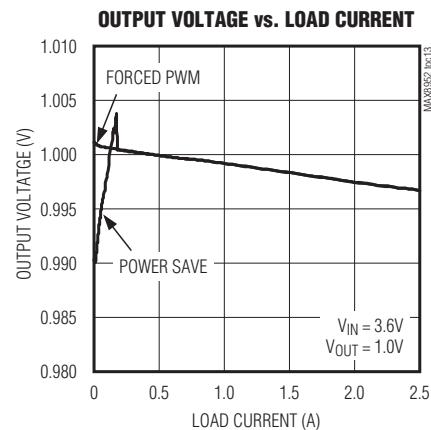

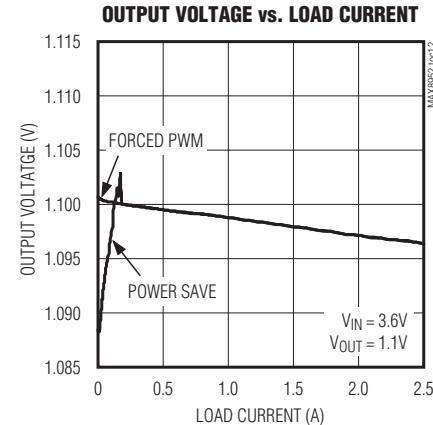

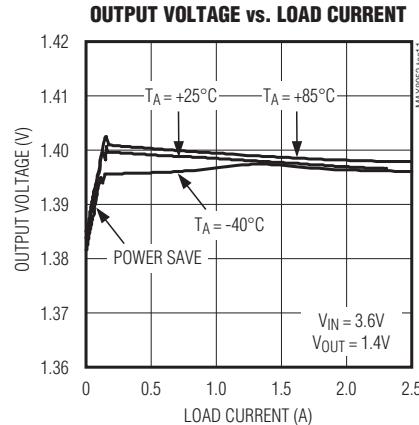

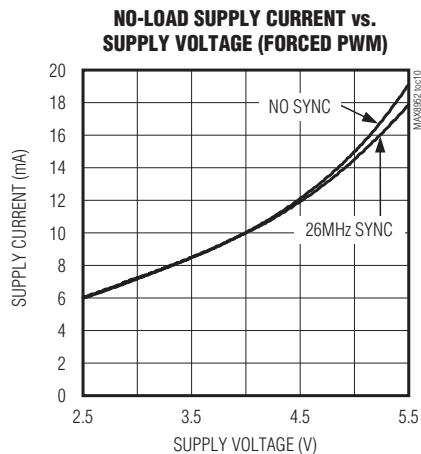

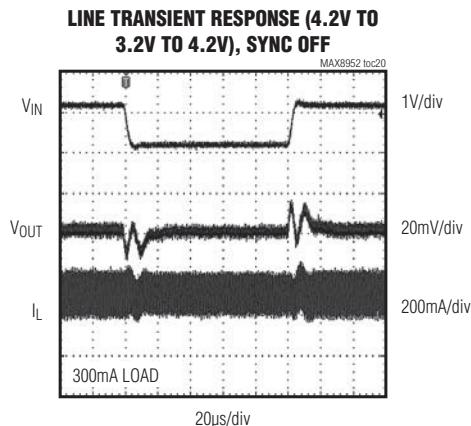

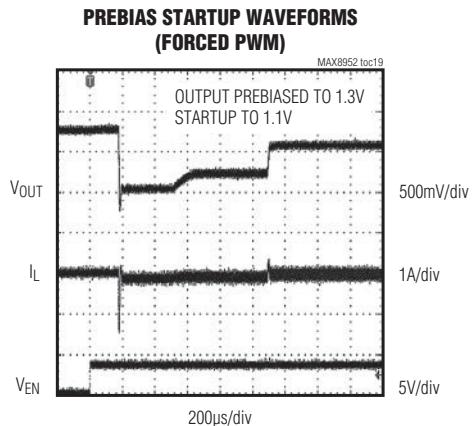

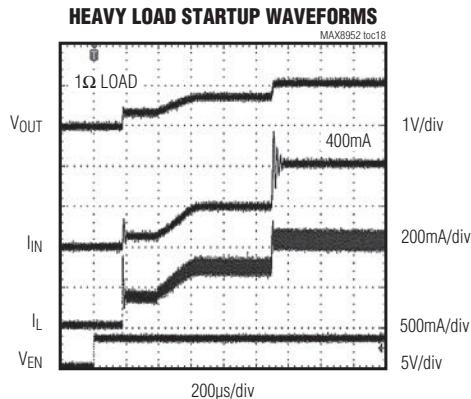

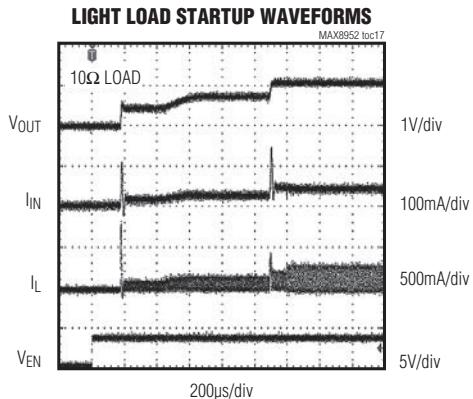

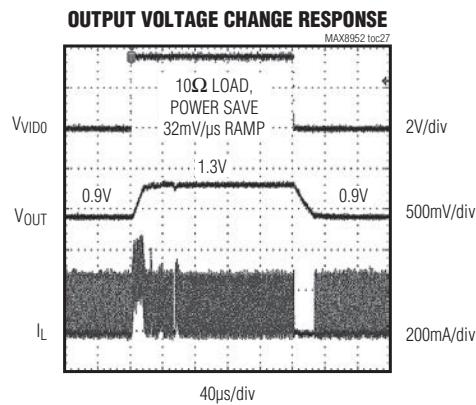

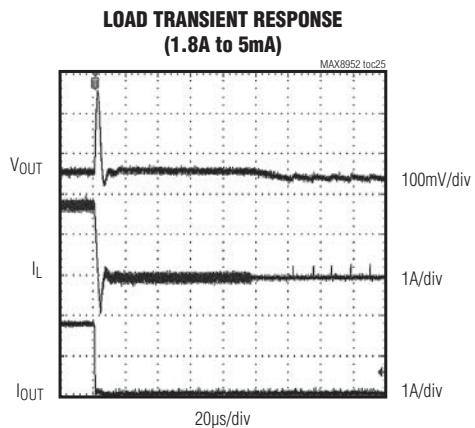

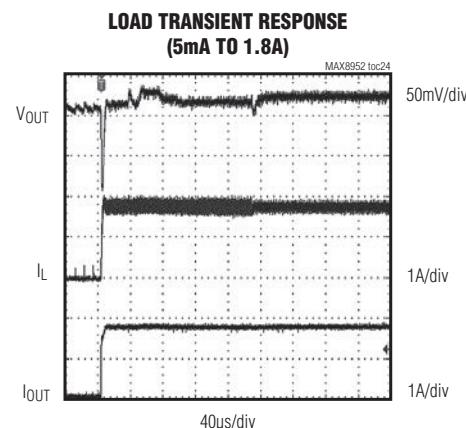

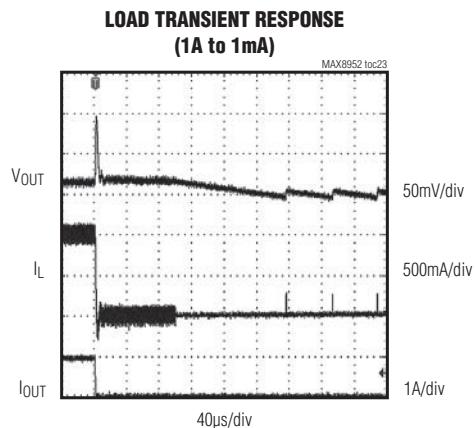

## 標準動作特性

(Typical Operating Circuit,  $V_{IN1} = V_{IN2} = 3.6V$ ,  $V_{AGND} = V_{PGND} = 0V$ ,  $V_{OUT} = 1.1V$ ,  $V_{DD} = 1.8V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

MAX8952

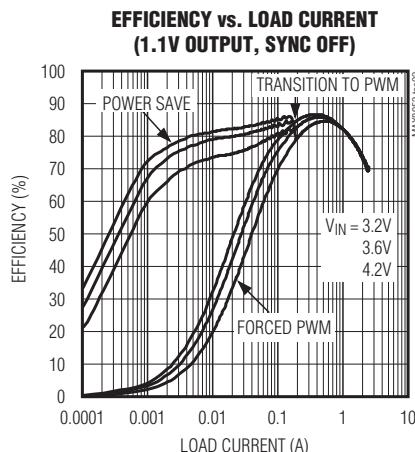

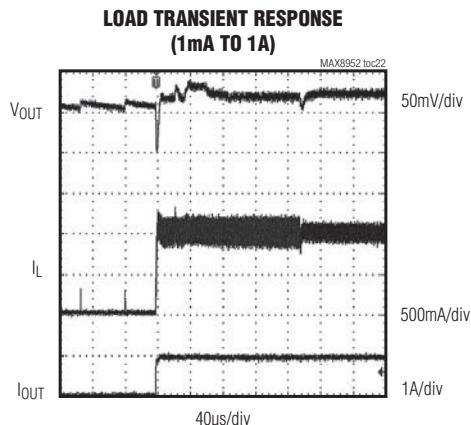

## 標準動作特性(続き)

(Typical Operating Circuit,  $V_{IN1} = V_{IN2} = 3.6V$ ,  $V_{AGND} = V_{PGND} = 0V$ ,  $V_{OUT} = 1.1V$ ,  $V_{DD} = 1.8V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

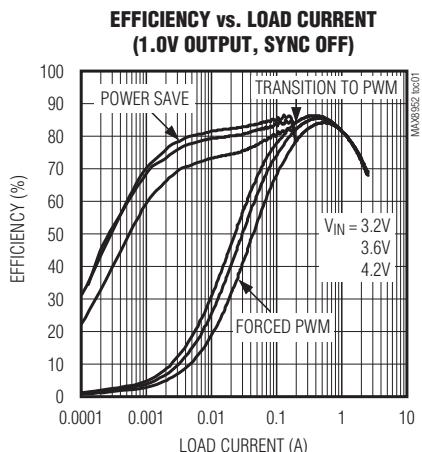

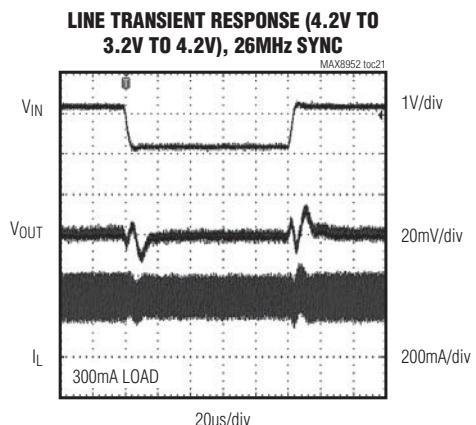

## 標準動作特性(続き)

(Typical Operating Circuit,  $V_{IN1} = V_{IN2} = 3.6V$ ,  $V_{AGND} = V_{PGND} = 0V$ ,  $V_{OUT} = 1.1V$ ,  $V_{DD} = 1.8V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

MAX8952

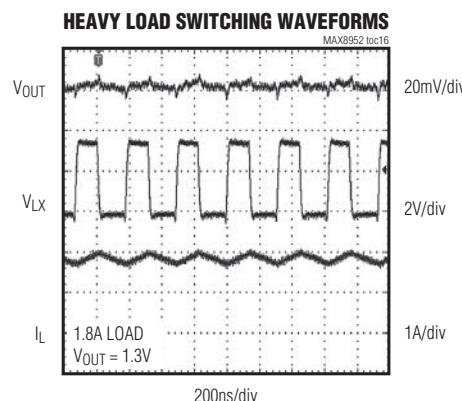

## 標準動作特性(続き)

( $T_A = +25^\circ\text{C}$ , unless otherwise noted.)

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

## 端子説明

| 端子     | 名称              | 機能                                                                                                                                                                                                      |

|--------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1     | IN1             | アナログ電源電圧入力。入力電圧範囲は2.5V～5.5Vです。11Ωの抵抗をIN1と入力電源の間に配置します。ICにできる限り近接させた0.1μFのセラミックコンデンサで、IN1をAGNDにバイパスします。IN1とIN2を同じ電源に接続します。                                                                               |

| A2     | AGND            | アナロググランド。AGNDをPCBのグランドプレーンに接続します。                                                                                                                                                                       |

| A3     | VID1            | 電圧ID制御入力。VID0およびVID1のロジック状態は、出力電圧を設定するレジスタを選択します。                                                                                                                                                       |

| A4     | IN2             | 電源電圧入力。入力電圧範囲は2.5V～5.5Vです。IN2は、内蔵のpチャネルとnチャネルMOSFETに電力を供給します。ICにできる限り近接させた2 x 10μFと0.1μFのセラミックコンデンサで、IN2をPGNDにバイパスします。IN1とIN2を同じ電源に接続します。                                                               |

| B1     | SNS+            | 出力電圧リモート検出の正入力。SNS+を負荷の出力に直接接続します。                                                                                                                                                                      |

| B2     | EN              | ロジックイネーブル入力。DC-DCステップダウンレギュレータをイネーブルするには、ENをハイに駆動します。シャットダウンモードに設定するには、ローに駆動します。シャットダウンモードでは、このロジック入力はAGNDへのプルダウン抵抗を内蔵しています。                                                                            |

| B3, B4 | LX              | インダクタ接続。LXは、内蔵pチャネルとnチャネルMOSFETのドレインに接続されています。シャットダウン時、LXはハイインピーダンスです。                                                                                                                                  |

| C1     | SNS-            | 出力電圧リモート検出の負入力。負荷の静かなグランドに直接接続します。                                                                                                                                                                      |

| C2     | VID0            | 電圧ID制御入力。VID0およびVID1のロジック状態は、出力電圧を設定するレジスタを選択します。                                                                                                                                                       |

| C3, C4 | PGND            | 電源グランド。両方のPGNDバンプをPCBのグランドプレーンに接続します。                                                                                                                                                                   |

| D1     | V <sub>DD</sub> | ロジック入力電源電圧。V <sub>DD</sub> をSDA、SCL、およびSYNCを駆動するロジック電源に接続します。0.1μFのセラミックコンデンサで、V <sub>DD</sub> をAGNDにバイパスします。V <sub>DD</sub> がUVLOスレッショルドより低下すると、I <sup>2</sup> Cレジスタはリセットされますが、EN制御はこのモードでアクティブのままでです。 |

| D2     | SDA             | I <sup>2</sup> Cデータ入力。SCLの立上りエッジでデータが読み取られ、SCLの立下りエッジでデータがクロック出力されます。                                                                                                                                   |

| D3     | SCL             | I <sup>2</sup> Cクロック入力                                                                                                                                                                                  |

| D4     | SYNC            | 外部クロック同期入力。SYNCを13MHz、19.2MHz、または26MHzのシステムクロックに接続します。I <sup>2</sup> C設定に応じて、DC-DCレギュレータをこの外部クロックと同期させることができます。表8を参照してください。SYNCはプルダウンを内蔵していません。使用しない場合は、SYNCをAGNDに接続します。                                |

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

MAX8952

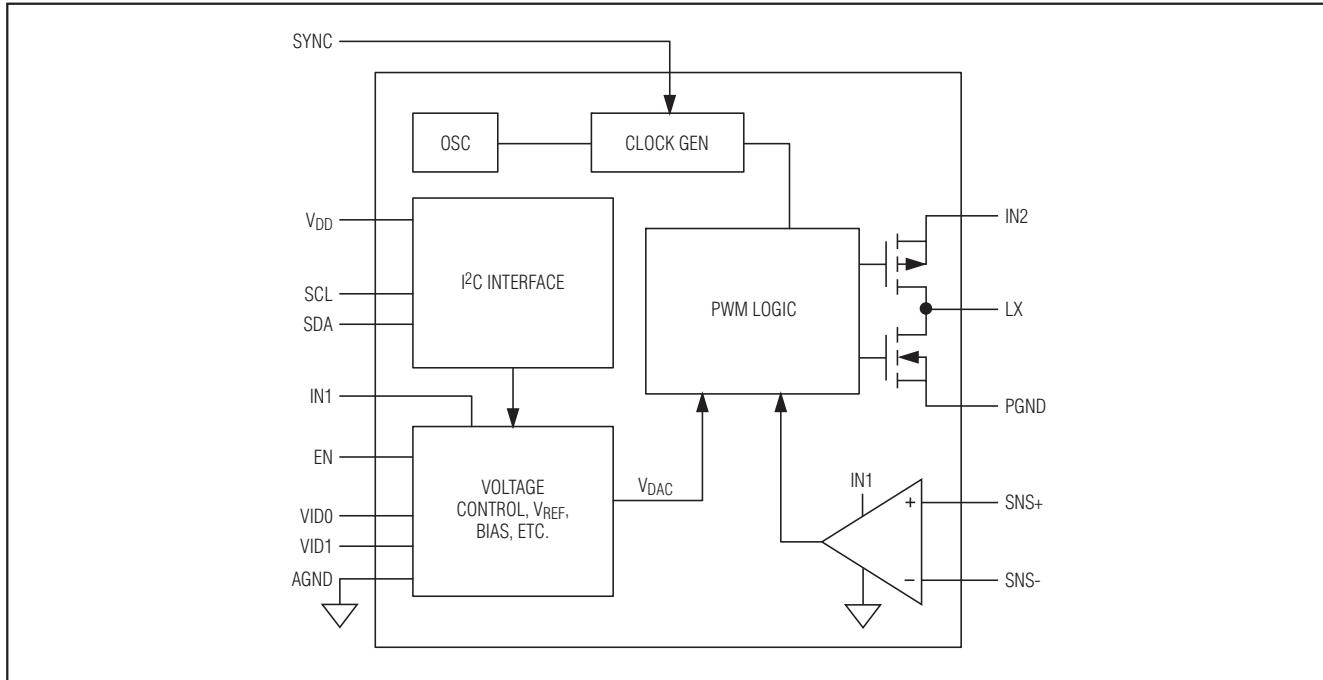

図1. ブロック図

## 詳細

高効率の3.25MHzステップダウンスイッチングレギュレータのMAX8952は、最大2.5Aの出力電流を供給します。このデバイスは、2.5V~5.5Vの入力電圧範囲で動作し、出力電圧は、10mVステップで0.77V~1.40VにI<sup>2</sup>Cでプログラム可能です。完全差動リモート検出が、負荷において高精度DCレギュレーションを確保しています。総出力誤差は、全負荷、ライン、および温度範囲で±1.5%以下となります。

## ダイナミック電圧スケーリング

出力電圧は、VID0およびVID1ロジック入力の使用によってダイナミックに調整されるため、4つのプリ設定された動作モード/電圧構成から選択が可能です。

それぞれの異なった出力モードに対し、以下のパラメータがプログラム可能です。

- 出力電圧：0.77V~1.40V、10mVステップ

- 動作モード：強制PWMまたは省電力

- 外部クロックソースとスイッチング周波数の同期イネーブル/ディセーブル

表1に、VID0/VID1と動作モードの関係が示されています。

VID\_入力は、プルダウン抵抗を内蔵しています。これらのプルダウン抵抗は、このICがイネーブルされた後にCONTROLレジスタを通じてディセーブルすることができ、最小可能な自己消費電流を達成します。ENがローのとき、CONTROLレジスタはデフォルトにリセットされ、プルダウン抵抗をイネーブルします。

表1. VID0およびVID1構成

| VID1 | VID0 | MODE  | I <sup>2</sup> C REGISTER | DEFAULT SWITCHING MODE | DEFAULT SYNCHRONIZATION | DEFAULT OUTPUT VOLTAGE (V) |

|------|------|-------|---------------------------|------------------------|-------------------------|----------------------------|

| 0    | 0    | MODE0 | Table 3                   | POWER SAVE             | OFF                     | 1.40                       |

| 0    | 1    | MODE1 | Table 4                   | POWER SAVE             | OFF                     | 1.00                       |

| 1    | 0    | MODE2 | Table 5                   | POWER SAVE             | OFF                     | 1.40                       |

| 1    | 1    | MODE3 | Table 6                   | POWER SAVE             | OFF                     | 1.10                       |

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

## イネーブル

DC-DCステップダウンレギュレータのMAX8952は、ENロジック入力を使用してイネーブル/ディセーブルされます。EN入力は、 $V_{IN1}$ までの入力電圧を処理することができ、ENロジック入力が多種多様な信号/電源によって制御可能なことを保証します。

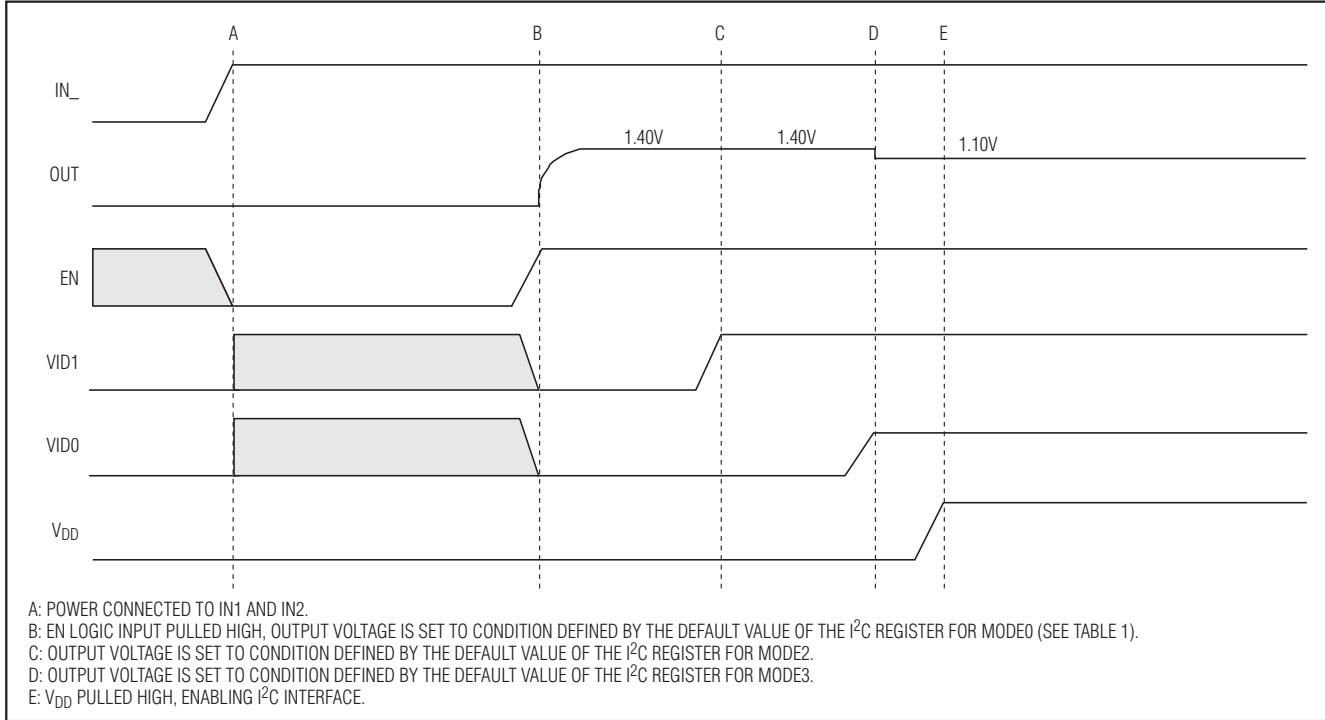

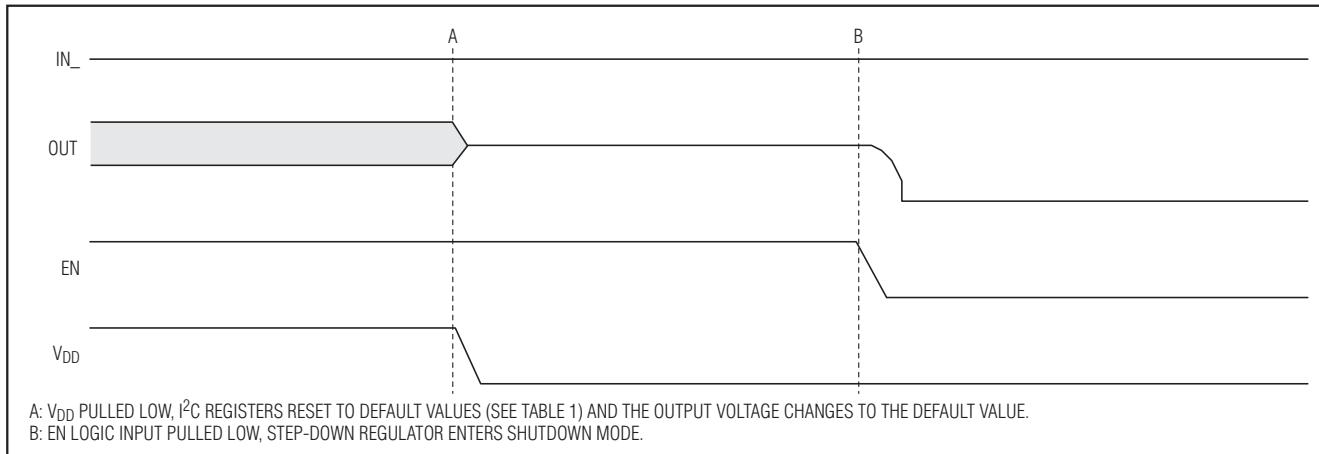

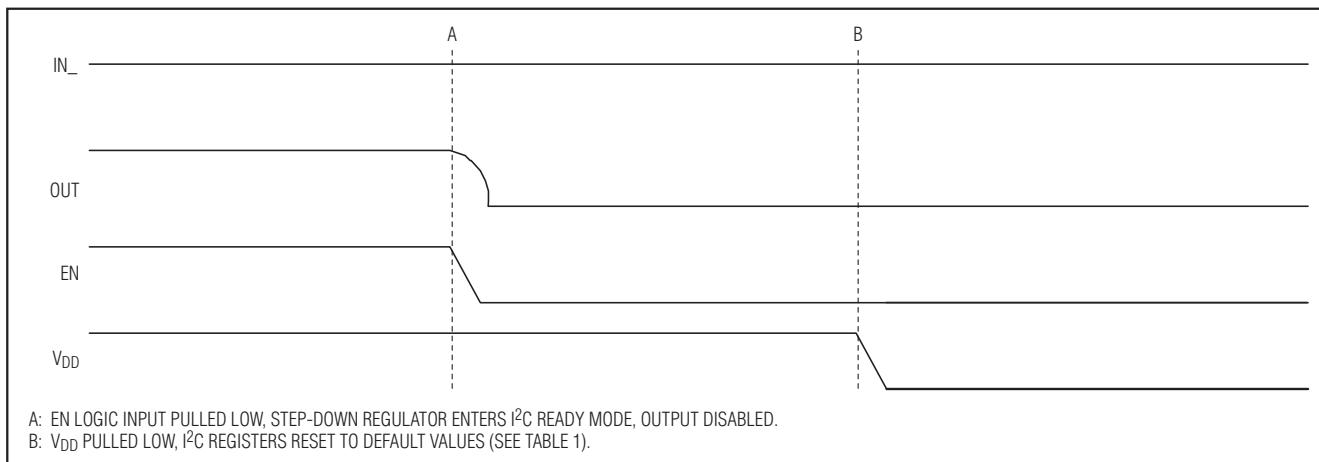

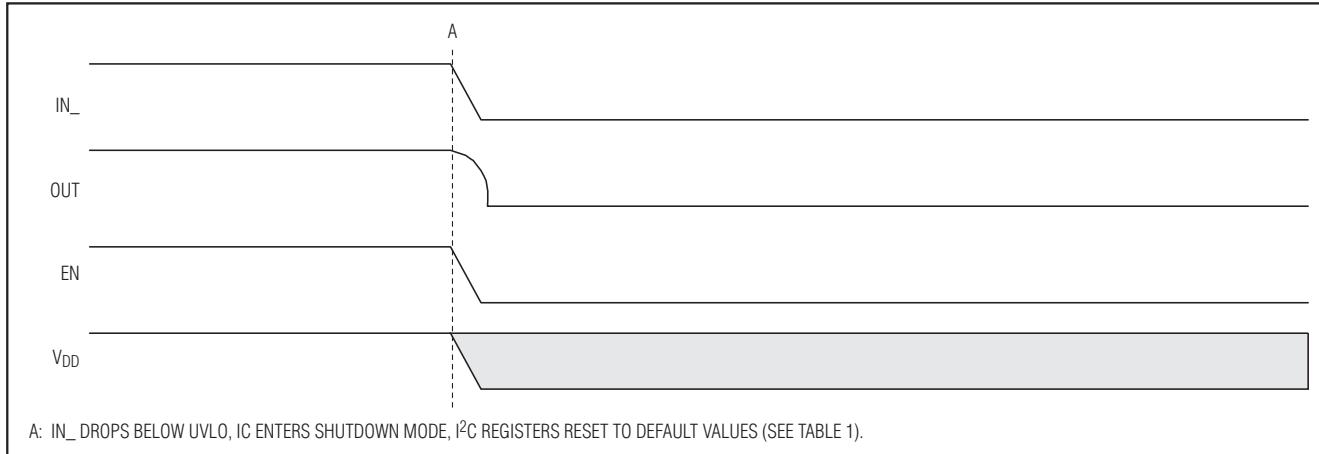

EN入力は、プルダウン抵抗を内蔵しており、オフ状態時にENが放電されるように保証します。このプルダウン抵抗は、このICがイネーブルされた後にCONTROLレジスタ(表7を参照)を通じてディセーブルすることができ、最小可能な自己消費電流を達成します。ENがローのとき、CONTROLレジスタはデフォルトにリセットされ、EN、VID0、およびVID1のプルダウン抵抗をイネーブルします。パワーアップおよびパワーダウンシーケンスと動作モード変更の詳細については、図2と図3を参照してください。

## DC-DCレギュレータの動作モード

このICは、VID\_入力の状態によって決定される4モードのいずれかで動作します(表1を参照)。パワーアップ時、このICはMODE0～MODE3の場合に省電力動作で動作するように設定されます。各動作モードにおいて、このDC-DCステップダウンレギュレータは、省電力モードまたは強制PWMモードのいずれかの動作を設定することができます。これは、MODE\_レジスタに書き込むことによって行われます(表3～表6を参照)。動作モードは、いつでも変更することができます。

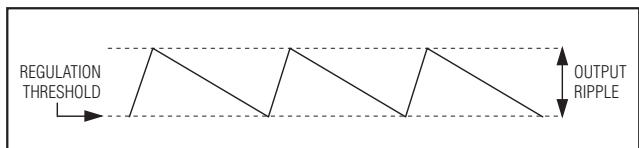

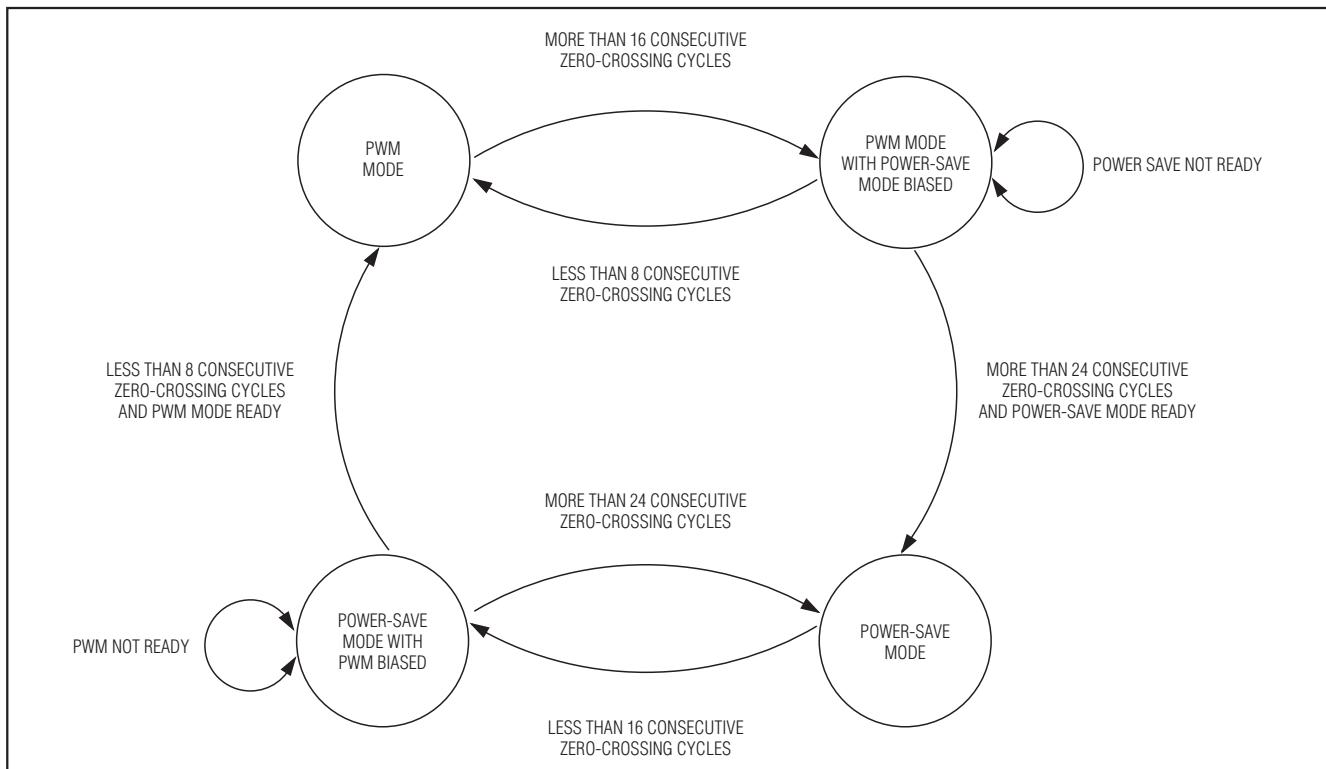

省電力モードでは、MAX8952のPWMスイッチング周波数は負荷電流によって決まります。中負荷から重負荷状態の場合、このICは固定周波数PWMモードで動作します。軽負荷状態の場合、このICはヒステリシスモードで動作します。独自のヒステリシスPWM制御方式によって、高効率、高速スイッチング、および高速過渡応答が保証されます。この制御方式は単純です。すなわち、出力電圧がレギュレーションスレッショルドより低下すると、エラーコンバレータがハイサイドスイッチをオンにすることによって、スイッチングサイクルを開始します。このスイッチは、最小オン時間が満了して、出力電圧がレギュレーションスレッショルド + ヒステリシスを超えるか、あるいはインダクタ電流が電流制限スレッショルドを超えるまでオンに維持されます。オフになると、ハイサイドスイッチは、最小オフ時間が満了して、出力電圧が再びレギュレーションスレッショルドより低下するまでオフに維持されます。オフ期間では、ローサイド同期整流器はオンになり、ハイサイドスイッチが再びオンになるか、あるいはインダクタ電流がゼロに近づくまでオンに維持されます。内蔵同期整流器によって、外付けのショットキーダイオードが不要です。PWMとヒステリシス動作の間の遷移は、連続ゼロクロスサイクルの数に基づいています。16回を超える連続ゼロクロスサイクルが検出されると、DC-DCステップダウンコンバータは、ヒステリシス動作のバイアスをイネーブルします。正常にバイアスされ、連続ゼロクロスサイクルの数が24回を超えると、DC-DCステップダウンコンバータはヒステリシス動作を開始します。

図2. パワーアップシーケンス

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

MAX8952

図3a. シャットダウン：EN前にV<sub>DD</sub>をローにプル

図3b. シャットダウン：V<sub>DD</sub>前にENをローにプル

図3c. シャットダウン：IN1の低電圧ロックアウト

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

ヒステリシス動作時、バーレレギュレーションの使用に起因するサイレントDCオフセットが生じます。図4を参照してください。

省電力モードで動作し、連続ゼロクロスサイクルの数が16回を超えないように負荷電流が増大すると、PWMモードはバイアスされます。完全にバイアスされて、ゼロクロスサイクルの数が8回より低下すると、DC-DCコンバータはPWM動作を開始します。負荷電流の増加とDC-DCコンバータのPWM開始の間には遅延があるため、コンバータは、ヒステリシス動作時の出力におけるフル電流をサポートしています。詳細な状態図については、図5を参照してください。

省電力動作は、ヒステリシスモードに変更して、負荷状態に応じてスイッチング周波数を下げることによって、軽負荷時の効率を向上させることができます。中負荷から重負荷の場合、レギュレータは、強制PWMモードの場合と同様に、固定スイッチング周波数でスイッ

図4. ヒステリシス動作における出力レギュレーション

チングします。省電力モードでは、ヒステリシスモードから固定周波数スイッチングへの遷移は、次式で指定される負荷電流において発生します。

$$I_{OUT} = \frac{V_{IN} - V_{OUT}}{2 \times L} \times \frac{V_{OUT}}{V_{IN} \times f_{OSC}}$$

強制PWMモードでは、レギュレータは、出力負荷に関係なく一定の(3.25MHzまたは外部クロックソースに同期した)スイッチング周波数で動作します。

強制PWMモードは、一定スイッチング周波数の倍数でスイッチング高調波が発生して、容易にフィルタで除去されるため、低ノイズシステムに最適です。ただし、強制PWMモードにおける軽負荷時の消費電力は、省電力モードの場合より大きくなります。

## ソフトスタート

このICは、ソフトスタート回路を内蔵しており、起動時の突入電流を除去し、入力ソースにおける過渡を低減します(「標準動作特性」を参照)。ソフトスタートは特に、Li+ (リチウムイオン)やアルカリセルなどのハイインピーダンス入力ソースの場合に有用です。このICをプリバイアス出力にイネーブルすると、このICは完全なソフトスタートサイクルを実行します。

図5. DC-DCステップダウンコンバータのモード変更

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

MAX8952

## 同期整流

内蔵のnチャネル同期整流器によって、外付けのショットキーダイオードが不要になり、効率が向上します。同期整流器は、各スイッチングサイクルの後半(オフ時間)中にオンになります。この期間に、インダクタの電圧は反転し、インダクタ電流は徐々に下降します。PWMモードでは、同期整流器はスイッチングサイクルの終了時にオフになります。省電力モードでは、同期整流器は、インダクタ電流が50mA (typ)よりも低下するかスイッチングサイクルの終了のいずれかが先に発生するとオフになります。

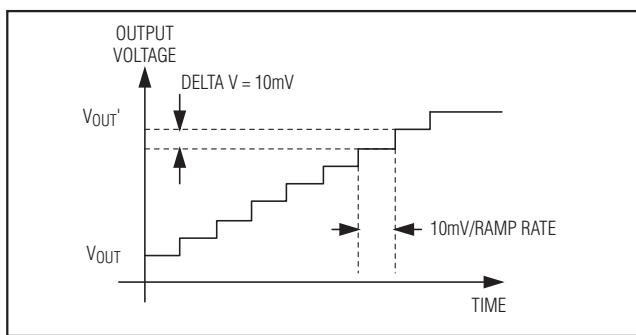

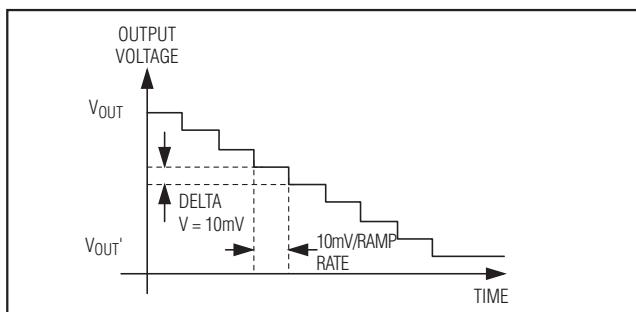

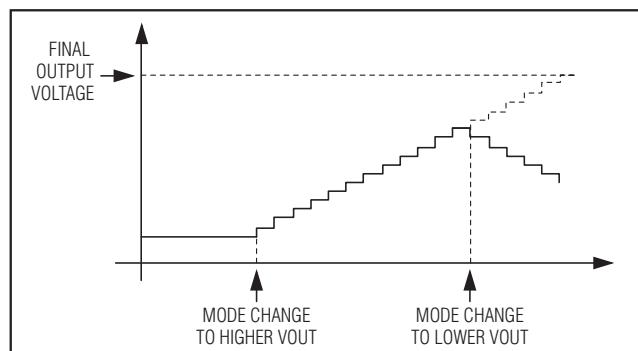

## ランプレート制御

MAX8952の出力電圧は、アクティブに制御される可変ランプレートを備えており、I<sup>2</sup>Cインターフェースで設定されます(図6、図7、および図8を参照)。RAMPレジスタに設定された値は、出力電圧のランプレートを制御します。RAMP\_DOWNビットは、省電力モードにおけるアクティブなランプダウン動作を制御します。レギュレータが省電力モードに設定され、RAMP\_DOWNビットがクリアされると、ランプダウンはアクティブに制御されず、レギュレータの出力電圧は、出力容量と外部負荷によって決定されるレートで下降します。負荷が小さい場合、出力電圧の減衰はRAMPで指定された値

図6. ランプアップ関数

図7. ランプダウン関数

より遅くなります。負荷が大きい場合、出力電圧の減衰はRAMPで指定された値以上に速くなりません。RAMP\_DOWNビットが省電力モードで設定されると、ゼロクロスコンパレータはランプダウン状態の間ディセーブルされます。アクティブランプダウン機能は、強制PWM動作に本質的に備わっています。

次式のように、ランプレートの最大および最小値を計算します。

$$t_{RAMP\_MIN} = \frac{V_{OUT\_LSB}}{t_{CLK\_MAX}} \times \frac{1}{2^{RAMP\_CODE}}$$

$$t_{RAMP\_MAX} = \frac{V_{OUT\_LSB}}{t_{CLK\_MIN}} \times \frac{1}{2^{RAMP\_CODE}}$$

ここで

$$V_{OUT\_LSB} = 10mV$$

$$t_{CLK\_MAX} = \frac{1}{f_{SW\_MIN}}$$

$$t_{CLK\_MIN} = \frac{1}{f_{SW\_MAX}}$$

$$f_{SW} = 3.25MHz \pm 10\% \text{ (PWM動作の場合)}$$

$$f_{SW} = 3.25MHz \pm 25\% \text{ (ヒステリシス動作の場合)}$$

$$f_{SYNC} = \frac{f_{SYNC}}{n}$$

$$f_{SYNC} = \text{外部クロックの周波数}$$

$n = 4$  (13MHzの場合)、 $6$  (19.2MHzの場合)、および $8$  (26MHzの場合)

RAMP\_CODE = RAMP[2:0]レジスタの値(表9を参照)

## 熱過負荷保護

熱過負荷保護は、このICの総消費電力を制限します。内蔵の熱センサーが+160°C (typ)を超えるダイ温度を検出すると、DC-DCステップダウンレギュレータは

図8. 最終値に達する前のモード変更

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

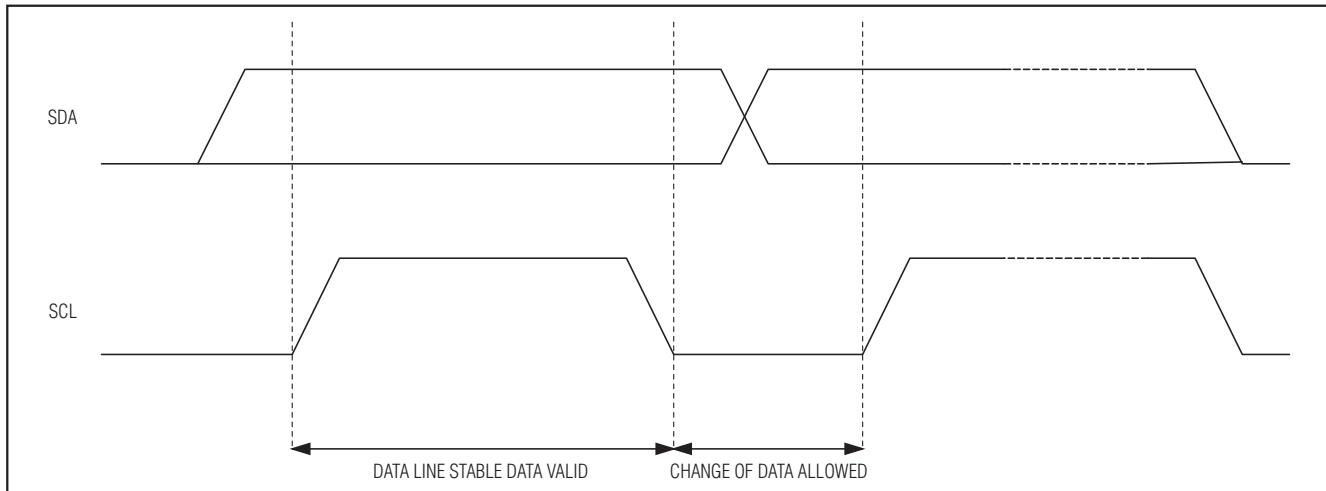

図9. I<sup>2</sup>Cビット転送

シャットダウンされ、ICは冷却されます。DC-DCステップダウンレギュレータは、ジャンクションが20°C (typ)冷却されると、再びオンになるため、連続的な熱過負荷状態中ではパルス出力になります。

熱過負荷時、I<sup>2</sup>Cインターフェースは、アクティブのままになります、すべてのレジスタ値が維持されます。

## I<sup>2</sup>Cインターフェース

I<sup>2</sup>C対応の2線式シリアルインターフェースは、ステップダウンコンバータの出力電圧、ランプレート、動作モード、および同期を制御します。シリアルバスは、双方向シリアルデータライン(SDA)とシリアルクロック入力(SCL)で構成されます。マスターは、バス上でデータ転送を開始し、データ転送を許可するSCLを生成します。I<sup>2</sup>Cはオープンドレインバスです。SDAとSCLには、プルアップ抵抗(500Ω以上)が必要です。SDAおよびSCLと直列のオプション(24Ω)は、バスライン上の高電圧スパイクからデバイス入力を保護します。また、直列抵抗は、バス信号上のクロストークやアンダーシュートを最小限に抑えます。

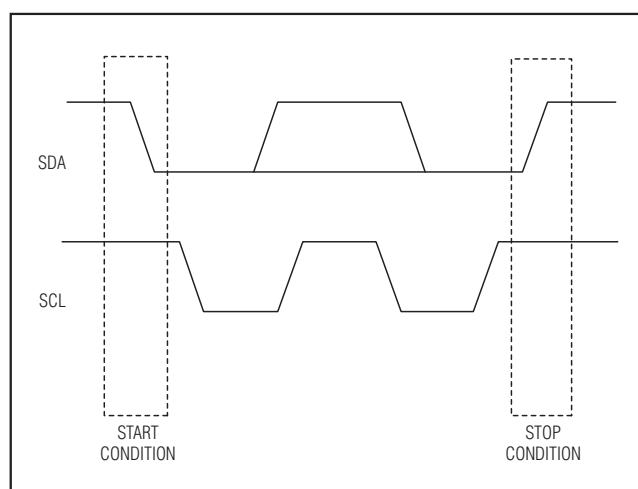

## ビット転送

各SCLクロックサイクルの間に1データビットが転送されます。SDAのデータは、SCLクロックパルスがハイの間は安定に維持される必要があります(図9を参照)。SCLがハイの間のSDAの変化は制御信号です(詳細については「STARTおよびSTOP条件」の項を参照)。

各送信シーケンスは、START (S)条件とSTOP (P)条件によってフレーム設定されます。各データパケットは9ビット長です。すなわち、8ビットのデータの後に

アクノリッジビットが続きます。このICは、最大400kHzのSCL周波数でのデータ転送速度をサポートしています。

## STARTおよびSTOP条件

シリアルインターフェースが非アクティブのとき、SDAとSCLはアイドルハイです。マスターは、START条件を発行することによって、通信を開始します。START条件は、SCLがハイの間に、SDAをハイからローに遷移させます。STOP条件は、SCLがハイの間に、SDAをローからハイに遷移させます(図10)。

マスターからのSTART条件は、このICへの送信の開始を知らせます。マスターは、非アクノリッジとその後にSTOP条件を発行することによって、送信を終了します(詳細については「アクノリッジ」の項を参照)。STOP条件はバスを解放します。一連のコマンドをスレーブに発行

図10. I<sup>2</sup>C STARTおよびSTOP条件

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

MAX8952

図11. I<sup>2</sup>Cマスター/スレーブ構成

する場合、マスターは、バスの制御を維持するためにSTOPコマンドの代りにREPEATED START (Sr)コマンドを発行することができます。一般的に、REPEATED STARTコマンドは機能的に通常のSTARTコマンドと同じです。

STOP条件または不正なアドレスが検出されると、このICは、次のSTART条件まで、内部でSCLをシリアルインターフェースから切断し、デジタルノイズとフィードスルーを最小限に抑えます。

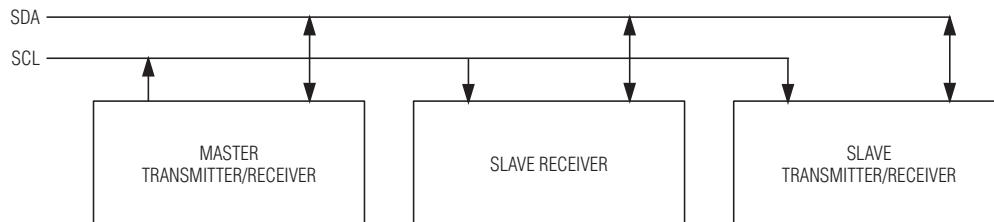

## システム構成

メッセージを生成するI<sup>2</sup>Cバス上のデバイスはトランスマッタと呼ばれ、メッセージを受け取るデバイスはレシーバと呼ばれます。メッセージを制御するデバイスはマスターで、マスターによって制御されるデバイスはスレーブと呼ばれます。図11を参照してください。

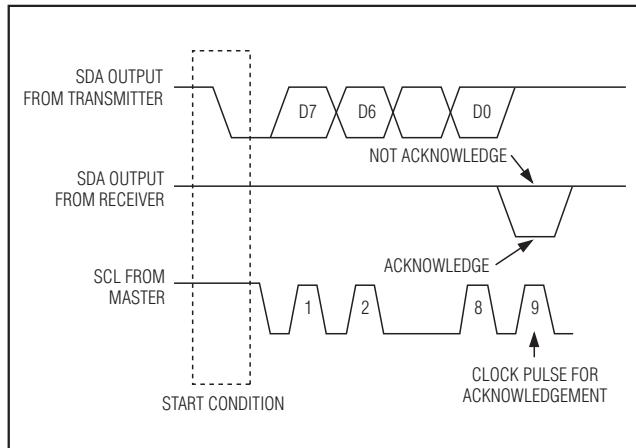

## アクノリッジ

トランスマッタとレシーバのSTART条件とSTOP条件の間のデータバイトの数は無制限です。各8ビットバイトの後に、1ビットのアクノリッジビットが続きます。アクノリッジビットは、マスターが特別なアクノリッジに関係したクロックパルスを生成する間レシーバによってSDA上に置かれるローレベル信号です。アドレス指定されたスレーブレシーバは、自身が受け取る各バイトの後にアクノリッジを生成する必要があります。また、マスター-レシーバは、自身が受け取るスレーブトランスマッタからクロック出力された各バイトの後にアクノリッジを生成する必要があります。図12を参照してください。

アクノリッジするデバイスは、アクノリッジクロックパルスのハイ期間の間SDAラインが安定したローになるように、アクノリッジクロックパルスの間SDAラインをプルダウンする必要があります(セットアップおよび

図12. I<sup>2</sup>Cアクノリッジ

ホールド時間も一致する必要があります)。マスター-レシーバは、スレーブからクロック出力された最後のバイトにアクノリッジビットを生成しないことによって、トランスマッタにデータの最後であることを知らせる必要があります。この場合、トランスマッタは、マスターがSTOP条件を生成することができるよう、SDAをハイに維持する必要があります。

## レジスタリセット

I<sup>2</sup>Cレジスタは、IN1またはV<sub>DD</sub>の電圧が対応するUVLOスレッショルドよりも下降するとデフォルト値にリセットされます(「Electrical Characteristics (電気的特性)」の表を参照)。

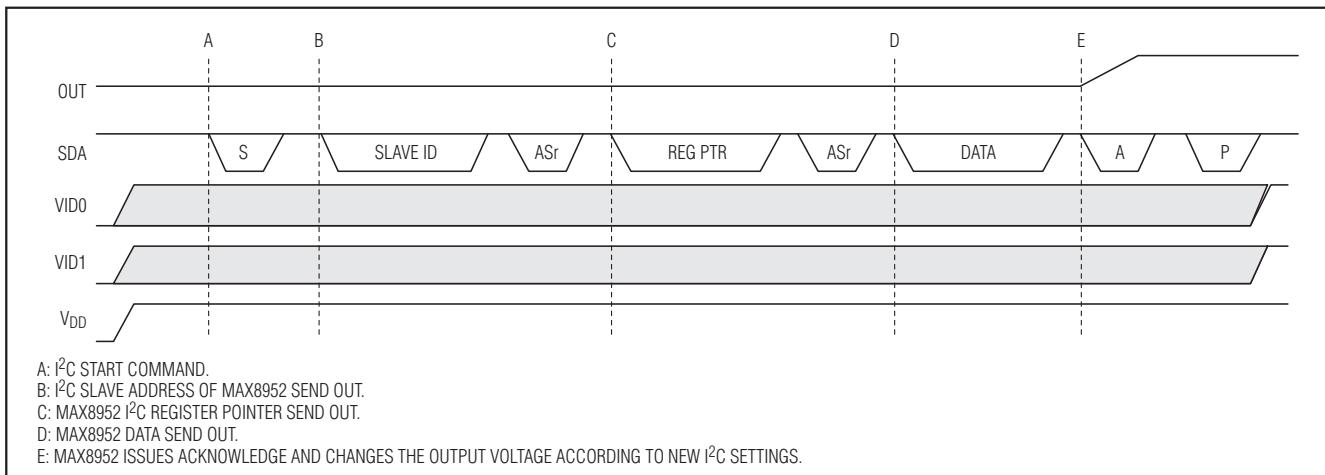

## 出力動作モードの更新

このICが現在動作しているモードの出力電圧またはOperation Modeレジスタを更新する場合、出力電圧/動作モードは、このICがI<sup>2</sup>Cデータバイトに対するアクノリッジを送出すると同時に更新されます(図13を参照)。

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

図13. 出力動作の更新

## スレーブアドレス

バスマスターは、START条件とその後にスレーブアドレスを続けて発行することによって、スレーブデバイス(MAX8952)との通信を開始します。スレーブアドレスバイトは、7つのアドレスビット(1100 000x)およびread/writeビット(R/W)で構成されます。適正なアドレスを受け取った後、このICは9番目のクロックサイクルの間SDAをローにプルすることによってアクノリッジを発行します。

他のスレーブアドレスを割り当てることができます。詳細については、お問い合わせください。

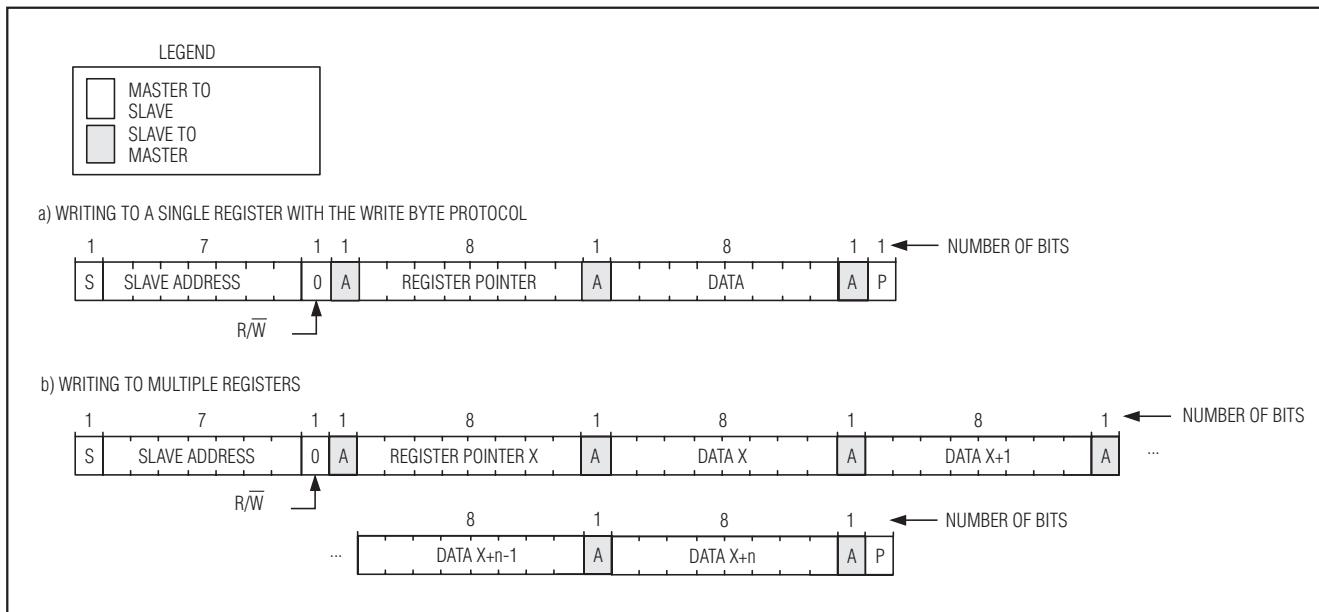

## 書き込み動作

このICは、図14aと図14bに示すようなSMBus<sup>TM</sup>規格に定義されたwrite byteプロトコルを認識します。write byteプロトコルによって、I<sup>2</sup>Cマスターデバイスは、1バイトのデータをスレーブデバイスに送出することができます。write byteプロトコルには、後続の書き込みのためにレジスタポインタアドレスが必要です。このICは、これらのレジスタのサブセットのみがデバイスに実際に存在する場合でも、すべてのレジスタポインタをアクノリッジします。write byteプロトコルは次のようにになります。

- 1) マスターが、STARTコマンドを送出します。

- 2) マスターが、7ビットのスレーブアドレスと1ビットのwriteビットを送出します。

- 3) アドレス指定されたスレーブが、SDAをローにプルしてアクノリッジをアサートします。

- 4) マスターが、8ビットのレジスタポインタを送出します。

- 5) スレーブが、レジスタポインタをアクノリッジします。

SMBusはIntel Corp.の商標です。

- 6) マスターが、データバイトを送出します。

- 7) スレーブが、データバイトをアクノリッジします。

- 8) スレーブが、新しいデータで更新します。

- 9) マスターが、STOP条件を送出します。

write byteプロトコルに加え、このICは、図14bに示すように、複数のレジスタに書き込むことができます。このプロトコルによって、I<sup>2</sup>Cマスターデバイスはスレーブを1回だけアドレス指定し、データをレジスタポインタで指定されたレジスタで始まる連続した1ブロックに送出することができます。

連続した1ブロックのレジスタに書き込むには、次の手順を使用します。

- 1) マスターが、STARTコマンドを送出します。

- 2) マスターが、7ビットのスレーブアドレスと1ビットのwriteビットを送出します。

- 3) アドレス指定されたスレーブが、SDAをローにプルしてアクノリッジをアサートします。

- 4) マスターが、書き込み先の先頭レジスタの8ビットのレジスタポインタを送出します。

- 5) スレーブが、レジスタポインタをアクノリッジします。

- 6) マスターが、データバイトを送出します。

- 7) スレーブが、データバイトをアクノリッジします。

- 8) スレーブが、新しいデータで更新します。

- 9) ブロック内のレジスタの数だけ、手順6～手順8が繰り返されます。レジスタポインタは毎回自動インクリメントされます。

- 10) マスターが、STOP条件を送出します。

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

MAX8952

図14aおよび14b. このICへの書き込み

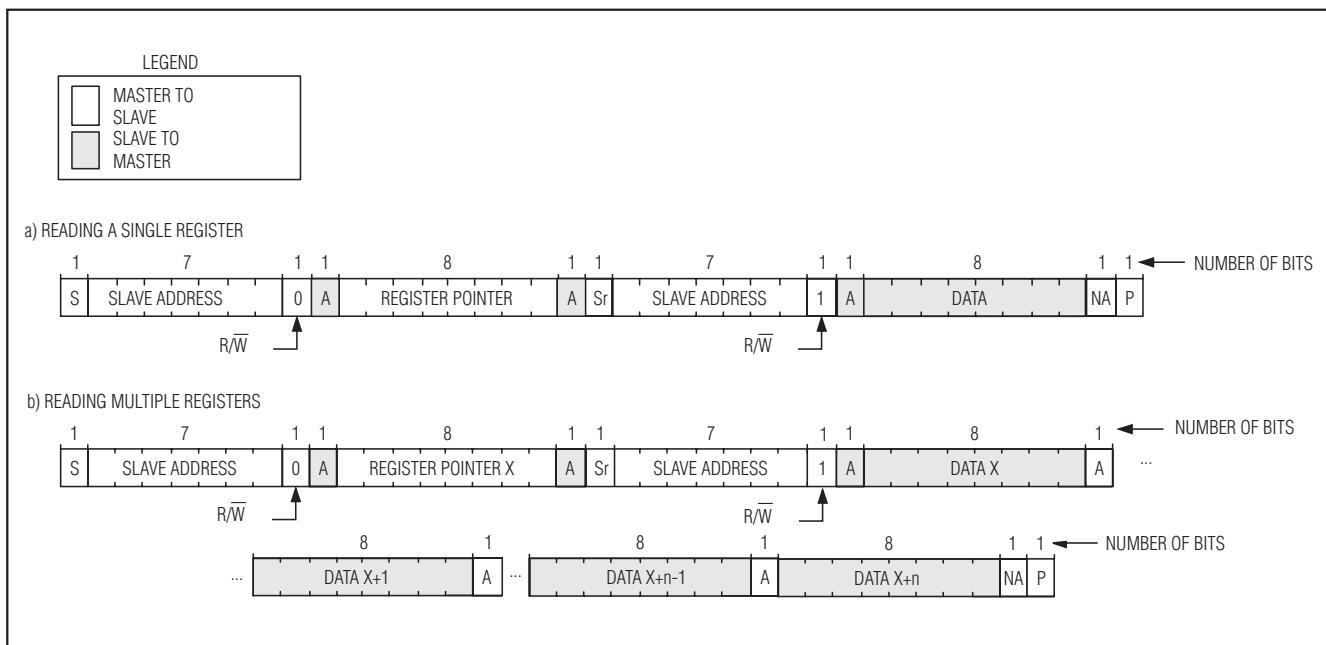

## 読み取り動作

単一レジスタ(バイト)を読み取る方法は、図15aに示されています。単一のレジスタを読み取るには、次の手順に従います。

- 1) マスターが、STARTコマンドを送出します。

- 2) マスターが、7ビットのスレーブアドレスと1ビットのwriteビットを送出します。

- 3) アドレス指定されたスレーブが、SDAをローにプルしてアクリティブをアサートします。

- 4) マスターが、ブロック内の先頭レジスタの8ビットレジスタポインタを送出します。

- 5) スレーブが、レジスタポインタをアクリティブします。

- 6) マスターが、REPEATED START条件を送出します。

- 7) マスターが、7ビットのスレーブアドレスと1ビットのreadビットを送出します。

- 8) スレーブが、SDAをローにプルしてアクリティブをアサートします。

- 9) スレーブが、8ビットデータ(レジスタの内容)を送出します。

- 10) マスターが、SDAをハイに維持して非アクリティブをアサートします。

- 11) マスターが、STOP条件を送出します。

さらに、このICは、図15bに示すように、1ブロックの連続した複数のレジスタを読み取ることができます。1ブロックの連続した複数のレジスタを読み取るには、次の手順を使用します。

- 1) マスターが、STARTコマンドを送出します。

- 2) マスターが、7ビットのスレーブアドレスと1ビットのwriteビットを送出します。

- 3) アドレス指定されたスレーブが、SDAをローにプルしてアクリティブをアサートします。

- 4) マスターが、ブロック内の先頭レジスタの8ビットレジスタポインタを送出します。

- 5) スレーブが、レジスタポインタをアクリティブします。

- 6) マスターが、REPEATED START条件を送出します。

- 7) マスターが、7ビットのスレーブアドレスと1ビットのreadビットを送出します。

- 8) スレーブが、SDAをローにプルしてアクリティブをアサートします。

- 9) スレーブが、8ビットデータ(レジスタの内容)を送出します。

- 10) マスターが、さらに読み取りデータがある場合は、SDAをローにプルしてアクリティブをアサートします。すべてのデータが読み取られた場合は、SDAをハイに維持して非アクリティブをアサートします。

- 11) ブロック内のレジスタの数だけ、手順9と手順10が繰り返されます。レジスタポインタは毎回自動インクリメントされます。

- 12) マスターが、STOP条件を送出します。

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

図15aおよび15b. このICからの読み取り

図16. I2Cタイミング図

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

MAX8952

表2. I<sup>2</sup>Cレジスタマップ

| POINTER | REGISTER | POR  | BIT7          | BIT6      | BIT5            | BIT4      | BIT3          | BIT2 | BIT1      | BIT0 |

|---------|----------|------|---------------|-----------|-----------------|-----------|---------------|------|-----------|------|

| 0x00    | MODE0    | 0x3F | OPER MODE     | SYNC MODE | VOUT MODE0[5:0] |           |               |      |           |      |

| 0x01    | MODE1    | 0x17 | OPER MODE     | SYNC MODE | VOUT MODE1[5:0] |           |               |      |           |      |

| 0x02    | MODE2    | 0x3F | OPER MODE     | SYNC MODE | VOUT MODE2[5:0] |           |               |      |           |      |

| 0x03    | MODE3    | 0x21 | OPER MODE     | SYNC MODE | VOUT MODE3[5:0] |           |               |      |           |      |

| 0x04    | CONTROL  | 0xE0 | EN_PD         | VID0_PD   | VID1_PD         | —         | —             | —    | —         | —    |

| 0x05    | SYNC     | 0x00 | SYNC[1:0]     |           | —               | —         | —             | —    | —         | —    |

| 0x06    | RAMP     | 0x01 | RAMP[2:0]     |           |                 | FORCE_HYS | FORCE_OSC     | —    | RAMP_DOWN | —    |

| 0x08    | CHIP_ID1 | 0x20 | DIE TYPE[7:4] |           |                 |           | DIE TYPE[3:0] |      |           |      |

| 0x09    | CHIP_ID2 | 0x1A | DASH[3:0]     |           |                 |           | MASK REV[3:0] |      |           |      |

表3. I<sup>2</sup>Cレジスタ : MODE0

このレジスタは、MODE0、VID0 = GND、VID1 = GNDにおける出力電圧と動作モード制御を含んでいます。

| REGISTER NAME    | MODE0                                 |

|------------------|---------------------------------------|

| Address          | 0x00h                                 |

| Reset Value      | 0x3Fh                                 |

| Type             | Read/write                            |

| Special Features | Reset upon V <sub>DD</sub> or IN_UVLO |

| BIT      | NAME           | DESCRIPTION                                                                                                                                                                                                                                                    | DEFAULT VALUE    |

|----------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| B7 (MSB) | FPWM_EN0       | <b>DC-DC Step-Down Converter Operation Mode for MODE0</b><br>0 = DC-DC converter automatically changes between hysteretic mode for light load conditions and PWM mode for medium to heavy load conditions.<br>1 = DC-DC converter operates in forced-PWM mode. | 0                |

| B6       | SYNC_MODE0     | <b>Disable/Enable Synchronization to External Clock</b><br>0 = DC-DC converter ignores the external SYNC input regardless of operation mode.<br>1 = DC-DC converter synchronizes to external SYNC input when available.                                        | 0                |

| B5       | OUT_MODE0[5:0] | <b>Output Voltage Selection for MODE0</b><br>000000 = 0.77V<br>000001 = 0.78V<br>110011 = 1.28V<br>110100 = 1.29V<br>110101 = 1.30V<br>111110 = 1.39V<br>111111 = 1.40V                                                                                        | 111111<br>(1.4V) |

| B4       |                |                                                                                                                                                                                                                                                                |                  |

| B3       |                |                                                                                                                                                                                                                                                                |                  |

| B2       |                |                                                                                                                                                                                                                                                                |                  |

| B1       |                |                                                                                                                                                                                                                                                                |                  |

| B0 (LSB) |                |                                                                                                                                                                                                                                                                |                  |

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

## 表4. I<sup>2</sup>Cレジスタ：MODE1

このレジスタは、MODE1、VID1 = GND、VID0 = V<sub>DD</sub>における出力電圧と動作モード制御を含んでいます。

| REGISTER NAME    | MODE1                                 |

|------------------|---------------------------------------|

| Address          | 0x01h                                 |

| Reset Value      | 0x17h                                 |

| Type             | Read/write                            |

| Special Features | Reset upon V <sub>DD</sub> or IN_UVLO |

| BIT      | NAME           | DESCRIPTION                                                                                                                                                                                                                                                    | DEFAULT VALUE     |

|----------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| B7 (MSB) | FPWM_EN1       | <b>DC-DC Step-Down Converter Operation Mode for MODE1</b><br>0 = DC-DC converter automatically changes between hysteretic mode for light load conditions and PWM mode for medium to heavy load conditions.<br>1 = DC-DC converter operates in forced-PWM mode. | 0                 |

| B6       | SYNC_MODE1     | <b>Disable/Enable Synchronization to External Clock</b><br>0 = DC-DC converter ignores the external SYNC input regardless of operation mode.<br>1 = DC-DC converter synchronizes to external SYNC input when available.                                        | 0                 |

| B5       | OUT_MODE1[5:0] | <b>Output Voltage Selection for MODE1</b><br>000000 = 0.77V<br>000001 = 0.78V<br>010110 = 0.99V<br>010111 = 1.00V<br>011000 = 1.01V<br>111110 = 1.39V<br>111111 = 1.40V                                                                                        | 010111<br>(1.00V) |

| B4       |                |                                                                                                                                                                                                                                                                |                   |

| B3       |                |                                                                                                                                                                                                                                                                |                   |

| B2       |                |                                                                                                                                                                                                                                                                |                   |

| B1       |                |                                                                                                                                                                                                                                                                |                   |

| B0 (LSB) |                |                                                                                                                                                                                                                                                                |                   |

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

MAX8952

## 表5. I<sup>2</sup>Cレジスタ：MODE2

このレジスタは、MODE2、VID1 = V<sub>DD</sub>、VID0 = GNDにおける出力電圧と動作モード制御を含んでいます。

| REGISTER NAME    | MODE2                                 |

|------------------|---------------------------------------|

| Address          | 0x02h                                 |

| Reset Value      | 0x3Fh                                 |

| Type             | Read/write                            |

| Special Features | Reset upon V <sub>DD</sub> or IN_UVLO |

| BIT      | NAME           | DESCRIPTION                                                                                                                                                                                                                                                    | DEFAULT VALUE    |

|----------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| B7 (MSB) | FPWM_EN2       | <b>DC-DC Step-Down Converter Operation Mode for MODE2</b><br>0 = DC-DC converter automatically changes between hysteretic mode for light load conditions and PWM mode for medium to heavy load conditions.<br>1 = DC-DC converter operates in forced-PWM mode. | 0                |

| B6       | SYNC_MODE2     | <b>Disable/Enable Synchronization to External Clock</b><br>0 = DC-DC converter ignores the external SYNC input regardless of operation mode.<br>1 = DC-DC converter synchronizes to external SYNC input when available.                                        | 0                |

| B5       | OUT_MODE2[5:0] | <b>Output Voltage Selection for MODE2</b><br>000000 = 0.77V<br>000001 = 0.78V<br>110011 = 1.28V<br>110100 = 1.29V<br>110101 = 1.30V<br>111110 = 1.39V<br>111111 = 1.40V                                                                                        | 111111<br>(1.4V) |

| B4       |                |                                                                                                                                                                                                                                                                |                  |

| B3       |                |                                                                                                                                                                                                                                                                |                  |

| B2       |                |                                                                                                                                                                                                                                                                |                  |

| B1       |                |                                                                                                                                                                                                                                                                |                  |

| B0 (LSB) |                |                                                                                                                                                                                                                                                                |                  |

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

## 表6. I<sup>2</sup>Cレジスタ：MODE3

このレジスタは、MODE3、VID1 = V<sub>DD</sub>、VID0 = V<sub>DD</sub>における出力電圧と動作モード制御を含んでいます。

| REGISTER NAME    | MODE3                                 |

|------------------|---------------------------------------|

| Address          | 0x03h                                 |

| Reset Value      | 0x21h                                 |

| Type             | Read/write                            |

| Special Features | Reset upon V <sub>DD</sub> or IN_UVLO |

| BIT      | NAME           | DESCRIPTION                                                                                                                                                                                                                                                    | DEFAULT VALUE |

|----------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| B7 (MSB) | FPWM_EN3       | <b>DC-DC Step-Down Converter Operation Mode for MODE3</b><br>0 = DC-DC converter automatically changes between hysteretic mode for light load conditions and PWM mode for medium to heavy load conditions.<br>1 = DC-DC converter operates in forced-PWM mode. | 0             |

| B6       | SYNC_MODE3     | <b>Disable/Enable Synchronization to External Clock</b><br>0 = DC-DC converter ignores the external SYNC input regardless of operation mode.<br>1 = DC-DC converter synchronizes to external SYNC input when available.                                        | 0             |

| B5       | OUT_MODE3[5:0] | <b>Output Voltage Selection for MODE3</b><br>000000 = 0.77V<br>000001 = 0.78V<br>100000 = 1.09V<br>100001 = 1.10V<br>100010 = 1.11V<br>111110 = 1.39V<br>111111 = 1.40V                                                                                        | 100001        |

| B4       |                |                                                                                                                                                                                                                                                                |               |

| B3       |                |                                                                                                                                                                                                                                                                |               |

| B2       |                |                                                                                                                                                                                                                                                                |               |

| B1       |                |                                                                                                                                                                                                                                                                |               |

| B0 (LSB) |                |                                                                                                                                                                                                                                                                |               |

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

MAX8952

## 表7. I<sup>2</sup>Cレジスタ : CONTROL

このレジスタは、プルダウン抵抗をイネーブルまたはディセーブルします。

| REGISTER NAME    | CONTROL                                               |

|------------------|-------------------------------------------------------|

| Address          | 0x04h                                                 |

| Reset Value      | 0xE0h                                                 |

| Type             | Read/write                                            |

| Special Features | Reset upon V <sub>DD</sub> , IN_UVLO or EN pulled low |

| BIT      | NAME    | DESCRIPTION                                                                       | DEFAULT VALUE |

|----------|---------|-----------------------------------------------------------------------------------|---------------|

| B7 (MSB) | EN_PD   | 0 = Pulldown on EN input is disabled.<br>1 = Pulldown on EN input is enabled.     | 1             |

| B6       | VID0_PD | 0 = Pulldown on VID0 input is disabled.<br>1 = Pulldown on VID0 input is enabled. | 1             |

| B5       | VID1_PD | 0 = Pulldown on VID1 input is disabled.<br>1 = Pulldown on VID1 input is enabled. | 1             |

| B4       | —       | Reserved for future use.                                                          | 0             |

| B3       | —       | Reserved for future use.                                                          | 0             |

| B2       | —       | Reserved for future use.                                                          | 0             |

| B1       | —       | Reserved for future use.                                                          | 0             |

| B0 (LSB) | —       | Reserved for future use.                                                          | 0             |

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

## 表8. I<sup>2</sup>Cレジスタ：SYNC

このレジスタは、外部クロックソースのクロック周波数を指定します。

| REGISTER NAME    | SYNC                                  |

|------------------|---------------------------------------|

| Address          | 0x05h                                 |

| Reset Value      | 0x00h                                 |

| Type             | Read                                  |

| Special Features | Reset upon V <sub>DD</sub> or IN_UVLO |

| BIT      | NAME      | DESCRIPTION                                                                                                                     | DEFAULT VALUE |

|----------|-----------|---------------------------------------------------------------------------------------------------------------------------------|---------------|

| B7 (MSB) | SYNC[1:0] | <b>Sets Clock Frequency of External Clock Present on SYNC Input</b><br>00 = 26MHz<br>01 = 13MHz<br>10 = 19.2MHz<br>11 = 19.2MHz | 00            |

| B6       |           |                                                                                                                                 |               |

| B5       | —         | Reserved for future use.                                                                                                        | 0             |

| B4       | —         | Reserved for future use.                                                                                                        | 0             |

| B3       | —         | Reserved for future use.                                                                                                        | 0             |

| B2       | —         | Reserved for future use.                                                                                                        | 0             |

| B1       | —         | Reserved for future use.                                                                                                        | 0             |

| B0 (LSB) | —         | Reserved for future use.                                                                                                        | 0             |

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

MAX8952

表9. I<sup>2</sup>Cレジスタ：RAMP

このレジスタは、ramp up/down関数を制御します。

| REGISTER NAME    | RAMP                                  |

|------------------|---------------------------------------|

| Address          | 0x06h                                 |

| Reset Value      | 0x01h                                 |

| Type             | Read                                  |

| Special Features | Reset upon V <sub>DD</sub> or IN_UVLO |

| BIT      | NAME      | DESCRIPTION                                                                                                                                                                                                                                                                                                    | DEFAULT VALUE |

|----------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| B7 (MSB) | RAMP[2:0] | <b>Control the RAMP Timing</b><br>000 = 32mV/μs<br>001 = 16mV/μs<br>010 = 8mV/μs<br>011 = 4mV/μs<br>100 = 2mV/μs<br>101 = 1mV/μs<br>110 = 0.5mV/μs<br>111 = 0.25mV/μs                                                                                                                                          | 000           |

| B6       |           |                                                                                                                                                                                                                                                                                                                |               |

| B5       |           |                                                                                                                                                                                                                                                                                                                |               |

| B4       | FORCE_HYS | <b>Only Valid When Converter is Operating with FPWM_EN_ = 0</b><br>0 = Automatically change between power-save mode and PWM mode, depending on load current.<br>1 = Converter always operates in power-save mode regardless of load current as long as FPWM_EN_ = 0. If FPWM_EN_ = 1, this setting is ignored. | 0             |

| B3       | FORCE_OSC | <b>Force Oscillator While Running in Hysteretic Mode</b><br>0 = Internal oscillator is disabled in power save when operating in hysteretic mode.<br>1 = Internal oscillator is enabled in power save even when operating in hysteretic mode.                                                                   | 0             |

| B2       | —         | Reserved for future use.                                                                                                                                                                                                                                                                                       | 0             |

| B1       | RAMP_DOWN | <b>Active Ramp-Down Control for Power-Save Mode</b><br>0 = Active ramp disabled for power-save mode.<br>1 = During ramp-down, the zero-crossing detector is disabled allowing negative current to flow through the nMOS device.                                                                                | 0             |

| B0 (LSB) | —         | Reserved for future use.                                                                                                                                                                                                                                                                                       | 1             |

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

**表10. I<sup>2</sup>Cレジスタ : CHIP\_ID1**

このレジスタは、ダイの型式番号(20)を含んでいます。

| REGISTER NAME    | CHIP_ID1 |

|------------------|----------|

| Address          | 0x08h    |

| Reset Value      | 0x20h    |

| Type             | Read     |

| Special Features | —        |

| BIT      | NAME          | DESCRIPTION       | DEFAULT VALUE |

|----------|---------------|-------------------|---------------|

| B7 (MSB) | DIE_TYPE[7:4] | BCD character (2) | 0010          |

| B6       |               |                   |               |

| B5       |               |                   |               |

| B4       |               |                   |               |

| B3       | DIE_TYPE[3:0] | BCD character (0) | 0000          |

| B2       |               |                   |               |

| B1       |               |                   |               |

| B0 (LSB) |               |                   |               |

**表11. I<sup>2</sup>Cレジスタ : CHIP\_ID2**

このレジスタは、ダイ型式の枝番号とマスクリビジョンレベルを含んでいます。

| REGISTER NAME    | CHIP_ID2 |

|------------------|----------|

| Address          | 0x09h    |

| Reset Value      | 0x1Ah    |

| Type             | Read     |

| Special Features | —        |

| BIT      | NAME          | DESCRIPTION         | DEFAULT VALUE |

|----------|---------------|---------------------|---------------|

| B7 (MSB) | DASH[7:4]     | BCD character 1 (1) | 0001          |

| B6       |               |                     |               |

| B5       |               |                     |               |

| B4       |               |                     |               |

| B3       | MASK_REV[3:0] | BCD character A (A) | 1010          |

| B2       |               |                     |               |

| B1       |               |                     |               |

| B0 (LSB) |               |                     |               |

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

MAX8952

## アプリケーション情報

### インダクタの選択

次式を使用して、インダクタ値( $L_{IDEAL}$ )を計算します。

$$L_{IDEAL} = \frac{4 \times V_{IN} \times D \times (1-D)}{I_{OUT(MAX)} \times f_{OSC}}$$

これによって、ピーク-ピークインダクタ電流リップルが最大出力電流の1/4に設定されます。発振器の周波数 $f_{OSC}$ は3.25MHzで、デューティサイクルDは次のようにになります。

$$D = \frac{V_{OUT}}{V_{IN}}$$

$L_{IDEAL}$ が計算されると、ピーク-ピークインダクタリップル電流は $0.25 \times I_{OUT(MAX)}$ になります。ピークインダクタ電流は $1.125 \times I_{OUT(MAX)}$ です。インダクタの飽和電流がピークインダクタ電流を超えていること、および定格最大DCインダクタ電流も最大出力電流( $I_{OUT(MAX)}$ )を超えていることを確認してください。 $L_{IDEAL}$ よりも小さいインダクタンス値を使用し、インダクタサイズを低減することができます。ただし、あまり小さい値を使用すると、ピークインダクタ電流が上昇し、より大きい出力コンデンサ容量が出力リップルを抑制するために必要となる可能性があります。 $L_{IDEAL}$ よりも大きいインダクタンス値を使用し、より大きい出力電流を得ることができますか、物理的により大きいインダクタサイズが必要になるのが普通です。推奨インダクタについては、表12を参照してください。

表12. 推奨インダクタ

| MANUFACTURER | SERIES      | INDUCTANCE<br>( $\mu$ H) | DC RESISTANCE<br>( $\Omega$ typ) | CURRENT RATING<br>(mA) | DIMENSIONS<br>L x W x H (mm) |

|--------------|-------------|--------------------------|----------------------------------|------------------------|------------------------------|

| Toko         | DE2815C     | 0.47<br>1.0              | 0.025<br>0.033                   | 3800<br>2700           | 3.2 x 3.0 x 1.5              |

|              | DB3015C     | 1.0                      | 0.036                            | 2700                   | 3.2 x 3.2 x 1.5              |

| TDK          | VLS252010ET | 0.47                     | 0.038                            | 2800                   | 2.5 x 2.0 x 1.0              |

|              | VLS4012ET   | 1.0                      | 0.050                            | 2800                   | 4.0 x 4.0 x 1.2              |

| Coilcraft    | LPS5015     | 1.0                      | 0.050                            | 3900                   | 5.0 x 5.0 x 1.5              |

|              | LPS5010     | 0.47                     | 0.038                            | 3400                   | 5.0 x 5.0 x 1.0              |

|              | LPS4414     | 0.7                      | 0.055                            | 3800                   | 4.4 x 4.4 x 1.4              |

| Wurth        | 744042001   | 1.0                      | 0.030                            | 2600                   | 4.8 x 4.8 x 1.8              |

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

## 入力コンデンサの選択

ステップダウンDC-DCレギュレータの入力コンデンサは、バッテリまたは他の入力電力ソースから供給される電流のピークを低減し、コントローラにおけるスイッチングノイズを低減します。通常のアプリケーションの場合は、10 $\mu$ Fのセラミックコンデンサと0.1 $\mu$ Fのセラミックコンデンサの並列接続が推奨されます。スイッチング周波数における入力コンデンサのインピーダンスは、高周波スイッチング電流が入力ソースを通過しないように、入力ソースのインピーダンスよりも低くする必要があります。入力コンデンサは、ステップダウンレギュレータによって課せられた入力リップル電流要件に適合する必要があります。セラミックコンデンサが、パワーアップサージ電流に対するその回復力によって推奨されます。入力リップルによる温度上昇が約+10°Cを超えないように、入力コンデンサを選択します。ステップダウンDC-DCレギュレータの場合、最大入力リップル電流は出力電流の1/2です。この最大入力リップル電流は、ステップダウンレギュレータが50%のデューティ係数( $V_{IN} = 2 \times V_{OUT}$ )で動作するときに発生します。入力コンデンサ別の推奨事項については、MAX8952の評価キットを参照してください。

## 出力コンデンサの選択

ステップダウンDC-DCレギュレータの出力コンデンサは、出力リップルを小さく維持し、制御ループの安定性を確保します。通常のアプリケーションの場合は、10 $\mu$ Fのセラミックコンデンサと0.1 $\mu$ Fのセラミックコンデンサの並列接続が推奨されます。また、出力コンデンサは、スイッチング周波数においてローインピーダンスを備えている必要があります。セラミック、ポリマ、タンタルコンデンサが適しており、これらのうち、セラミックが最低のESRと最低の高周波数インピーダンスを示します。容量(ESRは無視する)に起因する出力リップルはおおよそ次のようになります。

$$V_{RIPPLE} = \frac{I_{L(Peak)}}{2\pi \times f_{OSC} \times C_{OUT}}$$

コンデンサESRに起因する追加のリップルは次のようにになります。

$$V_{RIPPLE(ESR)} = I_{L(Peak)} \times ESR$$

出力コンデンサ別の推奨事項については、MAX8952の評価キットのデータシートを参照してください。

## 電力消費

このICは、サーマルシャットダウン機能を備えており、ダイ温度が+160°Cを超えるとICを損傷から保護します。詳細については、「熱過負荷保護」の項を参照してください。熱過負荷を防止し、各レギュレータの最大負荷電流を可能にするには、このICによって発生した熱がPCBに放熱されるように確保することが重要です。

多層PCBに正しく実装された場合、接合部-周囲熱抵抗( $\theta_{JA}$ )は標準で49°C/Wです。

## PCBレイアウト

高速スイッチング波形と大電流経路のため、最良の性能を得るには注意深いPCBレイアウトが必要です。ICとインダクタ、入力コンデンサ、および出力コンデンサの間のトレースの長さを最短にしてください。これらのトレースは短く、直接、幅広いものにしてください。 $C_{IN}$ および $C_{OUT}$ のグランド接続は、互いにできる限り近接させてPGNDに接続する必要があります。AGNDおよびPGNDをグランドプレーンに直接接続してください。MAX8952の評価キットには、PCBレイアウトと配線方法の例が示されています。

## チップ情報

PROCESS: BiCMOS

## パッケージ

最新のパッケージ図面情報およびランドパターンは、[japan.maxim-ic.com/packages](http://japan.maxim-ic.com/packages)を参照してください。なお、パッケージコードに含まれる「+」、「#」、または「-」はRoHS対応状況を表したものでしかありません。パッケージ図面はパッケージそのものに関するものでRoHS対応状況とは関係がなく、図面によってパッケージコードが異なることがある点を注意してください。

| パッケージタイプ           | パッケージコード | ドキュメントNo.      |

|--------------------|----------|----------------|

| 16 WLP 0.5mm Pitch | W162B2+1 | <b>21-0200</b> |

# 2.5Aステップダウンレギュレータ、 差動リモート検出内蔵、2mm x 2mmのWLPパッケージ

MAX8952

## 改訂履歴

| 版数 | 改訂日  | 説明 | 改訂ページ |

|----|------|----|-------|

| 0  | 6/10 | 初版 | —     |

マキシム・ジャパン株式会社 〒141-0032 東京都品川区大崎1-6-4 大崎ニューシティ 4号館 20F TEL: 03-6893-6600

Maximは完全にMaxim製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。Maximは隨時予告なく回路及び仕様を変更する権利を留保します。

**Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600** 31

© 2010 Maxim Integrated Products

MaximはMaxim Integrated Products, Inc.の登録商標です。