# 固定周波数、ハーフブリッジCCFL インバータコントローラ

**MAX8729**

## 概要

MAX8729は冷陰極蛍光管(CCFL)インバータコントローラであり、2個の外付けnチャネルパワーMOSFETで構成されるハーフブリッジインバータによって複数のCCFLを駆動するように設計されています。ハーフブリッジ構成によって部品点数を最小限に抑えながら、正弦波に近い駆動波形を供給します。MAX8729は点灯時に共振モードで動作し、ランプがすべて点灯すると固定周波数動作に切り替わります。この独自の機能によってどの状態でも信頼性の高い点灯が確保され、トランストレスが低減します。

MAX8729は、高精度のランプ電流レギュレーション( $\pm 2.5\%$ )を提供します。ランプ電流を外付け抵抗によって調整することができます。MAX8729はランプ電流を一定に維持しながら、デジタルパルス幅変調(DPWM)方式でCCFLをオン/オフすることによって輝度を変化させます。輝度をCNTL端子のアナログ電圧や、外部PWM信号によって調整することができます。

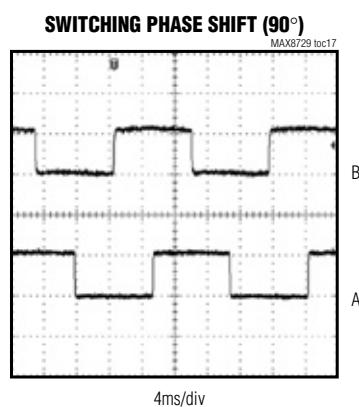

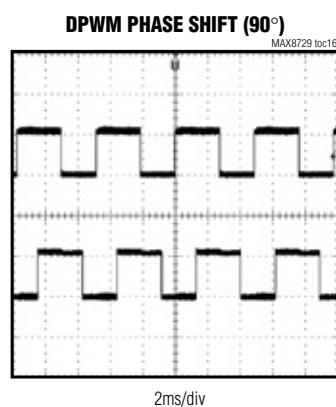

MAX8729は、ゲートドライバとDPWM発振器の位相の同期化と調整を行うことができます。これらの機能を使って、複数のMAX8729 ICをデイジーチェーン構成で接続することができます。マスタICのスイッチング周波数とDPWM周波数を外付け抵抗によって容易に調整することや、システム信号と同期させることができます。コントローラが外部同期信号を失うと、内部発振器に切り替わり、動作を維持します。位相シフト選択端子PS1およびPS2を使って4種類の位相シフトを設定し、最大5個のMAX8729を同時に使用することができます。

MAX8729は、ランプアウト、2次側過電圧、および2次側短絡障害からインバータを保護します。MAX8729は、1つのパワーワンが4個以上のCCFL管を並列駆動するアプリケーションで通常使用される大型パワーMOSFETを駆動することができます。5.35Vの内蔵リニアレギュレータは、MOSFETドライバと大部分の内部回路に電源供給します。MAX8729は低コストの28ピンQSOPパッケージで提供され、-40°C～+85°Cの拡張温度範囲で動作します。

## アプリケーション

|        |              |

|--------|--------------|

| LCDモニタ | ノートブックコンピュータ |

| LCD TV | 車載用インフォテイメント |

## 型番

| PART       | TEMP RANGE     | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX8729EEI | -40°C to +85°C | 28 QSOP     |

ピン配置はデータシートの最後に記載されています。

## 特長

- ◆ 低コスト、ハーフブリッジインバータ構成

- ◆ 共振モード点灯によって起動を保証

- ◆ ランプ点灯後に固定周波数動作

- ◆ 大型外付けMOSFETを駆動

- ◆ マルチランプアプリケーションをサポート

- ◆ 同期および位相シフト制御によってデイジーチェーン動作を実現

- ◆ スイッチング周波数およびDPWM周波数を調整可能

- ◆  $\pm 2.5\%$ のランプ電流レギュレーション

- ◆ 調光範囲：10 : 1

- ◆ 高精度なアナログ調光制御

- ◆ 可変タイムアウト付きランプアウト検出

- ◆ 2次電流/電圧制限

- ◆  $R_{DS(ON)}$ 検出付き1次電流制限

- ◆ DPWM立上り/立下り時間を調整可能

- ◆ 低コスト28ピンQSOPパッケージ

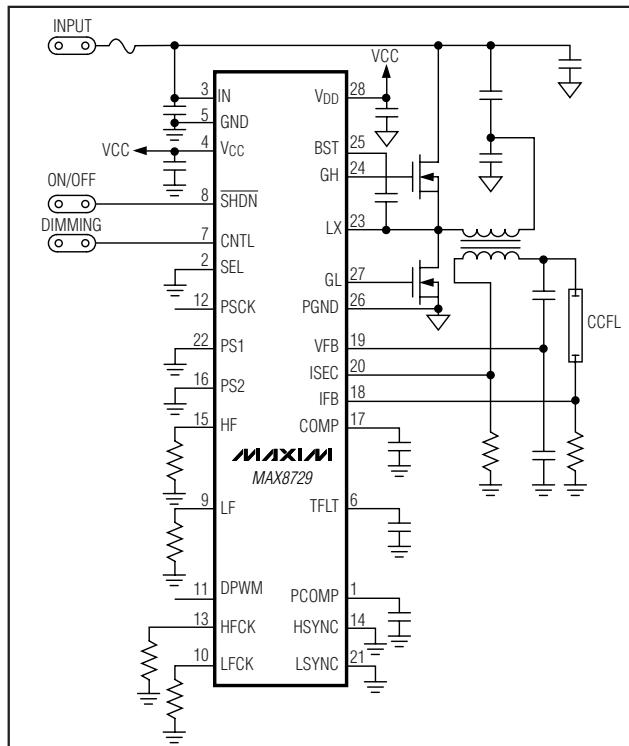

## 簡略動作回路

# 固定周波数、ハーフブリッジCCFL インバータコントローラ

## ABSOLUTE MAXIMUM RATINGS

|                                                                                                      |                                  |                                                                                                                                              |                 |

|------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| IN, LX to GND .....                                                                                  | -0.3V to +30V                    | SHDN to GND .....                                                                                                                            | -0.3V to +6V    |

| BST to GND .....                                                                                     | -0.3V to +36V                    | PGND to GND .....                                                                                                                            | -0.3V to +0.3V  |

| BST to LX .....                                                                                      | -0.3V to +6V                     | Continuous Power Dissipation ( $T_A = +70^\circ\text{C}$ )<br>28-Pin QSOP (derate 10.8mW/ $^\circ\text{C}$ above $+70^\circ\text{C}$ ) ..... | 860.2mW         |

| V <sub>CC</sub> , V <sub>DD</sub> to GND .....                                                       | -0.3V to +6V                     | Operating Temperature Range .....                                                                                                            | -40°C to +85°C  |

| GH to LX .....                                                                                       | -0.3V to V <sub>BST</sub> + 0.3V | Junction Temperature .....                                                                                                                   | +150°C          |

| CNTL, COMP, GL, DPWM, HF, LF, HFCK,<br>LFCK, HSYNC, LSYNC, PS1, PS2, PSCK, TFLT,<br>PCOMP, SEL ..... | -0.3V to V <sub>CC</sub> + 0.3V  | Storage Temperature Range .....                                                                                                              | -65°C to +150°C |

| IFB, ISEC, VFB to GND .....                                                                          | -6V to +6V                       | Lead Temperature (soldering, 10s) .....                                                                                                      | +300°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

(V<sub>IN</sub> = 12V, V<sub>DD</sub> = 5.3V,  $T_A = 0^\circ\text{C}$  to  $+85^\circ\text{C}$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ\text{C}$ .)

| PARAMETER                                                  | CONDITIONS                                                                            | MIN  | TYP  | MAX  | UNITS |

|------------------------------------------------------------|---------------------------------------------------------------------------------------|------|------|------|-------|

| IN Input Voltage Range                                     |                                                                                       | 6    | 28   |      | V     |

| IN Quiescent Current                                       | V <sub>SHDN</sub> = 5.3V, V <sub>IN</sub> = 28V                                       | 3.2  | 6    |      | mA    |

| IN Quiescent Current, Shutdown                             | SHDN = GND                                                                            | 6    | 20   |      | μA    |

| V <sub>CC</sub> Output Voltage, Normal Operation           | V <sub>SHDN</sub> = 5.3V, 6V < V <sub>IN</sub> < 28V,<br>0 < I <sub>LOAD</sub> < 10mA | 5.20 | 5.35 | 5.50 | V     |

| V <sub>CC</sub> Output Voltage, Shutdown                   | SHDN = GND, no load                                                                   | 3.5  | 4.6  | 5.5  | V     |

| V <sub>CC</sub> Undervoltage Lockout Threshold             | V <sub>CC</sub> rising (leaving lockout)                                              |      | 4.5  |      | V     |

|                                                            | V <sub>CC</sub> falling (entering lockout)                                            | 4.0  |      |      |       |

| V <sub>CC</sub> Undervoltage-Lockout Hysteresis            |                                                                                       | 200  |      |      | mV    |

| GH, GL On-Resistance, Low State                            | I <sub>TEST</sub> = 10mA                                                              | 1    | 2    |      | Ω     |

| GH, GL On-Resistance, High State                           | I <sub>TEST</sub> = 10mA                                                              | 4    | 6    |      | Ω     |

| BST Leakage Current                                        | V <sub>BST</sub> = 17V, V <sub>LX</sub> = 12V                                         |      | 5    |      | μA    |

| Resonant Frequency Range                                   | Not tested                                                                            | 30   | 80   |      | kHz   |

| Minimum Off-Time                                           |                                                                                       | 330  | 416  | 560  | ns    |

| Maximum Off-Time (LX-GND)                                  |                                                                                       | 24.0 | 30.7 | 42.0 | μs    |

| Low-Side MOSFET Maximum Current-Limit Threshold (LX-GND)   |                                                                                       | 370  | 400  | 470  | mV    |

| High-Side MOSFET Maximum Current-Limit Threshold (IN – LX) |                                                                                       | 370  | 400  | 470  | mV    |

| Low-Side MOSFET Zero-Current-Crossing Threshold (GND – LX) |                                                                                       | 0    | 10   | 18   | mV    |

| High-Side MOSFET Zero-Current-Crossing Threshold (LX – IN) |                                                                                       | -16  | +6   | +28  | mV    |

| Current-Limit Leading Edge Blanking                        |                                                                                       | 310  | 410  | 560  | ns    |

| IFB Regulation Point                                       | Internally full-wave rectified                                                        | 770  | 790  | 810  | mV    |

| IFB Maximum AC Voltage                                     |                                                                                       | ±3   |      |      | V     |

# 固定周波数、ハーフブリッジCCFL インバータコントローラ

MAX8729

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{IN} = 12V$ ,  $V_{DD} = 5.3V$ ,  $T_A = 0^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$ .)

| PARAMETER                                                      | CONDITIONS                                   | MIN   | TYP   | MAX  | UNITS            |

|----------------------------------------------------------------|----------------------------------------------|-------|-------|------|------------------|

| IFB Input Bias Current                                         | 0 < $V_{IFB} < 2V$                           | -3    | +3    |      | $\mu\text{A}$    |

|                                                                | -2V < $V_{IFB} < 0$                          | -150  |       |      |                  |

| IFB Lamp-Out Threshold                                         | Reject 1 $\mu\text{s}$ glitches              | 760   | 790   | 820  | mV               |

| IFB-to-COMP Transconductance                                   | 0.5V < $V_{COMP} < 2.4V$                     |       | 100   |      | $\mu\text{S}$    |

| COMP Output Impedance                                          |                                              |       | 10    |      | $\text{M}\Omega$ |

| COMP Discharge Current During Overvoltage or Overcurrent Fault | $V_{IFB} = 800\text{mV}$ , $V_{ISEC} = 2.5V$ |       | 1200  |      | $\mu\text{A}$    |

| COMP Discharge Current During DPWM Off-Time                    | $V_{IFB} = 800\text{mV}$ , $V_{COMP} = 1.5V$ |       | 100   |      | $\mu\text{A}$    |

| ISEC Input Voltage Range                                       |                                              | -3    | +3    |      | V                |

| ISEC Input Bias Current                                        |                                              | -0.3  | +0.3  |      | $\mu\text{A}$    |

| ISEC Overcurrent Threshold                                     |                                              | 1.18  | 1.21  | 1.26 | V                |

| VFB Input-Voltage Range                                        |                                              | -4    | +4    |      | V                |

| VFB Input Bias Current                                         | -4V < $V_{VFB} < 4V$                         | -25   | +25   |      | $\mu\text{A}$    |

| VFB Overvoltage Threshold                                      |                                              | 2.15  | 2.25  | 2.35 | V                |

| Main Oscillator Frequency                                      | $R_{HF} = 100\text{k}\Omega$                 | 51.7  | 53.8  | 55.9 | kHz              |

| Main Oscillator Frequency Range                                |                                              | 20    | 100   |      | kHz              |

| HF, HFCK, LF, LFCK Input-Low Voltage                           | Slave mode, $V_{CNTL} = V_{CC}$              |       |       | 0.8  | V                |

| HF, HFCK, LF, LFCK Input-High Voltage                          | Slave mode, $V_{CNTL} = V_{CC}$              |       | 2.1   |      | V                |

| HF, HFCK, LF, LFCK Input Hysteresis                            | Slave mode, $V_{CNTL} = V_{CC}$              |       | 200   |      | mV               |

| HF, HFCK, LF, LFCK Input Bias Current                          | Slave mode, $V_{CNTL} = V_{CC}$              |       | -1    | +1   | $\mu\text{A}$    |

| HF, HFCK, LF, LFCK Input Rise and Fall Time                    | Slave mode, $V_{CNTL} = V_{CC}$              |       |       | 200  | ns               |

| HF Input Frequency Range                                       | Slave mode, $V_{CNTL} = V_{CC}$              | 20    | 100   |      | kHz              |

| HFCK Input Frequency Range                                     | Slave mode, $V_{CNTL} = V_{CC}$              | 120   | 600   |      | kHz              |

| H SYNC Input Frequency Range                                   | $R_{HF} = 100\text{k}\Omega$                 | 190   | 460   |      | kHz              |

| LF Input Frequency Range                                       | Slave mode, $V_{CNTL} = V_{CC}$              | 80    | 300   |      | Hz               |

| LFCK Input Frequency Range                                     | Slave mode, $V_{CNTL} = V_{CC}$              | 10.24 | 38.40 |      | kHz              |

| L SYNC Input Frequency Range                                   | $R_{LF} = 150\text{k}\Omega$                 | 120   | 280   |      | Hz               |

| DPWM Chopping Frequency                                        | $R_{LF} = 150\text{k}\Omega$                 | 199   | 207   | 215  | Hz               |

| DPWM Frequency Range                                           | $R_{LF} = 300\text{k}\Omega$                 | 80    | 300   |      | Hz               |

# 固定周波数、ハーフブリッジCCFL インバータコントローラ

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{IN} = 12V$ ,  $V_{DD} = 5.3V$ ,  $T_A = 0^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$ .)

| PARAMETER                                         | CONDITIONS                                                              | MIN  | TYP  | MAX  | UNITS            |

|---------------------------------------------------|-------------------------------------------------------------------------|------|------|------|------------------|

| PS1, PS2, LSYNC, HSYNC, SEL<br>Input Low Voltage  |                                                                         |      |      | 0.8  | V                |

| PS1, PS2, LSYNC, HSYNC, SEL<br>Input High Voltage |                                                                         | 2.1  |      |      | V                |

| PS1, PS2, LSYNC, HSYNC, SEL<br>Input Hysteresis   |                                                                         |      | 200  |      | mV               |

| PS1, PS2, LSYNC, HSYNC, SEL<br>Input Bias Current |                                                                         | -1   |      | +1   | $\mu\text{A}$    |

| HFCK, LFCK, PSCK, DPWM<br>Output On-Resistance    | $I_{TEST} = 1\text{mA}$                                                 |      |      | 2.5  | $\text{k}\Omega$ |

| CNTL Minimum Duty-Cycle<br>Threshold              |                                                                         | 0.21 | 0.23 | 0.26 | V                |

| CNTL Maximum Duty-Cycle<br>Threshold              |                                                                         | 1.9  | 2.0  | 2.1  | V                |

| CNTL Input Current                                | $0 < V_{CNTL} < 2\text{V}$                                              | -0.1 |      | +0.1 | $\mu\text{A}$    |

| CNTL Input Threshold                              | Slave mode                                                              | 4.2  | 4.5  | 4.8  | V                |

| DPWM A/D Converter Resolution                     | Guaranteed monotonic                                                    |      | 5    |      | Bits             |

| SHDN Input Low Voltage                            |                                                                         |      |      | 0.8  | V                |

| SHDN Input High Voltage                           |                                                                         | 2.1  |      |      | V                |

| SHDN Input Bias Current                           |                                                                         | -1   |      | +1   | $\mu\text{A}$    |

| TFLT Charging Current                             | $V_{SEC} < 1.25$ and $V_{IFB} < 790\text{mV}$ ; $V_{FLT} = 2.0\text{V}$ | 0.95 | 1.00 | 1.05 | $\mu\text{A}$    |

|                                                   | $V_{SEC} < 1.25$ and $V_{IFB} > 790\text{mV}$ ; $V_{FLT} = 2.0\text{V}$ |      | -1   |      |                  |

|                                                   | $V_{SEC} > 1.25$ and $V_{IFB} < 790\text{mV}$ ; $V_{FLT} = 2.0\text{V}$ |      | 126  |      |                  |

| TFLT Trip Threshold                               |                                                                         | 3.9  | 4.0  | 4.1  | V                |

# 固定周波数、ハーフブリッジCCFL インバータコントローラ

MAX8729

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{IN} = 12V$ ,  $V_{DD} = 5.3V$ ,  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , unless otherwise noted.) (Note 1)

| PARAMETER                                                  | CONDITIONS                                                                             | MIN  | TYP     | MAX  | UNITS         |

|------------------------------------------------------------|----------------------------------------------------------------------------------------|------|---------|------|---------------|

| IN Input-Voltage Range                                     |                                                                                        | 6    | 28      |      | V             |

| IN Quiescent Current                                       | $V_{SHDN} = 5.3V$ , $V_{IN} = 28V$                                                     |      | 6       |      | mA            |

| IN Quiescent Current, Shutdown                             | $SHDN = GND$                                                                           |      | 20      |      | $\mu\text{A}$ |

| V <sub>CC</sub> Output Voltage, Normal Operation           | $V_{SHDN} = 5.3V$ , $6V < V_{IN} < 28V$ , $0 < I_{LOAD} < 10\text{mA}$                 | 5.20 | 5.50    |      | V             |

| V <sub>CC</sub> Output Voltage, Shutdown                   | $SHDN = GND$ , no load                                                                 | 3.5  | 5.5     |      | V             |

| V <sub>CC</sub> Undervoltage Lockout Threshold             | V <sub>CC</sub> rising (leaving lockout)<br>V <sub>CC</sub> falling (entering lockout) |      | 4.5     | 4.0  | V             |

| GH, GL On-Resistance, Low State                            | $I_{TEST} = 10\text{mA}$                                                               |      | 3       |      | $\Omega$      |

| GH, GL On-Resistance, High State                           | $I_{TEST} = 10\text{mA}$                                                               |      | 7       |      | $\Omega$      |

| Minimum Off-Time                                           |                                                                                        | 330  | 560     |      | ns            |

| Maximum Off-Time                                           |                                                                                        | 24.0 | 42.0    |      | $\mu\text{s}$ |

| Low-Side MOSFET Maximum Current-Limit Threshold (LX – GND) |                                                                                        | 350  | 500     |      | mV            |

| High-Side MOSFET Maximum Current-Limit Threshold (IN – LX) |                                                                                        | 350  | 500     |      | mV            |

| Low-Side MOSFET Zero-Current Crossing Threshold (GND – LX) |                                                                                        | 0    | 18      |      | mV            |

| High-Side MOSFET Zero-Current Crossing Threshold (LX – IN) |                                                                                        | -16  | +28     |      | mV            |

| Current-Limit Leading-Edge Blanking                        |                                                                                        | 310  | 560     |      | ns            |

| IFB Regulation Point                                       | Internally full-wave rectified                                                         | 770  | 810     |      | mV            |

| IFB Maximum AC Voltage                                     |                                                                                        |      | $\pm 3$ |      | V             |

| IFB Input Bias Current                                     | $0 < V_{IFB} < 2V$<br>$-2V < V_{IFB} < 0$                                              | -3   | +3      | -150 | $\mu\text{A}$ |

| IFB Lamp-Out Threshold                                     | Reject 1 $\mu\text{s}$ glitches                                                        | 760  | 820     |      | mV            |

| ISEC Input Voltage Range                                   |                                                                                        | -3   | +3      |      | V             |

| ISEC Overcurrent Threshold                                 |                                                                                        | 1.18 | 1.26    |      | V             |

| VFB Input Voltage Range                                    |                                                                                        | -4   | +4      |      | V             |

| VFB Overvoltage Threshold                                  |                                                                                        | 2.15 | 2.35    |      | V             |

| Main Oscillator Frequency                                  | $R_{HF} = 100\text{k}\Omega$                                                           | 50.0 | 57.6    |      | kHz           |

| Main Oscillator Frequency Range                            |                                                                                        | 20   | 100     |      | kHz           |

# 固定周波数、ハーフブリッジCCFL インバータコントローラ

## ELECTRICAL CHARACTERISTICS (continued)

(VIN = 12V, VDD = 5.3V, TA = -40°C to +85°C, unless otherwise noted.) (Note 1)

| PARAMETER                                      | CONDITIONS                                                                       | MIN   | TYP   | MAX | UNITS |

|------------------------------------------------|----------------------------------------------------------------------------------|-------|-------|-----|-------|

| HF, HFCK, LF, LFCK Input Low Voltage           | Slave mode, VCNTL = VCC                                                          |       |       | 0.8 | V     |

| HF, HFCK, LF, LFCK Input High Voltage          | Slave mode, VCNTL = VCC                                                          |       | 2.1   |     | V     |

| HF, HFCK, LF, LFCK Input Rise and Fall Time    | Slave mode, VCNTL = VCC                                                          |       |       | 200 | ns    |

| HF Input Frequency Range                       | Slave mode, VCNTL = VCC                                                          | 20    | 100   |     | kHz   |

| HFCK Input Frequency Range                     | Slave mode, VCNTL = VCC                                                          | 120   | 600   |     | kHz   |

| H SYNC Input Frequency Range                   | RHF = 100kΩ                                                                      | 190   | 460   |     | kHz   |

| LF Input Frequency Range                       | Slave mode, VCNTL = VCC                                                          | 80    | 300   |     | Hz    |

| LFCK Input Frequency Range                     | Slave mode, VCNTL = VCC                                                          | 10.24 | 38.40 |     | kHz   |

| LSYNC Input Frequency Range                    | RLF = 150kΩ                                                                      | 120   | 280   |     | Hz    |

| DPWM Chopping Frequency                        | RLF = 150kΩ                                                                      | 197   | 217   |     | Hz    |

| DPWM Input Frequency Range                     |                                                                                  | 80    | 300   |     | Hz    |

| PS1, PS2, LSYNC, HSYNC, SEL Input Low Voltage  |                                                                                  |       |       | 0.8 | V     |

| PS1, PS2, LSYNC, HSYNC, SEL Input High Voltage |                                                                                  |       | 2.1   |     | V     |

| HFCK, LFCK, PSCK, DPWM Output On-Resistance    | I <sub>TEST</sub> = 1mA                                                          |       |       | 2.5 | kΩ    |

| CNTL Minimum Duty-Cycle Threshold              |                                                                                  | 0.21  | 0.26  |     | V     |

| CNTL Maximum Duty-Cycle Threshold              |                                                                                  | 1.9   | 2.1   |     | V     |

| CNTL Input Threshold                           | Slave mode                                                                       | 4.2   | 4.8   |     | V     |

| SHDN Input Low Voltage                         |                                                                                  |       |       | 0.8 | V     |

| SHDN Input High Voltage                        |                                                                                  |       | 2.1   |     | V     |

| TFLT Charging Current                          | V <sub>SEC</sub> < 1.25 and V <sub>IFB</sub> < 600mV,<br>V <sub>FLT</sub> = 2.0V | 0.93  | 1.07  |     | µA    |

| TFLT Trip Threshold                            |                                                                                  | 3.9   | 4.1   |     | V     |

**Note 1:** Specifications to -40°C are guaranteed by design, based on final characterization results.

# 固定周波数、ハーフブリッジCCFL インバータコントローラ

MAX8729

## 標準動作特性

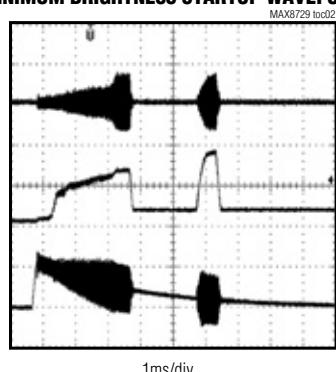

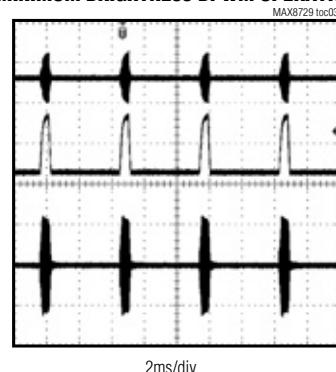

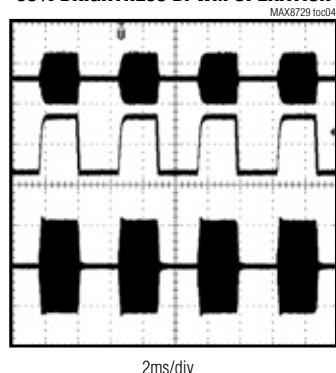

(Circuit of Figure 1.  $V_{IN} = 12V$ ,  $V_{CC} = V_{DD}$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

**NORMAL OPERATION**

**MINIMUM BRIGHTNESS STARTUP WAVEFORM**

**MINIMUM BRIGHTNESS DPWM OPERATION**

**50% BRIGHTNESS DPWM OPERATION**

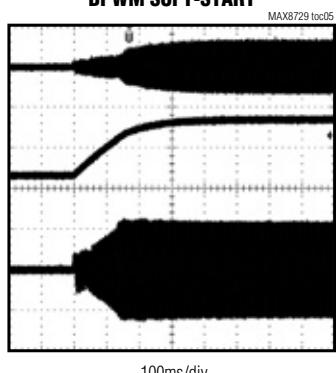

**DPWM SOFT-START**

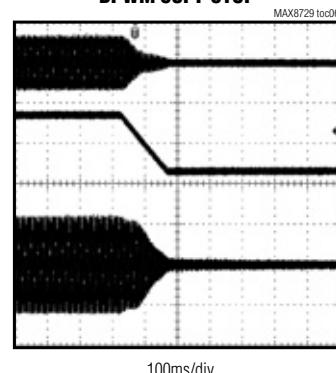

**DPWM SOFT-STOP**

**LAMP-OUT VOLTAGE

LIMITING AND TIMEOUT**

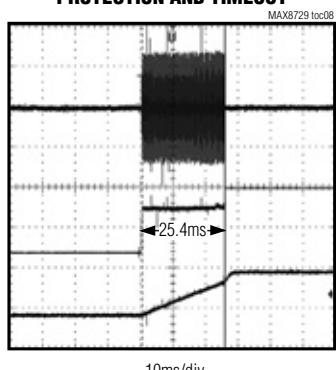

**SECONDARY SHORT-CIRCUIT

PROTECTION AND TIMEOUT**

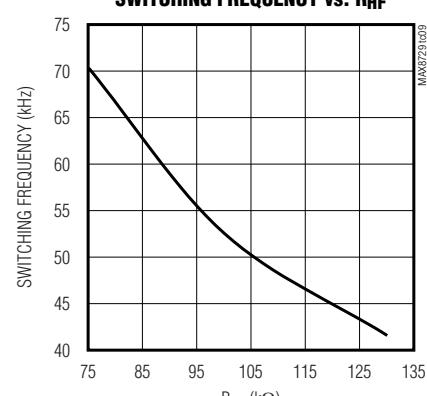

**SWITCHING FREQUENCY vs.  $R_{HF}$**

# 固定周波数、ハーフブリッジCCFL インバータコントローラ

## 標準動作特性(続き)

(Circuit of Figure 1.  $V_{IN} = 12V$ ,  $V_{CC} = V_{DD}$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

# 固定周波数、ハーフブリッジCCFL インバータコントローラ

MAX8729

## 標準動作特性(続き)

(Circuit of Figure 1.  $V_{IN} = 12V$ ,  $V_{CC} = V_{DD}$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

# 固定周波数、ハーフブリッジCCFL インバータコントローラ

## 端子説明

| 端子 | 名称              | 機能                                                                                                                                                                                                                              |

|----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | PCOMP           | 位相ロックループの補償ノード。位相ロックループを補償するには、0.1 $\mu$ FのコンデンサをPCOMPとGNDの間に接続します。                                                                                                                                                             |

| 2  | SEL             | 輝度制御選択入力。輝度をアナログ電圧や外部同期信号によって調整することができます。SELをGNDに接続すると、CNTL端子においてアナログ制御がイネーブルされます。SELをV <sub>CC</sub> に接続すると、LSYNC端子において外部同期信号によって輝度制御がイネーブルされます。                                                                               |

| 3  | IN              | 電源入力。デバイスに電源供給する5.35Vの内蔵リニアレギュレータへの入力。0.1 $\mu$ FのセラミックコンデンサでINをGNDにバイパスします。                                                                                                                                                    |

| 4  | V <sub>CC</sub> | 5.35V/10mAのリニアレギュレータ出力。V <sub>CC</sub> は、MAX8729の制御回路の大部分に電源供給します。1 $\mu$ FセラミックコンデンサでV <sub>CC</sub> をGNDにバイパスします。                                                                                                             |

| 5  | GND             | システムグラウンド                                                                                                                                                                                                                       |

| 6  | TFLT            | 障害タイマ設定端子。オープンランプ障害遅延時間を約1.2秒に、2次短絡障害遅延時間を約10msに設定するには、0.22 $\mu$ FのコンデンサをTFLTとGNDの間に接続します。詳細については、「障害遅延時間の設定」の項を参照してください。                                                                                                      |

| 7  | CNTL            | 輝度制御入力。利用可能な輝度制御範囲は0V～2Vです。V <sub>CNTL</sub> = 0は最低輝度を表します(10%のDPWMデューティサイクル)。2V以上、4.2V未満のV <sub>CNTL</sub> は最大輝度を表します(100%のDPWMデューティサイクル)。CNTLがV <sub>CC</sub> に接続されると、MAX8729はスレーブモードに移行します。詳細については、「デジタルPWM調光制御」の項を参照してください。 |

| 8  | SHDN            | シャットダウン制御入力。SHDNがGNDにブルされると、MAX8729はシャットダウンします。                                                                                                                                                                                 |

| 9  | LF              | DPWM周波数調整端子。DPWM発振器周波数を設定するには、抵抗をLFとGNDの間に接続します。CNTLがV <sub>CC</sub> に接続されている場合は、LFはロジック入力です。                                                                                                                                   |

| 10 | LFCK            | DPWM発振器クロック出力。CNTLがV <sub>CC</sub> に接続されている場合は、LFCKはロジック入力です。                                                                                                                                                                   |

| 11 | DPWM            | DPWM信号出力。DPWM出力を使って、マスタ-スレーブ動作においてスレーブICのDPWM周波数を制御することができます。                                                                                                                                                                   |

| 12 | PSCK            | 位相シフトクロック出力。CNTLがV <sub>CC</sub> に接続されている場合は、PSCKはロジック入力です。                                                                                                                                                                     |

| 13 | HFCK            | メインスイッチング発振器クロック出力。CNTLがV <sub>CC</sub> に接続されている場合は、HFCKはロジック入力です。                                                                                                                                                              |

| 14 | HSYNC           | メインスイッチング周波数同期入力。スイッチング周波数をHsync上の外部信号と同期させることができます。Hsyncには、シムミットトリガ入力があります。                                                                                                                                                    |

| 15 | HF              | スイッチング周波数調整端子。メイン発振器周波数を設定するには、抵抗をHFとGNDの間に接続します。CNTLがV <sub>CC</sub> に接続されている場合は、HFはロジック入力です。                                                                                                                                  |

| 16 | PS2             | 位相シフト選択入力。PS1およびPS2ロジック入力は、マスタ-スレーブ動作時、4つのプログラマブル位相シフト(60°、90°、120°、および180°)の中から位相シフトを選択します。PS1およびPS2は、各スレーブで同じ状態である必要があります。詳細については、「デイジーチェーン動作での位相シフト(PS1、PS2)」の項を参照してください。                                                    |

| 17 | COMP            | トランスクンダクタンスエラーアンプ出力。COMPとGNDの間に接続された0.01 $\mu$ Fのコンデンサによって、DPWM動作時のランプ電流エンベロープの立上り時間と立下り時間が設定されます。詳細については、「COMPコンデンサの選択」の項を参照してください。                                                                                            |

# 固定周波数、ハーフブリッジCCFL インバータコントローラ

MAX8729

## 端子説明(続き)

| 端子 | 名称              | 機能                                                                                                                                                                                                  |

|----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18 | IFB             | ランプ電流フィードバック入力。IFB検出信号は内部で全波整流されます。整流された信号の平均値は、ハイサイドMOSFETのオン時間を制御することによって790mV(typ)に安定化されます。IFBがTFLTで設定された時間の間、連続的に790mV(typ)を下回る場合は、オープンランプ障害が発生します。詳細については、「ランプアウト保護」および「障害遅延時間の設定」の項を参照してください。 |

| 19 | VFB             | トランス2次電圧フィードバック入力。VFBのピーク電圧が2.3V (typ)の過電圧スレッショルドを超えると、コントローラは1.2mAの内部電流シンクをオンにして、COMPコンデンサを放電します。CCFL管の高電圧端子とGNDの間にある容量性分圧器によって、起動およびランプアウト障害時の最大ランプ出力電圧が決定されます。詳細については、「2次電圧制限値の設定」の項を参照してください。   |

| 20 | ISEC            | トランス2次電流フィードバック入力。ISECのピーク電圧が内部過電流スレッショルドを超えると、コントローラは1.2mAの内部電流シンクをオンにして、COMPコンデンサを放電します。トランス2次側の低電圧端子とグランドの間に接続された電流検出抵抗によって、短絡障害時の最大2次電流が決定されます。詳細については、「2次電流制限値の設定」の項を参照してください。                 |

| 21 | LSYNC           | DPWM同期入力。DPWM周波数をLSYNC上の外部信号と同期させることができます。SELがV <sub>CC</sub> と接続されている場合は、LSYNC信号のデューティサイクルによって輝度が決定します。LSYNCは、シミュミットトリガ入力を持っています。                                                                  |

| 22 | PS1             | 位相シフト選択入力。PS1およびPS2ロジック入力は、マスター-スレーブ動作時、4つのプログラマブル位相シフト(60°、90°、120°、および180°)の中から位相シフトを選択します。PS1およびPS2は、各スレーブで同じ状態である必要があります。詳細については、「デイジーチェーン動作での位相シフト(PS1、PS2)」の項を参照してください。                       |

| 23 | LX              | スイッチングノード。LXは、ハイサイドゲートドライバのリターンです。LXは、1次電流制限およびゼロ交差コンパレータへの入力もあります。コントローラは1次過電流状態およびゼロ交差を検出するために、ハイサイドMOSFET(IN - LX)とローサイドMOSFET(LX - GND)の間の電圧を検出します。                                             |

| 24 | GH              | ハイサイドMOSFETゲートドライバ出力                                                                                                                                                                                |

| 25 | BST             | ローサイドゲートドライバ電源入力。MAX8729はブーストダイオードを内蔵しています。ブーストストラップ回路を構成するには、0.1μFのコンデンサをLXとBSTの間に接続します。                                                                                                           |

| 26 | PGND            | 電源グランド。PGNDは、ローサイドゲートドライバのリターンです。                                                                                                                                                                   |

| 27 | GL              | ローサイドMOSFETゲートドライバ出力                                                                                                                                                                                |

| 28 | V <sub>DD</sub> | ローサイドMOSFETゲートドライバ電源入力                                                                                                                                                                              |

# 固定周波数、ハーフブリッジCCFL インバータコントローラ

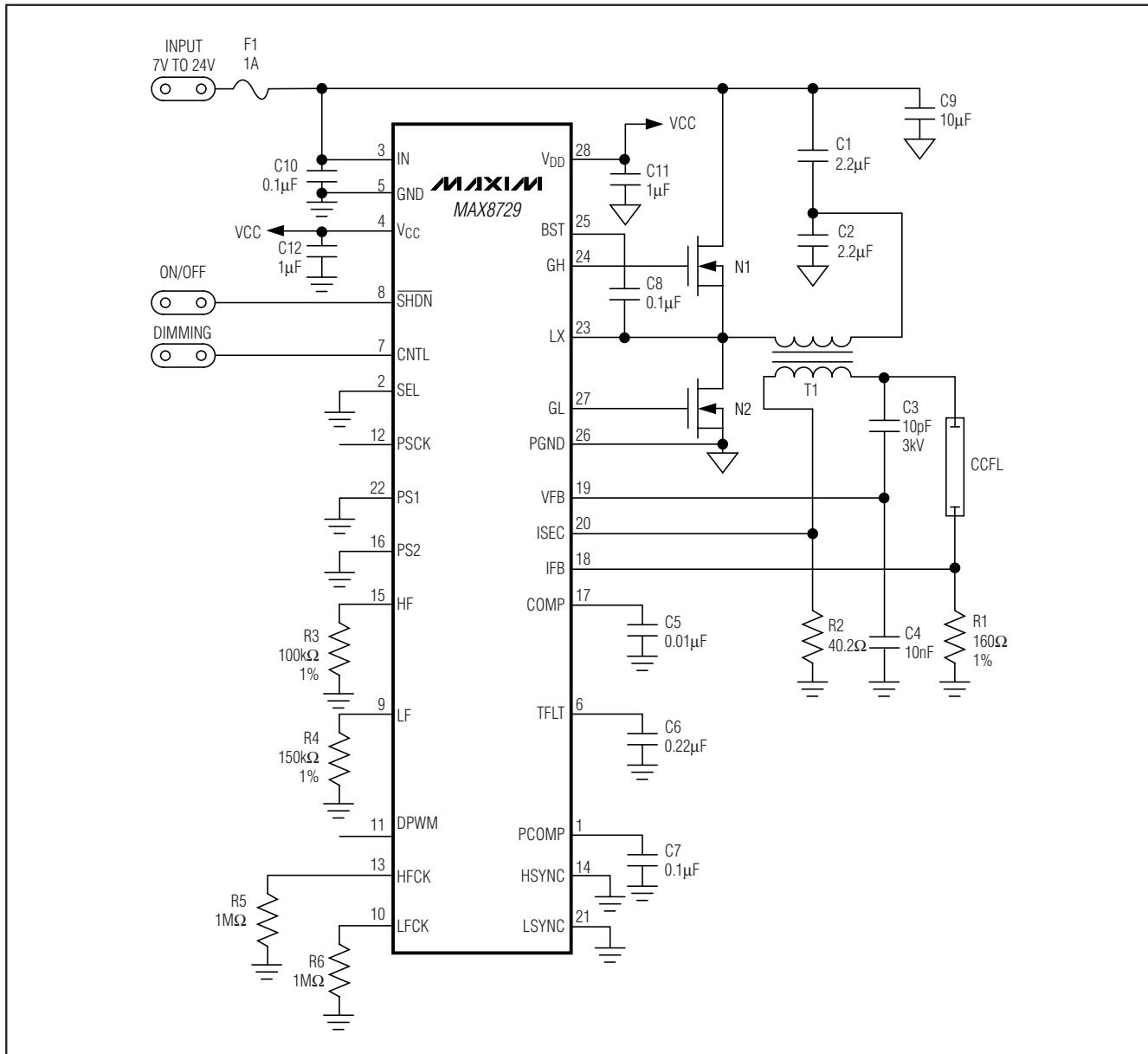

図1. 標準スタンドアロン動作回路

# 固定周波数、ハーフブリッジCCFL インバータコントローラ

**MAX8729**

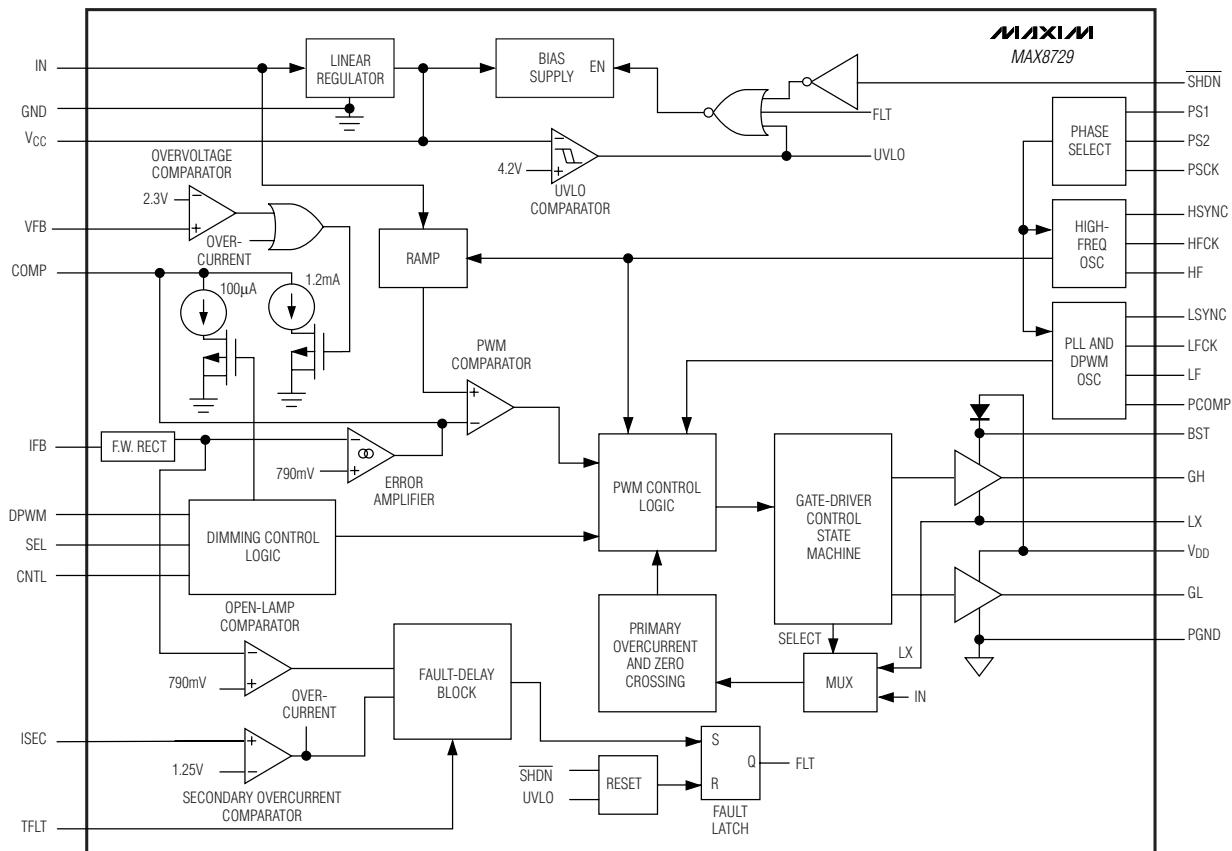

図2. ファンクションダイアグラム

# 固定周波数、ハーフブリッジCCFL インバータコントローラ

## 詳細

図1は、スタンドアロンの標準動作回路を示しています。図2は、MAX8729のファンクションダイアグラムを示しています。この回路アーキテクチャはハーフブリッジインバータによって構成され、このインバータは非安定化DCを正弦波に近い高周波AC出力に変換し、CCFLに電源供給します。MAX8729は、安定した動作とクリーンな起動特性を実現するUVLOコンパレータ付きの5.35Vの内蔵リニアレギュレータによってバイアスされています。1次側電流制限、2次側過電圧、2次短絡、およびオープンランプ障害を検出する、各コンパレータから構成される複数層の障害保護回路があります。障害状態の決定前に任意の障害が最小時間の間、持続するようにして、ロジックブロックはコンパレータ出力を制御します。独立したブロックが、アナログまたはDPWM入力に基づいて調光を制御します。最後に、専用ロジック回路は同期制御と位相制御機能を備え、位相オーバラップを伴わず最大5つのMAX8729をデイジーチェーンすることができます。

インバータは点灯時に共振モードで動作し、ランプがすべて点灯すると固定周波数動作に切り替わります。この独自の機能によってどの状態でも信頼性の高い点灯が確保され、トランストレスが低減します。固定周波数アーキテクチャは、デイジーチェーン接続されたアプリケーション用に、同期および、位相シフトを行うことができます。また、複数ランプを單一段内で並列駆動することもできます。MAX8729のゲートドライバは十分に強力であるため、1つのパワーワークが4個以上のCCFLランプを並列駆動する場合に必要な大型パワーMOSFETを駆動することができます。

MAX8729は、高精度のランプ電流レギュレーション( $\pm 2.5\%$ )を行います。1次側電流検出ではサイクルごとの電流制限とゼロ交差検出を行い、また2次電流は、外付け抵抗でランプ電流を微調整する独立したループによって検出されます。MAX8729はほぼ一定のランプ電流を維持しながら、DPWM方式でCCFLをオン/オフして、ランプ輝度を制御します。輝度の設定ポイントをCNTL端子のアナログ電圧または外部PWM信号によって調整することができます。

MAX8729は1個の補償入力(COMP)を備え、これによってソフトスタートとソフトストップのタイミング特性も設定されます。制御ロジックを通じて、インバータのダイナミック動作を調整するために動作モードに基づいてCOMPで利用可能な駆動電流が変更されます。

## 固定周波数動作

MAX8729は、通常動作においては固定周波数モードで動作します。スイッチング周波数を設定するには、以下の2つの方法があります。

- 1) HFとGNDの間に接続された外付け抵抗を使って、スイッチング周波数を設定することができます。スイッチング周波数は、次式から求められます。

$$f_{SW} = 54\text{kHz} \times \frac{100\text{k}\Omega}{R_{HF}}$$

スイッチング周波数の調整可能な範囲は、20kHz～100kHzです( $R_{HF}$ は270k $\Omega$ ～54k $\Omega$ )。

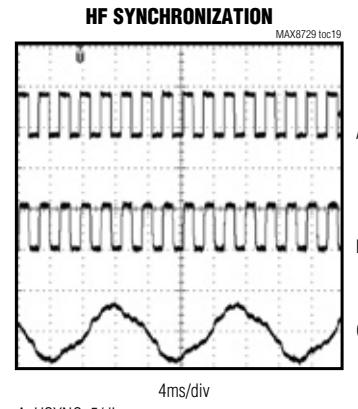

- 2) スイッチング周波数を外部の高周波信号によって同期させることができます。100k $\Omega$ 抵抗によってHFをGNDに接続し、HSYNCを外部高周波信号に接続します。結果として同期したスイッチング周波数( $f_{SW}$ )は、外部信号の周波数( $f_{EXT}$ )の1/6です。

$$f_{SW} = \frac{f_{EXT}}{6}$$

外部信号の周波数範囲は190kHz～460kHzの範囲である必要があり、 $R_{HF} + 100\text{k}\Omega$ で32kHz～77kHzのスイッチング周波数範囲になります。

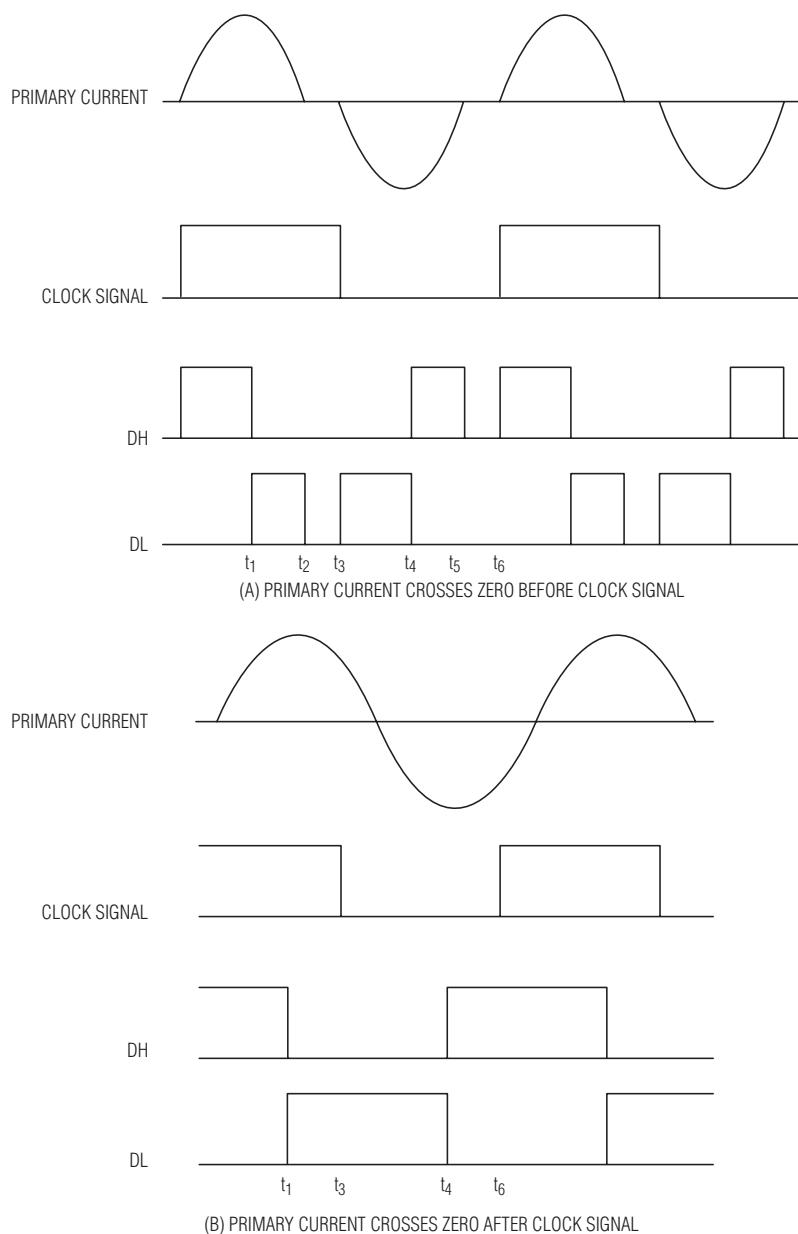

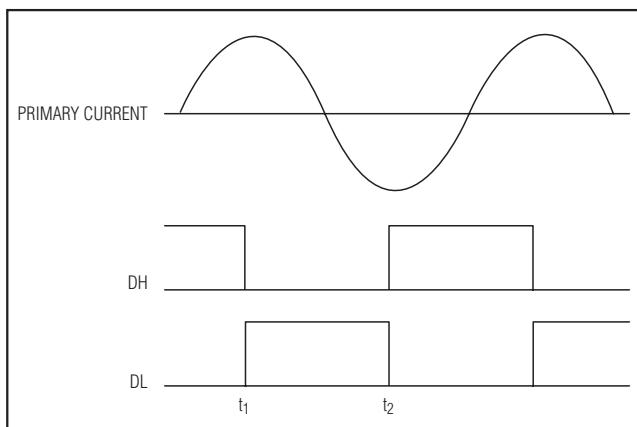

図3は、1次電流、クロック信号、およびゲート駆動信号を示すタイミング図によって固定周波数動作を示しています。正の半サイクルの初期に、ハイサイドスイッチはオンで、1次電流が増加します。コントローラは、 $t_1$ においてハイサイドスイッチをオフにします。1次電流は同方向に流れ続け、これによってハイサイドスイッチがオフになった後にローサイドスイッチのボディダイオードが順方向バイアスされます。コントローラがローサイドスイッチをオンにすると、このスイッチの両端の電圧降下はほぼゼロになります。ゼロ電圧スイッチング(ZVS)動作によって、スイッチング損失が低減します。DLがオンの場合は、1次電流は減少します。図3の(A)に示されるように、発振器クロックの立下りエッジが( $t_3$ )に達する前に1次電流がゼロ( $t_2$ )に達すると、コントローラは $t_2$ においてローサイドスイッチをオフにします。ハイサイドスイッチとローサイドスイッチはともに、 $t_3$ までオフ状態を維持します。

コントローラは、クロックの立下りエッジ( $t_3$ )でローサイドスイッチをオンにします。1次電流は他の方向に増加し、負の半サイクルを開始します。図3の(B)に示されるように、クロックの立下りエッジがゼロ交差に先行する場合、1次電流がゼロに達してから、負のサイクルを開始するためにグランド以下へと続くことが可能となるようにローサイドスイッチはオン状態を維持します。

# 固定周波数、ハーフブリッジCCFL インバータコントローラ

MAX8729

図3. 固定周波数動作タイミング図

# 固定周波数、ハーフブリッジCCFL インバータコントローラ

負の半サイクルの間に、コントローラは、 $t_4$ においてローサイドスイッチをオフにします。この後に、コントローラはZVS状態でハイサイドスイッチをオンにして、新たなサイクルが開始します。AとBのいずれの場合も、ZVS動作によって両方のパワースイッチの電源投入時のスイッチング損失が低減し、効率が向上します。

## 共振起動

MAX8729は、起動時に共振モードで動作します。共振動作ではインバータは、ランプが点灯するか、またはコントローラが過電圧保護を作動させるまで2次電圧を上昇させ続けます。共振モードでは、スイッチング周波数は共振タンク回路の自然共振周波数と同期されます。このタンク回路は、トランス漏洩インダクタンス、1次容量性分圧器、および2次共振コンデンサによって構成されています。同期化および位相シフト機能は、起動時にディセーブルされます。図4は、1次電流とゲート信号を示すタイミング図によって共振動作を示しています。共振モードでは、ハイサイドスイッチは正の半サイクルの初期にオンになります。1次電流が増加します。コントローラは $t_1$ においてハイサイドスイッチをオフにして、ランプ電流を制御します。1次電流は同方向に流れ続け、これによってハイサイドスイッチがオフになった後にローサイドスイッチのボティダイオードが順方向バイアスされます。コントローラがローサイドスイッチをオンすると、このスイッチの両端の電圧降下はほぼゼロになります。このZVS動作によって、スイッチング損失が低減します。DLがオンの場合は、コントローラがローサイドスイッチをオフにする $t_2$ まで、1次電流はゼロまで減少します。この後に、コントローラはZVS状態でハイサイドスイッチをオンにして、新たなサイクルが開始します。このアーキテクチャのZVS動作によって両方のパワースイッチの電源投入時のスイッチング損失が低減し、効率が向上します。

図4. 共振動作タイミング図

## ランプ電流レギュレーション

MAX8729はランプ電流制御ループを使って、CCFLに供給される電流を制御します。制御ループの中心は、図2におけるトランスコンダクタンスエラーアンプです。ACランプ電流は、ランプの低電圧端子と直列接続された検出抵抗によって検出されます。この抵抗の両端の電圧はIFB入力に供給され、内部で全波整流されます。トランスコンダクタンスエラーアンプは整流されたIFB電圧を790mV(typ)の内部リファレンスと比較して、エラー電流を生成します。エラー電流は、エラーアンプの出力(COMP)とグランドの間に接続されたコンデンサを充電/放電して、エラー電圧( $V_{COMP}$ )を生成します。次にハイサイドMOSFETのスイッチオン時間( $t_{ON}$ )を制御するために、 $V_{COMP}$ は内部ランプ信号と比較されます。

## トランス2次電圧制限

MAX8729は、起動時やオープンランプ障害時に2次電圧を制限して、トランスの2次巻線への電圧ストレスを低減します。トランス2次巻線のAC電圧は、容量性分圧器を通じて検出されます。分圧器のローサイドコンデンサの両端の電圧はVFB入力に供給され、内部で半波整流されます。過電圧コンパレータはVFB電圧を2.3V(typ)の内部スレッショルドと比較します。検出電圧が過電圧スレッショルドを超えると、MAX8729はCOMPコンデンサを放電する1.2mAの電流源をオンにします。COMP電圧が降下するにつれてハイサイドMOSFETのオン時間が短縮されるため、トランスの2次ピーク電圧が降下します。2次ピーク電圧が容量性分圧器で設定されるスレッショルドを下回ると、MAX8729はCOMPコンデンサの放電を停止します。このメカニズムを通じて、2次電圧が効率的に制限されます。

## ランプの起動

CCFLは、アバランシェモードで通常駆動されるガス放電管です。非イオン化ランプでイオン化を開始するには、印加電圧(点灯電圧)をランプでのイオン化の開始に必要なレベルまで上昇させる必要があります。例えば、標準的なCCFLの標準動作電圧は約650V<sub>RMS</sub>ですが、点灯電圧は最大1800V<sub>RMS</sub>にすることができます。

MAX8729独自の共振起動方式によって、信頼性の高い点灯が実現します。ランプがイオン化される前は、ランプインピーダンスは無限です。トランスの2次漏洩インダクタンスと高電圧並列コンデンサによって、無負荷時の共振周波数が決まります。無負荷時の共振回路は高Qを備えているため、ランプが点灯するか、またはコントローラが2次過電圧保護を作動させるまで、インバータは2次電圧を上昇させ続けます。

# 固定周波数、ハーフブリッジCCFL インバータコントローラ

MAX8729

電源投入時に $V_{COMP}$ は徐々に上昇し、ハイサイドMOSFETスイッチのデューティサイクルを増やし、ソフトスタートの判断基準を提供します。さらに、デバイスがイネーブルされた直後に、MAX8729は $V_{FB}$ を過電圧スレッショルド(2.3V, typ)まで充電します。 $V_{FB}$ のDC電圧は、起動時に内蔵抵抗を通じて徐々に放電されます。この機能は起動時の過電圧スレッショルドを徐々に上げることと同じです。このため、ソフトスタート動作がさらに改善します。ランプ電流が安定状態に到達すると、MAX8729は固定周波数動作に自動的に切り替わります。

## フィードフォワード制御およびドロップアウト動作

MAX8729は、ライントランジェントが発生すると、ランプ電流を厳格に制御するように設計されています。フィードフォワード制御によって、入力電圧( $V_{IN}$ )の変動に対してオン時間が瞬時に調整されます。この機能は入力電圧の変動に対する耐性を備え、広い入力電圧範囲にわたってループ補償を簡易化します。また、フィードフォワード制御によって、短いDPWMのオン時間に対するラインレギュレーションが向上し、起動トランジェントの入力電圧への依存度が低下します。

フィードフォワード制御は、 $V_{IN}$ が上昇する場合、内部電圧ランプレートを増加するように構成されています。これは、 $V_{COMP}$ でほぼ同じ信号レベルを維持しながら、 $t_{ON}$ を入力電圧の関数として変化させる効果を持ちます。補償コンデンサの両端の必要な電圧変化はごくわずかのため、入力電圧変動に対するコントローラの応答は実質的に瞬時です。

## デジタルPWM調光制御

MAX8729は、内蔵発振器または外部信号源からの低周波(100Hz~350Hz)デジタルPWM信号を使って

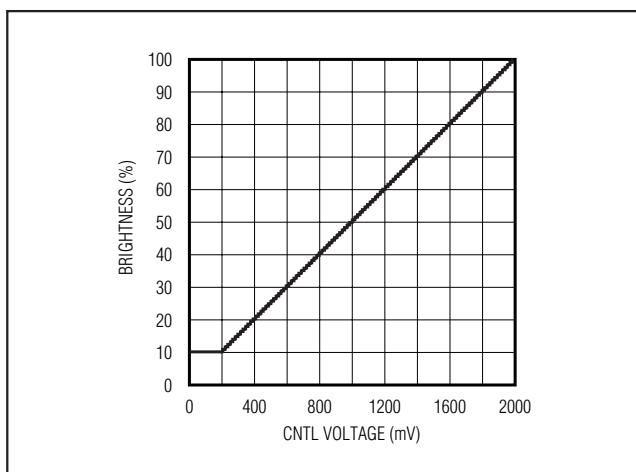

図5. 理論的輝度 対 制御電圧

ランプ電流のオン/オフを「チョッピング」することによって、CCFLの輝度を制御します。デジタルPWM動作で、 $COMP$ はランプ電流エンベロープの動きを制御します。デジタルPWMオンサイクルの初期に、ランプ電流フィードバック信号の平均値はレギュレーションポイントを下回るため、トランスクンダクタンスエラーアンプは電流を $COMP$ コンデンサにソースします。 $V_{COMP}$ が上昇するにつれてスイッチオン時間( $t_{ON}$ )が次第に増加し、ソフトスタートが行われます。デジタルPWMオンサイクルの終了時に、MAX8729は100μAの内部電流源をオンにします。電流源は $COMP$ コンデンサを直線的に放電し、 $t_{ON}$ を次第に減少し、ソフトストップが行われます。

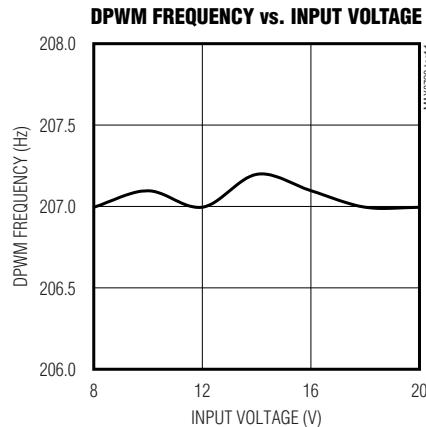

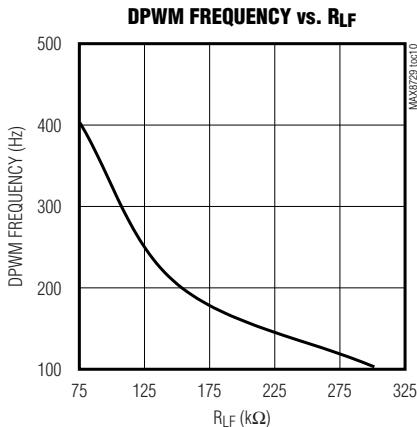

## 内蔵発振器の使用

$SEL$ 端子がグランドに接続されている場合は、MAX8729は内蔵発振器を使ってデジタルPWM信号を生成することができます。内蔵デジタルPWM発振器の周波数をLFとGNDの間に接続された抵抗を通じて調整することができます。デジタルPWM周波数は、次式から求められます。

$$f_{DPWM} = \frac{207\text{Hz} \times 150\text{k}\Omega}{R_{LF}}$$

DPWM周波数の調整可能な範囲は、100Hz~300Hzです( $R_{LF}$ は217kΩ~103kΩ)。

CCFLの輝度はDPWMデューティサイクルに比例します。このデューティサイクルは、 $CNTL$ 端子を通じて10%~100%に調整することができます。 $CNTL$ は0~2Vの使用可能な入力電圧範囲を備えるアナログ入力で、128の輝度レベルのいずれか1つを選択するように数値化されます。図5に示されるように、MAX8729は先頭から13のステップを無視するため、先頭の13ステップはすべて同じ輝度になります。 $V_{CNTL}$ が0~203mVの間にある場合は、DPWMのデューティサイクルは常に10%です。 $V_{CNTL}$ が203mVを超えると、 $CNTL$ での15.625mVの変動はDPWMデューティサイクルの0.78%の変動になります。 $V_{CNTL}$ が2V以上の場合は、DPWMデューティサイクルは常に100%です。

## 外部デジタルPWM信号の使用

外部デジタルPWM信号を使って輝度を制御するには、 $SEL$ を $V_{CC}$ に接続し、 $LSYNC$ を外部信号源に接続します。外部信号の周波数範囲は、 $R_{LF} = 150\text{k}\Omega$ で100Hz~300Hzの範囲です。このモードでは輝度制御入力 $CNTL$ はディセーブルされ、輝度は外部信号のデューティサイクルに比例します。外部信号のデューティサイクルが100%になると、CCFLは最大輝度に達します。外部信号のデューティサイクルが10%以下になると、CCFL輝度はそれに応じて調整されます。

# 固定周波数、ハーフブリッジCCFL インバータコントローラ

## ランプアウト保護

安全のために、MAX8729は、障害のあるランプやオープンCCFL管と短絡したIFB検出抵抗を検出するため、ランプ電流フィードバック(IFB)を監視します。「ランプ電流レギュレーション」の項に記載されているように、IFBの電圧は内部で全波整流されます。整流されたIFB電圧が790mVを下回る場合は、MAX8729はTFLTコンデンサを1 $\mu$ Aで充電します。TFLTの電圧が4Vを超えると、MAX8729はラッチオフします。通常のシャットダウンモードとは異なり、リニアレギュレータ出力( $V_{CC}$ )は5.3Vにとどまります。 $SHDN$ をトグルする、または入力電力をサイクルすると、デバイスが再起動します。

遅延期間の間、電流制御ループは、ハイサイドMOSFETのオン時間を増大することによって、ランプ電流レギュレーションを維持しようとします。オープン時にランプインピーダンスは非常に高いため、トランスの2次電圧は共振タンクの高Qファクタによって上昇します。2次電圧が過電圧スレッショルドを超えると、MAX8729はCOMPコンデンサを放電する1.2mAの電流源をオンにします。COMP電圧が下降するにつれて、ハイサイドMOSFETのオン時間は短縮され、2次電圧が下降します。このため、トランス2次巻線のピーク電圧は、ランプアウト遅延期間の間は制限値を超えません。

## 1次過電流保護

MAX8729は、サイクルごとに1次過電流保護を行います。電流検出アンプは、導通中のハイサイドおよびローサイドの両スイッチのドレイン-ソース間電圧を監視します。電圧が内部電流制限スレッショルド(400mV typ)を超える場合は、レギュレータはトランスの1次電流がさらに増加しないように1次側の向かい側のハイサイドスイッチをオフにします。

## 2次電流制限(ISEC)

トランスの高電圧端子とグランドの間に短絡や漏洩がある場合は、2次電流制限を通じてフェイルセーフ保護を行います。ISECは、トランスの低電圧2次端子とグランドの間に配置された検出抵抗の両端の電圧を監視します。ISEC電圧は内部で半波整流され、ISECレギュレーションスレッショルド(1.25V, typ)と連続的に比較されます。ISEC電圧がスレッショルドを超えるたびに、ブリッジのハイサイドスイッチのオン時間を短縮するために制御された電流がCOMPから引き出されます。同時に、MAX8729は126 $\mu$ Aの電流でTFLTコンデンサを充電します。TFLTの電圧が4Vを超えると、MAX8729はラッチオフします。通常のシャットダウンモードとは異なり、リニアレギュレータ出力( $V_{CC}$ )は5.3Vにとどまります。 $SHDN$ をトグルする、または入力電力をサイクルすると、デバイスが再起動します。

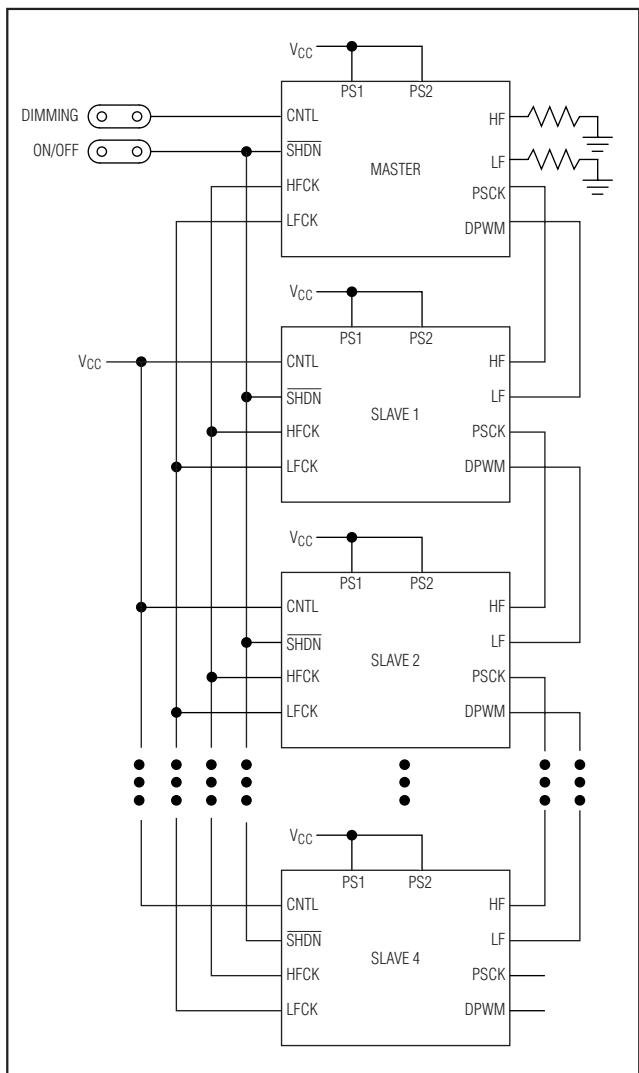

## デイジーチェーン動作での同期化 (HFCK, LFCK, PSCK, DPWM)

MAX8729は、複数のMAX8729の同期と位相シフトを可能にするデイジーチェーン動作をサポートしています。最大5つのMAX8729を図6に示すデイジーチェーン構成で接続することができます。CNTLを $V_{CC}$ に接続すると、デイジーチェーン動作がイネーブルされ、ICがスレーブモードになります。

図6. 5個のコントローラのデイジーチェーン動作

# 固定周波数、ハーフブリッジCCFL インバータコントローラ

MAX8729

表1. 位相シフトの設定

| PIN SETTING     |                 | PHASE SHIFT IN DEGREES |         |         |         |         | NO. OF PHASES |

|-----------------|-----------------|------------------------|---------|---------|---------|---------|---------------|

| PS2             | PS1             | MASTER                 | SLAVE 1 | SLAVE 2 | SLAVE 3 | SLAVE 4 |               |

| X               | X               | 0                      | N/A     | N/A     | N/A     | N/A     | 1             |

| GND             | GND             | 0                      | 180     | N/A     | N/A     | N/A     | 2             |

| GND             | V <sub>CC</sub> | 0                      | 120     | 240     | N/A     | N/A     | 3             |

| V <sub>CC</sub> | GND             | 0                      | 90      | 180     | 270     | N/A     | 4             |

| V <sub>CC</sub> | V <sub>CC</sub> | 0                      | 72      | 144     | 216     | 288     | 5             |

X = 任意

スイッチング周波数を同期させるには、スレーブICとマスタICのHFCK端子を相互に接続し、マスタICのPSCK端子をスレーブICのHF端子に接続します。DPWM周波数を同期させるには、スレーブICとマスタICのLFCK端子を相互に接続し、マスタICのDPWM端子をスレーブICのLF端子に接続します。

CNTL輝度制御はスレーブモードではディセーブルされます。マスタは調光信号をDPWM端子に送って、スレーブの輝度設定を直接制御します。

## デイジーチェーン動作での位相シフト (PS1、PS2)

MAX8729は、ゲートドライバおよびDPWM発振器の位相を調整する機能を備えています。この位相シフト機能を通じて入力RMSリップル電流が大幅に低減し、入力コンデンサの要件が緩和されます。位相シフトを2個のロジック入力端子(PS1およびPS2)を使って容易に設定することができます。これらの2個の端子を組み合わせると、72°、90°、120°、および180°の4つの位相シフトの選択が可能になります。位相シフトの選択は、デイジーチェーンで使用されるMAX8729の数に基づきます。

表1は、1、2、3、4、および5つの位相に対する位相シフトの推奨される選択を示しています。任意のマルチ位相回路の場合は、すべてのマスタおよびスレーブICはPS1、PS2に対して同じ設定を使用する必要があります。

表2は、全モードでのMAX8729の動作を要約しています。

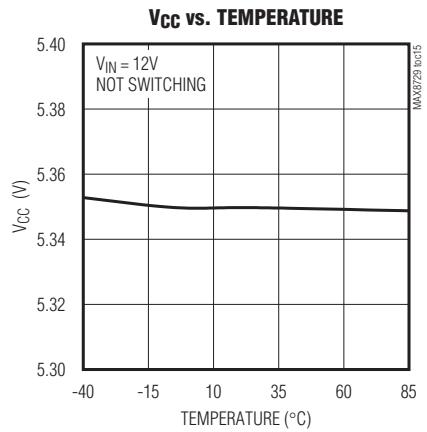

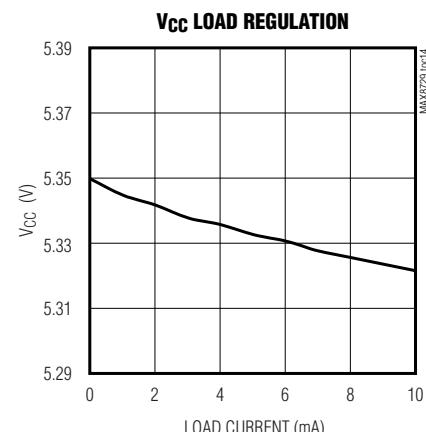

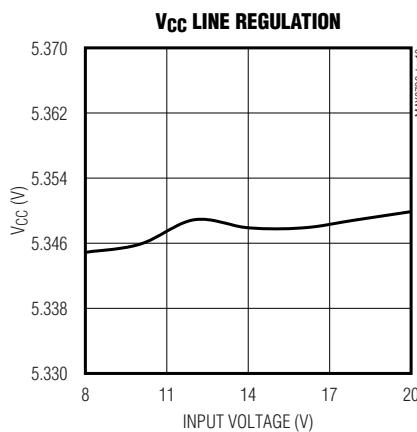

## リニアレギュレータ出力(V<sub>CC</sub>)

内蔵リニアレギュレータは、DC入力電圧を5.35V(typ)にステップダウンします。リニアレギュレータは、MAX8729の内部制御回路に電源を供給します。V<sub>CC</sub>をV<sub>DD</sub>に接続すると、V<sub>CC</sub>によってMOSFETゲートドライバに電源を供給することができます。また、V<sub>DD</sub>を外部電源から駆動することもできます。V<sub>CC</sub>電圧は、シャットダウン時には4.5Vに降下します。

## UVLO

MAX8729は、低電圧ロックアウト(UVLO)回路を内蔵しています。このUVLO回路は、V<sub>CC</sub>電圧を監視します。V<sub>CC</sub>が4.2V(typ)を下回ると、MAX8729はハイサイドおよびローサイドゲートドライバとともにディセーブルし、障害ラッチをリセットします。

## 低電力シャットダウン

MAX8729がシャットダウンモードに入ると、5.35Vのリニアレギュレータを除いてICの全機能がオフにされます。シャットダウン時には、リニアレギュレータの出力電圧は約4.5Vまで降下し、消費電流は6μA(typ)になります。シャットダウン時には、障害ラッチはリセットされます。SHDNをロジックローレベルにプルすると、デバイスをシャットダウンに移行させることができます。

# 固定周波数、ハーフブリッジCCFL インバータコントローラ

表2. 動作概要

| PIN NAME | MASTER MODE USING INTERNAL OSCILLATORS                    | MASTER MODE USING EXTERNAL SYNC SIGNAL (SYNC ONLY)                                                                                 | MASTER MODE USING EXTERNAL SYNC SIGNAL (SYNC AND DIMMING)                                                                                          | SLAVE MODE                                                                       |

|----------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| CNTL     | An analog voltage on CNTL sets the brightness.            | An analog voltage on CNTL sets the brightness.                                                                                     | CNTL control is disabled. The external signal controls the brightness. Connect CNTL to an analog voltage in case the external sync signal is lost. | Connect CNTL to V <sub>CC</sub> . Brightness is controlled by the master.        |

| SEL      | Connect SEL to GND.                                       | Connect SEL to GND.                                                                                                                | Connect SEL to V <sub>CC</sub> .                                                                                                                   | Don't care.                                                                      |

| HF       | Connect a resistor to GND to set the switching frequency. | Switching frequency is controlled by the external sync signal. Connect a resistor to GND in case the external sync signal is lost. | Switching frequency is controlled by the external sync signal. Connect a resistor to GND in case the external sync signal is lost.                 | Connect to the PSCK pin of its master controller.                                |

| LF       | Connect a resistor to GND to set DPWM frequency.          | DPWM frequency is determined by the external sync signal. Connect a resistor to GND in case the external sync signal is lost.      | DPWM frequency is determined by the external sync signal. Connect a resistor to GND in case the external sync signal is lost.                      | Connect to the DPWM pin of its master controller.                                |

| HFCK     | Connect to the HFCK pin of its slave controller.          | Connect to the HFCK pin of its slave controller.                                                                                   | Connect to the HFCK pin of its slave controller.                                                                                                   | Connect to the HFCK pin of its master controller. Connect a 1MΩ resistor to GND. |

| LFCK     | Connect to the LFCK pin of its slave controller.          | Connect to the LFCK pin of its slave controller.                                                                                   | Connect to the LFCK pin of its slave controller.                                                                                                   | Connect to the LFCK pin of its master controller. Connect a 1MΩ resistor to GND. |

| HSYNC    | Not used. Connect to GND.                                 | Connect to a high-frequency external signal to sync the switching frequency.                                                       | Connect to a high-frequency external signal to sync the switching frequency.                                                                       | Not used. Connect to GND.                                                        |

| LSYNC    | Not used. Connect to GND.                                 | Connect a low-frequency external signal to sync the digital PWM frequency.                                                         | Connect a low-frequency external signal to sync the digital PWM frequency. The duty cycle of the external signal determines the brightness.        | Not used. Connect to GND.                                                        |

| PSCK     | Connect to the HF pin of its slave controller.            | Connect to the HF pin of its slave controller.                                                                                     | Connect to the HF pin of its slave controller.                                                                                                     | Connect to the HF pin of its slave controller.                                   |

| DPWM     | Connect to the LF pin of its slave controller.            | Connect to the LF pin of its slave controller.                                                                                     | Connect to the LF pin of its slave controller.                                                                                                     | Connect to the LF pin of its slave controller.                                   |

# 固定周波数、ハーフブリッジCCFL インバータコントローラ

MAX8729

## アプリケーション情報

### MOSFET

MAX8729には、トランス1次側を駆動するフルブリッジインバータ回路を構成するのに2個の外付けnチャネルパワーMOSFETが必要です。正の半サイクルと負の半サイクルは対称的であるため、同じ種類のMOSFETをハイサイドおよびローサイドスイッチに使用する必要があります。MOSFETを選択する場合は、電圧定格、電流定格、オン抵抗( $R_{DS(ON)}$ )、総ゲートチャージ、および電力損失を重視します。

インバータの最大入力電圧より少なくとも25%高い電圧定格のMOSFETを選択します。例えば、最大入力電圧が24Vの場合は、MOSFETの電圧定格は30V以上にする必要があります。MOSFETの電流定格は、最低入力電圧と最大輝度におけるピーク1次電流よりも高くする必要があります。次式を使って、1次ピーク電流 $|I_{PEAK\_PRI}|$ を推計します。

$$|I_{PEAK\_PRI}| = \frac{\sqrt{2} \times P_{OUT\_MAX}}{V_{IN\_MIN} \times \eta}$$

ここで $P_{OUT\_MAX}$ は最大出力電力で、また $V_{IN\_MIN}$ は最低入力電圧であり、最低入力電圧での推定効率です。ハーフブリッジが4個のCCFLを駆動し、各ランプの最大出力電力が4.5Wと仮定すると、総最大出力電力は18Wです。最低入力電圧が8Vで、推定効率がその入力において75%の場合は、ピーク1次電流は約4.3Aです。このため、DC電流定格が5A以上のパワーMOSFETで十分です。

レギュレータは両方のMOSFETのオン状態のドレイン-ソース間電圧を検出し、トランス1次電流を検出するため、MOSFETの $R_{DS(ON)}$ が低くなると電流制限値が高くなります。このため、伝導損失を最低限に抑えるために低 $R_{DS(ON)}$ のnチャネルMOSFETを選択し、1次電流制限値を適切なレベルに維持する必要があります。次式を使って、1次電流制限値の最大および最低値を推計します。

$$I_{LIM\_MIN} = \frac{320\text{mV}}{R_{DS(ON)\_MAX}}$$

$$I_{LIM\_MAX} = \frac{480\text{mV}}{R_{DS(ON)\_MIN}}$$

両方のMOSFETは $V_{IN\_MIN}$ および $V_{IN\_MAX}$ におけるスイッチング損失に伝導損失を加えた値を消費可能である必要があります。両項を算出します。理想的には、 $V_{IN(MIN)}$ の損失が $V_{IN(MAX)}$ の損失とほぼ同じで、中間では損失が低減する必要があります。 $V_{IN(MIN)}$ の損失が $V_{IN(MAX)}$ の損失に比べて大幅に大きい場合は、MOSFETのサイズの増大を検討してください。逆に $V_{IN(MAX)}$ の損失が $V_{IN(MIN)}$ の損失に比べて大幅に大きい場合は、寄生容量がより低いMOSFETの選択を検討してください。 $V_{IN}$ が広範囲にわたって変動しない場合は、最低電力損失は、伝導損失がスイッチング損失と等しいところで発生します。

次式を使って、2個のMOSFETの総伝導電力損失を算出します。

$$PD_{CONDUCT} = |I_{PRI}|^2 \times R_{DS(ON)}$$

ここで、 $|I_{PRI}|$ は、次式によって算出された1次電流です。

$$|I_{PRI}| = \frac{P_{OUT\_MAX}}{\eta \times V_{IN}}$$

両方のMOSFETはZVS状態でオンになります。このためMOSFETに関連するスイッチング電力損失はありません。ただし、MOSFETがターンオフする時、電流はピークに達します。次式を使って、2個のMOSFETの総ターンオフスイッチング電力損失を算出します。

$$PD_{SWITCH} = \frac{\sqrt{2} \times C_{RSS} \times V_{IN}^2 \times f_{SW} \times |I_{PRI}|}{|I_{GATE}|}$$

ここで $C_{RSS}$ はMOSFETの帰還容量で、 $|I_{GATE}|$ はMOSFETがターンオフ中のピークゲート-駆動シンク電流です。

# 固定周波数、ハーフブリッジCCFL インバータコントローラ

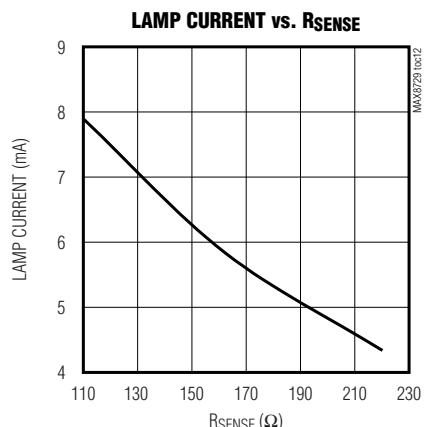

## ランプ電流の設定

MAX8729は、ランプの低電圧端子とグランドの間に接続された抵抗R1(図1)を流れるランプ電流を検出します。R1の両端の電圧はIFB入力に供給され、内部で全波整流されます。MAX8729は、整流されたIFB電圧の平均値を安定化して、必要とされるランプ電流を制御します。RMSランプ電流を設定するために、以下のようにR1を決定します。

$$R1 = \frac{\pi \times 790\text{mV}}{2\sqrt{2} \times I_{LAMP(RMS)}}$$

ここで、 $I_{LAMP(RMS)}$ は必要とされるRMSランプ電流で、790mVは「電気的特性(Electrical Characteristics)」表に規定されたIFBレギュレーションポイントの標準値です。RMSランプ電流を6mAに設定するには、R1の値を148Ωにする必要があります。最も近い標準的な1%抵抗は、147Ωと150Ωです。ランプ電流波形の正確な形状は、ランプの寄生分に依存します。得られる波形は不完全な正弦波波形であり、予測困難なRMS値を持っています。真の高周波RMS電流計(Yokogawa 2016など)を使ってRMS電流を測定し、R1を最終調整する必要があります。検出抵抗とランプの低電圧端子の間にこの電流計を挿入して、実RMS電流を測定します。

## 2次電圧制限値の設定

MAX8729は、起動およびランプアウト障害時にトランスの2次電圧を制限します。2次電圧は、C3およびC4で構成される容量性分圧器を通じて検出されます(図1)。VFBの電圧は、CCFL電圧に比例します。並列共振コンデンサC3の選択については、「トランス設計および共振部品の選択」の項に記載されています。C3の値が小さくなると、循環電流の減少によって効率が向上します。C3が小さすぎると、共振動作はパネルの寄生容量から影響を受けます。このため、C3は通常、10pF~18pFの間で選択されます。C3の値を設定したら、必要とされる最大RMS 2次電圧 $V_{LAMP(RMS)}_{MAX}$ に基づいてC4を選択します。

$$C4 = \frac{\sqrt{2} \times V_{LAMP(RMS)}_{MAX}}{2.34V} \times C3$$

ここで、ランプがオープン状態の場合は2.34VがVFBピーク電圧の標準値です。C3を12pFに設定し、最大RMS2次電圧を1800Vに設定するには、C4は13nF以下である必要があります。

## 2次電流制限値の設定

IFB検出抵抗が短絡、またはトランス2次電流がR1を通過せずにグランドに到達した場合でも、MAX8729は2次電流を制限します。ISECは、トランス2次巻線の低電圧端子とグランドの間に接続された検出抵抗R2の両端の電圧を監視します。次式を使って、R2の値を決定します。

$$R2 = \frac{1.28V}{\sqrt{2} \times I_{SEC(RMS)}_{MAX}}$$

ここで、 $I_{SEC(RMS)}_{MAX}$ は障害状態時の必要とされる最大RMSトランス2次電流であり、1.28Vは2次側が短絡している場合のISECのピーク電圧の標準値です。図1の回路の最大RMS 2次電流を22mAに設定するには、R2を40.2Ωに設定します。

## トランス設計および共振部品の選択

トランスは、共振タンク回路の中で最も重要な部品です。トランス設計の最初のステップは、トランスの巻数比の決定です。この比は、最低電源電圧でCCFL動作電圧に対応するのに十分な大きさである必要があります。以下のように、トランスの巻数比Nを算出することができます。

$$N \geq \frac{V_{LAMP(RMS)}}{0.45 \times V_{IN(MIN)}}$$

ここで、 $V_{LAMP(RMS)}$ は標準動作時の最大RMSランプ電圧、 $V_{IN(MIN)}$ は最低DC入力電圧です。標準動作時の最大RMSランプ電圧が800V、最低DC入力電圧が10Vの場合は、巻数比は178以上である必要があります。

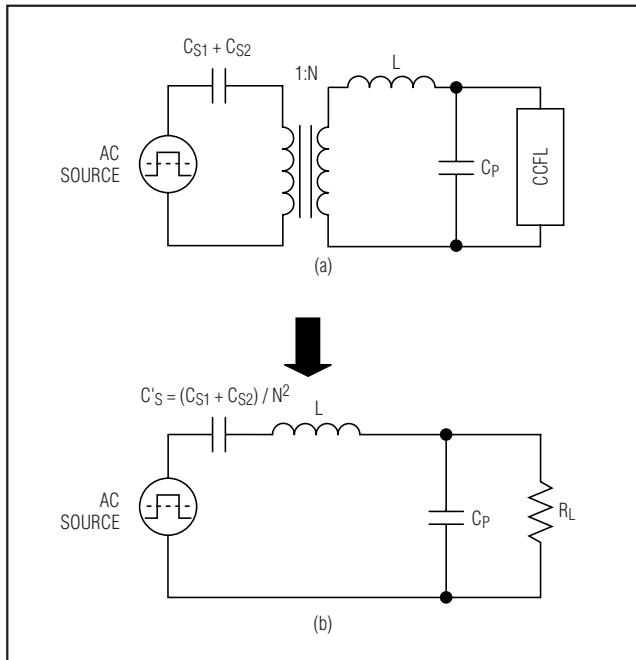

設計手順の次のステップは、共振周波数がHF抵抗で設定されるスイッチング周波数に近くなるように共振タンクを設計することです。スイッチング周波数が共振周波数に近くなると、ランプ電流は正弦波に近づきます。共振周波数は、1次容量性分圧器 $C_{S1}$ と $C_{S2}$ 、2次並列コンデンサ $C_p$ 、トランス2次漏洩インダクタンスL、およびCCFLランプによって決定されます。簡略化されたCCFLインバータ回路が図7のaに示されています。フルブリッジパワー段が簡略化され、方形波AC電源として表されています。トランスを取り除くと、共振タンク回路を図7のbまでさらに簡略化することができます。 $C_S$ は2次側に反映される1次容量性分圧器の容量であり、Nはトランスの巻数比です。

# 固定周波数、ハーフブリッジCCFL インバータコントローラ

MAX8729

図7. 簡略CCFLインバータ回路

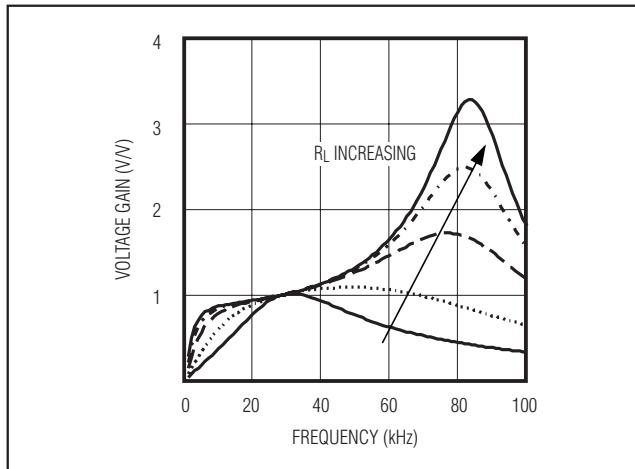

図8は、各負荷状態における共振タンクの電圧利得の周波数応答を示しています。1次側直列コンデンサは $1\mu\text{F}$ 、2次側並列コンデンサは $15\text{pF}$ 、トランスの巻数比は $1:78$ 、そして2次側漏洩インダクタンスは $260\text{mH}$ です。周波数応答には、 $f_S$ と $f_p$ の2つのピークがあることに注意してください。 $f_S$ は、2次側の漏洩インダクタンス( $L$ )と2次側に反映される直列コンデンサ( $C'_S$ )によって決定される直列共振ピークです。

$$f_S = \frac{1}{2\pi\sqrt{LC'_S}}$$

$f_p$ は、2次側の漏洩インダクタンス( $L$ )、並列コンデンサ( $C_P$ )、および2次側に反映される直列コンデンサ( $C'_S$ )によって決定される並列共振ピークです。

$$f_p = \frac{1}{2\pi\sqrt{L\frac{C'_S C_P}{C'_S + C_P}}}$$

実際の共振周波数は、これらの2つの共振ピーク間にあります。ランプがオフのときは、共振タンクの動作点はランプの無限インピーダンスによって並列共振ピークに

図8. 共振タンクの周波数応答

近くなります。この回路は並列負荷共振コンバータの特性を示します。並列負荷共振動作中はインバータは電圧源のように動作し、必要な点灯電圧を生成します。理論的には、ランプがイオン化されるか、またはICの2次電圧制限値に達するまで、共振コンバータの出力電圧が上昇します。ランプがイオン化されると、等価負荷抵抗が急減し、動作点は直列共振ピークに近づきます。直列共振動作中は、インバータは電流源のように動作します。

CCFLトランスの漏洩インダクタンスは、共振タンクの設計において重要なパラメータです。漏洩インダクタンスの値は、大きな許容値と、各製造バッチ間で大きなばらつきを持つ可能性があります。漏洩インダクタンス要件についてはトランスのベンダーと直接連携することを推奨します。2次漏洩インダクタンスが $200\text{mH} \sim 350\text{mH}$ にあるときに、MAX8729は最適に動作します。1次容量性分圧器 $C_1$ および $C_2$ によって最低動作周波数が設定され、この周波数は直列共振ピーク周波数の約2倍です。以下の式によって選択します。

$$C_1 = C_2 \leq \frac{N^2}{8\pi^2 \times f_{MIN}^2 \times L}$$

ここでは、 $f_{MIN}$ は最低動作周波数範囲です。図1の回路で、トランスの巻数比は178および2次漏洩インダクタンスは約 $300\text{mH}$ です。最低共振周波数を $40\text{kHz}$ に設定するには、 $C_1$ および $C_2$ に $2.2\mu\text{F}$ 以下のコンデンサを使用します。

# 固定周波数、ハーフブリッジCCFL インバータコントローラ

並列コンデンサC3によって最高動作周波数が設定され、この周波数は並列共振ピーク周波数でもあります。以下の式によって選択します。

$$C_3 \leq \frac{C_1 + C_2}{4\pi^2 \times f_{MAX}^2 \times L \times C_S - N^2}$$

図1の回路では、最高共振周波数は70kHz、C1およびC2は2.2μF、2次漏洩インダクタンスは約300mHです。このため、C3には12pF以上のコンデンサを使用します。

動作周波数の選択時には、トランスクアの飽和も考慮する必要があります。1次巻線は、どの動作状態でもトランスクアの飽和を防ぐために十分な巻数である必要があります。次式を使って、1次巻線の巻数N1の最低数を算出します。

$$N1 > \frac{D_{MAX} \times V_{IN(MAX)}}{B_S \times A \times f_{MIN}}$$

ここで、D<sub>MAX</sub>はハイサイドスイッチの最大デューティサイクル(約0.8)、V<sub>IN(MAX)</sub>は最大DC入力電圧、B<sub>S</sub>はコアの飽和磁束密度、そしてAはコアの最小断面積です。

## COMPコンデンサの選択

COMPコンデンサは、ランプ電流レギュレーションを維持しながら、起動時および入力電圧の変更に起因する過渡期間に使用される電流レギュレーションループの速度を設定します。安定した動作を維持するために、COMPコンデンサ(C<sub>COMP</sub>)は少なくとも3.3nFである必要があります。

「デジタルPWM調光制御」の項で述べたように、COMPコンデンサはデジタルPWM動作でランプ電流エンベロープの変動も制限します。デジタルPWMオンサイクルの終了時に、MAX8729は100μAの内部電流源をオンにして、COMPコンデンサを直線的に放電します。立下り時間を設定、は次式を使用します。

$$C_{COMP} = \frac{100\mu A \times t_{FALL}}{1.5V}$$

ここで、t<sub>FALL</sub>はランプ電流エンベロープの立下り時間であり、1.5VはCOMP電圧のダイナミックレンジです。デジタルPWMオンサイクルの開始時にCOMPコンデンサはトランスクンダクタンスエラーアンプによって充電されるため、充電電流は一定ではありません。平均充電電流は約30μAであるため、立上り時間は立下り時間より約3倍長くなっています。

## 障害遅延時間の設定

TFLTコンデンサによって、オープンランプ障害と2次短絡障害の遅延時間が決定されます。MAX8729はオープンランプ障害中には1μAの電流源でTFLTコンデンサを充電し、2次短絡障害中には126μAの電流源でTFLTコンデンサを充電します。このため、2次短絡の障害遅延時間は、オープンランプ障害の遅延時間に比べ約100分の1に短くなっています。TFLTの電圧が4Vに達すると、MAX8729は障害ラッチをセットします。オープンランプ障害遅延(T<sub>OPEN\_LAMP</sub>)と2次短絡障害遅延(T<sub>SEC\_SHORT</sub>)を算出には次式を使用します。

$$T_{OPEN\_LAMP} = \frac{C_{TFLT} \times 4V}{1\mu A}$$

$$T_{SEC\_SHORT} = \frac{C_{TFLT} \times 4V}{126\mu A}$$

## ブートストラップコンデンサ

ハイサイドゲートドライバはブートストラップ回路によって電源供給されます。MAX8729はブートストラップダイオードを内蔵しているため、0.1μFのブートストラップコンデンサが1個だけ必要です。ブートストラップ回路を構成するために、コンデンサをLXとBSTの間に接続します。

## レイアウトのガイドライン

安定した動作を達成するには、綿密なプリント基板のレイアウトが重要となります。回路の高電圧部とスイッチング部には特に注意が必要です。レイアウトの高電圧部を制御回路から十分に離す必要があります。適切なプリント基板レイアウトを行うために、以下のガイドラインに従ってください。

- 1) 大電流経路は、特にグランド端子部で短く幅広にします。これは、安定したジッタのない動作と高効率を実現するのに不可欠です。

- 2) 電源グランドとアナロググランドに星形グランド構成を採用します。電源グランドとアナロググランドは十分に離す必要があります、星形の中心でのみ接続します。この中心部は、アナロググランド端子(GND)に配置する必要があります。これらのグランドに独立した銅箔アイランドを使用すると、この作業を容易にすることができます。未使用のアナロググランドは、V<sub>CC</sub>、COMP、HF、LF、およびTFLTに使用します。

# 固定周波数、ハーフブリッジCCFL インバータコントローラ

MAX8729

- 3)高速スイッチングノードは、影響を受けやすいアナログ領域( $V_{CC}$ 、COMP、HF、LF、およびTFLT)から離して配線します。すべてのピンストラップ制御入力は、電源グランドや $V_{DD}$ ではなく、アナロググランドまたは $V_{CC}$ に接続します。

- 4)他の信号経路と共に用していない専用配線を使って、デカップリングコンデンサをICにできる限り近接して $V_{CC}$ とGNDの間に実装します。

- 5)LXからGNDおよびINからLXの電流検出経路は、電流制限精度を保証するためにケルビン検出接続によって構築する必要があります。8ピンSOPのMOSFETの場合は、GNDおよびLXを8ピンSOPパッケージの内部(下部)に接続し、最上の銅層を使って外側からMOSFETに電源を接続することを推奨します。

- 6)フィードバック接続は短く、かつ直線にします。IFB、VFB、およびISEC接続は、高電圧配線とトランスからできる限り遠くに離す必要があります。

- 7)トランス2次側の高電圧配線間の間隔は、できる限り広くする必要があります。また高電圧配線は、容量カップリング損失を防ぐために隣接するグラウンドプレーンからも離す必要があります。

- 8)トランス2次側の容量性分圧器への各配線は、アーク放電を防ぐために間隔を広くする必要があります。場合によっては、これらの配線を基板の反対側に移したほうが得策です。

## ピン配置

## チップ情報

TRANSISTOR COUNT: 7531

PROCESS: BiCMOS

# 固定周波数、ハーフブリッジCCFL インバータコントローラ

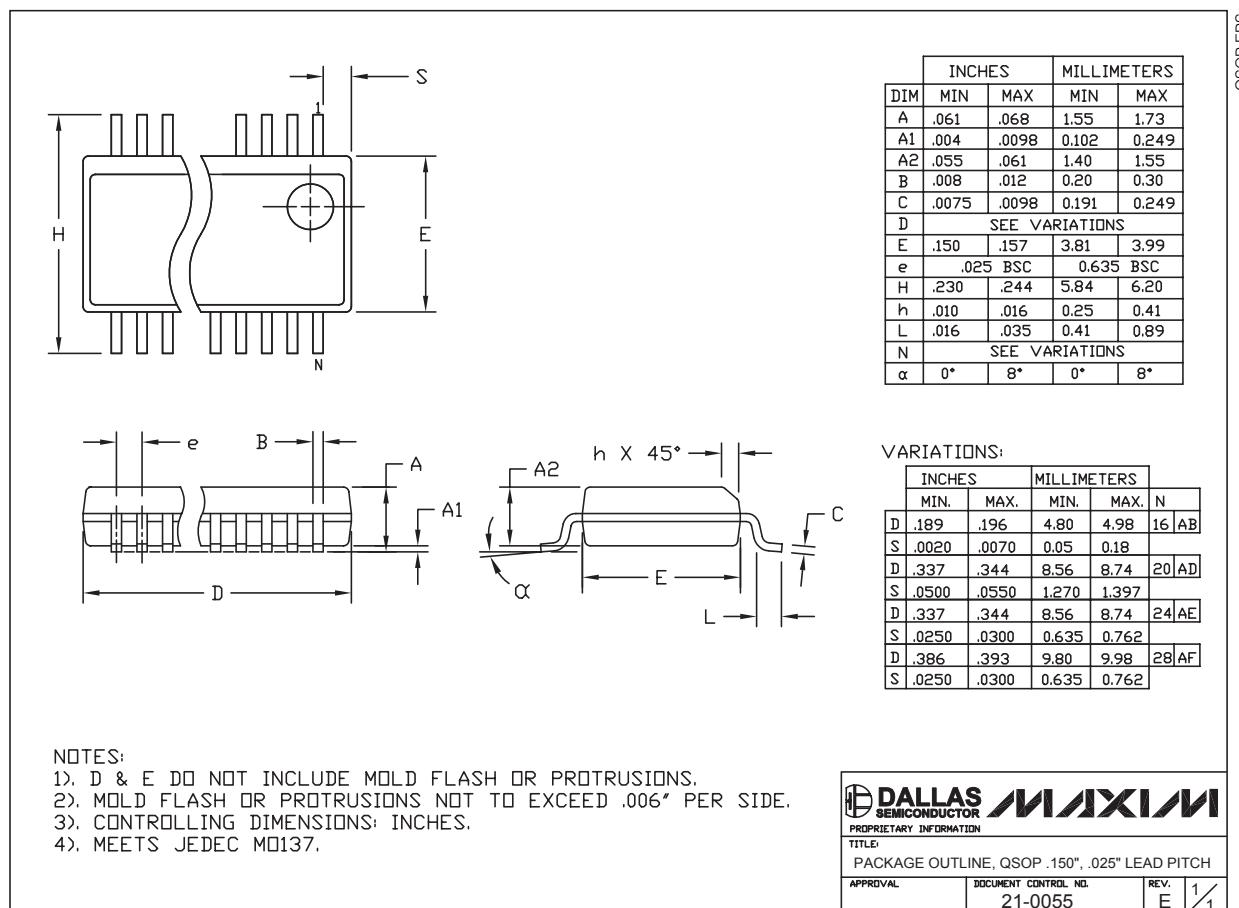

## パッケージ

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、[japan.maxim-ic.com/packages](http://japan.maxim-ic.com/packages)をご参照下さい。)

### NOTES:

- 1). D & E DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

- 2). MOLD FLASH OR PROTRUSIONS NOT TO EXCEED .006" PER SIDE.

- 3). CONTROLLING DIMENSIONS: INCHES.

- 4). MEETS JEDEC MO137.

マキシム・ジャパン株式会社

〒169-0051 東京都新宿区西早稲田3-30-16(ホリゾン1ビル)

TEL. (03)3232-6141 FAX. (03)3232-6149

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。マキシムは随时予告なく回路及び仕様を変更する権利を留保します。

26 **Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600**

© 2005 Maxim Integrated Products, Inc. All rights reserved. **MAXIM** is a registered trademark of Maxim Integrated Products, Inc.