# 8次、ローパス、バタワース、 スイッチトキャパシタフィルタ

**MAX7480**

## 概要

MAX7480は+5V単一電源で動作する8次ローパス、バタワース式スイッチトキャパシタフィルタ(SCF)です。このデバイスは消費電流が僅か2.9mAで、コーナ周波数として1Hz~2kHzが可能であるため、ローパワーポストDACフィルタリング及びアンチエイリアシングアプリケーションに最適です。MAX7480は消費電流を0.2µAに低減するシャットダウンモードを備えています。

クロッキングは、外部コンデンサを使ったセルフクロッキングと、コーナ周波数を厳密に制御するための外部クロッキングが可能です。オフセット調節ピンにより、DC出力レベルの調節が可能です。

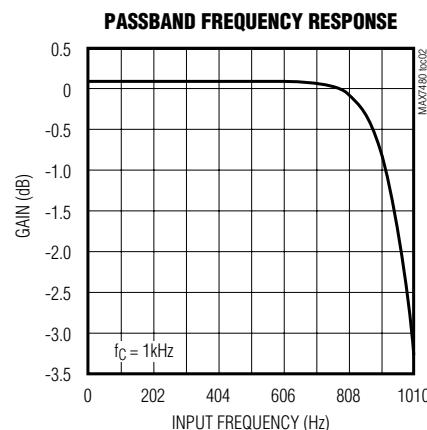

MAX7480バタワースフィルタは極めて平坦なパスバンド応答を提供します。固定応答のため、クロック周波数を選択する設計作業が単純化されます。

## アプリケーション

- ADCアンチエイリアシング

- ポストDACフィルタリング

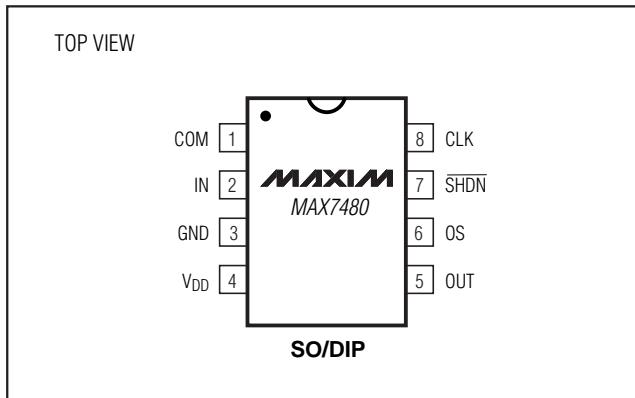

## ピン配置

## 特長

- ◆ 8次ローパスバタワースフィルタ

- ◆ 低ノイズ・低歪み : -73dB(THD+ノイズ)

- ◆ コーナ周波数はクロック同調可能 : 1Hz~2kHz

- ◆ クロック・コーナ比 : 100:1

- ◆ 単一電源 : +5V

- ◆ 低電力

- 2.9mA(動作モード)

- 0.2µA(シャットダウンモード)

- ◆ パッケージ : 8ピンSOP/DIP

- ◆ 低出力オフセット : ±5mV

## 型番

| PART       | TEMP. RANGE    | PIN-PACKAGE   |

|------------|----------------|---------------|

| MAX7480ESA | -40°C to +85°C | 8 SO          |

| MAX7480EPA | -40°C to +85°C | 8 Plastic DIP |

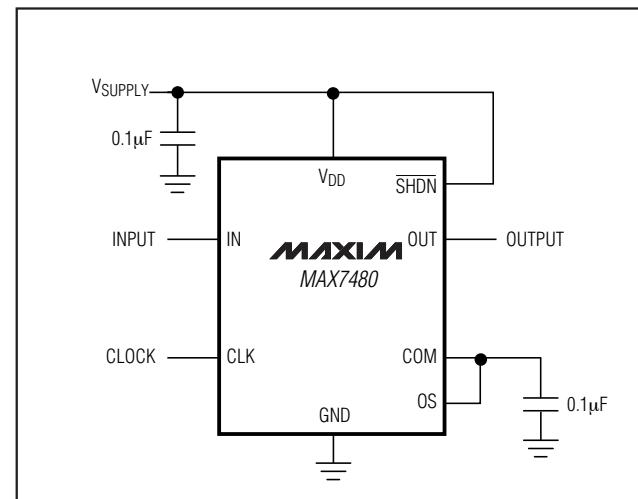

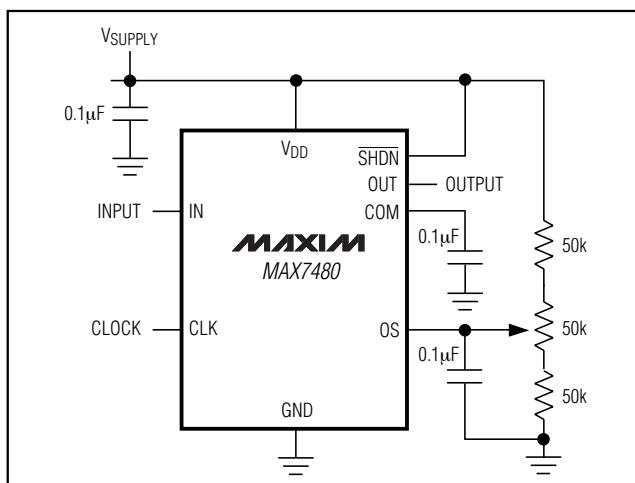

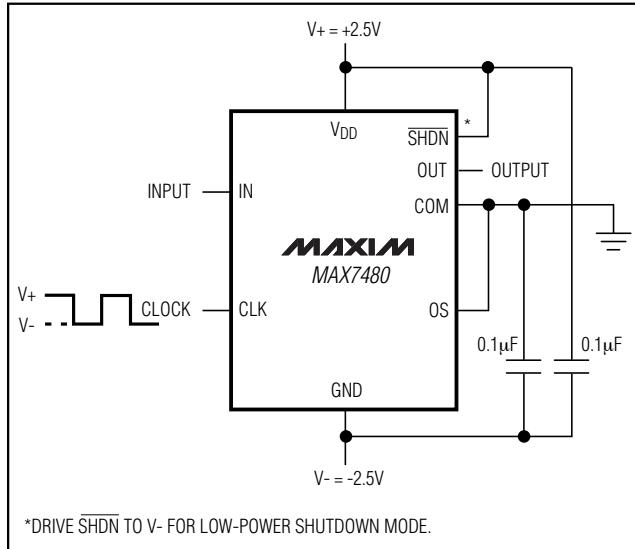

## 標準動作回路

# 8次、ローパス、バタワース、 スイッチトキャパシタフィルタ

**MAX7480**

## ABSOLUTE MAXIMUM RATINGS

|                                                                                                        |                                   |

|--------------------------------------------------------------------------------------------------------|-----------------------------------|

| V <sub>DD</sub> to GND .....                                                                           | -0.3V to +6V                      |

| IN, OUT, COM, OS, CLK .....                                                                            | -0.3V to (V <sub>DD</sub> + 0.3V) |

| SHDN .....                                                                                             | -0.3V to +6V                      |

| OUT Short-Circuit Duration .....                                                                       | 1sec                              |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)<br>8-Pin SO (derate 5.88mW/°C above +70°C) ..... | 471mW                             |

| 8-Pin DIP (derate 9.09mW/°C above +70°C) .....                                                         | 727mW                             |

|                                           |                 |

|-------------------------------------------|-----------------|

| Operating Temperature Range .....         | -40°C to +85°C  |

| Storage Temperature Range .....           | -65°C to +150°C |

| Lead Temperature (soldering, 10sec) ..... | +300°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

(V<sub>DD</sub> = +5V, filter output measured at OUT, 10kΩ || 50pF load to GND at OUT, OS = COM, 0.1μF from COM to GND, SHDN = V<sub>DD</sub>, f<sub>CLK</sub> = 100kHz, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                                    | SYMBOL                            | CONDITIONS                                                                         | MIN                          | TYP                          | MAX | UNITS  |

|----------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------|------------------------------|------------------------------|-----|--------|

| <b>FILTER CHARACTERISTICS</b>                |                                   |                                                                                    |                              |                              |     |        |

| Corner Frequency                             | f <sub>C</sub>                    | (Note 1)                                                                           | 0.001                        | to 2                         |     | kHz    |

| Clock-to-Corner Ratio                        | f <sub>CLK</sub> / f <sub>C</sub> |                                                                                    | 100:1                        |                              |     |        |

| Clock-to-Corner Tempco                       |                                   |                                                                                    | 10                           |                              |     | ppm/°C |

| Output Voltage Range                         |                                   |                                                                                    | 0.25                         | V <sub>DD</sub> - 0.25       |     | V      |

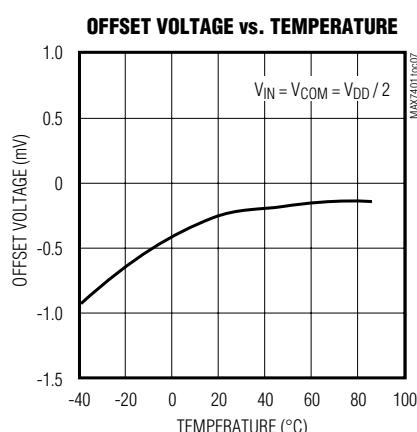

| Output Offset Voltage                        | V <sub>OFFSET</sub>               | V <sub>IN</sub> = V <sub>COM</sub> = V <sub>DD</sub> / 2                           | ±5                           | ±25                          |     | mV     |

| DC Insertion Gain with Output Offset Removed |                                   | V <sub>COM</sub> = V <sub>DD</sub> / 2 (Note 2)                                    | -0.1                         | 0.15                         | 0.3 | dB     |

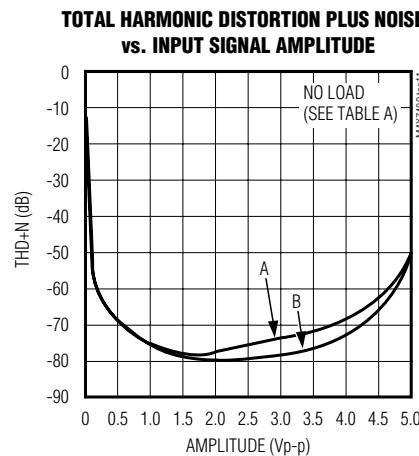

| Total Harmonic Distortion plus Noise         | THD+N                             | f <sub>IN</sub> = 200Hz, V <sub>IN</sub> = 4Vp-p,<br>measurement bandwidth = 22kHz | -73                          |                              |     | dB     |

| OS Voltage Gain to OUT                       | A <sub>OS</sub>                   |                                                                                    | 1                            |                              |     | V/V    |

| Input Voltage Range at OS                    | V <sub>OS</sub>                   |                                                                                    | V <sub>COM</sub> ± 0.1       |                              |     | V      |

| COM Voltage Range                            | V <sub>COM</sub>                  | Input, COM externally driven                                                       | V <sub>DD</sub> / 2<br>- 0.5 | V <sub>DD</sub> / 2<br>+ 0.5 |     |        |

|                                              |                                   | Output, COM internally biased                                                      | V <sub>DD</sub> / 2<br>- 0.2 | V <sub>DD</sub> / 2<br>+ 0.2 |     | V      |

| Input Resistance at COM                      | R <sub>COM</sub>                  |                                                                                    | 75                           | 125                          |     | kΩ     |

| Clock Feedthrough                            |                                   |                                                                                    | 10                           |                              |     | mVp-p  |

| Resistive Output Load Drive                  | R <sub>L</sub>                    |                                                                                    | 10                           | 1                            |     | kΩ     |

| Maximum Capacitive Load at OUT               | C <sub>L</sub>                    |                                                                                    | 50                           | 500                          |     | pF     |

| Input Leakage Current at COM                 |                                   | SHDN = GND, V <sub>COM</sub> = 0 to V <sub>DD</sub>                                | ±0.1                         | ±10                          |     | μA     |

| Input Leakage Current at OS                  |                                   | V <sub>OS</sub> = 0 to (V <sub>DD</sub> - 1V) (Note 3)                             | ±0.1                         | ±10                          |     | μA     |

| <b>CLOCK</b>                                 |                                   |                                                                                    |                              |                              |     |        |

| Internal Oscillator Frequency                | f <sub>Osc</sub>                  | C <sub>Osc</sub> = 1000pF (Note 4)                                                 | 40                           | 53                           | 67  | kHz    |

| Clock Input Current                          | I <sub>CLK</sub>                  | V <sub>CLK</sub> = 0 or 5V                                                         | ±24                          | ±40                          |     | μA     |

| Clock Input High                             | V <sub>IH</sub>                   |                                                                                    | V <sub>DD</sub> - 0.5        |                              |     | V      |

| Clock Input Low                              | V <sub>IL</sub>                   |                                                                                    | 0.5                          |                              |     | V      |

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{DD} = +5V$ , filter output measured at OUT,  $10k\Omega \parallel 50pF$  load to GND at OUT, OS = COM,  $0.1\mu F$  from COM to GND,  $\overline{SHDN} = V_{DD}$ ,  $f_{CLK} = 100kHz$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ .)

| PARAMETER                    | SYMBOL                | CONDITIONS                                              | MIN            | TYP      | MAX | UNITS   |

|------------------------------|-----------------------|---------------------------------------------------------|----------------|----------|-----|---------|

| <b>POWER REQUIREMENTS</b>    |                       |                                                         |                |          |     |         |

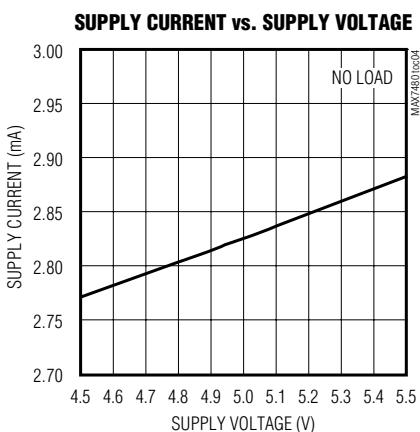

| Supply Voltage               | $V_{DD}$              |                                                         | 4.5            | 5.5      |     | V       |

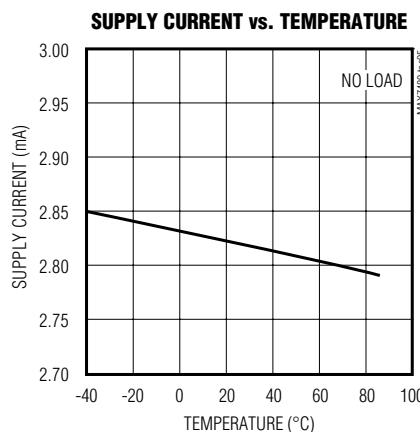

| Supply Current               | $I_{DD}$              | Operating mode, no load, IN = OS = COM                  |                | 2.9      | 3.5 | mA      |

| Shutdown Current             | $I_{\overline{SHDN}}$ | $\overline{SHDN} = GND$ , CLK driven from 0 to $V_{DD}$ |                | 0.2      | 1   | $\mu A$ |

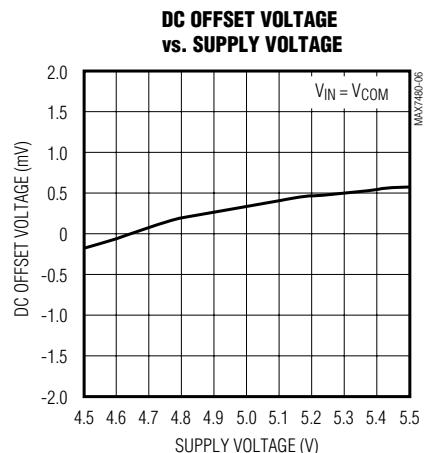

| Power-Supply Rejection Ratio | PSRR                  | Measured at DC                                          |                | 60       |     | dB      |

| <b>SHUTDOWN</b>              |                       |                                                         |                |          |     |         |

| $\overline{SHDN}$ Input High | $V_{SDH}$             |                                                         | $V_{DD} - 0.5$ |          |     | V       |

| $\overline{SHDN}$ Input Low  | $V_{SDL}$             |                                                         | 0.5            |          |     | V       |

| SHDN Input Leakage Current   |                       | $V_{\overline{SHDN}} = 0$ to $V_{DD}$                   | $\pm 0.1$      | $\pm 10$ |     | $\mu A$ |

## FILTER CHARACTERISTICS

( $V_{DD} = +5V$ , filter output measured at OUT,  $10k\Omega \parallel 50pF$  load to GND at OUT,  $\overline{SHDN} = V_{DD}$ ,  $V_{COM} = V_{OS} = V_{DD}/2$ ,  $f_{CLK} = 100kHz$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ .)

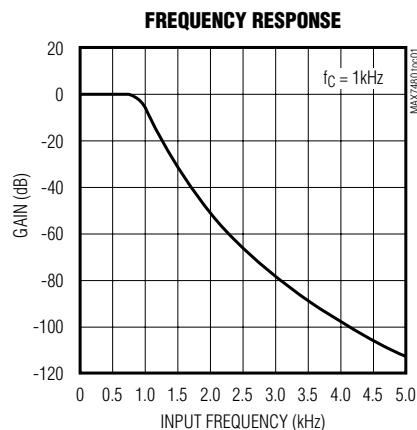

| PARAMETER                          | CONDITIONS        | MIN  | TYP  | MAX  | UNITS |

|------------------------------------|-------------------|------|------|------|-------|

| Insertion Gain Relative to DC Gain | $f_{IN} = 0.5f_C$ | -0.1 | 0.0  |      | dB    |

|                                    | $f_{IN} = f_C$    | -3.5 | -3.0 | -2.5 |       |

|                                    | $f_{IN} = 2f_C$   | -48  | -43  |      |       |

|                                    | $f_{IN} = 3f_C$   | -76  | -70  |      |       |

**Note 1:** The maximum  $f_C$  is defined as the clock frequency  $f_{CLK} = 100 \cdot f_C$  at which the peak SINAD drops to 68dB with a sinusoidal input at  $0.2f_C$ .

**Note 2:** DC insertion gain is defined as  $\Delta V_{OUT} / \Delta V_{IN}$ .

**Note 3:** OS voltages above  $V_{DD} - 1V$  saturate the input and result in a  $75\mu A$  typical input leakage current.

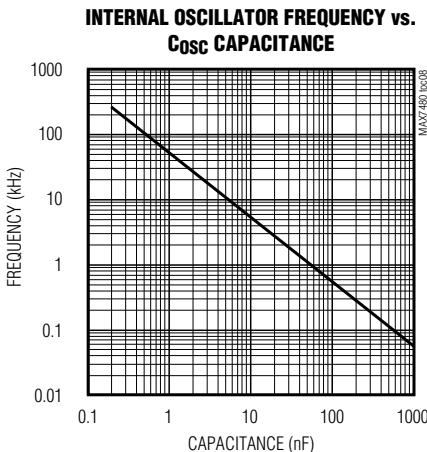

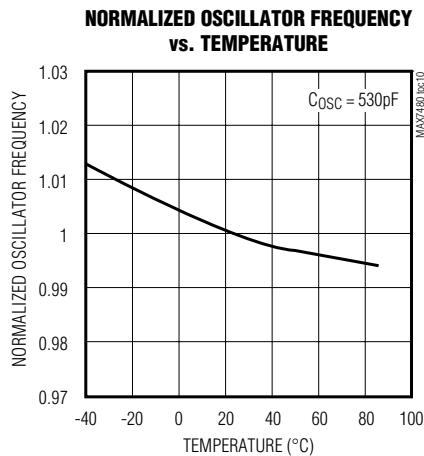

**Note 4:**  $f_{osc}$  (kHz)  $\cong 53 \cdot 10^3 / C_{osc}$  (pF).

# 8次、ローパス、バタワース、 スイッチトキャパシタフィルタ

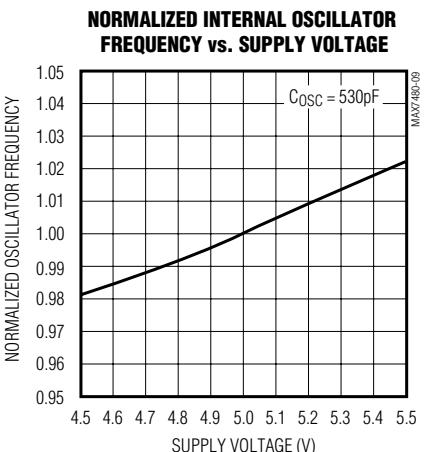

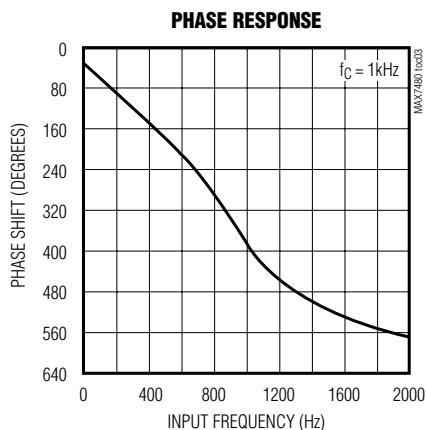

## 標準動作特性

( $V_{DD} = +5V$ ,  $f_{CLK} = 100\text{kHz}$ ,  $\overline{SHDN} = V_{DD}$ ,  $V_{COM} = V_{OS} = V_{DD}/2$ ,  $T_A = +25^\circ\text{C}$ , unless otherwise noted.)

# 8次、ローパス、バタワース、 スイッチトキャパシタフィルタ

MAX7480

## 標準動作特性(続き)

( $V_{DD} = +5V$ ,  $f_{CLK} = 100\text{kHz}$ ,  $\overline{SHDN} = V_{DD}$ ,  $V_{COM} = V_{OS} = V_{DD}/2$ ,  $T_A = +25^\circ\text{C}$ , unless otherwise noted.)

**Table A. THD+N vs. Input Signal Amplitude Test Conditions**

| TRACE | f <sub>IN</sub> (Hz) | f <sub>C</sub> (kHz) | f <sub>CLK</sub> (kHz) | MEASUREMENT BANDWIDTH (kHz) |

|-------|----------------------|----------------------|------------------------|-----------------------------|

| A     | 400                  | 2                    | 200                    | 22                          |

| B     | 200                  | 1                    | 100                    | 22                          |

# 8次、ローパス、バタワース、 スイッチトキャパシタフィルタ

## 端子説明

| 端子 | 名称              | 機能                                                                                                        |

|----|-----------------|-----------------------------------------------------------------------------------------------------------|

| 1  | COM             | コモン入力ピン。内部でミッドサプライ(電源中央値)にバイアスされています。外部で $0.1\mu F$ コンデンサを使ってGNDにバイパスして下さい。内部バイアスをオーバライドする時は外部電源で駆動して下さい。 |

| 2  | IN              | フィルタ入力                                                                                                    |

| 3  | GND             | グランド                                                                                                      |

| 4  | V <sub>DD</sub> | +5V電源入力                                                                                                   |

| 5  | OUT             | フィルタ出力                                                                                                    |

| 6  | OS              | オフセット調節入力。出力オフセットを調節するには、OSを外部からバイアスして下さい。オフセット調節が必要ない場合はOSをCOMに接続して下さい。「オフセット及びコモンモード入力調節」の項を参照して下さい。    |

| 7  | SHDN            | シャットダウン入力。ローに駆動するとシャットダウンモードがイネーブルされます。ハイに駆動、またはV <sub>DD</sub> に接続すると通常動作になります。                          |

| 8  | CLK             | クロック入力。内部発振器をオーバライドするには、外部クロックに接続して下さい。他の場合はCLKとGNDの間に外部コンデンサ(C <sub>OSC</sub> )を接続して内部発振器周波数を設定して下さい。    |

## 詳細

MAX7480バタワース式フィルタはクロック・コーナ周波数比100:1及び最大コーナ周波数2kHzで動作します。

ローパスバタワース式フィルタは最も平坦なパスバンド応答を提供するため、パスバンド全域でDC利得からの逸脱を最小限に保つ必要のある計測器アプリケーションに最適です。

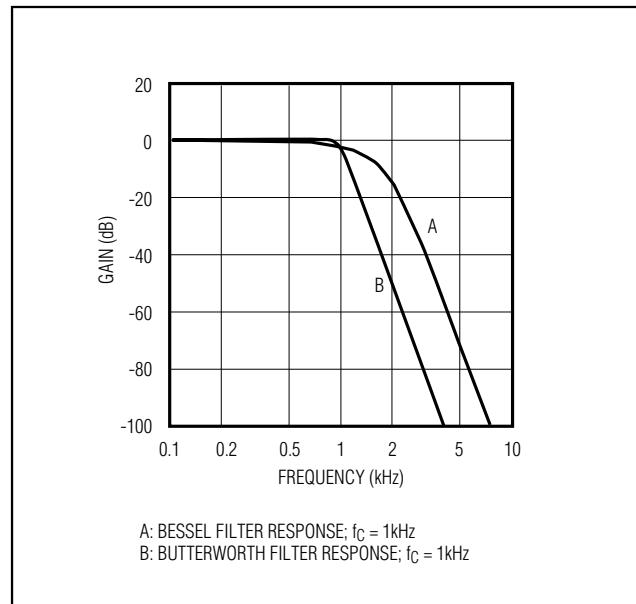

図1にベッセル式及びバタワース式フィルタの周波数応答の違いを示します。これはフィルタカットオフ周波数を1kHzに設定した場合で、曲線Aはベッセル式フィルタの応答を、曲線Bはバタワース式フィルタの応答を示しています。

## 背景技術

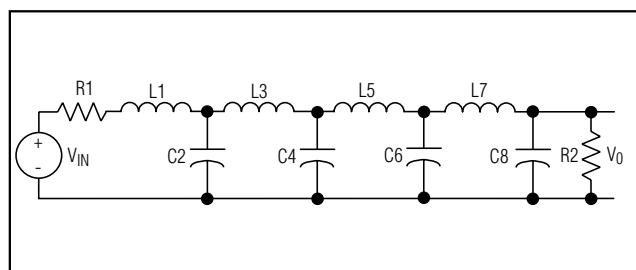

殆どのスイッチトキャパシタフィルタ(SCF)は複二次(バイクワッドラティック)セクションで設計されています。各セクションが2つのフィルタリングポールを作り、複数のセクションがカスケード接続されて高次フィルタを形成します。しかし、このタイプの設計はQの高いセクションがあると部品の変動に極めて敏感になります。代替方式として、加算及びスケーリング付のスイッチトキャパシタ積分器を使って受動ネットワークをエミュレートすることができます。図2に基本的な8次ラダーフィルタ構造を示します。

MAX7480のようなスイッチトキャパシタフィルタは受動ラダーフィルタをエミュレートします。このフィルタは、各部品が1つのポール・ゼロペアだけでなくフィルタ全体の形に影響するため、カスケード接続の複二次設計と比べて部品に対する敏感さが低減されています。別の言い方をすれば、複二次設計において部品のミスマッチングがあると、それに対応するポールで集中的に誤差が生じますが、ラダーフィルタ設計では同じミスマッチングによる誤差が全ポールに分散します。

図1. ベッセル式及びバタワース式フィルタの周波数応答の比較

図2. 8次ラダーフィルタネットワーク

## クロック信号

### 外部クロック

MAX7480 SCFはデューティサイクル40%~60%の外部クロックと共に使用するように設計されています。外部クロックを使用する場合は、0~V<sub>DD</sub>を電源とする

# 8次、ローパス、バタワース、 スイッチトキャパシタフィルタ

MAX7480

CMOSを使ってCLKを駆動して下さい。外部クロックの速度を変えることにより、次式に従ってフィルタのコーナ周波数が調節されます。

$$f_C = f_{CLK} / 100$$

## 内部クロック

内部発振器を使用する場合は、CLKとグランドの間にコンデンサ( $C_{OSC}$ )を接続して下さい。次式により、このコンデンサの値が発振器の周波数を決定します。

$$f_{OSC}(\text{kHz}) = \frac{53 \cdot 10^3}{C_{OSC}}; C_{OSC} \text{ in pF}$$

内部発振器の周波数に影響が出ないように、CLKにおける浮遊容量はできるだけ小さくして下さい。内部発振器の速度を変えることによってフィルタのコーナ周波数を調節して下さい。クロックとコーナ周波数の比は100:1です。例えば、100kHzの内部発振器を使った場合の公称コーナ周波数は1kHzです。

## 入力インピーダンス対クロック周波数

MAX7480の入力インピーダンスは実効的にスイッチトキャパシタ抵抗になります。そしてこのインピーダンスは周波数に反比例します。次式で決まる入力インピーダンスの値は平均入力インピーダンスです。これは、入力電流が連続でないためです。原則として、ドライバには、出力インピーダンスがフィルタの入力インピーダンスの10%よりも小さいものを使って下さい。フィルタの入力インピーダンスは次式で見積もって下さい。

$$Z_{IN} = \frac{1}{(f_{CLK} \cdot C_{IN})}$$

ここで、 $f_{CLK}$  = クロック周波数、 $C_{IN}$  = 2.31pFです。

## 低電力シャットダウンモード

このデバイスは、SHDNをローにすることで動作されるシャットダウンモードを備えています。シャットダウンモードにおいては、フィルタの消費電流は0.2μA(typ)に低減し、出力はハイインピーダンスになります。通常動作ではSHDNをハイに駆動するか、あるいはV<sub>DD</sub>に接続して下さい。

## アプリケーション情報

### オフセット及びコモンモード入力調節

COMにおける電圧がコモンモード入力電圧を決定しますが、この電圧は内部抵抗分圧器によってミッドサプライ(電源中央値)にバイアスされます。COMは0.1μFコンデンサでバイパスし、OSをCOMに接続して下さい。

オフセット調節又はDCレベルシフトを要するアプリケーションにおいては、図3に示すように抵抗分圧器を通じて外部バイアス電圧をOSに印加して下さい。(注: OSを無接続のままにしないで下さい。)出力電圧は次式で表されます。

$$V_{OUT} = (V_{IN} - V_{COM}) + V_{OS}$$

ここで、 $V_{COM} = V_{DD}/2$ (typ)です。 $(V_{IN} - V_{COM})$ がSCFによってローパスフィルタリングされ、 $V_{OS}$ は出力段で加えられます。COMとOSの電圧範囲については、「Electrical Characteristics」を参照して下さい。COM又はOSの電圧がミッドサプライから大きく外れるとフィルタのダイナミックレンジが減少します。

## 電源

MAX7480は+5V単一電源で動作します。V<sub>DD</sub>を0.1μFコンデンサでGNDにバイパスして下さい。デュアル電源(±2.5V)が必要な場合は、COMをシステムグランドに接続し、GNDを負電源に接続して下さい。図4にデュアル電源動作の例を示します。単一電源とデュアル電源は性能的には等価です。単一電源、デュアル電源のいずれの場合も、CLK及びSHDNはGND(デュアル電源の場合はV-)からV<sub>DD</sub>に駆動して下さい。±5Vデュアル電源アプリケーションの場合は、MAX291 ~ MAX297を使用して下さい。

## 入力信号振幅範囲

最適入力信号範囲は、与えられたコーナ周波数において全高調波歪み+ノイズ(THD+N)が最小になる電圧レベルを観察することによって決まります。「標準動作特性」に、入力信号のピーク間振幅を変化させた時のTHD+N応答を示します。この測定は、OS及びCOMをミッドサプライにバイアスした状態で行われました。

図3. オフセット調節回路

# 8次、ローパス、バタワース、 スイッチトキャパシタフィルタ

## アンチエイリアシング及び ポストDACフィルタリング

MAX7480をアンチエイリアシング又はポストDACフィルタリングに使用する場合は、DACとフィルタクロックを同期させて下さい。クロックが同期されていないと、ビート周波数がエイリアシングでパスバンドに入ってくる恐れがあります。

クロック・コナ周波数比が高い(100:1)ため、プレ及びポストSCFフィルタリングも簡単です。入力において、ローパスフィルタがクロック周波数付近の周波数がエイリアシングでパスバンドに入ってくるのを防ぐことができます。出力では、ローパスフィルタがクロックフィードスルーを減衰させます。

クロック・コナ周波数比が高いため、カットオフ周波数がSCFのコナ周波数よりも高く設定されたシンプルなRCローパスフィルタによって入力アンチエイリアシングと適切な出力クロック減衰を実現することができます。

## 高調波歪み

高調波歪みはフィルタ内の非直線性によって生じます。純粋なサイン波がフィルタ入力に印加された場合、この非直線性によって高調波が発生します。表1に、負荷が10k $\Omega$ 、T<sub>A</sub> = +25°C 時のMAX7480の標準高調波歪み値を示します。

表1. 標準高調波歪み

| FILTER  | f <sub>CLK</sub><br>(kHz) | f <sub>C</sub><br>(kHz) | f <sub>IN</sub><br>(Hz) | V <sub>IN</sub><br>(Vp-p) | TYPICAL HARMONIC DISTORTION (dB) |     |     |     |

|---------|---------------------------|-------------------------|-------------------------|---------------------------|----------------------------------|-----|-----|-----|

|         |                           |                         |                         |                           | 2nd                              | 3rd | 4th | 5th |

| MAX7480 | 100                       | 1                       | 200                     | 4                         | -89                              | -73 | -91 | -93 |

|         | 200                       | 2                       | 400                     |                           | -82                              | -68 | -85 | -89 |

図4. デュアル電源動作

## チップ情報

TRANSISTOR COUNT: 1116

マキシム・ジャパン株式会社

〒169-0051 東京都新宿区西早稲田3-30-16(ホリゾン1ビル)

TEL. (03)3232-6141 FAX. (03)3232-6149

マキシム社では全体がマキシム社製品で実現されている回路以外の回路の使用については責任を持ちません。回路特許ライセンスは明言されていません。マキシム社は隨時予告なしに回路及び仕様を変更する権利を保留します。

8 Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600