# 8個のプッシュプルおよび8個のオープンドレインI/O付き、 I<sup>2</sup>Cポートエキスパンダ

## 概要

2線式シリアルインタフェースペリフェラルのMAX7325は、16個のI/Oポートを備えています。ポートは、8個のプッシュプル出力と、選択可能な内部プルアップと遷移検出を備えた8個のI/Oに分かれています。8個のポートはプッシュプル出力であり、8個のI/Oをロジック入力またはオープンドレイン出力として使用することができます。各ポートは、+6Vまで過電圧保護されています。

入力として設定されるすべてのI/Oポートは、状態変化を常に監視されます(遷移検出)。状態変化は、INT出力によって示されます。割込みがラッチされるため、過渡的な変化を検出することができます。その後シリアルインターフェースを通じてMAX7325にアクセスすると、発行されている割込みがすべてクリアされます。オープンドレイン出力は20mAのシンク電流定格で、LEDを駆動可能です。RST入力によってシリアルインターフェースがクリアされ、MAX7325との間のすべてのI<sup>2</sup>C通信が終了します。

MAX7325では4レベルのロジックを持つ2個のアドレス入力によって16通りのI<sup>2</sup>Cスレーブアドレスが可能です。また、スレーブアドレスによって、通電時のI/Oポートの論理状態が決定され、40kΩの内部プルアップが4ポート1組でイネーブルまたはディセーブルされます。

MAX7325は、入力ポート、オープンドレインI/Oポート、およびプッシュプル出力ポートを選択可能なピン互換ポートエキスパンダファミリの1デバイスです(表1参照)。

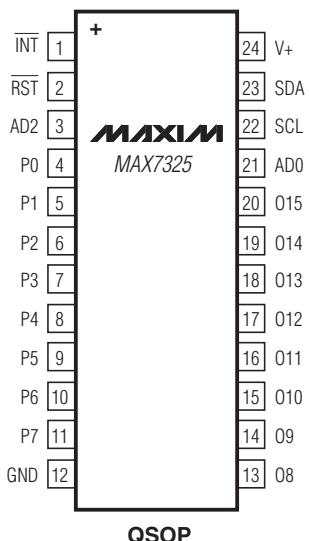

MAX7325は24ピンQSOPおよびTQFNパッケージで提供され、-40°C～+125°Cの車載用温度範囲での動作が保証されています。

## アプリケーション

|         |        |

|---------|--------|

| 携帯電話    | ノートブック |

| SAN/NAS | 衛星無線   |

| サーバ     | 車載用    |

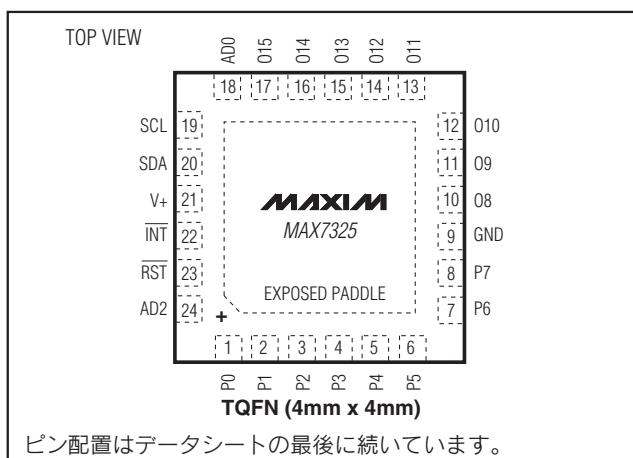

## ピン配置

ピン配置はデータシートの最後に続いています。

## 特長

- ◆ 400kHzのI<sup>2</sup>Cシリアルインタフェース

- ◆ 動作電圧：+1.71V～+5.5V

- ◆ 8個のプッシュプル出力ポート

- ◆ 20mAシンク電流定格の8個のオープンドレインI/Oポート

- ◆ I/Oポートの過電圧保護は最大+6V

- ◆ I/Oポートの電源投入時のデフォルト論理状態を選択可能

- ◆ 過渡的変化がラッチされるため、読み取り操作の合間に検出可能

- ◆ 入力の変化をINT出力によって通知

- ◆ AD0およびAD2入力によって16通りのスレーブアドレスを選択可能

- ◆ 低スタンバイ電流：0.6µA (typ)

- ◆ 動作温度範囲：-40°C～+125°C

## 型番

| PART        | TEMP RANGE      | PIN-PACKAGE                | PKG CODE |

|-------------|-----------------|----------------------------|----------|

| MAX7325AEG+ | -40°C to +125°C | 24 QSOP                    | E24-1    |

| MAX7325ATG+ | -40°C to +125°C | 24 TQFN-EP*<br>(4mm x 4mm) | T2444-3  |

+は鉛フリーパッケージを示します。

\*EP = エクスポートドパッド。

## 選択ガイド

| PART    | INPUTS  | INTERRUPT MASK | OPEN-DRAIN OUTPUTS | PUSH-PULL OUTPUTS |

|---------|---------|----------------|--------------------|-------------------|

| MAX7324 | 8       | Yes            | —                  | 8                 |

| MAX7325 | Up to 8 | —              | Up to 8            | 8                 |

| MAX7326 | 4       | Yes            | —                  | 12                |

| MAX7327 | Up to 4 | —              | Up to 4            | 12                |

標準動作回路および機能ブロック図はデータシートの最後に記載されています。

MAX7325

# 8個のプッシュプルおよび8個のオープンドレインI/O付き、 I<sup>2</sup>Cポートエキスパンダ

## ABSOLUTE MAXIMUM RATINGS

(All voltages referenced to GND.)

|                                     |                      |

|-------------------------------------|----------------------|

| Supply Voltage V+                   | -0.3V to +6V         |

| SCL, SDA, AD0, AD2, RST, INT, P0–P7 | -0.3V to +6V         |

| O8–O15                              | -0.3V to (V+ + 0.3V) |

| O8–O15 Output Current               | ±25mA                |

| P0–P7 Sink Current                  | 25mA                 |

| SDA Sink Current                    | 10mA                 |

| INT Sink Current                    | 10mA                 |

| Total V+ Current                    | 50mA                 |

|                                                       |                 |

|-------------------------------------------------------|-----------------|

| Total GND Current                                     | 100mA           |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |                 |

| 24-Pin QSOP (derate 9.5mW/°C over +70°C)              | 761.9mW         |

| 24-Pin TQFN (derate 20.8mW/°C over +70°C)             | 1666.7mW        |

| Operating Temperature Range                           | -40°C to +125°C |

| Junction Temperature                                  | +150°C          |

| Storage Temperature Range                             | -65°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## DC ELECTRICAL CHARACTERISTICS

(V+ = +1.71V to +5.5V, T<sub>A</sub> = -40°C to +125°C, unless otherwise noted. Typical values are at V+ = +3.3V, T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                                               | SYMBOL                            | CONDITIONS                                                            | MIN      | TYP      | MAX  | UNITS |

|---------------------------------------------------------|-----------------------------------|-----------------------------------------------------------------------|----------|----------|------|-------|

| Operating Supply Voltage                                | V+                                | T <sub>A</sub> = -40°C to +125°C                                      | 1.71     | 5.50     |      | V     |

| Power-On-Reset Voltage                                  | V <sub>POR</sub>                  | V+ falling                                                            |          | 1.6      |      | V     |

| Standby Current<br>(Interface Idle)                     | I <sub>STB</sub>                  | SCL and SDA and other digital inputs at V+                            |          | 0.6      | 1.9  | µA    |

| Supply Current<br>(Interface Running)                   | I <sub>+</sub>                    | f <sub>SCL</sub> = 400kHz; other digital inputs at V+                 |          | 23       | 55   | µA    |

| Input High-Voltage<br>SDA, SCL, AD0, AD2, RST, P0–P7    | V <sub>IH</sub>                   | V+ < 1.8V                                                             | 0.8 x V+ |          |      | V     |

|                                                         |                                   | V+ ≥ 1.8V                                                             | 0.7 x V+ |          |      |       |

| Input Low-Voltage<br>SDA, SCL, AD0, AD2, RST, P0–P7     | V <sub>IL</sub>                   | V+ < 1.8V                                                             | 0.2 x V+ |          |      | V     |

|                                                         |                                   | V+ ≥ 1.8V                                                             | 0.3 x V+ |          |      |       |

| Input Leakage Current<br>SDA, SCL, AD0, AD2, RST, P0–P7 | I <sub>IH</sub> , I <sub>IL</sub> | SDA, SCL, AD0, AD2, RST, P0–P7 at V+ or GND, internal pullup disabled | -0.2     |          | +0.2 | µA    |

| Input Capacitance<br>SDA, SCL, AD0, AD2, RST, P0–P7     |                                   |                                                                       |          | 10       |      | pF    |

| Output Low Voltage<br>O8–O15, P0–P7                     | V <sub>OL</sub>                   | V+ = +1.71V, I <sub>SINK</sub> = 5mA (QSOP)                           | 90       | 180      |      | mV    |

|                                                         |                                   | V+ = +1.71V, I <sub>SINK</sub> = 5mA (TQFN)                           | 90       | 230      |      |       |

|                                                         |                                   | V+ = +2.5V, I <sub>SINK</sub> = 10mA (QSOP)                           | 110      | 210      |      |       |

|                                                         |                                   | V+ = +2.5V, I <sub>SINK</sub> = 10mA (TQFN)                           | 110      | 260      |      |       |

|                                                         |                                   | V+ = +3.3V, I <sub>SINK</sub> = 15mA (QSOP)                           | 130      | 230      |      |       |

|                                                         |                                   | V+ = +3.3V, I <sub>SINK</sub> = 15mA (TQFN)                           | 130      | 280      |      |       |

|                                                         |                                   | V+ = +5V, I <sub>SINK</sub> = 20mA (QSOP)                             | 140      | 250      |      |       |

|                                                         |                                   | V+ = +5V, I <sub>SINK</sub> = 20mA (TQFN)                             | 140      | 300      |      |       |

| Output High Voltage<br>O8–O15                           | V <sub>OH</sub>                   | V+ = +1.71V, I <sub>SOURCE</sub> = 2mA                                | V+ - 250 | V+ - 30  |      | mV    |

|                                                         |                                   | V+ = +2.5V, I <sub>SOURCE</sub> = 5mA                                 | V+ - 360 | V+ - 70  |      |       |

|                                                         |                                   | V+ = +3.3V, I <sub>SOURCE</sub> = 5mA                                 | V+ - 260 | V+ - 100 |      |       |

|                                                         |                                   | V+ = +5V, I <sub>SOURCE</sub> = 10mA                                  | V+ - 360 | V+ - 120 |      |       |

| Output Low-Voltage SDA                                  | V <sub>OLSDA</sub>                | I <sub>SINK</sub> = 6mA                                               |          | 250      |      | mV    |

| Output Low-Voltage INT                                  | V <sub>OLINT</sub>                | I <sub>SINK</sub> = 5mA                                               |          | 130      | 250  | mV    |

| Port Input Pullup Resistor                              | R <sub>PU</sub>                   |                                                                       | 25       | 40       | 55   | kΩ    |

# 8個のプッシュプルおよび8個のオープンドレインI/O付き、 I<sup>2</sup>Cポートエキスパンダ

MAX7325

## PORT AND INTERRUPT INT TIMING CHARACTERISTICS

(V<sub>+</sub> = +1.71V to +5.5V, T<sub>A</sub> = -40°C to +125°C, unless otherwise noted. Typical values are at V<sub>+</sub> = +3.3V, T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                             | SYMBOL           | CONDITIONS             | MIN | TYP | MAX | UNITS |

|---------------------------------------|------------------|------------------------|-----|-----|-----|-------|

| Port Output Data Valid                | t <sub>PPV</sub> | C <sub>L</sub> ≤ 100pF |     | 4   |     | μs    |

| Port Input Setup Time                 | t <sub>PSU</sub> | C <sub>L</sub> ≤ 100pF | 0   |     |     | μs    |

| Port Input Hold Time                  | t <sub>PH</sub>  | C <sub>L</sub> ≤ 100pF | 4   |     |     | μs    |

| INT Input Data Valid Time             | t <sub>IV</sub>  | C <sub>L</sub> ≤ 100pF |     | 4   |     | μs    |

| INT Reset Delay Time from STOP        | t <sub>IP</sub>  | C <sub>L</sub> ≤ 100pF |     | 4   |     | μs    |

| INT Reset Delay Time from Acknowledge | t <sub>IR</sub>  | C <sub>L</sub> ≤ 100pF |     | 4   |     | μs    |

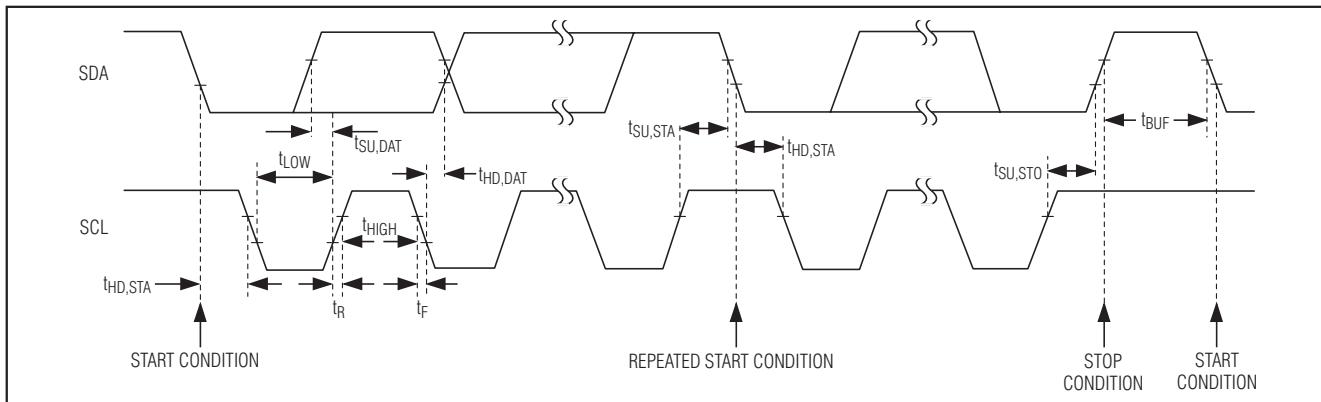

## TIMING CHARACTERISTICS

(V<sub>+</sub> = +1.71V to +5.5V, T<sub>A</sub> = -40°C to +125°C, unless otherwise noted. Typical values are at V<sub>+</sub> = +3.3V, T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                                          | SYMBOL               | CONDITIONS   | MIN                    | TYP | MAX | UNITS |

|----------------------------------------------------|----------------------|--------------|------------------------|-----|-----|-------|

| Serial-Clock Frequency                             | f <sub>SCL</sub>     |              |                        | 400 |     | kHz   |

| Bus Free Time Between a STOP and a START Condition | t <sub>BUF</sub>     |              | 1.3                    |     |     | μs    |

| Hold Time (Repeated) START Condition               | t <sub>HD, STA</sub> |              | 0.6                    |     |     | μs    |

| Repeated START Condition Setup Time                | t <sub>SU, STA</sub> |              | 0.6                    |     |     | μs    |

| STOP Condition Setup Time                          | t <sub>SU, STO</sub> |              | 0.6                    |     |     | μs    |

| Data Hold Time                                     | t <sub>HD, DAT</sub> | (Note 2)     |                        | 0.9 |     | μs    |

| Data Setup Time                                    | t <sub>SU, DAT</sub> |              | 100                    |     |     | ns    |

| SCL Clock Low Period                               | t <sub>LOW</sub>     |              | 1.3                    |     |     | μs    |

| SCL Clock High Period                              | t <sub>HIGH</sub>    |              | 0.7                    |     |     | μs    |

| Rise Time of Both SDA and SCL Signals, Receiving   | t <sub>R</sub>       | (Notes 3, 4) | 20 + 0.1C <sub>b</sub> | 300 |     | ns    |

| Fall Time of Both SDA and SCL Signals, Receiving   | t <sub>F</sub>       | (Notes 3, 4) | 20 + 0.1C <sub>b</sub> | 300 |     | ns    |

| Fall Time of SDA Transmitting                      | t <sub>F, TX</sub>   | (Notes 3, 4) | 20 + 0.1C <sub>b</sub> | 250 |     | ns    |

| Pulse Width of Spike Suppressed                    | t <sub>SP</sub>      | (Note 5)     | 50                     |     |     | ns    |

| Capacitive Load for Each Bus Line                  | C <sub>b</sub>       | (Note 3)     |                        | 400 |     | pF    |

| RST Pulse Width                                    | t <sub>W</sub>       |              | 500                    |     |     | ns    |

| RST Rising to START Condition Setup Time           | t <sub>RST</sub>     |              | 1                      |     |     | μs    |

**Note 1:** All parameters are tested at T<sub>A</sub> = +25°C. Specifications over temperature are guaranteed by design.

**Note 2:** A master device must provide a hold time of at least 300ns for the SDA signal (referred to V<sub>IL</sub> of the SCL signal) in order to bridge the undefined region of SCL's falling edge.

**Note 3:** Guaranteed by design.

**Note 4:** C<sub>b</sub> = total capacitance of one bus line in pF. I<sub>SINK</sub> ≤ 6mA. t<sub>R</sub> and t<sub>F</sub> measured between 0.3 x V<sub>+</sub> and 0.7 x V<sub>+</sub>.

**Note 5:** Input filters on the SDA and SCL inputs suppress noise spikes less than 50ns.

# 8個のプッシュプルおよび8個のオープンドレインI/O付き、 I<sup>2</sup>Cポートエキスパンダ

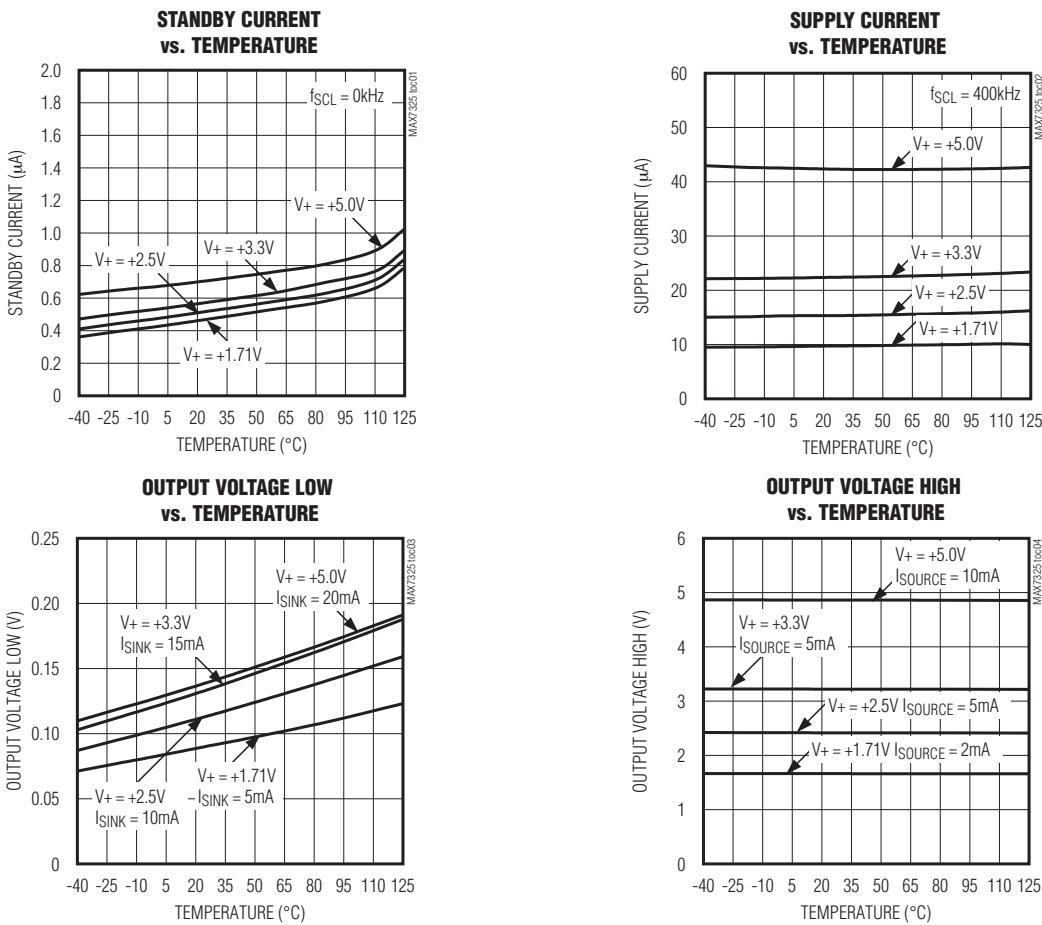

## 標準動作特性

( $T_A = +25^\circ\text{C}$ , unless otherwise noted.)

## 端子説明

| 端子    |        | 名称                      | 機能                                                                                                               |

|-------|--------|-------------------------|------------------------------------------------------------------------------------------------------------------|

| QSOP  | TQFN   |                         |                                                                                                                  |

| 1     | 22     | $\overline{\text{INT}}$ | 割込み出力、アクティブロー。 $\overline{\text{INT}}$ はオープンドレイン出力です。                                                            |

| 2     | 23     | $\overline{\text{RST}}$ | リセット入力。アクティブロー。 $\overline{\text{RST}}$ をローに駆動すると2線式インターフェースがクリアされます。                                            |

| 3, 21 | 24, 18 | AD2, AD0                | アドレス入力。AD0とAD2でデバイスのスレーブアドレスを選択します。AD0およびAD2を、GND、 $V_+$ 、SCL、またはSDAのいずれかに接続することで、4個のロジックの組み合わせが実現します(表2および3参照)。 |

| 4–11  | 1–8    | P0–P7                   | オープンドレインI/Oポート                                                                                                   |

| 12    | 9      | GND                     | グランド                                                                                                             |

| 13–20 | 10–17  | O8–O15                  | 出力ポート。O8～O15は定格20mAのプッシュプル出力です。                                                                                  |

| 22    | 19     | SCL                     | I <sup>2</sup> C互換シリアルクロック入力                                                                                     |

| 23    | 20     | SDA                     | I <sup>2</sup> C互換シリアルデータI/O                                                                                     |

| 24    | 21     | $V_+$                   | 正の電源電圧。少なくとも0.047μFのセラミックコンデンサで $V_+$ をGNDにバイパスしてください。                                                           |

| —     | EP     | EP                      | エクスポートードパッド。エクスポートードパッドをGNDに接続してください。                                                                            |

# 8個のプッシュプルおよび8個のオープンドレインI/O付き、 I<sup>2</sup>Cポートエキスパンダ

## 詳細

### MAX7319～MAX7329のファミリ内比較

MAX7324～MAX7327のファミリは、MAX7320の機能に加えて、MAX7319、MAX7321、MAX7322、またはMAX7323のいずれか1つの機能を統合した、ピン互換な4種類の16ポートエキスパンダで構成されています。

### 機能概説

MAX7325は、+1.71V～+5.5Vの電源で動作し、8個のプッシュプル出力と8個のオープンドレインI/Oポートを提供する、汎用のポートエキスパンダです。各オープンドレイン出力はシンク20mA、デバイス全体ではすべてのポートの組み合わせに対してシンク100mAという定格になっています。出力は最大+5.5Vの電源に接続された負荷を駆動します。

MAX7325は、アドレス選択入力AD0およびAD2を使用して32通りのI<sup>2</sup>Cスレーブアドレス(表2および3参照)の内の2つに設定され、I<sup>2</sup>Cシリアルインターフェースにおいて最大400kHzでアクセスされます。8個の出力と8個のI/Oは、異なるスレーブアドレスを持ちます。8個のプッシュプル出力が101xxxxというアドレス、8個の入力が110xxxxというアドレスになります。RST入力はバスがロックアップした場合にシリアルインターフェースをクリアし、MAX7325とのすべてのシリアルトランザクションを終了させます。

任意のポートを論理入力として構成するには、そのポートの出力を論理ハイに設定します(オープンドレイン出力の論理ハイは、ハイインピーダンスです)。シリアルインターフェースを通してMAX7325の読み取りを行うと、ポートにおける実際の論理レベルが読み取られます。

表1. MAX7319～MAX7329のファミリ内比較

| PART                     | I <sup>2</sup> C<br>SLAVE<br>ADDRESS | INPUTS  | INPUT<br>INTERRUPT<br>MASK | OPEN-<br>DRAIN<br>OUTPUTS | PUSH-<br>PULL<br>OUTPUTS | CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------|--------------------------------------|---------|----------------------------|---------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>16-PORT EXPANDERS</b> |                                      |         |                            |                           |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MAX7324                  | 101xxxx                              | 8       | Yes                        | —                         | 8                        | 8 input and 8 push-pull output versions:<br><br>8 input ports with programmable latching transition detection interrupt and selectable pullups.<br><br>8 push-pull outputs with selectable default logic levels.<br><br>Offers maximum versatility for automatic input monitoring. An interrupt mask selects which inputs cause an interrupt on transitions, and transition flags identify which inputs have changed (even if only for a transient) since the ports were last read.                                                                                                                                                 |

| MAX7325                  | 101xxxx<br>and<br>110xxxx            | Up to 8 | —                          | Up to 8                   | 8                        | 8 I/O and 8 push-pull output versions:<br>8 open-drain I/O ports with latching transition detection interrupt and selectable pullups.<br><br>8 push-pull outputs with selectable default logic levels.<br><br>Open-drain outputs can level shift the logic-high state to a higher or lower voltage than V <sub>+</sub> using external pullup resistors, but pullups draw current when output is low. Any open-drain port can be used as an input by setting the open-drain output to logic-high. Transition flags identify which open-drain port inputs have changed (even if only for a transient) since the ports were last read. |

MAX7325

## 8個のプッシュプルおよび8個のオープンドレインI/O付き、 I<sup>2</sup>Cポートエキスパンダ

表1. MAX7319～MAX7329のファミリ内比較(続き)

| PART                    | I <sup>2</sup> C<br>SLAVE<br>ADDRESS | INPUTS  | INPUT<br>INTERRUPT<br>MASK | OPEN-<br>DRAIN<br>OUTPUTS | PUSH-<br>PULL<br>OUTPUTS | CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------|--------------------------------------|---------|----------------------------|---------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX7326                 | 101xxxx<br>and<br>110xxxx            | 4       | Yes                        | —                         | 12                       | 4 input-only, 12 push-pull output versions:<br>4 input ports with programmable latching transition detection interrupt and selectable pullups.<br><br>12 push-pull outputs with selectable default logic levels.<br><br>Offers maximum versatility for automatic input monitoring. An interrupt mask selects which inputs cause an interrupt on transitions, and transition flags identify which inputs have changed (even if only for a transient) since the ports were last read.                                                                                                                                                |

| MAX7327                 |                                      | Up to 4 | —                          | Up to 4                   | 12                       | 4 I/O, 12 push-pull output versions:<br>4 open-drain I/O ports with latching transition detection interrupt and selectable pullups.<br><br>12 push-pull outputs with selectable default logic levels.<br><br>Open-drain outputs can level shift the logic-high state to a higher or lower voltage than V <sub>+</sub> using external pullup resistors, but pullups draw current when output is low. Any open-drain port can be used as an input by setting the open-drain output to logic-high. Transition flags identify which open-drain port inputs have changed (even if only for a transient) since the ports were last read. |

| <b>8-PORT EXPANDERS</b> |                                      |         |                            |                           |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| MAX7319                 | 110xxxx                              | 8       | Yes                        | —                         | —                        | Input-only versions:<br>8 input ports with programmable latching transition detection interrupt and selectable pullups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MAX7320                 | 101xxxx                              | —       | —                          | —                         | 8                        | Output-only versions:<br>8 push-pull outputs with selectable power-up default levels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| MAX7321                 | 110xxxx                              | Up to 8 | —                          | Up to 8                   | —                        | I/O versions:<br>8 open-drain I/O ports with latching transition detection interrupt and selectable pullups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| MAX7322                 | 110xxxx                              | 4       | Yes                        | —                         | 4                        | 4 input-only, 4 output-only versions:<br>4 input ports with programmable latching transition detection interrupt and selectable pullups.<br>4 push-pull outputs with selectable power-up default levels.                                                                                                                                                                                                                                                                                                                                                                                                                           |

# 8個のプッシュプルおよび8個のオープンドレインI/O付き、 I<sup>2</sup>Cポートエキスパンダ

表1. MAX7319～MAX7329のファミリ内比較(続き)

| PART               | I <sup>2</sup> C<br>SLAVE<br>ADDRESS | INPUTS  | INPUT<br>INTERRUPT<br>MASK | OPEN-<br>DRAIN<br>OUTPUTS | PUSH-<br>PULL<br>OUTPUTS | CONFIGURATION                                                                                                                                                                                       |

|--------------------|--------------------------------------|---------|----------------------------|---------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX7323            | 110xxxx                              | Up to 4 | —                          | Up to 4                   | 4                        | 4 I/O, 4 output-only versions:<br>4 open-drain I/O ports with latching transition<br>detection interrupt and selectable pullups.<br>4 push-pull outputs with selectable power-up default<br>levels. |

| MAX7328<br>MAX7329 | 0100xxx<br>0111xxx                   | Up to 8 | —                          | Up to 8                   | —                        | 8 open-drain I/O ports with nonlatching transition<br>detection interrupt and pullups on all ports.                                                                                                 |

オープンドレインポートを入力として使用する場合、ラッチ付きの遷移検出が提供されます。すべての入力ポートが常に変化を監視されます。入力が変化すると、8個のフラグビットの1つがセットされ、変化のあったポートを示します。MAX7325に対するその後の読み取りまたは書き込みトランザクションによって、すべてのフラグがクリアされます。

ラッチ付きの割込み出力( $\overline{INT}$ )は、入力として使用しているポートの論理の変化を知らせるようにプログラムされます。任意の入力ポートのデータ変化によって $\overline{INT}$ が論理ローになります。シリアルインターフェースを通してI/Oポートのレベルを変更しても割込みは発生しません。割込みの後にMAX7325がシリアルインターフェース経由でアクセスされたとき、割込み出力 $\overline{INT}$ のアサートが解除されます。

$V_+$ への内蔵プルアップ抵抗が、アドレス選択入力AD0およびAD2によって選択されます。プルアップは入力ポート4個1組についてイネーブルまたはディセーブルされます(表2参照)。スレーブアドレス選択を使用して、入力として使用するI/Oポートが通電時に論理ハイになることを保証してください。内蔵プルアップをイネーブルされたI/Oポートは、デフォルトで論理ハイの出力状態になります。内蔵プルアップをディセーブルされたI/Oポートは、デフォルトで論理ローの出力状態になります。出力ポートの通電時の論理レベルは、アドレス選択入力AD0およびAD2によって選択されます。各ポートは4個1組で起動時のデフォルトが論理ハイまたは論理ローになります(表2および3参照)。

## 初期起動

通電時には、遷移検出ロジックがリセットされ、 $\overline{INT}$ のアサートが解除されます。遷移フラグがクリアされ、データに変化がないことを示します。16個のI/Oポートの起動時デフォルト状態は、I<sup>2</sup>Cスレーブアドレス選択入力AD0およびAD2に従って設定されます(表2および3)。入力として使用するI/Oポートについては、デフォルトの状態が論理ハイであることを保証し、I/Oポートがハイインピーダンス状態で起動するようにしてください。

プルアップをイネーブルするように設定したI/Oポートも、すべて起動時の状態が論理ハイになります。

## パワーオンリセット

MAX7325は、起動時にすべてのレジスタが既知の状態にリセットされることを保証するパワーオンリセット(POR)回路を内蔵しています。 $V_+$ が $V_{POR}$ (1.6V max)を上回ると、POR回路がレジスタと2線式インターフェースを解放して通常動作可能になります。 $V_+$ が $V_{POR}$ 未満まで低下すると、MAX7325はすべてのレジスタの内容をPORのデフォルトにリセットします(表2および3)。

## RST入力

アクティブローのRST入力は、MAX7325が関与しているすべてのI<sup>2</sup>Cトランザクションを取消し、強制的にMAX7325をI<sup>2</sup>Cのストップ状態に遷移させます。リセットは、割込み出力( $\overline{INT}$ )には影響を与えません。

## スタンバイモード

シリアルインターフェースがアイドル状態のとき、MAX7325は自動的にスタンバイモードに入り、電源電流の使用量を最小化します。

## スレーブアドレス、起動時デフォルトの論理状態、 および入力プルアップの選択

アドレス入力AD0およびAD2によってMAX7325のスレーブアドレスが決まり、起動時のポートのI/O状態が設定され、どの入力がプルアップ抵抗を備えるかが選択されます。内蔵プルアップと起動時のデフォルト状態は、4個1組で設定されます(表2参照)。

MAX7325のスレーブアドレスは、伝送が実際にMAX7325をアドレス指定するものかどうかに関係なく、I<sup>2</sup>Cの伝送ごとに決定されます。MAX7325はこの伝送中に、アドレス入力AD0とAD2が固定の論理レベル $V_+$ またはGNDではなく、SDAまたはSCLに接続されているかどうかを識別します。MAX7325のスレーブアドレスは、デバイスの電源をオンオフすることなく、アプリケーション内で動的に設定することができます。

MAX7325

# 8個のプッシュプルおよび8個のオープンドレインI/O付き、 I<sup>2</sup>Cポートエキスパンダ

初めて通電したとき、最初のI<sup>2</sup>C伝送が行われるまでは、MAX7325はアドレス入力AD0およびAD2を完全にデコードできません。AD0とAD2は、最初はV+またはGNDに接続されているように見えます。アドレス選択を使用して、通電時の論理状態およびプルアップをイネーブルするかどうかが決定されるため、この点が重要になります。通電時にはI<sup>2</sup>CのSDAおよびSCLバスインターフェースラインは、MAX7325を含めて、バスに接続されているすべてのデバイス(マスタまたはスレーブ)の入力でハイインピーダンスになります。このことはI<sup>2</sup>C仕様の一部として保証されています。したがって、通電時にアドレス入力AD0およびAD2がSDAまたはSCLに接続されている場合、それらはV+に接続されているように見えます。

起動ロジックは、AD0を使ってポートP0～P3の通電時の状態およびプルアップをイネーブルするかどうかを選択し、AD2を使ってポートP4～P7の通電時の状態とプルアップをイネーブルするかどうかを選択します。ルールとしては、論理ハイ、SDA、またはSCLと接続されていればプルアップを選択し、デフォルトの論理状態をハイにします。論理ローなら、プルアップを切断し、デフォルトの論理状態をローにします(表2)。標準的なI<sup>2</sup>Cの構成、すなわちSDAまたはSCLが外部の

I<sup>2</sup>Cプルアップ抵抗によってV+にプルアップされている場合は、通電時に正しいポート構成になります。

場合によっては、通電時にSDA = SCL = V+になるという想定が通用しないこともあります。たとえば、通電時に適正なバス活動が行われるアプリケーションなどです。もしSDAとSCLがMAX7325の電源電圧とは別の電源電圧にプルアップ抵抗で終端されていたら、そしてそのプルアップ電源の立上りがMAX7325の電源より遅かったら、通電時にSDAまたはSCLがGNDに接続されているように見える可能性があります。こうしたアプリケーションでは、アドレス入力AD0とAD2をV+またはGNDに接続することによって選択される4通りのアドレスの組み合わせを使用してください(表2および3の太字箇所)。これらの選択肢は、SDAおよびSCLの挙動とは関係なく、通電時に正しくなることが保証されています。他の12通りのアドレスの組み合わせのいずれかを使用した場合、最初のI<sup>2</sup>C伝送(必ずしもMAX7325ではなく、任意のデバイスに対するもので構いません)がバス上に送出されるまでは、予想外のプルアップの組み合わせがアサートされる可能性があり、予想外のポートの組み合わせが(入力や論理ハイの出力ではなく)論理ローの出力として初期化されることになります。

表2. MAX7325のポートP0～P7のアドレスマップ

| PIN CONNECTION |            | DEVICE ADDRESS |          |          |          |          |          |          |          | PORT POWER-UP DEFAULT |          |          |          |          |          |          |          | 40kΩ INPUT PULLUPS ENABLED |          |          |          |          |          |          |  |

|----------------|------------|----------------|----------|----------|----------|----------|----------|----------|----------|-----------------------|----------|----------|----------|----------|----------|----------|----------|----------------------------|----------|----------|----------|----------|----------|----------|--|

| AD2            | AD0        | A6             | A5       | A4       | A3       | A2       | A1       | A0       | P7       | P6                    | P5       | P4       | P3       | P2       | P1       | P0       | P7       | P6                         | P5       | P4       | P3       | P2       | P1       | P0       |  |

| SCL            | GND        | 1              | 1        | 0        | 0        | 0        | 0        | 0        | 1        | 1                     | 1        | 1        | 0        | 0        | 0        | 0        | Y        | Y                          | Y        | Y        | —        | —        | —        | —        |  |

| SCL            | V+         | 1              | 1        | 0        | 0        | 0        | 0        | 1        | 1        | 1                     | 1        | 1        | 1        | 1        | 1        | 1        | Y        | Y                          | Y        | Y        | Y        | Y        | Y        | Y        |  |

| SCL            | SCL        | 1              | 1        | 0        | 0        | 0        | 1        | 0        | 1        | 1                     | 1        | 1        | 1        | 1        | 1        | 1        | Y        | Y                          | Y        | Y        | Y        | Y        | Y        | Y        |  |

| SCL            | SDA        | 1              | 1        | 0        | 0        | 0        | 1        | 1        | 1        | 1                     | 1        | 1        | 1        | 1        | 1        | 1        | Y        | Y                          | Y        | Y        | Y        | Y        | Y        | Y        |  |

| SDA            | GND        | 1              | 1        | 0        | 0        | 1        | 0        | 0        | 1        | 1                     | 1        | 1        | 1        | 0        | 0        | 0        | 0        | Y                          | Y        | Y        | Y        | —        | —        | —        |  |

| SDA            | V+         | 1              | 1        | 0        | 0        | 1        | 0        | 1        | 1        | 1                     | 1        | 1        | 1        | 1        | 1        | 1        | Y        | Y                          | Y        | Y        | Y        | Y        | Y        | Y        |  |

| SDA            | SCL        | 1              | 1        | 0        | 0        | 1        | 1        | 0        | 1        | 1                     | 1        | 1        | 1        | 1        | 1        | 1        | Y        | Y                          | Y        | Y        | Y        | Y        | Y        | Y        |  |

| SDA            | SDA        | 1              | 1        | 0        | 0        | 1        | 1        | 1        | 1        | 1                     | 1        | 1        | 1        | 1        | 1        | 1        | Y        | Y                          | Y        | Y        | Y        | Y        | Y        | Y        |  |

| <b>GND</b>     | <b>GND</b> | <b>1</b>       | <b>1</b> | <b>0</b> | <b>1</b> | <b>0</b> | <b>0</b> | <b>0</b> | <b>0</b> | <b>0</b>              | <b>0</b> | <b>0</b> | <b>0</b> | <b>0</b> | <b>0</b> | <b>0</b> | <b>—</b> | <b>—</b>                   | <b>—</b> | <b>—</b> | <b>—</b> | <b>—</b> | <b>—</b> | <b>—</b> |  |

| <b>GND</b>     | <b>V+</b>  | <b>1</b>       | <b>1</b> | <b>0</b> | <b>1</b> | <b>0</b> | <b>0</b> | <b>1</b> | <b>0</b> | <b>0</b>              | <b>0</b> | <b>0</b> | <b>0</b> | <b>1</b> | <b>1</b> | <b>1</b> | <b>1</b> | <b>—</b>                   | <b>—</b> | <b>—</b> | <b>Y</b> | <b>Y</b> | <b>Y</b> | <b>Y</b> |  |

| GND            | SCL        | 1              | 1        | 0        | 1        | 0        | 1        | 0        | 0        | 0                     | 0        | 0        | 0        | 1        | 1        | 1        | 1        | —                          | —        | —        | Y        | Y        | Y        | Y        |  |

| GND            | SDA        | 1              | 1        | 0        | 1        | 0        | 1        | 1        | 0        | 0                     | 0        | 0        | 0        | 1        | 1        | 1        | 1        | —                          | —        | —        | Y        | Y        | Y        | Y        |  |

| <b>V+</b>      | <b>GND</b> | <b>1</b>       | <b>1</b> | <b>0</b> | <b>1</b> | <b>1</b> | <b>0</b> | <b>0</b> | <b>1</b> | <b>1</b>              | <b>1</b> | <b>1</b> | <b>1</b> | <b>0</b> | <b>0</b> | <b>0</b> | <b>0</b> | <b>Y</b>                   | <b>Y</b> | <b>Y</b> | <b>Y</b> | <b>—</b> | <b>—</b> | <b>—</b> |  |

| <b>V+</b>      | <b>V+</b>  | <b>1</b>       | <b>1</b> | <b>0</b> | <b>1</b> | <b>1</b> | <b>0</b> | <b>1</b> | <b>1</b> | <b>1</b>              | <b>1</b> | <b>1</b> | <b>1</b> | <b>1</b> | <b>1</b> | <b>1</b> | <b>1</b> | <b>Y</b>                   | <b>Y</b> | <b>Y</b> | <b>Y</b> | <b>Y</b> | <b>Y</b> | <b>Y</b> |  |

| V+             | SCL        | 1              | 1        | 0        | 1        | 1        | 1        | 0        | 1        | 1                     | 1        | 1        | 1        | 1        | 1        | 1        | 1        | Y                          | Y        | Y        | Y        | Y        | Y        | Y        |  |

| V+             | SDA        | 1              | 1        | 0        | 1        | 1        | 1        | 1        | 1        | 1                     | 1        | 1        | 1        | 1        | 1        | 1        | 1        | Y                          | Y        | Y        | Y        | Y        | Y        | Y        |  |

# 8個のプッシュプルおよび8個のオープンドレインI/O付き、 I<sup>2</sup>Cポートエキスパンダ

MAX7325

表3. MAX7325の出力O8~O15のアドレスマップ

| PIN CONNECTION |            | DEVICE ADDRESS |          |          |          |          |          |          |          | OUTPUTS POWER-UP DEFAULT |          |          |          |          |          |          |  |

|----------------|------------|----------------|----------|----------|----------|----------|----------|----------|----------|--------------------------|----------|----------|----------|----------|----------|----------|--|

| AD2            | AD0        | A6             | A5       | A4       | A3       | A2       | A1       | A0       | O15      | O14                      | O13      | O12      | O11      | O10      | O9       | O8       |  |

| SCL            | GND        | 1              | 0        | 1        | 0        | 0        | 0        | 0        | 1        | 1                        | 1        | 1        | 0        | 0        | 0        | 0        |  |

| SCL            | V+         | 1              | 0        | 1        | 0        | 0        | 0        | 1        | 1        | 1                        | 1        | 1        | 1        | 1        | 1        | 1        |  |

| SCL            | SCL        | 1              | 0        | 1        | 0        | 0        | 1        | 0        | 1        | 1                        | 1        | 1        | 1        | 1        | 1        | 1        |  |

| SCL            | SDA        | 1              | 0        | 1        | 0        | 0        | 1        | 1        | 1        | 1                        | 1        | 1        | 1        | 1        | 1        | 1        |  |

| SDA            | GND        | 1              | 0        | 1        | 0        | 1        | 0        | 0        | 1        | 1                        | 1        | 1        | 0        | 0        | 0        | 0        |  |

| SDA            | V+         | 1              | 0        | 1        | 0        | 1        | 0        | 1        | 1        | 1                        | 1        | 1        | 1        | 1        | 1        | 1        |  |

| SDA            | SCL        | 1              | 0        | 1        | 0        | 1        | 1        | 0        | 1        | 1                        | 1        | 1        | 1        | 1        | 1        | 1        |  |

| SDA            | SDA        | 1              | 0        | 1        | 0        | 1        | 1        | 1        | 1        | 1                        | 1        | 1        | 1        | 1        | 1        | 1        |  |

| <b>GND</b>     | <b>GND</b> | <b>1</b>       | <b>0</b> | <b>1</b> | <b>1</b> | <b>0</b> | <b>0</b> | <b>0</b> | <b>0</b> | <b>0</b>                 | <b>0</b> | <b>0</b> | <b>0</b> | <b>0</b> | <b>0</b> | <b>0</b> |  |

| <b>GND</b>     | <b>V+</b>  | <b>1</b>       | <b>0</b> | <b>1</b> | <b>1</b> | <b>0</b> | <b>0</b> | <b>1</b> | <b>0</b> | <b>0</b>                 | <b>0</b> | <b>0</b> | <b>1</b> | <b>1</b> | <b>1</b> | <b>1</b> |  |

| GND            | SCL        | 1              | 0        | 1        | 1        | 0        | 1        | 0        | 0        | 0                        | 0        | 0        | 1        | 1        | 1        | 1        |  |

| GND            | SDA        | 1              | 0        | 1        | 1        | 0        | 1        | 1        | 0        | 0                        | 0        | 0        | 1        | 1        | 1        | 1        |  |

| <b>V+</b>      | <b>GND</b> | <b>1</b>       | <b>0</b> | <b>1</b> | <b>1</b> | <b>1</b> | <b>0</b> | <b>0</b> | <b>1</b> | <b>1</b>                 | <b>1</b> | <b>1</b> | <b>0</b> | <b>0</b> | <b>0</b> | <b>0</b> |  |

| <b>V+</b>      | <b>V+</b>  | <b>1</b>       | <b>0</b> | <b>1</b> | <b>1</b> | <b>1</b> | <b>0</b> | <b>1</b> | <b>1</b> | <b>1</b>                 | <b>1</b> | <b>1</b> | <b>1</b> | <b>1</b> | <b>1</b> | <b>1</b> |  |

| V+             | SCL        | 1              | 0        | 1        | 1        | 1        | 1        | 0        | 1        | 1                        | 1        | 1        | 1        | 1        | 1        | 1        |  |

| V+             | SDA        | 1              | 0        | 1        | 1        | 1        | 1        | 1        | 1        | 1                        | 1        | 1        | 1        | 1        | 1        | 1        |  |

## ポート入力

I/Oポート入力は、エキスパンダの電源電圧によって定義されるCMOSロジックレベルで切り換えが行われ、デバイスの電源電圧とは無関係に+6Vまでの過電圧耐性があります。

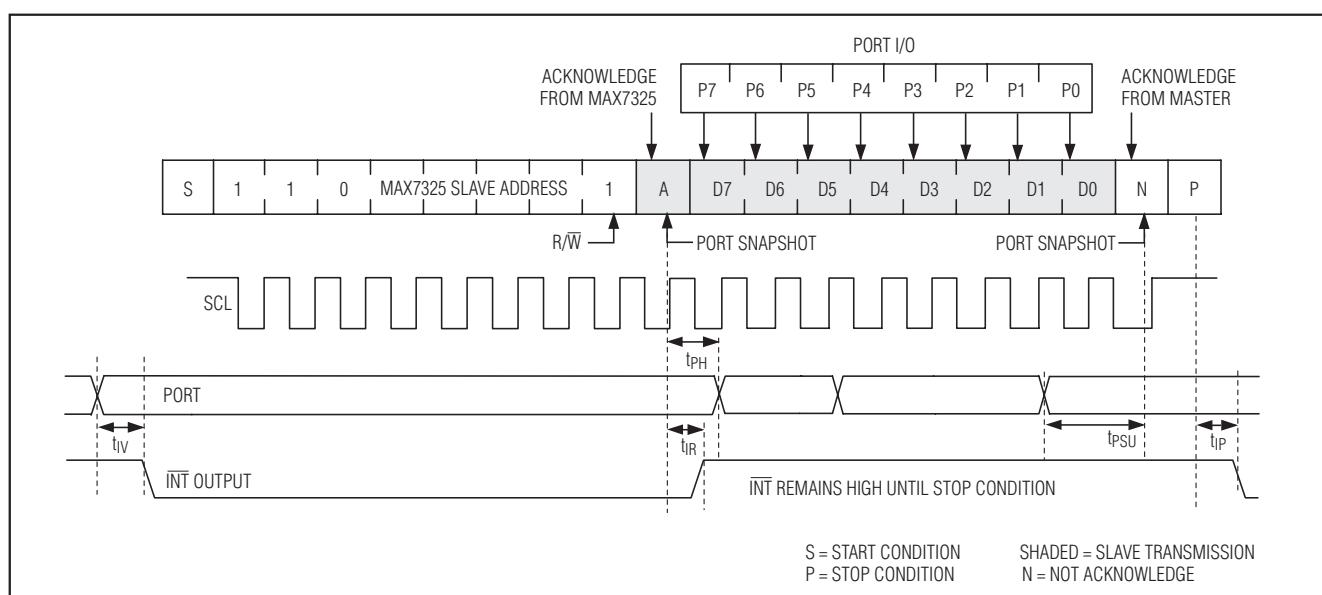

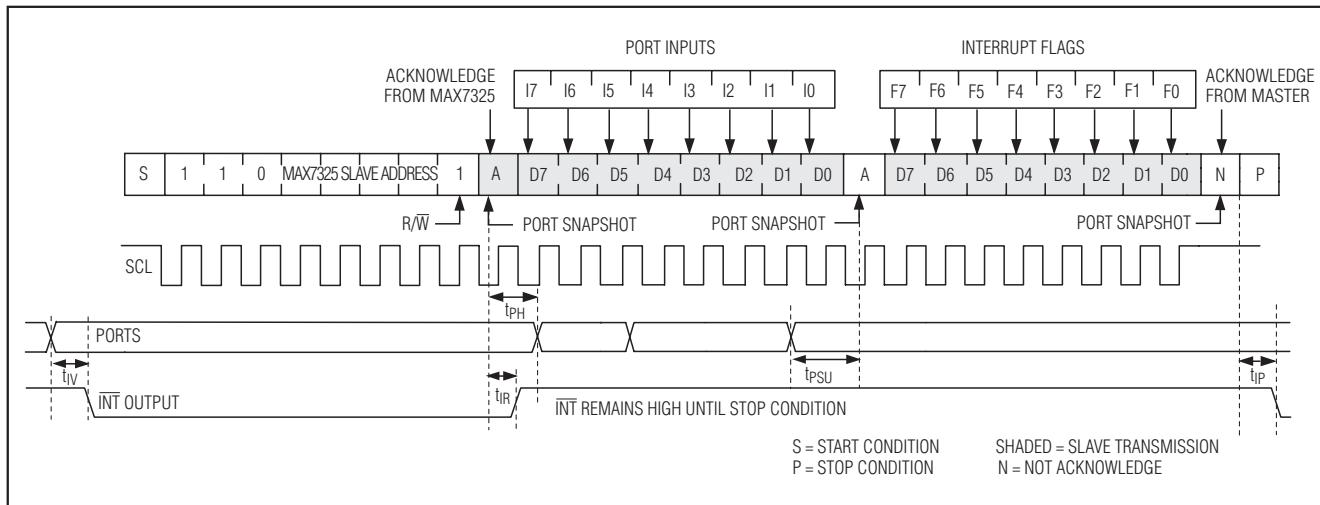

## I/Oポート入力の遷移検出

入力として設定されているすべてのI/Oは、シリアルインターフェース経由で最後にエキスパンダがアクセスされてから変化していないか監視されます。ポートの

状態は内部の「スナップショット」レジスタに格納され、遷移の監視に使用されます。スナップショットは、実際の入力の状態と常に比較され、いずれかのポート入力について変化が検出されると、INTがアサートされて状態の変化を知らせます。MAX7325の読み書きアクセスごとに、I<sup>2</sup>Cのアクノリッジ中に入力ポートがサンプリングされ(内部でスナップショットレジスタにラッチされ)、元の遷移フラグがクリアされます。それまでのポート遷移フラグは、2バイトの読み取りシーケンスの第2バイトとしてシリアルインターフェース経由で読み取られます。

# 8個のプッシュプルおよび8個のオープンドレインI/O付き、 I<sup>2</sup>Cポートエキスパンダ

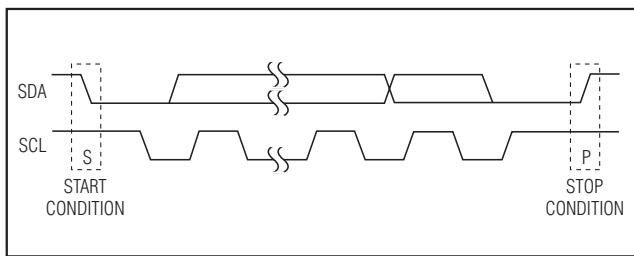

## シリアルインターフェース

### シリアルアドレス指定

MAX7325はI<sup>2</sup>Cインターフェース経由でデータの送受信を行い、スレーブとして動作します。このインターフェースは、シリアルデータライン(SDA)とシリアルクロックライン(SCL)を使用して、マスタ(複数可)とスレーブ(複数可)の間での双方向通信を実現するものです。マスタはMAX7325との間におけるすべてのデータ転送を開始し、データ転送の同期を取るためのSCLクロックを生成します(図1)。

SDAは、入力とオープンドレイン出力の両方として動作します。SDAにはプルアップ抵抗(通常は4.7kΩ)が必要です。SCLは入力としてのみ動作します。2線式インターフェース上に複数のマスタが存在する場合、またはシングルマスタシステムのマスタがオープンドレインのSCL出力を備えている場合には、SCLにもプルアップ抵抗(通常は4.7kΩ)が必要です。

個々の伝送は、マスタが送信するスタート状態、それに続くMAX7325の7ビットのスレーブアドレスとR/Wビット、1つ以上のデータバイト、そして最後にストップ状態という組み合わせで構成されます(図2)。

### スタートおよびストップ状態

インターフェースがビジーでないときは、SCLとSDAの両方ともハイの状態に保たれています。マスタは、SCLがハイの間にSDAをハイからローに遷移させることによってスタート(S)状態を発行し、転送の開始を伝えます。スレーブとの通信を終えたマスタは、SCLがハイの間にSDAをローからハイに遷移させることによってストップ(P)状態を発行します。これでバスが解放され、次の転送が可能になります(図2)。

### ビット転送

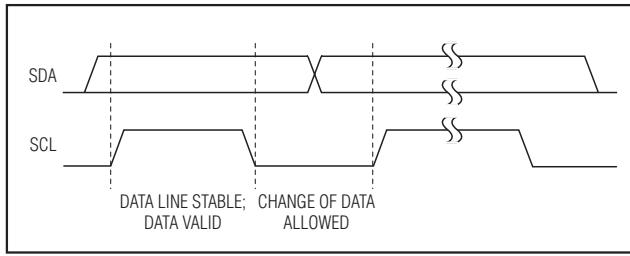

各クロックパルスの間に、1つのデータビットが転送されます。SDA上のデータは、SCLがハイの間は安定している必要があります(図3)。

図1. 2線式シリアルインターフェースのタイミング詳細

図2. スタートおよびストップ状態

図3. ビット転送

# 8個のプッシュプルおよび8個のオープンドレインI/O付き、 I<sup>2</sup>Cポートエキスパンダ

MAX7325

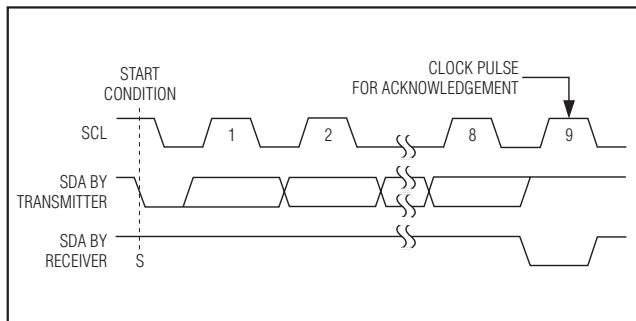

## アクノリッジ

アクノリッジビットは、データの各バイトの受領を通知するために受信側が使用する、9番目のビットです(図4)。転送されるすべてのバイトが実際に9ビットを必要とすることになります。マスタが9番目のクロックパルスを生成し、受信側はアクノリッジのクロックパルスの間SDAをプルダウンして、クロックパルスのハイの期間SDAラインが安定するようにします。マスタからMAX7325への送信中はMAX7325が受信側になるため、MAX7325がアクノリッジビットを生成します。MAX7325からマスタへの送信中はマスタが受信側になるため、マスタがアクノリッジビットを生成します。

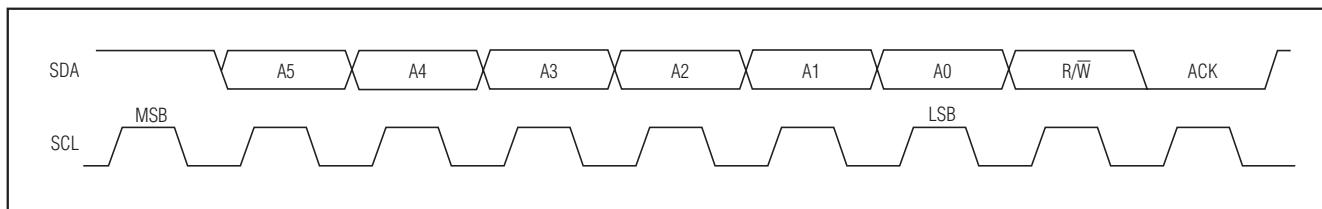

## スレーブアドレス

個々のMAX7325は、2つの異なる7ビット長のスレーブアドレスを持ちます(表2および3)。アドレスは、8個のプッシュプル出力と通信を行うか、8個のI/Oと通信を行います。

7ビットのスレーブアドレスに続く8番目のビットはR/Wビットです。書き込みコマンド時はロー、読み取りコマンド時はハイになります(図5)。MAX7325のスレーブアドレスの先頭(A6)、2番目(A5)、および3番目(A4)のビットは、常に1、1、0(P0～P7)または1、0、1(O8～O15)になります。AD0とAD2を、GND、V+、SDA、またはSCLに接続して、スレーブアドレスのビットA3、A2、

図4. アクノリッジ

図5. スレーブアドレス

A1、およびA0を選択します。すなわちMAX7325は16通りのスレーブアドレスのペアを選択可能であり(表2および3)、1つのI<sup>2</sup>Cバス上に最大16個のMAX7325デバイスが存在できることになります。

## MAX7325へのアクセス

MAX7325には、I<sup>2</sup>Cインターフェースを通してアクセスします。MAX7325は、8個のオープンドレインI/Oポート(P0～P7)と8個のプッシュプルポート(O8～O15)で、2つの異なる7ビットのスレーブアドレスを持っています。表2および3をご覧ください。

MAX7325のI/Oポート(P0～P7)からの**単一バイト読み取り**では、8個のI/Oポートの状態が返され、マスタがスレーブアドレスバイトをアクノリッジする際に、内部の遷移フラグとINT出力の両方がクリアされます。MAX7325の8個のプッシュプルポート(O8～O15)からの**単一バイト読み取り**では、8個の出力ポートの状態が返され、入力として読み取られます。

MAX7325のI/Oポート(P0～P7)からの**2バイト読み取り**では、8個のI/Oポートの状態が(単一バイト読み取りと同様に)返され、その後に遷移フラグが続けます。この場合も、内部の遷移フラグとINT出力は、マスタがスレーブアドレスバイトのアクノリッジを行う際にクリアされますが、それまでの遷移フラグのデータが2番目のバイトとして送られます。MAX7325のプッシュプル出力ポートからの**2バイト読み取り**では、8個の出力ポートの状態が繰り返して返却され、入力として読み取られます。

MAX7325のI/Oポート(P0～P7)からの**マルチバイト読み取り**(I<sup>2</sup>Cのストップビットまでに3バイト以上)では、ポートデータと遷移フラグが繰り返して返却されます。転送ごとにポートのデータが再サンプリングされ、遷移フラグが毎回リセットされるため、マルチバイト読み取りでは最新のデータが連続的に返され、あらゆる入力ポートの変化を識別することができます。

# 8個のプッシュプルおよび8個のオープンドレインI/O付き、 I<sup>2</sup>Cポートエキスパンダ

読み取りシーケンス中にポート入力データの変化が発生すると、I<sup>2</sup>Cのストップビット中にINTが再びアサートされます。MAX7325は、単一バイトまたはマルチバイト読み取り中に新たな割込みを生成することはありません。

入力ポートデータは、先行するI<sup>2</sup>Cアクノリッジビット(単一バイトまたは2バイト読み取りの場合、I<sup>2</sup>Cスレーブアドレスのアクノリッジビット)の間にサンプリングされます。

MAX7325のプッシュプルポートからのマルチバイト読み取りでは、8個の出力ポートの状態が繰り返して返却され、入力として読み取られます。

MAX7325のいずれかのポートグループに対する単一バイト書き込みでは、8個すべてのポートの論理状態が設定されます。

MAX7325のいずれかのポートグループに対するマルチバイト書き込みでは、8個すべてのポートの論理状態が繰り返し設定されます。

## MAX7325からの読み取り

MAX7325のオープンドレインI/Oポートからの読み取りは、マスタがR/Wビットをハイにしたポートグループのスレーブアドレスを送信することで始まります。MAX7325はスレーブアドレスをアクノリッジし、アクノリッジビットの間にポートのサンプリングを行います。スレーブアドレスのアクノリッジの間に、INTはアサートを解除されます。

通常、マスタはMAX7325から1バイトまたは2バイトを読み取り、最後のバイトを除いて、各バイトを受け取るごとにマスタによってアクノリッジが行われます。

マスタがMAX7325のオープンドレインポートから1バイトを読み取り、それに続いてストップ状態を発行すると(図6)、MAX7325は現在のポートデータを送信し、変化フラグをクリアし、遷移検出を再開します。INTはスレーブアドレスのアクノリッジ中にアサート解除されます。新しいスナップショットデータは、マスタに送信される現在の入力ポートデータになるため、転送中

図6. MAX7325のオープンドレインポートからの読み取り(1バイトのデータ)

8個のプッシュプルおよび8個のオープンドレインI/O付き、

I<sup>2</sup>Cポートエキスパンダ

に発生する入力ポートの変化はすべて検出されます。

INTはストップ状態までハイのままになります。

マスターはMAX7325のオープンドレインポートから2バイトを読み取り、その後ストップ状態を発行することができます(図7)。この場合、MAX7325は現在のポートデータを送信し、その後に変化フラグを送信します。そして変化フラグがクリアされ、遷移検出がリセットされます。 $\overline{\text{INT}}$ はスレーブアクノリッジの間ハイ(外付けプルアップ抵抗が取り付けられていない場合はハイインピーダンス)になります。新しいスナップショットデータは、マスターに送信される現在の入力ポートデータになるため、転送中に発生するポートの変化はすべて検出されます。 $\overline{\text{INT}}$ はストップ状態までハイのままになります。

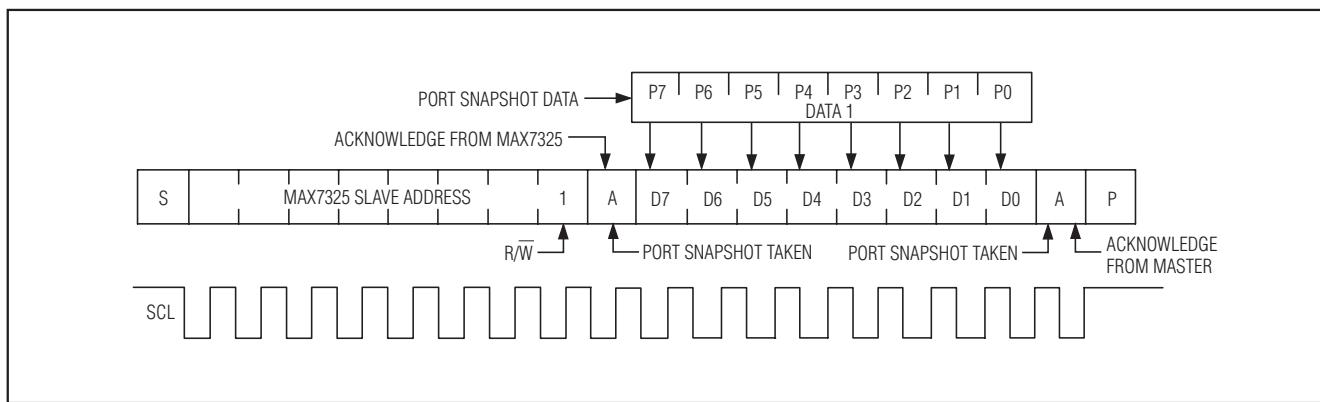

MAX7325のプッシュプルポートからの読み取りは、マスターがR/Wビットをハイにしたグループのスレーブアドレスを送信することで始まります。MAX7325はスレーブアドレスをアクノリッジし、アクノリッジビットの間に、出力ポートの論理状態をサンプリングします。マスターはMAX7325のプッシュプルポートから1バイト以上を読み取り、トップ状態を発行することができます(図8)。MAX7325は、アクノリッジ中に(ポートの出力ラッチではなく)実際のポート出力から読み取った、現在のポートデータを送信します。ポートが本来プログラムされたもの以外の論理状態を強制されている場合、読み取り結果にそれが反映されます。容量性負荷を駆動する場合、読み取ったポートレベルの検証アルゴリズムでは、RCの立上り/立下り時間を考慮に入れる必要があります。

# MAX7325

図7. MAX7325のオープンドレインポートからの読み取り(2バイトのデータ)

図8. MAX7325のプッシュプルポートからの読み取り

# 8個のプッシュプルおよび8個のオープンドレインI/O付き、 I<sup>2</sup>Cポートエキスパンダ

通常、マスタはMAX7325のプッシュプルポートから1バイトを読み取り、ストップ状態を発行します(図8)。しかし、マスタはMAX7325のグループBポートから2バイト以上を読み取って、ストップ状態を発行することもできます。この場合、MAX7325は各アクノリッジの間にポート出力の再サンプリングを行い、毎回新しいデータを送信します。

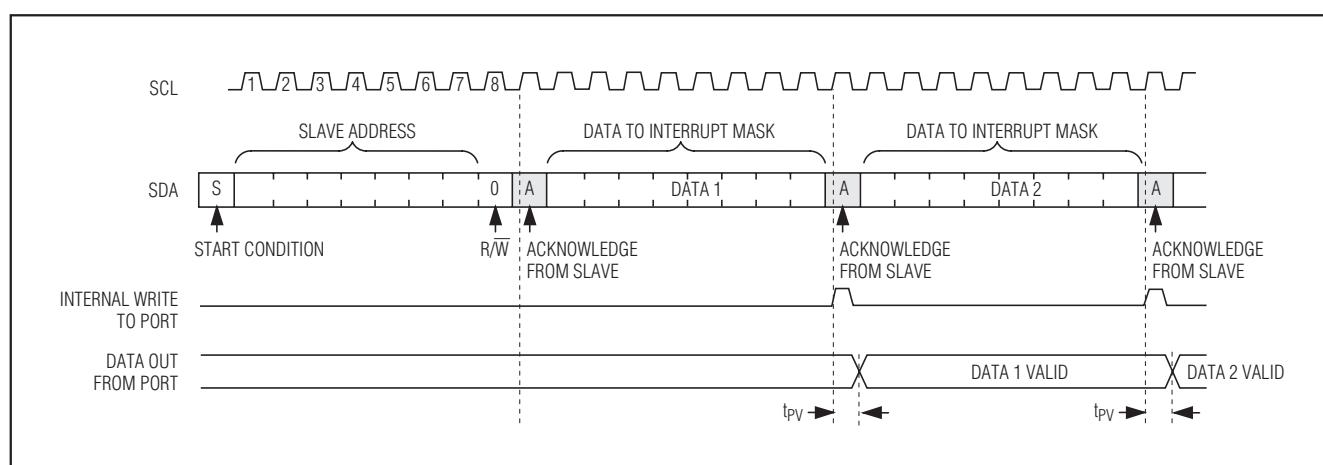

## MAX7325への書き込み

MAX7325のいずれかの出力ポートグループへの書き込みは、マスタがR/Wビットをローにしたグループのスレーブアドレスを送信することで始まります。MAX7325はスレーブアドレスをアクノリッジし、アクノリッジビットの間にポートのサンプリングを行います。オープンドレインポートへの書き込み時ののみ、INTはスレーブアクノリッジの間ハイ(外付けプルアップ抵抗が取り付けられていない場合はハイインピーダンス)になります。これでマスタは、1バイト以上のデータ送信を行うことができます。MAX7325はこれら後続のデータバイトのアクノリッジを行い、マスタがストップ状態を発行するまで、新しいバイトごとに該当するグループのポートを更新します(図9)。

## アプリケーション情報

### ポート入力とより高いまたは低い論理電圧からのI<sup>2</sup>Cインターフェースレベル変換

MAX7325のSDA、SCL、ADO、AD2、RST、INT、08～015、およびP0～P7は、+6Vまで過電圧保護されています。このためMAX7325は、I<sup>2</sup>Cインターフェースや8個のI/Oポートの中により高い論理レベル(たとえば+5V)で入力として駆動されているものがあるときに、

より低い電源電圧(たとえば+3.3V)で動作することが可能になっています。

MAX7325は、I<sup>2</sup>CインターフェースやI/OポートP0～P7の中により低い論理レベル(たとえば+2.5V)で駆動されているものがあるときに、より高い電源電圧(たとえば+3V)で動作することが可能です。V+ < 1.8Vの場合、いずれの入力についても論理ハイをアサートするには最小電圧 $0.8 \times V_+$ を印加してください。V+ ≥ 1.8Vの場合、論理ハイをアサートするには $0.7 \times V_+$ を印加してください。たとえば、MAX7325が+5V電源で動作している場合、公称+3.3Vの論理ハイは認識されない可能性があります。入力レベル変換のための1つの方法は、MAX7325のI/Oをオープンドレインの出力から駆動することです。V+以上の電源へのプルアップ抵抗を使用して、ハイの論理電圧が確実に $0.7 \times V_+$ より大きくなるようにしてください。

## ポート出力信号レベル変換

オープンドレイン出力アーキテクチャによって、MAX7325の電源よりも高い電圧や低い電圧へのレベル変換が可能になっています。任意の出力に外付けのプルアップ抵抗を使用して、ハイインピーダンスの論理ハイ状態を正の電圧レベルに変換してください。この抵抗は最大+6Vまでの任意の電圧に接続することが可能で、論理ロー状態においてシンク電流が20mAを越えないことを保証するように抵抗値を選択します。CMOS入力とのインターフェースの場合、最初はプルアップ抵抗値220kΩから試すのが適切です。消費電力が最重要ではないアプリケーションや、所定の容量性負荷に対するより高速な立ち上り時間が要求されるアプリケーションでは、より小さな抵抗を使用してノイズ耐性を向上させてください。

図9. MAX7325への書き込み

# 8個のプッシュプルおよび8個のオープンドレインI/O付き、 I<sup>2</sup>Cポートエキスパンダ

MAX7325

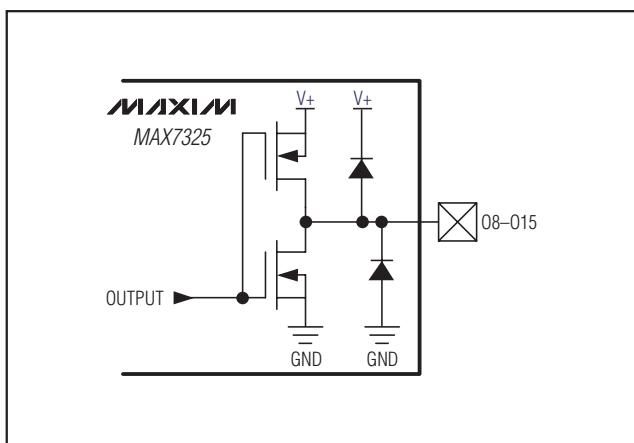

プッシュプル出力ポートは、いずれもV+とGNDへの保護ダイオードを備えています。ポート出力がV+より高い電圧またはGNDより低い電圧に駆動されると、適切な保護ダイオードが出力をダイオード降下分だけV+より上またはGNDより下にクランプします。MAX7325の電源がオフになると(V+ = 0V)、各出力ポートのV+とGNDへの保護ダイオードは、各出力からGNDへのダイオードクランプのように見えます(図10)。

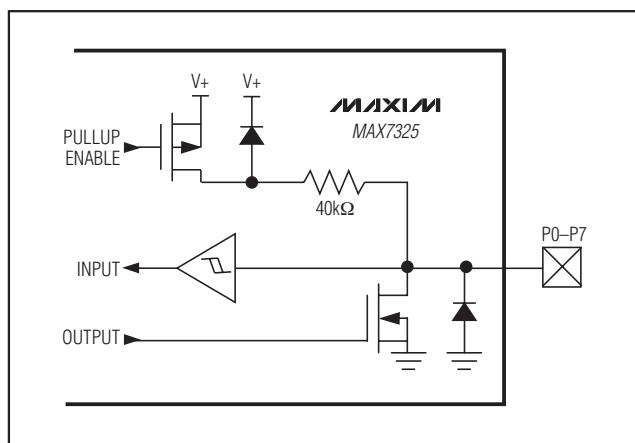

I/OポートP0～P7は、いずれもGNDへの保護ダイオードを備えています(図11)。ポートがGNDより低い電圧に駆動されると、保護ダイオードがGNDよりダイオード降下分だけ下にポートをクランプします。

I/OポートP0～P7は、イネーブルまたはディセーブルが可能な40kΩ (typ)のプルアップ抵抗も備えています。ポートがV+より高い電圧に駆動されると、プルアップイネーブルスイッチのボディダイオードが導通し、40kΩのプルアップ抵抗がイネーブルされます。MAX7325が電源オフされると(V+ = 0V)、各I/Oポートは0Vに接続されたダイオードと直列な40kΩの抵抗のように見えます。入力ポートはこれらすべての状況下において+6Vまで保護されます(図11)。

## LED負荷の駆動

出力のいずれかでLEDを駆動する場合、LEDと直列に抵抗を接続して、LEDの電流が20mAを超えないように制限する必要があります。LEDのカソードをMAX7325のポートに接続し、LEDのアノードを直列の電流制限抵抗R<sub>LED</sub>を通してV+に接続してください。LEDを点灯するには、ポートの出力をローにします。次の式に従って抵抗値を選択してください。

$$R_{LED} = (V_{SUPPLY} - V_{LED} - V_{OL}) / I_{LED}$$

ただし、

R<sub>LED</sub>はLEDと直列な抵抗の抵抗値(Ω)。

図10. MAX7325のプッシュプル出力ポート構造

V<sub>SUPPLY</sub>はLEDの駆動に使用する電源電圧(V)。

V<sub>LED</sub>はLEDのフォワード電圧(V)。

V<sub>OL</sub>はI<sub>LED</sub>シンク時におけるMAX7325の出力口一電圧(V)。

I<sub>LED</sub>は希望するLEDの動作電流(A)。

たとえば、2.2Vの赤色LEDを+5V電源から10mAで動作させる場合、

$$R_{LED} = (5 - 2.2 - 0.1) / 0.01 = 270\Omega$$

## 20mAを超える負荷電流の駆動

MAX7325は、出力の並列化によってリレーのような20mAを超える電流が流れる負荷の駆動に使用することができます。負荷電流20mA当り少なくとも1つの出力を使用してください。たとえば、5V 330mWのリレーには66mAが流れるため、4個の出力を並列化する必要があります。MAX7325に書き込むことによって、ポートの任意の組み合わせを同時にセットまたはクリアすることができるため、出力の任意の組み合わせを負荷分散設計の一部として使用することができます。デバイス全体でのシンク電流の合計が100mAを超えないようにしてください。

MAX7325は、誘導性負荷(リレーなど)の両端に逆バイアスダイオードを接続することによって、誘導性負荷をスイッチオフする際に生成される負の電圧トランジエントから保護する必要があります。誘導性負荷の動作電流よりも大きくなるようにダイオードのピーク電流を選択してください。

## 電源について

MAX7325は、+1.71V～+5.5Vの電源電圧で動作します。できる限りデバイスに近い位置で、少なくとも0.047μFのセラミックコンデンサを使って電源をGNDにバイパスしてください。TQFN版の場合、さらにエクスポートズドパッドをGNDに接続してください。

図11. MAX7325のオープンドレインI/Oポート構造

# 8個のプッシュプルおよび8個のオープンドレインI/O付き、 I<sup>2</sup>Cポートエキスパンダ

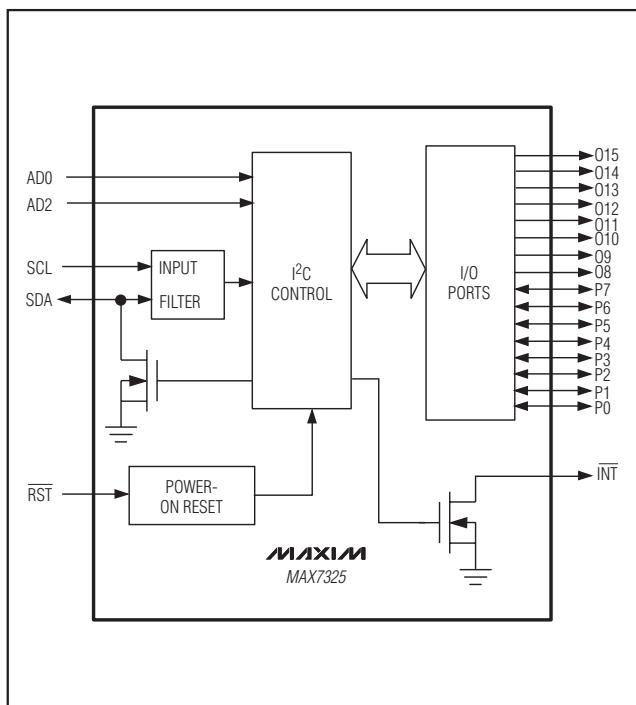

## 機能ブロック図

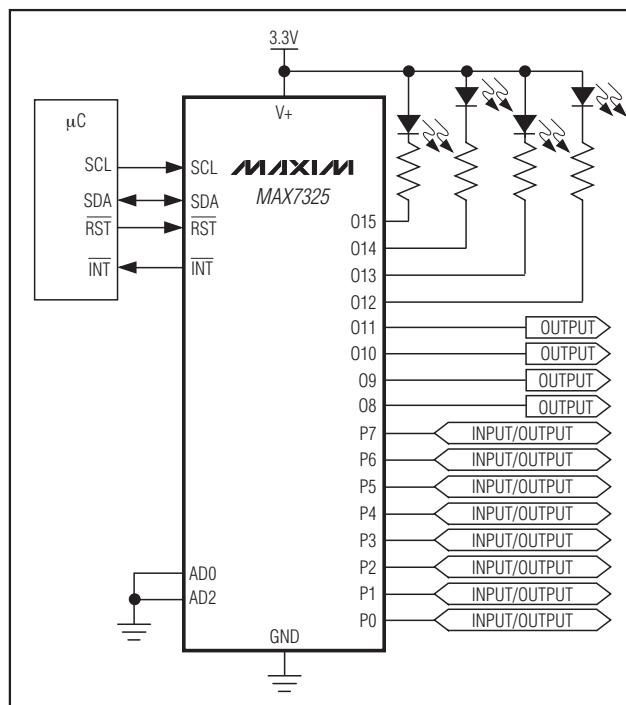

## 標準動作回路

## ピン配置(続き)

TOP VIEW

## チップ情報

PROCESS: BiCMOS

# 8個のプッシュプルおよび8個のオープンドレインI/O付き、 I<sup>2</sup>Cポートエキスパンダ

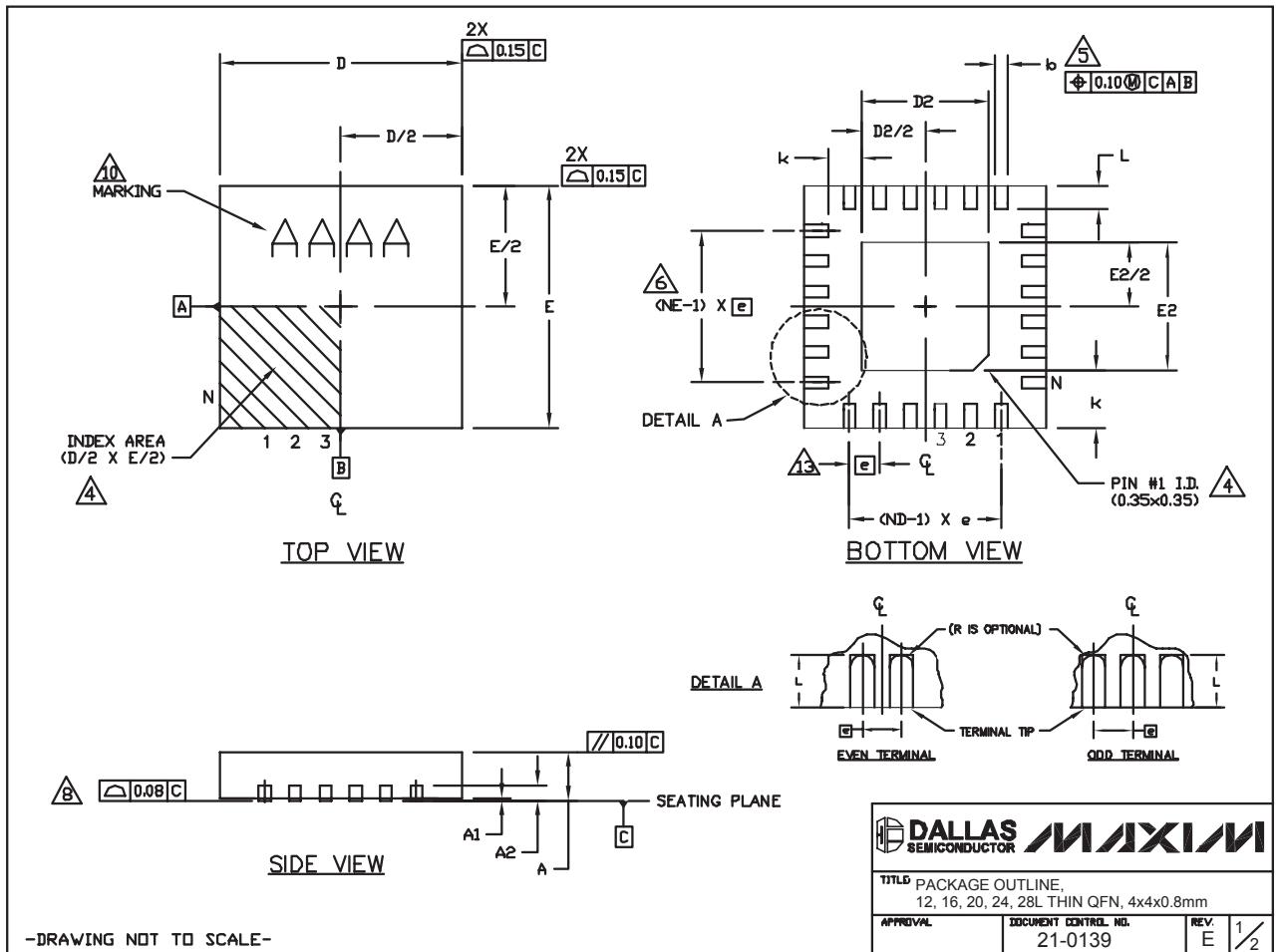

## パッケージ

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、[japan.maxim-ic.com/packages](http://japan.maxim-ic.com/packages)をご参照下さい。)

MAX7325

# 8個のプッシュプルおよび8個のオープンドレインI/O付き、 I<sup>2</sup>Cポートエキスパンダ

## パッケージ(続き)

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、[japan.maxim-ic.com/packages](http://japan.maxim-ic.com/packages)をご参照下さい。)

| COMMON DIMENSIONS |          |      |      |          |      |      |          |      |      |          |      | EXPOSED PAD VARIATIONS |          |      |      |      |      |      |      |                          |      |      |     |

|-------------------|----------|------|------|----------|------|------|----------|------|------|----------|------|------------------------|----------|------|------|------|------|------|------|--------------------------|------|------|-----|

| PKG.<br>REF.      | 12L 4x4  |      |      | 16L 4x4  |      |      | 20L 4x4  |      |      | 24L 4x4  |      |                        | 28L 4x4  |      |      | D2   |      | E2   |      | DOWN<br>BONDS<br>ALLOWED |      |      |     |

|                   | MIN.     | NOM. | MAX.                   | MIN.     | NOM. | MAX. | MIN. | NOM. | MAX. | MIN. | NOM.                     | MAX. |      |     |

| A                 | 0.70     | 0.75 | 0.80 | 0.70     | 0.75 | 0.80 | 0.70     | 0.75 | 0.80 | 0.70     | 0.75 | 0.80                   | 0.70     | 0.75 | 0.80 | 1.95 | 2.10 | 2.25 | 1.95 | 2.10                     | 2.25 | YES  |     |

| A1                | 0.0      | 0.02 | 0.05 | 0.0      | 0.02 | 0.05 | 0.0      | 0.02 | 0.05 | 0.0      | 0.02 | 0.05                   | 0.0      | 0.02 | 0.05 | 1.95 | 2.10 | 2.25 | 1.95 | 2.10                     | 2.25 | NO   |     |

| A2                | 0.20 REF |      |                        | 0.20 REF |      |      | 1.95 |      | 1.95 |      | 1.95                     |      | YES  |     |

| b                 | 0.25     | 0.30 | 0.35 | 0.25     | 0.30 | 0.35 | 0.20     | 0.25 | 0.30 | 0.18     | 0.23 | 0.30                   | 0.15     | 0.20 | 0.25 | 1.95 | 2.10 | 2.25 | 1.95 | 2.10                     | 2.25 | NO   |     |

| D                 | 3.90     | 4.00 | 4.10 | 3.90     | 4.00 | 4.10 | 3.90     | 4.00 | 4.10 | 3.90     | 4.00 | 4.10                   | 3.90     | 4.00 | 4.10 | 3.90 | 4.00 | 4.10 | 3.90 | 4.00                     | 4.10 | YES  |     |

| E                 | 3.90     | 4.00 | 4.10 | 3.90     | 4.00 | 4.10 | 3.90     | 4.00 | 4.10 | 3.90     | 4.00 | 4.10                   | 3.90     | 4.00 | 4.10 | 3.90 | 4.00 | 4.10 | 3.90 | 4.00                     | 4.10 | NO   |     |

| e                 | 0.80     | BSC. | 0.65 | BSC.     | 0.50 | BSC. | 0.50     | BSC. | 0.40 | BSC.     | 0.50 | BSC.                   | 0.40     | BSC. | 0.40 | BSC. | 2.45 | 2.60 | 2.63 | 2.45                     | 2.60 | 2.63 | YES |

| k                 | 0.25     | -    | -    | 0.25     | -    | -    | 0.25     | -    | -    | 0.25     | -    | -                      | 0.25     | -    | -    | 1.95 | 2.10 | 2.25 | 1.95 | 2.10                     | 2.25 | YES  |     |

| L                 | 0.45     | 0.55 | 0.65 | 0.45     | 0.55 | 0.65 | 0.45     | 0.55 | 0.65 | 0.30     | 0.40 | 0.50                   | 0.30     | 0.40 | 0.50 | 1.95 | 2.10 | 2.25 | 1.95 | 2.10                     | 2.25 | NO   |     |

| N                 | 12       |      |      | 16       |      |      | 20       |      |      | 24       |      |                        | 28       |      |      | 1.95 |      | 1.95 |      | 1.95                     |      | YES  |     |

| ND                | 3        |      |      | 4        |      |      | 5        |      |      | 6        |      |                        | 7        |      |      | 1.95 |      | 1.95 |      | 1.95                     |      | NO   |     |

| NE                | 3        |      |      | 4        |      |      | 5        |      |      | 6        |      |                        | 7        |      |      | 1.95 |      | 1.95 |      | 1.95                     |      | NO   |     |

| Yedec<br>Var.     | WGGB     |      |      | WGGC     |      |      | WGGD-1   |      |      | WGGD-2   |      |                        | WGGE     |      |      | 1.95 |      | 1.95 |      | 1.95                     |      | NO   |     |

NOTES:

1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

2. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

3. N IS THE TOTAL NUMBER OF TERMINALS.

THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A NOLD OR MARKED FEATURE.

DIMENSION b APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25 mm AND 0.30 mm FROM TERMINAL TIP.

ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

7. DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

9. DRAWING CONFORMS TO JEDEC NO220, EXCEPT FOR T2444-3, T2444-4 AND T2844-1.

MARKING IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

11. COPLANARITY SHALL NOT EXCEED 0.08mm

12. WARPAGE SHALL NOT EXCEED 0.10mm

LEAD CENTERLINES TO BE AT TRUE POSITION AS DEFINED BY BASIC DIMENSION "e", ±0.05.

14. NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY.

-DRAWING NOT TO SCALE-

| APPROVAL | DOCUMENT CONTROL NO. | REV.         |

|----------|----------------------|--------------|

|          | 21-0139              | E<br>2<br>/2 |

# 8個のプッシュプルおよび8個のオープンドレインI/O付き、 I<sup>2</sup>Cポートエキスパンダ

MAX7325

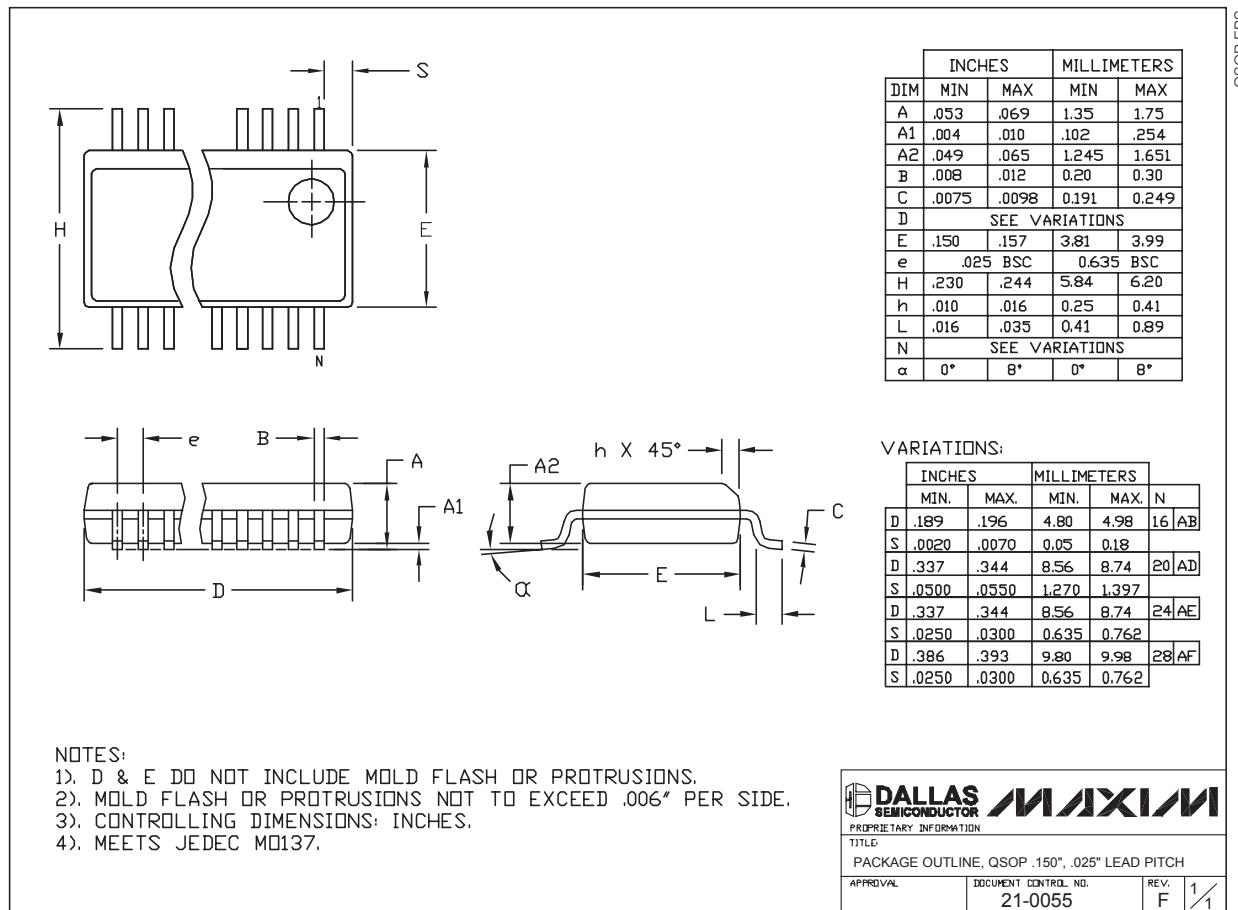

## パッケージ(続き)

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、[japan.maxim-ic.com/packages](http://japan.maxim-ic.com/packages)をご参照下さい。)

マキシム・ジャパン株式会社

〒169-0051 東京都新宿区西早稲田3-30-16(ホリゾン1ビル)

TEL. (03)3232-6141 FAX. (03)3232-6149

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。マキシムは随时予告なく回路及び仕様を変更する権利を留保します。

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

19

© 2006 Maxim Integrated Products, Inc. All rights reserved. MAXIM is a registered trademark of Maxim Integrated Products, Inc.