# Power over Ethernet用、ハイパワー クワッド、モノリシック、PSEコントローラ

**MAX5965A/MAX5965B**

## 概要

MAX5965A/MAX5965Bは、-48Vのモノリシッククワッドパワーコントローラで、IEEE® 802.3afに準拠し策定中のIEEE 802.3atに対応した給電機器(PSE)で使用するために設計されています。これらのデバイスは、IEEE 802.3af規格に準拠した受電機器(PD)の検出、分類、電流制限、DCおよびACの負荷切断の検出を行います。MAX5965A/MAX5965Bは、MAX5952/MAX5945/LTC4258/LTC4259A PSEコントローラとピンコンパチブルで、機能が追加されています。

MAX5965A/MAX5965Bは、ポート当り最大45Wを給電するハイパワーモードを備えています。MAX5965A/MAX5965Bは、ハイパワーPDの検出と分類のための新しいクラス5と2イベント分類(クラス6)を設けています。MAX5965A/MAX5965Bは、I<sup>2</sup>Cインターフェースを通じて各ポートの電流を瞬時に読み出します。また、MAX5965A/MAX5965Bには、レガシーパートのための大容量検出も用意されています。

これらのデバイスは、I<sup>2</sup>C対応の3線式シリアルインターフェースを備え、ソフトウェアによる完全な設定とプログラムが可能です。クラス過電流検出機能によって、PDに許容電流を上回る電流が流れかかどうかをシステムの電源管理で検出することができます。MAX5965A/MAX5965Bが備える豊富なプログラム能力は、システムの柔軟性を高め、フィールド診断および他のアプリケーションへの応用を可能にします。

MAX5965A/MAX5965Bは、さまざまなシステム要件を満たした4つの動作モードを備えています。自動モードでは、デバイスはソフトウェアによる監視なしで自動的に動作します。半自動モードでは、最初のソフトウェア起動後にポートに接続されたデバイスの検出と分類が自動的に行われますが、ソフトウェアによる指示があるまでそのポートの電源はオンにされません。マニュアルモードでは、ソフトウェアによってデバイスを完全に制御することが可能で、システム診断に有用です。シャットダウンモードでは、すべてのアクティビティを終了してポートへの電源を安全にオフにします。

MAX5965A/MAX5965Bは、入力低電圧ロツクアウト(UVLO)、入力低電圧検出、検出中の負荷安定性セーフティチェック、入力過電圧ロツクアウト、温度過昇検出、起動時の出力電圧スルーレート制限、パワーグッドステータス、および障害ステータスを提供します。MAX5965A/MAX5965Bは、起動タイムアウト、過電流タイムアウト、および負荷切断検出タイムアウトの設定が可能です。

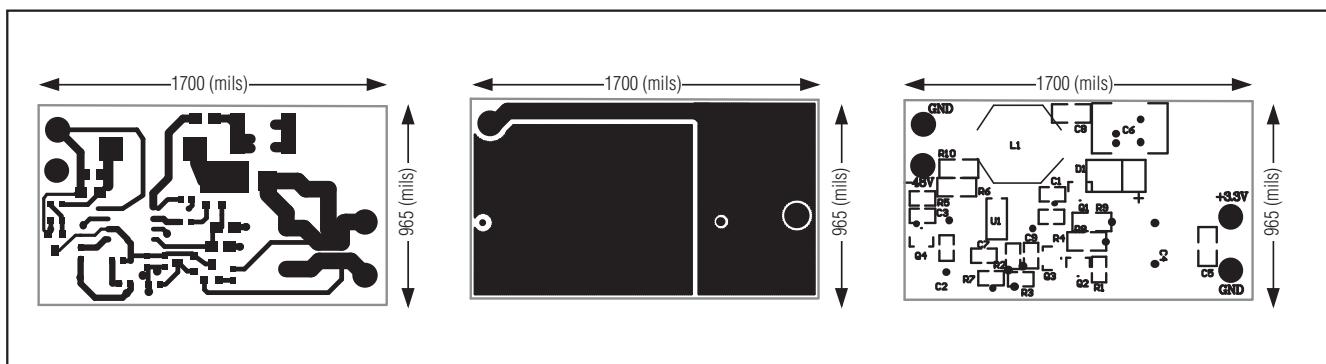

MAX5965A/MAX5965Bは、36ピンのSSOPパッケージで提供され、拡張(-40°C～+85°C)および上位民生用(0°C～+85°C)の両温度範囲での動作が保証されています。

## アプリケーション

給電機器(PSE)

スイッチ/ルータ

ミッドスパンパワーインジェクタ

IEEEはInstitute of Electrical and Electronics Engineers, Inc.の登録サービスマークです。

## 特長

- ◆ IEEE 802.3af準拠/フレIEEE 802.3at対応

- ◆ I<sup>2</sup>Cインターフェースを通じたポート電流の即時読出し

- ◆ ハイパワーモードでポート当り最大45Wが可能

- ◆ レガシーデバイスの大容量を検出

- ◆ MAX5952/MAX5945/LTC4258/LTC4259Aとピンコンパチブル

- ◆ 4つの独立したパワースイッチコントローラ

- ◆ PDの検出と分類(2イベント分類を含む)

- ◆ 検出中の負荷安定性セーフティチェックを選択可能

- ◆ DCおよびACの負荷除去検出をサポート

- ◆ I<sup>2</sup>C対応の3線式シリアルインターフェース

- ◆ 電流フォールドバックおよびデューティサイクル制御の電流制限

- ◆ オープンドレインのINT信号

- ◆ 直接高速シャットダウン制御機能

- ◆ クラス5の特別分類

## 型番

| PART                 | TEMP RANGE     | PIN-PACKAGE |

|----------------------|----------------|-------------|

| <b>MAX5965A</b> EAX+ | -40°C to +85°C | 36 SSOP     |

| MAX5965AUAX+*        | 0°C to +85°C   | 36 SSOP     |

| <b>MAX5965B</b> EAX+ | -40°C to +85°C | 36 SSOP     |

| MAX5965BUAX+*        | 0°C to +85°C   | 36 SSOP     |

+は鉛(Pb)フリー/RoHS準拠パッケージを表します。

\*開発中。入手性についてお問い合わせください。

## 選択ガイド

| PART         | PIN-PACKAGE | AC DISCONNECT FEATURE |

|--------------|-------------|-----------------------|

| MAX5965AEAX+ | 36 SSOP     | No                    |

| MAX5965AUAX+ | 36 SSOP     | No                    |

| MAX5965BEAX+ | 36 SSOP     | Yes                   |

| MAX5965BUAX+ | 36 SSOP     | Yes                   |

ピン配置はデータシートの最後に記載されています。

本データシートは日本語翻訳であり、相違及び誤りのある可能性があります。設計の際は英語版データシートを参照してください。

価格、納期、発注情報についてはMaxim Direct (0120-551056)にお問い合わせいただくなさいか、Maximのウェブサイト ([japan.maxim-ic.com](http://japan.maxim-ic.com))をご覧ください。

# Power over Ethernet用、ハイパワー クワッド、モノリシック、PSEコントローラ

## ABSOLUTE MAXIMUM RATINGS

|                                                                                              |                       |

|----------------------------------------------------------------------------------------------|-----------------------|

| (Voltages referenced to V <sub>EE</sub> , unless otherwise noted.)                           |                       |

| SCL, SDAIN, AUTO                                                                             | -0.3V to +80V         |

| OUT                                                                                          | -12V to (AGND + 0.3V) |

| GATE <sub>_</sub> (internally clamped) (Note 1)                                              | -0.3V to +11.4V       |

| SENSE <sub>_</sub>                                                                           | -0.3V to +24V         |

| V <sub>DD</sub> , RESET, MIDSPAN, A3-A0, SHD <sub>_</sub> , OSC, SCL, SDAIN and AUTO to DGND | -0.3V to +7V          |

| INT and SDAOUT to DGND                                                                       | -0.3V to +12V         |

**Note 1:** GATE<sub>\_</sub> is internally clamped to 11.4V above V<sub>EE</sub>. Driving GATE<sub>\_</sub> higher than 11.4V above V<sub>EE</sub> may damage the device.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

(V<sub>AGND</sub> = 32V to 60V, V<sub>EE</sub> = 0V, V<sub>DD</sub> to V<sub>DGND</sub> = +3.3V, all voltages are referenced to V<sub>EE</sub>, unless otherwise noted. Typical values are at V<sub>AGND</sub> = +48V, V<sub>DGND</sub> = +48V, V<sub>DD</sub> = (V<sub>DGND</sub> + 3.3V), T<sub>A</sub> = +25°C. Currents are positive when entering the pin and negative otherwise.) (Note 2)

| PARAMETER                               | SYMBOL            | CONDITIONS                                                                                                                                                                                                                                            | MIN | TYP | MAX  | UNITS |

|-----------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|-------|

| <b>POWER SUPPLIES</b>                   |                   |                                                                                                                                                                                                                                                       |     |     |      |       |

| Operating Voltage Range                 | V <sub>AGND</sub> | V <sub>AGND</sub> - V <sub>EE</sub>                                                                                                                                                                                                                   | 32  | 60  |      | V     |

|                                         | V <sub>DGND</sub> |                                                                                                                                                                                                                                                       | 0   | 60  |      |       |

|                                         | V <sub>DD</sub>   | V <sub>DD</sub> to V <sub>DGND</sub> , V <sub>DGND</sub> = V <sub>AGND</sub>                                                                                                                                                                          | 2.4 | 3.6 |      |       |

|                                         |                   | V <sub>DD</sub> to V <sub>DGND</sub> , V <sub>DGND</sub> = V <sub>EE</sub>                                                                                                                                                                            | 3.0 | 3.6 |      |       |

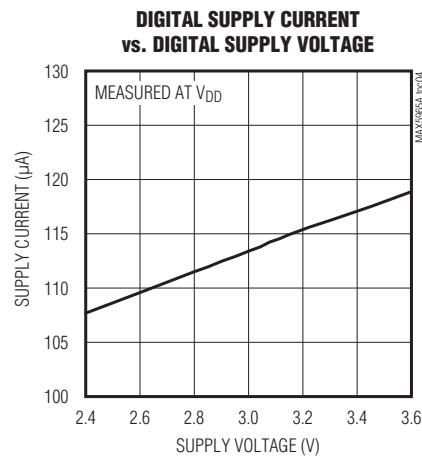

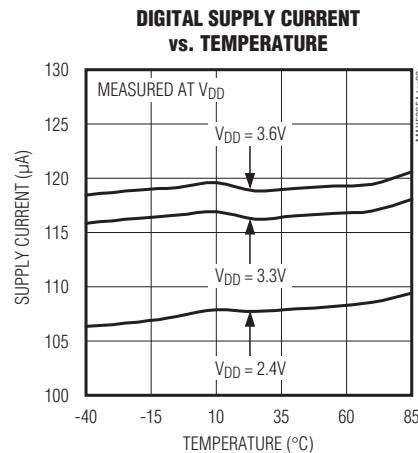

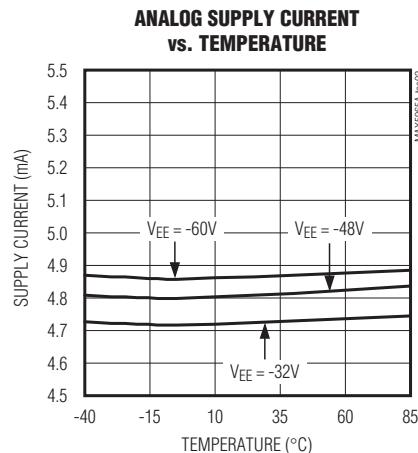

| Supply Currents                         | I <sub>EE</sub>   | V <sub>OUT</sub> = V <sub>EE</sub> , V <sub>SENSE</sub> = V <sub>EE</sub> , DET <sub>_</sub> = AGND, all logic inputs open, SCL = SDAIN = V <sub>DD</sub> . INT and SDAOUT unconnected. Measured at AGND in power mode after GATE <sub>_</sub> pullup |     | 4.8 | 6.8  | mA    |

|                                         | I <sub>DIG</sub>  | All logic inputs high, measured at V <sub>DD</sub>                                                                                                                                                                                                    |     | 0.2 | 0.4  |       |

| <b>GATE DRIVER AND CLAMPING</b>         |                   |                                                                                                                                                                                                                                                       |     |     |      |       |

| GATE <sub>_</sub> Pullup Current        | I <sub>PU</sub>   | Power mode, gate drive on, V <sub>GATE</sub> = V <sub>EE</sub> (Note 3)                                                                                                                                                                               | -40 | -50 | -65  | µA    |

| Weak GATE <sub>_</sub> Pulldown Current | I <sub>PDW</sub>  | SHD <sub>_</sub> = DGND, V <sub>GATE</sub> = V <sub>EE</sub> + 10V                                                                                                                                                                                    |     | 42  |      | µA    |

| Maximum Pulldown Current                | I <sub>PDS</sub>  | V <sub>SENSE</sub> = 600mV, V <sub>GATE</sub> = V <sub>EE</sub> + 2V                                                                                                                                                                                  |     | 100 |      | mA    |

| External Gate Drive                     | V <sub>GS</sub>   | V <sub>GATE</sub> - V <sub>EE</sub> , power mode, gate drive on, I <sub>PU</sub> = 1µA                                                                                                                                                                | 9   | 10  | 11.5 | V     |

# Power over Ethernet用、ハイパワー クワッド、モノリシック、PSEコントローラ

**MAX5965A/MAX5965B**

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{AGND} = 32V$  to  $60V$ ,  $V_{EE} = 0V$ ,  $V_{DD}$  to  $V_{DGND} = +3.3V$ , all voltages are referenced to  $V_{EE}$ , unless otherwise noted. Typical values are at  $V_{AGND} = +48V$ ,  $V_{DGND} = +48V$ ,  $V_{DD} = (V_{DGND} + 3.3V)$ ,  $T_A = +25^\circ C$ . Currents are positive when entering the pin and negative otherwise.) (Note 2)

| PARAMETER                                | SYMBOL                | CONDITIONS                                                                                                                                   | MIN                                      | TYP | MAX | UNITS |

|------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----|-----|-------|

| <b>CURRENT LIMIT</b>                     |                       |                                                                                                                                              |                                          |     |     |       |

| Current-Limit Clamp Voltage              | V <sub>SU_LIM</sub>   | Maximum V <sub>SENSE</sub> _allowed during current limit, V <sub>OUT_</sub> = 0V (ICUT = 000) (Note 4)                                       | I <sub>VEE</sub> = 00                    | 202 | 212 | 220   |

|                                          |                       |                                                                                                                                              | I <sub>VEE</sub> = 01                    | 192 | 202 | 212   |

|                                          |                       |                                                                                                                                              | I <sub>VEE</sub> = 10                    | 186 | 190 | 200   |

|                                          |                       |                                                                                                                                              | I <sub>VEE</sub> = 11                    | 170 | 180 | 190   |

| Overcurrent Threshold After Startup      | V <sub>FLT_LIM</sub>  | Overcurrent V <sub>SENSE</sub> _threshold allowed for $t \leq t_{FAULT}$ after startup; V <sub>OUT_</sub> = 0V (I <sub>VEE</sub> = 00)       | ICUT = 110 (Class 0/3)                   | 177 | 186 | 196   |

|                                          |                       |                                                                                                                                              | ICUT = 110 (Class 1)                     | 47  | 55  | 64    |

|                                          |                       |                                                                                                                                              | ICUT = 111 (Class 2)                     | 86  | 94  | 101   |

|                                          |                       |                                                                                                                                              | ICUT = 001                               | 265 | 280 | 295   |

|                                          |                       |                                                                                                                                              | ICUT = 010                               | 310 | 327 | 345   |

|                                          |                       |                                                                                                                                              | ICUT = 011                               | 355 | 374 | 395   |

|                                          |                       |                                                                                                                                              | ICUT = 100                               | 398 | 419 | 440   |

|                                          |                       |                                                                                                                                              | ICUT = 101                               | 443 | 466 | 488   |

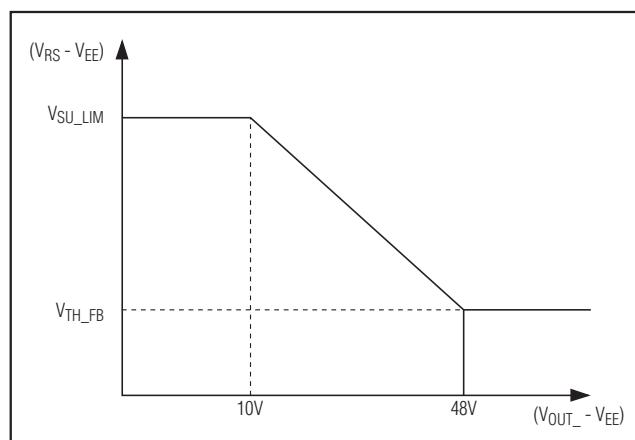

| Foldback Initial OUT_ Voltage            | V <sub>FLBK_ST</sub>  | V <sub>OUT_</sub> - V <sub>EE</sub> , above which the current-limit trip voltage starts folding back, I <sub>VEE</sub> = 00                  | ICUT = 000,<br>ICUT = 110,<br>ICUT = 111 | 32  |     | V     |

|                                          |                       |                                                                                                                                              | ICUT = 001...101                         | 13  |     |       |

| Foldback Final OUT_ Voltage              | V <sub>FLBK_END</sub> | I <sub>VEE</sub> = 00, ICUT = 000, V <sub>OUT_</sub> - V <sub>EE</sub> above which the current-limit trip voltage reaches V <sub>TH_FB</sub> |                                          | 50  |     | V     |

| Minimum Foldback Current-Limit Threshold | V <sub>TH_FB</sub>    | V <sub>OUT_</sub> = AGND = 60V, I <sub>VEE</sub> = 00, ICUT = 000                                                                            |                                          | 64  |     | mV    |

| SENSE_ Input Bias Current                |                       | V <sub>SENSE_</sub> = V <sub>EE</sub>                                                                                                        | -5                                       | +5  |     | µA    |

# Power over Ethernet用、ハイパワー クワッド、モノリシック、PSEコントローラ

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{AGND} = 32V$  to  $60V$ ,  $V_{EE} = 0V$ ,  $V_{DD}$  to  $V_{DGND} = +3.3V$ , all voltages are referenced to  $V_{EE}$ , unless otherwise noted. Typical values are at  $V_{AGND} = +48V$ ,  $V_{DGND} = +48V$ ,  $V_{DD} = (V_{DGND} + 3.3V)$ ,  $T_A = +25^\circ C$ . Currents are positive when entering the pin and negative otherwise.) (Note 2)

| PARAMETER                           | SYMBOL        | CONDITIONS                                                                                                        | MIN  | TYP | MAX | UNITS |

|-------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------|------|-----|-----|-------|

| <b>SUPPLY MONITORS</b>              |               |                                                                                                                   |      |     |     |       |

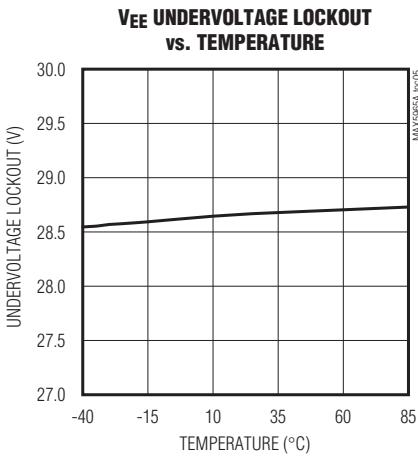

| VEE Undervoltage Lockout            | $V_{EEUVLO}$  | $AGND - V_{EE}$ , $AGND - V_{EE}$ increasing                                                                      | 28.5 |     |     | V     |

| VEE Undervoltage Lockout Hysteresis | $V_{EEUVLOH}$ | Ports shut down if $AGND - V_{EE} < V_{UVLO} - V_{EEUVLOH}$                                                       | 3    |     |     | V     |

| VEE Overvoltage Lockout             | $V_{EE\_OV}$  | $V_{EE\_OV}$ event bit sets and ports shut down if $AGND - V_{EE} > V_{EE\_OV}$ , $AGND$ increasing               | 62.5 |     |     | V     |

| VEE Overvoltage Lockout Hysteresis  | $V_{OVH}$     |                                                                                                                   | 1    |     |     | V     |

| VEE Undervoltage                    | $V_{EE\_UV}$  | $V_{EE\_UV}$ event bit is set if $AGND - V_{EE} < V_{EE\_UV}$ , $V_{EE}$ increasing                               | 40   |     |     | V     |

| VDD Overvoltage                     | $V_{DD\_OV}$  | $V_{DD\_OV}$ event bit is set if $V_{DD} - V_{DGND} > V_{DD\_OV}$ ; $V_{DD}$ increasing                           | 3.82 |     |     | V     |

| VDD Undervoltage                    | $V_{DD\_UV}$  | $V_{DD\_UV}$ is set if $V_{DD} - V_{DGND} < V_{DD\_UV}$ , $V_{DD}$ decreasing                                     | 2.7  |     |     | V     |

| VDD Undervoltage Lockout            | $V_{DDUVLO}$  | Device operates when $V_{DD} - DGND > V_{DDUVLO}$ , $V_{DD}$ increasing                                           | 2    |     |     | V     |

| VDD Undervoltage Lockout Hysteresis | $V_{DDHYS}$   |                                                                                                                   | 120  |     |     | mV    |

| Thermal Shutdown Threshold          | $T_{SHD}$     | Ports shut down and device resets if its junction temperature exceeds this limit, temperature increasing (Note 5) | +150 |     |     | °C    |

| Thermal Shutdown Hysteresis         | $T_{SHDH}$    | Thermal hysteresis, temperature decreasing (Note 5)                                                               | 20   |     |     | °C    |

| <b>OUTPUT MONITOR</b>               |               |                                                                                                                   |      |     |     |       |

| OUT_ Input Current                  | $I_{BOUT}$    | $V_{OUT\_} = AGND$ , all modes                                                                                    | 2    |     |     | µA    |

| Idle Pullup Current at OUT_         | $I_{DIS}$     | OUT_ discharge current, detection and classification off, port shutdown, $V_{OUT\_} = AGND - 2.8V$                | 200  | 265 |     | µA    |

| PGOOD High Threshold                | $PG_{TH}$     | $V_{OUT\_} - V_{EE}$ , OUT_ decreasing                                                                            | 1.5  | 2.0 | 2.5 | V     |

| PGOOD Hysteresis                    | $PG_{HYS}$    |                                                                                                                   | 220  |     |     | mV    |

| PGOOD Low-to-High Glitch Filter     | $t_{PGOOD}$   | Minimum time PGOOD has to be high to set bit in register 10h                                                      | 3    |     |     | ms    |

# Power over Ethernet用、ハイパワー クワッド、モノリシック、PSEコントローラ

MAX5965A/MAX5965B

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{AGND} = 32V$  to  $60V$ ,  $V_{EE} = 0V$ ,  $V_{DD}$  to  $V_{DGND} = +3.3V$ , all voltages are referenced to  $V_{EE}$ , unless otherwise noted. Typical values are at  $V_{AGND} = +48V$ ,  $V_{DGND} = +48V$ ,  $V_{DD} = (V_{DGND} + 3.3V)$ ,  $T_A = +25^\circ C$ . Currents are positive when entering the pin and negative otherwise.) (Note 2)

| PARAMETER                              | SYMBOL          | CONDITIONS                                                                                                               | MIN              | TYP  | MAX  | UNITS |

|----------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------|------------------|------|------|-------|

| <b>LOAD DISCONNECT</b>                 |                 |                                                                                                                          |                  |      |      |       |

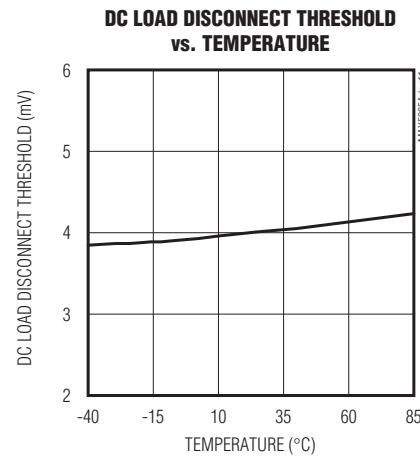

| DC Load Disconnect Threshold           | $V_{DCTH}$      | Minimum $V_{SENSE\_}$ allowed before disconnect (DC disconnect active), $V_{OUT\_} = 0V$                                 | 2.5              | 3.75 | 5.0  | mV    |

| AC Load Disconnect Threshold           | $I_{ACTH}$      | Current into $DET\_$ , for $I < I_{ACTH}$ the port powers off, $ACD\_EN\_$ bit = H; $V_{OSC} = 2.2V$ , MAX5965B (Note 6) | 285              | 320  | 360  | µA    |

| Oscillator Buffer Gain                 | $A_{OSC}$       | $V_{DET\_}/V_{OSC}$ , $ACD\_EN\_$ bit = H, MAX5965B                                                                      | 2.9              | 3.0  | 3.1  | V/V   |

| OSC Fail Threshold                     | $V_{OSC\_FAIL}$ | Port does not power on if $V_{OSC} < V_{OSC\_FAIL}$ and $ACD\_EN\_$ bit is high, MAX5965B (Note 7)                       | 1.8              |      | 2.2  | V     |

| OSC Input Impedance                    | $Z_{OSC}$       | OSC input impedance when all the $ACD\_EN\_$ are active, MAX5965B                                                        | 100              |      |      | kΩ    |

| Load Disconnect Timer                  | $t_{DISC}$      | Time from $V_{SENSE\_} < V_{DCTH}$ to gate shutdown (Note 8)                                                             | 300              |      | 400  | ms    |

| <b>DETECTION</b>                       |                 |                                                                                                                          |                  |      |      |       |

| Detection Probe Voltage (First Phase)  | $V_{DPH1}$      | $AGND - V_{DET\_}$ during the first detection phase                                                                      | 3.8              | 4    | 4.2  | V     |

| Detection Probe Voltage (Second Phase) | $V_{DPH2}$      | $AGND - V_{DET\_}$ during the second detection phase                                                                     | 9.0              | 9.3  | 9.6  | V     |

| Current-Limit Protection               | $I_{DLIM}$      | $V_{DET\_} = AGND$ , during detection, measure current through $DET\_$                                                   | 1.5              | 1.8  | 2.2  | mA    |

| Short-Circuit Threshold                | $V_{DCP}$       | If $AGND - V_{OUT\_} < V_{DCP}$ after the first detection phase a short circuit to AGND is detected                      |                  | 1    |      | V     |

| Open-Circuit Threshold                 | $I_{D\_OPEN}$   | First point measurement current threshold for open condition                                                             |                  | 12.5 |      | µA    |

| Resistor Detection Window              | $R_{DOK}$       | (Note 9)                                                                                                                 | 19.0             |      | 26.5 | kΩ    |

| Resistor Rejection Window              | $R_{DBAD}$      | Detection rejects lower values                                                                                           |                  |      | 15.2 | kΩ    |

|                                        |                 | Detection rejects higher values                                                                                          | 32               |      |      |       |

| <b>CLASSIFICATION</b>                  |                 |                                                                                                                          |                  |      |      |       |

| Classification Probe Voltage           | $V_{CL}$        | $V_{AGND} - V_{DET\_}$ during classification                                                                             | 16               |      | 20   | V     |

| Current-Limit Protection               | $I_{CILIM}$     | $DET\_ = AGND$ , during classification                                                                                   | 68               |      | 80   | mA    |

| Classification Current Thresholds      | $I_{CL}$        | Classification current thresholds between classes                                                                        | Class 0, Class 1 | 5.5  | 6.5  | 7.5   |

|                                        |                 |                                                                                                                          | Class 1, Class 2 | 13   | 14.5 | 16    |

|                                        |                 |                                                                                                                          | Class 2, Class 3 | 21   | 23   | 25    |

|                                        |                 |                                                                                                                          | Class 3, Class 4 | 31   | 33   | 35    |

|                                        |                 |                                                                                                                          | Class 4, Class 5 | 45   | 48   | 51    |

|                                        |                 |                                                                                                                          |                  |      |      | mA    |

# Power over Ethernet用、ハイパワー クワッド、モノリシック、PSEコントローラ

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{AGND} = 32V$  to  $60V$ ,  $V_{EE} = 0V$ ,  $V_{DD}$  to  $V_{DGND} = +3.3V$ , all voltages are referenced to  $V_{EE}$ , unless otherwise noted. Typical values are at  $V_{AGND} = +48V$ ,  $V_{DGND} = +48V$ ,  $V_{DD} = (V_{DGND} + 3.3V)$ ,  $T_A = +25^\circ C$ . Currents are positive when entering the pin and negative otherwise.) (Note 2)

| PARAMETER                                        | SYMBOL        | CONDITIONS                                                                                                           | MIN              | TYP  | MAX         | UNITS      |

|--------------------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------|------------------|------|-------------|------------|

| <b>DIGITAL INPUTS/OUTPUTS (Referred to DGND)</b> |               |                                                                                                                      |                  |      |             |            |

| Digital Input Low                                | $V_{IL}$      |                                                                                                                      |                  | 0.9  |             | V          |

| Digital Input High                               | $V_{IH}$      |                                                                                                                      | 2.4              |      |             | V          |

| Internal Input Pullup/Pulldown Resistor          | $R_{DIN}$     | Pullup (pulldown) resistor to $V_{DD}$ (DGND) to set default level                                                   | 25               | 50   | 75          | k $\Omega$ |

| Open-Drain Output Low Voltage                    | $V_{OL}$      | $I_{SINK} = 15mA$                                                                                                    |                  | 0.4  |             | V          |

| Digital Input Leakage                            | $I_{DL}$      | Input connected to the pull voltage                                                                                  |                  | 2    |             | $\mu A$    |

| Open-Drain Leakage                               | $I_{OL}$      | Open-drain high impedance, $V_{OUT\_} = 3.3V$                                                                        |                  | 2    |             | $\mu A$    |

| <b>TIMING</b>                                    |               |                                                                                                                      |                  |      |             |            |

| Startup Time                                     | $t_{START}$   | Time during which a current limit set by $V_{SU\_LIM}$ is allowed, starts when the $GATE\_$ is turned on (Note 9)    | 50               | 60   | 70          | ms         |

| Fault Time                                       | $t_{FAULT}$   | Maximum allowed time for an overcurrent condition set by $V_{FLT\_LIM}$ after startup (Note 9)                       | 50               | 60   | 70          | ms         |

| Port Turn-Off Time                               | $t_{OFF}$     | Minimum delay between any port turning off, does not apply in case of a reset                                        |                  | 0.5  |             | ms         |

| Detection Reset Time                             |               | Time allowed for the port voltage to reset before detection starts                                                   |                  | 80   | 90          | ms         |

| Detection Time                                   | $t_{DET}$     | Maximum time allowed before detection is completed                                                                   |                  | 330  |             | ms         |

| Midspan Mode Detection Delay                     | $t_{DMID}$    |                                                                                                                      | 2.0              | 2.4  |             | s          |

| Classification Time                              | $t_{CLASS}$   | Time allowed for classification                                                                                      |                  | 19   | 23          | ms         |

| VEEUVLO Turn-On Delay                            | $t_{DLY}$     | Time $V_{AGND}$ must be above the VEEUVLO thresholds before the device operates                                      | 2                | 4    |             | ms         |

| Restart Timer                                    | $t_{RESTART}$ | Time a port has to wait before turning on after an overcurrent fault during normal operation, $RSTR\_EN$ bits = high | $RSTR$ bits = 00 | 16 x | $t_{FAULT}$ | ms         |

|                                                  |               |                                                                                                                      | $RSTR$ bits = 01 | 32 x |             |            |

|                                                  |               |                                                                                                                      | $RSTR$ bits = 10 | 64 x |             |            |

|                                                  |               |                                                                                                                      | $RSTR$ bits = 11 | 0    |             |            |

| Watchdog Clock Period                            | $t_{WD}$      | Rate of decrement of the watchdog timer                                                                              |                  | 164  |             | ms         |

| <b>ADC PERFORMANCE</b>                           |               |                                                                                                                      |                  |      |             |            |

| Resolution                                       |               |                                                                                                                      |                  | 9    |             | Bits       |

| Range                                            |               |                                                                                                                      |                  | 0.51 |             | V          |

| LSB Step Size                                    |               |                                                                                                                      |                  | 1    |             | mV         |

| Integral Nonlinearity (Relative)                 | $INL$         |                                                                                                                      | 0.2              | 1.5  |             | LSB        |

# Power over Ethernet用、ハイパワー クワッド、モノリシック、PSEコントローラ

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{AGND} = 32V$  to  $60V$ ,  $V_{EE} = 0V$ ,  $V_{DD}$  to  $V_{DGND} = +3.3V$ , all voltages are referenced to  $V_{EE}$ , unless otherwise noted. Typical values are at  $V_{AGND} = +48V$ ,  $V_{DGND} = +48V$ ,  $V_{DD} = (V_{DGND} + 3.3V)$ ,  $T_A = +25^\circ C$ . Currents are positive when entering the pin and negative otherwise.) (Note 2)

| PARAMETER                                            | SYMBOL        | CONDITIONS            | MIN            | TYP | MAX | UNITS   |

|------------------------------------------------------|---------------|-----------------------|----------------|-----|-----|---------|

| Differential Nonlinearity                            | DNL           |                       |                | 0.2 | 1.5 | LSB     |

| Gain Error                                           |               |                       |                | 3   |     | %       |

| ADC Absolute Accuracy                                |               | $V_{SENSE\_} = 300mV$ | 295            | 300 | 305 | LSB     |

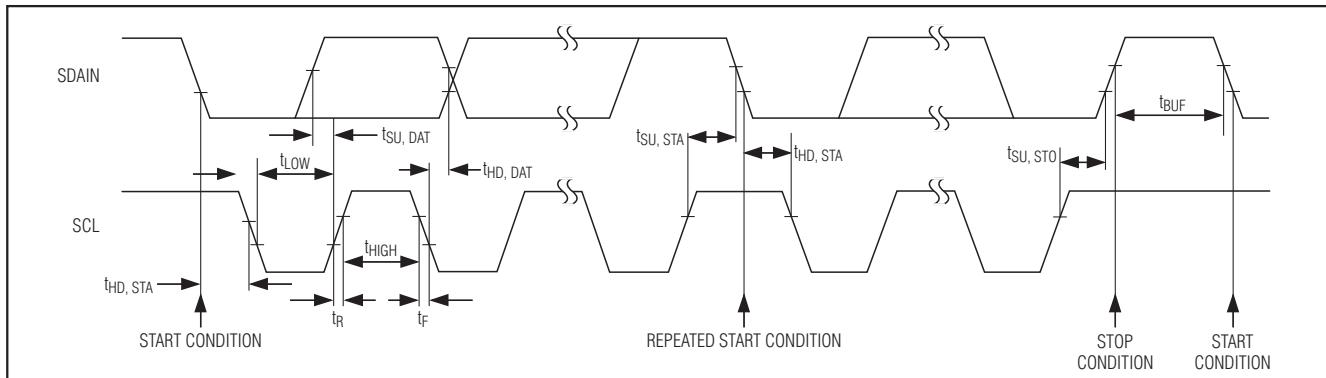

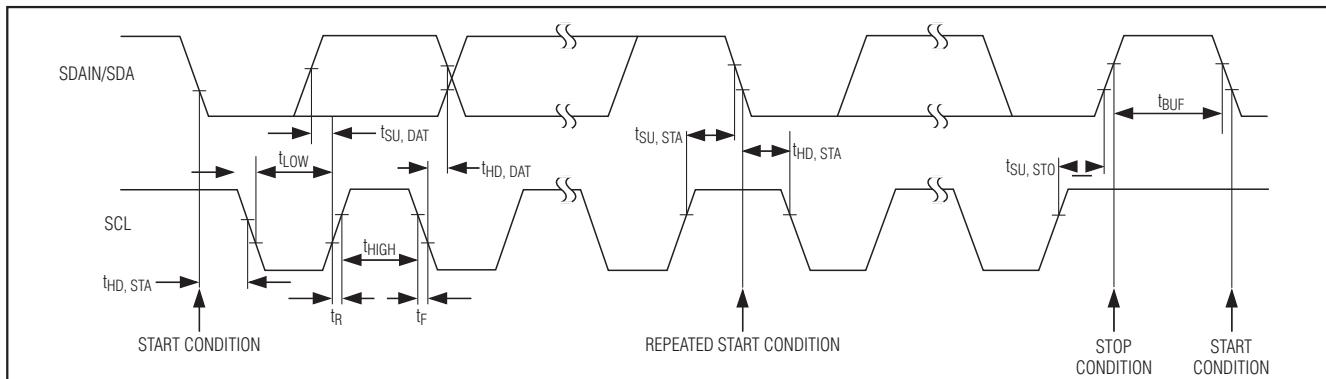

| <b>TIMING CHARACTERISTICS (For 2-Wire Fast Mode)</b> |               |                       |                |     |     |         |

| Serial-Clock Frequency                               | $f_{SCL}$     |                       |                | 400 |     | kHz     |

| Bus Free Time Between a STOP and START Condition     | $t_{BUF}$     |                       | 1.2            |     |     | $\mu s$ |

| Hold Time for a START Condition                      | $t_{HD, STA}$ |                       | 0.6            |     |     | $\mu s$ |

| Low Period of the SCL Clock                          | $t_{LOW}$     |                       | 1.2            |     |     | $\mu s$ |

| High Period of the SCL Clock                         | $t_{HIGH}$    |                       | 0.6            |     |     | $\mu s$ |

| Setup Time for a Repeated START Condition            | $t_{SU, STA}$ |                       | 0.6            |     |     | $\mu s$ |

| Data Hold Time                                       | $t_{HD, DAT}$ |                       | 100            | 300 |     | ns      |

| Data in Setup Time                                   | $t_{SU, DAT}$ |                       | 100            |     |     | ns      |

| Rise Time of Both SDA and SCL Signals, Receiving     | $t_R$         |                       | 20 + 0.1 $C_B$ | 300 |     | ns      |

| Fall Time of SDA Transmitting                        | $t_F$         |                       | 20 + 0.1 $C_B$ | 300 |     | ns      |

| Setup Time for STOP Condition                        | $t_{SU, STO}$ |                       | 0.6            |     |     | $\mu s$ |

| Capacitive Load for Each Bus Line                    | $C_B$         |                       |                | 400 |     | pF      |

| Pulse Width of Spike Suppressed                      | $t_{SP}$      |                       |                | 50  |     | ns      |

**Note 2:** Limits to  $T_A = -40^\circ C$  are guaranteed by design.

**Note 3:** Default values. The charge/discharge currents are programmable through the serial interface (see the *Register Map and Description* section).

**Note 4:** Default values. The current-limit thresholds are programmed through the I<sup>2</sup>C-compatible serial interface (see the *Register Map and Description* section).

**Note 5:** Functional test is performed over thermal shutdown entering test mode.

**Note 6:** This is the default value. Threshold can be programmed through serial interface R23h[2:0].

**Note 7:** AC disconnect works only if  $(V_{DD} - V_{DGND}) \geq 3V$  and DGND is connected to AGND.

**Note 8:**  $t_{DISC}$  can also be programmed through the serial interface (R16h) (see the *Register Map and Description* section).

**Note 9:**  $R_D = (V_{OUT2} - V_{OUT1}) / (I_{DET2} - I_{DET1})$ .  $V_{OUT1}$ ,  $V_{OUT2}$ ,  $I_{DET2}$ , and  $I_{DET1}$  represent the voltage at OUT<sub>\_</sub> and the current at DET<sub>\_</sub> during phase 1 and 2 of the detection.

**Note 10:** Default values. The startup and fault times can also be programmed through the I<sup>2</sup>C serial interface (see the *Register Map and Description* section).

# Power over Ethernet用、ハイパワー クワッド、モノリシック、PSEコントローラ

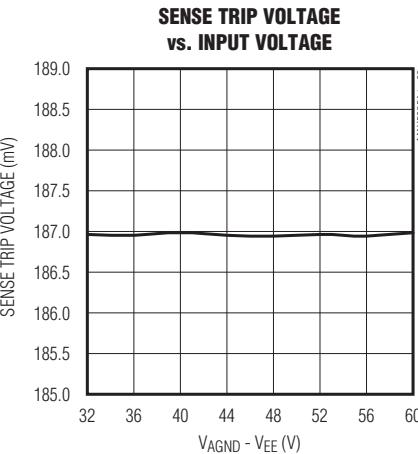

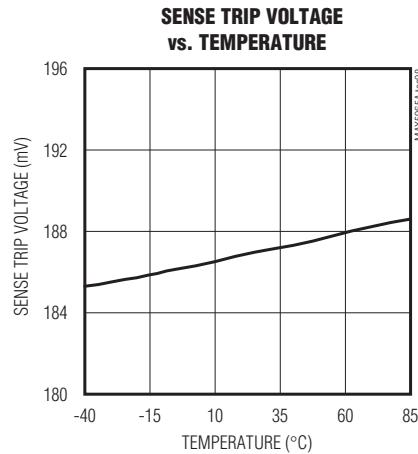

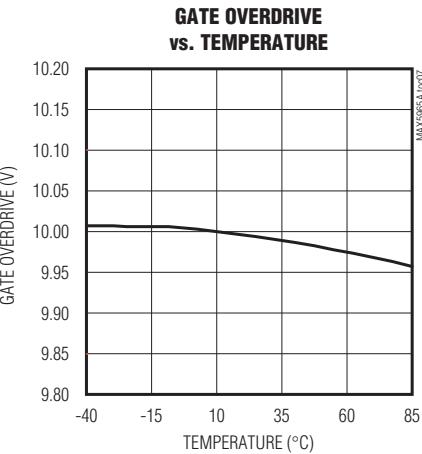

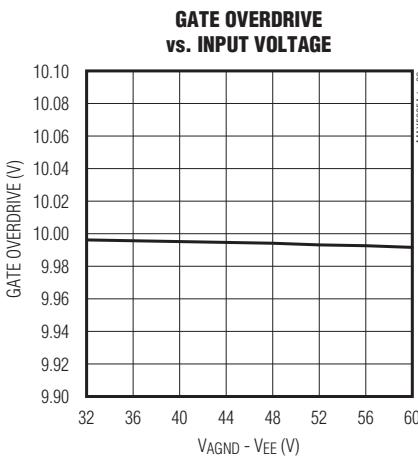

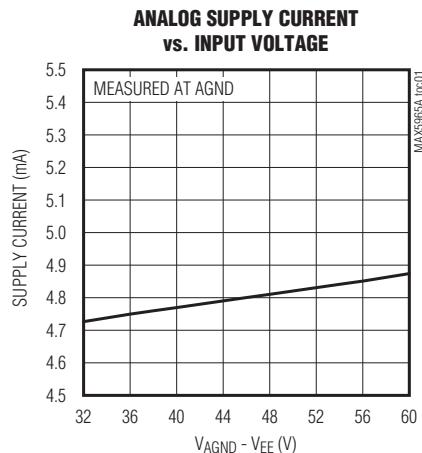

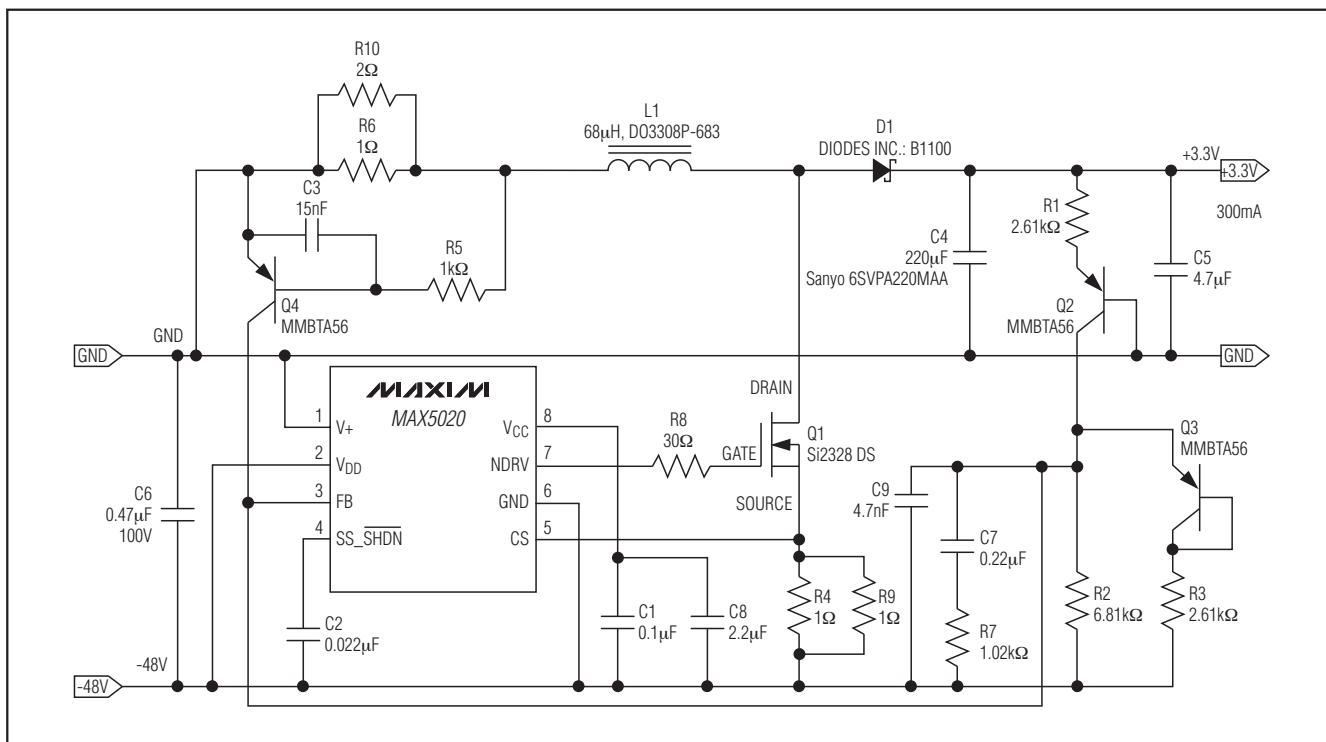

## 標準動作特性

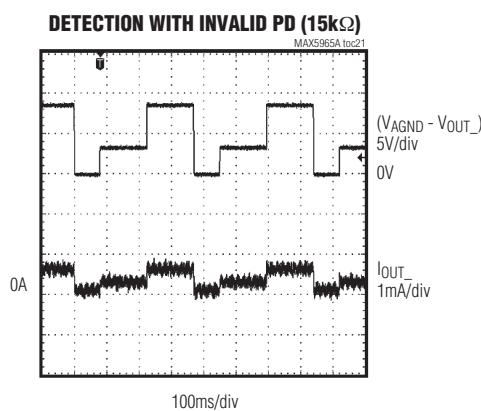

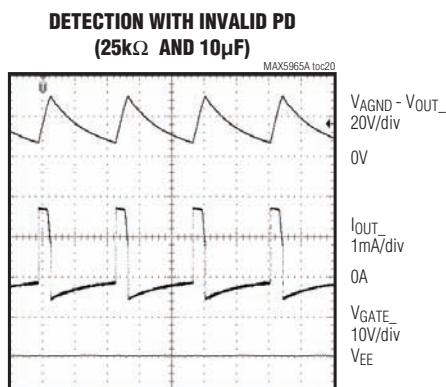

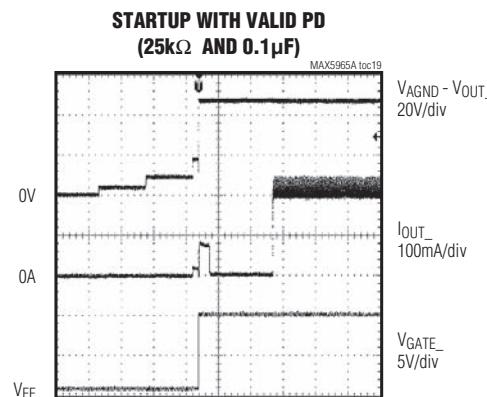

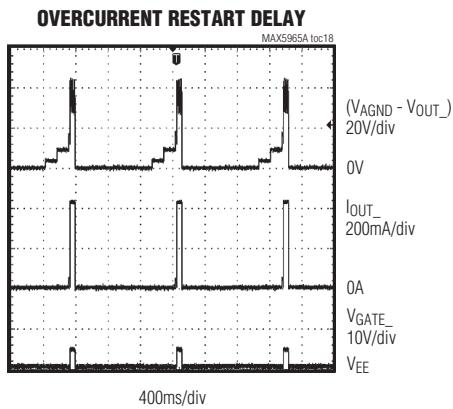

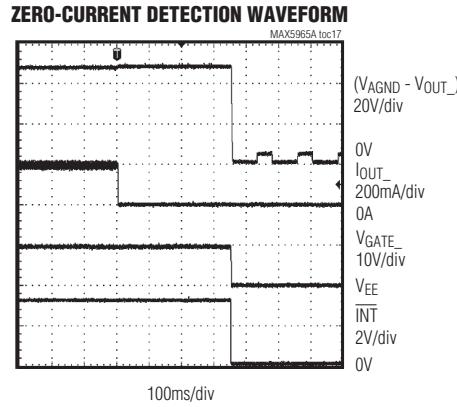

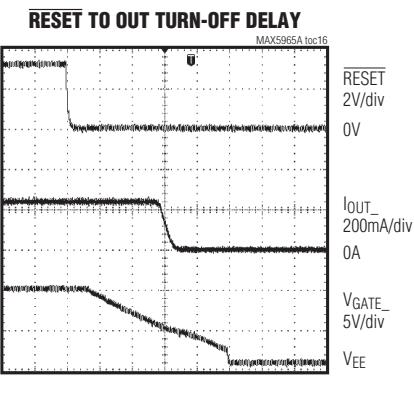

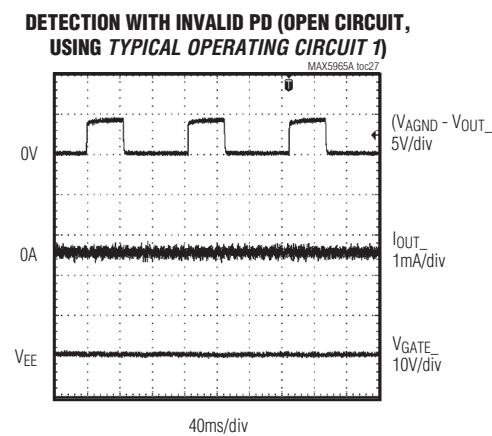

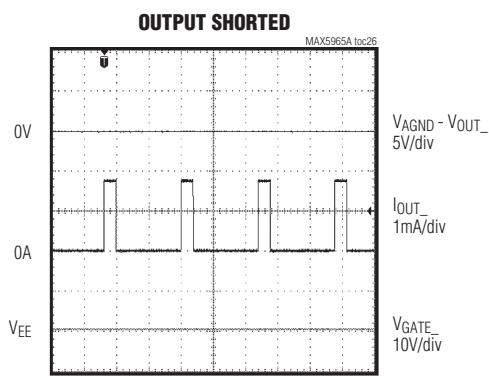

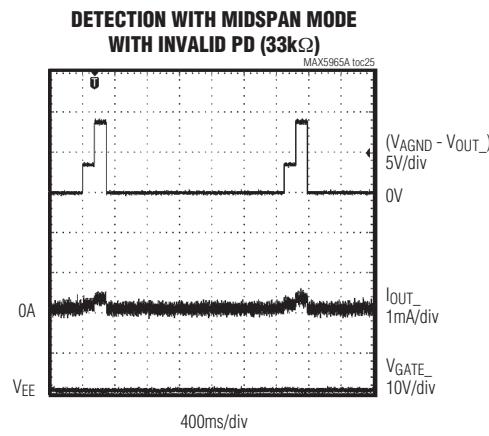

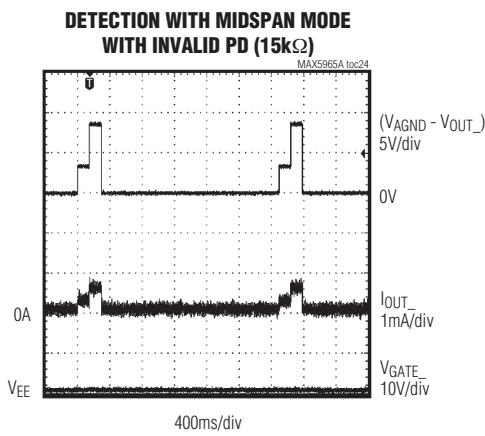

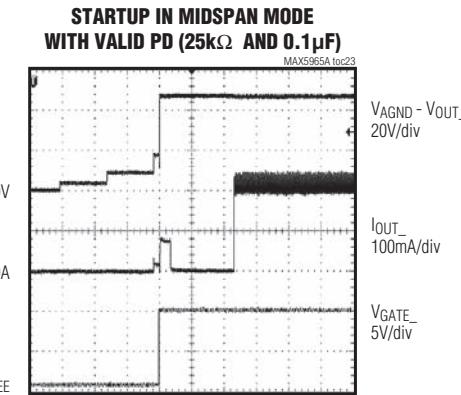

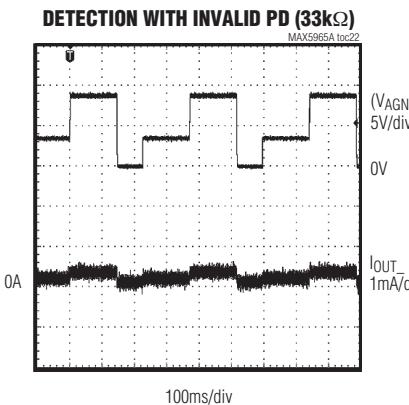

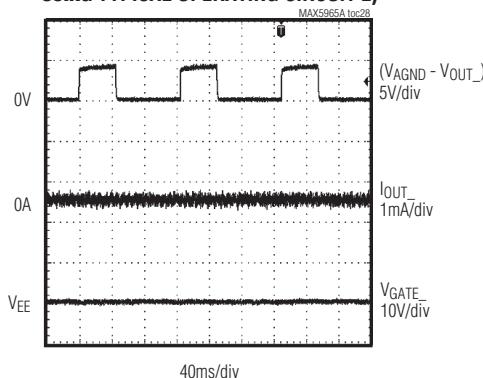

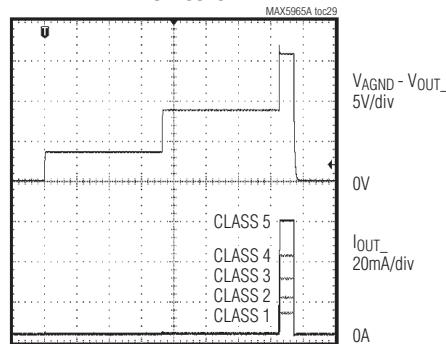

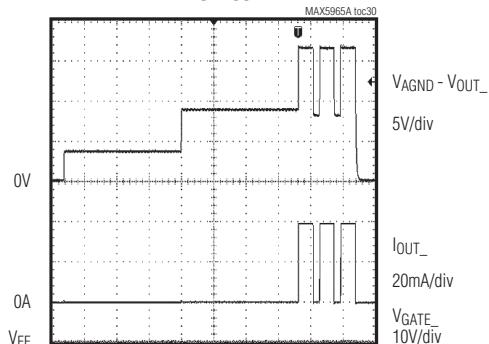

( $V_{EE} = -48V$ ,  $V_{DD} = +3.3V$ ,  $V_{AUTO} = V_{AGND} = V_{DGND} = 0V$ ,  $\overline{RESET} = \overline{SHD}_- = \text{unconnected}$ ,  $R_{SENSE\_} = 0.5\Omega$ ,  $I_{VEE} = 00$ ,  $ICUT = 000$ ,  $T_A = +25^\circ C$ , all registers = default setting, unless otherwise noted.)

# Power over Ethernet用、ハイパワー クワッド、モノリシック、PSEコントローラ

**MAX5965A/MAX5965B**

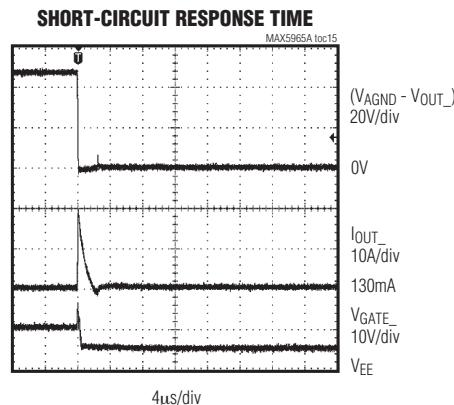

## 標準動作特性(続き)

( $V_{EE} = -48V$ ,  $V_{DD} = +3.3V$ ,  $V_{AUTO} = V_{AGND} = V_{DGND} = 0V$ ,  $\overline{RESET} = \overline{SHD}_- = \text{unconnected}$ ,  $R_{SENSE\_} = 0.5\Omega$ ,  $I_{VEE} = 00$ ,  $ICUT = 000$ ,  $T_A = +25^\circ C$ , all registers = default setting, unless otherwise noted.)

# Power over Ethernet用、ハイパワー クワッド、モノリシック、PSEコントローラ

**MAX5965A/MAX5965B**

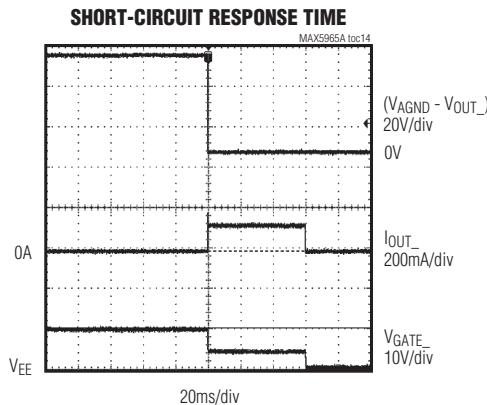

## 標準動作特性(続き)

( $V_{EE} = -48V$ ,  $V_{DD} = +3.3V$ ,  $V_{AUTO} = V_{AGND} = V_{DGND} = 0V$ ,  $\overline{RESET} = \overline{SHD}_- = \text{unconnected}$ ,  $R_{SENSE\_} = 0.5\Omega$ ,  $I_{VEE} = 00$ ,  $ICUT = 000$ ,  $T_A = +25^\circ C$ , all registers = default setting, unless otherwise noted.)

# Power over Ethernet用、ハイパワー クワッド、モノリシック、PSEコントローラ

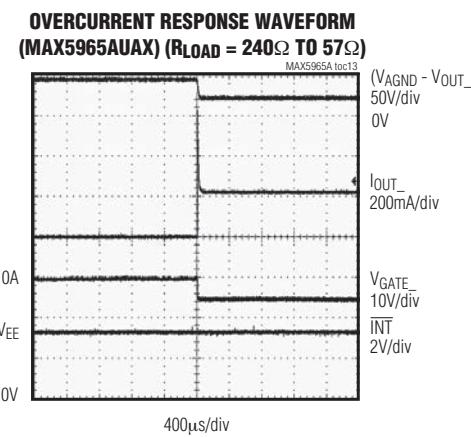

## 標準動作特性(続き)

( $V_{EE} = -48V$ ,  $V_{DD} = +3.3V$ ,  $V_{AUTO} = V_{AGND} = V_{DGND} = 0V$ ,  $\overline{RESET} = \overline{SHD}_- = \text{unconnected}$ ,  $R_{SENSE\_} = 0.5\Omega$ ,  $I_{VEE} = 00$ ,  $ICUT = 000$ ,  $T_A = +25^\circ C$ , all registers = default setting, unless otherwise noted.)

# Power over Ethernet用、ハイパワー クワッド、モノリシック、PSEコントローラ

## 標準動作特性(続き)

( $V_{EE} = -48V$ ,  $V_{DD} = +3.3V$ ,  $V_{AUTO} = V_{AGND} = V_{DGND} = 0V$ ,  $\overline{RESET} = \overline{SHD}_- = \text{unconnected}$ ,  $R_{SENSE\_} = 0.5\Omega$ ,  $I_{VEE} = 00$ ,  $ICUT = 000$ ,  $T_A = +25^\circ C$ , all registers = default setting, unless otherwise noted.)

**DETECTION WITH INVALID PD (OPEN CIRCUIT,

USING TYPICAL OPERATING CIRCUIT 2)**

**STARTUP WITH DIFFERENT

PD CLASSES**

**2-EVENT CLASSIFICATION

WITH A CLASS 4 PD**

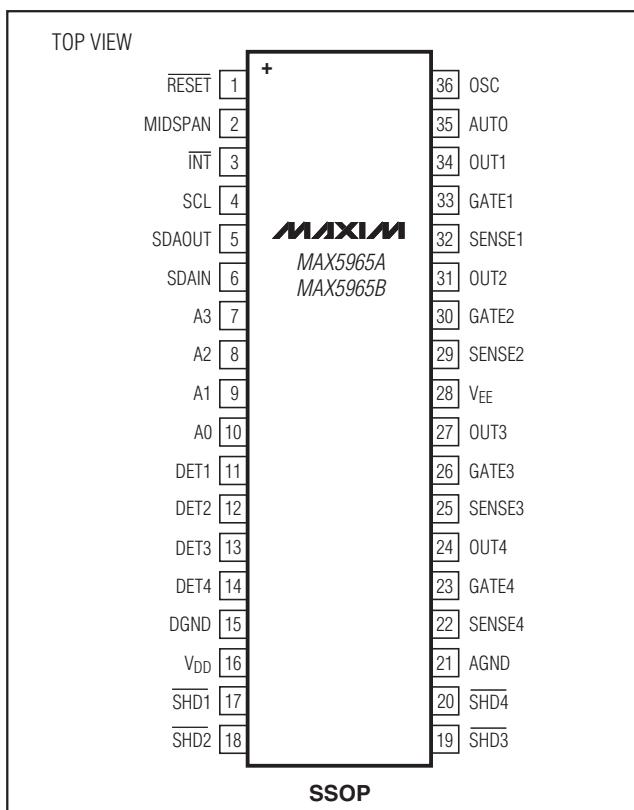

## 端子説明

| 端子 | 名称      | 機能                                                                                                                                                                                                         |

|----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | RESET   | ハードウェアリセット。デバイスをリセットするには、RESETを少なくとも300μsの間ローにプルダウンしてください。すべての内部レジスタがデフォルト値にリセットされます。アドレス(A0~A3)、AUTOおよびMIDSPANの入力ロジックレベルは、RESETのローからハイの遷移時にラッチされます。RESETは、50kΩの抵抗によって内部でV <sub>DD</sub> にプルアップされています。     |

| 2  | MIDSPAN | ミッドスパンモード入力。DGNDとの間に接続された内部50kΩプルダウン抵抗によって、デフォルトモードはエンドポイントのPSE動作(信号ペアによる電源供給)に設定されます。ミッドスパン動作を設定するためには、MIDSPANをV <sub>DIG</sub> にプルアップしてください。デバイスがパワーアップまたはリセットされると、MIDSPANの値はラッチされます([PD検出]の項を参照してください)。 |

| 3  | INT     | オープンドレイン割込み出力。INTは、障害状態が存在すると必ずローになります。ソフトウェアを使用するか、あるいはRESETをローにプルダウンすることによって、障害状態がリセットされます(割込み管理の詳細については、「割込み」の項を参照してください)。                                                                              |

| 4  | SCL     | シリアルインターフェースのクロックライン入力                                                                                                                                                                                     |

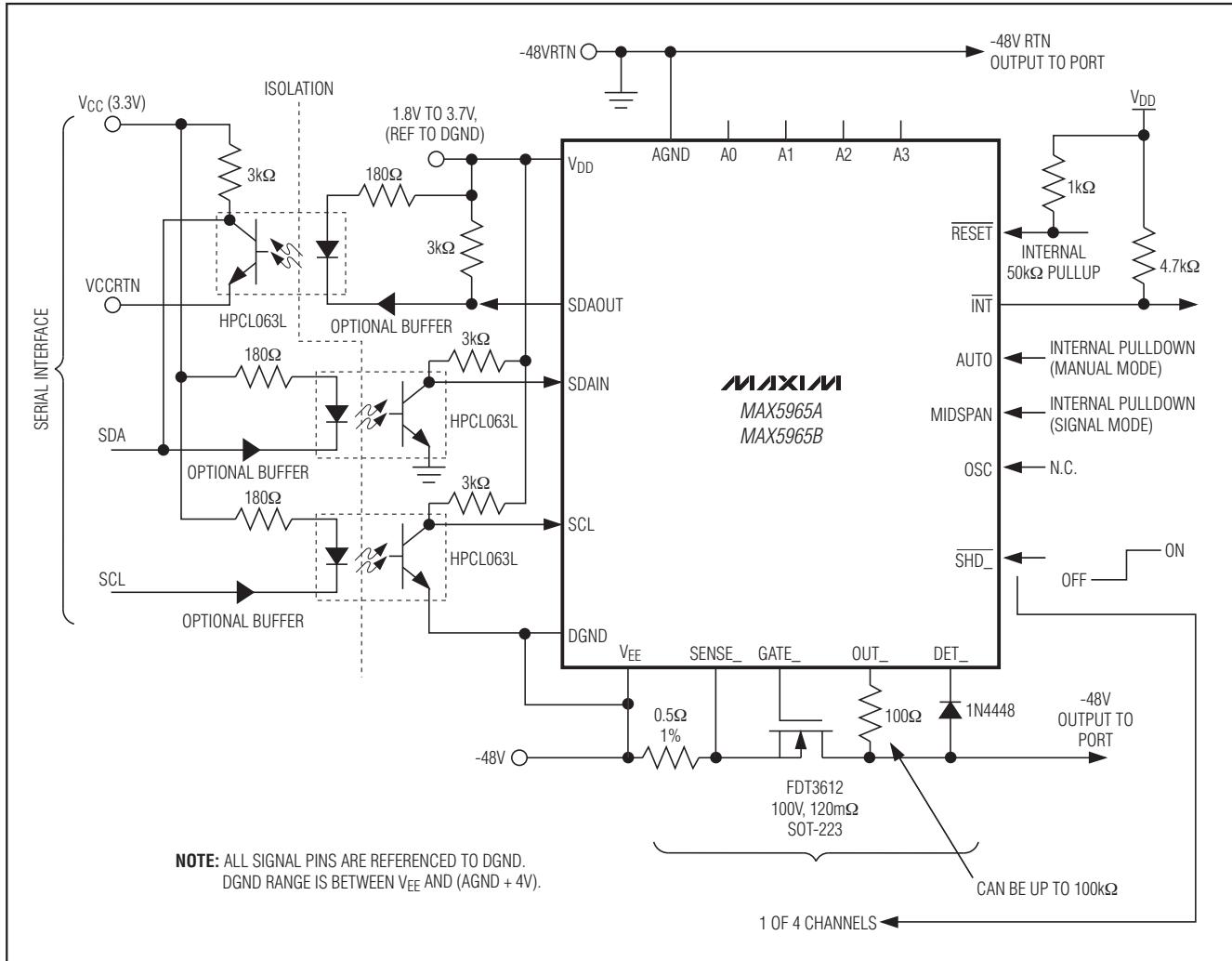

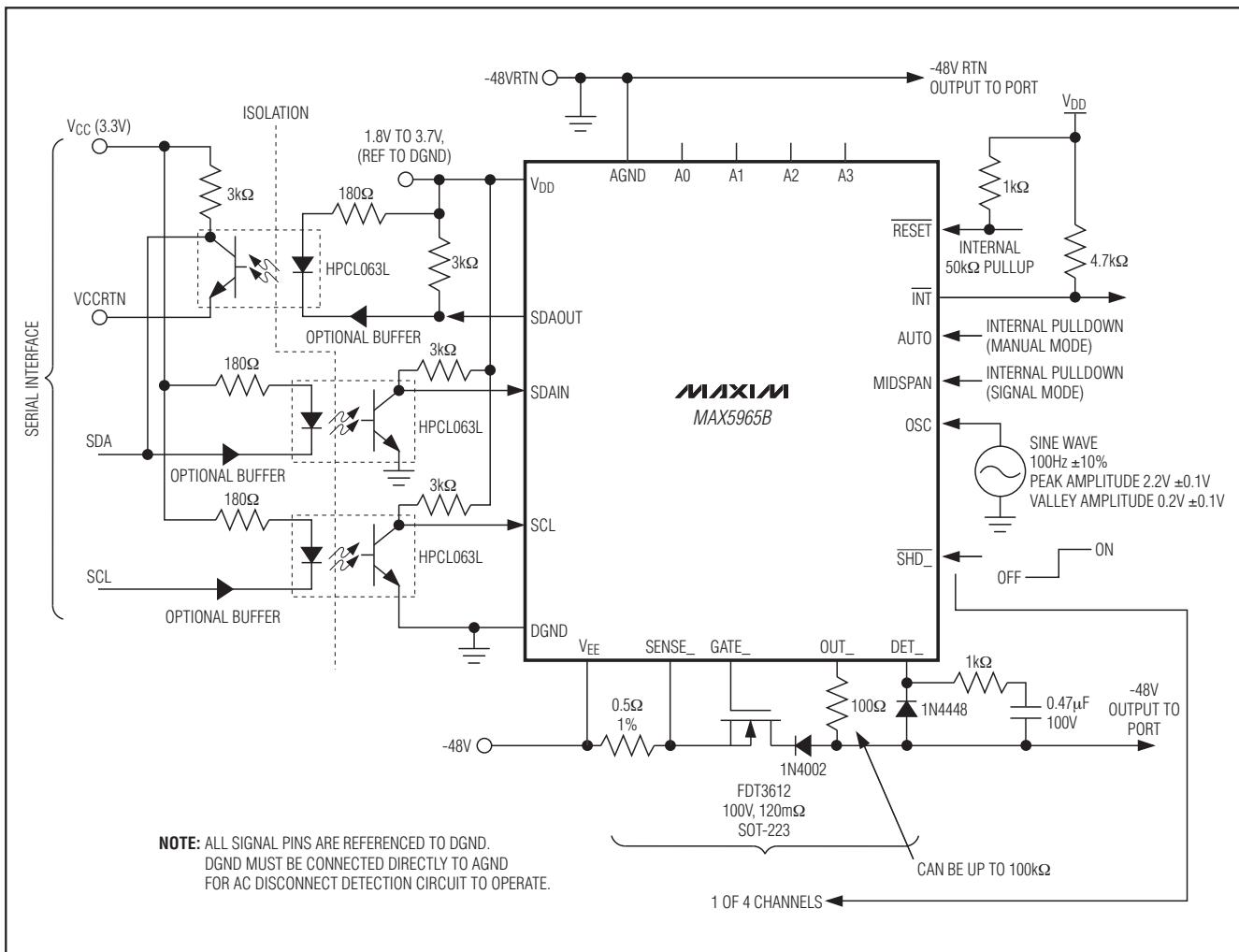

| 5  | SDAOUT  | シリアル出力データライン。データラインのフォトカプラ入力をSDAOUTに接続してください(「標準動作回路」を参照してください)。2線式のI <sup>2</sup> C対応システムを使用する場合は、SDAOUTをSDAINに接続してください。                                                                                  |

# Power over Ethernet用、ハイパワー クワッド、モノリシック、PSEコントローラ

MAX5965A/MAX5965B

## 端子説明(続き)

| 端子                | 名称                                      | 機能                                                                                                                                                                                                                                                                                                                                                              |

|-------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

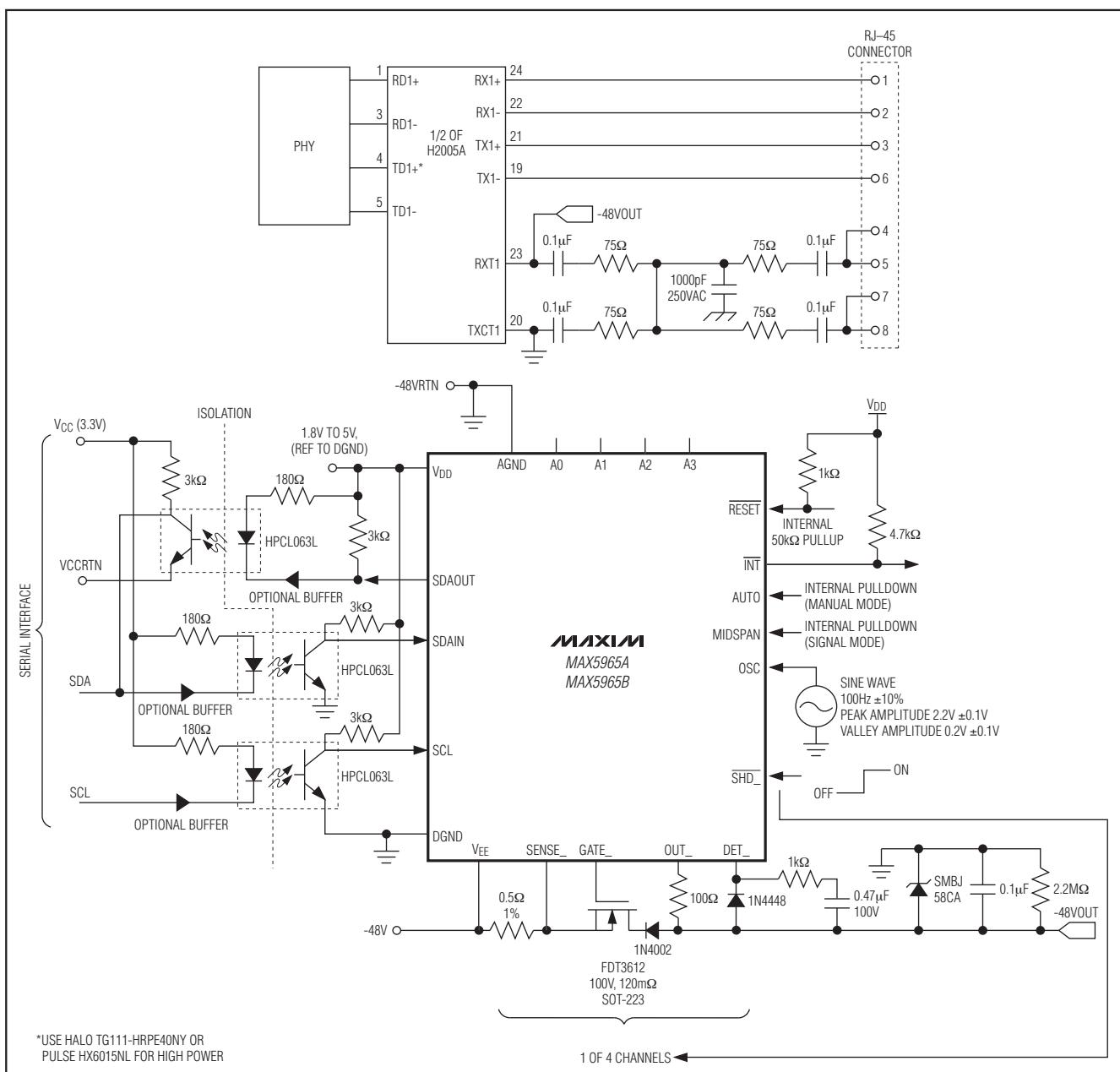

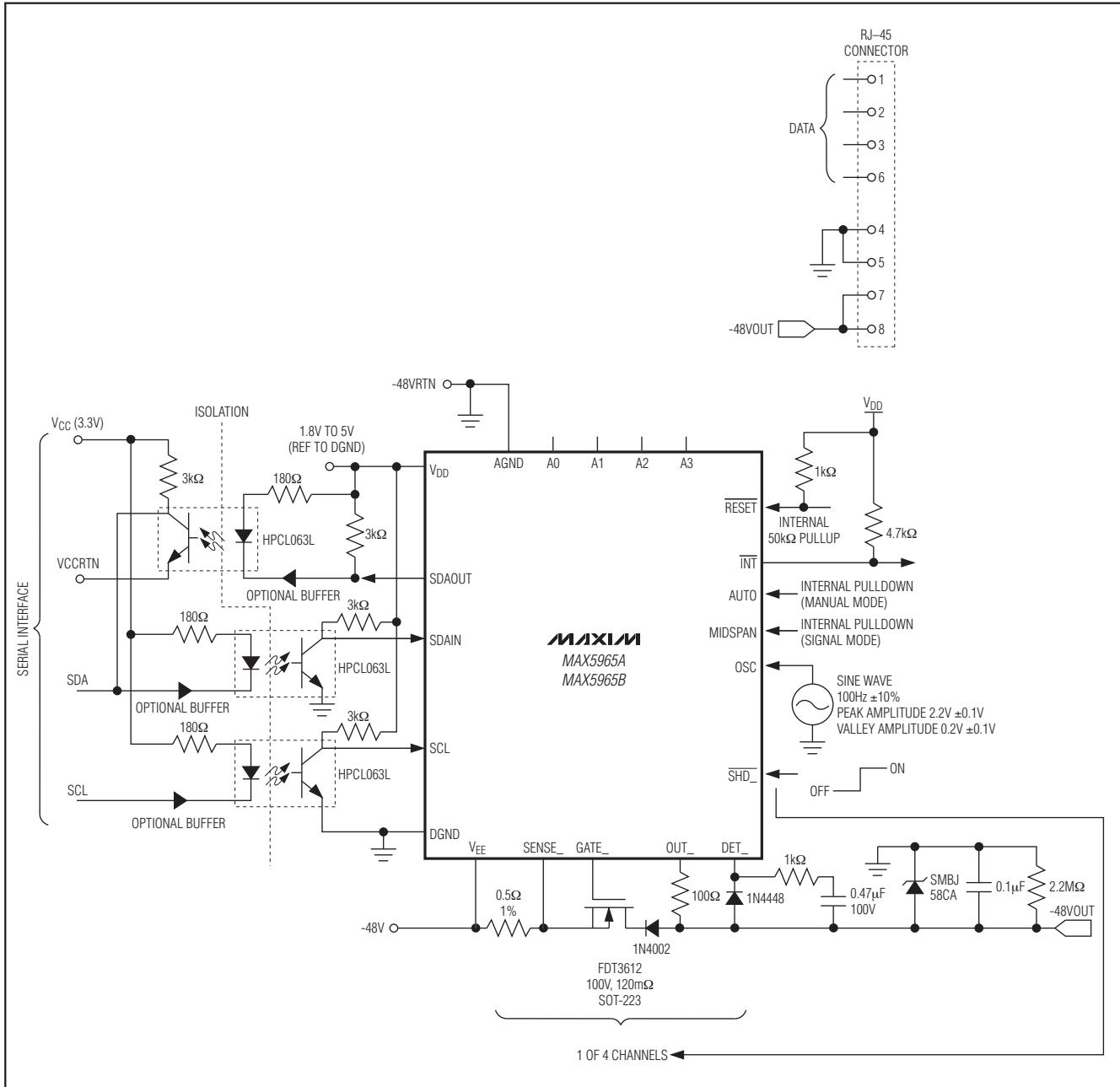

| 6                 | SDAIN                                   | シリアルインターフェースの入力データライン。データラインのフォトカプラ出力をSDAINに接続してください(「標準動作回路」を参照してください)。2線式のI <sup>2</sup> C対応システムを使用する場合は、SDAINをSDAOUTに接続してください。                                                                                                                                                                                                                               |

| 7-10              | A3-A0                                   | アドレスビット。A3~A0は、デバイスのアドレスの下部を構成します。アドレス入力は、内蔵の50kΩプルアップ抵抗でV <sub>DD</sub> (ハイ)にデフォルト設定されます。V <sub>DD</sub> またはV <sub>EE</sub> が立ち上り、そのUVLOスレッショルドを超えるか、またはリセットされると、アドレス値がラッチされます。アドレスのMSBの3個は、010に設定されます。                                                                                                                                                        |

| 11-14             | DET1-DET4                               | 検出/分類電圧出力。ポート1の検出および分類プローブ電圧を設定するためには、DET1を使用してください。AC切断方式を使用するときは、ポート1のAC電圧検出用にDET1を使用してください(「標準動作回路」を参照してください)。                                                                                                                                                                                                                                               |

| 15                | DGND                                    | デジタルグランド。デジタルグランドに接続してください。                                                                                                                                                                                                                                                                                                                                     |

| 16                | V <sub>DD</sub>                         | 正デジタル電源。デジタル電源(DGND基準)に接続してください。                                                                                                                                                                                                                                                                                                                                |

| 17-20             | SHD1-SHD4                               | ポートシャットダウン入力。port_の外付けFETをオフにするためには、SHD_をローにプルダウンしてください。50kΩ抵抗によって内部でV <sub>DD</sub> にプルアップされています。                                                                                                                                                                                                                                                              |

| 21                | AGND                                    | アナロググランド。ハイサイドアナログ電源に接続してください。                                                                                                                                                                                                                                                                                                                                  |

| 22, 25,<br>29, 32 | SENSE4,<br>SENSE3,<br>SENSE2,<br>SENSE1 | MOSFETソース電流検出負入力。パワーMOSFETのソースに接続し、SENSE_-とV <sub>EE</sub> の間に電流検出抵抗を接続してください(「標準動作回路」を参照してください)。                                                                                                                                                                                                                                                               |

| 23, 26,<br>30, 33 | GATE4,<br>GATE3,<br>GATE2,<br>GATE1     | port_のMOSFETゲートドライバ。GATE_を外付けMOSFETのゲートに接続してください(「標準動作回路」を参照してください)。                                                                                                                                                                                                                                                                                            |

| 24, 27,<br>31, 34 | OUT4, OUT3,<br>OUT2, OUT1               | MOSFETドレン出力電圧検出。OUT_-を、抵抗(100Ω~100kΩ)を介してパワーMOSFETのドレンに接続してください。OUT_-が低リーグであるため、抵抗両端間の電圧が100mV以下に制限されます(「標準動作回路」を参照してください)。                                                                                                                                                                                                                                     |

| 28                | V <sub>EE</sub>                         | ローサイドアナログ電源入力。ローサイドアナログ電源をV <sub>EE</sub> (-48V)に接続してください。AGNDとV <sub>EE</sub> を1μFのコンデンサでバイパスしてください。                                                                                                                                                                                                                                                           |

| 35                | AUTO                                    | 自動またはシャットダウンモード入力。リセットまたはパワーアップの後に自動モードに入るためには、AUTOをハイに強制してください。MAX5965A/MAX5965Bをシャットダウンモードにするためには、ローに駆動してください。シャットダウンモードでは、ソフトウェアがMAX5965A/MAX5965Bの動作モードを制御します。内蔵の50kΩプルダウン抵抗は、AUTOをローにデフォルト設定します。V <sub>DD</sub> またはV <sub>EE</sub> が立ち上り、そのUVLOスレッショルドを超えるか、またはデバイスがリセットされるとAUTOはラッチされます。ソフトウェアコマンドによって、AUTOがハイであってもMAX5965A/MAX5965BをAUTOから抜け出させることができます。 |

| 36                | OSC                                     | 発振器入力。AC切断検出機能ではOSCが使用されます。100Hz ±10%、2V <sub>p-p</sub> ±5%、+1.3Vのオフセットの正弦波をOSCに接続してください。発振器の正のピークが2VのOSC_FAILスレッショルド以下になると、AC機能がイネーブルされたポートがシャットダウンしてパワーアップすることができなくなります。AC切断検出機能を使用しないときは、OSCを無接続のままにしてください。                                                                                                                                                  |

# Power over Ethernet用、ハイパワー クワッド、モノリシック、PSEコントローラ

**MAX5965A/MAX5965B**

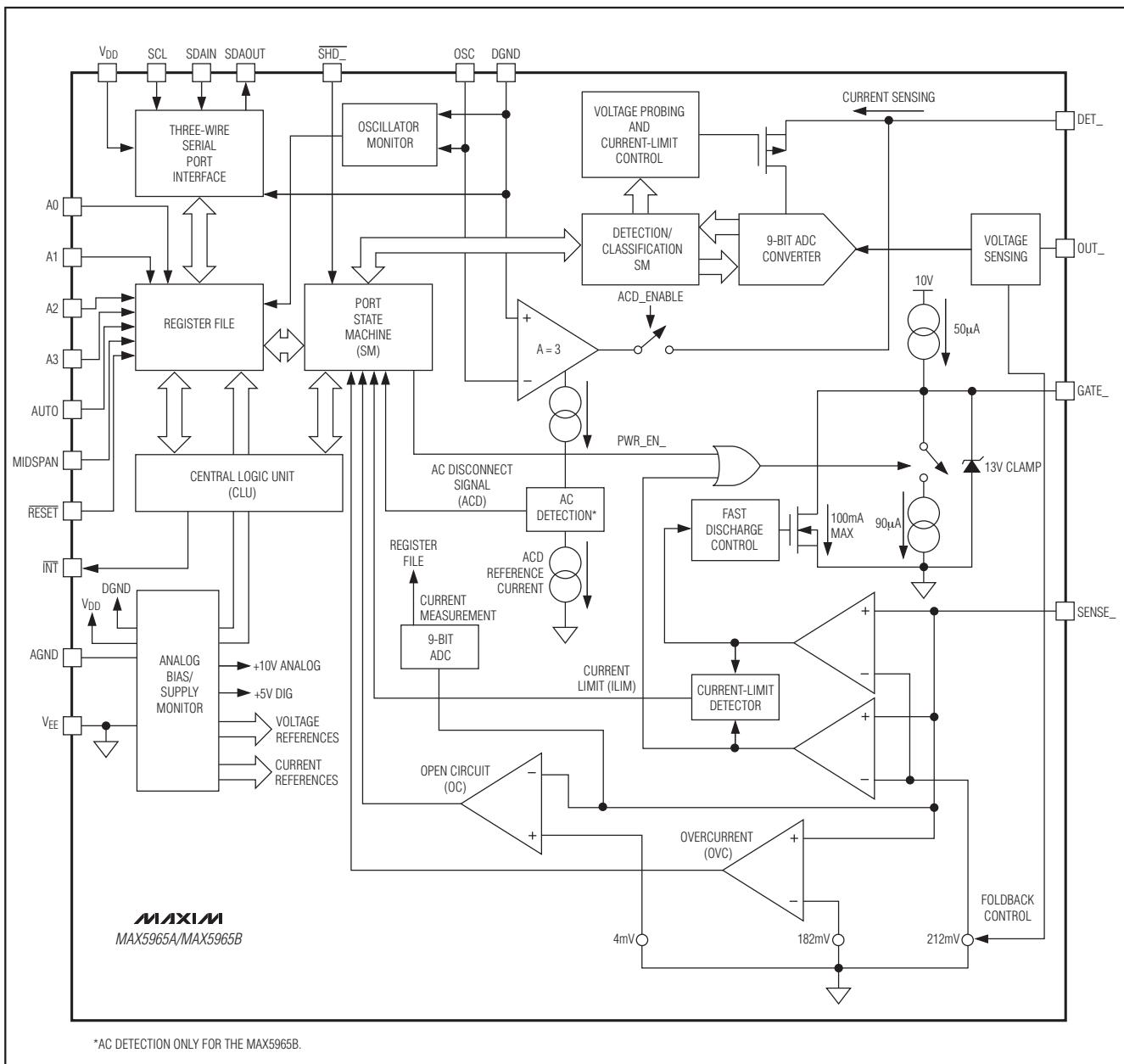

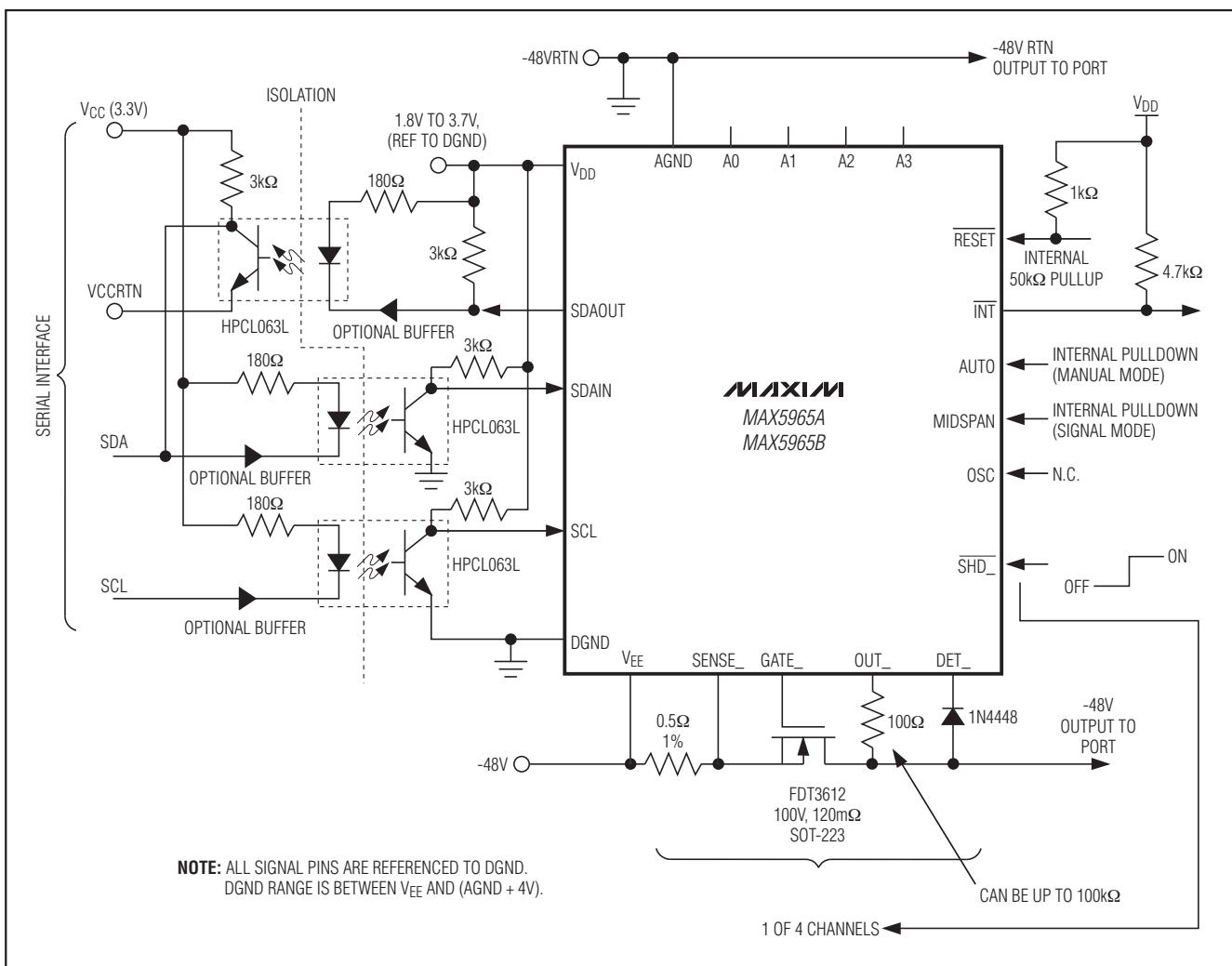

## ファンクションダイアグラム

# Power over Ethernet用、ハイパワークワッド、モノリシック、PSEコントローラ

MAX5965A/MAX5965B

## 詳細

MAX5965A/MAX5965Bは、-48Vのクワッドパワー コントローラであり、IEEE 802.3afに準拠し策定中の IEEE 802.3atに対応したPSEで使用するために設計されています。これらのデバイスは、IEEE 802.3af 規格に準拠したPDの検出、分類、電流制限、DCおよび ACの負荷切断検出を行います。MAX5965A/MAX5965B は、MAX5952/MAX5945/LTC4258/LTC4259Aの PSEコントローラとピンコンパチブルで、機能が追加されています。

MAX5965A/MAX5965Bは、ポート当たり最大45Wを供給するハイパワーモードを備えています。このデバイスでは、ユーザはデフォルトスレッショルドの最大2.5倍の電流制限および過電流スレッショルドをプログラムすることができます。また、高い動作電圧状態で出力電力を一定に保つために、MAX5965A/MAX5965Bの電流制限および過電流スレッショルドを15%だけ低くプログラムすることもできます。

MAX5965A/MAX5965Bは、ハイパワーPDの検出と分類のための新しいクラス5と2イベント分類(クラス6)を設けています。MAX5965A/MAX5965Bは、I<sup>2</sup>C インタフェースを通じて各ポートの電流を瞬時に読み出します。また、MAX5965A/MAX5965Bには、レガシーパートのための大容量検出も用意されています。

MAX5965A/MAX5965Bは49個のレジスタを備え、I<sup>2</sup>C 対応の3線式シリアルインターフェースを通じて、ソフトウェアによる完全な設定とプログラムが可能です。クラス過電流検出機能によって、PDに許容電流を上回る電流が流れるかどうかをシステム電源管理で検出することができます。MAX5965A/MAX5965Bの広範なプログラム能力は、システムの柔軟性を高め、フィールド診断および他のアプリケーションへの応用を可能にします。

MAX5965A/MAX5965Bは、さまざまなシステム要件を満たした4つの動作モードを備えています。自動モードでは、デバイスはソフトウェアによる監視なしで自動的に動作します。半自動モードでは、最初のソフトウェア起動後にポートに接続されたデバイスの検出と分類が自動的に行われますが、ソフトウェアによる指示があるまでそのポートの電源はオンにされません。マニュアルモードでは、ソフトウェアによってデバイスを完全に制御することが可能で、システム診断に有用です。シャットダウンモードでは、すべてのアクティビティを終了してポートへの電源を確実にオフにします。

MAX5965A/MAX5965Bは、入力低電圧ロックアウト、入力低電圧検出、検出中の負荷安定性セーフティチェック、入力過電圧ロックアウト、温度過昇検出、起動中の出力電圧スルーレート制限、パワーグッド、および障害ステータスを提供します。MAX5965A/MAX5965Bのプログラム機能には、起動タイムアウト、過電流タイムアウト、および負荷切断検出タイムアウトが含まれます。

MAX5965A/MAX5965Bは、I<sup>2</sup>C対応インターフェースを通じてシステムのマイクロコントローラと通信します。MAX5965A/MAX5965Bは、フォトカプラー絶縁用の独立した入力および出力データライン(SDAINとSDAOUT)を備えています。スレーブデバイスとして、MAX5965A/MAX5965Bは、16の固有アドレスを指定可能な4つのアドレス入力を備えています。1つの独立したTNT出力と4つの個別シャットダウン入力(SHD\_)によって、MAX5965A/MAX5965Bとマイクロコントローラの間で障害発生からポートシャットダウンまでが高速応答になります。RESET入力によって、デバイスのハードウェアリセットを行うことができます。

## リセット

MAX5965A/MAX5965Bは、以下の条件のいずれかの後にリセット状態になります。

- 1) パワーアップ( $V_{EE}$ および $V_{DD}$ が、それぞれUVLOスレッショルドを超えて上昇)後。

- 2) ハードウェアリセット。パワーアップ後の任意の時点でRESET入力をローに駆動し、その後で再びハイに戻す。

- 3) ソフトウェアリセット。パワーアップ後の任意の時点で1をR1Ah[4]に書き込む。

- 4) サーマルシャットダウン

リセット時、MAX5965A/MAX5965Bは、表37に示すようにレジスタマップをリセット状態にリセットし、AUTO (ピン35)およびMIDSPAN (ピン2)の状態をラッチ入力します。通常の動作時には、AUTOおよびMIDSPAN 入力の変化は無視されます。リセットの原因となる状態(すなわち、高温、RESET入力ロー、またはUVLO状態)が持続する限り、MAX5965A/MAX5965Bはシリアルインターフェースからのアドレス指定に確認応答しません。

## ポートリセット(R1Ah[3:0])

通常動作中に隨時ハイに設定すると、電源をオフにし、対応するポートのEventsおよびStatusレジスタがクリアされます。ポートリセットは、EventsおよびStatusレジスタのみをリセットします。

## ミッドスパンモード

ミッドスパンモードでは、このデバイスは検出段階で Cadenceタイミングを採用します。Cadenceタイミングがイネーブルされていて検出が行われないとき、ポートは2~2.4秒待機した後に再び検出を試みます。ミッドスパンモードは、R11h[1]をハイに設定するとアクティブになります。MIDSPANピンの状態は、起動中またはリセット後にR11h[1]に書き込まれます。MIDSPANは50kΩの抵抗によって内部でローにプルダウンされています。

# Power over Ethernet用、ハイパワー クワッド、モノリシック、PSEコントローラ

## 動作モード

MAX5965A/MAX5965Bは、4つのネットワークポートをリアルタイムで確実に制御するために独立した同一のステートマシンを4つ内蔵しています。各ステートマシンは、自動、半自動、マニュアル、およびシャットダウンの4つの動作モードを備えています。自動モードでは、デバイスがソフトウェアによる監視なしで自動的に動作します。半自動モードは、要求に応じてポートに接続されたデバイスの検出と分類を連続的に行いますが、ソフトウェアの指示があるまでそのポートはパワーアップされません。マニュアルモードは、ソフトウェアによってデバイスを完全に制御することが可能で、システム診断に有用です。シャットダウンモードは、すべてのアクティビティを終了してポートへの電源を確実にオフにします。

自動、半自動、またはマニュアルモードへの切替えは、ポートの動作に影響を与えません。ポートをシャットダウンモードに設定すると、ポートのすべての動作が直ちに停止して、そのポートはシャットダウンから抜けるまでアイドル状態を維持します。

### 自動(Auto)モード

自動(Auto)モードに入るためには、リセットに先だって AUTO 入力をハイに強制するか、または通常動作中に R12h[P\_M1,P\_M0] を [1,1] に設定してください(表16a と表16b を参照)。自動モードでは、正当な PD がポートで検出されると、MAX5965A/MAX5965B は検出と分類を行ってポートを自動的にパワーアップします。正当な PD がポートで検出されなければ、正当な PD が接続されるまで MAX5965A/MAX5965B は検出ルーチンを繰り返します。

自動モードに入ると、DET\_EN\_ ビットと CLASS\_EN\_ ビットがハイに設定されてソフトウェアによる変更がない限りハイに保たれます。ソフトウェアを使用して DET\_EN\_ および/または CLASS\_EN\_ をローに設定すると、MAX5965A/MAX5965B は検出および/または分類を行いません。自動モードで検出ルーチンをディセーブルすると、DET\_BY (R23h[4]) を 1 に設定しない限り、対応するポートの電源はオンにならないように保護されます。

AUTO の状態は、リセット中にのみレジスタにラッチされます。リセット後に AUTO 入力を変更しても無視されます。

### 半自動(Semi-Auto)モード

半自動モードに入るためには、通常動作中に R12h[P\_M1,P\_M0] を [1,0] に設定してください(表16a と表16b を参照)。半自動モードでは、MAX5965A/MAX5965B は、要求に応じて検出および/または分類を繰り返して行いますが、ポート接続の状態に関係なくポートの電源をオンにしません。

R19h[PWR\_ON\_] (表22) をハイに設定すると、検出/分類ルーチンは直ちに終了してポートへの電源がオンになります。

半自動モードでは、R14h[DET\_EN\_, CLASS\_EN\_] がローにデフォルト設定されます。検出および/または分類ルーチンを開始するためには、ソフトウェアを使用して R14h[DET\_EN\_, CLASS\_EN\_] をハイに設定してください。ソフトウェアがポートの電源オフを命令(リセットまたは PWR\_OFF\_ のいずれかによる)するたびに、R14h[DET\_EN\_, CLASS\_EN\_] はリセットされます。その他のかなる場合(負荷切断や障害状態が発生したことによって、ステートマシンが電源をオフにする場合など)も、これら各ビットの状態は不变です。

### マニュアルモード

マニュアルモードに入るためには、通常モード中に R12h[P\_M1,P\_M0] を [0,1] に設定してください(表16a と表16b を参照)。マニュアルモードでは、ソフトウェアが動作シーケンスを命令します。検出および分類の動作を開始するためには、R14h[DET\_EN\_] と R14h[CLASS\_EN\_] の両方にこの順序でそれぞれ 1 を書き込んでください。実行後、コマンドはレジスタからクリアされます。PWR\_ON\_ が最優先となります。PWR\_ON\_ を隨時ハイに設定すると、デバイスは直ちに給電モードに入ります。DET\_EN\_ と CLASS\_EN\_ を同時にハイに設定すると、最初に検出が行われます。いったん給電状態になると、デバイスは DET\_EN\_ または CLASS\_EN\_ のコマンドを無視します。

別のモードからマニュアルモードに切り替えると、DET\_EN\_、CLASS\_EN\_ はローにデフォルト設定されます。これらのビットは、設定ビットではなくプッシュボタンになります(すなわち、マニュアルモードの間にこれらのビットに 1 を書き込むと、デバイスは 1 サイクルの検出および/または分類を実行するよう命令されます)。実行が終了すると、各ビットはゼロにリセットされます。

### シャットダウンモード

シャットダウンモードに入るためには、リセットに先だって AUTO 入力をローに強制するか、または通常動作中に R12h[P\_M1,P\_M0] を [0,0] に設定してください(表16a と表16b を参照)。MAX5965A/MAX5965B をシャットダウンモードにすると、電源が直ちにオフになり、対応するポートに対する動作がすべて停止されます。影響を受けるポートのイベントビットとステータスビットもクリアされます。シャットダウンモードでは、DET\_EN\_、CLASS\_EN\_、および PWR\_ON\_ の各コマンドは無視されます。

シャットダウンモードでは、シリアルインターフェースは正常に動作します。

# Power over Ethernet用、ハイパワー クワッド、モノリシック、PSEコントローラ

MAX5965A/MAX5965B

## PD検出

PD検出がアクティブになると、MAX5965A/MAX5965Bは正当なPDであるか、出力を調べます。各検出サイクル後、このデバイスはDET\_END\_ビットのR04h/05h[3:0]をハイに設定して検出結果をStatusレジスタのR0Ch[2:0]、R0Dh[2:0]、R0Eh[2:0]、およびR0Fh[2:0]に通知します。R05hを読み取ったとき、またはポートのリセット後に、DET\_END\_ビットはローにリセットされます。

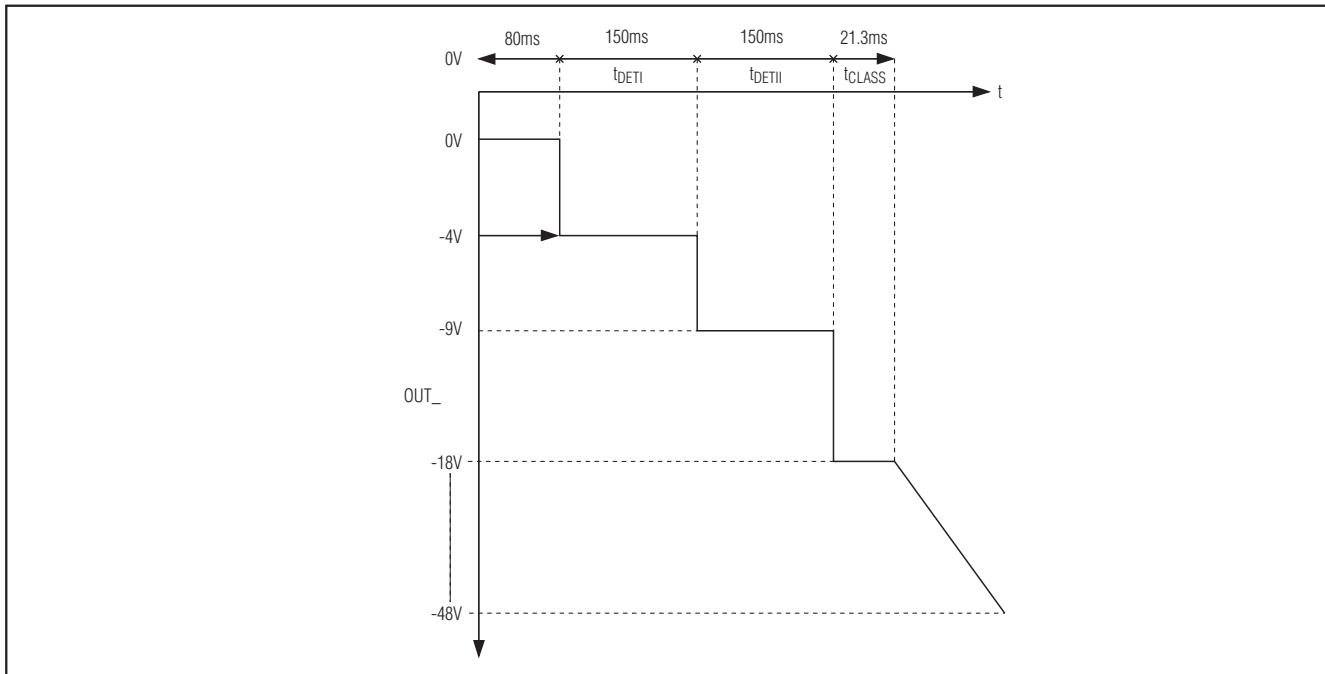

正当なPDは、IEEE 802.3af/at規格で規定されているとおり、 $25\text{k}\Omega$ の検出シグニチャ特性を備えています。表1は、正当なPDシグニチャを検出するPSEのIEEE 802.3af/at仕様を示しています。「標準動作回路」と図1a(検出、分類、およびポートのパワーアップシーケンス)を参照してください。MAX5965A/MAX5965Bは、正当なPD、開路、低抵抗負荷、高抵抗負荷、大容量性負荷、正DC電源、または負DC電源などの、ポートに接続された各種デバイスを調べて類別することができます。

検出では、MAX5965A/MAX5965Bは外付けMOSFETをオフ状態に維持してDET\_入力から2種のプローブ電圧を強制的に与えます。DET\_入力を流れる電流が、OUT\_の電圧と共に測定されます。ポートに接続されたデバイスを確認するために、IEEE 802.3af規格の規定に従って2点

間勾配測定が採用されています。MAX5965A/MAX5965Bは、適切なセトリング時間と50Hz/60Hzの電力線ノイズ結合の排除のための100msのデジタル積分を実現します。

DET\_入力と直列の外付けダイオードは、IEEE 802.3af/at規格の規定に従ってPD検出を第1象限に限定します。非PDデバイスの損傷を防止し、このデバイス自体を出力短絡から保護するために、MAX5965A/MAX5965Bは、PD検出時にDET\_に流れる最大電流を2mA以下に制限します。

ミッドスパンモードでは、MAX5965A/MAX5965Bは各異常検出の後、2.2秒待機してからもう一度検出サイクルを試みます。ただし、最初の検出は検出コマンドの送出直後に行われます。

## 大容量値の検出

レジスタR23h[5]のCLC\_ENビットは、レガシーピー・アンド・アイ(PD)デバイスの大容量コンデンサの検出機能をイネーブルします。CLC\_EN = 1のとき、この大容量検出限界は最大 $150\mu\text{F}$ まで拡大されます。CLC\_EN = 0は、通常のコンデンササイズの検出に対するデフォルト条件です。表1と「レジスタマップおよび説明」の項を参照してください。

表1. PSE PI検出モードの電気的要件(IEEE 802.3af規格の表33-2)

| PARAMETER                              | SYMBOL             | MIN  | MAX  | UNITS | ADDITIONAL INFORMATION                                |

|----------------------------------------|--------------------|------|------|-------|-------------------------------------------------------|

| Open-Circuit Voltage                   | V <sub>O</sub> C   | —    | 30   | V     | In detection mode only                                |

| Short-Circuit Current                  | I <sub>S</sub> C   | —    | 5    | mA    | In detection mode only                                |

| Valid Test Voltage                     | V <sub>VALID</sub> | 2.8  | 10   | V     |                                                       |

| Voltage Difference Between Test Points | ΔV <sub>TEST</sub> | 1    | —    | V     |                                                       |

| Time Between Any Two Test Points       | t <sub>BP</sub>    | 2    | —    | ms    | This timing implies a 500Hz maximum probing frequency |

| Slew Rate                              | V <sub>SLEW</sub>  |      | 0.1  | V/μs  |                                                       |

| Accept Signature Resistance            | R <sub>GOOD</sub>  | 19   | 26.5 | kΩ    |                                                       |

| Reject Signature Resistance            | R <sub>BAD</sub>   | < 15 | > 33 | kΩ    |                                                       |

| Open-Circuit Resistance                | R <sub>OPEN</sub>  | 500  | —    | kΩ    |                                                       |

| Accept Signature Capacitance           | C <sub>GOOD</sub>  | —    | 150  | nF    |                                                       |

| Reject Signature Capacitance           | C <sub>BAD</sub>   | 10   | —    | μF    |                                                       |

| Signature Offset Voltage Tolerance     | V <sub>OS</sub>    | 0    | 2.0  | V     |                                                       |

| Signature Offset Current Tolerance     | I <sub>OS</sub>    | 0    | 12   | μA    |                                                       |

# Power over Ethernet用、ハイパワー クワッド、モノリシック、PSEコントローラ

## 受電機器の分類(PD分類)

PD分類モードでは、MAX5965A/MAX5965BはDET\_にプローブ電圧(-18V)を強制的に印加して、DET\_に流れる電流を測定します。測定された電流がPDのクラスを決定します。

各分類サイクルの後、デバイスはCL\_END\_ビット(R04h[05h[7:4])をハイに設定し、分類結果をStatusレジスタのR0Ch[6:4]、R0Dh[6:4]、R0Eh[6:4]、およびR0Fh[6:4]に通知します。レジスタR05hから読み取りを行ったとき、またはポートリセット後に、CL\_END\_ビットはローにリセットされます。EventレジスタR04hとR05hはいずれもポートを電源オフにした後にクリアされます。表2は、電源インターフェース(PI)においてPDを分類するPSEに関するIEEE 802.3afの要件を示します。

MAX5965A/MAX5965Bは、分類を増やすことによってIEEE 802.3af規格を超えるハイパワーに対応します(クラス5および2イベント分類)。

## PDのクラス5分類

分類の際に、MAX5965A/MAX5965Bが $|I_{CLASS}| > 48mA$ を超える電流を検出した場合、PDはクラス5の受電機器として分類されます。StatusレジスタR0Ch[6:4]、R0Dh[6:4]、R0Eh[6:4]、またはR0Fh[6:4]がクラス5の分類結果を通知します。

## PDの2イベント(クラス6)分類

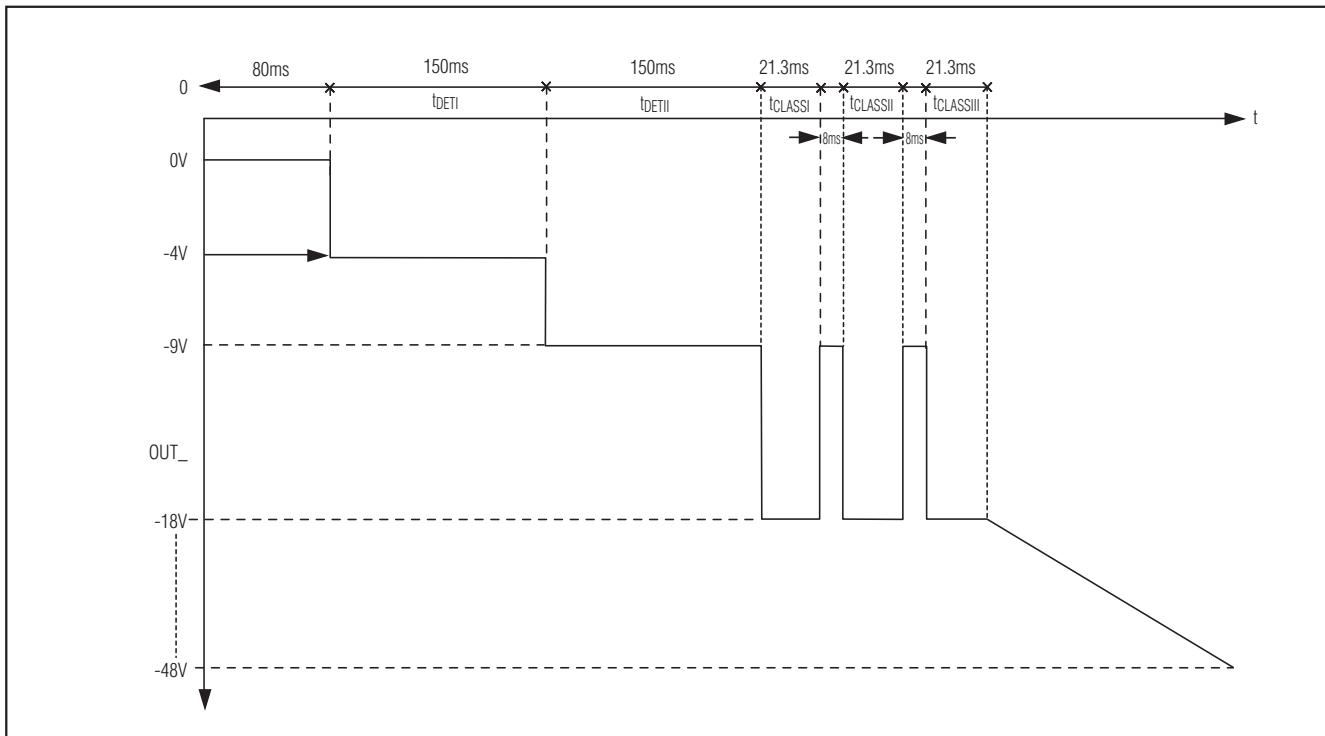

2イベント分類をアクティブにすると、各分類サイクル間で8msだけ待機してから分類サイクルを3回繰り返します(図1bを参照)。各分類サイクル間で、MAX5965A/MAX5965Bは、ポート電圧を完全にリセットしないで、出力電圧を-9Vに維持します。R1Ch[7:4]のEN\_CL6ビットによってポート単位で2イベント分類をイネーブルします。

**表2. PDのPSE分類(IEEE 802.3af規格の表33-4)**

| MEASURED $I_{CLASS}$ (mA) | CLASSIFICATION       |

|---------------------------|----------------------|

| 0 to 5                    | Class 0              |

| > 5 and < 8               | May be Class 0 and 1 |

| 8 to 13                   | Class 1              |

| > 13 and < 16             | May be Class 1 or 2  |

| 16 to 21                  | Class 2              |

| > 21 and < 25             | May be Class 2 or 3  |

| 25 to 31                  | Class 3              |

| > 31 and < 35             | May be Class 3 or 4  |

| 35 to 45                  | Class 4              |

| > 45 and < 51             | May be Class 4 or 5  |

| 51 to 68                  | Class 5              |

## 給電状態

MAX5965A/MAX5965Bが給電された状態に入ると、t<sub>START</sub>およびt<sub>DISC</sub>の各タイマーがリセットされます。MAX5965A/MAX5965Bは、ポート電源をオンにする前に、他のポートがオンになっていないかどうか、またt<sub>FAULT</sub>タイマーがゼロであるかどうかをチェックします。ACD\_EN\_ビットが設定されているかどうかがさらにチェックされ、この場合、ポートが給電されるためにはOSC\_FAILビットがロー(発振器OK)でなければなりません。

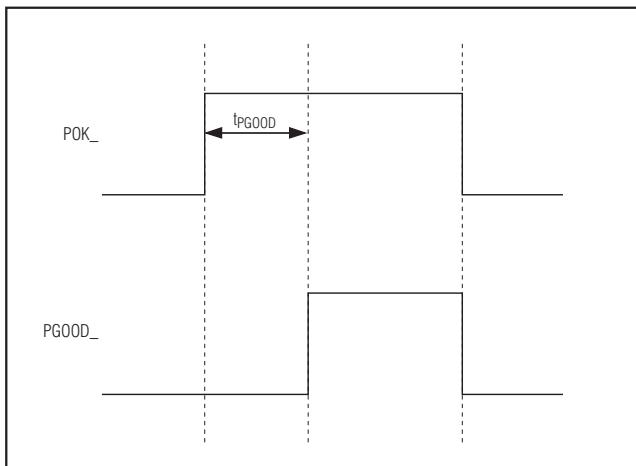

これらの条件が満たされると、MAX5965A/MAX5965Bは起動入り、ポートへの電源をオンにします。V<sub>OUT</sub>\_がV<sub>EE</sub>から2Vの範囲内にあるとき、内部信号POK\_はハイにアサートされます。POK\_がt<sub>PGOOD</sub>よりも長い間ハイのままであると、PGOOD\_ステータスピットがハイに設定されます。POK\_がローになると、PGOOD\_は直ちにリセットされます(図2を参照)。

ポートがパワーアップまたはパワーダウンになると、PG\_CHG\_ビットが設定されます。PWR\_EN\_は、ポートがパワーアップになると設定され、ポートがシャットダウンするとリセットされます。ポートシャットダウンタイマーは0.5msの間持続して、この期間に他のポートがオフになるのを防ぎます。ただし、緊急シャットダウン( $\overline{RESET} = L$ 、RESET\_IC = H、V<sub>EEUVLO</sub>、V<sub>DDUVLO</sub>、およびT<sub>SHD</sub>)の場合を除きます。

MAX5965A/MAX5965Bは、オフにする前に必ずすべてのポートのステータスをチェックします。優先順位ロジックシステムが各ポートのターンオンまたはターンオフの順序を決定して、これらの同時発生を防止します。序数の小さいポートが他のポートに優先します(すなわち、ポート1が最初に、ポート2が2番目、ポート3が3番目、そしてポート4が4番目になります)。PWR\_OFF\_をハイに設定すると、対応するポートへの電源がオフになります。

# Power over Ethernet用、ハイパワー クワッド、モノリシック、PSEコントローラ

**MAX5965A/MAX5965B**

図1a. 検出、分類、およびポートのパワーアップシーケンス

図1b. 検出、2イベント分類、およびポートのパワーアップシーケンス

# Power over Ethernet用、ハイパワー クワッド、モノリシック、PSEコントローラ

図2. PGOOD\_のタイミング

## 過電流保護

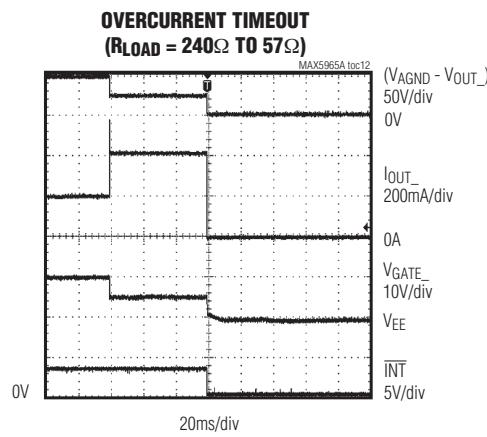

SENSE\_とV<sub>EE</sub>の間に接続された検出抵抗R<sub>S</sub>によって、負荷電流を監視します。通常の動作状態では、R<sub>S</sub>両端間の電圧(V<sub>RS</sub>)がスレッショルドV<sub>SU\_LIM</sub>を超えることはありません。V<sub>RS</sub>がV<sub>SU\_LIM</sub>を超えると、内部の電流制限回路がGATE\_電圧をレギュレートして電流はI<sub>LIM</sub> = V<sub>SU\_LIM</sub>/R<sub>S</sub>に制限されます。過渡状態においてV<sub>RS</sub>がV<sub>SU\_LIM</sub>を1V以上超えた場合、高速プルダウン回路が働いて電流のオーバーシュートを急速に回復します。起動時に電流制限状態が持続している場合、起動タイマーt<sub>START</sub>が満了するとポートが遮断されてSTRT\_FLT\_ビットが設定されます。通常の給電された状態では、MAX5965A/MAX5965Bは、V<sub>FILT\_LIM</sub> = V<sub>SU\_LIM</sub>のおよそ88%に設定された過電流状態にないかどうかをチェックします。t<sub>FAULT</sub>カウンタは、許容最大連続過電流期間を設定します。t<sub>FAULT</sub>カウンタは、V<sub>RS</sub>がV<sub>FILT\_LIM</sub>を超えると増加し、V<sub>RS</sub>がV<sub>FILT\_LIM</sub>以下に低下すると緩やかに減少します。t<sub>FAULT</sub>カウンタが緩やかにデクリメントすることによって、反復される短期間の過電流を検出することができます。カウンタがt<sub>FAULT</sub>限界に達すると、MAX5965A/MAX5965Bはポートへの給電を停止してIMAX\_FLT\_ビットをアサートします。連続過電圧の場合、t<sub>FAULT</sub>期間の直後に障害がラッチされます。V<sub>SU\_LIM</sub>は、ICUTレジスタR2Ah[6:4]、R2Ah[2:0]、R2Bh[6:4]、R2Bh[2:0]、およびレジスタR29h[1:0]のIVEEビットによってプログラムすることができます。ICUTレジスタの詳細については、「ハイパワーモード」の項を参照してください。

過電流障害による電源オフの後、およびRSTR\_ENビットが設定された場合、t<sub>FAULT</sub>タイマーは直ちにリセットされずに、それまでと同様に緩やかにデクリメントを開始

します。MAX5965A/MAX5965Bは、t<sub>FAULT</sub>カウンタがゼロのときにのみポートに給電することができます。この機能は、外付けMOSFETに対する自動デューティサイクル保護を設定して過熱を防止します。

電流がCLASS Statusレジスタで指定されたクラスの許容最大電流を超えると、MAX5965A/MAX5965Bは、連続的にフラグを立てます。クラス過電流が発生すると、MAX5965A/MAX5965BはレジスタR09hのIVC\_ビットを設定します。

## ICUTレジスタおよびハイパワーモード

### ICUTレジスタ

ICUTレジスタは、MAX5965A/MAX5965Bの各ポートに許容される最大電流制限値を決定します。3つのICUTビット(R2Ah[6:4]、R2Ah[2:0]、R2Bh[6:4]、およびR2Bh[2:0])を使用すると、IEEE規格の制限値を超える電流制限と過電流のスレッショルドをプログラムすることができます(表34a、表34b、および表34cを参照)。CL\_DISC (R17h[2])が0に設定されているときは、I<sup>2</sup>Cインターフェースを通じてICUTレジスタに直接、書き込むことができます(表3を参照)。この場合、ポートの電流制限は分類のステータスに無関係に設定されます。

CL\_DISCビットを1に設定すると、MAX5965A/MAX5965Bは、ポートの分類結果に基づいてICUTレジスタを自動的に設定します。表3と「レジスタマップおよび説明」の項を参照してください。

### ハイパワーモード

CL\_DISC (R17h[2])が0に設定されているときに、ICUTビットを000、110、または111以外の任意の組み合わせに設定することによってハイパワーモードが設定されます(000はIEEE規格の限界値のデフォルト値であることに留意してください)。表3と「レジスタマップおよび説明」の項を参照してください。

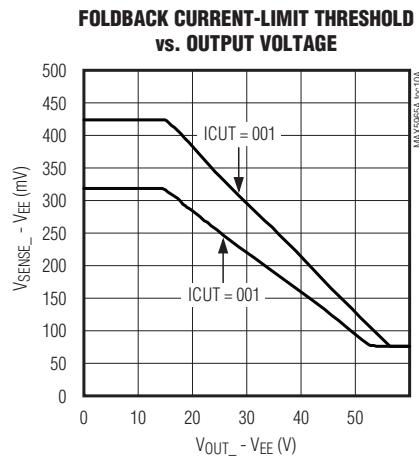

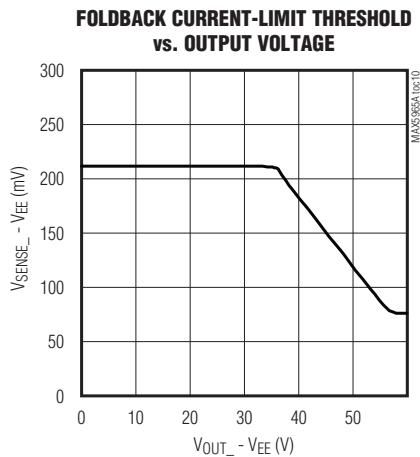

### フォールドバック電流

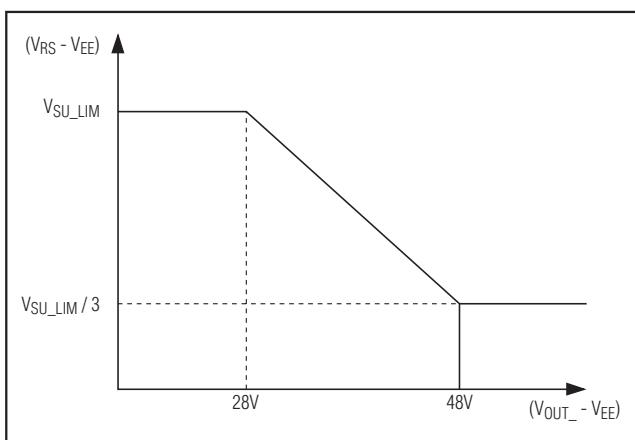

起動中および通常動作中に(V<sub>OUT\_-</sub> - V<sub>EE</sub>) > 28Vになると、内蔵回路はOUT\_の電圧を検出して電流制限値を下げます。フォールドバック機能は、FETの消費電力を低減するのに役立ちます。(V<sub>OUT\_-</sub> - V<sub>EE</sub>) > 48Vになると、電流制限は最終的にI<sub>LIM</sub>の1/3まで減少します(図3aを参照)。ハイパワーモードの場合、フォールドバックは(V<sub>OUT\_-</sub> - V<sub>EE</sub>) > 10Vのときに開始されます(図3bを参照)。ハイパワーモードでは、(V<sub>OUT\_-</sub> - V<sub>EE</sub>) > 48Vのときに、電流制限(I<sub>LIM</sub>)はフォールドバック電流(V<sub>TH\_FB</sub>/R<sub>S</sub>)の最小値まで減少します。

# Power over Ethernet用、ハイパワー クワッド、モノリシック、PSEコントローラ

MAX5965A/MAX5965B

表3. 自動ICUTプログラミング

| CL_DISC | PORT CLASSIFICATION RESULT | ENx_CL6 | EN_HP_ALL | EN_HP_CL6 | EN_HP_CL5 | EN_HP_CL4 | RESULTING ICUT REGISTER BITS |

|---------|----------------------------|---------|-----------|-----------|-----------|-----------|------------------------------|

| 0       | Any                        | X       | X         | X         | X         | X         | User programmed              |

| 1       | 1                          | X       | X         | X         | X         | X         | ICUT = 110                   |

| 1       | 2                          | X       | X         | X         | X         | X         | ICUT = 111                   |

| 1       | 0, 3                       | X       | X         | X         | X         | X         | ICUT = 000                   |

| 1       | 4, 5                       | X       | 0         | X         | X         | X         | ICUT = 000                   |

| 1       | 5                          | X       | 1         | X         | 1         | X         | ICUT = R24h[6:4]             |

| 1       | 5                          | X       | 1         | X         | 0         | X         | ICUT = 000                   |

| 1       | 4                          | X       | 1         | X         | X         | 1         | ICUT = R24h[6:4]             |

| 1       | 4                          | X       | 1         | X         | X         | 0         | ICUT = 000                   |

| 1       | 6 or Illegal               | 0       | X         | X         | X         | X         | —                            |

| 1       | 6 or Illegal               | 1       | 1         | 1         | X         | X         | (See Table 35a)              |

| 1       | 6 or Illegal               | 1       | 1         | 0         | X         | X         | ICUT = 000                   |

| 1       | 6 or Illegal               | 1       | 0         | X         | X         | X         | ICUT = 000                   |

## MOSFETゲートドライバ

外付けのnチャネルMOSFETのゲートをGATE\_に接続してください。内蔵の50μA電流源がGATE\_を(V<sub>EE</sub> + 10V)にプルアップしてMOSFETをオンにします。内蔵の40μA電流源がGATE\_をV<sub>EE</sub>にプルダウンしてMOSFETをオフにします。

プルアップ電流とプルダウン電流は、ターンオン時またはターンオフ時に出力の最大スルーレートを制御します。次式を使用して最大スルーレートを設定してください。

$$\frac{\Delta V_{OUT}}{\Delta t} = \frac{I_{GATE}}{C_{GD}}$$

ここで、C<sub>GD</sub>は、外付けMOSFETのGATEとDRAIN間の全容量です。電流制限とドレインにおける容量性負荷によって起動時のスルーレートが制御されます。電流制限のレギュレーションの間、MAX5965A/MAX5965BはGATE\_電圧を操作してSENSE\_の電圧(V<sub>RS</sub>)を制御します。V<sub>RS</sub>が制限スレッショルド(V<sub>SU\_LIM</sub>)を超えた場合は、高速プルダウンがアクティブになります。高速プルダウン電流はオーバーシュート量の増加に伴って増大します。最大高速プルダウン電流は100mAです。

ターンオフ時にGATE\_電圧が1.2Vを下回ると、強プルダウンスイッチがアクティブになってMOSFETを確実にオフ状態に保ちます。

図3a. フォールドバック電流特性

図3b. ハイパワーモードのフォールドバック電流特性

# Power over Ethernet用、ハイパワー クワッド、モノリシック、PSEコントローラ

## デジタルロジック

$V_{DD}$ 電源は、内蔵ロジック回路に給電します。 $V_{DD}$ は可変範囲が $+3.0V \sim +5.5V$ で、CMOS接続部(SDAIN、SDAOUT、SCL、AUTO、 $\overline{SHD}_-$ 、A<sub>\_</sub>)のロジックスレッショルドを決定します。この電圧範囲で、MAX5965A/MAX5965Bは、非絶縁型の低電圧マイクロコントローラとインターフェース接続することができます。MAX5965A/MAX5965Bは、デジタル電源と内蔵ロジックの対応性をチェックします。さらに、MAX5965A/MAX5965Bは、 $+2.0V$ の $V_{DD}$ 低電圧ロックアウト( $V_{DDUVLO}$ )も備えています。 $V_{DDUVLO}$ 状態では、MAX5965A/MAX5965Bはリセットされてポートは遮断された状態に保たれます。Supply Eventレジスタのビット0は、 $V_{DD}$ が回復した後の $V_{DDUVLO}$ の状態を示します(表12)。ロジック入力とロジック出力はすべてDGNDが基準です。AC切断検出の場合には、DGNDとAGNDを外部で相互に接続する必要があります。DGNDをMAX5965A/MAX5965Bにできる限り近接させてシステム内の1点でAGNDに接続してください。

## ハードウェアシャットダウン

$\overline{SHD}_-$ はシリアルインターフェースを使わずに応答するポートをシャットダウンします。ハードウェアシャットダウンは、電源をポートから高速で切断することが可能な緊急ターンオフ機能を提供します。 $\overline{SHD}_-$ をローにプルダウンすると電源が除去されます。また、 $\overline{SHD}_-$ によって応答するEventsとStatusレジスタビットもリセットされます。

## 割込み

MAX5965A/MAX5965Bは、割込み条件が存在するときローになるオープンドレインのロジック出力(INT)を内蔵しています。R00hとR01h(表6と表7)でInterruptレジスタが定義されています。マスクレジスタR01hは割込みをトリガするイベントを決定します。割込みに対する応答として、コントローラはEventレジスタのステータスを読み取って割込みの原因を判断し、その後の処置を取ります。また、各割込みイベントレジスタは、Clear on Read(CoR)レジスタを備えています。CoRレジスタアドレスを読み取ると割込みがクリアされます。割込みを読み取り専用アドレスから読み取るときはINTはローのままで。たとえば、ポート4の起動障害をクリアするためには、アドレス09hを読み取ってください(表11を参照)。複数の割込みをクリアするためには、レジスタ1Ahのグローバルプッシュボタンビット(ビット7、表23)を使用するか、ソフトウェアまたはハードウェアリセットを使用してください。

## 低電圧および過電圧保護

MAX5965A/MAX5965Bは、複数の低電圧および過電圧保護機能を備えています。「レジスタマップおよび説明」の項に掲げた表12は、低電圧および過電圧保護機能の詳細リストを示します。内蔵の $V_{EE}$ 低電圧ロックアウト( $V_{EEUVLO}$ )回路は、 $V_{AGND} - V_{EE}$ が3msより長く29Vを超えるまで、MOSFETをオフ状態に保ち、MAX5965A/MAX5965Bをリセット状態に保ちます。内部の $V_{EE}$ 過電圧( $V_{EE\_OV}$ )回路は、 $(V_{AGND} - V_{EE})$ が60Vを超えるとポートをシャットダウンします。デジタル電源も

低電圧ロックアウト( $V_{DDUVLO}$ )を備えています。また、MAX5965A/MAX5965Bは、他に $V_{EE}$ 低電圧割込み( $V_{EE\_UV}$ )、 $V_{DD}$ 低電圧割込み( $V_{DD\_UV}$ )、および $V_{DD}$ 過電圧割込み( $V_{DD\_OV}$ )の3つの低電圧および過電圧割込みを備えています。障害はSupply Eventsレジスタにラッチされますが(表12)、MAX5965A/MAX5965Bは $V_{EE\_UV}$ 、 $V_{DD\_UV}$ 、または $V_{DD\_OV}$ によってポートをシャットダウンしません。

## DC切断の監視

R13h[DCD\_EN\_]ビットをハイに設定すると、通常の給電された状態でDC負荷の監視が可能になります。 $V_{RS}$ ( $R_S$ 両端間の電圧)が $t_{DISC}$ を超えてDC負荷切斷スレッショルド $V_{DCTH}$ 以下になると、デバイスは電源をオフにして対応するポートのLD\_DISC\_ビットをアサートします。

## AC切斷の監視(MAX5965A/MAX5965B)

MAX5965A/MAX5965Bは、AC負荷切斷監視機能を備えています。外部から正弦波をOSCに印加してください。発振器の要件は次のとおりです。

- 1)  $V_{P-P} \times$ 周波数 =  $200V_{P-P} \times Hz \pm 15\%$

- 2) 正ピーク電圧 >  $+2.2V$

- 3) 周波数 >  $60Hz$

$100Hz \pm 10\%$ 、 $2V_{P-P} \pm 5\%$ 、 $+1.3V$ オフセット( $V_{PEAK} = +2.3V$  (typ))付きを推奨します。

MAX5965A/MAX5965Bは、外部発振器信号をバッファして3倍に増幅し、この信号をDET\_に送ります。ただし、正弦波は出力にAC結合されます。MAX5965A/MAX5965Bは、DET\_に戻るAC電流の振幅を監視して負荷の存在を検出します(「ファンクションダイアグラム」を参照)。

R13h[ACD\_EN\_]ビットをハイに設定すると、通常の給電状態でAC負荷切斷を監視することが可能になります。DET\_入力のAC電流ピークが $t_{DISC}$ を超えて $I_{ACTH}$ 以下になると、デバイスは電源をオフにして対応するポートのLD\_DISC\_ビットをアサートします。 $I_{ACTH}$ は、R23h[2:0]を使ってプログラムすることができます。

内蔵コンパレータは発振器入力の振幅が適正であるかどうかをチェックします。入力正弦波の正のピークが安全値の $2V$  (typ)以下になると、OSC\_FAILが設定されてポートがシャットダウンされます。ACD\_EN\_がハイに設定され、かつOSC\_FAILがハイに設定されているときは、電源をポートに印加することができません。AC切斷検出を使用しないときは、OSCを無接続のままにするか、これをDGNDに接続してください。

## サーマルシャットダウン

MAX5965A/MAX5965Bのダイ温度が $+150^{\circ}C$ に達すると、温度過昇障害が発生してMAX5965A/MAX5965Bはシャットダウンします。MOSFETはオフになります。温度過昇障害状態を除去するためには、MAX5965A/MAX5965Bのダイ温度を $+130^{\circ}C$ 未満に冷却する必要があります。サーマルシャットダウンの後、デバイスはリセットされます。

# Power over Ethernet用、ハイパワー クワッド、モノリシック、PSEコントローラ

**MAX5965A/MAX5965B**

## ウォッチドッグ

R1Eh、およびR1Fhの各レジスタは、ウォッチドッグ動作を制御します。ウォッチドッグ機能がイネーブルされると、MAX5965A/MAX5965Bは速やかに制御を引き継ぐか、あるいはソフトウェア/ファームウェアのクラッシュの場合にはポートへの電源を安全にシャットダウンします。詳しくはお問い合わせください。

## アドレス入力

A3、A2、A1、およびA0は、チップアドレスの4つの LSBを表します。完全なチップアドレスは7ビットになります(表4を参照)。

RESETがローからハイに遷移するか、または電源が( $V_{DD}$ または $V_{EE}$ のいずれかで)起動すると、4つのLSBがラッピングされます。アドレス入力は、内蔵の50kΩプルアップ抵抗によって $V_{DD}$ (ハイ)にデフォルト設定されています。また、MAX5965A/MAX5965Bは、グローバルアドレス30hからの呼出しに応答します(「グローバルアドレスおよびアラート応答プロトコル」の項を参照してください)。

表4. MAX5965A/MAX5965Bのアドレス

| 0 | 1 | 0 | A3 | A2 | A1 | A0 | R/W |

|---|---|---|----|----|----|----|-----|

|---|---|---|----|----|----|----|-----|

## I<sup>2</sup>C対応シリアルインターフェース

MAX5965A/MAX5965Bはスレーブとして動作し、I<sup>2</sup>C 対応の2線式または3線式インターフェースを通じてデータを送受信します。このインターフェースは、シリアルデータ入力ライン(SDAIN)、シリアルデータ出力ライン(SDAOUT)、およびシリアルクロックライン(SCL)を使用して、マスタとスレーブの間で双方向通信を実現します。マスタ(通常、マイクロコントローラ)は、MAX5965A/MAX5965Bとのすべてのデータ転送を開始し、データ転送に同期するSCLクロックを生成します。ほとんどのアプリケーションでは、SDAINラインとSDAOUTの両ラインを相互に接続してシリアルデータライン(SDA)を構成します。

独立した入力および出力データラインを使用することによって、絶縁型の電源からマイクロコントローラに給電するときのコントローラバスとのフォトカプラ結合が可能になります。

MAX5965A/MAX5965BのSDAINラインは入力として動作します。MAX5965A/MAX5965BのSDAOUTはオープンドレイン出力として動作します。SDAOUTには、通常4.7kΩのプルアップ抵抗が必要です。MAX5965A/MAX5965BのSCLラインは入力としてのみ動作します。複数のマスタが存在する場合、または単一マスタシステムのマスタがオープンドレインSCL出力を備えている場合、SCLには通常4.7kΩのプルアップ抵抗が必要になります。

図4. 2線式シリアルインターフェースのタイミング詳細

図5. 3線式シリアルインターフェースのタイミング詳細

# Power over Ethernet用、ハイパワー クワッド、モノリシック、PSEコントローラ

## シリアルアドレスの指定

各送信は、マスタによって送信されるSTART条件(図6)、これに続くMAX5965A/MAX5965Bの7ビットスレーブアドレスとR/Wビット、レジスタアドレスバイト、少なくとも1データバイト、および最後のSTOP条件から成ります。

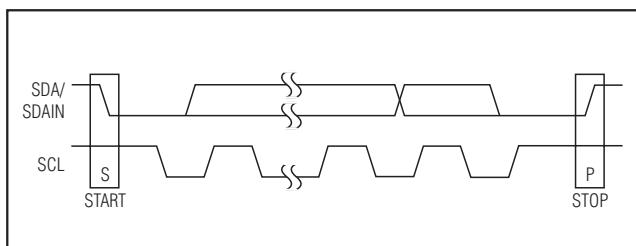

## STARTおよびSTOP条件

インターフェースがビジーでないとき、SCLとSDAはいずれもハイに保たれます。マスタは、SCLがハイの間にSDAをハイからローに遷移させるSTART (S)条件を用いて送信の開始を知らせます。スレーブとの通信を終了するとき、マスタはSCLがハイの間にSDAをローからハイに遷移させてSTOP (P)条件を送出します。STOP条件は、次の送信のためにバスを解放します。

図6. STARTおよびSTOP条件

## ビット転送

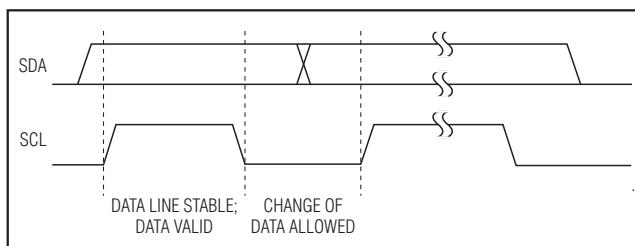

各クロックパルスで1データビットが転送されます(図7)。SCLがハイの間はSDA上のデータを安定な状態に保つ必要があります。

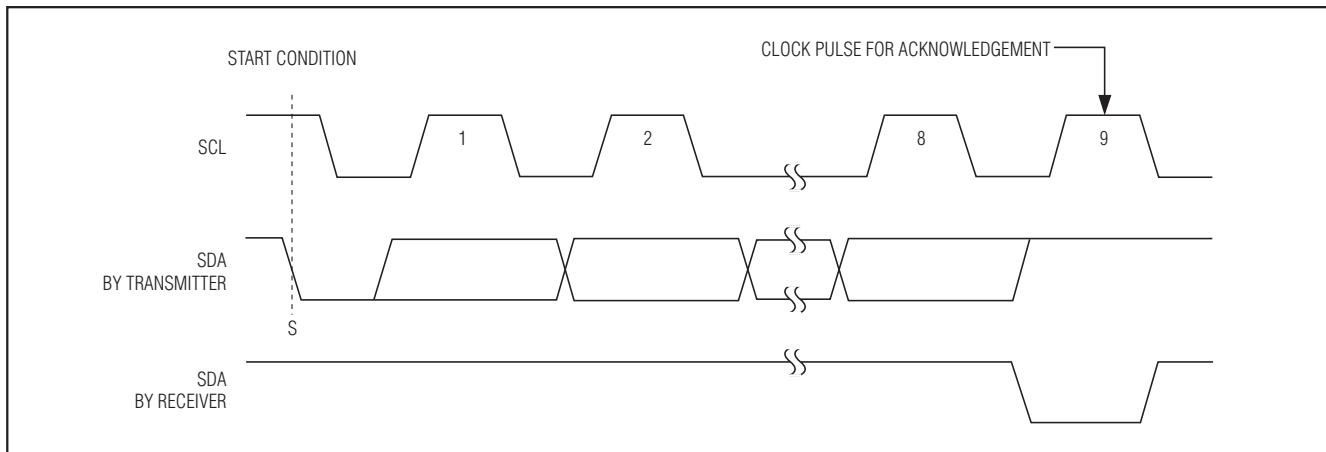

## 確認応答

確認応答ビットは、受信側が各データバイトのハンドシェーク受信用に使用するクロック駆動の9番目のビットです(図8)。すなわち、有効な各転送バイトは9ビットを必要とします。マスタは9番目のクロックパルスを生成し、受信側は確認応答クロックパルスの間にSDA(または、3線式インターフェースではSDAOUT)をプルダウンします。したがって、SDAラインはクロックパルスがハイの期間中、安定したローとなります。マスタがMAX5965A/MAX5965Bに送信すると、MAX5965A/MAX5965Bは確認応答ビットを生成します。MAX5965A/MAX5965Bがマスタに送信すると、マスタは確認応答ビットを生成します。

図7. ビット転送

図8. 確認応答

# Power over Ethernet用、ハイパワー クワッド、モノリシック、PSEコントローラ

MAX5965A/MAX5965B

## スレーブアドレス

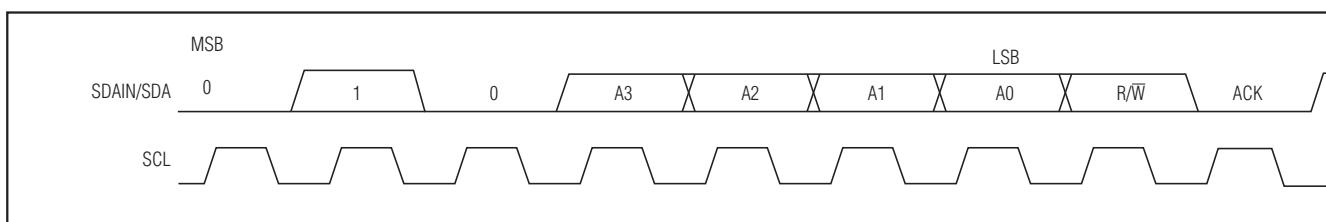

MAX5965A/MAX5965Bは7ビット長のスレーブアドレスを備えています(図9)。7ビットのスレーブアドレスに続くビット(ビット8)はR/Wビットで、これは書き込みコマンドの場合はローで、読み取りコマンドの場合はハイです。

010は、常にMAX5965A/MAX5965Bのスレーブアドレスの最初の3ビット(MSB)を表します。スレーブアドレスビットA3、A2、A1、およびA0は、MAX5965A/MAX5965BのA3、A2、A1、およびA0の各入力の状態を表すため、最大16個のMAX5965A/MAX5965Bデバイスがバスを共有することができます。A3、A2、A1、およびA0の状態は、MAX5965A/MAX5965BがリセットされるとレジスタのR11hにラッチされます。MAX5965A/MAX5965Bは、バスを常に監視してSTART条件とこれに続くMAX5965A/MAX5965Bのスレーブアドレスを待機します。MAX5965A/MAX5965Bは、そのスレーブアドレスを認識すると確認応答してから次の通信に備えます。

## グローバルアドレスおよび アラート応答プロトコル

グローバルアドレスの呼出しは、複数のデバイスの同じレジスタ(アドレス0x60)に書き込むために書き込みモードで使用されます。読み取りモード(アドレス0x61)では、グローバルアドレス呼出しアラート応答アドレスとして使用されます。グローバル呼出しに応答する際、割込みがアクティブのときにMAX5965A/MAX5965Bはそれ自体のアドレスをデータラインに出力します。SDAOUTラインに接続された、割込みがアクティブな他のデバイスもすべて同様です。各ビットが送信された後、MAX5965A/MAX5965Bは、送信しているデータ

に対してデータラインが有効に応答していることを確認します。有効に応答していない場合は、バックオフしてデータラインを解放します。この遅延対応プロトコルによって、常に最下位アドレスを持つデバイスに送信を終了させることができます。ここで、マイクロコントローラは割込みに応答して適切な処置を取ることができます。MAX5965A/MAX5965Bは、自身の割込みをアラート応答プロトコルの終了時にリセットしません。このリセットは、マイクロコントローラがCoRアドレスを通じてEventレジスタをクリアするか、あるいはCLR\_INTプッシュボタンを作動させて行う必要があります。

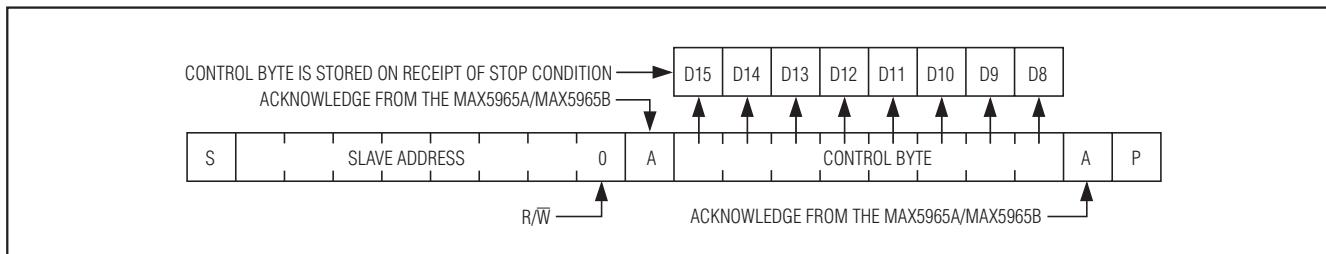

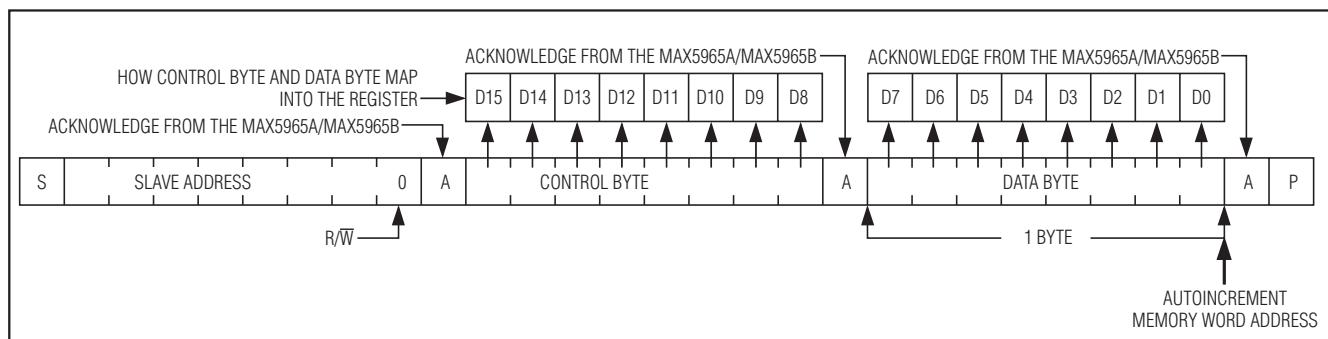

## MAX5965A/MAX5965Bへの書き込み用 メッセージフォーマット

MAX5965A/MAX5965Bへの書き込みは、R/Wビットを0に設定することによるMAX5965A/MAX5965Bのスレーブアドレス送信、およびこれに続く少なくとも1バイトの情報から成ります。情報の最初のバイトは、コマンドバイトです(図10)。コマンドバイトは、次のバイトを受信する場合のこのバイトの書き込み対象となるMAX5965A/MAX5965Bのレジスタを決定します。MAX5965A/MAX5965Bがコマンドバイトの受信後にSTOP条件を検出した場合、MAX5965A/MAX5965Bはコマンドバイトの保存後に新たな処置を取りません。コマンドバイトの後に受信されるバイトはデータバイトです。最初のデータバイトは、コマンドバイトによって選択されたMAX5965A/MAX5965Bの内部レジスタに保存されます。MAX5965A/MAX5965BがSTOP条件を検出する前に複数のデータバイトを送信すると、これらのバイトは、後続のMAX5965A/MAX5965Bの内部レジスタに保存されます。これは、制御バイトアドレスが自動インクリメントするためです。

図9. スレーブアドレス

図10. 受信される制御バイト

# Power over Ethernet用、ハイパワー クワッド、モノリシック、PSEコントローラ

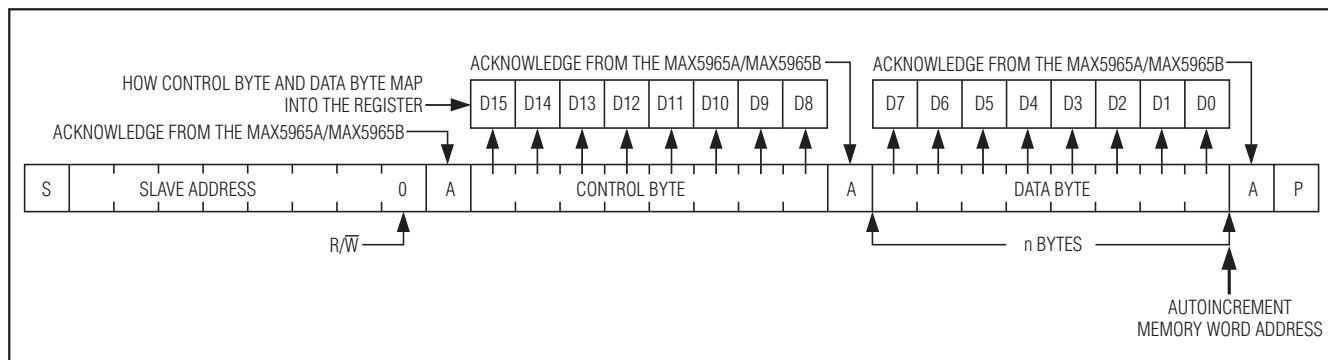

## 読み取り用メッセージフォーマット

MAX5965A/MAX5965Bは、内部にアドレスポインタとして保存されたコマンドバイトを使って読み取りを行いますが、これは書込みの場合にこの保存されたコマンドバイトがアドレスポインタとして使用されるのと同じです。ポインタは、書込みの場合と同じルールを使用して各データバイトの読み取り後に自動インクリメントします。したがって、読み取りは、書込みを行ってMAX5965A/MAX5965Bのコマンドバイトを最初に設定することによって開始されます。その後、マスタは、MAX5965A/MAX5965Bから連続した「n」バイトを読み取ります。その最初のデータバイトは、初期化されたコマンドバイトによってアドレス指定されたレジスタから読み取られます。書込み後の読み取り確認を行うときは必ずコマンドバイトのアドレスをリセットしてください。これは、保存された制御バイトアドレスが書込み後に自動インクリメントするためです。

## 複数マスタによる動作

MAX5965A/MAX5965Bが複数のマスタとともに2線式インターフェース上で動作するとき、MAX5965A/MAX5965Bを読み取るマスタは、MAX5965A/MAX5965Bのアドレスポインタを設定する書込みとその位置からデータを取り出す読み取りとの間で起動を繰り返す必要があります。マスタ1がMAX5965A/

MAX5965Bのアドレスポインタを設定した後で、マスタ1がデータを読み取る前であれば、マスタ2がバスを引き継ぐことは可能です。マスタ2が後でMAX5965A/MAX5965Bのアドレスポインタをリセットすると、マスタ1の読み取りは予期しない位置から行われることになります。

## コマンドアドレスの自動インクリメント

アドレスの自動インクリメントによって、コマンドアドレスに必要な送信回数を最小限に抑えてMAX5965A/MAX5965Bをより少ない送信で設定することができます。MAX5965A/MAX5965Bに保存されるコマンドアドレスは、一般に、各データバイトの書込みまたは読み取りが行われた後でインクリメントします(表5)。MAX5965A/MAX5965Bは、無効なレジスタアドレスへの書込みと不注意によるアドレスのラップアラウンドとが回避されるように設計されています。

表5. 自動インクリメントルール

| COMMAND BYTE ADDRESS RANGE | AUTOINCREMENT BEHAVIOR                                     |

|----------------------------|------------------------------------------------------------|

| 0x00 to 0x26               | Command address autoincrements after byte read or written  |

| 0x26                       | Command address remains at 0x26 after byte written or read |

図11. 受信される制御および單一データバイト

図12. 受信される「n」データバイト

# Power over Ethernet用、ハイパワー クワッド、モノリシック、PSEコントローラ

## レジスタマップおよび説明

Interruptレジスタ(表6)は、Eventレジスタのステータスの要約を示すもので、割込み信号(INTがローになる)をコントローラに送信するために使用されます。R1Ah[7]に1を書き込むと、すべてのInterruptおよびEventsレジスタがクリアされます。リセットすると、R00hは00hに設定されます。

INT\_EN (R17h[7])はグローバル割込みマスクです(表7)。MASK\_ビットはレジスタのR00hの対応する割込みビットを有効にします。INT\_EN (R17h[7])に0を書き込むと、INT出力がディセーブルされます。

リセットすると、R01hはAAA00A00bに設定されます。ここで、Aはリセット前のAUTO入力の状態です。

**表6. Interruptレジスタ**

| ADDRESS = 00h |     |     | DESCRIPTION                                                                                                              |

|---------------|-----|-----|--------------------------------------------------------------------------------------------------------------------------|

| SYMBOL        | BIT | R/W |                                                                                                                          |

| SUP_FLT       | 7   | R   | Interrupt signal for supply faults. SUP_FLT is the logic OR of all the bits [7:0] in register R0Ah/R0Bh (Table 12).      |

| TSTR_FLT      | 6   | R   | Interrupt signal for startup failures. TSTR_FLT is the logic OR of bits [7:0] in register R08h/R09h (Table 11).          |

| IMAX_FLT      | 5   | R   | Interrupt signal for current-limit violations. IMAX_FLT is the logic OR of bits [3:0] in register R06h/R07h (Table 10).  |

| CL_END        | 4   | R   | Interrupt signal for completion of classification. CL_END is the logic OR of bits [7:4] in register R04h/R05h (Table 9). |

| DET_END       | 3   | R   | Interrupt signal for completion of detection. DET_END is the logic OR of bits [3:0] in register R04h/R05h (Table 9).     |

| LD_DISC       | 2   | R   | Interrupt signal for load disconnection. LD_DISC is the logic OR of bits [7:4] in register R06h/R07h (Table 10).         |

| PG_INT        | 1   | R   | Interrupt signal for PGOOD status change. PG_INT is the logic OR of bits [7:4] in register R02h/R03h (Table 8).          |

| PEN_INT       | 0   | R   | Interrupt signal for power-enable status change. PEN_INT is the logic OR of bits [3:0] in register R02h/R03h (Table 8).  |

**表7. Interrupt Maskレジスタ**

| ADDRESS = 01h |     |     | DESCRIPTION                                                                                                       |

|---------------|-----|-----|-------------------------------------------------------------------------------------------------------------------|

| SYMBOL        | BIT | R/W |                                                                                                                   |

| MASK7         | 7   | R/W | Interrupt mask bit 7. A logic-high enables the SUP_FLT interrupts. A logic-low disables the SUP_FLT interrupts.   |

| MASK6         | 6   | R/W | Interrupt mask bit 6. A logic-high enables the TSTR_FLT interrupts. A logic-low disables the TSTR_FLT interrupts. |

| MASK5         | 5   | R/W | Interrupt mask bit 5. A logic-high enables the IMAX_FLT interrupts. A logic-low disables the IMAX_FLT interrupts. |

| MASK4         | 4   | R/W | Interrupt mask bit 4. A logic-high enables the CL_END interrupts. A logic-low disables the CL_END interrupts.     |

| MASK3         | 3   | R/W | Interrupt mask bit 3. A logic-high enables the DET_END interrupts. A logic-low disables the DET_END interrupts.   |

| MASK2         | 2   | R/W | Interrupt mask bit 2. A logic-high enables the LD_DISC interrupts. A logic-low disables the LD_DISC interrupts.   |

| MASK1         | 1   | R/W | Interrupt mask bit 1. A logic-high enables the PG_INT interrupts. A logic-low disables the PG_INT interrupts.     |

| MASK0         | 0   | R/W | Interrupt mask bit 0. A logic-high enables the PEN_INT interrupts. A logic-low disables the PEN_INT interrupts.   |

# Power over Ethernet用、ハイパワー クワッド、モノリシック、PSEコントローラ