EVALUATION KIT

AVAILABLE**MAXIM**

# 超低電力、高ダイナミック性能、 40Mspsアナログフロントエンド

**MAX5865**

## 概要

MAX5865は超低電力、高集積アナログフロントエンドで、携帯電話やPDA、WLAN、3Gワイヤレス端末などのポータブル通信機器に最適です。MAX5865は8ビット受信ADCと10ビット送信DACを2台ずつ内蔵しており、超低電力で最高のダイナミック性能を発揮します。ADCのアナログI-Q入力アンプは完全差動化されており、入力可能なフルスケール信号は $1V_{P-P}$ です。I-Qチャネル位相マッチングの標準値は $\pm 0.2^\circ$ であり、標準振幅マッチングは $\pm 0.05\text{dB}$ です。ADCは、 $f_{IN} = 5.5\text{MHz}$ 、 $f_{CLK} = 40\text{MHz}$ で、SINADが48.4dB、スプリアスフリーダイナミックレンジ(SFDR)が70dBcです。DACのアナログI-Q出力は完全差動化されており、フルスケール出力が $\pm 400\text{mV}$ 、コモンモードレベルが1.4Vです。I-Qチャネル位相マッチングの標準値は $\pm 0.15^\circ$ であり、標準利得マッチングは $\pm 0.05\text{dB}$ です。DACはまた、デュアル10ビット分解能を持ち、 $f_{OUT} = 2.2\text{MHz}$ 、 $f_{CLK} = 40\text{MHz}$ でSFDRが72dBc、SNRが57dBです。ADCとDACは同時動作と独立動作が可能で、周波数分割デュープレックス(FDD)モードと時分割デュープレックス(TDD)モードを実現することができます。パワーダウンモードとトランシーバモードもあり、3線式シリアルインターフェースでこれらの動作を制御します。標準動作電力は、 $f_{CLK} = 40\text{Msps}$ でADCとDACがトランシーバモードで動作している状態で $75.6\text{mW}$ です。MAX5865は、動作電圧と動作温度の全範囲にわたって安定な $1.024\text{V}$ 電圧リファレンスを内蔵しています。MAX5865は、 $+2.7\text{V} \sim +3.3\text{V}$ のアナログ電源やロジックコンパティビリティを持つ $+1.8\text{V} \sim +3.3\text{V}$ デジタルI/O用電源で動作します。自己消費電流はアイドルモードで $8.5\text{mA}$ 、シャットダウンモードで $1\mu\text{A}$ です。MAX5865は $-40^\circ\text{C} \sim +85^\circ\text{C}$ の拡張温度範囲での動作が保証され、48ピン薄型QFNパッケージで提供されます。

## アプリケーション

狭帯域/広帯域のCDMA端末とPDA

固定/モバイルのブロードバンドワイヤレスモジュール

3Gワイヤレス端末

## 型番

| PART       | TEMP RANGE                                        | PIN-PACKAGE                    |

|------------|---------------------------------------------------|--------------------------------|

| MAX5865ETM | $-40^\circ\text{C} \text{ to } +85^\circ\text{C}$ | 48 Thin QFN-EP*<br>(7mm x 7mm) |

| MAX5865E/D | $-40^\circ\text{C} \text{ to } +85^\circ\text{C}$ | Dice**                         |

\* EP = エクスポートドパッド

\*\* ダイスの仕様についてはお問い合わせください。

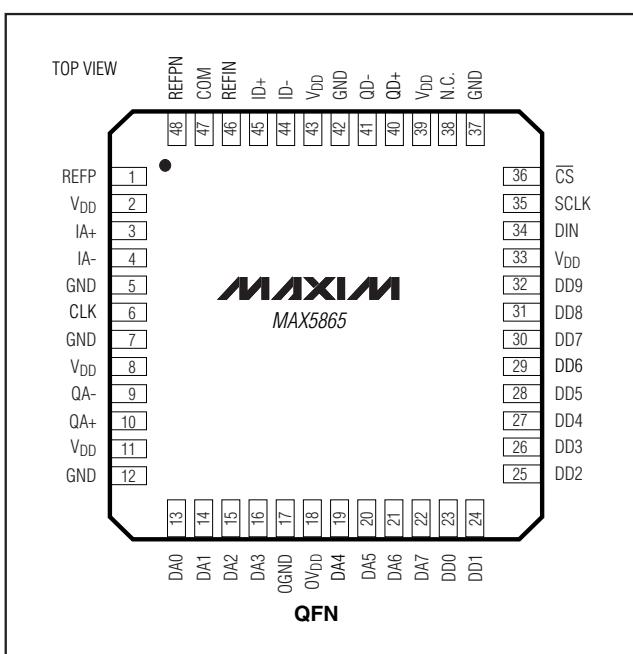

ピン配置はデータシートの最後に記載されています。

## 特長

- ◆ デュアル8ビットADCとデュアル10ビットDACを内蔵

- ◆ 超低電力

- 75.6mW( $f_{CLK} = 40\text{MHz}$ 時)(トランシーバモード)

- 64mW( $f_{CLK} = 22\text{MHz}$ 時)(トランシーバモード)

- 低消費電流アイドル/シャットダウンモード

- ◆ 卓越したダイナミック性能

- $f_{IN} = 5.5\text{MHz}$ で、48.4dB SINAD (ADC)

- $f_{OUT} = 2.2\text{MHz}$ で、70dB SFDR (DAC)

- ◆ 卓越した利得/位相マッチング

- $\pm 0.2^\circ$ 位相、 $\pm 0.05\text{dB}$ 利得( $f_{IN} = 5.5\text{MHz}$ 時)(ADC)

- ◆ 内部/外部リファレンスを選択可能

- ◆ ディジタル出力レベル (TTL/CMOSコンパチブル) :  $+1.8\text{V} \sim +3.3\text{V}$

- ◆ ADC/DAC用マルチプレクス型パラレルディジタル入出力

- ◆ 超小型の48ピンのThin QFNパッケージ (7mm x 7mm)

- ◆ 評価キットを提供(MAX5865EVKITを請求してください)

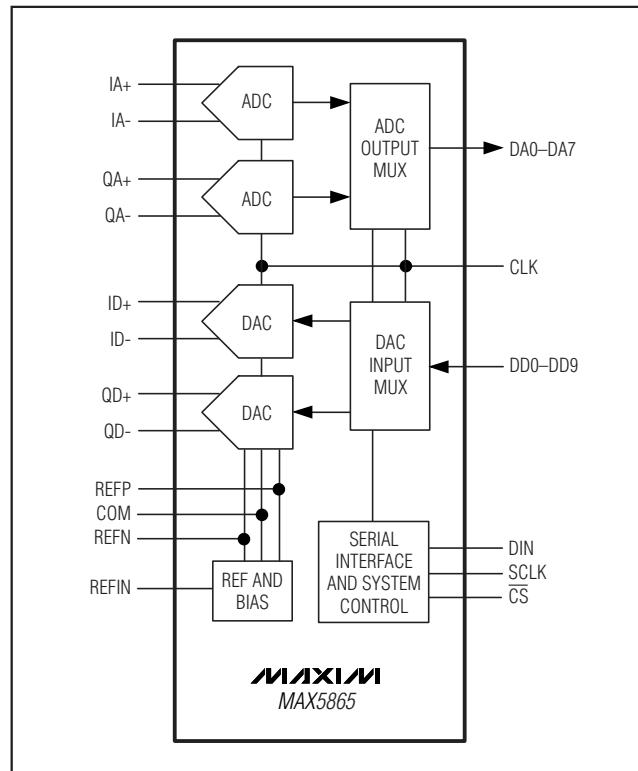

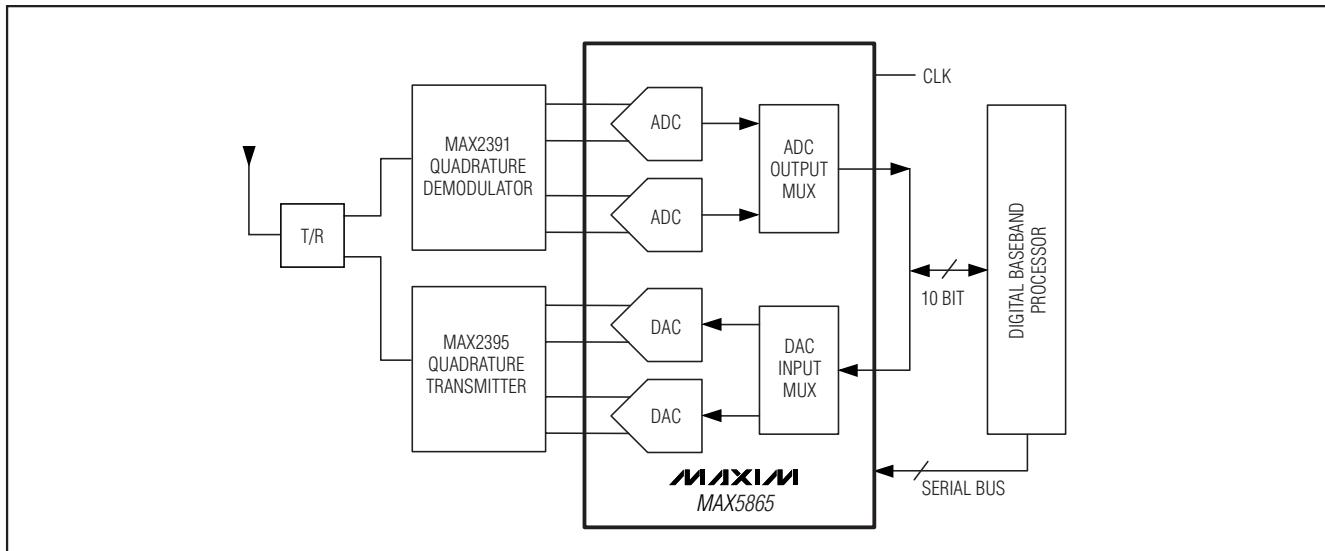

## ファンクションダイアグラム

**MAXIM**

Maxim Integrated Products 1

本データシートに記載された内容はMaxim Integrated Productsの公式な英語版データシートを翻訳したものです。翻訳により生じる相違及び誤りについては責任を負いかねます。正確な内容の把握には英語版データシートをご参照ください。

無料サンプル及び最新版データシートの入手には、マキシムのホームページをご利用ください。<http://japan.maxim-ic.com>

# 超低電力、高ダイナミック性能、 40Mspsアナログフロントエンド

## ABSOLUTE MAXIMUM RATINGS

|                                                                                                                                                                                  |                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| V <sub>DD</sub> to GND, OV <sub>DD</sub> to OGND                                                                                                                                 | -0.3V to +3.3V                     |

| GND to OGND                                                                                                                                                                      | -0.3V to +0.3V                     |

| I <sub>A+</sub> , I <sub>A-</sub> , Q <sub>A+</sub> , Q <sub>A-</sub> , I <sub>D+</sub> , I <sub>D-</sub> , Q <sub>D+</sub> , Q <sub>D-</sub> , REFP, REFN,<br>REFIN, COM to GND | -0.3V to (V <sub>DD</sub> + 0.3V)  |

| DD0–DD9, SCLK, DIN, CS, CLK,<br>DA0–DA7 to OGND                                                                                                                                  | -0.3V to (OV <sub>DD</sub> + 0.3V) |

|                                                                                                            |                 |

|------------------------------------------------------------------------------------------------------------|-----------------|

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)<br>48-Pin Thin QFN (derate 26.3mW/°C above<br>+70°C) | 2.1W            |

| Thermal Resistance θ <sub>JA</sub>                                                                         | +38°C/W         |

| Operating Temperature Range                                                                                | -40°C to +85°C  |

| Junction Temperature                                                                                       | +150°C          |

| Storage Temperature Range                                                                                  | -60°C to +150°C |

| Lead Temperature (soldering, 10s)                                                                          | +300°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

(V<sub>DD</sub> = 3V, OV<sub>DD</sub> = 1.8V, internal reference (1.024V), C<sub>L</sub> ≈ 10pF on all digital outputs, f<sub>CLK</sub> = 40MHz, ADC input amplitude = -0.5dBFS, DAC output amplitude = 0dBFS, differential ADC input, differential DAC output, C<sub>REFP</sub> = C<sub>REFN</sub> = C<sub>COM</sub> = 0.33μF, Xcvr mode, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                       | SYMBOL           | CONDITIONS                                                                                                                  | MIN  | TYP              | MAX | UNITS |

|---------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------|------|------------------|-----|-------|

| <b>POWER REQUIREMENTS</b>       |                  |                                                                                                                             |      |                  |     |       |

| Analog Supply Voltage           | V <sub>DD</sub>  |                                                                                                                             | 2.7  | 3.0              | 3.3 | V     |

| Output Supply Voltage           | OV <sub>DD</sub> |                                                                                                                             | 1.8  | OV <sub>DD</sub> |     | V     |

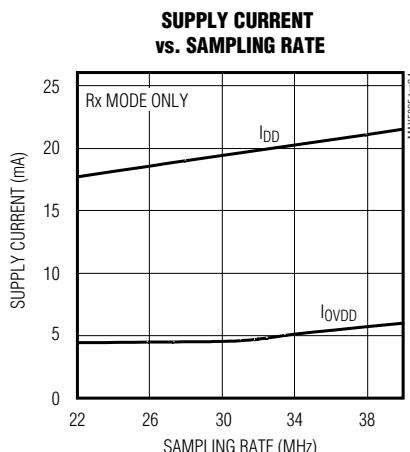

| V <sub>DD</sub> Supply Current  |                  | ADC operating mode, f <sub>IN</sub> = 5.5MHz, f <sub>CLK</sub> = 40MHz, DAC operating mode, f <sub>OUT</sub> = 2.2MHz       | 25.2 | 32               |     | mA    |

|                                 |                  | ADC operating mode (Rx), f <sub>IN</sub> = 5.5MHz, f <sub>CLK</sub> = 40MHz, DAC digital inputs at zero or OV <sub>DD</sub> | 21   |                  |     |       |

|                                 |                  | DAC operating mode (Tx), f <sub>OUT</sub> = 2.2MHz, f <sub>CLK</sub> = 40MHz, ADC off                                       | 12.8 |                  |     |       |

|                                 |                  | Standby mode, DAC digital inputs and CLK at zero or OV <sub>DD</sub>                                                        | 2.0  |                  |     |       |

|                                 |                  | Idle mode, DAC digital inputs at zero or OV <sub>DD</sub> , f <sub>CLK</sub> = 40MHz                                        | 11   |                  |     |       |

|                                 |                  | Shutdown mode, digital inputs and CLK at zero or OV <sub>DD</sub> , CS = OV <sub>DD</sub>                                   | 1    |                  |     | μA    |

| OV <sub>DD</sub> Supply Current |                  | ADC operating mode, f <sub>IN</sub> = 5.5MHz, f <sub>CLK</sub> = 40Msps, DAC operating mode, f <sub>OUT</sub> = 2.2MHz      | 3.8  |                  |     | mA    |

|                                 |                  | Idle mode, DAC digital inputs at zero or OV <sub>DD</sub> , f <sub>CLK</sub> = 40MHz                                        | 37.4 |                  |     | μA    |

|                                 |                  | Shutdown mode, DAC digital inputs and CLK at zero or OV <sub>DD</sub> , CS = OV <sub>DD</sub>                               | 1    |                  |     |       |

# 超低電力、高ダイナミック性能、 40Mspsアナログフロントエンド

MAX5865

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{DD} = 3V$ ,  $OV_{DD} = 1.8V$ , internal reference ( $1.024V$ ),  $C_L \approx 10pF$  on all digital outputs,  $f_{CLK} = 40MHz$ , ADC input amplitude =  $-0.5dBFS$ , DAC output amplitude =  $0dBFS$ , differential ADC input, differential DAC output,  $C_{REFP} = C_{REFN} = C_{COM} = 0.33\mu F$ , Xcvr mode, unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ , unless otherwise noted.) (Note 1)

| PARAMETER                                   | SYMBOL           | CONDITIONS                                                      | MIN  | TYP          | MAX        | UNITS           |

|---------------------------------------------|------------------|-----------------------------------------------------------------|------|--------------|------------|-----------------|

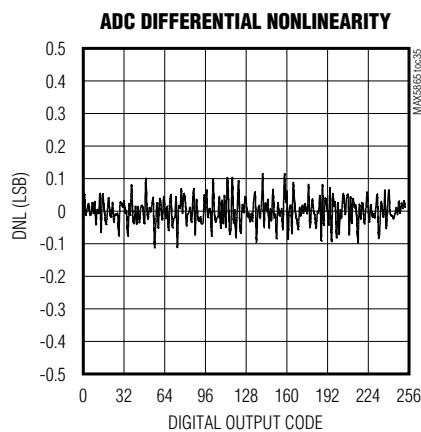

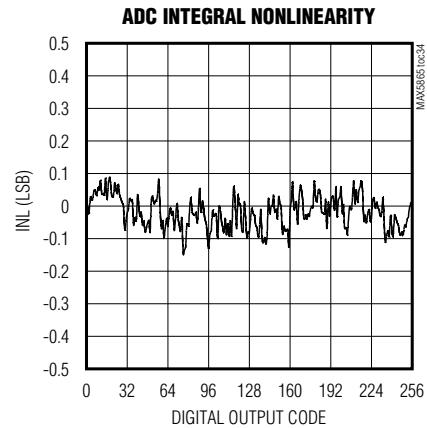

| <b>ADC DC ACCURACY</b>                      |                  |                                                                 |      |              |            |                 |

| Resolution                                  |                  |                                                                 | 8    |              |            | Bits            |

| Integral Nonlinearity                       | INL              |                                                                 |      | $\pm 0.15$   |            | LSB             |

| Differential Nonlinearity                   | DNL              | No missing codes over temperature                               |      | $\pm 0.15$   |            | LSB             |

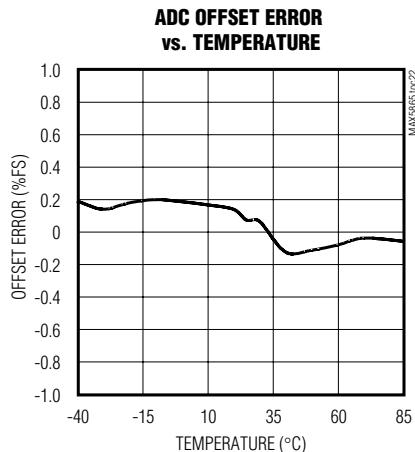

| Offset Error                                |                  | Residual DC offset error                                        |      | $\pm 0.22$   | $\pm 5$    | %FS             |

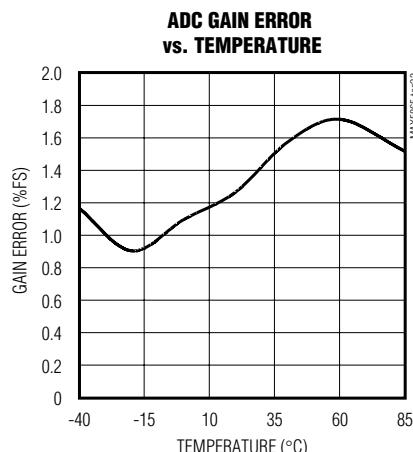

| Gain Error                                  |                  | Includes reference error                                        |      | $\pm 0.48$   | $\pm 5$    | %FS             |

| DC Gain Matching                            |                  |                                                                 |      | $\pm 0.03$   | $\pm 0.25$ | dB              |

| Offset Matching                             |                  |                                                                 |      | $\pm 3$      |            | LSB             |

| Gain Temperature Coefficient                |                  |                                                                 |      | $\pm 42$     |            | ppm/ $^\circ C$ |

| Power-Supply Rejection                      | PSRR             | Offset error ( $V_{DD} \pm 5\%$ )                               |      | $\pm 0.2$    |            | LSB             |

|                                             |                  | Gain error ( $V_{DD} \pm 5\%$ )                                 |      | $\pm 0.07$   |            |                 |

| <b>ADC ANALOG INPUT</b>                     |                  |                                                                 |      |              |            |                 |

| Input Differential Range                    | VID              | Differential or single-ended inputs                             |      | $\pm 0.512$  |            | V               |

| Input Common-Mode Voltage Range             |                  |                                                                 |      | $V_{DD} / 2$ |            | V               |

| Input Impedance                             | R <sub>IN</sub>  | Switched capacitor load                                         |      | 120          |            | k $\Omega$      |

|                                             | C <sub>IN</sub>  |                                                                 |      | 5            |            | pF              |

| <b>ADC CONVERSION RATE</b>                  |                  |                                                                 |      |              |            |                 |

| Maximum Clock Frequency                     | f <sub>CLK</sub> | (Note 2)                                                        |      | 40           |            | MHz             |

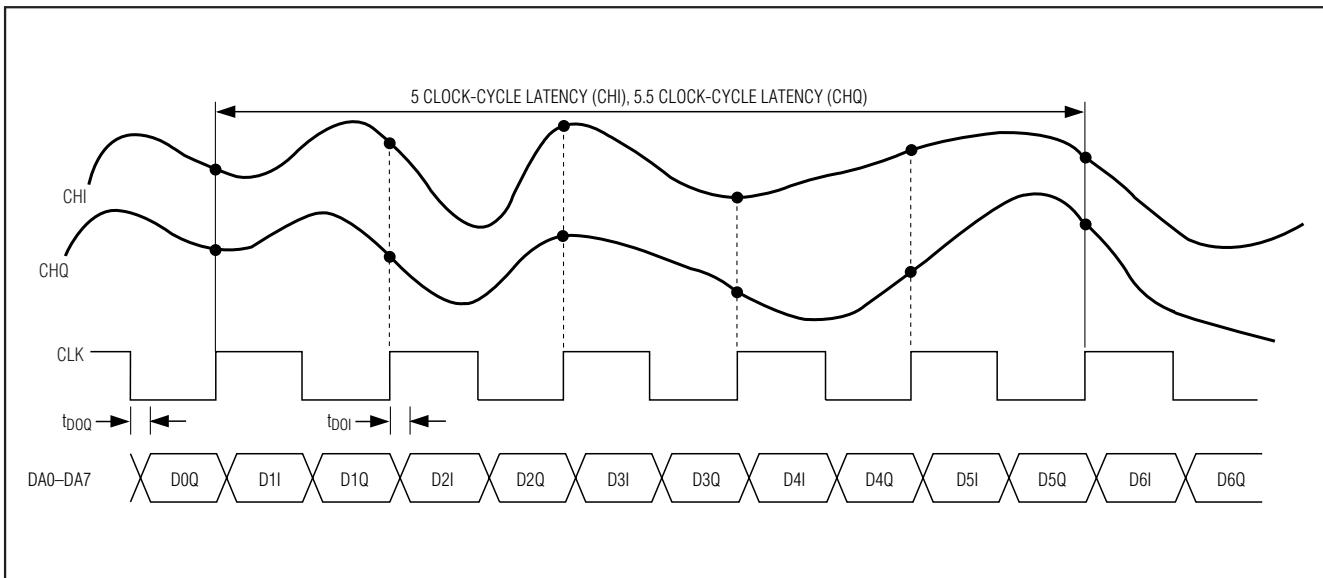

| Data Latency                                |                  | Channel I                                                       |      | 5            |            | Clock cycles    |

|                                             |                  | Channel Q                                                       |      | 5.5          |            |                 |

| <b>ADC DYNAMIC CHARACTERISTICS</b> (Note 3) |                  |                                                                 |      |              |            |                 |

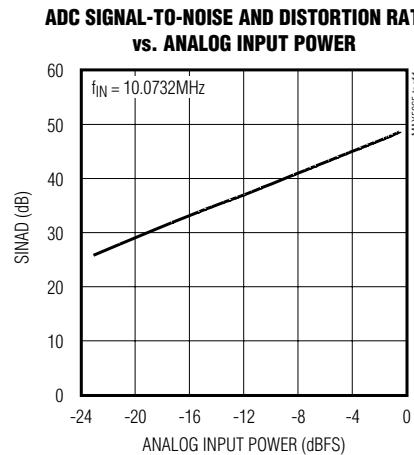

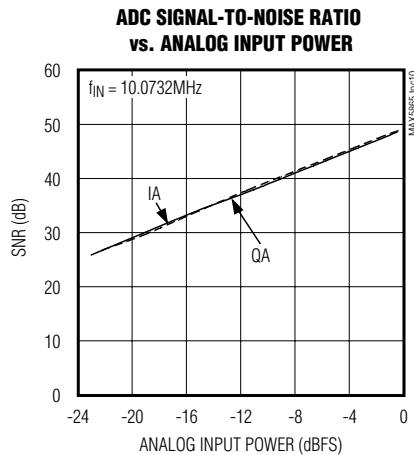

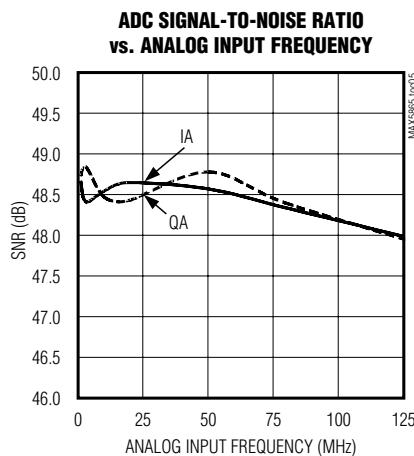

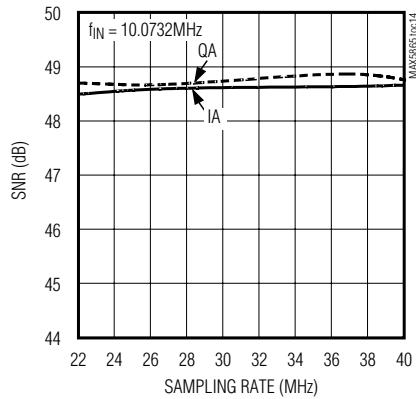

| Signal-to-Noise Ratio                       | SNR              | f <sub>IN</sub> = 5.5MHz                                        | 47   | 48.5         |            | dB              |

|                                             |                  | f <sub>IN</sub> = 20MHz                                         |      | 48.2         |            |                 |

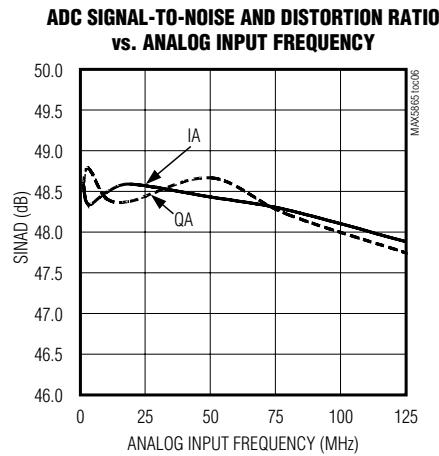

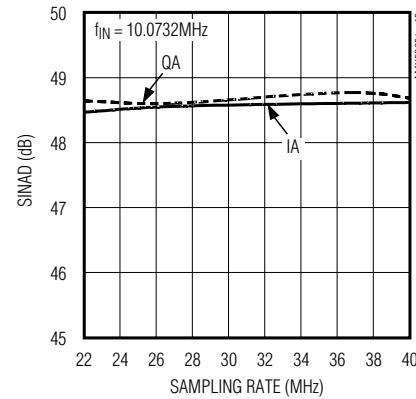

| Signal-to-Noise and Distortion Ratio        | SINAD            | f <sub>IN</sub> = 5.5MHz                                        | 46.5 | 48.4         |            | dB              |

|                                             |                  | f <sub>IN</sub> = 20MHz                                         |      | 48.2         |            |                 |

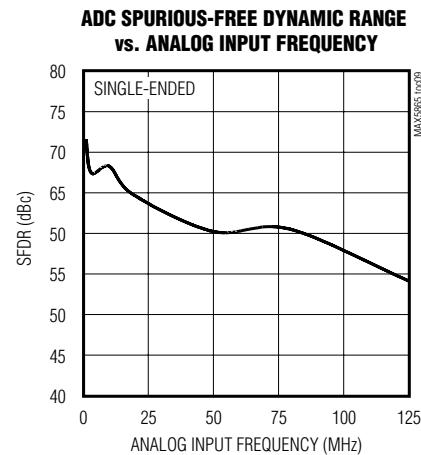

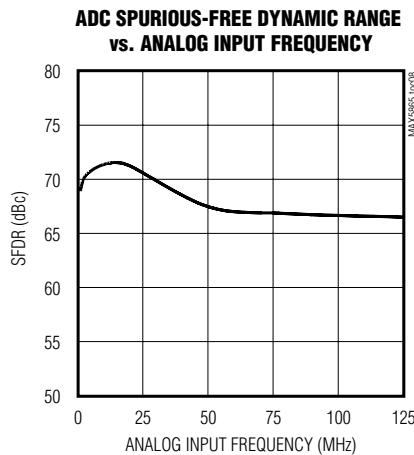

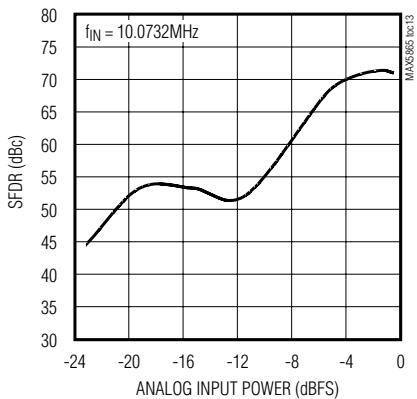

| Spurious-Free Dynamic Range                 | SFDR             | f <sub>IN</sub> = 5.5MHz                                        | 58   | 70           |            | dBc             |

|                                             |                  | f <sub>IN</sub> = 20MHz                                         |      | 70           |            |                 |

| Third-Harmonic Distortion                   | HD3              | f <sub>IN</sub> = 5.5MHz                                        |      | -75.4        |            | dBc             |

|                                             |                  | f <sub>IN</sub> = 20MHz                                         |      | -75          |            |                 |

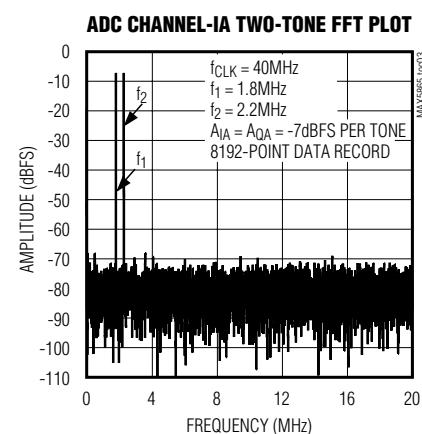

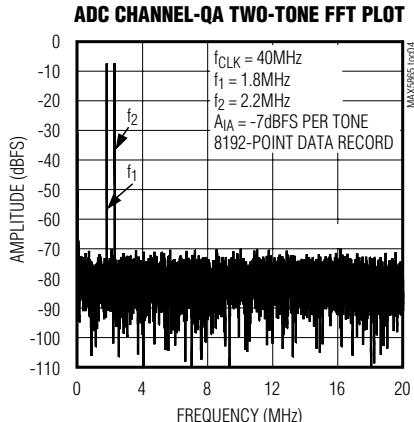

| Intermodulation Distortion                  | IMD              | f <sub>1</sub> = 2MHz, -7dBFS; f <sub>2</sub> = 2.01MHz, -7dBFS |      | -66          |            | dBc             |

| Third-Order Intermodulation Distortion      | IM3              | f <sub>1</sub> = 2MHz, -7dBFS; f <sub>2</sub> = 2.01MHz, -7dBFS |      | -70          |            | dBc             |

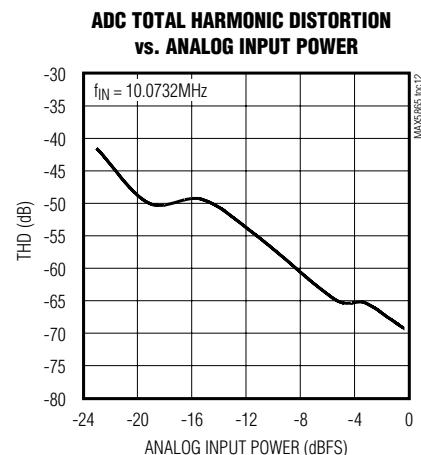

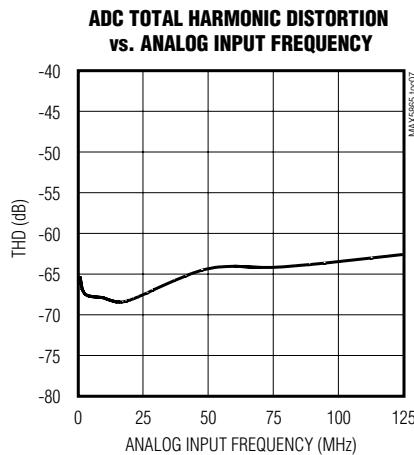

| Total Harmonic Distortion                   | THD              | f <sub>IN</sub> = 5.5MHz                                        |      | -71          | -57        | dBc             |

|                                             |                  | f <sub>IN</sub> = 20MHz                                         |      | -70          |            |                 |

# 超低電力、高ダイナミック性能、 40Mspsアナログフロントエンド

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{DD} = 3V$ ,  $OV_{DD} = 1.8V$ , internal reference (1.024V),  $C_L \approx 10pF$  on all digital outputs,  $f_{CLK} = 40MHz$ , ADC input amplitude = -0.5dBFS, DAC output amplitude = 0dBFS, differential ADC input, differential DAC output,  $CREFP = CREFN = CCOM = 0.33\mu F$ , Xcvr mode, unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ , unless otherwise noted.) (Note 1)

|                         |     |                        |     |             |

|-------------------------|-----|------------------------|-----|-------------|

| Large-Signal Bandwidth  | FBW | $A_{IN} = -0.5dBFS$    | 440 | MHz         |

| Aperture Delay          |     |                        | 3.3 | ns          |

| Aperture Jitter         |     |                        | 2.7 | $\mu s RMS$ |

| Overdrive Recovery Time |     | 1.5 × full-scale input | 2   | ns          |

### ADC INTERCHANNEL CHARACTERISTICS

|                     |  |                                                                         |            |         |

|---------------------|--|-------------------------------------------------------------------------|------------|---------|

| Crosstalk Rejection |  | $f_{INX} = 5.5MHz$ at -0.5dBFS, $f_{INY} = 0.3MHz$ at -0.5dBFS (Note 5) | -75        | dB      |

| Amplitude Matching  |  | $f_{IN} = 5.5MHz$ at -0.5dBFS (Note 6)                                  | $\pm 0.05$ | dB      |

| Phase Matching      |  | $f_{IN} = 5.5MHz$ at -0.5dBFS (Note 6)                                  | $\pm 0.2$  | Degrees |

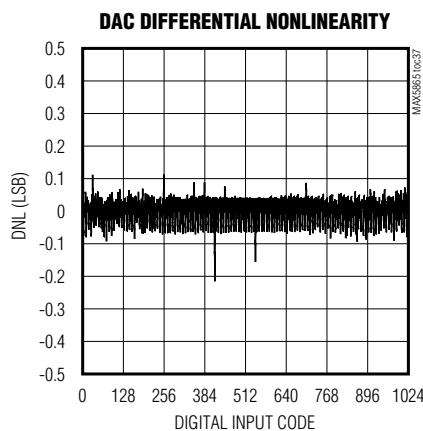

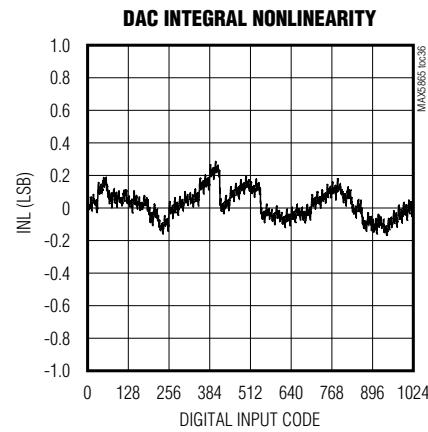

### DAC DC ACCURACY

|                           |     |                         |           |      |     |

|---------------------------|-----|-------------------------|-----------|------|-----|

| Resolution                | N   |                         | 10        | Bits |     |

| Integral Nonlinearity     | INL |                         | $\pm 1$   | LSB  |     |

| Differential Nonlinearity | DNL | Guaranteed monotonic    | $\pm 0.5$ | LSB  |     |

| Zero-Scale Error          |     | Residual DC offset      | $\pm 3$   | LSB  |     |

| Full-Scale Error          |     | Include reference error | -35       | +35  | LSB |

### DAC DYNAMIC PERFORMANCE

|                                        |      |                                                         |        |        |     |

|----------------------------------------|------|---------------------------------------------------------|--------|--------|-----|

| DAC Conversion Rate                    |      | (Note 2)                                                | 40     | Msps   |     |

| Noise over Nyquist                     | ND   | $f_{OUT} = 2.2MHz$ , $f_{CLK} = 40MHz$                  | -130.6 | dBc/Hz |     |

| Output-of-Band Noise Power Density     | NO   | $f_{OUT} = 1.2MHz$ , $f_{CLK} = 22MHz$ , offset = 10MHz | -130.9 | dBc/Hz |     |

| Glitch Impulse                         |      |                                                         | 10     | pVs    |     |

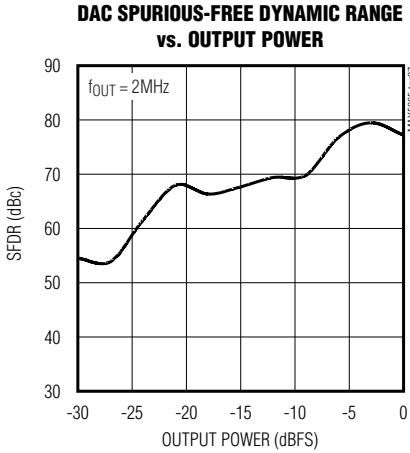

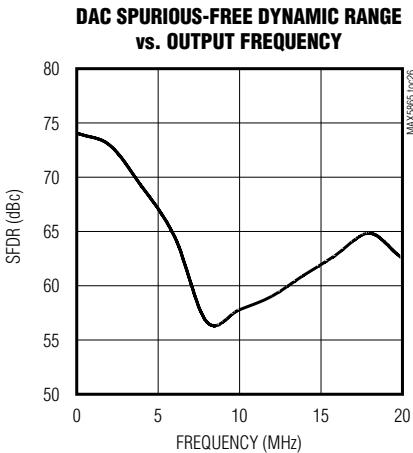

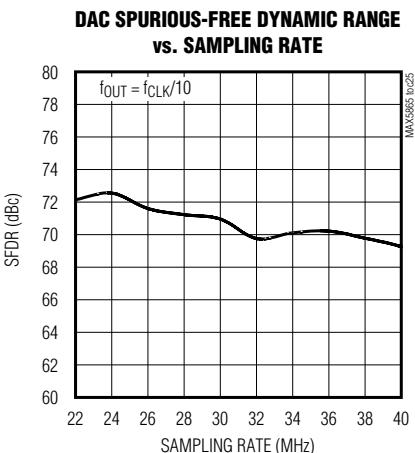

| Spurious-Free Dynamic Range            | SFDR | $f_{CLK} = 40MHz$                                       | 59     | 72.3   | dBc |

|                                        |      | $f_{CLK} = 22MHz$                                       |        | 73.5   |     |

| Total Harmonic Distortion (to Nyquist) | THD  | $f_{CLK} = 40MHz$ , $f_{OUT} = 2.2MHz$                  | -70    | -58.5  | dB  |

| Signal-to-Noise Ratio (to Nyquist)     | SNR  | $f_{CLK} = 40MHz$ , $f_{OUT} = 2.2MHz$                  | 57     |        | dB  |

### DAC INTERCHANNEL CHARACTERISTICS

|                                    |  |                                                 |            |         |

|------------------------------------|--|-------------------------------------------------|------------|---------|

| DAC-to-DAC Output Isolation        |  | $f_{OUTX}, Y = 2.2MHz$ , $f_{OUTX}, Y = 2.0MHz$ | 80         | dB      |

| Gain Mismatch Between DAC Outputs  |  | $f_{OUT} = 2.2MHz$ , $f_{CLK} = 40MHz$          | 0.05       | dB      |

| Phase Mismatch Between DAC Outputs |  | $f_{OUT} = 2.2MHz$ , $f_{CLK} = 40MHz$          | $\pm 0.15$ | Degrees |

# 超低電力、高ダイナミック性能、 40Mspsアナログフロントエンド

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{DD} = 3V$ ,  $OV_{DD} = 1.8V$ , internal reference ( $1.024V$ ),  $C_L \approx 10pF$  on all digital outputs,  $f_{CLK} = 40MHz$ , ADC input amplitude =  $-0.5dBFS$ , DAC output amplitude =  $0dBFS$ , differential ADC input, differential DAC output,  $C_{REFP} = C_{REFN} = C_{COM} = 0.33\mu F$ , Xcvr mode, unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ , unless otherwise noted.) (Note 1)

| PARAMETER                                                         | SYMBOL        | CONDITIONS                                                                                | MIN      | TYP       | MAX | UNITS   |

|-------------------------------------------------------------------|---------------|-------------------------------------------------------------------------------------------|----------|-----------|-----|---------|

| <b>DAC ANALOG OUTPUT</b>                                          |               |                                                                                           |          |           |     |         |

| Full-Scale Output Voltage                                         | $V_{FS}$      |                                                                                           |          | $\pm 400$ |     | mV      |

| Output Common-Mode Range                                          |               |                                                                                           | 1.29     | 1.5       |     | V       |

| <b>ADC-DAC INTERCHANNEL CHARACTERISTICS</b>                       |               |                                                                                           |          |           |     |         |

| ADC-DAC Isolation                                                 |               | ADC $f_{INI} = f_{INQ} = 5.5MHz$ , DAC $f_{OUTI} = f_{OUTQ} = 2.2MHz$ , $f_{CLK} = 40MHz$ |          | 75        |     | dB      |

| <b>ADC-DAC TIMING CHARACTERISTICS</b>                             |               |                                                                                           |          |           |     |         |

| CLK Rise to I-ADC Channel-I Output Data Valid                     | $t_{DOI}$     | Figure 3 (Note 4)                                                                         | 7.4      | 9         |     | ns      |

| CLK Fall to Q-ADC Channel-Q Output Data Valid                     | $t_{DOQ}$     | Figure 3 (Note 4)                                                                         | 6.9      | 9         |     | ns      |

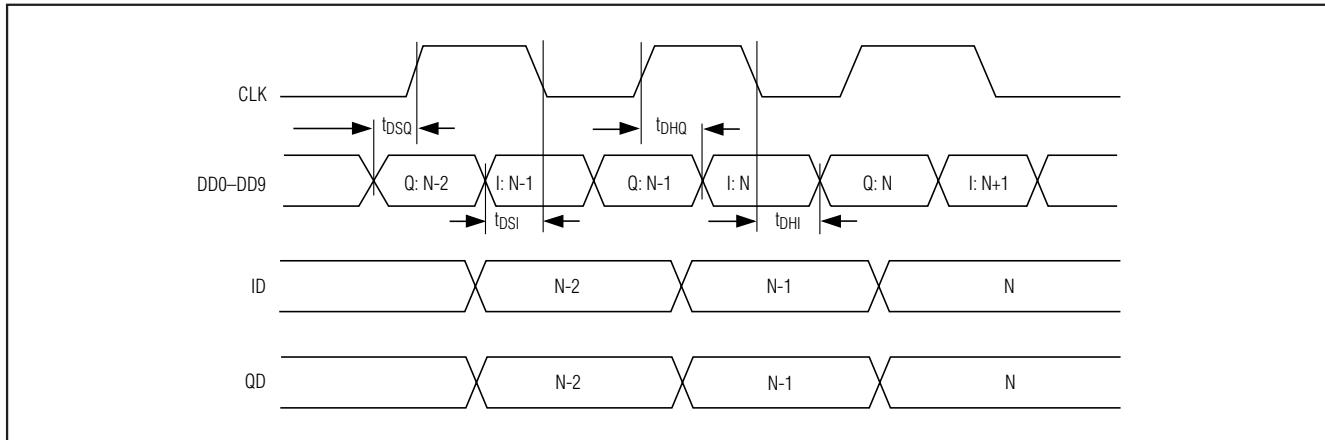

| I-DAC Data to CLK Fall Setup Time                                 | $t_{DSI}$     | Figure 4 (Note 4)                                                                         | 10       |           |     | ns      |

| Q-DAC Data to CLK Rise Setup Time                                 | $t_{DSQ}$     | Figure 4 (Note 4)                                                                         | 10       |           |     | ns      |

| CLK Fall to I-DAC Data Hold Time                                  | $t_{DHI}$     | Figure 4 (Note 4)                                                                         | 0        |           |     | ns      |

| CLK Rise to Q-DAC Data Hold Time                                  | $t_{DHQ}$     | Figure 4 (Note 4)                                                                         | 0        |           |     | ns      |

| Clock Duty Cycle                                                  |               |                                                                                           | 50       |           |     | %       |

| CLK Duty-Cycle Variation                                          |               |                                                                                           | $\pm 15$ |           |     | %       |

| Digital Output Rise/Fall Time                                     |               | 20% to 80%                                                                                | 2.6      |           |     | ns      |

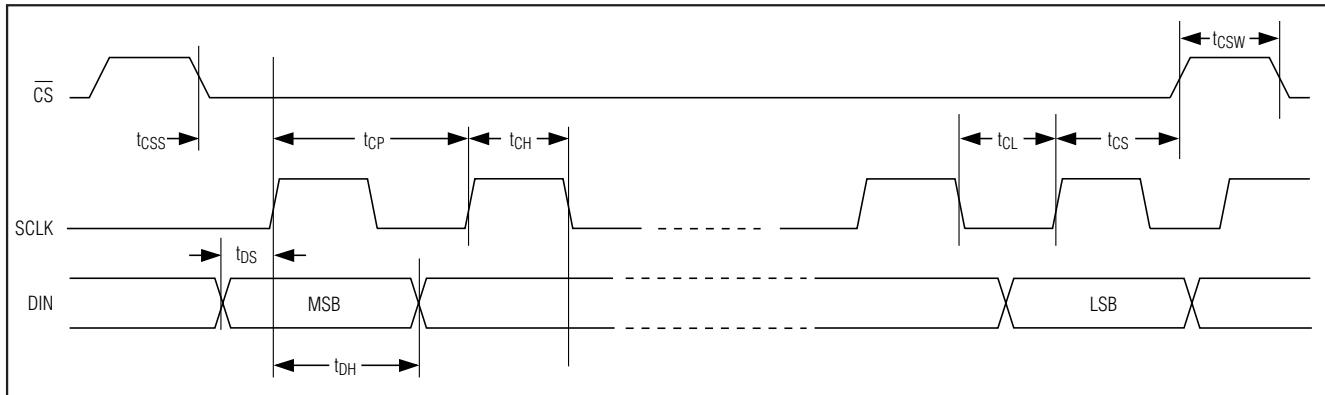

| <b>SERIAL INTERFACE TIMING CHARACTERISTICS</b>                    |               |                                                                                           |          |           |     |         |

| Falling Edge of $\overline{CS}$ to Rising Edge of First SCLK Time | $t_{CSS}$     | Figure 5 (Note 4)                                                                         | 10       |           |     | ns      |

| DIN to SCLK Setup Time                                            | $t_{DS}$      | Figure 5 (Note 4)                                                                         | 10       |           |     | ns      |

| DIN to SCLK Hold Time                                             | $t_{DH}$      | Figure 5 (Note 4)                                                                         | 0        |           |     | ns      |

| SCLK Pulse Width High                                             | $t_{CH}$      | Figure 5 (Note 4)                                                                         | 25       |           |     | ns      |

| SCLK Pulse Width Low                                              | $t_{CL}$      | Figure 5 (Note 4)                                                                         | 25       |           |     | ns      |

| SCLK Period                                                       | $t_{CP}$      | Figure 5 (Note 4)                                                                         | 50       |           |     | ns      |

| SCLK to $\overline{CS}$ Setup Time                                | $t_{CS}$      | Figure 5 (Note 4)                                                                         | 0        |           |     | ns      |

| $\overline{CS}$ High Pulse Width                                  | $t_{CSW}$     | Figure 5 (Note 4)                                                                         | 80       |           |     | ns      |

| <b>MODE RECOVERY TIMING CHARACTERISTICS</b>                       |               |                                                                                           |          |           |     |         |

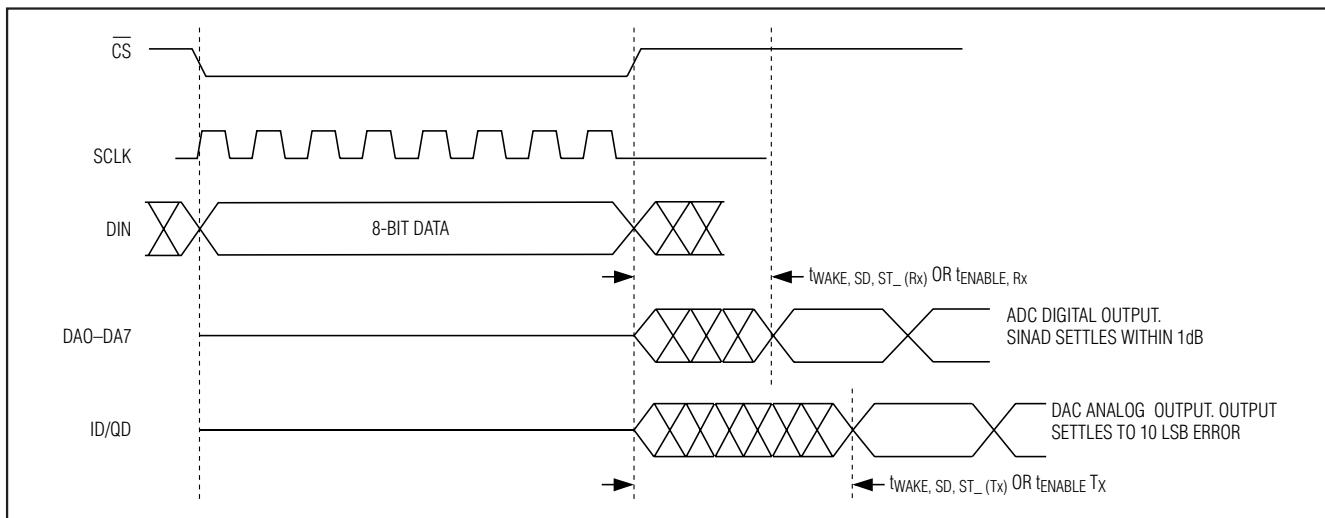

| Shutdown Wake-Up Time                                             | $t_{WAKE,SD}$ | From shutdown to Rx mode, Figure 6, ADC settles to within 1dB                             |          | 20        |     | $\mu s$ |

|                                                                   |               | From shutdown to Tx mode, Figure 6, DAC settles to within 10 LSB error                    |          | 40        |     |         |

MAX5865

# 超低電力、高ダイナミック性能、 40MspSアナログフロントエンド

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{DD} = 3V$ ,  $OV_{DD} = 1.8V$ , internal reference (1.024V),  $C_L \approx 10pF$  on all digital outputs,  $f_{CLK} = 40MHz$ , ADC input amplitude = -0.5dBFS, DAC output amplitude = 0dBFS, differential ADC input, differential DAC output,  $C_{REFP} = C_{REFN} = C_{COM} = 0.33\mu F$ , Xcvr mode, unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ , unless otherwise noted.) (Note 1)

| PARAMETER                                                                                                                  | SYMBOL           | CONDITIONS                                                                                   | MIN                    | TYP                    | MAX                    | UNITS           |

|----------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------|------------------------|------------------------|------------------------|-----------------|

| Idle Wake-Up Time (with CLK)                                                                                               | $t_{WAKE,ST0}$   | From idle to Rx mode with CLK present during idle, Figure 6, ADC settles to within 1dB SINAD |                        | 10                     |                        | $\mu s$         |

|                                                                                                                            |                  | From idle to Tx mode with CLK present during idle, Figure 6, DAC settles to 10 LSB error     |                        | 10                     |                        |                 |

| Standby Wake-Up Time                                                                                                       | $t_{WAKE,ST1}$   | From standby to Rx mode, Figure 6, ADC settles to within 1dB SINAD                           |                        | 10                     |                        | $\mu s$         |

|                                                                                                                            |                  | From standby to Tx mode, Figure 6, DAC settles to 10 LSB error                               |                        | 40                     |                        |                 |

| Enable Time from Xcvr or Tx to Rx                                                                                          | $t_{ENABLE, Rx}$ | ADC settles to within 1dB SINAD                                                              |                        | 10                     |                        | $\mu s$         |

| Enable Time from Xcvr or Rx to Tx                                                                                          | $t_{ENABLE, Tx}$ | DAC settles to 10 LSB error                                                                  |                        | 10                     |                        | $\mu s$         |

| <b>INTERNAL REFERENCE</b> ( $REFIN = V_{DD}$ . $V_{REFP}$ , $V_{REFN}$ and $V_{COM}$ are generated internally.)            |                  |                                                                                              |                        |                        |                        |                 |

| Positive Reference                                                                                                         |                  | $V_{REFP} - V_{COM}$                                                                         |                        | 0.256                  |                        | V               |

| Negative Reference                                                                                                         |                  | $V_{REFN} - V_{COM}$                                                                         |                        | -0.256                 |                        | V               |

| Common-Mode Output Voltage                                                                                                 | $V_{COM}$        |                                                                                              | $V_{DD} / 2$<br>- 0.15 | $V_{DD} / 2$<br>+ 0.15 | $V_{DD} / 2$<br>+ 0.15 | V               |

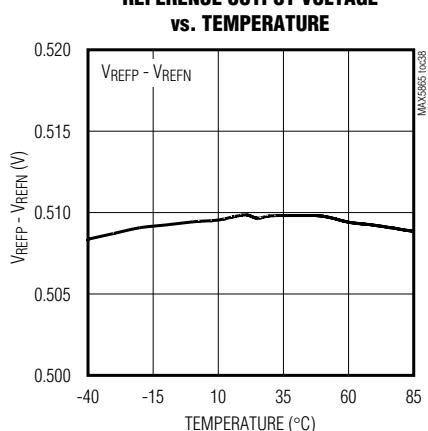

| Differential Reference Output                                                                                              | $V_{REF}$        | $V_{REFP} - V_{REFN}$                                                                        | +0.49                  | +0.512                 | +0.534                 | V               |

| Differential Reference Temperature Coefficient                                                                             | $REFTC$          |                                                                                              |                        | $\pm 30$               |                        | ppm/ $^\circ C$ |

| Maximum REFP/REFN/COM Source Current                                                                                       | $I_{SOURCE}$     |                                                                                              |                        | 2                      |                        | mA              |

| Maximum REFP/REFN/COM Sink Current                                                                                         | $I_{SINK}$       |                                                                                              |                        | 2                      |                        | mA              |

| <b>BUFFERED EXTERNAL REFERENCE</b> ( $REFIN = 1.024V$ . $V_{REFP}$ , $V_{REFN}$ , and $V_{COM}$ are generated internally.) |                  |                                                                                              |                        |                        |                        |                 |

| Reference Input                                                                                                            | $V_{REFIN}$      |                                                                                              |                        | 1.024                  |                        | V               |

| Differential Reference Output                                                                                              | $V_{DIFF}$       | $V_{REFP} - V_{REFN}$                                                                        |                        | 0.512                  |                        | V               |

| Common-Mode Output Voltage                                                                                                 | $V_{COM}$        |                                                                                              |                        | $V_{DD} / 2$           |                        | V               |

| Maximum REFP/REFN/COM Source Current                                                                                       | $I_{SOURCE}$     |                                                                                              |                        | 2                      |                        | mA              |

| Maximum REFP/REFN/COM Sink Current                                                                                         | $I_{SINK}$       |                                                                                              |                        | 2                      |                        | mA              |

| REFIN Input Resistance                                                                                                     |                  |                                                                                              |                        | >500                   |                        | k $\Omega$      |

| REFIN Input Current                                                                                                        |                  |                                                                                              |                        | -0.7                   |                        | $\mu A$         |

| <b>DIGITAL INPUTS (CLK, SCLK, DIN, CS, DD0–DD9)</b>                                                                        |                  |                                                                                              |                        |                        |                        |                 |

| Input High Threshold                                                                                                       | $V_{IH}$         | DD0–DD9, CLK, SCLK, DIN, $\overline{CS}$                                                     | 0.7 x $OV_{DD}$        |                        |                        | V               |

# 超低電力、高ダイナミック性能、 40MspSアナログフロントエンド

MAX5865

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{DD} = 3V$ ,  $OV_{DD} = 1.8V$ , internal reference (1.024V),  $C_L \approx 10\text{pF}$  on all digital outputs,  $f_{CLK} = 40\text{MHz}$ , ADC input amplitude = -0.5dBFS, DAC output amplitude = 0dBFS, differential ADC input, differential DAC output,  $C_{REFP} = C_{REFN} = C_{COM} = 0.33\mu\text{F}$ , Xcvr mode, unless otherwise noted. Typical values are at  $T_A = +25^\circ\text{C}$ , unless otherwise noted.) (Note 1)

| PARAMETER                        | SYMBOL     | CONDITIONS                                                   | MIN             | TYP             | MAX | UNITS         |

|----------------------------------|------------|--------------------------------------------------------------|-----------------|-----------------|-----|---------------|

| Input Low Threshold              | $V_{INL}$  | DD0–DD9, CLK, SCLK, DIN, $\overline{CS}$                     |                 | 0.3 x $OV_{DD}$ |     | V             |

| Input Leakage                    | $DI_{IN}$  | DD0–DD9, CLK, SCLK, DIN, $\overline{CS} = OGND$ or $OV_{DD}$ |                 | $\pm 5$         |     | $\mu\text{A}$ |

| Input Capacitance                | $DC_{IN}$  |                                                              | 5               |                 |     | pF            |

| <b>DIGITAL OUTPUTS (DA0–DA7)</b> |            |                                                              |                 |                 |     |               |

| Output Voltage Low               | $V_{OL}$   | $I_{SINK} = 200\mu\text{A}$                                  |                 | 0.2 x $OV_{DD}$ |     | V             |

| Output Voltage High              | $V_{OH}$   | $I_{SOURCE} = 200\mu\text{A}$                                | 0.8 x $OV_{DD}$ |                 |     | V             |

| Tri-State Leakage Current        | $I_{LEAK}$ |                                                              |                 | $\pm 5$         |     | $\mu\text{A}$ |

| Tri-State Output Capacitance     | $C_{OUT}$  |                                                              | 5               |                 |     | pF            |

**Note 1:** Specifications from  $T_A = +25^\circ\text{C}$  to  $+85^\circ\text{C}$  are guaranteed by product tests. Specifications from  $T_A = +25^\circ\text{C}$  to  $-40^\circ\text{C}$  are guaranteed by design and characterization.

**Note 2:** The minimum clock frequency for the MAX5865 is 22MHz.

**Note 3:** SNR, SINAD, SFDR, HD3, and THD are based on a differential analog input voltage of -0.5dBFS referenced to the amplitude of the digital outputs. SINAD and THD are calculated using HD2 through HD6.

**Note 4:** Guaranteed by design and characterization.

**Note 5:** Crosstalk rejection is measured by applying a high-frequency test tone to one channel and a low-frequency tone to the second channel. FFTs are performed on each channel. The parameter is specified as the power ratio of the first and second channel FFT test tone bins.

**Note 6:** Amplitude/phase matching is measured by applying the same signal to each channel, and comparing the magnitude and phase of the fundamental bin on the calculated FFT.

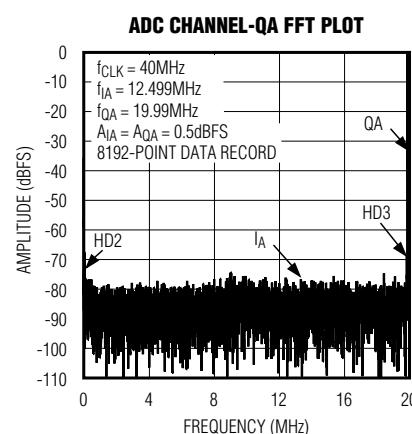

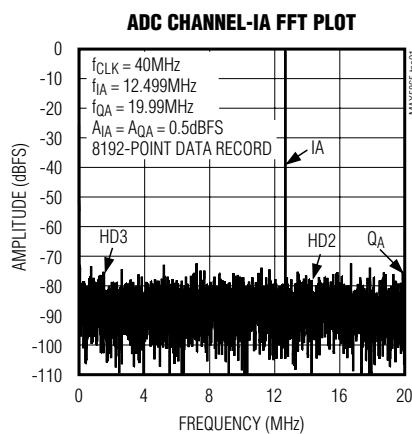

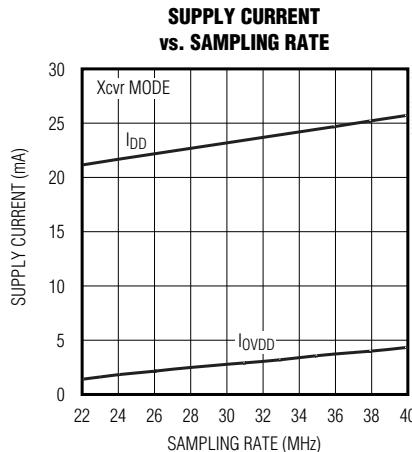

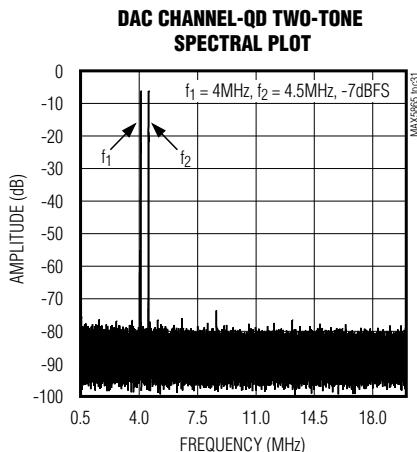

## 標準動作特性

( $V_{DD} = DV_{DD} = 3V$ ,  $OV_{DD} = 1.8V$ , internal reference (1.024V),  $C_L \approx 10\text{pF}$  on all digital outputs,  $f_{CLK} = 40\text{MHz}$  50% duty cycle, ADC input amplitude = -0.5dBFS, DAC output amplitude = 0dBFS, differential ADC input, differential DAC output,  $C_{REFP} = C_{REFN} = C_{COM} = 0.33\mu\text{F}$ , Xcvr mode,  $T_A = +25^\circ\text{C}$ , unless otherwise noted.)

# 超低電力、高ダイナミック性能、 40Mspsアナログフロントエンド

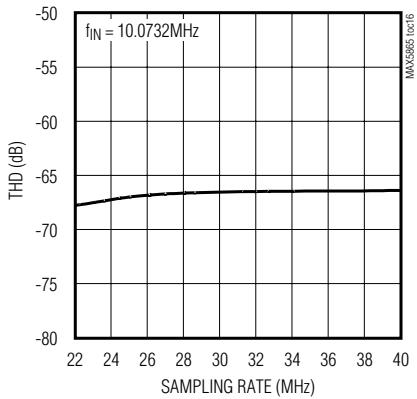

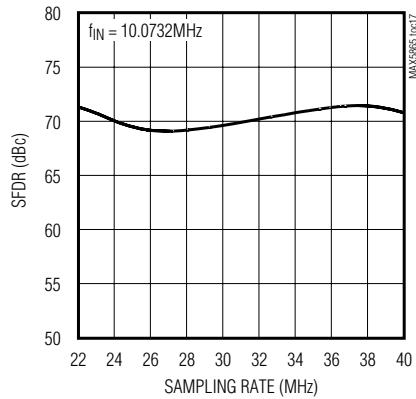

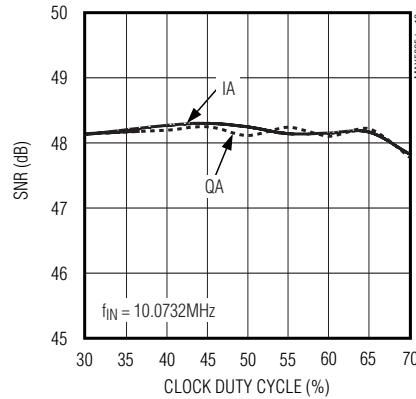

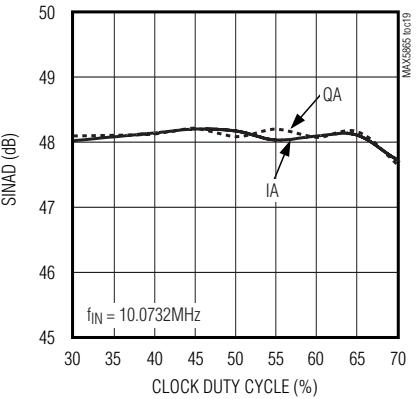

## 標準動作特性(続き)

( $V_{DD} = DV_{DD} = 3V$ ,  $OV_{DD} = 1.8V$ , internal reference (1.024V),  $C_L \approx 10\text{pF}$  on all digital outputs,  $f_{CLK} = 40\text{MHz}$  50% duty cycle, ADC input amplitude = -0.5dBFS, DAC output amplitude = 0dBFS, differential ADC input, differential DAC output,  $C_{REFP} = C_{REFN} = C_{COM} = 0.33\mu\text{F}$ , Xcvr mode,  $T_A = +25^\circ\text{C}$ , unless otherwise noted.)

# 超低電力、高ダイナミック性能、 40MspSアナログフロントエンド

**MAX5865**

## 標準動作特性(続き)

( $V_{DD} = DV_{DD} = 3V$ ,  $OV_{DD} = 1.8V$ , internal reference (1.024V),  $C_L \approx 10\text{pF}$  on all digital outputs,  $f_{CLK} = 40\text{MHz}$  50% duty cycle, ADC input amplitude = -0.5dBFS, DAC output amplitude = 0dBFS, differential ADC input, differential DAC output,  $CREFP = CREFN = C_{COM} = 0.33\mu\text{F}$ , Xcvr mode,  $T_A = +25^\circ\text{C}$ , unless otherwise noted.)

ADC SPURIOUS-FREE DYNAMIC RANGE

vs. ANALOG INPUT POWER

ADC SIGNAL-TO-NOISE RATIO

vs. SAMPLING RATE

ADC SIGNAL-TO-NOISE AND DISTORTION RATIO

vs. SAMPLING RATE

ADC TOTAL HARMONIC DISTORTION

vs. SAMPLING RATE

ADC SPURIOUS-FREE DYNAMIC RANGE

vs. SAMPLING RATE

ADC SIGNAL-TO-NOISE RATIO

vs. CLOCK DUTY CYCLE

ADC SIGNAL-TO-NOISE AND DISTORTION

RATIO vs. CLOCK DUTY CYCLE

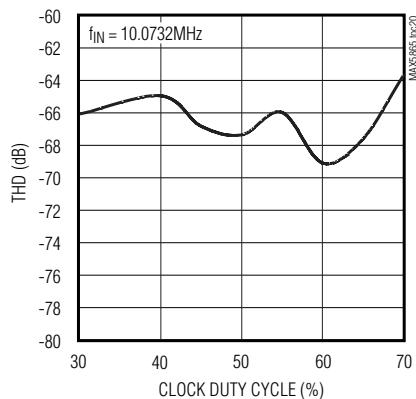

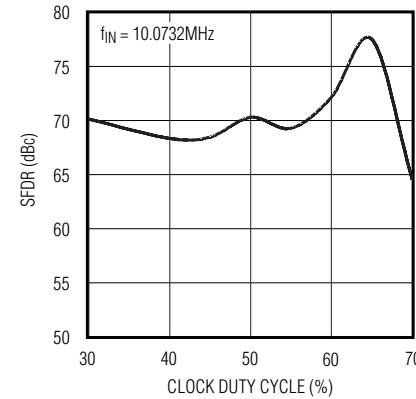

ADC TOTAL HARMONIC DISTORTION

vs. CLOCK DUTY CYCLE

ADC SPURIOUS-FREE DYNAMIC RANGE

vs. CLOCK DUTY CYCLE

# 超低電力、高ダイナミック性能、 40Mspsアナログフロントエンド

## 標準動作特性(続き)

( $V_{DD} = DV_{DD} = 3V$ ,  $OV_{DD} = 1.8V$ , internal reference (1.024V),  $C_L \approx 10\text{pF}$  on all digital outputs,  $f_{CLK} = 40\text{MHz}$  50% duty cycle, ADC input amplitude = -0.5dBFS, DAC output amplitude = 0dBFS, differential ADC input, differential DAC output,  $C_{REFP} = C_{REFN} = C_{COM} = 0.33\mu\text{F}$ , Xcvr mode,  $T_A = +25^\circ\text{C}$ , unless otherwise noted.)

# 超低電力、高ダイナミック性能、 40Mspsアナログフロントエンド

**MAX5865**

## 標準動作特性(続き)

( $V_{DD} = DV_{DD} = 3V$ ,  $OV_{DD} = 1.8V$ , internal reference (1.024V),  $C_L \approx 10\text{pF}$  on all digital outputs,  $f_{CLK} = 40\text{MHz}$  50% duty cycle, ADC input amplitude = -0.5dBFS, DAC output amplitude = 0dBFS, differential ADC input, differential DAC output,  $C_{REFP} = C_{REFN} = C_{COM} = 0.33\mu\text{F}$ , Xcvr mode,  $T_A = +25^\circ\text{C}$ , unless otherwise noted.)

# 超低電力、高ダイナミック性能、 40MspSアナログフロントエンド

## 端子説明

| 端子                  | 名称               | 機能                                                                                                                                 |

|---------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 1                   | REFP             | 正リファレンス電圧。0.33μFのコンデンサによって、REFPのできるだけ近くでGNDにバイパスします。                                                                               |

| 2, 8, 43            | V <sub>DD</sub>  | アナログ電源電圧。2.2μFと0.1μFのコンデンサを並列接続したものでGNDにバイパスします。                                                                                   |

| 3                   | IA+              | チャネルIA正アナログ入力。シングルエンド動作では、IA+に信号ソースを接続します。                                                                                         |

| 4                   | IA-              | チャネルIA負アナログ入力。シングルエンド動作では、IA-をCOMに接続します。                                                                                           |

| 5, 7, 12, 37,<br>42 | GND              | アナロググランド。すべての端子をGNDグランドプレーンに接続します。                                                                                                 |

| 6                   | CLK              | 変換クロック入力。ADCとDACの両方で使うクロック信号です。                                                                                                    |

| 9                   | QA-              | チャネルQA負アナログ入力。シングルエンド動作では、QA-をCOMに接続します。                                                                                           |

| 10                  | QA+              | チャネルQA正アナログ入力。シングルエンド動作では、QA+に信号ソースを接続します。                                                                                         |

| 11, 33, 39          | V <sub>DD</sub>  | アナログ電源電圧。デバイスのできるだけ近くでV <sub>DD</sub> 電源プレーンに接続します。                                                                                |

| 13–16, 19–22        | DA0–DA7          | ADCトライステートディジタル出力ビット。DA7が最上位ビット(MSB)、<br>DA0が最下位ビット(LSB)です。                                                                        |

| 17                  | OGND             | 出力ドライバグランド                                                                                                                         |

| 18                  | OV <sub>DD</sub> | 出力ドライバ電源。ほとんどのロジックレベルに対応することができるよう、+1.8V~V <sub>DD</sub> の電源<br>を供給します。OV <sub>DD</sub> は、2.2μFと0.1μFのコンデンサを並列接続したものでOGNDにバイパスします。 |

| 23–32               | DD0–DD9          | DACデジタル入力ビット。DD9がMSB、DD0がLSBです。                                                                                                    |

| 34                  | DIN              | 3線式シリアルインターフェースデータ入力。データは、SCLKの立上りエッジでラッチされます。                                                                                     |

| 35                  | SCLK             | 3線式シリアルインターフェースクロック入力                                                                                                              |

| 36                  | CS               | 3線式シリアルインターフェースチップ選択入力。ロジックローとするとシリアルインターフェースがイネーブルになります。                                                                          |

| 38                  | N.C.             | 接続なし                                                                                                                               |

| 40, 41              | QD+, QD-         | DACチャネルQD差動電圧出力                                                                                                                    |

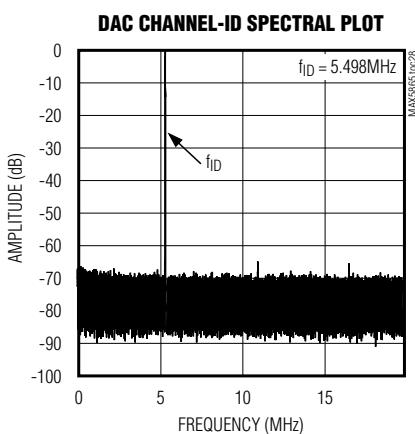

| 44, 45              | ID-, ID+         | DACチャネルID差動電圧出力                                                                                                                    |

| 46                  | REFIN            | リファレンス入力。内部リファレンスを使用するときには、V <sub>DD</sub> に接続します。                                                                                 |

| 47                  | COM              | コモンモード電圧I/O。0.33μFコンデンサでGNDにバイパスします。                                                                                               |

| 48                  | REFN             | 負リファレンスI/O。変換範囲は±(V <sub>REFP</sub> - V <sub>REFN</sub> )です。<br>0.33μFコンデンサでGNDにバイパスします。                                           |

| —                   | EP               | エクスポートドパッド。エクスポートドパッドは内部でGNDに接続されています。GNDプレーンに接続してください。                                                                            |

# 超低電力、高ダイナミック性能、 40Mspsアナログフロントエンド

MAX5865

## 詳細

MAX5865はデュアル8ビット受信ADCとデュアル10ビット送信DACを持ち、変換速度40Mspsで非常に高いダイナミック性能と超低電力性能を発揮します。ADCのアナログ入力アンプは完全差動化されており、入力可能なフルスケール信号は1V<sub>P-P</sub>です。DACのアナログ出力も完全差動化されており、フルスケール出力範囲が±400mV、コモンモードが1.4Vとなっています。

MAX5865では、3線式シリアルインターフェースによって動作モードの制御と電源管理が行えます。このシリアルインターフェースは、SPI™とMICROWIRE™と互換です。MAX5865のシリアルインターフェースから選べるモードは、シャットダウン、アイドル、スタンバイ、送信、受信、及びトランシーバです。

3線式シリアルインターフェースでMAX5865を送信、受信、またはトランシーバモードとして使うと、FDDアプリケーションやTDDアプリケーションに使用することができます。TDDモードでは、受信ADCと送信DACでデジタルバスを共有し、デジタルI/Oを減らして10ビットパラレルマルチプレクス型バス、1本で動作させることができます。FDDモードでは、MAX5865のデジタルI/Oを18ビットのパラレルマルチプレクス型バスとして構成し、デュアル8ビットADCとデュアル10ビットDACに対応させます。

MAX5865は、動作電圧と動作温度の全範囲にわたって安定な高精度1.024Vバンドギャップリファレンスを内蔵しています。

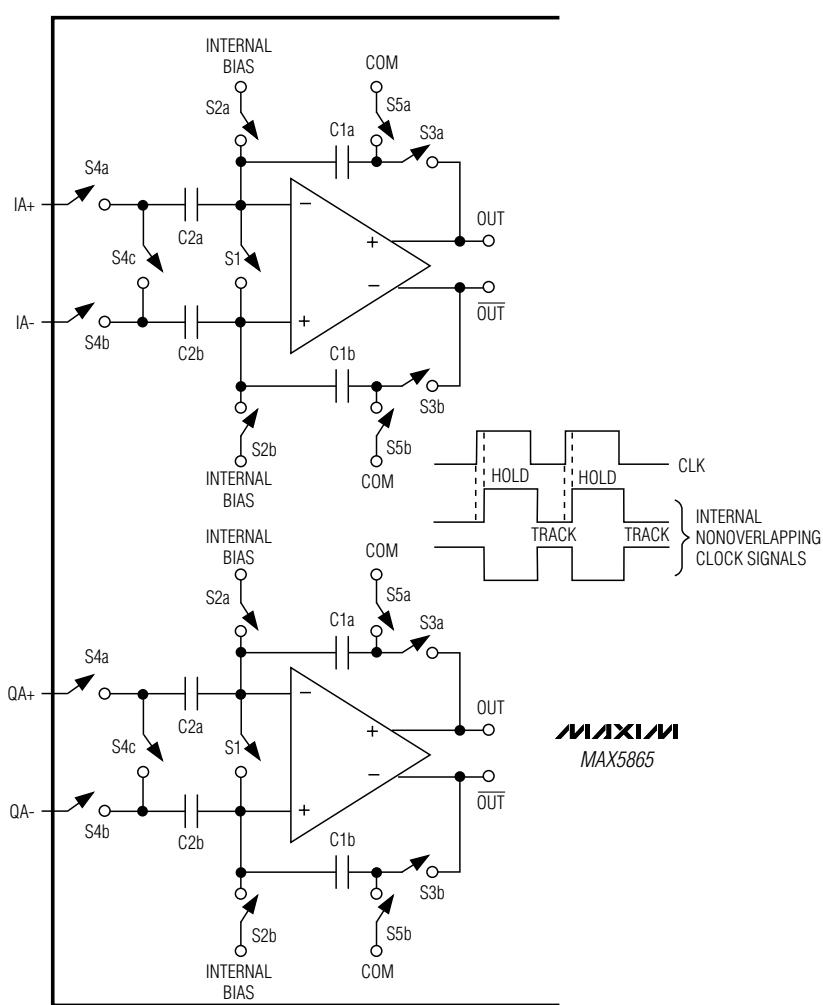

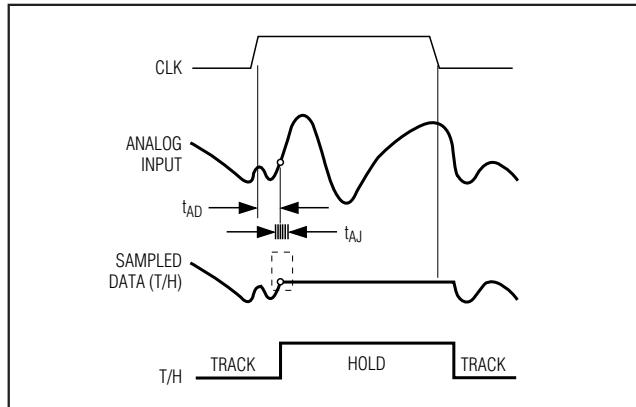

図1. MAX5865のADCに内蔵されたT/H回路

SPIはMotorola, Inc.の商標です。MICROWIREはNational Semiconductor Corp.の商標です。

# 超低電力、高ダイナミック性能、 40MspSアナログフロントエンド

## デュアル8ビットADC

ADCは、7段の完全差動パイプラインアーキテクチャによって、最小の電力消費で高速変換を実現しています。サンプリングされた入力は、半クロックサイクルごとに1段ずつ、パイプラインを通過していきます。出力ラッチの遅延も含めたトータルのクロックサイクル待ち時間は、チャネルIAで5クロックサイクル、チャネルQAで5.5クロックサイクルです。ADCは、フルスケールアナログ入力範囲が $\pm V_{REF}$ 、コモンモード入力範囲が $V_{DD}/2 \pm 0.2V$ です。 $V_{REF}$ は $V_{REFP}$ と $V_{REFN}$ の差です。詳細は、「リファレンス構成」の項目を参照してください。

## 入力トラック/ホールド(T/H)回路

図1に、ADC入力のT/H回路の概略ファンクションダイアグラムを示します。トラックモードでは、S1とS2a、S2b、S4a、S4b、S5a、S5bの各スイッチが閉じています。これは完全差動回路で、入力信号はスイッチS4aとS4b経由で2つのコンデンサ(C2aとC2b)にサンプリングされます。S2aとS2bはアンプ入力をコモンモードにセットするスイッチで、S1と同時に開き、入力波形のサンプリングを行います。続いて、スイッチS4a、S4b、S5a、S5bが開き、その後、スイッチS3aとS3bが閉じてC1aとC1bの2つのコンデンサがアンプ出力に接続され、スイッチS4cが閉じます。得られた差動電圧はC2aとC2bのコンデンサに保持されます。C1aとC1bのコンデンサは、アンプによって、C2aとC2bに保持されている電荷と同じ値まで充電されます。その後、この

値が第1段の数値化器に入力されるとともに、パイプラインが急速に変化する入力から切り離されます。T/Hアンプは入力帯域が広く、ナイキスト周波数を超える高周波数のアナログ入力もトラックし、サンプル/ホールドすることができます。ADC入力はいずれも(IA+、 QA+、 IA-、 QA-)、差動動作とすることもシングルエンドとすることもできます。最高の性能を得るためにIA+とIA-、 QA+とQA-のインピーダンスをマッチングさせ、コモンモード電圧として $V_{DD}/2$ をセットしてください。

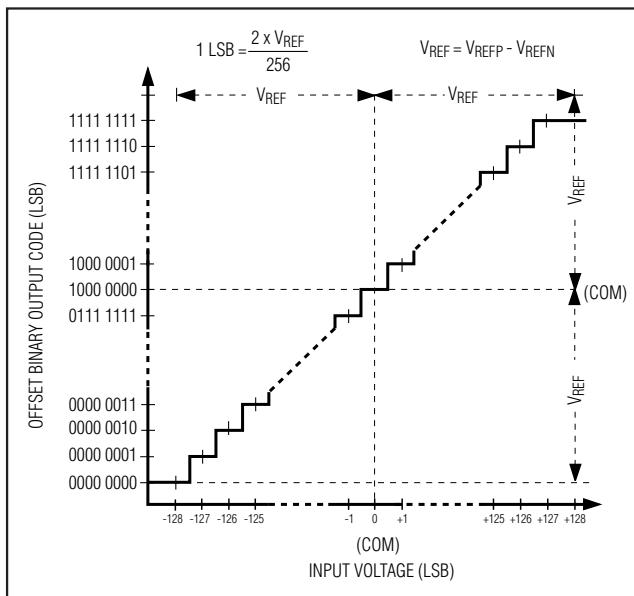

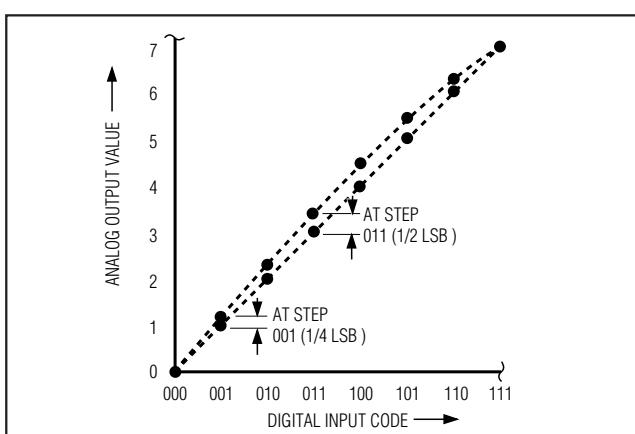

## ADCデジタル出力データ(DA0～DA7)

DA0～DA7は、ADCのデジタルロジック出力です。ロジックレベルは、 $0V_{DD}$ によって1.8Vと $V_{DD}$ の間にセットします。デジタル出力コーディングはオフセットバイナリです(表1、図2)。デジタル出力(DA0～DA7)につなぐ容量性負荷はできるだけ小さくし(15pF以下)、MAX5865のアナログ部分に大きなデジタル電流がフィードバックされ、ダイナミック性能が低下することを避けてください。

容量性負荷が大きい場合、デジタル出力にバッファを追加すれば、その影響を避けることができます。100Ω抵抗をデジタル出力に直列に取り付けると(MAX5865にできるだけ近い位置に取り付ける)、より高いADC性能を得ることができます。100Ωの直列抵抗経由でデジタル出力によってデジタルバッファを駆動する方法は、MAX5865評価キットの図を参照してください。

表1. 出力コードと入力電圧の関係

| DIFFERENTIAL INPUT VOLTAGE        | DIFFERENTIAL INPUT (LSB)     | OFFSET BINARY (DA7-DA0) | OUTPUT DECIMAL CODE |

|-----------------------------------|------------------------------|-------------------------|---------------------|

| $V_{REF} \times \frac{127}{128}$  | 127<br>(+full scale - 1LSB)  | 1111 1111               | 255                 |

| $V_{REF} \times \frac{126}{128}$  | 126<br>(+full scale - 2LSB)  | 1111 1110               | 254                 |

| $V_{REF} \times \frac{1}{128}$    | +1                           | 1000 0001               | 129                 |

| $V_{REF} \times \frac{0}{128}$    | 0<br>(bipolar zero)          | 1000 0000               | 128                 |

| $-V_{REF} \times \frac{1}{128}$   | -1                           | 0111 1111               | 127                 |

| $-V_{REF} \times \frac{127}{128}$ | -127<br>(-full scale + 1LSB) | 0000 0001               | 1                   |

| $-V_{REF} \times \frac{128}{128}$ | -128<br>(-full scale)        | 0000 0000               | 0                   |

# 超低電力、高ダイナミック性能、 40MspSアナログフロントエンド

MAX5865

## ADCシステムタイミング条件

図3は、クロックとアナログ入力、そして、その結果出力されるデータの関係です。チャネルIA(CHI)とチャネルQA(CHQ)が、クロック信号(CLK)の立上りエッジで同時にサンプリングされ、マルチプレクス型の結果データがDA0～DA7に出力されます。CHIデータはCLKの立上りエッジで更新され、CHQデータは立下りエッジで更新されます。出力ラッチの遅延も含めたトータルのクロックサイクル待ち時間は、CHIで5クロックサイクル、CHQで5.5クロックサイクルです。

図2. ADCの伝達関数

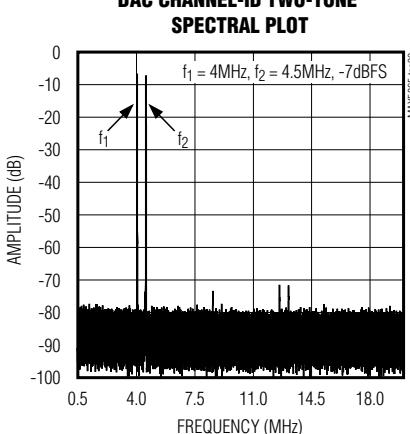

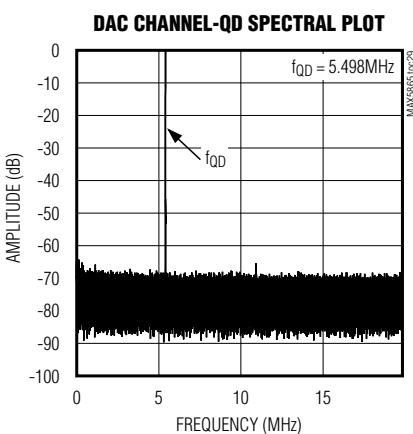

## デュアル10ビットDAC

DACは10ビットで、最高40MHzのクロックで動作することができます。DACのデジタル入力(DD0～DD9)はマルチプレクス型であり、1本の10ビットバスで動作します。このデータコンバータのフルスケール出力電圧はリファレンス電圧によって決まります。リファレンス電圧の設定方法は、「リファレンス構成」の項目を参照してください。このDACでは、電流行列手法によって400Ωの内部抵抗を1mAのフルスケール出力電流で駆動し(リファレンスは1.024V)、±400mVのフルスケール差動出力電圧を得ています。MAX5865は差動出力のみを持ち、シングルエンドアプリケーションでの使用は考慮していません。アナログ出力は1.4Vのコモンモードにバイアスされており、70kΩ以上の入力インピーダンスを持つ差動入力段に接続することを前提に設計されています。このため、RF直交アップコンバータとMAX5865とのアナログインターフェースが簡単になっています。RFアップコンバータは、コモンモードバイアスとして1.3V～1.5Vを必要とします。MAX5865はDCコモンモードバイアスを内蔵しているため、レベル設定抵抗やコードによるレベルシフトなしで、各送信DACのダイナミックレンジは完全に維持されます。表2に、出力電圧と入力コードの関係を示します。

図3. ADCシステムのタイミングダイアグラム

# 超低電力、高ダイナミック性能、 40MspSアナログフロントエンド

表2. DAC出力電圧と入力コードの関係(内部リファレンスマード:  $V_{REFDAC} = 1.024V$ 、

外部リファレンスマード:  $V_{REFDAC} = V_{REFIN}$ )

| DIFFERENTIAL OUTPUT VOLTAGE                         | OFFSET BINARY<br>(DD0-DD9) | INPUT DECIMAL CODE |

|-----------------------------------------------------|----------------------------|--------------------|

| $\frac{V_{REFDAC}}{2.56} \times \frac{1023}{1023}$  | 11 1111 1111               | 1023               |

| $\frac{V_{REFDAC}}{2.56} \times \frac{1021}{1023}$  | 11 1111 1110               | 1022               |

| $\frac{V_{REFDAC}}{2.56} \times \frac{3}{1023}$     | 10 0000 0001               | 513                |

| $\frac{V_{REFDAC}}{2.56} \times \frac{1}{1023}$     | 10 0000 0000               | 512                |

| $-\frac{V_{REFDAC}}{2.56} \times \frac{1}{1023}$    | 01 1111 1111               | 511                |

| $-\frac{V_{REFDAC}}{2.56} \times \frac{1021}{1023}$ | 00 0000 0001               | 1                  |

| $-\frac{V_{REFDAC}}{2.56} \times \frac{1023}{1023}$ | 00 0000 0000               | 0                  |

図4. DACシステムのタイミングダイアグラム

## DACタイミング

図4は、クロックと入力データ、アナログ出力の関係です。Iチャネルのデータ(ID)はクロック信号の立下りエッジでラッチされ、Qチャネルのデータ(QD)は立上りエッジでラッチされます。I出力もQ出力も、次のクロック信号の立上りエッジで同時に更新されます。

## 3線式シリアルインタフェースと動作モード

MAX5865は、3線式シリアルインタフェースで動作モードを制御します。所定のモードとなるように、パワーアップ時にMAX5865をプログラミングするのです。3線式シリアルインタフェースから選択できる動作モードは、シャットダウン、アイドル、スタンバイ、Rx、Tx、またはXcvrです。表3に示すように、動作モードを決定するのは8ビットのデータレジスタです。なお、どの動作モードでも、シリアルインタフェースはアクティブのままでです。

# 超低電力、高ダイナミック性能、 40Mspsアナログフロントエンド

MAX5865

表3. MAX5865の動作モード

| FUNCTION | DESCRIPTION                                                                                                                                            | D7<br>(MSB) | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----|----|----|----|----|----|----|

| Shutdown | Device shutdown. REF is off, ADCs are off, and the ADC bus is tri-stated; DACs are off and the DAC input bus must be set to zero or OV <sub>DD</sub> . | X           | X  | X  | X  | X  | 0  | 0  | 0  |

| Idle     | REF and CLK are on, ADCs are off, and the ADC bus is tri-stated; DACs are off and the DAC input bus must be set to zero or OV <sub>DD</sub> .          | X           | X  | X  | X  | X  | 0  | 0  | 1  |

| Rx       | REF is on, ADCs are on; DACs are off, and the DAC input bus must be set to zero or OV <sub>DD</sub> .                                                  | X           | X  | X  | X  | X  | 0  | 1  | 0  |

| Tx       | REF is on, ADCs are off, and the ADC bus is tri-stated; DACs are on.                                                                                   | X           | X  | X  | X  | X  | 0  | 1  | 1  |

| Xcvr     | REF is on, ADCs and DACs are on.                                                                                                                       | X           | X  | X  | X  | X  | 1  | 0  | 0  |

| Standby  | REF is on, ADCs are off, and the ADC bus is tri-stated; DACs are off and the DAC input bus must be set to zero or OV <sub>DD</sub> .                   | X           | X  | X  | X  | X  | 1  | 0  | 1  |

X = 任意

もっとも省電力となるのはシャットダウンモードで、MAX5865のアナログセクションをすべてシャットダウンするとともにADCのデジタル出力をトライステートモードにします。この場合、ADCの出力がトライステートからオンに遷移するとき、最後に変換されたワードがデジタル出力に出力されます。DACのデジタルバスは内部でプルアップされていないので、その入力はゼロかOV<sub>DD</sub>でなければなりません。シャットダウンモードから復帰するとき、DACに蓄えられていたデータは失われます。シャットダウンモードからのウェイクアップ時間は、REFP、REFN、及びCOMに接続されたコンデンサを充電する時間によって支配されます。内部リファレンスマードやバッファ付外部リファレンスマードにおける標準的なウェイクアップ時間は、Xcvrモードへの復帰で40μs、Rxモードへの復帰で20μs、Txモードへの復帰で40μsです。

アイドルモードでは、リファレンス回路とクロック分配回路のみに電源が供給され、その他の機能はすべてオフになります。ADC出力はトライステートになります。DACのデジタルバスは内部でプルアップされていないので、その入力はゼロかOV<sub>DD</sub>でなければなりません。アイドルモードからADCとDACが動作準備を完了するまでに必要なウェイクアップ時間は、10μsです。ADCの出力がトライステートからオンに遷移するとき、最後に変換されたワードがデジタル出力に出力されます。クロック入力をゼロあるいはOV<sub>DD</sub>にすれば、

アイドルモードの消費電流を小さくすることができますが、ウェイクアップ時間が40μsと長くなります。

スタンバイモードでは、ADCのリファレンスのみに電源が供給され、その他の機能はすべてオフになります。パイプラインADCもオフとなり、DA0からDA7はトライステートモードになります。DACのデジタルバスは内部でプルアップされていないので、その入力はゼロかOV<sub>DD</sub>でなければなりません。スタンバイモードからXcvrモードへのウェイクアップ時間は、パイプラインADCとDACをアクティブにするために必要な時間(40μs)に支配されます。ADCの出力がトライステートからアクティブに遷移するとき、最後に変換されたワードがデジタル出力に出力されます。

このシリアルデジタルインターフェースは標準的な3線式接続で、SPI/QSPI™/MICROWIRE/DSPインタフェースと互換です。 $\overline{CS}$ をローにするとシリアルデータがDINにロードできるようになります。続いて $\overline{CS}$ をハイからローに遷移させると、シリアルクロック(SCLK)の立上りエッジでMSBから順に、データが同期シフトしていきます。8ビットのすべてがシリアル入力レジスタにロードされたら、データが転送され、ラッピングされます。次のシーケンスを開始する前に、 $\overline{CS}$ を80ns以上、ハイに保つ必要があります。この間、SCLKはアイドルとなり、ハイ/ローは不定です。図5に3線式シリアルインターフェースの詳細なタイミングダイアグラムを示します。

QSPIはMotorola, Inc.の商標です。

# 超低電力、高ダイナミック性能、 40MspSアナログフロントエンド

図5. 3線式シリアルインターフェースのタイミングダイアグラム

図6. MAX5865のモード回復タイミングダイアグラム

## モード回復タイミング

図6は、モード回復タイミングダイアグラムです。t<sub>WAKE</sub>はシャットダウン、アイドル、スタンバイの各モードから復帰し、Rx、Tx、Xcvrの各モードに入るときのウェイクアップ時間です。t<sub>ENABLE</sub>は、Rx、Tx、Xcvrの各モード間を切り換えるときの回復時間です。t<sub>WAKE</sub>もt<sub>ENABLE</sub>も、ADCが所定のSINAD性能の1dB以内に整定し、DACが10 LSB誤差まで整定するのに必要な時間です。t<sub>WAKE</sub>とt<sub>ENABLE</sub>は、8ビットシリアルコマンドがCSの遷移ハイによってMAX5865にラッチされてからの時間を計測しています。Xcvrモードのt<sub>ENABLE</sub>は、DACウェイクアップ時間によって支配されます。Xcvr、Tx、Rxの各モード間を切り換えるときに必要な回復時間は10μsです。シャットダウンモードやスタンバイモードからXcvrモードに切り換えるときの回復時間は40μsです。

## システムクロック入力(CLK)

CLK入力は、すべてのADCとDACで共有しています。CMOSコンパチブルの信号が入力可能で、そのレベルはOV<sub>DD</sub>で1.8VからV<sub>DD</sub>の間に設定することができます。デバイスの段間変換は外部クロックの立上りエッジと立下りエッジの再現性に左右されるため、ジッタが少なく、立上り及び立下りの速い(2ns以下)外部クロックを使用するようしてください。クロック信号の立上りエッジでサンプリングを行うため、このエッジ部のジッタが低いことが特に重要です。クロックジッタが大きいと、次式のように内蔵ADCのSN比が制限されてしまいます。

$$\text{SNR} = 20 \times \log\left(\frac{1}{2 \times \pi \times f_{IN} \times t_{AJ}}\right)$$

ただし、f<sub>IN</sub>はアナログ入力周波数、t<sub>AJ</sub>はクロックジッタの時間です。

# 超低電力、高ダイナミック性能、 40Msp/sアナログフロントエンド

アンダサンプリングアプリケーションでは、クロックジッタが特に重要です。クロック入力をアナログ入力として取り扱い、他のアナログ入力ラインやデジタル信号ラインから離して配線してください。MAX5865は、電圧スレッショルドが $V_{DD}/2$ で、デューティサイクルが $50\% \pm 15\%$ のクロックを使用することができます。

## リファレンス構成

MAX5865は、動作電圧と動作温度の全範囲にわたって安定な、高精度の1.024V/バンドギャップリファレンスを内蔵しています。2種類のリファレンス動作モードがあり、その切り換えをREFIN入力で行います。REFINに加える電圧( $V_{REFIN}$ )によってリファレンス動作のモードが変化するのです(表4)。

内部リファレンスマードとするには、REFINを $V_{DD}$ に接続します。内部で生成された0.512Vという電圧が $V_{REF}$ として表れます。COM、REFP、及びREFNがローインピーダンス出力となり、 $V_{COM} = V_{DD}/2$ 、 $V_{REFP} = V_{DD}/2 + V_{REF}/2$ 、及び $V_{REFN} = V_{DD}/2 - V_{REF}/2$ となります。REFPとREFN、及びCOMは、一つずつ、 $0.33\mu F$ のコンデンサでバイパスします。REFINからGNDへは、 $0.1\mu F$ のコンデンサでバイパスします。

バッファ付外部リファレンスマードでは、 $1.024V \pm 10\%$ をREFINに加えます。このモードでは、COMとREFP、REFNがローインピーダンス出力となり、 $V_{COM} = V_{DD}/2$ 、 $V_{REFP} = V_{DD}/2 + V_{REFIN}/4$ 、及び $V_{REFN} = V_{DD}/2 - V_{REFIN}/4$ となります。REFP、REFN、及びCOMは、一つずつ、 $0.33\mu F$ のコンデンサでバイパスします。REFINからGNDへは、 $0.1\mu F$ のコンデンサでバイパスします。このモードでは、DACのフルスケール出力電圧とコモンモード電圧が外部リファレンスに比例して変化します。たとえば、 $V_{REFIN}$ を10%(max)高くすると、DACのフルスケール出力電圧も10%高くなり、 $\pm 440mV$ になります。コモンモード電圧も、10%高くなります。

表4. リファレンスマード

| $V_{REFIN}$          | REFERENCE MODE                                                                                                                                                                                                                                                                |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $>0.8 \times V_{DD}$ | Internal reference mode. $V_{REF}$ is internally generated to be 0.512V. Bypass REFp, REFN, and COM each with a $0.33\mu F$ capacitor.                                                                                                                                        |

| $1.024V \pm 10\%$    | Buffered external reference mode. An external $1.024V \pm 10\%$ reference voltage is applied to REFIN. $V_{REF}$ is internally generated to be $V_{REFIN}/2$ . Bypass REFp, REFN, and COM each with a $0.33\mu F$ capacitor. Bypass REFIN to GND with a $0.1\mu F$ capacitor. |

## アプリケーション情報

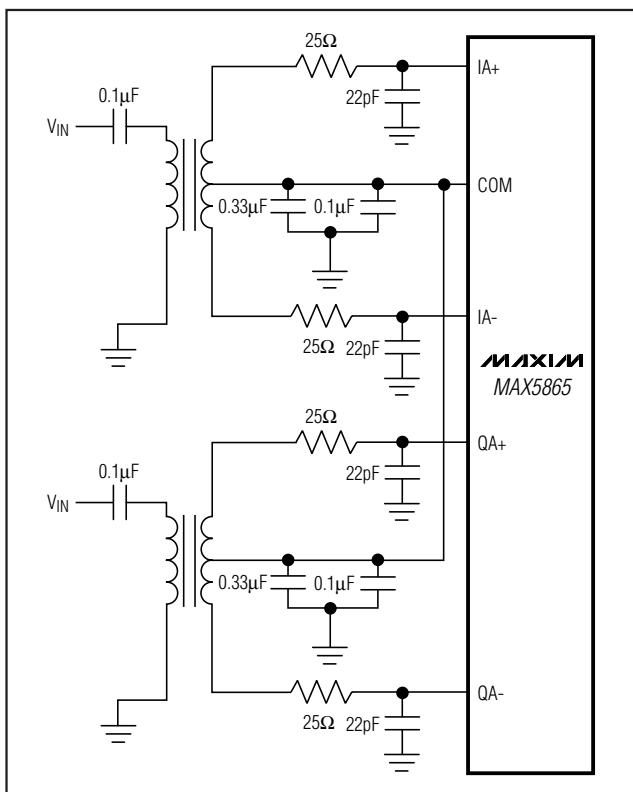

### 平衡不平衡変換器によるACカップリング

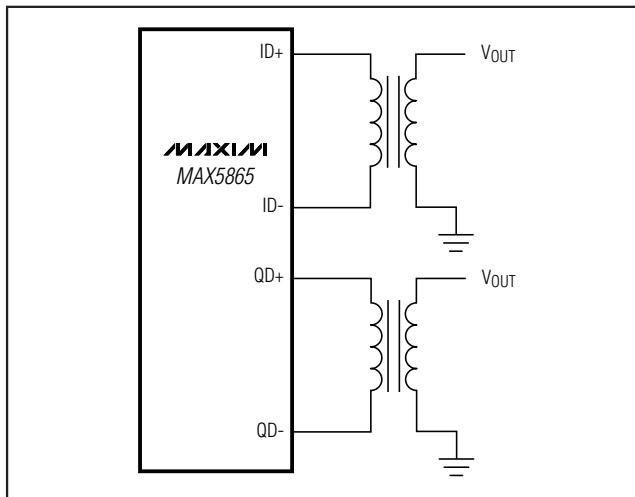

シングルエンド入力ソースの信号を完全差動信号とし、ADCの性能を十分に活用するためには、RFトランス(図7)の採用が一番いいでしょう。トランスのセンター・タップをCOMにつなげば、入力を $V_{DD}/2$  DCレベルにシフトすることができます。1:1トランスも使えますが、ステップアップトランスを使って駆動制限を緩和することも可能です。一般に、MAX5865は、シングルエンド信号よりも完全差動入力信号とした方が、SFDRやTHDといった性能が高くなります。この効果は、入力周波数が高くなると顕著に表れます。差動モードでは入力( $IA+$ 、 $IA-$ 、 $QA+$ 、 $QA-$ )がバランスを保つため偶数次高調波が低くなるとともに、ADC入力が必要とする信号スイングがシングルエンド入力モードの半分になります。図8の例は、RFトランスを使ってMAX5865のDACの差動アナログ出力をシングルエンドに変換する回路です。

図7. 平衡不平衡変換器結合によって、ADCの駆動方法をシングルエンドから差動入力に変換

# 超低電力、高ダイナミック性能、 40MspSアナログフロントエンド

図8. 平衡不平衡変成器結合によって、DAC出力を差動からシングルエンドに変換

図9. ADCのシングルエンド駆動

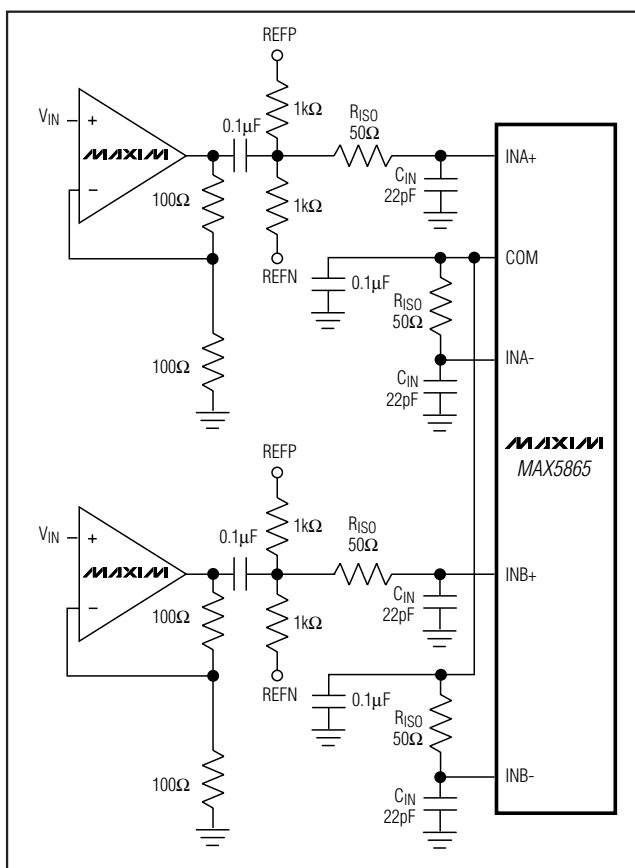

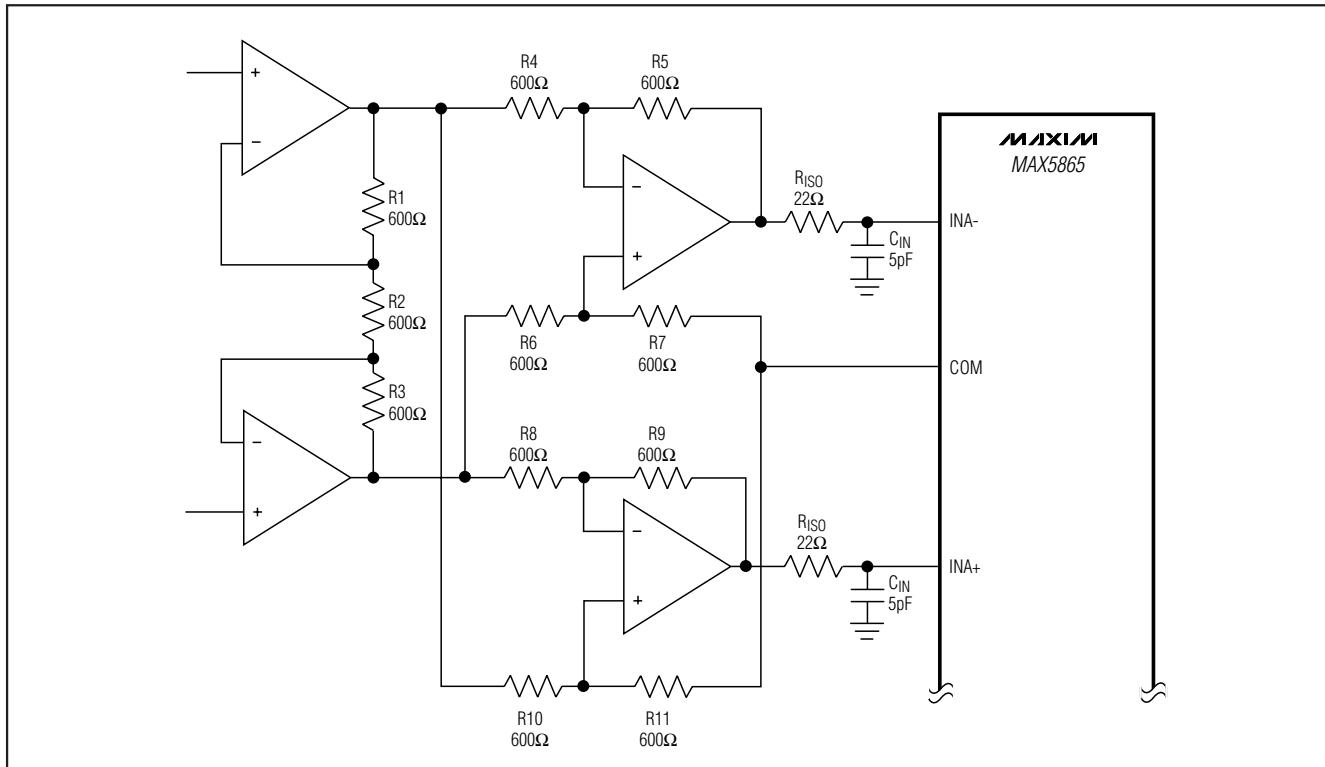

## オペアンプ結合の使用

平衡不平衡変成器が使えない場合は、オペアンプでMAX5865のADCを駆動します。図9と図10に、オペアンプを使ってADCを駆動し、AC結合のシングルエンドアプリケーションとDC結合の差動アプリケーションとする例を示します。入力信号の完全性を保つため、MAX4354/MAX4454といった、高速、広帯域、低ノイズ、低歪みのアンプを使用してください。図10の回路をDACの差動アナログ出力のインターフェースとして用い、利得を加えたりバッファとしてもできます。DACの差動アナログ出力は、内部で1.4VDCのコモンモードレベルとしているため、シングルエンドモードで使うことはできません。また、DACアナログ出力は、入力インピーダンスが70kΩ以上の差動入力段を駆動するように設計されています。シングルエンド出力としたい場合には、アンプを追加して差動出力をシングルエンドに変換します。このとき、入力コモンモード電圧の範囲が適切なアンプを選ぶようにしてください。

## FDDモードとTDDモード

MAX5865は、FDDモードやTDDモードで動作するさまざまなアプリケーションで使用することができます。MAX5865は、WCDMA-3GPP(FDD)や4G技術といったFDDアプリケーションでは、Xcvrモードで使用します。また、MAX5865は、TD-SCDMA、WCDMA-3GPP(TDD)、IEEE802.11a/b/g、及びIEEE802.16といったTDDアプリケーションでは、TxモードとRxモードを切り換えながら使用します。

FDDモードでは、ADCとDACが同時に動作します。ADCバスとDACバスが独立するので、18ビットパラレル(ADC 8ビットとDAC 10ビット)としてデジタルベースバンドプロセッサに接続しなければなりません。3線式シリアルインターフェースでXcvrモードとし、変換クロックでデータをラッチします。MAX5865の消費電力は、 $f_{CLK} = 40MHz$ で75.6mWとなります。これは、同時に動作しているADCとDACの消費電力の合計です。

TDDモードでは、ADCとDACが独立に動作します。ADCとDACがバスを共有し、一緒に接続されるので、デジタルベースバンドプロセッサへの接続は10ビットのパラレルバスが1本になります。3線式シリアルインターフェースでRxモードにするとADCがイネーブルとなり、TxモードにするとDACがイネーブルとなります。Rxモードでは、コアがディセーブルなのでDACからの送信が行われることはなく、一方、TxモードではADCバスがトライステートになります。この結果、不要なスプリアス放射がなく、バスの競合が防止されます。TDDモードでは、MAX5865の消費電力は、 $f_{CLK} = 40MHz$ のRxモードで63mW、TxモードでDACの消費電力は38.4mWとなります。

# 超低電力、高ダイナミック性能、 40Mspsアナログフロントエンド

**MAX5865**

図10. ADCからDC結合による差動回路の駆動

図11. TDDの標準動作回路

# 超低電力、高ダイナミック性能、 40MspSアナログフロントエンド

図11は、MAX5865とMAX2820を組み合わせてTDDモードを実現し、802.11b無線フロントエンドソリューションとした例です。MAX5865はDACがコモンモードレベル、1.4Vで完全差動のアナログ出力で、かつ、ADCがコモンモードレンジの広い入力を持つため、RFトランシーバと直接接続が可能で、外付けの部品やアンプでレベルシフト回路を組む必要がありません。また、コモンモードレベルがIC内部で作られるため、コードによるレベルシフトや抵抗レベルシフトによる減衰もなく、DACのダイナミックレンジをすべて活用することができます。MAX5865のADCはフルスケールレンジが1V<sub>P-P</sub>であり、入力コモンモードレベルがV<sub>DD</sub>/2(±200mV)となっています。このためADCとRF直交復調器を簡単にアナログでインタフェースすることが可能です。外付けの利得アンプやレベルシフト部品も不要です。

## グランド、バイパス、 基板レイアウト

MAX5865を使用するためには、高速基板レイアウトの設計技術が必要です。基板レイアウトについては、MAX5865評価キットのデータシートを参照してください。バイパスコンデンサは、すべて、デバイスにできるだけ近い位置に取り付けます。できれば、表面実装としてデバイスと同じ面に取り付けると、インダクタンスを最小限に抑えることができます。V<sub>DD</sub>からGNDは、0.1μFのセラミックコンデンサと2.2μFのコンデンサを並列接続してバイパスします。OV<sub>DD</sub>からOGNDも、0.1μFのセラミックコンデンサと2.2μFのコンデンサを並列接続してバイパスします。REFP、REFN、及びCOMも、それぞれ、0.33μFのセラミックコンデンサでGNDにバイパスします。REFINからGNDのバイパスは0.1μFのコンデンサで行います。

信号の完全性を高めるために、十分なグランドプレーンと電源プレーンを持つマルチレイヤボードを使用します。スプリットグランドプレーンを、デバイスパッケージのアナロググランド(GND)とデジタル出力ドライバグランド(OGND)の物理的な位置に合わせて配置します。MAX5865の背面エクスポートドパッドは、GNDプレーンに接続します。2つのグランドプレーンは

1点接続とし、ノイズの多いデジタルグランド電流がアナロググランドプレーンに影響を与えないようにします。1点接続の位置は、グランドプレーン間のギャップに沿って実験的に最適な位置を求めます。接続は、抵抗値の小さな表面実装抵抗(1Ω~5Ω)か、フェライトビーズ、あるいは短い直接配線で行います。あるいは、グランドプレーンがノイズの多いデジタルシステムのグランドプレーン(下流の出力バッファやDSPグランドプレーン)から十分に絶縁されている場合には、すべてのグランドピンを一つのグランドプレーンに接続するという方法も使えます。

高速デジタル信号トレースは、影響を受けやすいアナログトレースから離して配線します。チャネル間クロストークを抑えるため、各コンバータへのアナログ入力ラインを十分に分離してください。信号ラインはできるだけ短くするとともに、90°の曲がりを避けます。

## ダイナミック性能パラメータの定義

### ADCとDACに関するスタティック性能

#### パラメータの定義

##### 積分非線形性(INL)

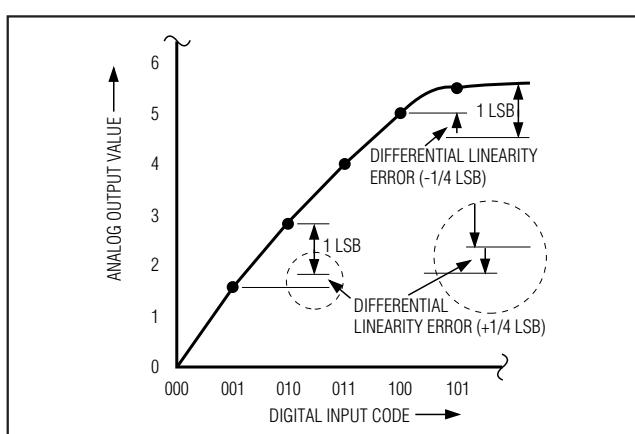

積分非線形性とは、伝達関数の直線からのずれを指します。直線は、最良近似直線を使う場合と、オフセット誤差と利得誤差を除去した後の伝達関数の始点と終点を結んだ線を使う場合があります。スタティックな線形性パラメータは、始点と終点を結んだ線をベースに測定しています。(DAC:図12a)

##### 微分非線形性(DNL)

微分非線形性とは、実際のステップ幅と1 LSBという理想値との差を指します。DNL誤差性能が1 LSBよりも小さいと、ミッシングコードがないことが保証され(ADC)、伝達関数が単調になります(ADCとDAC)。(DAC:図12b)

##### ADCオフセット誤差

ミッドスケールは、理想的には、ミッドスケールよりも0.5 LSB大きくなった時点で遷移します。オフセット誤差とは、実際の遷移ポイントと理想的な遷移ポイントの差を指します。

図12a. 積分非線形性

図12b. 微分非線形性

# 超低電力、高ダイナミック性能、 40Msp/sアナログフロントエンド

MAX5865

## DACオフセット誤差

オフセット誤差(図12a)とは、オフセットポイントの理想値と実際の値の差を指します。オフセットポイントは、デジタル入力がミッドスケールのときに出力される値です。この誤差はすべてのコードに等しく影響するため、トリミングで補償することができます。

## ADC利得誤差

理想的な状態では、ADCのフルスケール遷移がフルスケールから1.5 LSB低い点で発生します。利得誤差は、オフセット誤差を除去したあと、理想的な遷移ポイントから実際の遷移ポイントがどのくらいずれているかを示します。

## ADCダイナミック性能パラメータの定義

### アーチャジッタ

図13に、アーチャジッタ( $t_{AJ}$ )の例を示します。これは、サンプル間におけるアーチャ遅延の差です。

### アーチャ遅延

アーチャ遅延( $t_{AD}$ )は、サンプリングクロックの立上がりエッジから実際にサンプリングされる瞬間までの時間です(図13)。

### 信号対雑音比(SNR比)

デジタルサンプルから波形を完全に再構築できたとすると、そのSNR比は、理論上、フルスケールアナログ入力(RMS値)とRMS数値化誤差(残存誤差)の比になります。この値は、ADCの分解能(Nビット)によって決定されます。

$$SNR(\text{max}) = 6.02\text{dB} \times N + 1.76\text{dB} \text{ (in dB)}$$

現実には、数値化ノイズ以外に、サーマルノイズやリファレンスノイズ、クロックジッタなど、さまざまなノイズソースがあります。SNR比は、RMS信号とRMSノイズの比をとって算出します。RMSノイズには、基本周波数、最初の5高調波、及びDCオフセットを除くナイキスト周波数の全スペクトル成分が含まれます。

### 信号対ノイズ + 歪み(SINAD)

SINADは、RMS信号とRMSノイズの比として算出します。RMSノイズには、基本周波数とDCオフセットを除くナイキスト周波数の全スペクトル成分が含まれます。

### 実効ビット数(ENOB)

ENOBから、特定の入力周波数とサンプリングレートにおけるADCのダイナミック性能がわかります。理想的なADCでは、誤差は数値化ノイズのみとなります。フルスケールの入力サイン波に対するENOBは、次式で算出できます。

$$ENOB = (\text{SINAD} - 1.76) / 6.02$$

図13. T/Hアーチャタイミング

### 全高調波歪み(THD)

THDとは、入力信号の最初の5高調波のRMSを合計したものと基本周波数のRMSの比で、次式で表されます。

$$\text{THD} = 20\log \left[ \frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + V_5^2 + V_6^2}}{V_1} \right]$$

ただし、 $V_1$ は基本周波数の振幅、 $V_2 \sim V_6$ は第2高調波から第6高調波の振幅です。

### 3次高調波歪み(HD3)

HD3とは、基本入力信号に対する3次高調波成分のRMS値の比です。

### スピアスフリーダイナミックレンジ(SFDR)

SFDRは、基本周波数のRMS振幅(信号の最大成分)とDCオフセットを除く最大のスピアス成分のRMS値の比をデシベル単位で表したものです。

### 相互変調歪み(IMD)

IMDとは、相互変調積の合計電力を、 $f_1$ と $f_2$ というツートーンの合計入力電力に対する相対値で表したものです。相互変調積は $(f_1 \pm f_2)$ 、 $(2 \times f_1)$ 、 $(2 \times f_2)$ 、 $(2 \times f_1 \pm f_2)$ 、 $(2 \times f_2 \pm f_1)$ で、各入力トーンのレベルは-7dBFSです。

### 3次相互変調(IM3)

IM3とは、ナイキスト周波数に対する3次相互変調積の総歪み電力を、 $f_1$ と $f_2$ というツートーンの合計入力電力に対する相対値で表したものです。3次相互変調積は $(2 \times f_1 \pm f_2)$ と $(2 \times f_2 \pm f_1)$ で、各入力トーンのレベルは-7dBFSです。

# 超低電力、高ダイナミック性能、 40MspSアナログフロントエンド

## 電源除去比

電源除去比とは、電源が±5%変動したときのオフセットと利得誤差のシフト量です。

## 小信号帯域幅

信号のスルーレートによってADC性能が制限されない形で、ADCに-20dBFSという小さなアナログ入力信号を加えます。デジタル化した結果の振幅が-3dB低下するまで入力周波数をスイープします。小信号入力帯域幅の上限はT/H性能によって決まることが多いことに注意する必要があります。

## フルパワー帯域幅

ADCに-0.5dBFSという大きなアナログ入力信号を加え、デジタル化した結果の振幅が-3dB低下するまで入力周波数をスイープします。この点をフルパワー帯域周波数といいます。

## DACダイナミック性能パラメータの定義

### 全高調波歪み(THD)

THDは、出力高調波のRMSをナイキスト周波数まで合計したものと基本周波数のRMSの比で、次式で表されます。

$$\text{THD} = 20 \log \left[ \frac{\sqrt{(V_2^2 + V_3^2 + \dots + V_n^2)}}{V_1} \right]$$

ただし、 $V_1$ は基本振幅、 $V_2$ から $V_n$ までは2次からn次まで(ナイキスト周波数以下)の高調波の振幅です。

### スプリアスフリーダイナミックレンジ

スプリアスフリーダイナミックレンジ(SFDR)は、基本周波数のRMS振幅(信号の最大成分)と、ナイキスト周波数以下でDCオフセットを除く最大のスプリアス成分のRMS値の比をデシベル単位で表したものです。

## ピン配置

## チップ情報

TRANSISTOR COUNT: 16,765

PROCESS: CMOS

# 超低電力、高ダイナミック性能、 40MspSアナログフロントエンド

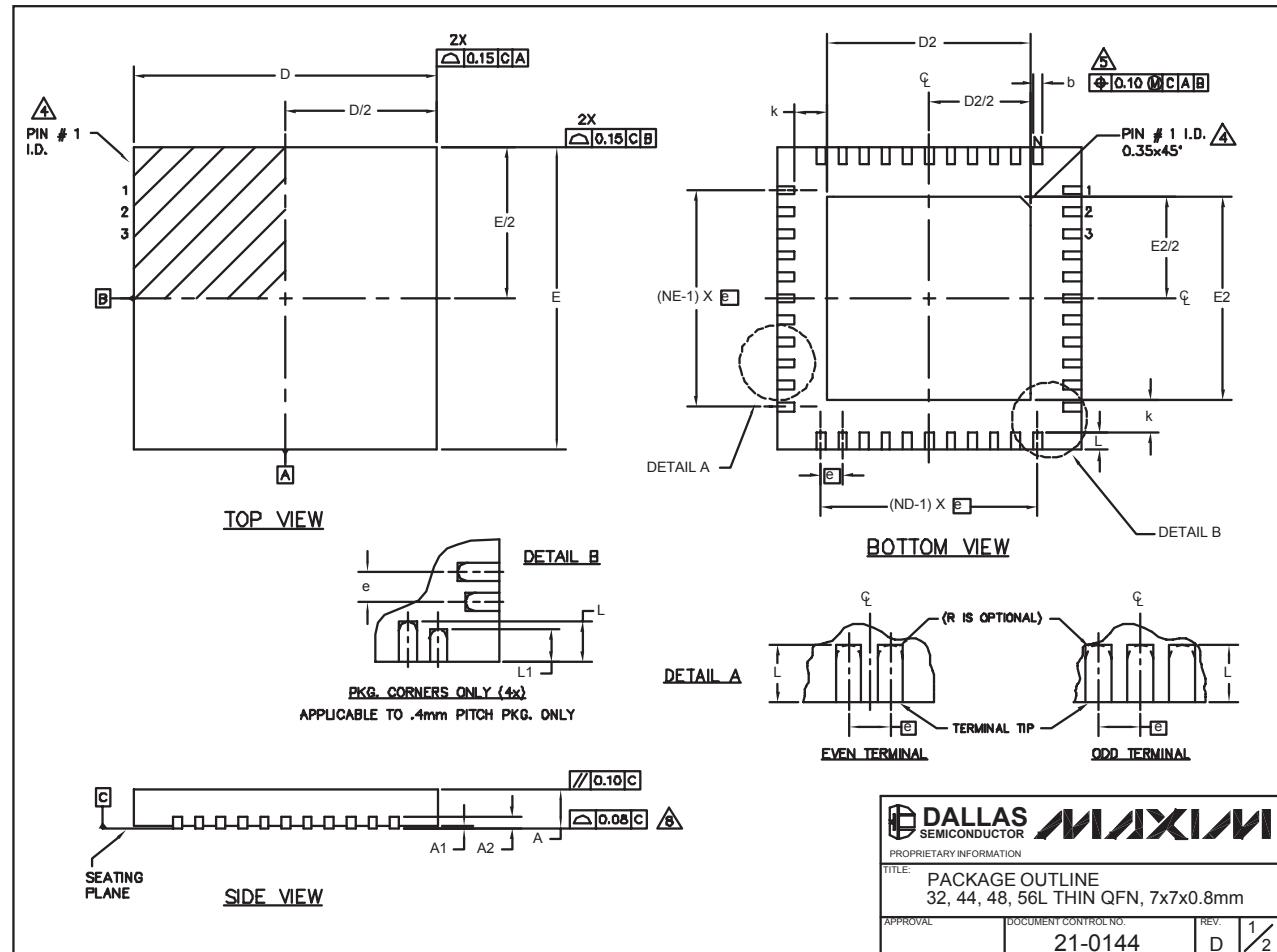

## パッケージ

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、<http://japan.maxim-ic.com/packages>をご参照下さい。)

**MAX5865**

32, 44, 48L QFN EPS

# 超低電力、高ダイナミック性能、 40Msp/sアナログフロントエンド

## パッケージ(続き)

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、<http://japan.maxim-ic.com/packages>をご参照下さい。)

| COMMON DIMENSIONS |           |      |      |           |      |      |           |      |      |                          |      |      |           |      |      | EXPOSED PAD VARIATIONS |      |       |               |                      |      |      |      |      |                          |  |                          |  |

|-------------------|-----------|------|------|-----------|------|------|-----------|------|------|--------------------------|------|------|-----------|------|------|------------------------|------|-------|---------------|----------------------|------|------|------|------|--------------------------|--|--------------------------|--|

| PKG.              | 32L 7x7   |      |      | 44L 7x7   |      |      | 48L 7x7   |      |      | CUSTOM PKG.<br>(T4877-1) |      |      | 48L 7x7   |      |      | 56L 7x7                |      |       | PKG.<br>CODES | DEPOPULATED<br>LEADS | D2   |      | E2   |      | JEDEC<br>MO220<br>REV. C |  | DOWN<br>BONDS<br>ALLOWED |  |

|                   | MIN.      | NOM. | MAX. | MIN.      | NOM. | MAX. | MIN.      | NOM. | MAX. | MIN.                     | NOM. | MAX. | MIN.      | NOM. | MAX. | MIN.                   | NOM. | MAX.  | MIN.          | NOM.                 | MAX. | MIN. | NOM. | MAX. |                          |  |                          |  |

| SYMBOL            |           |      |      |           |      |      |           |      |      |                          |      |      |           |      |      |                        |      |       |               |                      |      |      |      |      |                          |  |                          |  |

| A                 | 0.70      | 0.75 | 0.80 | 0.70      | 0.75 | 0.80 | 0.70      | 0.75 | 0.80 | 0.70                     | 0.75 | 0.80 | 0.70      | 0.75 | 0.80 |                        |      |       |               |                      |      |      |      |      |                          |  |                          |  |

| A1                | 0         | 0.02 | 0.05 | 0         | 0.02 | 0.05 | 0         | 0.02 | 0.05 | 0                        | 0.02 | 0.05 | 0         | 0.02 | 0.05 | 0                      | -    | -0.05 |               |                      |      |      |      |      |                          |  |                          |  |

| A2                | 0.20 REF. |      |      | 0.20 REF. |      |      | 0.20 REF. |      |      | 0.20 REF.                |      |      | 0.20 REF. |      |      | 0.20 REF.              |      |       |               |                      |      |      |      |      |                          |  |                          |  |

| b                 | 0.25      | 0.30 | 0.35 | 0.20      | 0.25 | 0.30 | 0.20      | 0.25 | 0.30 | 0.20                     | 0.25 | 0.30 | 0.20      | 0.25 | 0.30 | 0.15                   | 0.20 | 0.25  |               |                      |      |      |      |      |                          |  |                          |  |

| D                 | 6.90      | 7.00 | 7.10 | 6.90      | 7.00 | 7.10 | 6.90      | 7.00 | 7.10 | 6.90                     | 7.00 | 7.10 | 6.90      | 7.00 | 7.10 | 6.90                   | 7.00 | 7.10  |               |                      |      |      |      |      |                          |  |                          |  |

| E                 | 6.90      | 7.00 | 7.10 | 6.90      | 7.00 | 7.10 | 6.90      | 7.00 | 7.10 | 6.90                     | 7.00 | 7.10 | 6.90      | 7.00 | 7.10 | 6.90                   | 7.00 | 7.10  |               |                      |      |      |      |      |                          |  |                          |  |

| e                 | 0.65 BSC. |      |      | 0.50 BSC. |      |      | 0.50 BSC. |      |      | 0.50 BSC.                |      |      | 0.40 BSC. |      |      |                        |      |       |               |                      |      |      |      |      |                          |  |                          |  |

| k                 | 0.25      | -    | -    | 0.25      | -    | -    | 0.25      | -    | -    | 0.25                     | -    | -    | 0.25      | -    | -    | 0.25                   | 0.35 | 0.45  |               |                      |      |      |      |      |                          |  |                          |  |

| L                 | 0.45      | 0.55 | 0.65 | 0.45      | 0.55 | 0.65 | 0.30      | 0.40 | 0.50 | 0.45                     | 0.55 | 0.65 | 0.40      | 0.50 | 0.60 |                        |      |       |               |                      |      |      |      |      |                          |  |                          |  |

| L1                | -         | -    | -    | -         | -    | -    | -         | -    | -    | -                        | -    | -    | -         | -    | -    | 0.30                   | 0.40 | 0.50  |               |                      |      |      |      |      |                          |  |                          |  |

| N                 | 32        |      |      | 44        |      |      | 48        |      |      | 44                       |      |      | 56        |      |      |                        |      |       |               |                      |      |      |      |      |                          |  |                          |  |

| ND                | 8         |      |      | 11        |      |      | 12        |      |      | 10                       |      |      | 14        |      |      |                        |      |       |               |                      |      |      |      |      |                          |  |                          |  |

| NE                | 8         |      |      | 11        |      |      | 12        |      |      | 12                       |      |      | 14        |      |      |                        |      |       |               |                      |      |      |      |      |                          |  |                          |  |

\*\* NOTE: T4877-1 IS A CUSTOM 48L PKG. WITH 4 LEADS DEPOPULATED.

TOTAL NUMBER OF LEADS ARE 44.

### NOTES:

1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

2. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

3. N IS THE TOTAL NUMBER OF TERMINALS.

4. THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

5. DIMENSION b APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25 mm AND 0.30 mm FROM TERMINAL TIP.

6. ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

7. DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

8. COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

9. DRAWING CONFORMS TO JEDEC MO220 EXCEPT THE EXPOSED PAD DIMENSIONS OF T3277-1; T4877-1/-2/-3/-4/-5/-6 & T5677-1.

10. WARPAGE SHALL NOT EXCEED 0.10 mm.

マキシム・ジャパン株式会社

〒169-0051 東京都新宿区西早稲田3-30-16(ホリゾン1ビル)

TEL. (03)3232-6141 FAX. (03)3232-6149

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。マキシムは隨時予告なく回路及び仕様を変更する権利を留保します。

26 Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600