EVALUATION KIT

AVAILABLE

MAXIM

## デュアル、10ビット、80Msps、電流出力DAC

MAX5853

## 概要

MAX5853は、デュアル、10ビット、80Msps、デジタル-アナログコンバータ(DAC)で、広帯域通信システムにおいて卓越したダイナミック性能を発揮します。このデバイスは、2個の10ビットDACコアと、1.24Vリファレンスを内蔵しています。このコンバータは、シングルエンド及び差動動作モードに対応しています。MAX5853のダイナミック性能は、2.7V～3.6Vの全電源動作範囲にわたって維持します。アナログ出力は、-1.0V～+1.25Vの電圧に対応しています。

また、MAX5853はインターリーブデータモードで動作することができ、I/Oピン点数が削減します。このため、このコンバータを10ビット単一バス上で入れ替えすることができます。

MAX5853は、0.05dB刻みの16ステップで、チャネル利得マッチングを±0.4dB以内にディジタル制御する機能を備えています。アナログ直交変調のアプリケーションでは、チャネルマッチングによって側波帯抑制能力が向上します。1.24Vの内蔵バンドギャップリファレンスには制御アンプが装備され、このアンプによって1個の抵抗を通じて両チャネルを外部からフルスケール調整することができます。高精度アプリケーション用に内部リファレンスをディセーブルにして、外部リファレンスを使用することができます。

MAX5853は2mA～20mAのフルスケール電流出力を備え、2.7V～3.6Vの単一電源で動作します。このDACは、標準、低電力スタンバイ、及び完全パワーダウンの3つの電源制御動作モードを備えています。パワーダウンモードでは、動作電流は1µAまで低減します。

MAX5853は裏面放熱パドル(EP)付40ピン薄型QFNパッケージで提供され、拡張温度範囲(-40°C～+85°C)での動作が保証されています。

ピンコンパチブル、高速、及び低分解能バージョンも提供されます。詳細については、MAX5854(10ビット、165Msps)、MAX5852\*\* (8ビット、165Msps)、及びMAX5851\*\* (8ビット、80Msps)のデータシートを参照してください。データシートの最後に記載されている表4を参照してください。

## アプリケーション

## 通信

SatCom、LMDS、MMDS、HFC、DSL、WLAN、

ポイント間マイクロ波リンク

## ワイヤレス基地局

## 直交変調

## ダイレクトデジタル合成(DDS)

## 計測/ATE

\*\* 開発中の製品。入手性についてはお問い合わせください。

## 特長

- ◆ 10ビット、80Msps、デュアルDAC

- ◆ 低電力

$I_{FS} = 5\text{mA}$ の場合、77mW ( $f_{CLK} = 80\text{MHz}$ 時)

- ◆ 単一電源：2.7V～3.6V

- ◆ 2.7V電源電圧でフル出力スイング及びダイナミック性能

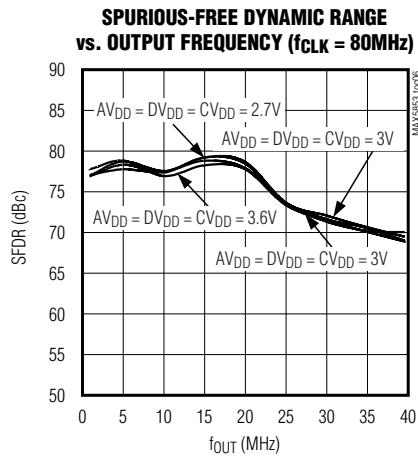

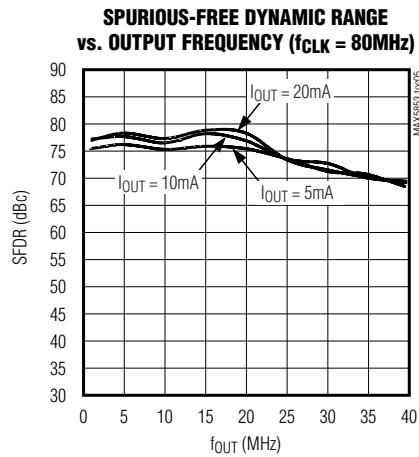

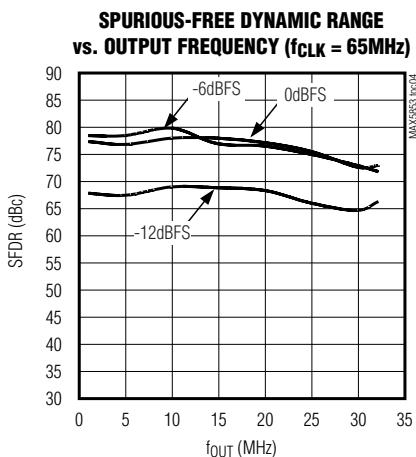

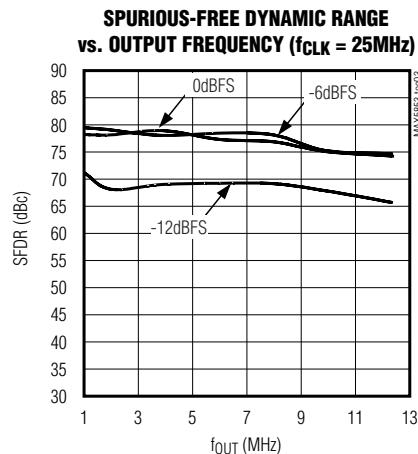

- ◆ 卓越したダイナミック性能

$78\text{dBc SFDR}$  ( $f_{OUT} = 20\text{MHz}$ 時)

- ◆ プログラマブルなチャネル利得マッチング

- ◆ 1.24Vの低ノイズバンドギャップリファレンス内蔵

- ◆ 単一抵抗による利得制御

- ◆ インタリーブデータモード

- ◆ シングルエンド及び差動の、クロック入力モード

- ◆ 超小型40ピン、Thin QFNパッケージ(6mm x 6mm)

- ◆ 評価キットを提供(MAX5854 EV Kit)

## 型番

| PART       | TEMP RANGE     | PIN-PACKAGE     |

|------------|----------------|-----------------|

| MAX5853ETL | -40°C to +85°C | 40 Thin QFN-EP* |

\*EP = 裏面放熱パドル

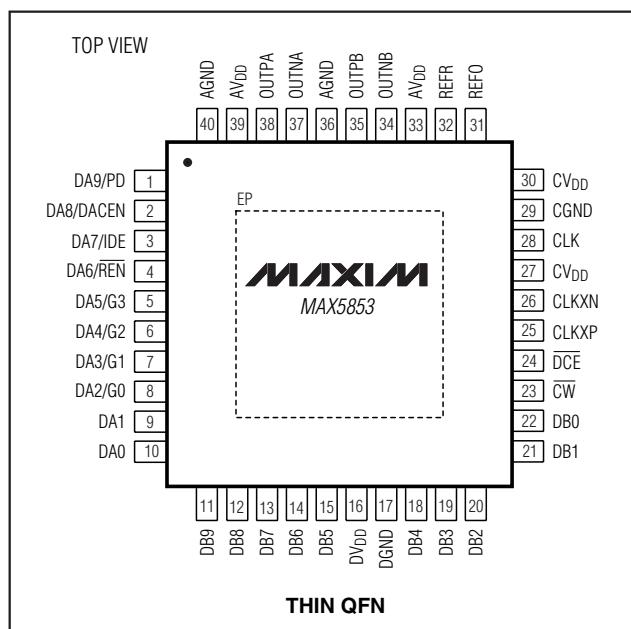

## ピン配置

MAXIM

本データシートに記載された内容はMaxim Integrated Productsの公式な英語版データシートを翻訳したものです。翻訳により生じる相違及び誤りについては責任を負いかねます。正確な内容の把握には英語版データシートをご参照ください。

無料サンプル及び最新版データシートの入手には、マキシムのホームページをご利用ください。<http://japan.maxim-ic.com>

# デュアル、10ビット、80Msps、電流出力DAC

## ABSOLUTE MAXIMUM RATINGS

|                                            |                                    |                                                                  |                                                        |

|--------------------------------------------|------------------------------------|------------------------------------------------------------------|--------------------------------------------------------|

| AV <sub>DD</sub> to AGND .....             | -0.3V to +4V                       | OUTPA, OUTNA to AGND .....                                       | (AV <sub>DD</sub> - 4.8V) to (AV <sub>DD</sub> + 0.3V) |

| DV <sub>DD</sub> to DGND .....             | -0.3V to +4V                       | OUTPB, OUTNB to AGND .....                                       | (AV <sub>DD</sub> - 4.8V) to (AV <sub>DD</sub> + 0.3V) |

| CV <sub>DD</sub> to CGND .....             | -0.3V to +4V                       | Maximum Current into Any Pin<br>(excluding power supplies) ..... | ±50mA                                                  |

| AV <sub>DD</sub> to DV <sub>DD</sub> ..... | -4V to +4V                         | Continuous Power Dissipation (T <sub>A</sub> = +70°C) .....      |                                                        |

| AGND to DGND .....                         | -0.3V to +0.3V                     | 40-Pin Thin QFN (derate 26.3mW/°C above +70°C) .....             | 2105mW                                                 |

| AGND to CGND .....                         | -0.3V to +0.3V                     | Operating Temperature Range .....                                | -40°C to +85°C                                         |

| DGND to CGND .....                         | -0.3V to +0.3V                     | Storage Temperature Range .....                                  | -65°C to +150°C                                        |

| DA9-DA0, DB9-DB0, CW, DCE to DGND .....    | -0.3V to +4V                       | Junction Temperature .....                                       | +150°C                                                 |

| CLK to CGND .....                          | -0.3V to (CV <sub>DD</sub> + 0.3V) | Lead Temperature (soldering, 10s) .....                          | +300°C                                                 |

| CLKXN, CLKXP to CGND .....                 | -0.3V to +4V                       |                                                                  |                                                        |

| REFR, REFO to AGND .....                   | -0.3V to (AV <sub>DD</sub> + 0.3V) |                                                                  |                                                        |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

(AV<sub>DD</sub> = DV<sub>DD</sub> = CV<sub>DD</sub> = 3V, AGND = DGND = CGND = 0, f<sub>DAC</sub> = 80Msps, differential clock, external reference, V<sub>REF</sub> = 1.2V, I<sub>FS</sub> = 20mA, differential output, output amplitude = 0dBFS, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. T<sub>A</sub> ≥ +25°C, guaranteed by production test. T<sub>A</sub> < +25°C guaranteed by design and characterization. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                                                   | SYMBOL          | CONDITIONS                                                                                     | MIN                      | TYP   | MAX   | UNITS  |

|-------------------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------|--------------------------|-------|-------|--------|

| <b>STATIC PERFORMANCE</b>                                   |                 |                                                                                                |                          |       |       |        |

| Resolution                                                  | N               |                                                                                                | 10                       |       |       | Bits   |

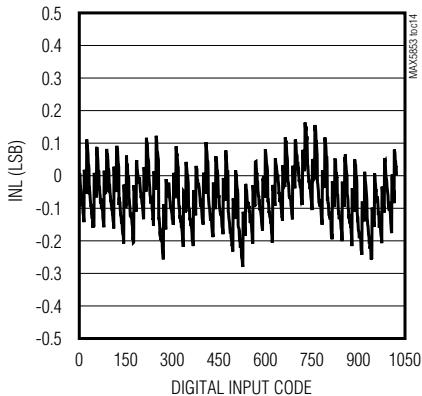

| Integral Nonlinearity                                       | INL             | R <sub>L</sub> = 0                                                                             | -1.0                     | ±0.25 | +1.0  | LSB    |

| Differential Nonlinearity                                   | DNL             | Guaranteed monotonic, R <sub>L</sub> = 0                                                       | -0.5                     | ±0.2  | +0.5  | LSB    |

| Offset Error                                                | V <sub>OS</sub> |                                                                                                | -0.5                     | ±0.1  | +0.5  | LSB    |

| Gain Error (See Also <i>Gain Error Definition Section</i> ) | GE              | Internal reference (Note1)                                                                     | -11.0                    | ±1.5  | +6.8  | %FSR   |

|                                                             |                 | External reference                                                                             | -6.25                    | ±0.7  | +4.10 |        |

| Gain-Error Temperature Drift                                |                 | Internal reference                                                                             |                          | ±150  |       | ppm/°C |

|                                                             |                 | External reference                                                                             |                          | ±100  |       |        |

| <b>DYNAMIC PERFORMANCE</b>                                  |                 |                                                                                                |                          |       |       |        |

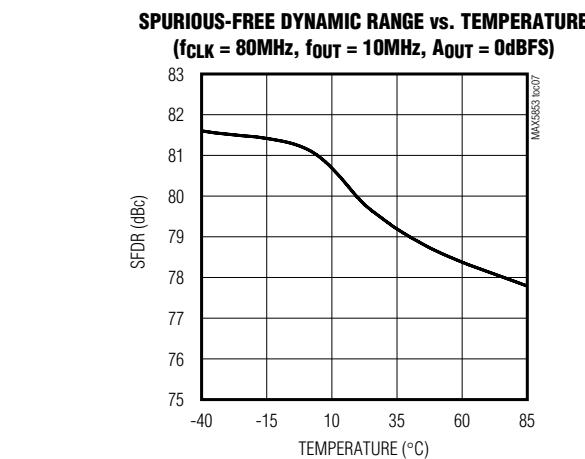

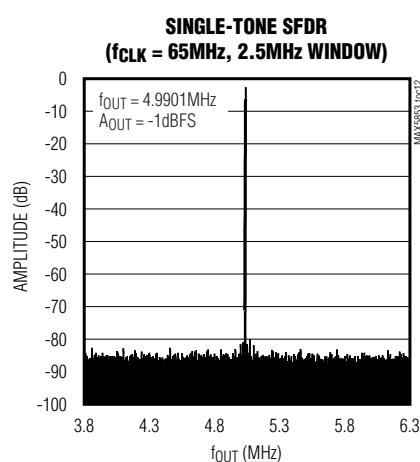

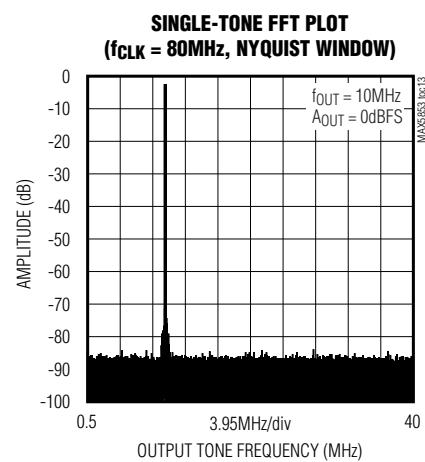

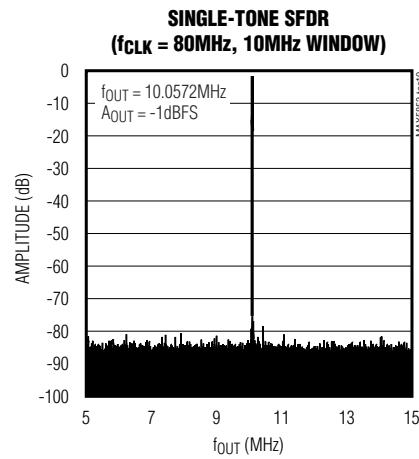

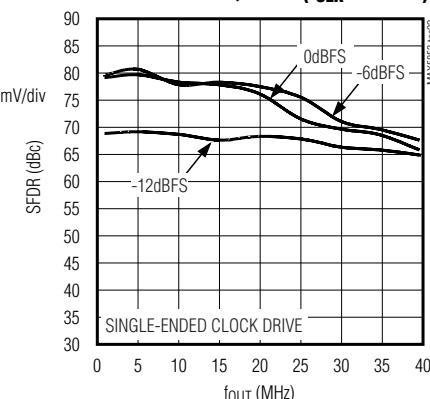

| Spurious-Free Dynamic Range to Nyquist                      | SFDR            | f <sub>CLK</sub> = 80MHz,<br>A <sub>OUT</sub> = -1dBFS                                         | f <sub>OUT</sub> = 10MHz | 69.5  | 78    | dBc    |

|                                                             |                 |                                                                                                | f <sub>OUT</sub> = 20MHz |       | 78    |        |

|                                                             |                 |                                                                                                | f <sub>OUT</sub> = 30MHz |       | 72    |        |

|                                                             |                 | f <sub>CLK</sub> = 44MHz,<br>A <sub>OUT</sub> = -1dBFS                                         | f <sub>OUT</sub> = 10MHz |       | 78    |        |

|                                                             |                 |                                                                                                | f <sub>OUT</sub> = 1MHz  |       | 79    |        |

| Spurious-Free Dynamic Range Within a Window                 | SFDR            | f <sub>CLK</sub> = 80MHz, f <sub>OUT</sub> = 10MHz,<br>A <sub>OUT</sub> = -1dBFS, span = 10MHz |                          |       | 85    | dBc    |

|                                                             |                 | f <sub>CLK</sub> = 65MHz, f <sub>OUT</sub> = 5MHz,<br>A <sub>OUT</sub> = -1dBFS, span = 2.5MHz |                          |       | 82    |        |

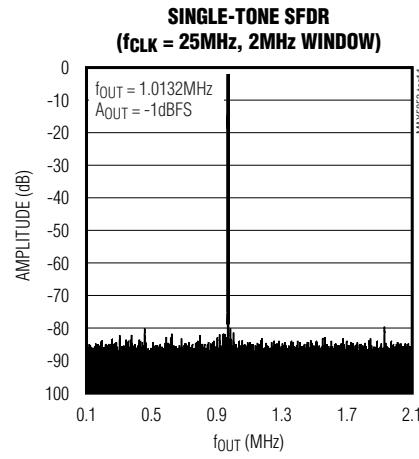

|                                                             |                 | f <sub>CLK</sub> = 25MHz, f <sub>OUT</sub> = 1MHz,<br>A <sub>OUT</sub> = -1dBFS, span = 2MHz   |                          |       | 82    |        |

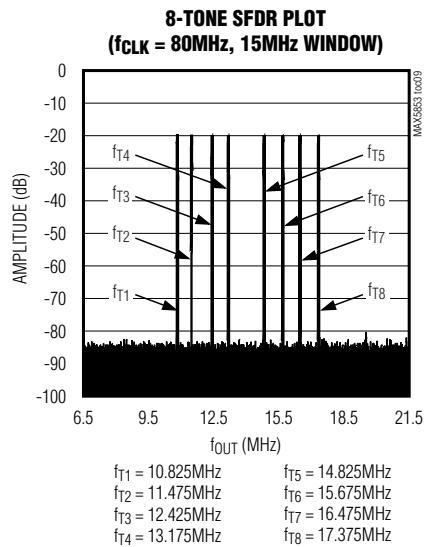

| Multitone Power Ratio to Nyquist                            | MTPR            | 8 tones at 400kHz spacing, f <sub>CLK</sub> = 78MHz,<br>f <sub>OUT</sub> = 15MHz to 18.2MHz    |                          |       | 74    | dBc    |

# デュアル、10ビット、80Msps、電流出力DAC

MAX5853

## ELECTRICAL CHARACTERISTICS (continued)

(AVDD = DVDD = CVDD = 3V, AGND = DGND = CGND = 0, fDAC = 80Msps, differential clock, external reference, VREF = 1.2V, IFS = 20mA, differential output, output amplitude = 0dBFS, TA = TMIN to TMAX, unless otherwise noted. TA  $\geq$  +25°C, guaranteed by production test. TA < +25°C guaranteed by design and characterization. Typical values are at TA = +25°C.)

| PARAMETER                                                                        | SYMBOL  | CONDITIONS                                                                       | MIN          | TYP  | MAX   | UNITS             |

|----------------------------------------------------------------------------------|---------|----------------------------------------------------------------------------------|--------------|------|-------|-------------------|

| Multitone Spurious-Free Dynamic Range Within a Window                            |         | 8 tones at 811kHz spacing, fCLK = 80MHz, fOUT = 10.8MHz to 17.2MHz, span = 15MHz | 76           |      |       | dBc               |

| Total Harmonic Distortion to Nyquist (2nd- Through 8th-Order Harmonics Included) | THD     | fCLK = 80MHz, AOUT = -1dBFS                                                      | fOUT = 10MHz | -76  |       | dBc               |

|                                                                                  |         |                                                                                  | fOUT = 20MHz | -75  |       |                   |

|                                                                                  |         |                                                                                  | fOUT = 30MHz | -70  |       |                   |

|                                                                                  |         | fCLK = 44MHz, AOUT = -1dBFS                                                      | fOUT = 10MHz | -76  |       |                   |

|                                                                                  |         | fCLK = 25MHz, AOUT = -1dBFS                                                      | fOUT = 1MHz  | -76  |       |                   |

| Output Channel-to-Channel Isolation                                              |         | fOUT = 10MHz                                                                     | 90           |      |       | dB                |

| Channel-to-Channel Gain Mismatch                                                 |         | fOUT = 10MHz, G[3:0] = 1000                                                      | 0.025        |      |       | dB                |

| Channel-to-Channel Phase Mismatch                                                |         | fOUT = 10MHz                                                                     | 0.05         |      |       | Degrees           |

| Signal-to-Noise Ratio to Nyquist                                                 | SNR     | fCLK = 80MHz, fOUT = 5MHz, IFS = 20mA                                            | 62           |      |       | dB                |

|                                                                                  |         | fCLK = 80MHz, fOUT = 5MHz, IFS = 5mA                                             | 62           |      |       |                   |

| Maximum DAC Conversion Rate                                                      | fDAC    | Interleaved mode disabled, IDE = 0                                               | 80           |      |       | Msps              |

|                                                                                  |         | Interleaved mode enabled, IDE = 1                                                | 80           |      |       |                   |

| Glitch Impulse                                                                   |         |                                                                                  | 5            |      |       | pV-s              |

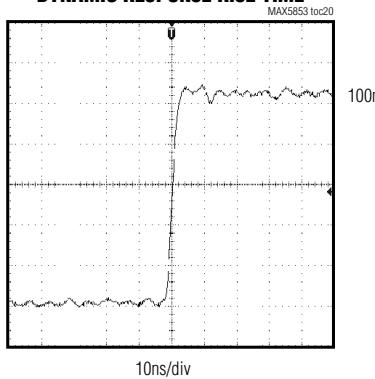

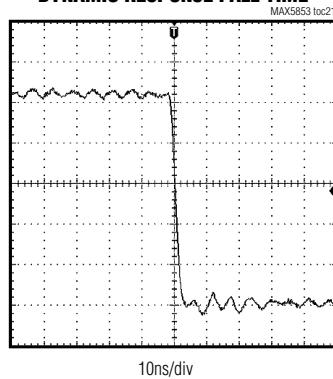

| Output Settling Time                                                             | tS      | To $\pm 0.1\%$ error band (Note 3)                                               | 12           |      |       | ns                |

| Output Rise Time                                                                 |         | 10% to 90% (Note 3)                                                              | 2.2          |      |       | ns                |

| Output Fall Time                                                                 |         | 90% to 10% (Note 3)                                                              | 2.2          |      |       | ns                |

| <b>ANALOG OUTPUT</b>                                                             |         |                                                                                  |              |      |       |                   |

| Full-Scale Output Current Range                                                  | IFS     |                                                                                  | 2            | 20   |       | mA                |

| Output Voltage Compliance Range                                                  |         |                                                                                  | -1.00        |      | +1.25 | V                 |

| Output Leakage Current                                                           |         | Shutdown or standby mode                                                         | -5           |      | +5    | $\mu$ A           |

| <b>REFERENCE</b>                                                                 |         |                                                                                  |              |      |       |                   |

| Internal-Reference Output Voltage                                                | VREFO   | $\overline{REN} = 0$                                                             | 1.13         | 1.24 | 1.32  | V                 |

| Internal-Reference Supply Rejection                                              |         | AVDD varied from 2.7V to 3.6V                                                    | 0.5          |      |       | mV/V              |

| Internal-Reference Output-Voltage Temperature Drift                              | TCVREFO | $\overline{REN} = 0$                                                             | $\pm 50$     |      |       | ppm/ $^{\circ}$ C |

# デュアル、10ビット、80MspS、電流出力DAC

## ELECTRICAL CHARACTERISTICS (continued)

(AVDD = DVDD = CVDD = 3V, AGND = DGND = CGND = 0, fDAC = 80Msps, differential clock, external reference, VREF = 1.2V, IFS = 20mA, differential output, output amplitude = 0dBFS, TA = TMIN to TMAX, unless otherwise noted. TA  $\geq$  +25°C, guaranteed by production test. TA < +25°C guaranteed by design and characterization. Typical values are at TA = +25°C.)

| PARAMETER                                                                     | SYMBOL           | CONDITIONS                                             | MIN            | TYP           | MAX  | UNITS     |

|-------------------------------------------------------------------------------|------------------|--------------------------------------------------------|----------------|---------------|------|-----------|

| Internal-Reference Output Drive Capability                                    |                  | $\overline{REN} = 0$                                   |                | 50            |      | $\mu$ A   |

| External-Reference Input Voltage Range                                        |                  | $\overline{REN} = 1$                                   | 0.10           | 1.2           | 1.32 | V         |

| Current Gain                                                                  | $I_{FS}/I_{REF}$ |                                                        |                | 32            |      | mA/mA     |

| <b>LOGIC INPUTS</b> (DA9–DA0, DB9–DB0, $\overline{CW}$ )                      |                  |                                                        |                |               |      |           |

| Digital Input-Voltage High                                                    | $V_{IH}$         |                                                        | 0.65 x<br>DVDD |               |      | V         |

| Digital Input-Voltage Low                                                     | $V_{IL}$         |                                                        |                | 0.3 x<br>DVDD |      | V         |

| Digital Input Current                                                         | $I_{IN}$         |                                                        | -1             |               | +1   | $\mu$ A   |

| Digital Input Capacitance                                                     | $C_{IN}$         |                                                        |                | 3             |      | pF        |

| <b>SINGLE-ENDED CLOCK INPUT/OUTPUT AND DCE INPUT</b> (CLK, $\overline{DCE}$ ) |                  |                                                        |                |               |      |           |

| Digital Input-Voltage High                                                    | $V_{IH}$         | $\overline{DCE} = 1$                                   | 0.65 x<br>CVDD |               |      | V         |

| Digital Input-Voltage Low                                                     | $V_{IL}$         | $\overline{DCE} = 1$                                   |                | 0.3 x<br>CVDD |      | V         |

| Digital Input Current                                                         | $I_{IN}$         | $\overline{DCE} = 1$                                   | -1             |               | +1   | $\mu$ A   |

| Digital Input Capacitance                                                     | $C_{IN}$         | $\overline{DCE} = 1$                                   |                | 3             |      | pF        |

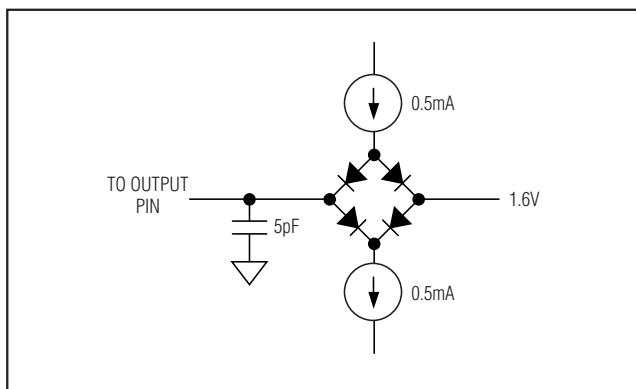

| Digital Output-Voltage High                                                   | $V_{OH}$         | $\overline{DCE} = 0$ , $I_{SOURCE} = 0.5$ mA, Figure 1 | 0.9 x<br>CVDD  |               |      | V         |

| Digital Output-Voltage Low                                                    | $V_{OL}$         | $\overline{DCE} = 0$ , $I_{SINK} = 0.5$ mA, Figure 1   |                | 0.1 x<br>CVDD |      | V         |

| <b>DIFFERENTIAL CLOCK INPUTS</b> (CLKXP/CLKXN)                                |                  |                                                        |                |               |      |           |

| Differential Clock Input Internal Bias                                        |                  |                                                        |                | CVDD / 2      |      | V         |

| Differential Clock Input Swing                                                |                  |                                                        | 0.5            |               |      | V         |

| Clock Input Impedance                                                         |                  | Measured single ended                                  |                | 5             |      | $k\Omega$ |

| <b>POWER REQUIREMENTS</b>                                                     |                  |                                                        |                |               |      |           |

| Analog Power-Supply Voltage                                                   | AVDD             |                                                        | 2.7            | 3             | 3.6  | V         |

| Digital Power-Supply Voltage                                                  | DVDD             |                                                        | 2.7            | 3             | 3.6  | V         |

| Clock Power-Supply Voltage                                                    | CVDD             |                                                        | 2.7            | 3             | 3.6  | V         |

| Analog Supply Current                                                         | $I_{AVDD}$       | $I_{FS} = 20$ mA (Note 2), single-ended clock mode     |                | 43.2          | 46   | mA        |

|                                                                               |                  | $I_{FS} = 20$ mA (Note 2), differential clock mode     |                | 43.2          |      |           |

|                                                                               |                  | $I_{FS} = 2$ mA (Note 2), single-ended clock mode      |                | 5             |      |           |

|                                                                               |                  | $I_{FS} = 2$ mA (Note 2), differential clock mode      |                | 5             |      |           |

# デュアル、10ビット、80Msps、電流出力DAC

MAX5853

## ELECTRICAL CHARACTERISTICS (continued)

(AVDD = DVDD = CVDD = 3V, AGND = DGND = CGND = 0, fDAC = 80Msps, differential clock, external reference, VREF = 1.2V, IFS = 20mA, differential output, output amplitude = 0dBFS, TA = TMIN to TMAX, unless otherwise noted. TA  $\geq$  +25°C, guaranteed by production test. TA < +25°C guaranteed by design and characterization. Typical values are at TA = +25°C.)

| PARAMETER               | SYMBOL               | CONDITIONS                                                | MIN                 | TYP   | MAX  | UNITS |

|-------------------------|----------------------|-----------------------------------------------------------|---------------------|-------|------|-------|

| Digital Supply Current  | IDVDD                | IFS = 20mA (Note 2), single-ended clock mode              |                     | 3.4   | 4    | mA    |

|                         |                      | IFS = 20mA (Note 2), differential clock mode              |                     | 3.4   |      |       |

| Clock Supply Current    | ICVDD                | Single-ended clock mode ( $\overline{DCE} = 1$ ) (Note 2) |                     | 11.1  | 13.5 | mA    |

|                         |                      | Differential clock mode ( $\overline{DCE} = 0$ ) (Note 2) |                     | 16.7  |      |       |

| Total Standby Current   | I <sub>STANDBY</sub> | I <sub>AVDD</sub> + I <sub>DVDD</sub> + I <sub>CVDD</sub> |                     | 3.1   | 3.7  | mA    |

| Total Shutdown Current  | I <sub>SHDN</sub>    | I <sub>AVDD</sub> + I <sub>DVDD</sub> + I <sub>CVDD</sub> |                     | 1     |      | μA    |

| Total Power Dissipation | P <sub>TOT</sub>     | Single-ended clock mode ( $DCE = 1$ )                     | IFS = 20mA (Note 2) | 173   | 191  | mW    |

|                         |                      |                                                           | IFS = 2mA (Note 2)  | 58    |      |       |

|                         |                      | Differential clock mode ( $DCE = 0$ )                     | IFS = 20mA (Note 2) | 190   |      |       |

|                         |                      |                                                           | IFS = 2mA (Note 2)  | 75    |      |       |

|                         |                      | Standby                                                   |                     | 9.3   | 11.1 |       |

|                         |                      | Shutdown                                                  |                     | 0.003 |      |       |

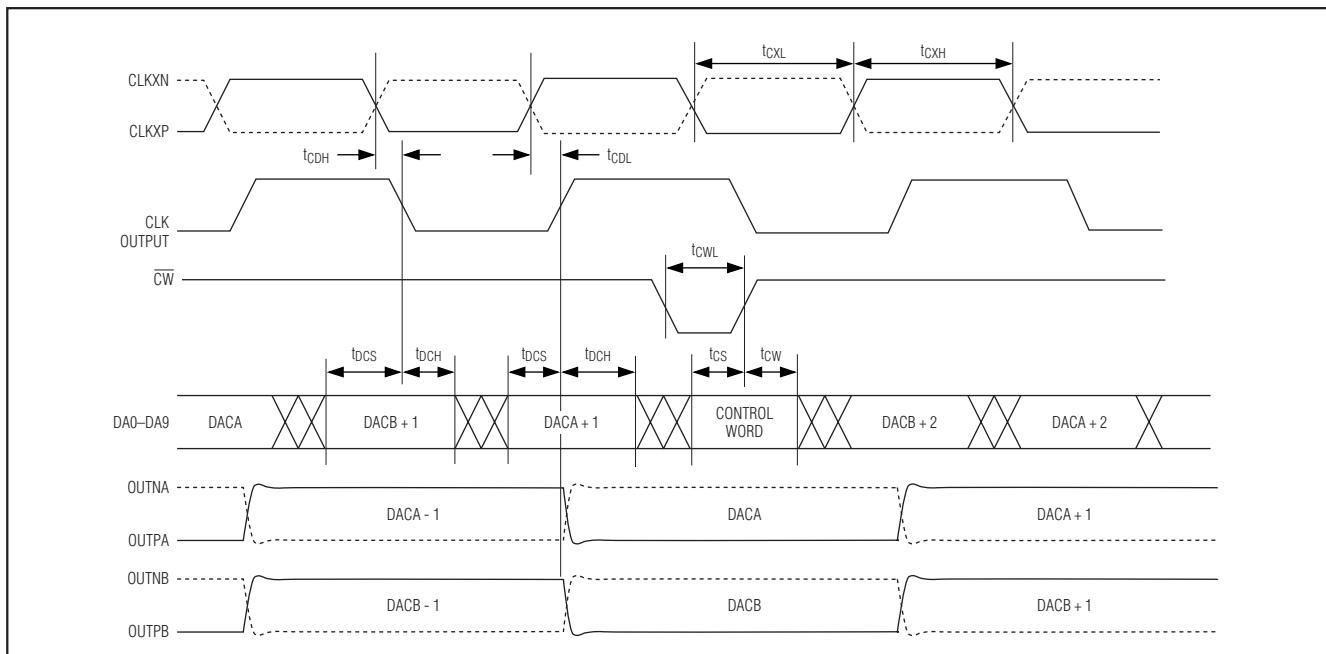

## TIMING CHARACTERISTICS (Figures 5 and 6)

|                                                 |                  |                                                           |      |              |

|-------------------------------------------------|------------------|-----------------------------------------------------------|------|--------------|

| Propagation Delay                               |                  |                                                           | 1    | Clock cycles |

| DAC Data to CLK Rise/Fall Setup Time            | t <sub>DCS</sub> | Single-ended clock mode ( $\overline{DCE} = 1$ ) (Note 4) | 1.2  | ns           |

|                                                 |                  | Differential clock mode ( $\overline{DCE} = 0$ ) (Note 4) | 2.7  |              |

| DAC Data to CLK Rise/Fall Hold Time             | t <sub>DCH</sub> | Single-ended clock mode ( $\overline{DCE} = 1$ ) (Note 4) | 0.8  | ns           |

|                                                 |                  | Differential clock mode ( $\overline{DCE} = 0$ ) (Note 4) | -0.5 |              |

| Control Word to $\overline{CW}$ Rise Setup Time | t <sub>CWS</sub> |                                                           | 2.5  | ns           |

| Control Word to $\overline{CW}$ Rise Hold Time  | t <sub>CWH</sub> |                                                           | 2.5  | ns           |

| $\overline{CW}$ High Time                       | t <sub>CWH</sub> |                                                           | 5    | ns           |

| $\overline{CW}$ Low Time                        | t <sub>CWL</sub> |                                                           | 5    | ns           |

# デュアル、10ビット、80MspS、電流出力DAC

## ELECTRICAL CHARACTERISTICS (continued)

(AVDD = DVDD = CVDD = 3V, AGND = DGND = CGND = 0, fDAC = 80Msps, differential clock, external reference, VREF = 1.2V, IFS = 20mA, differential output, output amplitude = 0dBFS, TA = TMIN to TMAX, unless otherwise noted. TA  $\geq$  +25°C, guaranteed by production test. TA < +25°C guaranteed by design and characterization. Typical values are at TA = +25°C.)

| PARAMETER                                             | SYMBOL | CONDITIONS           | MIN | TYP | MAX | UNITS |

|-------------------------------------------------------|--------|----------------------|-----|-----|-----|-------|

| DACEN = 1 to VOUT Stable Time (Coming Out of Standby) | tSTB   |                      |     | 3   |     | μs    |

| PD = 0 to VOUT Stable Time (Coming Out of Power-Down) | tSHDN  |                      |     | 500 |     | μs    |

| Maximum Clock Frequency at CLKXP/CLKXN Input          | fCLK   |                      | 80  |     |     | MHz   |

| Clock High Time                                       | tCXH   | CLKXP or CLKXN input | 3   |     |     | ns    |

| Clock Low Time                                        | tCXL   | CLKXP or CLKXN input | 3   |     |     | ns    |

| CLKXP Rise to CLK Output Rise Delay                   | tCDH   | $\overline{DCE} = 0$ |     | 2.7 |     | ns    |

| CLKXP Fall to CLK Output Fall Delay                   | tCDL   | $\overline{DCE} = 0$ |     | 2.7 |     | ns    |

**Note 1:** Including the internal reference voltage tolerance and reference amplifier offset.

**Note 2:** fDAC = 80Msps, fOUT = 10MHz.

**Note 3:** Measured single ended with 50Ω load and complementary output connected to ground.

**Note 4:** Guaranteed by design, not production tested.

図1. CLK出力用の負荷試験回路

# デュアル、10ビット、80MspS、電流出力Dac

MAX5853

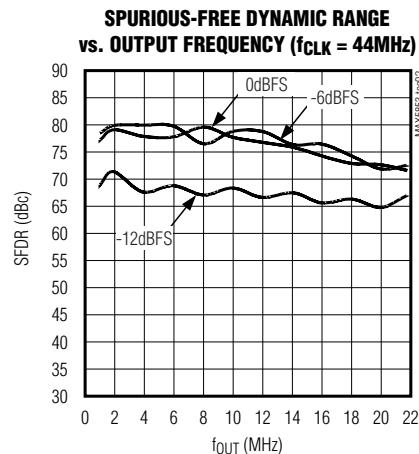

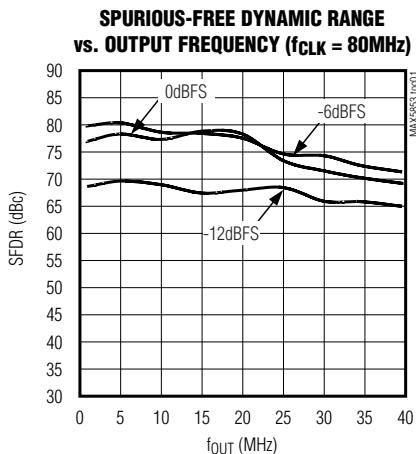

## 標準動作特性

(AV<sub>DD</sub> = DV<sub>DD</sub> = CV<sub>DD</sub> = 3V, AGND = DGND = CGND = 0, external reference, I<sub>FS</sub> = 20mA, differential output, differential clock (unless otherwise noted), T<sub>A</sub> = +25°C.)

# デュアル、10ビット、80MspS、電流出力DAC

## 標準動作特性(続き)

(AV<sub>DD</sub> = DV<sub>DD</sub> = CV<sub>DD</sub> = 3V, AGND = DGND = CGND = 0, external reference, I<sub>FS</sub> = 20mA, differential output, differential clock (unless otherwise noted), T<sub>A</sub> = +25°C.)

# デュアル、10ビット、80MspS、電流出力Dac

MAX5853

## 標準動作特性(続き)

(AVDD = DVDD = CVDD = 3V, AGND = DGND = CGND = 0, external reference, IFS = 20mA, differential output, differential clock (unless otherwise noted), TA = +25°C.)

INTEGRAL NONLINEARITY

vs. DIGITAL INPUT CODE

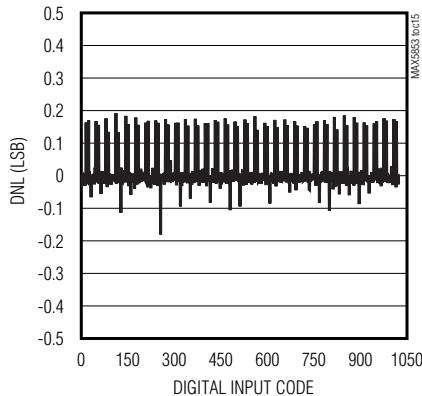

DIFFERENTIAL NONLINEARITY

vs. DIGITAL INPUT CODE

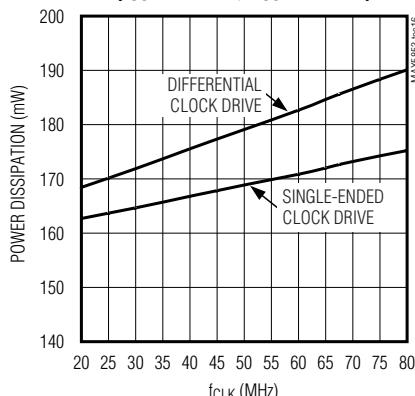

POWER DISSIPATION vs. CLOCK FREQUENCY

(fOUT = 10MHz, AOUT = 0dBFS)

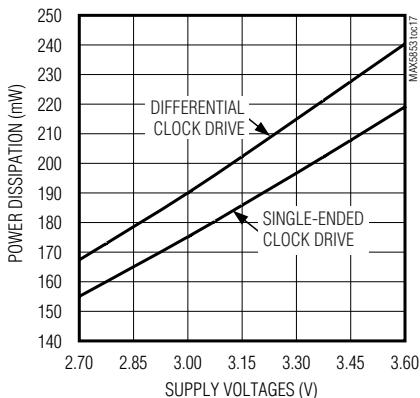

POWER DISSIPATION vs. SUPPLY VOLTAGES

(fCLK = 80MHz, fOUT = 10MHz)

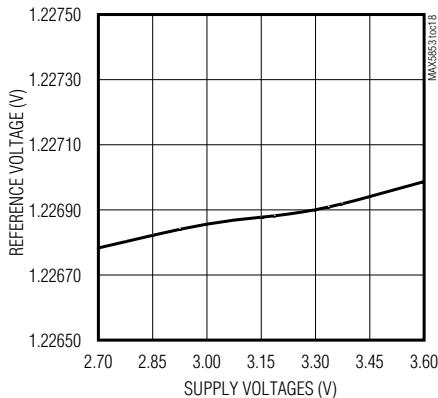

REFERENCE VOLTAGE vs. SUPPLY VOLTAGES

(fCLK = 80MHz, fOUT = 10MHz)

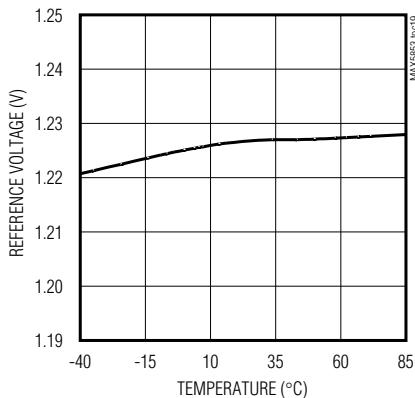

REFERENCE VOLTAGE vs. TEMPERATURE

DYNAMIC RESPONSE RISE TIME

DYNAMIC RESPONSE FALL TIME

SPURIOUS-FREE DYNAMIC RANGE

vs. OUTPUT FREQUENCY (fCLK = 80MHz)

# デュアル、10ビット、80MspS、電流出力DAG

## 端子説明

| 端子     | 名称               | 機能                                                                                                                                                                                                                   |

|--------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | DA9/PD           | チャネルA入力データビット9(MSB)/パワーダウン                                                                                                                                                                                           |

| 2      | DA8/DACEN        | チャネルA入力データビット8/DACイネーブル制御                                                                                                                                                                                            |

| 3      | DA7/IDE          | チャネルA入力データビット7/インターブデータイネーブル                                                                                                                                                                                         |

| 4      | DA6/REN          | チャネルA入力データビット6/リファレンスイネーブル。 $\overline{REN} = 0$ に設定すると、内部リファレンスをイネーブル。 $\overline{REN} = 1$ に設定すると、内部リファレンスをディセーブル。                                                                                                 |

| 5      | DA5/G3           | チャネルA入力データビット5/チャネルA利得調整ビット3                                                                                                                                                                                         |

| 6      | DA4/G2           | チャネルA入力データビット4/チャネルA利得調整ビット2                                                                                                                                                                                         |

| 7      | DA3/G1           | チャネルA入力データビット3/チャネルA利得調整ビット1                                                                                                                                                                                         |

| 8      | DA2/G0           | チャネルA入力データビット2/チャネルA利得調整ビット0                                                                                                                                                                                         |

| 9      | DA1              | チャネルA入力データビット1                                                                                                                                                                                                       |

| 10     | DA0              | チャネルA入力データビット0(LSB)                                                                                                                                                                                                  |

| 11     | DB9              | チャネルB入力データビット9(MSB)                                                                                                                                                                                                  |

| 12     | DB8              | チャネルB入力データビット8                                                                                                                                                                                                       |

| 13     | DB7              | チャネルB入力データビット7                                                                                                                                                                                                       |

| 14     | DB6              | チャネルB入力データビット6                                                                                                                                                                                                       |

| 15     | DB5              | チャネルB入力データビット5                                                                                                                                                                                                       |

| 16     | DV <sub>DD</sub> | デジタル電源入力。詳細については、「電源、バイパス、デカップリング、及びレイアウト」の項を参照してください。                                                                                                                                                               |

| 17     | DGND             | デジタルグランド                                                                                                                                                                                                             |

| 18     | DB4              | チャネルB入力データビット4                                                                                                                                                                                                       |

| 19     | DB3              | チャネルB入力データビット3                                                                                                                                                                                                       |

| 20     | DB2              | チャネルB入力データビット2                                                                                                                                                                                                       |

| 21     | DB1              | チャネルB入力データビット1                                                                                                                                                                                                       |

| 22     | DB0              | チャネルB入力データビット0(LSB)                                                                                                                                                                                                  |

| 23     | $\overline{CW}$  | アクティブロー制御ワード書き込みパルス。制御ワードは、 $\overline{CW}$ の立上りエッジでラッチされます。                                                                                                                                                         |

| 24     | $\overline{DCE}$ | アクティブロー差動クロックイネーブル入力。差動クロック入力CLKXP及びCLKXNをイネーブルするには、 $\overline{DCE}$ をローにします。差動クロック入力をディセーブルして、シングルエンドCLK入力をイネーブルするには、 $\overline{DCE}$ をハイにします。                                                                    |

| 25     | CLKXP            | 正差動クロック入力。 $\overline{DCE} = 0$ の場合に、CLKXP及びCLKXNはイネーブルされます。 $\overline{DCE} = 1$ の場合に、CLKXP及びCLKXNはディセーブルされます。差動クロックがディセーブルされている場合は、CLKXPをCGNDに接続します。                                                               |

| 26     | CLKXN            | 負差動クロック入力。 $\overline{DCE} = 0$ の場合に、CLKXP及びCLKXNはイネーブルされます。 $\overline{DCE} = 1$ の場合に、CLKXP及びCLKXNはディセーブルされます。差動クロックがディセーブルされている場合は、CLKXNをCV <sub>DD</sub> に接続します。                                                  |

| 27, 30 | CV <sub>DD</sub> | クロック電源入力。詳細については、「電源、バイパス、デカップリング、及びレイアウト」の項を参照してください。                                                                                                                                                               |

| 28     | CLK              | シングルエンドクロック入力/出力。差動クロックがディセーブルされている場合は( $\overline{DCE} = 1$ )、CLKはシングルエンド変換クロック入力になります。差動クロックがイネーブルされている場合は( $\overline{DCE} = 0$ )、CLKは差動クロック入力CLKXP及びCLKXNを反映(ミラー)するシングルエンド出力です。CLKの詳細については、「クロックモード」の項を参照してください。 |

| 29     | CGND             | クロックグランド                                                                                                                                                                                                             |

| 31     | REFO             | リファレンス入力/出力。REFOは、内部リファレンスがディセーブルされている場合はリファレンス入力として機能します。1.24Vの内部リファレンスがイネーブルされている場合は、REFOは内部リファレンスの出力として機能します。内部リファレンスがイネーブルされている場合は、0.1 $\mu$ FコンデンサでREFOからAGNDにバイパスします。                                          |

# デュアル、10ビット、80Mps、電流出力DAC

MAX5853

## 端子説明(続き)

| 端子     | 名称    | 機能                                                                                                     |

|--------|-------|--------------------------------------------------------------------------------------------------------|

| 32     | REFR  | フルスケール電流調整。出力フルスケール電流を設定するには、外付け抵抗RSETをREFRとAGNDの間に接続します。出力フルスケール電流は、 $32 \times V_{REF0}/R_{SET}$ です。 |

| 33, 39 | AVDD  | アナログ電源入力。詳細については、「電源、バイパス、デカップリング、及びレイアウト」の項を参照してください。                                                 |

| 34     | OUTNB | チャネルB負アナログ電流出力                                                                                         |

| 35     | OUTPB | チャネルB正アナログ電流出力                                                                                         |

| 36, 40 | AGND  | アナロググランド                                                                                               |

| 37     | OUTNA | チャネルA負アナログ電流出力                                                                                         |

| 38     | OUTPA | チャネルA正アナログ電流出力                                                                                         |

| —      | EP    | 裏面放熱パドル。EPを全グランドプレーンの共通ポイントに接続します。                                                                     |

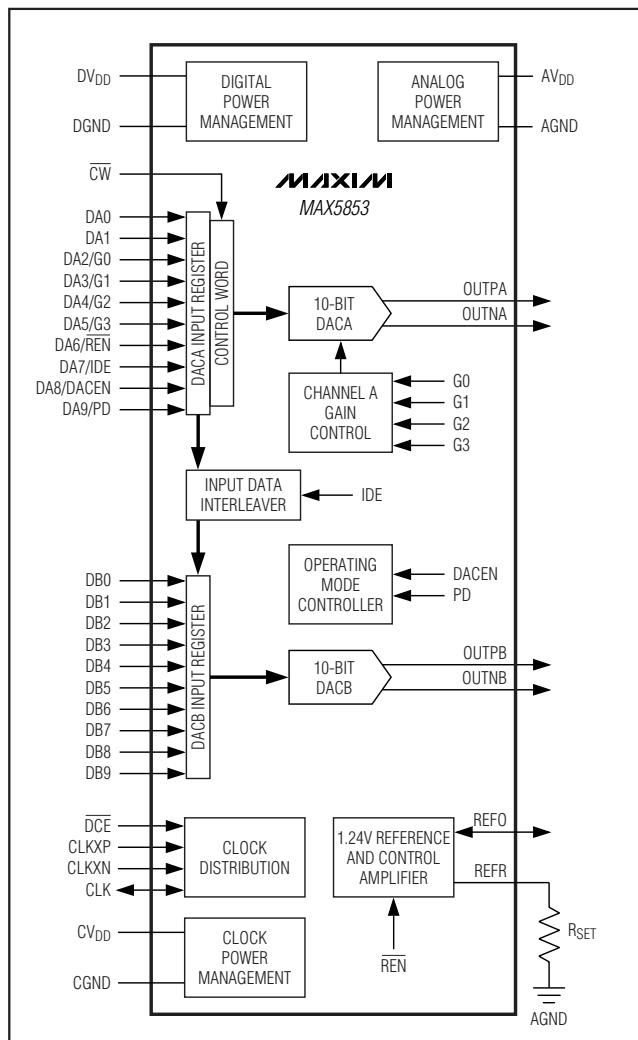

図2. 略図

## 詳細

MAX5853は、デュアル、高速、10ビット、電流出力、デジタル-アナログコンバータ(DAC)で、低歪みのアナログ信号再生が必要な通信システムにおいて優れた性能を発揮します。MAX5853は、2個のDACと1.24V内部リファレンスを内蔵しています(図2)。DACの電流出力を差動動作またはシングルエンド動作に設定することができます。フルスケール出力電流は2mA～20mAの範囲で可変で、電力消費と利得制御を最適化します。MAX5853は入力データを80MHz DAC変換レートで受け入れます。入力はクロックの立上りエッジでラッチされ、また出力は次の立上りエッジでラッチされます。

MAX5853は、標準、スタンバイ、及びパワーダウンの3種類の動作モードを備えています(表2)。これらのモードによって、効率的に電源を管理することができます。パワーダウンモードでは、MAX5853の消費電流はわずか1µAです。スタンバイモードから標準DAC動作までのウェイクアップ時間は、3µsです。

## DACの設定

チャネルAのデータポート経由で送られる8ビット制御ワードを使って、MAX5853の利得マッチング、リファレンス、及び動作モードを設定します。制御ワードは、 $\overline{CW}$ の立上りエッジでラッチされます。 $\overline{CW}$ は、DACクロックから独立しています。制御ワードがDACに書き込まれると、DACのクロックは常時作動状態を維持することができます。表1及び表2は、制御ワードのフォーマットと機能を示しています。

チャネルAの利得を、ユーザシステム内の2つのチャネル間で利得マッチングを行うように、設定することができます。ビットG3からG0を使って、チャネルAの利得を0.05dB刻みで-0.4dB～0.35dBの範囲で設定することができます(表3参照)。

# デュアル、10ビット、80Msps、電流出力D/Aコンバータ

表1. 制御ワードのフォーマット及び機能

| MSB          |                                                                                                                                                                                                                                                                                                               |     |     |    |    |    |    |   |   | LSB |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|----|----|----|----|---|---|-----|

| PD           | DACEN                                                                                                                                                                                                                                                                                                         | IDE | REN | G3 | G2 | G1 | G0 | X | X |     |

| CONTROL WORD | FUNCTION                                                                                                                                                                                                                                                                                                      |     |     |    |    |    |    |   |   |     |

| PD           | Power-Down. The part enters power-down mode if PD = 1.                                                                                                                                                                                                                                                        |     |     |    |    |    |    |   |   |     |

| DACEN        | DAC Enable. When DACEN = 0 and PD = 0, the part enters standby mode.                                                                                                                                                                                                                                          |     |     |    |    |    |    |   |   |     |

| IDE          | Interleaved Data Mode. IDE = 1 enables the interleaved data mode. In this mode, digital data for both channels is applied through channel A in a multiplexed fashion. Channel B data is written on the falling edge of the clock signal and channel A data is written on the rising edge of the clock signal. |     |     |    |    |    |    |   |   |     |

| REN          | Reference Enable Bit. REN = 0 activates the internal reference. REN = 1 disables the internal reference and requires the user to apply an external reference between 0.1V to 1.32V.                                                                                                                           |     |     |    |    |    |    |   |   |     |

| G3           | Bit 3 (MSB) of Gain Adjust Word                                                                                                                                                                                                                                                                               |     |     |    |    |    |    |   |   |     |

| G2           | Bit 2 of Gain Adjust Word                                                                                                                                                                                                                                                                                     |     |     |    |    |    |    |   |   |     |

| G1           | Bit 1 of Gain Adjust Word                                                                                                                                                                                                                                                                                     |     |     |    |    |    |    |   |   |     |

| G0           | Bit 0 (LSB) of Gain Adjust Word                                                                                                                                                                                                                                                                               |     |     |    |    |    |    |   |   |     |

表2. 設定モード

| MODE                                                                       | PD | DACEN | IDE | REN |

|----------------------------------------------------------------------------|----|-------|-----|-----|

| Normal operation;<br>noninterleaved inputs;<br>internal reference active   | 0  | 1     | 0   | 0   |

| Normal operation;<br>noninterleaved inputs;<br>internal reference disabled | 0  | 1     | 0   | 1   |

| Normal operation;<br>interleaved inputs;<br>internal reference disabled    | 0  | 1     | 1   | 1   |

| Standby                                                                    | 0  | 0     | X   | X   |

| Power-down                                                                 | 1  | X     | X   | X   |

| Power-up                                                                   | 0  | 1     | X   | X   |

X = 任意

表3. 利得差の設定

| GAIN ADJUSTMENT ON CHANNEL A (dB) | G3 | G2 | G1 | G0 |

|-----------------------------------|----|----|----|----|

| +0.4                              | 0  | 0  | 0  | 0  |

| 0                                 | 1  | 0  | 0  | 0  |

| -0.35                             | 1  | 1  | 1  | 1  |

## デバイスのパワーアップ及び動作状態

パワーアップ時のMAX5853のデフォルト設定は、内部リファレンス、利得が0dBの非インタリーブ入力モード、及び完全動作コンバータです。シャットダウンではMAX5853の電流消費はわずか1 $\mu$ Aで、スタンバイでは3.1mAです。スタンバイモードから標準動作までのウェイクアップ時間は、3 $\mu$ sです。

## クロックモード

MAX5853はシングルエンドCMOS及び差動クロックモード動作に対応し、最高80Mspsの更新レートをサポートしています。これらのモードは、 $\overline{DCE}$ と呼ばれるアクティブロー制御ラインを通じて選択されます。シングルエンドクロックモード( $\overline{DCE} = 1$ )では、CLK端子は入力として機能します。この入力はユーザ準備のクロック信号を受け付けます。データは、クロックの立上りエッジでコンバータに書き込まれます。DAC出力(前のデータであったものは)は、同じエッジで同時に更新されます。

$\overline{DCE}$ 端子がローにプルダウンされている場合は、MAX5853は差動クロックモードで動作します。このモードでは、クロック信号を差動クロック入力端子CLKXP/CLKXNに印加する必要があります。差動入力は0.5V<sub>p-p</sub>以上の入力範囲と1V~(CV<sub>DD</sub> - 0.5V)のコモンモード範囲に対応しているため、低入力振幅クロックの駆動に最適です。また、CLKXP/CLKXNによって、ジッタを最低限に抑制し、また水晶発振器をMAX5853に直接接続することもできます。

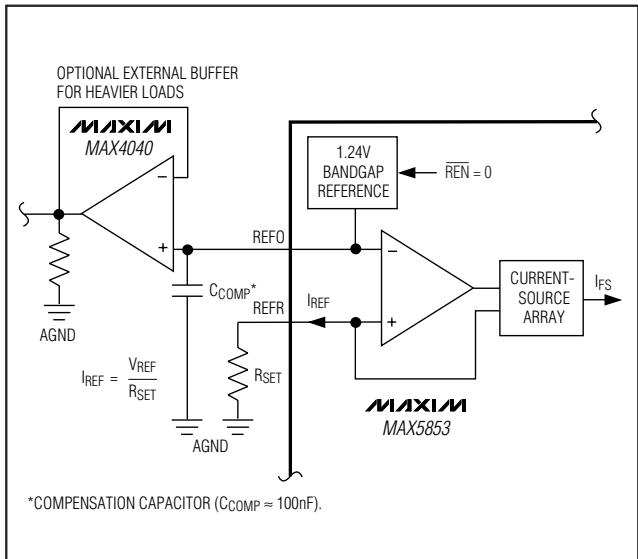

図3. 1.24V内部リファレンス及び制御アンプを使って $I_{FS}$ を設定

図4. 外部リファレンス付MAX5853

CLK端子が出力になっており、差動クロック信号をシングルエンドで供給します。これを使って、入力データを同期化することができます。データは、CLK信号の立上りエッジでデバイスに書き込まれます。

## 内部リファレンス及び制御アンプ

MAX5853は、50ppm/°C、1.24V、低ノイズ、バンドギャップリファレンスを内蔵しています。このリファレンスをディセーブルにして、外部リファレンス電圧と置き換えることができます。を、REFOは、外部リファレンス入力、または内部リファレンス出力のいずれかとして機能します。 $\overline{REN} = 0$ の場合は、内部リファレンスが選択され、REFOは1.24V (50µA)の出力を供給します。重負荷を駆動する際、外付けアンプを使ってREFOをバッファします。

また、MAX5853は、デバイスの両出力のフルスケール出力電流( $I_{FS}$ )を同時に安定化するために制御アンプを使用します。その出力電流は、次のように算出します。

$$I_{FS} = 32 \times I_{REF}$$

ここで、 $I_{REF}$ はリファレンス出力電流( $I_{REF} = V_{REF0} / R_{SET}$ )で、 $I_{FS}$ はフルスケール出力電流です。 $R_{SET}$ は、MAX5853のアンプ出力電流を決定するリファレンス抵抗です(図3)。この電流は電流ソースアレイにミラーされ、このアレイで $I_{FS}$ はマッチングした電流セグメント間に等分配され、それらの合計はDACの有効出力電流読み取り値になります。

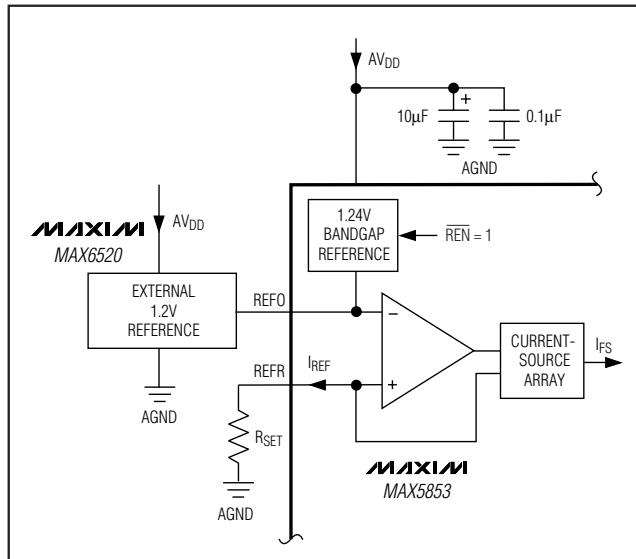

## 外部リファレンス

MAX5853の内部リファレンスをディセーブルするには、 $\overline{REN} = 1$ に設定します。温度が安定した外部リファレンスを印加して、REFO端子を駆動し、フルスケール出力を設定します(図4)。精度とドリフト性能を改善するためには、1.2V、25ppm/°CのMAX6520バンドギャップリファレンスなどの固定出力電圧リファレンスを選択します。

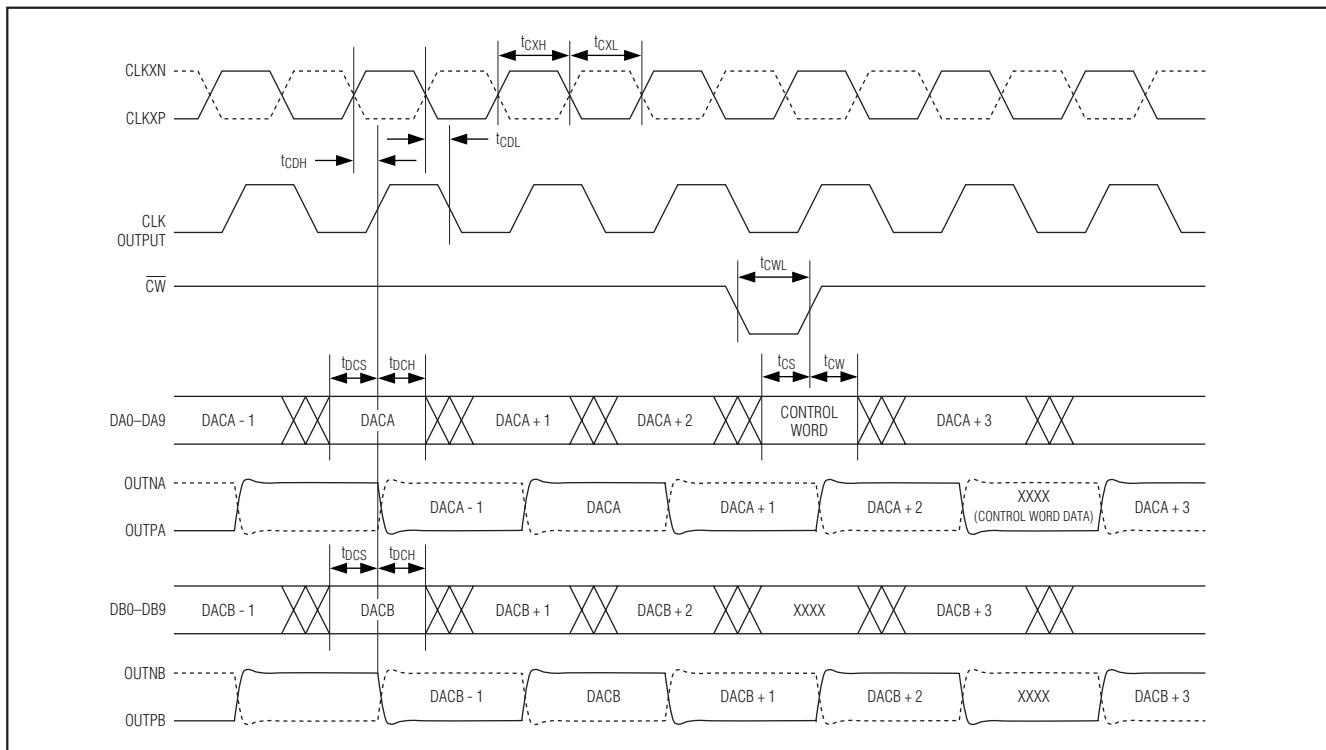

## タイミングの詳細

MAX5853は、入力データと最高80MspsのDAC変換レートに対応します。入力はクロックの立上りエッジでラッチされ、また出力は次の立上りエッジでラッチされます。

図5は、非インタリーブモードでの2つのDACの書き込みサイクルを示しています。

また、MAX5853はインタリーブデータモードで動作することもできます。IDEビットをハイレベルに設定すると、このモードが作動します(表1及び表2)。インタリーブモードでは、両DACチャネルのデータは入力ポートAを通じて書き込まれます。チャネルBのデータはクロック信号の立下りエッジで書き込まれ、次にチャネルAのデータがクロック信号の次の立上りエッジで書き込まれます。両DAC出力(チャネルA及びB)は、クロックの次の立上りエッジで同時に更新されます。低データレートが許容可能で10ビット単一バスでのインターフェースが必要なアプリケーションに、インタリーブデータモードは適しています(図6)。

# デュアル、10ビット、80MspS、電流出力DAC

図5. 非インタリーブデータモードのタイミング図(IDE = 0)

図6. インタリーブデータモードのタイミング図(IDE = 1)

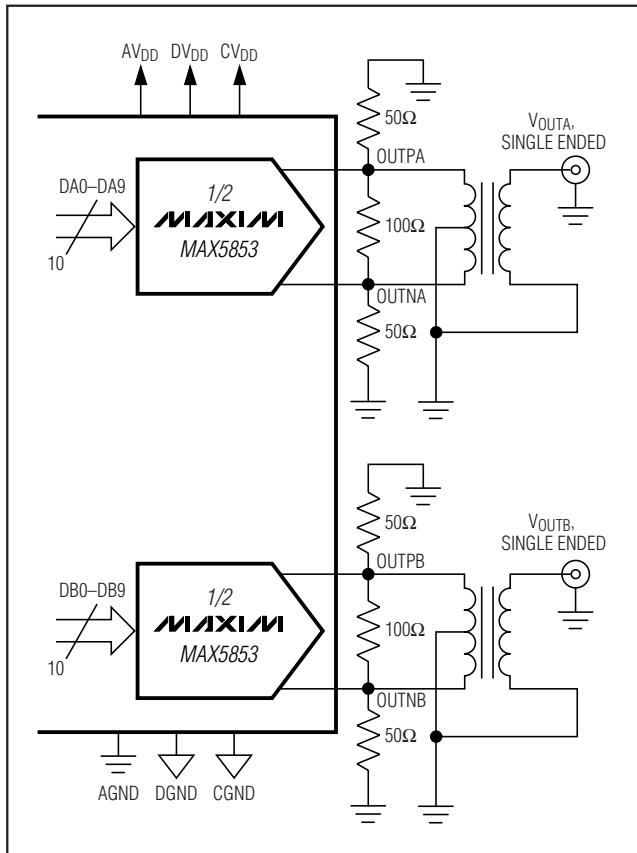

図7. 差動からシングルエンドへの変換を行う出力トランス付

アプリケーション

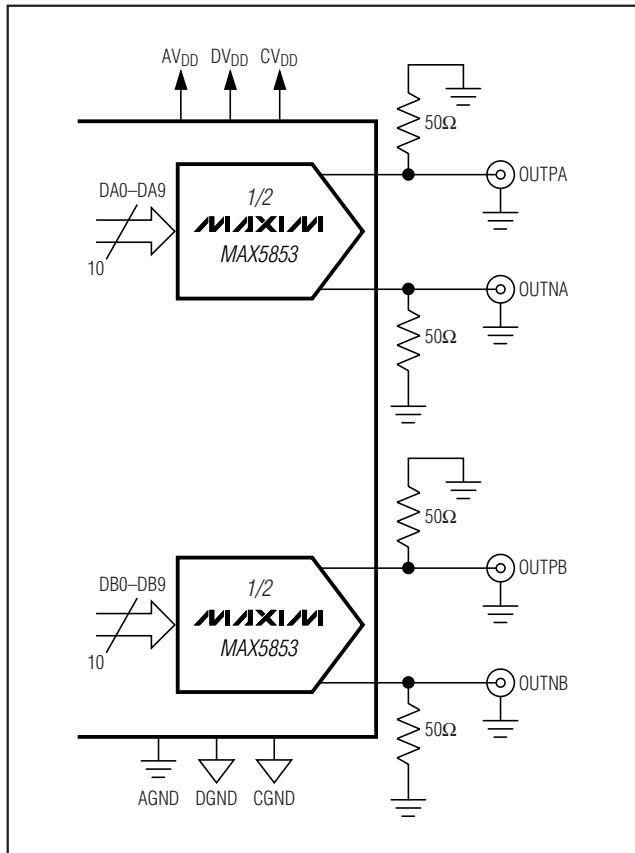

図8. DC結合差動出力付アプリケーション

## アプリケーション情報

### 差動からシングルエンドへの変換

MAX5853は優れたダイナミック性能を発揮して、OFDMの高次QAM変調などの各種変調方式を統合することができます。

図7は、差動からシングルエンドへの必要な信号変換を行う出力トランス付の標準アプリケーション回路を示しています。この構成でMAX5853は差動モードで動作するため、偶数次高調波が低減し、利用出力電力が増大します。

### 差動DC結合構成

図8は、差動DC結合モードで動作するMAX5853出力を示しています。アナログ直交アップコンバータを使用し、I/Q合成用にベースバンドサンプリング、デュアルチャネル、高速DACが必要な通信システムで、この構成を用いることができます。こうしたアプリケーションで、情報帯域幅は10MHzから数百キロヘルツまで拡大することができます。高価で大容量の結合コンデンサで問題となる長い放電時定数を避けるには、DC結合が適して

います。アナログ直交アップコンバータは、0.7V~1.0V(typ)のDCコモンモード入力要件を備えています。MAX5853差動I/Q出力は、2.85V(±5%)の単一電源から電源供給される場合、規定の0.7V~1.0VのDCコモンモードレベルで、任意のフルスケールレベルを維持することができます。MAX5853はダイナミックレンジのわずかな低減でこの低電力要件を満たし、レベルシフト抵抗ネットワークが不要になります。

### 電源、バイパス、デカップリング、及びレイアウト

グランド接続方法と電源デカップリングは、MAX5853の性能に多大な影響を及ぼします。望ましくないデジタルクロストークは、入力、リファレンス、電源、及びグランド接続部を通じて結合し、信号対ノイズ比やス皮アスフリーダイナミックレンジなどのダイナミック仕様に影響を及ぼします。また、電磁干渉(EMI)がMAX5853と結合したり、またはMAX5853によって発生したりします。高速、高周波数アプリケーション用のグランド接続及び電源デカップリングのガイドラインを順守してください。ダイナミック性能が最適になる電源及びフィルタ構成にしてください。

# デュアル、10ビット、80Mps、電流出力DAG

独立したグランド層と電源層のある多層プリント(PC)基板を使用することを推奨します。高速信号は、グランド面の上を直ぐに流れます。MAX5853は、独立したアナログ、クロック、及びデジタルのグランドバス(それぞれ、AGND、CGND、及びDGND)を備えています。別々のアナログ、デジタル、及びクロックのセクションのグランド部を、プリント基板上の1点でのみ接続します。グランド接続点はデバイスの下に配置して、裏面放熱パドルに接続する必要があります。デジタル信号はデジタルグランド面上に、アナログ/クロック信号はアナログ/クロックグランド面上に流します。デジタル信号は、敏感なアナログ、クロック、及びリファレンス入力から離す必要があります。伝搬遅延とデータスキューのミスマッチを回避するために、デジタル信号経路を短くかつメタルトレース長を調整します。MAX5853は、アナログ(AV<sub>DD</sub>)、デジタル(DV<sub>DD</sub>)、及びクロック(CV<sub>DD</sub>)の3つの独立した電源入力を備えています。1個のリニアレギュレータ電源ソースを使って、3つの独立電源ライン(AV<sub>DD</sub>、DV<sub>DD</sub>、CV<sub>DD</sub>)とリターン(AGND、DGND、CGND)に分岐させます。フェライトビーズと10μFコンデンサから構成されるLCフィルタを使って、各リターンラインまで各電源ラインをフィルタリングします。0.1μFセラミックコンデンサで各電源入力を各リターンラインに対して局部的にフィルタします。

注: 「Electrical Characteristics (電気特性)」のダイナミック性能を維持するために、DV<sub>DD</sub>、AV<sub>DD</sub>、及びCV<sub>DD</sub>間の電圧差が150mVを上回らないようにします。

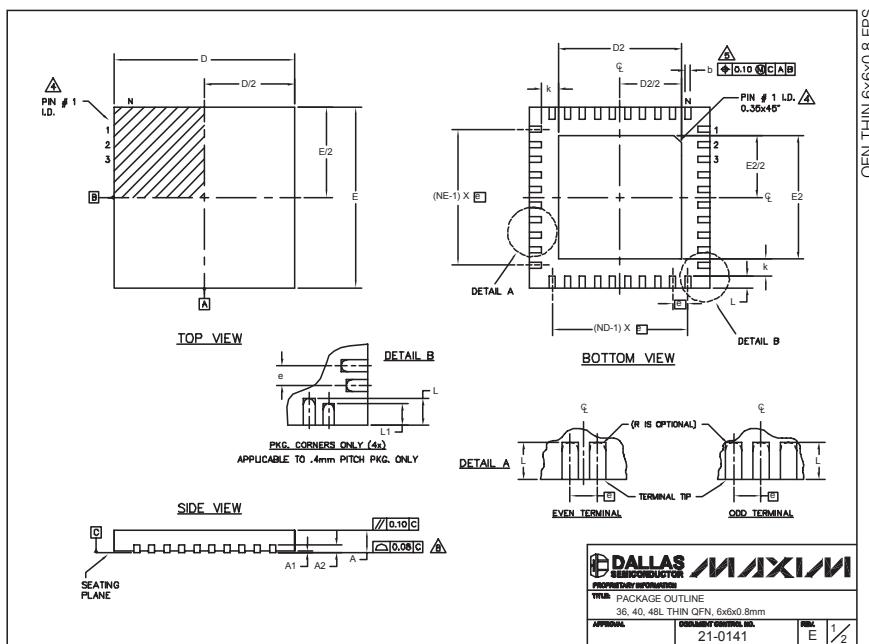

## 熱特性とパッケージング

### 熱抵抗

40リード薄型QFN-EPの熱抵抗:

$$\theta_{JA} = 38^{\circ}\text{C}/\text{W}$$

MAX5853は40ピン、薄型QFN-EPパッケージで提供されており、設計柔軟性と熱効率が向上し、DACのAC性能が最適化されます。EPによって、最高性能の動作を実現するのに不可欠なグランディング技術を実装することができます。

このパッケージでは、データコンバータダイはEPリードフレームに取り付けられ、そのEPリードフレームの裏側は、パッケージのプリント基板側に面して露出しています。このため、標準赤外線(IR)フロー半田付け技術でプリント基板にパッケージを堅固に取り付けることができます。EPのサイズ(4.1mm x 4.1mm)に合ったプリント基板上の特製ランドパターンによって、DACの

適切な接続とグランド接続が実現します。プリント基板設計でランド領域へのビア\*を設けて、広いグランド面を実現すると、DACを最高性能で動作させることができます。3 x 3のビアアレイ(1ビアホール当たり直径0.3mm以下でビアホール間のピッチは1.2mm)をこの40ピン、薄型QFN-EPパッケージ(パッケージコード:T4066-1)に使用してください。

## ダイナミック性能パラメータ定義

### 全高調波歪み(THD)

THDは、入力信号のすべての基本高調波(ナイキストウインドウ内)のRMS和と、基本波そのものの比です。これは、次式のように表すことができます。

$$\text{THD} = 20 \times \log \left( \frac{\sqrt{(V_2^2 + V_3^2 + V_4^2 + \dots + V_N^2)}}{V_1} \right)$$

ここで、V<sub>1</sub>は基本波の振幅、V<sub>2</sub>~V<sub>N</sub>は2次~N次高調波の振幅です。MAX5853は、この計算用に先頭から7つの高調波を使用します。

### スプリアスフリーダイナミックレンジ(SFDR)

SFDRは、搬送周波数(最大信号成分)のRMS振幅と、次に大きなスペクトル成分のRMS値との比です。SFDRは、搬送周波数振幅についてはdBcで、またDACのフルスケール範囲についてはdBFSで通常測定されます。試験条件に応じて、SFDRは事前設定されたウインドウ内またはナイキスト内で観察されます。

### マルチトーン電力比(MTPR)

一連の等間隔のトーンが、1トーンを範囲のセンターから排除して、DACに印加されます。MTPRは、最悪の歪み(通常、基本波周波数の3次高調波積)として定義されます。この歪みは、シーケンスにおける欠落トーンの周波数での最大スパーとして発生します。この試験を任意の入力トーン数で実行することができます。ただし4個及び8個のトーンが、CDMA及びGSM/EDGEタイプのアプリケーションで最も一般的な試験条件です。

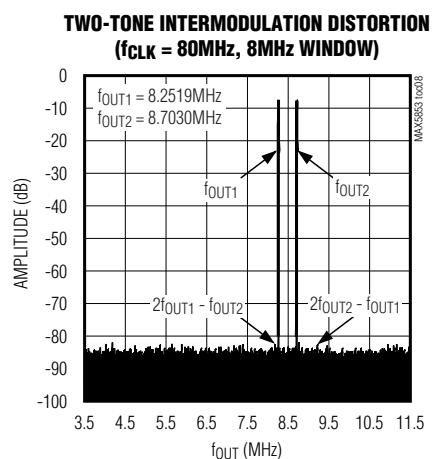

### 相互変調歪み(IMD)

2トーンIMDは、いずれかの出力トーンと最悪の3次(またはそれ以上の)IMD積の比をdBc単位で表したもので

\* ビアは、ランドパターンを内側または外側銅面に接続します。

## 静的性能パラメータの定義

### 積分非直線性(INL)

積分非直線性(INL)は、オフセット及び利得誤差をヌル(ゼロ)にした後に、伝達関数の両端間を結んだ線と実際の伝達関数値の偏差です。DACの場合は、偏差は各ステップで測定されます。

### 微分非直線性(DNL)

微分非直線性(DNL)は、実際のステップの高さと1 LSBの理想値との差です。DNL誤差仕様が-1 LSB以下であるため、伝達関数の単調性が保証されます。

### オフセット誤差

オフセット誤差は、デジタル入力コードがゼロに設定されているときに、正DAC出力から流れる電流です。オフセット誤差は、LSBで表されます。

### 利得誤差

利得誤差は、オフセット誤差をゼロにした後の、伝達曲線上の実際のフルスケール出力電流と理想値との差です。この誤差は伝達関数の傾きを変更し、各ステップの同じ百分率誤差に対応します。理想的な電流は、 $V_{REF0} / I_{REF} \times 32$ のリファレンス電圧で定義されます。

### セトリング時間

セトリング時間は、遷移の開始からDAC出力値がコンバータの仕様精度内の新しい出力値に落ち着くまでに要する時間です。

### グリッチインパルス

グリッチは、DACが2つのコード間で切り替わるときに発生します。最大グリッチは、通常、入力パターンが011...111から100...000に遷移するときにミッドスケール遷移の前後で発生します。これはビット間のタイミング変化によるものです。グリッチインパルスは、ミッドスケール遷移時にグリッチ電圧を集積することで発生します。グリッチインパルスは、通常pV-sで表されます。

表4. 部品選択表

| PART    | SPEED (Msps) | RESOLUTION   |

|---------|--------------|--------------|

| MAX5851 | 80           | 8-bit, dual  |

| MAX5852 | 165          | 8-bit, dual  |

| MAX5853 | 80           | 10-bit, dual |

| MAX5854 | 165          | 10-bit, dual |

### チップ情報

TRANSISTOR COUNT: 9,035

PROCESS: CMOS

# デュアル、10ビット、80MspS、電流出力DAC

## パッケージ

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、[japan.maxim-ic.com/packages](http://japan.maxim-ic.com/packages)をご参照下さい。)

| COMMON DIMENSIONS |         |      |      |         |      |      |         |      |      |  |

|-------------------|---------|------|------|---------|------|------|---------|------|------|--|

| PKG.              | 36L 6x6 |      |      | 40L 6x6 |      |      | 48L 6x6 |      |      |  |

|                   | MIN.    | NOM. | MAX. | MIN.    | NOM. | MAX. | MIN.    | NOM. | MAX. |  |

| A                 | 0.70    | 0.75 | 0.80 | 0.70    | 0.75 | 0.80 | 0.70    | 0.75 | 0.80 |  |

| A1                | 0       | 0.02 | 0.05 | 0       | 0.02 | 0.05 | 0       | —    | 0.05 |  |

| A2                | 0.20    | 0.20 | REF. | 0.20    | 0.20 | REF. | 0.20    | 0.20 | 0.20 |  |

| b                 | 0.20    | 0.25 | 0.30 | 0.20    | 0.25 | 0.30 | 0.15    | 0.20 | 0.25 |  |

| D                 | 5.90    | 6.00 | 6.10 | 5.90    | 6.00 | 6.10 | 5.80    | 6.00 | 6.10 |  |

| E                 | 5.90    | 6.00 | 6.10 | 5.90    | 6.00 | 6.10 | 5.80    | 6.00 | 6.10 |  |

| e                 | 0.50    | 0.50 | 0.50 | 0.50    | 0.50 | 0.50 | 0.40    | 0.40 | 0.40 |  |

| k                 | 0.25    | —    | —    | 0.25    | —    | —    | 0.25    | 0.35 | 0.45 |  |

| L                 | 0.45    | 0.35 | 0.65 | 0.30    | 0.40 | 0.50 | 0.40    | 0.50 | 0.60 |  |

| L1                | —       | —    | —    | —       | —    | —    | 0.30    | 0.40 | 0.50 |  |

| N                 | 36      |      |      | 40      |      |      | 48      |      |      |  |

| ND                | 9       |      |      | 10      |      |      | 12      |      |      |  |

| NE                | 9       |      |      | 10      |      |      | 12      |      |      |  |

| JEDEC             | WJD-1   |      |      | WJD-2   |      |      | —       |      |      |  |

NOTES:

1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

2. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

3. N IS THE TOTAL NUMBER OF TERMINALS.

△ THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

△ DIMENSION b APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25 mm AND 0.30 mm FROM TERMINAL TIP.

6. ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

7. DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

△ COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

9. DRAWING CONFORMS TO JEDEC MO220, EXCEPT FOR 0.4mm LEAD PITCH PACKAGE T4866-1.

10. WARPAGE SHALL NOT EXCEED 0.10 mm.

| EXPOSED PAD VARIATIONS |      |      |      | DOWN BONDS ALLOWED |      |      |     |

|------------------------|------|------|------|--------------------|------|------|-----|

| PKG. CODES             | D2   |      | E2   |                    |      |      |     |

|                        | MIN. | NOM. | MAX. | MIN.               | NOM. | MAX. |     |

| T3666-1                | 3.60 | 3.70 | 3.80 | 3.60               | 3.70 | 3.80 | NO  |

| T3666-2                | 3.60 | 3.70 | 3.80 | 3.60               | 3.70 | 3.80 | YES |

| T3666-3                | 3.60 | 3.70 | 3.80 | 3.60               | 3.70 | 3.80 | NO  |

| T4066-1                | 4.00 | 4.10 | 4.20 | 4.00               | 4.10 | 4.20 | NO  |

| T4066-2                | 4.00 | 4.10 | 4.20 | 4.00               | 4.10 | 4.20 | YES |

| T4066-3                | 4.00 | 4.10 | 4.20 | 4.00               | 4.10 | 4.20 | YES |

| T4066-4                | 4.00 | 4.10 | 4.20 | 4.00               | 4.10 | 4.20 | NO  |

| T4066-5                | 4.00 | 4.10 | 4.20 | 4.00               | 4.10 | 4.20 | NO  |

| T4866-1                | 4.20 | 4.30 | 4.40 | 4.20               | 4.30 | 4.40 | YES |

DALLAS SEMICONDUCTOR

MAXIM

TITLE: PACKAGE OUTLINE

36, 40, 48L THIN QFN, 6x6x0.8mm

APPROVAL: 21-0141 E 1/2

## マキシム・ジャパン株式会社

〒169-0051 東京都新宿区西早稲田3-30-16(ホリゾン1ビル)

TEL. (03)3232-6141 FAX. (03)3232-6149

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。マキシムは隨時予告なく回路及び仕様を変更する権利を留保します。

18 **Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600**

© 2004 Maxim Integrated Products

**MAXIM** is a registered trademark of Maxim Integrated Products.