# クワッド、12ビット、低電力、2線、シリアル 電圧出力DAC

**MAX5842**

## 概要

MAX5842は、クロックレート最高400kHzまで動作するI<sup>2</sup>Cコンパチブル2線インターフェース付クワッド、12ビット電圧出力、D/Aコンバータ(DAC)です。本デバイスは単一電源2.7V~5.5Vで動作し、消費電流はV<sub>DD</sub>=3.6Vにおいて僅か230μAです。パワーダウンモードにおいては1μA以下まで消費電流を低減します。MAX5842はソフト選択可能な3つのパワーダウン出力インピーダンス(100kΩ、1kΩ、ハイインピーダンス)を備えています。その他に高精度レイルトゥレイル出力バッファ、及び100kΩパワーダウンモード時にDACを起動するパワーオンリセット(POR)回路も装備しています。

MAX5842は、複数のデバイスが1つのバスを共有できるダブルバッファI<sup>2</sup>Cコンパチブルのシリアルインターフェースを備えています。全てのロジック入力はCMOSロジックと互換性があり、オプティカル及びトランジストで分離されたインターフェースと直接インターフェースが可能のようにシミュットトリガでバッファされています。MAX5842はアドレスのミスマッチが検出されると、クロック信号(SCL)を残りのデバイスから切断することによって、デジタルノイズのフィードスルーを最小化します。

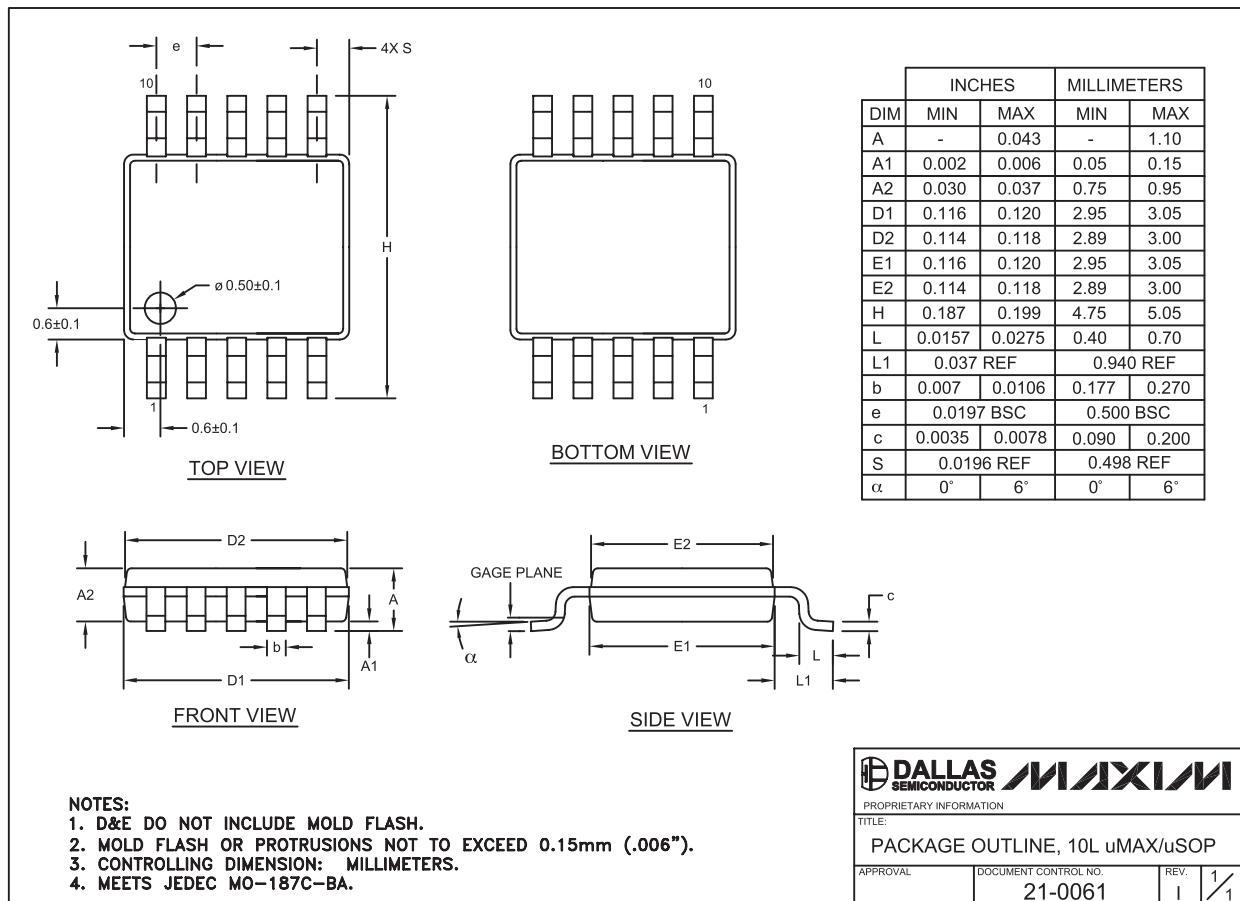

MAX5842は、拡張温度範囲(-40°C~+85°C)の仕様となっており、小型10ピンμMAXパッケージで提供されています。10ビットのバージョンに関してはMAX5841のデータシートを参照して下さい。

## アプリケーション

- デジタル利得及びオフセット調整

- プログラマブル電圧及び電流ソース

- プログラマブル減衰

- VCO/バラクタダイオード制御

- 低コスト計測器

- バッテリ駆動機器

- ATE

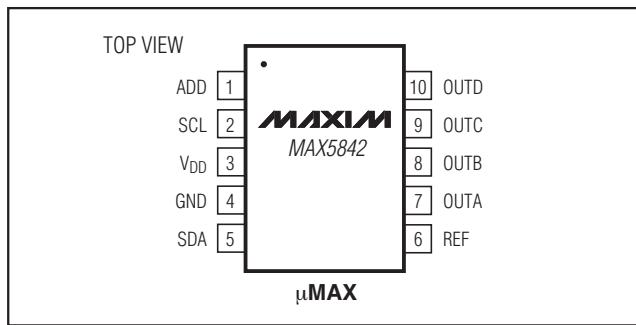

## ピン配置

## 特長

- ◆ 超低消費電流

230μA@V<sub>DD</sub> = 3.6V

280μA@V<sub>DD</sub> = 5.5V

- ◆ 低電力パワーダウンモード : 300nA

- ◆ 単一電源電圧 : 2.7V~5.5V

- ◆ I<sup>2</sup>Cコンパチブル高速400kHz 2線シリアルインターフェース

- ◆ フォトカプラに直接インターフェース可能なシミュットトリガ入力

- ◆ レイルトゥレイル出力バッファアンプ

- ◆ ソフト選択可能な3つのパワーダウンモード出力インピーダンス

100kΩ、1kΩ、及びハイインピーダンス

- ◆ バス及びデータ検査用のリードバックモード

- ◆ パワーオンリセットでゼロスケール

- ◆ パッケージ : 10ピンμMAX

## 型番

| PART        | TEMP RANGE     | PIN-PACKAGE | ADDRESS  |

|-------------|----------------|-------------|----------|

| MAX5842LEUB | -40°C to +85°C | 10 μMAX     | 0111 10X |

| MAX5842MEUB | -40°C to +85°C | 10 μMAX     | 1011 10X |

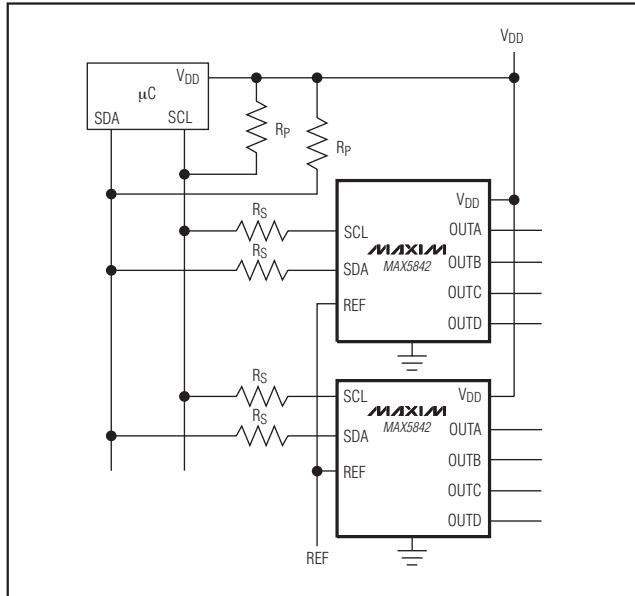

## 標準動作回路

# クワッド、12ビット、低電力、2線、シリアル 電圧出力DAC

## ABSOLUTE MAXIMUM RATINGS

|                                                       |                                 |

|-------------------------------------------------------|---------------------------------|

| V <sub>DD</sub> , SCL, SDA to GND                     | -0.3V to +6V                    |

| OUT <sub>−</sub> , REF, ADD to GND                    | -0.3V to V <sub>DD</sub> + 0.3V |

| Maximum Current into Any Pin                          | 50mA                            |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |                                 |

| 10-Pin µMAX (derate 5.6mW above +70°C)                | 444mW                           |

|                                   |                 |

|-----------------------------------|-----------------|

| Operating Temperature Range       | -40°C to +85°C  |

| Storage Temperature Range         | -65°C to +150°C |

| Maximum Junction Temperature      | +150°C          |

| Lead Temperature (soldering, 10s) | +300°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

(V<sub>DD</sub> = +2.7V to +5.5V, GND = 0, V<sub>REF</sub> = V<sub>DD</sub>, R<sub>L</sub> = 5kΩ, C<sub>L</sub> = 200pF, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at V<sub>DD</sub> = +5V, T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                        | SYMBOL           | CONDITIONS                                                                                                       | MIN                   | TYP             | MAX | UNITS  |

|----------------------------------|------------------|------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------|-----|--------|

| <b>STATIC ACCURACY (NOTE 2)</b>  |                  |                                                                                                                  |                       |                 |     |        |

| Resolution                       | N                |                                                                                                                  | 12                    |                 |     | Bits   |

| Integral Nonlinearity            | INL              | (Note 3)                                                                                                         |                       | ±2              | ±16 | LSB    |

| Differential Nonlinearity        | DNL              | Guaranteed monotonic (Note 3)                                                                                    |                       | ±1              |     | LSB    |

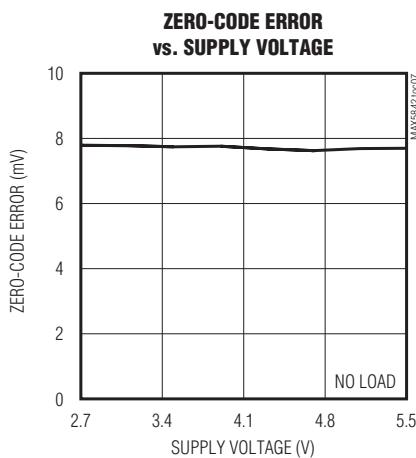

| Zero-Code Error                  | ZCE              | Code = 000 hex, V <sub>DD</sub> = 2.7V                                                                           | 6                     | 40              |     | mV     |

| Zero-Code Error Tempco           |                  |                                                                                                                  | 2.3                   |                 |     | ppm/°C |

| Gain Error                       | GE               | Code = FFF hex                                                                                                   | -0.8                  | -3              |     | %FSR   |

| Gain-Error Tempco                |                  |                                                                                                                  | 0.26                  |                 |     | ppm/°C |

| Power-Supply Rejection Ratio     | PSRR             | Code = FFF hex, V <sub>DD</sub> = 4.5V to 5.5V                                                                   | 58.8                  |                 |     | dB     |

| DC Crosstalk                     |                  |                                                                                                                  | 30                    |                 |     | µV     |

| <b>REFERENCE INPUT</b>           |                  |                                                                                                                  |                       |                 |     |        |

| Reference Input Voltage Range    | V <sub>REF</sub> |                                                                                                                  | 0                     | V <sub>DD</sub> |     | V      |

| Reference Input Impedance        |                  |                                                                                                                  | 32                    | 45              |     | kΩ     |

| Reference Current                |                  | Power-down mode                                                                                                  | ±0.3                  | ±1              |     | µA     |

| <b>DAC OUTPUT</b>                |                  |                                                                                                                  |                       |                 |     |        |

| Output Voltage Range             |                  | No load (Note 4)                                                                                                 | 0                     | V <sub>DD</sub> |     | V      |

| DC Output Impedance              |                  | Code = 800 hex                                                                                                   |                       | 1.2             |     | Ω      |

| Short-Circuit Current            |                  | V <sub>DD</sub> = 5V, V <sub>OUT</sub> = full scale (short to GND)                                               | 42.2                  |                 |     | mA     |

|                                  |                  | V <sub>DD</sub> = 3V, V <sub>OUT</sub> = full scale (short to GND)                                               | 15.1                  |                 |     |        |

| Wake-Up Time                     |                  | V <sub>DD</sub> = 5V                                                                                             | 8                     |                 |     | µs     |

|                                  |                  | V <sub>DD</sub> = 3V                                                                                             | 8                     |                 |     |        |

| DAC Output Leakage Current       |                  | Power-down mode = high impedance, V <sub>DD</sub> = 5.5V, V <sub>OUT</sub> <sub>−</sub> = V <sub>DD</sub> or GND | ±0.1                  | ±1              |     | µA     |

| <b>DIGITAL INPUTS (SCL, SDA)</b> |                  |                                                                                                                  |                       |                 |     |        |

| Input High Voltage               | V <sub>IH</sub>  |                                                                                                                  | 0.7 × V <sub>DD</sub> |                 |     | V      |

| Input Low Voltage                | V <sub>IL</sub>  |                                                                                                                  | 0.3 × V <sub>DD</sub> |                 |     | V      |

# クワッド、12ビット、低電力、2線、シリアル 電圧出力DAC

**MAX5842**

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{DD} = +2.7V$  to  $+5.5V$ ,  $GND = 0$ ,  $V_{REF} = V_{DD}$ ,  $R_L = 5k\Omega$ ,  $C_L = 200pF$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $V_{DD} = +5V$ ,  $T_A = +25^\circ C$ .) (Note 1)

| PARAMETER                                       | SYMBOL       | CONDITIONS                                                                | MIN                | TYP       | MAX     | UNITS      |

|-------------------------------------------------|--------------|---------------------------------------------------------------------------|--------------------|-----------|---------|------------|

| Input Hysteresis                                |              |                                                                           | 0.05 ×<br>$V_{DD}$ |           |         | V          |

| Input Leakage Current                           |              | Digital inputs = 0 or $V_{DD}$                                            |                    | $\pm 0.1$ | $\pm 1$ | $\mu A$    |

| Input Capacitance                               |              |                                                                           | 6                  |           |         | pF         |

| <b>DIGITAL OUTPUT (SDA)</b>                     |              |                                                                           |                    |           |         |            |

| Output Logic Low Voltage                        | $V_{OL}$     | $I_{SINK} = 3mA$                                                          |                    | 0.4       |         | V          |

| Three-State Leakage Current                     | $I_L$        | Digital inputs = 0 or $V_{DD}$                                            |                    | $\pm 0.1$ | $\pm 1$ | $\mu A$    |

| Three-State Output Capacitance                  |              |                                                                           | 6                  |           |         | pF         |

| <b>DYNAMIC PERFORMANCE</b>                      |              |                                                                           |                    |           |         |            |

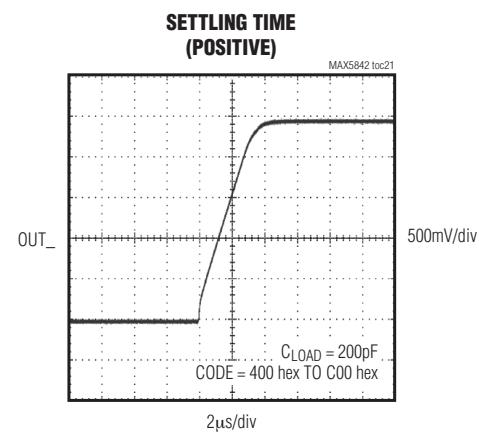

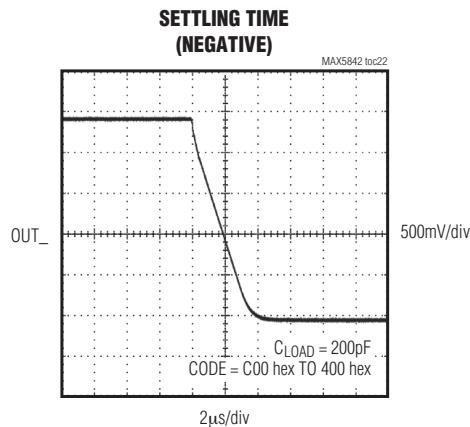

| Voltage Output Slew Rate                        | SR           |                                                                           | 0.5                |           |         | V/ $\mu s$ |

| Voltage Output Settling Time                    |              | To 1/2LSB code 400 hex to C00 hex or C00 hex to 400 hex (Note 5)          | 4                  | 12        |         | $\mu s$    |

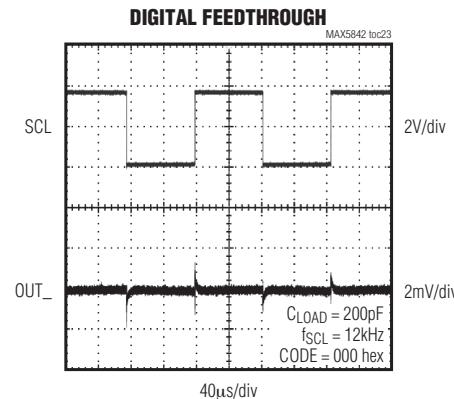

| Digital Feedthrough                             |              | Code = 000 hex, digital inputs from 0 to $V_{DD}$                         | 0.2                |           |         | nV-s       |

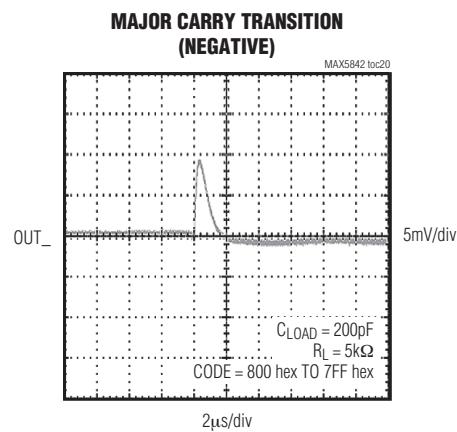

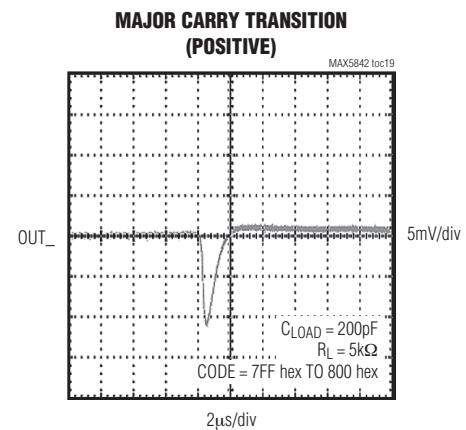

| Digital-to-Analog Glitch Impulse                |              | Major carry transition (code = 7FF hex to 800 hex and 800 hex to 7FF hex) | 12                 |           |         | nV-s       |

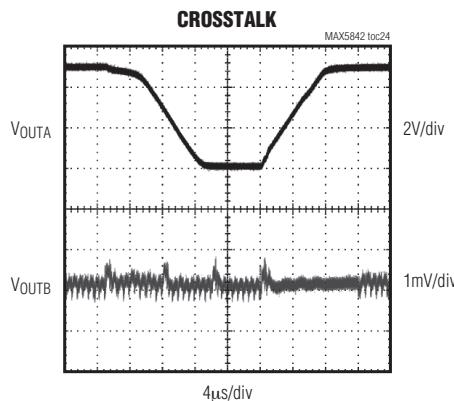

| DAC-to-DAC Crosstalk                            |              |                                                                           | 2.4                |           |         | nV-s       |

| <b>POWER SUPPLIES</b>                           |              |                                                                           |                    |           |         |            |

| Supply Voltage Range                            | $V_{DD}$     |                                                                           | 2.7                | 5.5       |         | V          |

| Supply Current with No Load                     | $I_{DD}$     | All digital inputs at 0 or $V_{DD} = 3.6V$                                | 230                | 395       |         | $\mu A$    |

|                                                 |              | All digital inputs at 0 or $V_{DD} = 5.5V$                                | 280                | 420       |         |            |

| Power-Down Supply Current                       | $I_{DDPD}$   | All digital inputs at 0 or $V_{DD} = 5.5V$                                | 0.3                | 1         |         | $\mu A$    |

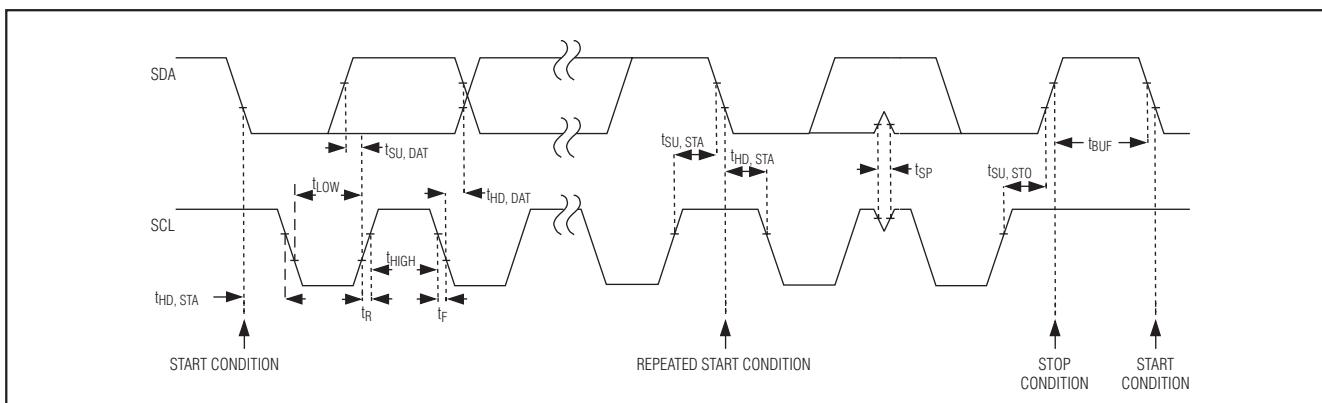

| <b>TIMING CHARACTERISTICS (FIGURE 1)</b>        |              |                                                                           |                    |           |         |            |

| Serial Clock Frequency                          | $f_{SCL}$    |                                                                           | 0                  | 400       |         | kHz        |

| Bus Free Time Between STOP and START Conditions | $t_{BUF}$    |                                                                           | 1.3                |           |         | $\mu s$    |

| START Condition Hold Time                       | $t_{HD,STA}$ |                                                                           | 0.6                |           |         | $\mu s$    |

| SCL Pulse Width Low                             | $t_{LOW}$    |                                                                           | 1.3                |           |         | $\mu s$    |

| SCL Pulse Width High                            | $t_{HIGH}$   |                                                                           | 0.6                |           |         | $\mu s$    |

| Repeated START Setup Time                       | $t_{SU,STA}$ |                                                                           | 0.6                |           |         | $\mu s$    |

| Data Hold Time                                  | $t_{HD,DAT}$ |                                                                           | 0                  | 0.9       |         | $\mu s$    |

| Data Setup Time                                 | $t_{SU,DAT}$ |                                                                           | 100                |           |         | ns         |

| SDA and SCL Receiving Rise Time                 | $t_r$        | (Note 5)                                                                  | 0                  | 300       |         | ns         |

| SDA and SCL Receiving Fall Time                 | $t_f$        | (Note 5)                                                                  | 0                  | 300       |         | ns         |

| SDA Transmitting Fall Time                      | $t_f$        | (Note 5)                                                                  | $20 + 0.1C_b$      | 250       |         | ns         |

| STOP Condition Setup Time                       | $t_{SU,STO}$ |                                                                           | 0.6                |           |         | $\mu s$    |

# クワッド、12ビット、低電力、2線、シリアル 電圧出力DAC

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{DD} = +2.7V$  to  $+5.5V$ ,  $GND = 0$ ,  $V_{REF} = V_{DD}$ ,  $R_L = 5k\Omega$ ,  $C_L = 200pF$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $V_{DD} = +5V$ ,  $T_A = +25^{\circ}\text{C}$ .) (Note 1)

| PARAMETER                                   | SYMBOL   | CONDITIONS | MIN | TYP | MAX | UNITS |

|---------------------------------------------|----------|------------|-----|-----|-----|-------|

| Bus Capacitance                             | $C_b$    | (Note 5)   |     | 400 |     | pF    |

| Maximum Duration of Suppressed Pulse Widths | $t_{SP}$ |            | 0   | 50  |     | ns    |

**Note 1:** All devices are 100% production tested at  $T_A = +25^{\circ}\text{C}$  and are guaranteed by design for  $T_A = T_{MIN}$  to  $T_{MAX}$ .

**Note 2:** Static specifications are tested with the output unloaded.

**Note 3:** Linearity is guaranteed from codes 115 to 3981.

**Note 4:** Offset and gain error limit the FSR.

**Note 5:** Guaranteed by design. Not production tested.

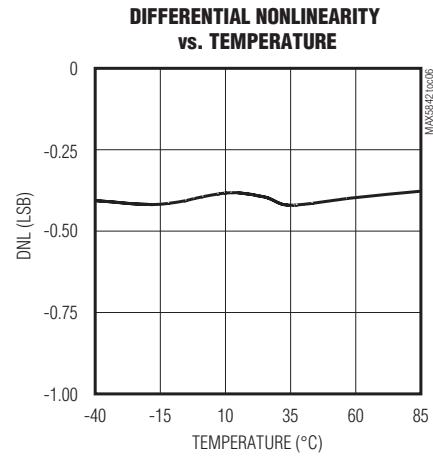

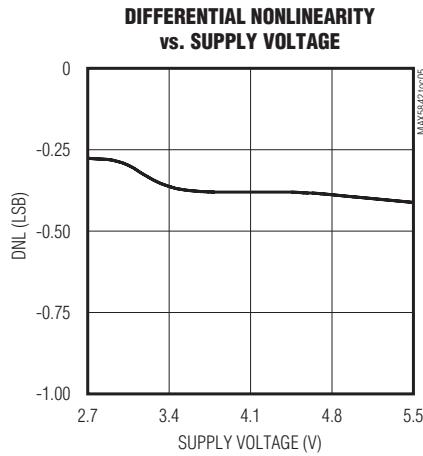

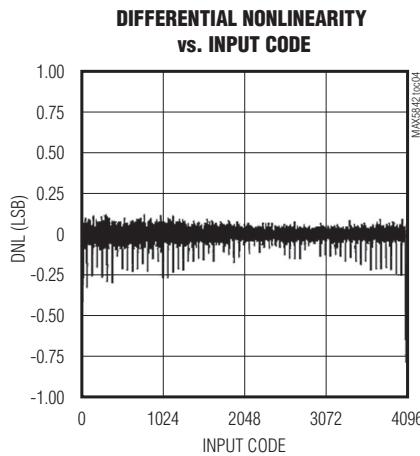

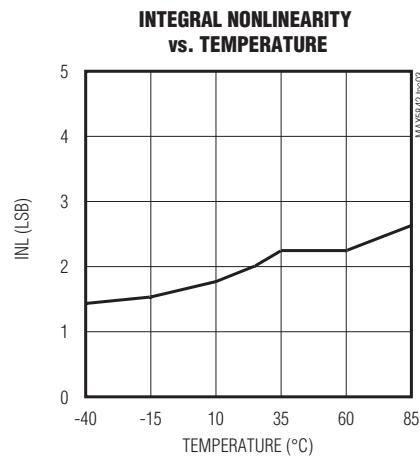

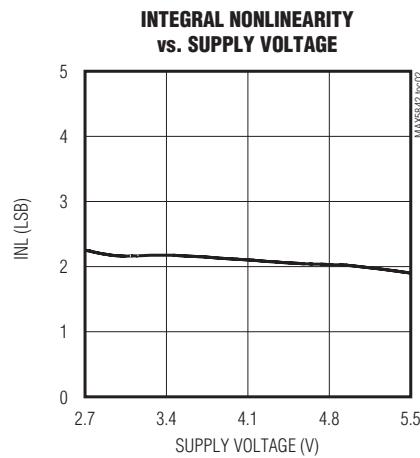

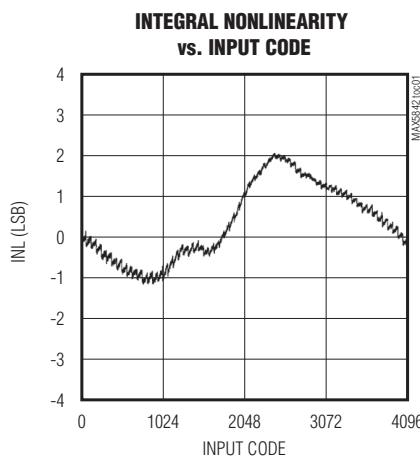

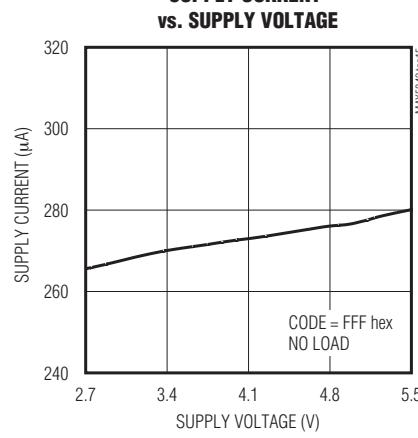

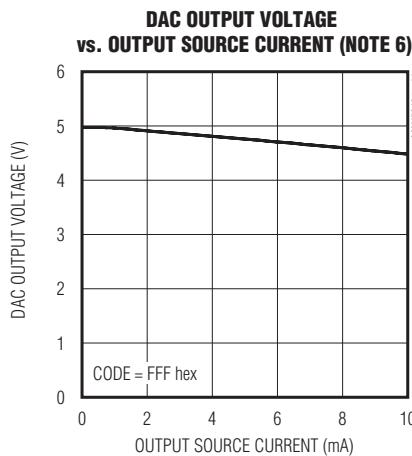

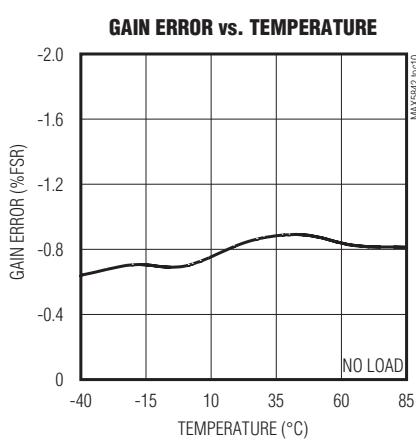

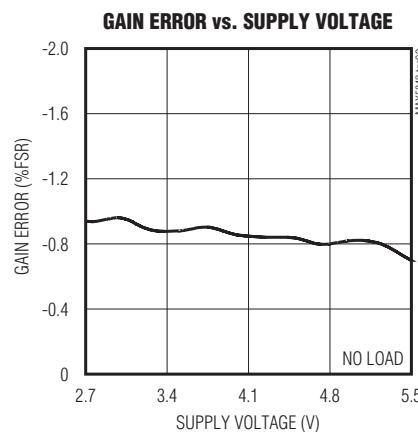

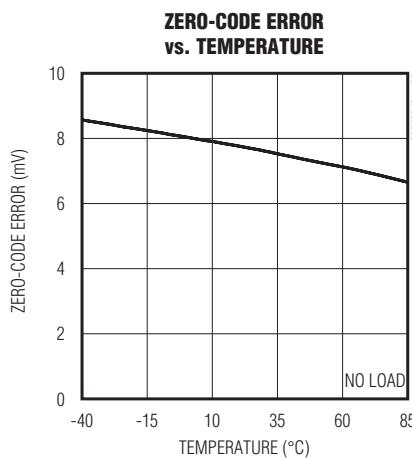

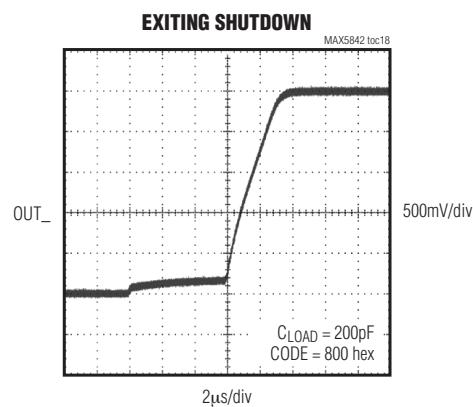

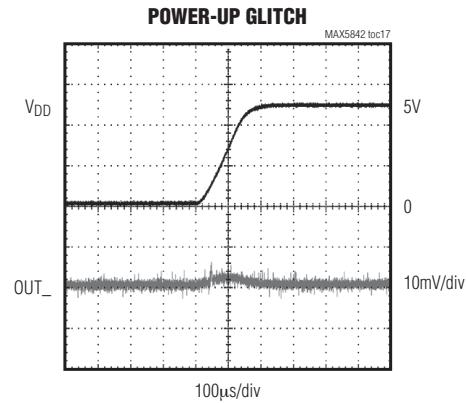

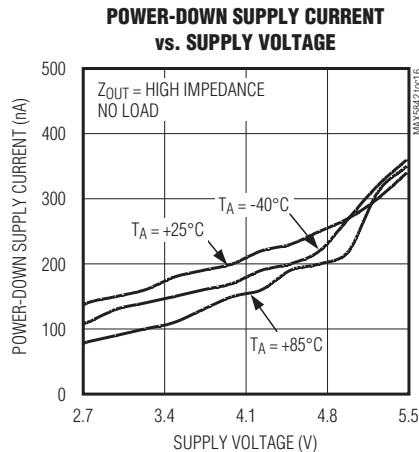

## 標準動作特性

( $V_{DD} = +5V$ ,  $R_L = 5k\Omega$ .)

# クワッド、12ビット、低電力、2線、シリアル 電圧出力DAC

**MAX5842**

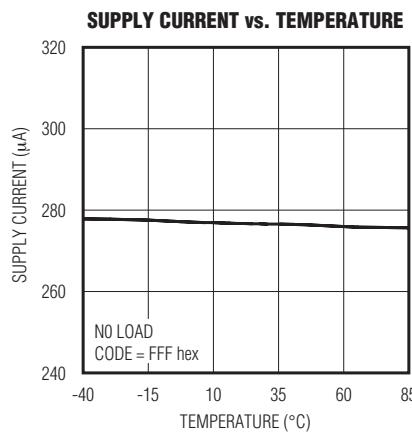

## 標準動作特性(続き)

( $V_{DD} = +5V$ ,  $R_L = 5k\Omega$ .)

# クワッド、12ビット、低電力、2線、シリアル 電圧出力DAC

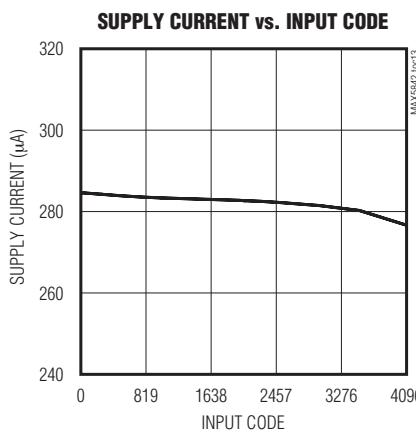

## 標準動作特性(続き)

( $V_{DD} = +5V$ ,  $R_L = 5k\Omega$ .)

# クワッド、12ビット、低電力、2線、シリアル 電圧出力DAC

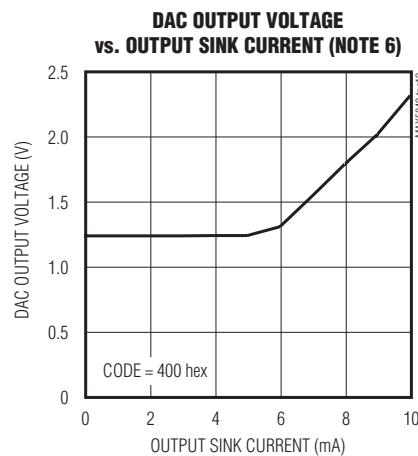

## 標準動作特性(続き)

( $V_{DD} = +5V$ ,  $R_L = 5k\Omega$ .)

**Note 6:** The ability to drive loads less than  $5k\Omega$  is not implied.

# クワッド、12ビット、低電力、2線、シリアル 電圧出力DAC

## 端子説明

| 端子 | 名称              | 機能                                                       |

|----|-----------------|----------------------------------------------------------|

| 1  | ADD             | アドレス選択。ロジックハイがアドレス LSBを1に設定します。ロジックローがアドレス LSBをゼロに設定します。 |

| 2  | SCL             | シリアルクロック入力                                               |

| 3  | V <sub>DD</sub> | 電源                                                       |

| 4  | GND             | グランド                                                     |

| 5  | SDA             | 双方向シリアルデータインターフェース                                       |

| 6  | REF             | リファレンス入力                                                 |

| 7  | OUTA            | DAC A出力                                                  |

| 8  | OUTB            | DAC B出力                                                  |

| 9  | OUTC            | DAC C出力                                                  |

| 10 | OUTD            | DAC D出力                                                  |

## 詳細

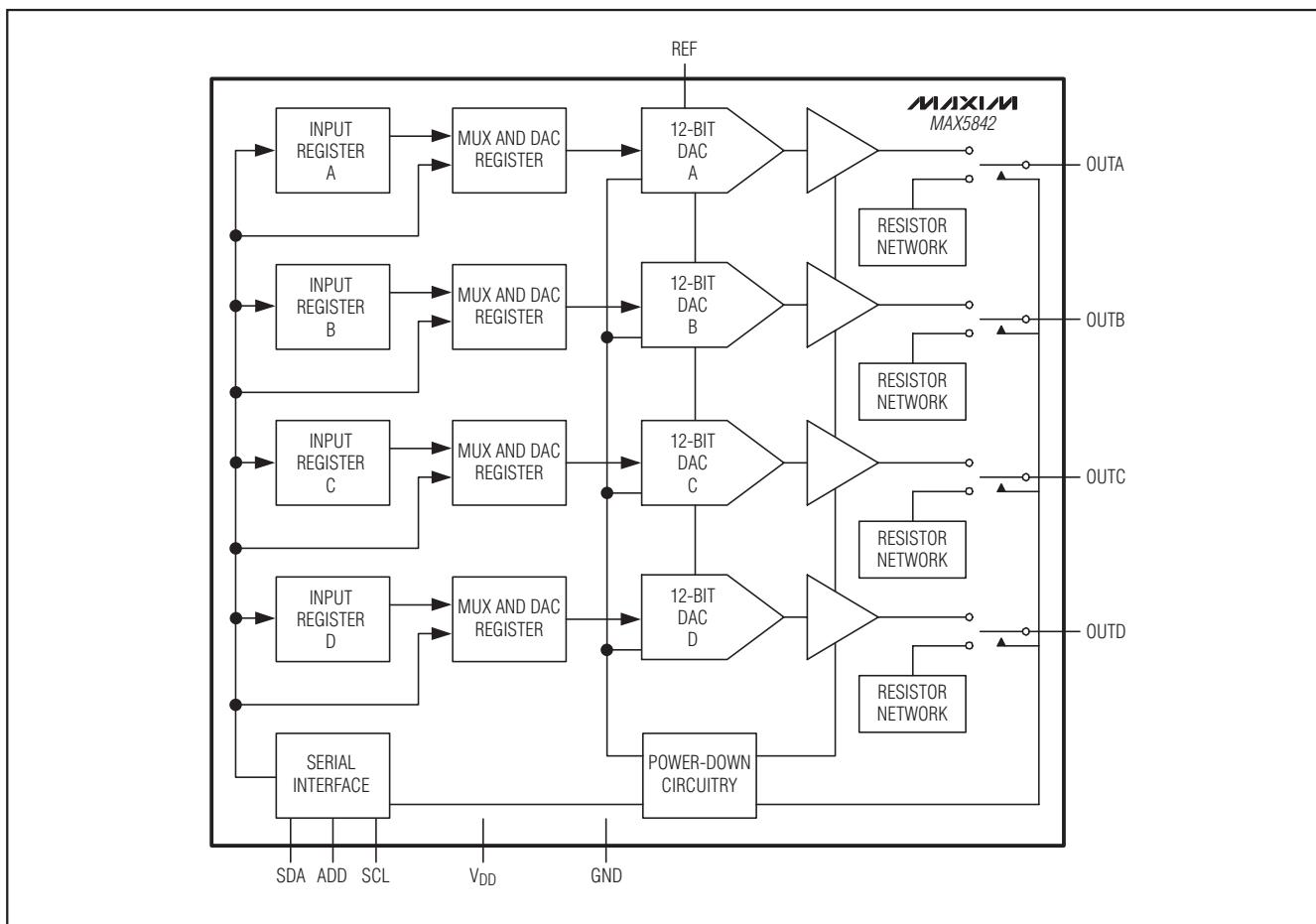

MAX5842はI<sup>2</sup>C/SMBusコンパチブル2線インターフェース付のクワッド、12ビット、電圧出力DACです。本デバイスは、シリアルインターフェース、パワーダウン回路、4つの入力及びDACレジスタ、4つの12ビット抵抗ストリングDAC、4つのユニティゲイン出力バッファ、及び出力抵抗ネットワークで構成されています。シリアルインターフェースはアドレス及び制御ビットを認識し、データを適切な入力又はDACレジスタへ出力します。デバイスの出力を瞬時に更新するようにデータはDACレジスタへ直接書き込みが可能か、又はDAC出力を変えることなく入力レジスタへ書き込むことが可能です。両レジスタはデバイスに電源が投入されている限りデータを保持します。

## DAC動作

MAX5842はセグメント化された抵抗ストリングDAC構成を使い、システム全体の電力を節減し、出力単調性を保証します。MAX5842の入力コードはストレートバイナリで、出力電圧は次式で求められます。

$$V_{\text{OUT}} = \frac{V_{\text{REF}} \times (D)}{2^N}$$

この場合、N=12(ビット)、及びD=入力コード(0~4095)の10進数値です。

## 出力バッファ

MAX5842アナログ出力はスルーレート0.5V/μsの高精度、ユニティゲインフォロワによってバッファされます。各バッファ出力はレイルトゥレイルで振ることが出来、200pFと並列の5kΩの駆動が可能です。出力は±0.5LSBへ4μs以内でセトリングします。

## パワーオンリセット

MAX5842は起動時にデバイスを初期化する内部POR回路を装備しています。DACレジスタはゼロスケールに設定され、デバイスは出力バッファをディセーブルし、出力が100kΩ終端抵抗を介してグランドへプルされパワーダウンします。起動時に続いて、変換が実行される前にウェイクアップコマンドが開始される必要があります。

## パワーダウンモード

MAX5842は、ソフトで制御された3つの低電力、パワーダウンモードを備えています。3つ全てのモードで出力バッファをディセーブルして、DAC抵抗ストリングをREFから切断し、消費電流を1μAまで、及びリファレンス電流の消費を1μA以下に低減します。パワーダウンモード0の時、デバイス出力はハイインピーダンスです。パワーダウンモード1の時は、デバイス出力は1kΩ終端抵抗によって内部でグランドへ接続されます。パワーダウンモード2では、デバイス出力は内部で100kΩ終端抵抗によってグラウンドに接続されます。表1にパワーダウンモードのコマンドワードが示されています。

ウェイクアップ時には、DAC出力は以前の値に復元されます。パワーダウンモードの間データは入力及びDACレジスタに保持されます。

## デジタルインターフェース

MAX5842は、シリアルデータライン(SDA)及びシリアルクロックライン(SCL)で構成されたI<sup>2</sup>C/SMBusコンパチブルの2線インターフェースを備えています。MAX5842はV<sub>DD</sub>=2.7V~3.6Vの範囲内でSMバスコンパチブルです。SDA及びSCLはMAX5842とマスター間の双方向通信を最高400kHzのレートで実現します。図1は2線

# クワッド、12ビット、低電力、2線、シリアル電圧出力DAC

MAX5842

表1. パワーダウンコマンドビット

| POWER-DOWN<br>COMMAND BITS |     | MODE/FUNCTION                                                                  |

|----------------------------|-----|--------------------------------------------------------------------------------|

| PD1                        | PD0 |                                                                                |

| 0                          | 0   | Power-up device. DAC output restored to previous value.                        |

| 0                          | 1   | Power-down mode 0. Power down device with output floating.                     |

| 1                          | 0   | Power-down mode 1. Power down device with output terminated with 1kΩ to GND.   |

| 1                          | 1   | Power-down mode 2. Power down device with output terminated with 100kΩ to GND. |

インターフェースのタイミングダイアグラムです。MAX5842は送受信スレーブのみのデバイスで、クロック信号の生成はマスタに依存します。マスタ(通常マイクロコントローラ)はバス上のデータ転送を開始して転送を許可するSCLを発生します。

マスタデバイスは適切なアドレスに続いてコマンド及び/又はデータワードを送信することによってMAX5842と通信します。各送信シーケンスはSTART(S)又はREPEATED START( $S_r$ )条件及びSTOP(P)条件によってフレームされます。バスを介して送信される各ワードは8ビット長で必ずアクノリッジクロックパルスが後に続きます。

MAX5842のSDA及びSCLドライバはオープンドレイン出力で、ロジックハイ電圧を生成するのにプルアップ抵抗を必要とします。(「標準動作回路」を参照)直列抵抗 $R_S$ はオプションです。これらの直列抵抗はバス線上の高圧スパイクからMAX5842の入力段を保護して、バス信号のクロストーク及びアンダーシュートを最小化します。

## ビットトランスマスク

1つのデータビットが各SCLクロックサイクル中に伝送されます。SDA上のデータはSCLクロックパルスがハイの期間中安定していかなければなりません。SCLがハイの間のSDAの変化は制御信号です(「START及びSTOP条件」を参照)。SDA及びSCLは両方ともI<sup>2</sup>Cバスが使用中でない時はハイでアイドルします。

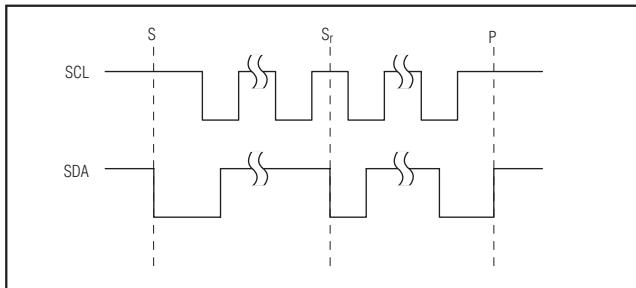

## START及びSTOP条件

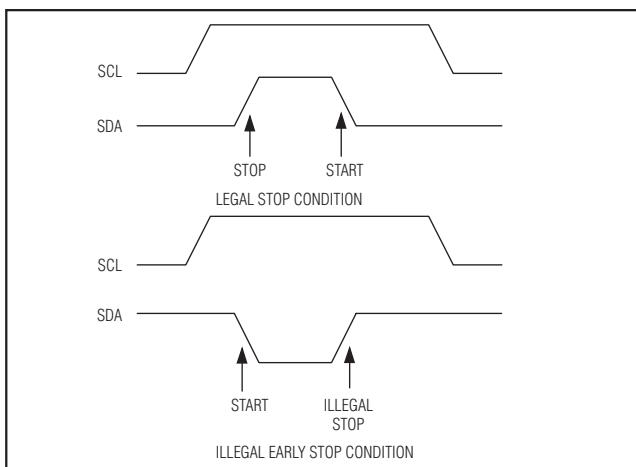

シリアルインターフェースが非動作状態の場合、SDA及びSCLはハイでアイドルします。マスタデバイスはSTART条件を発行することによって通信を開始します。START条件とはSCLがハイの時、SDAのハイからローへの移行のことです。STOP条件とはSCLがハイの時、SDAのローからハイへの移行のことです(図2を参照)。マスタからのSTART条件がMAX5842への伝送開始を命令します。マスタはノットアクノリッジに続いてSTOP条件を発行することにより伝送を中止します(「アクノリッジビット(ACK)」を参照)。STOP条件はバスを解放します。STOP条件の代わりにREPEATED START条件( $S_r$ )が選択された場合、バスは有効状態を保ちます。STOP条件又は間違ったアドレスが検出された場合、MAX5842はデジタルノイズとフィードスルーを最小限に抑えるため、次のSTART条件までSCLをシリアルインターフェースから内部で切断します。

## 初期のSTOP条件

MAX5842はSTOP条件がSTART条件と同じハイパルス状態で起きる以外は、伝送中のどの時点においてもSTOP条件を認識します(図3)。この条件は標準I<sup>2</sup>Cの形式ではありません。START及びSTOP条件は少なくともクロックパルス1つによって離されている必要があります。

## REPEATED START条件

REPEATED START( $S_r$ )条件はバス上のデータ方向変更を示すことがあります。このような変化はコマンドワードがリード(読み取り)動作を開始する必要がある場合に

図1. 2線シリアルインターフェースタイミング図

# クワッド、12ビット、低電力、2線、シリアル 電圧出力DAC

図2. START及びSTOP条件

図3. 初期STOP条件

起こります。又、 $S_f$ は、バスマスターが複数のI<sup>2</sup>Cデバイスに書き込みをする時、及びバスの制御を放棄したくない時に使われます。MAX5842のシリアルインターフェースは $S_f$ 条件が連続書き込み動作を分けているかいないかに関わらずそれらをサポートします。連続書き込み動作にはデータフローの方向変化のために $S_f$ 条件が必要となります。

## アクノリッジビット(ACK)

アクノリッジビット(ACK)は全ての8ビットデータワードにも付加される9番目のビットです。ACKは常に受信デバイスによって生成されます。MAX5842は9番目のクロック期間にSDAをローにし、アドレス又はデータを受信している時にACKを発生します。データを伝送する時、MAX5842は受信デバイスがACKを発生するのを待ちます。ACKを監視することによってデータ伝送の失敗を検出することができます。データ伝送の不成功は受信デバイスが使用中又はシステムに障害が起きた場合に発生します。データ伝送不成功的イベントが起きた場合、バスマスターは後に通信を再度試みます。

## スレーブアドレス

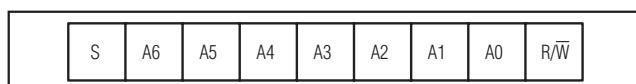

バスマスターはSTART条件に続いて7ビットスレーブアドレスを送信することによりスレーブデバイスとの

通信を開始します(図4)。アイドル時、MAX5842はスレーブアドレスが後に続くSTART条件を待ちます。シリアルインターフェースは各アドレス値をビット毎に比較し、不適切なアドレスが検出されるとインターフェースをただちにパワーダウンすることを可能にします。アドレスワードの LSB は Read(読み取り)/Write(書き込み)(R/W)ビットです。R/WはマスターがMAX5842から読み取り又は書き込みを実行しているかを表示します(R/W=0は書き込み条件、R/W=1は読み取り条件を選択します)。適切なアドレスを受信すると、その後MAX5842は1クロックサイクルの間にSDAをローにすることでACKを送信します。

MAX5842には異なる4つの出荷時/ユーザ設定アドレスがあります(表2)。アドレスビットA6からA1はプリセットされ、A0はADDによって制御されます。ADDをGNDに接続することによりA0=0、ADDをV<sub>DD</sub>に接続することによりA0=1が設定されます。この機能は最高4つのMAX5842が同じバスを共有することを可能にします。

表2. MAX5842 I<sup>2</sup>Cスレーブアドレス

| PART     | V <sub>ADD</sub> | DEVICE ADDRESS (A6...A0) |

|----------|------------------|--------------------------|

| MAX5842L | GND              | 0111 100                 |

| MAX5842L | V <sub>DD</sub>  | 0111 101                 |

| MAX5842M | GND              | 1011 100                 |

| MAX5842M | V <sub>DD</sub>  | 1011 101                 |

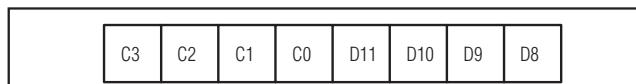

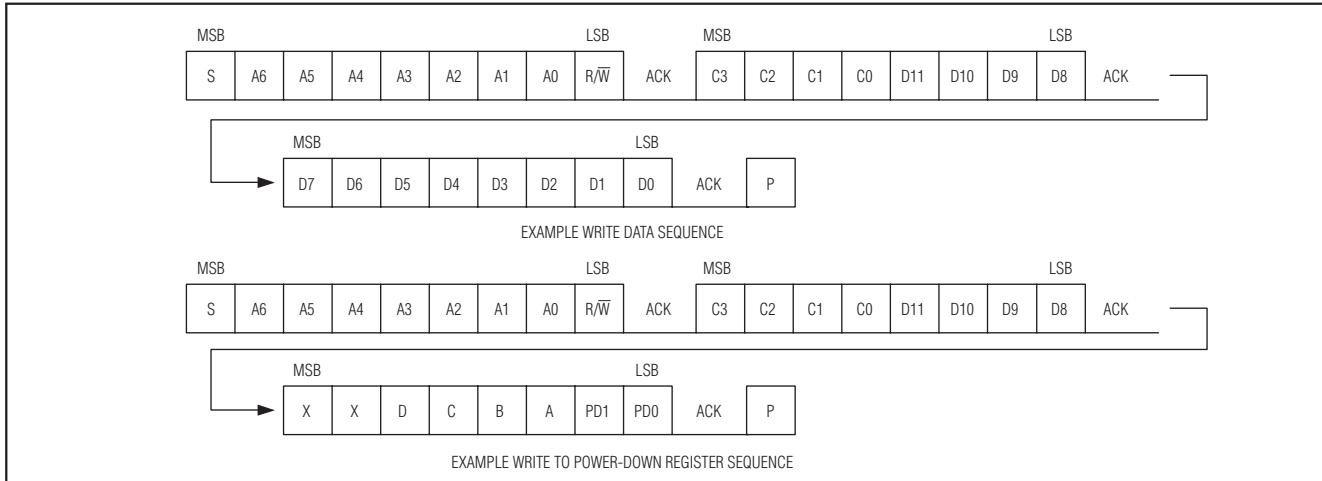

## 書き込みデータフォーマット

書き込みモード(R/W=0)では、アドレスバイトに続くデータがMAX5842を制御します(図5)。ビットC3-C0がMAX5842を構成します(表3)。ビットD11-D0はDACデータです。入力及びDACレジスタはアクノリッジビット期間にSCLの立下りエッジを更新します。書き込みサイクルが早期に打ち切られた場合、データは更新されず、書き込みサイクルを繰り返す必要があります。図6は書き込みデータシーケンスの2つの例を示しています。

図4. スレーブアドレスバイトの定義

図5. コマンドバイトの定義

# クワッド、12ビット、低電力、2線、シリアル 電圧出力DAC

図6. 書き込みコマンドシーケンスの例

## 拡張コマンドモード

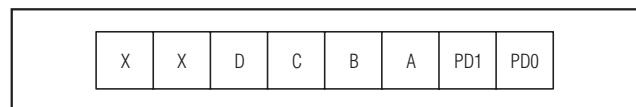

MAX5842はC3-C0=1に及びD11-D8=0に設定することによってアクセスされる拡張コマンドモードを備えています。次のデータバイトはシャットダウンレジスタに書き込みます(図7)。ビットA、B、C又はDを1に設定することによってPD0又はPD1の状態に基づき選択されたパワーダウンモードにDACを設定します(表1)。4つのDACのどのような組み合わせでも1つの書き込みシーケンスで制御することができます。

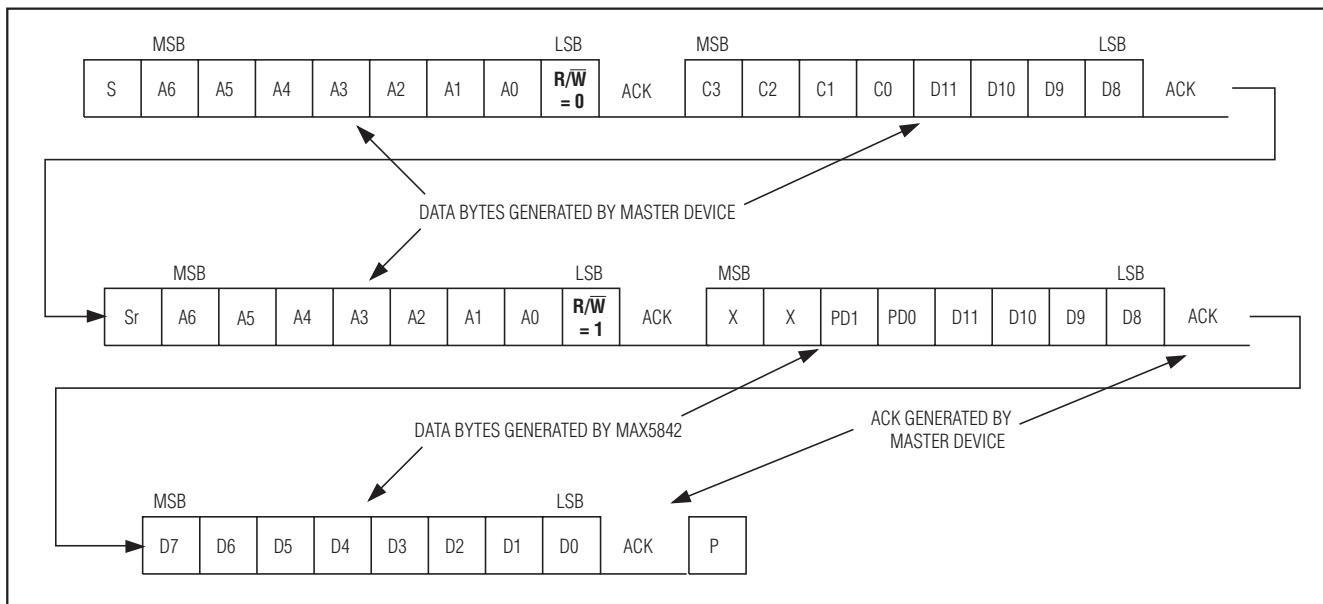

## 読み取りデータフォーマット

読み取りモード( $R/\bar{W}=1$ )では、MAX5842はDACレジスタの内容をバスに書き込みます。MAX5842によってアドレスが認識されるとデータ送信の方向が逆転します。デバイスはデータの最初のバイトを伝送し、マスクが認識するのを待ってから次のバイトを伝送します。図8が読み取りデータシーケンスの例を示しています。

## I<sup>2</sup>C互換性

MAX5842は既存のI<sup>2</sup>Cシステムと互換性があります。SCL及びSCAはハイインピーダンス入力です。SDAは9番目のクロックパルス期間にデータラインをローにプルするオーブンドレインを備えています。「標準動作回路」が標準I<sup>2</sup>Cアプリケーションを示しています。通信プロトコルが標準I<sup>2</sup>C 8ビット通信をサポートします。一般呼び出しあドレスは無視されます。MAX5842のアドレスは7ビットI<sup>2</sup>Cアドレスプロトコルにのみコンパチブルです。10ビットアドレス形式はサポートされていません。

## デジタルフィードスルー抑圧

MAX5842がアドレスのミスマッチを検出すると、シリアルインターフェースはSCL信号をコア回路から切断します。これは静止出力においてSCL信号によって

図7. 拡張コマンドバイトの定義

起きるデジタルフィードスルーを最小限に抑えます。シリアルインターフェースは有効なSTART条件が検出されるとSCL信号を再接続します。

## アプリケーション情報

### デジタル入力及びインタフェースロジック

MAX5842は2線デジタルインターフェースでI<sup>2</sup>C/SMBUSコンパチブルです。2つのデジタル入力(SCL及びSDA)はデジタル入力をDACに逐次ロードします。シムットトリガでバッファされた入力はフォトカプラーが直接デバイスにインタフェースするような低速遷移型インターフェースを可能にします。デジタル入力はCMOSロジックレベルとコンパチブルです。

### 電源バイパス及びグランド管理

システムの性能を最適にするため慎重なPCBのレイアウトが重要になります。アナログとデジタルの信号を隔離してノイズの介入とデジタルのフィードスルーを低減するようにします。グランドプレーンを使ってGNDから電源グランドへのグランドリターンが短く低インピーダンスであることを確認して下さい。 $V_{DD}$ を0.1 $\mu$ Fコンデンサを使い、できる限りデバイスに近接してグランドへバイパスして下さい。

## チップ情報

TRANSISTOR COUNT: 17,213

PROCESS: BiCMOS

# クワッド、12ビット、低電力、2線、シリアル 電圧出力DAC

表3. コマンドバイト定義

| SERIAL DATA INPUT |    |    |    |          |          |          |          | FUNCTION                                                                                                                                                                               |

|-------------------|----|----|----|----------|----------|----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C3                | C2 | C1 | C0 | D11      | D10      | D9       | D8       |                                                                                                                                                                                        |

| 0                 | 0  | 0  | 0  | DAC DATA | DAC DATA | DAC DATA | DAC DATA | Load DAC A input and DAC registers with new data. Contents of DAC B, C, and D input registers are transferred to the respective DAC registers. All outputs are updated.                |

| 0                 | 0  | 0  | 1  | DAC DATA | DAC DATA | DAC DATA | DAC DATA | Load DAC B input and DAC registers with new data. Contents of DAC A, C, and D input registers are transferred to the respective DAC registers. All outputs are updated.                |

| 0                 | 0  | 1  | 0  | DAC DATA | DAC DATA | DAC DATA | DAC DATA | Load DAC C input and DAC registers with new data. Contents of DAC A, B, and D input registers are transferred to the respective DAC registers. All outputs are updated.                |

| 0                 | 0  | 1  | 1  | DAC DATA | DAC DATA | DAC DATA | DAC DATA | Load DAC D input and DAC registers with new data. Contents of DAC A, B, and C input registers are transferred to the respective DAC registers. All outputs are updated simultaneously. |

| 0                 | 1  | 0  | 0  | DAC DATA | DAC DATA | DAC DATA | DAC DATA | Load DAC A input register with new data. DAC outputs remain unchanged.                                                                                                                 |

| 0                 | 1  | 0  | 1  | DAC DATA | DAC DATA | DAC DATA | DAC DATA | Load DAC B input register with new data. DAC outputs remain unchanged.                                                                                                                 |

| 0                 | 1  | 1  | 0  | DAC DATA | DAC DATA | DAC DATA | DAC DATA | Load DAC C input register with new data. DAC outputs remain unchanged.                                                                                                                 |

| 0                 | 1  | 1  | 1  | DAC DATA | DAC DATA | DAC DATA | DAC DATA | Load DAC D input register with new data. DAC outputs remain unchanged.                                                                                                                 |

| 1                 | 0  | 0  | 0  | DAC DATA | DAC DATA | DAC DATA | DAC DATA | Data in all input registers is transferred to respective DAC registers. All DAC outputs are updated simultaneously. New data is loaded into DAC A input register.                      |

| 1                 | 0  | 0  | 1  | DAC DATA | DAC DATA | DAC DATA | DAC DATA | Data in all input registers is transferred to respective DAC registers. All DAC outputs are updated simultaneously. New data is loaded into DAC B input register.                      |

| 1                 | 0  | 1  | 0  | DAC DATA | DAC DATA | DAC DATA | DAC DATA | Data in all input registers is transferred to respective DAC registers. All DAC outputs are updated simultaneously. New data is loaded into DAC C input register.                      |

| 1                 | 0  | 1  | 1  | DAC DATA | DAC DATA | DAC DATA | DAC DATA | Data in all input registers is transferred to respective DAC registers. All DAC outputs are updated simultaneously. New data is loaded into DAC D input register.                      |

| 1                 | 1  | 0  | 0  | DAC DATA | DAC DATA | DAC DATA | DAC DATA | Load all DACs with new data and update all DAC outputs simultaneously. Both input and DAC registers are updated with new data.                                                         |

| 1                 | 1  | 0  | 1  | DAC DATA | DAC DATA | DAC DATA | DAC DATA | Load all input registers with new data. DAC outputs remain unchanged.                                                                                                                  |

# クワッド、12ビット、低電力、2線、シリアル 電圧出力D/Aコンバータ

**MAX5842**

表3. コマンドバイト定義(続き)

| SERIAL DATA INPUT |    |    |    |     |     |    |    |                                                                                                           | FUNCTION |  |  |  |  |  |  |  |

|-------------------|----|----|----|-----|-----|----|----|-----------------------------------------------------------------------------------------------------------|----------|--|--|--|--|--|--|--|

| C3                | C2 | C1 | C0 | D11 | D10 | D9 | D8 |                                                                                                           |          |  |  |  |  |  |  |  |

| 1                 | 1  | 1  | 0  | X   | X   | X  | X  | Update all DAC outputs simultaneously. Device ignores D11-D8. Do not send the data byte.                  |          |  |  |  |  |  |  |  |

| 1                 | 1  | 1  | 1  | 0   | 0   | 0  | 0  | Extended command mode. The next word writes to the power-down registers ( <i>Extended Command Mode</i> ). |          |  |  |  |  |  |  |  |

| 1                 | 1  | 1  | 1  | 0   | 0   | 0  | 1  | Read DAC A data. The device expects an S <sub>r</sub> condition followed by an address word with R/W = 1. |          |  |  |  |  |  |  |  |

| 1                 | 1  | 1  | 1  | 0   | 0   | 1  | 0  | Read DAC B data. The device expects an S <sub>r</sub> condition followed by an address word with R/W = 1. |          |  |  |  |  |  |  |  |

| 1                 | 1  | 1  | 1  | 0   | 1   | 0  | 0  | Read DAC C data. The device expects an S <sub>r</sub> condition followed by an address word with R/W = 1. |          |  |  |  |  |  |  |  |

| 1                 | 1  | 1  | 1  | 1   | 0   | 0  | 0  | Read DAC D data. The device expects an S <sub>r</sub> condition followed by an address word with R/W = 1. |          |  |  |  |  |  |  |  |

図8. 読み取りワードデータシーケンスの例

# クワッド、12ビット、低電力、2線、シリアル 電圧出力DAC

## ファンクションダイアグラム

# クワッド、12ビット、低電力、2線、シリアル 電圧出力DAC

## パッケージ

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、[japan.maxim-ic.com/packages](http://japan.maxim-ic.com/packages)をご参照下さい。)

**MAX5842**

10L\_uMAX.EPS

マキシム・ジャパン株式会社

〒169-0051 東京都新宿区西早稲田3-30-16(ホリゾン1ビル)

TEL. (03)3232-6141 FAX. (03)3232-6149

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。マキシムは隨時予告なく回路及び仕様を変更する権利を留保します。

**Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600**

15

© 2002 Maxim Integrated Products, Inc. All rights reserved. **MAXIM** is a registered trademark of Maxim Integrated Products, Inc.