# 低電力、低グリッヂ、オクタル10ビット電圧出力DAC シリアルインタフェース付

**MAX5308/MAX5309**

## 概要

MAX5308/MAX5309は、省スペース16ピンTSSOPパッケージに収められた10ビット、8チャネル、低電力電圧出力D/Aコンバータ(DAC)です。各DACにつき、電源電圧範囲は広範囲な+2.7V~5.5Vまで、又、消費電流は最大215 $\mu$ A以下なので、低電力、低電圧のアプリケーション用として最適です。MAX5308/MAX5309は、2nV-s低グリッヂエネルギーのため、高速応答のデジタル制御用及び閉ループシステム用に理想的なデバイスです。

MAX5308は複数のデバイスをデイジーチェーン接続するのに使えるデジタル出力(DOUT)を備えています。MAX5309は、全てのレジスタ及びDACを0にクリアするハードウェアのリセット入力(CLR)を備えています。MAX5308/MAX5309は消費電流を1 $\mu$ Aまで低減するソフトウェアで設定可能なシャットダウン機能を備えています。MAX5308/MAX5309には8つ全てのDACの出力を同時に更新するロードDAC(LDAC)機能が装備されています。

3線SPI™/QSPI™/MICROWIRE™及びDSPコンパチブルのシリアルインタフェースは、1つのソフトウェアコマンドによって、入力及びDACレジスタをそれぞれ独立して、あるいは同時に更新することができます。これらのデバイスは、デジタル入力から出力までのデジタルノイズのフィードスルーを低減するダブルバッファ設計となっています。

MAX5308/MAX5309の動作温度範囲は-40°C ~ +85°Cです。

## アプリケーション

- 利得及びオフセット調整

- パワーアンプ制御

- I/Oボードのプロセス制御

- ポータブル計測器

- 光学部品の制御

SPI及びQSPIはMotorola, Inc.の商標です。

MICROWIREはNational Semiconductor, Corp.の商標です。

## 特長

- ◆ 16ピンTSSOP(6.4mm x 5mm)パッケージに収められた、8つの高集積化10ビットDAC

- ◆ 超低グリッヂエネルギー：2nV-s以下

- ◆ 低トータル消費電流：

$V_{REF} = V_{DD} = +5.5V$ で1.7mA(最大)

- ◆ 単一電源：広範囲な+2.7V~+5.5V

- ◆ 高速セトリング時間：5 $\mu$ s

- ◆ ソフトウェア選択可能なシャットダウンモード：1 $\mu$ A以下

- ◆ 15MHz SPI/QSPI/MICROWIREコンパチブル3線シリアルインタフェース

- ◆ パワーアップリセット：ゼロスケール

## 型番

| PART              | TEMP. RANGE    | PIN-PACKAGE |

|-------------------|----------------|-------------|

| <b>MAX5308EUE</b> | -40°C to +85°C | 16 TSSOP    |

| <b>MAX5309EUE</b> | -40°C to +85°C | 16 TSSOP    |

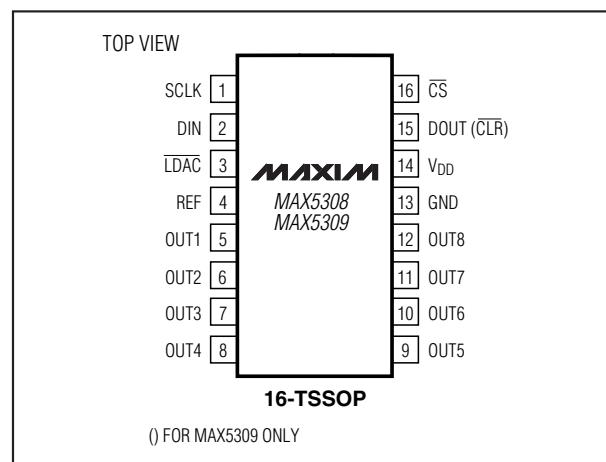

## ピン配置

# 低電力、低グリッチ、オクタル10ビット電圧出力DAC シリアルインターフェース付

## ABSOLUTE MAXIMUM RATINGS

|                                                       |                                   |

|-------------------------------------------------------|-----------------------------------|

| V <sub>DD</sub> to GND                                | -0.3V to +6V                      |

| All Other Pins to GND                                 | -0.3V to (V <sub>DD</sub> + 0.3V) |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |                                   |

| 16-Pin TSSOP (derate 9.4mW/°C above +70°C)            | 775mW                             |

| Maximum Current into Any Pin                          | ±50mA                             |

|                                   |                 |

|-----------------------------------|-----------------|

| Operating Temperature Range       | -40°C to +85°C  |

| Junction Temperature              | +150°C          |

| Storage Temperature Range         | -65°C to +150°C |

| Lead Temperature (soldering, 10s) | +300°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

(V<sub>DD</sub> = +2.7V to +5.5V, GND = 0, V<sub>REF</sub> = V<sub>DD</sub>, C<sub>L</sub> = 200pF, R<sub>L</sub> = 2kΩ, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at V<sub>DD</sub> = +5V, T<sub>A</sub> = +25°C.)

| PARAMETER                              | SYMBOL             | CONDITIONS              | MIN   | TYP                     | MAX  | UNITS   |

|----------------------------------------|--------------------|-------------------------|-------|-------------------------|------|---------|

| <b>STATIC ACCURACY</b> (Notes 1, 2)    |                    |                         |       |                         |      |         |

| Resolution                             | N                  |                         | 10    |                         |      | Bits    |

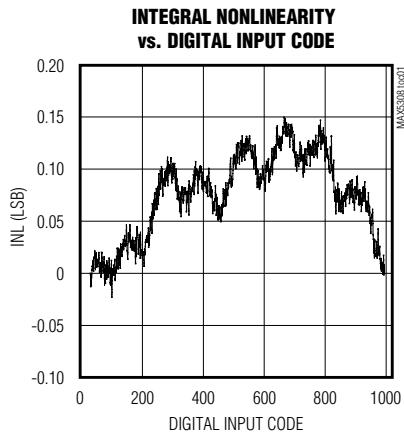

| Integral Nonlinearity                  | INL                |                         |       | ±0.5                    | ±2   | LSB     |

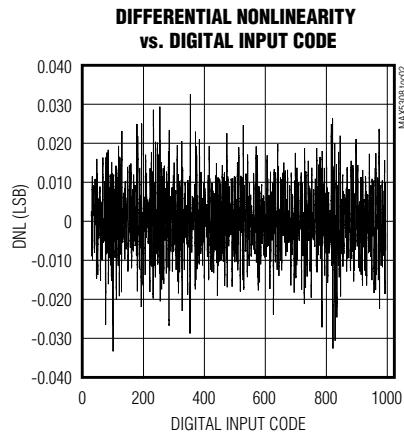

| Differential Nonlinearity              | DNL                | Guaranteed monotonic    |       |                         | ±0.5 | LSB     |

| Offset Error (Note 3)                  | VOE                |                         |       | ±10                     | ±60  | mV      |

| Offset Error Temperature Coefficient   |                    |                         |       | ±10                     |      | µV/°C   |

| Gain Error (Note 3)                    | VGE                |                         |       | ±0.1                    | ±1   | % of FS |

| Gain Error Temperature Coefficient     |                    |                         |       | ±5                      |      | ppm/°C  |

| <b>REFERENCE INPUT</b>                 |                    |                         |       |                         |      |         |

| Reference Input Voltage Range (Note 4) | V <sub>REF</sub>   |                         | 0.8   | V <sub>DD</sub>         |      | V       |

| Reference Input Impedance              | R <sub>REFIN</sub> |                         | 135   | 200                     | 265  | kΩ      |

| Reference Current                      | I <sub>REFPD</sub> | In power-down mode      |       | 1                       | 10   | µA      |

| <b>DAC OUTPUTS</b>                     |                    |                         |       |                         |      |         |

| Output Voltage Range                   |                    | With no-load            | 0.020 | V <sub>DD</sub> - 0.020 |      | V       |

| DC Output Impedance                    |                    |                         |       | 0.5                     |      | Ω       |

| Capacitive Load                        | C <sub>L</sub>     |                         |       | 500                     |      | pF      |

| Resistive Load                         | R <sub>L</sub>     |                         |       | 2                       |      | kΩ      |

| Short-Circuit Current                  |                    | V <sub>DD</sub> = +5V   |       | 33                      |      | mA      |

|                                        |                    | V <sub>DD</sub> = +2.7V |       | 20                      |      |         |

| Wake-Up Time                           |                    | From shutdown mode      |       | 24                      |      | µs      |

# 低電力、低グリッチ、オクタル10ビット電圧出力D/Aコンバータ シリアルインターフェース付

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{DD} = +2.7V$  to  $+5.5V$ ,  $GND = 0$ ,  $V_{REF} = V_{DD}$ ,  $C_L = 200\text{pF}$ ,  $R_L = 2\text{k}\Omega$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $V_{DD} = +5V$ ,  $T_A = +25^\circ\text{C}$ .)

| PARAMETER                                                | SYMBOL   | CONDITIONS                                                                 | MIN            | TYP       | MAX      | UNITS                      |

|----------------------------------------------------------|----------|----------------------------------------------------------------------------|----------------|-----------|----------|----------------------------|

| <b>DIGITAL INPUTS (SCLK, DIN, CS, LDAC, CLR—MAX5309)</b> |          |                                                                            |                |           |          |                            |

| Input High Voltage                                       | $V_{IH}$ | $V_{DD} = +5V \pm 10\%$                                                    | 2.4            |           |          | V                          |

|                                                          |          | $V_{DD} = +3V \pm 10\%$                                                    | 2.1            |           |          |                            |

| Input Low Voltage                                        | $V_{IL}$ | $V_{DD} = +5V \pm 10\%$                                                    |                | 0.8       |          | V                          |

|                                                          |          | $V_{DD} = +3V \pm 10\%$                                                    |                | 0.6       |          |                            |

| Input Leakage Current                                    | $I_{IN}$ | All digital inputs 0 or $V_{DD}$                                           |                | $\pm 0.1$ | $\pm 10$ | $\mu\text{A}$              |

| Input Capacitance                                        | $C_{IN}$ |                                                                            |                | 10        |          | $\text{pF}$                |

| <b>DIGITAL OUTPUT (MAX5308)</b>                          |          |                                                                            |                |           |          |                            |

| Output Low Voltage                                       | $V_{OL}$ | $I_{SINK} = 1\text{mA}$                                                    |                | 0.5       |          | V                          |

| Output High Voltage                                      | $V_{OH}$ | $I_{SOURCE} = 1\text{mA}$                                                  | $V_{DD} - 0.5$ |           |          | V                          |

| <b>DYNAMIC PERFORMANCE</b>                               |          |                                                                            |                |           |          |                            |

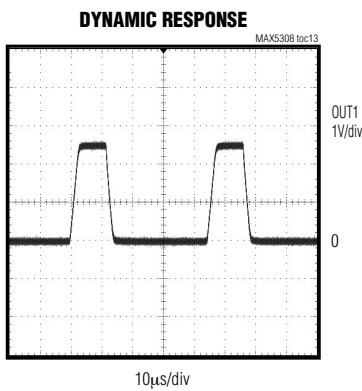

| Voltage-Output Slew Rate                                 | SR       | Positive and negative                                                      | 1              |           |          | $\text{V}/\mu\text{s}$     |

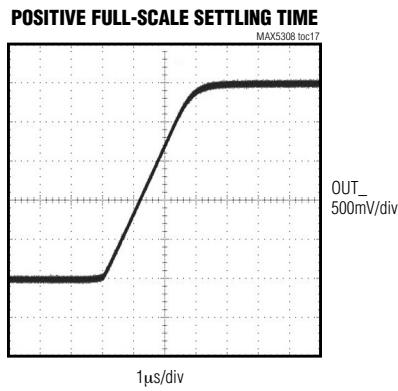

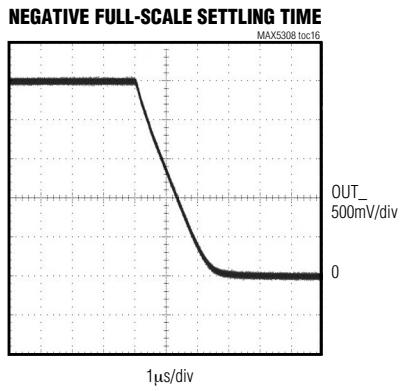

| Voltage-Output Settling Time                             | $t_S$    | FFHhex to 2FFhex                                                           | 5              |           |          | $\mu\text{s}$              |

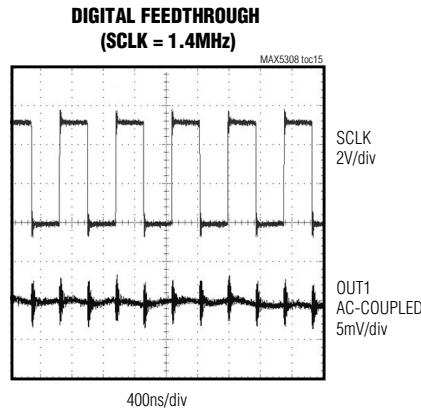

| Digital Feedthrough                                      |          | Code 0, all digital inputs from 0 to $V_{DD}$                              | 0.5            |           |          | $\text{nV}\cdot\text{s}$   |

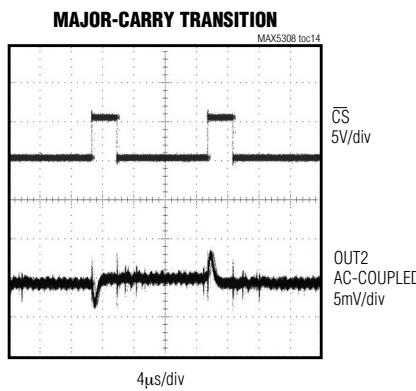

| DAC Glitch Impulse                                       |          | Major carry glitch                                                         | 2              |           |          | $\text{nV}\cdot\text{s}$   |

| DAC Output Noise                                         |          |                                                                            | 600            |           |          | $\mu\text{V}_{\text{p-p}}$ |

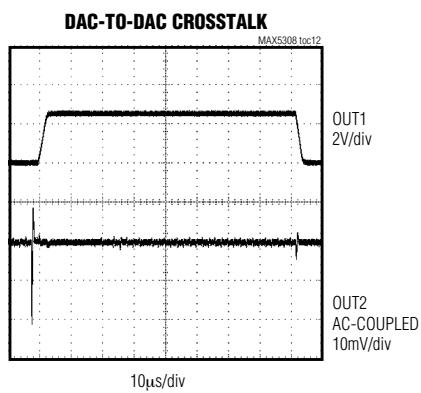

| DAC to DAC crosstalk                                     |          |                                                                            | 0.5            |           |          | $\text{nV}\cdot\text{s}$   |

| <b>POWER REQUIREMENTS</b>                                |          |                                                                            |                |           |          |                            |

| Supply Voltage Range                                     | $V_{DD}$ |                                                                            | 2.7            | 5.5       |          | V                          |

| Supply Current with No-Load (Note 5)                     | $I_{DD}$ | All digital inputs at 0 or $V_{DD}$ , $V_{DD} = V_{REF} = +5.5V$           | 1.5            | 1.7       |          | mA                         |

|                                                          |          | All digital inputs at 0 or $V_{DD}$ , $V_{DD} = +5.5V$ , $V_{REF} = +1.2V$ | 1.1            | 1.3       |          |                            |

|                                                          |          | All digital inputs at 0 or $V_{DD}$ , $V_{DD} = V_{REF} = +3V$             | 1.3            |           |          |                            |

|                                                          |          | Shutdown mode                                                              | 1              | 10        |          |                            |

# 低電力、低グリッチ、オクタル10ビット電圧出力DAC シリアルインターフェース付

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{DD} = +2.7V$  to  $+5.5V$ ,  $GND = 0$ ,  $V_{REF} = V_{DD}$ ,  $C_L = 200\text{pF}$ ,  $R_L = 2\text{k}\Omega$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $V_{DD} = +5V$ ,  $T_A = +25^\circ\text{C}$ .)

| PARAMETER                                    | SYMBOL        | CONDITIONS                       | MIN | TYP | MAX | UNITS |

|----------------------------------------------|---------------|----------------------------------|-----|-----|-----|-------|

| <b>TIMING CHARACTERISTICS</b>                |               |                                  |     |     |     |       |

| Serial Clock Frequency                       | $f_{SCLK}$    |                                  | 0   | 15  |     | MHz   |

| SCLK Pulse Width High                        | $t_{CH}$      |                                  | 33  |     |     | ns    |

| SCLK Pulse Width Low                         | $t_{CL}$      |                                  | 33  |     |     | ns    |

| $\overline{CS}$ Fall to SCLK Fall Setup Time | $t_{CSS}$     |                                  | 16  |     |     | ns    |

| SCLK Fall to $\overline{CS}$ Rise Setup Time | $t_{CSH}$     |                                  | 20  |     |     | ns    |

| LDAC Pulse Width Low                         | $t_{LDACPWL}$ |                                  | 20  |     |     | ns    |

| $\overline{CLR}$ Pulse Width Low             | $t_{CLRPWL}$  | MAX5309 only                     | 20  |     |     | ns    |

| DIN to SCLK Fall Setup Time                  | $t_{DS}$      |                                  | 16  |     |     | ns    |

| DIN to SCLK Fall Hold Time                   | $t_{DH}$      |                                  | 10  |     |     | ns    |

| $\overline{CS}$ Pulse Width High             | $t_{CSPWH}$   |                                  | 20  |     |     | ns    |

| SCLK Rise to DOUT Fall                       | $t_{SDL}$     | Load capacitance = $20\text{pF}$ |     | 50  |     | ns    |

| SCLK Rise to DOUT Rise                       | $t_{SDH}$     | Load capacitance = $20\text{pF}$ |     | 50  |     | ns    |

**Note 1:** Static accuracy tested without load.

**Note 2:** Linearity is tested within codes 1Dhex to 3E3hex.

**Note 3:** Gain and offset tested within codes 1Dhex to 3E3hex.

**Note 4:** Static accuracy specifications valid for  $V_{REF} = 1.2V$  to  $V_{DD}$ .

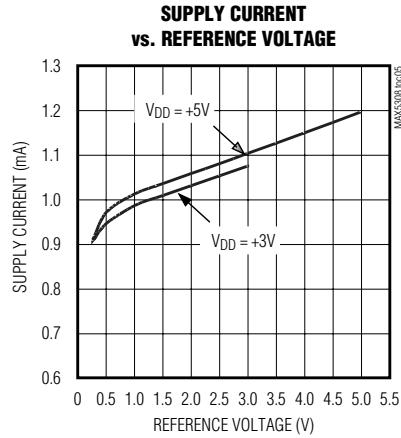

**Note 5:** Current scales linearly between these two extremes of  $V_{REF}$ .

# 低電力、低グリッチ、オクタル10ビット電圧出力D/Aコンバータ シリアルインターフェース付

**MAX5308/MAX5309**

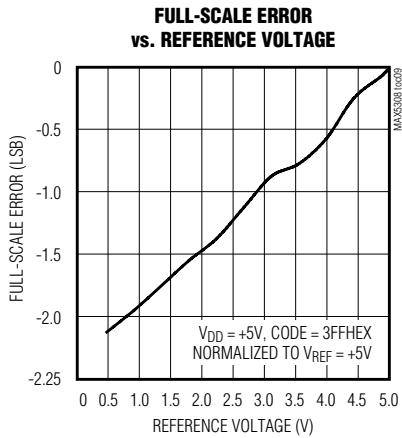

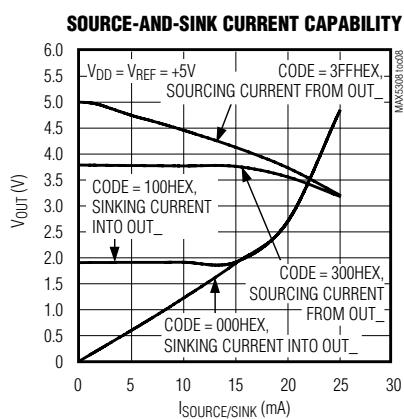

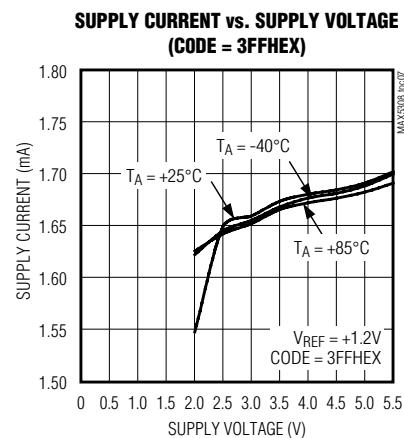

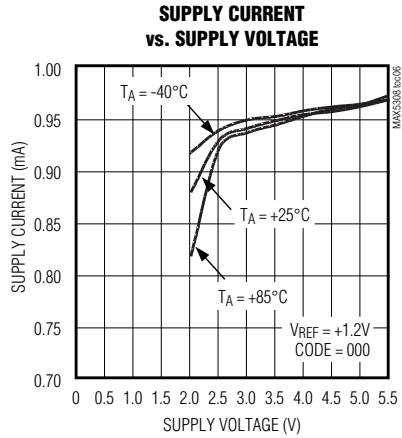

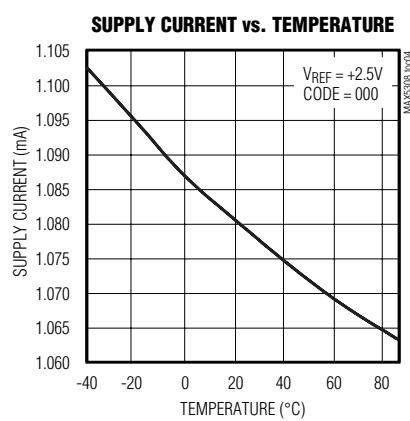

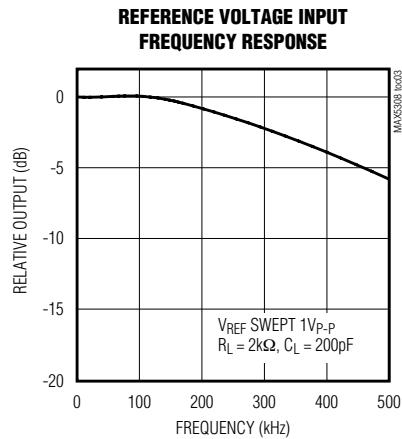

## 標準動作特性

( $V_{DD} = +5V$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

# 低電力、低グリッチ、オクタル10ビット電圧出力DAC シリアルインターフェース付

## 標準動作特性(続き)

( $V_{DD} = +5V$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

$V_{REF} = +2.5V$ ,  $R_L = 2k\Omega$ ,  $C_L = 200pF$

SWITCHING FROM CODE 000HEX TO FFFHEX

$V_{REF} = +2.5V$ ,  $R_L = 2k\Omega$ ,  $C_L = 200pF$

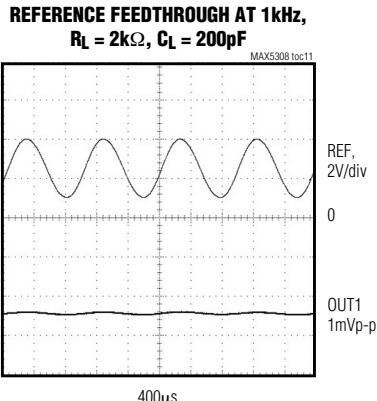

$V_{REF} = +2.5V$ ,  $R_L = 2k\Omega$ ,  $C_L = 200pF$

$CS = +5V$ ,  $DIN = 0$

DAC 1 CODE SET to 800HEX

# 低電力、低グリッチ、オクタル10ビット電圧出力D/Aコンバータ シリアルインターフェース付

MAX5308/MAX5309

## 端子説明

| 端子   | 名称              | 機能                                                                            |

|------|-----------------|-------------------------------------------------------------------------------|

| 1    | SCLK            | シリアルクロック入力。シリアルデータはSCLKの立下りエッジでロードされます。                                       |

| 2    | DIN             | シリアルデータ入力                                                                     |

| 3    | LDAC            | ロードD/A。LDACはD/A出力を同時に更新する非同期性アクティブロー入力です。LDACがローに駆動される場合、D/Aレジスタはトランスペアレントです。 |

| 4    | REF             | リファレンス電圧入力                                                                    |

| 5-12 | OUT_            | アナログ出力信号                                                                      |

| 13   | GND             | グランド                                                                          |

| 14   | V <sub>DD</sub> | 電源。0.1μFのコンデンサを使ってV <sub>DD</sub> をGNDへバイパスします。                               |

| 15   | DOUT            | データ出力(MAX5308)。DOUTはSCLKの立下りエッジで更新されます。                                       |

|      | CLR             | 非同期性クリアD/A(MAX5309)。全てのD/Aとレジスタをクリアにするアクティブロー入力です。全出力を0にリセットします。              |

| 16   | CS              | チップ選択入力(アクティブロー)                                                              |

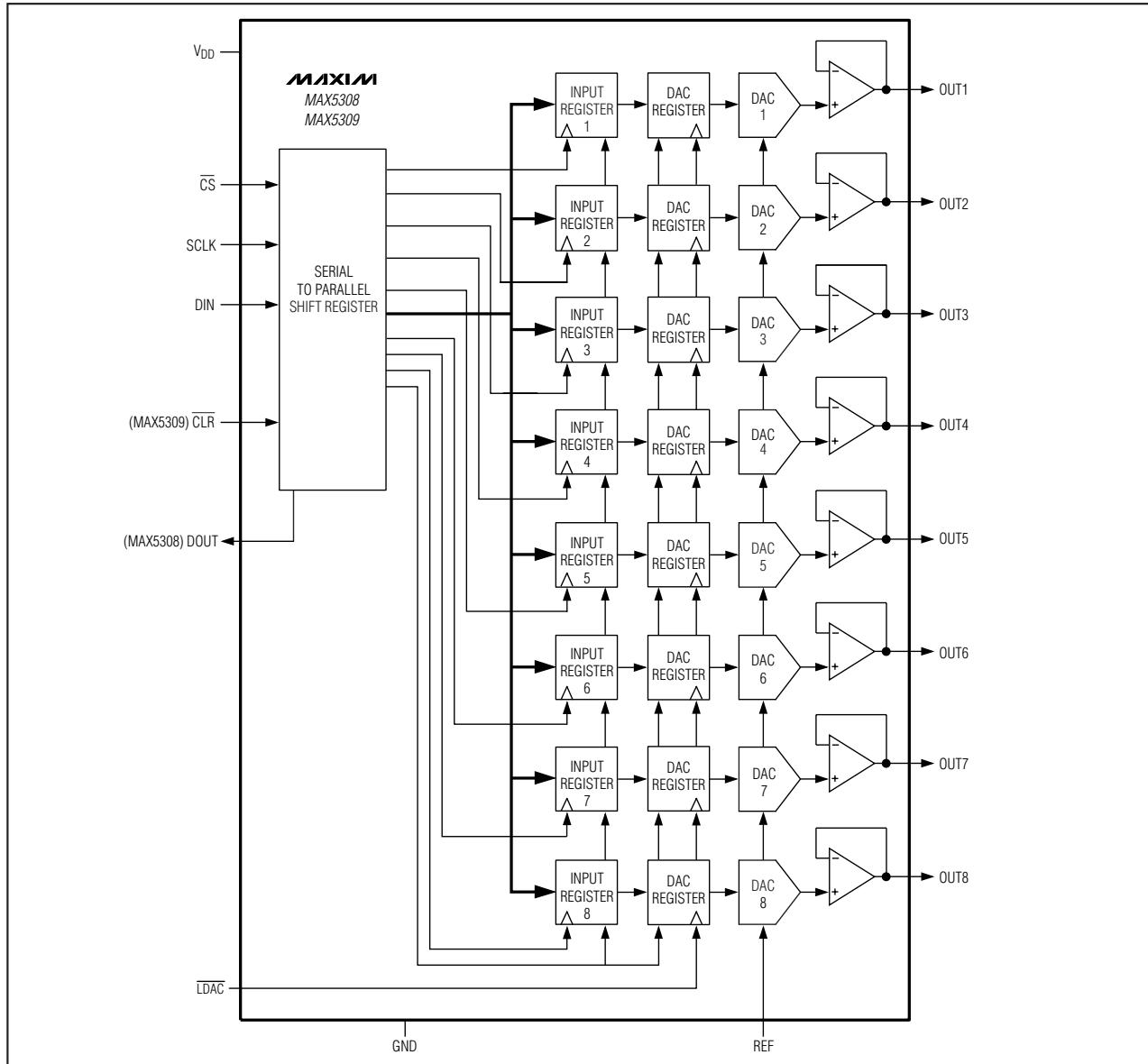

## 詳細

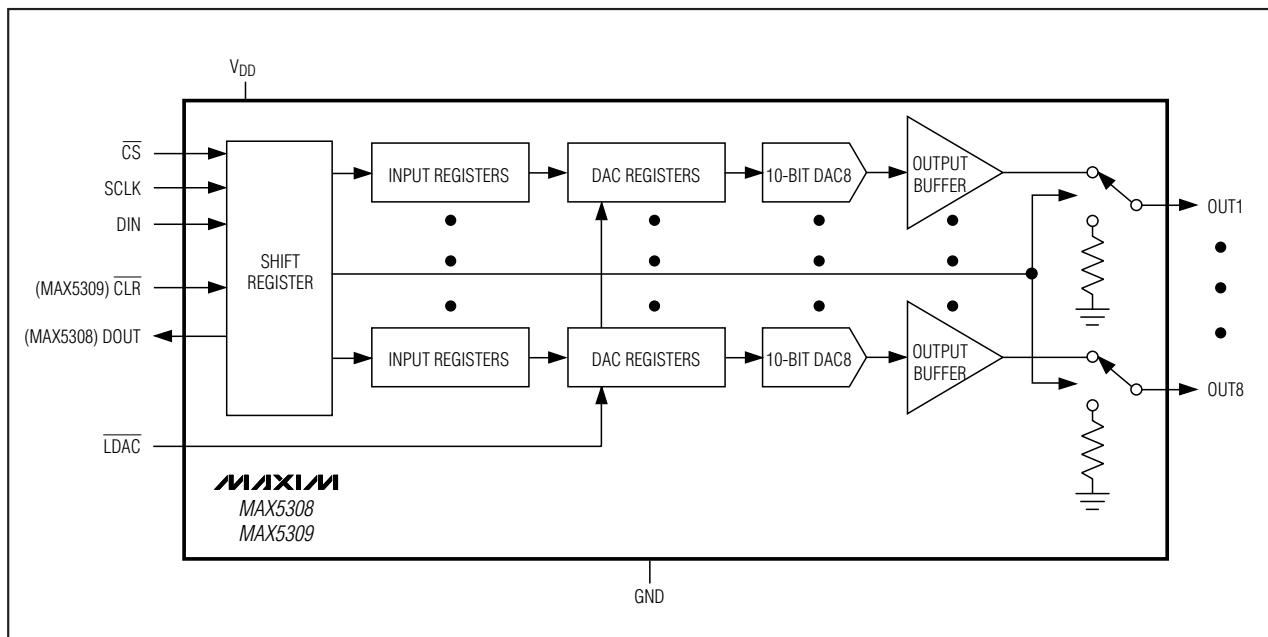

MAX5308/MAX5309は、シンプルな3線シリアルインターフェースを使って簡単にアドレスが可能な10ビット、8チャネル、低電力、電圧出力D/Aコンバータ(D/A)です。これらのデバイスは、共通の16ビットシリアル/パラレルシフトレジスタを使った8つのダブルバッファD/A、パワーオンリセット(POR)回路及び8つの出力バッファアンプを備えています。

図1はMAX5308/MAX5309のブロック図です。シフトレジスタは最大15MHzのクロックレートで動作し、各入力レジスタのためにシリアル16ビットワードをパラレルデータに変換します。シフトレジスタへの3線デジタルインターフェースは、チップ選択(CS)、シリアルクロック(SCLK)及びデータ入力(DIN)から構成されています。DINのシリアルデータはSCLKの立下りエッジでロードされます。

8つのダブルバッファD/Aは、入力及びD/Aレジスタで構成されています。入力レジスタは直接シフトレジスタに接続されており、最新の書き込み動作の結果を保持します。8つの10ビットD/Aレジスタは各D/Aの現行の出力コードを保持します。データは、ハードウェアインターフェース(LDAC)又はソフトウェアコマンドによって、入力レジスタからD/Aレジスタへ移行することができます。D/Aの出力は8つのレイルトゥレイルオペアンプを通してバッファされます。

MAX5308は、単一シリアルバス上に複数のデバイスをデジ털接続するのに使用できるデジタル出力(DOUT)を備えています。MAX5309は、内部レジスタを全てクリアにし、又D/Aを全てパワーダウンするハードウェアシャットダウン(CLR)機能を備えています。

MAX5308/MAX5309は、MAX6161ファミリーのような外部リファレンスを必要とします。リファレンス電圧範囲は0.8V~V<sub>DD</sub>です。

POR回路は、起動時にD/Aを定義した状態にします。起動時にはオフの状態となっているべきバルブや、他のトランジスタを駆動するアプリケーションを更に安全なものにするために、起動時に100kΩ抵抗を介してD/A出力をゼロにリセットします。

MAX5308/MAX5309は低デジタルフィードスルーの機能で、MSB遷移上のグリッヂエネルギーを最小にします。3線SPI、QSPI、MICROWIRE、及びDSPコンパチブルシリアルインターフェースによって回路ボードのスペースが更に節約されます。

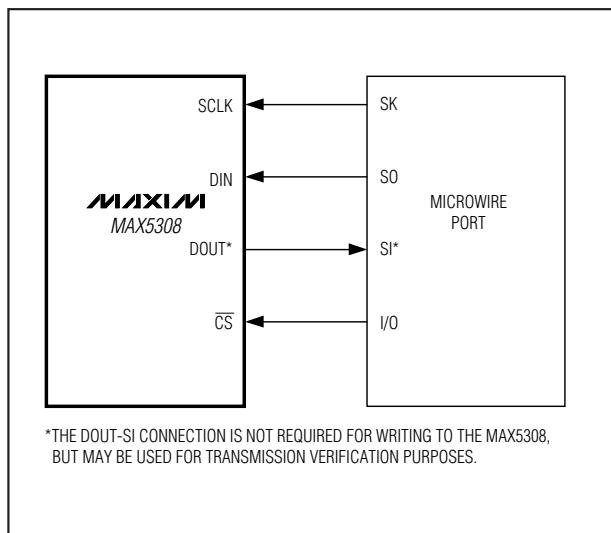

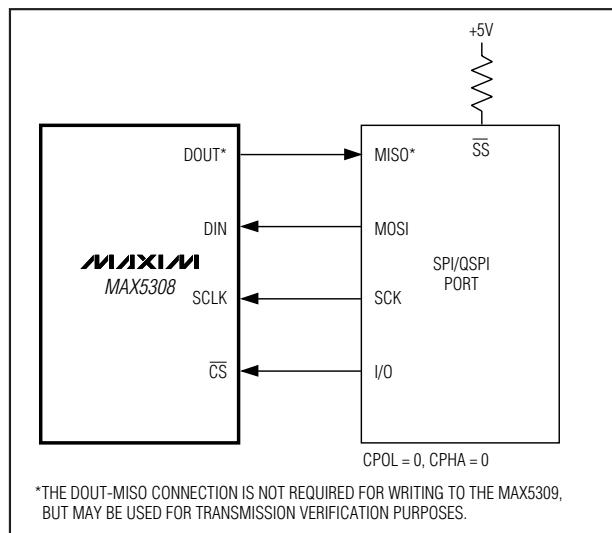

## シリアルインターフェースの構成

MAX5308/MAX5309の3線シリアルインターフェースはMICROWIRE、SPI、QSPI、及びDSP(図2と図3)とコンパチブルです。チップ選択入力(CS)は、DINにおけるシリアルデータのロードをフレームします。CSのハイからローへの遷移に続いて、データは同時にシフトされ、シリアルクロック入力(SCLK)の各立下りエッジで入力レジスタにラッチされます。各シリアルワードは16ビットで、最初の4ビットは表1に示されているように10データビット(MSBが先頭)に続く制御ワードです。最後の2データビットはゼロにする必要があります。10ビットD/Aコードは、1LSB=V<sub>REF</sub>/1024のユニポーラバイナリです。

シリアル入力レジスタは、16ビットのデータをロードし、CSをハイに駆動した後、内容を入力レジスタに移行します。CSの立下りエッジで書き込みシーケンスが開始するので、次の書き込みシーケンスの前に最低20nsの

# 低電力、低グリッチ、オクタル10ビット電圧出力DAC シリアルインターフェース付

表1. シリアルインターフェースの構成

| 16-BIT SERIAL WORD |    |    |    |           |       |       |       |       |       |       |       |     |     |   |       |          |                                                                                                                                            |

|--------------------|----|----|----|-----------|-------|-------|-------|-------|-------|-------|-------|-----|-----|---|-------|----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| CONTROL BITS       |    |    |    | DATA BITS |       |       |       |       |       |       |       |     |     |   |       |          |                                                                                                                                            |

| MSB                |    |    |    | LSB       |       |       |       |       |       |       |       |     |     |   |       |          |                                                                                                                                            |

| C3                 | C2 | C1 | C0 | D09       | D08   | D07   | D06   | D05   | D04   | D03   | D02   | D01 | D00 |   | DESC. | FUNCTION |                                                                                                                                            |

| 0                  | 0  | 0  | 0  | X         | X     | X     | X     | X     | X     | X     | X     | X   | X   | 0 | 0     | NOP      | No Operation                                                                                                                               |

| 0                  | 0  | 0  | 1  | X         | X     | X     | X     | X     | X     | X     | X     | X   | X   | 0 | 0     | RESET    | RESET All Internal Registers.<br>Power-down DACs, outputs pulled down with 100kΩ.<br>Equivalent to software CLR.                           |

| 0                  | 0  | 1  | 0  |           |       |       |       |       |       |       |       |     |     | 0 | 0     | DAC 1    | D9–D0 to Input Register 1, DAC Output Unchanged                                                                                            |

| 0                  | 0  | 1  | 1  |           |       |       |       |       |       |       |       |     |     | 0 | 0     | DAC 2    | D9–D0 to Input Register 2, DAC Output Unchanged                                                                                            |

| 0                  | 1  | 0  | 0  |           |       |       |       |       |       |       |       |     |     | 0 | 0     | DAC 3    | D9–D0 to Input Register 3, DAC Output Unchanged                                                                                            |

| 0                  | 1  | 0  | 1  |           |       |       |       |       |       |       |       |     |     | 0 | 0     | DAC 4    | D9–D0 to Input Register 4, DAC Output Unchanged                                                                                            |

| 0                  | 1  | 1  | 0  |           |       |       |       |       |       |       |       |     |     | 0 | 0     | DAC 5    | D9–D0 to Input Register 5, DAC Output Unchanged                                                                                            |

| 0                  | 1  | 1  | 1  |           |       |       |       |       |       |       |       |     |     | 0 | 0     | DAC 6    | D9–D0 to Input Register 6, DAC Output Unchanged                                                                                            |

| 1                  | 0  | 0  | 0  |           |       |       |       |       |       |       |       |     |     | 0 | 0     | DAC 7    | D9–D0 to Input Register 7, DAC Output Unchanged                                                                                            |

| 1                  | 0  | 0  | 1  |           |       |       |       |       |       |       |       |     |     | 0 | 0     | DAC 8    | D9–D0 to Input Register 8, DAC Output Unchanged                                                                                            |

| 1                  | 0  | 1  | 0  |           |       |       |       |       |       |       |       |     |     | 0 | 0     | DAC 1–4  | D9–D0 to Input Registers 1–4 and DAC Registers 1–4, DAC Outputs Updated (Write-Thru).                                                      |

| 1                  | 0  | 1  | 1  |           |       |       |       |       |       |       |       |     |     | 0 | 0     | DAC 5–8  | D9–D0 to Input Registers and DAC Registers, DAC Outputs Updated (Write-Thru).                                                              |

| 1                  | 1  | 0  | 0  |           |       |       |       |       |       |       |       |     |     | 0 | 0     | DAC 1–8  | D9–D0 to Input Registers and DAC Registers, DAC Outputs Updated (Write-Thru).                                                              |

| 1                  | 1  | 0  | 1  |           |       |       |       |       |       |       |       |     |     | 0 | 0     | DAC 1–8  | D9–D0 to Input Registers, DAC Outputs Unchanged                                                                                            |

| 1                  | 1  | 1  | 0  | DAC 8     | DAC 7 | DAC 6 | DAC 5 | DAC 4 | DAC 3 | DAC 2 | DAC 1 | X   | X   | 0 | 0     | DAC 1–8  | Input Registers to DAC Registers Indicated by Ones, DAC Outputs Updated, Equivalent to Software LDAC. (No effect on DACs indicated by 0s.) |

X = Don't Care

# 低電力、低グリッチ、オクタル10ビット電圧出力DAC シリアルインターフェース付

**MAX5308/MAX5309**

図1. ファンクションブロック図

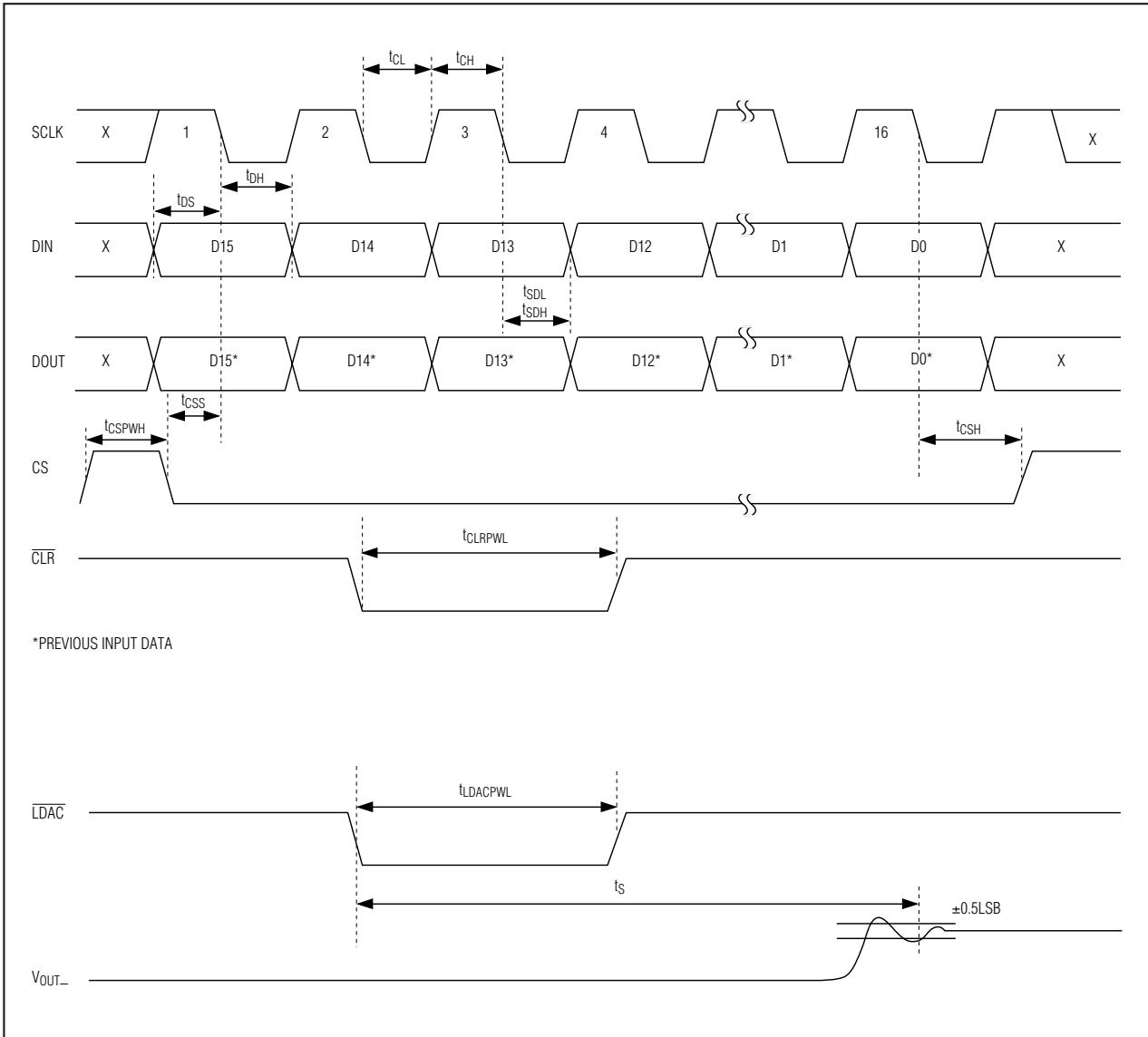

間 $\overline{CS}$ をハイにしておく必要があります。 $\overline{CS}$ がSCLKの16サイクルを完了する前にハイになった場合、入力データは廃棄されます。新しいデータの移行を開始するためには $\overline{CS}$ を再度ローに駆動して下さい。 $\overline{CS}$ 書き込みパルスの間、シリアルクロック(SCLK)はハイ又はローのどちらでも可能です。図4は完全な3線シリアルインターフェース伝送のタイミングダイアグラムです。

MAX5308/MAX5309のデジタル入力はダブルバッファされています。シリアルインターフェースを介して発せられたコマンドによって、DACレジスタに影響を及ぼすことなく入力レジスタにロードすることが可能であり、DACレジスタに直接ロードすることもできます。又は全ての8つのレジスタが入力レジスタから同時に更新されることも可能です。

# 低電力、低グリッチ、オクタル10ビット電圧出力DAC シリアルインターフェース付

表2. シリアルインターフェースのパワーアップ及びシャットダウンコマンド

| CONTROL BITS |    |    |    | DATA BITS |       |       |       |       |       |       |       |     |     |     |     |            |                                                                                                                                                                                                                         | FUNCTION |

|--------------|----|----|----|-----------|-------|-------|-------|-------|-------|-------|-------|-----|-----|-----|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| C3           | C2 | C1 | C0 | DAC 8     | DAC 7 | DAC 6 | DAC 5 | DAC 4 | DAC 3 | DAC 2 | DAC 1 | D03 | D02 | D01 | D00 | DESC.      |                                                                                                                                                                                                                         |          |

| 1            | 1  | 1  | 1  |           |       |       |       |       |       |       |       | 1   | 1   | X   | X   | Power-Up   | Power-Up individual DAC buffers indicated by data in DAC1 through DAC8. A one indicates the DAC output is connected and active. A zero does not affect the DACs present state.                                          |          |

| 1            | 1  | 1  | 1  |           |       |       |       |       |       |       |       | 0   | 1   | X   | X   | Shutdown 1 | Shutdown individual DAC buffers indicated by data in DAC1 through DAC8. A one indicates the DAC output is high-impedance. A zero does not affect the DACs' present state.                                               |          |

| 1            | 1  | 1  | 1  |           |       |       |       |       |       |       |       | 1   | 0   | X   | X   | Shutdown 2 | Shutdown individual DAC buffers indicated by data in DAC1 through DAC8. A one indicates the DAC is shutdown and the output is connected to GND through a 1kΩ resistor. A zero does not affect the DACs present state.   |          |

| 1            | 1  | 1  | 1  |           |       |       |       |       |       |       |       | 0   | 0   | X   | X   | Shutdown 3 | Shutdown individual DAC buffers indicated by data in DAC1 through DAC8. A one indicates the DAC is shutdown and the output is connected to GND through a 100kΩ resistor. A zero does not affect the DACs present state. |          |

X = Don't Care

## シャットダウンモード

MAX5308/MAX5309は、消費電流を1μA以下に低減する3つのソフトウェア制御のシャットダウンモードを備えています。3つのシャットダウンモードのうち2つ(シャットダウン2と3)は、各DACの出力が1kΩ又は100kΩ(デフォルト)のレジスタを介して個別にグランドに接続されています。3つ目のシャットダウン(シャットダウン1)コマンドはDACの出力を高インピーダンス状態にしておきます。表2はパワーアップコマンド、及び3つのシャットダウンモード動作をリストしたものです。

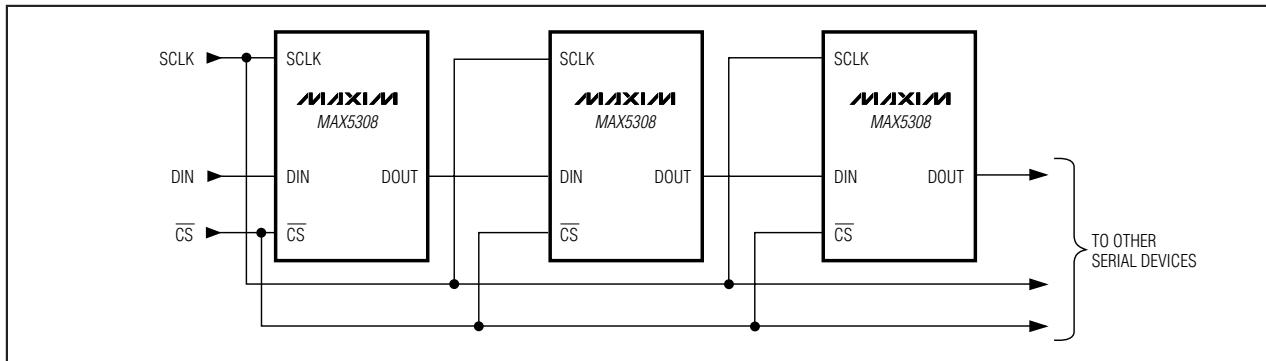

## シリアルデータ出力(DOUT)

DOUT(MAX5308)は16クロックサイクルの遅延でDINに続きます。DOUTはSCLKの立下りエッジから(最大)50nsの遅延で20pF負荷の駆動が可能です。

DOUTは複数のデバイスをデイジーチェーン接続するために主に使われます。オプションとして、DOUTをマイクロプロセッサ入力に接続することにより、DOUTを有効な通信を目的としたシリアルインターフェースの監視に使用することができます。

# 低電力、低グリッチ、オクタル10ビット電圧出力DAC シリアルインターフェース付

MAX5308/MAX5309

図2. MICROWIREの接続

## ハードウェアクリア( $\overline{CLR}$ )

MAX5309はアクティブローの $\overline{CLR}$ 入力を備えています。内部レジスタを全てクリアするために、DACを全てシャットダウンするために、又全DAC出力を $100\text{k}\Omega$ の抵抗を介してGNDへ終端処理するためには $\overline{CLR}$ をローに駆動して下さい。 $\overline{CLR}$ は非同期性で、いつでも適用できます。シリアルワードのロード中に $\overline{CLR}$ がローにトグルされる場合、そのワードは終了してしまうので再度ロードされる必要があります。

## リファレンス入力

外部リファレンス入力は $200\text{k}\Omega$ の標準入力インピーダンスを備えています。入力電圧範囲は $800\text{mV} \sim V_{DD}$ です。 $V_{DD}$ はMAX5308/MAX5309のためのリファレンスとして使うことが可能です。その場合DAC出力は $V_{DD}$ のレシオメトリック比率となります。

## 出力バッファ

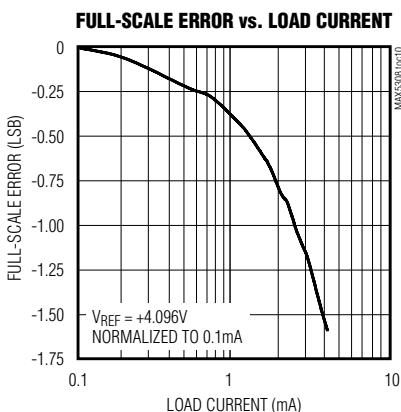

レイルトゥレイルバッファアンプは、 $2\text{k}\Omega$ 以上の抵抗負荷と $500\text{pF}$ 以下の容量負荷のいかなる組み合わせにおいても安定しています。 $200\text{pF}$ の容量負荷の場合、出力バッファのスルーレートは $1\text{V}/\mu\text{s}$ です。 $1/4\text{FS}$ から $3/4\text{FS}$ への出力遷移には、アンプ出力は通常 $200\text{pF}$ と並列に $2\text{k}\Omega$ をロードした時、セトリング時間 $10\mu\text{s}$ 以下で $1/2\text{LSB}$ に落ち着きます。

## パワーオンリセット

MAX5308/MAX5309は $V_{DD}$ が最初に適用される時、DAC出力をゼロに設定するPOR回路を備えています。これは、例えば電力損失の後システムを起動する場合、

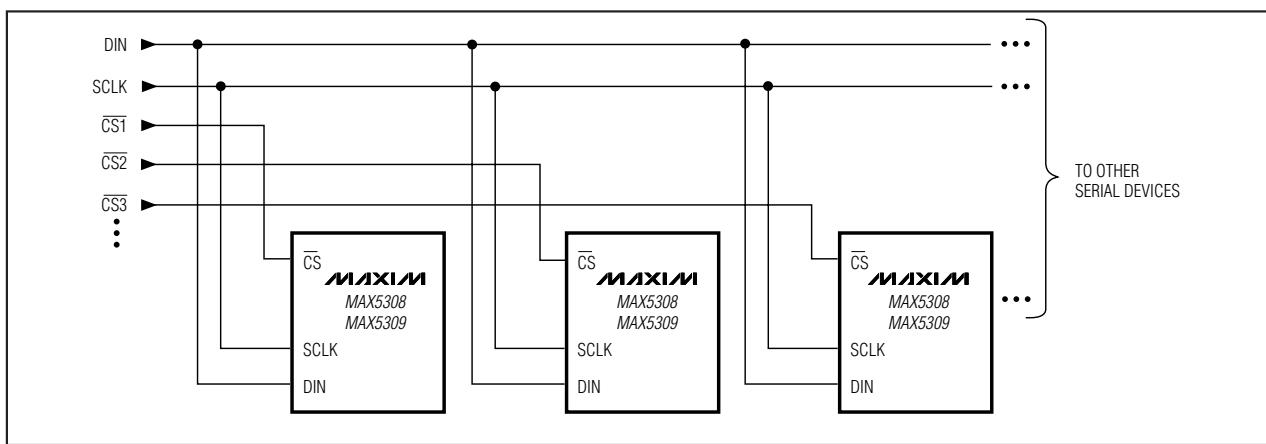

図3. SPI/QSPIの接続

起動直後に好ましくないDAC電圧出力が発生しないことを保証します。POR回路は最初のパワーアップ時に全てのDACレジスタがクリアされていること、DACはパワーダウンの状態であること、出力が $100\text{k}\Omega$ の抵抗を介してグランドに終端されていることを保証します。

## アプリケーション情報

### デバイスのデイジーチェーン接続

1つのデバイスのDOUTピンを次のデバイスのDINピンに接続することによって、任意の数のMAX5308をデイジーチェーン接続することができます。(図5)。チェーンに書きこむには、すべての $n \times 16$ クロックサイクル( $n$ はチェーン中のデバイスの数)及び関連データが最初のデバイスに適用されるまでCSをローに駆動します。 $\overline{CS}$ がハイに駆動されている時、チェーン中の各デバイスは、各入力レジスタの16ビットで作用します。チェーン中のデバイスの1つを調整するには、ノーオペレーション(NOP)コマンドが他の全てのデバイスにロードされる必要があります。

図6は複数のMAX5308及びMAX5309を接続する代替方法を示しています。この構成ではデータバスが全デバイスに共通であるため、データはデイジーチェーンを通してシフトされません。この構成では、各ICが専用のチップ選択入力( $\overline{CS}$ )を必要とするため、多くのI/O線が必要とされます。

### ユニポーラ出力

MAX5308/MAX5309は通常ユニポーラ出力用に構成されています。表3はユニポーラ電圧出力対デジタルコードの表です。

# 低電力、低グリッチ、オクタル10ビット電圧出力DAC シリアルインターフェース付

図4. タイミングダイアグラム

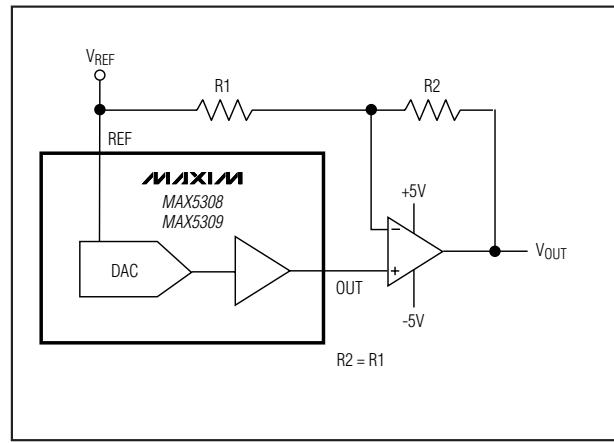

## バイポーラ出力

MAX5308/MAX5309の出力は、図7の回路を使ってバイポーラ動作に設定できます。

$$V_{OUT} = V_{REF} [(2D / 1024) - 1]$$

この場合、DはDACのバイナリ入力コードの10進値です。表4はデジタルコード(オフセットバイナリ)及び図7の回路の対応する出力電圧を示しています。

## 電源の考慮

パワーアップすると、全ての入力及びDACレジスタはクリアされ、DOUTはローの状態にあります。0.1μFコンデンサと並列に4.7μFコンデンサを使ってV<sub>DD</sub>をGNDにバイパスして下さい。短いリード線を使い、電源ピンとできるだけ近くにバイパスコンデンサを配置して下さい。

# 低電力、低グリッチ、オクタル10ビット電圧出力D/Aコンバータ シリアルインターフェース付

表3. ユニポーラコード表

| DAC CONTENTS |      |    | ANALOG OUTPUT                                                     |

|--------------|------|----|-------------------------------------------------------------------|

| MSB          | LSB  |    |                                                                   |

| 1111         | 1111 | 11 | $+ V_{REF} \left( \frac{1023}{1024} \right)$                      |

| 1000         | 0000 | 01 | $+ V_{REF} \left( \frac{513}{1024} \right)$                       |

| 1000         | 0000 | 00 | $+ V_{REF} \left( \frac{512}{1024} \right) = \frac{+ V_{REF}}{2}$ |

| 0111         | 1111 | 11 | $+ V_{REF} \left( \frac{511}{1024} \right)$                       |

| 0000         | 0000 | 01 | $V_{REF} \left( \frac{1}{1024} \right)$                           |

| 0000         | 0000 | 00 | 0V                                                                |

表4. バイポーラコード表

| DAC CONTENTS |      |    | ANALOG OUTPUT                                        |

|--------------|------|----|------------------------------------------------------|

| MSB          | LSB  |    |                                                      |

| 1111         | 1111 | 11 | $+V_{REF} \left( \frac{511}{512} \right)$            |

| 1000         | 0000 | 01 | $+V_{REF} \left( \frac{1}{512} \right)$              |

| 1000         | 0000 | 00 | 0V                                                   |

| 0111         | 1111 | 11 | $-V_{REF} \left( \frac{1}{512} \right)$              |

| 0000         | 0000 | 01 | $-V_{REF} \left( \frac{511}{512} \right)$            |

| 0000         | 0000 | 00 | $-V_{REF} \left( \frac{512}{512} \right) = -V_{REF}$ |

MAX5308/MAX5309

図5. 複数のMAX5308のデイジーチェーン接続

図6. 複数のMAX5308又はMAX5309が共通のDIN線を共有する場合

# 低電力、低グリッチ、オクタル10ビット電圧出力DAC シリアルインターフェース付

## 簡素化ブロック図

図7. バイポーラ出力回路

## チップ情報

TRANSISTOR COUNT: 19,000

PROCESS TECHNOLOGY: BiCMOS

# 低電力、低グリッヂ、オクタル10ビット電圧出力DAC シリアルインターフェース付

**MAX5308/MAX5309**

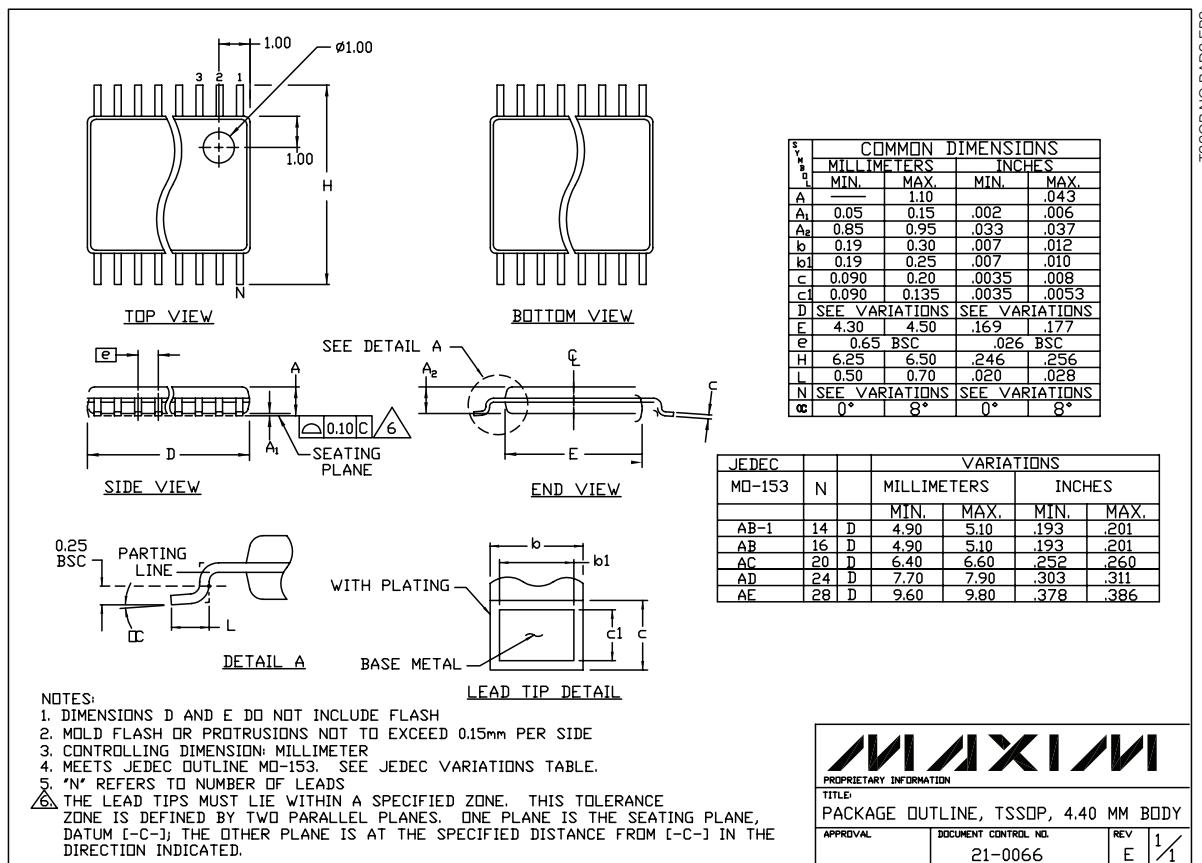

## パッケージ

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、[japan.maxim-ic.com/packages](http://japan.maxim-ic.com/packages)をご参照下さい。)

マキシム・ジャパン株式会社

〒169-0051 東京都新宿区西早稲田3-30-16(ホリゾン1ビル)

TEL. (03)3232-6141 FAX. (03)3232-6149

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。マキシムは隨時予告なく回路及び仕様を変更する権利を留保します。

**Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600** 15

© 2001 Maxim Integrated Products, Inc. All rights reserved. **MAXIM** is a registered trademark of Maxim Integrated Products, Inc.