### 概要

MAX5251は、+3Vで駆動し、4個の低電力、電圧出力10ビットディジタルアナログコンバータ(DAC)、及び4個の高精度出力アンプを省スペースの20ピンパッケージに収めています。4個の電圧出力に加えて、各アンプの負入力も使用できます。これにより、特定の利得設定、リモートセンシング及び大出力駆動能力の実現が容易になるため、MAX5251は工業用プロセス制御アプリケーションに最適です。その他の特長としては、ソフトウェアシャットダウン、ハードウェアシャットダウンロックアウト、全てのレジスタ及びDACをゼロにクリアするアクティブローリセット、ユーザプログラマブルロジック出力及びシリアルデータ出力等が挙げられます。

各DACは、入力レジスタにDACレジスタが続く構成のダブルバッファ付入力を備えています。データは、16ビットのシリアルワードで各入力/DACレジスタにロードされます。3線シリアルインタフェースは、SPI™/QSPI™及びMicrowire™とコンパチブルです。入力及びDACレジスタは単一のソフトウェアコマンドでそれぞれ独立に、あるいは同時に更新することができます。全てのロジック入力は、TTL/CMOSロジックコンパチブルです。

### アプリケーション

ディジタルオフセット及び利得調節 マイクロプロセッサ制御のシステム

工業用プロセス制御

自動試験機器

遠隔工業用制御

モーションコントロール

### 特長

- ◆ 設定可能な出力アンプ付の4個の10ビットDAC

- ◆ 電源:+3.0V~+3.6V単一

- ◆ 低消費電流: 0.8mA (通常動作)

- 3μA (シャットダウンモード)

- ◆ パッケージ: 20ピンSSOP

- ◆ パワーオンリセットで全てのレジスタ及びDACを ゼロにクリア

- ◆ SPI/QSPI及びMicrowireコンパチブル

- ◆ 3線シリアルインタフェースを通じてDACを同時 又は独立に制御

- ◆ ユーザプログラマブルディジタル出力

- ◆ 直接フォトカプラインタフェース用の シュミットトリガ入力

- ◆ 12ビットグレードアップ: MAX5253

### 型番

| PART        | TEMP. RANGE  | PIN-PACKAGE    | INL<br>(LSB) |

|-------------|--------------|----------------|--------------|

| MAX5251ACPP | 0°C to +70°C | 20 Plastic DIP | ±1/2         |

| MAX5251BCPP | 0°C to +70°C | 20 Plastic DIP | ±1           |

| MAX5251ACAP | 0°C to +70°C | 20 SSOP        | ±1/2         |

| MAX5251BCAP | 0°C to +70°C | 20 SSOP        | ±1           |

Ordering Information continued on last page.

Pin Configuration appears at end of data sheet.

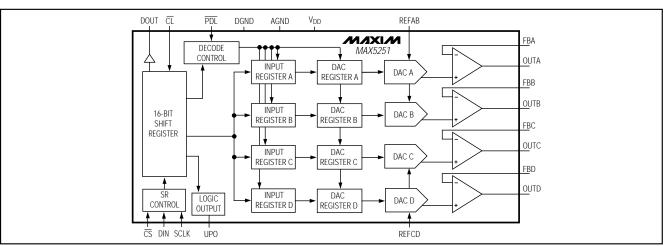

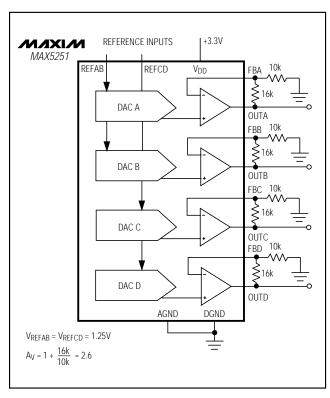

### ファンクションダイアグラム

SPI及びQSPIはMotorola Inc.の商標です。MicrowireはNational Semiconductor Corp.の商標です。

N/IXI/N

Maxim Integrated Products 1

integrated i roducts

本データシートに記載された内容はMaxim Integrated Productsの公式な英語版データシートを翻訳したものです。翻訳により生じる相違及び 誤りについては責任を負いかねます。正確な内容の把握には英語版データシートをご参照ください。

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to AGND0.3V to +6V<br>V <sub>DD</sub> to DGND0.3V to +6V |

|--------------------------------------------------------------------------|

| AGND to DGND±0.3V                                                        |

| REFAB, REFCD to AGND0.3V to (VDD + 0.3V)                                 |

| OUT_, FB_ to AGND0.3V to (V <sub>DD</sub> + 0.3V)                        |

| Digital Inputs to DGND0.3V to +6V                                        |

| DOUT, UPO to DGND0.3V to (V <sub>DD</sub> + 0.3V)                        |

| Continuous Current into Any Pin±20mA                                     |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )                    |

| Plastic DIP (derate 8.00mW/°C above +70°C)640mW                          |

| SSOP (derate 8.00mW/°C above +70°C)640mW                                 |

| CERDIP (derate 11.11mW/°C above +70°C)889mW                              |

| Operating Temperature Range  | es             |

|------------------------------|----------------|

| MAX5251_C_P                  | 0°C to +70°C   |

| MAX5251_E_P                  | 40°C to +85°C  |

| MAX5251BMJP                  | 55°C to +125°C |

| Storage Temperature Range    | 65°C to +150°C |

| Lead Temperature (soldering, | 10sec)+300°C   |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

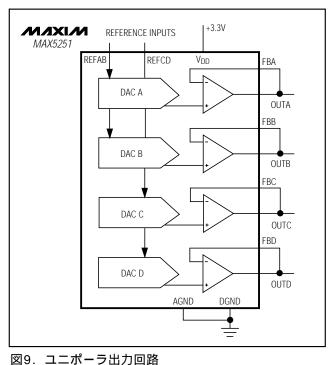

$(V_{DD}=+3.0V~to~+3.6V,~AGND=DGND=0V,~REFAB=REFCD=1.25V,~R_L=5k\Omega,~C_L=100pF,~T_A=T_{MIN}~to~T_{MAX},~unless~otherwise~noted.~Typical~values~are~at~T_A=+25^{\circ}C.~Output~buffer~connected~in~unity-gain~configuration~(Figure~9).)$

| PARAMETER                         | PARAMETER SYMBOL CONDITIONS |                                         | MIN | TYP   | MAX                   | UNITS  |

|-----------------------------------|-----------------------------|-----------------------------------------|-----|-------|-----------------------|--------|

| STATIC PERFORMANCE—ANALOG SECTION |                             |                                         |     |       |                       |        |

| Resolution                        | N                           |                                         | 10  |       |                       | Bits   |

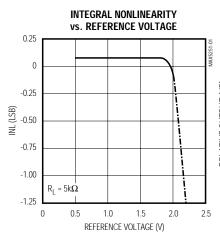

| Integral Manlinearity             |                             | MAX5251AC/E                             |     | ±0.25 | ±0.5                  |        |

| Integral Nonlinearity (Note 1)    | INL                         | MAX5251BC/E                             |     |       | ±1.0                  | LSB    |

|                                   |                             | MAX5251BMJP                             |     |       | ±2.0                  |        |

| Differential Nonlinearity         | DNL                         | Guaranteed monotonic                    |     |       | ±1.0                  | LSB    |

| Offset Error                      | Vos                         |                                         |     |       | ±6.0                  | mV     |

| Offset-Error Tempco               |                             |                                         |     | 6     |                       | ppm/°C |

| Gain Error (Note 1)               | GE                          |                                         |     |       | ±2.4                  | LSB    |

| Gain-Error Tempco                 |                             |                                         |     | 1     |                       | ppm/°C |

| Power-Supply Rejection Ratio      | PSRR                        | $V_{DD} = +3.0V \text{ to } +3.6V$      |     | 100   | 800                   | μV/V   |

| REFERENCE INPUT                   | •                           |                                         |     |       |                       | •      |

| Reference Input Range             | V <sub>REF</sub>            |                                         | 0   |       | V <sub>DD</sub> - 1.4 | V      |

| Reference Input Resistance        | R <sub>REF</sub>            | Code dependent, minimum at code 554 hex | 8   |       |                       | kΩ     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +3.0 \text{V to } +3.6 \text{V}, \text{AGND} = \text{DGND} = 0 \text{V}, \text{REFAB} = \text{REFCD} = 1.25 \text{V}, \text{R}_{L} = 5 \text{k}\Omega, \text{C}_{L} = 100 \text{pF}, \text{T}_{A} = \text{T}_{MIN} \text{ to T}_{MAX}, \text{unless otherwise noted. Typical values are at T}_{A} = +25 ^{\circ}\text{C}. \text{Output buffer connected in unity-gain configuration (Figure 9).}$

| PARAMETER                                | SYMBOL          | CONDITIONS                                                                  | MIN                   | TYP                | MAX  | UNITS |

|------------------------------------------|-----------------|-----------------------------------------------------------------------------|-----------------------|--------------------|------|-------|

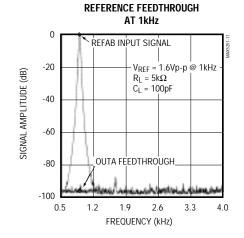

| MULTIPLYING-MODE PERFOR                  | MANCE           |                                                                             |                       |                    |      |       |

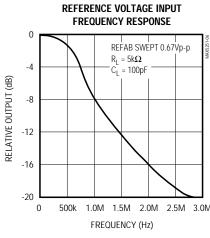

| Reference -3dB Bandwidth                 |                 | $V_{REF} = 0.67Vp-p$                                                        |                       | 650                |      | kHz   |

| Reference Feedthrough                    |                 | Input code = all 0s, V <sub>REF</sub> = 1.6Vp-p at 1kHz                     |                       | -84                |      | dB    |

| Signal-to-Noise Plus<br>Distortion Ratio | SINAD           | VREF = 1Vp-p at 25kHz, code = full scale                                    |                       | 72                 |      | dB    |

| DIGITAL INPUTS                           | •               |                                                                             |                       |                    |      | •     |

| Input High Voltage                       | VIH             |                                                                             | 2.0                   |                    |      | V     |

| Input Low Voltage                        | VIL             |                                                                             |                       |                    | 0.6  | V     |

| Input Leakage Current                    | liN             | VIN = OV or VDD                                                             |                       | 0.01               | ±1.0 | μΑ    |

| Input Capacitance                        | CIN             |                                                                             |                       | 8                  |      | pF    |

| DIGITAL OUTPUTS                          |                 |                                                                             | •                     |                    |      |       |

| Output High Voltage                      | Voн             | ISOURCE = 2mA                                                               | V <sub>DD</sub> - 0.5 |                    |      | V     |

| Output Low Voltage                       | VoL             | I <sub>SINK</sub> = 2mA                                                     |                       | 0.13               | 0.4  | V     |

| DYNAMIC PERFORMANCE                      |                 |                                                                             |                       |                    |      |       |

| Voltage Output Slew Rate                 | SR              |                                                                             |                       | 0.6                |      | V/µs  |

| Output Settling Time                     |                 | To $\pm 1/2$ LSB, V <sub>STEP</sub> = 1.25V                                 |                       | 12                 |      | μs    |

| Output Voltage Swing                     |                 | Rail-to-rail (Note 2)                                                       | (                     | to V <sub>DD</sub> |      | V     |

| Current into FB_                         |                 |                                                                             |                       | 0                  | 0.1  | μΑ    |

| OUT_ Leakage Current in Shutdown         |                 | R <sub>L</sub> = ∞                                                          |                       | 0.01               | ±1   | μΑ    |

| Start-Up Time Exiting<br>Shutdown Mode   |                 |                                                                             |                       | 20                 |      | μs    |

| Digital Feedthrough                      |                 | $\overline{\text{CS}} = \text{V}_{\text{DD}},  \text{DIN} = 100 \text{kHz}$ |                       | 5                  |      | nV-s  |

| Digital Crosstalk                        |                 |                                                                             |                       | 5                  |      | nV-s  |

| POWER SUPPLIES                           |                 |                                                                             |                       |                    |      |       |

| Supply Voltage                           | V <sub>DD</sub> | (Note 3)                                                                    | 3.0                   |                    | 3.6  | V     |

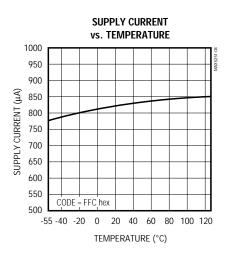

| Supply Current                           | I <sub>DD</sub> | (Note 4)                                                                    |                       | 0.82               | 0.98 | mA    |

| Supply Current in Shutdown               |                 | (Note 4)                                                                    |                       | 3                  | 20   | μΑ    |

| Reference Current in Shutdown            |                 |                                                                             |                       | 0.01               | ±1   | μΑ    |

**Note 1:** Guaranteed from code 5 to code 1023 in unity-gain configuration.

Note 2: Accuracy is better than 1LSB for VouT = 6mV to VDD - 80mV, guaranteed by PSR test at the endpoints.

**Note 3:** Remains operational with supply voltage as low as +2.7V.

**Note 4:**  $R_L = \infty$ , digital inputs at DGND or  $V_{DD}$ .

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +3.0 \text{V to } +3.6 \text{V}, \text{AGND} = \text{DGND} = 0 \text{V}, \text{REFAB} = \text{REFCD} = 1.25 \text{V}, \text{R}_{L} = 5 \text{k} \Omega, \text{C}_{L} = 100 \text{pF}, \text{T}_{A} = \text{T}_{MIN} \text{ to T}_{MAX}, \text{unless otherwise noted. Typical values are at T}_{A} = +25 ^{\circ}\text{C}. \text{Output buffer connected in unity-gain configuration (Figure 9).)}$

| PARAMETER                                          | SYMBOL           | CONDITIONS             | MIN | TYP | MAX | UNITS |  |  |

|----------------------------------------------------|------------------|------------------------|-----|-----|-----|-------|--|--|

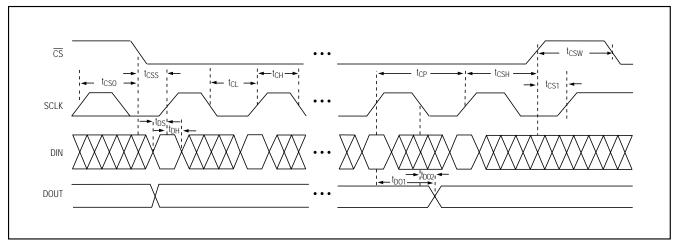

| TIMING CHARACTERISTICS (Figure 6)                  |                  |                        |     |     |     |       |  |  |

| SCLK Clock Period                                  | tcp              |                        | 100 |     |     | ns    |  |  |

| SCLK Pulse Width High                              | tсн              |                        | 40  |     |     | ns    |  |  |

| SCLK Pulse Width Low                               | tcL              |                        | 40  |     |     | ns    |  |  |

| CS Fall to SCLK Rise Setup Time                    | tcss             |                        | 40  |     |     | ns    |  |  |

| SCLK Rise to $\overline{\text{CS}}$ Rise Hold Time | tcsh             |                        | 0   |     |     | ns    |  |  |

| DIN Setup Time                                     | t <sub>DS</sub>  |                        | 40  |     |     | ns    |  |  |

| DIN Hold Time                                      | tDH              |                        | 0   |     |     | ns    |  |  |

| SCLK Rise to DOUT Valid<br>Propagation Delay       | tD01             | C <sub>L</sub> = 200pF |     |     | 120 | ns    |  |  |

| SCLK Fall to DOUT Valid<br>Propagation Delay       | t <sub>D02</sub> | C <sub>L</sub> = 200pF |     |     | 120 | ns    |  |  |

| SCLK Rise to CS Fall Delay                         | t <sub>CS0</sub> |                        | 40  |     |     | ns    |  |  |

| CS Rise to SCLK Rise Hold Time                     | tcs1             |                        | 40  |     |     | ns    |  |  |

| CS Pulse Width High                                | tcsw             |                        | 100 |     |     | ns    |  |  |

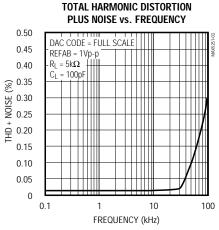

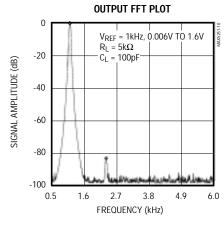

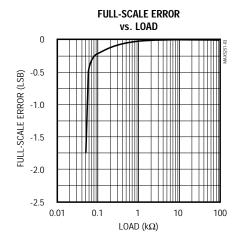

### 標準動作特性

$(V_{DD} = +3.3V, T_A = +25^{\circ}C, unless otherwise noted.)$

### 標準動作特性(続き)\_

$(V_{DD} = +3.3V, T_A = +25^{\circ}C, unless otherwise noted.)$

### 標準動作特性(続き)\_\_\_\_\_

$(V_{DD} = +3.3V, V_{REF} = 1.25V, R_L = 5k\Omega, C_L = 100pF, T_A = +25^{\circ}C, unless otherwise noted.)$

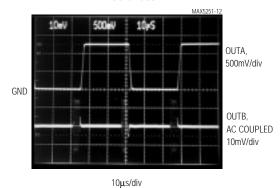

### MAJOR-CARRY TRANSITION

10µs/div

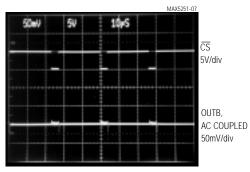

### DIGITAL FEEDTHROUGH (SCLK = 100kHz)

$\overline{\text{CS}} = \overline{\text{PDL}} = \overline{\text{CL}} = 3.3\text{V}, \text{ DIN} = 0\text{V}$ DAC A CODE SET TO 800 hex

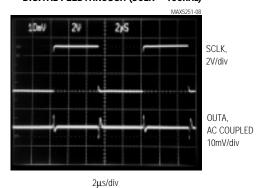

### ANALOG CROSSTALK

DAC A CODE SWITCHING FROM 00C hex TO FFC hex DAC B CODE SET TO 800 hex

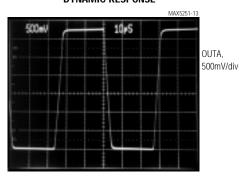

### DYNAMIC RESPONSE

10µs/div

SWITCHING FROM CODE 000 hex TO FB4 hex OUTPUT AMPLIFIER GAIN = +2.6

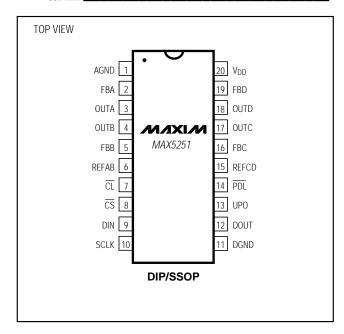

### 端子説明 \_\_\_\_\_\_

| 端子 | 名称              | 機能                                                     |

|----|-----------------|--------------------------------------------------------|

| 1  | AGND            | アナロググランド                                               |

| 2  | FBA             | DAC A出力アンプフィードバック                                      |

| 3  | OUTA            | DAC A出力電圧                                              |

| 4  | OUTB            | DAC B出力電圧                                              |

| 5  | FBB             | DAC B出力アンプフィードバック                                      |

| 6  | REFAB           | DAC A及びDAC Bのリファレンス電圧入力                                |

| 7  | CL              | 全てのDAC及びレジスタをクリア。全ての出力(OUT_、UPO、DOUT)を0にリセット(アクティブロー)。 |

| 8  | CS              | チップセレクト入力。アクティブロー。                                     |

| 9  | DIN             | シリアルデータ入力                                              |

| 10 | SCLK            | シリアルクロック入力                                             |

| 11 | DGND            | ディジタルグランド                                              |

| 12 | DOUT            | シリアルデータ出力                                              |

| 13 | UPO             | ユーザプログラマブルロジック出力                                       |

| 14 | PDL             | パワーダウンロックアウト。アクティブロー。ローの時ソフトウェアシャットダウンがロックアウトされます。     |

| 15 | REFCD           | DAC CとDAC Dのリファレンス電圧入力                                 |

| 16 | FBC             | DAC C出力アンプフィードバック                                      |

| 17 | OUTC            | DAC C出力電圧                                              |

| 18 | OUTD            | DAC D出力電圧                                              |

| 19 | FBD             | DAC D出力アンプフィードバック                                      |

| 20 | V <sub>DD</sub> | 正電源                                                    |

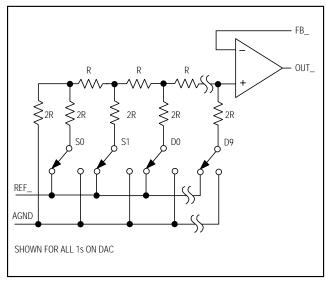

図1. DACの概略回路図

### 詳細

MAX5251は、シンプルな3線シリアルインタフェースで簡単にアドレス指定できる電圧出力ディジタルアナログコンバータ(DAC)を4個内蔵しています。16ビットデータイン/データアウトシフトレジスタを備え、各DACは入力レジスタ及びDACレジスタから成るダブルバッファ付入力を備えています(ファンクションダイアグラムを参照)。4つの電圧出力に加えて、各アンプの負入力を使用できます。

DACは、ディジタル入力(10ビット及び2個のサブビット)を印加されたリファレンス電圧入力に比例する等価アナログ出力電圧に変換する反転R-2Rラダーネットワークです。DAC A及びBはREFABリファレンス入力を共有し、DAC C及びDはREFCDリファレンス入力を共有しています。2つのリファレンス入力があるため、各DACペアが異なるフルスケール出力電圧で動作することができます。図1に、4個のDACの内の1つの概略回路図を示します。

### リファレンス入力

2つのリファレンス入力は、正のDC及びAC信号を受け入れます。各リファレンスにおける電圧が、対応する2つのDACのフルスケール出力電圧を設定します。リファレンス入力電圧範囲は、 $0V \sim (V_{DD}-1.4V)$ です。出力電圧 $(V_{OUT})$ は、次式に示すディジタル的に設定可能な電圧ソースとなります。

V<sub>OUT</sub> = (V<sub>REF</sub> x NB/1024) x 利得

ここでNBは、DACの入力コードの数値 $(0 \sim 1023)$ です。  $V_{REF}$ は、リファレンス電圧で利得は外部で設定された電圧利得です。

各リファレンス入力でのインピーダンスはコードに依存し、そのリファレンスに接続されている両方のDACの入力コードが16進の554の時に最小値の10kとなり、入力コードが16進の000の時に最大値(リーク電流に起因し、数G 以上)となります。リファレンスピンの入力インピーダンスがコードに依存するため、リファレンスソースの負荷レギュレーションが重要になります。

REFAB及びREFCDリファレンス入力は、最小入力インピーダンス10k を保証しています。2つのリファレンス入力が同じソースによって駆動されている場合、実効最小インピーダンスは5k です。REFABピンとREFCDピンを個別に駆動するとリファレンス精度が向上します。

MAX5251のREFAB及びREFCD入力は、シャットダウンモードではハイインピーダンス状態になり、入力リーク電流は $0.01\mu A(typ)$ となります。

リファレンス入力容量もやはりコードに依存し、入力コードが全て0の時に20pF、フルスケールでは100pF(typ)になります。

### 出力アンプ

MAX5251 DACの全ての出力は、内部の高精度アンプ (標準スルーレート $0.6V/\mu s$ )でバッファされています。各出力アンプの反転入力へのアクセスが可能であるため、ユーザによる出力利得設定/信号調節の自由度が高くなっています(「アプリケーション情報」の項を参照)。MAX5251の出力でフルスケール遷移があった場合の $\pm 1/2LSB$ への標準セトリング時間は、負荷が5kと100pFの並列の時に $12\mu s$ です(負荷が2k以下になると性能が劣化します)。

MAX5251の出力アンプの出力動的応答及びセトリング性能は、「標準動作特性」に示されています。

### パワーダウンモード

MAX5251は、ソフトウェアでプログラムできるシャット ダウンモードを備えており、この時の消費電流は  $3\mu A(typ)$ まで低減します。シャットダウンモードをイネーブルするためには、パワーダウンロックアウト (PDL)ピンがハイでなければなりません。入力制御ワードに1100XXXXXXXXXXXXXを書き込むとシャット ダウンモードになります(表1)。

シャットダウンモードでは、出力アンプ及びリファレンス入力がハイインピーダンス状態になります。シリアルインタフェースは、アクティブのままです。入力レジスタ内のデータはシャットダウン中も保持されるため、MAX5251はシャットダウンに入る前の出力

状態を呼び起こすことができます。パワーダウン状態を解除するには、以前の設定を呼び起こすか、新しいデータを使用してDACを更新します。本製品をパワーアップする時及びシャットダウンを解除する時は、出力安定時間として20us待ってください。

### シリアルインタフェースの構成

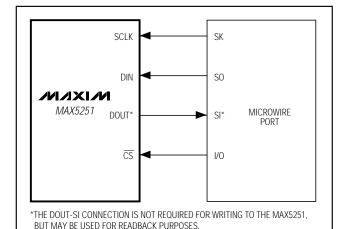

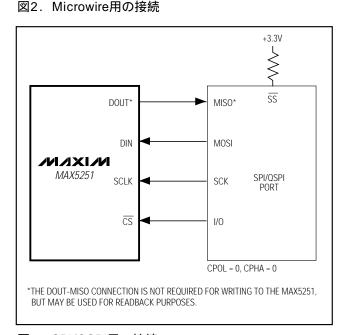

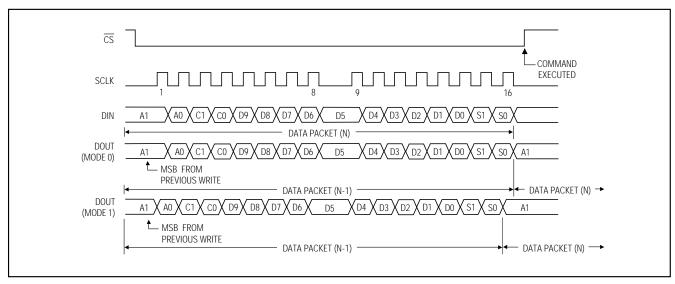

MAX5251の3線シリアルインタフェースは、Microwire<sup>TM</sup> (図2)及びSPI<sup>TM</sup>/QSPI<sup>TM</sup>(図3)の両方とコンパチブルです。シリアル入力ワードは、アドレスビット2個及び制御ビット2個の後に10+2個のデータビット(MSBが先頭)が続く構成になっています(図4)。この4ビットのアドレス/制御コードによって、表1に示すMAX5251の応答が決定されます。DOUTとシリアルインタフェースポートの間の接続は必ずしも必要ではありませんが、データエコーに使用することができます。MAX5251のシフトレジスタに保存されているデータは、DOUTからシフトアウトしてマイクロプロセッサ( $\mu$ P)に戻し、データの確認を行うことができます。

MAX5251のディジタル入力は、ダブルバッファ付です。シリアルインタフェースからのコマンドに従って、DACレジスタに影響を与えずに入力レジスタにロードし、DACレジスタに直接ロードして、又は入力レジスタから4個のDACレジスタを同時に更新できます(表1)。

### シリアルインタフェースの内容

MAX5251は、16ビットのシリアルデータを必要とします。表1は、シリアルインタフェースプログラミングコマンドのリストです。コマンドによっては、10+2個のデータビットは「ドントケア(任意)」となっています。データはMSBを先頭にして送られ、2つの8ビットパケットあるいは1つの16ビットワードとして送ることができます(16ビットが転送されるまで $\overline{CS}$ がローに保持される必要があります)。シリアルデータは、2個のDACアドレスビット(A1、A0)及び2個の制御ビット(C1、C0)に10+2個のデータビットD9…D0、S1、S0が続く構成になっています(図4)。サブビット(S0、S1)は両方ともゼロに設定してください。4ビットのアドレス/制御コードによって下記が決まります。

- 更新するべきレジスタ

- データがシリアルデータ出力(DOUT)からクロック アウトされるクロックエッジの選択

- ユーザプログラマブルロジック出力(UPO)の状態

- デバイスがシャットダウンモードに入るかどうか (PDLがハイであると仮定)

- シャットダウンモードを解除したときのデバイス設定

### 図3. SPI/QSPI用の接続

図4. シリアルデータフォーマット

### 表1. シリアルインタフェースのプログラミングコマンド

|                  |                  | 1                | 6-BIT            | SERIAL WORD                                                              |                  |             |                                                                                                                                                                                                         |  |

|------------------|------------------|------------------|------------------|--------------------------------------------------------------------------|------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A1               | Α0               | C1               | C0               | D9D0<br>MSBLSB                                                           | S1               | S0          | FUNCTION                                                                                                                                                                                                |  |

| 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 0<br>0<br>0<br>0 | 1<br>1<br>1<br>1 | 10-bit DAC data<br>10-bit DAC data<br>10-bit DAC data<br>10-bit DAC data | 0<br>0<br>0      | 0<br>0<br>0 | Load input register A; DAC registers unchanged. Load input register B; DAC registers unchanged. Load input register C; DAC registers unchanged. Load input register D; DAC registers unchanged.         |  |

| 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 1<br>1<br>1<br>1 | 1<br>1<br>1      | 10-bit DAC data<br>10-bit DAC data<br>10-bit DAC data<br>10-bit DAC data | 0<br>0<br>0<br>0 | 0<br>0<br>0 | Load input register A; all DAC registers updated. Load input register B; all DAC registers updated. Load input register C; all DAC registers updated. Load input register D; all DAC registers updated. |  |

| 0                | 1                | 0                | 0                | XXXXXXXXX                                                                | Х                | Χ           | Update all DAC registers from their respective input registers (also exit shutdown mode).                                                                                                               |  |

| 1                | 0                | 0                | 0                | 10-bit DAC data                                                          | 0                | 0           | Load all DAC registers from shift register (also exit shutdown mode).                                                                                                                                   |  |

| 1                | 1                | 0                | 0                | XXXXXXXXX                                                                | Х                | Χ           | Enter shutdown mode (provided PDL = 1).                                                                                                                                                                 |  |

| 0                | 0                | 1                | 0                | XXXXXXXXX                                                                | Х                | Χ           | UPO goes low (default).                                                                                                                                                                                 |  |

| 0                | 1                | 1                | 0                | XXXXXXXXX                                                                | Χ                | Χ           | UPO goes high.                                                                                                                                                                                          |  |

| 0                | 0                | 0                | 0                | XXXXXXXXX                                                                | Х                | Χ           | No operation (NOP) to DAC registers                                                                                                                                                                     |  |

| 1                | 1                | 1                | 0                | XXXXXXXXX                                                                | Х                | Χ           | Mode 1, DOUT clocked out on SCLK's rising edge. All DAC registers updated.                                                                                                                              |  |

| 1                | 0                | 1                | 0                | XXXXXXXXX                                                                | Х                | Х           | Mode 0, DOUT clocked out on SCLK's falling edge. All DAC registers updated (default).                                                                                                                   |  |

"X" = 任意

図5に、シリアルインタフェースのタイミングの必要条件を示します。DACのシリアルインタフェースをイネーブルするには、チップセレクトピン( $\overline{CS}$ )がローであることが必要です。 $\overline{CS}$ がハイの時、インタフェース制御回路はディセーブルされます。最初のビットを正しくクロックインするには、 $\overline{CS}$ がシリアルクロック(SCLK)の立上りエッジよりも少なくとも $t_{CSS}$ だけ以前にローになっている必要があります。 $\overline{CS}$ がローの時、データはSCLKの立上りエッジでシリアルデータ入力ピン(DIN)を通じて内部シフトレジスタにクロックインされます。最大保証クロック周波数は、10MHzです。データは $\overline{CS}$ の立上りエッジで該当するMAX5251入力/DACレジスタにラッチインされます。

プログラミングコマンド「Load-All-DACs-From-Shift-Register(全てのDACをシフトレジスタからロード)」を使用すると、入力シフトレジスタの同じディジタルコードを同時に全ての入力及びDACレジスタにロードできます。空動作(NOP)コマンドはレジスタの内容に影響を与えないため、MAX5251をデイジーチェーン接続する場合に便利です(「デバイスのデイジーチェーン接続」の項を参照)。シリアルデータをDOUTからシフトア

ウトするためのクロックエッジを変更するコマンドにより、全ての入力レジスタのデータを対応するDACレジスタにロードする動作も実行できます。

### シリアルデータ出力(DOUT)

シリアルデータ出力(DOUT)は、内部シフトレジスタの出力です。MAX5251では、データをDOUTからクロックアウトするタイミングをSCLKの立上リエッジ(モード1)にするか、立下がリエッジ(モード0)にするかを指定できます。モード0におけるDOUTの出力データは、DINの入力データから16.5クロックサイクル遅れるため、Microwire及びSPI/QSPI及びその他のシリアルインタフェースとのコンパチビリティが保持されます。モード1の出力データは、入力データから16クロックサイクル遅れます。パワーアップ時のDOUTは、デフォルトでモード0のタイミングになります。

### ユーザプログラマブルロジック出力(UPO)

ユーザプログラマブルロジック出力(UPO)を使用する と、MAX5251のシリアルインタフェースを通じて外部 デバイスを制御できます(表1)。

図5. シリアルインタフェースタイミング図

図6. シリアルインタフェースタイミング詳細図

### パワーダウンロックアウト(PDL)

パワーダウンロックアウトピンPDLがローの時、ソフトウェアシャットダウンがディセーブルされます。シャットダウン時にPDLがハイからローに遷移すると、ウェイクアップしてシャットダウン前の出力状態になります。PDLは、デバイスを非同期でウェイクアップするために使用することもできます。

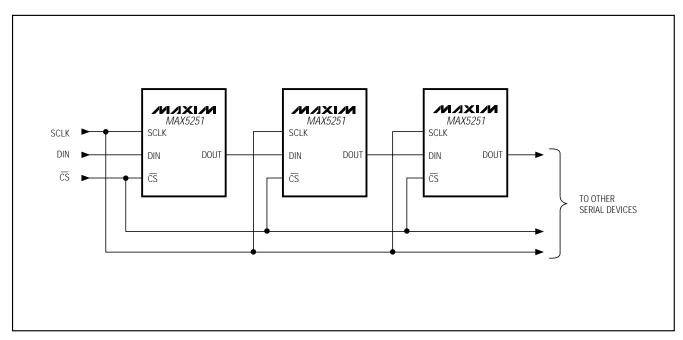

### デイジーチェーン接続

デバイスのDOUTピンを次のデバイスのDINピンに接続していくことにより、任意の数のMAX5251をデイジーチェーン接続できます(図7)。

MAX5251のDOUTピンは内部にアクティブなプルアップを備えているため、DOUTのシンク/ソース能力によって容量性負荷の放電/充電に必要な時間が決定されます。「電気的特性」のシリアルデータ出力VOH及びVOLの仕様を参照してください。

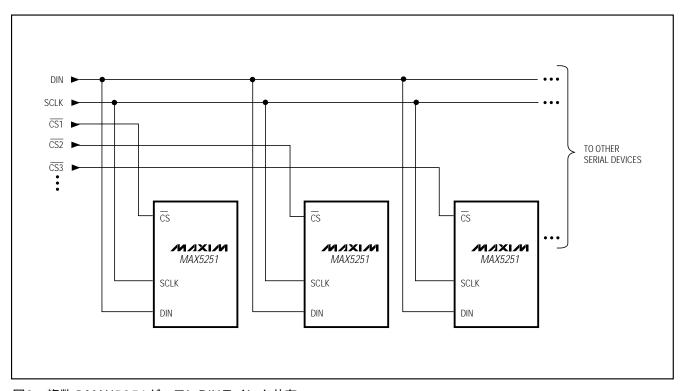

図8に、複数のMAX5251を接続するための別方法を示します。この構成のデータバスは、全てのデバイスに共通になっており、デイジーチェーンを通じてデータをシフトするわけではありません。この構成では、各ICについて専用のチップセレクト入力(CS)が必要であることから必要なI/Oラインの数が増えます。

図7. MAX5251のデイジーチェーン接続

図8. 複数のMAX5251がコモンDINラインを共有

### アプリケーション情報

### ユニポーラ出力

ユニポーラ出力の場合、出力電圧とリファレンス入力 は同じ極性を持っています。図9に、MAX5251のユニ ポーラ出力回路を示します(これが標準動作回路になっ ています)。表2に、ユニポーラ出力コードを示します。 レイルトゥレイルの出力については、図10を参照して ください。この回路はMAX5251の出力アンプが閉 ループ利得+2.6に設定されており、1.25Vのリファ レンスを使用した場合に0V~3.25Vのフルスケール 電圧範囲を提供するようになっています。

### 表2. ユニポーラコード表

| DAC<br>MSB | CONTEN | ITS<br>LSB | ANALOG OUTPUT                                                |

|------------|--------|------------|--------------------------------------------------------------|

| 1111       | 1111   | 11(00)     | +VREF ( 1023 )                                               |

| 1000       | 0000   | 01(00)     | +V <sub>REF</sub> ( 513 )                                    |

| 1000       | 0000   | 00(00)     | $+V_{REF}\left(\frac{512}{1024}\right) = \frac{+V_{REF}}{2}$ |

| 0111       | 1111   | 11(00)     | +V <sub>REF</sub> ( 511 / 1024 )                             |

| 0000       | 0000   | 01(00)     | +V <sub>REF</sub> ( 1/1024 )                                 |

| 0000       | 0000   | 00(00)     | OV                                                           |

### 表3. バイポーラコード表

| DAC<br>MSB | CONTEN | ITS<br>LSB | ANALOG OUTPUT                                     |

|------------|--------|------------|---------------------------------------------------|

| 1111       | 1111   | 11(00)     | +V <sub>REF</sub> ( <u>511</u> )                  |

| 1000       | 0000   | 01(00)     | +V <sub>REF</sub> ( 1/512 )                       |

| 1000       | 0000   | 00(00)     | OV                                                |

| 0111       | 1111   | 11(00)     | -V <sub>REF</sub> ( 1/512)                        |

| 0000       | 0000   | 01(00)     | -V <sub>REF</sub> ( <u>511</u> )                  |

| 0000       | 0000   | 00(00)     | $-V_{REF}\left(\frac{512}{512}\right) = -V_{REF}$ |

### () Sub-bits

レイルトゥレイルは日本モトローラの登録商標です。

### バイポーラ出力

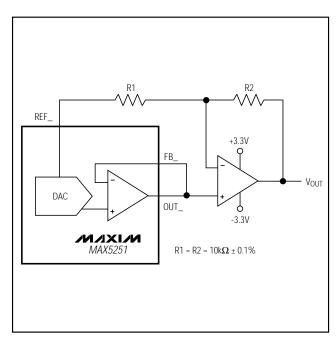

MAX5251の出力は、図11の回路を使用してバイポーラ 動作用に構成できます。

$$V_{OUT} = V_{REF}[(2NB/1024) - 1]$$

ここで、NBはDACのバイナリ入力コードの数値です。 表3に、図11の回路のディジタルコード(オフセット バイナリ)及び対応する出力電圧を示します。

図10. ユニポーラのレイルトゥレイル出力の回路

図11. バイポーラ出力回路

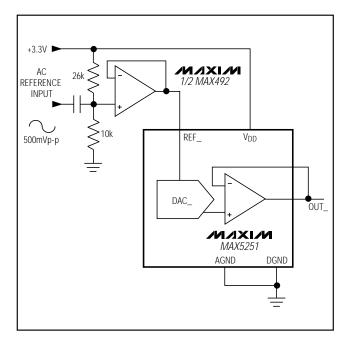

### ACリファレンスの使用

MAX5251は、リファレンスにAC信号要素が含まれるアプリケーションでは、リファレンス入力範囲仕様内で乗算能力を備えています。図12に、リファレンス入力にサイン波信号を印加する技法を示します(AC信号はREFAB/REFCDに印加される前にオフセットされます)。リファレンス電圧がDGNDよりもマイナスにならないようにしてください。

MAX5251の全高調波歪み及びノイズ(THD + N)は、信号スイングが1Vp-pで入力周波数が最大25kHzの時に(フルスケールコードで)-72dB以下(typ)です。「標準動作特性」のグラフに示すように、標準的な-3dB周波数は650kHzとなっています。

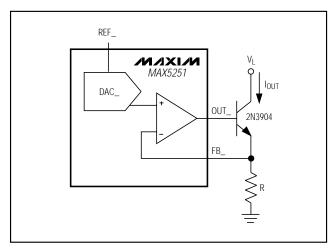

### ディジタルプログラマブル電流ソース

図13の回路を使用すると、オペアンプのフィードバックループ内のNPNトランジスタ(2N3904等)がディジタルでプログラムできる一方向性電流ソースになります。この回路は、工業用制御アプリケーションでよく使われる4mA~20mAの電流ループの駆動に使用できます。出力電流は、次式で計算されます。

$$I_{OUT} = (V_{REF}/R) \times (NB/1024)$$

ここで、NBはDACのバイナリ入力コードの数値、Rは図13に示されている検出抵抗です。

図12. ACリファレンス入力回路

図13. ディジタルプログラマブル電流ソース

### 電源に関する考慮

パワーアップ時に、全ての入力及びDACレジスタは クリア(ゼロコードに設定)され、DOUTはモード0にな ります(シリアルデータはクロックの立下がりエッジで DOUTからシフトアウト)。

MAX5251に定格通りの性能を発揮させるために、REFAB/REFCDを( $V_{DD}$ -1.4V)よりも低くしてください。 $V_{DD}$ は、 $4.7\mu$ Fコンデンサと $0.1\mu$ Fコンデンサを並列に使用してAGNDにバイパスしてください。リード線は短くし、バイパスコンデンサは電源ピンのできるだけ近くに取り付けてください。

### 接地及びレイアウト

AGNDとDGNDの間のディジタル又はACトランジェント 信号のためにアナログ出力にノイズが発生することがあります。AGNDとDGNDをDACでまとめて接続し、それをさらにできるだけ良質のグランドに接続してください。

プリント基板のグランドレイアウトを良くすることによって、DAC出力、リファレンス入力及びディジタル入力の間のクロストークを最小限に抑えることができます。アナログラインをディジタルラインから遠ざけてクロストークを低減してください。ワイヤラッピングボードは、お勧めできません。

### ピン配置 \_\_\_\_\_\_

型番(続き) \_\_\_\_\_

| PART        | TEMP. RANGE     | PIN-PACKAGE    | INL<br>(LSB) |

|-------------|-----------------|----------------|--------------|

| MAX5251AEPP | -40°C to +85°C  | 20 Plastic DIP | ±1/2         |

| MAX5251BEPP | -40°C to +85°C  | 20 Plastic DIP | ±1           |

| MAX5251AEAP | -40°C to +85°C  | 20 SSOP        | ±1/2         |

| MAX5251BEAP | -40°C to +85°C  | 20 SSOP        | ±1           |

| MAX5251BMJP | -55°C to +125°C | 20 CERDIP*     | ±2           |

<sup>\*</sup>Contact factory for availability and processing to MIL-STD-883.

### チップ情報

TRANSISTOR COUNT: 4337

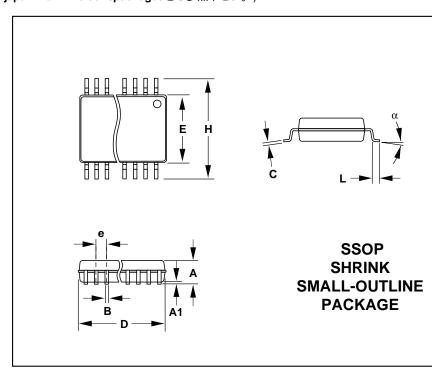

### パッケージ

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、japan.maxim-ic.com/packagesをご参照下さい。)

| ым    | INC   | HES     | MILLIMETERS |      |  |

|-------|-------|---------|-------------|------|--|

| DIIVI | MIN   | MAX     | MIN         | MAX  |  |

| Α     | 0.068 | 0.078   | 1.73        | 1.99 |  |

| A1    | 0.002 | 0.008   | 0.05        | 0.21 |  |

| В     | 0.010 | 0.015   | 0.25        | 0.38 |  |

| С     | 0.004 | 0.008   | 0.09        | 0.20 |  |

| D     | ;     | SEE VAR | IATIONS     |      |  |

| Е     | 0.205 | 0.209   | 5.20        | 5.38 |  |

| е     | 0.025 | 6 BSC   | 0.65        | BSC  |  |

| Н     | 0.301 | 0.311   | 7.65        | 7.90 |  |

| L     | 0.025 | 0.037   | 0.63        | 0.95 |  |

| α     | 0°    | 8°      | 0°          | 8°   |  |

| DIM | PINS | INCHES |       | MILLIMETERS |       |

|-----|------|--------|-------|-------------|-------|

|     |      | MIN    | MAX   | MIN         | MAX   |

| D   | 14   | 0.239  | 0.249 | 6.07        | 6.33  |

| D   | 16   | 0.239  | 0.249 | 6.07        | 6.33  |

| D   | 20   | 0.278  | 0.289 | 7.07        | 7.33  |

| D   | 24   | 0.317  | 0.328 | 8.07        | 8.33  |

| D   | 28   | 0.397  | 0.407 | 10.07       | 10.33 |

21-0056A

## マキシム・ジャパン株式会社

〒169-0051東京都新宿区西早稲田3-30-16(ホリゾン1ビル) TEL. (03)3232-6141 FAX. (03)3232-6149

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。マキシムは随時予告なく回路及び仕様を変更する権利を留保します。

16 \_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 (408) 737-7600