**MAXIM**

# +2.7V ~ +5.5V、 8ビットDAC、

## 概要

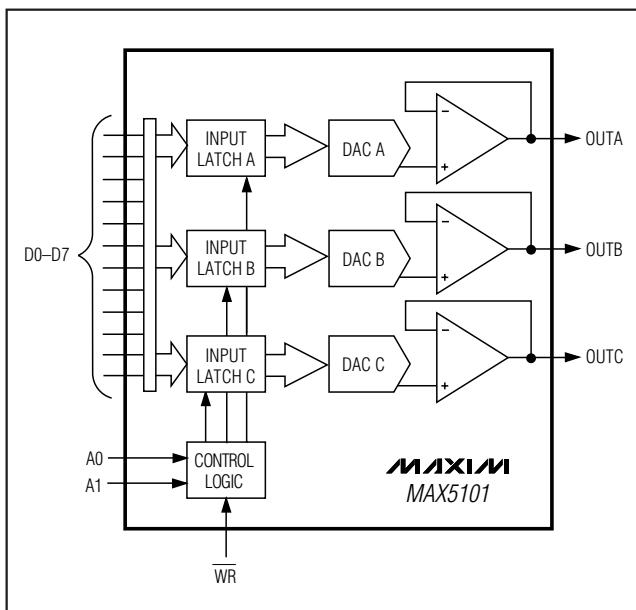

MAX5101は、+2.7V ~ +5.5V単一電源で動作するパラレル入力、電圧出力トリプル8ビットD/Aコンバータ(DAC)です。省スペースの16ピンTSSOPパッケージで提供されています。内部高精度バッファはレイルトゥレイル®スイングが可能です。3つのDAC全ての内部リファレンス電圧は、V<sub>DD</sub>に接続されています。

MAX5101は、3つの各DACに独立の入力ラッチが備えられています。データは、共通の8ビット入力ポートからこれらの入力ラッチに転送されます。各々のDACはアドレス入力A0及びA1で選択され、WRをローにする事によって更新されます。

MAX5101は、電流を1μAに低減するソフトウェアシャットダウンモード及びパワーアップ時に全てのレジスタをコード00 hexにリセットするパワーオンリセットモードを備えています。

## アプリケーション

デジタル利得及びオフセット調整

設定可能なアッテネータ

ポータブル機器

パワーアンプバイアス制御

## ファンクションダイアグラム

# 低電力、トリプル、パラレル レイルトゥレイル電圧出力付

**MAX5101**

## 特長

- ◆ 電源 : +2.7V ~ +5.5V単一

- ◆ 超低消費電流:

動作中0.3mA

ソフトウェアシャットダウンモードにおいて1μA

- ◆ パッケージ : 超小型16ピンTSSOP

- ◆ 出力バッファアンプはレイルトゥレイルで

スイング可能

- ◆ パワークリセッタは全てのレジスタをゼロに設定

## 型番

| PART        | TEMP. RANGE    | PIN-PACKAGE | INL (LSB) |

|-------------|----------------|-------------|-----------|

| MAX5101AEUE | -40°C to +85°C | 16 TSSOP    | ±1        |

| MAX5101BEUE | -40°C to +85°C | 16 TSSOP    | ±2        |

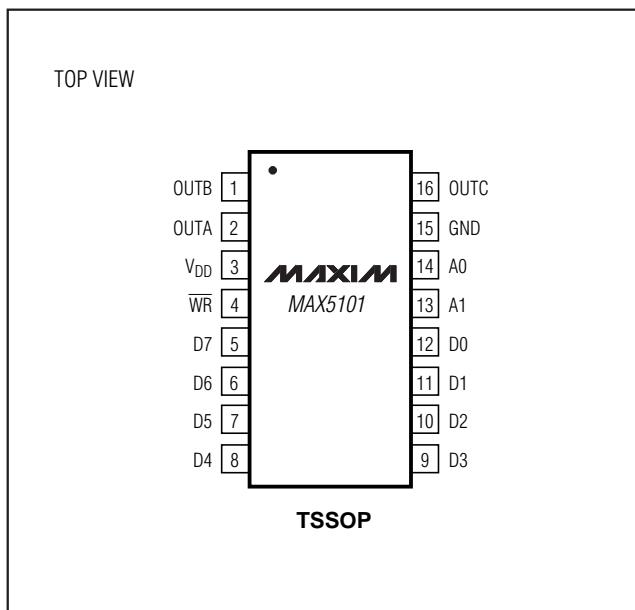

## ピン配置

レイルトゥレイルは日本モトローラの登録商標です。

**MAXIM**

Maxim Integrated Products 1

無料サンプル及び最新版データシートの入手にはマキシム社のホームページをご利用下さい。[www.maxim-ic.com](http://www.maxim-ic.com)

# +2.7V ~ +5.5V、低電力、トリプル、パラレル 8ビットDAC、レイルトゥレイル電圧出力付

## ABSOLUTE MAXIMUM RATINGS

|                                                             |                          |

|-------------------------------------------------------------|--------------------------|

| V <sub>DD</sub> to GND .....                                | -0.3V to +6V             |

| D <sub>−</sub> , A <sub>−</sub> , WR to GND .....           | -0.3V to +6V             |

| OUT <sub>−</sub> to GND .....                               | -0.3V to V <sub>DD</sub> |

| Maximum Current into Any Pin .....                          | ±50mA                    |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) ..... | 457mW                    |

| 16-Pin TSSOP (derate 5.7mW/°C above +70°C) .....            | 457mW                    |

|                                           |                 |

|-------------------------------------------|-----------------|

| Operating Temperature Range               |                 |

| MAX5101_EUE .....                         | -40°C to +85°C  |

| Maximum Junction Temperature .....        | +150°C          |

| Storage Temperature Range .....           | -65°C to +150°C |

| Lead Temperature (soldering, 10sec) ..... | +300°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

(V<sub>DD</sub> = +2.7V to +5.5V, R<sub>L</sub> = 10kΩ, C<sub>L</sub> = 100pF, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at V<sub>DD</sub> = +3V and T<sub>A</sub> = +25°C.)

| PARAMETER                             | SYMBOL          | CONDITIONS                                    | MIN | TYP             | MAX | UNITS  |

|---------------------------------------|-----------------|-----------------------------------------------|-----|-----------------|-----|--------|

| <b>STATIC ACCURACY</b>                |                 |                                               |     |                 |     |        |

| Resolution                            |                 |                                               |     | 8               |     | Bits   |

| Integral Nonlinearity (Note 1)        | INL             | MAX5101A                                      |     | ±1              |     | LSB    |

|                                       |                 | MAX5101B                                      |     | ±2              |     |        |

| Differential Nonlinearity (Note 1)    | DNL             | Guaranteed monotonic                          |     | ±1              |     | LSB    |

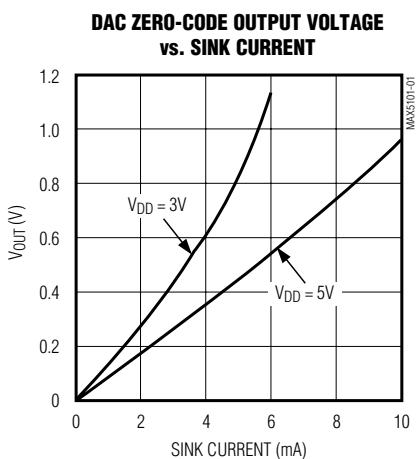

| Zero-Code Error                       | ZCE             | Code = 00 hex                                 |     | ±20             |     | mV     |

| Zero-Code-Error Supply Rejection      |                 | Code = 00 hex, V <sub>DD</sub> = 2.7V to 5.5V |     | 10              |     | mV     |

| Zero-Code Temperature Coefficient     |                 | Code = 00 hex                                 |     | ±10             |     | µV/°C  |

| Gain Error (Note 2)                   |                 | Code = F0 hex                                 |     | ±1              |     | %      |

| Gain-Error Temperature Coefficient    |                 | Code = F0 hex                                 |     | ±0.001          |     | LSB/°C |

| <b>DAC OUTPUTS</b>                    |                 |                                               |     |                 |     |        |

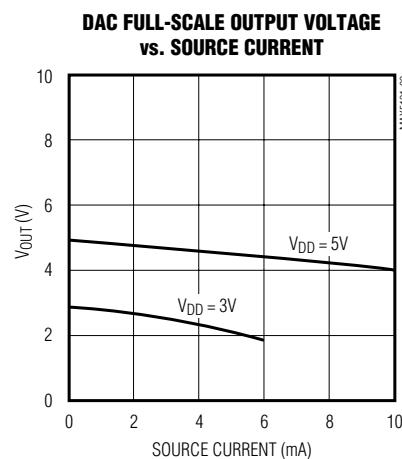

| Output Voltage Range                  |                 | R <sub>L</sub> = ∞                            | 0   | V <sub>DD</sub> |     | V      |

| <b>DIGITAL INPUTS</b>                 |                 |                                               |     |                 |     |        |

| Input High Voltage                    | V <sub>IH</sub> | V <sub>DD</sub> = 2.7V to 3.6V                | 2   |                 |     | V      |

|                                       |                 | V <sub>DD</sub> = 3.6V to 5.5V                | 3   |                 |     |        |

| Input Low Voltage                     | V <sub>IL</sub> |                                               |     | 0.8             |     | V      |

| Input Current                         | I <sub>IN</sub> | V <sub>IN</sub> = V <sub>DD</sub> or GND      |     | ±1.0            |     | µA     |

| Input Capacitance                     | C <sub>IN</sub> |                                               |     | 10              |     | pF     |

| <b>DYNAMIC PERFORMANCE</b>            |                 |                                               |     |                 |     |        |

| Output Voltage Slew Rate              |                 | From code 00 to code F0 hex                   | 0.6 |                 |     | V/µs   |

| Output Settling Time (Note 3)         |                 | To 1/2LSB, from code 10 to code F0 hex        | 6   |                 |     | µs     |

| Channel-to-Channel Isolation (Note 4) |                 | Code 00 to code FF hex                        | 500 |                 |     | nVs    |

| Digital Feedthrough (Note 5)          |                 | Code 00 to code FF hex                        | 0.5 |                 |     | nVs    |

**+2.7V~+5.5V、低電力、トリプル、パラレル

8ビットDAC、レイルトゥレイル電圧出力付**

**MAX5101**

**ELECTRICAL CHARACTERISTICS (continued)**

( $V_{DD} = +2.7V$  to  $+5.5V$ ,  $R_L = 10k\Omega$ ,  $C_L = 100pF$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $V_{DD} = +3V$  and  $T_A = +25^\circ C$ .)

| PARAMETER                                 | SYMBOL           | CONDITIONS                                          | MIN | TYP | MAX           | UNITS   |

|-------------------------------------------|------------------|-----------------------------------------------------|-----|-----|---------------|---------|

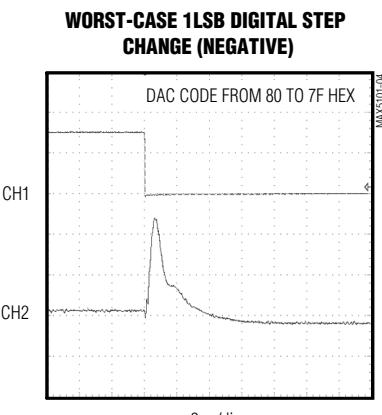

| Digital-to-Analog Glitch Impulse          |                  | Code 80 hex to code 7F hex                          | 90  |     | nVs           |         |

| Wideband Amplifier Noise                  |                  |                                                     | 60  |     | $\mu V_{RMS}$ |         |

| Shutdown Recovery Time                    | t <sub>SDR</sub> | To $\pm 1/2$ LSB of final value of V <sub>OUT</sub> | 13  |     | $\mu s$       |         |

| Time to Shutdown                          | t <sub>SDN</sub> | I <sub>DD</sub> < 5 $\mu A$                         | 20  |     | $\mu s$       |         |

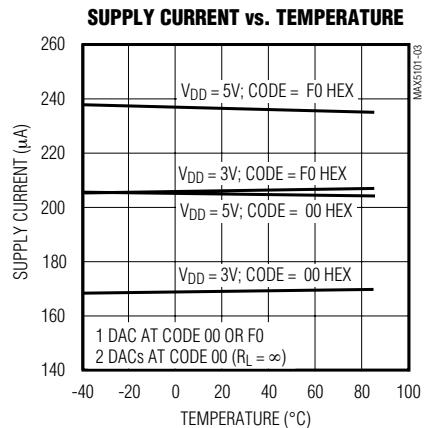

| <b>POWER SUPPLIES</b>                     |                  |                                                     |     |     |               |         |

| Power-Supply Voltage                      | V <sub>DD</sub>  |                                                     | 2.7 | 5.5 |               | V       |

| Supply Current (Note 6)                   | I <sub>DD</sub>  |                                                     | 280 | 520 |               | $\mu A$ |

| Shutdown Current                          |                  |                                                     | 1   | 3   |               | $\mu A$ |

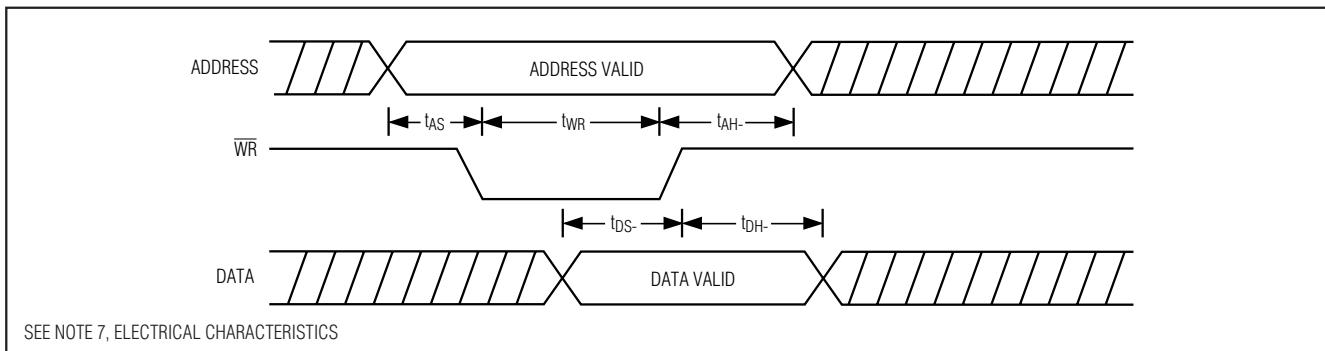

| <b>DIGITAL TIMING</b> (Figure 1) (Note 7) |                  |                                                     |     |     |               |         |

| Address to WR Setup                       | t <sub>AS</sub>  |                                                     | 5   |     |               | ns      |

| Address to WR Hold                        | t <sub>AH</sub>  |                                                     | 0   |     |               | ns      |

| Data to WR Setup                          | t <sub>DS</sub>  |                                                     | 25  |     |               | ns      |

| Data to WR Hold                           | t <sub>DH</sub>  |                                                     | 0   |     |               | ns      |

| WR Pulse Width                            | t <sub>WR</sub>  |                                                     | 20  |     |               | ns      |

**Note 1:** Reduced digital code range (code 00 hex to code F0 hex) due to swing limitations when the output amplifier is loaded.

**Note 2:** Gain error is:  $[100 (V_{F0,meas} - ZCE - V_{F0,ideal}) / V_{DD}]$ . Where  $V_{F0,meas}$  is the DAC output voltage with input code F0 hex, and  $V_{F0,ideal}$  is the ideal DAC output voltage with input code F0 hex (i.e.,  $V_{DD} \cdot 240 / 256$ ).

**Note 3:** Output settling time is measured from the 50% point of the falling edge of WR to  $\pm 1/2$ LSB of V<sub>OUT</sub>'s final value.

**Note 4:** Channel-to-Channel Isolation is defined as the glitch energy at a DAC output in response to a full-scale step change on any other DAC output. The measured channel has a fixed code of 80 hex.

**Note 5:** Digital Feedthrough is defined as the glitch energy at any DAC output in response to a full-scale step change on all eight data inputs with WR at V<sub>DD</sub>.

**Note 6:**  $R_L = \infty$ , digital inputs at GND or V<sub>DD</sub>.

**Note 7:** Timing measurement reference level is  $(V_{IH} + V_{IL}) / 2$ .

**+2.7V ~ +5.5V、低電力、トリプル、パラレル

8ビットDAC、レイルトゥレイル電圧出力付**

図1. タイミング図

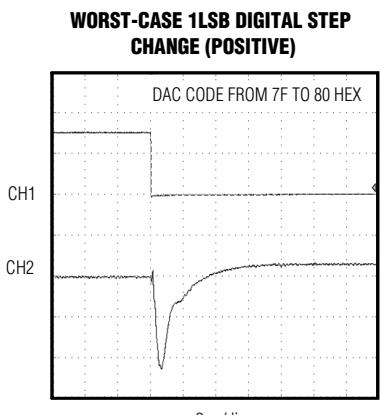

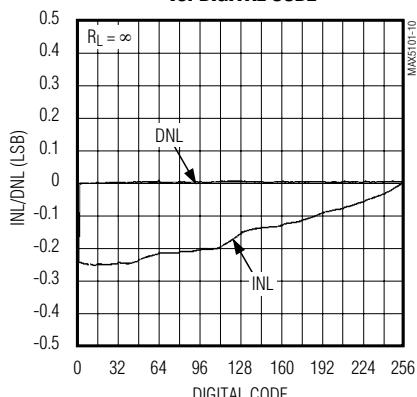

**標準動作特性**

( $V_{DD} = +3V$ ,  $R_L = 10k\Omega$ ,  $C_L = 100pF$ , code = FF hex,  $T_A = +25^\circ C$ , unless otherwise noted.)

**+2.7V~+5.5V、低電力、トリプル、パラレル

8ビットDAC、レイルトゥレイル電圧出力付**

**MAX5101**

**標準動作特性(続き)**

( $V_{DD} = +3V$ ,  $R_L = 10k\Omega$ ,  $C_L = 100pF$ , code = FF hex,  $T_A = +25^\circ C$ , unless otherwise noted.)

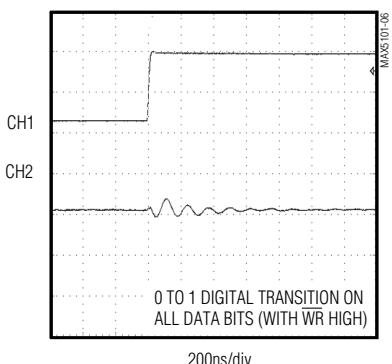

**DIGITAL FEEDTHROUGH GLITCH IMPULSE

(0 TO 1 DIGITAL TRANSMISSION)**

0 TO 1 DIGITAL TRANSITION ON ALL DATA BITS (WITH WR HIGH)

CH1 = D7, 2V/div

CH2 =  $V_{OUTA}$ , 1mV/div, AC-COUPLED

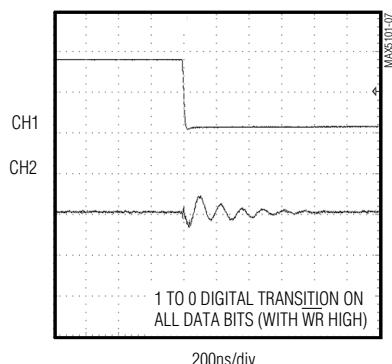

**DIGITAL FEEDTHROUGH GLITCH IMPULSE

(1 TO 0 DIGITAL TRANSMISSION)**

1 TO 0 DIGITAL TRANSITION ON ALL DATA BITS (WITH WR HIGH)

CH1 = D7, 2V/div

CH2 =  $V_{OUTB}$ , 1mV/div, AC-COUPLED

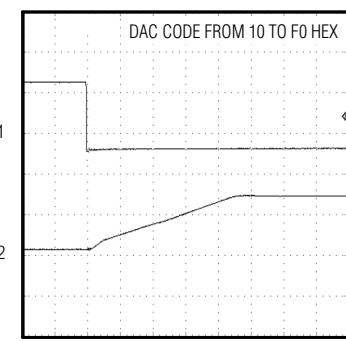

**POSITIVE SETTLING TIME**

1μs/div

CH1 =  $\overline{WR}$ , 2V/div

CH2 =  $V_{OUTA}$ , 2V/div

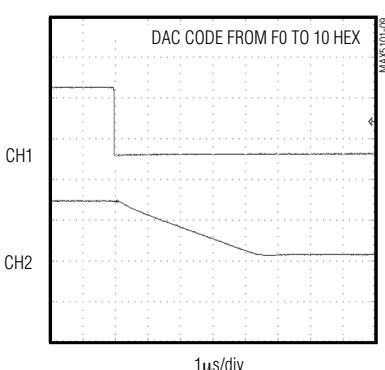

**NEGATIVE SETTLING TIME**

1μs/div

CH1 =  $\overline{WR}$ , 2V/div

CH2 =  $V_{OUTA}$ , 2V/div

**INTEGRAL AND DIFFERENTIAL NONLINEARITY

vs. DIGITAL CODE**

# +2.7V ~ +5.5V、低電力、トリプル、パラレル 8ビットDAC、レイルトゥレイル電圧出力付

## 端子説明

| 端子   | 名称              | 機能                                                         |

|------|-----------------|------------------------------------------------------------|

| 1    | OUTB            | DAC B電圧出力                                                  |

| 2    | OUTA            | DAC A電圧出力                                                  |

| 3    | V <sub>DD</sub> | 正電源電圧。0.1μFコンデンサを使用してV <sub>DD</sub> をGNDにバイパスして下さい。       |

| 4    | WR              | 書き込み入力(アクティブロー)。A0とA1で選択されたDAC入力ラッチにデータをロードするのにWRを使用して下さい。 |

| 5-12 | D7-D0           | データ入力7 ~ 0。                                                |

| 13   | A1              | DACアドレス選択ビット(MSB)                                          |

| 14   | A0              | DACアドレス選択ビット LSB)                                          |

| 15   | GND             | グランド                                                       |

| 16   | OUTC            | DAC C電圧出力                                                  |

## 詳細

### デジタルアナログ部

MAX5101は、DACにマトリックスディコーディング構造を採用しています。内部リファレンス電圧はV<sub>DD</sub>に接続され、マトリックス状に配置された抵抗ストリングによって分割されます。行及び列ディコーダが抵抗ストリングから適切なタップを選択して、必要なアナログ電圧を提供します。抵抗ネットワークが8ビットデジタル入力を相当するアナログ出力電圧(電源電圧V<sub>DD</sub>に比例)に変換します。抵抗ストリングは、電源に対してコード依存性のない入力インピーダンスを示し、単調な出力を保証します。

電圧はフォロワ構成で接続されたレイルトゥレイルオペアンプでバッファされて、電源電圧範囲の出力を提供します(ファンクションダイアグラムを参照)。

### 出力バッファアンプ

DAC出力は、内部で標準スルーレート0.6V/μsの高精度アンプによってバッファされています。10k<sub>Ω</sub>と100pFの並列負荷の時、出力の±1/2LSBへのセトリング時間は6μsです。

### DACリファレンス電圧

MAX5101のリファレンスは、内部でV<sub>DD</sub>に接続されています。DACの出力電圧(V<sub>OUT</sub>)は、次式のデジタルプログラマブル電圧ソースとして表すことができます。

$$V_{OUT} = (N_B \cdot V_{DD}) / 256$$

ここで、N<sub>B</sub>はDACのバイナリ入力コードの数値表現です。

### デジタル入力及びインターフェースロジック

MAX5101においては、アドレスラインA0及びA1がD0 ~ D7からデータを受け取るDACを選択します(表1参照)。WRがローの時、アドレス指定されたDACの入力ラッチはトランスペアレントです。WRがハイの場合にデータはラッチされます。DAC出力(OUTA、OUTB)は、3つの8ビット入力ラッチに保持されているデータを表します。WRがローになる前にデータが有効になるようにして、MAX5101の出力グリッチを避けて下さい。

### 低電力シャットダウンモード

MAX5101は、ソフトウェアシャットダウンモードを備えています。アドレスA1 = H、A0 = Hへの書き込みがデバイスをシャットダウンします。その後でその他3つのアドレスのどれかに書き込みがあるとシャットダウンがディセーブルされ、アナログ回路がオンになります。MAX5101がシャットダウン状態から抜け出る時、全てのレジスタはシャットダウン以前のデジタル値を保持しています。但し、素子がパワーアップする時(即ちV<sub>DD</sub>が上昇する時)、全てのラッチは内部でコード00 = hexにプリセットされます。シャットダウンモードにおいては、出力アンプがハイインピーダンス状態になります。シャットダウンを解除する時は、出力の安定化時間として13μs待って下さい。

### 電源バイパス及びグランド管理

GND上のデジタル又はACトランジエント信号は、アナログ出力のノイズの原因となります。GNDはできるだけ良質のグランドに戻して下さい。V<sub>DD</sub>はV<sub>DD</sub>とGNDにできるだけ近く配置された0.1μFコンデンサでバイパスして下さい。

プリント基板のグランドレイアウトを注意深く行うことにより、DAC出力とデジタル入力の間のクロストークを最小限に抑えることができます。

**+2.7V~+5.5V、低電力、トリプル、パラレル

8ビットDAC、レイルトゥレイル電圧出力付**

**MAX5101**

表1. MAX5101のアドレス表(部分)

| <b>WR</b> | <b>A1</b> | <b>A0</b> | <b>OPERATION</b>              |

|-----------|-----------|-----------|-------------------------------|

| H         | X         | X         | Input data latched            |

| L         | L         | L         | DAC A input latch transparent |

| L         | L         | H         | DAC A input latch transparent |

| L         | H         | L         | DAC A input latch transparent |

| L         | H         | H         | Enter shutdown mode           |

H = ハイ、L = ロー、X = 任意

チップ情報

TRANSISTOR COUNT: 6848

**+2.7V ~ +5.5V、低電力、トリプル、パラレル

8ビットD/A、レイルトゥレイル電圧出力付**

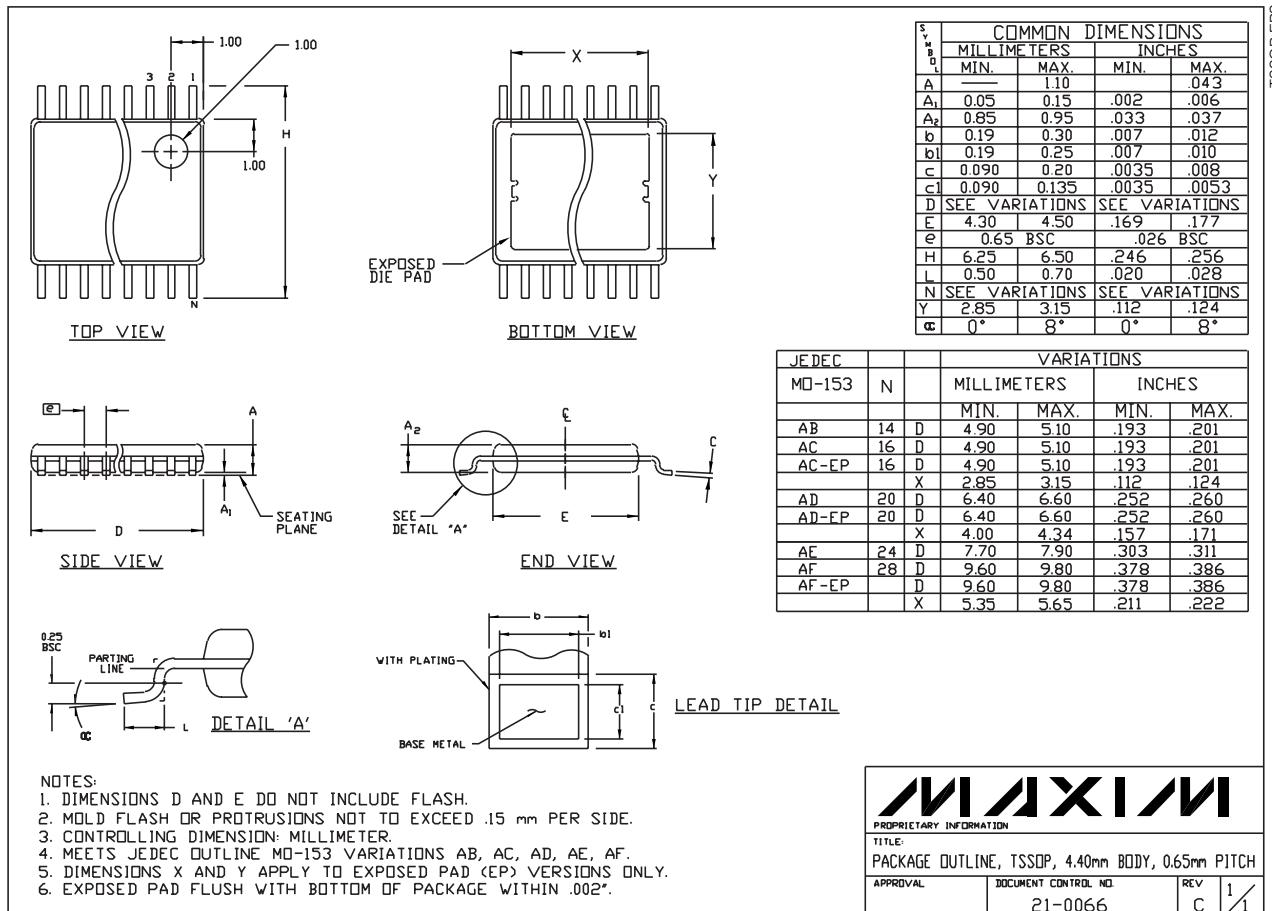

パッケージ

販売代理店

マキシム・ジャパン株式会社

〒169-0051 東京都新宿区西早稲田3-30-16(ホリゾン1ビル)

TEL. (03)3232-6141 FAX. (03)3232-6149

マキシム社では全体がマキシム社製品で実現されている回路以外の回路の使用については責任を持ちません。回路特許ライセンスは明言されていません。

マキシム社は随时予告なしに回路及び仕様を変更する権利を保留します。

8 Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 1999 Maxim Integrated Products

MAXIM is a registered trademark of Maxim Integrated Products.