#

### クワッド/トリプル、SPDT、RGBスイッチ 250MHzビデオバッファアンプ付

概要

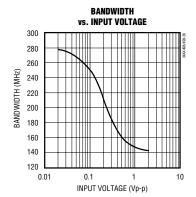

MAX498/MAX499は、閉ループバッファアンプ付の 高速クワッド/トリプル単極/双投ビデオスイッチです。 バッファアンプは、利得+6dB(A<sub>VCI</sub> = 2V/V)、-3dB 帯域幅250MHz、0.1dB利得平坦性70MHz及びスルー レート1250V/usの性能を備えています。これらのデバ イスは、高速スイッチング(3ns)及び高速セトリング (4Vステップで12ns)であるため、広範囲のビデオアプ リケーションに最適です。低微分利得/位相エラー (0.03%/0.06°)及び広帯域幅特性であるため、コンポ ジットビデオ及びRGBアプリケーションの両方に適し ています。アンプは逆終端の50 又は75 ケーブル を±2.5Vまで駆動することができ、75 負荷を±2V まで駆動できるため、単一の出力で複数のケーブルを 駆動することができます。

大きなスイッチアレイを構成できるように、低電力 ディセーブルモードによりアンプ出力をハイインピー ダンス状態にできます。チャネル選択及び出力イネー ブル/ディセーブルは、4つのTTL/CMOSコンパチブル ロジック入力により制御されています。各ビデオ入力 はACグランドピンで隔離されているため、チャネル間 の容量が最小限に抑えられ、クロストークが90dB (10MHz)まで低減されています。

4チャネルのMAX498は、全ての出力バッファがイネー ブルされた状態で±5V DC電源動作の場合に390mW(typ) を消費します。全てのバッファをディセーブルすると電 力消費が130mWまで減少します。3チャネルの MAX499では、電力消費はイネーブル状態で300mW、 ディセーブル状態で100mWです。

#### アプリケーション

ビデオスイッチング及び分配

放送用品質のコンポジットビデオ多重化

ワークステーション

ビデオ編集機

放送用及び高品位TV機器

マルチメディア製品

医療用画像処理機

#### 特長

◆ 高速性:

小信号-3dB帯域幅: 250MHz フルパワー-3dB帯域幅:135MHz

◆ 0.1dB帯域幅: 70MHz ◆ スルーレート: 1250V/µs

◆ 0.1%までのセトリング時間: 12ns

◆ 微分利得/位相エラー: 0.03%/0.06°

◆ 入力容量: 2pF

◆ チャネルスイッチング時間:3ns

◆ チャネルスイッチングトランジェント:120mVp-p

◆ スリーステート出力により大型スイッチアレイが可能

◆ 50 又は75 逆終端ケーブルを直接駆動

#### 型番

| PART      | TEMP. RANGE  | PIN-PACKAGE |

|-----------|--------------|-------------|

| MAX498CWI | 0°C to +70°C | 28 SO       |

| MAX499CWG | 0°C to +70°C | 24 SO       |

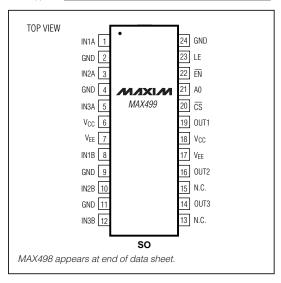

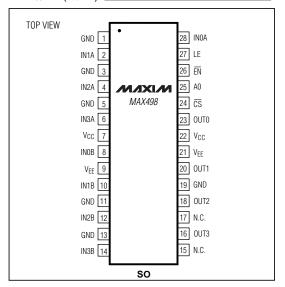

#### ピン配置

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage (V <sub>CC</sub> to V <sub>EE</sub> )+12V | Continuous Power Dissipation (T <sub>A</sub> = +70°C) |

|----------------------------------------------------------|-------------------------------------------------------|

| Voltage on IN to GND(VEE - 0.3V) to (VCC + 0.3V)         | 24-Pin SO (derate 11.76mW/°C above +70°C)941mW        |

| Voltage on Digital Inputs                                | 28-Pin SO (derate 12.5mW/°C above +70°C)1W            |

| (LE, EN, A0, CS)0.3V to (V <sub>CC</sub> + 0.3V)         | Operating Temperature Range0°C to +70°                |

| Voltage on OUT_ (disabled)±4V                            | Storage Temperature Range65°C to +150°C               |

| Output Short-Circuit Duration                            | Lead Temperature (soldering, 10sec)+300°C             |

| to -4V < OLIT < +4V Continuous                           |                                                       |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +5V, V_{EE} = -5V, V_{IN} = 0V, R_L = 150\Omega, LE = \overline{EN} = \overline{CS} = 0V, T_A = 0^{\circ}C$  to  $+70^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                          | SYMBOL               | YMBOL CONDITIONS                                                                                      |        | MIN   | TYP   | MAX   | UNITS |

|------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------|--------|-------|-------|-------|-------|

| Input Voltage Range                | V <sub>IN</sub>      |                                                                                                       |        | ±1.25 | ±1.70 |       | V     |

| Voltage Cain                       | ۸                    | $R_L = 150\Omega$ , $-1.25V \le V_{IN} \le +1.25V$<br>$R_L = 75\Omega$ , $-1.0V \le V_{IN} \le +1.0V$ |        | 1.985 |       | 2.030 | - V/V |

| Voltage Gain                       | Av                   |                                                                                                       |        | 1.965 |       | 2.030 |       |

| Input Offset Voltage               | Vos                  |                                                                                                       |        |       | ±2    | ±9    | mV    |

| Input Offset Voltage Drift         | TCV <sub>OS</sub>    |                                                                                                       |        |       | ±50   |       | μV/°C |

| Input Bias Current                 | lΒ                   |                                                                                                       |        |       | ±1    | ±7    | μΑ    |

| Input Resistance                   | RIN                  | -1.25V ≤ V <sub>IN</sub> ≤ +1.25V                                                                     |        | 200   | 700   |       | kΩ    |

| Input Capacitance                  | CIN                  | Channel on or off                                                                                     |        |       | 2     |       | рF    |

| Output Short-Circuit Current       | I <sub>OUT(SC)</sub> | -3.5V ≤ OUT_ ≤ +3.5V (Note 1)                                                                         |        |       | 120   |       | mA    |

| Output Current                     | lout_                | $-2.0V \le V_{OUT} \le +2.0V, R_{L} = 75\Omega$                                                       | 2      | ±27   | ±40   |       | mA    |

| On Output Resistance               | Rout                 |                                                                                                       |        |       | 0.15  |       | Ω     |

| On Output Impedance                |                      | f = 10MHz                                                                                             |        |       | 3.0   |       | Ω     |

| Off Output Resistance              |                      | -2.50V ≤ V <sub>OUT</sub> ≤ +2.50V                                                                    |        | 1.0   | 1.2   |       | kΩ    |

| Operating Supply-Voltage Range     |                      |                                                                                                       |        | ±4.50 |       | ±5.50 | V     |

| Positive Power-Supply Rejection    | PSR+                 | $4.50V \le V_{CC} \le 5.50V$ , $V_{EE} = -5.0V$                                                       |        | 55    | 72    |       | dB    |

| Negative Power-Supply<br>Rejection | PSR-                 | -5.50V ≤ V <sub>EE</sub> ≤ -4.5V, V <sub>CC</sub> = +5.0V                                             |        | 55    | 72    |       | dB    |

| Logic Low Voltage                  | V <sub>INLL</sub>    |                                                                                                       |        | 0.8   |       |       | V     |

| Logic High Voltage                 | V <sub>INLH</sub>    |                                                                                                       |        |       |       | 2     | V     |

| Logic Input Current                | linl                 | 0V ≤ V <sub>INL</sub> ≤ V <sub>CC</sub>                                                               |        | -10   |       | 130   | μΑ    |

|                                    |                      | <del>EN</del> = 0                                                                                     | MAX498 |       | 40    | 52    |       |

| Positive Supply Current            | laa                  | EIN = U                                                                                               | MAX499 |       | 31    | 41    | - mA  |

| Fositive Supply Current            | Icc                  | <del>FN</del> = 1                                                                                     | MAX498 |       | 14    | 17    |       |

|                                    |                      | EIN = I                                                                                               | MAX499 |       | 11    | 14    |       |

|                                    |                      | <del>FN</del> = 0                                                                                     | MAX498 |       | 38    | 50    |       |

| Negative Supply Current            | IFF                  | EIN = U                                                                                               | MAX499 |       | 29    | 39    | mA    |

| riegative Supply Culterit          | i iEE                | <del>EN</del> = 1                                                                                     | MAX498 |       | 12    | 15    | IIIA  |

|                                    |                      | EIN = 1                                                                                               | MAX499 |       | 9     | 12    |       |

Note 1: Limited by package power dissipation.

#### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +5V, V_{EE} = -5V, V_{IN} = 0V, R_L = 100\Omega, LE = \overline{EN} = \overline{CS} = 0V, T_A = +25^{\circ}C, unless otherwise noted.)$

| PARAMETER                    | SYMBOL     | CONDITIONS                                | MIN | TYP  | MAX | UNITS   |

|------------------------------|------------|-------------------------------------------|-----|------|-----|---------|

| Small-Signal, -3dB Bandwidth | BW-3dB     | V <sub>IN</sub> ≤ 100mVp-p                |     | 250  |     | MHz     |

| ±0.1dB Gain Flatness         |            | V <sub>IN</sub> ≤ 100mVp-p                |     | 70   |     | MHz     |

| Full-Power, -3dB Bandwidth   | FPBW       | V <sub>OUT</sub> = ±2V                    |     | 135  |     | MHz     |

| Slew Rate                    | SR         | Vout = 4V step                            |     | 1250 |     | V/µs    |

| Settling Time                | ts         | 0.1%, V <sub>OUT</sub> = 4V step          |     | 12   |     | ns      |

| Input Voltage Noise Density  |            | f = 100kHz                                |     | 7.8  |     | nV/√Hz  |

| Input Current Noise Density  |            | f = 100kHz                                |     | 2.6  |     | pA/√Hz  |

| Total Harmonic Distortion    | THD        | f = 10MHz                                 |     | -50  |     | dB      |

| Spurious-Free Dynamic Range  | SFDR       | fc = 3MHz                                 |     | -66  |     | dBc     |

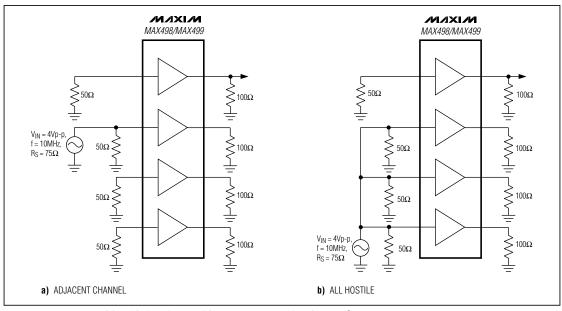

| Adjacent-Channel Crosstalk   |            | f = 10MHz (Note 2)                        |     | 90   |     | dB      |

| All-Hostile Crosstalk        |            | f = 10MHz (Note 3)                        |     | 62   |     | dB      |

| Off-Isolation                |            | EN = 1, f = 10MHz (Note 4)                |     | 81   |     | dB      |

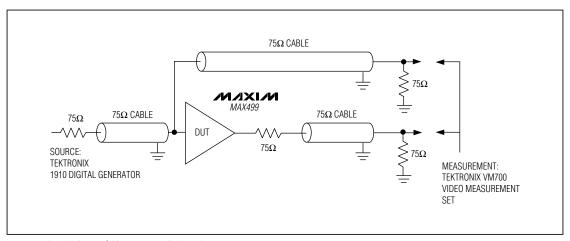

| Differential Gain            | Diff Gain  | $f = 3.58MHz$ (Note 5), $R_L = 150\Omega$ |     | 0.03 |     | %       |

| Differential Phase           | Diff Phase | $f = 3.58MHz$ (Note 5), $R_L = 150\Omega$ |     | 0.06 |     | degrees |

#### **TIMING CHARACTERISTICS**

$(V_{CC} = +5V, V_{EE} = -5V, V_{IN} = 0V, R_L = 150\Omega, LE = \overline{EN} = \overline{CS} = 0V, T_A = 0^{\circ}C$  to  $+70^{\circ}C$ . Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                              | SYMBOL         | CONDITIO           | CONDITIONS |    | TYP | MAX | UNITS |  |

|----------------------------------------|----------------|--------------------|------------|----|-----|-----|-------|--|

| A0/EN to CS Setup Time                 | tsu            | LE = high (Note 6) |            | 8  |     |     | ns    |  |

| A0/EN to CS Hold Time                  | t <sub>H</sub> | LE = high (Note 6) |            |    |     | 4   | ns    |  |

| CS Pulse Width                         | tcs            | (Note 6)           |            | 15 |     |     | ns    |  |

| Channel-Switching<br>Propagation Delay | tPD            | (Note 7)           |            |    | 20  |     | ns    |  |

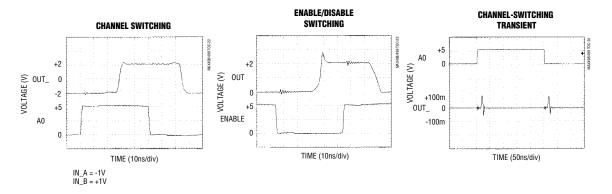

| Channel-Switching Time                 | tsw            | (Note 8)           | (Note 8)   |    | 3   |     | ns    |  |

| Channel-Switching Transient            |                | V                  | Positive   |    | 70  |     | m\/   |  |

| Charmer-Switching Transient            |                | VINA = VINB = 0V   | Negative   |    | 50  |     | mV    |  |

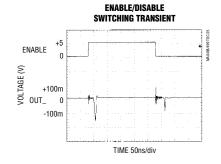

| Enable/Disable Switching               |                | VINA = VINB = 0V   | Positive   |    | 10  |     | mV    |  |

| Transient                              |                | AINY = AINR = OA   | Negative   |    | 150 |     | IIIV  |  |

| Amplifier-Disable Time                 | toff           | (Note 9)           |            |    | 16  |     | ns    |  |

| Amplifier-Enable Time                  | ton            | (Note 10)          | (Note 10)  |    | 24  |     | ns    |  |

|                                        |                |                    |            |    |     |     |       |  |

- Note 2: Test-channel input grounded through a 50Ω resistor. Adjacent channel driven to a 2Vp-p output with a 10MHz sine wave (Figure 9).

- Note 3: Same as Note 2, except all channels but the test channel are driven to a 2Vp-p output with a 10MHz sine wave (Figure 9).

- **Note 4:** Test-channel input connected to a 2V<sub>p-p</sub> sine wave at 10MHz. The test channel's output is measured with the outputs disabled (Figure 9).

- Note 5: Input test signal is a 3.58MHz sine wave of 40IRE amplitude, superimposed on a 0IRE to 100IRE linear ramp (Figure 10).

- Note 6: Guaranteed by design.

- Note 7:  $V_{INA} = +1V$ ,  $V_{INB} = -1V$ , delay from  $\overline{CS}$  to 10% of  $V_{OUT}$ .

- **Note 8:**  $V_{INA} = +1V$ ,  $V_{INB} = -1V$ , delay from  $\overline{CS}$  to 10% of  $V_{OUT}$ .

- Note 9: Delay from EN to 90% of Vout.

- Note 10: Delay from EN to 10% of Vout.

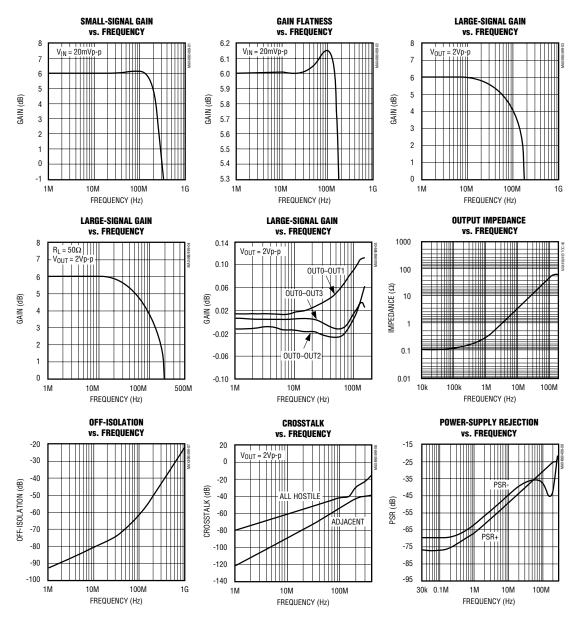

#### 標準動作特性

$(V_{CC} = +5V, V_{EE} = -5V, R_L = 100\Omega, T_A = +25^{\circ}C, unless otherwise noted.)$

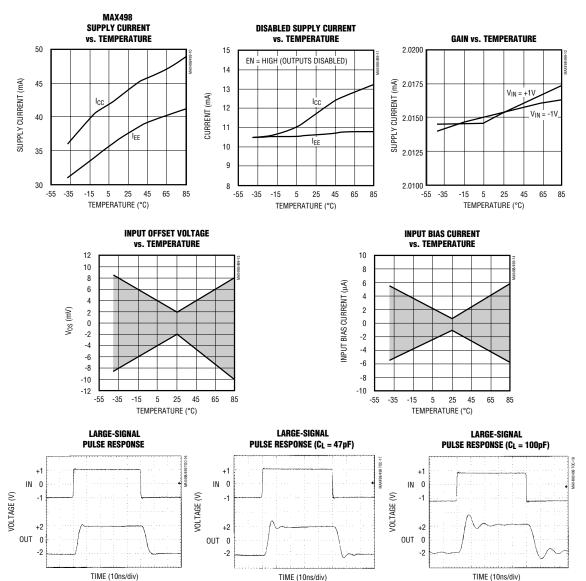

#### 標準動作特性(続き)

$(V_{CC} = +5V, V_{EE} = -5V, R_L = 100\Omega, T_A = +25^{\circ}C, unless otherwise noted.)$

# MAX498/MAX499

## クワッド/トリプル、SPDT、RGBスイッチ 250MHzビデオバッファアンプ付

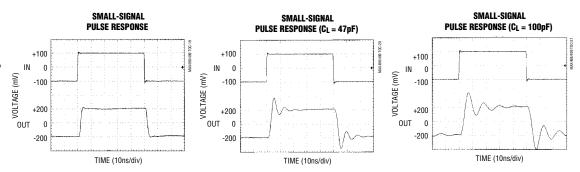

#### 標準動作特性(続き)

$(V_{CC} = +5V, V_{EE} = -5V, R_L = 100\Omega, T_A = +25^{\circ}C, unless otherwise noted.)$

#### 端子説明 \_\_\_\_\_\_

| 端子                        |                    | es th           | 1414 61-                                                                                                                                                                                                                                                                                                                |  |  |  |

|---------------------------|--------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MAX498                    | MAX499             | 名称              | 機能                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 1, 3, 5,<br>11, 13,<br>19 | 2, 4, 9,<br>11, 24 | GND             | アナロググランド。全てのグランドピンは内部接続されています。インピーダンスを最小限に<br>抑えるため、全てのグランドピンを外部でグランドに接続して下さい。                                                                                                                                                                                                                                          |  |  |  |

| 2                         | 1                  | IN1A            | 信号入力1(チャネルA)                                                                                                                                                                                                                                                                                                            |  |  |  |

| 4                         | 3                  | IN2A            | 信号入力2(チャネルA)                                                                                                                                                                                                                                                                                                            |  |  |  |

| 6                         | 5                  | IN3A            | 信号入力3(チャネルA)                                                                                                                                                                                                                                                                                                            |  |  |  |

| 7, 22                     | 6, 18              | Vcc             | 正電源電圧。 $V_{CC}$ は $+5$ Vに接続して下さい。 $V_{CC}$ ピン同士は、内部接続されています。電源インピーダンスを最小限に抑えるため、両方のピンを外部で $+5$ Vに接続して下さい。 $0.1\mu$ Fのセラミックコンデンサで各ピンをグランドにバイパスして下さい。                                                                                                                                                                     |  |  |  |

| 8                         | _                  | IN0B            | 信号入力0(チャネルB)                                                                                                                                                                                                                                                                                                            |  |  |  |

| 9, 21                     | 7, 17              | V <sub>EE</sub> | 負電源電圧。V <sub>EE</sub> は-5Vに接続して下さい。V <sub>EE</sub> ピン同士は、内部接続されています。電源<br>インピーダンスを最小限に抑えるため、両方のピンを外部で-5Vに接続して下さい。0.1μFの<br>セラミックコンデンサで各ピンをグランドにバイパスして下さい。                                                                                                                                                               |  |  |  |

| 10                        | 8                  | IN1B            | 信号入力1(チャネルB)                                                                                                                                                                                                                                                                                                            |  |  |  |

| 12                        | 10                 | IN2B            | 信号入力2(チャネルB)                                                                                                                                                                                                                                                                                                            |  |  |  |

| 14                        | 12                 | IN3B            | 信号入力3(チャネルB)                                                                                                                                                                                                                                                                                                            |  |  |  |

| 15, 17                    | 13, 15             | N.C.            | 無接続。内部接続されていません。                                                                                                                                                                                                                                                                                                        |  |  |  |

| 16                        | 14                 | OUT3            | 出力3                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 18                        | 16                 | OUT2            | 出力2                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 20                        | 19                 | OUT1            | 出力1                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 23                        | _                  | OUT0            | 出力0                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 24                        | 20                 | <del>CS</del>   | チップセレクト入力。 CSがローの時、A0及びENラッチはトランスペアレントです。 CSが<br>ハイになる時にA0のデータがラッチされます。 ENがA0と共にラッチされるか、 ENラッチが<br>CSに関係なくトランスペアレント状態のままであるかは、LEの状態によって決まります。                                                                                                                                                                           |  |  |  |

| 25                        | 21                 | A0              | アドレス入力。 $\overline{\text{CS}}$ がローの時にA0 = 0の場合チャネルAが選択され、A0 = 1の場合チャネルBが選択されます。 $\overline{\text{CS}}$ がローからハイに遷移する時にA0がラッチされます。                                                                                                                                                                                        |  |  |  |

| 26                        | 22                 | ĒN              | 出力バッファイネーブル入力。 $\overline{\text{CS}}$ がローの時に $\overline{\text{EN}}$ = $0$ の場合出力バッファアンブがイネーブルされ、 $\overline{\text{EN}}$ = $1$ の場合出力バッファがディセーブルされます。 $\overline{\text{LE}}$ が入れての時に $\overline{\text{CS}}$ がローからハイに遷移すると $\overline{\text{EN}}$ がラッチされます。 $\overline{\text{LE}}$ がつの時には $\overline{\text{EN}}$ はラッチされません。 |  |  |  |

| 27 23 LE                  |                    | LE              | ラッチイネーブル入力。 $LE=1$ の場合 $\overline{CS}$ がハイになる時に $\overline{EN}$ は $A0$ と共にラッチされます。<br>$LE=0$ の場合、 $\overline{CS}$ の状態に関係なく $\overline{EN}$ ラッチはトランスペアレントです。                                                                                                                                                             |  |  |  |

| 28                        | _                  | INOA            | 信号入力0(チャネルA)                                                                                                                                                                                                                                                                                                            |  |  |  |

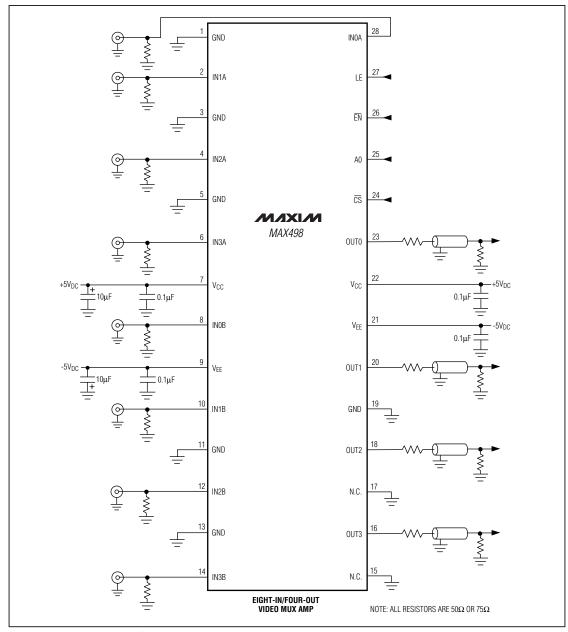

図1a. MAX498の標準アプリケーション回路

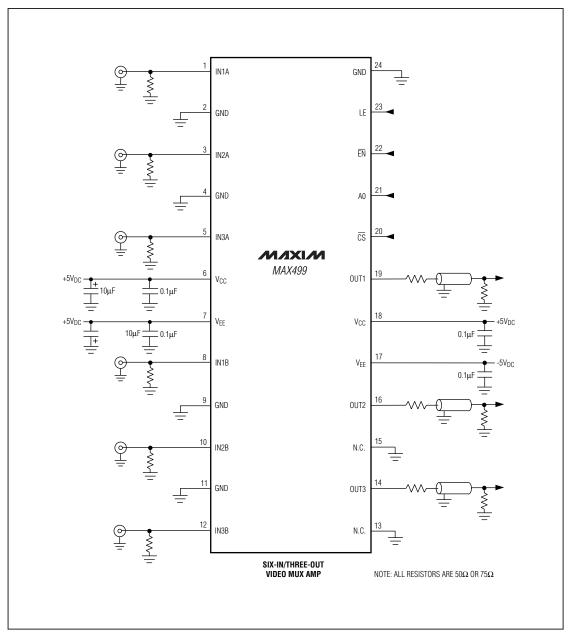

図1b. MAX499の標準アプリケーション回路

#### 詳細

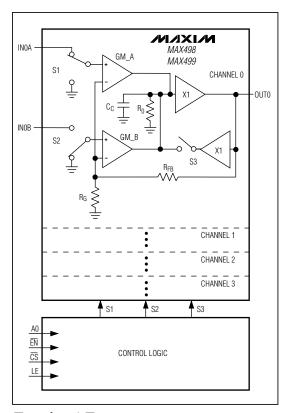

MAX498/MAX499は、利得2V/Vに設定された高速閉ループ電圧フィードバックアンプ付のクワッド/トリプルビデオスイッチです。図1に、標準アプリケーション回路を示します。アンプは、ユニークな2段電圧フィードバック構造を採用しています。これは、精度を保ちつつ広帯域幅と高スルーレートを実現するために従来の電圧フィードバック及び電流フィードバックトポロジーの利点を組み合わせた構造です。

図2に、MAX498/MAX499の簡略プロック図を示します。4つのアンプ/スイッチブロックはどれもCh\_0に示すものと同一です。共通制御ロジックプロックは、外部ロジック入力としてAO、EN、CS及びLEを受け付け、各アンプのスイッチS1、S2及びS3の状態を並列に制御します(「ディジタルインタフェース」の項を参照)。イネーブル状態ではS3はオープンになり、Ch\_Aが選択されている場合はS1がIN\_Aに接続され、S2がGNDに接続されます。Ch\_Bが選択されている場合は、S1がGNDに接続されます。選択されていないGM\_ブロックをGNDに接続することにより、フィードスルーを最小限に抑えることができます。

ディセーブル状態ではS3が閉じ、S1とS2は両方ともGNDに接続されます。両方の入力の接続を切断し、アンプの入力をGNDに接続するとオフ・アイソレーションが著しく改善されます。

#### アプリケーション情報

#### 電力消費

MAX498/MAX499の最大出力電流は、パッケージの最大許容電力消費によって制限されています。最大ジャンクション温度が+150 を越えないようにして下さい。負荷が増大すると電力消費も増大します。この関係は次式によって近似できます。

V<sub>OUT</sub> > 0Vの場合:¦V<sub>CC</sub> - V<sub>OUT</sub>¦I<sub>LOAD</sub> 又は

VOUT < 0Vの場合: | VEE - VOUT | ILOAD これらのデバイスは、各出力に接続された100 の負荷を定格出力スイング及び温度範囲の全域で駆動できます。出力は120mAの短絡保護が施されていますが、必ずしも全ての条件下で最大ジャンクション温度を超えないことが保証されているわけではありません。「絶対最大定格」の項で与えられているディレーティング値を超えないで下さい。

図2. ブロック図

#### 全ノイズ

MAX498/MAX499は、入力電流ノイズが2.6pA/√Hz、電圧ノイズが7.8nV/√Hzと、標準的な電流モードフィードバックアンプよりも全ノイズが低くなっています(標準的な電流モードフィードバックアンプは入力電流ノイズが大幅に高くなっています)。電流モードフィードバックアンプでは、入力電流ノイズとフィードバック抵抗の積が主なノイズ源です。

#### 微分利得及び位相エラー

コンポジット(NTSC、PAL、SECAM)ビデオアプリケーションでは、微分利得及び位相エラーの仕様が重要です。これは、これらのエラーがコンポジットビデオ機器で表示される画像の色の変化に直接対応するためです。MAX498/MAX499は、利得及び位相エラーが低いため(0.03%/0.06°)、放送用品質のコンポジットビデオアプリケーションに最適です。

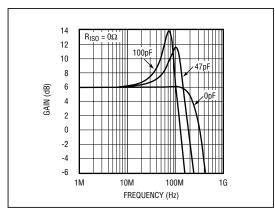

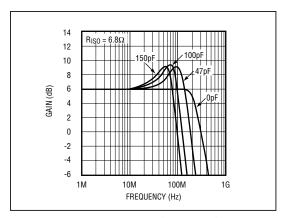

図3a. 小信号利得対周波数及び負荷コンデンサ (R<sub>L</sub> = 100 、R<sub>ISO</sub> = 0 )

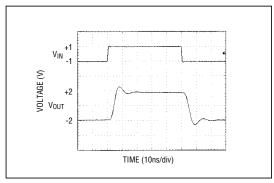

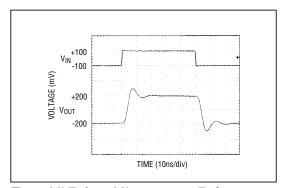

図4a. 大信号パルス応答(C<sub>L</sub> = 100pF及び R<sub>ISO</sub> = 5.1 )

#### 同軸ケーブルドライバ

MAX498/MAX499は、高速性、優秀な出力電流能力及び +2の内部固定利得を備えているため、逆終端の50 又は75 同軸ケーブルを±2.5Vまで駆動するのに最適 です。

標準的なアプリケーションでは、MAX498/MAX499 は逆終端ケーブルを駆動します(図1)。出力位置の逆終端抵抗によってケーブルの被駆動端のインピーダンスがケーブルのインピーダンスとマッチングされるため、信号の反射が排除されます。この抵抗及び負荷終端抵抗が分圧器を形成するため、ケーブルの出力における信号は1/2に減衰します。MAX498/MAX499は、内部で+2V/Vの閉ループ利得を備えているため、ケーブル出力でユニティゲインを提供します。

図3b. 小信号利得対周波数及び負荷コンデンサ (R<sub>I</sub> = 100 、R<sub>ISO</sub> = 6.8 )

図4b. 小信号パルス応答(C<sub>L</sub> = 100pF及び R<sub>ISO</sub> = 5.1 )

#### 容量性負荷の駆動

始どのアンプ回路の場合、大きな容量性負荷を駆動すると発振の可能性が増加します。この傾向は、電圧フォロワのような高ループ利得の回路では特に顕著です。アンプの出力抵抗及び容量性負荷がRCフィルタを形成して、ループ応答にポールが付加されます。このポールの周波数がある程度低いと(例えば大きな容量性負荷を駆動する場合)、位相マージンが劣化して発振が生じることがあります。

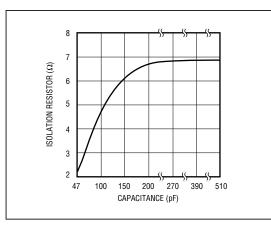

MAX498/MAX499は、持続的な発振を起こさずに 100pFまでの容量性負荷を駆動しますが、ある程度の ピーキングが生じることがあります(図3a及び3b)。 大きな容量性負荷を駆動する場合やピーキングを低減したい場合は、アンプの出力と容量性負荷の間にアイソレーション抵抗(R<sub>ISO</sub>)を付加して下さい(図4a、4b及び5)。

図5. アイソレーション抵抗対容量性負荷

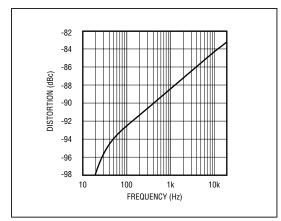

#### オーディオ信号のスイッチング (オーディオ歪み測定)

オーディオ信号のスイッチングで性能上最も重要な事項は歪みです。図6に、MAX498/MAX499のオーディオ範囲での全高調波歪み対周波数のグラフを示します。

#### 大型スイッチアレイ

MAX498/MAX499のイネーブル機能ENを使用すると、大きなクロスポイントスイッチアレイが可能です。アンプがディセーブルされている時の出力インピーダンスは、フィードバックと利得抵抗に起因する1.2k(typ)です。このため、バッファなしに並列に接続できる出力の数が制限されます。各出力が100 を駆動できるため、通常8個までの出力をまとめて接続できます。それ以上の出力を並列に接続する必要がある場合は、MAX4178(シングル)、MAX496(クワッド)又は相当するユニティゲインバッファを使用して下さい。

イネーブル状態でもディセーブル状態でも、各入力には200k 以上の抵抗があります。1つの出力に接続できる入力の数を制限している主な原因は容量です。各出力は100pFの容量をアイソレーション抵抗なしに駆動できるため、1つの出力で50個の入力(C<sub>IN</sub> = 2pF、typ)を駆動することができます。但し、入力を増やすとピーキングが発生し(図3)、そのために0.1dB帯域幅が減少します。

図6. 全高調波歪み(オーディオ)対周波数

#### ディジタルインタフェース

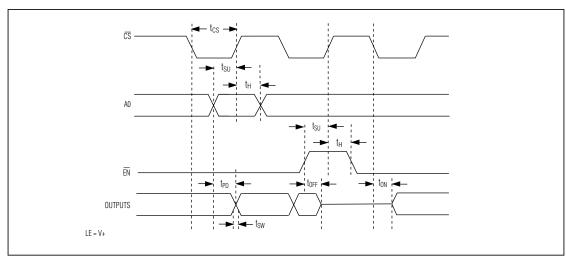

MAX498/MAX499マルチプレクサは、入力チャネル同士が相互に接続されない構造になっています。チャネルを選択するには、A0の状態を変え(チャネルAの場合A0 = 0、チャネルBの場合A0 = 1)、 $\overline{\text{CS}}$ をパルス的にローにして下さい(表1a及び1bを参照)。図7にロジックタイミング図を示します。

イネーブル入力 ( $\overline{\text{EN}}$ )をTTLロー状態にすると、MAX498/MAX499のアンプ出力がイネーブルされます。 $\overline{\text{EN}}$ をハイにすると、アンプ出力がディセーブルされます。ディセーブルされていると、MAX498/MAX499は内部フィードバック抵抗に起因する1.2kのディセーブル出力抵抗があります。

LEは $\overline{\text{EN}}$ が $\overline{\text{CS}}$ でラッチされるか、独立に動作するかを決定します。 ラッチイネーブル入力(LE)がV+に接続されていると、 $\overline{\text{CS}}$ が $\overline{\text{EN}}$ 入力レジスタのラッチを制御します。  $\overline{\text{CS}}$ がローの時、 $\overline{\text{EN}}$ 及びA0の両方のラッチがトランスペアレントになります。 $\overline{\text{CS}}$ がハイに戻るとA0及び $\overline{\text{EN}}$ の両方がラッチされます。

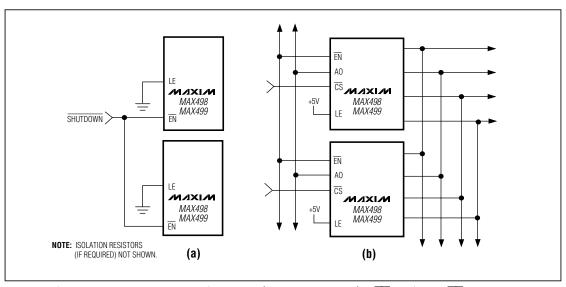

LEがグランドに接続されていると、ENラッチがトランスペアレントになり、CSから独立します。これにより、CSの入力状態に関係なく全てのMAX498/MAX499デバイスを同時にシャットダウンできます。LEをグランドに接続し、全てのEN入力をまとめて接続するだけです(図8a)。ディジタル入力からINOAへののクロストークを防ぐために、(LEをゲートで駆動するのではなく)LEをV+又はグランドにハード配線して下さい。

出力をディセーブルするもう1つの方法としては、LEをV+に接続し、幾つかのMAX498/MAX499の出力を並列に接続し、 $\overline{EN}$ を使って使用中のもの以外の全てのデバイスを個々にディセーブルする方法があります(図8b参照)。

出力がディセーブルされている場合、アンプ出力のアナログ入力からのオフアイソレーションは10MHzで81dB(typ)です。

#### 接地及びレイアウト

MAX498/MAX499の帯域幅は、RF周波数範囲にあります。PCポードのサイズ及び動作周波数によっては、マイクロストリップ又はストリップライン技法を使用する必要があります。

これらの高速バッファのAC性能を十分に発揮させるためには、電源バイパス及びボードレイアウトに注意する必要があります。PCボードは少なくとも2層のものを使用し(誘導性が大きすぎるため、ワイヤラップボードの使用は避けて下さい)、片方は信号層とし、他方は大きな低インピーダンスのグランドプレーンとします。多層ボードの場合は、特定の信号トレース専用になっていない層にグランドプレーンを配置して下さい。グランドプレーンにはできるだけ空所を作らないようにして下さい。全てのグランドピンをグランドプレーンに接続して下さい。

両方の正電源ピンをまとめて接続し、各電源ピン位置 (デバイスのできるだけ近く)で0.1µFのセラミックコン デンサを使用してバイパスして下さい。負電源ピンも同様に処理して下さい。インダクタンスを最小限に抑えるため、コンデンサのリード線はできるだけ短くして下さい。理想的には、表面実装チップコンデンサを使用します。電流負荷が大きい場合には、各電源に大容量(10µF以上)のタンタル又は電解バイパスコンデンサが必要な場合があります。このコンデンサの位置は重要ではありません。

MAX498/MAX499のアナログ入力ピンは、グランドピンによって隔離されています。これはクロストークやアンプの安定性を劣化させる寄生カップリングを最小限に抑えるためです。インダクタンスを最小限に抑えるため、信号経路はできるだけ短くして下さい。4つのチャネルトレースが同じ長さになるようにします。クロストークをさらに小さくするため、同軸ケーブルのシールドをグランドプレーンの75 終端抵抗のグランド側に接続し、未使用の入力は全てグランドに終端処理し、出力は100 又は150 抵抗でグランドに終端処理して下さい。

表1a. LE = V+時のアンプ及びチャネル選択

| <u>cs</u> | ĒN | A0 | 機能                          |

|-----------|----|----|-----------------------------|

| 0         | 0  | 0  | アンプ出力をイネーブル。チャネルAを<br>選択    |

| 0         | 0  | 1  | アンプ出力をイネーブル。チャネルBを<br>選択    |

| 0         | 1  | Χ  | アンプをディセーブル。出力はハイ<br>インピーダンス |

| 1         | Х  | Х  | A0、ENをラッチ。出力は無変化。           |

表1b. LE = GND時のアンプ及び チャネル選択

| CE | ĒN | Ā0 | 機能                                                         |  |  |

|----|----|----|------------------------------------------------------------|--|--|

| 0  | 0  | 0  | アンプ出力をイネーブル。チャネルA<br>を選択                                   |  |  |

| 1  | 0  | X  | アンブ出力をイネーブル。CSの最終<br>エッジにおけるAOの状態によって、<br>出力A又は出力BにAOをラッチ。 |  |  |

| Х  | 1  | Х  | アンプをディセーブル。出力はハイ<br>インピーダンス。A0ラッチは出力A。                     |  |  |

| 0  | 0  | 1  | アンプ出力をイネーブル。チャネルB<br>を選択                                   |  |  |

図7. ロジックタイミング図

図8. (a) 全てのMAX498/MAX499の同時シャットダウン; (b) イネーブル(EN)レジスタをCSでラッチ

図9. クロストーク測定用試験回路; a) 隣接チャネル; b) 他の全てのピン

図10. 微分位相及び利得エラー試験回路

#### ピン配置(続き)

#### チップ情報

SUBSTRATE CONNECTED TO: VEE TRANSISTOR COUNT: 813

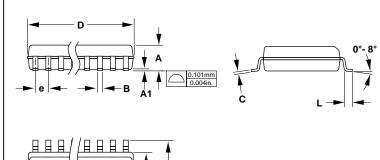

#### パッケージ

| DIM | INC     | HES   | MILLIMETERS |       |  |

|-----|---------|-------|-------------|-------|--|

| DIN | MIN     | MAX   | MIN         | MAX   |  |

| Α   | 0.093   | 0.104 | 2.35        | 2.65  |  |

| A1  | B 0.014 | 0.012 | 0.10        | 0.30  |  |

| В   |         | 0.019 | 0.35        | 0.49  |  |

| С   |         | 0.013 | 0.23        | 0.32  |  |

| Е   | 0.291   | 0.299 | 7.40        | 7.60  |  |

| е   | 0.0     | 050   | 1.          | 27    |  |

| Н   | 0.394   | 0.419 | 10.00       | 10.65 |  |

| L   | 0.016   | 0.050 | 0.40        | 1.27  |  |

Wide SO SMALL-OUTLINE PACKAGE (0.300 in.)

| DIM | PINS | INC   | HES   | MILLIMETERS |       |  |

|-----|------|-------|-------|-------------|-------|--|

| DIN |      | MIN   | MAX   | MIN         | MAX   |  |

| D   | 16   | 0.398 | 0.413 | 10.10       | 10.50 |  |

| D   | 18   | 0.447 | 0.463 | 11.35       | 11.75 |  |

| D   | 20   | 0.496 | 0.512 | 12.60       | 13.00 |  |

| D   | 24   | 0.598 | 0.614 | 15.20       | 15.60 |  |

| D   | 28   | 0.697 | 0.713 | 17.70       | 18.10 |  |

21-0042A

## マキシム・ジャパン株式会社

〒169 東京都新宿区西早稲田3-30-16(ホリゾン1ビル) TEL. (03)3232-6141 FAX. (03)3232-6149

マキシム社では全体がマキシム社製品で実現されている回路以外の回路の使用については責任を持ちません。回路特許ライセンスは明言されていません。マキシム社は随時予告なしに回路及び仕様を変更する権利を保留します。

16 \_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 (408) 737-7600