## 概要

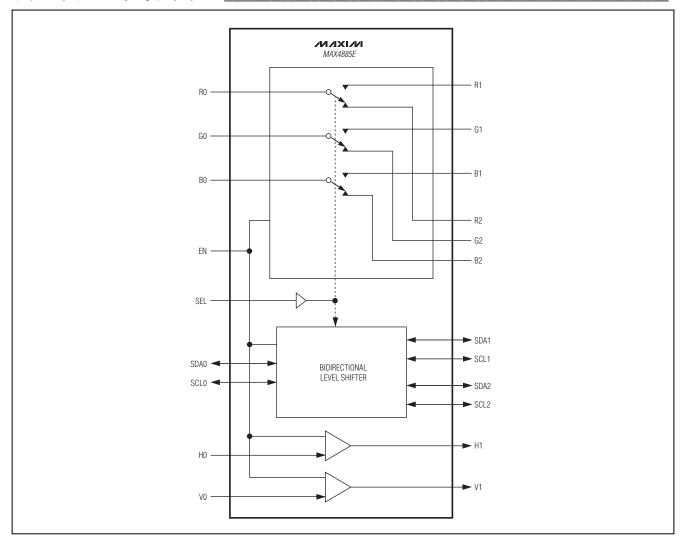

MAX4885Eは、VGA信号用の完全な1:2のマルチプレ クサを実現する、広帯域アナログスイッチ、およびレベル 変換バッファを備えています。このデバイスは、RGB、 ディスプレイデータチャネル(DDC)用のスイッチング 機能を提供します。

水平および垂直同期(HSYNC/VSYNC)入力は、±8mAの VESA要件を満足し、低電圧CMOSまたは標準TTL互換 のグラフィックスコントローラをサポートするための、 レベルシフト用バッファを備えています。SDA および SCL で構成されるDDCは、容量性の負荷を減少させる 双方向アクティブレベル変換スイッチです。MAX4885E は、外部へ接続される12個すべての端子について ±15kVのヒューマンボディモデル(HBM)の高ESD保護 を備えています。「端子説明」の項を参照してください。 他のすべてのピンは、±10kVのヒューマンボディモデル (HBM)に対して保護されています。

MAX4885Eは、-40℃~+85℃の拡張温度範囲で規定 され、4mm×4mmの24ピンTQFNパッケージで提供 されます。

## アプリケーション

ノートブックコンピュータ/ドッキングステーション ディジタルプロジェクタ

コンピュータモニタ

サーバ/記憶装置

KVMスイッチ

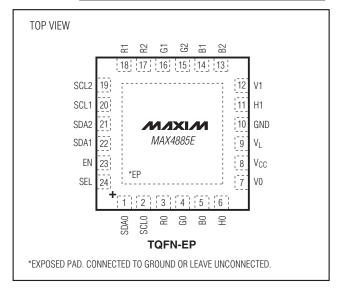

## ピン配置

### 特長

- ◆ 外部へ接続される端子の±15kV HBM ESD保護

- ◆ 1GHzの帯域幅

- ◆ 5Ω (typ)の低オン抵抗(R、G、B信号)

- ♦ 6pF (typ)の低オン容量(R、G、B信号)

- ◆ -50ps (typ)のR、G、B低スキュー

- ◆ ほぼゼロの消費電力(< 2µA)</p>

- ◆ 超小型、24ピンTQFNパッケージ(4mm x 4mm)

### 型番

| PART         | TEMP RANGE     | PIN-PACKAGE |

|--------------|----------------|-------------|

| MAX4885EETG+ | -40°C to +85°C | 24 TQFN-EP* |

\*EP = エクスポーズドパッド

+は、鉛フリーパッケージ/RoHS準拠パッケージを示します。

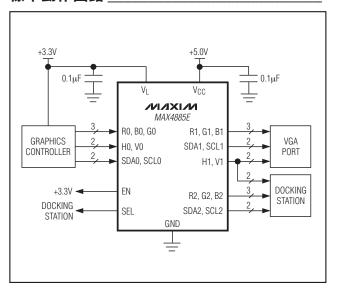

### 標準動作回路

####

## **ABSOLUTE MAXIMUM RATINGS**

| (All voltages referenced to GND.)                 |                       |

|---------------------------------------------------|-----------------------|

| VCC, VLC                                          | ).3V to +6V           |

| R_, G_, B_, SDA1, SCL1, SDA2, SCL2,               |                       |

| H1, V1, (Note 1)0.3V to V                         | √CC + 0.3V            |

| H0, V0, SDA0, SCL0, EN, SEL0.3V to                | V <sub>L</sub> + 0.3V |

| Continuous Current through RGB Switches           | ±30mA                 |

| Continuous Current through DDC Switches           | ±30mA                 |

| Peak Current through RGB Switches                 |                       |

| (pulsed at 1ms, 10% duty cycle)                   | ±90mA                 |

| Peak Current through DDC Switches (pulsed at 1ms, |                       |

| 10% duty cycle)                                   | ±90mA                 |

|                                                   |                       |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)<br>24-Pin TQFN (derate 27.8mW/°C above +70°C)<br>Junction to Ambient Thermal Resistance (θ <sub>JA</sub> ) (Note 2 |           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 24-Pin TQFN                                                                                                                                                              |           |

| Junction to Ambient Thermal Resistance (θ <sub>JC</sub> ) (Note 2                                                                                                        | ,         |

| 24-Pin TQFN                                                                                                                                                              | 3°C/W     |

| Operating Temperature Range40°C                                                                                                                                          | to +85°C  |

| Storage Temperature Range65°C                                                                                                                                            | to +150°C |

| Junction Temperature                                                                                                                                                     |           |

| Lead Temperature (soldering, 10s)                                                                                                                                        | +300°C    |

|                                                                                                                                                                          |           |

Note 1: Signals exceeding V<sub>CC</sub> or GND are clamped by internal diodes. Limit forward-diode current to maximum current rating.

**Note 2:** Package thermal resistances were obtained using the method described in JEDEC specifications. For detailed information on package thermal considerations, refer to <a href="https://www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +5.0V \pm 10\%, V_L = +2V \text{ to } +5.5V, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = +5.0V, V_L = +3.3V$  and  $T_A = +25^{\circ}C.)$  (Note 3)

| PARAMETER                                | SYMBOL                 | со                                                                                             | NDITIONS                                                                 | MIN                      | TYP | MAX                      | UNITS |

|------------------------------------------|------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------|-----|--------------------------|-------|

| V Outpassed Curable Course               | la a                   | V                                                                                              | EN = V <sub>L</sub>                                                      |                          |     | 4                        |       |

| V <sub>CC</sub> Quiescent Supply Current | Icc                    | $V_{CC} = +5.0V$                                                                               | EN = GND                                                                 |                          |     | 1                        | μΑ    |

| V. Ouissaant Cumply Current              | ls a                   | V <sub>I</sub> = +3.3V                                                                         | EN = V <sub>L</sub>                                                      |                          |     | 1                        |       |

| V <sub>L</sub> Quiescent Supply Current  | I <sub>VL</sub>        | VL = +3.3V                                                                                     | EN = GND                                                                 |                          |     | ı                        | μA    |

| RGB ANALOG SWITCHES                      |                        |                                                                                                |                                                                          |                          |     |                          |       |

| On-Resistance                            | Ron                    | V <sub>CC</sub> = +5.0V, I <sub>IN</sub> = (Note 4)                                            | $-10$ mA, $V_{IN} = +0.7V$                                               |                          | 6   |                          | Ω     |

| On-Resistance Matching                   | ΔR <sub>ON</sub>       | $0 \le V_{IN} \le 0.7V$ , $I_{IN}$                                                             | = -10mA                                                                  |                          | 0.5 |                          | Ω     |

| On-Resistance Flatness                   | R <sub>FLAT</sub> (ON) | $0 \le V_{IN} \le 0.7V, I_{IN}$                                                                | = -10mA                                                                  |                          | 0.5 |                          | Ω     |

| Off-Leakage Current                      | I <sub>L(OFF)</sub>    | $V_{CC} = +5.5V$ , $V_{IN} = V_{EN} = 0$ or $V_{L}$                                            | $V_{CC} = +5.5V$ , $V_{IN} = +0.3V$ or $+5.5V$ , $V_{EN} = 0$ or $V_{L}$ |                          |     | +1                       | μΑ    |

| On-Leakage Current                       | I <sub>L(ON)</sub>     | V <sub>CC</sub> = +5.5V, V <sub>IN</sub> = +0.3V or +5.5V,<br>V <sub>EN</sub> = V <sub>L</sub> |                                                                          | -1                       |     | +1                       | μA    |

| HV BUFFER                                | •                      |                                                                                                |                                                                          | •                        |     |                          | •     |

| Input Voltage Low                        | VILHV                  |                                                                                                |                                                                          |                          |     | 0.33 x<br>V <sub>L</sub> | V     |

| Input Voltage High                       | VIHHV                  |                                                                                                |                                                                          | 0.66 x<br>V <sub>L</sub> |     |                          | V     |

| Input Logic Hysteresis                   | V <sub>HYST</sub>      |                                                                                                |                                                                          |                          | 75  |                          | mV    |

| Input Leakage Current                    | linhv                  | $V_{CC} = +5.5V, V_{L} =$                                                                      | $+5.5V$ , $V_{IN} = 0$ or $V_{L}$                                        | -1                       |     | +1                       | μΑ    |

| High-Output Drive Current                | Іонну                  | V <sub>OHHV</sub> ≥ 3.0V                                                                       |                                                                          | 8.0                      |     |                          | mA    |

| Low-Output Drive Current                 | lolhv                  | V <sub>OLHV</sub> ≤ 0.6V                                                                       |                                                                          | 8.0                      |     |                          | mA    |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +5.0V \pm 10\%, V_L = +2V \text{ to } +5.5V, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = +5.0V, V_L = +3.3V$  and  $T_A = +25^{\circ}C$ .) (Note 3)

| PARAMETER                               | SYMBOL             | CONDITIONS                                                                                                     | MIN                      | TYP | MAX                      | UNITS |

|-----------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------|--------------------------|-----|--------------------------|-------|

| SDA_, SCL_                              |                    |                                                                                                                |                          |     |                          |       |

| Supply Voltage                          | VL                 |                                                                                                                | 2.0                      |     | 5.5                      | V     |

| On-Resistance                           | Ron                | $V_{IN} = +0.4V$ , $I_{IN} = \pm 2mA$ , $V_L = +2.0V$                                                          |                          | 10  |                          | Ω     |

| On-Capacitance                          | Con                | f = 100kHz                                                                                                     |                          | 15  |                          | рF    |

| High-Impedance Input Leakage<br>Current | IINHIZ             | EN = GND, $V_{CC}$ = +5.5V, $V_L$ = +3.6V,<br>SCL0, SDA0, SCL1, SCL2, SDA1, SDA2<br>= GND or $V_{VL}$ (Note 5) | -1                       |     | +1                       | μA    |

| Off-Input Leakage Current               | INOFF              | $EN = V_L, V_L = +3.6V, V_{IN} = V_L - 0.2V$                                                                   | -1                       |     | +1                       | μΑ    |

| CONTROL LOGIC (SEL, EN)                 |                    |                                                                                                                |                          |     |                          |       |

| Input Voltage Low                       | V <sub>ILLOG</sub> |                                                                                                                |                          |     | 0.33 x<br>V <sub>L</sub> | V     |

| Input Voltage High                      | Vihlog             |                                                                                                                | 0.66 x<br>V <sub>L</sub> |     |                          | V     |

| Input Logic Hysteresis                  | V <sub>HYST</sub>  |                                                                                                                |                          | 75  |                          | mV    |

| Input Leakage Current                   | INLEK              | $V_{CC} = +5.5V$ , $V_{L} = +3.6V$ , $V_{IN} = 0$ or $V_{L}$                                                   | -1                       |     | +1                       | μΑ    |

| ESD PROTECTION                          |                    |                                                                                                                |                          |     |                          |       |

| ESD Protection                          |                    | Human Body Model; R1, G1, B1, R2, G2, B2, SDA1, SCL1, SDA2, SCL2, H1, V1                                       |                          | ±15 |                          | kV    |

|                                         |                    | Human Body Model; all other pins                                                                               |                          | ±10 |                          |       |

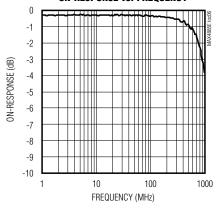

## **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +5.0V \pm 10\%, V_L = +2V \text{ to } +5.5V, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } V_{CC} = +5.0V, V_L = +3.3V \text{ and } T_A = +25^{\circ}C.)$  (Note 3)

| PARAMETER       | SYMBOL           | CONDITIONS                                      | MIN | TYP | MAX | UNITS |

|-----------------|------------------|-------------------------------------------------|-----|-----|-----|-------|

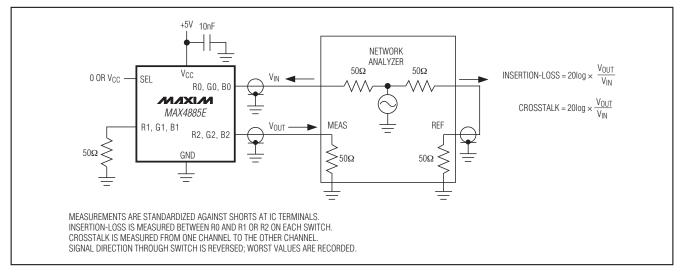

| Bandwidth       | f <sub>MAX</sub> | $R_S = R_L = 50\Omega$                          |     | 1   |     | GHz   |

| Insertion Loss  | ILOS             | $f = 1MHz$ , $R_S = R_L = 50\Omega$ , Figure 1  |     | 0.6 |     | dB    |

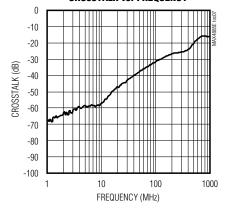

| Crosstalk       | V <sub>C</sub> T | $f = 50MHz$ , $R_S = R_L = 50\Omega$ , Figure 1 |     | -40 |     | dB    |

| Off-Capacitance | Coff             | f = 250MHz                                      |     | 4.5 |     | рF    |

| On-Capacitance  | Con              | f = 250MHz                                      |     | 6.4 |     | рF    |

### **TIMING CHARACTERISTICS**

$(V_{CC} = +5.0V \pm 10\%, V_L = +2V \text{ to } +5.5V, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } V_{CC} = +5.0V, V_L = +3.3V \text{ and } T_A = +25^{\circ}C.) \text{ (Note 3)}$

| PARAMETER                 | SYMBOL          | CONDITIONS                                       | MIN | TYP | MAX | UNITS |

|---------------------------|-----------------|--------------------------------------------------|-----|-----|-----|-------|

| RGB ANALOG SWITCHES       |                 |                                                  |     |     |     |       |

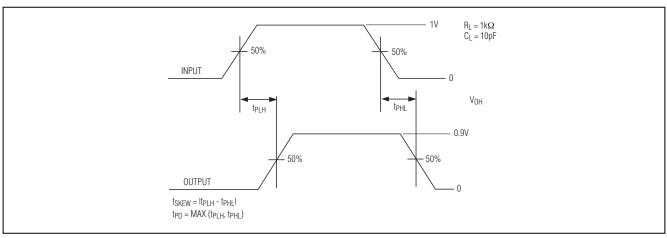

| Output Skew Between Ports | tskew           | Skew between any two ports: R_, G_, B_, Figure 2 | 50  |     |     | ps    |

| HV BUFFER                 |                 |                                                  |     |     |     |       |

| Propagation Delay         | t <sub>PD</sub> | $R_L = 1k\Omega$ , $C_L = 10pF$ , Figure 2       |     | 15  |     | ns    |

Note 3: All devices are 100% production tested at  $T_A = +25$ °C. Specifications over the full temperature range are guaranteed by design.

Note 4: On-resistance guarantees the low-static logic level.

Note 5: SDA\_, SCL\_ off-input leakage current guarantees the high-static logic level.

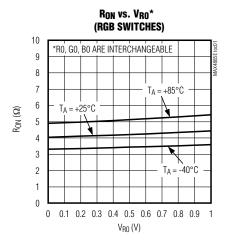

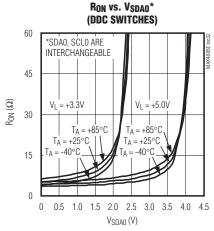

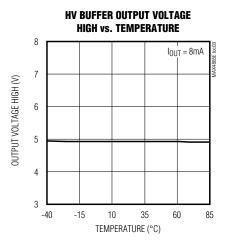

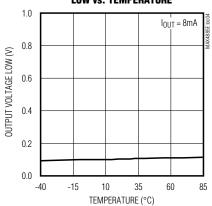

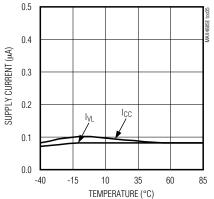

## 標準動作特性

$(V_{CC} = +5.0V, V_L = +3.3V \text{ and } T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

## 標準動作特性(続き)

( $V_{CC} = +5.0V$ ,  $V_L = +3.3V$  and  $T_A = +25$ °C, unless otherwise noted.)

## HV BUFFER OUTPUT VOLTAGE LOW vs. TEMPERATURE

## SUPPLY CURRENT vs. TEMPERATURE

### ON-RESPONSE vs. FREQUENCY

### CROSSTALK vs. FREQUENCY

## タイミング回路/タイミング図

図1. 挿入損失およびクロストーク

図2. 伝搬遅延およびスキュー波形

### 端子説明

| 端子 | 名称   | 機能                                                                                     |

|----|------|----------------------------------------------------------------------------------------|

| 1  | SDA0 | SDA I/O                                                                                |

| 2  | SCL0 | SCL I/O                                                                                |

| 3  | R0   | RGBアナログI/O                                                                             |

| 4  | G0   | RGBアナログI/O                                                                             |

| 5  | В0   | RGBアナログI/O                                                                             |

| 6  | H0   | 水平同期入力                                                                                 |

| 7  | V0   | 垂直同期入力                                                                                 |

| 8  | Vcc  | 供給電圧。 $V_{CC} = +5.0V \pm 10\%$ 。 $0.1 \mu F$ 以上のセラミックコンデンサで $V_{CC}$ をGNDへバイパスしてください。 |

| 9  | VL   | 供給電圧。 $+2V \le V_L \le +5.5V$ 。 $0.1\mu$ F以上のセラミックコンデンサで $V_L$ をGNDへバイパスしてください。        |

| 10 | GND  | グランド                                                                                   |

| 11 | H1   | 水平同期出力*                                                                                |

| 12 | V1   | 垂直同期出力*                                                                                |

| 13 | B2   | RGBアナログI/O*                                                                            |

| 14 | B1   | RGBアナログI/O*                                                                            |

| 15 | G2   | RGBアナログI/O*                                                                            |

| 16 | G1   | RGBアナログI/O*                                                                            |

| 17 | R2   | RGBアナログI/O*                                                                            |

| 18 | R1   | RGBアナログI/O*                                                                            |

| 19 | SCL2 | SCL I/O*                                                                               |

| 20 | SCL1 | SCL I/O*                                                                               |

| 21 | SDA2 | SDA I/O*                                                                               |

| 22 | SDA1 | SDA I/O*                                                                               |

| 23 | EN   | イネーブル入力。通常動作のためには、ENをハイに駆動してください。デバイスをディセーブルするためには、ENをローに駆動してください。                     |

| 24 | SEL  | 選択入力。RGBおよびDDCスイッチを切り替えるロジック入力。                                                        |

|    | EP   | エクスポーズドパッド。エクスポーズドパッドは、グランドに接続、または未接続としてください。                                          |

<sup>\*±15</sup>kV ESD—ヒューマンボディモデル保護端子

### 詳細

MAX4885Eは、VGA信号用の完全な1:2のマルチプレクサを実現する、広帯域アナログスイッチ、およびレベル変換バッファを備えています。このデバイスは、RGB、HSYNC、VSYNC、SDA\_、およびSCL\_信号のスイッチング機能を提供します。

低電圧グラフィックスコントローラからのTTLロジックレベル出力を取り扱うために、HSYNCとVSYNC入力はレベルシフト用バッファを備えています。バッファされたこれらのスイッチは、最小+2.0V~最大+5.5Vまで駆動することができます。RGB信号は、同様の高性能アナログスイッチによって経路が選択され、SDA\_、SCL\_信号は、VLに供給される電圧からダイオード降下分低い電圧にクランプされます。電圧クランプは、SDA\_、SCL\_信号および低電圧ASICの保護と互換性を提供します。キーボード/ビデオ/マウス(KVM)アプリケーションでは、

VESA標準によって規定されているように、低電圧 クランプが不要なため、 $V_L$ は通常+5Vに設定されます。

MAX4885Eをシャットダウンするためには、ENをロジックローに駆動します。シャットダウンモード時は、すべてのスイッチはハイインピーダンスになり、高い信号分離を提供します。RGB、HSYNC、VSYNC、SDA\_、およびSCL\_出力は、±15kVまでのヒューマンボディモデルについてESD保護されています。

#### RGBスイッチ

MAX4885Eは、VGA R、G、およびBの標準信号の経路を選択するための3個のSPDT高帯域スイッチを提供します(表1を参照)。R、G、およびBのアナログスイッチは同一で、3個のスイッチのいずれも、赤、緑、または青のビデオ信号の経路を選択するために使用することができます。

## 表1. RGBの真理値表

| EN | SEL | FUNCTION                         |

|----|-----|----------------------------------|

| 1  | 0   | R0 to R1<br>G0 to G1<br>B0 to B1 |

| 1  | 1   | R0 to R2<br>G0 to G2<br>B0 to B2 |

| 0  | Х   | R_, B_, and G_, high impedance   |

X = 任意

### 表2. HVの真理値表

| EN | FUNCTION   |

|----|------------|

| 0  | H_, V_ = 0 |

X = 任意

## 表3. DDCの真理値表

| EN | SEL | FUNCTION                     |

|----|-----|------------------------------|

| 1  | 0   | SDA0 to SDA1<br>SCL0 to SCL1 |

| 1  | 1   | SDA0 to SDA2<br>SCL0 to SCL2 |

| 0  | Х   | SDA_, SCL_, high impedance   |

X = 任意

### 水平/垂直同期レベルシフタ

HSYNC/VSYNCは、VESA規格を満たすレベルシフトおよび駆動能力を提供するためにバッファされています。

### ディスプレイデータチャネルマルチプレクサ

MAX4885Eは、DDC信号の経路を選択するために、電圧クランプされた2個のスイッチを提供します(表3を参照)。各スイッチは、 $V_L$ に供給される電圧よりダイオード降下分低い電圧に信号をクランプします。VESAの $I^2$ C互換信号について電圧クランプを提供するためには、 $V_L$ に+3.3Vを供給してください。電圧クランプが不要な場合、 $V_L$ を $V_C$ Cに接続してください。SDA\_およびSCL\_スイッチは同一で、各スイッチは、SDA\_とSCL\_信号の経路を選択するために使用することができます。

#### ESD保護

出荷および製造時に遭遇する静電気放電から保護するために、全マキシム製のデバイスと同様のESD保護構造がすべてのピンに装備されています。さらに、MAX4885Eは、RGB、HSYNC、VSYNC、SDA\_、およびSCL 出力を、±15kVのヒューマンボディモデル

(HBM)に対して保護しています。「端子説明」の項を参照してください。最大のESD性能を得るために、 $0.1\mu$ F以上のセラミックコンデンサで各 $V_{CC}$ ピンをグランドへバイパスしてください。

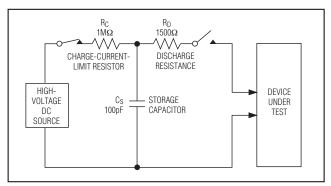

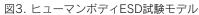

## ヒューマンボディモデル(HBM)

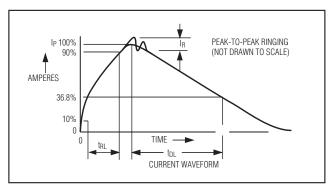

ESD構造の強度を測定するために、複数のESD試験標準が存在します。MAX4885EのESD保護は、ヒューマンボディモデルによって規定されています。図3は、人体との接触に起因するESDイベントのシミュレーションに使用されたモデルを示します。このモデルは、高電圧に充電され、その後1.5kΩの抵抗を通して放電される100pFのストレージコンデンサで構成されています。図4は、ストレージコンデンサが低インピーダンスに放電される時の電流波形を示しています。

### ESD試験条件

ESD性能はさまざまな条件に依存します。試験設定、 方法、および結果を文書化した信頼性リポートについて は、マキシムにお問い合わせください。

## アプリケーション情報

MAX4885Eは、グラフィックスコントローラから2個の標準VGAポートを駆動するための、最低+2.2Vのレベルシフトを提供します。内蔵バッファは、VGA標準のTTLレベルのHSYNCおよびVSYNC信号を駆動します。DDCマルチプレクサは、 $V_L$ からダイオード降下分の電圧に信号をクランプするレベルシフト機能を提供します(「標準動作回路」を参照)。通常動作のためには $V_L$ を+3.3 $V_L$ に、DDC信号の電圧クランプをディセーブルするためには $V_L$ を $V_L$ を $V_L$ とに接続してください。

### 供給電源のデカップリング

$0.1\mu F$ 以上のセラミックコンデンサをデバイスの各 $V_{CC}$ ピンおよび $V_L$ に可能な限り近くに配置し、グランドへバイパスしてください。

## **PCBレイアウト**

MAX4885Eなどの高速なスイッチは、最大の性能を得るために適切なPCBレイアウトを必要とします。高速信号に対してインピーダンス制御されたPCBトレースの長さが整合していて可能な限り短いことを確実にしてください。エクスポーズドパッドを、広いグランドプレーンに接続してください。

### チップ情報

PROCESS: BICMOS

図4. HBM放電電流波形

## ファンクションダイアグラム

| 11 | 111 | 4- | 2% |

|----|-----|----|----|

| •  | • / |    |    |

最新のパッケージ情報とランドパターンは、japan.maxim-ic.com/packagesをご参照ください。

| パッケージタイプ   | パッケージコード | ドキュメントNo.      |

|------------|----------|----------------|

| 24 TQFN-EP | T2444-4  | <u>21-0139</u> |

# マキシム・ジャパン株式会社

〒169-0051東京都新宿区西早稲田3-30-16(ホリゾン1ビル) TEL. (03)3232-6141 FAX. (03)3232-6149

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。マキシムは随時予告なく回路及び仕様を変更する権利を留保します。

10 \_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600