EVALUATION KIT

AVAILABLE

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサー

## 概要

MAX4810/MAX4811/MAX4812集積回路は、低電圧ロジック入力から、高電圧で高周波の、ユニポーラまたはバイポーラのパルスを生成します。これらのデュアルパルサーは、独立したロジック入力、アクティブクランプ内蔵の独立した高電圧パルサー出力、および独立した高電圧電源入力を備えています。

MAX4810/MAX4811/MAX4812は、高電圧出力について9Ωの出力インピーダンス、アクティブクランプについて27Ωのインピーダンスを備えています。高電圧出力は1.3Aの出力電流の供給が保証されています。

すべてのデバイスは、チャネルごとに3つのロジック入力を使用して、正/負のパルスとアクティブクランプを制御します。また、2つの独立したイネーブル入力も備えています。ENをティセーブルすることで、高速電源ランピング中に誤って出力MOSFETがオンにならないようにすることができます。これによって、ランプ時間が高速になり、パルスマード間の遅延を小さくすることができます。低電力シャットダウンモードによって、消費電力を1μA未満に低減します。すべてのデジタル入力はCMOS対応です。

MAX4810は、クランプ出力の過電圧保護を備えており、MAX4811は、パルサー出力とクランプ出力の両方の過電圧保護を備えています。MAX4812は過電圧保護を備えていません。「型番/選択ガイド」を参照してください。

MAX4810/MAX4811/MAX4812は、56ピン(7mm x 7mm)、TQFNエクスポートドパッドパッケージで提供され、民生用温度範囲(0°C ~ +70°C)で仕様が定められています。

## アプリケーション

超音波医療用画像処理

不具合検出

洗浄機器

圧電ドライバ

テスト装置

## 型番/選択ガイド

| PART         | PROTECTED OUTPUTS                                                       | OUTPUT CURRENT (A) | PIN-PACKAGE  |

|--------------|-------------------------------------------------------------------------|--------------------|--------------|

| MAX4810CTN+  | OCP <sub>_</sub> , OCN <sub>_</sub>                                     | 1.3                | 56 TQFN-EP** |

| MAX4811CTN+  | OCP <sub>_</sub> , OCN <sub>_</sub> , OP <sub>_</sub> , ON <sub>_</sub> | 1.3                | 56 TQFN-EP** |

| MAX4812CTN+* | None                                                                    | 1.3                | 56 TQFN-EP** |

注：すべてのデバイスは、0°C ~ +70°Cの動作温度範囲で規定されています。

\*+は鉛フリー/RoHS準拠のパッケージを示します。

\*開発中。入手性に関してはお問い合わせ下さい。

\*\*EP = エクスポートドパッド

警告：MAX4810/MAX4811/MAX4812は高電圧で動作するように設計されています。十分に注意してください。

MAX4810/MAX4811/MAX4812

## 特長

- ♦ 高集積、高電圧、高周波数、ユニポーラ/バイポーラパルサー

- ♦ 出力インピーダンス：9Ω、出力電流：1.3A (min)

- ♦ アクティブクランプ：27Ω

- ♦ パルサーとクランプの過電圧保護(MAX4810/MAX4811)

- ♦ ユニポーラ出力：0~+220V、またはバイポーラ出力：±110V

- ♦ 整合された立上り/立下り時間および整合された伝播遅延

- ♦ CMOS対応ロジック入力

- ♦ 7mm x 7mmの56ピンTQFNパッケージ

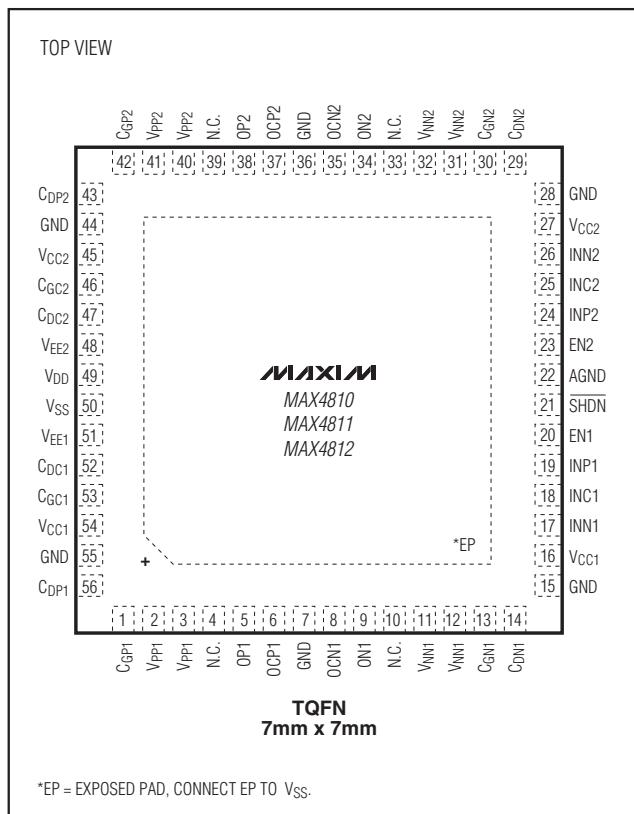

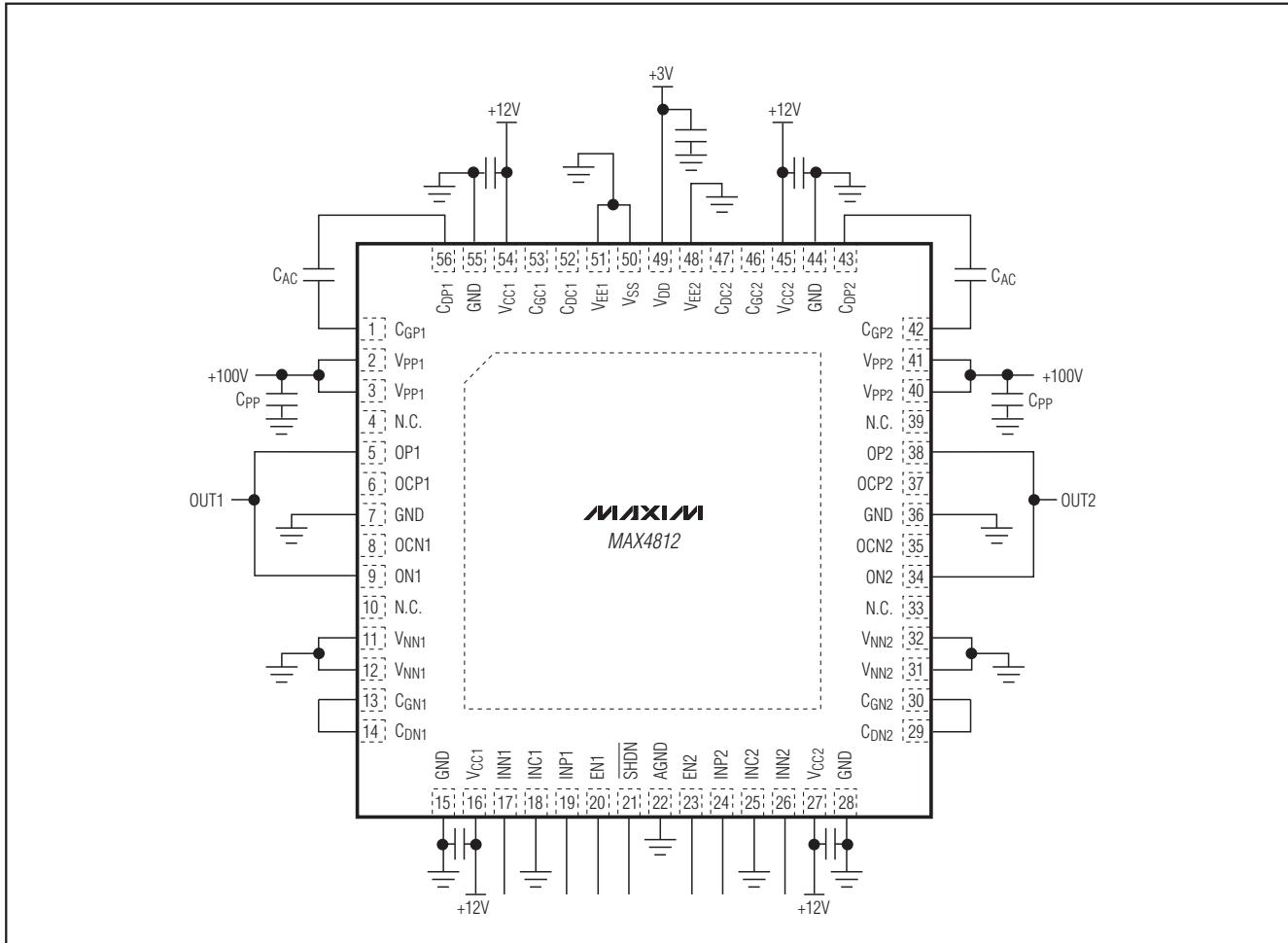

## ピン配置

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサー

## ABSOLUTE MAXIMUM RATINGS

(Voltages referenced to GND.)

|                                                                                             |                                                             |

|---------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| V <sub>DD</sub> Logic Supply Voltage                                                        | -0.3V to +6V                                                |

| V <sub>CC_</sub> Output Driver Positive Supply Voltage                                      | -0.3V to +15V                                               |

| V <sub>EE_</sub> Output Driver Negative Supply Voltage                                      | -15V to +0.3V                                               |

| V <sub>PP_</sub> High Positive Supply Voltage                                               | -0.3V to +230V                                              |

| V <sub>NN_</sub> High Negative Supply Voltage                                               | -230V to +0.3V                                              |

| V <sub>SS</sub> Voltage                                                                     | (V <sub>PP_</sub> - 250V) to V <sub>NN_</sub>               |

| V <sub>PP1</sub> - V <sub>NN1</sub> , V <sub>PP2</sub> - V <sub>NN2</sub> Supply Voltage    | -0.6V to +250V                                              |

| INP <sub>_</sub> , INN <sub>_</sub> , INC <sub>_</sub> , EN <sub>_</sub> , SHDN Logic Input | -0.3V to V <sub>DD</sub> + 0.3V                             |

| OP <sub>_</sub> , OCP <sub>_</sub> , OLN <sub>_</sub> , ON <sub>_</sub>                     | (-0.3V + V <sub>NN_</sub> ) to (-0.3V to V <sub>PP_</sub> ) |

| CGN <sub>_</sub> Voltage                                                                    | (-0.3V + V <sub>NN_</sub> ) to (+15V + V <sub>NN_</sub> )   |

| CGP <sub>_</sub> Voltage                                                                    | (+0.3V + V <sub>PP_</sub> ) to (-15V + V <sub>PP_</sub> )   |

| C <sub>GC</sub> <sub>_</sub> Voltage                                                        | -15V to +15V                                                |

|                                                                |                           |

|----------------------------------------------------------------|---------------------------|

| C <sub>DC_</sub> , C <sub>DP_</sub> , C <sub>DN_</sub> Voltage | -0.3V to V <sub>CC_</sub> |

| Peak Current per Output Channel                                | 3.0A                      |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) (Note 1) |                           |

| 56-Pin TQFN (derate 40mW/°C above +70°C)                       | 3200mW                    |

| Thermal Resistance (Note 2)                                    |                           |

| θ <sub>JA</sub>                                                | 25°C/W                    |

| θ <sub>JC</sub>                                                | 0.8°C/W                   |

| Operating Temperature Range                                    | 0°C to +70°C              |

| Junction Temperature                                           | +150°C                    |

| Storage Temperature Range                                      | -65°C to +150°C           |

| Lead Temperature (soldering, 10s)                              | +300°C                    |

**Note 1:** This specification is based on the thermal characteristic of the package, the maximum junction temperature, and the setup described by JEDEC 51. The maximum power dissipation for the MAX4810/MAX4811/MAX4812 might be limited by the thermal protection included in the device.

**Note 2:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to [www.maxim-ic.com/thermal-tutorial](http://www.maxim-ic.com/thermal-tutorial).

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

(V<sub>DD</sub> = +2.7V to +6V, V<sub>CC\_</sub> = +4.75V to +12.6V, V<sub>EE\_</sub> = -12.6V to -4.75V, V<sub>NN\_</sub> = -200V to 0, V<sub>PP\_</sub> = 0 to (V<sub>NN\_</sub> + 200V), V<sub>SS</sub> ≤ the lower of V<sub>NN1</sub> or V<sub>NN2</sub>, T<sub>A</sub> = T<sub>J</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 3) (See Figures 8, 9, and 10.)

| PARAMETER                                                                                                | SYMBOL           | CONDITIONS                                                                                                                                                                                                                                       | MIN   | TYP                    | MAX   | UNITS |

|----------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------|-------|-------|

| <b>POWER SUPPLY (V<sub>DD</sub>, V<sub>CC_</sub>, V<sub>EE_</sub>, V<sub>PP_</sub>, V<sub>NN_</sub>)</b> |                  |                                                                                                                                                                                                                                                  |       |                        |       |       |

| Logic Supply Voltage                                                                                     | V <sub>DD</sub>  |                                                                                                                                                                                                                                                  | +2.7  | +3                     | +6    | V     |

| Positive Drive Supply Voltage                                                                            | V <sub>CC_</sub> |                                                                                                                                                                                                                                                  | +4.75 | +12                    | +12.6 | V     |

| Negative Drive Supply Voltage                                                                            | V <sub>EE_</sub> |                                                                                                                                                                                                                                                  | -12.6 | -12                    | -4.75 | V     |

| High-Side Supply Voltage                                                                                 | V <sub>PP_</sub> |                                                                                                                                                                                                                                                  | 0     | V <sub>NN_</sub> + 220 |       | V     |

| Low-Side Supply Voltage                                                                                  | V <sub>NN_</sub> |                                                                                                                                                                                                                                                  | -200  | 0                      |       | V     |

| V <sub>PP_</sub> - V <sub>NN_</sub> Supply Voltage                                                       |                  |                                                                                                                                                                                                                                                  | 0     | +220                   |       | V     |

| <b>SUPPLY CURRENT (Single Channel)</b>                                                                   |                  |                                                                                                                                                                                                                                                  |       |                        |       |       |

| V <sub>DD</sub> Supply Current                                                                           | I <sub>DD</sub>  | V <sub>INN_</sub> = V <sub>INP_</sub> = 0, V <sub>SHDN</sub> = 0                                                                                                                                                                                 |       | 1                      |       | µA    |

|                                                                                                          |                  | V <sub>EN_</sub> = V <sub>DD</sub> , V <sub>SHDN</sub> = V <sub>DD</sub> , V <sub>INC_</sub> = 0 or V <sub>DD</sub> , V <sub>INN_</sub> = V <sub>INP_</sub> , f = 5MHz                                                                           | 100   | 200                    |       |       |

| V <sub>CC_</sub> Supply Current                                                                          | I <sub>CC_</sub> | V <sub>SHDN</sub> = 0, CH1 and CH2                                                                                                                                                                                                               |       | 1                      |       | µA    |

|                                                                                                          |                  | V <sub>EN_</sub> = V <sub>DD</sub> , V <sub>SHDN</sub> = V <sub>DD</sub> , CH1 and CH2                                                                                                                                                           | 130   | 200                    |       |       |

|                                                                                                          |                  | V <sub>EN_</sub> = V <sub>DD</sub> , V <sub>SHDN</sub> = V <sub>DD</sub> , V <sub>INC_</sub> = 0 or V <sub>DD</sub> , V <sub>INN_</sub> = V <sub>INP_</sub> , f = 5MHz, V <sub>CC_</sub> = 5V, V <sub>DD</sub> = 3V, only one channel switching  |       | 15                     |       | mA    |

|                                                                                                          |                  | V <sub>EN_</sub> = V <sub>DD</sub> , V <sub>SHDN</sub> = V <sub>DD</sub> , V <sub>INC_</sub> = 0 or V <sub>DD</sub> , V <sub>INN_</sub> = V <sub>INP_</sub> , f = 5MHz, V <sub>CC_</sub> = 12V, V <sub>DD</sub> = 3V, only one channel switching |       | 36                     |       |       |

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサー

**MAX4810/MAX4811/MAX4812**

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{DD} = +2.7V$  to  $+6V$ ,  $V_{CC\_} = +4.75V$  to  $+12.6V$ ,  $V_{EE\_} = -12.6V$  to  $-4.75V$ ,  $V_{NN\_} = -200V$  to  $0V$ ,  $V_{PP\_} = 0$  to ( $V_{NN\_} + 200V$ ),  $V_{SS} \leq$  the lower of  $V_{NN1}$  or  $V_{NN2}$ ,  $T_A = T_J$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ .) (Note 3) (See Figures 8, 9, and 10.)

| PARAMETER                                                                                     | SYMBOL             | CONDITIONS                                                                                                                                                                                                                                                                | MIN                     | TYP                     | MAX | UNITS    |

|-----------------------------------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------|-----|----------|

| V <sub>EE</sub> _ Supply Current                                                              | I <sub>EE</sub> _  | V <sub>SHDN</sub> = 0, CH1 and CH2                                                                                                                                                                                                                                        |                         | 25                      |     | $\mu A$  |

|                                                                                               |                    | V <sub>EN</sub> _ = V <sub>DD</sub> , V <sub>SHDN</sub> = V <sub>DD</sub> , CH1 and CH2                                                                                                                                                                                   |                         | 1                       |     |          |

|                                                                                               |                    | V <sub>EN</sub> _ = V <sub>DD</sub> , V <sub>SHDN</sub> = V <sub>DD</sub> , V <sub>INC</sub> _ = 0 or V <sub>DD</sub> , V <sub>NN</sub> _ = V <sub>INP</sub> _, f = 5MHz, V <sub>EE</sub> _ = -5V, only one channel switching                                             |                         | 200                     |     |          |

|                                                                                               |                    | V <sub>EN</sub> _ = V <sub>DD</sub> , V <sub>SHDN</sub> = V <sub>DD</sub> , V <sub>INC</sub> _ = 0 or V <sub>DD</sub> , V <sub>NN</sub> _ = V <sub>INP</sub> _, f = 5MHz, V <sub>EE</sub> _ = -12V, only one channel switching                                            |                         | 200                     |     |          |

| V <sub>PP</sub> _ Supply Current                                                              | I <sub>PP</sub> _  | V <sub>SHDN</sub> = 0, CH1 and CH2                                                                                                                                                                                                                                        |                         | 1                       |     | $\mu A$  |

|                                                                                               |                    | V <sub>EN</sub> _ = V <sub>DD</sub> , V <sub>SHDN</sub> = V <sub>DD</sub> , CH1 and CH2                                                                                                                                                                                   | 90                      | 160                     |     |          |

|                                                                                               |                    | V <sub>EN</sub> _ = V <sub>DD</sub> , V <sub>SHDN</sub> = V <sub>DD</sub> , V <sub>INC</sub> _ = 0 or V <sub>DD</sub> , V <sub>NN</sub> _ = V <sub>INP</sub> _, f = 5MHz, V <sub>PP</sub> _ = +5V, V <sub>NN</sub> _ = -5V, no load, only one channel switching           |                         | 9                       |     |          |

|                                                                                               |                    | V <sub>EN</sub> _ = V <sub>DD</sub> , V <sub>SHDN</sub> = V <sub>DD</sub> , V <sub>INC</sub> _ = 0 or V <sub>DD</sub> , V <sub>PP</sub> _ = +80V, V <sub>NN</sub> _ = -80V, pulse repetition frequency = 10kHz, f = 10MHz, 4 periods, no load, only one channel switching |                         | 0.6                     |     |          |

| V <sub>NN</sub> _ Supply Current                                                              | I <sub>NN</sub> _  | V <sub>SHDN</sub> = 0, CH1 and CH2                                                                                                                                                                                                                                        |                         | 1                       |     | $\mu A$  |

|                                                                                               |                    | V <sub>EN</sub> _ = V <sub>DD</sub> , V <sub>SHDN</sub> = V <sub>DD</sub> , CH1 and CH2                                                                                                                                                                                   | 40                      | 80                      |     |          |

|                                                                                               |                    | V <sub>EN</sub> _ = V <sub>DD</sub> , V <sub>SHDN</sub> = V <sub>DD</sub> , V <sub>INC</sub> _ = 0 or V <sub>DD</sub> , V <sub>NN</sub> _ = V <sub>INP</sub> _, f = 5MHz, V <sub>NN</sub> _ = -5V, V <sub>PP</sub> _ = +5V, no load, only one channel switching           |                         | 9                       |     |          |

|                                                                                               |                    | V <sub>EN</sub> _ = V <sub>DD</sub> , V <sub>SHDN</sub> = V <sub>DD</sub> , V <sub>INC</sub> _ = 0 or V <sub>DD</sub> , V <sub>PP</sub> _ = +80V, V <sub>NN</sub> _ = -80V, pulse repetition frequency = 10kHz, f = 10MHz, 4 periods, no load, only one channel switching |                         | 0.6                     |     |          |

| <b>LOGIC INPUTS (EN<sub>_</sub>, SHDN, INN<sub>_</sub>, INP<sub>_</sub>, INC<sub>_</sub>)</b> |                    |                                                                                                                                                                                                                                                                           |                         |                         |     |          |

| Low-Level Input Voltage                                                                       | V <sub>IL</sub>    |                                                                                                                                                                                                                                                                           |                         | 0.25 x V <sub>DD</sub>  |     | V        |

| High-Level Input Voltage                                                                      | V <sub>IH</sub>    |                                                                                                                                                                                                                                                                           | 0.75 x V <sub>DD</sub>  |                         |     | V        |

| Logic-Input Capacitance                                                                       | C <sub>IN</sub>    |                                                                                                                                                                                                                                                                           | 5                       |                         |     | pF       |

| Logic-Input Leakage                                                                           | I <sub>IN</sub>    | V <sub>IN</sub> = 0 or V <sub>DD</sub>                                                                                                                                                                                                                                    |                         | ±1                      |     | $\mu A$  |

| <b>OUTPUT (OUT<sub>_</sub>)</b>                                                               |                    |                                                                                                                                                                                                                                                                           |                         |                         |     |          |

| OUT <sub>_</sub> Output-Voltage Range                                                         | V <sub>OUT</sub> _ | No load at OUT <sub>_</sub>                                                                                                                                                                                                                                               | V <sub>NN</sub> _       | V <sub>PP</sub> _       |     | V        |

|                                                                                               |                    | Unprotected outputs (see the Ordering Information/Selector Guide), 100mA load                                                                                                                                                                                             | V <sub>NN</sub> _ + 1.5 | V <sub>PP</sub> _ - 1.5 |     |          |

|                                                                                               |                    | Protected outputs (see the Ordering Information/Selector Guide), 100mA load                                                                                                                                                                                               | V <sub>NN</sub> _ + 2.5 | V <sub>PP</sub> _ - 2.5 |     |          |

| Low-Side Small-Signal Output Impedance                                                        | R <sub>OLS</sub>   | I <sub>OP</sub> _ = -100mA, V <sub>CC</sub> _ = +12V ±5%, DC-coupled                                                                                                                                                                                                      | 9                       | 17                      |     | $\Omega$ |

|                                                                                               |                    | I <sub>OP</sub> _ = -100mA, V <sub>CC</sub> _ = +5V ±5%, DC-coupled                                                                                                                                                                                                       | 9.5                     | 18                      |     |          |

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサー

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{DD} = +2.7\text{V}$  to  $+6\text{V}$ ,  $V_{CC\_} = +4.75\text{V}$  to  $+12.6\text{V}$ ,  $V_{EE\_} = -12.6\text{V}$  to  $-4.75\text{V}$ ,  $V_{NN\_} = -200\text{V}$  to  $0\text{V}$ ,  $V_{PP\_} = 0\text{V}$  to ( $V_{NN\_} + 200\text{V}$ ),  $V_{SS} \leq$  the lower of  $V_{NN1}$  or  $V_{NN2}$ ,  $T_A = T_J$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ\text{C}$ .) (Note 3) (See Figures 8, 9, and 10.)

| PARAMETER                                                                                                              | SYMBOL     | CONDITIONS                                                                                                                                             | MIN     | TYP | MAX | UNITS         |

|------------------------------------------------------------------------------------------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|-----|---------------|

| High-Side Small-Signal Output Impedance                                                                                | RoHS       | $I_{OP\_} = -100\text{mA}$ , $V_{CC\_} = +12\text{V} \pm 5\%$ , DC-coupled                                                                             | 10.5    | 17  |     | $\Omega$      |

|                                                                                                                        |            | $I_{OP\_} = -100\text{mA}$ , $V_{CC\_} = +5\text{V} \pm 5\%$ , DC-coupled                                                                              | 12      | 18  |     |               |

| Low-Side Output Current                                                                                                | $I_{OL}$   | $V_{CC\_} = +12\text{V} \pm 5\%$ , $V_{OUT\_} - V_{NN\_} = 100\text{V}$                                                                                | 1.3     |     |     | A             |

| High-Side Output Current                                                                                               | $I_{OH}$   | $V_{CC\_} = +12\text{V} \pm 5\%$ , $V_{OUT\_} - V_{PP\_} = 100\text{V}$                                                                                | 1.3     |     |     | A             |

| Off-Output Capacitance                                                                                                 | Co(OFF)    | OP <sub>_</sub> , ON <sub>_</sub> , OCP <sub>_</sub> and OCN <sub>_</sub> connected together,<br>$V_{PP\_} = +100\text{V}$ , $V_{NN\_} = -100\text{V}$ | MAX4810 | 45  |     | pF            |

|                                                                                                                        |            |                                                                                                                                                        | MAX4811 | 75  |     |               |

| Off-Output Leakage Current                                                                                             | $I_{LK}$   | $V_{NN\_} = -100\text{V}$ , $V_{PP\_} = 100\text{V}$ , $EN\_ = 0$ ,<br>$OUT = -100\text{V}$ to $+100\text{V}$                                          | -1      | +1  |     | $\mu\text{A}$ |

| Low-Side Signal-Clamp Output Impedance                                                                                 | RCLS       | $I_{OCN\_} = -100\text{mA}$ , DC-coupled, $V_{CC\_} = +12\text{V} \pm 5\%$ ,<br>$V_{EE\_} = -V_{CC\_}$                                                 |         | 22  | 50  | $\Omega$      |

|                                                                                                                        |            | $I_{OCN\_} = -100\text{mA}$ , DC-coupled, $V_{CC\_} = +5\text{V} \pm 5\%$ ,<br>$V_{EE\_} = -V_{CC\_}$                                                  |         | 24  | 65  |               |

| High-Side Signal-Clamp Output Impedance                                                                                | RCHS       | $I_{OCP\_} = -100\text{mA}$ , DC-coupled, $V_{CC\_} = +12\text{V} \pm 5\%$ ,<br>$V_{EE\_} = -V_{CC\_}$                                                 |         | 28  | 50  | $\Omega$      |

|                                                                                                                        |            | $I_{OCP\_} = -100\text{mA}$ , DC-coupled, $V_{CC\_} = +5\text{V} \pm 5\%$ ,<br>$V_{EE\_} = -V_{CC\_}$                                                  |         | 38  | 65  |               |

| Low-Side Gate Short Impedance                                                                                          | RLSH       | $V_{CC\_} = +12\text{V} \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$ , $I_{CGN} = 10\text{mA}$ ,<br>$EN\_ = 0$                                                    |         |     | 100 | $\Omega$      |

|                                                                                                                        |            | $V_{CC\_} = +12\text{V} \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$ , $I_{CGN} = 10\text{mA}$ ,<br>$EN\_ = V_{DD}$                                               | 5       | 7.5 | 10  | k $\Omega$    |

| High-Side Gate Short Impedance                                                                                         | RHSH       | $V_{CC\_} = +12\text{V} \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$ , $I_{CGN} = 10\text{mA}$ ,<br>$EN\_ = 0$                                                    |         |     | 100 | $\Omega$      |

|                                                                                                                        |            | $V_{CC\_} = +12\text{V} \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$ , $I_{CGN} = 10\text{mA}$ ,<br>$EN\_ = V_{DD}$                                               | 5       | 7.5 | 10  | k $\Omega$    |

| <b>THERMAL SHUTDOWN</b>                                                                                                |            |                                                                                                                                                        |         |     |     |               |

| Thermal Shutdown                                                                                                       | $T_{SHDN}$ | Junction temperature rising                                                                                                                            |         | 150 |     | °C            |

| Thermal-Shutdown Hysteresis                                                                                            |            |                                                                                                                                                        |         | 20  |     | °C            |

| <b>DYNAMIC CHARACTERISTICS (<math>R_L = 100\Omega</math>, <math>C_L = 100\text{pF}</math>, unless otherwise noted)</b> |            |                                                                                                                                                        |         |     |     |               |

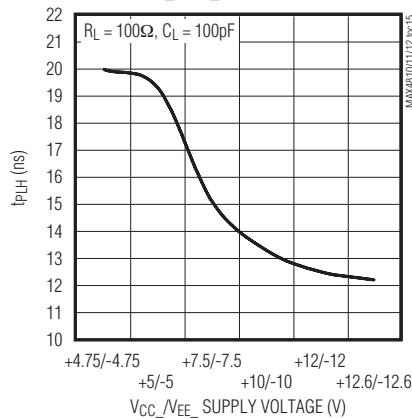

| Logic Input to Output Rise Propagation Delay                                                                           | $t_{PLH}$  | $V_{CC\_} = +12\text{V}$ , $V_{PP\_} = +5\text{V}$ , $V_{NN\_} = -5\text{V}$ , Figure 4                                                                |         | 15  |     | ns            |

| Logic Input to Output Fall Propagation Delay                                                                           | $t_{PHL}$  | $V_{CC\_} = +12\text{V}$ , $V_{PP\_} = +5\text{V}$ , $V_{NN\_} = -5\text{V}$ , Figure 4                                                                |         | 15  |     | ns            |

| Logic Input to Output Rise Propagation Delay                                                                           | $t_{POH}$  | $V_{CC\_} = +12\text{V}$ , $V_{PP\_} = +5\text{V}$ , $V_{NN\_} = -5\text{V}$ , Figure 4                                                                |         | 15  |     | ns            |

| Logic Input to Output Fall Propagation Delay                                                                           | $t_{POL}$  | $V_{CC\_} = +12\text{V}$ , $V_{PP\_} = +5\text{V}$ , $V_{NN\_} = -5\text{V}$ , Figure 4                                                                |         | 15  |     | ns            |

| Logic Input to Output-Rise Propagation Delay Clamp                                                                     | $t_{PLO}$  | $V_{CC\_} = +12\text{V}$ , $V_{PP\_} = +5\text{V}$ , $V_{NN\_} = -5\text{V}$ , Figure 4                                                                |         | 15  |     | ns            |

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサー

**MAX4810/MAX4811/MAX4812**

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{DD} = +2.7V$  to  $+6V$ ,  $V_{CC\_} = +4.75V$  to  $+12.6V$ ,  $V_{EE\_} = -12.6V$  to  $-4.75V$ ,  $V_{NN\_} = -200V$  to  $0V$ ,  $V_{PP\_} = 0$  to ( $V_{NN\_} + 200V$ ),  $V_{SS} \leq$  the lower of  $V_{NN1}$  or  $V_{NN2}$ ,  $T_A = T_J = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ .) (Note 3) (See Figures 8, 9, and 10.)

| PARAMETER                                          | SYMBOL       | CONDITIONS                                                                                              | MIN | TYP   | MAX | UNITS |

|----------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------|-----|-------|-----|-------|

| Logic Input to Output-Fall Propagation Delay Clamp | $t_{PHO}$    | $V_{CC\_} = +12V$ , $V_{PP\_} = +5V$ , $V_{NN\_} = -5V$ , Figure 4                                      |     | 15    |     | ns    |

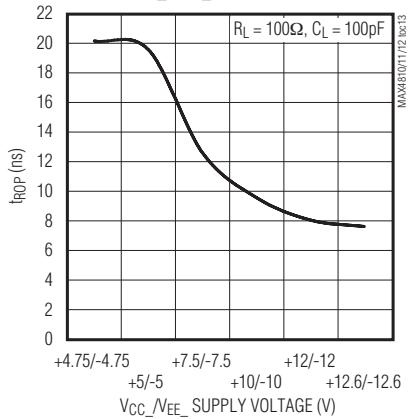

| OUT_ Rise Time (GND to $V_{PP\_}$ )                | $t_{ROP}$    | $V_{PP\_} = +100V$ , $V_{NN\_} = -100V$ , $V_{CC\_} = +12V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$ , Figure 4 |     | 9     | 20  | ns    |

| OUT_ Rise Time ( $V_{NN\_}$ to GND)                | $t_{RNO}$    | $V_{PP\_} = +100V$ , $V_{NN\_} = -100V$ , $V_{CC\_} = +12V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$ , Figure 4 |     | 17    | 35  | ns    |

| OUT_ Rise Time ( $V_{NN\_}$ to $V_{PP\_}$ )        | $t_{RNP}$    | $V_{PP\_} = +100V$ , $V_{NN\_} = -100V$ , $V_{CC\_} = +12V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$ , Figure 4 |     | 10.5  | 35  | ns    |

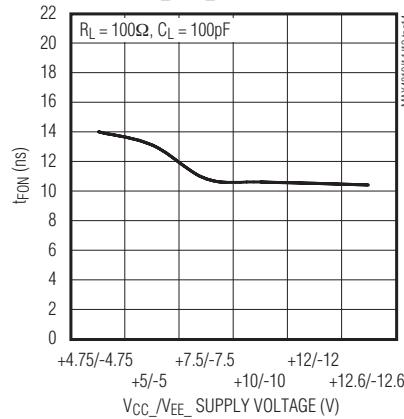

| OUT_ Fall Time (GND to $V_{NN\_}$ )                | $t_{FON}$    | $V_{PP\_} = +100V$ , $V_{NN\_} = -100V$ , $V_{CC\_} = +12V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$ , Figure 4 |     | 9     | 20  | ns    |

| OUT_ Fall Time ( $V_{PP\_}$ to GND)                | $t_{FP0}$    | $V_{PP\_} = +100V$ , $V_{NN\_} = -100V$ , $V_{CC\_} = +12V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$ , Figure 4 |     | 17    | 35  | ns    |

| OUT_ Fall Time ( $V_{PP\_}$ to $V_{NN\_}$ )        | $t_{FPN}$    | $V_{PP\_} = +100V$ , $V_{NN\_} = -100V$ , $V_{CC\_} = +12V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$ , Figure 4 |     | 10.5  | 35  | ns    |

| OUT Enable Time from EN (Figure 5)                 | $t_{EN}$     | $V_{CC\_} = +12V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$                                                      |     | 100   |     | ns    |

|                                                    |              | $V_{CC\_} = +5V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$                                                       |     | 150   |     |       |

| OUT Disable Time from EN (Figure 5)                | $t_{DI}$     | $V_{CC\_} = +12V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$                                                      |     | 100   |     | ns    |

|                                                    |              | $V_{CC\_} = +5V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$                                                       |     | 150   |     |       |

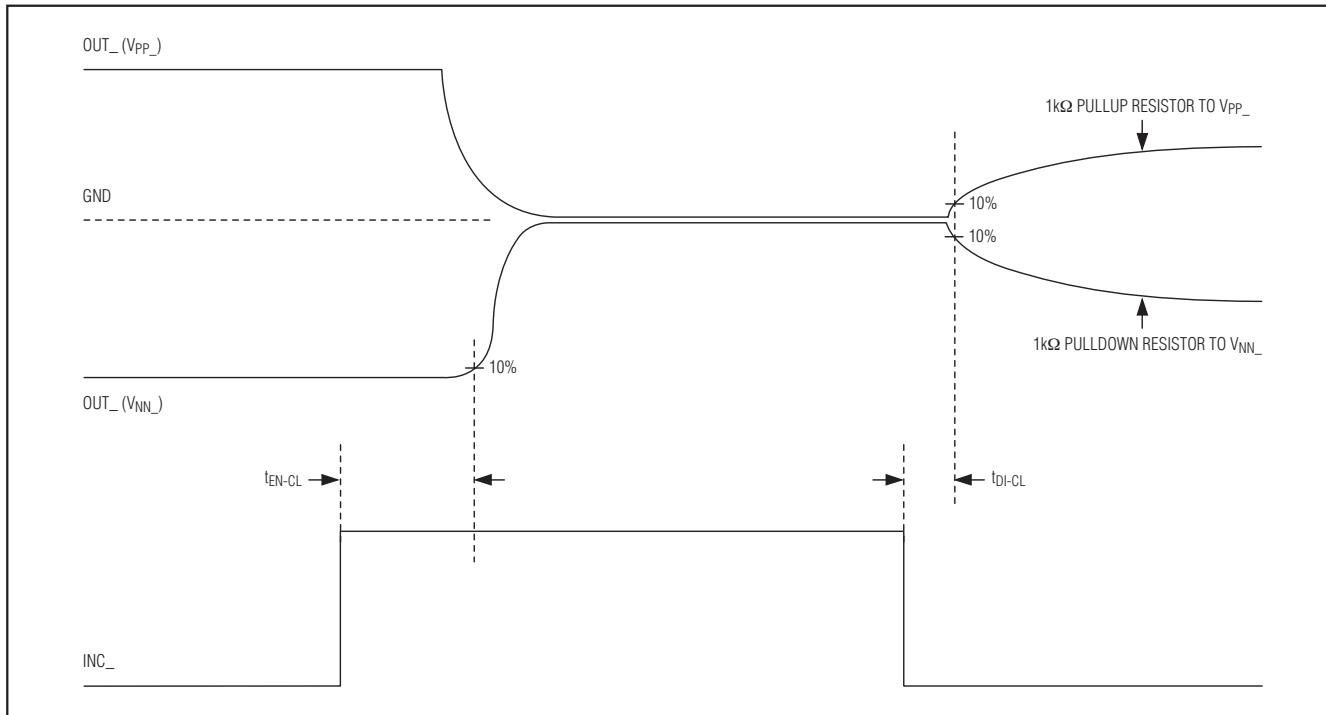

| Clamp Enable Time from INC (Figure 6)              | $t_{EN-CL}$  | $V_{CC\_} = +12V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$                                                      |     | 150   |     | ns    |

|                                                    |              | $V_{CC\_} = +5V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$                                                       |     | 180   |     |       |

| Clamp Disable Time from INC (Figure 6)             | $t_{DI-CL}$  | $V_{CC\_} = +12V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$                                                      |     | 150   |     | ns    |

|                                                    |              | $V_{CC\_} = +5V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$                                                       |     | 150   |     |       |

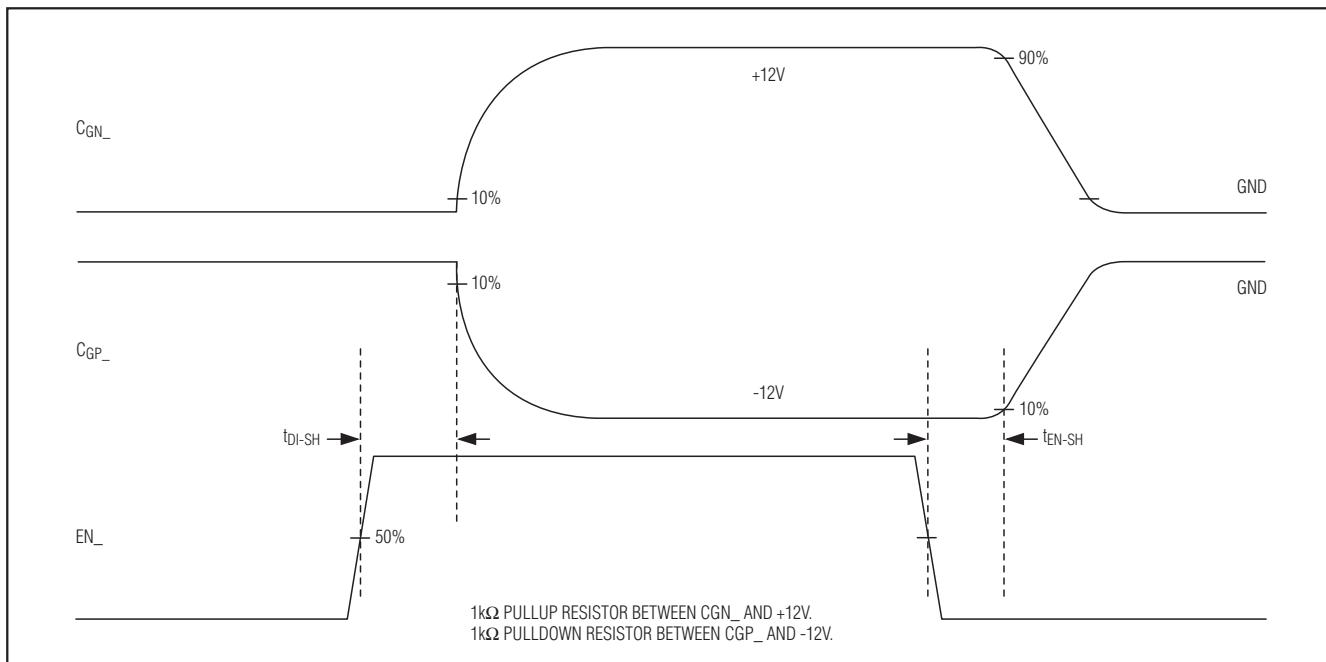

| Short Enable Time from EN (Figure 7)               | $t_{EN\_SH}$ | $V_{PP\_} = 12V$ , $V_{NN\_} = 0$ , $V_{CC\_} = +12V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$                  |     | 1000  |     | ns    |

|                                                    |              | $V_{PP\_} = 5V$ , $V_{NN\_} = 0$ , $V_{CC\_} = +5V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$                    |     | 1000  |     |       |

| Short Disable Time from EN (Figure 7)              | $t_{DI\_SH}$ | $V_{PP\_} = 12V$ , $V_{NN\_} = 0$ , $V_{CC\_} = +12V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$                  |     | 250   |     | ns    |

|                                                    |              | $V_{PP\_} = 5V$ , $V_{NN\_} = 0$ , $V_{CC\_} = +5V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$                    |     | 250   |     |       |

| INP_ to INN_ Overlap Tolerance                     |              |                                                                                                         |     | $I_3$ |     | ns    |

| Crosstalk                                          |              | $V_{PP\_} = V_{CC\_} = +5V$ , $V_{NN\_} = V_{EE\_} = -5V$ , $f = 5MHz$                                  |     | 69    |     | dB    |

| 2nd Harmonic Distortion                            | 2HD          | $V_{PP\_} = V_{NN\_} = 100V$ , $f_{OUT} = 5MHz$ , $V_{CC\_} = 12V$                                      |     | -48   |     | dB    |

| RMS Output Jitter                                  | $t_J$        | $V_{CC\_} = 12V$                                                                                        |     | 9     |     | ps    |

**Note 3:** Specifications are guaranteed for the stated global conditions, unless otherwise noted and are 100% production tested at  $T_A = +25^\circ C$  and  $T_A = +70^\circ C$ . Specifications at  $T_A = 0^\circ C$  are guaranteed by design.

**Note 4:** 100% production tested at  $T_A = +25^\circ C$ . Specifications over temperature are guaranteed by design.

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサー

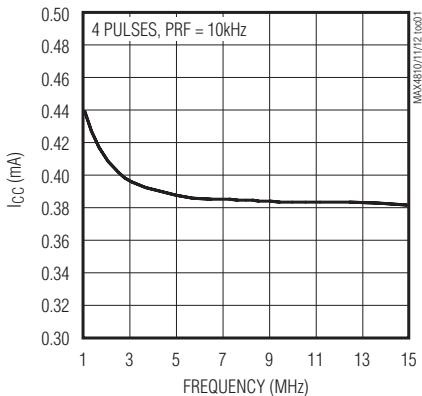

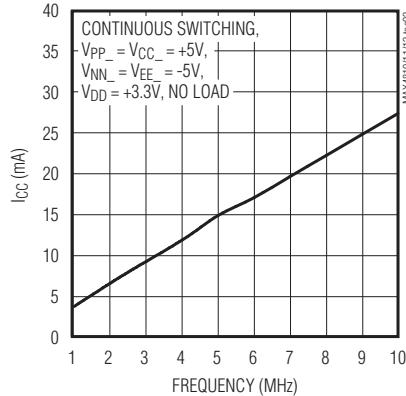

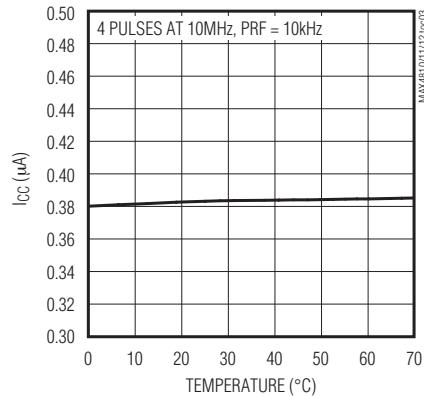

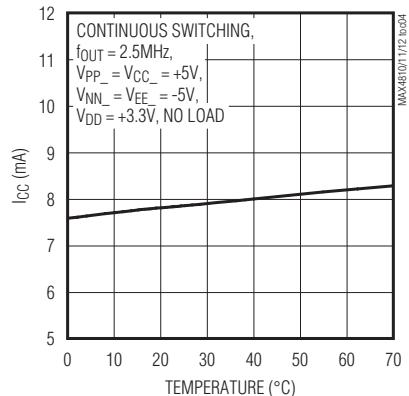

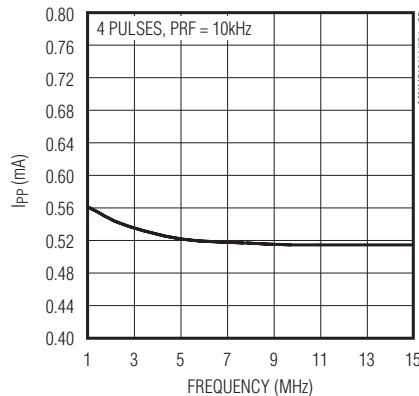

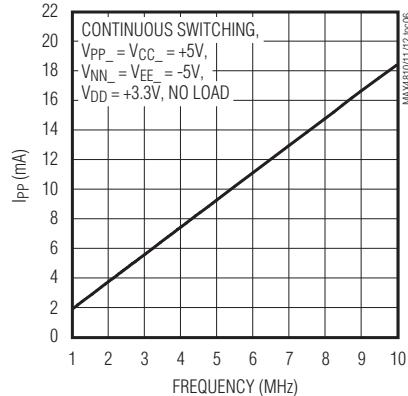

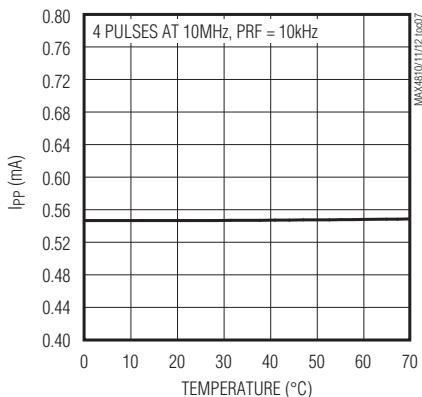

## 標準動作特性

( $V_{DD} = +3.3V$ ,  $V_{CC\_} = +12V$ ,  $V_{EE\_} = -12V$ ,  $V_{SS} = -100V$ ,  $V_{PP\_} = +100V$ ,  $V_{NN\_} = -100V$ ,  $f_{OUT} = 5MHz$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

**I<sub>CC</sub> vs. OUTPUT FREQUENCY**

**I<sub>CC</sub> vs. OUTPUT FREQUENCY**

**I<sub>CC</sub> vs. TEMPERATURE**

**I<sub>CC</sub> vs. TEMPERATURE**

**I<sub>PP</sub> vs. OUTPUT FREQUENCY**

**I<sub>PP</sub> vs. OUTPUT FREQUENCY**

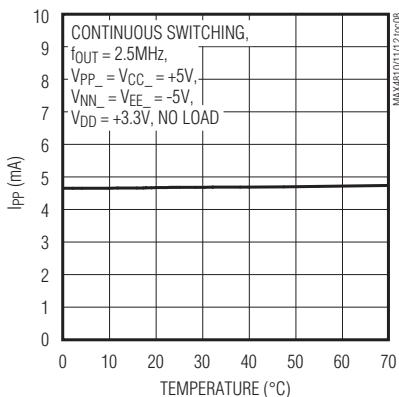

**I<sub>PP</sub> vs. TEMPERATURE**

**I<sub>PP</sub> vs. TEMPERATURE**

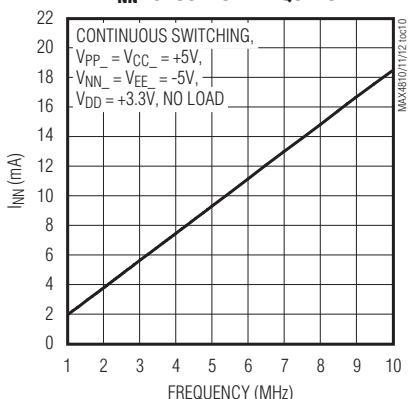

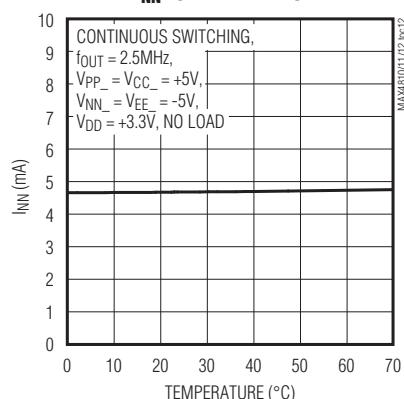

**I<sub>NN</sub> vs. OUTPUT FREQUENCY**

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサー

## 標準動作特性(続き)

( $V_{DD} = +3.3V$ ,  $V_{CC\_} = +12V$ ,  $V_{EE\_} = -12V$ ,  $V_{SS} = -100V$ ,  $V_{PP\_} = +100V$ ,  $V_{NN\_} = -100V$ ,  $f_{OUT} = 5MHz$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

**MAX4810/MAX4811/MAX4812**

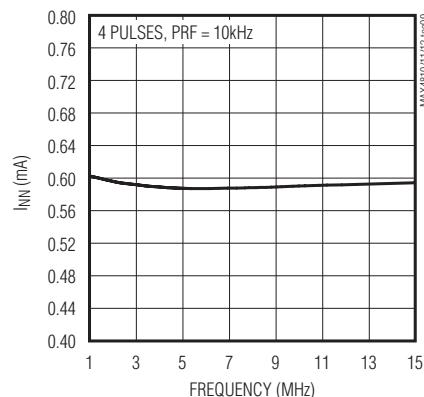

### $I_{INN}$ vs. OUTPUT FREQUENCY

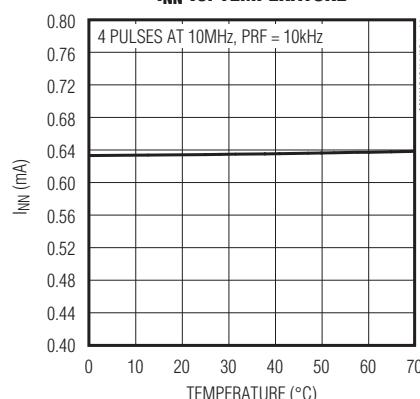

### $I_{INN}$ vs. TEMPERATURE

### $I_{INN}$ vs. TEMPERATURE

### OUT RISE TIME (GND TO $V_{PP\_}$ ) vs. $V_{CC\_}/V_{EE\_}$ SUPPLY VOLTAGE

### OUT FALL TIME (GND TO $V_{NN\_}$ ) vs. $V_{CC\_}/V_{EE\_}$ SUPPLY VOLTAGE

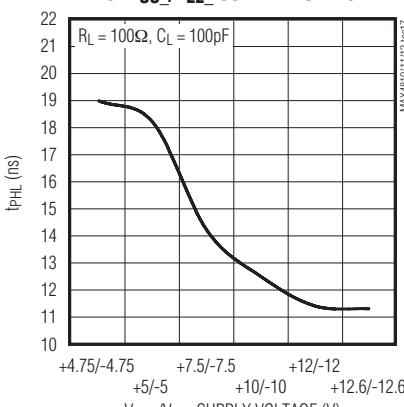

### INP-TO-OUT RISE PROPAGATION DELAY vs. $V_{CC\_}/V_{EE\_}$ SUPPLY VOLTAGE

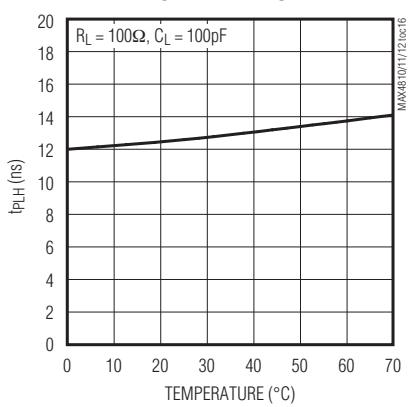

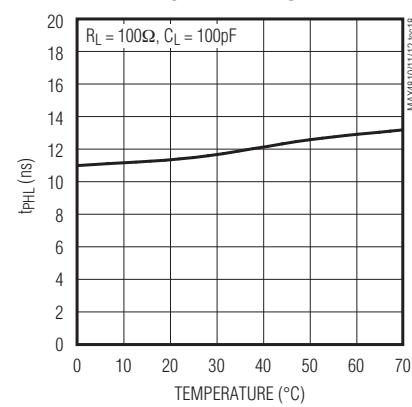

### INP-TO-OUT RISE PROPAGATION DELAY vs. TEMPERATURE

### INP-TO-OUT FALL PROPAGATION DELAY vs. $V_{CC\_}/V_{EE\_}$ SUPPLY VOLTAGE

### INP-TO-OUT FALL PROPAGATION DELAY vs. TEMPERATURE

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサー

## 端子説明

| 端子                       | 名称               | 機能                                                                                                                       |

|--------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------|

| 1                        | C <sub>GP1</sub> | チャネル1のハイサイドゲート入力。C <sub>DP1</sub> とC <sub>GP1</sub> の間で、できる限りデバイス近くに1nF～10nFのコンデンサを接続してください。                             |

| 2, 3                     | V <sub>PP1</sub> | チャネル1の正のハイサイド電源電圧入力。できる限りデバイス近くにV <sub>PP1</sub> を0.1μFでGNDにバイパスしてください。「電源およびバイパス」の項を参照してください。出力に応じてバイパスの追加が必要な場合があります。  |

| 4, 10, 33,<br>39         | N.C.             | 接続なし。内部で接続されていません。                                                                                                       |

| 5                        | OP1              | チャネル1のハイサイドドレイン出力                                                                                                        |

| 6                        | OCP1             | チャネル1のハイサイドクランプ出力                                                                                                        |

| 7, 15, 28,<br>36, 44, 55 | GND              | グランド                                                                                                                     |

| 8                        | OCN1             | チャネル1のローサイドクランプ出力                                                                                                        |

| 9                        | ON1              | チャネル1のローサイドドレイン出力                                                                                                        |

| 11, 12                   | V <sub>NN1</sub> | チャネル1の負のローサイド電源電圧入力。できる限りデバイス近くに、V <sub>NN1</sub> を0.1μFでGNDにバイパスしてください。「電源およびバイパス」の項を参照してください。出力に応じてバイパスの追加が必要な場合があります。 |

| 13                       | C <sub>GN1</sub> | チャネル1のローサイドゲート入力。C <sub>DN1</sub> とC <sub>GN1</sub> の間で、できる限りデバイス近くに1nF～10nFのコンデンサを接続してください。                             |

| 14                       | C <sub>DN1</sub> | チャネル1のローサイドドライバ出力。C <sub>DN1</sub> とC <sub>GN1</sub> の間で、できる限りデバイス近くに1nF～10nFのコンデンサを接続してください。                            |

| 16, 54                   | V <sub>CC1</sub> | チャネル1のゲートドライブ電源電圧入力。できる限りデバイス近くにV <sub>CC1</sub> を0.1μFでGNDにバイパスしてください。「電源およびバイパス」の項を参照してください。出力に応じてバイパスの追加が必要な場合があります。  |

| 17                       | INN1             | チャネル1のローサイドロジック入力(表1)                                                                                                    |

| 18                       | INC1             | チャネル1のクランプロジック入力。クランプOCP1とOCN1はINC1がハイのとき、およびINP1とINN1がローのときにオンになります(表1を参照)。                                             |

| 19                       | INP1             | チャネル1のハイサイドロジック入力(表1)                                                                                                    |

| 20                       | EN1              | チャネル1のイネーブルロジック入力。OP1とON1をイネーブルするには、EN1をハイに駆動してください。ゲート-ソース間の短絡をオンにするには、EN1をローにプルダウンしてください(表1を参照)。                       |

| 21                       | SHDN             | シャットダウンロジック入力(表1)                                                                                                        |

| 22                       | AGND             | アナロググランド。コモンGNDに接続する必要があります。                                                                                             |

| 23                       | EN2              | チャネル2のイネーブルロジック入力。OP2とON2をイネーブルするには、EN2をハイに駆動してください。ゲート-ソース間の短絡をオンにするには、EN2をローにプルダウンしてください。表1を参照。                        |

| 24                       | INP2             | チャネル2のハイサイドロジック入力(表1)                                                                                                    |

| 25                       | INC2             | チャネル2のクランプロジック入力。クランプOCP2とOCN2はINC2がハイのとき、およびINP2とINN2がローのときにオンになります。表1を参照。                                              |

| 26                       | INN2             | チャネル2のローサイドロジック入力(表1)                                                                                                    |

| 27, 45                   | V <sub>CC2</sub> | チャネル2のゲートドライブ電源電圧入力。できる限りデバイス近くにV <sub>CC2</sub> を0.1μFでGNDにバイパスしてください。「電源およびバイパス」の項を参照してください。出力に応じてバイパスの追加が必要な場合があります。  |

| 29                       | C <sub>DN2</sub> | チャネル2のローサイドドライバ出力。C <sub>DN2</sub> とC <sub>GN2</sub> の間で、できる限りデバイス近くに1nF～10nFのコンデンサを接続してください。                            |

| 30                       | C <sub>GN2</sub> | チャネル2のローサイドゲート入力。C <sub>DN2</sub> とC <sub>GN2</sub> の間で、できる限りデバイス近くに1nF～10nFのコンデンサを接続してください。                             |

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサー

## 端子説明(続き)

| 端子     | 名称               | 機能                                                                                                                                                                              |

|--------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31, 32 | V <sub>NN2</sub> | チャネル2の負のローサイド電源電圧入力。できる限りデバイス近くにV <sub>NN2</sub> を0.1μFでGNDにバイパスしてください。「電源およびバイパス」の項を参照してください。出力に応じてバイパスの追加が必要な場合があります。                                                         |

| 34     | ON2              | チャネル2のローサイドドレイン出力                                                                                                                                                               |

| 35     | OCN2             | チャネル2のローサイドクランプ出力                                                                                                                                                               |

| 37     | OCP2             | チャネル2のハイサイドクランプ出力                                                                                                                                                               |

| 38     | OP2              | チャネル2のハイサイドドレイン出力                                                                                                                                                               |

| 40, 41 | V <sub>PP2</sub> | チャネル2のハイサイド正電源電圧入力。できる限りデバイス近くにV <sub>PP2</sub> を0.1μFでGNDにバイパスしてください。「電源およびバイパス」の項を参照してください。出力に応じてバイパスの追加が必要な場合があります。                                                          |

| 42     | C <sub>GP2</sub> | チャネル2のハイサイドゲート入力。C <sub>DP2</sub> とC <sub>GP2</sub> の間で、できる限りデバイス近くに1nF~10nFのコンデンサを接続してください。                                                                                    |

| 43     | C <sub>DP2</sub> | チャネル2のハイサイドドライバ出力。C <sub>DP2</sub> とC <sub>GP2</sub> の間で、できる限りデバイス近くに1nF~10nFのコンデンサを接続してください。                                                                                   |

| 46     | C <sub>GC2</sub> | チャネル2のハイサイドクランプゲート入力。C <sub>DC2</sub> とC <sub>GC2</sub> の間で、できる限りデバイス近くに1nF~10nFのコンデンサを接続してください。                                                                                |

| 47     | C <sub>DC2</sub> | チャネル2のハイサイドクランプドライバ出力。C <sub>DC2</sub> とC <sub>GC2</sub> の間で、できる限りデバイス近くに1nF~10nFのコンデンサを接続してください。                                                                               |

| 48     | V <sub>EE2</sub> | チャネル2の負電源入力。 V <sub>EE2</sub>   ≤ V <sub>CC2</sub> 。OCP2クランプのためのゲートドライブ電源電圧。できる限りデバイス近くにV <sub>EE2</sub> を0.1μFでGNDにバイパスしてください。「電源およびバイパス」の項を参照してください。出力に応じてバイパスの追加が必要な場合があります。 |

| 49     | V <sub>DD</sub>  | ロジックの電源電圧入力。できる限りデバイス近くにV <sub>DD</sub> を0.1μFでGNDにバイパスしてください。「電源およびバイパス」の項を参照してください。出力に応じてバイパスの追加が必要な場合があります。                                                                  |

| 50     | V <sub>SS</sub>  | サブストレートの電圧。V <sub>SS</sub> は、V <sub>NN1</sub> またはV <sub>NN2</sub> と同じか、またはそれより低い電圧に接続してください。                                                                                    |

| 51     | V <sub>EE1</sub> | チャネル1の負電源入力。 V <sub>EE1</sub>   ≤ V <sub>CC1</sub> 。OCP1クランプのためのゲートドライブ電源電圧。できる限りデバイス近くにV <sub>EE1</sub> を0.1μFでGNDにバイパスしてください。「電源およびバイパス」の項を参照してください。出力に応じてバイパスの追加が必要な場合があります。 |

| 52     | C <sub>DC1</sub> | チャネル1のハイサイドクランプドライバ出力。C <sub>DC1</sub> とC <sub>GC1</sub> の間で、できる限りデバイス近くに1nF~10nFのコンデンサを接続してください。                                                                               |

| 53     | C <sub>GC1</sub> | チャネル1のハイサイドクランプゲート入力。C <sub>DC1</sub> とC <sub>GC1</sub> の間で、できる限りデバイス近くに1nF~10nFのコンデンサを接続してください。                                                                                |

| 56     | C <sub>DP1</sub> | チャネル1のハイサイドドライバ出力。C <sub>DP1</sub> とC <sub>GP1</sub> の間で、できる限りデバイス近くに1nF~10nFのコンデンサを接続してください。                                                                                   |

| —      | EP               | エクスポートドパッド。エクスポートドパッド(EP)は、V <sub>SS</sub> に接続する必要があります。エクスポートドパッドをデバイスの唯一のV <sub>SS</sub> 接続として使用しないでください。                                                                     |

## 詳細

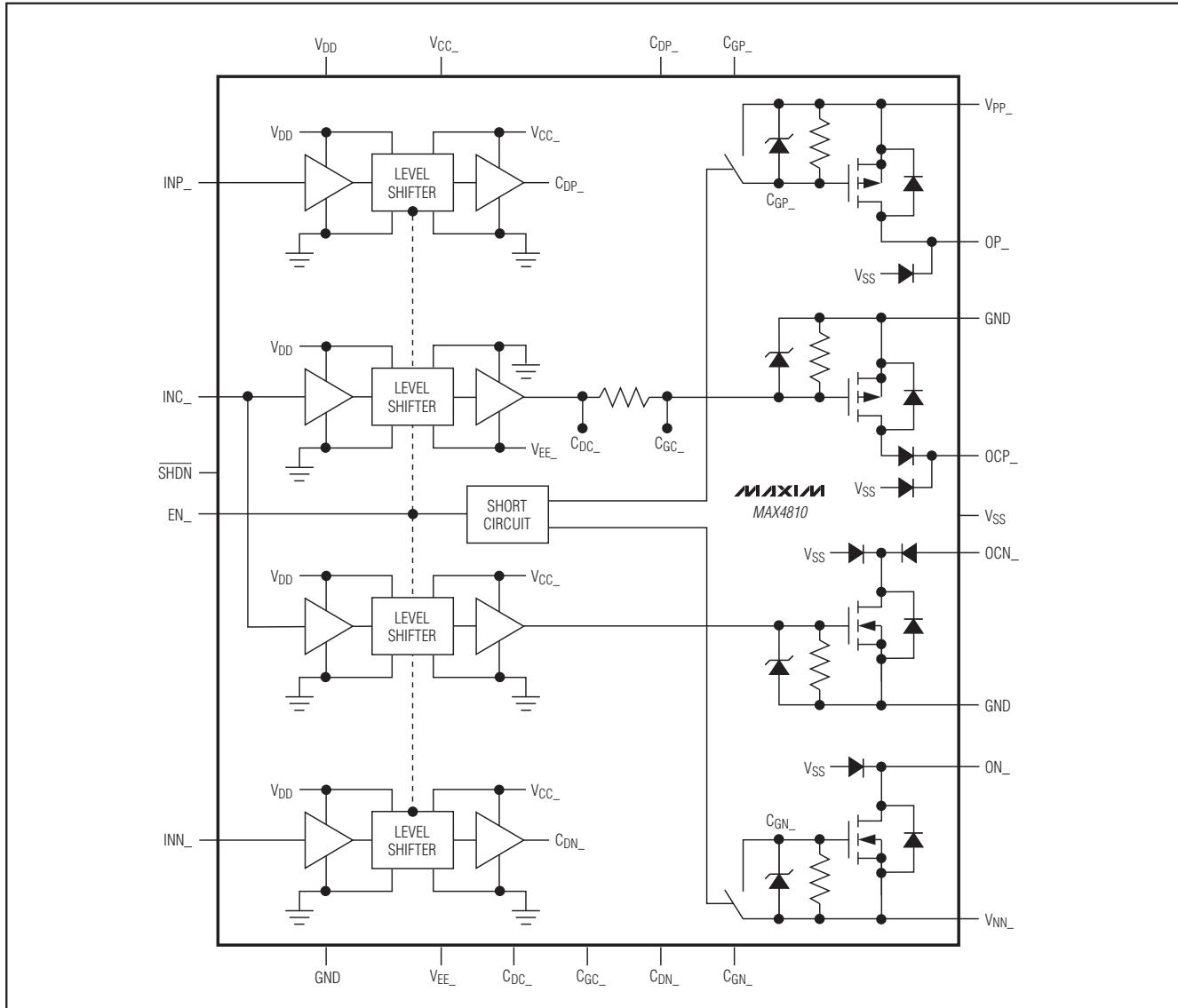

MAX4810/MAX4811/MAX4812は、ユニポーラまたはバイポーラのいずれかのパルス出力でも独立して構成可能なデュアル、高電圧、高速パルサーです。これらのデバイスは、完全パルス制御のための独立したロジック入力と独立したアクティブクランプを備えています。クランプ入力INC\_をハイに設定することで、正または負の高電圧源に対してもデバイスがパルスを生成していないときに自動的にクランプを起動することができます。

## ロジック入力(INP\_、INN\_、INC\_、EN\_、SHDN)

MAX4810/MAX4811/MAX4812は、合計で9個のロジック入力信号を備えています。SHDNはデバイスのパワーアップおよびパワーダウンを制御します。2組のINP\_、INN\_、INC\_、およびEN\_信号があり、各チャネルに1組備わっています。INP\_はハイサイドFETのオンとオフの状態を制御、INN\_はローサイドFETのオンとオフの状態を制御、INC\_はアクティブクランプを制御、EN\_はゲート-ソース間の短絡を制御します。これらの信号によって、各ドライバの出力段を完全に制御することができます(すべてのロジックの組み合わせについてについては、表1を参照)。

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサー

表1. 真理値表

| INPUTS |     |      |      |      | OUTPUTS           |                   |                | STATE                                                        |

|--------|-----|------|------|------|-------------------|-------------------|----------------|--------------------------------------------------------------|

| SDHN   | EN_ | INP_ | INN_ | INC_ | OP_               | ON_               | OCP_, OCN_     |                                                              |

| 0      | X   | X    | X    | 0    | High impedance    | High impedance    | High impedance | Powered down, INP_/INN_ disabled, gate-source short disabled |

| 0      | X   | X    | X    | 1    | High impedance    | High impedance    | GND            | Powered down, INP_/INN_ disabled, gate-source short disabled |

| 1      | 0   | X    | X    | 0    | High impedance    | High impedance    | High impedance | Powered up, INP_/INN_ disabled, gate-source short enabled    |

| 1      | 0   | X    | X    | 1    | High impedance    | High impedance    | GND            | Powered up, INP_/INN_ disabled, gate-source short enabled    |

| 1      | 1   | 0    | 0    | 0    | High impedance    | High impedance    | High impedance | Powered up, all inputs enabled, gate-source short disabled   |

| 1      | 1   | 0    | 0    | 1    | High impedance    | High impedance    | GND            | Powered up, all inputs enabled, gate-source short disabled   |

| 1      | 1   | 0    | 1    | X    | High impedance    | V <sub>NN</sub> _ | High impedance | Powered up, all inputs enabled, gate-source short disabled   |

| 1      | 1   | 1    | 0    | X    | V <sub>PP</sub> _ | High impedance    | High impedance | Powered up, all inputs enabled, gate-source short disabled   |

| 1      | 1   | 1    | 1    | X    | V <sub>PP</sub> _ | V <sub>NN</sub> _ | High impedance | Not allowed (3ns maximum overlap)                            |

X = 任意

0 = ロジックロー

1 = ロジックハイ

MAX4810/MAX4811/MAX4812ロジック入力は、CMOSロジックに対応しており、ロジックレベルは、最大限の柔軟性を得るためにV<sub>DD</sub>を基準としています。ロジック入力の入力容量は5pF (typ)という低容量であるため、負荷が低減され、スイッチング速度が向上します。

## 高電圧出力保護(MAX4811のみ)

MAX4811の高電圧出力は、過電圧保護回路を内蔵しており、ユーザは、複数のパルサーチャネルの出力を並列に接続することによってマルチレベルのパルス機能を実現することができます。ON\_とOP\_の出力に直列に配置した内蔵ダイオードによって、V<sub>NN</sub>\_またはV<sub>PP</sub>\_を超える電圧が出力された場合、ハイサイドとローサイドのFETのボディダイオードがオンに切り替わるのを防ぎます。図2を参照してください。

## アクティブクランプ

MAX4810/MAX4811/MAX4812はアクティブクランプ回路を備えており、パルス品質を向上させ、2次高調波出力を低減します。クランプ回路は、Nチャネル(DC結合)とPチャネル(ACとDCの遅延結合)の高電圧FETで

構成され、ロジッククランプ入力(INC\_)によってオンまたはオフに切り替えられます。MAX4810/MAX4811は、保護クランプデバイスを備えており、バイポーラパルス回路でクランプ回路を使用することができます(図1および図2を参照)。OCN\_出力に直列のダイオードによって、GNDより低い電圧が出力された場合、ローサイドFETのボディダイオードがオンになるのを防ぎます。OCP\_出力に直列のもう1つのダイオードによって、グランドより高い電圧が出力された場合、ハイサイドFETのボディダイオードがオンになるのを防ぎます。MAX4812は、クランプ出力上にダイオードの保護がありません。したがって、このデバイスはユニポーラパルスのみ要求される回路での使用に適しています。

ユーザは、アクティブクランプ入力(INC\_)をロジックハイ電圧に接続してINP\_とINN\_の入力のみを駆動することで、デバイスを駆動するのに使用する信号の数を最小限に抑えることができます。この場合、INP\_とINN\_の入力がともにローで、INC\_入力がハイのときは必ず、アクティブクランプ回路はOCP\_とOCN\_の出力を介して出力をGNDにプルダウンします(詳細については表1を参照)。

# デュアル、ユニポーラ/バイポーラ、高電圧ディジタルパルサー

## 電源電圧のランピングとゲート-ソース間の短絡

MAX4810/MAX4811/MAX4812は、イネーブル入力(*EN\_*)によって制御されるゲート-ソース間の短絡を備えています。*SHDN*がハイで、*EN\_*がローのとき、60Ωスイッチがハイサイド出力FETのゲートとソースをともに短絡します。同時に、同様のスイッチがローサイド出力FETのゲートとソースをともに短絡します(表1)。ゲート-ソース間の短絡回路は、*V<sub>PP</sub>*と*V<sub>NN</sub>*上の電圧のランピングによって出力FETが誤ってオンになるのを防ぎ、ランピング速度を速くでき、パルスモード間の遅延時間を小さくすることができます。

## シャットダウンモード

*SHDN*はチャネル1とチャネル2の両方に共通で、デバイスの電源をオン/オフします。すべての内部回路をパワーダウンするには、*SHDN*をローにします(クランプ回路は除く)。*SHDN*をローにすると、デバイスは最も低い電力消費(1μA)になり、ゲート-ソース間の短絡回路は無効になります。*SHDN*をディセーブルすると、デバイスがアクティブになるまで1μs(typ)かかります。

## サーマル保護

+150°Cの標準スレッショルドを備えたサーマルシャットダウン回路は、過度の電力消費による損傷を防ぎます。接合部温度がT<sub>J</sub> = +150°Cを超えると、すべての出力がディセーブルされます。一般に、ICの接合部温度が+130°C未満に降下すると通常の動作が再開されます。

## アプリケーション情報

### AC結合コンデンサの選択

すべてのAC結合コンデンサの値(*C<sub>DP</sub>*と*C<sub>GP</sub>*の間、および*C<sub>DN</sub>*と*C<sub>GN</sub>*の間)は、1nF~10nFでなければなりません。コンデンサの電圧定格は、少なくとも*V<sub>PP</sub>*と同じだけ高くする必要があります。コンデンサは、できる限りデバイス近くに配置する必要があります。

*INP\_*と一部の*INC\_*は、出力デバイスにAC結合されているため、デバイスがアクティブのとき、いつまでもハイに駆動することはできません。

### 電力消費

MAX4810/MAX4811/MAX4812の電力消費は、*V<sub>CC</sub>*、*V<sub>PP</sub>*、および*V<sub>NN</sub>*の消費電流によって生じる3つの主要な要素で構成されます。これらの要素の総和(*P<sub>VCC</sub>*、*P<sub>VPP</sub>*、および*P<sub>VNN</sub>*)は、電力消費の最大限界値未満に維持する必要があります。標準消費電流

対スイッチング周波数の詳細については、「標準動作特性」を参照してください。

デバイスは、大部分の消費電流を*V<sub>CC</sub>*電源から消費して、ハイサイドFET (*C<sub>P</sub>*)およびローサイドFET (*C<sub>N</sub>*)のゲート容量などの内部ノードを充電および放電します。わずかな自己消費電流と、内部ゲートクランプFETの充電と放電に使用するわずかな電流を無視すると、消費電力は、次式で推定することができます。

$$P_{VCC} = \left[ (C_N \times V_{CC\_}^2 \times f_{IN}) + (C_P \times V_{CC\_}^2 \times f_{IN}) \right] \times (BRF \times BTD)$$

$$f_{IN} = f_{INN} + f_{INP}$$

ここで、*f<sub>INN</sub>*と*f<sub>INP</sub>*は、それぞれINNとINPの入力のスイッチング周波数であり、BRFはバースト繰り返し周波数、BTDはバースト継続時間です。パワーFETのゲート容量の標準値は、*C<sub>N</sub>* = 0.2nF、*C<sub>P</sub>* = 0.4nFです。

抵抗が*R<sub>L</sub>*で容量が*C<sub>L</sub>*の出力負荷の場合、MAX4810/MAX4811/MAX4812の電力消費は次式で推定することができます(方形波出力であるものと想定し、スイッチの抵抗は無視できます)。

$$P_{VPP} = \left[ (C_O + C_L) \times f_{IN} \times (V_{PP\_} - V_{NN\_})^2 \right] + \left[ \frac{V_{PP\_}^2}{R_L} \times \frac{1}{2} \right] \times (BRF \times BTD)$$

ここで、*C<sub>O</sub>*はデバイスの出力容量です。

### 電源およびバイパス

MAX4810/MAX4811/MAX4812は、独立した電源電圧セット(*V<sub>DD</sub>*と*V<sub>SS</sub>*だけが両方のチャネルに共通)で動作します。ロジック入力回路は、+2.7V~+6Vの単一電源(*V<sub>DD</sub>*)で動作します。レベルシフトドライバのデュアル電源*V<sub>CC</sub>/V<sub>EE</sub>*は、±4.75V~±12.6Vで動作します。

*V<sub>PP</sub>/V<sub>NN</sub>*のハイサイドとローサイドの電源は、最大+220Vの単一正電源、最大-200Vの単一負電源、または±110Vデュアル電源で駆動されます。*V<sub>PP</sub>*または*V<sub>NN</sub>*のいずれかを0に設定することができます。各電源入力は、できる限りデバイス近くに0.1μFコンデンサで接地してください。

入力の負荷によっては、出力の遷移中に*V<sub>NN</sub>*と*V<sub>PP</sub>*の出力を安定させるために追加のバイパスが必要になる場合があります。たとえば、*C<sub>OUT</sub>* = 100pFで*R<sub>OUT</sub>* = 100Ω負荷の場合、10μF (typ)コンデンサの追加を推奨します。*V<sub>SS</sub>*はサブストレートの電圧であり、*V<sub>NN1</sub>*または*V<sub>NN2</sub>*と同じか、またはそれより低い電圧に接続する必要があります。

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサー

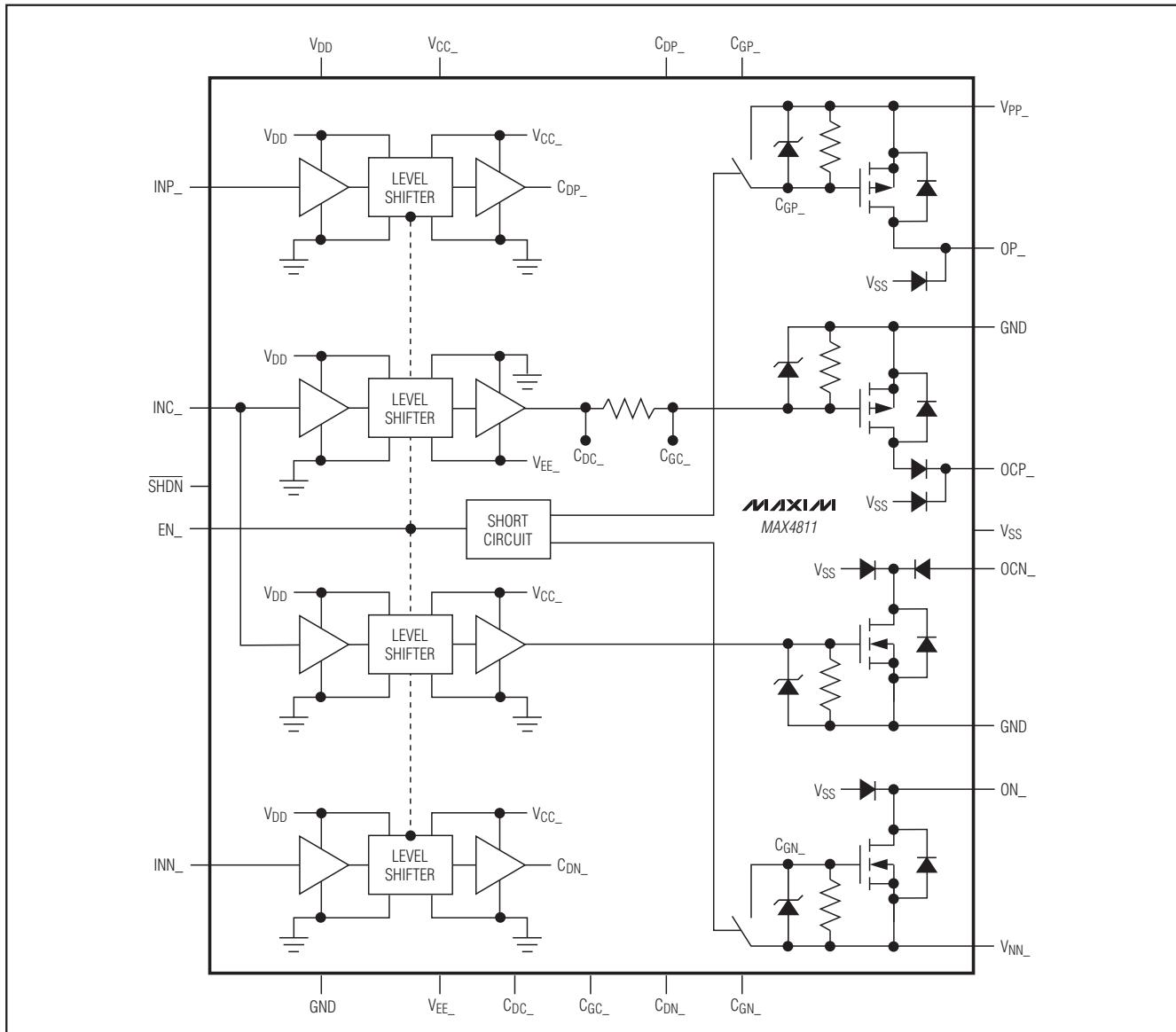

図1. MAX4810の1チャネルについて簡略化したファンクションダイアグラム

## エクスポートドパッドとレイアウトの問題

MAX4810/MAX4811/MAX4812は、放熱性能を向上するためにTQFNパッケージの下側にエクスポートドパッド(EP)が用意されています。エクスポートドパッドは、内部でV<sub>SS</sub>に接続されています。エクスポートドパッドを外部でV<sub>SS</sub>に接続し、短絡を防ぐためにパッケージの下側にトレースをレイアウトしないでください。熱を放散しやすくするために、PCB部品面のエクスポートドパッドと同形状のパッドへ接続してください。このパッドは、メッキされたいくつかのスルーホール

によって半田面の広い熱拡散銅領域に接続して、熱をデバイスの外に伝導する必要があります。

MAX4810/MAX4811/MAX4812高速パルサーは、電源入力への低インダクタンスのバイパスコンデンサを必要とします。高速PCBのトレース設計を実施することを推奨します。トレース長が最短となるように特に注意を払い、またインダクタンスを低減するため十分に広いトレース幅を使用してください。表面実装部品の使用も推奨します。

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサー

**MAX4810/MAX4811/MAX4812**

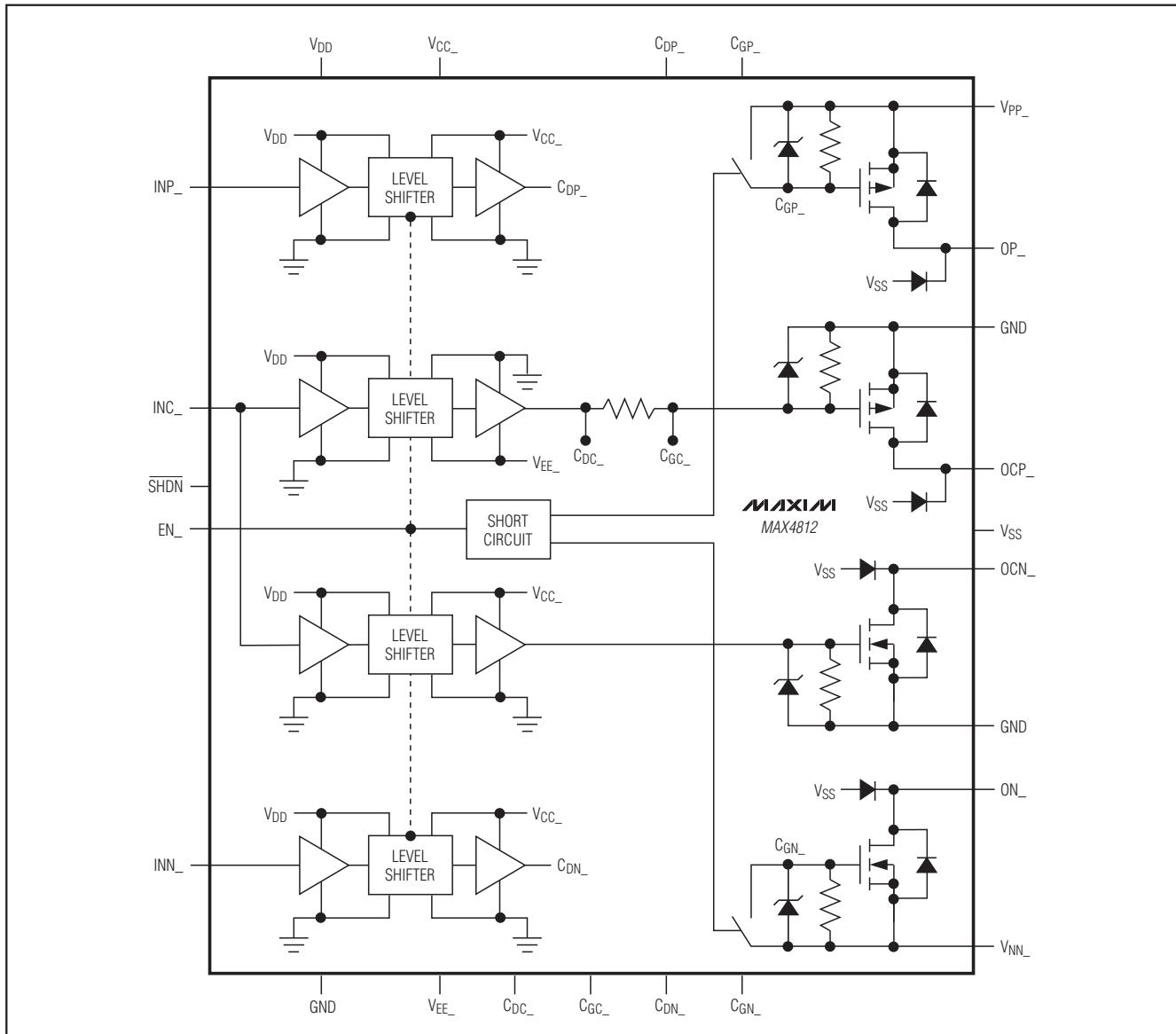

図2. MAX4811の1チャネルについて簡略化したファンクションダイアグラム

## 電源シーケンシング

$V_{SS}$ は常に、 $V_{NN1}$ または $V_{NN2}$ のうちどちらか低い方の電圧と同じかそれ以下でなければなりません。MAX4810/MAX4811/MAX4812では、それ以外の電源シーケンシングは不要です。

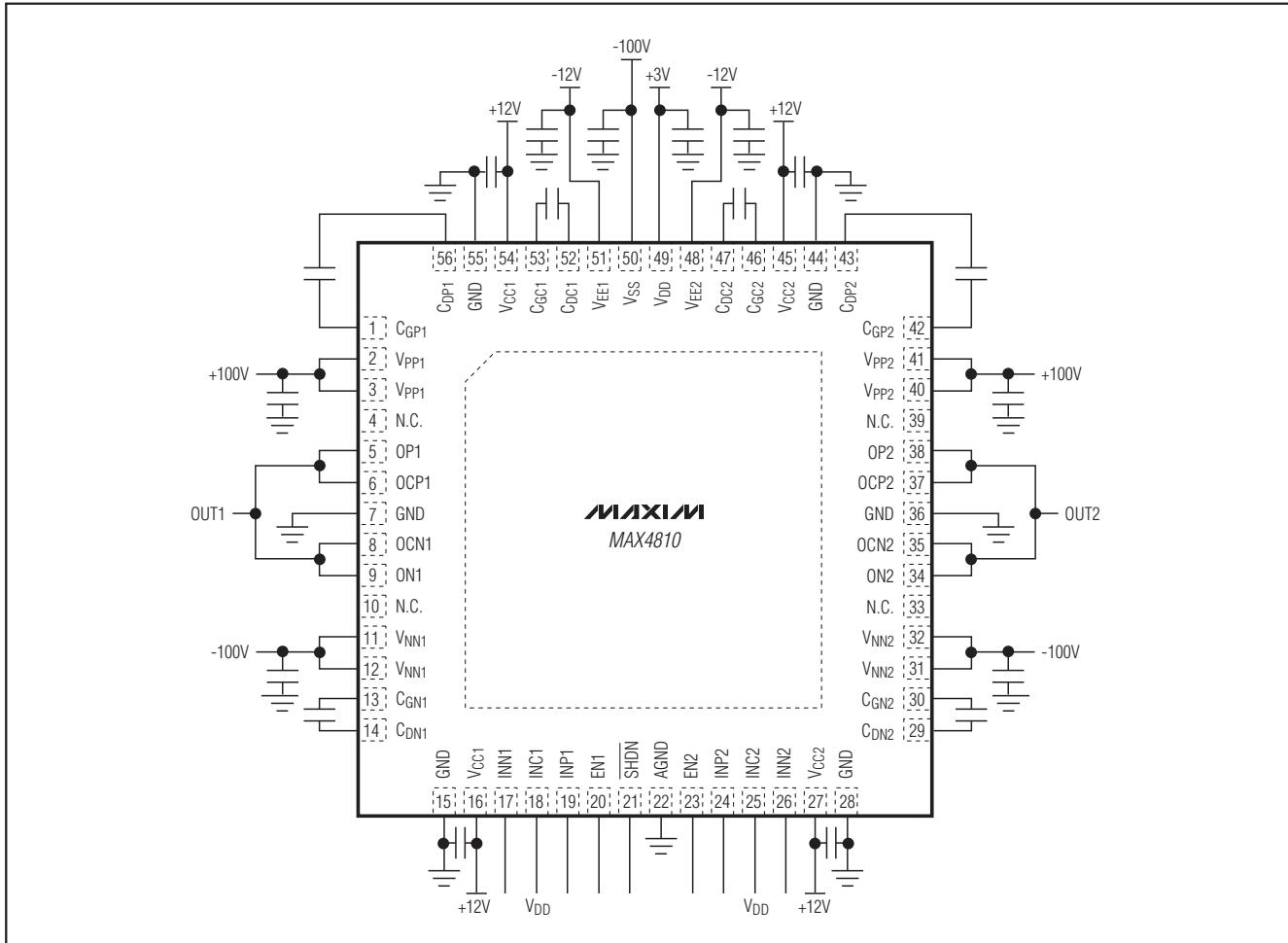

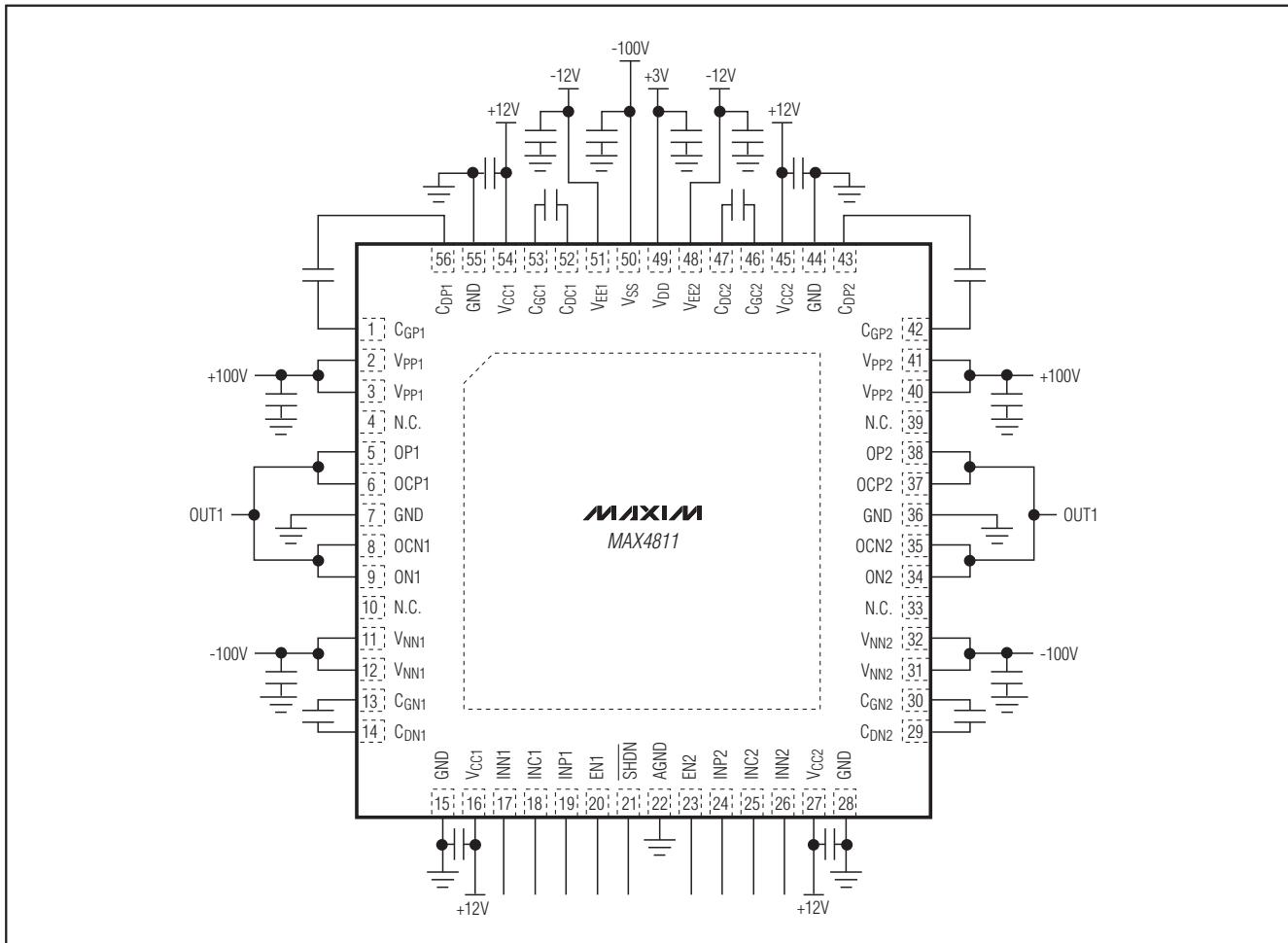

## 標準動作回路

図8、図9、および図10は、MAX4810/MAX4811/MAX4812の標準動作を示します。図8は、バイポーラパルス接続で使用されるMAX4810を示します。図9は、5段階パルス動作でのMAX4811を示し、図10はユニポーラ動作でのMAX4812を示します。

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサー

図3. MAX4812の1チャネルについて簡略化したファンクションダイアグラム

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサー

**MAX4810/MAX4811/MAX4812**

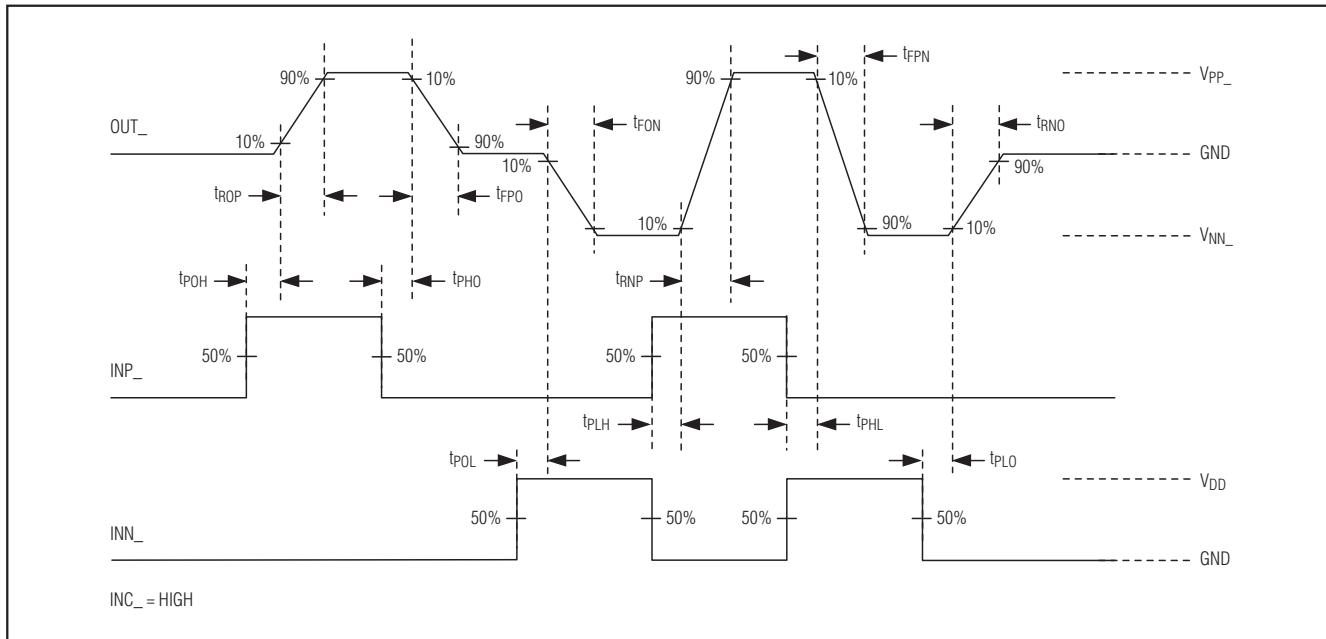

図4. タイミングの詳細( $R_L = 100\Omega$ 、 $C_L = 100\text{pF}$ )

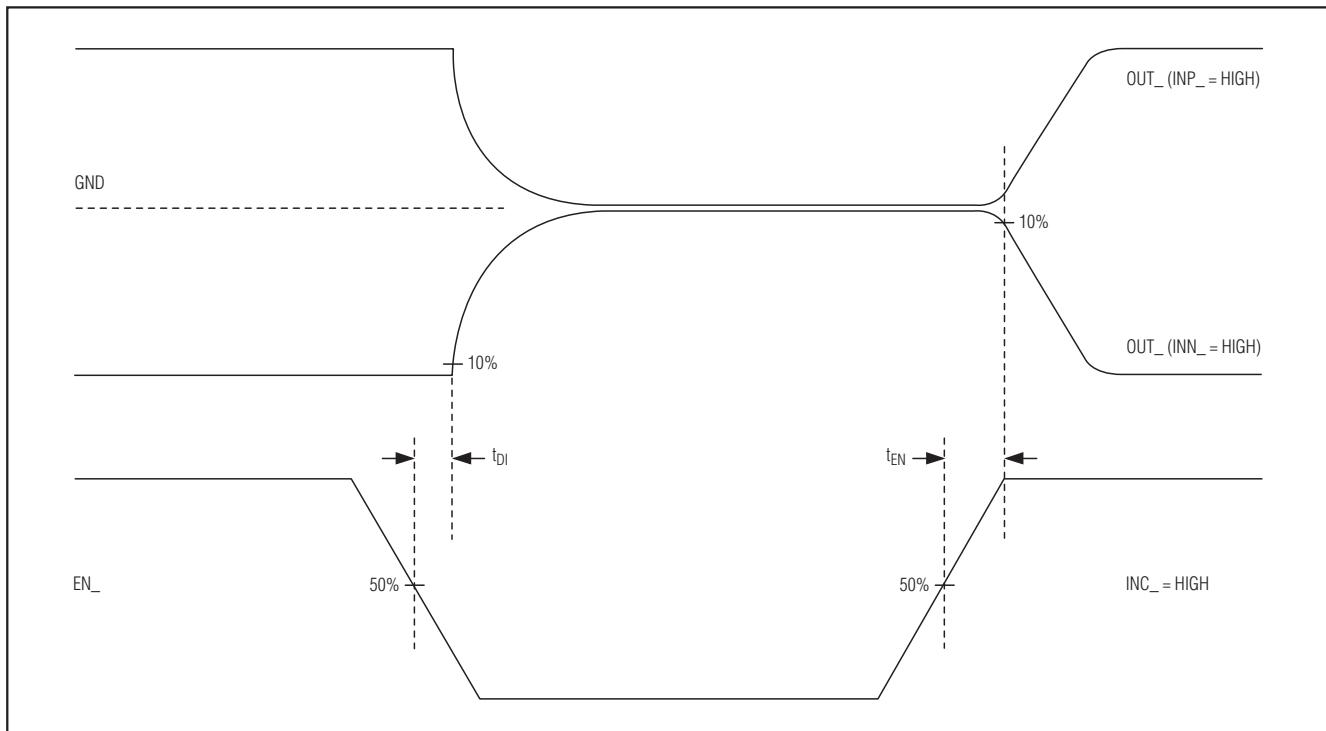

図5. イネーブルのタイミング( $R_L = 100\Omega$ 、 $C_L = 100\text{pF}$ )

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサー

図6. アクティブクランプのタイミング

図7. 短絡のタイミング

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサー

**MAX4810/MAX4811/MAX4812**

図8. MAX4810 : デュアルバイポーラパルス、±100V、GND

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサー

図9. MAX4811 : 5段階パレス、±100V、±50V、GND

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサー

**MAX4810/MAX4811/MAX4812**

図10. MAX4812 : デュアルユニポーラパルス、+100V、GND

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサー

## パッケージ

最新のパッケージ情報とランドパターンは、[japan.maxim-ic.com/packages](http://japan.maxim-ic.com/packages)をご参照ください。

| パッケージタイプ | パッケージコード | ドキュメントNo.      |

|----------|----------|----------------|

| 56 TQFN  | T5677-1  | <b>21-0144</b> |

マキシム・ジャパン株式会社

〒169-0051 東京都新宿区西早稲田3-30-16(ホリゾン1ビル)

TEL. (03)3232-6141 FAX. (03)3232-6149

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。

マキシムは隨時予告なく回路及び仕様を変更する権利を留保します。

20 **Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600**

© 2008 Maxim Integrated Products

**MAXIM** is a registered trademark of Maxim Integrated Products, Inc.