EVALUATION KIT

AVAILABLE

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサ

## 概要

MAX4806/MAX4807/MAX4808の集積回路は、低電圧のロジック入力から高電圧で高周波数のユニポーラパルスまたはバイポーラパルスを生成します。これらのデュアルパルサは、独立したロジック入力、アクティブクランプ付きの独立した高電圧パルサ出力、および独立した高電圧電源入力を特長としています。

また、MAX4806/MAX4807/MAX4808は、高電圧出力については6Ω出力インピーダンス、およびアクティブクランプについては20Ωインピーダンスを備えています。高電圧出力は、2Aの出力電流を供給することができます。

すべてのデバイスは、チャネルごとに3つのロジック入力を使用して、正および負のパルスとアクティブクランプを制御します。さらに2つの独立したイネーブル入力が含まれます。EN\_をディセーブルすることで、電源電圧の高速なランピング時に出力MOSFETが誤ってオンにならないようにしています。これによって、ランピングの高速化やパルスモード間の短い遅延に対応することができるようになります。低電力のシャットダウンモードによって消費電力が1μA未満に低減されます。すべてのデジタル入力はCMOS互換です。

MAX4806はクランプ出力の過電圧保護を備えており、MAX4807はパルサ出力とクランプ出力の両方の過電圧保護を備えています。MAX4808には過電圧保護はありません(「型番/選択ガイド」を参照)。

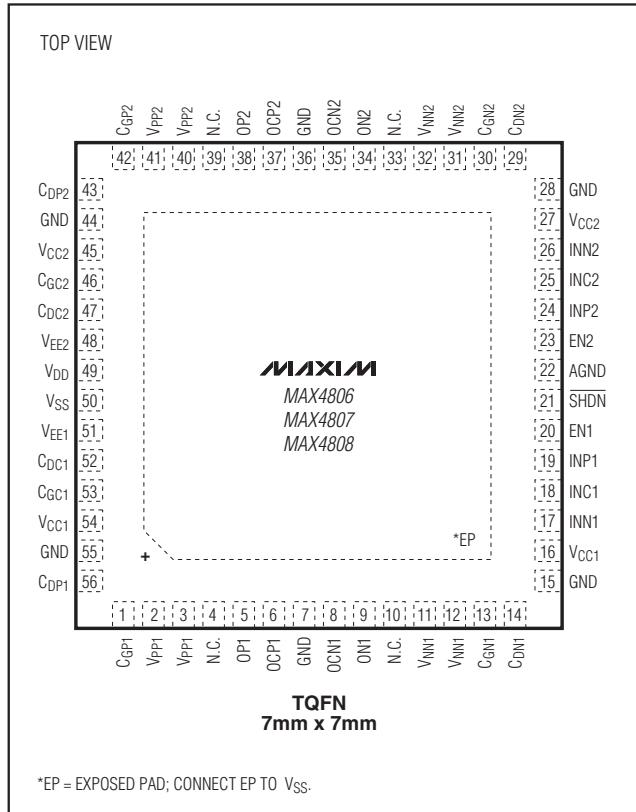

MAX4806/MAX4807/MAX4808は、56ピン(7mm x 7mm)のTQFNエクスポートドパッドパッケージで提供されており、0°C~+70°Cの民生用温度範囲で仕様が定められています。

## アプリケーション

|        |        |

|--------|--------|

| 超音波医療  | 欠陥検出   |

| 画像処理   | 圧電ドライバ |

| 産業用センサ | テスト装置  |

## 型番/選択ガイド

| PART         | PROTECTED OUTPUTS    | OUTPUT CURRENT (A) | PIN-PACKAGE  |

|--------------|----------------------|--------------------|--------------|

| MAX4806CTN+  | OCP_, OCN_           | 2                  | 56 TQFN-EP** |

| MAX4807CTN+  | OCP_, OCN_, OP_, ON_ | 2                  | 56 TQFN-EP** |

| MAX4808CTN+* | None                 | 2                  | 56 TQFN-EP** |

注：すべてのデバイスは、0°C~+70°Cの動作温度範囲で仕様が定められています。

+は鉛フリー/RoHS準拠のパッケージを示します。

\*開発中。入手性についてはお問い合わせください。

\*\*EP = エクスポートドパッド

警告：MAX4806/MAX4807/MAX4808は、高電圧で動作するように設計されています。注意が必要です。

## 特長

- ◆ 高集積、高電圧、高周波数、ユニポーラ/バイポーラパルサ

- ◆ 6Ωの出力インピーダンスおよび2A (min)の出力電流

- ◆ 20Ωのアクティブクランプ

- ◆ パルサとクランプの過電圧保護(MAX4806/MAX4807)

- ◆ 0~+220Vのユニポーラ出力または±110Vのバイポーラ出力

- ◆ 立上り/立下り時間の整合、および伝播遅延の整合

- ◆ CMOS互換のロジック入力

- ◆ 7mm x 7mmの56ピンTQFNパッケージ

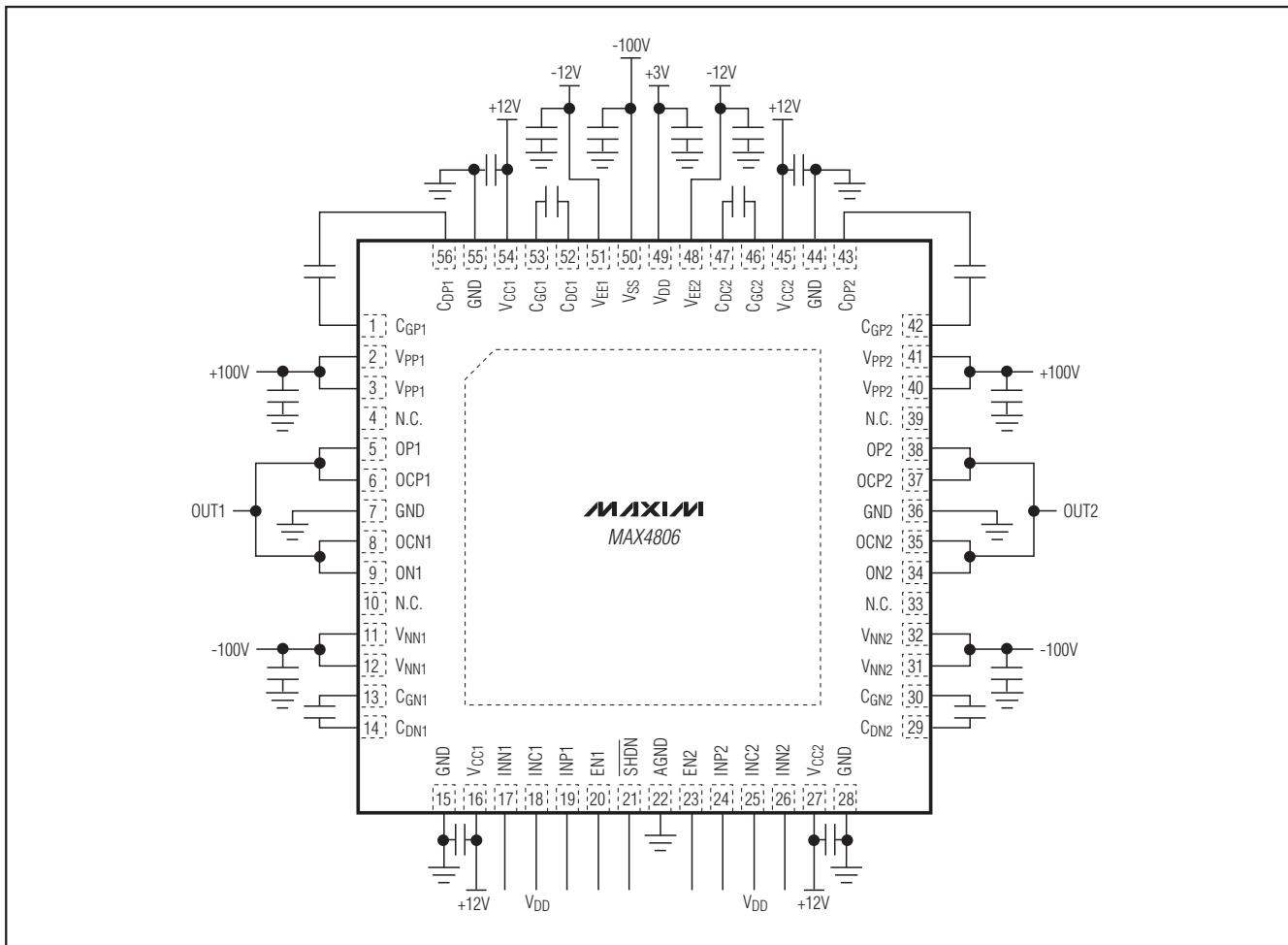

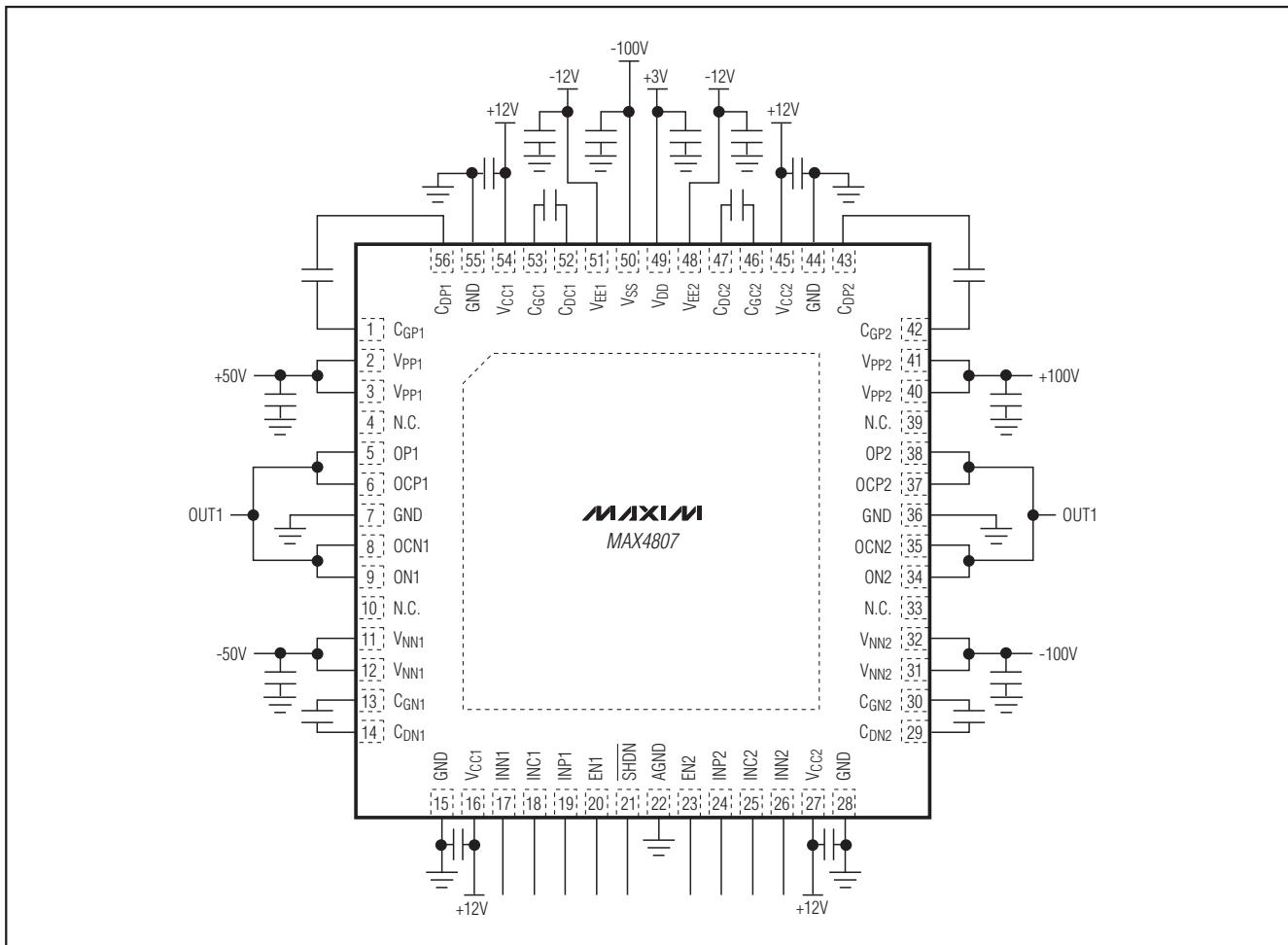

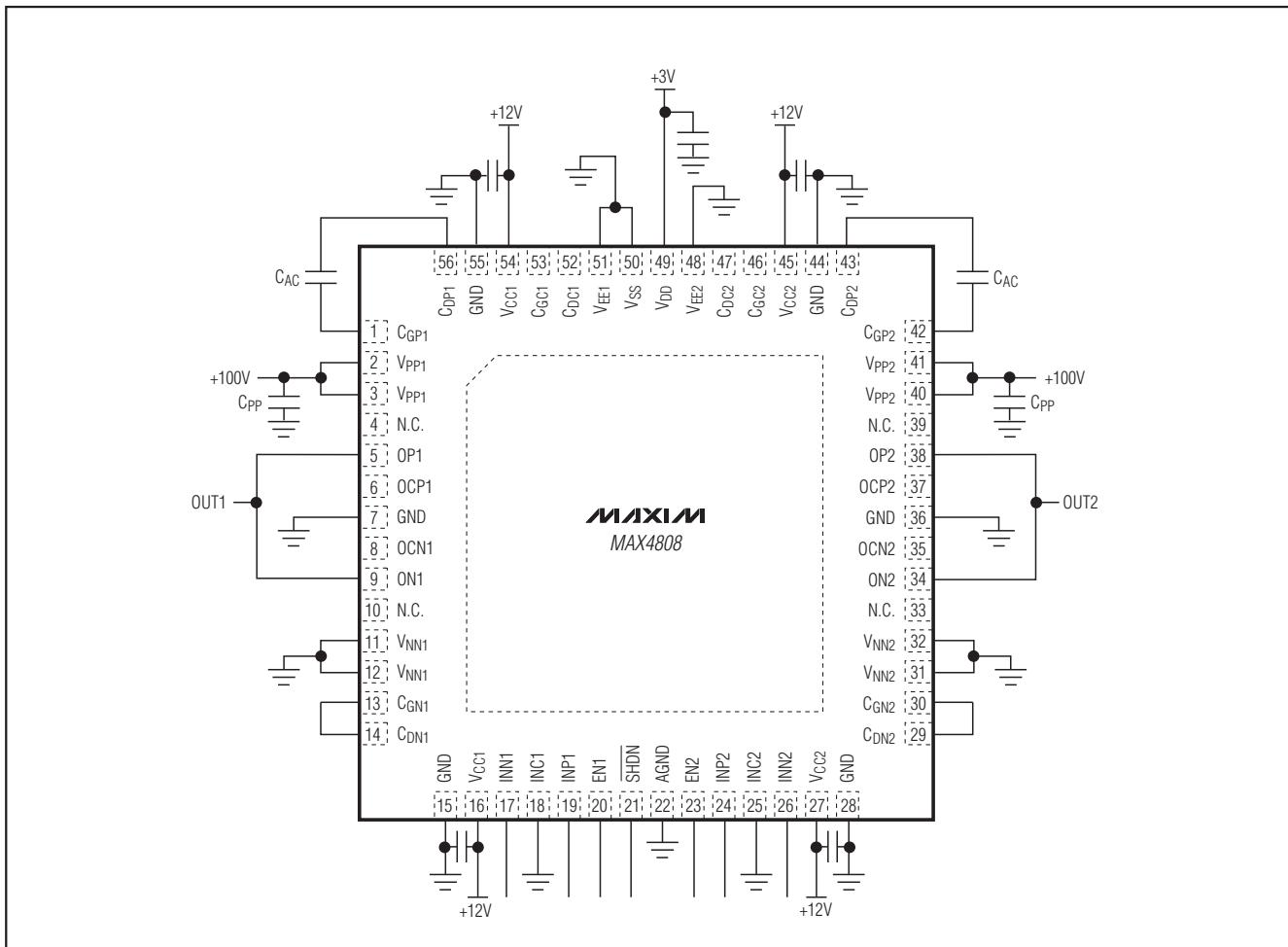

## ピン配置

**MAXIM**

Maxim Integrated Products 1

本データシートに記載された内容はMaxim Integrated Productsの公式な英語版データシートを翻訳したものです。翻訳により生じる相違及び誤りについては責任を負いかねます。正確な内容の把握には英語版データシートをご参照ください。

無料サンプル及び最新版データシートの入手には、マキシムのホームページをご利用ください。<http://japan.maxim-ic.com>

**MAX4806/MAX4807/MAX4808**

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサ

## ABSOLUTE MAXIMUM RATINGS

(Voltages referenced to GND.)

|                                            |                                   |

|--------------------------------------------|-----------------------------------|

| VDD Logic Supply Voltage                   | -0.3V to +6V                      |

| VCC_ Output Driver Positive Supply Voltage | -0.3V to +15V                     |

| VEE_ Output Driver Negative Supply Voltage | -15V to +0.3V                     |

| VPP_ High Positive Supply Voltage          | -0.3V to +230V                    |

| VNN_ High Negative Supply Voltage          | -230V to +0.3V                    |

| VSS Voltage                                | (VPP_ - 250V) to VNN_             |

| VPP1 - VNN1, VPP2 - VNN2 Supply Voltage    | -0.3V to +250V                    |

| INP_, INN_, INC_, EN_, SHDN Logic Input    | -0.3V to (VDD + 0.3V)             |

| OP_, OCP_, OCN_, ON                        | (-0.3V + VNN_) to (-0.3V to VPP_) |

| CGN_ Voltage                               | (-0.3V + VNN_) to (+15V + VNN_)   |

| CGP_ Voltage                               | (+0.3V + VPP_) to (-15V + VPP_)   |

| CGC_ Voltage                               | -15V to +15V                      |

|                                                                        |                                               |

|------------------------------------------------------------------------|-----------------------------------------------|

| CDC_, CDP_, CDN_ Voltage                                               | -0.3V to VCC_                                 |

| Peak Current per Output Channel                                        | $\pm 3.0\text{A}$                             |

| Continuous Power Dissipation ( $T_A = +70^\circ\text{C}$ ) (Note 1)    |                                               |

| 56-Pin TQFN (derate 40mW/ $^\circ\text{C}$ above $+70^\circ\text{C}$ ) | 3200mW                                        |

| Thermal Resistance (Note 2)                                            |                                               |

| $\theta_{JA}$                                                          | +25 $^\circ\text{C}/\text{W}$                 |

| $\theta_{JC}$                                                          | +0.8 $^\circ\text{C}/\text{W}$                |

| Operating Temperature Range                                            | 0 $^\circ\text{C}$ to +70 $^\circ\text{C}$    |

| Junction Temperature                                                   | +150 $^\circ\text{C}$                         |

| Storage Temperature Range                                              | -65 $^\circ\text{C}$ to +150 $^\circ\text{C}$ |

| Lead Temperature (soldering, 10s)                                      | +300 $^\circ\text{C}$                         |

**Note 1:** This specification is based on the thermal characteristic of the package, the maximum junction temperature, and the setup described by JEDEC 51. The maximum power dissipation for the MAX4806/MAX4807/MAX4808 might be limited by the thermal protection included in the device.

**Note 2:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to [www.maxim-ic.com/thermal-tutorial](http://www.maxim-ic.com/thermal-tutorial).

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

( $VDD = +2.7\text{V}$  to  $+6\text{V}$ ,  $VCC_ = +4.75\text{V}$  to  $+12.6\text{V}$ ,  $VEE_ = -12.6\text{V}$  to  $-4.75\text{V}$ ,  $VNN_ = -200\text{V}$  to  $0\text{V}$ ,  $VPP_ = 0\text{V}$  to ( $VNN_ + 200\text{V}$ ),  $VSS \leq$  the lower of  $VNN1$  or  $VNN2$ ,  $T_A = T_J = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ\text{C}$ .) (Note 3)

| PARAMETER                                                                                                          | SYMBOL    | CONDITIONS                                                                                                                                                                      | MIN   | TYP          | MAX   | UNITS         |

|--------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------|-------|---------------|

| <b>POWER SUPPLY (<math>VDD</math>, <math>VCC_</math>, <math>VEE_</math>, <math>VPP_</math>, <math>VNN_</math>)</b> |           |                                                                                                                                                                                 |       |              |       |               |

| Logic Supply Voltage                                                                                               | $VDD$     |                                                                                                                                                                                 | +2.7  | +3           | +6    | V             |

| Positive Drive Supply Voltage                                                                                      | $VCC_$    |                                                                                                                                                                                 | +4.75 | +12          | +12.6 | V             |

| Negative Drive Supply Voltage                                                                                      | $VEE_$    |                                                                                                                                                                                 | -12.6 | -12          | -4.75 | V             |

| High-Side Supply Voltage                                                                                           | $VPP_$    |                                                                                                                                                                                 | 0     | $VNN_ + 220$ |       | V             |

| Low-Side Supply Voltage                                                                                            | $VNN_$    |                                                                                                                                                                                 | -200  | 0            |       | V             |

| $VPP_ - VNN_$ Supply Voltage                                                                                       |           |                                                                                                                                                                                 | 0     | +220         |       | V             |

| <b>SUPPLY CURRENT (Single Channel)</b>                                                                             |           |                                                                                                                                                                                 |       |              |       |               |

| VDD Supply Current                                                                                                 | $I_{DD}$  | $V_{INN_} = V_{INP_} = 0$ , $V_{SHDN} = 0$                                                                                                                                      |       | 1            |       | $\mu\text{A}$ |

|                                                                                                                    |           | $V_{EN_} = VDD$ , $V_{SHDN} = VDD$ , $V_{INC_} = 0$ or $VDD$ , $V_{INN_} = V_{INP_}$ , $f = 5\text{MHz}$                                                                        | 100   | 350          |       |               |

| VCC_ Supply Current                                                                                                | $I_{CC_}$ | $V_{SHDN} = 0$ , channel 1 and channel 2                                                                                                                                        |       | 1            |       | $\mu\text{A}$ |

|                                                                                                                    |           | $V_{EN_} = VDD$ , $V_{SHDN} = VDD$ , channel 1 and channel 2                                                                                                                    | 130   | 200          |       |               |

|                                                                                                                    |           | $V_{EN_} = VDD$ , $V_{SHDN} = VDD$ , $V_{INC_} = 0$ or $VDD$ , $V_{INN_} = V_{INP_}$ , $f = 5\text{MHz}$ , $VCC_ = 5\text{V}$ , $VDD = 3\text{V}$ , only one channel switching  |       | 18           |       | $\text{mA}$   |

|                                                                                                                    |           | $V_{EN_} = VDD$ , $V_{SHDN} = VDD$ , $V_{INC_} = 0$ or $VDD$ , $V_{INN_} = V_{INP_}$ , $f = 5\text{MHz}$ , $VCC_ = 12\text{V}$ , $VDD = 3\text{V}$ , only one channel switching |       | 44           |       |               |

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサ

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{DD} = +2.7V$  to  $+6V$ ,  $V_{CC\_} = +4.75V$  to  $+12.6V$ ,  $V_{EE\_} = -12.6V$  to  $-4.75V$ ,  $V_{NN\_} = -200V$  to  $0V$ ,  $V_{PP\_} = 0V$  to ( $V_{NN\_} + 200V$ ),  $V_{SS} \leq$  the lower of  $V_{NN1}$  or  $V_{NN2}$ ,  $T_A = T_J$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ .) (Note 3)

| PARAMETER                                                                                                 | SYMBOL              | CONDITIONS                                                                                                                                                                                                                                                                 | MIN                     | TYP                     | MAX | UNITS |

|-----------------------------------------------------------------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------|-----|-------|

| V <sub>EE</sub> _ Supply Current                                                                          | I <sub>EE</sub> _   | V <sub>SHDN</sub> = 0, channel 1 and channel 2                                                                                                                                                                                                                             |                         | 1                       |     | μA    |

|                                                                                                           |                     | V <sub>EN</sub> _ = V <sub>DD</sub> , V <sub>SHDN</sub> = V <sub>DD</sub> , channel 1 and channel 2                                                                                                                                                                        |                         |                         | 1   |       |

|                                                                                                           |                     | V <sub>EN</sub> _ = V <sub>DD</sub> , V <sub>SHDN</sub> = V <sub>DD</sub> , V <sub>INC</sub> _ = 0 or V <sub>DD</sub> , V <sub>NN</sub> _ = V <sub>INP</sub> _, f = 5MHz, V <sub>EE</sub> _ = -5V, only 1 channel switching                                                |                         | 200                     |     |       |

|                                                                                                           |                     | V <sub>EN</sub> _ = V <sub>DD</sub> , V <sub>SHDN</sub> = V <sub>DD</sub> , V <sub>INC</sub> _ = 0 or V <sub>DD</sub> , V <sub>NN</sub> _ = V <sub>INP</sub> _, f = 5MHz, V <sub>EE</sub> _ = -12V, only 1 channel switching                                               |                         | 200                     |     |       |

| V <sub>PP</sub> _ Supply Current                                                                          | I <sub>PP</sub> _   | V <sub>SHDN</sub> = 0, channel 1 and channel 2                                                                                                                                                                                                                             |                         | 1                       |     | μA    |

|                                                                                                           |                     | V <sub>EN</sub> _ = V <sub>DD</sub> , V <sub>SHDN</sub> = V <sub>DD</sub> , channel 1 and channel 2                                                                                                                                                                        | 90                      | 160                     |     |       |

|                                                                                                           |                     | V <sub>EN</sub> _ = V <sub>DD</sub> , V <sub>SHDN</sub> = V <sub>DD</sub> , V <sub>INC</sub> _ = 0 or V <sub>DD</sub> , V <sub>NN</sub> _ = V <sub>INP</sub> _, f = 5MHz, V <sub>PP</sub> _ = +5V, V <sub>NN</sub> _ = -5V, no load, only 1 channel switching              |                         | 13                      |     |       |

|                                                                                                           |                     | V <sub>EN</sub> _ = V <sub>DD</sub> , V <sub>SHDN</sub> = V <sub>DD</sub> , V <sub>INC</sub> _ = 0 or V <sub>DD</sub> , V <sub>PP</sub> _ = +80V, V <sub>NN</sub> _ = -80V, pulse repetition frequency = 10kHz, f = 10MHz, four periods, no load, only 1 channel switching |                         | 0.65                    |     |       |

| V <sub>NN</sub> _ Supply Current                                                                          | I <sub>NN</sub> _   | V <sub>SHDN</sub> = 0, channel 1 and channel 2                                                                                                                                                                                                                             |                         | 1                       |     | μA    |

|                                                                                                           |                     | V <sub>EN</sub> _ = V <sub>DD</sub> , V <sub>SHDN</sub> = V <sub>DD</sub> , channel 1 and channel 2                                                                                                                                                                        | 40                      | 80                      |     |       |

|                                                                                                           |                     | V <sub>EN</sub> _ = V <sub>DD</sub> , V <sub>SHDN</sub> = V <sub>DD</sub> , V <sub>INC</sub> _ = 0 or V <sub>DD</sub> , V <sub>NN</sub> _ = V <sub>INP</sub> _, f = 5MHz, V <sub>NN</sub> _ = -5V, V <sub>PP</sub> _ = +5V, no load, only 1 channel                        |                         | 13                      |     |       |

|                                                                                                           |                     | V <sub>EN</sub> _ = V <sub>DD</sub> , V <sub>SHDN</sub> = V <sub>DD</sub> , V <sub>INC</sub> _ = 0 or V <sub>DD</sub> , V <sub>PP</sub> _ = +80V, V <sub>NN</sub> _ = -80V, pulse repetition frequency = 10kHz, f = 10MHz, four periods, no load, only 1 channel switching |                         | 0.65                    |     |       |

| <b>LOGIC INPUTS (EN<sub>_</sub>, SHDN<sub>_</sub>, INN<sub>_</sub>, INP<sub>_</sub>, INC<sub>_</sub>)</b> |                     |                                                                                                                                                                                                                                                                            |                         |                         |     |       |

| Low-Level Input Voltage                                                                                   | V <sub>IL</sub>     |                                                                                                                                                                                                                                                                            |                         | 0.25 × V <sub>DD</sub>  |     | V     |

| High-Level Input Voltage                                                                                  | V <sub>IH</sub>     |                                                                                                                                                                                                                                                                            |                         | 0.75 × V <sub>DD</sub>  |     | V     |

| Logic-Input Capacitance                                                                                   | C <sub>IN</sub>     |                                                                                                                                                                                                                                                                            |                         | 5                       |     | pF    |

| Logic-Input Leakage                                                                                       | I <sub>IN</sub>     | V <sub>IN</sub> = 0 or V <sub>DD</sub>                                                                                                                                                                                                                                     |                         | ±1                      |     | μA    |

| <b>OUTPUT (OUT<sub>_</sub>)</b>                                                                           |                     |                                                                                                                                                                                                                                                                            |                         |                         |     |       |

| OUT <sub>_</sub> Output Voltage Range                                                                     | V <sub>OUT</sub> _  | No load at OUT <sub>_</sub>                                                                                                                                                                                                                                                | V <sub>NN</sub> _       | V <sub>PP</sub> _       |     | V     |

|                                                                                                           |                     | Unprotected outputs (see the <i>Ordering Information/Selector Guide</i> ), 100mA load                                                                                                                                                                                      | V <sub>NN</sub> _ + 1.5 | V <sub>PP</sub> _ - 1.5 |     |       |

|                                                                                                           |                     | Protected outputs (see the <i>Ordering Information/Selector Guide</i> ), 100mA load                                                                                                                                                                                        | V <sub>NN</sub> _ + 2.5 | V <sub>PP</sub> _ - 2.5 |     |       |

| Low-Side Small-Signal Output Impedance (MAX4806)                                                          | ROUT <sub>_LS</sub> | I <sub>OP</sub> _ = -100mA, V <sub>CC</sub> _ = +12V ±5%, DC-coupled                                                                                                                                                                                                       | 5                       | 12                      |     | Ω     |

|                                                                                                           |                     | I <sub>OP</sub> _ = -100mA, V <sub>CC</sub> _ = +5V ±5%, DC-coupled                                                                                                                                                                                                        | 5                       | 12                      |     |       |

**MAX4806/MAX4807/MAX4808**

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサ

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{DD} = +2.7\text{V}$  to  $+6\text{V}$ ,  $V_{CC\_} = +4.75\text{V}$  to  $+12.6\text{V}$ ,  $V_{EE\_} = -12.6\text{V}$  to  $-4.75\text{V}$ ,  $V_{NN\_} = -200\text{V}$  to  $0\text{V}$ ,  $V_{PP\_} = 0\text{V}$  to ( $V_{NN\_} + 200\text{V}$ ),  $V_{SS} \leq$  the lower of  $V_{NN1}$  or  $V_{NN2}$ ,  $T_A = T_J$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ\text{C}$ .) (Note 3)

| PARAMETER                                                                                                              | SYMBOL            | CONDITIONS                                                                                                                                         | MIN     | TYP | MAX  | UNITS |

|------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|------|-------|

| Low-Side Small-Signal Output Impedance (MAX4807)                                                                       | ROUT_LS           | IOP <sub>_</sub> = -100mA, V <sub>CC_</sub> = +12V ±5%, DC-coupled                                                                                 | 6       | 13  |      | Ω     |

|                                                                                                                        |                   | IOP <sub>_</sub> = -100mA, V <sub>CC_</sub> = +5V ±5%, DC-coupled                                                                                  | 6       | 13  |      |       |

| High-Side Small-Signal Output Impedance (MAX4806)                                                                      | ROUT_HS           | IOP <sub>_</sub> = -100mA, V <sub>CC_</sub> = +12V ±5%, DC-coupled                                                                                 | 6       | 12  |      | Ω     |

|                                                                                                                        |                   | IOP <sub>_</sub> = -100mA, V <sub>CC_</sub> = +5V ±5%, DC-coupled                                                                                  | 8       | 15  |      |       |

| High-Side Small-Signal Output Impedance (MAX4807)                                                                      | ROUT_HS           | IOP <sub>_</sub> = -100mA, V <sub>CC_</sub> = +12V ±5%, DC-coupled                                                                                 | 7       | 13  |      | Ω     |

|                                                                                                                        |                   | IOP <sub>_</sub> = -100mA, V <sub>CC_</sub> = +5V ±5%, DC-coupled                                                                                  | 9       | 17  |      |       |

| Low-Side Output Current                                                                                                | I <sub>OL</sub>   | V <sub>CC_</sub> = +12V ±5%, V <sub>OUT\_</sub> - V <sub>NN\_</sub> = 100V                                                                         | 2       |     |      | A     |

| High-Side Output Current                                                                                               | I <sub>OH</sub>   | V <sub>CC_</sub> = +12V ±5%, V <sub>OUT\_</sub> - V <sub>PP\_</sub> = 100V                                                                         | 2       |     |      | A     |

| Off-Output Capacitance                                                                                                 | CO(OFF)           | OP <sub>_</sub> , ON <sub>_</sub> , OCP <sub>_</sub> and OCN <sub>_</sub> connected together; V <sub>PP\_</sub> = +100V, V <sub>NN\_</sub> = -100V | MAX4806 | 110 |      | pF    |

|                                                                                                                        |                   |                                                                                                                                                    | MAX4807 | 70  |      |       |

| Off-Output Leakage Current                                                                                             | I <sub>LK</sub>   | V <sub>NN\_</sub> = -100V, V <sub>PP\_</sub> = 100V, EN <sub>_</sub> = 0, OUT <sub>_</sub> = -100V to +100V                                        | -1      |     | +1   | μA    |

| Low-Side Signal-Clamp Output Impedance                                                                                 | RCLS              | I <sub>OCN\_</sub> = -30mA, DC-coupled, V <sub>CC_</sub> = +12V ±5%, V <sub>EE\_</sub> = -V <sub>CC_</sub>                                         | 20      | 40  |      | Ω     |

|                                                                                                                        |                   | I <sub>OCN\_</sub> = -30mA, DC-coupled, V <sub>CC_</sub> = +5V ±5%, V <sub>EE\_</sub> = -V <sub>CC_</sub>                                          | 20      | 50  |      |       |

| High-Side Signal-Clamp Output Impedance                                                                                | RCHS              | I <sub>OCP\_</sub> = -30mA, DC-coupled, V <sub>CC_</sub> = +12V ±5%, V <sub>EE\_</sub> = -V <sub>CC_</sub>                                         | 20      | 40  |      | Ω     |

|                                                                                                                        |                   | I <sub>OCP\_</sub> = -30mA, DC-coupled, V <sub>CC_</sub> = +5V ±5%, V <sub>EE\_</sub> = -V <sub>CC_</sub>                                          | 33      | 50  |      |       |

| Low-Side Gate Short Impedance                                                                                          | RLSH              | V <sub>CC_</sub> = +12V ±5%, V <sub>EE\_</sub> = -V <sub>CC_</sub> , I <sub>CGN</sub> = 10mA, V <sub>EN\_</sub> = 0                                |         |     | 100  | Ω     |

|                                                                                                                        |                   | V <sub>CC_</sub> = +12V ±5%, V <sub>EE\_</sub> = -V <sub>CC_</sub> , I <sub>CGN</sub> = 10mA, EN <sub>_</sub> = V <sub>DD</sub>                    | 5       | 7.5 | 10   | kΩ    |

| High-Side Gate Short Impedance                                                                                         | RHSH              | V <sub>CC_</sub> = +12V ±5%, V <sub>EE\_</sub> = -V <sub>CC_</sub> , I <sub>CGN</sub> = 10mA, V <sub>EN\_</sub> = 0                                |         |     | 100  | Ω     |

|                                                                                                                        |                   | V <sub>CC_</sub> = +12V ±5%, V <sub>EE\_</sub> = -V <sub>CC_</sub> , I <sub>CGN</sub> = 10mA, EN <sub>_</sub> = V <sub>DD</sub>                    | 5       | 7.5 | 10   | kΩ    |

| <b>THERMAL SHUTDOWN</b>                                                                                                |                   |                                                                                                                                                    |         |     |      |       |

| Thermal Shutdown                                                                                                       | T <sub>SHDN</sub> | Junction temperature rising                                                                                                                        |         |     | +155 | °C    |

| Thermal-Shutdown Hysteresis                                                                                            |                   |                                                                                                                                                    |         |     | 20   | °C    |

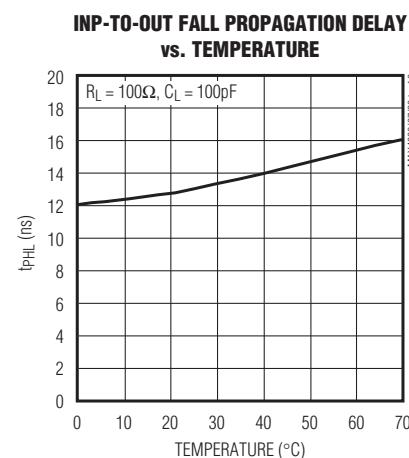

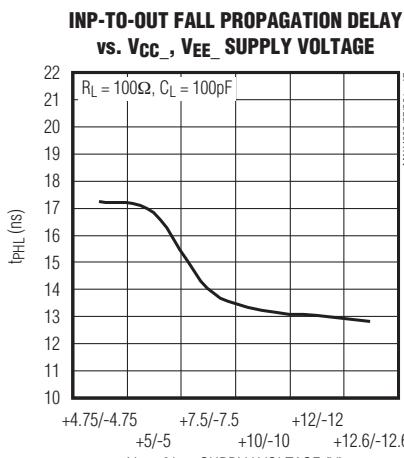

| <b>DYNAMIC CHARACTERISTICS (R<sub>L</sub> = 100Ω, C<sub>L</sub> = 100pF, unless otherwise noted. See Figures 4–7.)</b> |                   |                                                                                                                                                    |         |     |      |       |

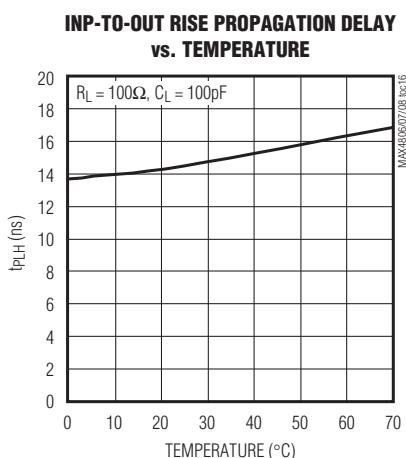

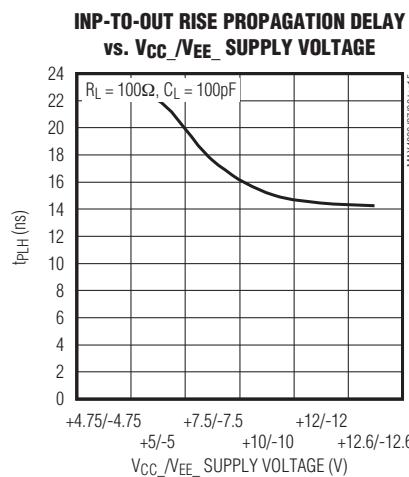

| Logic Input to Output Rise Propagation Delay                                                                           | t <sub>PLH</sub>  | V <sub>CC_</sub> = +12V, V <sub>PP\_</sub> = +5V, V <sub>NN\_</sub> = -5V, Figure 4                                                                |         |     | 15   | ns    |

| Logic Input to Output Fall Propagation Delay                                                                           | t <sub>PHL</sub>  | V <sub>CC_</sub> = +12V, V <sub>PP\_</sub> = +5V, V <sub>NN\_</sub> = -5V, Figure 4                                                                |         |     | 15   | ns    |

| Logic Input to Output Rise Propagation Delay                                                                           | t <sub>POH</sub>  | V <sub>CC_</sub> = +12V, V <sub>PP\_</sub> = +5V, V <sub>NN\_</sub> = -5V, Figure 4                                                                |         |     | 15   | ns    |

| Logic Input to Output Fall Propagation Delay                                                                           | t <sub>POL</sub>  | V <sub>CC_</sub> = +12V, V <sub>PP\_</sub> = +5V, V <sub>NN\_</sub> = -5V, Figure 4                                                                |         |     | 15   | ns    |

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサ

**MAX4806/MAX4807/MAX4808**

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{DD} = +2.7V$  to  $+6V$ ,  $V_{CC\_} = +4.75V$  to  $+12.6V$ ,  $V_{EE\_} = -12.6V$  to  $-4.75V$ ,  $V_{NN\_} = -200V$  to  $0V$ ,  $V_{PP\_} = 0V$  to ( $V_{NN\_} + 200V$ ),  $V_{SS} \leq$  the lower of  $V_{NN1}$  or  $V_{NN2}$ ,  $T_A = T_J$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ .) (Note 3)

| PARAMETER                                          | SYMBOL      | CONDITIONS                                                                                              | MIN | TYP  | MAX | UNITS |

|----------------------------------------------------|-------------|---------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| Logic Input to Output-Rise Propagation Delay Clamp | $t_{PLO}$   | $V_{CC\_} = +12V$ , $V_{PP\_} = +5V$ , $V_{NN\_} = -5V$ , Figure 4                                      |     | 15   |     | ns    |

| Logic Input to Output-Fall Propagation Delay Clamp | $t_{PHO}$   | $V_{CC\_} = +12V$ , $V_{PP\_} = +5V$ , $V_{NN\_} = -5V$ , Figure 4                                      |     | 15   |     | ns    |

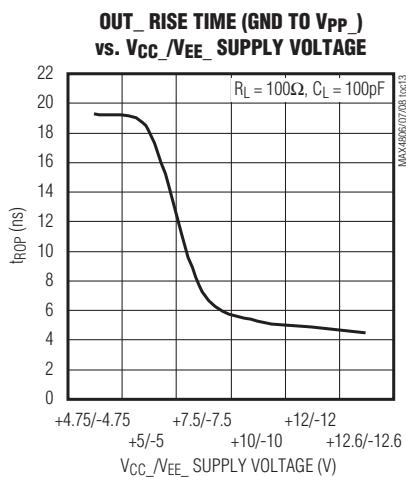

| OUT_Rise Time (GND to $V_{PP\_}$ )                 | $t_{ROP}$   | $V_{PP\_} = +100V$ , $V_{NN\_} = -100V$ , $V_{CC\_} = +12V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$ , Figure 4 |     | 20   |     | ns    |

| OUT_Rise Time ( $V_{NN\_}$ to GND)                 | $t_{RN0}$   | $V_{PP\_} = +100V$ , $V_{NN\_} = -100V$ , $V_{CC\_} = +12V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$ , Figure 4 |     | 35   |     | ns    |

| OUT_Rise Time ( $V_{NN\_}$ to $V_{PP\_}$ )         | $t_{RNP}$   | $V_{PP\_} = +100V$ , $V_{NN\_} = -100V$ , $V_{CC\_} = +12V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$ , Figure 4 |     | 35   |     | ns    |

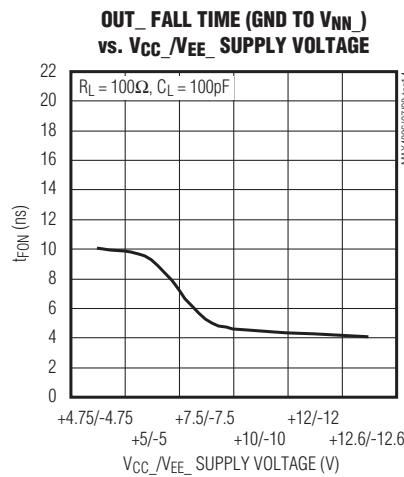

| OUT_Fall Time (GND to $V_{NN\_}$ )                 | $t_{FON}$   | $V_{PP\_} = +100V$ , $V_{NN\_} = -100V$ , $V_{CC\_} = +12V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$ , Figure 4 |     | 20   |     | ns    |

| OUT_Fall Time ( $V_{PP\_}$ to GND)                 | $t_{FP0}$   | $V_{PP\_} = +100V$ , $V_{NN\_} = -100V$ , $V_{CC\_} = +12V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$ , Figure 4 |     | 35   |     | ns    |

| OUT_Fall Time ( $V_{PP\_}$ to $V_{NN\_}$ )         | $t_{FPN}$   | $V_{PP\_} = +100V$ , $V_{NN\_} = -100V$ , $V_{CC\_} = +12V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$ , Figure 4 |     | 35   |     | ns    |

| OUT_Enable Time from EN_ (Figure 5)                | $t_{EN}$    | $V_{CC\_} = +12V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$                                                      |     | 100  |     | ns    |

|                                                    |             | $V_{CC\_} = +5V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$                                                       |     | 150  |     |       |

| OUT_Disable Time from EN_ (Figure 5)               | $t_{DI}$    | $V_{CC\_} = +12V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$                                                      |     | 100  |     | ns    |

|                                                    |             | $V_{CC\_} = +5V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$                                                       |     | 0    | 150 |       |

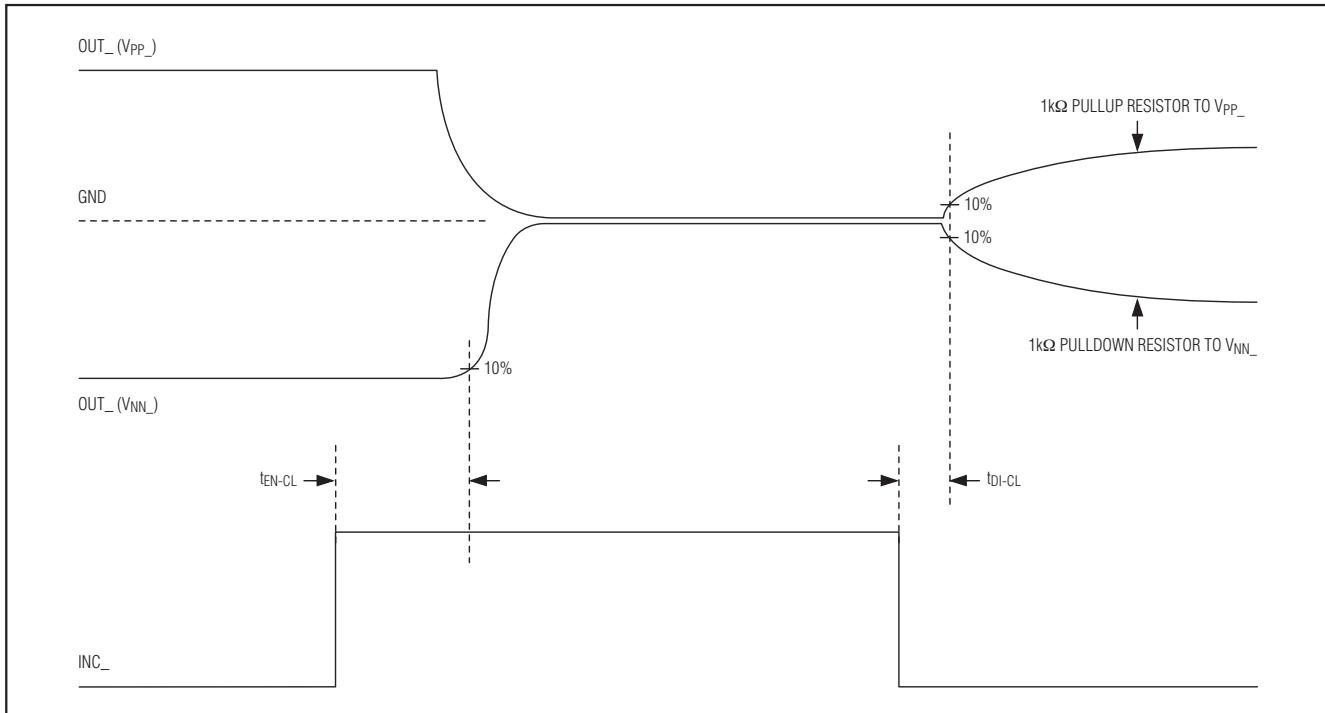

| Clamp Enable Time from INC_                        | $t_{EN-CL}$ | $V_{CC\_} = +12V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$ , Figure 6                                           |     | 150  |     | ns    |

| Clamp Disable Time from INC_                       | $t_{DI-CL}$ | $V_{CC\_} = +12V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$ , Figure 6                                           |     | 0    | 150 | ns    |

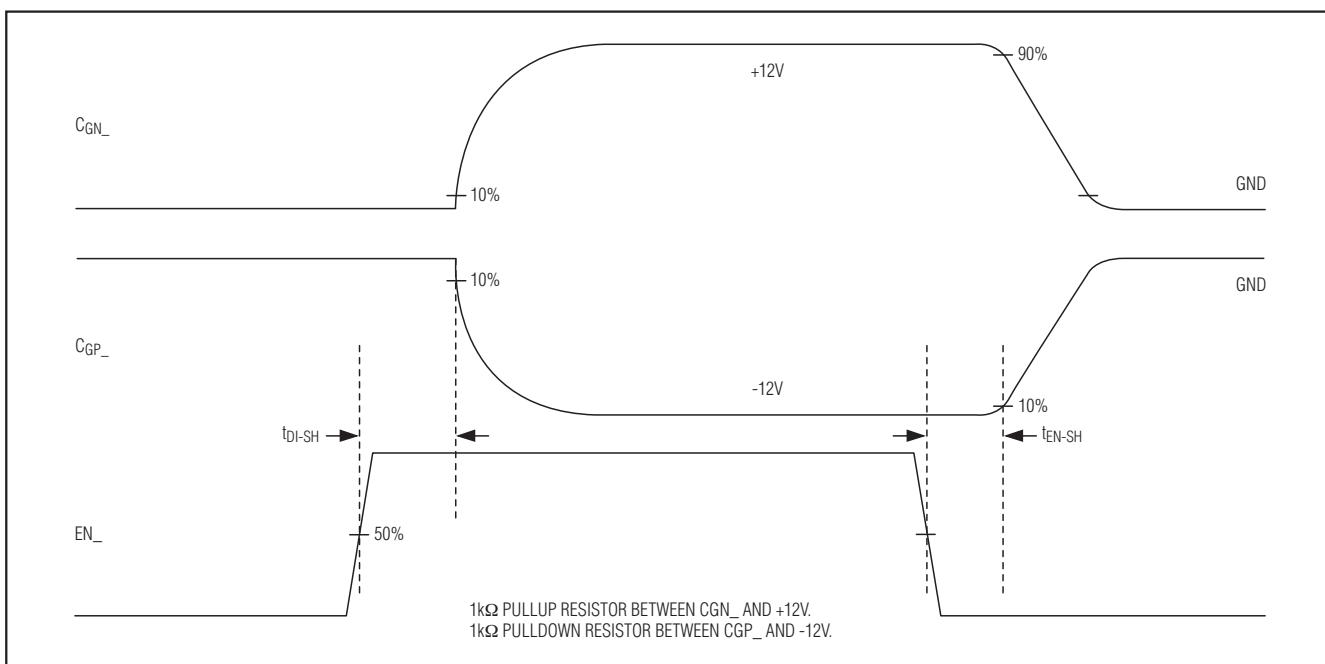

| Short Enable Time from EN_                         | $t_{EN-SH}$ | $V_{PP\_} = +12V$ , $V_{NN\_} = -12V$ , $V_{CC\_} = +12V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$ , Figure 7   |     | 1000 |     | ns    |

| Short Disable Time from EN_                        | $t_{DI-SH}$ | $V_{PP\_} = +12V$ , $V_{NN\_} = -12V$ , $V_{CC\_} = +12V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$ , Figure 7   |     | 250  |     | ns    |

| Recovery Time from SHDN                            |             | $V_{PP\_} = +12V$ , $V_{NN\_} = -12V$ , $V_{CC\_} = +12V \pm 5\%$ , $V_{EE\_} = -V_{CC\_}$              |     | 36.8 |     | ns    |

| Crosstalk                                          |             | $V_{PP\_} = V_{CC\_} = +5V$ , $V_{NN\_} = V_{EE\_} = -5V$ , $f = 5MHz$                                  |     | 69   |     | dB    |

| 2nd Harmonic Distortion                            | 2HD         | $V_{PP\_} = +100V$ , $V_{NN\_} = -100V$ , $f_{OUT} = 5MHz$ , $V_{CC\_} = +12V$                          |     | 40   |     | dB    |

| RMS Output Jitter                                  | $t_J$       | $V_{CC\_} = +12V$                                                                                       |     | 9    |     | ps    |

**Note 3:** Specifications are guaranteed for the stated global conditions, unless otherwise noted and are 100% production tested at  $T_A = +25^\circ C$  and  $T_A = +70^\circ C$ . Specifications at  $T_A = 0^\circ C$  are guaranteed by design.

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサ

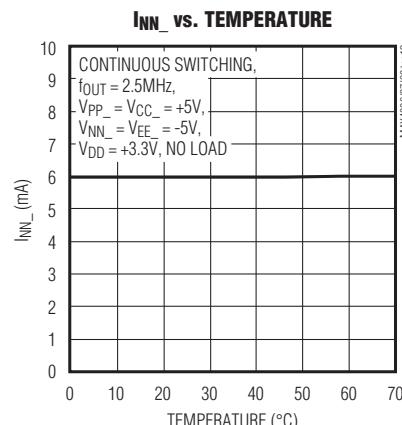

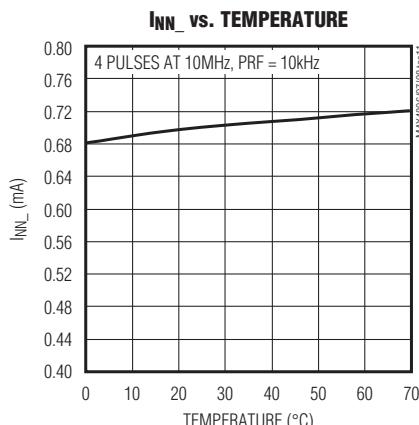

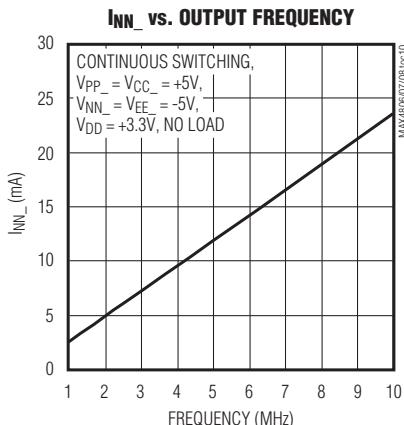

## 標準動作特性

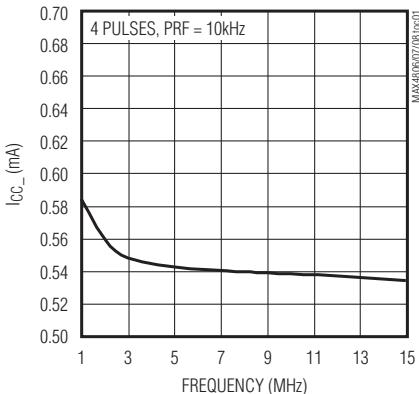

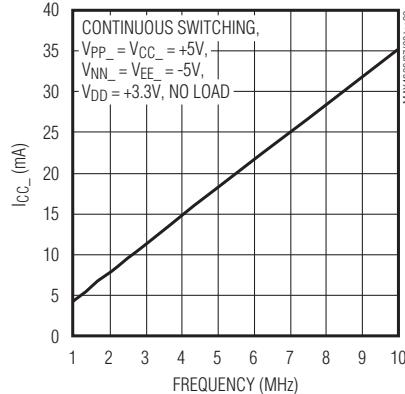

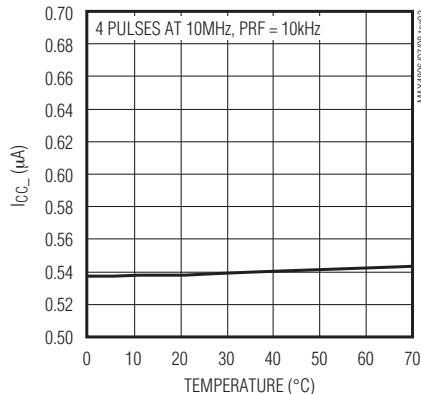

( $V_{DD} = +3.3V$ ,  $V_{CC\_} = +12V$ ,  $V_{EE\_} = -12V$ ,  $V_{SS} = -100V$ ,  $V_{PP\_} = +100V$ ,  $V_{NN\_} = -100V$ ,  $f_{OUT} = 5MHz$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

**I<sub>CC</sub>\_ vs. OUTPUT FREQUENCY**

**I<sub>CC</sub>\_ vs. OUTPUT FREQUENCY**

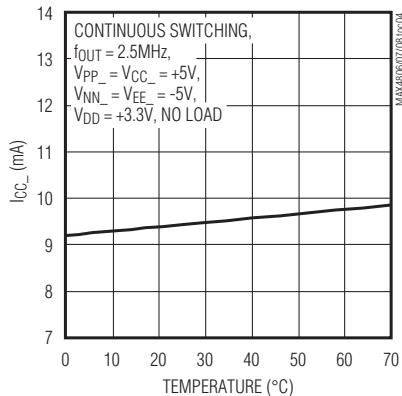

**I<sub>CC</sub>\_ vs. TEMPERATURE**

**I<sub>CC</sub>\_ vs. TEMPERATURE**

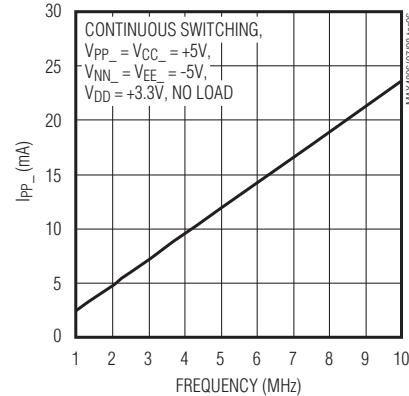

**I<sub>PP</sub>\_ vs. OUTPUT FREQUENCY**

**I<sub>PP</sub>\_ vs. OUTPUT FREQUENCY**

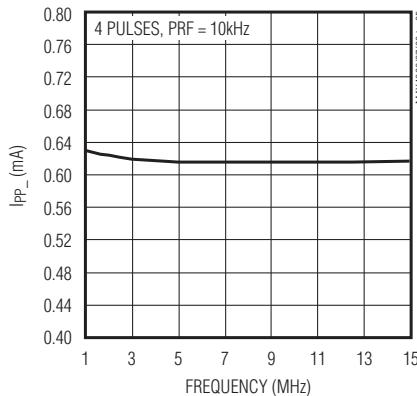

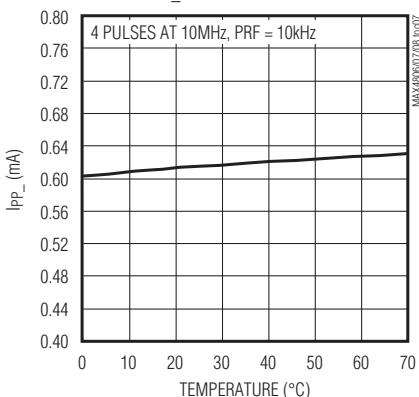

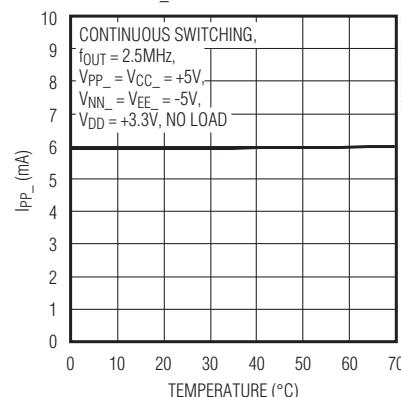

**I<sub>PP</sub>\_ vs. TEMPERATURE**

**I<sub>PP</sub>\_ vs. TEMPERATURE**

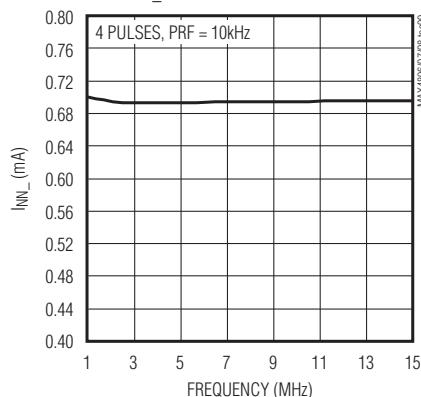

**I<sub>NN</sub>\_ vs. OUTPUT FREQUENCY**

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサ

## 標準動作特性(続き)

( $V_{DD} = +3.3V$ ,  $V_{CC\_} = +12V$ ,  $V_{EE\_} = -12V$ ,  $V_{SS} = -100V$ ,  $V_{PP\_} = +100V$ ,  $V_{NN\_} = -100V$ ,  $f_{OUT} = 5MHz$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサ

## 端子説明

| 端子                       | 名称               | 機能                                                                                                                                                 |

|--------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                        | CGP1             | チャネル1のハイサイドゲート入力。デバイスのできる限り近くで、1nF~10nFのコンデンサをC <sub>DP1</sub> とC <sub>GP1</sub> の間に接続してください。                                                      |

| 2, 3                     | V <sub>PP1</sub> | チャネル1のハイサイド正電源電圧入力。V <sub>PP1</sub> は、デバイスのできる限り近くで、0.1μFのコンデンサでGNDにバイパスしてください(「アプリケーション情報」の項の「電源とバイパス処理」を参照)。アプリケーションによっては、追加のバイパス処理が必要な場合があります。  |

| 4, 10, 33,<br>39         | N.C.             | 接続なし。内部で接続されていません。                                                                                                                                 |

| 5                        | OP1              | チャネル1のハイサイドドレイン出力                                                                                                                                  |

| 6                        | OCP1             | チャネル1のハイサイドクランプ出力                                                                                                                                  |

| 7, 15, 28,<br>36, 44, 55 | GND              | グランド                                                                                                                                               |

| 8                        | OCN1             | チャネル1のローサイドクランプ出力                                                                                                                                  |

| 9                        | ON1              | チャネル1のローサイドドレイン出力                                                                                                                                  |

| 11, 12                   | V <sub>NN1</sub> | チャネル1のローサイド負電源電圧入力。V <sub>NN1</sub> は、デバイスのできる限り近くで、0.1μFのコンデンサでGNDにバイパスしてください(「アプリケーション情報」の項の「電源とバイパス処理」を参照)。アプリケーションによっては、追加のバイパス処理が必要な場合があります。  |

| 13                       | C <sub>GN1</sub> | チャネル1のローサイドゲート入力。デバイスのできる限り近くで、1nF~10nFのコンデンサをC <sub>DN1</sub> とC <sub>GN1</sub> の間に接続してください。                                                      |

| 14                       | C <sub>DN1</sub> | チャネル1のローサイドドライバ出力。デバイスのできる限り近くで、1nF~10nFのコンデンサをC <sub>DN1</sub> とC <sub>GN1</sub> の間に接続してください。                                                     |

| 16, 54                   | V <sub>CC1</sub> | チャネル1のゲートドライブ電源電圧入力。V <sub>CC1</sub> は、デバイスのできる限り近くで、0.1μFのコンデンサでGNDにバイパスしてください(「アプリケーション情報」の項の「電源とバイパス処理」を参照)。出力によっては、追加のバイパス処理が必要な場合があります。       |

| 17                       | INN1             | チャネル1のローサイドロジック入力(表1を参照)                                                                                                                           |

| 18                       | INC1             | チャネル1のクランプロジック入力。INC1がハイで、かつINP1とINN1がローのとき、クランプOCP1とOCN1はオンになります(表1を参照)。                                                                          |

| 19                       | INP1             | チャネル1のハイサイドロジック入力(表1を参照)                                                                                                                           |

| 20                       | EN1              | チャネル1のイネーブルロジック入力。OP1とON1をイネーブルするには、EN1をハイにしてください。ゲート-ソース間の短絡回路をオンにするには、EN1をローにプルダウンしてください(表1を参照)。                                                 |

| 21                       | SHDN             | シャットダウンロジック入力(表1を参照)                                                                                                                               |

| 22                       | AGND             | アナロググランド。共通GNDに接続する必要があります。                                                                                                                        |

| 23                       | EN2              | チャネル2のイネーブルロジック入力。OP2とON2をイネーブルするには、EN2をハイにしてください。ゲート-ソース間の短絡をオンにするには、EN2をローにプルダウンしてください(表1を参照)。                                                   |

| 24                       | INP2             | チャネル2のハイサイドロジック入力(表1を参照)                                                                                                                           |

| 25                       | INC2             | チャネル2のクランプロジック入力。INC2がハイで、かつINP2とINN2がローのとき、クランプOCP2とOCN2はオンになります(表1を参照)。                                                                          |

| 26                       | INN2             | チャネル2のローサイドロジック入力(表1を参照)                                                                                                                           |

| 27, 45                   | V <sub>CC2</sub> | チャネル2のゲートドライブ電源電圧入力。V <sub>CC2</sub> は、デバイスのできる限り近くで、0.1μFのコンデンサでGNDにバイパスしてください(「アプリケーション情報」の項の「電源とバイパス処理」を参照)。アプリケーションによっては、追加のバイパス処理が必要な場合があります。 |

| 29                       | C <sub>DN2</sub> | チャネル2のローサイドドライバ出力。デバイスのできる限り近くで、1nF~10nFのコンデンサをC <sub>DN2</sub> とC <sub>GN2</sub> の間に接続してください。                                                     |

| 30                       | C <sub>GN2</sub> | チャネル2のローサイドゲート入力。デバイスのできる限り近くで、1nF~10nFのコンデンサをC <sub>DN2</sub> とC <sub>GN2</sub> の間に接続してください。                                                      |

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサ

## 端子説明(続き)

| 端子     | 名称               | 機能                                                                                                                                                               |

|--------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31, 32 | VNN2             | チャネル2のローサイド負電源電圧入力。 $V_{NN2}$ は、デバイスのできる限り近くで、 $0.1\mu F$ のコンデンサでGNDにバイパスしてください(「アプリケーション情報」の項の「電源とバイパス処理」を参照)。アプリケーションによっては、追加のバイパス処理が必要な場合があります。               |

| 34     | ON2              | チャネル2のローサイドドレイン出力                                                                                                                                                |

| 35     | OCN2             | チャネル2のローサイドクランプ出力                                                                                                                                                |

| 37     | OCP2             | チャネル2のハイサイドクランプ出力                                                                                                                                                |

| 38     | OP2              | チャネル2のハイサイドドレイン出力                                                                                                                                                |

| 40, 41 | VPP2             | チャネル2のハイサイド正電源電圧入力。 $V_{PP2}$ は、デバイスのできる限り近くで、 $0.1\mu F$ のコンデンサでGNDにバイパスしてください(「アプリケーション情報」の項の「電源とバイパス処理」を参照)。アプリケーションによっては、追加のバイパス処理が必要な場合があります。               |

| 42     | C <sub>GP2</sub> | チャネル2のハイサイドゲート入力。デバイスのできる限り近くで、 $1nF \sim 10nF$ のコンデンサをC <sub>DP2</sub> とC <sub>GP2</sub> の間に接続してください。                                                           |

| 43     | C <sub>DP2</sub> | チャネル2のハイサイドドライバ出力。デバイスのできる限り近くで、 $1nF \sim 10nF$ のコンデンサをC <sub>DP2</sub> とC <sub>GP2</sub> の間に接続してください。                                                          |

| 46     | C <sub>GC2</sub> | チャネル2のハイサイドクランプゲート入力。デバイスのできる限り近くで、 $1nF \sim 10nF$ のコンデンサをC <sub>DC2</sub> とC <sub>GC2</sub> の間に接続してください。                                                       |

| 47     | C <sub>DC2</sub> | チャネル2のハイサイドクランプドライバ出力。デバイスのできる限り近くで、 $1nF \sim 10nF$ のコンデンサをC <sub>DC2</sub> とC <sub>GC2</sub> の間に接続してください。                                                      |

| 48     | V <sub>EE2</sub> | チャネル2の負電源入力。OCP2クランプのゲートドライブ電源電圧。 $V_{EE2}$ は、デバイスのできる限り近くで、 $0.1\mu F$ のコンデンサでGNDにバイパスしてください(「アプリケーション情報」の項の「電源とバイパス処理」を参照)。アプリケーションによっては、追加のバイパス処理が必要な場合があります。 |

| 49     | V <sub>DD</sub>  | ロジック電源電圧入力。 $V_{DD}$ は、デバイスのできる限り近くで、 $0.1\mu F$ のコンデンサでGNDにバイパスしてください(「アプリケーション情報」の項の「電源とバイパス処理」を参照)。アプリケーションによっては、追加のバイパス処理が必要な場合があります。                        |

| 50     | V <sub>SS</sub>  | 基板電圧。 $V_{NN1}$ と $V_{NN2}$ のうち負の値の大きい方に等しいか、あるいはさらに負の値の大きい電圧をV <sub>SS</sub> に接続してください。                                                                         |

| 51     | V <sub>EE1</sub> | チャネル1の負電源入力。OCP1クランプのゲートドライブ電源電圧。 $V_{EE1}$ は、デバイスのできる限り近くで、 $0.1\mu F$ のコンデンサでGNDにバイパスしてください(「アプリケーション情報」の項の「電源とバイパス処理」を参照)。アプリケーションによっては、追加のバイパス処理が必要な場合があります。 |

| 52     | C <sub>DC1</sub> | チャネル1のハイサイドクランプドライバ出力。デバイスのできる限り近くで、 $1nF \sim 10nF$ のコンデンサをC <sub>DC1</sub> とC <sub>GC1</sub> の間に接続してください。                                                      |

| 53     | C <sub>GC1</sub> | チャネル1のハイサイドクランプゲート入力。デバイスのできる限り近くで、 $1nF \sim 10nF$ のコンデンサをC <sub>DC1</sub> とC <sub>GC1</sub> の間に接続してください。                                                       |

| 56     | C <sub>DP1</sub> | チャネル1のハイサイドドライバ出力。デバイスのできる限り近くで、 $1nF \sim 10nF$ のコンデンサをC <sub>DP1</sub> とC <sub>GP1</sub> の間に接続してください。                                                          |

| —      | EP               | エクスポートドバッド。EPはV <sub>SS</sub> に接続する必要があります。EPをデバイスの唯一のV <sub>SS</sub> 接続として使用しないでください。                                                                           |

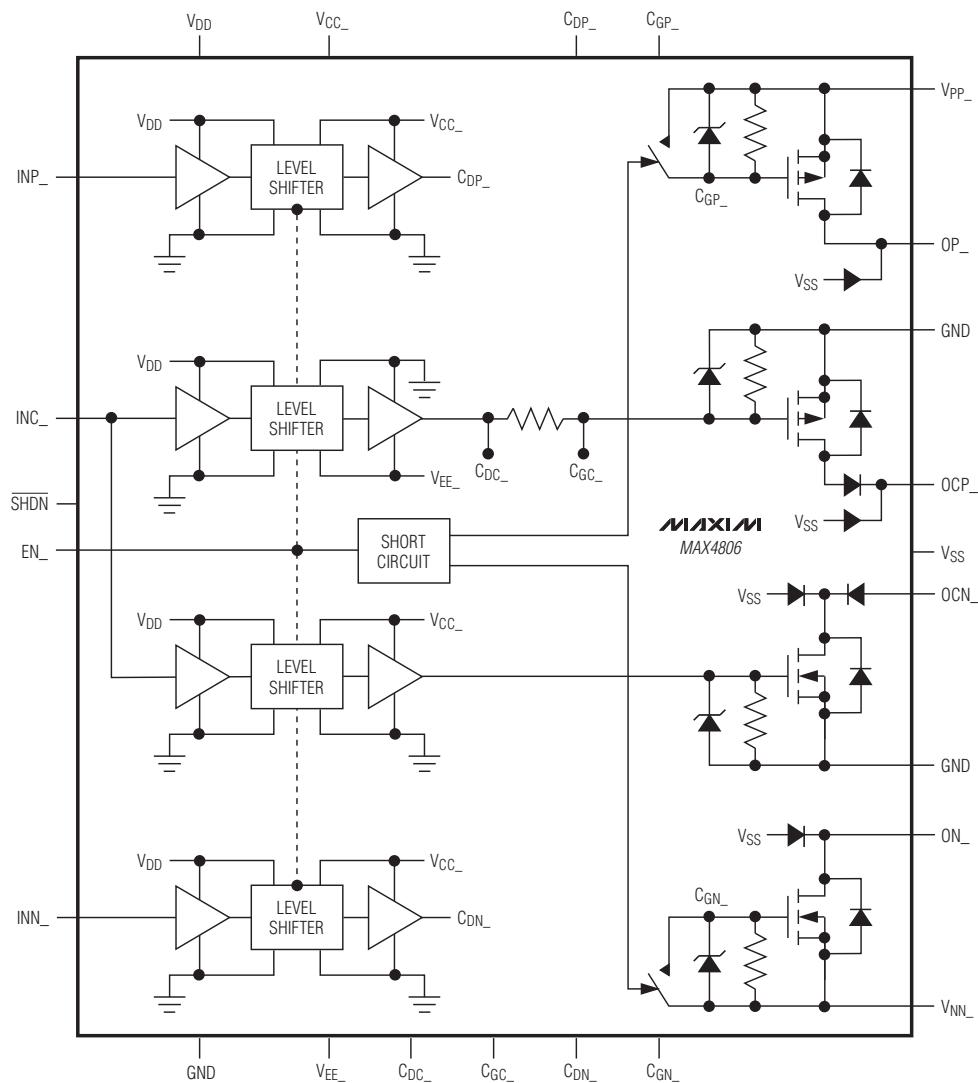

## 詳細

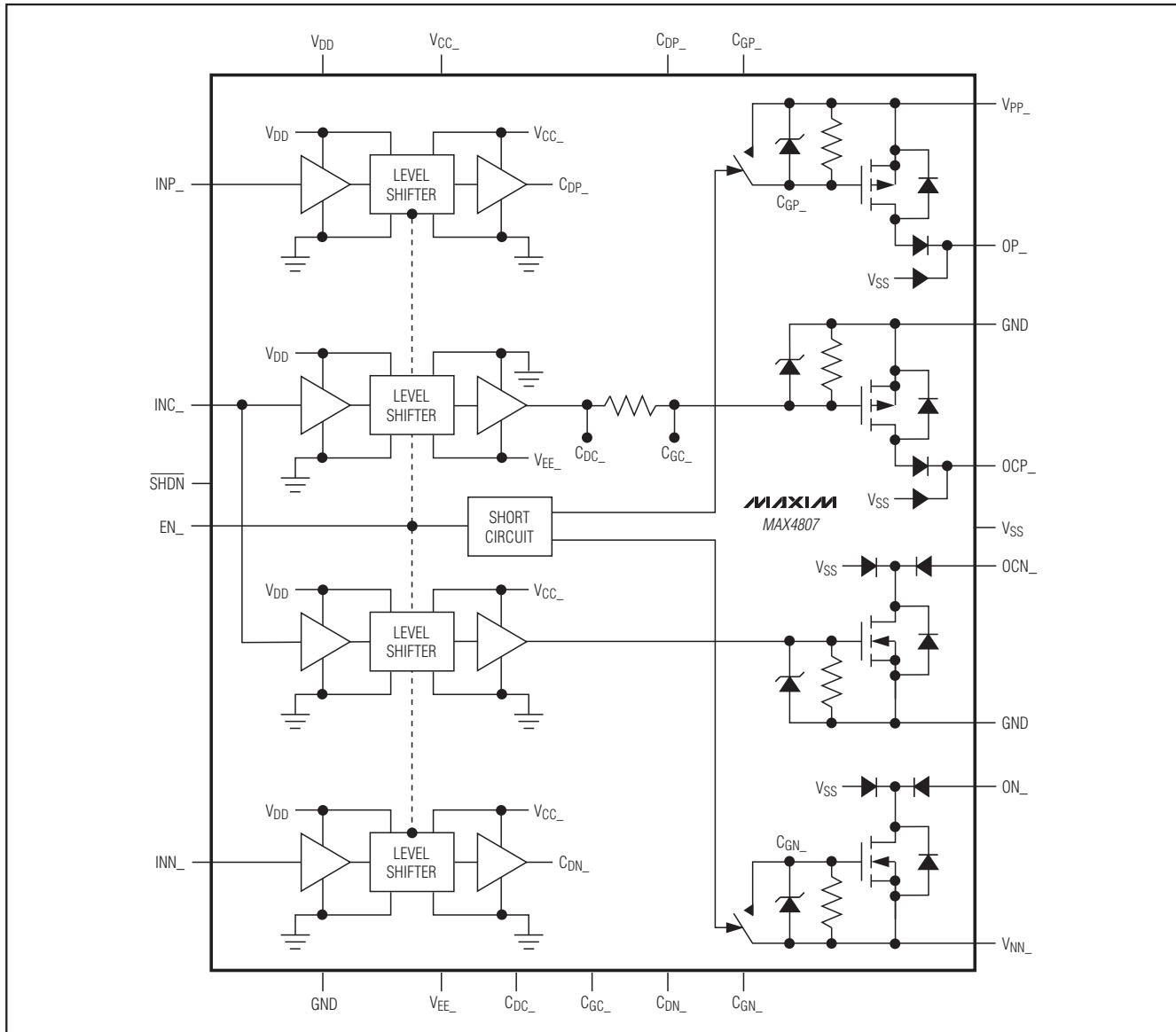

MAX4806/MAX4807/MAX4808は、高電圧で高速なデュアルパルサであり、ユニポーラまたはバイポーラのパルス出力用に独立して構成することができます。これらのデバイスは、完全なパルス制御が行えるように独立したロジック入力と、独立したアクティブクランプを備えています。デバイスが正または負の高電圧電源についてパルス動作していないとき、クランプ入力INC\_をハイに設定してクランプを自動的に起動することができます(図1、2、および3を参照)。

### ロジック入力(INP\_、INN\_、INC\_、EN\_、SHDN)

MAX4806/MAX4807/MAX4808には、合計9つのロジック入力信号があります。SHDNは、デバイスのパワーアップとパワーダウンを制御します。チャネルごとに1セット、計2セットのINP\_、INN\_、INC\_、およびEN\_信号があります。INP\_はハイサイドFETのオン/オフ状態を、INN\_はローサイドFETのオン/オフ状態を、INC\_はアクティブクランプを、EN\_はゲートソース間の短絡を制御します。これらの信号は、各ドライバの出力段を完全に制御します(ロジックのすべての組み合わせについては、表1を参照)。

MAX4806/MAX4807/MAX4808

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサ

表1. 真理値表

| INPUTS |     |      |      |      | OUTPUTS           |                   |                | STATE                                                        |

|--------|-----|------|------|------|-------------------|-------------------|----------------|--------------------------------------------------------------|

| SHDN   | EN_ | INP_ | INN_ | INC_ | OP_               | ON_               | OCP_-, OCN_-   |                                                              |

| 0      | X   | X    | X    | 0    | High Impedance    | High Impedance    | High Impedance | Powered down, INP_/INN_ disabled, gate-source short disabled |

| 0      | X   | X    | X    | 1    | High Impedance    | High Impedance    | GND            | Powered down, INP_/INN_ disabled, gate-source short disabled |

| 1      | 0   | X    | X    | 0    | High Impedance    | High Impedance    | High Impedance | Powered up, INP_/INN_ disabled, gate-source short enabled    |

| 1      | 0   | X    | X    | 1    | High Impedance    | High Impedance    | GND            | Powered up, INP_/INN_ disabled, gate-source short enabled    |

| 1      | 1   | 0    | 0    | 0    | High Impedance    | High Impedance    | High Impedance | Powered up, all inputs enabled, gate-source short disabled   |

| 1      | 1   | 0    | 0    | 1    | High Impedance    | High Impedance    | GND            | Powered up, all inputs enabled, gate-source short disabled   |

| 1      | 1   | 0    | 1    | X    | High Impedance    | V <sub>NN</sub> _ | High Impedance | Powered up, all inputs enabled, gate-source short disabled   |

| 1      | 1   | 1    | 0    | X    | V <sub>PP</sub> _ | High Impedance    | High Impedance | Powered up, all inputs enabled, gate-source short disabled   |

| 1      | 1   | 1    | 1    | X    | V <sub>PP</sub> _ | V <sub>NN</sub> _ | High Impedance | Not allowed (3ns maximum overlap)                            |

X = 任意

0 = ロジックロー

1 = ロジックハイ

MAX4806/MAX4807/MAX4808のロジック入力はCMOSロジック互換であり、またロジックレベルはV<sub>DD</sub>を基準としているため、極めて柔軟な対応が可能です。ロジック入力の入力容量は5pF (typ)と低いため、負荷が低減され、スイッチング速度が速くなります。

## 高電圧出力保護(MAX4807のみ)

MAX4807の高電圧出力は、複数のパルサチャネル出力を並列に接続することでマルチレベルパルスシングの装備を可能にする過電圧保護回路を内蔵しています。ON\_とOP\_出力に直列の内部ダイオードは、V<sub>NN</sub>\_またはV<sub>PP</sub>\_よりも高い電圧が出力上に存在するときにハイサイドFETとローサイドFETのボディダイオードがオンに切り替わらないようにしています(図9を参照)。

## アクティブクランプ

MAX4806/MAX4807/MAX4808は、パルスの品質を改善して2次高調波出力を低減するアクティブクランプ回路を備えています。クランプ回路は、ロジッククランプ入力(INC\_)によってオン/オフが切り替わる、nチャネル(DC結合)とpチャネル(ACおよびDCの遅延

結合)の高電圧FETで構成されています。MAX4806とMAX4807は保護クランプデバイスを備え、バイポーラパルス回路でクランプ回路を使用することができます(図1および2を参照)。OCN\_出力と直列のダイオードは、GNDよりも低い電圧が存在するときにローサイドFETのボディダイオードがオンにならないようにしています。OCP\_出力と直列のもう1つのダイオードは、グランドよりも高い電圧が存在するときにハイサイドFETのボディダイオードがオンにならないようにしています。MAX4808には、クランプ出力に対するダイオード保護はありません。したがって、このデバイスはユニポーラパルスのみを必要とする回路に適しています。

アクティブクランプ入力(INC\_)をロジックハイの電圧に接続してINP\_とINN\_の入力のみを駆動することで、デバイスの駆動に使用する信号の数を最小限に抑えることができます。この場合、INP\_とINN\_の入力がどちらもロー、INC\_入力がハイのときは必ず、アクティブクランプ回路は、OCP\_およびOCN\_出力を通じて出力をGNDにプルダウンします(詳細については、表1を参照)。

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサ

MAX4806/MAX4807/MAX4808

**電源電圧のランピングとゲート-ソース間の短絡回路**

MAX4806/MAX4807/MAX4808には、イネーブル入力(EN\_)で制御するゲート-ソース間の短絡回路が備わっています。SHDNがハイでEN\_がローのとき、60Ωのスイッチはハイサイド出力FETのゲートとソースを短絡します。同時に、類似のスイッチがローサイド出力FETのゲートとソースを短絡します(表1)。ゲート-ソース間の短絡回路は、V<sub>PP</sub>\_とV<sub>NN</sub>\_でのランピング電圧によって出力FETが誤ってオンになることを防止しており、ランピングの高速化やパルスモード間の短い遅延に対応することができます。

## シャットダウンモード

SHDNはチャネル1とチャネル2に共通であり、デバイスのパワーアップとパワーダウンを行います。SHDNをローに駆動すると、すべての内部回路がパワーダウンされます(クランプ回路を除く)。SHDNがローのとき、デバイスは最小電力状態(1μA)になり、ゲート-ソース間の短絡回路はディセーブルになります。SHDNがディセーブルになると、デバイスがアクティブになるのに36.8ns (typ)かかります。

## 熱保護

標準スレッショルドが+155°Cのサーマルシャットダウン回路は、過剰な電力消費によって生じる損傷を防ぎます。接合部温度がT<sub>J</sub> = +150°Cを超えると、すべての出力はディセーブルになります。ICの接合部温度が+130°C未満に低下すれば、通常の動作が再開されます。

## アプリケーション情報

### ACカップリングコンデンサの選択

ACカップリングコンデンサ(C<sub>DP</sub>\_とC<sub>GP</sub>\_の間、およびC<sub>DN</sub>\_とC<sub>GN</sub>\_の間)の値は、1nF~10nFにする必要があります。コンデンサの定格電圧は、V<sub>PP</sub>\_およびV<sub>NN</sub>\_よりも大きくする必要があります。コンデンサはデバイスのできる限り近くに配置する必要があります。

INP\_およびINC\_の一部は、出力デバイスにAC結合されているため、デバイスがアクティブのときに無制限にハイにすることはできません。

## 電力消費

MAX4806/MAX4807/MAX4808の電力消費は、V<sub>CC</sub>\_、V<sub>PP</sub>\_、およびV<sub>NN</sub>\_の電流消費によって生じる3つの主要な要素で構成されます。これらの要素(P<sub>VCC</sub>、P<sub>VPP</sub>、およびP<sub>VNN</sub>)の合計を電力消費の最大許容限度よりも低く抑える必要があります。標準消費電流 対 スイッ

チング周波数の詳細については、「標準動作特性」の項を参照してください。

デバイスは、V<sub>CC</sub>\_電源の供給電流の大部分を、ハイサイドFET (C<sub>P</sub>)とローサイドFET (C<sub>N</sub>)のゲート容量などの内部ノードの充放電に消費します。少量の自己消費電流と内部ゲートクランプFETの容量の充放電で使用する少量の電流を無視すれば、消費電力は、次式で概算することができます。

$$P_{VCC} = \left[ (C_N \times V_{CC}^2 \times f_{IN}) + (C_P \times V_{CC}^2 \times f_{IN}) \right] \times (BRF \times BTD)$$

$$f_N = f_{INN} = f_{INP}$$

ここで、f<sub>INN</sub> と f<sub>INP</sub> は、それぞれINN\_とINP\_の入力スイッチング周波数、BRFはバースト繰り返し周波数、およびBTDはバースト継続時間です。パワーFETのゲート容量の標準値は、C<sub>N</sub> = 0.3μFおよびC<sub>P</sub> = 0.6μFです。

抵抗分がR<sub>L</sub>で容量分がC<sub>L</sub>の出力負荷の場合、MAX4806/MAX4807/MAX4808の電力消費は、次式で概算することができます(出力が方形波であるものと仮定し、スイッチの抵抗分を無視します)。

$$P_{VPP} = \left[ (C_O + C_L) \times f_{IN} \times (V_{PP} - V_{NN})^2 \right] + \left[ \frac{V_{PP}^2}{R_L} \times \frac{1}{2} \right] \times (BRF \times BTD)$$

ここで、C<sub>O</sub>はデバイスの出力容量です。

## 電源とバイパス処理

MAX4806/MAX4807/MAX4808は、独立した電源電圧のセットで動作します(V<sub>DD</sub>とV<sub>SS</sub>のみ、両方のチャネルに共通です)。ロジック入力回路は、+2.7V~+6Vの単一電源(V<sub>DD</sub>)で動作します。レベルシフトドライバのデュアル電源V<sub>CC</sub>\_ / V<sub>EE</sub>\_は、±4.75V~±12.6Vで動作します。

V<sub>PP</sub>\_ / V<sub>NN</sub>\_のハイサイドとローサイドの電源は、最大+220Vの単一正電源、最大-200Vの単一負電源、または±110Vのデュアル電源です。V<sub>PP</sub>\_またはV<sub>NN</sub>\_のいずれかは、0Vに設定することができます。各電源入力は、デバイスのできる限り近くで、0.1μFのコンデンサでグランドにバイパスしてください。

出力遷移の間V<sub>NN</sub>\_とV<sub>PP</sub>\_の両方の入力を安定させるため、アプリケーションによっては、追加のバイパス処理が必要な場合があります。たとえば、C<sub>OUT</sub> = 100pFおよびR<sub>OUT</sub> = 100Ωの負荷では、10μF (typ)の電解コンデンサを追加することをお勧めします。V<sub>SS</sub>はサブストレートの電圧です。V<sub>NN1</sub>とV<sub>NN2</sub>の電圧のうち低い方に等しいか、あるいはさらに負の値の大きい方にV<sub>SS</sub>を接続します。

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサ

図1. MAX4806の簡略化ファンクションダイアグラム(1チャネルの場合)

## エクスポートドパッドとレイアウトについて

MAX4806/MAX4807/MAX4808では、放熱性能を改善するために、TQFNパッケージの底にエクスポートドパッド(EP)が設けられています。EPは、内部でV<sub>SS</sub>に接続されています。外部でEPをV<sub>SS</sub>に接続します。放熱を促進するため、PCBの部品面にあるほぼ同じサイズのパッドにEPを接続します。デバイスから伝導で熱を取り除くために、このパッドは、熱拡散用の広い銅領域に通じるメッキ処理された複数のスルーホールを通して、半田面の銅に接続する必要があります。

MAX4806/MAX4807/MAX4808の高速パルサでは、電源入力への低インダクタンスのバイパスコンデンサが必要になります。高速PCBのトレース設計を実施することをお勧めします。インダクタンスを低減するため、トレース長を最小限にして十分なトレース幅を使用するよう特に注意してください。表面実装部品の使用をお勧めします。

# デュアル、ユニポーラ/バイポーラ、高電圧ディジタルパルサ

**MAX4806/MAX4807/MAX4808**

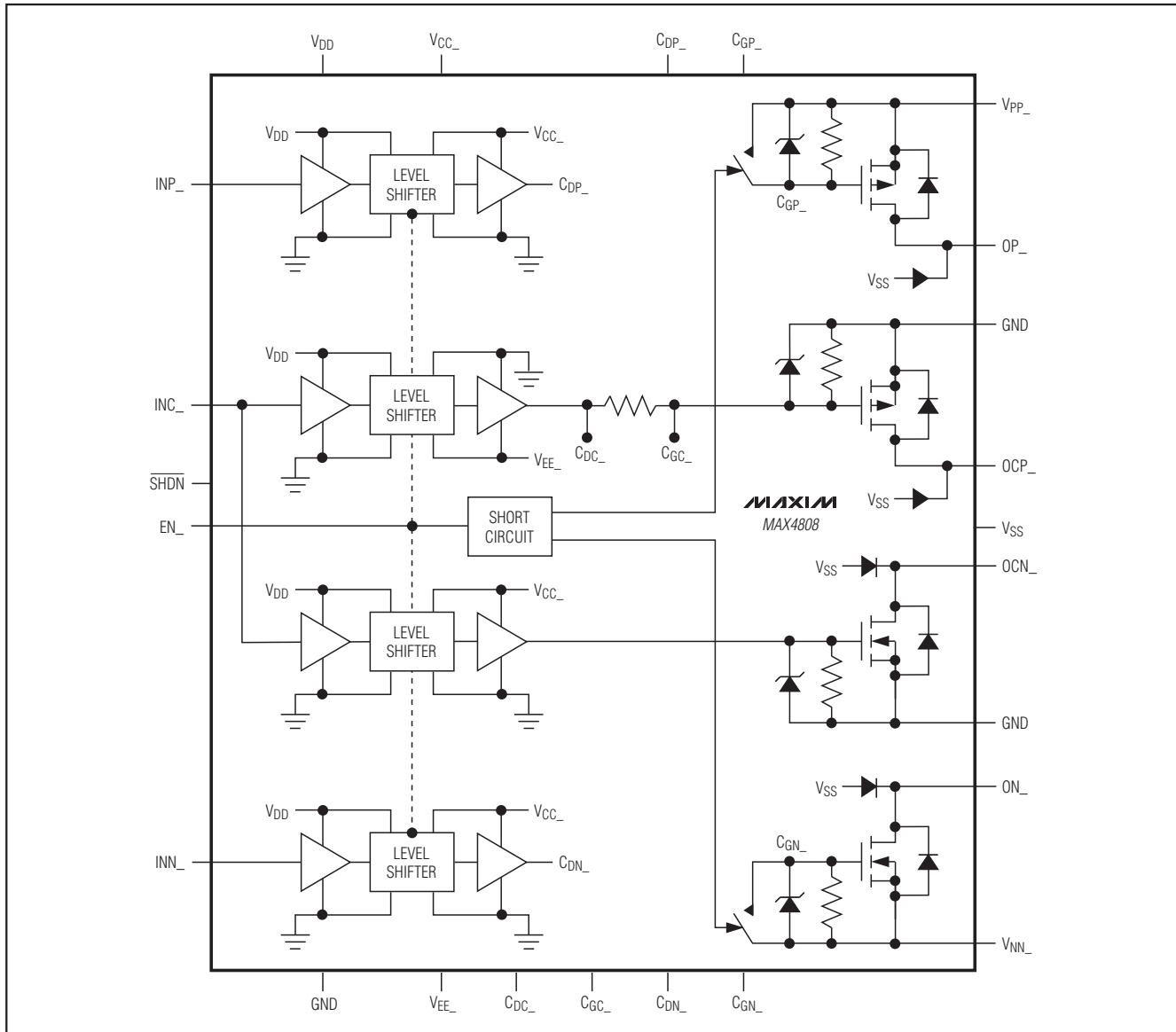

図2. MAX4807の簡略化ファンクションダイアグラム(1チャネルの場合)

## 電源シーケンシング

V<sub>SS</sub>は常に、V<sub>NN1</sub>とV<sub>NN2</sub>のうち負の値の大きい方の電圧以下でなければなりません。また、他の電源電圧の前にオンにする必要があります。MAX4806/MAX4807/MAX4808では、その他の電源シーケンシングは必要ありません。

## 標準アプリケーション回路

図8、9および10は、MAX4806/MAX4807/MAX4808の標準アプリケーション回路を示しています。図8は、バイポーラパルス接続で使用されるMAX4806を示しています。図9は、5レベルのパルスアプリケーションにおけるMAX4807を、図10は、ユニポーラアプリケーションで使用されるMAX4808を示しています。

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサ

図3. MAX4808の簡略化ファンクションダイアグラム(1チャネルの場合)

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサ

**MAX4806/MAX4807/MAX4808**

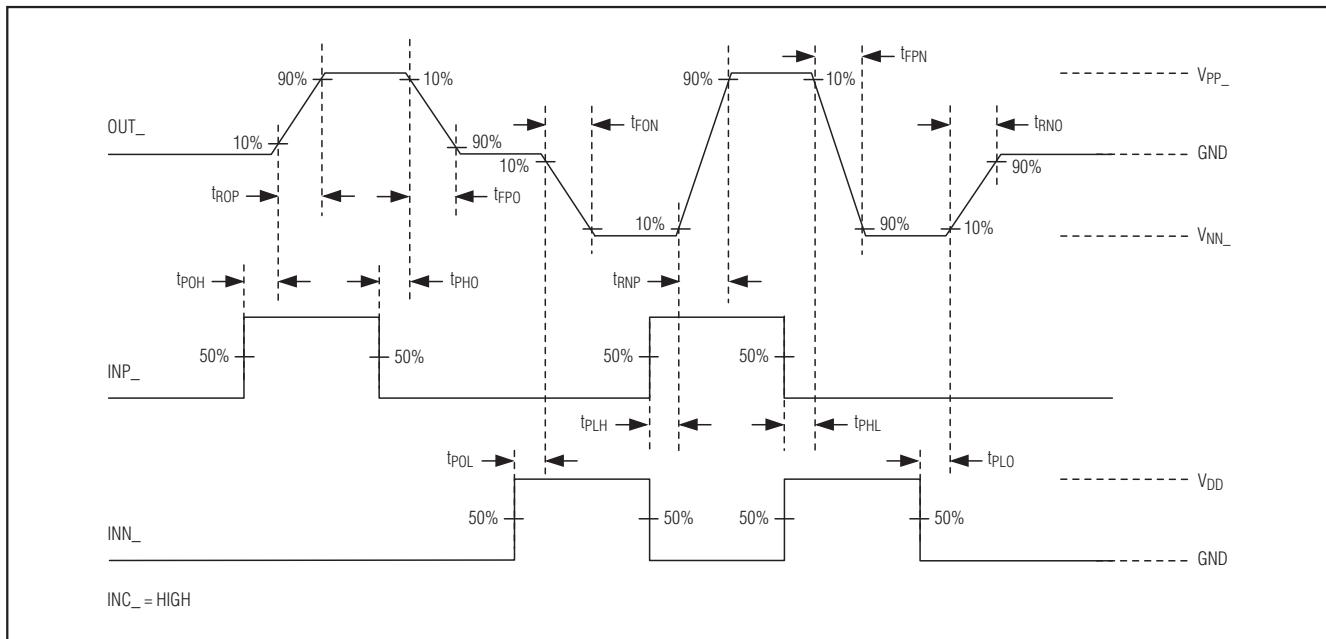

図4. タイミングの詳細( $R_L = 100\Omega$ 、 $C_L = 100\text{pF}$ )

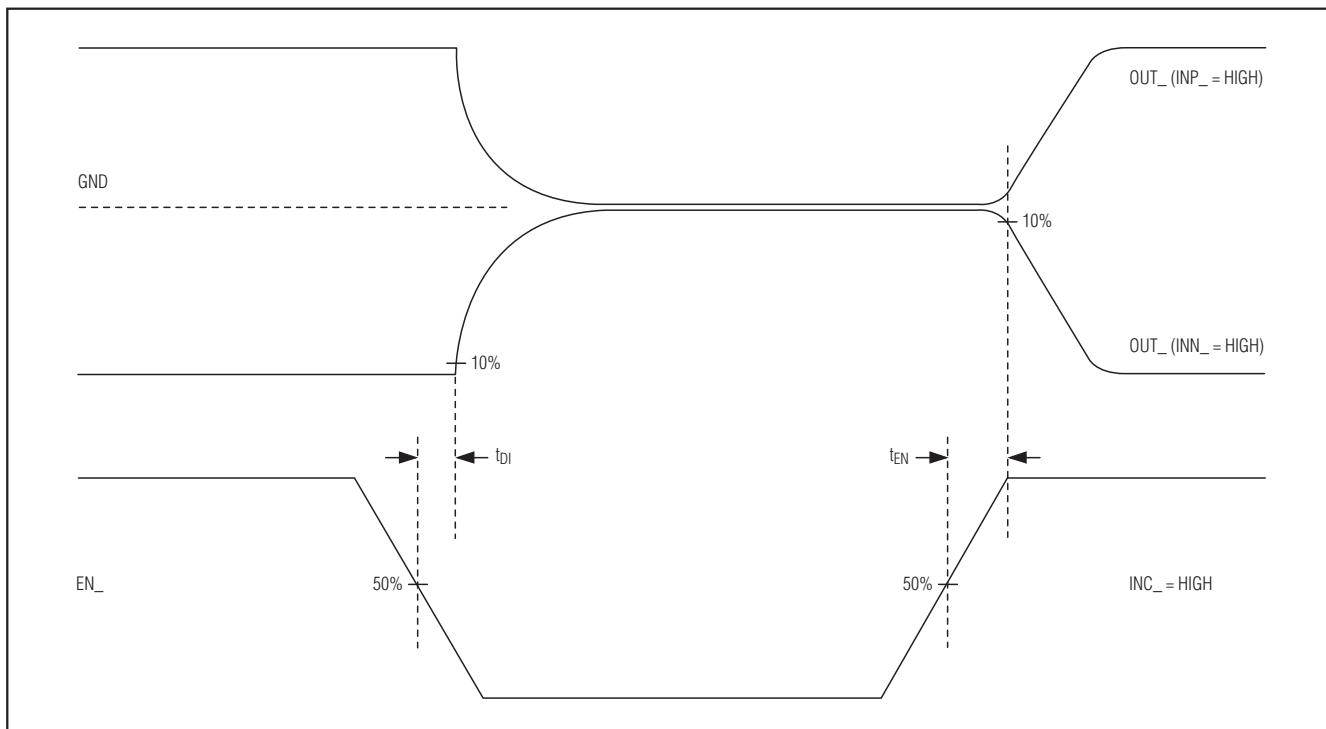

図5. イネーブルのタイミング( $R_L = 100\Omega$ 、 $C_L = 100\text{pF}$ )

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサ

図6. アクティブクランプのタイミング

図7. 短絡のタイミング

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサ

**MAX4806/MAX4807/MAX4808**

図8. MAX4806 : デュアルバイポーラパルス、±100V、GND

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサ

**MAX4806/MAX4807/MAX4808**

図9. MAX4807 : 5レベルのパルス、±100V、±50V、GND

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサ

**MAX4806/MAX4807/MAX4808**

図10. MAX4808 : デュアルユニポーラ/パルス、+100V、GND

# デュアル、ユニポーラ/バイポーラ、 高電圧ディジタルパルサ

## パッケージ

最新のパッケージ情報とランドパターンは、[japan.maxim-ic.com/packages](http://japan.maxim-ic.com/packages)をご参照ください。

| パッケージタイプ | パッケージコード | ドキュメントNo.      |

|----------|----------|----------------|

| 56 TQFN  | T5677-1  | <b>21-0144</b> |

**マキシム・ジャパン株式会社**

〒169-0051 東京都新宿区西早稲田3-30-16(ホリゾン1ビル)

TEL. (03)3232-6141 FAX. (03)3232-6149

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。マキシムは隨時予告なく回路及び仕様を変更する権利を留保します。

20 **Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600**

© 2008 Maxim Integrated Products

Maxim is a registered trademark of Maxim Integrated Products, Inc.