# MIXIM

### 低電圧、高アイソレーション、 デュアル、4チャネルRF/ビデオマルチプレクサ

### 概要

MAX4588は、50 及び75 機器において最大180MHz の周波数でRF及びビデオ信号を処理するために設計され た低電圧デュアル4チャネルマルチプレクサです。フレ キシブルなディジタルインタフェースにより、パラレ ルインタフェース又はSPI™/MICROWIRE™シリアル ポートを通じて内部の制御が可能です。

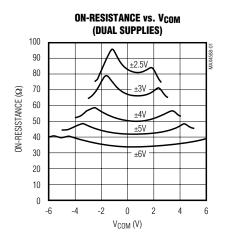

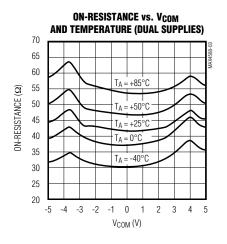

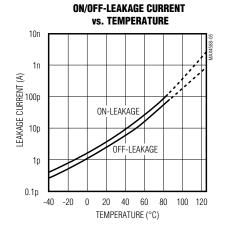

MAX4588の各チャネルはT型スイッチ構成を使って 設計されているため、優れた高周波数オフアイソレー ションを提供します。MAX4588はオン抵抗が60 (max)と低く、全チャネルのオン抵抗マッチングが4 (max)となっています。さらに、オン抵抗は指定信号範 囲にわたって平坦(2 max)です。オフリーク電流は  $T_A = +25$  で1nA以下、 $T_A = +85$  で10nA以下です。

MAX4588は+2.7V~+12V単一電源又は±2.7V~±6V デュアル電源で動作します。+5V電源で動作する場合、 入力はTTL及びCMOSとコンパチブルです。MAX4588 は28ピンナローDIP、ワイドSOP及び省スペースの SSOPパッケージで供給されています。

### アプリケーション

RFスイッチング

自動試験機器

ビデオ信号分配

ネットワーク

高速データ収集

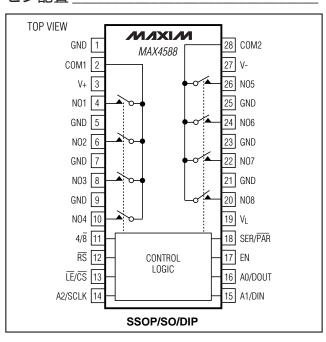

### ピン配置

### 特長

- ◆ 低インサーションロス: -2.5dB(100MHzまで)

- ◆ 高オフアイソレーション:-74dB(10MHz)

- ◆ 低クロストーク: -70dB(10MHzまで)

- ◆ -0.1dB信号帯域幅:16MHz

- ◆ -3dB信号帯域幅: 180MHz

- ◆ オン抵抗(±5V電源):60 (max)

- ◆ オン抵抗マッチング(±5V電源): 4 (max)

- ◆ オン抵抗平坦性(±5V電源):2 (max)

- ◆ 電源:+2.7V~+12V単一 ±2.7V~±6Vデュアル

- ◆ 低消費電力: < 20µW

- ◆ 双方向のレイルトゥレイル®信号に対応

- ◆ パラレル又はSPI/MICROWIREコンパチブルの シリアルインタフェース

- ◆ ESD保護: ±2kV以上(3015.7法)

- ◆ TTL/CMOSコンパチブル入力(V<sub>I</sub> = +5V)

#### 型番

| TEMP. RANGE    | PIN-PACKAGE                                                                      |

|----------------|----------------------------------------------------------------------------------|

| 0°C to +70°C   | 28 SSOP                                                                          |

| 0°C to +70°C   | 28 Wide SO                                                                       |

| 0°C to +70°C   | 28 Narrow Plastic DIP                                                            |

| -40°C to +85°C | 28 SSOP                                                                          |

| -40°C to +85°C | 28 Wide SO                                                                       |

| -40°C to +85°C | 28 Narrow Plastic DIP                                                            |

|                | 0°C to +70°C<br>0°C to +70°C<br>0°C to +70°C<br>-40°C to +85°C<br>-40°C to +85°C |

SPIはMotorola, Inc.の商標です。

MICROWIREはNational Semiconductor Corp.の商標です。 レイルトゥレイルは日本モトローラの登録商標です。

#### **ABSOLUTE MAXIMUM RATINGS**

| (Voltages referenced to GND)  V+0.3V to +13.0V  VL0.3V to (V+ + 0.3V) or 7V (whichever is lower)  V13.0V to +0.3V  V+ to V0.3V to +13.0V  VNO_, VCOM_ (Note 1)(V 0.3V) to (V+ + 0.3V)  4/8, RS, LE/CS, A2/SCLK, A1/DIN, | ESD per Method 3015.7 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

**Note 1:** Voltages on these pins exceeding V+ or V- are clamped by internal diodes. Limit forward diode current to maximum current rating.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS—Dual Supplies**

$(V+ = V_L = +4.5V \text{ to } +5.5V, V- = -4.5V \text{ to } -5.5V, V_{INH} = +2.4V, V_{INL} = +0.8V, T_A = T_{MIN} \text{ to } T_{MAX}, unless otherwise noted. Typical values are at T_A = +25°C, V+ = V_L = +5V, V- = -5V.) (Note 2)$

| PARAMETER                       | SYMBOL                                     | CONDITIONS                                     | TA    | MIN                | TYP  | MAX | UNITS |

|---------------------------------|--------------------------------------------|------------------------------------------------|-------|--------------------|------|-----|-------|

| ANALOG SWITCH                   |                                            |                                                | l     |                    |      |     | I.    |

| Analog Signal Range<br>(Note 3) | V <sub>COM_</sub> ,<br>V <sub>NO</sub>     |                                                |       | V-                 |      | V+  | V     |

| On-Resistance                   | Ron                                        | V+ = 5V, V- = -5V, V <sub>NO</sub> _ = ±2V,    | +25°C |                    | 40   | 60  | Ω     |

|                                 | 014                                        | $I_{COM} = 4mA$                                | C, E  |                    |      | 75  |       |

| On-Resistance Match Between     | ΔRON                                       | $V+ = 5V, V- = 5V, V_{NO} = \pm 2V,$           | +25°C |                    | 1    | 4   | Ω     |

| Channels (Note 4)               | Δi (O)((                                   | $I_{COM} = 4mA$                                | C, E  |                    |      | 5   | 32    |

| On-Resistance Flatness          |                                            | $V+ = 5V; V- = -5V; V_{NO} = 1V, 0, -1V;$      | +25°C |                    | 0.5  | 2.5 | Ω     |

| (Note 5)                        | TIFLAT(ON)                                 | I <sub>COM</sub> _ = 1mA                       | C, E  |                    |      | 3   | 32    |

| NO_ Off-Leakage Current         | lue (OFF)                                  | V+ = 5.5V, V- = -5.5V,                         | +25°C | -1                 | 0.01 | 1   | nA    |

| (Note 6)                        | INO_(OFF)                                  | $V_{COM} = \pm 4.5V, V_{NO} = \mp 4.5V$        | C, E  | -10                |      | 10  | 117 ( |

| COM_ Off-Leakage Current        | off-Leakage Current V+ = 5.5V, V- = -5.5V, |                                                | +25°C | -2                 | 0.01 | 2   | nA    |

| (Note 6)                        | ICOM_(OFF)                                 | $V_{COM} = \pm 4.5V, V_{NO} = \mp 4.5V$        | C, E  | -20                |      | 20  |       |

| COM_ On-Leakage Current         | loon (on)                                  | $V + = 5.5V, V - = -5.5V, V_{COM} = \pm 4.5V,$ | +25°C | -2                 | 0.01 | 2   | nA    |

| (Note 6)                        | ICOM_(ON)                                  | $V_{NO}$ = ±4.5V or floating                   | C, E  | -20                |      | 20  | 1 114 |

| LOGIC INPUTS (4/8, RS, LE/CS    | , A2/SCLK,                                 | A1/DIN, A0/DOUT, EN, SER/PAR)                  |       |                    |      |     |       |

| Input Logic Threshold High      | VINH                                       |                                                | C, E  | 2.4                | 1.7  |     | V     |

| Input Logic Threshold Low       | V <sub>INL</sub>                           |                                                | C, E  |                    | 1.5  | 0.8 | V     |

| Input Threshold Hysteresis      |                                            |                                                |       |                    | 0.2  |     | V     |

| Input Current                   | I <sub>IN</sub>                            | V <sub>IN</sub> _ = 0 or V <sub>L</sub>        |       | -1                 | 0.03 | 1   | μΑ    |

| LOGIC OUTPUT (SERIAL INTE       | RFACE)                                     |                                                |       |                    |      |     |       |

| DOUT Logic Low Output           | VoL                                        | ISINK = 3.2mA                                  | C, E  |                    |      | 0.4 | V     |

| DOUT Logic High Output          | Voh                                        | ISOURCE = -1mA                                 | C, E  | V <sub>L</sub> - 1 |      |     | V     |

### **ELECTRICAL CHARACTERISTICS—Dual Supplies (continued)**

$(V+ = V_L = +4.5V \text{ to } +5.5V, V- = -4.5V \text{ to } -5.5V, V_{INH} = +2.4V, V_{INL} = +0.8V, T_A = T_{MIN} \text{ to } T_{MAX}, unless otherwise noted. Typical values are at T_A = +25°C, V+ = V_L = +5V, V- = -5V.) (Note 2)$

| PARAMETER                                        | SYMBOL                | COND                                                             | ITIONS                                                                          | TA      | MIN | TYP | MAX  | UNITS   |

|--------------------------------------------------|-----------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------|---------|-----|-----|------|---------|

| SWITCH DYNAMIC CHARACTE                          | RISTICS               |                                                                  |                                                                                 |         |     |     |      | ı       |

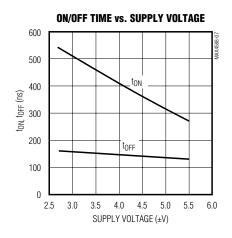

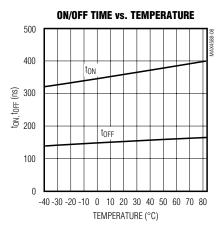

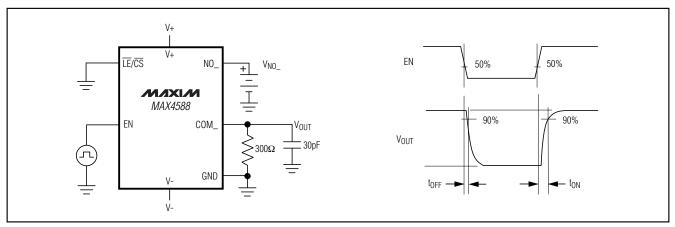

| Turn On Time                                     | +                     | V <sub>NO</sub> = 3V, V+ = 4                                     | 4.5V, V- = -4.5V,                                                               | +25°C   |     | 380 | 550  | 20      |

| Turn-On Time                                     | ton                   | Figure 1                                                         |                                                                                 | C, E    |     |     | 600  | ns      |

| Turn-Off Time                                    | torr                  | V <sub>NO</sub> _ = 3V, V+ = 4                                   | V <sub>NO</sub> _ = 3V, V+ = 4.5V, V- = -4.5V,<br>Figure 1                      |         |     | 150 | 300  | no      |

| Turr-On Time                                     | toff                  | Figure 1                                                         |                                                                                 |         |     |     | 350  | ns      |

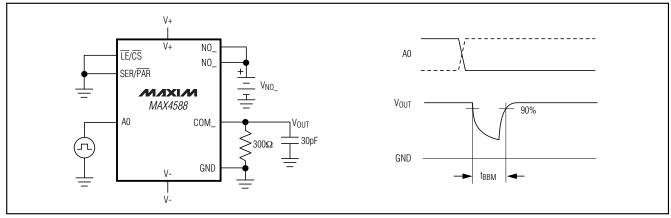

| Break-Before-Make Time Delay (Note 3)            | t <sub>BBM</sub>      | $V_{NO_{-}} = \pm 3V, V + =$ Figure 2                            | $V_{NO}$ = ±3V, V+ = 5.5V, V- = -5.5V, Figure 2                                 |         |     | 180 |      | ns      |

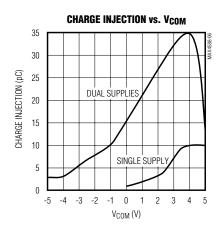

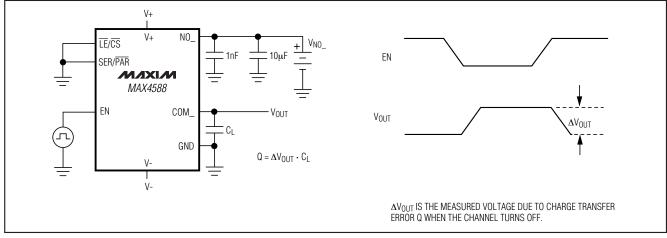

| Charge Injection                                 | Q                     | C <sub>L</sub> = 1.0nF, V <sub>NO</sub><br>Figure 3              | $= 0, R_S = 0,$                                                                 | +25°C   |     | 15  |      | рС      |

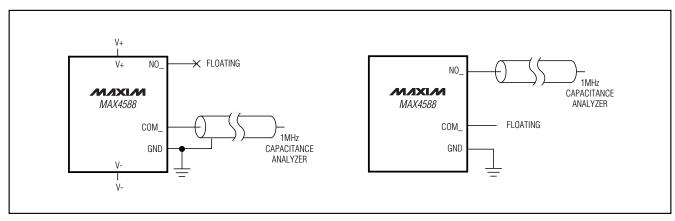

| NO_ Off-Capacitance                              | C <sub>NO_(OFF)</sub> | $V_{NO_{-}} = 0$ , $f_{IN} = 1$ M                                | 1Hz, Figure 4                                                                   | +25°C   |     | 2   |      | pF      |

| COM_ Off-Capacitance                             | CCOM_(OFF)            | $V_{COM} = 0$ , $f_{IN} = 1$                                     | MHz, Figure 4                                                                   | +25°C   |     | 4   |      | pF      |

| COM_ On-Capacitance                              | CCOM_(ON)             | $V_{COM} = 0$ , $f_{IN} = 1$                                     | MHz, Figure 4                                                                   | +25°C   |     | 7   |      | pF      |

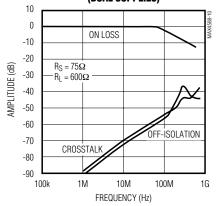

| Off-Isolation (Note 7)                           | V <sub>ISO</sub>      | V <sub>NO</sub> _ = 1V <sub>RMS</sub> , f = all channels off, Fi | V <sub>NO_</sub> = 1V <sub>RMS</sub> , f = 10MHz,<br>all channels off, Figure 5 |         |     | -74 |      | dB      |

| Channel-to-Channel Crosstalk                     | V <sub>C</sub> T      | $V_{NO} = 1V_{RMS}, f =$                                         | 10MHz, Figure 5                                                                 | +25°C   |     | -70 |      | dB      |

| 2dD Dondwidth                                    | BW                    | Figure F                                                         | 4-channel mode                                                                  | . 0E°C  |     | 180 |      | NALI-   |

| -3dB Bandwidth                                   | BVV                   | Figure 5                                                         | 8-channel mode                                                                  | +25°C   |     | 140 |      | MHz     |

| -0.1dB Bandwidth                                 | BW                    | Figure 5                                                         | 4-channel mode                                                                  | +25°C   |     | 16  |      | MHz     |

| -0. Tub Bariuwiuiii                              | DVV                   | rigure 5                                                         | 8-channel mode                                                                  | 1 +25 0 |     | 11  |      | IVIITIZ |

| PARALLEL-INTERFACE TIMING                        | 3                     |                                                                  |                                                                                 |         |     |     |      |         |

| A_, EN to $\overline{\text{LE}}$ Rise Setup Time | t <sub>DS</sub>       | Figure 6                                                         |                                                                                 | C, E    | 80  |     |      | ns      |

| A_, EN to $\overline{\text{LE}}$ Rise Hold Time  | tDH                   | Figure 6                                                         |                                                                                 | C, E    | 0   |     |      | ns      |

| LE Low Pulse Width                               | t∟                    | Figure 6                                                         |                                                                                 | C, E    | 80  |     |      | ns      |

| RS Low Pulse Width                               | trs                   | Figure 6                                                         |                                                                                 | C, E    | 80  |     |      | ns      |

| SERIAL-INTERFACE TIMING                          |                       |                                                                  |                                                                                 |         |     |     |      |         |

| Operating Frequency                              | fCLK                  | Figure 7                                                         |                                                                                 | C, E    |     |     | 6.25 | MHz     |

| SCLK Pulse Width High                            | tCH                   | Figure 7                                                         |                                                                                 | C, E    | 80  |     |      | ns      |

| SCLK Pulse Width Low                             | t <sub>CL</sub>       | Figure 7                                                         |                                                                                 | C, E    | 80  |     |      | ns      |

| DIN to SCLK Rise Setup Time                      | tDS                   | Figure 7                                                         |                                                                                 | C, E    | 60  |     |      | ns      |

| DIN to SCLK Rise Hold Time                       | tDH                   | Figure 7                                                         |                                                                                 | C, E    | 0   |     |      | ns      |

| CS Fall to SCLK Rise Setup Time                  | tcsso                 | Figure 7                                                         |                                                                                 | C, E    | 50  |     |      | ns      |

| SCLK Rise to DOUT Valid                          | t <sub>DO</sub>       | $C_L = 50pF$ , Figure                                            | C, E                                                                            |         |     | 150 | ns   |         |

| CS Rise to SCLK Rise Hold Time                   | tCSH1                 | Figure 7                                                         |                                                                                 | C, E    | 0   |     |      | ns      |

| CS Rise to SCLK Rise Setup<br>Time               | tcss1                 | Figure 7                                                         | C, E                                                                            | 80      |     |     | ns   |         |

| CS Fall to SCLK Rise Hold Time                   | tcss1                 | Figure 7                                                         |                                                                                 | C, E    | 80  |     |      | ns      |

| RS Low Pulse Width                               | t <sub>RS</sub>       | Figure 6                                                         |                                                                                 | C, E    | 80  |     |      | ns      |

### **ELECTRICAL CHARACTERISTICS—Dual Supplies (continued)**

$(V+=V_L=+4.5V\ to\ +5.5V,\ V-=-4.5V\ to\ -5.5V,\ V_{INH}=+2.4V,\ V_{INL}=+0.8V,\ T_A=T_{MIN}\ to\ T_{MAX},\ unless\ otherwise\ noted.$  Typical values are at  $T_A=+25^{\circ}C,\ V+=V_L=+5V,\ V-=-5V.$ ) (Note 2)

| PARAMETER                     | SYMBOL | SYMBOL CONDITIONS                        |       |      | TYP    | MAX | UNITS |  |

|-------------------------------|--------|------------------------------------------|-------|------|--------|-----|-------|--|

| POWER SUPPLY                  |        |                                          |       |      |        |     |       |  |

| Power-Supply Range            | V+, V- |                                          |       | ±2.7 |        | ±6  | V     |  |

| Fower-Supply Halige           | VL     |                                          |       | 2.7  |        | V+  | v     |  |

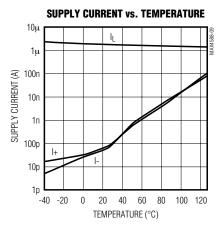

| V+ Supply Current             | 1+     | V+ = 5.5V, V- = -5.5V                    | +25°C | -1   | 0.0001 | 1   | μA    |  |

| v+ Supply Current             | 1+     | V+ = 3.3V, V- = -3.3V                    | C, E  | -10  |        | 10  | - μΑ  |  |

| V - Supply Current            | 1      | V+ = 5.5V, V- = -5.5V                    | +25°C | -1   | 0.0001 | 1   | μA    |  |

| v - Supply Current            | I-     | V+ = 5.5V, V- = -5.5V                    | C, E  | -10  |        | 10  | ] μΑ  |  |

| V <sub>L</sub> Supply Current | ΙL     | $V_L = 5.5V$ , all $V_{IN} = 0$ or $V_L$ | C, E  | -10  | 2      | 10  | μΑ    |  |

### **ELECTRICAL CHARACTERISTICS—Single +5V Supply**

$(V+ = V_L = +4.5V \text{ to } +5.5V, V- = 0, V_{INH} = +2.4V, V_{INL} = +0.8V, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C, V+ = V_L = +5V.)$  (Note 2)

| PARAMETER                    | SYMBOL                                  | CONDITIONS                                                                | TA    | MIN                | TYP   | MAX | UNITS |  |

|------------------------------|-----------------------------------------|---------------------------------------------------------------------------|-------|--------------------|-------|-----|-------|--|

| ANALOG SWITCH                | 1                                       |                                                                           | 1     |                    |       |     |       |  |

| Analog Signal Range (Note 3) | V <sub>COM_</sub> ,<br>V <sub>NO_</sub> |                                                                           |       | 0                  |       | V+  | V     |  |

| On-Resistance                | Ron                                     | V+ = 5V, V <sub>NO</sub> = 3V, I <sub>COM</sub> = 4mA                     | +25°C |                    | 80    | 120 | Ω     |  |

| OII-nesistatice              | HON                                     | V+ = 5V, VNO_ = 5V, ICOM_ = 4IIIA                                         | C, E  |                    |       | 150 | 1 22  |  |

| On-Resistance Match Between  | ΔR <sub>ON</sub>                        | V+ = 5V, V <sub>NO</sub> = 3V, I <sub>COM</sub> = 4mA                     | +25°C |                    | 1     | 8   | Ω     |  |

| Channels (Note 4)            | AHON                                    | V+ = 5V, VNO_ = 5V, ICOM_ = 4IIIA                                         | C, E  |                    |       | 10  | 22    |  |

| On-Resistance Flatness       | R <sub>FLAT(ON)</sub>                   | $V + = 5V$ , $I_{COM} = 4mA$ ,                                            | +25°C |                    | 4     | 10  | Ω     |  |

| (Note 5)                     | TIFLAT(ON)                              | VNO_ = 2 V, O V, +V                                                       | C, E  |                    |       | 12  | 32    |  |

| NO_ Off Leakage Current      | luo (OFF)                               | $V+ = 5.5V; V_{COM} = 4.5V, 1V;$                                          | +25°C | -1                 | 0.005 | 1   | nA    |  |

| (Notes 6, 9)                 | I <sub>NO_(OFF)</sub>                   | V <sub>NO</sub> _ = 1V, 4.5V                                              | C, E  | -10                |       | 10  |       |  |

| COM_ Off Leakage Current     | loovyous                                | V+ = 5.5V; V <sub>COM</sub> _ = 4.5V, 1V;<br>V <sub>NO</sub> _ = 1V, 4.5V | +25°C | -2                 | 0.005 | 2   | nA    |  |

| (Notes 6, 9)                 | ICOM(OFF)                               |                                                                           | C, E  | -20                |       | 20  |       |  |

| COM_ On Leakage Current      | leer, (er.)                             | V+ = 5.5V; V <sub>COM</sub> = 4.5V, 1V;                                   | +25°C | -2                 | 0.005 | 2   | n 1   |  |

| (Notes 6, 9)                 | ICOM_(ON)                               | $V_{NO} = 4.5V$ , 1V, or floating                                         | C, E  | -20                |       | 20  | nA nA |  |

| LOGIC INPUTS (4/8, RS, LE/CS | A2/SCLK,                                | A1/DIN, A0/DOUT, EN, SER/PAR)                                             |       |                    |       |     |       |  |

| Input Logic Threshold High   | VINH                                    |                                                                           | C, E  | 2.4                | 1.7   |     | V     |  |

| Input Logic Threshold Low    | V <sub>INL</sub>                        |                                                                           | C, E  |                    | 1.5   | 8.0 | V     |  |

| Input Threshold Hysteresis   |                                         |                                                                           |       |                    | 0.2   |     | V     |  |

| Input Current                | I <sub>IN</sub>                         | $V_{IN} = 0$ or $V_L$                                                     | C, E  | -1                 |       | 1   | μΑ    |  |

| LOGIC OUTPUT (SERIAL INTE    | RFACE)                                  |                                                                           | •     |                    |       |     | •     |  |

| DOUT Logic Low Output        | V <sub>OL</sub>                         | I <sub>SINK</sub> = 3.2mA                                                 | C, E  |                    |       | 0.4 | V     |  |

| DOUT Logic High Output       | VoH                                     | ISOURCE = -1mA                                                            | C, E  | V <sub>L</sub> - 1 |       |     | V     |  |

### **ELECTRICAL CHARACTERISTICS—Single +5V Supply (continued)**

$(V+ = V_L = +4.5V \text{ to } +5.5V, V- = 0, V_{INH} = +2.4V, V_{INL} = +0.8V, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C, V+ = V_L = +5V.)$  (Note 2)

| PARAMETER                                        | SYMBOL            | COND                                                            | ITIONS                                | TA      | MIN | TYP | MAX  | UNITS  |

|--------------------------------------------------|-------------------|-----------------------------------------------------------------|---------------------------------------|---------|-----|-----|------|--------|

| SWITCH DYNAMIC CHARACTE                          | RISTICS           |                                                                 |                                       |         |     |     |      | I      |

| Turne On Time                                    |                   | 01/11/                                                          | 4 EV E:                               | +25°C   |     | 550 | 800  |        |

| Turn-On Time                                     | ton               | $V_{NO} = 3V, V + = 4$                                          | 4.5V, Figure I                        | C, E    |     |     | 900  | ns     |

| Turn-Off Time                                    |                   | \/                                                              | 4 5\/   Figure 4                      | +25°C   |     | 150 | 300  |        |

| Turn-Oil Time                                    | tOFF              | $VNO_{-} = 3V, V + = 4$                                         | $V_{NO} = 3V, V_{+} = 4.5V, Figure 1$ |         |     |     | 350  | ns     |

| Break-Before-Make Time Delay (Note 3)            | t <sub>BBM</sub>  | V <sub>NO</sub> _ = 3V, V+ = 5                                  | 5.5V, Figure 2                        | C, E    | 10  | 200 |      | ns     |

| Charge Injection                                 | Q                 | C <sub>L</sub> = 1.0nF, V <sub>NO</sub> _<br>Figure 3           | $= 2.5V, R_S = 0,$                    | +25°C   |     | 5   |      | рС     |

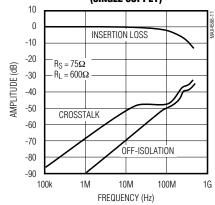

| Off-Isolation                                    | V <sub>ISO</sub>  | V <sub>NO</sub> _ = 1V <sub>RMS</sub> , f = all channels off, F |                                       | +25°C   |     | -65 |      | dB     |

| Channel-to-Channel Crosstalk                     | VCT               | V <sub>NO_</sub> = 1V <sub>RMS</sub> , f =                      | = 10MHz, Figure 5                     | +25°C   |     | -70 |      | dB     |

| -3dB Bandwidth                                   | width BW Figure 5 | Eiguro 5                                                        | 4-channel mode                        | +25°C   |     | 100 |      | MHz    |

| -Sub bandwidth                                   |                   | rigure 5                                                        | 8-channel mode                        | 1 +25 0 |     | 75  |      | IVIITZ |

| -0.1dB Bandwidth                                 | BW                | Figure 5                                                        | 4-channel mode                        | +25°C   |     | 10  |      | MHz    |

| -0. IUD Dariuwiutii                              | DVV               | rigure 5                                                        | 8-channel mode                        | 1 +25 0 |     | 7   |      | IVIITZ |

| PARALLEL-INTERFACE TIMING                        | 3                 |                                                                 |                                       |         |     |     |      |        |

| A_, EN to $\overline{\text{LE}}$ Rise Setup Time | t <sub>DS</sub>   | Figure 6                                                        |                                       | C, E    | 80  |     |      | ns     |

| A_, EN to $\overline{\text{LE}}$ Rise Hold Time  | tDH               | Figure 6                                                        |                                       | C, E    | 0   |     |      | ns     |

| LE Low Pulse Width                               | t∟                | Figure 6                                                        |                                       | C, E    | 80  |     |      | ns     |

| RS Low Pulse Width                               | t <sub>RS</sub>   | Figure 6                                                        |                                       | C, E    | 80  |     |      | ns     |

| SERIAL-INTERFACE TIMING                          |                   |                                                                 |                                       |         |     |     |      |        |

| Operating Frequency                              | fCLK              | Figure 7                                                        |                                       | C, E    |     |     | 6.25 | MHz    |

| SCLK Pulse Width High                            | tсн               | Figure 7                                                        |                                       | C, E    | 80  |     |      | ns     |

| SCLK Pulse Width Low                             | t <sub>CL</sub>   | Figure 7                                                        |                                       | C, E    | 80  |     |      | ns     |

| DIN to SCLK Rise Setup Time                      | t <sub>DS</sub>   | Figure 7                                                        |                                       | C, E    | 60  |     |      | ns     |

| DIN to SCLK Rise Hold Time                       | tDH               | Figure 7                                                        |                                       | C, E    | 0   |     |      | ns     |

| CS Fall to SCLK Rise Setup Time                  | tcsso             | Figure 7                                                        |                                       | C, E    | 50  |     |      | ns     |

| CS Fall to SCLK Rise Hold Time                   | tcss1             | Figure 7                                                        |                                       | C, E    | 80  |     |      | ns     |

| CS Rise to SCLK Rise Hold Time                   | tCSH1             | Figure 7                                                        | C, E                                  | 0       |     |     | ns   |        |

| CS Rise to SCLK Rise Setup<br>Time               | tcss1             | Figure 7                                                        | C, E                                  | 80      |     |     | ns   |        |

| SCLK Rise to DOUT Valid                          | t <sub>DO</sub>   | $C_L = 50pF$ , Figure                                           | 7                                     | C, E    |     |     | 150  | ns     |

| RS Low Pulse Width                               | trs               | Figure 6                                                        |                                       | C, E    | 80  |     |      | ns     |

### **ELECTRICAL CHARACTERISTICS—Single +5V Supply (continued)**

$(V+ = V_L = +4.5V \text{ to } +5.5V, V- = 0, V_{INH} = +2.4V, V_{INL} = +0.8V, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C, V+ = V_L = +5V.)$  (Note 2)

| PARAMETER                     | SYMBOL | CONDITIONS                                       | TA    | MIN | TYP | MAX | UNITS |

|-------------------------------|--------|--------------------------------------------------|-------|-----|-----|-----|-------|

| POWER SUPPLY                  |        |                                                  |       |     |     |     |       |

| Power-Supply Range            | V+     |                                                  |       | 2.7 |     | 12  |       |

|                               | VL     | V+ ≤ 6.5V                                        |       | 2.7 |     | V+  | V     |

|                               | ٧L     | V+ > 6.5V                                        |       | 2.7 |     | 6.5 |       |

| V+ Supply Current             | 1+     | V+ = 5.5V, V <sub>IN</sub> = 0 or V <sub>I</sub> | +25°C | -1  |     | 1   | μΑ    |

| v+ Supply Current             | 1+     | V+ = 5.5V, V N = 0 01 VL                         | C, E  | -10 |     | 10  | ]     |

| V <sub>L</sub> Supply Current | IL     | $V_L = 5.5V$ , all $V_{IN} = 0$ or $V_L$         | C, E  | -10 | 2   | 10  | μΑ    |

### **ELECTRICAL CHARACTERISTICS—Single +3V Supply**

$(V+ = V_L = +2.7V \text{ to } +3.6V, V- = 0, V_{INH} = +2V, V_{INL} = +0.5V, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}C$ ,  $V+ = V_L = +3.0V$ .)

| PARAMETER                             | SYMBOL                                       | CONDITIONS                                    | TA    | MIN | TYP | MAX  | UNITS |

|---------------------------------------|----------------------------------------------|-----------------------------------------------|-------|-----|-----|------|-------|

| ANALOG SWITCH                         | 1                                            |                                               |       |     |     |      |       |

| Analog Signal Range                   | V <sub>COM_</sub> ,<br>V <sub>NO_</sub>      |                                               |       | 0   |     | V+   | V     |

| On-Resistance                         | Ron                                          | V+ = 2.7V, V <sub>NO</sub> _ = 1V,            | +25°C |     | 240 | 350  | Ω     |

| On-mesistance                         | TION                                         | I <sub>COM</sub> _ = 1mA                      | C, E  |     |     | 450  | 52    |

| LOGIC INPUTS (4/8, RS, LE/CS          | A2/SCLK,                                     | A1/DIN, A0/DOUT, EN, SER/PAR)                 |       |     |     |      |       |

| Input Logic Threshold High            | VINH                                         |                                               | C, E  | 2.0 |     |      | V     |

| Input Logic Threshold Low             | V <sub>INL</sub>                             |                                               | C, E  |     |     | 0.5  | V     |

| Input Current                         | I <sub>IN</sub>                              | V <sub>IN</sub> _ = 0 or V <sub>L</sub>       | C, E  | -1  |     | 1    | μΑ    |

| SWITCH DYNAMIC CHARACTE               | RISTICS                                      |                                               |       |     |     |      |       |

| Turn-On Time                          | imo tou M                                    | V <sub>NO</sub> = 1.5V, V+ = 2.7V, Figure 1   | +25°C |     | 700 | 1000 | ns    |

| Turr-Ori Time                         | ton                                          | VNO_ = 1.5V, V+ = 2.7V, Figure 1              | C, E  |     |     | 200  | 113   |

| Turn-Off Time                         | torr                                         | V <sub>NO</sub> = 1.5V, V+ = 2.7V, Figure 1   | +25°C |     | 250 | 400  | no    |

|                                       | toff                                         | VNO_ = 1.5V, V+ = 2.7V, Figure 1              | C, E  |     |     | 500  | ns    |

| Break-Before-Make Time Delay (Note 3) | t <sub>BBM</sub>                             | V <sub>NO</sub> _ = 1.5V, V+ = 3.6V, Figure 2 | +25°C | 10  | 350 |      | ns    |

| PARALLEL-INTERFACE TIMIN              | G                                            |                                               |       |     |     |      |       |

| A_, EN to LE Rise Setup Time          | tDS                                          | Figure 6                                      | C, E  | 200 |     |      | ns    |

| A_, EN to LE Rise Hold Time           | tDH                                          | Figure 6                                      | C, E  | 0   |     |      | ns    |

| LE Low Pulse Width                    | t∟                                           | Figure 6                                      | C, E  | 200 |     |      | ns    |

| RS Low Pulse Width                    | t <sub>RS</sub>                              | Figure 6                                      | C, E  | 200 |     |      | ns    |

| SERIAL-INTERFACE TIMING               | 11                                           |                                               |       |     |     |      |       |

| Operating Frequency                   | f <sub>CLK</sub>                             | Figure 7                                      | C, E  |     |     | 2.1  | MHz   |

| SCLK Pulse Width High                 | tch                                          | Figure 7                                      | C, E  | 200 |     |      | ns    |

| SCLK Pulse Width Low                  | tCL                                          | Figure 7                                      | C, E  | 200 |     |      | ns    |

| DIN to SCLK Rise Setup Time           | t <sub>DS</sub>                              | Figure 7                                      | C, E  | 100 |     |      | ns    |

| DIN to SCLK Rise Hold Time            | SCLK Rise Hold Time t <sub>DH</sub> Figure 7 |                                               | C, E  | 0   |     |      | ns    |

| RS Low Pulse Width                    | trs                                          | Figure 6                                      | C, E  | 200 |     |      | ns    |

### **ELECTRICAL CHARACTERISTICS—Single +3V Supply (continued)**

$(V+ = V_L = +2.7V \text{ to } +3.6V, V- = 0, V_{INH} = +2V, V_{INL} = +0.5V, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}C$ ,  $V+ = V_L = +3.0V$ .)

| PARAMETER                       | SYMBOL | CONDITIONS                               | TA    | MIN | TYP | MAX | UNITS |

|---------------------------------|--------|------------------------------------------|-------|-----|-----|-----|-------|

| CS Fall to SCLK Rise Setup Time | tcsso  | Figure 7                                 | C, E  | 100 |     |     | ns    |

| CS Rise to SCLK Rise Hold Time  | tCSH1  | Figure 7                                 | C, E  | 0   |     |     | ns    |

| CS Rise to SCLK Rise Setup Time | tcss1  | Figure 7                                 | C, E  | 200 |     |     | ns    |

| CS Fall to SCLK Rise Hold Time  | tCSS1  | Figure 7                                 | C, E  | 200 |     |     | ns    |

| SCLK Rise to DOUT Valid         | tDO    | C <sub>L</sub> = 50pF, Figure 7          | C, E  |     |     | 250 | ns    |

| POWER SUPPLY                    |        |                                          | •     |     |     |     |       |

| V+ Supply Current               | l+     | $V+ = 3.6V, V_{IN} = 0 \text{ or } V_L$  | +25°C | -1  |     | 1   | μΑ    |

| v+ Supply Guiterit              | 1+     | V+ = 3.0V, V  \                          | C, E  | -10 |     | 10  | μΑ    |

| V <sub>L</sub> Supply Current   | ΙL     | $V_L = 3.6V$ , all $V_{IN} = 0$ or $V_L$ | C, E  | -10 | 1   | 10  | μΑ    |

Note 2: The algebraic convention is used in this data sheet; the most negative value is shown in the minimum column.

Note 3: Guaranteed by design.

**Note 4:**  $\Delta R_{ON} = \Delta R_{ON(MAX)} - \Delta R_{ON(MIN)}$ .

**Note 5:** Resistance flatness is defined as the difference between the maximum and the minimum value of on-resistance as measured over the specified analog-signal range.

Note 6: Leakage parameters are 100% tested at maximum rated hot temperature and guaranteed by correlation at TA = +25°C.

Note 7: Off isolation = 20log<sub>10</sub> [V<sub>COM</sub>\_ / (V<sub>NC</sub>\_ or V<sub>NO</sub>\_)], V<sub>COM</sub>\_ = output, V<sub>NC</sub>\_ or V<sub>NO</sub>\_ = input to off switch.

Note 8: Between any two switches.

Note 9: Leakage testing for single-supply operation is guaranteed by testing with dual supplies.

標準動作特性

$(V + = V_L = +5V, V - = -5V, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

標準動作特性(続き)\_

$(V + = V_L = +5V, V - = -5V, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

#### INSERTION LOSS, OFF-ISOLATION, AND CROSSTALK vs. FREQUENCY (DUAL SUPPLIES)

#### INSERTION LOSS, OFF-ISOLATION, AND CROSSTALK vs. FREQUENCY (SINGLE SUPPLY)

### 端子説明 \_\_\_\_\_\_

| 端子                           | 名称      | 機能                                                                                                                                                                                                                   |

|------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 5, 7,<br>9, 21,<br>23, 25 | GND     | グランド。全てのグランドピンはグランドプレーンに接続して下さい。「グランディング」の項を参照して下さい。                                                                                                                                                                 |

| 2                            | COM1    | アナログスイッチのコモン端子。「真理値表」を参照して下さい。                                                                                                                                                                                       |

| 3                            | V+      | アナログ正電源電圧入力                                                                                                                                                                                                          |

| 4                            | NO1     | ノーマリオープンのアナログ入力端子。「真理値表」を参照して下さい。                                                                                                                                                                                    |

| 6                            | NO2     | ノーマリオープンのアナログ入力端子。「真理値表」を参照して下さい。                                                                                                                                                                                    |

| 8                            | NO3     | ノーマリオープンのアナログ入力端子。「真理値表」を参照して下さい。                                                                                                                                                                                    |

| 10                           | NO4     | ノーマリオープンのアナログ入力端子。「真理値表」を参照して下さい。                                                                                                                                                                                    |

| 11                           | 4/8     | マルチプレクサ構成制御。V_に接続するとデュアル2チャネルモードが選択されます。GNDに接続すると、<br>シングル4チャネルマルチプレクサ動作になります。「真理値表」を参照して下さい。                                                                                                                        |

| 12                           | RS      | アクティブローリセット入力。シリアルモードにおいて、 $\overline{\text{RS}}$ をローにすると、ラッチとシフトレジスタが強制的にパワーオンリセット状態になり、全てのスイッチが強制的にオープンになります。パラレルモードにおいては、 $\overline{\text{RS}}$ をローにするとラッチがパワーダウンリセット状態になり、全てのスイッチが強制的にオープンになります。「真理値表」を参照して下さい。 |

| 13                           | LE/CS   | パラレルモードにおいては、このピンはトランスペアレントなラッチイネーブルです。シリアルモードにおいては、このピンはチップセレクト入力です。「真理値表」を参照して下さい。                                                                                                                                 |

| 14                           | A2/SCLK | 4/8がローの時、このピンはパラレルモードの最上位アドレスビットです。4/8がハイの時、このピンは無視されます。シリアルモードにおいては、これがシリアルシフトクロック入力です。データはSCLKの立上がりエッジでロードされます。「真理値表」を参照して下さい。                                                                                     |

| 15                           | A1/DIN  | パラレルモードにおいてはアドレス入力。シリアルモードにおいてはシリアルデータ入力。シリアルモードではデータはSCLKの立上がりエッジでロードされます。                                                                                                                                          |

| 16                           | A0/DOUT | パラレルモードにおける最下位アドレス入力。シリアルモードではこれは内部4ビットシフトレジスタからの出力です。DOUTはデイジーチェーン・カスケード接続に使えるようになっています。DOUTはCSによってスリーステートになりません。「シリアル動作」を参照して下さい。                                                                                  |

| 17                           | EN      | スイッチイネーブル。ENをローにすると、全てのチャネルが強制的にオフになります。ハイにすると、通常のマルチプレクサ動作が可能になります。シリアルモードでは非同期で動作します。パラレルモードでは、LE信号がハイの時にENがラッチされます。                                                                                               |

| 18                           | SER/PAR | インタフェース選択入力。ローにすると、パラレルデータインタフェース動作になります。ハイにすると、シリアルデータインタフェース動作となり、DOUTドライバがイネーブルされます。                                                                                                                              |

| 19                           | VL      | ロジック電源入力。DOUTドライバ及びその他のディジタル回路を駆動します。VLはディジタル入力及び出力ロジックレベルの両方を設定します。                                                                                                                                                 |

| 20                           | NO8     | ノーマリオープンのアナログ入力端子。「真理値表」を参照して下さい。                                                                                                                                                                                    |

| 22                           | NO7     | ノーマリオープンのアナログ入力端子。「真理値表」を参照して下さい。                                                                                                                                                                                    |

| 24                           | NO6     | ノーマリオープンのアナログ入力端子。「真理値表」を参照して下さい。                                                                                                                                                                                    |

| 26                           | NO5     | ノーマリオープンのアナログ入力端子。「真理値表」を参照して下さい。                                                                                                                                                                                    |

| 27                           | V-      | アナログ負電源電圧入力。単一電源動作の場合はグランドプレーンに接続して下さい。                                                                                                                                                                              |

| 28                           | COM2    | アナログスイッチのコモン端子。「真理値表」を参照して下さい。                                                                                                                                                                                       |

図1. ターンオン/ターンオフ時間

図2. ブレーク・ビフォ・メークタイムディレー

図3. チャージインジェクション

図4. NO\_、COM\_容量

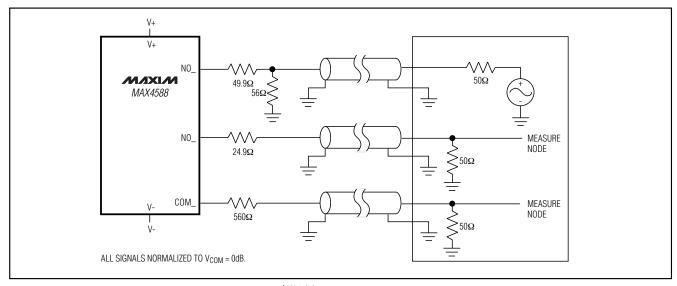

図5. オフアイソレーション、クロストーク及び帯域幅

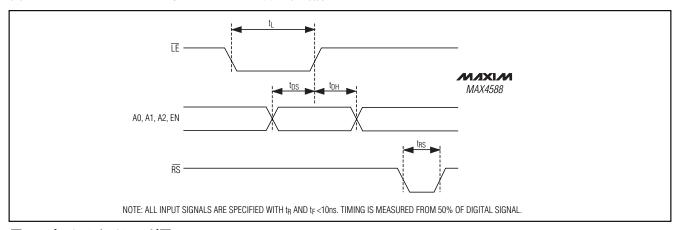

図6. パラレルタイミング図

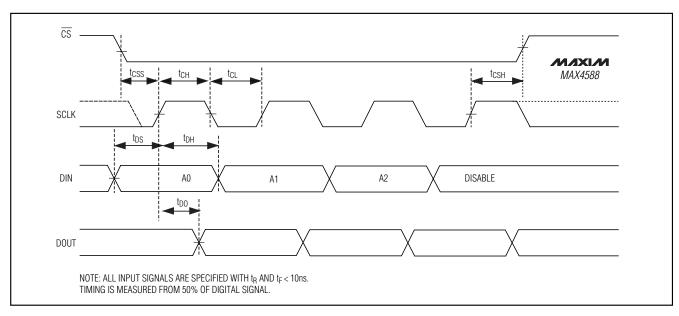

図7. シリアルタイミング図

### 詳細

#### ロジックレベルトランスレータ

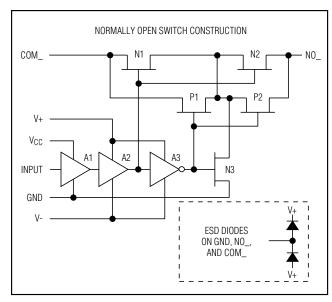

MAX4588は、図8に示すように高周波"T"スイッチとして構成されています。ロジックレベル入力はアンプA1によって $V_+ \sim V_-$ のロジック信号に変換され、それによってアンプA2を駆動します。アンプA2は、NチャネルMOSFET N1及びN2のゲートを $V_+ \sim V_-$ の範囲で駆動して完全にターンオン又はターンオフします。同じ信号により、インバータA3はPチャネルMOSFET P1及びP2を $V_+ \sim V_-$ の範囲で駆動して完全にターンオン又はターンオフします。またNチャネルMOSFET N3をターンオン/オフします。ロジックレベルスレッショルドは $V_L$ 及びGNDによって決定されます。

#### スイッチオン状態

スイッチがオンの場合、MOSFET N1、N2、P1及びP2はオンで、MOSFET N3はオフとなります(図8)。信号経路はCOM\_からNO\_で、Nチャネル及びPチャネルのMOSFETがいずれも純粋の抵抗として動作するため、対称となっています(信号を両方向に流すことができます)。オフ状態のMOSFET N3はDC電流を全く流しませんが、GNDに対して小さな容量があります。4つのオン状態のMOSFETもやはりグランドに対して容量を持っているため、直列抵抗と共にローパスフィルタを形成します。これらの容量は直列抵抗に沿って均等に配分されているため、単純なRCフィルタではなく伝送ラインとして動作します。スイッチがオン時のMAX4588の帯域幅が180MHzと優秀であるのはこの構造のためです。

図8. T型スイッチの構造

75 システムの標準的な減衰は-2.5dBで、50MHzまで 比較的平坦です。これよりインピーダンスの高い回路 は減衰がさらに小さくなります(この逆も成り立ちます) が、内部及び外部容量とスイッチの内部抵抗の効果が 増大するために帯域幅がやや小さくなります。

MAX4588は、±5V動作用に最適化されています。電源電圧を低くしたり、単一電源を使用するとスイッチング時間が増加し、オン抵抗が(従ってオン状態の減衰も)増大し、非直線性も増大します。

#### スイッチオフ状態

スイッチがオフの時、MOSFETのN1、N2、P1及びP2はオフで、MOSFET N3はオンとなります(図8)。信号経路は直列MOSFETの寄生オフ容量を通りますが、N3によってグランドにシャントされます。これによりハイパスフィルタが形成されますが、その特性はソース及び負荷インピーダンスに依存します。75システム及び10MHz以下の場合は、減衰が80dBを超えることがあります。周波数及び回路インピーダンスが増加するに従って、この値は減少します。全体的な性能には、外部容量及び基板レイアウトが大きく影響します。

#### アプリケーション情報

#### 電源に関する考慮

#### 概要

MAX4588はCMOSアナログスイッチの標準的な構造になっており、 $V_+$ 、 $V_-$  、 $V_L$ 及びGNDの4つの電源端子を備えています。 $V_+$ と $V_-$  は内部CMOSスイッチを駆動するため、及び個々のスイッチのアナログ電圧制限を設定するために使用されます。各アナログ信号ピンと $V_+$ 及び $V_-$  の間には、逆ESD保護ダイオードが内部で接続されています。任意のピンの電圧が $V_+$ 又は $V_-$  を超えると、これらのダイオードの1つに電流が通ります。通常動作中は、これらの逆バイアスESDダイオードのリークのみが、 $V_-$  及び $V_+$ から消費される電流となります。

アナログリーク電流の殆ど全てがESDダイオードを通じて生じます。1つの信号ピンに接続されている2つのESDダイオードは互いに同等であるため、かなりバランスがとれていますが、逆バイアスが互いに異なっています。各々がV+又はV-とアナログ信号によってバイアスされています。つまり、信号が異なるとリーク電流も異なります。2つのダイオードによる信号経路からV+ピンとV-ピンへのリーク電流の差がアナログ信号経路リーク電流となります。アナログリーク電流は全て電源端子に流れ込み、他のスイッチ端子には流れません。このため、1つのスイッチの両側のリーク電流極性は同じかあるいは反対になります。

アナログ信号経路とGNDの間には接続がありません。アナログ信号経路は、互いのソース同士とドレイン同士が並列に接続されたNチャネル及びPチャネルMOSFETからなり、これらのMOSFETのゲートはロジックレベルトランスレータによって互いに逆位相でV+及びV-に駆動されます。

V<sub>L</sub>とGNDは内部ロジック及びロジックレベルトランスレータを駆動し、入力のロジックスレッショルドを設定します。ロジックレベルトランスレータはロジックレベルをV+及びV-にスイッチングされた信号に変換し、アナログスイッチのゲートを駆動します。ロジック電源と

アナログ電源は、この駆動信号によってのみ接続されています。

### バイポーラ電源動作

MAX4588は、±2.7V~±6Vのバイポーラ電源で動作します。V+及びV-の電源が対称である必要はありませんが、合計電圧が最大定格の13.0Vを超えることは許されません。MAX4588のV+ピンを+3Vに接続した状態で、ロジックレベル入力ピンを+5Vロジックレベル信号に接続しないで下さい。このレベルはが絶対最大定格を超過するため、デバイス又は外部回路を損傷する恐れがあります。

注意: $V_+ \& V_-$  の電圧差の絶対最大定格は13.0Vです。通常の公差 $\pm 10\%$ の $\pm 6V$ 又は1 $\pm 2V$ 電源は最大13.2Vに達する可能性があります。この電圧は、MAX4588を損傷させる恐れがあります。公差が $\pm 5\%$ の電源でも、オーバシュートやノイズスパイクによって13.0Vを超える可能性があります。

#### 単一電源動作

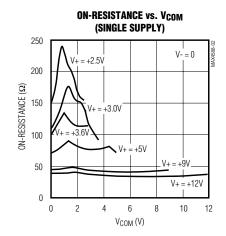

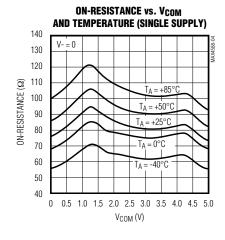

V- をGNDに接続すると、MAX4588は+2.7V~+12Vの単一電源で動作します。「バイポーラ電源動作」の注意事項に従って下さい。但し、これらのデバイスは±5V動作用に最適化されているため、±5V以下で使用した場合、AC及びDC特性にかなりの劣化が見られることに注意して下さい。全体的な電源電圧(V+とV-の差)が小さくなると、スイッチング速度、オン抵抗、オフアイソレーション及び歪みが劣化します(「標準動作特性」を参照)。

単一電源動作の場合は信号レベルも制限され、接地された信号への干渉が生じます。V-=0Vの場合、AC信号は-0.3Vまでに制限されます。-0.3V以下の電圧は内部ESD保護ダイオードによってクランプされ、過剰な電流が流れるとデバイスが損傷します。

#### 電源オフ

「絶対最大定格」は、MAX4588の電源がオフの場合 (即ちV+=0VかつV-=0V)にも適用されます。これは、MAX4588のいかなるピンも、±0.3Vを超えることが許されないことを意味します。±0.3V以上の電圧がかかると内部ESD保護ダイオードが電流を通し、破壊的な結果を招く恐れがあります。

#### 電源シーケンス

MAX4588の電源を投入する時は、V+、V-(グランド以外の電位にバイアスされている場合)、VLそしてロジック入力という順番で行って下さい。V+、V-及びGNDの電圧が設定された後は、いつでもアナログNO\_及びCOM\_ピンに信号を印加することができます。回路設計で同時パワーアップが保証されている場合に限り、全てのピンを同時にターンオンすることが許されます。

パワーダウンシーケンスはパワーアップシーケンスの逆です。すなわち、VL及びロジック入力がまずゼロ電位になり、その後(あるいは同時に)V-、そして次にV+の順番でゼロ電位になる必要があります。適正な動作を保証するためには、常に「絶対最大定格」を守って下さい。

#### グランディング

#### DCグランドの考慮

良好な高周波動作を得るには、グランディングに注意深い配慮が必要です。殆どのアプリケーションではグランドプレーンの使用が推奨されます。また、全てのGNDピンを銅の導体でグランドプレーンに接続して下さい。V+及びV-電源ピンはパッケージ内の全てのスイッチに共通ですが、各入力は互いに内部で接続されていないグランドピンによって分離されています。これにより、チャネル間のクロストークが低減され、全体的な高周波性能が向上します。全てのGNDピンはESDダイオードを通じてV+及びV-に接続されています。

ディジタルグランドとアナログ(信号)グランドが別になったシステムでは、全てのGNDピンをアナログ信号グランドに接続して下さい。良好なディジタルグランドを確保するよりも良好な信号グランドを確保することの方がずっと重要です。グランド電流は僅か数 n Aです。

ディジタル入力の電圧スレッショルドは、V+及びGNDで決まります(V-はロジックレベルスレッショルドには影響しません)。 $V_L$ に+5Vが印加された状態のスレッショルドは約1.6Vであるため、TTL及びCMOSロジックドライバとのコンパチビリティが保証されます。

#### ACグランド及びバイパス

高周波数で十分な性能を発揮させるには、グランドプレーンが必須です。試作の際に手で配線したり、ワイヤラップボードを使用するのは避けて下さい。全てのGNDピンは銅の導体でグランドプレーンに接続して下さい。(GNDピンにより高周波グランドがパッケージのワイヤフレームを通じてシリコンそのものにまで延長されるため、アイソレーションが改善されます。)デバイスの下のグランドプレーンは隙間や穴のない金属にして下さい。デバイスの下にトレースが来ないようにして下さい。デバイスの下にトレースが来ないようにして下さい。DIPパッケージの場合、これは配線ボードの両面について適用されます。これを怠ると、スイッチの高周波におけるオン特性には殆ど影響がありませんが、オフアイソレーションとクロストークが劣化します。

MAX4588のSOPパッケージをグランドプレーンが埋もれているプリント基板で使用する場合、各GNDピンを別々のビアでグランドプレーンに接続して下さい。このビアを他のグランド経路と共有しないで下さい。SMTランドの両側にグランドビアを設けると、寄生インダク

タンスが小さくなり、オフアイソレーションがさらに 改善されます。DIPパッケージの場合、スルーホールを 埋もれたプレーンに直接接続するか、あるいは製造上の 条件を満たすために必要に応じてスルーホールに耐熱用 リリーフを設けて下さい。ここでも、スルーホール パッドを他の部品の電流経路として使わないようにして 下さい。

全てのV+及びV-ピンは、表面実装0.01µFコンデンサでグランドプレーンにバイパスして下さい。コンデンサはデバイスと同じ側のこれらのピンのできるだけ近くに取り付けて下さい。バイパスコンデンサには、フィードスルーやビアは使用しないで下さい。基板レイアウトの関係でバイパスコンデンサを基板の反対側に取り付ける場合は、V+及びV-ピンの直下で、短いフィードスルー又はビアを使用して下さい。可能であれば複数のビアを使って下さい。V-が0Vの場合は、銅の導体でグランドプレーンに直接接続して下さい。全てのトレースを短くして下さい。

#### 信号配線

全ての信号リードをできるだけ短くして下さい。全ての信号リードをお互い及びその他の干渉しそうなトレースから分離して下さい。信号トレース同士の間を大きめのサイズのグランドワイヤで隔離すると干渉を抑えることができます。MAX4588のできるだけ近くで終端処理された同軸ケーブルを使って信号を配線すると最高のアイソレーションが得られます。

#### 基板レイアウト

ICソケットは高周波性能を劣化させるため、信号帯域幅が5MHz以上の場合は使用しないで下さい。表面実装デバイスは内部リードフレームが短いため、最良の高周波性能を実現します。全てのバイパスコンデンサはデバイスの近くに配置し、全ての信号リードはグランドプレーンで分離して下さい。この様なグランドはデバイスに近くなるに従ってくさび形になります。ボードの両側のグランドプレーン同士を接続するにはビアを使用して下さい。このビアは、信号リード同士を分離するくさび形のグランドの頂点に配置して下さい。ロジックレベル信号リードの配置は重要ではありません。

#### インピーダンスマッチング

MAX4588は(入力がICの外で終端処理され、COM端子から見たインピーダンスが600 以上の)75 機器で使用するよう設計されています。MAX4588はICを通した終端処理を施した50 及び75 機器でも動作しますが、オン抵抗及びオン抵抗平坦性の変動により非直線性が生じます。

#### クロストーク及びオフアイソレーション

「標準動作特性」に示すクロストークとオフアイソレーションのグラフは隣接するチャネルについて測定されたものです。隣接チャネルは最悪の条件です。例えば、NO1はCOM1との間のオフアイソレーションが最悪ですが、これは互いに近接しているためです。さらに、NO1はNO2とのクロストークが最も大きく、NO4とのクロストークは最も小さくなっています。チャネルの賢明な選定には、最も敏感なチャネルを最も有害なチャネルから分離することが必須です。これはNO5~NO8入力とCOM2ピンについても成り立ちます。

#### パワーオンリセット(POR)

MAX4588はパワーアップ時に既知の状態になることを保証する内部回路を備えています。デフォルト状態においては、A0 = A1 = A2 = 0、ディセーブル=1、及び全てのスイッチがオフになります。この状態は通常動作において $\overline{RS}$ を発生した場合と同じです。

#### シリアル動作

シリアルモードはSER/PAR入力ピンをロジックハイに 駆動することによって起動されます。データは通常の SPI/MICROWIRE書込み動作を使って入力されます。 シリアルインタフェースロジックの詳細は図7を参照して下さい。シフトレジスタ内に4つのフリップフロップがあり、4番目のシフトレジスタの出力がDOUTピンの出力になっています。注:DOUTはSCLKの立上がりエッジで変化します。

これにより、ただ1本のチップセレクトラインを使って複数のMAX4588をカスケード接続することができます。例えば、1つの16ビット書込みにより4つのカスケード接続されたMAX4588のシフトレジスタにロードすることができます。シフトレジスタからのデータはCSの立上がりエッジでのみ内部制御ラッチに移されるため、4つのMAX4588の全ての状態が同時に変化します。

#### パラレル動作

パラレルモードはSER/PARをロジックローに駆動することによって起動されます。MAX4588はラッチ付パラレルバス方式でプログラムされます。パラレルインタフェースロジックの詳細については図6を参照して下さい。4/8はラッチされないことに注意して下さい。希望の動作モードになるように4/8を既知の状態にハード配線するか、あるいは専用のマイクロコントローラポートピンを使って下さい。

#### 真理値表

### パラレル動作

| SER/PAR | A2 | A1 | Α0 | EN | Œ | RS | 4/8 | SWITCH STATES                                       |

|---------|----|----|----|----|---|----|-----|-----------------------------------------------------|

| 0       | Х  | Х  | Х  | Х  | 1 | 1  | Х   | Maintain previous state.                            |

| Х       | Х  | Х  | Х  | Х  | х | 0  | Х   | All switches off, latches are cleared.              |

| 1       | Х  | х  | х  | Х  | х | 1  | х   | Serial Mode. Refer to Serial Operation Truth Table. |

| 0       | Х  | Х  | Х  | 0  | 0 | 1  | Х   | All switches off.                                   |

| 0       | 0  | 0  | 0  | 1  | 0 | 1  | 0   | Connects NO1 to COM1                                |

| 0       | 0  | 0  | 1  | 1  | 0 | 1  | 0   | Connects NO2 to COM1                                |

| 0       | 0  | 1  | 0  | 1  | 0 | 1  | 0   | Connects NO3 to COM1                                |

| 0       | 0  | 1  | 1  | 1  | 0 | 1  | 0   | Connects NO4 to COM1                                |

| 0       | 1  | 0  | 0  | 1  | 0 | 1  | 0   | Connects NO5 to COM2                                |

| 0       | 1  | 0  | 1  | 1  | 0 | 1  | 0   | Connects NO6 to COM2                                |

| 0       | 1  | 1  | 0  | 1  | 0 | 1  | 0   | Connects NO7 to COM2                                |

| 0       | 1  | 1  | 1  | 1  | 0 | 1  | 0   | Connects NO8 to COM2                                |

| 0       | Х  | 0  | 0  | 1  | 0 | 1  | 1   | Connect NO1 to COM1 and NO5 to COM2                 |

| 0       | Х  | 0  | 1  | 1  | 0 | 1  | 1   | Connect NO2 to COM1 and NO6 to COM2                 |

| 0       | Х  | 1  | 0  | 1  | 0 | 1  | 1   | Connect NO3 to COM1 and NO7 to COM2                 |

| 0       | Х  | 1  | 1  | 1  | 0 | 1  | 1   | Connect NO4 to COM1 and NO8 to COM2                 |

#### x = 任意

**Note:** 4/8 is not latched when LE is high. When LE is low, all latches are transparent. A2, A1, A0, and EN are latched. Connect COM1 to COM2 externally for 1-of-8 single-ended operation.

真理値表(続き)\_\_\_\_\_

### シリアル動作

| SER/PAR | <u>cs</u> | SCLK | DIN | EN | RS | DOUT   | ON SWITCHES/STATES                                                                                |

|---------|-----------|------|-----|----|----|--------|---------------------------------------------------------------------------------------------------|

| 1       | Х         | х    | Х   | ×  | 0  | 0      | All switches off. Latches and shift register are cleared. This is the power-on reset (POR) state. |

| 0       | х         | ×    | ×   | ×  | х  | High-Z | Parallel Mode. Refer to Parallel Operation Truth Table.                                           |

| 1       | Х         | Х    | Х   | 0  | 1  | *      | All switches off.                                                                                 |

| 1       | 1         | Х    | Х   | 1  | 1  | *      | Chip unselected.                                                                                  |

| 1       | 0         |      | 0   | 1  | 1  | *      | Input shift register loads one bit from DIN. DOUT updates on SCLK's rising edge.                  |

| 1       | 0         |      | 1   | 1  | 1  | *      | Input shift register loads one bit from DIN. DOUT updates on SCLK's rising edge.                  |

| 1       |           | ×    | Х   | 1  | 1  | *      | Contents of shift register transferred to control latches.                                        |

x = 任意

### 制御ビット及び4/8ロジック

| DISABLE<br>BIT | A2<br>BIT | A1<br>BIT | A0<br>BIT | 4/8<br>PIN | ON SWITCHES/STATES                  |

|----------------|-----------|-----------|-----------|------------|-------------------------------------|

| 1              | Х         | Х         | Х         | Х          | All switches off.                   |

| 0              | 0         | 0         | 0         | 0          | Connect NO1 to COM1                 |

| 0              | 0         | 0         | 1         | 0          | Connect NO2 to COM1                 |

| 0              | 0         | 1         | 0         | 0          | Connect NO3 to COM1                 |

| 0              | 0         | 1         | 1         | 0          | Connect NO4 to COM1                 |

| 0              | 1         | 0         | 0         | 0          | Connect NO5 to COM2                 |

| 0              | 1         | 0         | 1         | 0          | Connect NO6 to COM2                 |

| 0              | 1         | 1         | 0         | 0          | Connect NO7 to COM2                 |

| 0              | 1         | 1         | 1         | 0          | Connect NO8 to COM2                 |

| 0              | Х         | 0         | 0         | 1          | Connect NO1 to COM1 and NO5 to COM2 |

| 0              | Х         | 0         | 1         | 1          | Connect NO2 to COM1 and NO6 to COM2 |

| 0              | Х         | 1         | 0         | 1          | Connect NO3 to COM2 and NO7 to COM2 |

| 0              | Х         | 1         | 1         | 1          | Connect NO4 to COM2 and NO8 to COM2 |

#### x = 任意

Note: DISABLE, A2, A1, and A0 are the 4 bits latched into the MAX4588 with a MICROWIRE/SPI write. A0 is the LSB (first bit in time). DISABLE is the MSB (last bit in time).

<sup>\*</sup>DOUT is delayed by 4 clock cycles from DIN.

| チップ情報 |  |

|-------|--|

|       |  |

TRANSISTOR COUNT: 1033

パッケージ \_\_\_\_\_

|                                       |            |                 |                           |        |         | ٦«            |

|---------------------------------------|------------|-----------------|---------------------------|--------|---------|---------------|

| NOTES:                                |            | INCH            | ES                        | MILLIM | 1ETERS  | 28I NPDIP FPS |

| 1. D&E DO NOT INCLUDE MOLD FLASH.     | DIM        | MIN             | MAX                       | MIN    | MAX     | 2             |

| 2. MOLD FLASH OR PROTRUSIONS          | Α .        |                 | 0.180                     |        | 4.572   | °             |

| NOT TO EXCEED .254mm(.010").          | A1         | 0.020           |                           | 0.508  |         |               |

| 3. CONTROLLING DIMENSION: MILLIMETER. | A2 I       | 0.125           | 0.150                     | 3.175  | 3.810   |               |

| 4. MEETS JEDEC MO-095-AH.             | В          | 0.015           | 0.022                     | 0.381  | 0.559   |               |

|                                       | B1         | 0.045           | 0.060                     | 1.143  | 1.524   |               |

| <u> </u>                              | B2 I       | 0.035           | 0.045                     | 0.889  | 1.143   |               |

|                                       |            | 0.008           | 0.012                     | 0.203  | 0.305   |               |

|                                       | _          | 1.350           |                           | 34.290 |         |               |

| 4                                     | _          | 0.300           | 0.325                     | 7.620  | 8.255   |               |

|                                       |            | 0.275           | 0.295                     | 6.985  | 7.493   |               |

|                                       | <u>e1</u>  | .100 I          |                           |        | BSC     |               |

|                                       | eА         | .300            |                           | 7.62   |         |               |

|                                       | _          | 0.115           | 0.150                     | 2.921  | 3.810   |               |

|                                       | α          | 0°              | 15°                       | 0*     | 15°     | 1             |

|                                       | ETARY INFO | RMATION  VAR) F | PDIP □L ent control -0400 |        | rev A 1 |               |

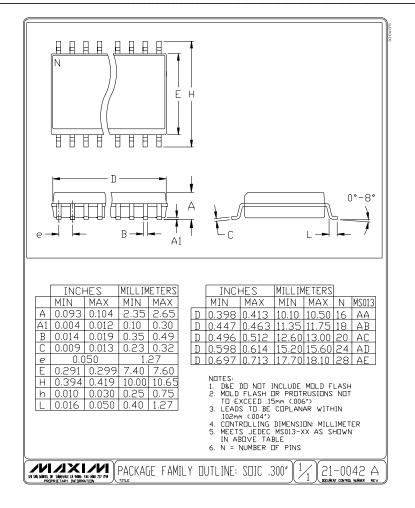

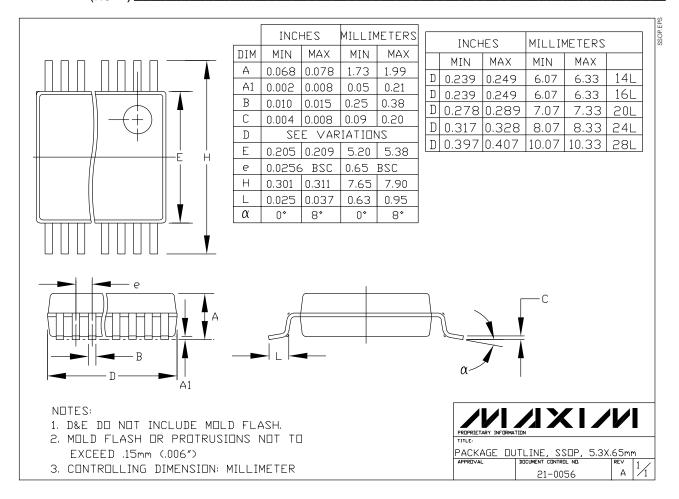

パッケージ(続き)

パッケージ(続き)

| <b></b> 販売代理店 |   |

|---------------|---|

|               |   |

|               |   |

|               |   |

|               |   |

|               |   |

|               | , |

## マキシム・ジャパン株式会社

〒169-0051東京都新宿区西早稲田3-30-16(ホリゾン1ビル) TEL. (03)3232-6141 FAX. (03)3232-6149

マキシム社では全体がマキシム社製品で実現されている回路以外の回路の使用については責任を持ちません。回路特許ライセンスは明言されていません。マキシム社は随時予告なしに回路及び仕様を変更する権利を保留します。

20 \_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600