## クワッド、鋼ケーブルシグナルコンディショナ

## 概要

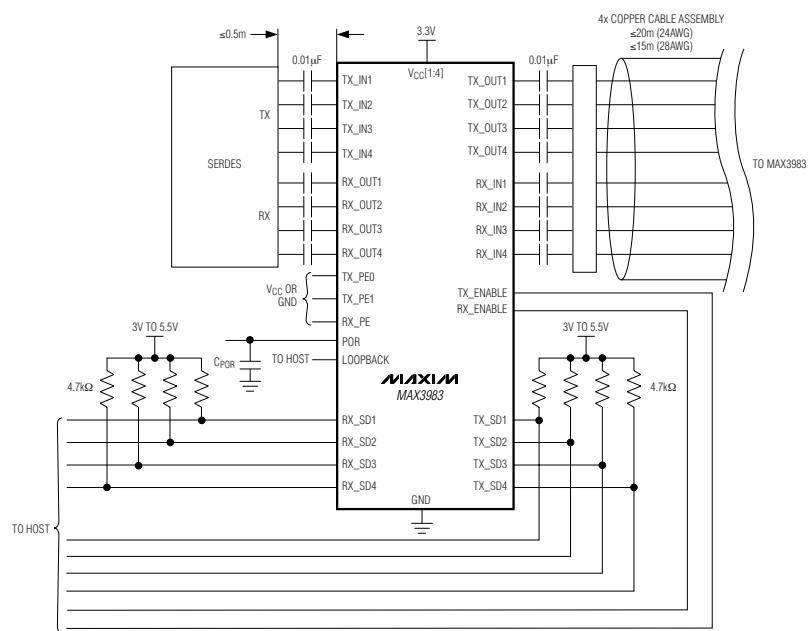

MAX3983は、動作速度2.5Gbps～3.2Gbpsのクワッド銅ケーブルシグナルコンディショナです。4x銅ケーブルInfiniBandや10GBASE-CX4 Ethernetリンク用に補償を行うデバイスで、24AWGで20m、28AWGで15mという伝送距離を実現します。ケーブルドライバ部は、4つのプリエンファシスレベルが選べます。ケーブルドライバへの入力は、FR4プリント基板で0.5mまで補償します。ケーブルレシーバ部にも固定入力イコライゼーションが用意されているだけでなく、選択可能なプリエンファシスにより0.5mまでのFR4プリント基板を駆動できます。

MAX3983は8本の入力すべてに対して信号検出し、診断テスト用の内部ループバックも用意しています。10mm x 10mmの68ピンQFNパッケージで提供されており、動作温度は0°C~+85°Cです。

## アプリケーション

- 4x InfiniBand(4 x 2.5Gbps)

- 10GBASE-CX4 Ethernet(4 x 3.125Gbps)

- 10GファイバチャネルXAUUI(4 x 3.1875Gbps)

- 4x銅ケーブルまたはバックプレーン伝送(1Gbps~3.2Gbps)

## 標準動作回路

## 特長

## ◆ リンクの特長

伝送距離：20m(24AWG)、15m(28AWG)

ホストごとのFR4基板上の伝送距離：0.5m

消費電力:1.6W(3.3V電源)

ループバック機能

#### ◆ ケーブルドライバの特長

選択可能な出力プリエンファシス

FR4入力のイコライゼーション

チャネルごとの信号検出

出力ディィセーブル

#### ◆ ケーブルレシーバの特長

選択可能なFR4出力プリエンファシス

ケーブル入力のイコライゼーション

チャネルごとの信号検出

出力ディイセーブル

番型

| PART       | TEMP RANGE   | PIN-PACKAGE | PKG CODE |

|------------|--------------|-------------|----------|

| MAX3983UGK | 0°C to +85°C | 68 QFN      | G6800-4  |

ピン配置はデータシートの最後に記載されています。

# クワッド、銅ケーブルシグナルコンディショナ

## ABSOLUTE MAXIMUM RATINGS

Supply Voltage,  $V_{CC}$ .....-0.5V to +6.0V

Continuous CML Output Current at

$TX_{OUT}[1:4]\pm, RX_{OUT}[1:4]\pm$ .....±25mA

Voltage at  $TX_{IN}[1:4]\pm, RX_{IN}[1:4]\pm, RX_{SD}[1:4]$ ,

$TX_{SD}[1:4], RX_{ENABLE}, TX_{ENABLE}, RX_{PE}$ ,

$TX_{PE[0:1]}, LOOPBACK, POR$

(with series resistor  $\geq 4.7\text{k}\Omega$ ).....-0.5V to ( $V_{CC} + 0.5\text{V}$ )

Continuous Power Dissipation ( $T_A = +85^\circ\text{C}$ )

68-Pin QFN (derate 41.7mW/°C above +85°C).....2.7W

Operating Junction Temperature Range ( $T_J$ ).....-55°C to +150°C

Storage Ambient Temperature Range ( $T_S$ ).....-55°C to +150°C

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

( $V_{CC} = +3.0\text{V}$  to  $+3.6\text{V}$ ,  $T_A = 0^\circ\text{C}$  to  $+85^\circ\text{C}$ . Typical values are at  $V_{CC} = +3.3\text{V}$  and  $T_A = +25^\circ\text{C}$ , unless otherwise noted.)

| PARAMETER                                                                                           | SYMBOL   | CONDITIONS                                                                                                                                                     | MIN  | TYP  | MAX | UNITS                    |

|-----------------------------------------------------------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|--------------------------|

| Supply Current                                                                                      |          | $RX_{EN} = V_{CC}, TX_{EN} = 0\text{V}$                                                                                                                        | 360  | 430  |     | mA                       |

|                                                                                                     |          | $RX_{EN} = 0\text{V}, TX_{EN} = V_{CC}$                                                                                                                        | 365  | 430  |     |                          |

|                                                                                                     |          | $RX_{EN} = V_{CC}, TX_{EN} = V_{CC}$                                                                                                                           | 495  | 580  |     |                          |

| <b>OPERATING CONDITIONS</b>                                                                         |          |                                                                                                                                                                |      |      |     |                          |

| Supply Voltage                                                                                      | $V_{CC}$ |                                                                                                                                                                | 3.0  | 3.3  | 3.6 | V                        |

| Supply Noise Tolerance                                                                              |          | $1\text{MHz} \leq f < 2\text{GHz}$                                                                                                                             |      | 40   |     | $\text{mV}_{\text{P-P}}$ |

| Operating Ambient Temperature                                                                       | $T_A$    |                                                                                                                                                                | 0    | 25   | 85  | °C                       |

| Bit Rate                                                                                            |          | NRZ data (Note 1)                                                                                                                                              | 2.5  | 3.2  |     | Gbps                     |

| CID                                                                                                 |          | Consecutive identical digits (bits)                                                                                                                            |      | 10   |     | Bits                     |

| <b>STATUS OUTPUTS: <math>RX_{SD}[1:4], TX_{SD}[1:4]</math></b>                                      |          |                                                                                                                                                                |      |      |     |                          |

| Signal-Detect Open-Collector Current Sink                                                           |          | Signal detect asserted                                                                                                                                         | 0    | 25   |     | $\mu\text{A}$            |

|                                                                                                     |          | Signal detect unasserted $V_{OL} \leq 0.4\text{V}$ with $4.7\text{k}\Omega$ pullup resistor                                                                    | 1.0  | 1.11 |     | mA                       |

|                                                                                                     |          | $V_{CC} = 0\text{V}$ , pullup supply = $5.5\text{V}$ , external pullup resistor $\geq 4.7\text{k}\Omega$                                                       | 0    | 25   |     | $\mu\text{A}$            |

| Signal-Detect Response Time                                                                         |          | Time from $RX_{IN}[1:4]$ or $TX_{IN}[1:4]$ dropping below $85\text{mV}_{\text{P-P}}$ or rising above $175\text{mV}_{\text{P-P}}$ to 50% point of signal detect |      | 0.35 |     | $\mu\text{s}$            |

| Signal-Detect Transition Time                                                                       |          | Rise time or fall time (10% to 90%)                                                                                                                            |      | 200  |     | ns                       |

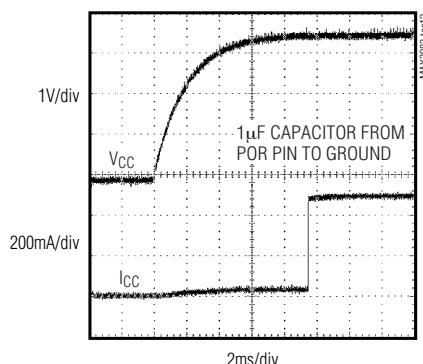

| Power-On Reset Delay                                                                                |          | $1\mu\text{F}$ capacitor on POR to GND                                                                                                                         |      | 6    |     | ms                       |

| <b>CONTROL INPUTS: <math>RX_{ENABLE}, TX_{ENABLE}, RX_{PE}, TX_{PE0}, TX_{PE1}, LOOPBACK</math></b> |          |                                                                                                                                                                |      |      |     |                          |

| Voltage, Logic High                                                                                 | $V_{IH}$ |                                                                                                                                                                | 1.5  |      |     | V                        |

| Voltage, Logic Low                                                                                  | $V_{IL}$ |                                                                                                                                                                |      | 0.5  |     | V                        |

| Current, Logic High                                                                                 | $I_{IH}$ | $V_{IH} = V_{CC}$                                                                                                                                              | -150 | +150 |     | $\mu\text{A}$            |

| Current, Logic Low                                                                                  | $I_{IL}$ | $V_{IL} = 0\text{V}$                                                                                                                                           | -150 | +150 |     | $\mu\text{A}$            |

# クワッド、銅ケーブルシグナルコンディショナ

MAX3983

## ELECTRICAL CHARACTERISTICS (continued)

(V<sub>CC</sub> = +3.0V to +3.6V, T<sub>A</sub> = 0°C to +85°C. Typical values are at V<sub>CC</sub> = +3.3V and T<sub>A</sub> = +25°C, unless otherwise noted.)

| PARAMETER                                                       | SYMBOL                          | CONDITIONS                                                     |                | MIN    | TYP    | MAX  | UNITS             |  |

|-----------------------------------------------------------------|---------------------------------|----------------------------------------------------------------|----------------|--------|--------|------|-------------------|--|

| <b>TX SECTION (CABLE DRIVER)</b>                                |                                 |                                                                |                |        |        |      |                   |  |

| PC Board Input Swing                                            |                                 | Measured differentially at the signal source (Note 1)          |                |        | 800    | 1600 | mV <sub>P-P</sub> |  |

| Input Resistance                                                |                                 | TX_IN[1:4]+ to TX_IN[1:4]-, differential                       |                |        | 85     | 100  | 115               |  |

| Input Return Loss                                               |                                 | 100MHz to 2GHz (Note 1)                                        |                |        | 10     | 17   | dB                |  |

| Output Swing                                                    |                                 | TX_ENABLE = high (Notes 1, 2)                                  |                |        | 1300   | 1500 | 1600              |  |

|                                                                 |                                 | TX_ENABLE = low                                                |                |        |        | 30   | mV <sub>P-P</sub> |  |

| Output Resistance                                               |                                 | TX_OUT[1:4]+ or TX_OUT[1:4]- to V <sub>CC</sub> , single ended |                |        | 42     | 50   | 58                |  |

| Output Return Loss                                              |                                 | 100MHz to 2GHz (Note 1)                                        |                |        | 10     | 13   | dB                |  |

| Output Transition Time                                          | t <sub>r</sub> , t <sub>f</sub> | 20% to 80% (Notes 1, 3)                                        |                |        |        | 80   | ps                |  |

| Random Jitter                                                   |                                 | (Notes 1, 3)                                                   |                |        |        | 1.6  | psRMS             |  |

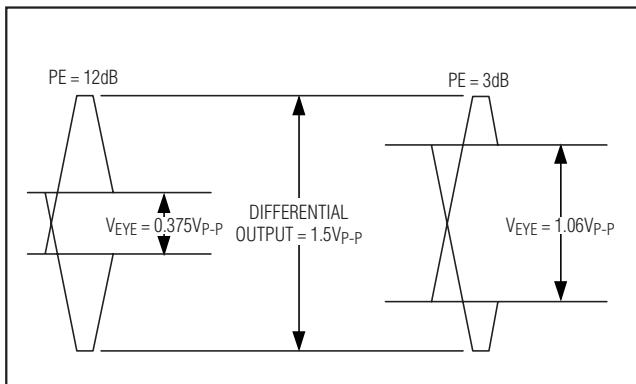

| Output Preemphasis                                              | See Figure 1                    |                                                                | TX_PE1         | TX_PE0 |        |      | dB                |  |

|                                                                 |                                 |                                                                | 0              | 0      |        | 3    |                   |  |

|                                                                 |                                 |                                                                | 0              | 1      |        | 6    |                   |  |

|                                                                 |                                 |                                                                | 1              | 0      |        | 9    |                   |  |

|                                                                 |                                 |                                                                | 1              | 1      |        | 12   |                   |  |

| Residual Output Deterministic Jitter at 2.5Gbps (Notes 1, 4, 5) |                                 | Source to TX_IN                                                | TX_OUT to Load | TX_PE1 | TX_PE0 |      | UIP-P             |  |

|                                                                 |                                 |                                                                | 1m, 28AWG      | 0      | 0      |      |                   |  |

|                                                                 |                                 |                                                                | 5m, 28AWG      | 0      | 1      |      |                   |  |

|                                                                 |                                 |                                                                | 10m, 24AWG     | 1      | 0      |      |                   |  |

|                                                                 |                                 |                                                                | 15m, 24AWG     | 1      | 1      |      |                   |  |

| Residual Output Deterministic Jitter at 3.2Gbps (Notes 1, 4, 5) |                                 | Source to TX_IN                                                | TX_OUT to Load | TX_PE1 | TX_PE0 |      | UIP-P             |  |

|                                                                 |                                 |                                                                | 1m, 28AWG      | 0      | 0      |      |                   |  |

|                                                                 |                                 |                                                                | 5m, 28AWG      | 0      | 1      |      |                   |  |

|                                                                 |                                 |                                                                | 10m, 24AWG     | 1      | 0      |      |                   |  |

|                                                                 |                                 |                                                                | 15m, 24AWG     | 1      | 1      |      |                   |  |

| Signal-Detect Assert Level                                      |                                 | TX_IN for TX_SD = high (Note 6)                                |                |        | 800    |      | mV <sub>P-P</sub> |  |

| Signal-Detect Off                                               |                                 | TX_IN for TX_SD = low (Note 6)                                 |                |        |        | 200  | mV <sub>P-P</sub> |  |

| <b>RX SECTION (CABLE RECEIVER)</b>                              |                                 |                                                                |                |        |        |      |                   |  |

| Cable Input Swing                                               |                                 | Measured differentially at the signal source (Note 1)          |                |        | 1000   | 1600 | mV <sub>P-P</sub> |  |

| Input Vertical Eye Opening                                      |                                 | Measured differentially at the input of the MAX3983 (Note 1)   |                |        | 175    | 1600 | mV <sub>P-P</sub> |  |

| Input Resistance                                                |                                 | RX_IN[1:4]+ to RX_IN[1:4]-, differential                       |                |        | 85     | 100  | 115               |  |

| Input Return Loss                                               |                                 | 100MHz to 2GHz (Note 1)                                        |                |        | 10     | 18   | dB                |  |

## クワッド、銅ケーブルシグナルコンディショナ

## ELECTRICAL CHARACTERISTICS (continued)

(V<sub>CC</sub> = +3.0V to +3.6V, T<sub>A</sub> = 0°C to +85°C. Typical values are at V<sub>CC</sub> = +3.3V and T<sub>A</sub> = +25°C, unless otherwise noted.)

| PARAMETER                                                             | SYMBOL                          | CONDITIONS                                                     |                 |        | MIN       | TYP            | MAX   | UNITS     |       |

|-----------------------------------------------------------------------|---------------------------------|----------------------------------------------------------------|-----------------|--------|-----------|----------------|-------|-----------|-------|

| Output Swing                                                          |                                 | RX_ENABLE = high (Notes 1, 7)                                  |                 |        | 1100      | 1500           |       | mVp-p     |       |

|                                                                       |                                 | RX_ENABLE = low                                                |                 |        |           | 30             |       |           |       |

| Output Resistance                                                     |                                 | RX_OUT[1:4]+ or RX_OUT[1:4]- to V <sub>CC</sub> , single ended |                 |        | 42        | 50             | 58    | Ω         |       |

| Output Return Loss                                                    |                                 | 100MHz to 2GHz (Note 1)                                        |                 |        | 10        | 15             |       | dB        |       |

| Output Transition Time                                                | t <sub>r</sub> , t <sub>f</sub> | 20% to 80% (Notes 1, 8)                                        |                 |        |           | 45             | 80    | ps        |       |

| Random Jitter                                                         |                                 | (Notes 1, 8)                                                   |                 |        |           | 1.6            |       | psrms     |       |

| Output Preemphasis                                                    |                                 | RX_PE = low                                                    |                 |        |           | 3              |       | dB        |       |

|                                                                       |                                 | RX_PE = high                                                   |                 |        |           | 6              |       |           |       |

| Residual Output Deterministic Jitter at 2.5Gbps (Notes 1, 5, 9, 10)   |                                 | Source to RX_IN                                                | RX_OUT to Load  | RX_PE  | 0.10 0.15 |                |       | UIp-p     |       |

|                                                                       |                                 | 5m, 28AWG IB Cable Assembly without preemphasis                | 0in, 6-mil FR4  | 0      |           |                |       |           |       |

|                                                                       |                                 |                                                                | 20in, 6-mil FR4 | 1      |           |                |       |           |       |

|                                                                       |                                 | 5m, 28AWG IB cable assembly without preemphasis                | 0in, 6-mil FR4  | 0      |           |                |       |           |       |

|                                                                       |                                 |                                                                | 20in, 6-mil FR4 | 1      |           |                |       |           |       |

| Signal-Detect Assert Level                                            |                                 | RX_IN for RX_SD = high (Note 11)                               |                 |        | 175       |                |       | mVp-p     |       |

| Signal-Detect Off                                                     |                                 | RX_IN for RX_SD = low (Note 11)                                |                 |        |           | 85             |       | mVp-p     |       |

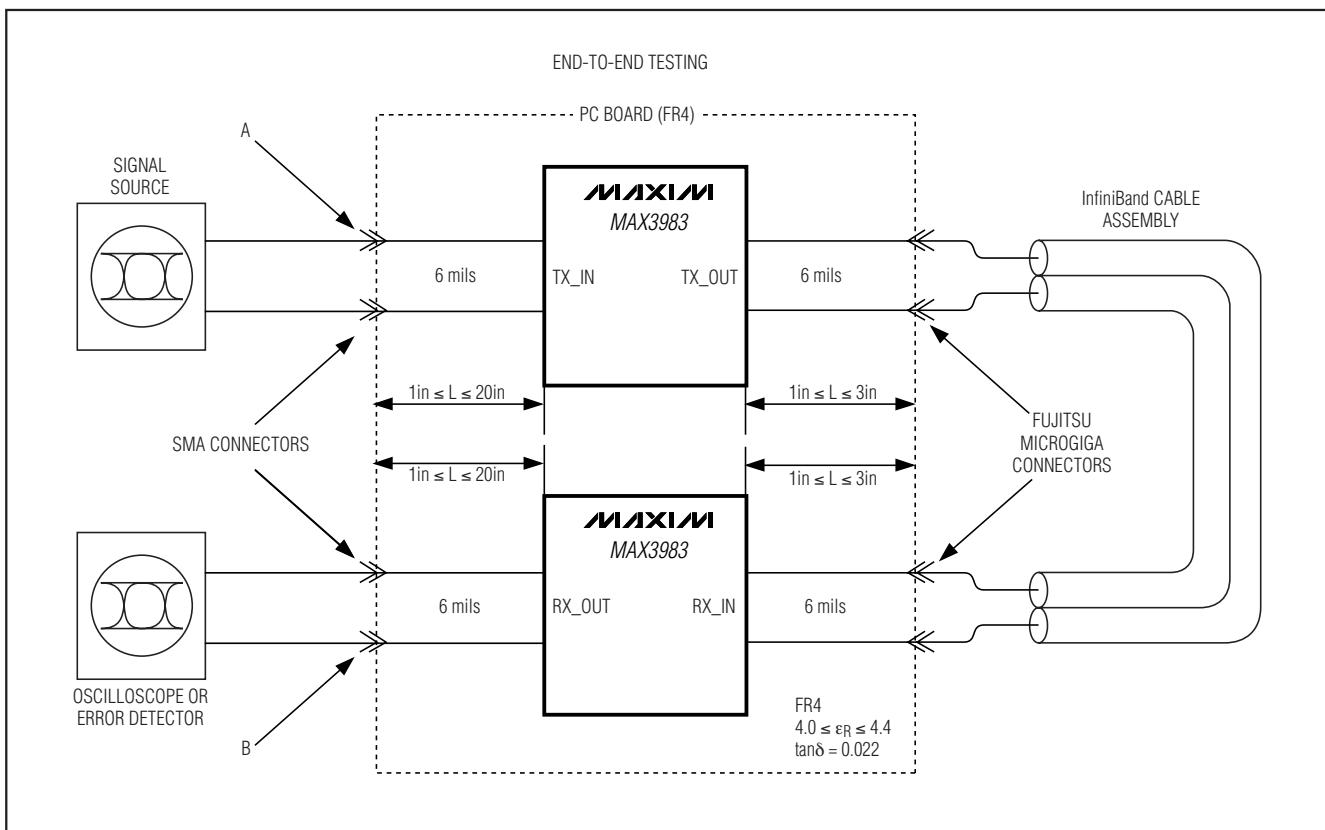

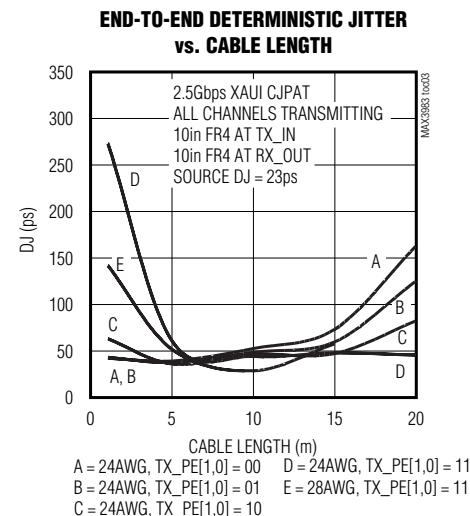

| <b>END-TO-END JITTER (TX AND RX COMBINED PERFORMANCE)</b>             |                                 |                                                                |                 |        |           |                |       |           |       |

| Residual Output Deterministic Jitter at 2.5Gbps (Notes 1, 12, 13, 14) |                                 | Source to TX_IN                                                | TX_OUT to RX_IN | TX_PE1 | TX_PE0    | RX_OUT to Load | RX_PE | 0.15 0.20 | UIp-p |

|                                                                       |                                 | 6-mil FR4 ≤ 20in                                               | 1m, 24AWG       | 0      | 0         | 0in            | 0     |           |       |

|                                                                       |                                 |                                                                | 15m, 24AWG      | 1      | 1         | 20in           | 1     |           |       |

|                                                                       |                                 |                                                                | 20m, 24AWG      | 1      | 1         | 20in           | 1     |           |       |

## ELECTRICAL CHARACTERISTICS (continued)

(V<sub>CC</sub> = +3.0V to +3.6V, T<sub>A</sub> = 0°C to +85°C. Typical values are at V<sub>CC</sub> = +3.3V and T<sub>A</sub> = +25°C, unless otherwise noted.)

| PARAMETER                                                                | SYMBOL | CONDITIONS        |                 |        |        | MIN            | TYP   | MAX                         | UNITS |

|--------------------------------------------------------------------------|--------|-------------------|-----------------|--------|--------|----------------|-------|-----------------------------|-------|

| Residual Output Deterministic Jitter at 3.2Gbps<br>(Notes 1, 12, 13, 14) |        | Source to TX_IN   | TX_OUT to RX_IN | TX_PE1 | TX_PE0 | RX_OUT to Load | RX_PE | 0.20<br>0.25<br>0.25<br>0.3 | UIp-P |

|                                                                          |        | 6-mil FR4 ≤ 20 in | 1m, 24AWG       | 0      | 0      | 5in            | 0     |                             |       |

|                                                                          |        |                   | 15m, 24AWG      | 1      | 1      | 20in           | 1     |                             |       |

|                                                                          |        |                   | 20m, 24AWG      | 1      | 1      | 20in           | 1     |                             |       |

**Note 1:** Guaranteed by design and characterization.**Note 2:** Measured with 2in of FR4 through InfiniBand connector with TX\_PE1 = TX\_PE0 = 1.**Note 3:** Measured at the chip using 0000011111 or equivalent pattern. TX\_PE1 = TX\_PE0 = 0 for minimum preemphasis.**Note 4:** All channels under test are not transmitting during test. Channel tested with XAUI CJPAT, as well as this pattern: 19 zeros, 1, 10 zeros, 1010101010 (D21.5 character), 1100000101 (K28.5+ character), 19 ones, 0, 10 ones, 0101010101 (D10.2 character), 0011111010 (K28.5- character).**Note 5:** Cables are unequalized, Amphenol Spectra-Strip 24AWG and 28AWG or equivalent equipped with Fujitsu "MicroGiga" connector or equivalent. All other channels are quiet. Residual deterministic jitter is the difference between the source jitter and the output jitter at the load. The deterministic jitter (DJ) at the output of the transmission line must be from media-induced loss and not from clock-source modulation. Depending upon the system environment, better results can be achieved by selecting different preemphasis levels.**Note 6:** Tested with a 1GHz sine wave applied at TX\_IN under test with less than 5in of FR4.**Note 7:** Measured with 3in of FR4 with RX\_PE = 1.**Note 8:** Measured at the chip using 0000011111 or equivalent pattern. RX\_PE = low (minimum). Signal source is 1Vp-P with 5m, 28AWG InfiniBand cable.**Note 9:** All other receive channels are quiet. TX\_ENABLE = 0. Channel tested with XAUI CJPAT as well as this pattern: 19 zeros, 1, 10 zeros, 1010101010 (D21.5 character), 1100000101 (K28.5+ character), 19 ones, 0, 10 ones, 0101010101 (D10.2 character), 0011111010 (K28.5- character).**Note 10:** FR4 board material: 6-mil-wide, 100Ω, edge-coupled stripline ( $\tan\delta = 0.022$ ,  $4.0 < \epsilon_R < 4.4$ ).**Note 11:** Tested with a 1GHz sine wave applied at RX\_IN under test with less than 5in of FR4.**Note 12:** Channel tested with XAUI CJPAT as well as this pattern: 19 zeros, 1, 10 zeros, 1010101010 (D21.5 character), 1100000101 (K28.5+ character), 19 ones, 0, 10 ones, 0101010101 (D10.2 character), 0011111010 (K28.5- character).**Note 13:** Cables are unequalized, Amphenol Spectra-Strip 24AWG or equivalent equipped with Fujitsu "MicroGiga" connector or equivalent. Residual deterministic jitter is the difference between the source jitter at point A and the load jitter at point B in Figure 2. The deterministic jitter (DJ) at the output of the transmission line must be from media-induced loss and not from clock-source modulation. Depending upon the system environment, better results can be achieved by selecting different preemphasis levels.**Note 14:** Valid with pattern generator deterministic jitter as high as 0.17UIp-P.

# クワッド、銅ケーブルシグナルコンディショナ

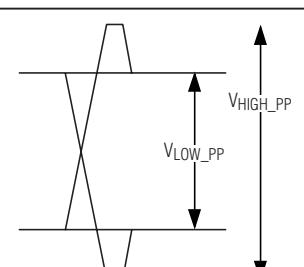

図1. TXプリエンファシス(dBによる表現)

図2. エンドツーエンドテスト用構成。A点とB点がACパラメータテスト条件の基準となります。

# クワッド、銅ケーブルシグナルコンディショナ

MAX3983

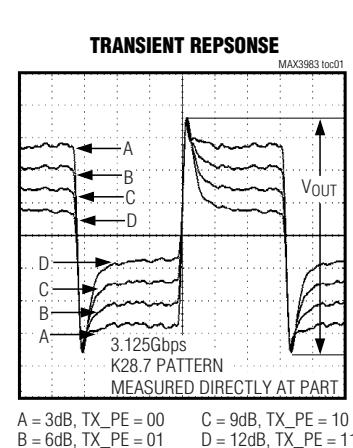

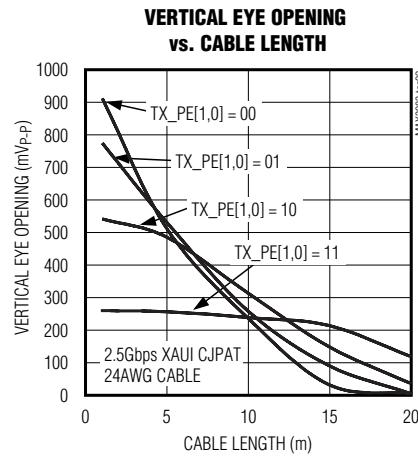

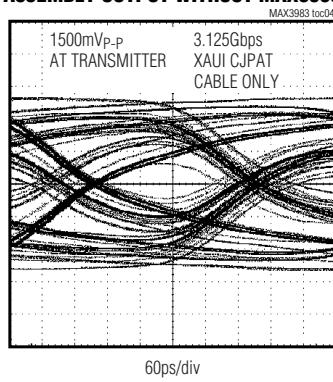

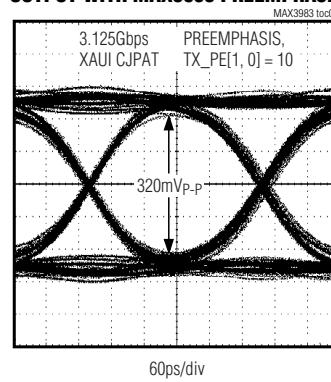

## 標準動作特性

( $V_{CC} = +3.3V$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

A = 3dB, TX\_PE = 00      C = 9dB, TX\_PE = 10

B = 6dB, TX\_PE = 01      D = 12dB, TX\_PE = 11

## 10m 24AWG UNEQUALIZED CABLE ASSEMBLY OUTPUT WITHOUT MAX3983

## 10m 24AWG UNEQUALIZED CABLE ASSEMBLY OUTPUT WITH MAX3983 PREEMPHASIS

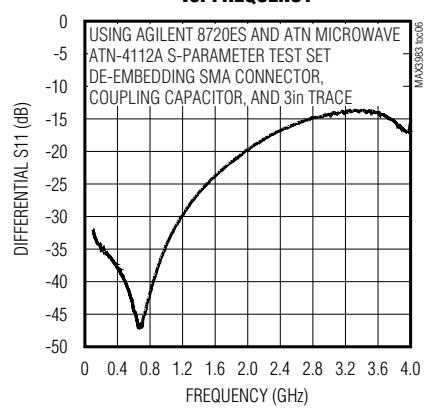

## TX\_IN INPUT RETURN LOSS vs. FREQUENCY

# クワッド、銅ケーブルシグナルコンディショナ

## 標準動作特性(続き)

( $V_{CC} = +3.3V$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

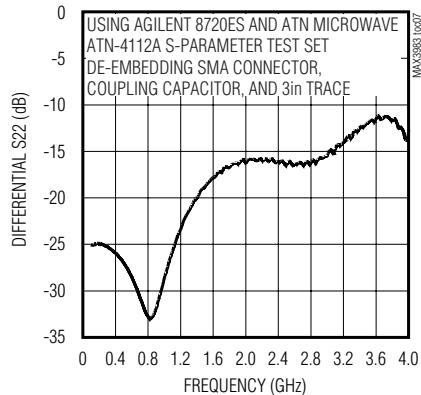

### TX\_OUT OUTPUT RETURN LOSS vs. FREQUENCY

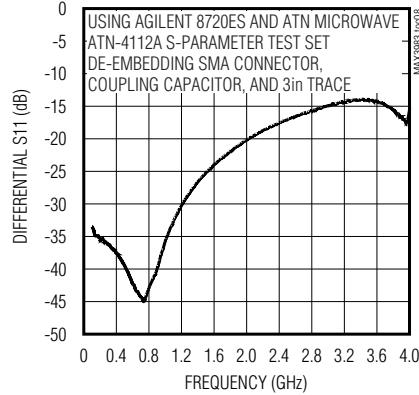

### RX\_IN INPUT RETURN LOSS vs. FREQUENCY

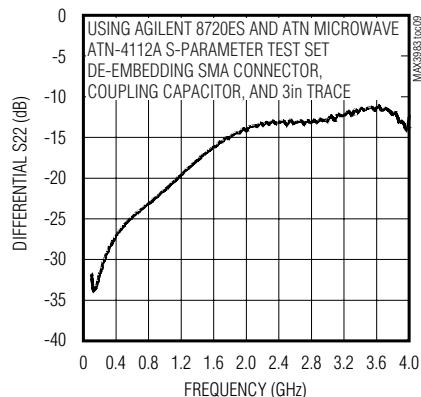

### RX\_OUT OUTPUT RETURN LOSS vs. FREQUENCY

### POWER-ON RESET DELAY WITH SUPPLY RAMP

# クワッド、銅ケーブルシグナルコンディショナ

MAX3983

## 端子説明

| 端子                   | 名称                   | 機能                                                                                                                                                                                      |

|----------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 16, 17         | TX_SD1 to TX_SD4     | プリント基板レシーバ、信号検出(TTL出力)。オープンコレクタTTL出力で、 $4.7\text{k}\Omega$ ~ $10\text{k}\Omega$ の外付プルアップ抵抗で $V_{CC}$ に接続する必要があります。入力信号が無効なレベルになると、これらの出力は電流をシンクします。                                     |

| 3, 15                | $V_{CC1}$            | TX入力用電源電圧。+3.3Vに接続します。                                                                                                                                                                  |

| 4, 7, 10, 13         | TX_IN1- to TX_IN4-   | プリント基板レシーバ、負データ入力(CML)。対応するTX_IN+に対し、 $100\Omega$ で内部差動終端されています。                                                                                                                        |

| 5, 8, 11, 14         | TX_IN1+ to TX_IN4+   | プリント基板レシーバ、正データ入力(CML)。対応するTX_IN-に対し、 $100\Omega$ で内部差動終端されています。                                                                                                                        |

| 6, 9, 12, 40, 43, 46 | GND                  | 回路グランド                                                                                                                                                                                  |

| 18                   | TX_ENABLE            | ケーブルトランスマッタ、イネーブル入力(LVTTL、 $40\text{k}\Omega$ 内部プルアップ)。この端子により、ケーブルトランスマッタ4本すべての出力、TX_OUT[1:4]をイネーブルにすることができます。ローにすると差動出力が $30\text{mV}_{\text{P-P}}$ 以下になります。通常動作ではハイまたはオープンにします。      |

| 19                   | N.C.                 | 接続なし。この端子はどこにも接続しないでください。                                                                                                                                                               |

| 20, 23, 26, 29, 32   | $V_{CC2}$            | TX出力用電源電圧。+3.3Vに接続します。                                                                                                                                                                  |

| 21, 24, 27, 30       | TX_OUT1+ to TX_OUT4+ | ケーブルトランスマッタ、正データ出力(CML)。 $50\Omega$ 抵抗で $V_{CC2}$ に終端されています。                                                                                                                            |

| 22, 25, 28, 31       | TX_OUT1- to TX_OUT4- | ケーブルトランスマッタ、負データ出力(CML)。 $50\Omega$ 抵抗で $V_{CC2}$ に終端されています。                                                                                                                            |

| 33                   | TX_PE0               | ケーブルトランスマッタ、プリエンファシスコントロール入力(LVTTL、 $40\text{k}\Omega$ 内部プルアップ)。この端子は、2ビットのプリエンファシスコントロールの最下位ビットです。ハイあるいはオープンにすると、このビットがアサートされます。                                                       |

| 34                   | TX_PE1               | ケーブルトランスマッタ、プリエンファシスコントロール入力(LVTTL、 $40\text{k}\Omega$ 内部プルアップ)。この端子は、2ビットのプリエンファシスコントロールの最上位ビットです。ハイあるいはオープンにすると、このビットがアサートされます。                                                       |

| 35, 36, 50, 51       | RX_SD4 to RX_SD1     | ケーブルレシーバ、信号検出(TTL出力)。オープンコレクタTTL出力で、 $4.7\text{k}\Omega$ ~ $10\text{k}\Omega$ の外付プルアップ抵抗で $V_{CC}$ に接続する必要があります。入力信号が無効なレベルになると、これらの出力は電流をシンクします。                                       |

| 37, 49               | $V_{CC3}$            | RX入力用電源電圧。+3.3Vに接続します。                                                                                                                                                                  |

| 38, 41, 44, 47       | RX_IN4- to RX_IN1-   | ケーブルレシーバ、負データ入力(CML)。対応するRX_IN+に対し、 $100\Omega$ で内部差動終端されています。                                                                                                                          |

| 39, 42, 45, 48       | RX_IN4+ to RX_IN1+   | ケーブルレシーバ、正データ入力(CML)。対応するRX_IN-に対し、 $100\Omega$ で内部差動終端されています。                                                                                                                          |

| 52                   | RX_ENABLE            | プリント基板トランスマッタ、イネーブル入力(LVTTL、 $40\text{k}\Omega$ 内部プルアップ)。この端子により、プリント基板トランスマッタ4本すべての出力、RX_OUT[1:4]をイネーブルにすることができます。ローにすると差動出力が $30\text{mV}_{\text{P-P}}$ 以下になります。通常動作ではハイあるいはオープンにします。 |

| 53                   | POR                  | パワーオンリセット。外付コンデンサ( $0.1\mu\text{F} \leq C_{POR} \leq 10\mu\text{F}$ )でグランドに接続します。 <a href="#">[詳細]</a> をご覧ください。                                                                         |

| 54, 57, 60, 63, 66   | $V_{CC4}$            | RX出力用電源電圧。+3.3Vに接続します。                                                                                                                                                                  |

# クワッド、銅ケーブルシグナルコンディショナ

## 端子説明(続き)

| 端子                | 名称                      | 機能                                                                                                                    |

|-------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------|

| 55, 58, 61,<br>64 | RX_OUT4+ to<br>RX_OUT1+ | プリント基板トランシッタ、正データ出力(CML)。50Ω抵抗でV <sub>CC</sub> 4に終端されています。                                                            |

| 56, 59, 62,<br>65 | RX_OUT4- to<br>RX_OUT1- | プリント基板トランシッタ、負データ出力(CML)。50Ω抵抗でV <sub>CC</sub> 4に終端されています。                                                            |

| 67                | RX_PE                   | プリント基板トランシッタ、プリエンファシスコントロール入力(LVTTL、40kΩ内部プルアップ)。ハイあるいはオープンにすると、このビットがアサートされます。                                       |

| 68                | LOOPBACK                | ループバックイネーブル入力(LVTTL、40kΩ内部プルアップ)。通常動作ではローにします。ハイあるいはオープンにすると、TX_INを内部でRX_OUTに接続します。ループバックをイネーブルにしても、TX_OUTからの送信は続きます。 |

| EP                | Exposed Pad             | エクスポートドパッド。信号と電源のグランド。高周波数特性と熱伝導特性を確保するため、このパッドは必ずプリント基板のグランドに半田付けします。                                                |

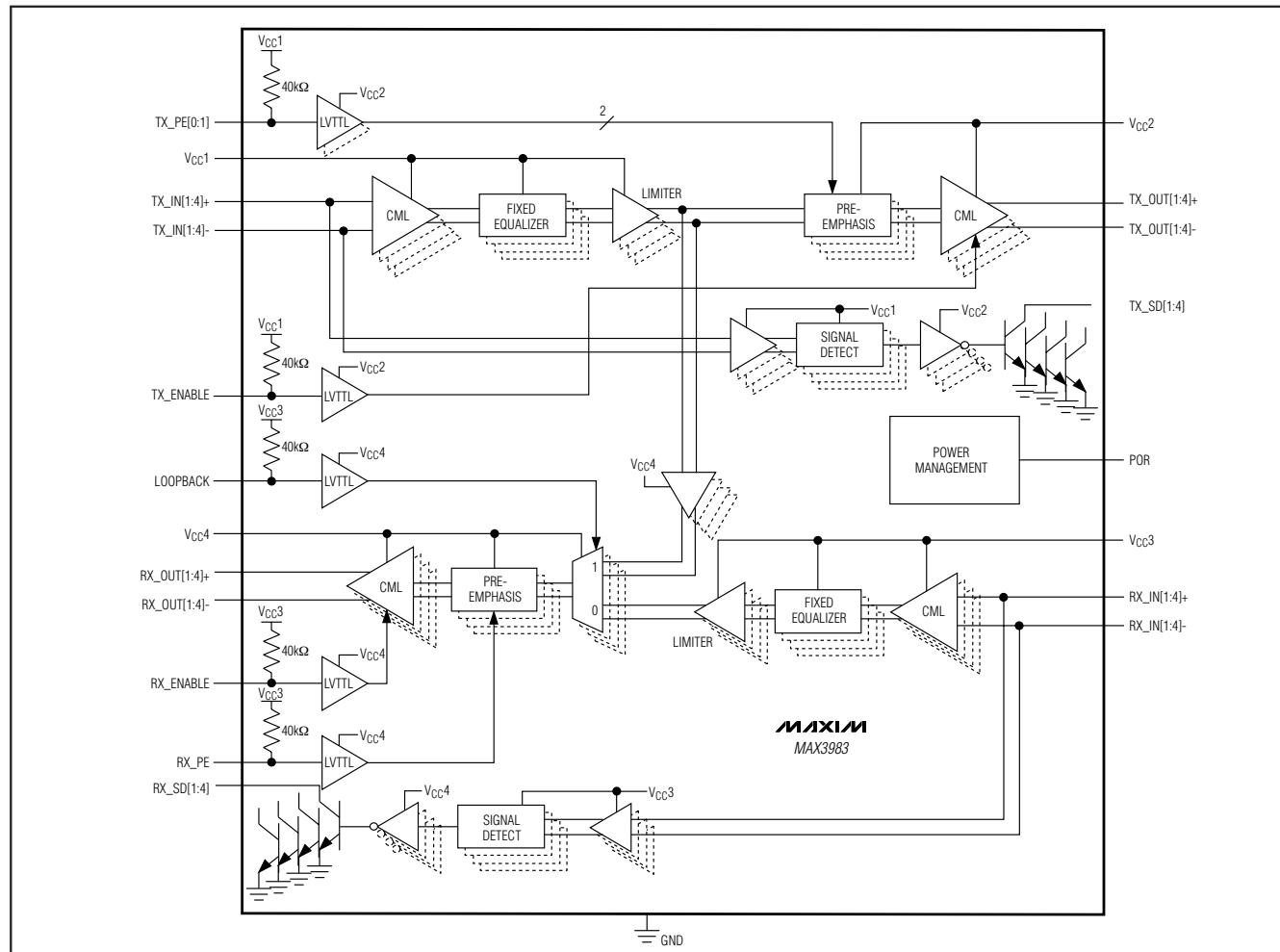

図3. ファンクションダイアグラム

## 詳細

MAX3983は、プリント基板レシーバとケーブルドライバ部(TX)及びケーブルレシーバとプリント基板ドライバ部(RX)という構成になっています。レシーバはそれぞれイコライゼーション機能と信号検出機能を、トランスマッタはそれぞれプリエンファシス機能を持ちます。MAX3983では、TX出力とRX出力を個別にイネーブルすることが可能です。診断テスト用のループバック機能もあります。

### プリント基板レシーバとケーブルドライバ (TX\_INとTX\_OUT)

ホストからMAX3983に供給されたデータは、CML入力段と固定イコライゼーション段を通過します。プリント基板レシーバの固定イコライザでは、FR4プリント基板での損失を最大20インチ(50cm)まで補償します。ケーブルドライバには4ステートプリエンファシス機能が組み込まれており、100Ω平衡ケーブル上の24AWGで最大20mまで補償します。プリエンファシスにはいろいろな表現方法があるため、換算用の表(表1)を用意しました。ソースジッタが0.17UI<sub>P-P</sub>以下であれば、MAX3983の残留ジッタは影響を受けません。

### ケーブルレシーバとプリント基板ドライバ (RX\_INとRX\_OUT)

各RX入力に組み込まれている固定イコライザにより、約6dBのイコライゼーションを行い、100Ω平衡ケーブル上の28AWGで最大5mまで補償します。プリント基板ドライバには2ステートプリエンファシス機能が組み込まれており、FR4プリント基板上で最大20インチ(50cm)まで補償します。

## 信号検出出力

8本のデータ入力すべてに対し、信号検出(SD)が用意されています。SD出力はプルアップ抵抗を介して3.0V～5.5Vの電源に接続します。信号検出出力が利用できるのは、パワーアップが終了してからです。信号検出応答時間は、通常、0.35μsです。

RX部は、RX\_IN信号の振幅が175mV<sub>P-P</sub>を超えると、SD出力がアサートされてハイになります。RX\_IN信号の振幅が85mV<sub>P-P</sub>を下回ると、RX\_SDがデアサートされてローになります。

TX部では、TX\_IN信号の振幅が800mV<sub>P-P</sub>を超えると、SD出力がアサートされてハイになります。TX\_IN信号の振幅が200mV<sub>P-P</sub>を下回ると、TX\_SDがデアサートされてローになります。

## TXとRXイネーブル

TX\_ENABLE端子によりTXを、RX\_ENABLE端子によりRXをイネーブルします。通常、イネーブル時間は15ns、ディセーブル時間は25nsです。イネーブル入力を信号検出出力に接続すれば、入力信号を自動検出することが可能です(「自動検出」セクションをご覧ください)。

## パワーオンリセット

突入電流をおさえるために、MAX3983はパワーオンリセット回路を内蔵しています。外付コンデンサ(0.1μF ≤ C<sub>POR</sub> ≤ 10μF)でPORとグランドを接続します。C<sub>POR</sub> = 1μFでパワーオン遅延が6ms(typ)となります。

表1. プリエンファシスの換算

| RATIO                              | α                                                               | 10Gbase-CX4                            | IN dB                                                                    |  |

|------------------------------------|-----------------------------------------------------------------|----------------------------------------|--------------------------------------------------------------------------|--|

| $\frac{V_{HIGH\_PP}}{V_{LOW\_PP}}$ | $\frac{V_{HIGH\_PP} - V_{LOW\_PP}}{V_{HIGH\_PP} + V_{LOW\_PP}}$ | $1 - \frac{V_{LOW\_PP}}{V_{HIGH\_PP}}$ | $20 \left[ \log \left( \frac{V_{HIGH\_PP}}{V_{LOW\_PP}} \right) \right]$ |  |

| 1.41                               | 0.17                                                            | 0.29                                   | 3                                                                        |  |

| 2.00                               | 0.33                                                            | 0.50                                   | 6                                                                        |  |

| 2.82                               | 0.48                                                            | 0.65                                   | 9                                                                        |  |

| 4.00                               | 0.60                                                            | 0.75                                   | 12                                                                       |  |

# クワッド、銅ケーブルシグナルコンディショナ

## アプリケーション情報

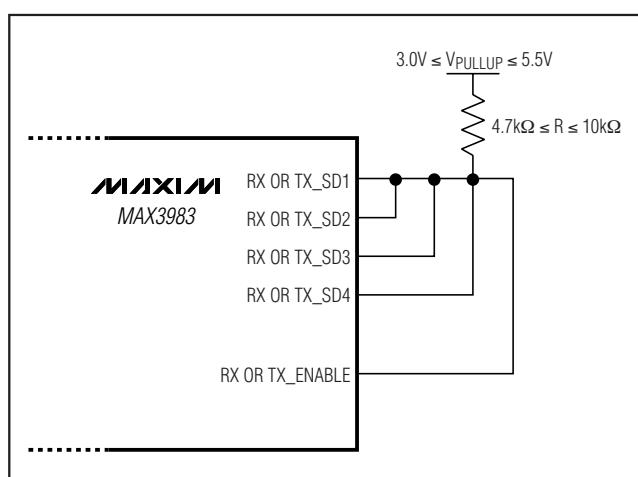

### 信号検出出力の漏れ電流に関する考察

RXあるいはTXの信号検出出力4本をまとめて1本の信号検出とする場合には、出力段の漏れ電流のことを考慮する必要があります。各SD出力は、アサート状態で最大 $25\mu\text{A}$ の電流をシンクするため、4本をまとめると最大 $100\mu\text{A}$ の電流がシンクされる可能性があります。この漏れ電流によって出力電圧が次段のスレッショルド以下に低下しないように、プルアップ電圧、 $V_{\text{PULLUP}}$ 、に接続するプルアップ抵抗の値を設定する必要があります。たとえば、信号検出出力をまとめ、 $1.5\text{V}$ というロジックハイスレッショルドを持つ段に接続する場合には、 $V_{\text{PULLUP}} - I_{\text{LEAKAGE}} \times R_{\text{PULLUP}} > 1.5\text{V}$ となるようにプルアップ抵抗を設定します。この場合では、 $V_{\text{PULLUP}} = 3.0\text{V}$ とすると、 $R_{\text{PULLUP}}$ は $15\text{k}\Omega$ 以下となります。

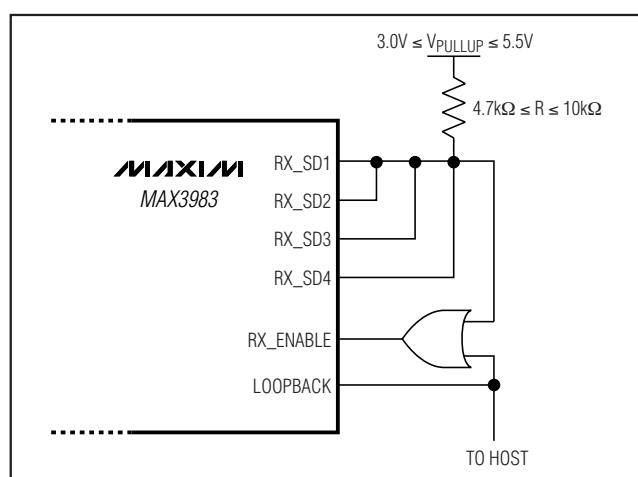

### 自動検出

MAX3983では、入力信号を自動的に検出し、適切な出力をイネーブルとすることが可能です。RX側で自動検出を行うには、RX\_SD[1:4]とプルアップ抵抗( $4.7\text{k}\Omega$ ～ $10\text{k}\Omega$ で $V_{\text{CC}}$ に接続)をRX\_ENABLEに接続します。TX側で自動検出を行うには、TX\_SD[1:4]とプルアップ抵抗( $4.7\text{k}\Omega$ ～ $10\text{k}\Omega$ で $V_{\text{CC}}$ に接続)をTX\_ENABLEに接続します(図4)。すべてのチャネルで信号が検出されると、SDがハイとなり、対応するイネーブル端子もハイとなります。なお、MAX3983に対する入力をオープンのまま(フローティング)にすべきではありません。ノイズ

が増幅され望ましくない出力信号が発生する可能性があるためです。ノイズ増幅や発振の危険性をなくすためには、自動検出を推奨します。自動検出では、リンク長を受信信号強度から求めます。そのため、自動検出としないほうが伝送距離は伸びる可能性があります。

### ループバックと自動検出の組み合わせ

MAX3983で自動検出を行う場合、RX\_ENABLEはRX\_SD[1:4]出力によって制御されます。ループバックではRX\_ENABLEをハイにしなければならないため、シンプルなORゲートによって、RX\_SD[1:4]がハイあるいはループバックがハイになればRX出力がイネーブルとなるようにすることができます(図5)。

### InfiniBandと10GBASE-CX4の遷移時間規定

InfiniBandでは最小遷移時間(20%～80%)が $100\text{ps}$ 、CX4では $60\text{ps}$ と規定されています。いずれもケーブルとのコネクタインターフェースで規定されています。MAX3983出力の遷移時間は $45\text{ps}(\text{typ})$ であるため、遷移時間を長くする工夫が必要です。4ミル( $0.1\text{mm}$ )線幅FR4基板の3インチ( $7.5\text{cm}$ )ほどで遷移時間を $60\text{ps}$ まで延ばすことができます。 $100\text{ps}$ まで延ばすには線路を長くするか、あるいはMAX3983出力端子間に $1.5\text{pF}$ のコンデンサを追加します。InfiniBandやCX4タイプのコネクタシステムでは、プリント基板に高速誘電体材料を使ってはいけません。高速誘電体材料を使うと、MAX3983の高速エッジによりInfiniBandやCX4のケーブルアッセンブリに過度のクロストークが発生してしまいます。

図4. 対応する信号検出出力とイネーブル入力の組み合わせによる自動検出

図5. 自動検出モード時のループバック

## クロストーク

InfiniBandや10GBASE-CX4アプリケーションでは、ケーブルアッセンブリ近端におけるクロストーク特性を知る必要があります。10GBASE-CX4では、アグレッサが1つの場合についても複数の場合についても、近端クロストーク(NEXT)に対して周波数上に上限を定めています。InfiniBandでは、トランスマッタ出力に関して時間領域での割合で規定されているだけです。どのような規定方法であっても、NEXTがリンク性能に重大な影響を与えることには変わりはありません。プリエンファシス量を増やすと受信アイパターンの高さが低くなり、NEXTの影響を受けやすくなってしまいます。大きな送信プリエンファシスが必要な状況では、1GHz～3GHzの周波数におけるNEXTを-30dB以下に抑える必要があります。10GBASE-CX4 NEXTとMDNEXTの基準を満たすケーブルであれば、十分な絶縁が得られます。

## レイアウト上の考慮

MAX3983の性能は、プリント基板のレイアウトと設計に大きく影響されます。グランドインダクタンスを抑え、データ信号の伝送線路のインピーダンスを適切に調整するなど、優れた高周波設計技法を用いてください。電源デカップリングは、 $V_{CC}$ 端子の直近に配置してください。電源に対するフィルタリングも十分にしてください。すべての $V_{CC}$ は、必ず、電源プレーンに接続してください。フィールドスルーを低減するために出力信号と入力を隔離してください。イコライザの特性は、損失が大きな環境に対して最適化されています。誘電正接損失が約0.02の基板と4ミル(0.1mm)幅の伝送線路を使用すると、高い性能を得ることができます。誘電正接損失が0.01以下の高速材料を使うことも可能ですが、その場合、ケーブルアッセンブリにおける近端クロストークを低減する工夫が必要になります。

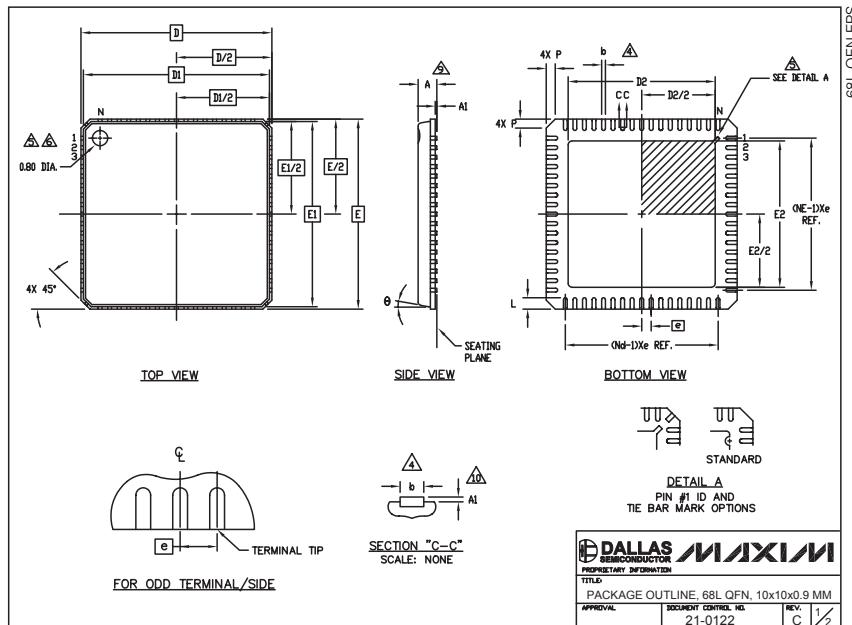

## エクスポーズドパッドパッケージ

エクspoーズドパッド68ピンQFNパッケージは、IC除熱バスの熱抵抗が非常に小さいという特長を持ちます。エクspoーズドパッドはMAX3983の電気的グランドでもあるため、適正な熱的及び電気的性能を得るためにプリント基板に半田付けします。エクspoーズドパッドパッケージについての詳細は、マキシムアプリケーションノート、"HFAN-08.1: Thermal Considerations of QFN and Other Exposed-Paddle Packages" (英語)をご覧ください。

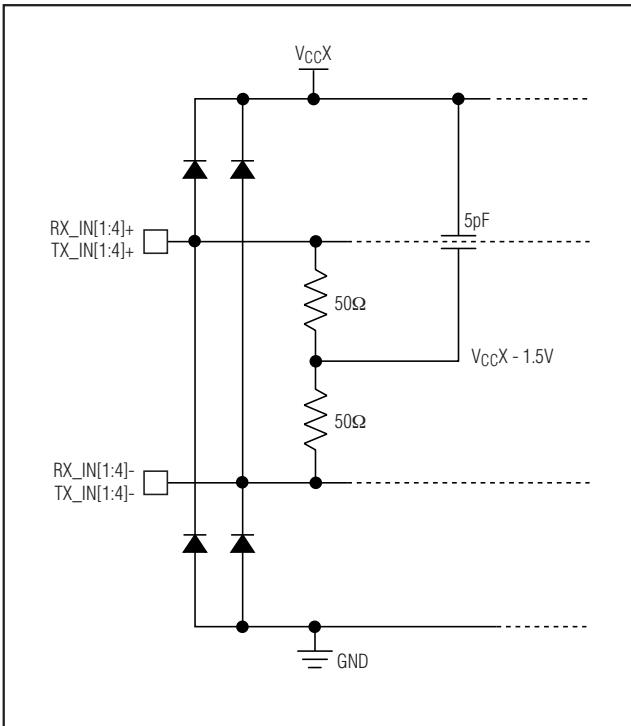

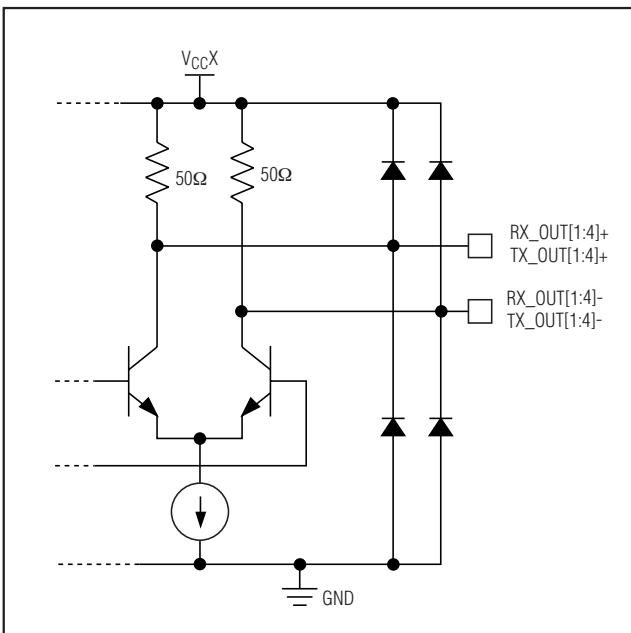

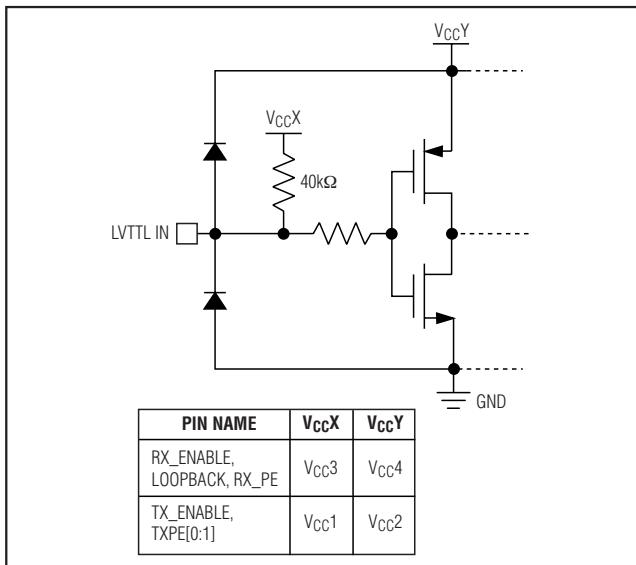

## インターフェース回路

図6. RX\_INとTX\_INの等価入力回路

図7. RX\_OUTとTX\_OUTの等価出力回路

## クワッド、銅ケーブルシグナルコンディショナ

図8. LVTTL等価入力回路

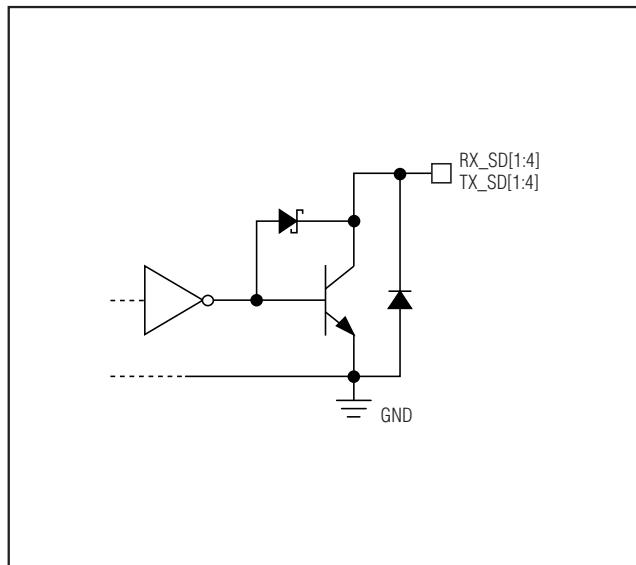

図9. 信号検出等価出力回路

# クワッド、銅ケーブルシグナルコンディショナ

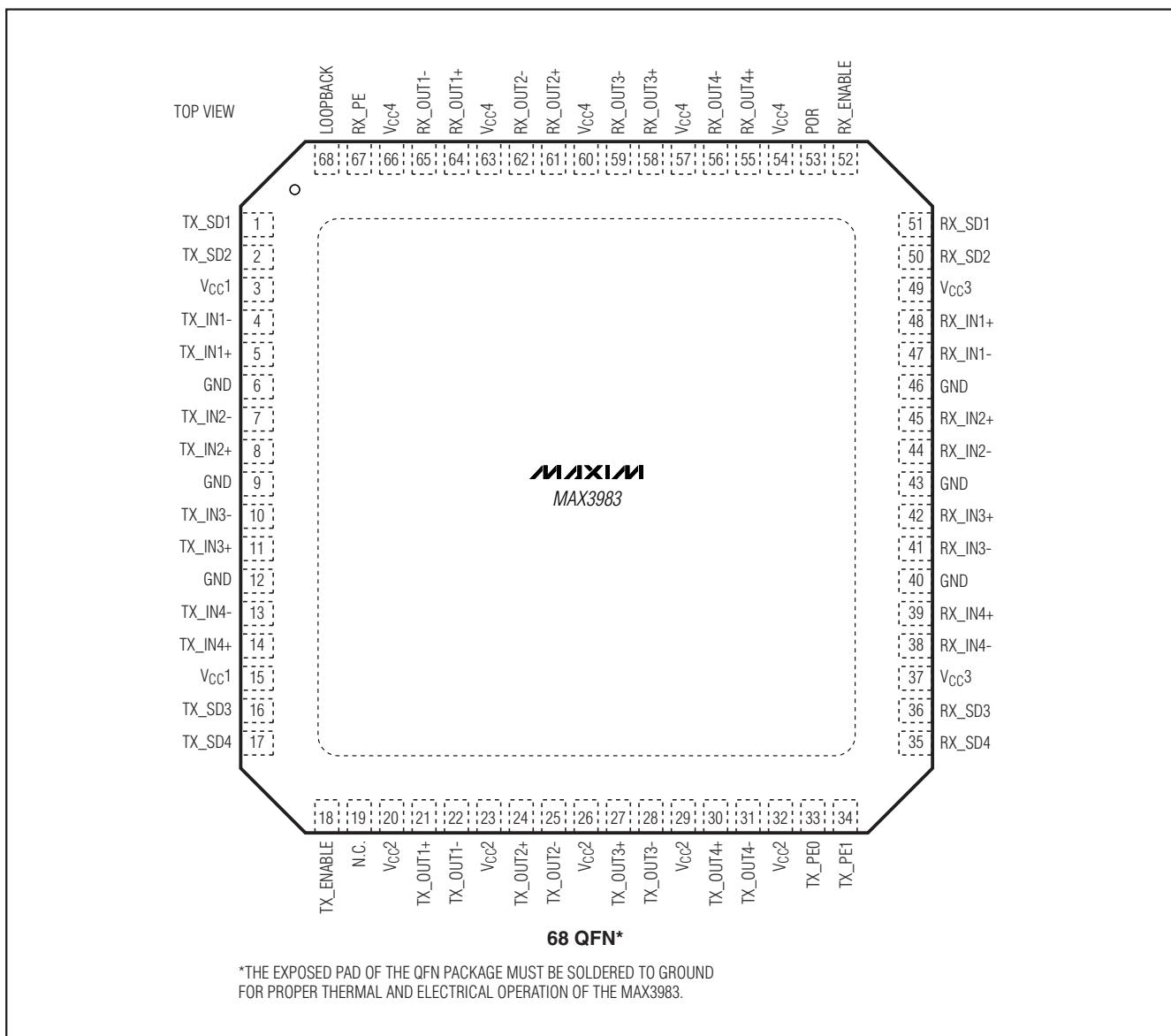

## ピン配置

MAX3983

## チップ情報

TRANSISTOR COUNT: 7493

PROCESS: SiGe Bipolar

# クワッド、銅ケーブルシグナルコンディショナ

## パッケージ

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、<http://japan.maxim-ic.com/packages>をご参照下さい。)

| COMMON DIMENSIONS |       |      |      | Ne |

|-------------------|-------|------|------|----|

|                   | MIN.  | NOM. | MAX. | Ne |

| A                 | —     | 0.90 | 1.00 |    |

| A1                | 0.00  | 0.01 | 0.05 | 11 |

| b                 | 0.18  | 0.23 | 0.30 | 4  |

| D                 | 10.00 | BSC  |      |    |

| D1                | 9.75  | BSC  |      |    |

| E                 | 0.50  | BSC  |      |    |

| E1                | 9.75  | BSC  |      |    |

| L                 | 0.50  | 0.60 | 0.65 |    |

| N                 | 68    |      |      | 3  |

| Nd                | 17    |      |      | 3  |

| Ne                | 17    |      |      | 3  |

| θ                 | 0     |      | 12°  |    |

| P                 | 0     | 0.42 | 0.60 |    |

1. DIE THICKNESS ALLOWABLE IS .012 INCHES MAXIMUM.

2. DIMENSIONING TOLERANCES CONFORM TO ASME Y14.5M. - 1994.

3. Nd IS THE NUMBER OF TERMINALS.

4. Ne IS THE NUMBER OF TERMINALS IN X-DIRECTION & Ne IS THE NUMBER OF TERMINALS IN Y-DIRECTION.

5. DIMENSION b APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.20 AND 0.25mm FROM TERMINAL TIP.

6. THE PIN #1 IDENTIFIER MUST BE LOCATED ON THE TOP SURFACE OF THE PACKAGE BY USING INDENTATION MARK OR OTHER FEATURE OF PACKAGE BODY. DETAILS OF PIN #1 IDENTIFIER IS OPTIONAL, BUT MUST BE LOCATED WITHIN ZONE INDICATED.

7. EXACT SHAPE AND SIZE OF THIS FEATURE IS OPTIONAL.

8. ALL DIMENSIONS ARE IN MILLIMETERS.

9. PACKAGE WARPAGE MAX 0.10mm.

10. APPLIES TO EXPOSED SURFACE OF PADS AND TERMINALS.

11. APPLIES ONLY TO TERMINALS.

12. MEETS JEDEC MD-220.

| EXPOSED PAD VARIATIONS |      |      |      |      |      |      |

|------------------------|------|------|------|------|------|------|

| PKG CODE               | D2   |      | E2   |      |      |      |

|                        | MIN  | NOM  | MAX  | MIN  | NOM  | MAX  |

| G6800-2                | 7.55 | 7.70 | 7.85 | 7.55 | 7.70 | 7.85 |

| G6800-4                | 5.65 | 5.80 | 5.95 | 5.65 | 5.80 | 5.95 |

| DALLAS SEMICONDUCTOR MAXIM PROPRIETARY INFORMATION |                      |      |     |

|----------------------------------------------------|----------------------|------|-----|

| TITLE: PACKAGE OUTLINE: 68L QFN, 10x10x0.9 MM      |                      |      |     |

| APPROVAL                                           | DOCUMENT CONTROL NO. | REV. | 1/2 |

| 21-0122                                            |                      | C    |     |

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。マキシムは隨時予告なく回路及び仕様を変更する権利を留保します。