### 概要

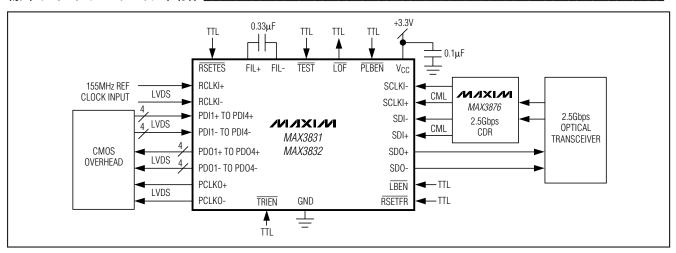

MAX3831/MAX3832は、自動チャネルアサインメント付 の4:1マルチプレクサ及び1:4デマルチプレクサです。 +3.3V単一電源で動作するマルチプレクサは4つの パラレル622Mbps SDH/SONETチャネルを受信します。 これらのチャネルはビットインタリーブされて、光又は 電気的ドライバにインタフェースするための2.488Gbps のシリアルデータストリームが生成されます。10ビット 幅のエラスティックバッファは、任意のパラレルデータ 入力とリファレンスクロックの間に±7.5nsまでの スキューを許容します。出力するデータストリームの タイミング用に内蔵PLLが高周波2.488GHzクロックを 合成するために、外部155MHzリファレンスクロック が必要です。

MAX3831/MAX3832のデマルチプレクサは、2.488Gbps のシリアルデータ及び2.488GHzのクロックを外部 クロック/データリカバリ素子(MAX3876)から受けて、 それを4つの622Mbps LVDS出力に変換します。 MAX3831は622MHz LVDSクロック出力を供給し、 MAX3832は155MHz LVDSクロックを供給します。内部 フレームディテクタが622Mbps SDH/SONETフレー ミングパターンを探し、デマルチプレクサをロールして 出力における適正なチャネル割当を維持します。

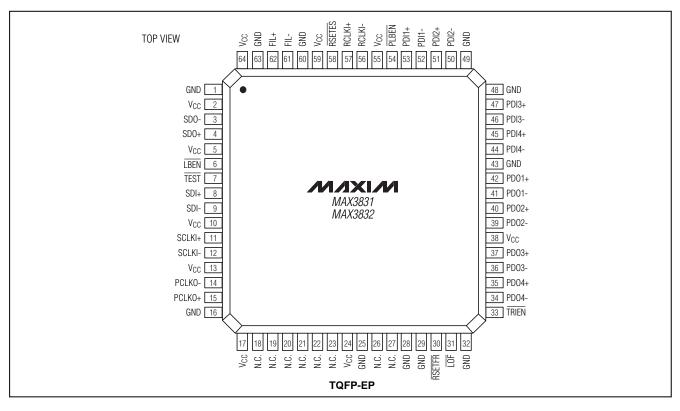

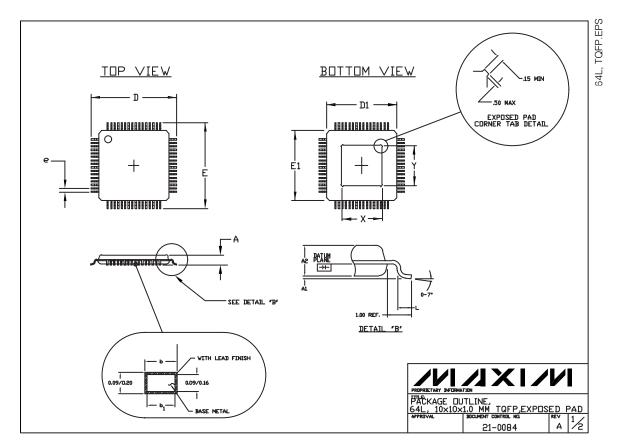

これらの素子は、フルスピード内蔵セルフテスト(BIST) を可能にする埋込型パターン発生器も備えています。2つ の異なるループバックモードがシステムテストの融通性 を提供します。TTLロスオブフレームモニタが含まれて います。MAX3831/MAX3832は64ピンTQFP-EP (露出パドル)パッケージで提供されており、温度範囲は 高温民生用(0 ~+85 )のものが用意されています。

ピン配置はデータシートの最後に記載されています。

### 特長

- ◆ 電源:+3.3V単一

- ◆ 電力消費: 1.45W

- ◆ 4チャネルマルチプレクサ/デマルチプレクサ、 完全集積化2.488GHzクロック発生器付

- ◆ フレーム検出でチャネル割当を維持

- ◆ エラスティックストア範囲:±7.5ns

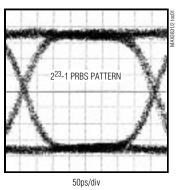

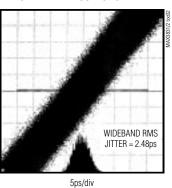

- ◆ RMSシリアルデータ出力ランダムジッタ:2.5ps

- ◆ シリアルデータ出力確定的ジッタ:8ps

- ◆ LVDSパラレル入力/出力: 622Mbps

- ◆ シリアルCML入力/出力: 2.488Gbps

- ◆ 内蔵パターン発生器が高速BISTを提供

- ◆ システムテストの融通性:システムループバック、 ラインループバック

- ◆ ロスオブフレームインジケータ

### アプリケーション

ATMスイッチング SDH/SONET バックプレーン ネットワーク 高速パラレルリンク ラインエクステンダ 高密度ディジタル イントララック/ サブラック相互接続 クロスコネクト

| PART       | TEMP. RANGE  | PIN-PACKAGE |

|------------|--------------|-------------|

| MAX3831UCB | 0°C to +85°C | 64 TQFP-EP  |

| MAX3832UCB | 0°C to +85°C | 64 TQFP-EP  |

### 標準アプリケーション回路

### **ABSOLUTE MAXIMUM RATINGS**

| $\begin{array}{llllllllllllllllllllllllllllllllllll$ | Continuous Power Dissipation (T <sub>A</sub> = +85°C) (Note 1) 64-Pin TQFP-EP (derate 40.0mW/°C above +85°C)2.6W Operating Temperature Range0°C to +85°C Storage Temperature Range60°C to +150°C Lead Temperature (soldering, 10sec)+300°C |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CML Output Currents                                  |                                                                                                                                                                                                                                            |

Note 1: Based on empirical data from the MAX3831/MAX3832 evaluation kit.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, \text{LVDS} \text{ differential load} = 100\Omega \pm 1\%, \text{CML load} = 50\Omega \pm 1\% \text{ to V}_{CC}, \text{ all TTL inputs are open, T}_{A} = 0^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at T}_{A} = +25^{\circ}\text{C} \text{ and V}_{CC} = +3.3 \text{V}.)$

| PARAMETER                                                                         | SYMBOL             | CONDITIONS                         |         | MIN                   | TYP       | MAX                   | UNITS |

|-----------------------------------------------------------------------------------|--------------------|------------------------------------|---------|-----------------------|-----------|-----------------------|-------|

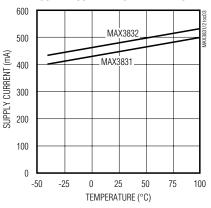

| Complet Comment                                                                   | 1                  | CML inputs and outputs open,       | MAX3831 |                       | 440       | 580                   | Л     |

| Supply Current                                                                    | Icc                | LVDS input Vos = 1.2V (Note 2)     | MAX3832 |                       | 480       | 614                   | mA    |

| LVDS INPUTS AND OUTPUTS                                                           | 1                  |                                    |         |                       |           |                       |       |

| Input Voltage Range                                                               | VIN                |                                    |         | 0                     |           | 2400                  | mV    |

| Differential Input Threshold                                                      | V <sub>IDTH</sub>  |                                    |         | -100                  |           | +100                  | mV    |

| Threshold Hysteresis                                                              | VHYST              |                                    |         |                       | 90        |                       | mV    |

| Input Impedance                                                                   | RIN                |                                    |         | 85                    | 100       | 115                   | Ω     |

| Input Common-Mode Current                                                         | los                | LVDS input, V <sub>OS</sub> = 1.2V |         |                       | 270       |                       | μΑ    |

| Output Voltage High                                                               | Vон                |                                    |         |                       |           | 1.475                 | V     |

| Output Voltage Low                                                                | V <sub>OL</sub>    |                                    |         | 0.925                 |           |                       | V     |

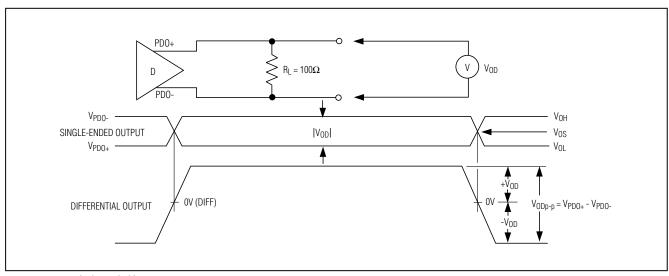

| Differential Output Voltage                                                       | IV <sub>OD</sub> I | Figure 1                           |         | 250                   |           | 400                   | mV    |

| Change in Magnitude of<br>Differential Output Voltage for<br>Complementary States | ΔIVODI             |                                    |         |                       |           | ±25                   | mV    |

| Output Offset Voltage                                                             | Vos                |                                    |         | 1.125                 |           | 1.275                 | V     |

| Change in Magnitude of Output<br>Offset Voltage for Complementary<br>States       | ΔIVOSI             |                                    |         |                       |           | ±25                   | mV    |

| D:(( ): 10 ) 11 1                                                                 |                    | TRIEN = GND                        |         |                       | >1        |                       | MΩ    |

| Differential Output Impedance                                                     |                    | TRIEN = V <sub>CC</sub>            |         | 80                    |           | 120                   | Ω     |

| Output Current                                                                    |                    | Short outputs together (Note 3)    |         |                       |           | 12                    | mA    |

| CML INPUTS AND OUTPUTS                                                            | I                  |                                    | L       |                       |           |                       |       |

| Differential Output Voltage                                                       | V <sub>ODp-p</sub> |                                    |         | 640                   | 800       | 1000                  | mVp-p |

| Differential Output Impedance                                                     |                    |                                    |         | 85                    | 100       | 115                   | Ω     |

| Output Common-Mode Voltage                                                        |                    |                                    |         |                       | Vcc - 0.2 |                       | V     |

| Single-Ended Input Voltage Range                                                  | Vis                |                                    |         | V <sub>CC</sub> - 0.6 |           | V <sub>CC</sub> + 0.4 | V     |

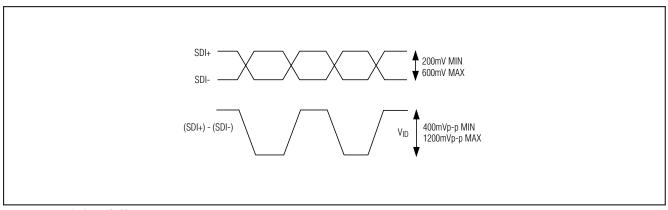

| Differential Input Voltage Swing                                                  |                    | Figure 2                           |         | 400                   |           | 1200                  | mVp-p |

| Differential Input Impedance                                                      |                    |                                    |         | 85                    | 100       | 115                   | Ω     |

### DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, \text{LVDS} \text{ differential load} = 100\Omega \pm 1\%, \text{CML load} = 50\Omega \pm 1\% \text{ to V}_{CC}, \text{ all TTL inputs are open, T}_{A} = 0^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at T}\_{A} = +25^{\circ}\text{C} \text{ and V}\_{CC} = +3.3 \text{V}.)

| PARAMETER              | SYMBOL          | CONDITIONS             | MIN  | TYP | MAX  | UNITS |

|------------------------|-----------------|------------------------|------|-----|------|-------|

| TTL INPUTS AND OUTPUTS |                 |                        |      |     |      |       |

| Input Voltage High     | VIH             |                        | 2.0  |     |      | V     |

| Input Voltage Low      | VIL             |                        |      |     | 0.8  | V     |

| Input Current High     | liH             | V <sub>IH</sub> = 2.0V | -250 |     | -50  | μΑ    |

| Input Current Low      | IIL             | V <sub>IL</sub> = 0    | -550 |     | -100 | μΑ    |

| Output Voltage High    | VoH             | I <sub>OH</sub> = 20μA | 2.4  |     |      | V     |

| Output Voltage Low     | V <sub>OL</sub> | I <sub>OL</sub> = 2mA  |      |     | 0.4  | V     |

| Output Impedance       |                 | TRIEN = GND            |      | 6   |      | kΩ    |

**Note 2:** When  $\overline{\text{TEST}} = \text{GND}$ , the pattern generator will consume an additional 30mA.

Note 3: Guaranteed by design and characterization.

### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, \text{LVDS} \text{ differential load} = 100 \Omega \pm 1\%, \text{CML load} = 50 \Omega \pm 1\% \text{ to } V_{CC}, \text{ all TTL inputs are open, } T_A = 0^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}\text{C}$  and  $V_{CC} = +3.3 \text{V}.)$  (Note 4)

| PARAMETER                                  | SYMBOL                          | CONDITIONS            | MIN  | TYP     | MAX | UNITS             |

|--------------------------------------------|---------------------------------|-----------------------|------|---------|-----|-------------------|

| 4:1 MULTIPLEXER WITH CLOCK                 | GENERAT                         | OR                    | '    |         |     |                   |

| Parallel Input Data Rate                   |                                 |                       |      | 622.08  |     | Mbps              |

| Maximum Parallel Input Skew                | tes                             | (Note 5)              |      | ±7.5    |     | ns                |

| Serial-Data Output Rate                    |                                 |                       |      | 2.48832 |     | Gbps              |

| Serial-Data Output Rise/Fall Time          | t <sub>r</sub> , t <sub>f</sub> | 20% to 80%            |      |         | 120 | ps                |

| Carial Data Output Dandam littar           | SRJ                             | (Note 6)              |      |         | 3.5 | psrms             |

| Serial-Data Output Random Jitter           | SNJ                             | (Note 6)              |      |         | 40  | psp-p             |

| Serial-Data Output Deterministic<br>Jitter | SDJ                             | (Note 7)              |      | 8       | 18  | ps <sub>p-p</sub> |

| 1:4 DEMULTIPLEXER                          | 1                               |                       | <br> |         |     | I.                |

| Serial-Data Input Rate                     |                                 |                       |      | 2.48832 |     | Gbps              |

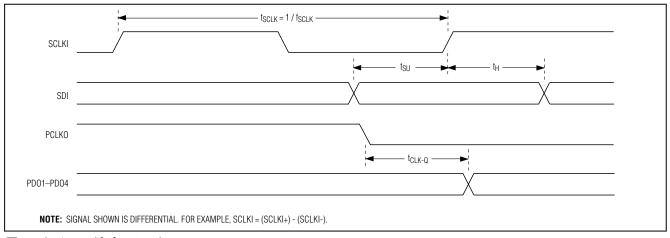

| Serial-Data Setup Time                     | tsu                             | Figure 3              | 100  |         |     | ps                |

| Serial-Data Hold Time                      | tH                              | Figure 3              | 100  |         |     | ps                |

| Parallel-Data Output Rate                  | PDO±                            |                       |      | 622.08  |     | Mbps              |

| Parallal Clask Output Fraguenay            | PCLKO±                          | MAX3831               |      | 622.08  |     | MHz               |

| Parallel-Clock Output Frequency            |                                 | MAX3832               |      | 155.52  |     |                   |

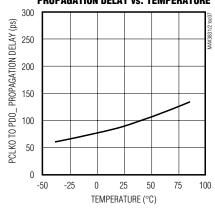

| PCLKO to PDO_ Delay                        | tclk-Q                          | MAX3831, Figure 3     | -100 | 90      | 300 | ps                |

| LVDS Output Rise/Fall Time                 |                                 | 20% to 80%            |      |         | 350 | ps                |

| LVDS Differential Skew                     | tskew1                          | Any differential pair |      |         | 65  | ps                |

| LVDS Channel-to-Channel Skew               | tskew2                          | PDO1± to PDO4±        |      | <100    |     | ps                |

| LVDS Three-State Enable Time               |                                 |                       |      | 30      |     | ns                |

**Note 4:** AC characteristics are guaranteed by design and characterization.

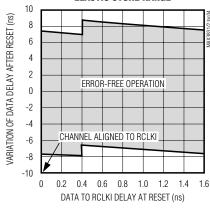

Note 5: Relative to the positive edge of the 155MHz reference clock. PDI1 to PDI4 aligned to RCLKI at reset.

Note 6: Measured with a reference clock jitter of <1ps<sub>RMS</sub>.

Note 7: Deterministic jitter is the arithmetic sum of pattern-dependent jitter and pulse-width distortion.

図1. LVDS出力の定義

図2. CML入力の定義

図3. タイミングパラメータ

標準動作特性

$(V_{CC} = +3.3V, T_A = +25^{\circ}C, unless otherwise noted.)$

### SERIAL-DATA OUTPUT EYE DIAGRAM

### **SERIAL-DATA OUTPUT JITTER**

### SUPPLY CURRENT vs. TEMPERATURE

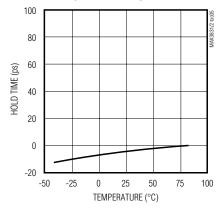

### SERIAL-DATA HOLD TIME

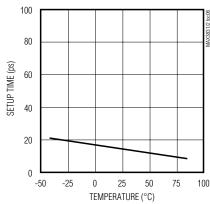

### **SERIAL-DATA SETUP TIME**

# MAX3831 PARALLEL CLOCK-TO-DATA OUTPUT PROPAGATION DELAY vs. TEMPERATURE

### 端子説明 \_\_\_\_\_\_

| 端子                                              | 名称             | 機能                                                                                                                                                                                                                                        |  |  |  |

|-------------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1, 16, 25, 28,<br>29, 32, 43, 48,<br>49, 60, 63 | GND            | 電源グランド                                                                                                                                                                                                                                    |  |  |  |

| 2, 5, 10, 13,<br>17, 24, 38, 55,<br>59, 64      | Vcc            | +3.3V電源電圧                                                                                                                                                                                                                                 |  |  |  |

| 3                                               | SDO-           | 負CMLシリアルデータ出力(2.488Gbps)                                                                                                                                                                                                                  |  |  |  |

| 4                                               | SDO+           | 正CMLシリアルデータ出力(2.488Gbps)                                                                                                                                                                                                                  |  |  |  |

| 6                                               | LBEN           | ラインループバックイネーブル。このTTL入力を強制的にローにすると、CMLシリアルデータ入力 $(SDl_{\pm})$ が直接CMLシリアルデータ出力 $(SDO_{\pm})$ に送られます。その他の入力又は出力は影響されません。 通常動作では内部15k プルアップ抵抗が LBENをハイに引き上げます。「テストループバック」を参照。                                                                 |  |  |  |

| 7                                               | TEST           | セルフテストイネーブル。このTTL入力を強制的にローにすると、内蔵パターン発生器が標準OC-12 SONETライクなフレーム(12個のA1、12個のA2及び9696バイトの2 <sup>7</sup> -1疑似ランダムビット)を生成します。これはまた、内部シリアルシステムループバック経路をイネーブルします。このモードでは、CML入力(SDI±及びSCLK±)及びLVDS入力は無視されます。通常動作では、内部15k プルアップ抵抗が TESTをハイに引き上げます。 |  |  |  |

| 8                                               | SDI+           | 正CMLシリアルデータ入力(2.488Gbps)                                                                                                                                                                                                                  |  |  |  |

| 9                                               | SDI-           | 負CMLシリアルデータ入力(2.488Gbps)                                                                                                                                                                                                                  |  |  |  |

| 11                                              | SCLKI+         | 正CMLシリアルクロック入力(2.488GHz)                                                                                                                                                                                                                  |  |  |  |

| 12                                              | SCLKI-         | 負CMLシリアルクロック入力(2.488GHz)                                                                                                                                                                                                                  |  |  |  |

| 14                                              | PCLKO-         | 負LVDSパラレルクロック出力、622.08MHz(MAX3831); 155.52MHz(MAX3832)                                                                                                                                                                                    |  |  |  |

| 15                                              | PCLKO+         | 正LVDSパラレルクロック出力、622.08MHz(MAX3831); 155.52MHz(MAX3832)                                                                                                                                                                                    |  |  |  |

| 18-23, 26, 27                                   | N.C.           | 接続なし                                                                                                                                                                                                                                      |  |  |  |

| 30                                              | RSETFR         | フレームリセット。このTTL入力を強制的にローにすると、フレームディテクタと<br>パターン発生器がリセットされます。LOF出力もローになります。通常動作では、<br>内部15k プルアップ抵抗がRSETFRをハイに引き上げます。                                                                                                                       |  |  |  |

| 31                                              | LOF            | TTLロスオブフレーム出力。ロスオブフレーム条件においてローになります。                                                                                                                                                                                                      |  |  |  |

| 33                                              | TRIEN          | 3ステートイネーブル。このTTL入力を強制的にローにすると、全てのTTL及びLVDS出力がハイイン<br>ピーダンス状態になります。通常動作では、内部15k プルアップ抵抗がTRIENをハイに引き上げます。                                                                                                                                   |  |  |  |

| 34, 36, 39, 41                                  | PDO4- to PDO1- | 負LVDSパラレルデータ出力(622Mbps)                                                                                                                                                                                                                   |  |  |  |

| 35, 37, 40, 42                                  | PDO4+ to PDO1+ | 正LVDSパラレルデータ出力(622Mbps)                                                                                                                                                                                                                   |  |  |  |

| 44, 46, 50, 52                                  | PDI4- to PDI1- | 負LVDSパラレルデータ入力(622Mbps)                                                                                                                                                                                                                   |  |  |  |

| 45, 47, 51, 53                                  | PDI4+ to PDI1+ | 正LVDSパラレルデータ入力(622Mbps)                                                                                                                                                                                                                   |  |  |  |

| 54                                              | PLBEN          | パラレルシステムループバックイネーブル。このTTL入力を強制的にローにすると、LVDS<br>パラレル入力はエラスティックストアを通り、LVDSパラレル出力に送られます。これは、<br>高速マルチプレクサ及びデマルチプレクサをバイパスします。通常動作では、内部15k<br>プルアップ抵抗が PLBEN をハイに引き上げます。                                                                       |  |  |  |

| 56                                              | RCLKI-         | 負LVDSリファレンスクロック入力(155.52MHz)                                                                                                                                                                                                              |  |  |  |

| 57                                              | RCLKI+         | 正LVDSリファレンスクロック入力(155.52MHz)                                                                                                                                                                                                              |  |  |  |

### 端子説明(続き)\_

| 端子 | 名称             | 機能                                                                                                                                                              |

|----|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 58 | RSETES         | エラスティックストアリセット。エラスティックバッファはRESETSの立上がりエッジを中心にしています。これによってエラスティックストア範囲が最大限になります。少なくとも10nsのパルスを入力する10μs前にデータが存在していることが必要です。通常動作では、内部15k プルアップ抵抗がRESETSをハイに引き上げます。 |

| 61 | FIL-           | 負PLLフィルタコンデンサ入力。FIL+とFIL-の間に0.33µFコンデンサを接続して下さい。                                                                                                                |

| 62 | FIL+           | 正PLLフィルタコンデンサ入力。FIL+とFIL-の間に0.33µFコンデンサを接続して下さい。                                                                                                                |

| EP | Exposed Paddle | グランド。適正な熱的性能を実現するには、これを回路基板にハンダ付けする必要があります(「パッケージ」を参照)。                                                                                                         |

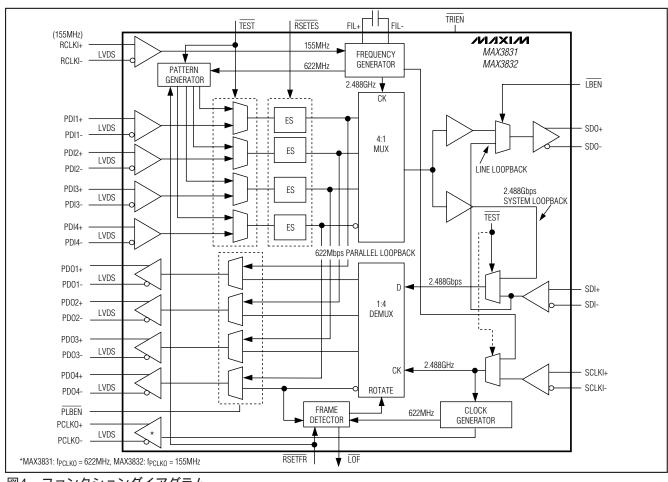

### 詳細

MAX3831/MAX3832は、エラスティックストアバッファ付の4:1マルチプレクサ及び1:4デマルチプレクサを使用することによりSDH/SONET相互接続I/Oルーティングを簡単にします。622Mbps LVDSパラレル入力は10ビットエラスティックストアバッファを通ります。このバッファは、任意のシングル入力について、155MHzのリファレンスクロック入力RCLKIに対して±7.5nsのスキューを吸収します。このリファレンスクロックは、エラスティックストア及び4:1マルチプレクサを駆動するために使用される内部2.488GHzクロックを合成するために必要です。全てのTTL及びLVDS出力はハイインピーダンス状態にすることができます。図4にファンクションダイアグラムを示します。

4:1マルチプレクサはパラレルデータをビットインターリーブして、2.488Gbps CMLシリアル出力を光又は電気的ドライバに供給します。CMLシリアル入力は2.488Gbpsデータを受け取り、デマルチプレクサがそれを622Mbpsにデインターリーブして、そのデータをフレームディテクタに送ります。フレームディテクタはチャネル割当が適正になるようにデマルチプレクサをロールします。MAX3831/MAX3832は高速内蔵セルフテスト(BIST)を備えています。この機能は又622Mbpsパラレルシステムループバック及び2.488Gbpsラインループバックのテストを可能にします。

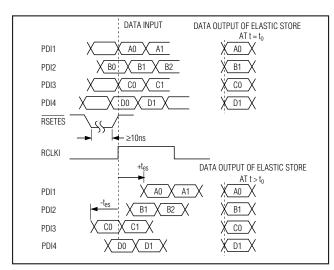

### エラスティックストアバッファ

各パラレルデータ入力(PDI1~PDI4)は、各々の10ビットエラスティックストアバッファを通ります。エラスティックストアリセットの後、このバッファは任意の入力について、155MHzリファレンスクロックに対して±7.5nsのスキューを吸収します。図5に、エラスティックストアバッファのRCLKIとの関係を示します。「標準動作特性」のエラスティックストア範囲のグラフに、許容されるデータスキューの量が示されています。

10μsのパワーアップ期間の後、個々のデータチャネルビット遷移の位置が取り込まれて、データの保全を保証します。このブロックの出力が直接4:1マルチプレクサ

に送られます。パワーアップの後、少なくとも10nsのローパルスを $\overline{RSETES}$ に入力し、エラスティックストアバッファをリセットする必要があります。

パラレルデータ入力同士のデータ遷移に固有の不確定性のため、これらの入力の間にはビット又はフレームアラインメントがありません。しかし、デマルチプレクサは正しいチャネル割当が維持されることを保証します。

### ビットインターリーブマルチプレクサ/ デマルチプレクサ

MAX3831/MAX3832は、ビット・インタリーブ/デインタリーブマルチプレクサ/デマルチプレクサを使用しています。チャネル割当を保証するため、4つのチャネルのうち1つは多重化の前に反転され、これによりデマルチプレックス中のフレームディテクタのリファレンスを提供します。デマルチプレクスの後、同じチャネルが反転されて元のデータフォーマットに戻されます。

### フレームディテクタ

2.5Gbpsシリアルデータが4つの622Mbpsチャネルにビットデインターリープされた後、SDH/SONETフレームディテクタが第4のチャネルを監視して、OC-12へッダ内の32ビットパターン(A1A1A2A2)を探します。適正なチャネル割当を維持するために、32ビットオーバーへッドパターンが確実に検出されるまでデマルチプレクサ出力は循環します。ロスオブフレーム出力( $\overline{\text{LOF}}$ )は、受信されたデータがフレームに収まっているかどうかを表示します。 $\overline{\text{LOF}}$ がハイになると、フレームパターンが検出されてデマルチプレクサ出力が正しく割り当てられます。 $\overline{\text{LOF}}$ がローの時、フレーム検出回路は正しいフレームを探しています。必要に応じてフレームディテクタをリセットできるように、 $\overline{\text{RSETFR}}$ (TTL、アクティブロー)があります。

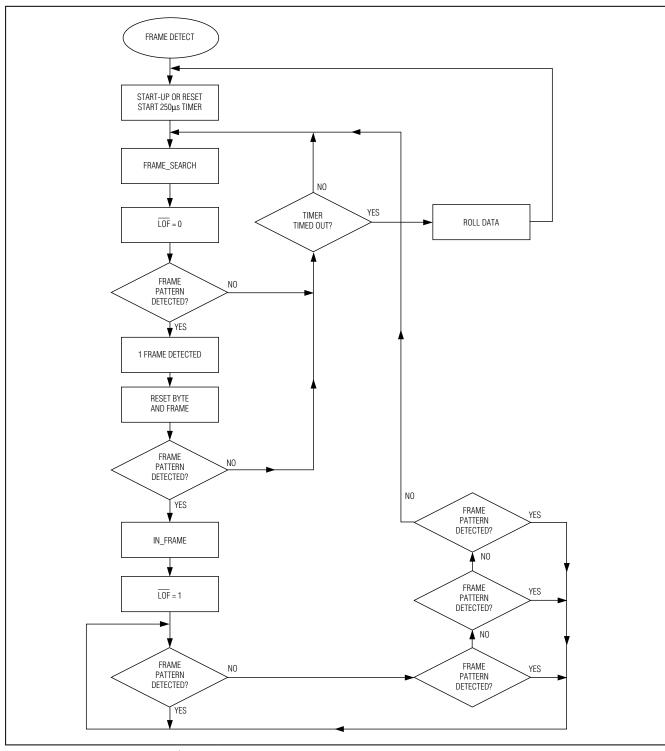

フレームディテクタは、インフレーム条件及びロスオブフレーム条件を検出するためにアルゴリズムを使用しています。このアルゴリズムは、SONETのインフレーム及び不正フレーム仕様に適合するようにできています。

図4. ファンクションダイアグラム

図5. エラスティックストア機能の例

スタートアップ又はリセット時にframe\_search状態が 発生します。この状態では、フレームディテクタが着信 シリアルデータをスキャンして、デマルチプレクサの チャネル4出力でフレーミングパターンを探します。 この状態でフレーミングパターンが250us以内に見つ からないと、デマルチプレクサチャネルがシフト(ロール) され、フレーム検出を継続します(図6)。

SONETフレーム(9720バイト)内の正しいバイト位置で 2つの連続したフレーミングパターンが見つかると、 インフレームが宣言されます。このパターンが正しい位置 になければ(不正フレーム)、ステートマシンは上述の frame\_search状態に戻ります。in\_frame状態においては、 各フレームで正しい位置にフレーミングパターンが あるかどうかチェックされます。不正フレームが4つ 連続すると、ステートマシンは上述のframe\_search状態 に戻ります。連続する疑似フレームが3つ以下の場合は、 不正フレームカウンタがリセットされます。

オンチップシリアルループバック付の 内蔵セルフテスト

オンチップパターン発生器をイネーブルして、 622Mbps SDH/SONETライクなトランスポート

図6. フレーム検出のフローダイアグラム

オーバーヘッドとそれに続く疑似ランダムビットシー ケンスを生成できます。これは12個のA1、12個のA2 及び疑似ランダムビットストリーム(PRBS =  $2^7$ -1)から なっています。TESTがローの時、このパターンは全ての パラレル入力に分配され、LVDS入力バッファをバイパス します。このパターンは各チャネルの間で622MHz クロックサイクル1つ分だけスキューされることに注意 して下さい。このテストモードにおいては、シリアル データは内部でデマルチプレクサにループバックされ ます。全てのフレーム検出口ジックはこのモードで 行われます。CML入力(SDI±及びSCLK±)及びLVDS入力 (PDI\_±)はこのモードでは無視されます。BISTモードが イネーブルされた後、ロスオブフレームフラグLOFが ハイになり、セルフテストに合格したことを知らせます。 通常動作においては、TESTはオープンのまま(内部でハイ にプルアップ)となり、パターン発生器がディセーブル され、パラレル入力チャネルからデータを受け付けます。

### テストループバック

パラレルシステムループバック及びシリアルライン ループバックの2つのテストループバックが提供されて います。

### パラレルシステムループバック

パラレルシステムループバックの場合、4つの622Mbps パラレル入力チャネルは対応する10ビットエラスティックストアによって位相アラインメントされ、出力 LVDSバッファに送られます。このループバックは、PLBENをローにすることによって制御されます。PLBENがハイ(内部でハイにプルアップ)になると、通常のデータ伝送が再開します。

### シリアルラインループバック

シリアルラインループバックは、光トランシーバ及び 伝送リンクの性能をテストするために使用されます。 受信された2.488Gbpsデータストリームは、送信CML 出力バッファに送られます。ラインループバックは、 IBEN出力がローになるとイネーブルされます。IBEN がオープンのままにされると(内部でプルアップ)、通常 シリアルデータ伝送が再開します。

### LVDSパラレルインタフェース

MAX3831パラレルインタフェースは、4つのOC-12 データ入力、155MHzリファレンスクロック入力、4つの622Mbpsパラレルデータ出力及び622MHzパラレルクロック出力(MAX3832、f<sub>PCLKO</sub>=155MHz)を含んでいます。電力消費を最小限に抑え、遷移時間を短くし、ノイズ耐性を改善するため、全てのパラレル入出力は

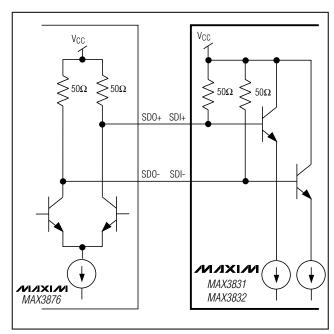

図7. CMLからCMLへのインタフェース

LVDSコンパチブルになっています。RCLKIにおける 155 MHz入力信号は、 $40\% \sim 60\%$ のデューティサイクルを必要とします。

TRIENが強制的にローになると、LVDS出力はハイインピーダンスになります。これによってLVDS出力にベクターを強制することができるようになり、システムチェックが簡単になります。

### CMLシリアルインタフェース

MAX3831/MAX3832は2.488Gbpsのシリアルデータストリームをドライバに供給し、外部クロックとデータリカバリ素子(MAX3876)から2.488Gbpsシリアルデータ及び2.488GHzクロック信号を受け取ります。高速インタフェースはCMLコンパチブルであるため、システム消費電力が低減され、優れた性能が得られます(図7)。

### アプリケーション情報

### 低電圧差動信号入力/出力

MAX3831/MAX3832は、高速ディジタル回路とのインタフェース用にLVDS入出力を備えています。全てのLVDS入力及び出力は、IEEE 1596.3 LVDS仕様とコンパチブルです。この技術では、250mV~400mVの差動低電圧スイングを使用して、高速遷移、低消費電力、及びノイズ耐性を実現しています。

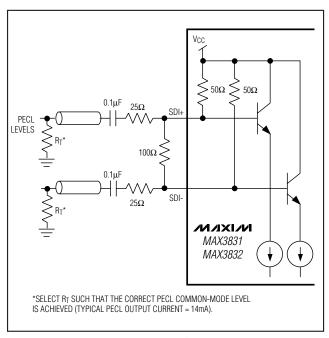

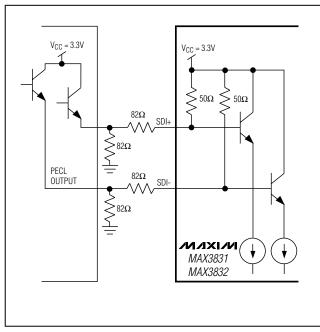

図8. PECLからCMLへのインタフェース

パラレルクロック及びデータLVDS出力(PCLKO+、PCLKO-、PDO\_+、PDO\_-)が適正に動作するには、反転出力と非反転出力の間において100 の差動DC終端処理を必要とします。これらの出力は、グランドに対して終端処理しないで下さい。パラレルデータLVDS入力(PDI\_+、PDI\_-)は、100 の内部差動入力抵抗で終端処理されているため、外部で終端処理する必要はありません。

### PECL/ECL入力レベルとのインタフェース

差動PECL入力レベルとインタフェースする場合は、50 終端処理を維持しつつ信号を減衰させることが重要です (図8及び9)。同相入力電圧仕様を守って下さい。3.3V 以外のV<sub>CC</sub>を使用する場合は、入力同相レベルを維持 するためにACカップリングが必要です(図8)。

### レイアウト技法

最高の性能を得るには、良好の高周波レイアウト技法を使用して下さい。電圧電源をフィルタリングし、グランド接続を短くし、可能なところでは複数のビアを使用して下さい。MAX3831/MAX3832の高速入力及び出力とインタフェースする時は、インピーダンスが調整された伝送ラインを使用して下さい。

電源デカップリングは、V<sub>CC</sub>のできるだけ近くに配置して下さい。フィードスルーを小さくするため、入力信号が出力信号から分離されるようにして下さい。

図9. PECL出力をMAX3831/MAX3832に 直接カップリング

ピン配置 \_\_\_\_\_\_

チップ情報 \_\_\_\_\_\_

TRANSISTOR COUNT: 14,134

パッケージ \_\_\_\_\_

パッケージ(続き)\_

### NOTES:

- 1. ALL DIMENSIONING AND TOLERANCING CONFORM TO ANSI Y14.5-1982.

2. DATUM PLANE \_-H-\_ IS LOCATED AT MOLD PARTING LINE AND COINCIDENT WITH LEAD, WHERE LEAD EXITS PLASTIC BODY AT BOTTOM OF PARTING LINE.

- WITH LEAD, WHERE LEAD EXITS PLASTIC BODY AT BOTTOM OF PARTINO

3, DIMENSIONS DI AND EL DO NOT INCLUDE MOLD PROTRUSION.

ALLOWABLE MOLD PROTRUSION IS 0.254 MM ON DI AND EL DIMENSIONS.

4. THE TOP OF PACKAGE IS SMALLER THAN THE BOTTOM

OF PACKAGE BY 0.15 MILLINETERS.

5. DIMENSION & DIES NOT INCLUDE DAMBAR PROTRUSION.

ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08mm TOTAL

IN EXCESS OF THE & DIMENSION AT MAXIMUM MATERIAL

CONDITION.

6. CONTROLLING TIMENSION, MILLINETED

- CONDITION.

6. CUNTROLLING DIMENSION: MILLIMETER.

7. THIS DUTLINE CONFORMS TO JEDEC PUBLICATION 95

REGISTRATION MD-136, VARIATION AJ.

8. EXPOSED DIE PAD SHALL BE COPLANAR WITH BOTTOM

OF PACKAGE WITHIN 2 NILS (.05 MM).

9. LEADS SHALL BE COPLANAR WITHIN .004 INCH.

|                  | JEDEC VARIATION               |      |  |  |  |  |

|------------------|-------------------------------|------|--|--|--|--|

| S Y              | ALL DIMENSIONS IN MILLIMETERS |      |  |  |  |  |

| S<br>Y<br>B<br>D | AJ                            |      |  |  |  |  |

| ĭ                | MIN.                          | MAX. |  |  |  |  |

| Α                | 4                             | 1.20 |  |  |  |  |

| A <sub>1</sub>   | 0.05                          | 0.15 |  |  |  |  |

| Az               | 0.95 1.05                     |      |  |  |  |  |

| D                | 12.00 BSC.                    |      |  |  |  |  |

| D <sub>1</sub>   | 10.00 BSC.                    |      |  |  |  |  |

| Ε                | 12.00 BSC.                    |      |  |  |  |  |

| E <sub>1</sub>   | 10.00 BSC.                    |      |  |  |  |  |

| L                | 0.45                          | 0.75 |  |  |  |  |

| N                | 64                            |      |  |  |  |  |

| e                | 0.50 BSC.                     |      |  |  |  |  |

| lo               | 0.17                          | 0.27 |  |  |  |  |

| b1               | 0.17                          | 0.23 |  |  |  |  |

| ×                | 4.7                           | 5.30 |  |  |  |  |

| Υ                | 4.70                          | 5.30 |  |  |  |  |

# MAX3831/MAX3832

# +3.3V、2.5Gbps、SDH/SONET、4チャネル相互接続 マルチプレクサ/デマルチプレクサIC、クロック発生器付

**NOTES**

**///XI///** \_\_\_\_\_\_\_ 15

**NOTES**

| 販売代理店 |  |

|-------|--|

|       |  |

|       |  |

|       |  |

|       |  |

# マキシム・ジャパン株式会社

〒169-0051東京都新宿区西早稲田3-30-16(ホリゾン1ビル) TEL. (03)3232-6141 FAX. (03)3232-6149

マキシム社では全体がマキシム社製品で実現されている回路以外の回路の使用については責任を持ちません。回路特許ライセンスは明言されていません。マキシム社は随時予告なしに回路及び仕様を変更する権利を保留します。

16 \_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600