EVALUATION KIT

AVAILABLE

# 3.3V、622Mbps、SDH/SONET 1:4デシリアライザ、LVDS出力付

**MAX3681****概要**

MAX3681は、ATM及びSDH/SONETアプリケーションにおいて622Mbpsシリアルデータを4ビット幅の155Mbpsパラレルデータに変換するのに最適なデシリアライザです。+3.3V単一電源で動作し、PECL及びシリアルクロックを受けて、高速ディジタル回路とのインターフェース用のデータ出力及び低電圧差動信号(LVDS)クロックを提供します。また、データのアライメント及びリフレーミングを可能にするLVDS同期入力も備えています。

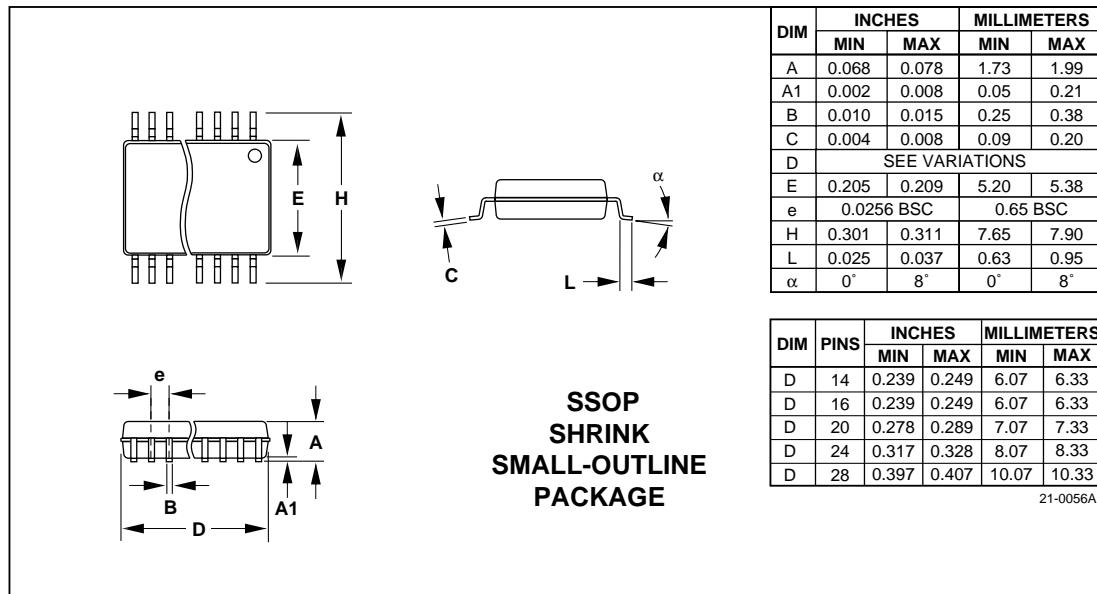

MAX3681は、拡張工業用温度範囲(-40 ~ +85)のものが24ピンSSOPパッケージで供給されています。

**アプリケーション**

622Mbps SDH/SONET伝送システム

622Mbps ATM/SONETアクセスノード

アド/ドロップマルチプレクサ

デジタルクロスコネクト

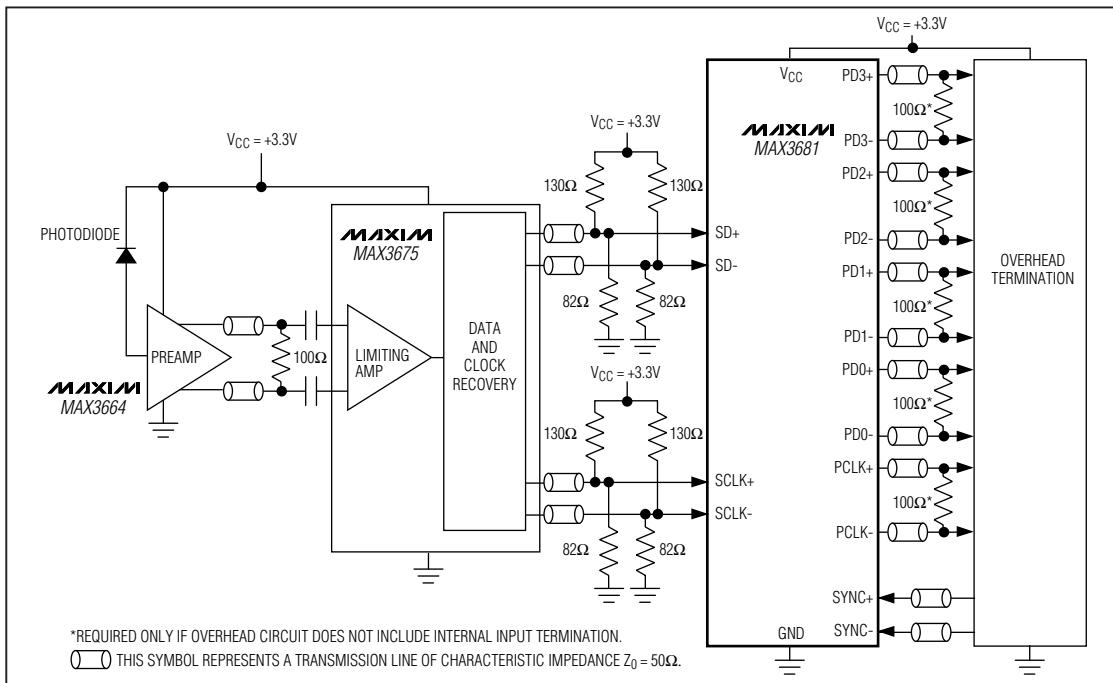

**標準動作回路****特長**

- ◆ 電源 : +3.3V単一

- ◆ 622Mbpsシリアルから155Mbpsパラレルへの変換

- ◆ 消費電力 : 265mW

- ◆ LVDSデータ出力及び同期入力

- ◆ データのアライメント及びリフレーミング用の同期入力

- ◆ 差動3.3V PECLクロック及びデータ入力

**型番**

| PART       | TEMP. RANGE    | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX3681EAG | -40°C to +85°C | 24 SSOP     |

ピン配置はデータシートの最後に記載されています。

# 3.3V, 622Mbps, SDH/SONET 1:4デシリアライザ、LVDS出力付

## ABSOLUTE MAXIMUM RATINGS

|                                               |                        |

|-----------------------------------------------|------------------------|

| Terminal Voltage (with respect to GND)        |                        |

| V <sub>CC</sub>                               | -0.5V to 5V            |

| PECL Inputs (SD+/-, SCLK+/-)                  | V <sub>CC</sub> + 0.5V |

| LVDS Inputs (SYNC+/-)                         | V <sub>CC</sub> + 0.5V |

| Output Current, LVDS Outputs (PCLK+/-, PD+/-) | 10mA                   |

|                                                       |                 |

|-------------------------------------------------------|-----------------|

| Continuous Power Dissipation (T <sub>A</sub> = +85°C) |                 |

| SSOP (derate 8.00mW/°C above +85°C)                   | 520mW           |

| Operating Temperature Range                           | -40°C to +85°C  |

| Storage Temperature Range                             | -65°C to +160°C |

| Lead Temperature (soldering, 10sec)                   | +300°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## DC ELECTRICAL CHARACTERISTICS

(V<sub>CC</sub> = +3.0V to +3.6V, differential loads = 100Ω, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted. Typical values are at V<sub>CC</sub> = +3.3V, T<sub>A</sub> = +25°C.)

| PARAMETER                                                                      | SYMBOL            | CONDITIONS                              | MIN                    | TYP                    | MAX   | UNITS |

|--------------------------------------------------------------------------------|-------------------|-----------------------------------------|------------------------|------------------------|-------|-------|

| Supply Current                                                                 | I <sub>CC</sub>   |                                         | 55                     | 80                     | 120   | mA    |

| <b>PECL INPUTS (SD+/-, SCLK+/-)</b>                                            |                   |                                         |                        |                        |       |       |

| Input High Voltage                                                             | V <sub>IH</sub>   |                                         | V <sub>CC</sub> - 1.16 | V <sub>CC</sub> - 0.88 |       | V     |

| Input Low Voltage                                                              | V <sub>IL</sub>   |                                         | V <sub>CC</sub> - 1.81 | V <sub>CC</sub> - 1.48 |       | V     |

| Input High Current                                                             | I <sub>IH</sub>   | V <sub>IN</sub> = V <sub>IH</sub> (MAX) | -10                    | 10                     |       | µA    |

| Input Low Current                                                              | I <sub>IL</sub>   | V <sub>IN</sub> = V <sub>IL</sub> (MAX) | -10                    | 10                     |       | µA    |

| <b>LVDS INPUTS AND OUTPUTS (SYNC+/-, PCLK+/-, PD+/-)</b>                       |                   |                                         |                        |                        |       |       |

| Input Voltage Range                                                            | V <sub>I</sub>    | Differential input voltage = 100mV      | 0                      | 2.4                    |       | V     |

| Differential Input Threshold                                                   | V <sub>IDTH</sub> | Common-mode voltage = 50mV              | -100                   | 100                    |       | mV    |

| Threshold Hysteresis                                                           | V <sub>HYST</sub> |                                         |                        | 70                     |       | mV    |

| Differential Input Resistance                                                  | R <sub>IN</sub>   |                                         | 85                     | 100                    | 115   | Ω     |

| Output High Voltage                                                            | V <sub>OH</sub>   |                                         |                        |                        | 1.475 | V     |

| Output Low Voltage                                                             | V <sub>OL</sub>   |                                         |                        | 0.925                  |       | V     |

| Differential Output Voltage                                                    | V <sub>OD</sub>   |                                         | 250                    | 400                    |       | mV    |

| Change in Magnitude of Differential Output Voltage for Complementary States    | ΔV <sub>OD</sub>  |                                         |                        |                        | 25    | mV    |

| Output Offset Voltage                                                          | V <sub>OS</sub>   | T <sub>A</sub> = +25°C                  | 1.125                  | 1.275                  |       | V     |

| Change in Magnitude of Output Offset Voltage for Complementary States          | ΔV <sub>OS</sub>  |                                         |                        |                        | 25    | mV    |

| Single-Ended Output Resistance                                                 | R <sub>O</sub>    |                                         | 40                     | 70                     | 140   | Ω     |

| Change in Magnitude of Single-Ended Output Resistance for Complementary States | ΔR <sub>O</sub>   |                                         |                        | ±1                     | ±10   | %     |

## AC ELECTRICAL CHARACTERISTICS

(V<sub>CC</sub> = +3.0V to +3.6V, differential loads = 100Ω, T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                           | SYMBOL              | CONDITIONS | MIN | TYP | MAX | UNITS |

|-------------------------------------|---------------------|------------|-----|-----|-----|-------|

| Maximum Serial Clock Frequency      | f <sub>SCLK</sub>   |            | 622 |     |     | MHz   |

| Serial Data Setup Time              | t <sub>SU</sub>     |            | 800 |     |     | ps    |

| Serial Data Hold Time               | t <sub>H</sub>      |            | 50  |     |     | ps    |

| Parallel Clock to Data Output Delay | t <sub>CCLK-Q</sub> |            | 200 | 550 | 900 | ps    |

**Note 1:** AC Characteristics guaranteed by design and characterization.

# 3.3V、622Mbps、SDH/SONET 1:4デシリアライザ、LVDS出力付

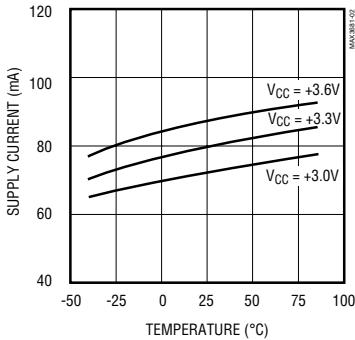

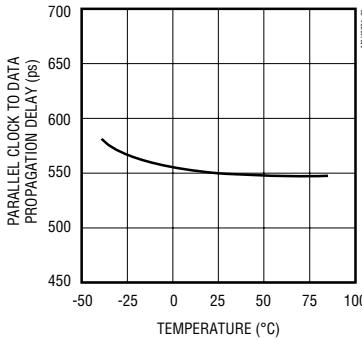

## 標準動作特性

( $V_{CC}$  = +3.0V to +3.6V, differential loads =  $100\Omega$ , unless otherwise noted.)

**MAX3681**

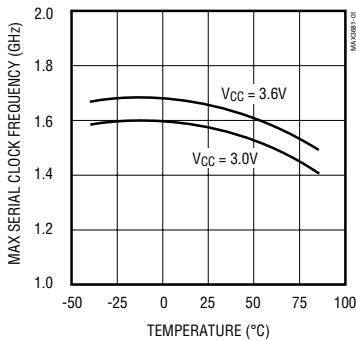

**MAXIMUM SERIAL CLOCK FREQUENCY

vs. TEMPERATURE**

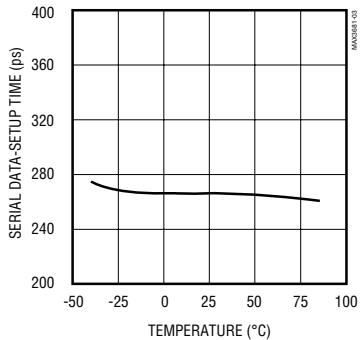

**SERIAL DATA-SETUP TIME

vs. TEMPERATURE**

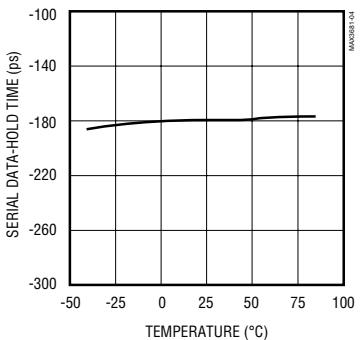

**SERIAL DATA-HOLD TIME

vs. TEMPERATURE**

**SUPPLY CURRENT

vs. TEMPERATURE**

**PARALLEL CLOCK TO DATA

OUTPUT PROPAGATION DELAY

vs. TEMPERATURE**

# 3.3V、622Mbps、SDH/SONET 1:4デシリアライザ、LVDS出力付

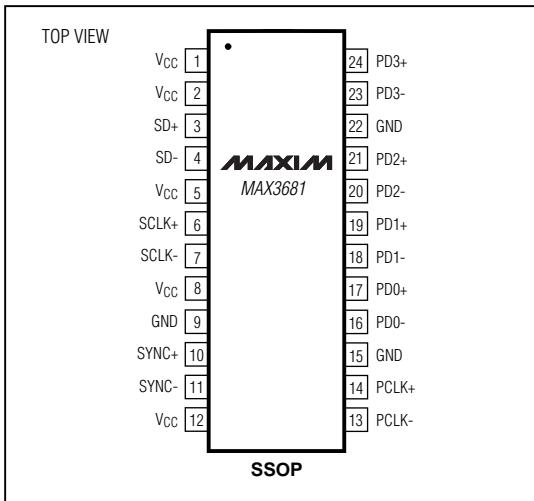

## 端子説明

| 端子             | 名称           | 機能                                                                                  |

|----------------|--------------|-------------------------------------------------------------------------------------|

| 1, 2, 5, 8, 12 | VCC          | +3.3V電源電圧                                                                           |

| 3              | SD+          | 非反転PECLシリアルデータ入力。データはSCLKの正遷移でクロックされます。                                             |

| 4              | SD-          | 反転PECLシリアルデータ入力。データはSCLKの正遷移でクロックされます。                                              |

| 6              | SCLK+        | 非反転PECLシリアルクロック入力                                                                   |

| 7              | SCLK-        | 反転PECLシリアルクロック入力                                                                    |

| 9, 15, 22      | GND          | グラウンド                                                                               |

| 10             | SYNC+        | 非反転LVDS同期パルス入力。SYNC信号を少なくともSCLKの2周期だけハイにして、1ビットをドロップすることによってデータアライメントをシフトしてください。    |

| 11             | SYNC-        | 反転LVDS同期パルス入力。SYNC信号を少なくともSCLKの2周期だけハイにして、1ビットをドロップすることによってデータアライメントをシフトしてください。     |

| 13             | PCLK-        | 反転LVDSパラレルクロック出力                                                                    |

| 14             | PCLK+        | 非反転LVDSパラレルクロック出力                                                                   |

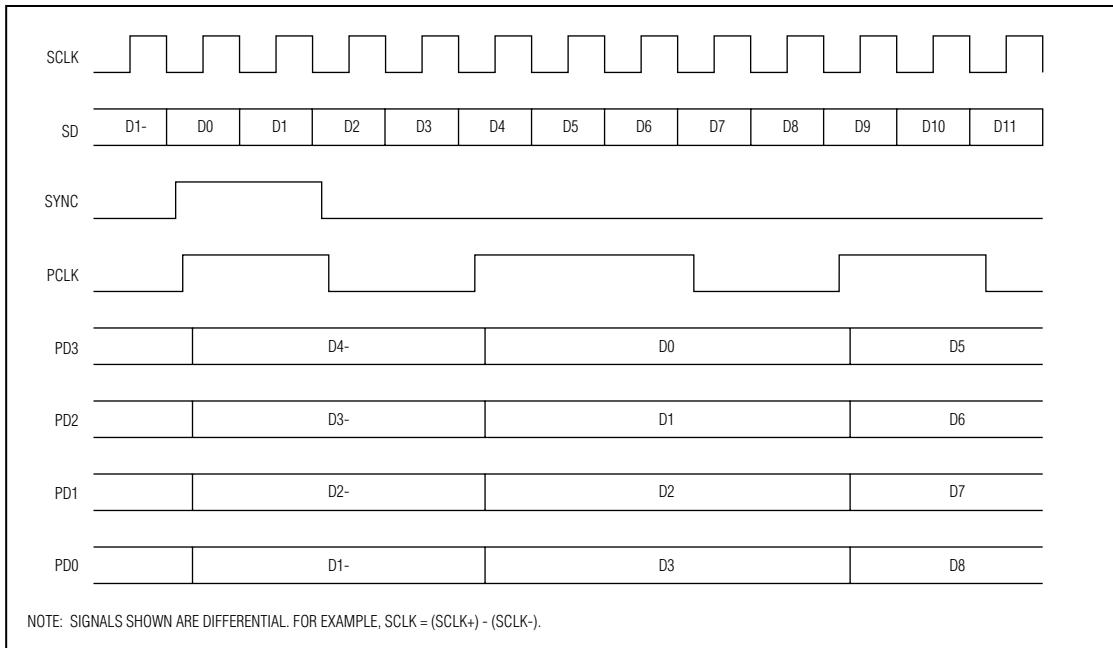

| 16, 18, 20, 23 | PDO- to PD3- | 反転LVDSパラレルデータ出力。データはPCLK信号の正遷移で更新されます。シリアルデータビット位置と出力データビット指定の関係については、図2を参照してください。  |

| 17, 19, 21, 24 | PDO+ to PD3+ | 非反転LVDSパラレルデータ出力。データはPCLK信号の正遷移で更新されます。シリアルデータビット位置と出力データビット指定の関係については、図2を参照してください。 |

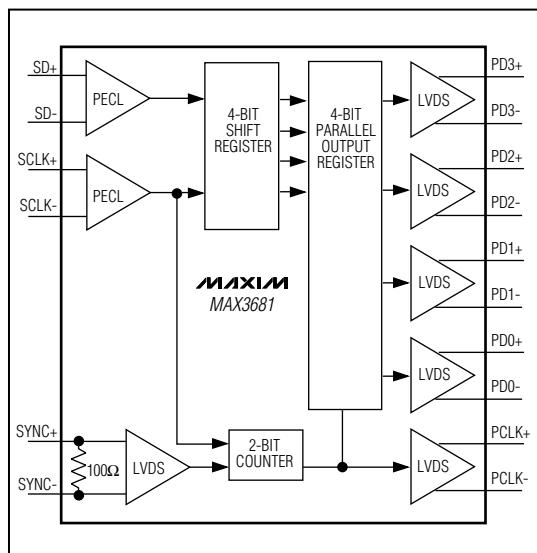

## 詳細

MAX3681は4ビットシフトレジスタ、4ビットパラレル出力レジスタ、2ビットカウンタ、PECL入力バッファ、及び低電圧差動信号(LVDS)入力/出力バッファを用いて、622Mbpsシリアルデータを4ビット幅の155Mbpsパラレルデータに変換します(図1)。

入力シフトレジスタは、シリアルクロック(SCLK)の正遷移で入ってくるデータを連続的にクロックします。2ビットカウンタは、シリアルクロック周波数を分周することによってパラレル出力クロックを生成します。PCLK信号は、パラレル出力レジスタのクロックとして使用されます。通常動作中、カウンタはSCLK周波数を4分周し、その結果出力レジスタが入ってくるシリアルデータを4ビットずつラッピします。

同期入力(SYNC+、SYNC-)は、データのアライメント及びリフレーミングに使用されます。SYNC信号が少なくとも2 SCLKサイクル期間パルス的にハイになると、パラレル出力データが1 SCLKサイクルだけ遅延されます。このアライメントは、SYNC信号の正遷移から2 PCLKサイクル以内に発生することが保証されています。この結果、そのPCLKサイクル中に入ってきた

図1. ファンクションダイアグラム

# 3.3V、622Mbps、SDH/SONET 1:4デシリアライザ、LVDS出力付

**MAX3681**

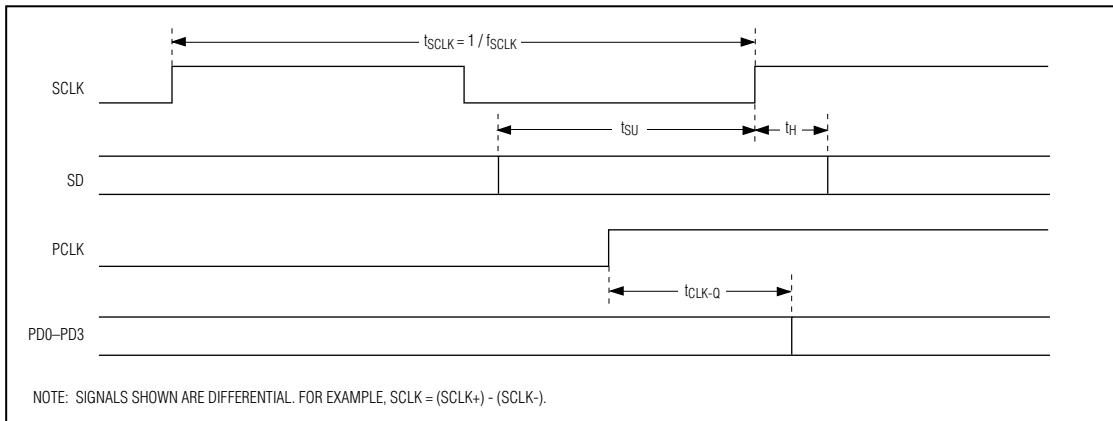

図2. 機能タイミング図

図3. タイミングパラメータ

# 3.3V、622Mbps、SDH/SONET 1:4デシリアライザ、LVDS出力付

データの最初のビットがドロップされ、PCLKとデータの間のアライメントを1ビットだけシフトします。

図2の機能タイミング図及び図3のタイミングパラメータ図を参照してください。

## 低電圧差動信号(LVDS)入出力

MAX3681は、高速ディジタル回路とのインターフェースを目的としたLVDS入出力を備えています。LVDS規格は、IEEE 1596.3であるLVDS規格に基づいています。この技術では250mVp-p ~ 400mVp-pの差動低電圧スイングを使用して高速遷移、低消費電力、及びノイズ耐性を実現しています。

パラレルクロック及びデータLVDS出力(PCLK+、PCLK-、PD\_+、PD\_-)が適正に動作するためには、反転出力と非反転出力の間で100 の差動DC終端処理を必要とします。これらの出力は、グランドに対して終端処理しないでください。

同期LVDS入力(SYNC+、SYNC-)は100 の内部差動入力抵抗で終端処理されているため、外部で終端処理する必要はありません。

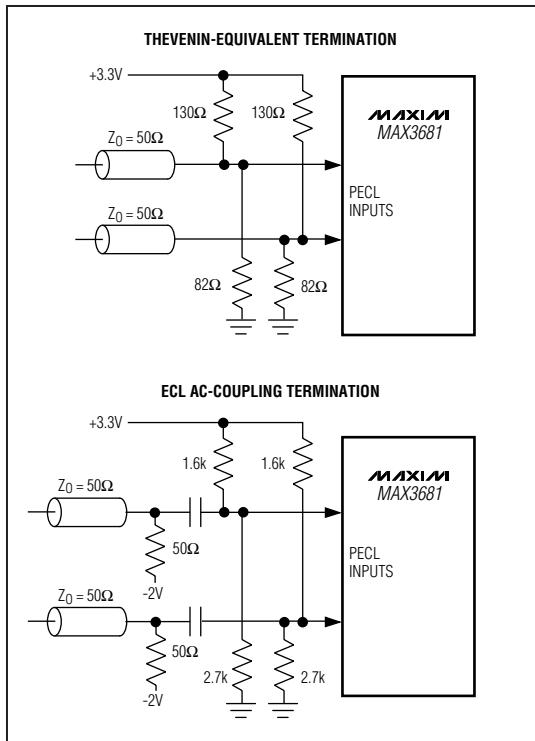

## PECL入力

シリアルデータ及びクロックPECL入力(SD+、SD-、SCLK+、SCLK-)をPECLソースとインターフェースするためには、50 で( $V_{CC} - 2V$ )に対して終端処理する必要があります(「PECL入力終端処理の別方法」を参照)。

## アプリケーション情報

### PECL入力終端処理の別方法

図4に、PECL入力終端処理の別方法を示します。 $(V_{CC} - 2V)$ 終端電圧が得られない場合には、テブナン等価終端を使用してください。ECL出力デバイスとのインターフェース等でACカップリングが必要な場合は、ECL ACカップリング終端を使用してください。

### レイアウト技法

最高の性能を得るために、優れた高周波レイアウト技法を使用してください。電源にはフィルタリングを施し、グランドへの接続は短くしてください。できるだけピアを多く用いてください。また、MAX3681のデータ入出力とのインターフェースには、制御されたインピーダンス伝送ラインを使用してください。

図4. PECL入力終端処理の別方法

**3.3V、622Mbps、SDH/SONET

1:4デシリアライザ、LVDS出力付**

**MAX3681**

ピン配置

チップ情報

TRANSISTOR COUNT: 724

*3.3V, 622 Mbps, SDH/SONET

1:4デシリアライザ、LVDS出力付*

パッケージ

販売代理店

マキシム・ジャパン株式会社

〒169 東京都新宿区西早稲田3-30-16(ホリゾン1ビル)

TEL. (03)3232-6141 FAX. (03)3232-6149

マキシム社では全体がマキシム社製品で実現されている回路以外の回路の使用については責任を持ちません。回路特許ライセンスは明言されていません。

マキシム社は隨時予告なしに回路及び仕様を変更する権利を保留します。

8 Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 (408) 737-7600

© 1996 Maxim Integrated Products

MAXIM is a registered trademark of Maxim Integrated Products.