### 概要

MAX3640は、OC-12データレート用のデュアルパス・ クロスポイントスイッチです。MAX3640は、ジッタの 蓄積を最小限に抑えつつ、622Mbps低電圧差動信号 (LVDS)をバックプレーン経由で送受信するために使用 できます。各経路は入力バッファ、マルチプレクサ、 クロスポイントスイッチ及び出力ドライバを備えてい ます。4つの出力チャネルは、テスト又はファンアウト 用に一組の冗長出力を備えています。本素子は重要な データストリーム用に信号経路の冗長性を提供して います。

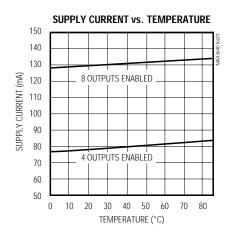

MAX3640はユニークな省電力機能を備えています。 4出力チャネルの1組が未選択になると、出力ドライバ がパワーダウンして消費電力を165mW低減します。 完全差動構造であるため、クロストーク、ジッタ蓄積 及び信号スキューが低減されています。

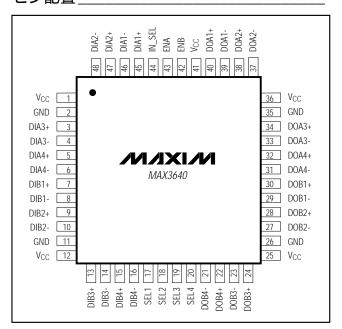

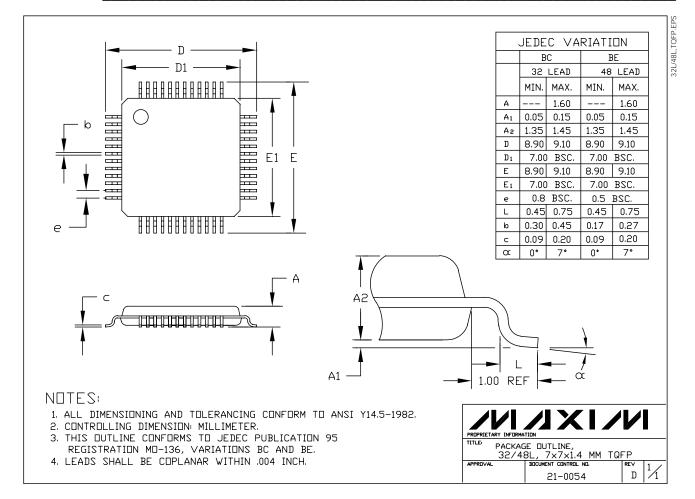

MAX3640は48ピンTQFPパッケージで提供されており、 +3.3V電源で動作します(温度範囲は0 ~ +85 )。

### アプリケーション

SONET/SDHバックプレーン 高速パラレルリンク ディジタルクロスコネクト システム相互接続 ATMスイッチコア

### 特長

- ◆ 単一電源:+3.3V

- ◆ 消費電力: 257mW(4つの出力チャネルが イネーブルされた状態)

- ◆ 出力ランダムジッタ2.8psRMS

- ◆ 出力確定的ジッタ:42ps

- ◆ 選択されていない出力のパワーダウン機能

- ◆ チャネル間スキュー: 110ps

- ◆ 出力エッジ速度: 240ps

- ◆ LVDS入力/出力

- ◆ LVDS出力3ステートイネーブル

| PART       | TEMP. RANGE  | PIN-PACKAGE | _ |

|------------|--------------|-------------|---|

| MAX3640UCM | 0°C to +85°C | 48 TQFP     |   |

ピン配置はデータシートの最後に記載されています。

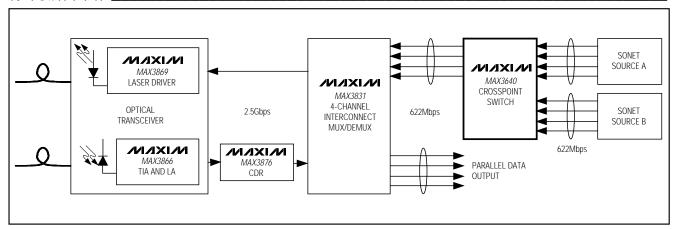

### 標準動作回路

###

### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, V <sub>CC</sub>                | 0.5V to 5.0V     | Operating Temperature Range       | 0°C to +85°C    |

|------------------------------------------------|------------------|-----------------------------------|-----------------|

| Input Voltage (LVDS, TTL)0.5V to (\            | $/_{CC} + 0.5V)$ | Storage Temperature Range         | -55°C to +150°C |

| Output Voltage (LVDS)0.5V to (\                |                  | Lead Temperature (soldering, 10s) | +300°C          |

| Continuous Power Dissipation ( $T_A = +85$ °C) |                  |                                   |                 |

| 48-Pin TQFP (derate 12.5mW/°C)                 | 813mW            |                                   |                 |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +3.0V \text{ to } 3.6V, \text{ LVDS differential load} = 100\Omega \pm 1\%, \text{ T}_{A} = 0^{\circ}\text{C to } +85^{\circ}\text{C}.$  Typical values are at  $V_{CC} = +3.3V, \text{ T}_{A} = +25^{\circ}\text{C}, \text{ unless otherwise noted.})$

| PARAMETER                                                                   | SYMBOL             | CONDITIONS                         | MIN   | TYP | MAX   | UNITS |  |

|-----------------------------------------------------------------------------|--------------------|------------------------------------|-------|-----|-------|-------|--|

| Cupply Current                                                              | Icc                | Eight outputs enabled              |       | 130 | 175   | то Л  |  |

| Supply Current                                                              |                    | Four outputs enabled               |       | 78  |       | mA    |  |

| LVDS INPUTS AND OUTPUTS                                                     |                    |                                    |       |     |       |       |  |

| Input Voltage Range                                                         | VIN                |                                    | 0     |     | 2400  | mV    |  |

| Differential Input Threshold                                                | V <sub>IDTH</sub>  |                                    | -100  |     | 100   | mV    |  |

| Threshold Hysteresis                                                        | V <sub>H</sub> YST |                                    |       | 90  |       | mV    |  |

| Differential Input Impedance                                                | RIN                |                                    | 85    | 100 | 115   | Ω     |  |

| Input Common-Mode Current                                                   | los                | LVDS input, V <sub>OS</sub> = 1.2V |       | 245 |       | μΑ    |  |

| Output Voltage High                                                         | VoH                | Figure 1                           |       |     | 1.475 | V     |  |

| Output Voltage Low                                                          | V <sub>OL</sub>    | Figure 1                           | 0.925 |     |       | V     |  |

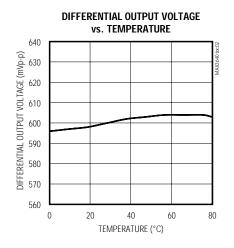

| Output Voltage Swing                                                        | V <sub>OD</sub>    | Figure 1                           | 250   |     | 400   | mV    |  |

| Change in Magnitude of<br>Differential Output for<br>Complementary States   | ΔV <sub>OD</sub>   |                                    |       |     | 25    | mV    |  |

| Offset Output Voltage                                                       | Vos                | Figure 1                           | 1.125 |     | 1.275 | mV    |  |

| Change in Magnitude of<br>Output Offset Voltage for<br>Complementary States | ΔV <sub>OS</sub>   |                                    |       |     | 25    | mV    |  |

| Differential Outrot Harmania                                                |                    | ENA, ENB = GND                     |       | 1   |       | MΩ    |  |

| Differential Output Impedance                                               |                    | ENA, ENB = V <sub>CC</sub>         | 80    |     | 120   | Ω     |  |

| Output Current                                                              |                    | Shorted together                   |       |     | 12    | mA    |  |

| TTL INPUTS                                                                  |                    |                                    |       |     |       |       |  |

| Input Voltage High                                                          | VIH                |                                    | 2.0   |     |       | V     |  |

| Input Voltage Low                                                           | VIL                |                                    |       |     | 0.8   | V     |  |

| Input Current High                                                          | lін                | $V_{IH} = 2.0V$                    | -250  |     |       | μΑ    |  |

| Input Current Low                                                           | IIL                | $V_{IL} = 0.8V$                    | -550  |     |       | μΑ    |  |

\_\_\_\_\_\_NIXI/N

### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3.0 \text{V to } 3.6 \text{V}$ , LVDS differential load =  $100\Omega$  ±1%, T<sub>A</sub> = 0°C to +85°C. Typical values are at  $V_{CC} = +3.3 \text{V}$ , T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                   | SYMBOL                          | CONDITIONS | MIN | TYP | MAX | UNITS |

|---------------------------------------------|---------------------------------|------------|-----|-----|-----|-------|

| Parallel Input/Output Data Rate             |                                 |            |     | 622 |     | Mbps  |

| Output Rise/Fall Time                       | t <sub>r</sub> , t <sub>f</sub> | 20% to 80% | 150 | 240 | 350 | ps    |

| Output Random Jitter                        | RJ                              |            |     | 2.8 | 4   | psrms |

| Output Deterministic Jitter                 | DJ                              | (Note 2)   |     | 42  | 200 | ps    |

| LVDS Output Differential Skew               | tskew1                          |            |     | 24  | 50  | ps    |

| LVDS Output Channel-to-<br>Channel Skew     | tSKEW2                          |            |     |     | 110 | ps    |

| LVDS Output Enable Time                     |                                 |            |     | 266 |     | ns    |

| LVDS Output Disable Time                    |                                 |            |     | 66  |     | ns    |

| LVDS Propagation Delay from Input to Output | t <sub>D</sub>                  |            |     |     | 2.5 | ns    |

Note 1: AC characteristics are guaranteed by design and characterization.

Note 2: Deterministic jitter (DJ) is the arithmetic sum of pattern-dependent jitter and pulse-width distortion. DJ is measured while applying 100mVp-p noise (f ≤ 2MHz) to the power supply.

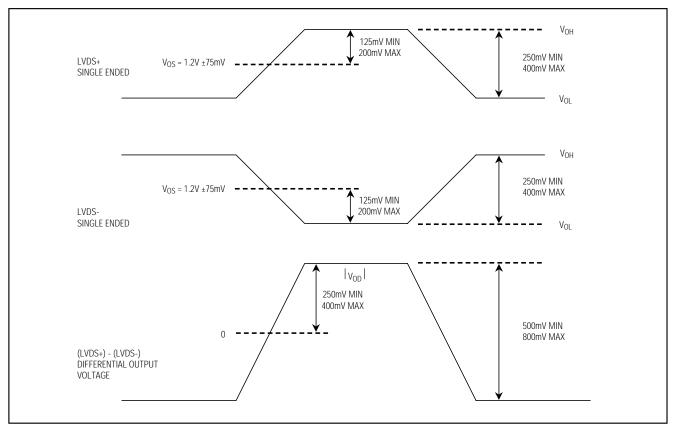

図1. LVDS出力レベル

### 標準動作特性

( $V_{CC} = +3.3V$ ,  $T_A = +25$ °C, unless otherwise noted.)

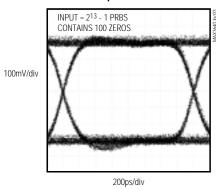

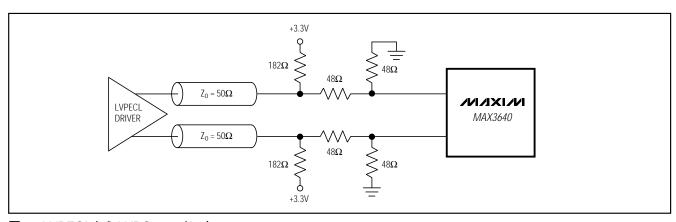

### 622Mbps EYE DIAGRAM

### 1.25Gbps EYE DIAGRAM

### 端子説明

| 端子                   | 名称                            | 機能                                                                                                       |

|----------------------|-------------------------------|----------------------------------------------------------------------------------------------------------|

| 1, 12, 25, 36,<br>41 | Vcc                           | 正電源電圧                                                                                                    |

| 2, 11, 26, 35        | GND                           | 電源グランド                                                                                                   |

| 3, 5, 45, 47         | DIA3+, DIA4+, DIA1+,<br>DIA2+ | 正LVDS、チャネルAデータ入力                                                                                         |

| 4, 6, 46, 48         | DIA3-, DIA4-, DIA1-,<br>DIA2- | 負LVDS、チャネルAデータ入力                                                                                         |

| 7, 9, 13, 15         | DIB1+, DIB2+, DIB3+,<br>DIB4+ | 正LVDS、チャネルBデータ入力                                                                                         |

| 8, 10, 14, 16        | DIB1-, DIB2-, DIB3-,<br>DIB4- | 負LVDS、チャネルBデータ入力                                                                                         |

| 17–20                | SEL1-SEL4                     | クロスポイントスイッチ選択、TTL入力(表1)                                                                                  |

| 21, 23, 27, 29       | DOB4-, DOB3-, DOB2-,<br>DOB1- | 負LVDS、チャネルBデータ出力                                                                                         |

| 22, 24, 28, 30       | DOB4+, DOB3+,<br>DOB2+, DOB1+ | 正LVDS、チャネルBデータ出力                                                                                         |

| 31, 33, 37, 39       | DOA4-, DOA3-, DOA2-,<br>DOA1- | 負LVDS、チャネルAデータ出力                                                                                         |

| 32, 34, 38, 40       | DOA4+, DOA3+,<br>DOA2+, DOA1+ | 正LVDS、チャネルAデータ出力                                                                                         |

| 42                   | ENB                           | チャネルB出力イネーブル、TTL入力。ENB = ハイの時にDOB1 ~ DOB4がイネーブルされます。<br>ENB = ローの時にDOB1 ~ DOB4パワーダウンされ、ハイインピーダンス状態になります。 |

| 43                   | ENA                           | チャネルA出力イネーブル、TTL入力。ENA = ハイの時にDOA1~DOA4がイネーブルされます。<br>ENA = ローの時にDOA1~DOA4パワーダウンされ、ハイインピーダンス状態になります。     |

| 44                   | IN_SEL                        | 入力選択ピン、TTL入力。ロジックハイ(又はV <sub>CC</sub> )に接続すると、DIA1~DIA4が選択されます。ロジックロー(又はGND)に接続すると、DIB1~DIB4が選択されます。     |

### 詳細

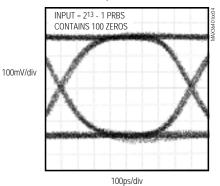

図2にMAX3640の構造を示します。本素子は2つのデータ経路からなっています。各データ経路は4つの差動入力バッファで始まります。IN\_SELピンは、AとBのどちらのチャネルがその後に続く2x2クロスポイントスイッチに接続されるかを選択します。SEL\_ピンがクロスポイントスイッチの経路を制御します。各クロスポイントスイッチの出力が1対のLVDS出力ドライバを駆動します。これにより、ファンアウト又はテスト用に使用できる冗長出力セットが得られます。各出力セット(DOA\_及びDOB\_)はENA及びENBピンによってイネーブル又はディセーブルされます。出力分配制御については表1を参照して下さい。

### LVDS入出力

MAX3640は、高速ディジタル回路とインタフェースするためのLVDS入出力を備えています。LVDS規格はIEEE 1596.3 LVDS規格に基づいています。この技術は、500mV~800mVの差動低電圧スイングを使用することにより、高速遷移、低消費電力及び優れたノイズ耐性を実現しています。

適正動作には、データ出力の反転ピンと非反転ピンの間に100 の差動終端処理が必要です。これらの出力をグランドに対して終端処理しないで下さい。LVDSの出力電圧仕様については図1を参照して下さい。

データ入力は内部で100 差動終端処理されているため、 外部終端処理は必要ありません。

図2. ファンクションダイアグラム

## 表1. 出力のルーティング

| ROUTING CONTROLS |      |      | OUTPUT SIGNALS      |                     |  |

|------------------|------|------|---------------------|---------------------|--|

| IN_SEL           | SEL1 | SEL2 | Signal at DOA1/DOB1 | Signal at DOA2/DOB2 |  |

| 0                | 0    | 0    | DIB1                | DIB1                |  |

| 0                | 0    | 1    | DIB1                | DIB2                |  |

| 0                | 1    | 0    | DIB2                | DIB1                |  |

| 0                | 1    | 1    | DIB2                | DIB2                |  |

| 1                | 0    | 0    | DIA1                | DIA1                |  |

| 1                | 0    | 1    | DIA1                | DIA2                |  |

| 1                | 1    | 0    | DIA2                | DIA1                |  |

| 1                | 1    | 1    | DIA2                | DIA2                |  |

| IN_SEL           | SEL3 | SEL4 | Signal at DOA3/DOB3 | Signal at DOA4/DOB4 |  |

| 0                | 0    | 0    | DIB3                | DIB3                |  |

| 0                | 0    | 1    | DIB3                | DIB4                |  |

| 0                | 1    | 0    | DIB4                | DIB3                |  |

| 0                | 1    | 1    | DIB4                | DIB4                |  |

| 1                | 0    | 0    | DIA3                | DIA3                |  |

| 1                | 0    | 1    | DIA3                | DIA4                |  |

| 1                | 1    | 0    | DIA4                | DIA3                |  |

| 1                | 1    | 1    | DIA4                | DIA4                |  |

**Note:** Disabling the outputs by using ENA or ENB will drive the DOA\_ or DOB\_ data outputs to a high-impedance state.

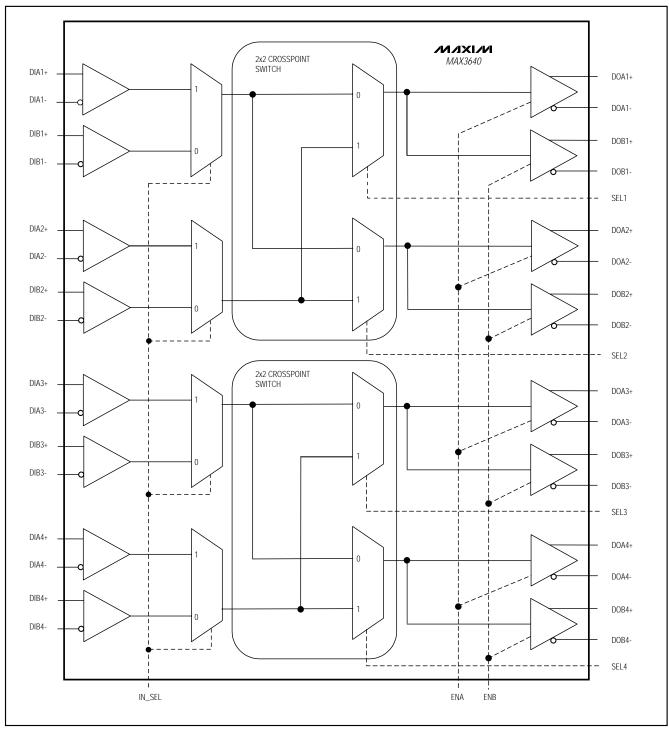

図3. LVPECLからLVDSへのインタフェース

M/IXI/N

アプリケーション情報

LVPECL出力からMAX3640のLVDS入力へのインタフェース

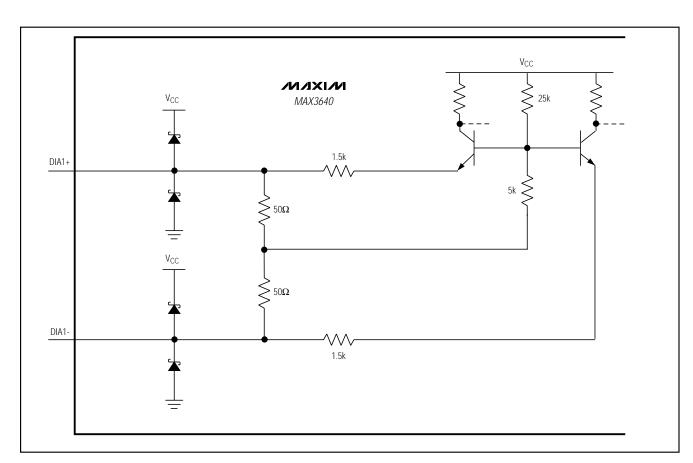

LVPECLからLVDSへのDCカップリングを行うには、図3に示す抵抗ネットワークを使用して下さい。LVPECL出力はV<sub>CC</sub>-2Vへの50Ω負荷に対して最適化されているため、それに相当するネットワークが使用されます。また、このネットワークの減衰は、減衰後のLVPECL出力信号がLVDS入力範囲に余裕を持って収まるように選択して下さい。

LVDS入力インピーダンスは、入力間で真の100Ωであることに注意して下さい。差動インピーダンスはDC終端インピーダンスには寄与しませんが、AC終端インピーダンスには寄与することに注意して下さい。これは、ACインピーダンスとDCインピーダンスが常に異なることを意味します。

### レイアウト技法

最適な性能を得るために、良好な高周波レイアウト技法を使用して下さい。電圧電源のフィルタリングを行い、グランドへの接続は短くして下さい。可能なところでは複数のビアを使用して下さい。また、MAX3640のデータ入出力とインタフェースする時は、インピーダンスが調整された伝送ラインを使用して下さい

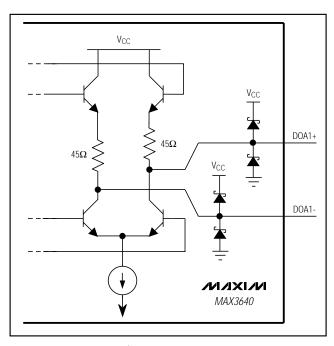

### インタフェースモデル

図4にLVDS入力のインタフェースモデルを示します。 図5にLVDS出力のモデルを示します。

図4. LVDS入力モデル

図5. LVDS出力モデル

### チップ情報

**TRANSISTOR COUNT: 2453**

### ピン配置

パッケージ

# *MAX3640*

# 3.3V、622Mbps LVDS **デュアル**4:2**クロスポイントスイッチ**

**NOTES**

**MAXIM** \_\_\_\_\_\_ 11

**NOTES**

| 販売代理店 |  |  |  |

|-------|--|--|--|

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

# マキシム・ジャパン株式会社

〒169-0051東京都新宿区西早稲田3-30-16(ホリゾン1ビル) TEL. (03)3232-6141 FAX. (03)3232-6149

マキシム社では全体がマキシム社製品で実現されている回路以外の回路の使用については責任を持ちません。回路特許ライセンスは明言されていません。マキシム社は随時予告なしに回路及び仕様を変更する権利を保留します。

12 \_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600