# MAX3601

## レーザドライバ、プロジェクタ用

### 概要

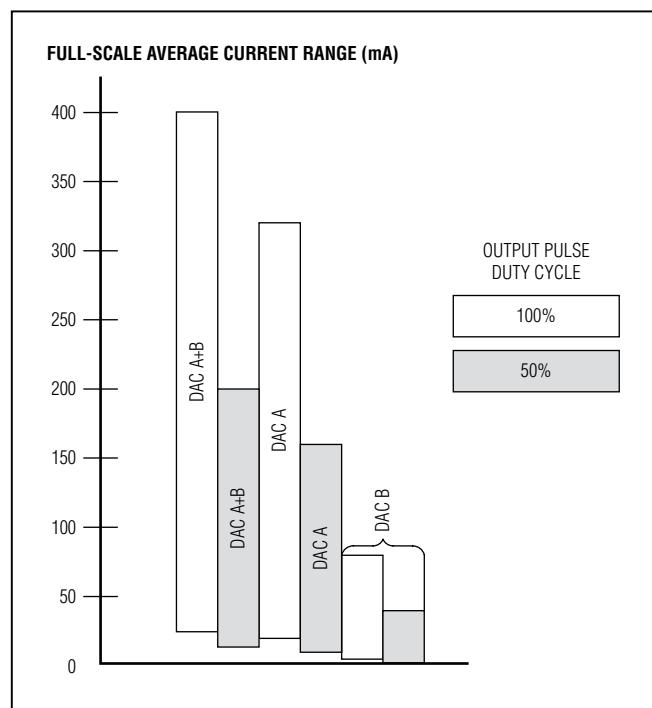

ピコプロジェクト用レーザドライバのMAX3601は、RGBレーザによるビデオイメージングをサポートします。各出力には、設定可能な利得とチャネル当り最大400mAの駆動能力を持つ2つの8ビットデジタル-アナログコンバータ(DAC)が組み込まれています。DAC Aのフルスケール電流は最大320mA、DAC Bのフルスケール電流は最大80mAです。3つのチャネルすべてを組み合わせて、最大1.2Aの駆動能力を持つ単一のチャネルにすることができます。

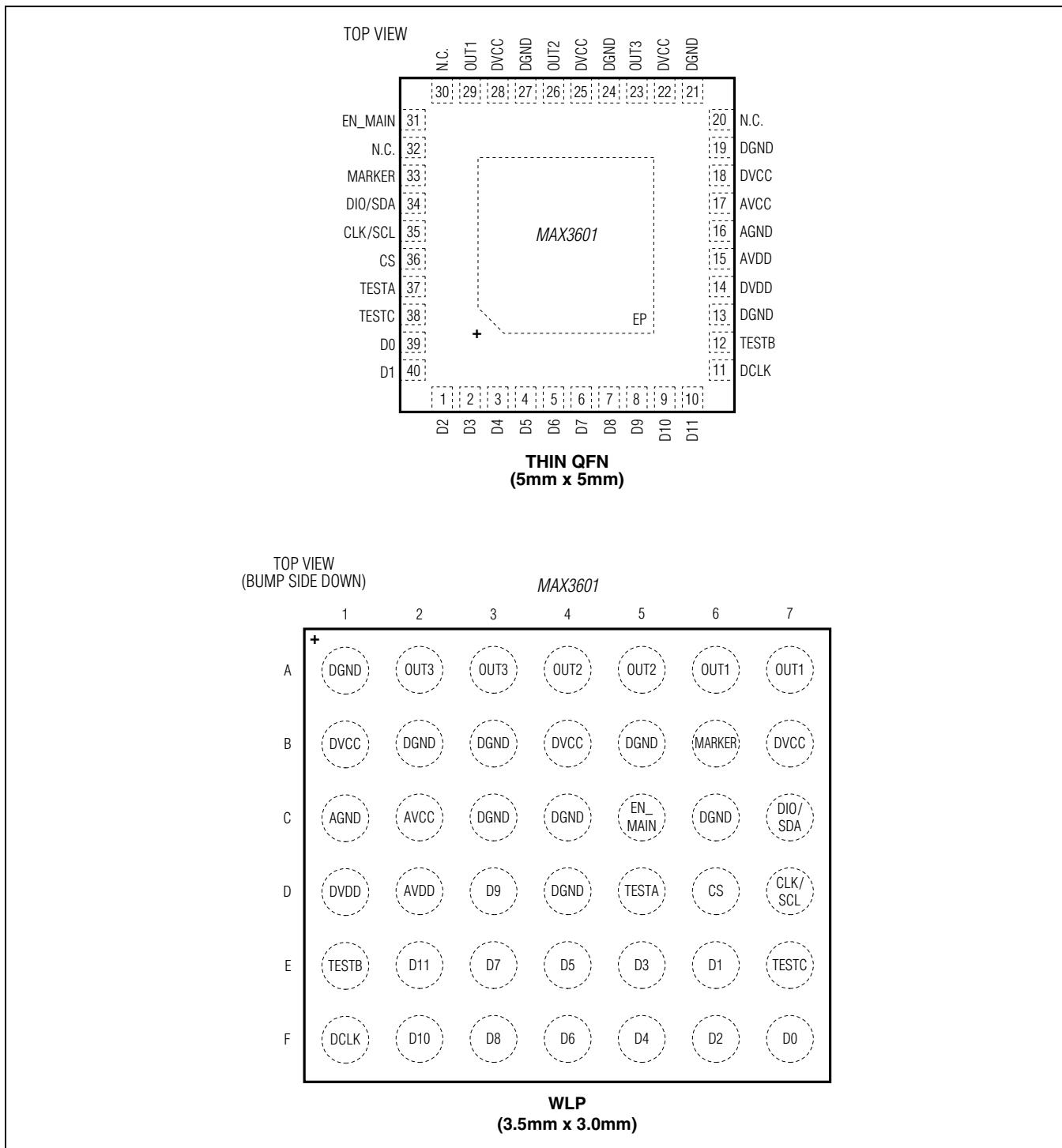

特許を取得したMaxim独自の技術が、スペックルノイズを抑制しつつパルス電流によるレーザの効率的な動作を可能にしています。この機能はビデオデータクロックに基づいて動作します。このドライバは、一般的の商用アプリケーションには42ピン、ウェハレベルパッケージ(3.0mm x 3.5mm)で提供され、工業や車載アプリケーションには40ピンTQFNパッケージ(5mm x 5mm)で提供されます。

### アプリケーション

RGBピコレーザプロジェクタ

LCOSプロジェクタ用レーザ光源

大電流LEDまたはレーザパルスジェネレータ

### 利点および特長

- ◆ 3つの電流出力レーザドライバを集積化

- ✧ 大部分のRGBレーザとコンパチブル

- ✧ 8ビットビデオDAC、DC~167MHz動作

- ✧ 特許取得済みのパルス機能によるレーザスペックルの抑制

- ✧ 出力スイッチング時間：1ns

- ✧ パルススイッチング速度エンハンサー

- ◆ 機能集積化によるPCB面積の最小化

- ✧ SPIまたはI<sup>2</sup>Cシリアルポート制御

- ✧ 動作範囲：1.8V~3.3V

- ✧ 8ビット利得調整

- ✧ 設定可能なパルス電流

- ✧ 42ピンWLP (3.0mm x 3.5mm)パッケージと40ピンTQFN (5mm x 5mm)パッケージ

- ✧ 温度センサー内蔵

- ◆ 低電力要件

- ✧ ブラックビデオイメージの場合：80mW以下

- ✧ ビデオマーカを使用した出力ディセーブル

- ✧ 出力電圧センサー

- ◆ レーザイネーブル機能による安全準拠性の確保

型番はデータシートの最後に記載されています。

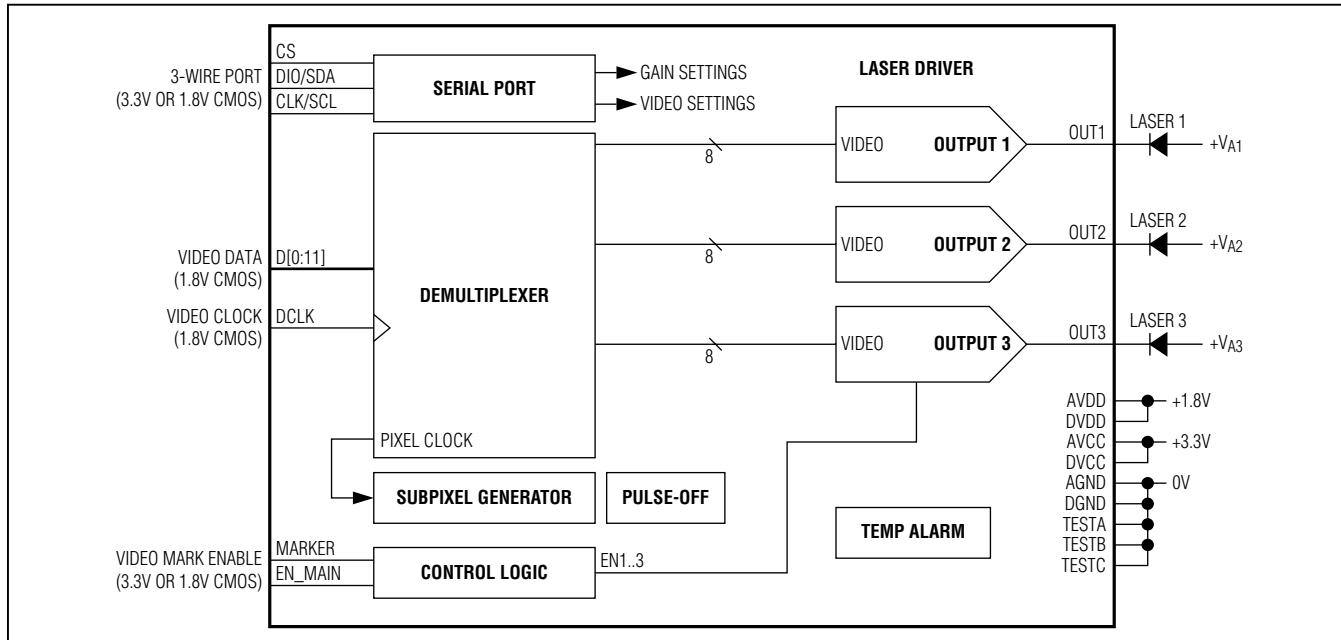

### 簡易ファンクションダイアグラム

関連部品およびこの製品とともに使用可能な推奨製品については、[japan.maximintegrated.com/MAX3601.related](http://japan.maximintegrated.com/MAX3601.related)を参照してください。

本データシートは日本語翻訳であり、相違及び誤りのある可能性があります。設計の際は英語版データシートを参照してください。

価格、納期、発注情報についてはMaxim Direct (0120-551056)にお問い合わせいただくか、Maximのウェブサイト ([japan.maximintegrated.com](http://japan.maximintegrated.com))をご覧ください。

# レーザドライバ、プロジェクタ用

---

## 目次

---

|                                           |    |

|-------------------------------------------|----|

| 概要 . . . . .                              | 1  |

| アプリケーション . . . . .                        | 1  |

| 利点および特長 . . . . .                         | 1  |

| 簡易ファンクションダイアグラム . . . . .                 | 1  |

| Absolute Maximum Ratings . . . . .        | 6  |

| Package Thermal Characteristics . . . . . | 6  |

| Electrical Characteristics . . . . .      | 6  |

| 標準動作特性 . . . . .                          | 15 |

| ピン配置 . . . . .                            | 18 |

| 端子説明 . . . . .                            | 19 |

| ファンクションダイアグラム . . . . .                   | 21 |

| 詳細 . . . . .                              | 22 |

| ビデオデマルチブレクサ . . . . .                     | 22 |

| デマルチブレクサA . . . . .                       | 22 |

| デマルチブレクサB . . . . .                       | 22 |

| デマルチブレクサC . . . . .                       | 23 |

| パルスタイミングジェネレータ . . . . .                  | 24 |

| サブピクセル設定 . . . . .                        | 25 |

| パルスオフ . . . . .                           | 25 |

| ドライバ出力 . . . . .                          | 26 |

| ビデオDAC . . . . .                          | 26 |

| パルスオフとパルスオフアシスト . . . . .                 | 28 |

| コンプライアンス電圧センサー . . . . .                  | 28 |

| 温度アラーム . . . . .                          | 29 |

| 制御ロジック . . . . .                          | 29 |

| ビデオの選択 . . . . .                          | 29 |

| レーザの制御 . . . . .                          | 29 |

| シリアルポートおよびレジスタ . . . . .                  | 30 |

| I <sup>2</sup> Cインターフェース . . . . .        | 30 |

| データ転送 . . . . .                           | 30 |

| STARTおよびSTOP条件 . . . . .                  | 30 |

| アクノリッジ . . . . .                          | 31 |

| スレーブアドレス . . . . .                        | 31 |

| I <sup>2</sup> C通信プロトコル . . . . .         | 31 |

| 單一レジスタへの書き込み . . . . .                    | 32 |

| 連続するレジスタへの書き込み . . . . .                  | 32 |

# レーザドライバ、プロジェクト用

---

## 目次 (続き)

---

|                                   |    |

|-----------------------------------|----|

| 単一レジスタからの読み取り .....               | 33 |

| 連続するレジスタからの読み取り .....             | 33 |

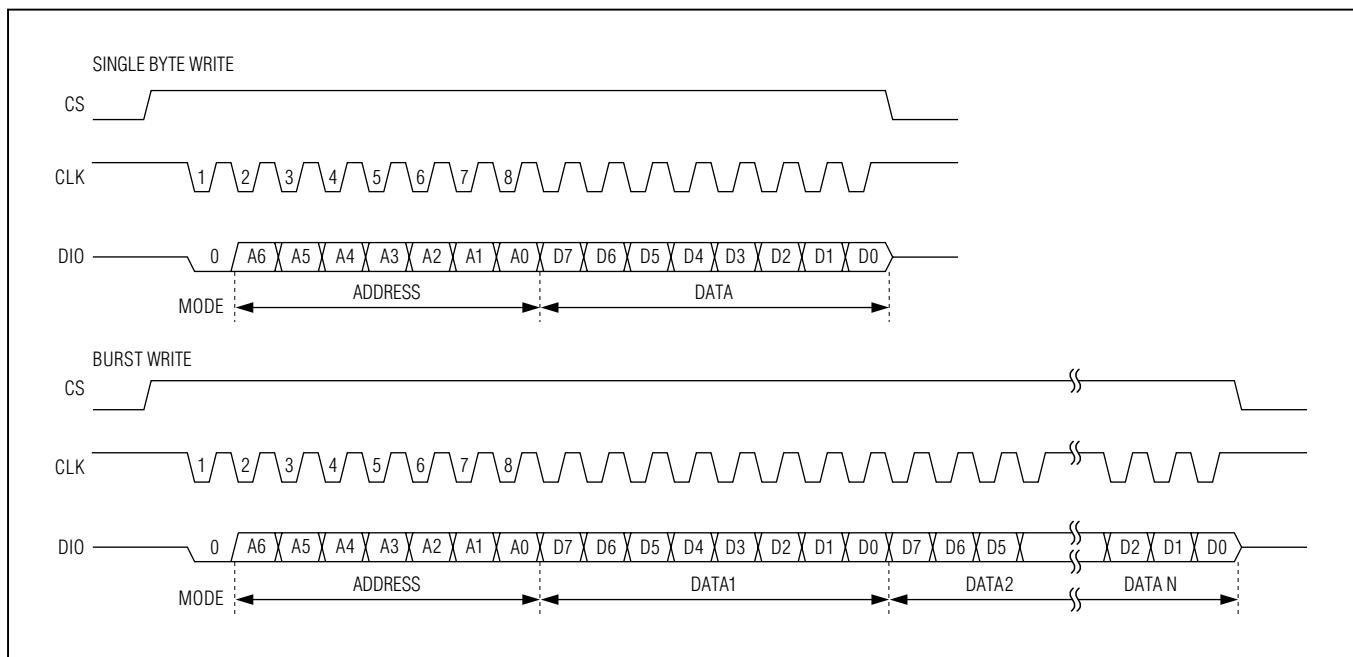

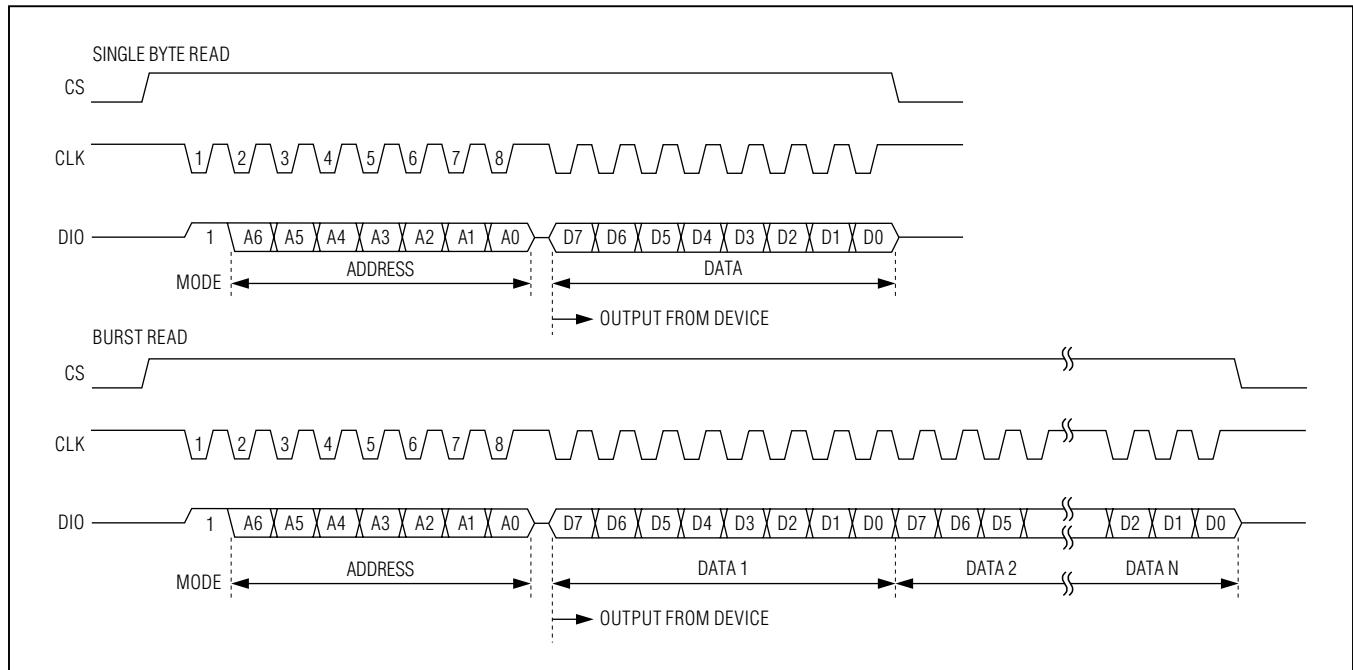

| SPIインターフェース .....                 | 34 |

| 3線式SPIを使用するデータの読み取り/書き込み .....    | 34 |

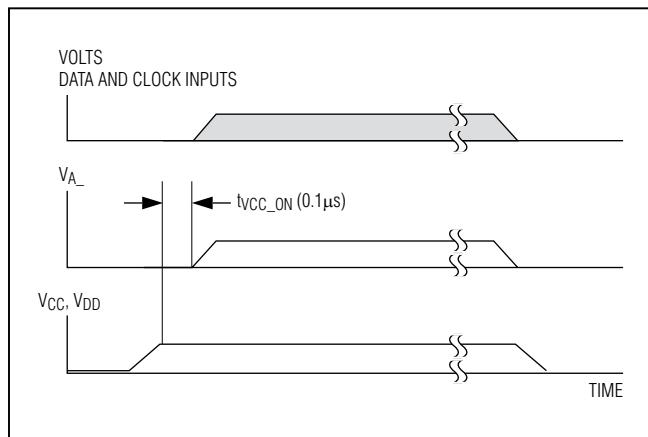

| パワーオンリセット .....                   | 39 |

| 設計手順 .....                        | 39 |

| レーザの選択 .....                      | 39 |

| 電源フィルタ .....                      | 39 |

| 補償回路 .....                        | 40 |

| PCBレイアウト .....                    | 40 |

| レーザドライバの熱について .....               | 40 |

| アプリケーション情報 .....                  | 40 |

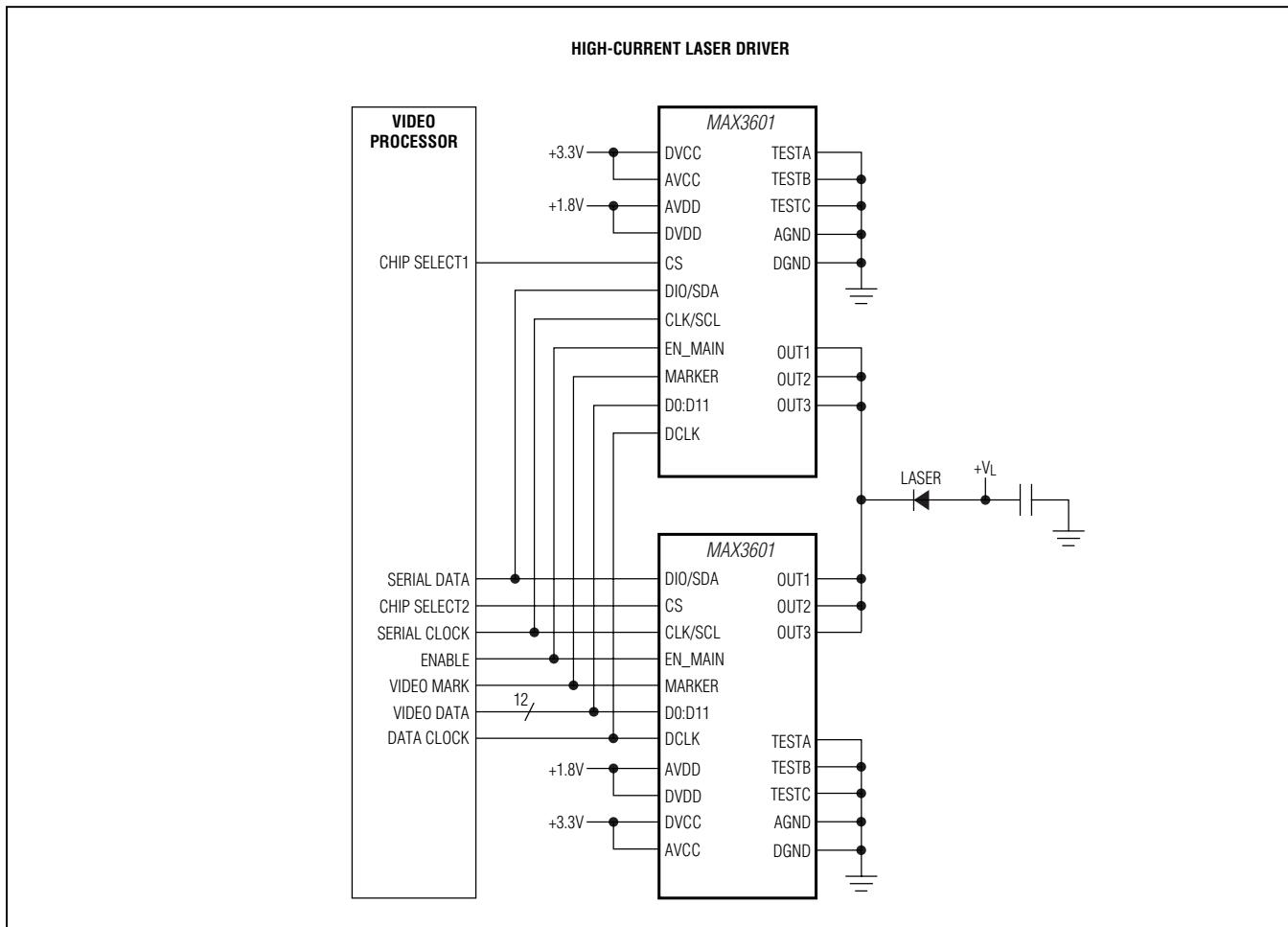

| 複数の出力の接続 .....                    | 40 |

| アイセーフティ .....                     | 40 |

| ウェハレベルパッケージ(WLP)のアプリケーション情報 ..... | 40 |

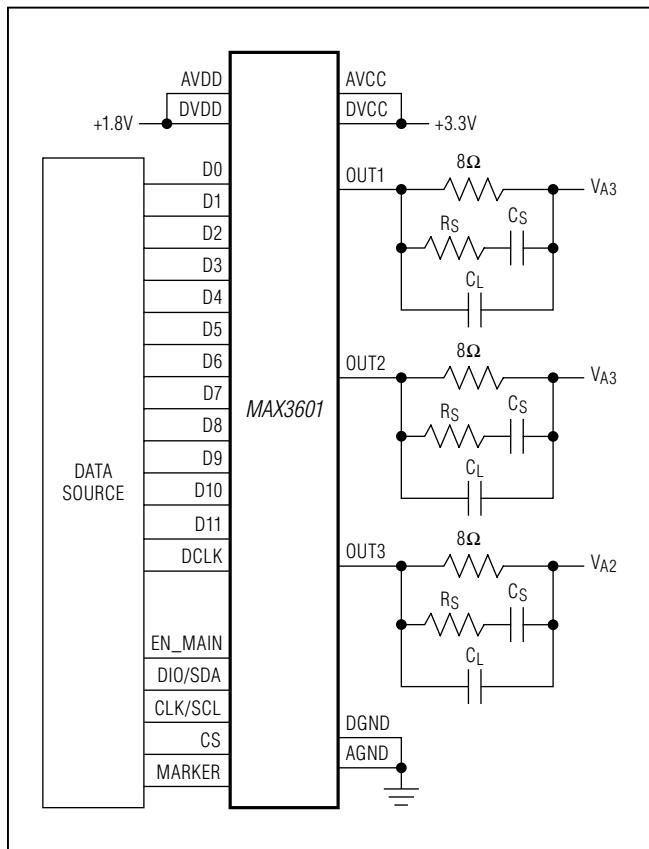

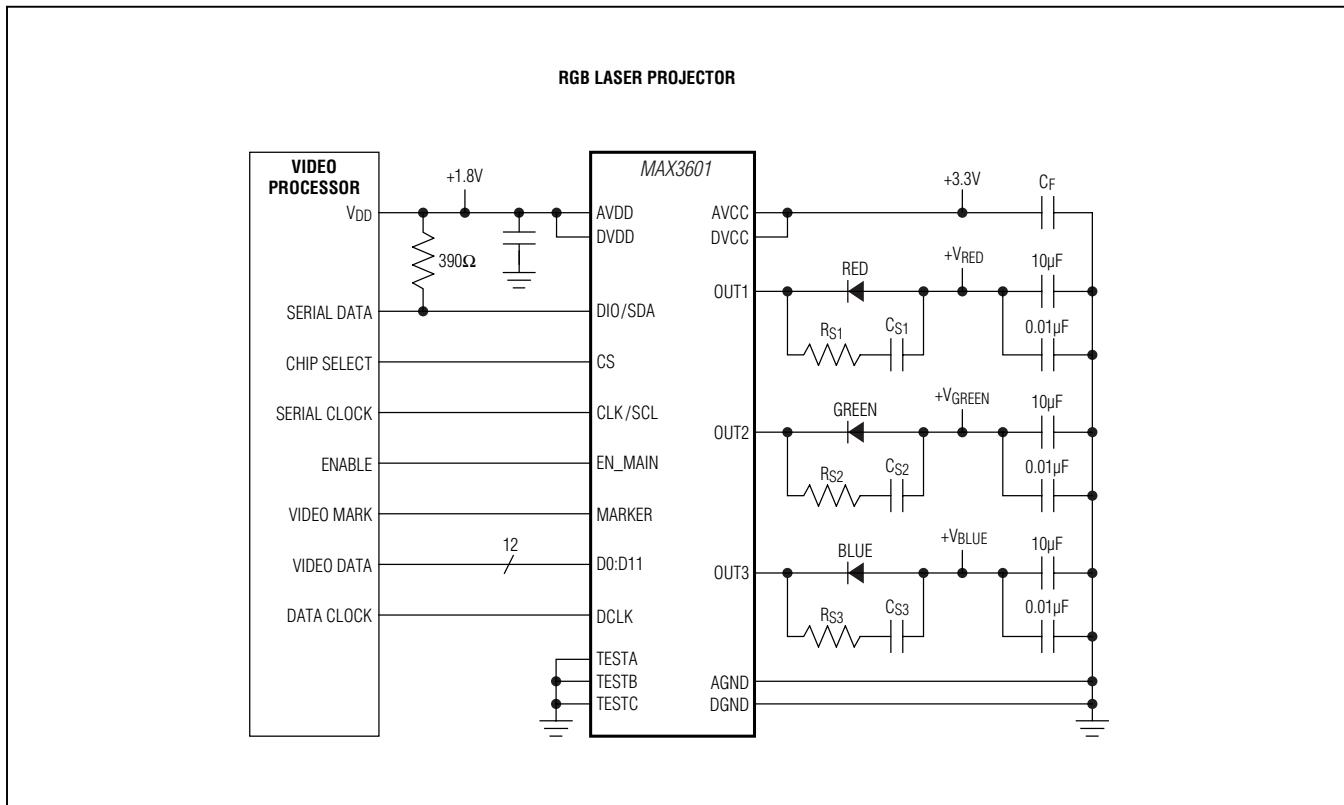

| 標準動作回路 .....                      | 49 |

| 型番 .....                          | 50 |

| パッケージ .....                       | 50 |

| 改訂履歴 .....                        | 51 |

# レーザドライバ、プロジェクト用

## 図リスト

|                                                  |    |

|--------------------------------------------------|----|

| 図1. テスト回路 . . . . .                              | 13 |

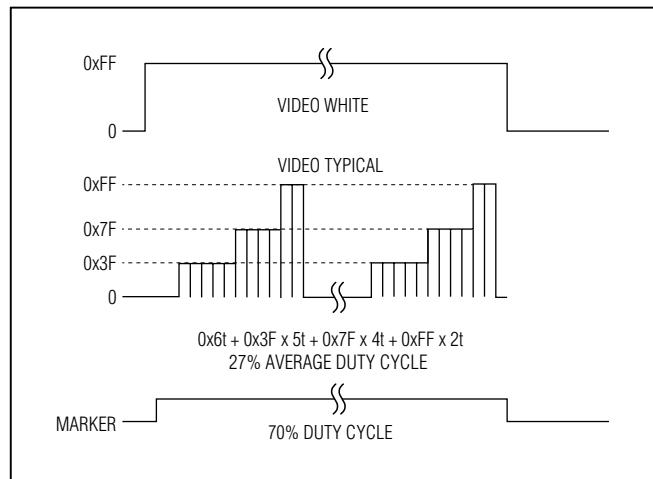

| 図2. ビデオテストパターン . . . . .                         | 13 |

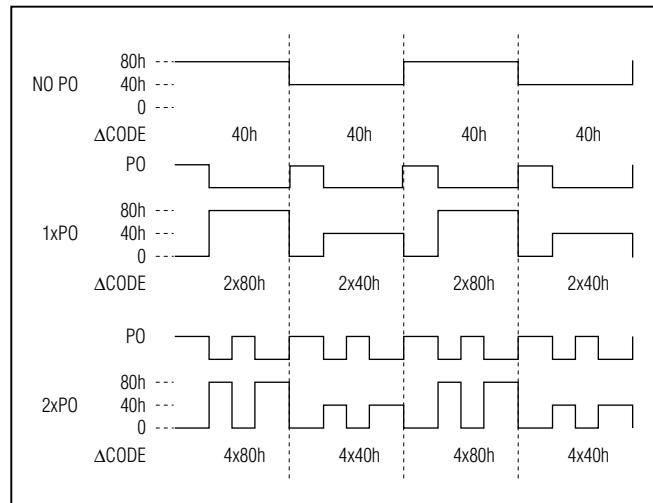

| 図3. Δコードの例 . . . . .                             | 13 |

| 図4. 電源の計算 . . . . .                              | 14 |

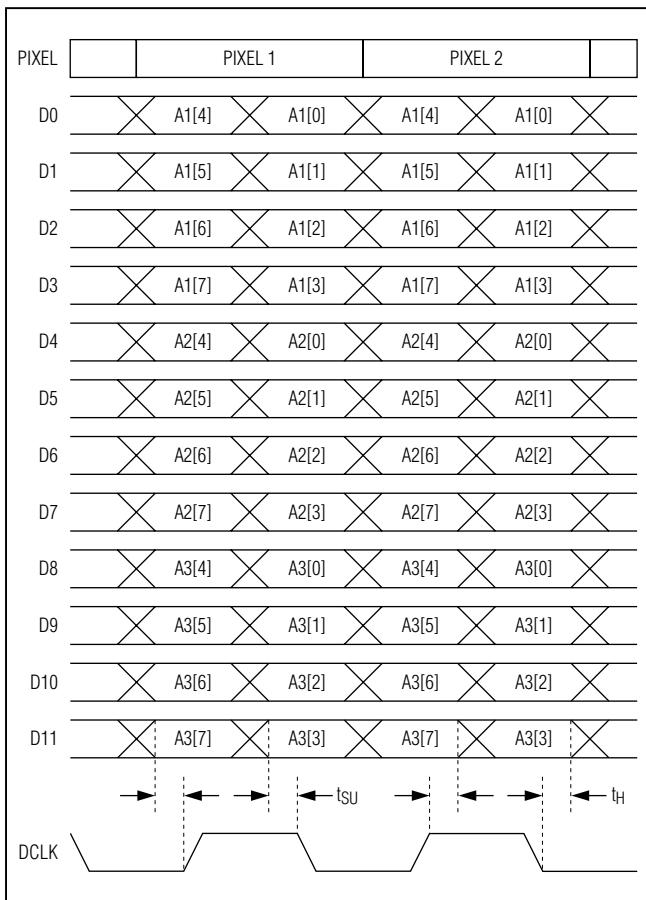

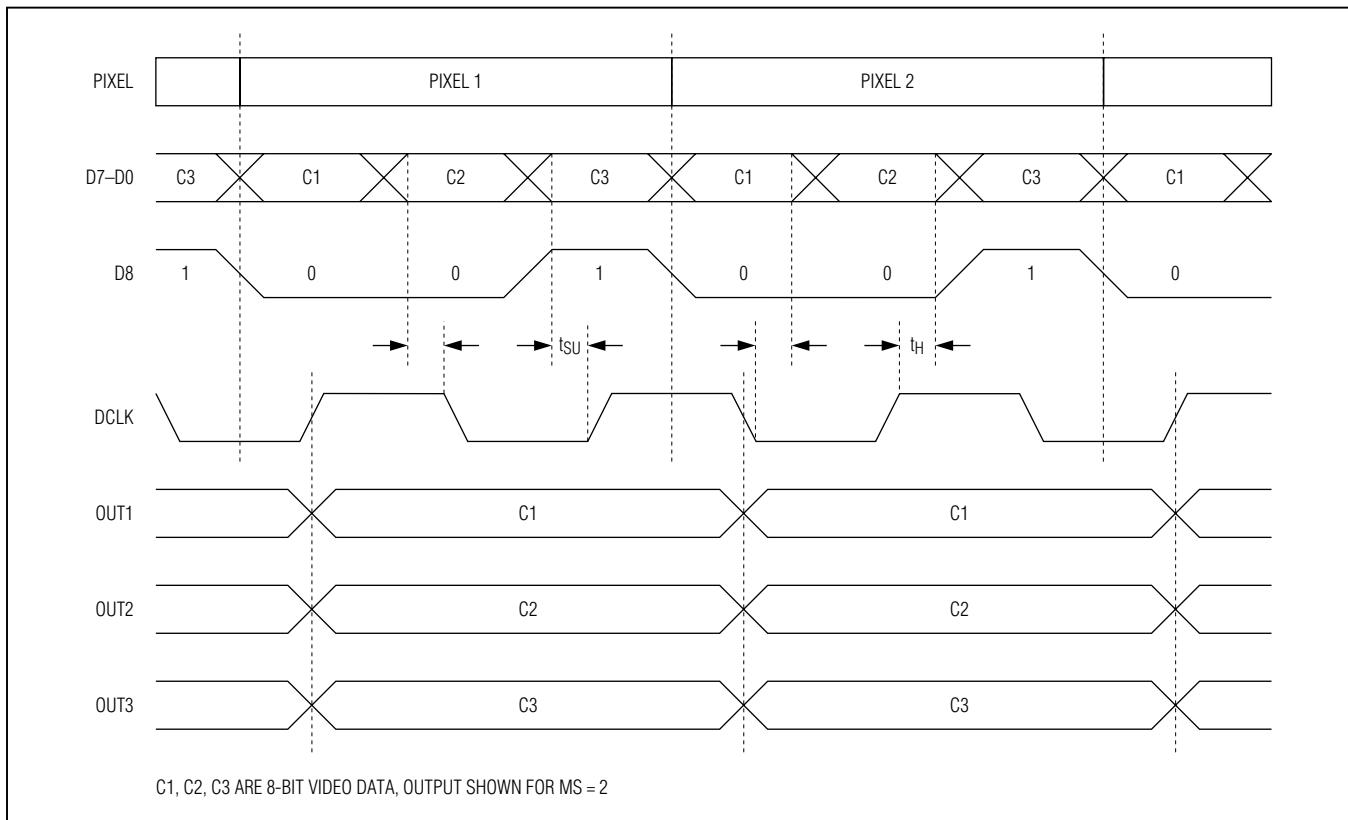

| 図5. ビデオデマルチプレクサAの入力波形 . . . . .                  | 22 |

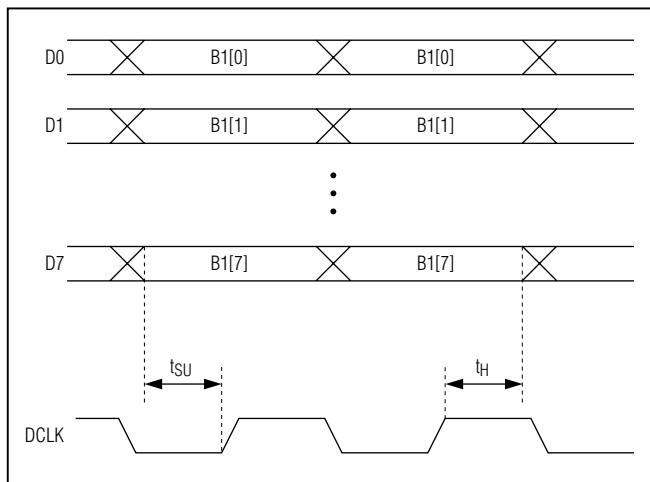

| 図6. ビデオデマルチプレクサBの入力波形 . . . . .                  | 22 |

| 図7. ビデオデマルチプレクサCの入力波形 . . . . .                  | 23 |

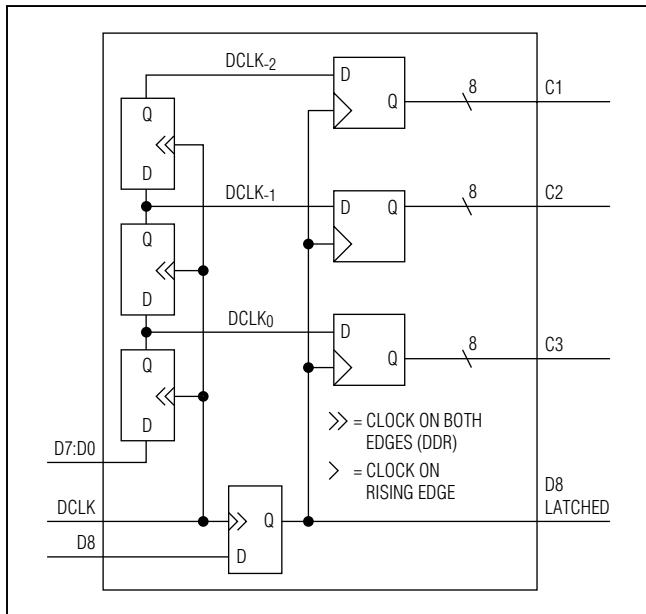

| 図8. ビデオデマルチプレクサC . . . . .                       | 23 |

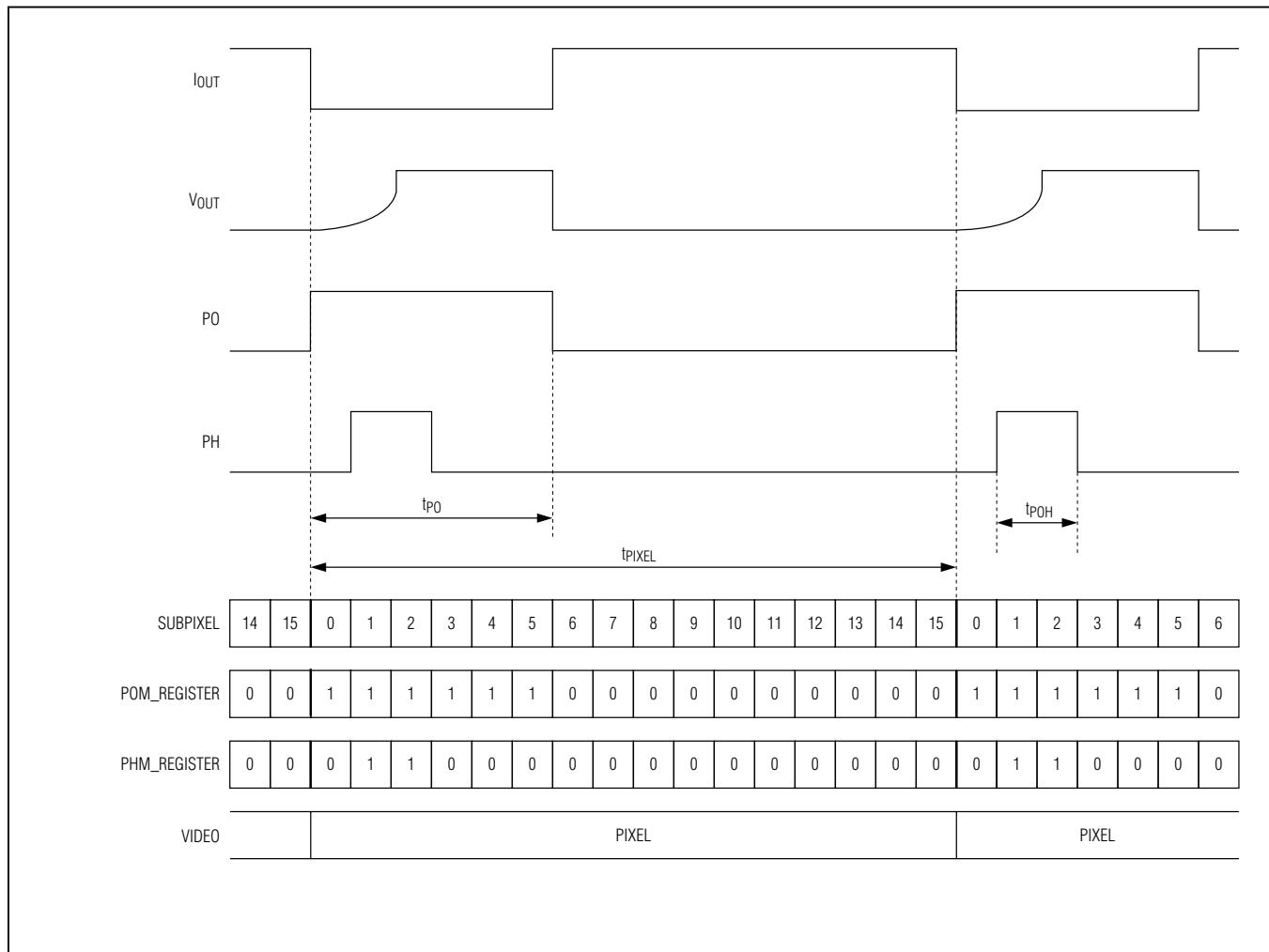

| 図9. パルスタイミングジェネレータ . . . . .                     | 24 |

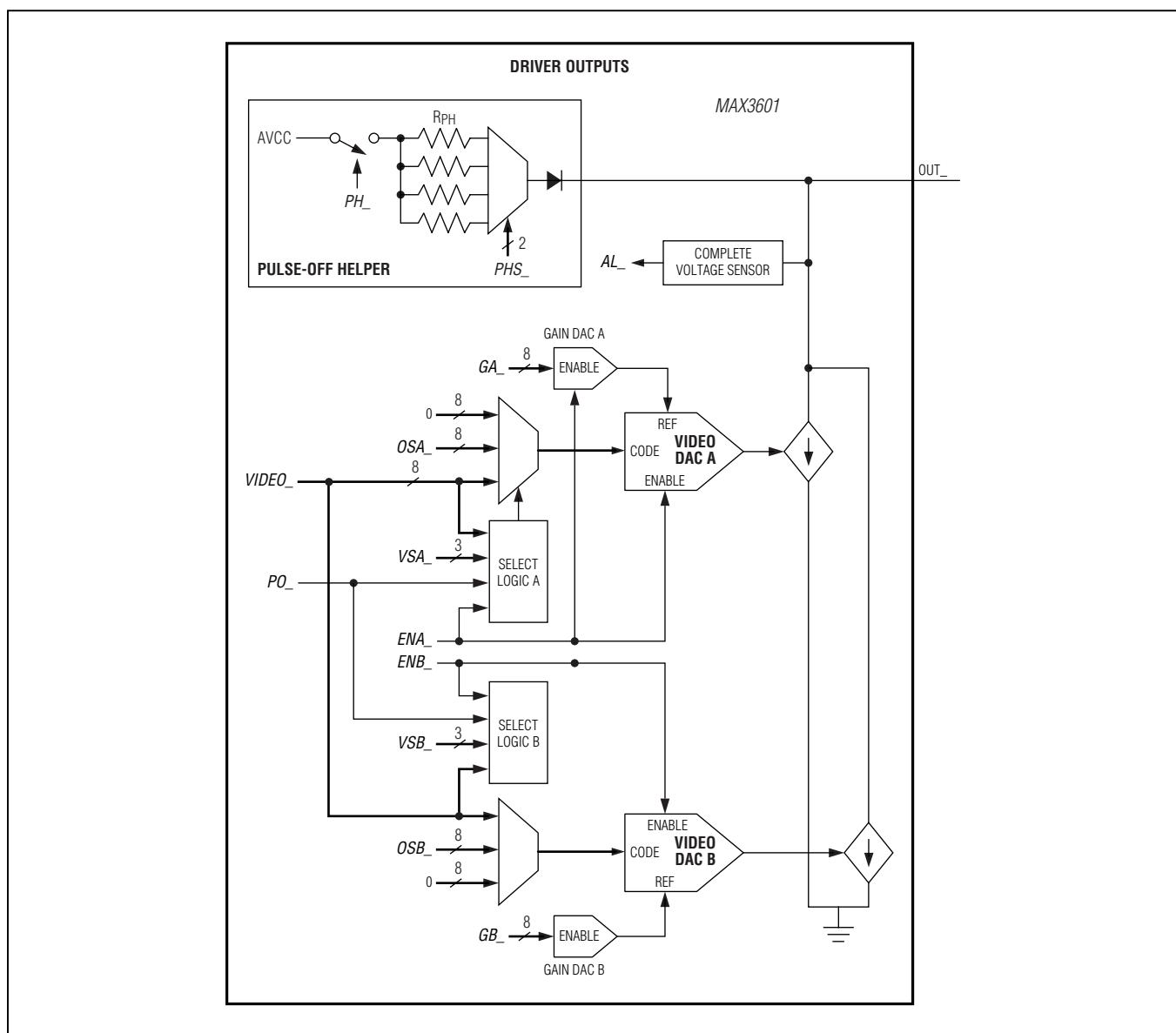

| 図10. ドライバ出力 . . . . .                            | 26 |

| 図11. ドライバ出力のフルスケール電流範囲 . . . . .                 | 27 |

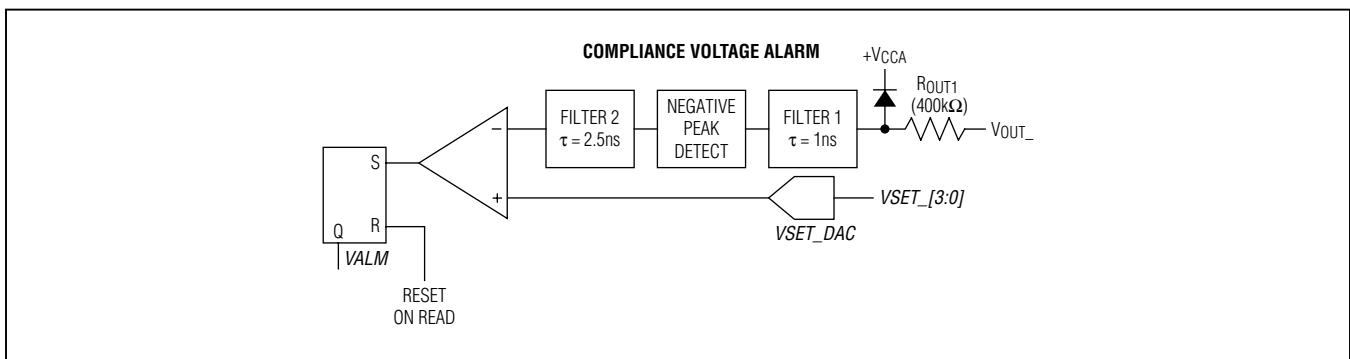

| 図12. 出力コンプライアンスセンサー . . . . .                    | 28 |

| 図13. コンプライアンスセンサーの使用例 . . . . .                  | 28 |

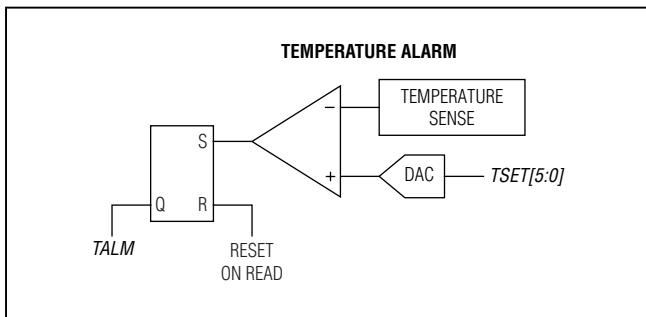

| 図14. 温度アラーム . . . . .                            | 29 |

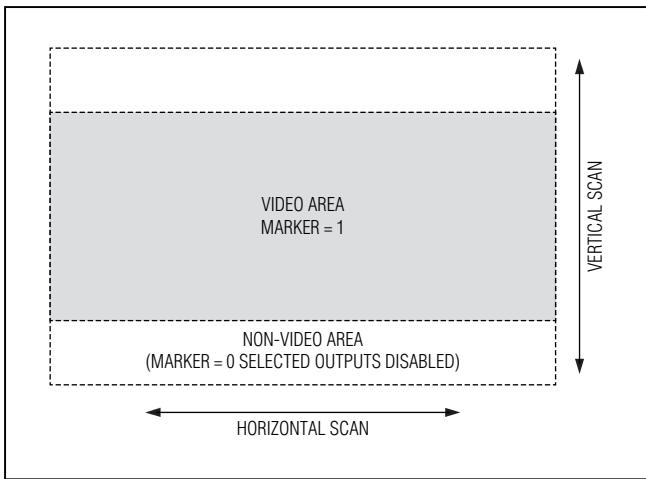

| 図15. ビデオマーカ . . . . .                            | 29 |

| 図16. I <sup>2</sup> Cのマスター/スレーブ構成 . . . . .      | 30 |

| 図17. I <sup>2</sup> Cのビット転送 . . . . .            | 30 |

| 図18. I <sup>2</sup> CのSTARTおよびSTOP条件 . . . . .   | 30 |

| 図19. I <sup>2</sup> Cのアクノリッジ . . . . .           | 31 |

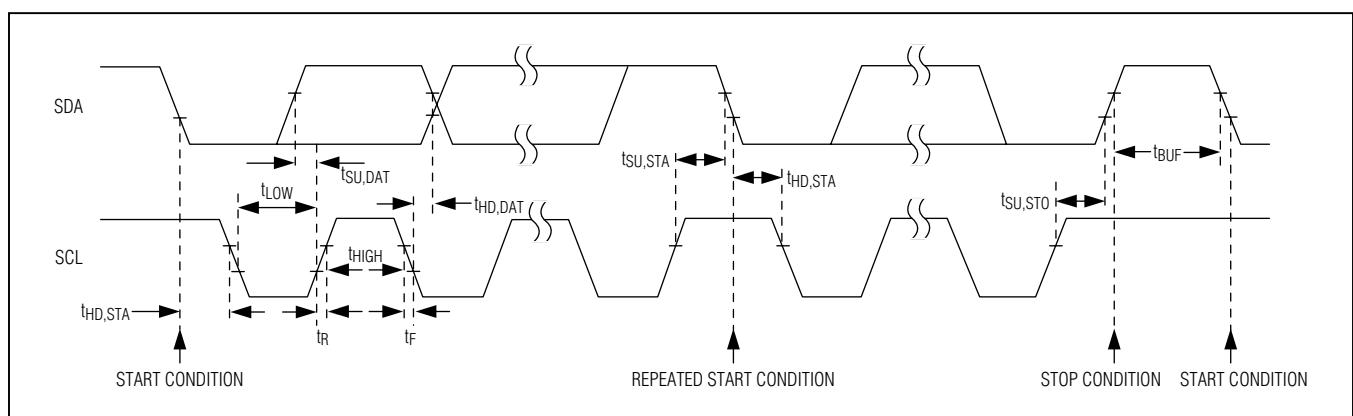

| 図20. I <sup>2</sup> Cのタイミング図 . . . . .           | 31 |

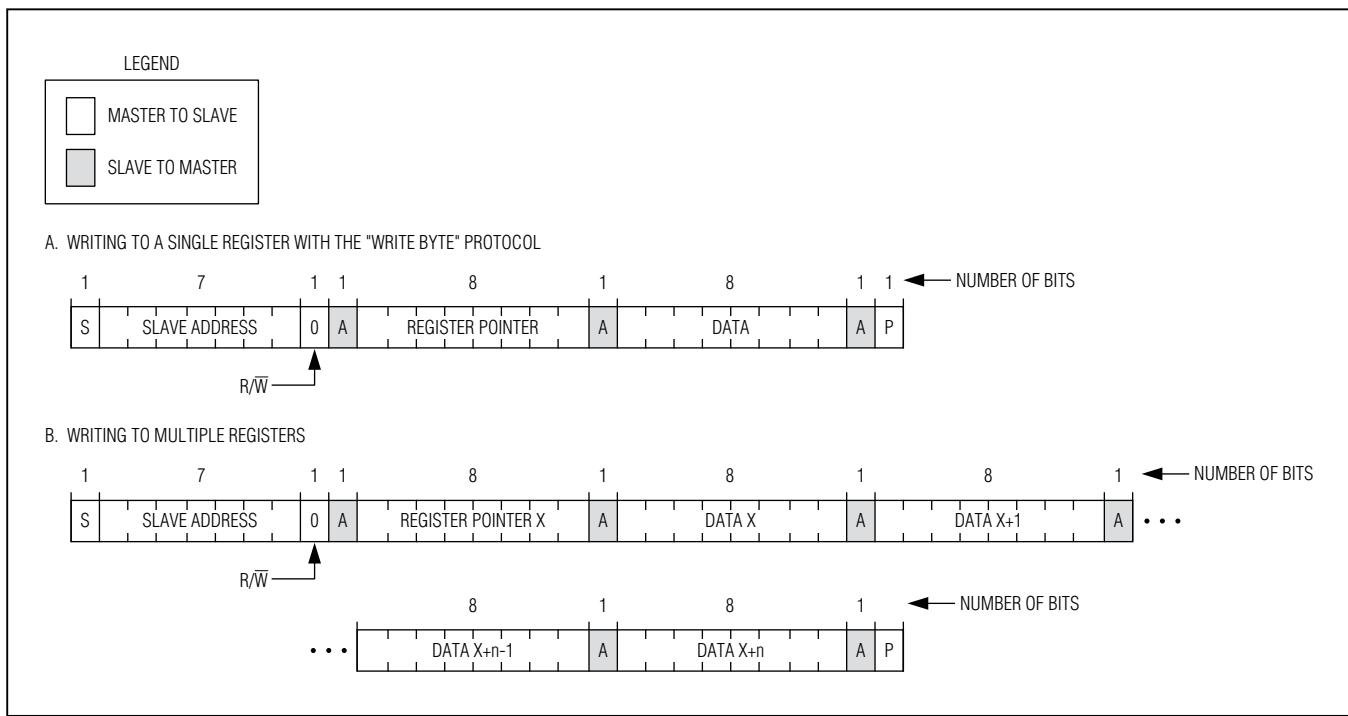

| 図21. I <sup>2</sup> Cの書き込み . . . . .             | 32 |

| 図22. I <sup>2</sup> Cの読み取り . . . . .             | 33 |

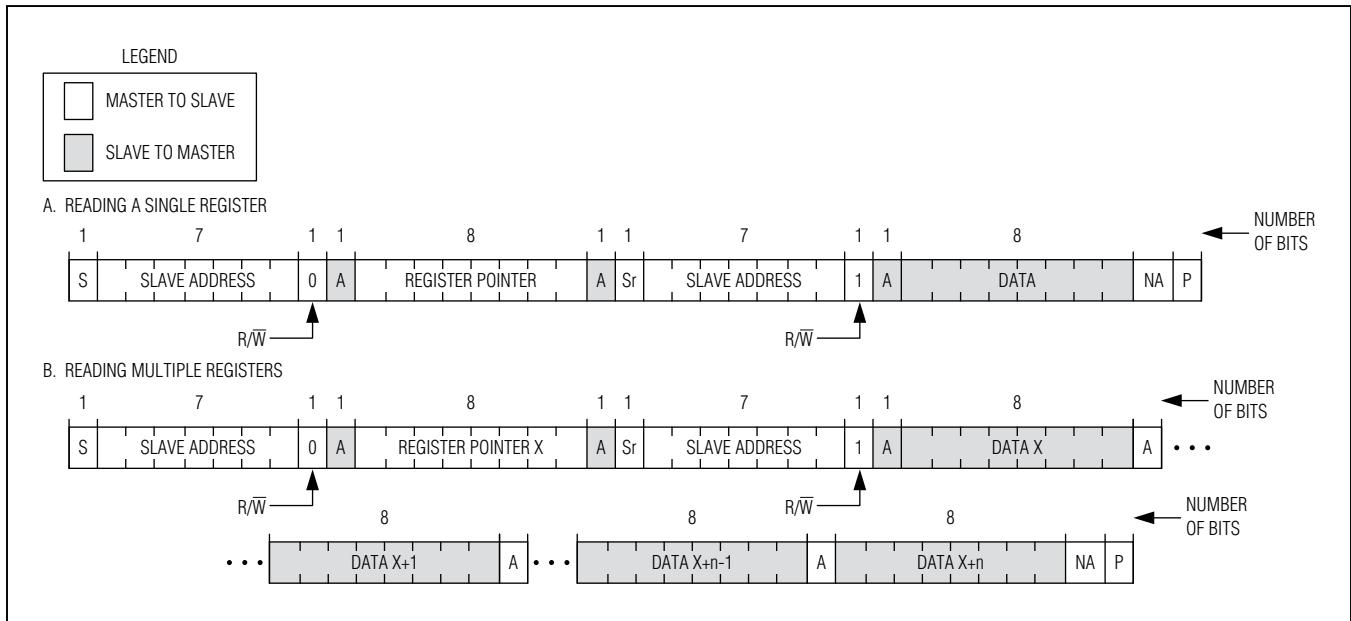

| 図23. SPIモードにするためのAVDD、DVDD、およびCSのタイミング . . . . . | 34 |

| 図24. SPIのタイミング . . . . .                         | 34 |

| 図25. SPIの書き込みタイミング . . . . .                     | 35 |

| 図26. SPIの読み取りタイミング . . . . .                     | 35 |

| 図27. 電源シーケンシング . . . . .                         | 39 |

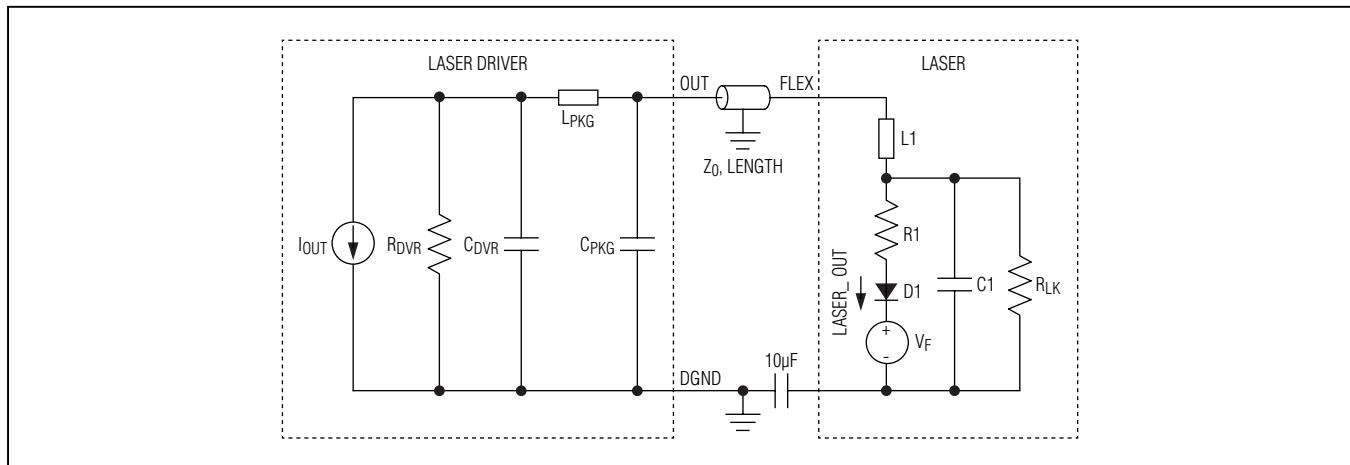

| 図28. レーザとパッケージのモデル . . . . .                     | 39 |

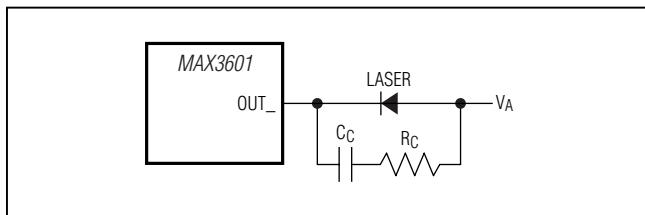

| 図29. オプションの補償部品 . . . . .                        | 40 |

## レーザドライバ、プロジェクト用

---

### 表リスト

---

|                                                 |    |

|-------------------------------------------------|----|

| 表1. サブピクセル設定(SPレジスタ) . . . . .                  | 25 |

| 表2. パルスオフデューティサイクル(POC_レジスタ) . . . . .          | 25 |

| 表3. ランダムパルスオフの設定 . . . . .                      | 25 |

| 表4. DAC Aのビデオ選択ロジック . . . . .                   | 27 |

| 表5. DAC Bのビデオ選択ロジック . . . . .                   | 27 |

| 表6. コンプライアンスアラームのセットポイント . . . . .              | 28 |

| 表7. ビデオデマルチプレクサ選択ロジック . . . . .                 | 29 |

| 表8. レジスタ表. . . . .                              | 36 |

| 表9. 標準的なレーザダイオードのパラメータ . . . . .                | 39 |

| 表10. 詳細レジスタ表( <a href="#">表8</a> を参照) . . . . . | 41 |

## レーザドライバ、プロジェクト用

## ABSOLUTE MAXIMUM RATINGS

|                                                                      |                                                            |                                                                                                        |

|----------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| AVDD to AGND .....                                                   | -0.3V to +2.2V                                             | D0–D11, DCLK, SCL, SDA,                                                                                |

| DVDD to DGND .....                                                   | -0.3V to +2.2V                                             | CS, EN_MAIN, MARKER Current .....                                                                      |

| AVCC to AGND .....                                                   | -0.3V to +4.0V                                             | -50mA to +50mA                                                                                         |

| DVCC to DGND .....                                                   | -0.3V to +4.0V                                             | Continuous Power Dissipation                                                                           |

| AVDD to DVDD .....                                                   | -0.3V to +0.3V                                             | TQFN ( $T_A = +85^\circ\text{C}$ , derate 35.7mW/ $^\circ\text{C}$ above $+85^\circ\text{C}$ )..2320mW |

| AVCC to DVCC .....                                                   | -0.3V to +0.3V                                             | WLP ( $T_A = +70^\circ\text{C}$ , derate 28.5mW/ $^\circ\text{C}$ above $+70^\circ\text{C}$ )..2200mW  |

| AGND to DGND .....                                                   | -0.3V to +0.3V                                             | Junction Temperature .....                                                                             |

| OUT_ to DGND .....                                                   | -0.3V to +7.5V                                             | +150°C                                                                                                 |

| OUT_ Current                                                         |                                                            | Operating Temperature Range                                                                            |

| Continuous.....                                                      | 400mA                                                      | TQFN .....                                                                                             |

| Peak ( $t < 1\mu\text{s}$ ).....                                     | 800mA                                                      | WLP .....                                                                                              |

| D0–D11, DCLK, TESTC to DGND .....                                    | -0.3V to lower of +2.2V or<br>( $V_{DVDD} + 0.3\text{V}$ ) | Storage Temperature Range..... -55°C to +150°C                                                         |

| CLK/SCL, DIO/SDA, CS, EN_MAIN, MARKER,<br>TESTA, TESTB to DGND ..... | -0.3V to lower of +4.0V or<br>( $V_{DVCC} + 0.3\text{V}$ ) | Lead Temperature (soldering, 10s; TQFN only) .....                                                     |

|                                                                      |                                                            | +300°C                                                                                                 |

|                                                                      |                                                            | Soldering Temperature (reflow) .....                                                                   |

|                                                                      |                                                            | +260°C                                                                                                 |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## PACKAGE THERMAL CHARACTERISTICS (Note 1)

## TQFN

Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) .....2°C/W

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) .....28°C/W

## WLP

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) .....36°C/W

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to [japan.maximintegrated.com/thermal-tutorial](http://japan.maximintegrated.com/thermal-tutorial).

## ELECTRICAL CHARACTERISTICS

( $V_{AVDD} = V_{DVDD} = 1.7\text{V}$  to  $1.9\text{V}$ ,  $V_{AVCC} = V_{DVCC} = 2.9\text{V}$  to  $3.5\text{V}$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ ,  $T_J < +125^\circ\text{C}$ , EN\_MAIN and MARKER high,  $V_{OUT} \geq 0.7\text{V}$ , unless otherwise noted. Typical values are at  $V_{AVDD} = V_{DVDD} = 1.8\text{V}$ ,  $V_{AVCC} = V_{DVCC} = 3.3\text{V}$ ,  $T_J = +85^\circ\text{C}$ . Consumer grade parts are tested at  $T_A = +70^\circ\text{C}$ . Automotive grade parts are tested at  $T_A = +105^\circ\text{C}$ . Minimum and maximum specifications are guaranteed by design, characterization and/or production test.)(Note 2)

| PARAMETER                              | SYMBOL          | CONDITIONS                                                                              | MIN  | TYP    | MAX | UNITS                                               |

|----------------------------------------|-----------------|-----------------------------------------------------------------------------------------|------|--------|-----|-----------------------------------------------------|

| <b>OPERATING CONDITIONS</b>            |                 |                                                                                         |      |        |     |                                                     |

| Output Voltage                         | $V_{OUT}$       | Output enabled                                                                          | 0.5  | 0.6    | 7.5 | V                                                   |

| <b>POWER SUPPLY (Note 3, Figure 4)</b> |                 |                                                                                         |      |        |     |                                                     |

| +1.8V Supply Current                   | $I_{AVDD\_DIS}$ | EN_MAIN low or SP_EN = 1                                                                | 0.01 | (1)    |     | $\mu\text{A}$                                       |

|                                        | $I_{AVDD}$      | SP_EN High                                                                              | 5    | 7      |     | mA                                                  |

|                                        | $I_{DVDD1}$     | SP_EN = 0                                                                               | 0.02 | (0.03) |     | mA/MHz                                              |

|                                        |                 | SP_EN = 1, $f_{PO} = 75\text{MHz}$                                                      | 0.1  | (0.2)  |     |                                                     |

|                                        | $I_{DVDD\_G1A}$ | Video dependency DAC A                                                                  | 1.1  | (1.5)  |     | $\mu\text{A}/(\text{MHz} \times \Delta\text{CODE})$ |

|                                        | $I_{DVDD\_G1B}$ | Video dependency DAC B                                                                  | 0.5  | (0.6)  |     |                                                     |

|                                        | $I_{DVDD}$      | Maximum digital supply current<br>$f_{PIXEL} = 150\text{MHz}$ , $f_{PO} = 75\text{MHz}$ |      | (45)   |     | mA                                                  |

## レーザドライバ、プロジェクト用

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{AVDD} = V_{DVDD} = 1.7V$  to  $1.9V$ ,  $V_{AVCC} = V_{DVCC} = 2.9V$  to  $3.5V$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ ,  $T_J < +125^\circ C$ , EN\_MAIN and MARKER high,  $V_{OUT} \geq 0.7V$ , unless otherwise noted. Typical values are at  $V_{AVDD} = V_{DVDD} = 1.8V$ ,  $V_{AVCC} = V_{DVCC} = 3.3V$ ,  $T_J = +85^\circ C$ . Consumer grade parts are tested at  $T_A = +70^\circ C$ . Automotive grade parts are tested at  $T_A = +105^\circ C$ . Minimum and maximum specifications are guaranteed by design, characterization and/or production test.)(Note 2)

| PARAMETER                                                 | SYMBOL          | CONDITIONS                                                                                        | MIN      | TYP   | MAX    | UNITS       |

|-----------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------|----------|-------|--------|-------------|

| +3.3V Supply Current                                      | $I_{AVCC}$      | Core analog                                                                                       | 1.5      | 1.8   |        | mA          |

|                                                           | $I_{DVCC\_DIS}$ | $ENA_ = ENB_ = 0$                                                                                 | 0.01     | 0.1   |        |             |

|                                                           | $I_{DVCC\_G1A}$ | $GA_ = 0x00$ (per channel)                                                                        | 3.4      | 4.8   |        |             |

|                                                           | $I_{DVCC\_G2A}$ | $GA_ = 0xFF$ (per channel)                                                                        | 8.2      | 9.1   |        |             |

|                                                           | $I_{DVCC\_G1B}$ | $GB_ = 0x00$ (per channel)                                                                        | 1.2      | 1.6   |        |             |

|                                                           | $I_{DVCC\_G2B}$ | $GB_ = 0xFF$ (per channel)                                                                        | MAX3601C | 2.5   | 2.8    |             |

|                                                           |                 |                                                                                                   | MAX3601G | 2.5   | 3.3    |             |

|                                                           | $I_{AVCC}$      | Maximum analog supply current $GA_ = GB_ = 0xFF$ , $ENA_ = ENB_ = 1$                              | MAX3601C |       | (37.6) |             |

|                                                           |                 |                                                                                                   | MAX3601G |       | (39.1) |             |

| Pulse-Off Assist Current (Note 4)                         | $I_{CCD\_G1}$   | $PHS_ = 0$                                                                                        | 5        | (10)  |        | $\mu A/MHz$ |

|                                                           | $I_{CCD\_G2}$   | $f_{PO} = f_{POH} = 75MHz$ , $f_{PIXEL} = 150MHz$ , $C_L = 0pF$ , $V_{OUT\_MIN} = 0.8V$ to $1.8V$ | 2.3      | (4.6) |        |             |

| Power In MAX3601 Driver (Note 5)                          |                 | Outputs off, clock stopped                                                                        | 0.2      |       |        | mW          |

|                                                           |                 | 0% video                                                                                          | < 83     | (100) |        |             |

|                                                           |                 | 27% video                                                                                         | 130      |       |        |             |

|                                                           |                 | 100% video                                                                                        | 270      |       |        |             |

|                                                           |                 | 27% video with pulse-off                                                                          | 150      |       |        |             |

|                                                           |                 | 27% video with pulse-off assist                                                                   | 160      |       |        |             |

| Typical Output Sensitivity to Supply Voltage (Note 6)     |                 | $I_{OUT}/V_{AVDD}$                                                                                | 1        |       |        | %/ $V$      |

|                                                           |                 | $I_{OUT}/V_{DVDD}$                                                                                | 1        | (3)   |        |             |

|                                                           |                 | $I_{OUT}/V_{AVCC}$                                                                                | 2        | (17)  |        |             |

|                                                           |                 | $I_{OUT}/V_{DVCC}$                                                                                | 2.2      | (6)   |        |             |

| <b>VIDEO DAC (8-Bit, Note 7)</b>                          |                 |                                                                                                   |          |       |        |             |

| Maximum Conversion Rate                                   |                 |                                                                                                   | 150      | 160   | (250)  | Msps        |

| Settling Time                                             | $t_S$           | Within 12 LSBs ( $GAIN = 0x0F$ to $0xFF$ )                                                        | 6.7      | (12)  |        | ns          |

|                                                           |                 | Within 3 LSBs ( $GAIN = 0xFF$ )                                                                   | 12       | (25)  |        |             |

|                                                           |                 | Within 1 LSB ( $GAIN = 0xFF$ )                                                                    | 23       | (34)  |        |             |

| Rise/Fall Time                                            |                 | 20% to 80%                                                                                        | 1.5      | (2.5) |        | ns          |

| Offset Error ( $GSA_ = GSB_ = 0xFF$ , $ENA_ = ENB_ = 1$ ) | $OS\_ER$        | $0V \leq V_{OUT} \leq V_{AVCC} + 0.5V$                                                            | 1.0      | 24    |        | $\mu A$     |

|                                                           |                 | $V_{OUT} = 7.5V$                                                                                  | (1.0)    | 10.5  | 37     |             |

| Resistor R <sub>OUT1</sub>                                | $R_{OUT1}$      | $V_{OUT} = 7.5V$ , see Figure 12                                                                  | (290)    | 400   | (490)  | $k\Omega$   |

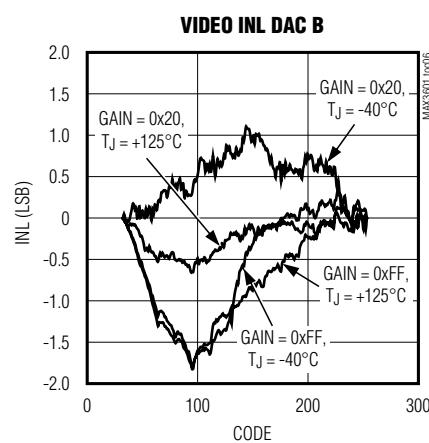

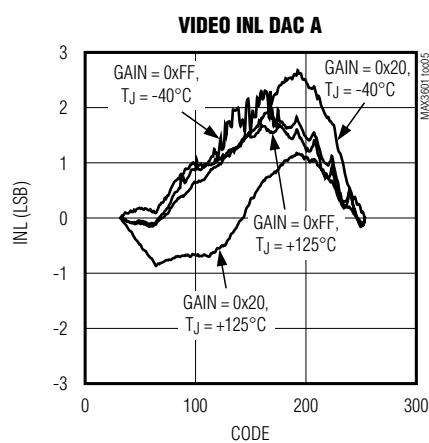

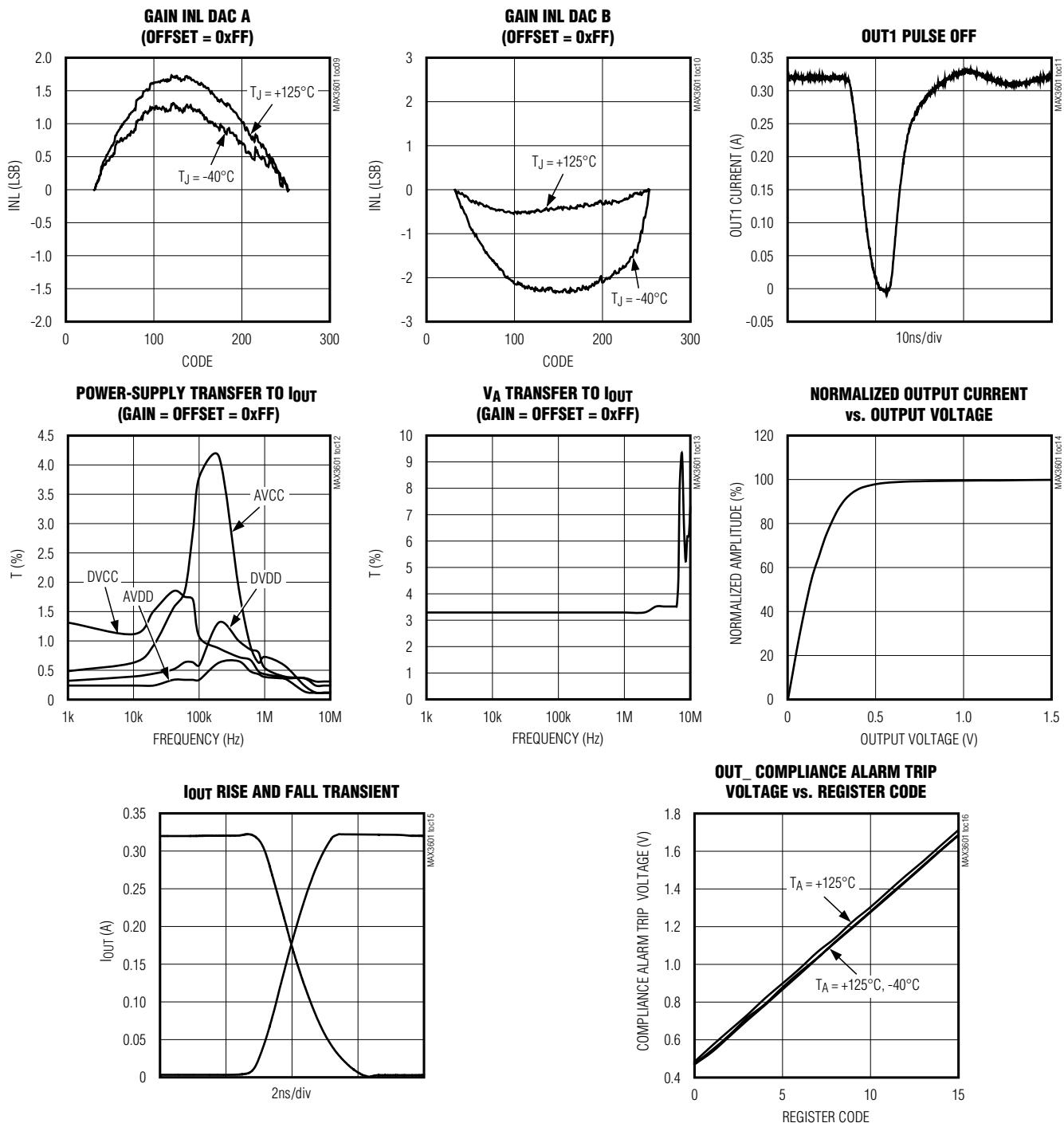

| Video INL (Notes 8 and 9)                                 |                 | Code > $0x1F$                                                                                     | (-15)    |       | (15)   | LSB         |

| INL Drift (Notes 8 and 9)                                 |                 | $0x1F < GAIN < 0xFF$ , $0^\circ C < T_J < +125^\circ C$<br>$V_{OUT\_MIN} = 0.6V$ to $1.6V$        | 1.5      | (3)   |        | LSB         |

## レーザドライバ、プロジェクト用

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{AVDD} = V_{DVDD} = 1.7V$  to  $1.9V$ ,  $V_{AVCC} = V_{DVCC} = 2.9V$  to  $3.5V$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ ,  $T_J < +125^\circ C$ , EN\_MAIN and MARKER high,  $V_{OUT} \geq 0.7V$ , unless otherwise noted. Typical values are at  $V_{AVDD} = V_{DVDD} = 1.8V$ ,  $V_{AVCC} = V_{DVCC} = 3.3V$ ,  $T_J = +85^\circ C$ . Consumer grade parts are tested at  $T_A = +70^\circ C$ . Automotive grade parts are tested at  $T_A = +105^\circ C$ . Minimum and maximum specifications are guaranteed by design, characterization and/or production test.)(Note 2)

| PARAMETER                                   | SYMBOL       | CONDITIONS                                                                        | MIN                                             | TYP   | MAX    | UNITS        |

|---------------------------------------------|--------------|-----------------------------------------------------------------------------------|-------------------------------------------------|-------|--------|--------------|

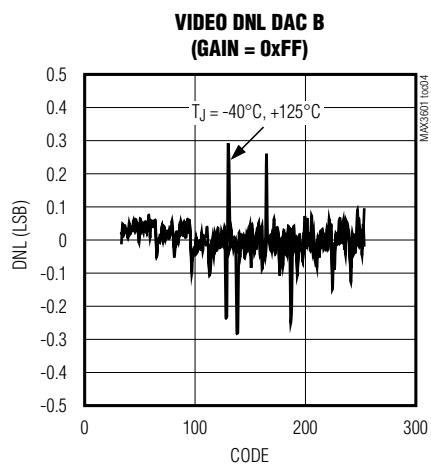

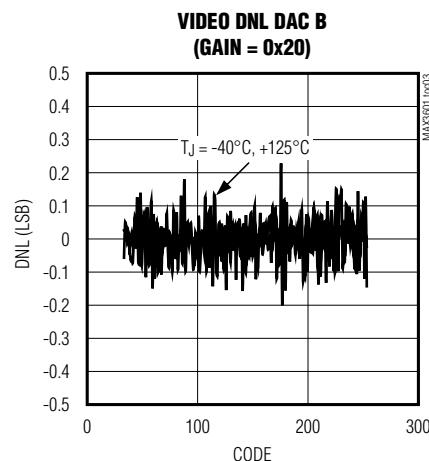

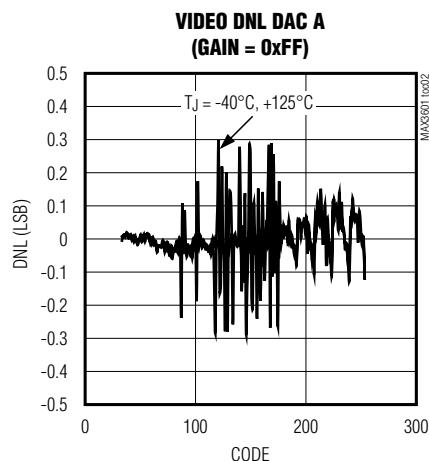

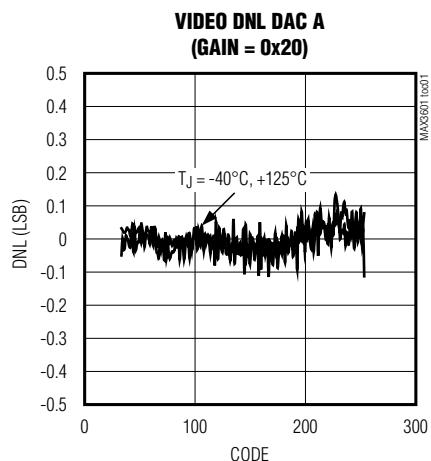

| Video DNL (GAIN = 0x0F to 0xFF) (Note 8)    |              | Guaranteed monotonic                                                              | (-1)                                            |       | (+1)   | LSB          |

| Propagation Delay (Delay = PD1 + PD2)       |              | PD1                                                                               |                                                 | 2     |        | Pixel clocks |

|                                             |              | PD2                                                                               |                                                 | 11    |        | ns           |

| Propagation Delay Variation                 |              |                                                                                   | (-1)                                            |       | (+1)   | ns           |

| Transfer of $V_{OUT}$ to $I_{OUT}$ (Note 5) |              | $f < 50\text{kHz}$ , $V_{OUT} > 0.9V$                                             | 0.2                                             | (1)   |        | %/ $V$       |

|                                             |              | $f < 1\text{MHz}$ , $V_{OUT} > 0.6V$                                              | 6                                               | (10)  |        |              |

|                                             |              | $f < 1\text{MHz}$ , $V_{OUT} > 0.5V$                                              | 12                                              | (15)  |        |              |

| Output Capacitance (CODE_A = CODE_B = 0x00) | $C_{DVR}$    | $V_{OUT} = 0.6V$                                                                  | 260                                             |       |        | pF           |

|                                             |              | $V_{OUT} = 1.1V$                                                                  | 125                                             |       |        |              |

|                                             |              | $V_{OUT} = 2.0V$                                                                  | 100                                             |       |        |              |

| <b>PULSE OFF ASSIST</b>                     |              |                                                                                   |                                                 |       |        |              |

| Rise Time                                   |              | 20% to 80%, $V_{A\_} = 1.0V$ , $C_L = 0\text{pF}$ ,<br>$PHS\_ = 3$ , VIDEO = 0x00 | 1.6                                             | (3)   |        | ns           |

| Incremental Resistance<br>$PH\_ = 0xFFFF$   |              | PHS_ = 3,                                                                         | 8                                               |       |        | $\Omega$     |

|                                             |              | PHS_ = 2                                                                          | 16                                              |       |        |              |

|                                             |              | PHS_ = 1                                                                          | 32                                              |       |        |              |

|                                             |              | PHS_ = 0                                                                          | 64                                              |       |        |              |

| Compliance Voltage                          | $V_{O\_POH}$ | Relative to $V_{AVCC}$ , $I_{OUT} = 1\text{mA}$ ( $T_A = 0$ to $+125^\circ C$ )   |                                                 |       | (-0.8) | V            |

|                                             |              | $T_A = -40^\circ C$ to $+125^\circ C$                                             |                                                 |       | (-0.9) |              |

| <b>OUTPUT GAIN (VIDEO_ = 0xFF)</b>          |              |                                                                                   |                                                 |       |        |              |

| Resolution                                  |              |                                                                                   |                                                 | 8     |        | Bits         |

| Current at OUT                              |              | GA_ = 0x00, GB_ = 0x00                                                            | 0.01                                            | (1)   |        | mA           |

|                                             |              | GA_ = 0xFF,<br>GB_ = 0x00                                                         | MAX3601C                                        | 280   | 320    | 400          |

|                                             |              |                                                                                   | MAX3601G, $T_A = +25^\circ C$ to $+105^\circ C$ | 275   | 320    | 400          |

|                                             |              | GA_ = 0x00,<br>GB_ = 0xFF                                                         | MAX3601G, $T_A < +25^\circ C$                   | 260   | 320    | 400          |

|                                             |              |                                                                                   | MAX3601C                                        | 69    | 80     | 100          |

|                                             |              |                                                                                   | MAX3601G, $T_A = +25^\circ C$ to $+105^\circ C$ | 68    | 80     | 100          |

|                                             |              | GA_ = 0xFF,<br>GB_ = 0xFF                                                         | MAX3601G, $T_A < +25^\circ C$                   | 60    | 80     | 100          |

|                                             |              |                                                                                   | MAX3601C                                        | (349) | 400    | (500)        |

|                                             |              |                                                                                   | MAX3601G                                        | (320) | 400    | (500)        |

## レーザドライバ、プロジェクト用

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{AVDD} = V_{DVDD} = 1.7V$  to  $1.9V$ ,  $V_{AVCC} = V_{DVCC} = 2.9V$  to  $3.5V$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ ,  $T_J < +125^\circ C$ , EN\_MAIN and MARKER high,  $V_{OUT} \geq 0.7V$ , unless otherwise noted. Typical values are at  $V_{AVDD} = V_{DVDD} = 1.8V$ ,  $V_{AVCC} = V_{DVCC} = 3.3V$ ,  $T_J = +85^\circ C$ . Consumer grade parts are tested at  $T_A = +70^\circ C$ . Automotive grade parts are tested at  $T_A = +105^\circ C$ . Minimum and maximum specifications are guaranteed by design, characterization and/or production test.)(Note 2)

| PARAMETER                                                | SYMBOL          | CONDITIONS                             | MIN      | TYP                          | MAX    | UNITS  |

|----------------------------------------------------------|-----------------|----------------------------------------|----------|------------------------------|--------|--------|

| <b>COMPLIANCE ALARM</b>                                  |                 |                                        |          |                              |        |        |

| VSET DAC Resolution                                      |                 | 4 bit                                  | (70)     | 80                           | (90)   | mV     |

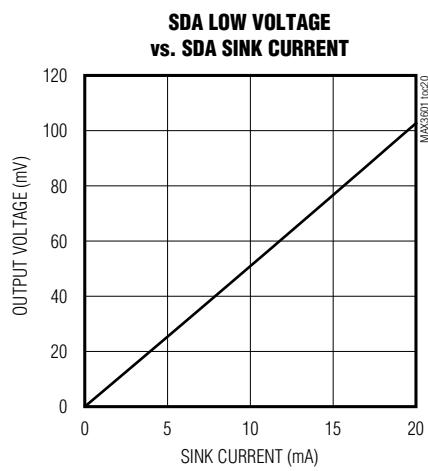

| VSET DAC Range                                           |                 | VSET_ = 0x0                            | 0.32     | 0.4                          | 0.48   | V      |

|                                                          |                 | VSET_ = 0xF                            | 1.4      | 1.6                          | 1.8    |        |

| Filter 1 Time Constant                                   |                 |                                        |          | 1                            |        | ns     |

| Filter 2 Time Constant                                   |                 |                                        |          | 2.7                          |        | ns     |

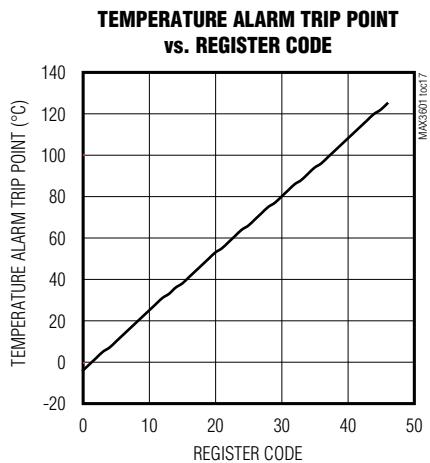

| <b>TEMPERATURE ALARM</b>                                 |                 |                                        |          |                              |        |        |

| Temperature Range                                        |                 |                                        | (5)      | (150)                        |        | °C     |

| Temperature Accuracy                                     |                 | $T_J = +20^\circ C$ to $+125^\circ C$  | (-10)    | (10)                         |        | °C     |

| Temperature Resolution                                   |                 | $T_J = +20^\circ C$ to $+125^\circ C$  | (2.25)   | 2.5                          | (2.75) | °C/LSB |

| <b>LOGIC I/O (DIO/SDA, CLK/SCL, CS, MARKER, EN_MAIN)</b> |                 |                                        |          |                              |        |        |

| Input Low Voltage                                        | $V_{IL2}$       | Test condition                         |          | 0.4                          |        | V      |

| Input High Voltage                                       | $V_{IH2}$       | Test condition                         | 1.45     |                              |        | V      |

| Input High Threshold                                     |                 | Relative to $V_{DVDD}$                 | (50)     | 60                           | (70)   | %      |

| Input Low Threshold                                      |                 | Relative to $V_{DVDD}$                 | (40)     | 50                           | (60)   | %      |

| Input Hysteresis                                         |                 | Relative to $V_{DVDD}$                 | (5)      |                              |        | %      |

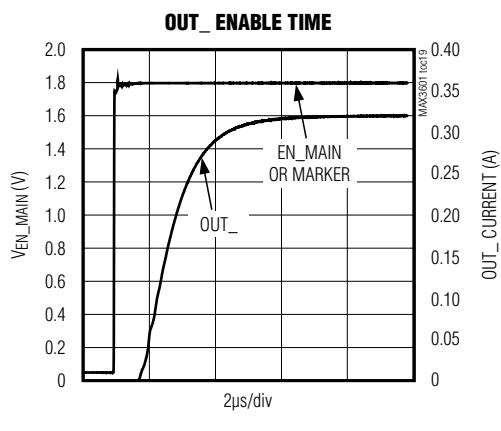

| Input Current                                            |                 | DIO/SDA, CLK/SCL                       | -10      | $\pm 0.2$                    | +10    | µA     |

| Input Resistance                                         | $R_{EN\_MAIN}$  | EN_MAIN to DGND                        | 50       | 100                          | 200    | kΩ     |

|                                                          | $R_{MARKER}$    | MARKER to DVDD                         | 50       | 100                          | 200    |        |

|                                                          | $R_{CS}$        | CS to DGND                             | 50       | 100                          | 200    |        |

| Input Capacitance                                        |                 |                                        |          | 1                            |        | pF     |

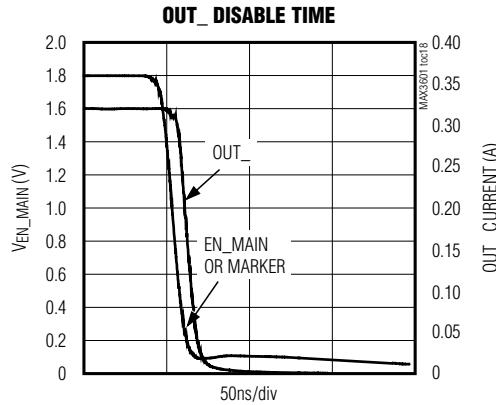

| Disable Time                                             | $t_{DIS}$       | EN_MAIN or MARKER to $I_{OUT}$ falling | 0.1      | 1                            |        | µs     |

| Enable Settling Time Constant                            | $t_{EN}$        | EN_MAIN rising or MARKER rising        | 0.5      | 1.5                          |        | µs     |

| DIO/SDA Low Voltage                                      |                 | $I_{DIO/SDA} = 16mA$                   | 0.1      | 0.4                          |        | V      |

| <b>VIDEO DATA INPUTS</b>                                 |                 |                                        |          |                              |        |        |

| Maximum Frequency                                        | $f_{DCLK\_MAX}$ |                                        | 150      | > 160                        |        | MHz    |

| DCLK Duty Cycle                                          |                 | $f_{DCLK} > 100MHz$                    | (45)     | (55)                         |        | %      |

| DCLK High Time                                           |                 | Relative to $2/f_{DCLK}$               | (-0.5)   | (+0.5)                       |        | ns     |

| Video Input Setup Time                                   | $t_{SU}$        | Operating condition                    | 1        |                              |        | ns     |

| Video Input Hold Time                                    | $t_H$           | Operating condition                    | MAX3601C | 0.25                         |        | ns     |

|                                                          |                 |                                        | MAX3601G | 0.35                         |        |        |

| Input Switching Time                                     |                 | 10% to 90%, operating condition        |          | 1.2                          |        | ns     |

| Input Low Voltage                                        | $V_{IN-L}$      |                                        |          | 0.5 x<br>$V_{DVDD}$<br>- 0.1 |        | V      |

## レーザドライバ、プロジェクタ用

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{AVDD} = V_{DVDD} = 1.7V$  to  $1.9V$ ,  $V_{AVCC} = V_{DVCC} = 2.9V$  to  $3.5V$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ ,  $T_J < +125^\circ C$ , EN\_MAIN and MARKER high,  $V_{OUT} \geq 0.7V$ , unless otherwise noted. Typical values are at  $V_{AVDD} = V_{DVDD} = 1.8V$ ,  $V_{AVCC} = V_{DVCC} = 3.3V$ ,  $T_J = +85^\circ C$ . Consumer grade parts are tested at  $T_A = +70^\circ C$ . Automotive grade parts are tested at  $T_A = +105^\circ C$ . Minimum and maximum specifications are guaranteed by design, characterization and/or production test.)(Note 2)

| PARAMETER                            | SYMBOL        | CONDITIONS                | MIN                          | TYP      | MAX    | UNITS |

|--------------------------------------|---------------|---------------------------|------------------------------|----------|--------|-------|

| Input High Voltage                   | $V_{IN-H}$    |                           | 0.5 x<br>$V_{DVDD}$<br>+ 0.1 |          |        | V     |

| Input Threshold                      |               | Relative to $V_{DVDD}$    |                              | 50       |        | %     |

| Input Hysteresis                     |               |                           |                              | 0.1      |        | V     |

| Input Current                        |               |                           | -10                          | $<\pm 1$ | +10    |       |

| Data Input Capacitance               | $C_D$         |                           |                              | 1        |        | pF    |

| <b>SUBPIXEL GENERATOR</b>            |               |                           |                              |          |        |       |

| Pixel Clock Frequency Range          |               | Subpixel generator active | 24                           | 150      | (250)  | MHz   |

| Minimum Pulse Width                  |               | 1 subpixel                |                              |          | (2)    | ns    |

| Subpixel Timing Accuracy             |               | $T_{PODM} - T_{POD}$      | (-1)                         |          | (+1)   | ns    |

| PLL Bandwidth                        |               |                           | (1200)                       | 2000     | (3100) | kHz   |

| <b>I<sup>2</sup>C TIMING</b>         |               |                           |                              |          |        |       |

| Clock Frequency                      | $f_{SCL}$     |                           |                              | 400      |        | kHz   |

| Bus Free Time Between START and STOP | $t_{BUF}$     |                           |                              | 1.3      |        | μs    |

| HOLD Time for a START Condition      | $t_{HD\_STA}$ |                           |                              | 0.6      |        | μs    |

| Setup Time Repeated START Condition  | $t_{SU\_STA}$ |                           |                              | 0.6      |        | μs    |

| SCL Low Time                         | $t_{LOW}$     |                           |                              | 1.3      |        | μs    |

| SCL High Time                        | $t_{HIGH}$    |                           |                              | 0.6      |        | μs    |

| SDA Hold Time                        | $t_{HD\_DAT}$ |                           | 0                            | 0.6      |        | μs    |

| SDA Setup Time                       | $t_{SU\_DAT}$ |                           |                              | 0.1      |        | μs    |

| Setup Time for STOP Condition        | $t_{SU\_STO}$ |                           |                              | 0.6      |        | μs    |

| Pulse Width of Suppressed Spikes     | $t_{SP}$      |                           |                              | 0.05     |        | μs    |

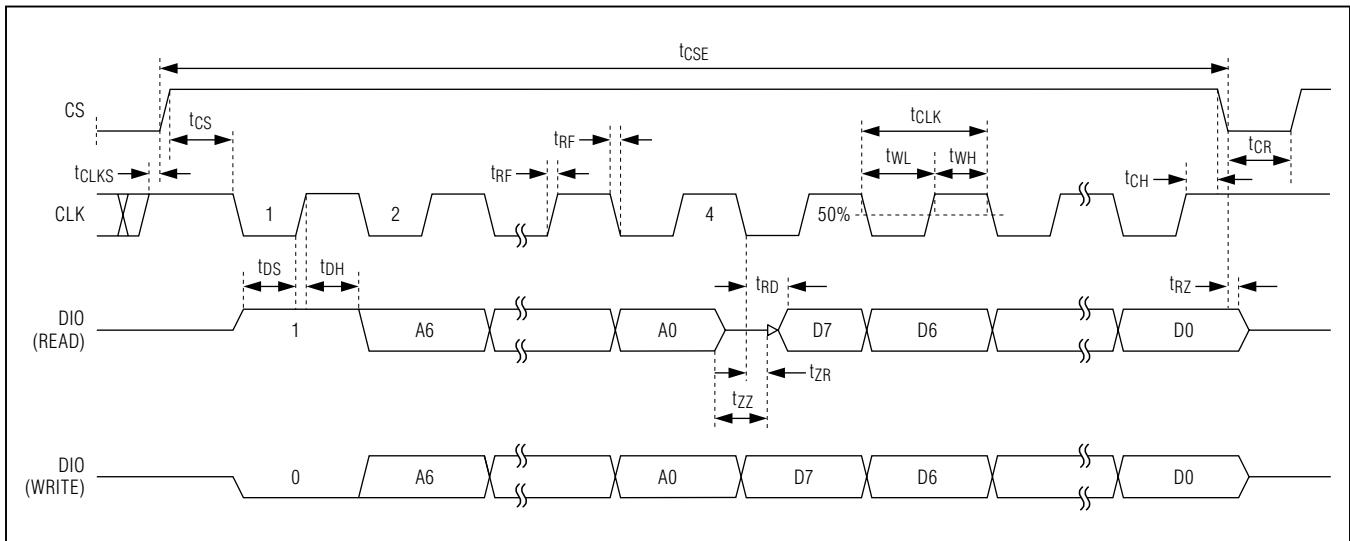

| <b>SPI TIMING</b>                    |               |                           |                              |          |        |       |

| SPI Clock Cycle                      | $t_{CLK}$     |                           | 83                           |          |        | ns    |

| SCL High Pulse Width                 | $t_{WH}$      |                           | 41.5                         |          |        | ns    |

| SCL Low Pulse Width                  | $t_{WL}$      |                           | 41.5                         |          |        | ns    |

| SCL Rise/Fall Time                   | $t_{RF}$      | At $f_{CLK} = 12MHz$      |                              | 16       |        | ns    |

| SCL Setup Time                       | $t_{CLKS}$    |                           | 8                            |          |        | ns    |

| CS Setup/Hold Time                   | $t_{CS}$      |                           | 32                           |          |        | ns    |

| CS Recovery Time                     | $t_{CR}$      |                           | 50                           |          |        | ns    |

## レーザドライバ、プロジェクト用

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{AVDD} = V_{DVDD} = 1.7V$  to  $1.9V$ ,  $V_{AVCC} = V_{DVCC} = 2.9V$  to  $3.5V$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ ,  $T_J < +125^\circ C$ , EN\_MAIN and MARKER high,  $V_{OUT} \geq 0.7V$ , unless otherwise noted. Typical values are at  $V_{AVDD} = V_{DVDD} = 1.8V$ ,  $V_{AVCC} = V_{DVCC} = 3.3V$ ,  $T_J = +85^\circ C$ . Consumer grade parts are tested at  $T_A = +70^\circ C$ . Automotive grade parts are tested at  $T_A = +105^\circ C$ . Minimum and maximum specifications are guaranteed by design, characterization and/or production test.)(Note 2)

| PARAMETER                          | SYMBOL   | CONDITIONS                               | MIN   | TYP  | MAX   | UNITS |

|------------------------------------|----------|------------------------------------------|-------|------|-------|-------|

| Write Data Setup Time              | $t_{DS}$ |                                          | 16    |      |       | ns    |

| Write Data Hold Time               | $t_{DH}$ |                                          | 16    |      |       | ns    |

| Read Data Delay Time               | $t_{RD}$ |                                          |       | 34   |       | ns    |

| DIO Output Switching Time          | $t_{ZR}$ | $R_{DIO} = 390\Omega$ , $C_{DIO} = 20pF$ |       | 11   | (16)  | ns    |

| DIO Output Disable Time            | $t_{RZ}$ | MAX3601C                                 |       | 34   |       | ns    |

|                                    |          | MAX3601G                                 |       | 36   |       |       |

| DIO Conflict Avoid Time            | $t_{ZZ}$ |                                          | 0     |      |       | ns    |

| <b>POWER-ON RESET (Figure 27)</b>  |          |                                          |       |      |       |       |

| $V_{AVDD}, V_{DVDD}$ On Threshold  | 2VPOR+   |                                          |       | 1.32 | (1.6) | V     |

| $V_{AVDD}, V_{DVDD}$ Off Threshold | 2VPOR-   |                                          | (1)   | 1.28 |       | V     |

| $V_{DVCC}, V_{DVCC}$ On Threshold  | 3VPOR+   |                                          |       | 2.5  | (2.8) | V     |

| $V_{AVCC}, V_{DVCC}$ Off Threshold | 3VPOR-   |                                          | (2.2) | 2.4  |       | V     |

**Note 2:** Parameters measured using circuit of [Figure 1](#).  $R_S$ ,  $C_S$ ,  $C_L$  = open, unless otherwise noted. Parameters in parentheses ( ) are provided for guidance, but are not tested or guaranteed.

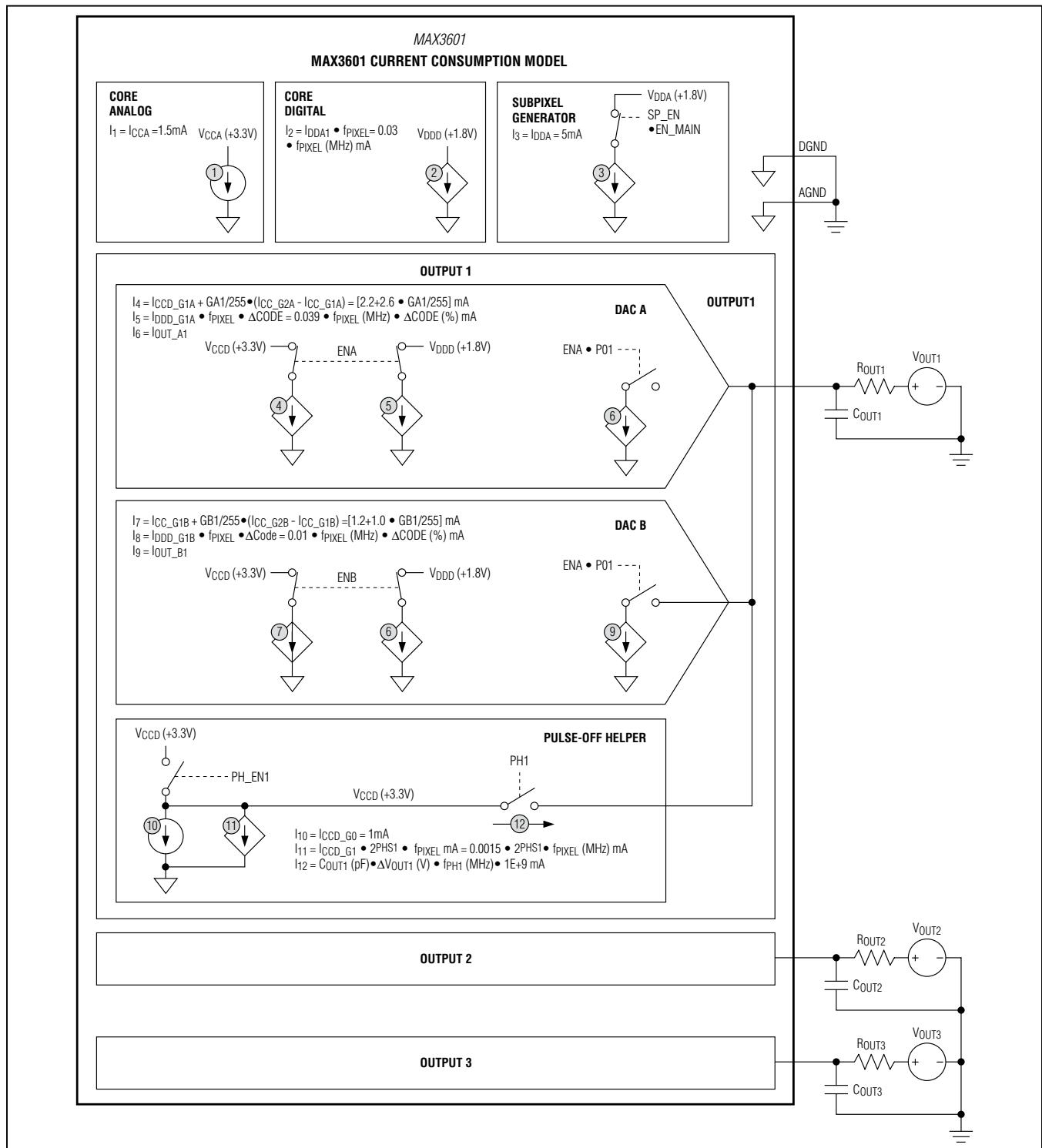

**Note 3:** Power Consumption Calculations:

$$I_{DVDD}(\text{mA}) = I_{DVDD}(\text{mA/MHz}) \times f_{PIXEL}(\text{MHz}) + \sum_{N=1}^3 [EN_{A_N} \times I_{DVDD,G1A}(\text{mA/MHz}) \times \Delta CODE_{A_N} + EN_{B_N} \times I_{DVDD,G1B}(\text{mA/MHz}) \times \Delta CODE_{B_N}] + f_{PIXEL}(\text{MHz})$$

$$I_{DVCC}(\text{mA}) = \sum_{N=1}^3 [EN_{A_N} \times I_{DVCC,G1A} + (I_{DVCC,G2A} - I_{DVCC,G1A}) \times \frac{GA_N}{255} + EN_{B_N} \times I_{DVCC,G1B} + (I_{DVCC,G2B} - I_{DVCC,G1B}) \times \frac{GB_N}{255}]$$

where:

N = OUTPUT 1,2,3,  $f_{PIXEL}$  is the pixel clock frequency (MHz),  $EN_{A\_}$  and  $EN_{B\_}$  are the DAC enable signals with value 0 or 1,  $\Delta CODE$  is the average number of video code changes per pixel (0 to 255). If the Pulse-Off feature is used 1 time per pixel,  $\Delta CODE = 2x$  Average Video Code Value. If Pulse-Off is used 2 times per pixel,  $\Delta CODE = 4x$  Average Video Code Value ([Figure 3](#)).

**Note 4:** Pulse-Off Assist Current Calculation:

$$I_{DVCCD} \approx \sum_{N=1}^3 [(I_{DVCC,G1} + C_{OUTN} \times \Delta V_{OUTN}) \times f_{PON}]$$

where:

N = Output 1,2,3,  $C_{OUTN}$  is the total capacitance at OUTN (MAX3601 output capacitance + external capacitance),  $\Delta V_{OUTN}$  is the resulting voltage change at OUTN,  $f_{PON}$  is the frequency of pulse-events in MHz.  $f_{PON}$  is generally equal to the pixel clock, but could be lower or higher, depending on the pulse-off duty cycle and number of pulse-off events per pixel.

## レーザドライバ、プロジェクタ用

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{AVDD} = V_{DVDD} = 1.7V$  to  $1.9V$ ,  $V_{AVCC} = V_{DVCC} = 2.9V$  to  $3.5V$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ ,  $T_J < +125^\circ C$ , EN\_MAIN and MARKER high,  $V_{OUT} \geq 0.7V$ , unless otherwise noted. Typical values are at  $V_{AVDD} = V_{DVDD} = 1.8V$ ,  $V_{AVCC} = V_{DVCC} = 3.3V$ ,  $T_J = +85^\circ C$ . Consumer grade parts are tested at  $T_A = +70^\circ C$ . Automotive grade parts are tested at  $T_A = +105^\circ C$ . Minimum and maximum specifications are guaranteed by design, characterization and/or production test.)(Note 2)

**Note 5:** Power Estimation Conditions:

For each output, DAC A is enabled, DAC B is off, VIDEO = 27% data as shown in [Figure 2](#),  $f_{PIXEL} = 150MHz$ . Vertical Image Duty cycle is 70%, and the MARKER signal is used to reduce power during vertical flyback.

The load emulates:

Red Laser on OUT1:  $4I + 2.3V$

Green Laser on OUT2:  $8I + 3.8V$

Blue Laser on OUT3:  $16I + 3.5V$

|   | <b>PARAMETER</b>      | <b>VIDEO</b> | <b>GAIN1<br/>(mA)</b> | <b>GAIN2<br/>(mA)</b> | <b>GAIN3<br/>(mA)</b> | <b>V<sub>OUT</sub><br/>@I<sub>PEAK</sub></b> | <b>V<sub>A1</sub><br/>(V)</b> | <b>V<sub>A2</sub><br/>(V)</b> | <b>V<sub>A3</sub><br/>(V)</b> | <b>PO_EN</b> | <b>POC</b> | <b>POM_</b> | <b>PHM_</b> |

|---|-----------------------|--------------|-----------------------|-----------------------|-----------------------|----------------------------------------------|-------------------------------|-------------------------------|-------------------------------|--------------|------------|-------------|-------------|

| 1 | 0% Video              | 00h          | 200                   | 180                   | 70                    | 0.6V                                         | 3.7                           | 5.9                           | 5.2                           | 0            | 0          | 0           | 0           |

| 2 | 27% Video             | 27%          | 200                   | 180                   | 70                    | 0.6V                                         | 3.7                           | 5.9                           | 5.2                           | 0            | 0          | 0           | 0           |

| 3 | 100% Video            | FFh          | 200                   | 180                   | 70                    | 0.6V                                         | 3.7                           | 5.9                           | 5.2                           | 0            | 0          | 0           | 0           |

| 4 | Pulse-Off             | 27%          | 300                   | 270                   | 105                   | 0.8V                                         | 4.3                           | 6.8                           | 6.0                           | 1            | 4h         | FF00h       | 0           |

| 5 | With Pulse-off Assist | 27%          | 300                   | 270                   | 105                   | 0.8V                                         | 4.3                           | 6.8                           | 6.0                           | 1            | 4h         | FF00h       | FF00h       |

**Note 6:** Transfer from supply to  $I_{OUT}$  measured with  $100mV_{P-P}$  sine wave applied at the supply.

$$T = \frac{fI_{OUT}}{I_{OUT}} \times \frac{100\%}{fV}$$

with units %/V.  $I_{OUT} = 325mA$ ,  $T_J \leq +110^\circ C$ ,  $f_{OUT} = 60Hz$  to  $1MHz$ . Typical values are at  $10kHz$ , maximum value at  $1MHz$  typical corner.

**Note 7:** AC Parameters characterized with a video pattern of 0x00 to 0xFF, GAIN = 0xFF, 0x3F, 0x1F, 0x0F. All combinations of output VIDEO DACs: DAC A only, DAC B only, DAC A and DAC B. An external filter network ( $R_S$ ,  $C_S$ ) or digital filter may be used to reduce ringing.

$$\text{Note 8: } 1lsb = \frac{|I_{OUT}(\text{CODE}=0xFF)}{} - |I_{OUT}(\text{CODE}=0x00)}{255}$$

**Note 9:** Integral nonlinearity (INL) is measured as: [ $|I_{OUT}$  - Least Squares approximation of current].

## レーザドライバ、プロジェクト用

図1. テスト回路

図2. ビデオテストパターン

図3.  $\Delta$ コードの例

## レーザドライバ、プロジェクタ用

図4. 電源の計算

## レーザドライバ、プロジェクト用

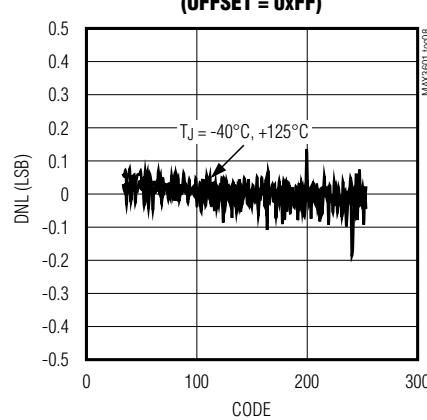

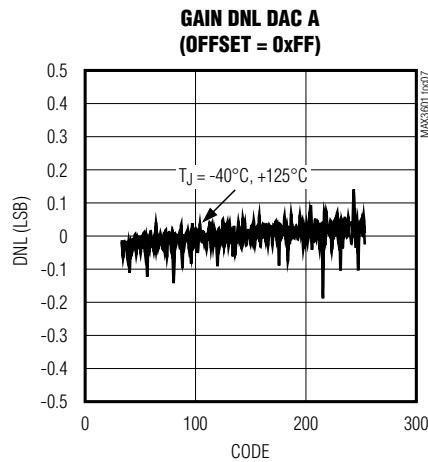

## 標準動作特性

( $V_{AVDD} = V_{DVDD} = 1.8V$ ,  $V_{AVCC} = V_{DVCC} = 3.3V$ ,  $V_{OUT} = 0.7V$ ,  $R_L = 8\Omega$ , EN\_MAIN high,  $T_A = +25^\circ C$ , unless otherwise noted.)

## レーザドライバ、プロジェクト用

## 標準動作特性(続き)

(V<sub>AVDD</sub> = V<sub>DVDD</sub> = 1.8V, V<sub>AVCC</sub> = V<sub>DVCC</sub> = 3.3V, V<sub>OUT</sub> = 0.7V, R<sub>L</sub> = 8Ω, EN\_MAIN high, T<sub>A</sub> = +25°C, unless otherwise noted.)

**レーザドライバ、プロジェクト用****標準動作特性(続き)**

( $V_{AVDD} = V_{DVDD} = 1.8V$ ,  $V_{AVCC} = V_{DVCC} = 3.3V$ ,  $V_{OUT} = 0.7V$ ,  $R_L = 8\Omega$ , EN\_MAIN high,  $T_A = +25^\circ C$ , unless otherwise noted.)

## レーザドライバ、プロジェクト用

## ピン配置

## レーザドライバ、プロジェクト用

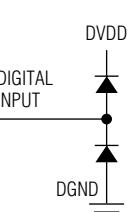

## 端子説明

| 端子                    |                                         | 名称                        | 機能                                                                                                | 等価入力回路図                                                                             |

|-----------------------|-----------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| TQFN-EP               | WLP                                     |                           |                                                                                                   |                                                                                     |

| 1                     | F6                                      | D2                        | 同期ビデオデータ入力                                                                                        |  |

| 2                     | E5                                      | D3                        |                                                                                                   |                                                                                     |

| 3                     | F5                                      | D4                        |                                                                                                   |                                                                                     |

| 4                     | E4                                      | D5                        |                                                                                                   |                                                                                     |

| 5                     | F4                                      | D6                        |                                                                                                   |                                                                                     |

| 6                     | E3                                      | D7                        |                                                                                                   |                                                                                     |

| 7                     | F3                                      | D8                        | 同期ビデオデータ入力。DEMUX Cモードでは、D8はピクセルクロックとして機能します。                                                      | —                                                                                   |

| 8                     | D3                                      | D9                        | 同期ビデオデータ入力                                                                                        |  |

| 9                     | F2                                      | D10                       |                                                                                                   |                                                                                     |

| 10                    | E2                                      | D11                       | 同期ビデオデータ入力、MSB                                                                                    | —                                                                                   |

| 11                    | F1                                      | DCLK                      | ビデオクロック入力                                                                                         | —                                                                                   |

| 12, 37, 38            | D5, E1, E7                              | TESTA,<br>TESTB,<br>TESTC | テスト端子。DGNDに接続してください。                                                                              | —                                                                                   |

| 13, 19, 21,<br>24, 27 | A1, B2,<br>B3, B5,<br>C3, C4,<br>C6, D4 | DGND                      | デジタルグランド。0Vに接続してください。                                                                             | —                                                                                   |

| 14                    | D1                                      | DVDD                      | 1.8Vデジタル電源。できる限りデバイスの近くに配置した0.1μFと0.01μFのコンデンサでDVDDをDGNDに接続してください(値の小さい方のコンデンサがDVDD側)。            | —                                                                                   |

| 15                    | D2                                      | AVDD                      | 1.8Vアナログ電源。できる限りデバイスの近くに配置した0.1μFと0.01μFのコンデンサでAVDDをAGNDに接続してください(値の小さい方のコンデンサがAVDD側)。            | —                                                                                   |

| 16                    | C1                                      | AGND                      | アナロググランド。0Vに接続してください。                                                                             | —                                                                                   |

| 17                    | C2                                      | AVCC                      | 3.3Vアナログ電源。できる限りデバイスの近くに配置した0.1μFと0.01μFのコンデンサでAVCCをAGNDに接続してください(値の小さい方のコンデンサがAVCC側)。            | —                                                                                   |

| 18, 22, 25,<br>28     | B1, B4, B7                              | DVCC                      | 3.3Vデジタル電源。できる限りデバイスの近くに配置した0.1μFと0.01μFのコンデンサ(端子当り1つのペア)でDVCCをDGNDに接続してください(値の小さい方のコンデンサがDVCC側)。 | —                                                                                   |

| 20, 30, 32            | —                                       | N.C.                      | 接続なし。パッケージからICへの接続はありません。                                                                         | —                                                                                   |

## レーザドライバ、プロジェクト用

## 端子説明(続き)

| 端子      |        | 名称      | 機能                                                                                                            | 等価入力回路図                                                                                                                                 |

|---------|--------|---------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| TQFN-EP | WLP    |         |                                                                                                               |                                                                                                                                         |

| 23      | A2, A3 | OUT3    | レーザ3用の接続。使用しない場合はOUT3を未接続のままとしてください。                                                                          | <pre>     graph TD       OUT3[LASER OUTPUT] --&gt; R1[ ]       OUT3 --&gt; R2[ ]       R1 --- AGND[AGND]       R2 --- AGND   </pre>     |

| 26      | A4, A5 | OUT2    | レーザ2用の接続。使用しない場合はOUT2を未接続のままとしてください。                                                                          |                                                                                                                                         |

| 29      | A6, A7 | OUT1    | レーザ1用の接続。使用しない場合はOUT1を未接続のままとしてください。                                                                          |                                                                                                                                         |

| 31      | C5     | EN_MAIN | レーザイネーブル入力(DGNDへの100kΩのプルダウン内蔵)。OUT1～OUT3をイネーブルする場合は、EN_MAIN = ハイに設定してください。                                   | <pre>     graph TD       EN_MAIN[DVCC] --&gt; R[ ]       R --- DIGITAL_INPUT[DIGITAL INPUT]       DIGITAL_INPUT --- DGND[DGND]   </pre> |

| 33      | B6     | MARKER  | ビデオマーカ入力(DVDDへの100kΩのプルアップ内蔵)                                                                                 |                                                                                                                                         |

| 34      | C7     | DIO/SDA | SPIおよびI <sup>2</sup> Cシリアルデータ入出力                                                                              |                                                                                                                                         |

| 35      | D7     | CLK/SCL | SPIおよびI <sup>2</sup> Cシリアルクロック入力                                                                              |                                                                                                                                         |

| 36      | D6     | CS      | SPIチップセレクト(DGNDへの100kΩのプルダウン内蔵)。I <sup>2</sup> Cモードとする場合は、CSをDVDDに接続してください。SPIモードとする場合は、起動時にCS = ローに設定してください。 |                                                                                                                                         |

| 39      | F7     | D0      | 同期ビデオデータ入力、LSB                                                                                                | <pre>     graph TD       D0[DVDD] --&gt; R[ ]       R --- DIGITAL_INPUT[DIGITAL INPUT]       DIGITAL_INPUT --- DGND[DGND]   </pre>      |

| 40      | E6     | D1      | 同期ビデオデータ入力                                                                                                    |                                                                                                                                         |

| —       | —      | EP      | エクスポートズドバッド(TQFNのみ)。EPは内部でDGNDに接続されています。適切な熱的および電気的性能を実現するために、ビアのアレイを介してEPをPCBのグランドプレーンに接続する必要があります。          | —                                                                                                                                       |

## レーザドライバ、プロジェクタ用

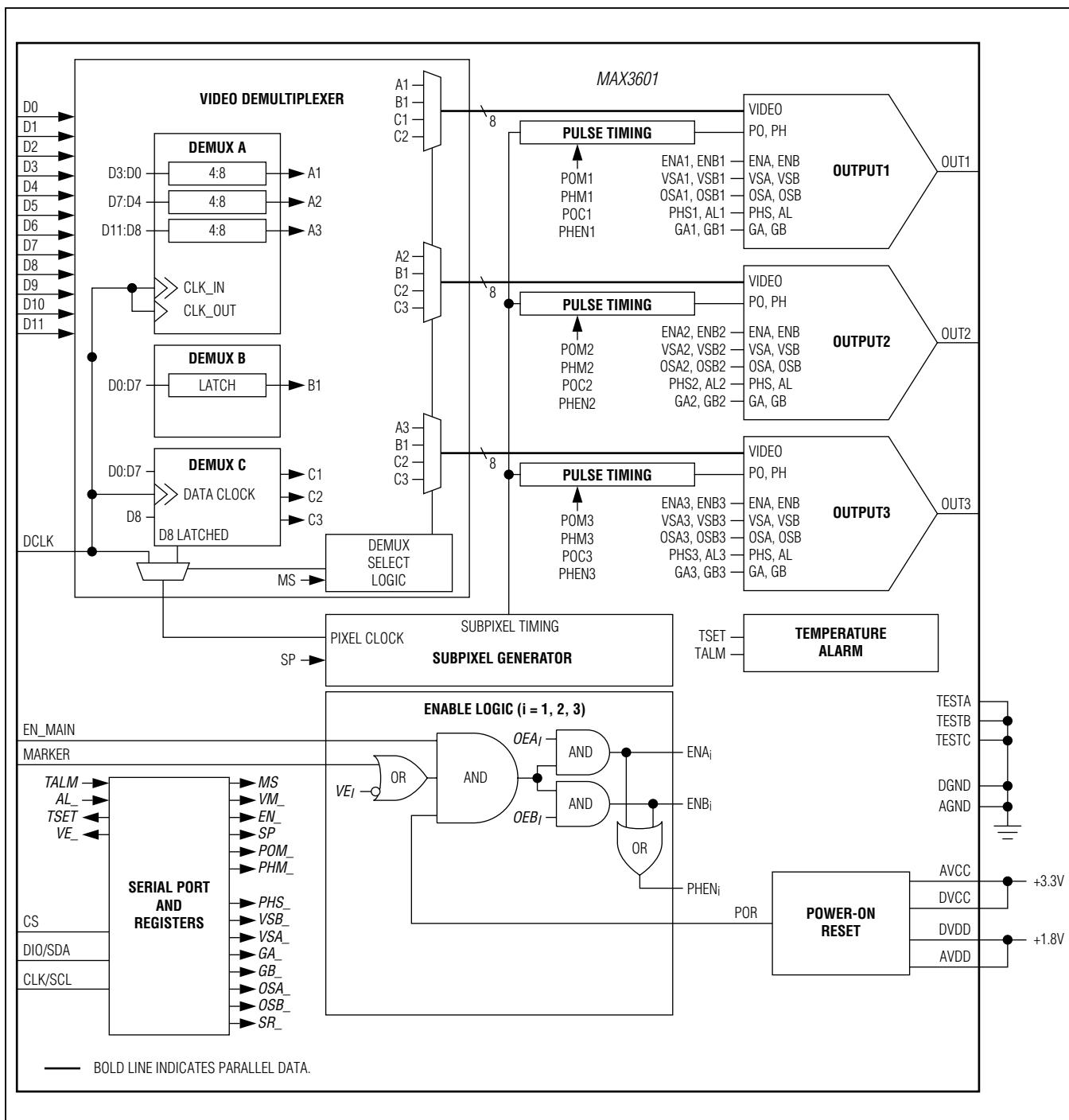

## ファンクションダイアグラム

# レーザドライバ、プロジェクタ用

## 詳細

このプロジェクト用レーザドライバは、RGBレーザによるビデオイメージングをサポートします。各出力には、設定可能な利得およびオフセットを備えた2つの8ビットビデオ/オフセットDACが組み込まれています。

### ビデオデマルチプレクサ

ビデオデマルチプレクサは、3つのビデオ形式およびピクセルクロック構成をサポートします。ビデオ形式およびデマルチプレクサは、[表7](#)に示すようにMUX Selectレジスタ(MS)によって選択されます。

図5. ビデオデマルチプレクサAの入力波形

### デマルチプレクサA

デマルチプレクサAは、DDRクロックを備えた4ビット入力を、ピクセルクロックを備えた8ビットデータに変換します。入力データは、[図5](#)に示す形式を備える必要があります。4つのMSBはDCLKの立上りエッジでラッチされ、4つの LSBはDCLKの立下りエッジでラッチされます。

### デマルチプレクサB

デマルチプレクサBは、8ビットのビデオ入力をクロックの立上りエッジでラッチします。同じビデオがすべての出力に送信されます。

図6. ビデオデマルチプレクサBの入力波形

## レーザドライバ、プロジェクタ用

図7. ビデオデマルチプレクサCの入力波形

図8. ビデオデマルチプレクサC

## デマルチプレクサC

デマルチプレクサCは、MAX3600のデータ形式と互換性があります。3つの出力用のデータは時間上で多重化され、DDRクロックを使用します。

## レーザドライバ、プロジェクタ用

### パルスタイミングジェネレータ

パルスタイミングジェネレータは、サブピクセルと呼ばれるピクセルクロックの位相を生成します(図9)。サブピクセルタイミング信号によりレーザ電流出力のパルス化が可能となり、レーザ光のスペックル抑制とともに使用すること

ができます。レーザドライバの各出力を異なるパルス幅または複数のパルスとすることが可能です。使用しない場合は、サブピクセルジェネレータをディセーブルすることにより(レジスタ0x0BのD0)、さらなる省電力化が可能です。

図9. パルスタイミングジェネレータ

## レーザドライバ、プロジェクタ用

### サブピクセル設定

サブピクセル設定ビット(レジスタ0x0CのD[2:0])は、サブピクセル数およびパルス時間の長さを決定します([表1](#))。パルス幅は、設定されたパルスオフ長 > 0のときに個々のピクセルに適用されます。これを動的に実装することにより、さまざまな照明条件に応じた調整が可能になります。

### パルスオフ

パルスタイミングジェネレータは、パルスイベントをスキップして電力を節約するように設定することができます。Pulse-Off Configuration (POC)レジスタは、[表2](#)に示す

オプションを選択します。ランダムパルスオフィベントは、31ビットの疑似ランダムビットストリーム(PRBS)によってトリガれます。デフォルトでは、PRBSはすべての出力に共通です。POC\_レジスタのビットD4は、どのPRBSビットにより各出力が制御されるかを決定します([表3](#))。

POC\_レジスタが一致し、POC\_[4] = 0のとき、出力間のパルスオフの同期化が発生します。たとえば、POC1 = POC2 = POC3かつPOC\_[4] = 0の場合、すべての出力におけるランダム化されたパルスオフィベントの発生が同期化されます。

**表1. サブピクセル設定

(SPレジスタ)**

| SP          | fPIXEL (MHz) |            | ACTIVE SUBPIXELS | INACTIVE SUBPIXELS |

|-------------|--------------|------------|------------------|--------------------|

|             | MIN          | MAX        |                  |                    |

| 000         | 150          | 200        | 0:7              | 8:15               |

| <b>001*</b> | <b>75</b>    | <b>150</b> | <b>0:15</b>      | —                  |

| 010         | 50           | 100        | 0:11             | 12:15              |

| 011         | 37.5         | 75         | 0:15             | —                  |

| 100         | 30           | 60         | 0:9              | 10:15              |

| 101         | 25           | 50         | 0:15             | —                  |

| 110         | 21.4         | 42.8       | 0:13             | 14:15              |

| 111         | 18.75        | 37.5       | 0:15             | —                  |

\*起動時のデフォルト

**表2. パルスオフデューティサイクル

(POC\_レジスタ)**

| POC_[3:0]   | PULSE-OFF DUTY CYCLE                        |

|-------------|---------------------------------------------|

| <b>0000</b> | <b>Every pixel, 100% (Power-on default)</b> |

| 0001        | Random, 87.5%                               |

| 0010        | Random, 75.0%                               |

| 0011        | Random, 62.5%                               |

| 0100        | Random, 50.0%                               |

| 0101        | Random, 37.5%                               |

| 0110        | Random, 25.0%                               |

| 0111        | Random, 12.0%                               |

| 1XXX        | Every other pixel, 50%                      |

**表3. ランダムパルスオフの設定**

| POC_[4] | PRBS31 BITS USED    |                     |                       |

|---------|---------------------|---------------------|-----------------------|

|         | OUTPUT 1            | OUTPUT 2            | OUTPUT 3              |

| 0*      | PRBS31[4], [3], [0] | PRBS31[8], [7], [0] | PRBS31[16], [15], [0] |

| 1       | PRBS31[2:0]         | PRBS31[2:0]         | PRBS31[2:0]           |

\*起動時のデフォルト

## レーザドライバ、プロジェクタ用

### ドライバ出力

3つのレーザドライバ出力は、それぞれ2つのビデオDAC、2つの利得DAC、コンプライアンス電圧アラーム、およびパルスオフアシストを内蔵しています。省電力化のために、MAX3601は出力が未使用の際に消費電流を低減します。

### ビデオDAC

各レーザドライバ出力は、ビデオイメージを表す電流を生成する2つのビデオDACを内蔵しています(図10)。DAC

AはDAC Bの4倍の電流出力能力を備えていますが、それ以外の点では同一です。ビデオデータは高速データ入力から入力されます。VSA\_およびVSB\_は、2つのビデオDACの出力の動作を決定します(表4および表5)。どちらのDACの出力ビデオも、以下の任意のものにすることができます。

- ビデオデータ

- パルスオフ(振幅ゼロ)

図10. ドライバ出力

## レーザドライバ、プロジェクト用

表4. DAC Aのビデオ選択ロジック

| <b>ENA</b> | <b>VSA</b> | <b>VIDEO</b> | <b>PO</b> | <b>CODE DAC A</b> |

|------------|------------|--------------|-----------|-------------------|

| 0          | X          | X            | X         | 0                 |

|            | 000*       | X            | 0         | VIDEO             |

|            |            |              | 1         | 0                 |

|            | 001        | X            | 0         | VIDEO             |

|            |            |              | 1         | OSA_              |

|            | 010        | X            | 0         | OSA_              |

|            |            |              | 1         | 0                 |

|            | 011        | X            | 0         | OSA_              |

|            |            |              | 1         | OSA_              |

|            | 100        | 0            | X         | 0                 |

|            |            | > 0          | 0         | OSA_              |

|            |            |              | 1         | 0                 |

| 1          | 101        | X            | X         | 0                 |

|            | 110        | X            | X         | 0                 |

|            | 111        | X            | X         | 0                 |

\*起動時のデフォルト

表5. DAC Bのビデオ選択ロジック

| <b>ENB</b> | <b>VSB</b> | <b>VIDEO</b> | <b>PO</b> | <b>CODE DAC B</b> |

|------------|------------|--------------|-----------|-------------------|

| 0          | X          | X            | X         | 0                 |

|            | 000*       | X            | 0         | VIDEO             |

|            |            |              | 1         | 0                 |

|            | 001        | X            | 0         | VIDEO             |

|            |            |              | 1         | OSB_              |

|            | 010        | X            | 0         | OSB_              |

|            |            |              | 1         | 0                 |

|            | 011        | X            | 0         | OSB_              |

|            |            |              | 1         | OSB_              |

|            | 100        | 0            | X         | 0                 |

|            |            | > 0          | 0         | OSB_              |

|            |            |              | 1         | 0                 |

| 1          | 101        | X            | X         | 0                 |

|            | 110        | X            | X         | 0                 |

|            | 111        | X            | X         | 0                 |

\*起動時のデフォルト

- パルスオフ(振幅ゼロ以外)

- シリアルポートから設定された定数値

- 振幅ゼロ

- VIDEO > 0に対して定数値、VIDEO = 0のときはゼロ

- 2つの利得DACは、フルスケール出力電流を調整してレーザのスロープ効率およびカラーバランスを実現します。ビデオ利得はシリアルポートから設定します。ビデオDAC AおよびBのフルスケール出力は、それぞれのピーク出力である最大320mAおよび80mAまでの範囲で調整可能です(図11)。レーザドライバの出力電流は、DAC AおよびBの出力の組み合わせです。

$$I_{OUT}(\text{mA}) = \frac{\text{CODEA}[\text{GA}]}{\text{FFh}} \times 320 + \frac{\text{CODEB}[\text{GB}]}{\text{FFh}} \times 80 + \text{OSERR}$$

ここで、OSERRはオフセット誤差です。

出力電流の絶対最大定格を注意深く考慮してください。製品寿命にわたり $I_{OUT}$ のピークが400mAでデューティサイクルが50%の場合、平均DC電流は200mAになります。

図11. ドライバ出力のフルスケール電流範囲

## レーザドライバ、プロジェクト用

図12. 出力コンプライアンスセンサー

図13. コンプライアンスセンサーの使用例

### パルスオフとパルスオファシスト

パルス機能は、レーザを素早くオフに変動させます。「オフ」のレベルは、VSA\_およびVSB\_レジスタによって設定されます(表4、表5)。

PHM\_レジスタ > 0に設定し、ENA\_またはENB\_をハイに設定することにより、パルスオファシスト回路がイネーブルされます。さらに、MARKERがハイでどちらかの出力がイネーブルされているときにのみ回路はアクティブになります。低速レーザのターンオフ時間を改善するために、パルスオファイント中、レーザ電圧は瞬間に3.3Vに接続されます。パルスオファシストは、パルスオフ中にOSA\_およびOSB\_レジスタにゼロが設定されている場合にのみ有効であることに注意してください。

### コンプライアンス電圧センサー

出力電圧は、オーバーシュート、セトリング時間、およびリニアリティに影響します。コンプライアンスアラームは、設定されたスレッショルド(表6)より低い出力電圧を検出して、コンプライアンスアラーム(VALM\_)ビットをセットします(図12)。アラームは、読み取った時点でクリアされます。コンプライアンスアラームを使用して、50nsの高輝度ピクセルを含むビデオデータが送信されたあとにレーザ電源を調整することができます(図13)。VALMビットは通常は起動時にセットされます。

表6. コンプライアンスアラームのセットポイント

| VSET_[3:0] | TYPICAL COMPLIANCE VOLTAGE THRESHOLD (V) |

|------------|------------------------------------------|

| 0000*      | 0.40                                     |

| 0001       | 0.48                                     |

| 0010       | 0.56                                     |

|            | .                                        |

|            | .                                        |

| 1110       | 1.52                                     |

| 1111       | 1.60                                     |

\*起動時のデフォルト

## レーザドライバ、プロジェクタ用

図14. 温度アラーム

図15. ビデオマーカ

表7. ビデオマルチプレクサ選択ロジック

| MS[2:0] | PIXEL CLOCK SOURCE | VIDEO 1 | VIDEO 2 | VIDEO 3 |

|---------|--------------------|---------|---------|---------|

| 000*    | DCLK               | A1      | A2      | A3      |

| 001     | DCLK               | B1      | B1      | B1      |

| 010     | D8**               | C1      | C2      | C3      |

| 011     | D8**               | C2      | C2      | C2      |

| 100     | D8**               | C2      | C2      | C3      |

| 101     | D8**               | C2      | C3      | C3      |

| 110     | RESERVED           |         |         |         |

| 111     | RESERVED           |         |         |         |

\*起動時のデフォルト

\*\*D8はDCLKによりゲートされます。

### 温度アラーム

温度アラームは、[図14](#)に示すように、ドライバ温度が設定可能なスレッショルドを超えたかどうかを通知します。アラームは、TALMレジスタが読み取られるとクリアされます。チップ温度がまだスレッショルドを上回っている場合、温度アラームは自ら即座に再アサートします。温度スレッショルドは、T\_SETレジスタで設定します。温度アラームスレッショルドには、温度センサーのオフセットが含まれます。既知の温度でアラームを較正することにより、スレッショルドの精度が向上します。

たとえば、温度アラームを  $T_J = +125^\circ\text{C}$  に設定する場合、 $T_A = +25^\circ\text{C}$  および出力をディセーブルした状態で TSET を上昇させて TALM を読み取ります。アラームがセットされるコード TSET<sub>25</sub> が、 $T_J \approx +25^\circ\text{C}$  に相当します。TSET<sub>125</sub>  $\approx$  TSET<sub>25</sub> + 100°C/2.5°C/LSB です。

### 制御ロジック

制御ロジックは、ビデオの選択、レーザのイネーブル、および省電力を提供します。

#### ビデオの選択

ビデオマルチプレクサ A、B、および C は、信号 A1 ~ A3、B1、および C1 ~ C3 を生成します。MS ビットは、VIDEO1、VIDEO2、および VIDEO3 の入力ソースビデオを選択します。

#### レーザの制御

EN\_MAIN がローのとき、すべてのドライバはオフです。この信号は非同期に機能します(出力のディセーブルにクロックは不要です)。

ビデオマーカ(MARKER)入力を使用して、ビデオ信号を受信していないときに選択されている出力をディセーブルすることができます([図15](#))。VE[1:3]ビットの設定によって、どの出力が MARKER 信号に反応するかが決まります。

## レーザドライバ、プロジェクト用

### シリアルポートおよびレジスタ

MAX3601は、I<sup>2</sup>Cインターフェースおよび3線式SPIインターフェースを内蔵しています。通信モードは、起動時のCSの状態によって決定されます。CSがハイ(DVDDに接続)の場合は、I<sup>2</sup>Cモードが選択されます。起動時にCSがオープンまたはローの場合は、SPIモードが選択されます。

### I<sup>2</sup>Cインターフェース

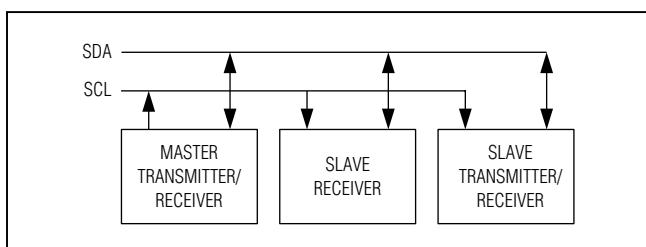

シリアルバスは、双方向のシリアルデータライン(SDA)と、シリアルクロック入力(SCL)で構成されます。マスターはクロック信号を生成します(図16)。

I<sup>2</sup>Cはオープンドレインのバスです。SDAおよびSCLにはプルアップ抵抗(500Ω以上)が必要です。入力の電圧クランプは、絶対最大電圧定格を超えない高電圧スパイクからデバイスを保護します。

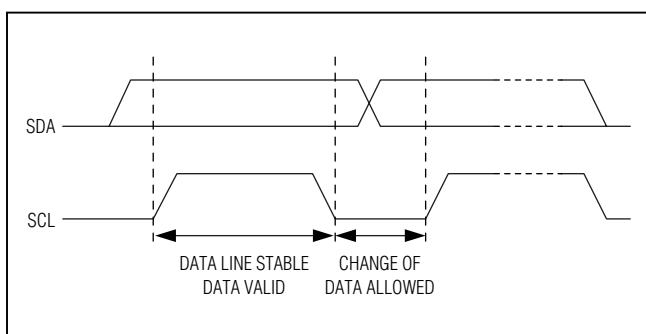

### データ転送

各SCLクロックサイクル内で1ビットのデータが転送されます。SDA上のデータは、SCLクロックパルスがハイの期

図16. I<sup>2</sup>Cのマスター/スレーブ構成

図17. I<sup>2</sup>Cのビット転送

間にわたって安定している必要があります(図17)。SCLがハイの間にSDAが変化した場合は、制御信号になります(詳細については「STARTおよびSTOP条件」の項を参照)。

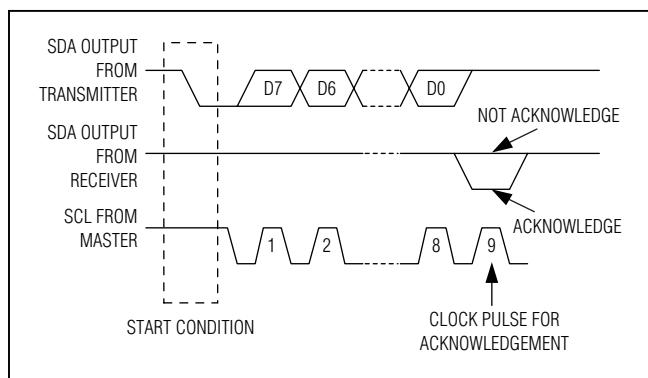

各送信シーケンスは、START (S)条件とSTOP (P)条件によって区切られます。各データパケットは9ビット長で、8ビットのデータのあとにアクノリッジビットが続きます。

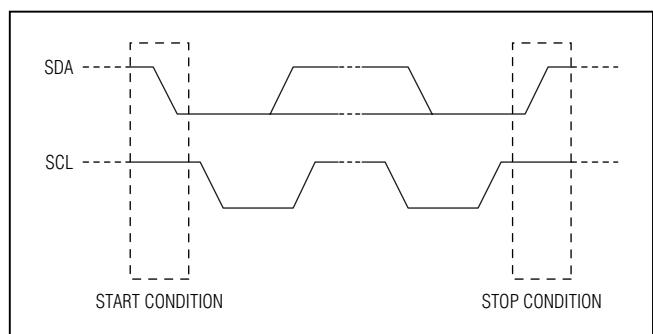

### STARTおよびSTOP条件

シリアルインターフェースがアクティブでない場合、SDAおよびSCLはアイドル状態を示すハイになります。マスターデバイスは、START条件を発生させることによって通信を開始します。START条件とは、SCLがハイの状態でSDAがハイからローに遷移することです。STOP条件とは、SCLがハイの状態でSDAがローからハイに遷移することです(図18)。

マスターからのSTART条件によって転送の開始が通知されます。マスターは、非アクノリッジに続けてSTOP条件を発生させることによって転送を終了します(詳細については図19を参照)。STOP条件によってバスが解放されます。スレーブに対して一連のコマンドを発行する場合、バスの制御を維持するために、マスターはSTOPコマンドの代わりにRepeated START (Sr)コマンドを発生させることができます。一般に、Repeated STARTコマンドは通常のSTARTコマンドと機能的に同等です。

STOP条件または不正なアドレスが検出された場合、MAX3601は次のSTART条件まで内部でSCLをシリアルインターフェースから切り離し、デジタルノイズおよびフィードスルーを最小限に抑えます。

図18. I<sup>2</sup>CのSTARTおよびSTOP条件

## レーザドライバ、プロジェクト用

### アクノリッジ

マスターとMAX3601(スレーブ)の両方が、データ受信時にアクノリッジビットを生成します。アクノリッジビットは、各9ビットのデータパケットの最後のビットです(図19)。アクノリッジ(A)を生成する場合は、アクノリッジ関連のクロックパルス(9番目のパルス)の立上りエッジより前に受信側デバイスがSDAをローに駆動して、そのクロックパルスがハイの間SDAをローに維持する必要があります。非アクノリッジ(NA)を生成する場合は、アクノリッジ関連のクロックパルスの立上りエッジより前に受信側デバイスはSDAがハイに駆動されるのを許容し、そのクロックパルスがハイの間SDAをハイのままにします。

図19. I<sup>2</sup>Cのアクノリッジ

アクノリッジビットを監視することによって、データ転送の失敗を検出することができます。データ転送の失敗は、受信側デバイスがピジーであるか、またはシステム障害の発生によって起こります。データ転送に失敗した場合、バスマスターはあとで通信を再試行してください。

### スレーブアドレス

バスマスターは、START条件を発生させたあとにスレーブアドレスを送信することによって、スレーブデバイスとの通信を開始します。スレーブアドレスバイトは7ビットのアドレスビット(1110 001)と1ビットの読み取り/書き込みビット(R/W、書き込み時は0/読み取り時は1)で構成されます。適切なアドレスを受信したあと、MAX3601は9番目のクロックサイクルの間SDAをローに駆動することによってアクノリッジを送信します。MAX3601の書き込みアドレスは0xE2です。MAX3601の読み取りアドレスは0xE3です。

### I<sup>2</sup>C通信プロトコル

以下のI<sup>2</sup>C通信プロトコルがMAX3601によってサポートされています。

- 1) 単一レジスタへの書き込み

- 2) 連続するレジスタへの書き込み

- 3) 単一レジスタからの読み取り

- 4) 連続するレジスタからの読み取り

図20. I<sup>2</sup>Cのタイミング図

## レーザドライバ、プロジェクト用

### 単一レジスタへの書き込み

図21は、I<sup>2</sup>CマスターデバイスがMAX3601に1バイトのデータを書き込むためのプロトコルを示しています。「バイト書き込み」プロトコルは、以下のとおりです。

- 1) マスターがSTARTコマンド(S)を送信する。

- 2) マスターが7ビットのスレーブアドレスとそれに続く書き込みビットを送信する。

- 3) アドレス指定されたスレーブはSDAをローに駆動することによってアクノリッジ(A)をアサートする。

- 4) マスターが8ビットのレジスタポインタを送信する。

- 5) スレーブがレジスタポインタのアクノリッジを行う。

- 6) マスターがデータバイトを送信する。

- 7) スレーブが新しいデータで更新を行う。

- 8) スレーブがデータバイトのアクノリッジを行う。

- 9) マスターがSTOP条件を送信する。

### 連続するレジスタへの書き込み

図21は、I<sup>2</sup>CマスターデバイスがMAX3601にデータを連續して書き込むためのプロトコルを示しています。連續書き込みプロトコルは、以下のとおりです。

- 1) マスターがSTARTコマンド(S)を送信する。

- 2) マスターが7ビットのスレーブアドレスとそれに続く書き込みビットを送信する。

- 3) アドレス指定されたスレーブはSDAをローに駆動することによってアクノリッジ(A)をアサートする。

- 4) マスターが8ビットのレジスタポインタを送信する。

- 5) スレーブがレジスタポインタのアクノリッジを行う。

- 6) マスターがデータバイトを送信する。

- 7) スレーブが新しいデータで更新を行う。

- 8) スレーブがデータバイトのアクノリッジを行う。

- 9) マスターが必要とする回数だけステップ6~8が繰り返される。

- 10) マスターがSTOP条件を送信する。

図21. I<sup>2</sup>Cの書き込み

## レーザドライバ、プロジェクト用

### 単一レジスタからの読み取り

図22は、I<sup>2</sup>CマスターデバイスがMAX3601から1バイトのデータを読み取るためのプロトコルを示しています。

「read byte」プロトコルは、以下のとおりです。

- 1) マスターがSTARTコマンド(S)を送信する。

- 2) マスターが7ビットのスレーブアドレスに続けて書込みビットを送信する。

- 3) アドレス指定されたスレーブはSDAをローに駆動することによってアクノリッジ(A)をアサートする。

- 4) マスターが8ビットのレジスタポインタを送信する。

- 5) スレーブがレジスタポインタのアクノリッジを行う。

- 6) マスターがRepeated STARTコマンド(Sr)を送信する。

- 7) マスターが7ビットのスレーブアドレスとそれに続く読み取りビットを送信する。

- 8) アドレス指定されたスレーブはSDAをローに駆動することによってアクノリッジをアサートする。

- 9) アドレス指定されたスレーブはレジスタポインタで指定された位置から8ビットのデータをバス上に出力する。

- 10) マスターは非アクノリッジ(NA)を送信する。

- 11) マスターはSTOP条件(P)を送信する。

手順(6)のSrは、STOP (P)とSTART (S)に置き換えることはできません。

### 連続するレジスタからの読み取り