## ISDB-T 1セグメントチューナ

概要

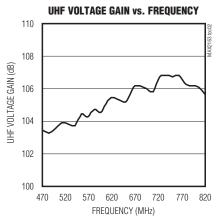

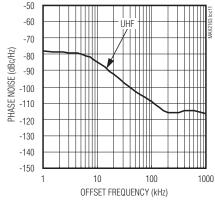

低IFチューナーICのMAX2163は1セグメントISDB-T アプリケーション用に設計されています。MAX2163は 広帯域I/Qダウンコンバータを使用して、直接、UHF帯 信号を低IFに変換します。動作周波数範囲は470MHz ~806MHzのUHF帯をカバーしています。

MAX2163はLNA、RF可変利得アンプ、IおよびOのダ ウン変換ミキサ、ベースバンド可変利得アンプ、および 低IFフィルタを備えています。MAX2163の各可変利得 アンプは100dBを超える制御範囲を備えています。

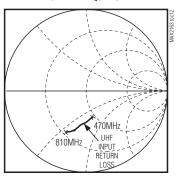

MAX2163は完全モノリシックVCOおよび内蔵の水晶 発振器と出力バッファなどの完全な周波数シンセサイザ を含んでいます。このデバイスは32MHz~36MHzの 水晶で動作します。

MAX2163は2線式I<sup>2</sup>C対応のシリアル制御インタフェー スを備えています。ローパワースタンバイモードが利 用可能で、制御インタフェースおよびレジスタ回路を アクティブにしたままで、信号経路をシャットダウン します。さらに外部端子でデバイス全体をシャットダ ウンすることが可能です。

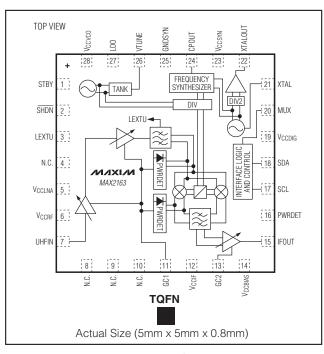

MAX2163は-40℃~+85℃の拡張温度範囲での動作が 保証されており、5mm x 5mm x 0.8mmの28ピン TQFN、鉛フリーのエクスポーズドパッド(EP)付きのプ ラスティックパッケージでご利用頂けます。

#### アプリケーション

携帯電話モバイルTV

携帯情報端末(PDA)

ゲームコンソール

ポータブルTVデバイス

ポータブルオーディオデバイス

車載機器

ホームビデオ

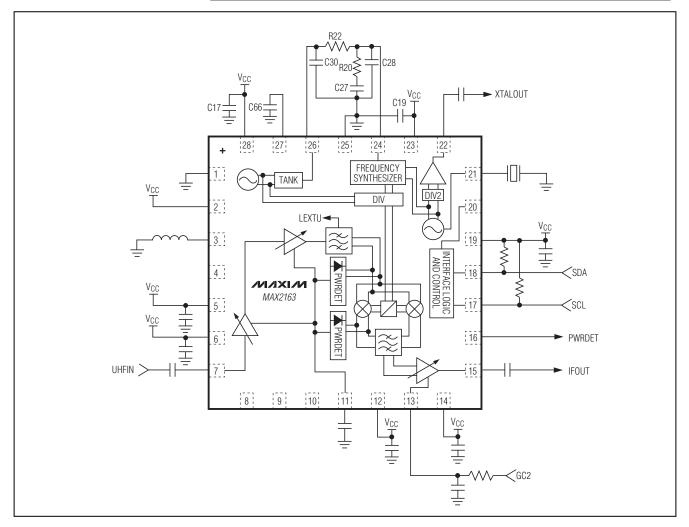

標準アプリケーション回路はデータシートの最後に記載されて います。

#### 特長

◆ 周波数範囲

UHF: 470MHz~806MHz (UHFIN)

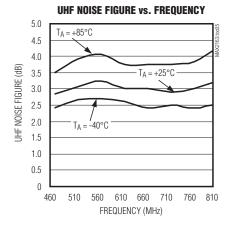

- ◆ 低ノイズ指数: 3.2dB (typ)

- ◆ 広ダイナミックレンジ:-99dBm~0dBm

- ◆ オプションのUHFトラッキングフィルタ

- ◆ 内蔵VCOおよび周波数シンセサイザ

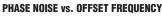

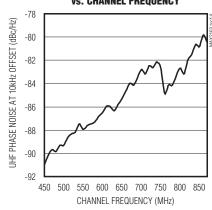

- ◆ 低LO位相ノイズ: -87dBc/Hz (10kHzにおいて)

- ◆ 可変帯域幅の低IFフィルタ内蔵

- ◆ 40dBを超えるイメージリジェクション

- ◆ 単一電源:+2.4V~+3.47V

- ◆ ローパワー: +2.5Vで80mW (typ)

- ◆ 2線式I<sup>2</sup>Cシリアル制御インタフェース

- ◆ ローパワーのシャットダウンおよびスタンバイモード

| PART          | TEMP RANGE     | PIN-<br>PACKAGE |

|---------------|----------------|-----------------|

| MAX2163ETI+   | -40°C to +85°C | 28 TQFN-EP*     |

| MAX2163ETI/V+ | -40°C to +85°C | 28 TQFN-EP*     |

+は鉛(Pb)フリー/RoHS準拠パッケージを表します。 \*EP = エクスポーズドパッド

/Vは車載認定製品を表します。

## ピン配置/ファンクションダイアグラム

NIXIN

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| All V <sub>CC</sub> _Pins to GND0.3V to +3.6V UHFIN to GND0.3V to +0.9V IFOUT to GND0.3V to (V <sub>CC</sub> + 0.3V) | Short-Circuit Duration IFOUT, CPOUT, XTALOUT, PWRDET, SDA, MUX |

|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| GC1, GC2, VTUNE, XTALOUT,                                                                                            | 28-Pin Thin QFN (derate 34.5mW/°C above +70°C)2758mW           |

| XTAL to GND0.3V to (V <sub>CC</sub> + 0.3V)                                                                          | Operating Temperature Range40°C to +85°C                       |

| CPOUT, XTLOUT, PWRDET to GND0.3V to (V <sub>CC</sub> + 0.3V)                                                         | Junction Temperature+150°C                                     |

| SDA, SCL, SHDN, STBY to GND0.3V to (V <sub>CC</sub> + 0.3V)                                                          | Storage Temperature Range65°C to +150°C                        |

| MUX, LEXTU, LDO to GND0.3V to (V <sub>CC</sub> + 0.3V)                                                               | Lead Temperature (soldering, 10s)+300°C                        |

| Maximum RF Input Signal UHFIN+10dBm                                                                                  | , , , , , , , , , , , , , , , , , , , ,                        |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

(MAX2163 Evaluation Kit,  $V_{CC}$  = +2.4V to +3.47V,  $V_{GC1}$  =  $V_{GC2}$  = 0.3V (maximum gain), no RF input signal at UHFIN. IFOUT is open circuited and the VCO is active with  $f_{LO}$  = 557.714MHz, default register settings,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{CC}$  = +2.5V,  $T_A$  =+25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                          | CONDITIONS                 | MIN          | TYP  | MAX                       | UNITS |

|----------------------------------------------------|----------------------------|--------------|------|---------------------------|-------|

| SUPPLY VOLTAGE AND SUPPLY CURRE                    | NT                         | 1            |      |                           |       |

| Supply Voltage                                     |                            | 2.4          | 2.5  | 3.47                      | V     |

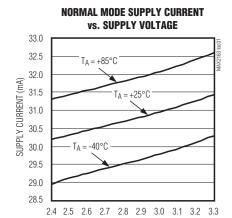

| Supply Current Normal Mode                         |                            |              | 30.4 | 40                        | mA    |

| Supply Current High-Linearity Mode                 | RFVGA = 1; MXR = 1         |              | 35   | 44                        | mA    |

| Supply Current HW or SW Standby Mode               |                            |              | 1.1  | 2.0                       | mA    |

| Supply Current Shutdown Mode                       |                            |              | 1    | 20                        | μΑ    |

| ANALOG GAIN-CONTROL INPUTS (GC1, G                 | C2)                        |              |      |                           |       |

| Voltage Range                                      | Maximum gain = 0.3V        | 0.3          |      | 2.1                       | V     |

| Input Bias Current                                 |                            | -15          |      | +15                       | μΑ    |

| POWER DETECTOR OUTPUT BUFFER (PV                   | VRDET)                     |              |      |                           |       |

| Output Voltage Range                               | Load impedance = 2kΩII10pF | 0.3          |      | 2.1                       | V     |

| Output Impedance                                   |                            |              | 25   |                           | Ω     |

| VCO TUNING VOLTAGE INPUT (VTUNE)                   |                            |              |      |                           |       |

| Voltage Range                                      |                            | 0.35         |      | 2.05                      | V     |

| DIGITAL CONTROLS (SHDN, STBY)                      |                            |              |      |                           |       |

| Input Logic-Level High                             |                            | 0.7 x<br>VCC |      |                           | V     |

| Input Logic-Level Low                              |                            |              |      | 0.3 x<br>V <sub>C</sub> C | V     |

| 2-WIRE SERIAL I <sup>2</sup> C DIGITAL INPUTS (SCL | ., SDA)                    | •            |      |                           |       |

| Clock Frequency                                    |                            |              |      | 400                       | kHz   |

| Input Logic-Level High                             |                            | 0.7 x<br>VCC |      |                           | V     |

| Input Logic-Level Low                              |                            |              |      | 0.3 x<br>V <sub>CC</sub>  | V     |

### DC ELECTRICAL CHARACTERISTICS (continued)

(MAX2163 Evaluation Kit,  $V_{CC}$  = +2.4V to +3.47V,  $V_{GC1}$  =  $V_{GC2}$  = 0.3V (maximum gain), no RF input signal at UHFIN. IFOUT is open circuited and the VCO is active with  $f_{LO}$  = 557.714MHz, default register settings,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{CC}$  = +2.5V,  $T_A$  =+25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                           | CONDITIONS | MIN                       | TYP | MAX                      | UNITS |

|-----------------------------------------------------|------------|---------------------------|-----|--------------------------|-------|

| 2-WIRE SERIAL I <sup>2</sup> C DIGITAL OUTPUT (SDA) |            |                           |     |                          |       |

| Output Logic-Level Low                              |            |                           |     | 0.4                      | V     |

| MUX DIGITAL OUTPUT                                  |            |                           |     |                          |       |

| Output Logic-Level Low                              |            |                           |     | 0.3 x<br>V <sub>CC</sub> | V     |

| Output Logic-Level High                             |            | 0.7 x<br>V <sub>C</sub> C |     |                          | V     |

#### **AC ELECTRICAL CHARACTERISTICS**

(MAX2163 Evaluation Kit,  $V_{CC} = +2.4V$  to +3.47V,  $f_{RF} = 557.143MHz$ ,  $f_{LO} = 557.714MHz$ ,  $f_{IF} = 571kHz$ ,  $f_{XTAL} = 36MHz$ ,  $V_{GC1} = V_{GC2} = 0.3V$  (maximum gain), default register settings, RF input signals as specified, IF output load as specified,  $T_{A} = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $V_{CC} = +2.5V$ ,  $T_{A} = +25^{\circ}C$ ,  $\overline{SHDN} = V_{CC}$ , STBY = GND, unless otherwise noted.) (Note 1)

| PARAMETER                          | PARAMETER CONDITIONS                                                      |     |     |     | UNITS |

|------------------------------------|---------------------------------------------------------------------------|-----|-----|-----|-------|

| MAIN SIGNAL PATH PERFORMANCE       |                                                                           |     |     |     |       |

| Receive Input Frequency Range      | UHFIN (Note 2)                                                            | 470 |     | 806 | MHz   |

| Maximum Voltage Gain               | -100dBm CW tone, $V_{GC1} = V_{GC2} = 0.3V$<br>$V_{IFOUT} = 0.225V_{P-P}$ | 96  |     |     | dB    |

| Minimum Voltage Gain               | 0dBm CW tone, $V_{GC1} = V_{GC2} = 2.1V$<br>$V_{IFOUT} = 0.1V_{P-P}$      |     |     | -2  | dB    |

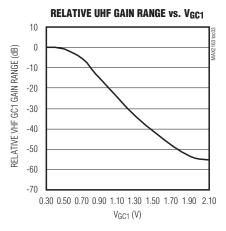

| RF Gain Control Range (GC1)        |                                                                           | 40  | 52  |     | dB    |

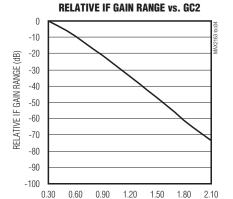

| Analog IF Gain Control Range (GC2) |                                                                           | 60  | 76  |     | dB    |

| In-Band IM3                        | (Note 3)                                                                  |     | -40 |     | dBc   |

| Out-of-Band IIP3                   | (Note 4)                                                                  |     | 30  |     | dBm   |

| Input P <sub>1dB</sub>             | In-band CW tone, V <sub>GC1</sub> = V <sub>GC2</sub> = 2.1V               |     | 0   |     | dBm   |

| Image Rejection                    | $T_A = +25^{\circ}C, +85^{\circ}C$                                        | 40  | 49  |     | dB    |

| Noise Figure                       | T <sub>A</sub> = +25°C, 470MHz < f <sub>RF</sub> < 806MHz                 |     | 3.2 | 5.3 | dB    |

| OPTIONAL UHF TRACKING FILTER       |                                                                           |     |     |     |       |

| Center Frequency                   |                                                                           |     | 640 |     | MHz   |

| Nominal 3dB Bandwidth              | LEXTU = 18nH, Q <sub>MIN</sub> = 35                                       |     | 320 |     | MHz   |

| WIDEBAND RF OVERLOAD DETECTOR      |                                                                           |     |     |     |       |

| Typical RF Attack Point            | Relative to RFAGC attack point                                            |     | +28 |     | dB    |

## **AC ELECTRICAL CHARACTERISTICS (continued)**

(MAX2163 Evaluation Kit,  $V_{CC}$  = +2.4V to +3.47V,  $f_{RF}$  = 557.143MHz,  $f_{LO}$  = 557.714MHz,  $f_{IF}$  = 571kHz,  $f_{XTAL}$  = 36MHz,  $V_{GC1}$  =  $V_{GC2}$  = 0.3V (maximum gain), default register settings, RF input signals as specified, IF output load as specified,  $T_{A}$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{CC}$  = +2.5V,  $T_{A}$  = +25°C,  $\overline{SHDN}$  =  $V_{CC}$ , STBY = GND, unless otherwise noted.) (Note 1)

| PARAMETER                           | CONDITIONS                           | MIN      | TYP  | MAX   | UNITS             |

|-------------------------------------|--------------------------------------|----------|------|-------|-------------------|

| IF POWER DETECTOR                   |                                      | '        |      |       | '                 |

| Minimum Attack Point                |                                      |          | -66  |       | dBm               |

| Maximum Attack Point                |                                      |          | -52  |       | dBm               |

| Detector Accuracy                   |                                      |          | 1.5  |       | dB                |

|                                     | PDBW[1:0]=00                         |          | 43   |       |                   |

| 0.10 5                              | PDBW[1:0]=01                         |          | 26   |       | ]<br>  NALL_      |

| 3dB Frequency Response              | PDBW[1:0]=10                         |          | 17   |       | MHz               |

|                                     | PDBW[1:0]=11                         |          | 13   |       | 1                 |

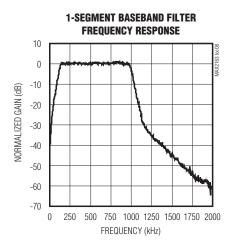

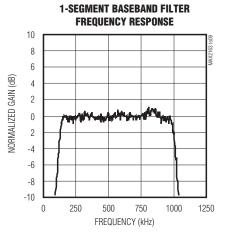

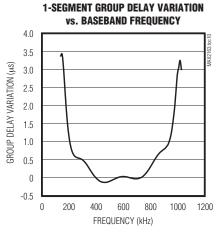

| LOW-IF FILTER RESPONSE              |                                      | <b>'</b> |      |       | '                 |

| Center Frequency                    |                                      |          | 571  |       | kHz               |

| 10 111 5                            | ±219kHz offset from center frequency | -2.8     |      | +2.8  | in.               |

| 1-Segment Mode Frequency Response   | 1MHz offset from center frequency    |          | -80  |       | dB                |

| LOW-IF OUTPUT CHARACTERISTICS       |                                      | '        |      |       |                   |

| Nominal Output-Voltage Swing        | $R_{LOAD} = 10k\Omega II10pF$        |          | 225  |       | mV <sub>P-P</sub> |

| Output Impedance                    | Single-ended, real                   |          | 31   |       | Ω                 |

| FREQUENCY SYNTHESIZER               |                                      | •        |      |       | •                 |

| N-Divider Frequency Range           |                                      | 90       |      | 804   | MHz               |

| N-Divider Range                     |                                      | 256      |      | 4095  | _                 |

| Reference Divider Frequency Range   |                                      | 32       |      | 36    | MHz               |

| Reference Divider Range (R)         |                                      | 112      |      | 280   | _                 |

| Phase Detector Comparison Frequency |                                      | 1/7      |      | 2/7   | MHz               |

| PLL Referred Phase Noise Floor      | f <sub>COMP</sub> = 2/7MHz           |          | -153 |       | dBc/Hz            |

| Spurious Products                   | f <sub>COMP</sub> spurious           |          | -70  |       | dBc               |

|                                     | CP bits = 00                         | 1.0      | 1.5  | 2.0   |                   |

| Observed Develop October Occurrent  | CP bits = 01                         | 1.4      | 2.0  | 2.6   | ] ^               |

| Charge-Pump Output Current          | CP bits = 10                         | 1.8      | 2.5  | 3.3   | mA                |

|                                     | CP bits = 11                         | 2.1      | 3.0  | 3.9   | 1                 |

| VOLTAGE-CONTROLLED OSCILLATOR AN    | ID LO GEN                            | •        |      |       | •                 |

| Guaranteed VCO Frequency Range      |                                      | 1890     |      | 3216  | MHz               |

| Guaranteed LO Frequency Range       |                                      | 472.5    |      | 804.0 | MHz               |

|                                     | foffset = 1kHz                       |          | -82  |       |                   |

|                                     | foffset = 10kHz                      |          | -87  |       | ]                 |

| LO Phase Noise                      | fOFFSET = 100kHz                     |          | -108 |       | dBc/Hz            |

|                                     | fOFFSET = 1MHz                       |          | -128 |       | ]                 |

|                                     | foffset > 10MHz                      |          | -140 |       | ]                 |

## **AC ELECTRICAL CHARACTERISTICS (continued)**

(MAX2163 Evaluation Kit,  $V_{CC} = +2.4V$  to +3.47V,  $f_{RF} = 557.143$ MHz,  $f_{LO} = 557.714$ MHz,  $f_{IF} = 571$ kHz,  $f_{XTAL} = 36$ MHz,  $V_{GC1} = V_{GC2} = 0.3V$  (maximum gain), default register settings, RF input signals as specified, IF output load as specified,  $T_{A} = -40^{\circ}$ C to  $+85^{\circ}$ C, unless otherwise noted. Typical values are at  $V_{CC} = +2.5V$ ,  $T_{A} = +25^{\circ}$ C,  $\overline{SHDN} = V_{CC}$ ,  $\overline{STBY} = \overline{GND}$ , unless otherwise noted.) (Note 1)

| PARAMETER                       | CONDITIONS                           | MIN | TYP | MAX | UNITS            |

|---------------------------------|--------------------------------------|-----|-----|-----|------------------|

| CRYSTAL OSCILLATOR INPUT (XTAL) |                                      | •   |     |     | •                |

| Frequency Range                 |                                      | 32  |     | 36  | MHz              |

| Input Capacitance               | Crystal load capacitance             |     | 8   |     | рF               |

| Input Overdrive Level           | AC-coupled sine wave input           | 0.5 |     | 1.5 | V <sub>P-P</sub> |

| Input Negative Resistance       | f <sub>XTAL</sub> = 36MHz            |     | 575 |     | Ω                |

| REFERENCE OSCILLATOR BUFFER OL  | JTPUT (XTALOUT)                      |     |     |     |                  |

| Output Frequency Range          |                                      | 16  |     | 18  | MHz              |

| Output Voltage Swing            | $Z_L = 4k\Omega$ II10pF              | 0.5 |     | 1.0 | V <sub>P-P</sub> |

| Output Buffer Divide Range      |                                      | 2   |     | 2   | _                |

| Output Duty Cycle               |                                      | 45  |     | 55  | %                |

| Output Turn-On Time             | XTAL amplitude > 0.5V <sub>P-P</sub> |     |     | 4   | ms               |

- Note 1: Min and max values are production tested at T<sub>A</sub> = +85°C. Min and max limits at T<sub>A</sub> = -40°C and +25°C are guaranteed by design and characterization.

- Note 2: IFOUT output voltage level met over this range.

- Note 3: In-band IM3 is measured with two tones at  $f_{LO}$  450kHz and  $f_{LO}$  550kHz. The RFAGC is engaged and set for the default attack point of -58dBm. IFL[1:0] = 01, RFVGA = MXR = 1. V<sub>GC2</sub> is adjusted to maintain 225mV<sub>P-P</sub> at IF<sub>OUT</sub>. Input power levels (tone 1 plus tone 2) up to -10dBm and > 30dBc for levels from -10dBm to 0dBm.

- Note 4: V<sub>GC1</sub> is set for maximum attenuation (2.1V) and V<sub>GC2</sub> is adjusted to maintain 225mV<sub>P-P</sub> at I<sub>FOUT</sub> for an equivalent 0dBm input desired level. Closed loop, attack point at -58dBm, f<sub>RF</sub> = 767.143MHz, f<sub>LO</sub> = 767.714MHz, f<sub>RF1</sub> = f<sub>RF</sub> + 4.25MHz, f<sub>RF2</sub> = f<sub>RF</sub> + 8MHz, -10dBm/tone. RFGR = 1, RFVGA = 1, and MXR = 1.

### 標準動作特性

(MAX2163 Evaluation Kit,  $V_{CC}$  = +2.5V, default register settings,  $V_{GC1}$  =  $V_{CG2}$  = 0.3V,  $V_{IFOUT}$  = 225m $V_{P-P}$ ,  $f_{LO}$  = 557.714MHz,  $T_A$  = +25°C, unless otherwise noted.)

SUPPLY VOLTAGE (V)

V<sub>GC2</sub> (V)

## 標準動作特性(続き)

(MAX2163 Evaluation Kit,  $V_{CC}$  = +2.5V, default register settings,  $V_{GC1}$  =  $V_{CG2}$  = 0.3V,  $V_{IFOUT}$  = 225m $V_{P-P}$ ,  $f_{LO}$  = 557.714MHz,  $T_A$  = +25°C, unless otherwise noted.)

## XTAL PORT INPUT IMPEDANCE vs. XTAL FREQUENCY

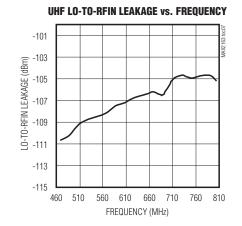

UHF LO PHASE NOISE AT 10kHz OFFSET vs. Channel Frequency

## 端子説明 \_\_\_\_\_\_

| 端子          | 名称      | 機能                                                                                                                                                 |

|-------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | STBY    | デバイススタンバイ。論理ハイに接続するとデバイスはスタンバイモードになります。論理ローに接続すると、通常の動作になります。この端子はSTBYビットと論理OR接続されます。                                                              |

| 2           | SHDN    | デバイスシャットダウン。論理ローに接続するとデバイスはシャットダウンモードになります。                                                                                                        |

| 3           | LEXTU   | オプションのUHFトラッキングフィルタインダクタ。18nHのインダクタをこの端子とグランド間に接続してください。                                                                                           |

| 4, 8, 9, 10 | N.C.    | 無接続。PCBのグランドプレーンに接続してください。                                                                                                                         |

| 5           | VCCLNA  | LNA用のDC電源。+2.5Vの低ノイズ電源に接続してください。端子に可能な限り近づけて配置した 0.1µFのコンデンサでGNDにバイパスしてください。コンデンサのビアは他のグランド接続と共用しないでください。                                          |

| 6           | VCCRF   | RF回路用のDC電源。+2.5Vの低ノイズ電源に接続してください。端子に可能な限り近づけて配置した 0.1µFのコンデンサでGNDにバイパスしてください。コンデンサのビアは他のグランド接続と共用しないでください。                                         |

| 7           | UHFIN   | UHF 50Ω RF入力。内部にDCブロッキングコンデンサを組み込んでいます。                                                                                                            |

| 11          | GC1     | RF利得制御入力。閉ループRFAGCモード(PDBM[1:0] = 11)において、GC1とグランド間にコンデンサを接続すると、AGCの応答時間が設定されます。開ループRFAGCモード(PDBM[1:0] = 10)において、GC1はRFAGCを制御するハイインピーダンスのアナログ入力です。 |

| 12          | Vccif   | IF回路用のDC電源。+2.5Vの低ノイズ電源に接続してください。端子に可能な限り近づけて配置した 0.1μFのコンデンサでGNDにバイパスしてください。コンデンサのビアは他のグランド接続と共用しないでください。                                         |

| 13          | GC2     | IF利得制御入力。ハイインピーダンスのアナログ入力。                                                                                                                         |

| 14          | VCCBIAS | バイアス回路用のDC電源。+2.5Vの低ノイズ電源に接続してください。端子に可能な限り近づけて配置した0.1μFのコンデンサでGNDにバイパスしてください。コンデンサのビアは他のグランド接続と共用しないでください。                                        |

| 15          | IFOUT   | 低IF出力。DCブロッキングコンデンサが必要です。                                                                                                                          |

| 16          | PWRDET  | 低インピーダンスのパワー検出出力バッファ。ビットPDBM[1:0]がこの出力端子の機能を制御します。<br>表6を参照してください。                                                                                 |

| 17          | SCL     | 2線式シリアルクロックインタフェース。V <sub>CCDIG</sub> に対するプルアップ抵抗が必要です。                                                                                            |

| 18          | SDA     | 2線式シリアルデータインタフェース。V <sub>CCDIG</sub> に対するプルアップ抵抗が必要です。                                                                                             |

## 端子説明(続き)\_\_\_\_\_\_

| 端子 | 名称                 | 機能                                                                                                                 |

|----|--------------------|--------------------------------------------------------------------------------------------------------------------|

| 19 | Vccdig             | ディジタルロジック回路用のDC電源。+2.5Vの低ノイズ電源に接続してください。端子に可能な限り近づけて配置した0.1µFのコンデンサでGNDにバイパスしてください。コンデンサのビアは他のグランド接続と共用しないでください。   |

| 20 | MUX                | デバイスTEST。詳細は表14を参照してください。                                                                                          |

| 21 | XTAL               | 内部のコルピッツ発振器のベースコンタクト。詳細は「標準アプリケーション回路」を参照してください。                                                                   |

| 22 | XTALOUT            | 水晶発振器のバッファ出力。外部回路の駆動には、DCブロッキングコンデンサを使用する必要があります。                                                                  |

| 23 | V <sub>CCSYN</sub> | シンセサイザ回路用のDC電源。+2.5Vの低ノイズ電源に接続してください。端子に可能な限り近づけて配置した0.1µFのコンデンサでGNDにバイパスしてください。コンデンサのビアは他のグランド接続と共用しないでください。      |

| 24 | CPOUT              | チャージポンプ出力。この出力は可能な最短の接続でPLLループフィルタ入力に接続してください。                                                                     |

| 25 | GNDSYN             | シンセサイザグランド。PCBのグランドプレーンに接続してください。グランドビアは他のグランド接続と共用しないでください。                                                       |

| 26 | VTUNE              | ハイインピーダンスのVCO調整入力。可能な限り短い接続で、PLLループフィルタ出力をこの端子に直接、接続してください。                                                        |

| 27 | LDO                | 内部LDOバイパス。端子に可能な限り近づけて配置した470nFのコンデンサでGNDにバイパスしてください。コンデンサのビアは他のグランド接続と共用しないでください。                                 |

| 28 | Vccvco             | VCO回路用のDC電源。+2.5Vの低ノイズ電源に接続してください。端子に可能な限り近づけて配置した<br>0.1µFのコンデンサでGNDにバイパスしてください。コンデンサのビアは他のグランド接続と共用しな<br>いでください。 |

| _  | EP                 | エクスポーズドパッド。適正なRF性能と熱消費の強化のために基板のグランドプレーンに均等に半田付けしてください。電気的な接続ポイントとして意図しないでください。                                    |

//I/XI/M \_\_\_\_\_\_

| 詳細」 |  |  |  |

|-----|--|--|--|

|     |  |  |  |

#### レジスタの説明

MAX2163には16の設定用レジスタと2つの読取り専用レジスタがあります。注:すべての設定用レジスタはデバイスの起動後または電圧低下状態(V<sub>CC</sub>が1V以下に低下する状態)から回復し100µs以後に書込みが行われる

ようにしてください。フォローアップとして、チャネル/ 周波数設定に必要なレジスタ(レジスタ00~08)を再度 書き込みするか、または単にすべてのレジスタを再度 書き込みしてください。表1~15に記載されたデフォ ルト値は参考用です。ユーザー側ですべてのレジスタ値 を書き込んでください(「Factory Use Only」の値も含む)。

### 表1. I<sup>2</sup>Cおよび4線式レジスタの構成

| DECICTED           | DEGIGTED             | DEAD/          | DEGIGTED            |       |       |       | M     | SB    |       |       |       |

|--------------------|----------------------|----------------|---------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| REGISTER<br>NUMBER | REGISTER<br>NAME     | READ/<br>WRITE | REGISTER<br>ADDRESS |       |       |       | DATA  | BYTE  |       |       |       |

|                    |                      |                | 7.221.200           | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

| 00                 | IF Filter            | Read/<br>Write | 0x00                | TUN2  | TUN1  | TUN0  | FLTS  | IFL1  | IFL0  | PDBW1 | PDBW0 |

| 01                 | VAS                  | Read/<br>Write | 0x01                | 1     | VASS  | VAS   | CPS   | ADL   | ADE   | LTC1  | LTC0  |

| 02                 | VCO                  | Read/<br>Write | 0x02                | 0     | VCO1  | VCO0  | VSB3  | VSB2  | VSB1  | VSB0  | VCOB  |

| 03                 | PDET/<br>RF-FILT     | Read/<br>Write | 0x03                | PDBM1 | PDBM0 | PDET2 | PDET1 | PDET0 | RFLT2 | RFLT1 | RFLT0 |

| 04                 | MODE                 | Read/<br>Write | 0x04                | RFVB  | RFFB  | HSLS  | 0     | 0     | 0     | 0     | 0     |

| 05                 | R-Divider<br>MSB     | Read/<br>Write | 0x05                | R8    | R7    | R6    | R5    | R4    | R3    | R2    | R1    |

| 06                 | R-Divider<br>LSB/CP  | Read/<br>Write | 0x06                | CP1   | CP0   | 0     | DRFD  | RFDA1 | RFDA0 | 1     | R0    |

| 07                 | N-Divider<br>MSB     | Read/<br>Write | 0x07                | N11   | N10   | N9    | N8    | N7    | N6    | N5    | N4    |

| 08                 | N-Divider<br>LSB/LIN | Read/<br>Write | 0x08                | N3    | N2    | N1    | N0    | 0     | MIX   | RFVGA | STBY  |

| 09                 | STATUS               | Read<br>Only   | 0X09                | Х     | Х     | ADC2  | ADC1  | ADC0  | VCP1  | VCP0  | PWR   |

| 0A                 | VAS<br>STATUS        | Read<br>Only   | 0x0A                | VVCO1 | VVCO0 | VVSB3 | VVSB2 | VVSB1 | VVSB0 | VASA  | VASE  |

| 0B-11              | Factory<br>Use Only  | Read/<br>Write | 0x0B-<br>0x11       | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

## I<sup>2</sup>Cの読取り/書込みアドレス

MAX2163の $I^2$ Cの読取り/書込みアドレスはC1/C0です。 詳細は表2を参照してください。

## 表2. MAX2163のI<sup>2</sup>Cの書込みアドレス

| DEVICE<br>ADDRESS | ADDRESS<br>TYPE | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|-------------------|-----------------|----|----|----|----|----|----|----|----|

| C0                | WRITE           | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  |

| C1                | READ            | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 1  |

## 表3. IFフィルタのレジスタ

| BIT NAME  | BIT LOCATION<br>(0 = LSB) | DEFAULT | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------|---------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TUN[2:0]  | 7, 6, 5                   | 011     | Sets the IF filter center frequency. This filter's center frequency is trimmed at the factory, but can be manually adjusted by setting the FLTS bit and programming the TUN[2:0] bits as follows:  000 - 0.75 x f <sub>IF</sub> (Not factory tested.)  001 - 0.84 x f <sub>IF</sub> (Not factory tested.)  010 - 0.92 x f <sub>IF</sub> (Not factory tested.)  011 - f <sub>IF</sub> (571kHz)  100 - 1.08 x f <sub>IF</sub> (Not factory tested.)  110 - 1.25 x f <sub>IF</sub> (Not factory tested.)  111 - 1.33 x f <sub>IF</sub> (Not factory tested.) |

| FLTS      | 4                         | 0       | Selects which registers set low-IF bandpass filter center frequency and bandwidth.  0 = Selects internal factory set register.  1 = Selects manual trim register TUN[2:0] (Not factory tested).                                                                                                                                                                                                                                                                                                                                                           |

| IFL[1:0]  | 3, 2                      | 01      | Set the bias current for the low-IF circuits to provide for fine linearity adjustments. Program to 01 upon power-up.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PDBW[1:0] | 1, 0                      | 11      | Sets the IF power detector bandwidth.  00 = 43MHz bandwidth.  01 = 26MHz bandwidth.  10 = 17MHz bandwidth.  11 = 13MHz bandwidth.                                                                                                                                                                                                                                                                                                                                                                                                                         |

## 表4. VASレジスタ

| BIT NAME | BIT LOCATION<br>(0 = LSB) | DEFAULT | FUNCTION                                                                                                                                                                                                                                                     |

|----------|---------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Х        | 7                         | 1       | Factory use only. Must be programmed to 1 upon power-up.                                                                                                                                                                                                     |

| VASS     | 6                         | 0       | Controls the VCO autoselect (VAS) start conditions function.  0 = VAS starts from the current VCO/VCOSB loaded in the VCO[1:0] and VSB[3:0] registers.  1 = VAS starts from the currently used VCO and VCOSB.                                                |

| VAS      | 5                         | 1       | Controls the VCO autoselect (VAS) function.  0 = Disables the VCO autoselect function and allows manual VCO selection through the VCO[1:0] and VSB[3:0] bits.  1 = Enables the on-chip VCO autoselect state machine.                                         |

| CPS      | 4                         | 1       | Sets the charge-pump current selection mode between automatic and manual.  0 = Charge-pump current is set manually through the CP[1:0] bits.  1 = Charge-pump current is automatically selected. Also requires ADE, ADL, and VAS bits to be programmed to 1. |

| ADL      | 3                         | 0       | Enables or disables the VCO tuning voltage ADC latch.  0 = Disables the ADC latch.  1 = Latches the ADC value.                                                                                                                                               |

| ADE      | 2                         | 0       | Enables or disables VCO tuning voltage ADC.  0 = Disables ADC read.  1 = Enables ADC read.                                                                                                                                                                   |

| LTC[1:0] | 1, 0                      | 11      | Sets the VCO autoselect wait time.  00 = 14336/f <sub>XTAL</sub> .  01 = 24576/f <sub>XTAL</sub> .  10 = 34816/f <sub>XTAL</sub> .  11 = 45056/f <sub>XTAL</sub> .                                                                                           |

## 表5. VCOレジスタ

| BIT NAME | BIT LOCATION<br>(0 = LSB) | DEFAULT | FUNCTION                                                                                                                                                                                                                               |

|----------|---------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X        | 7                         | 0       | Factory use only. Must be programmed to 0 upon power-up.                                                                                                                                                                               |

| VCO[1:0] | 6, 5                      | 01      | Controls which VCO band is activated when using manual VCO programming mode. This also serves as the starting point for VCO autoselect mode when VASS = 0.  00 = Select VCO-0.  01 = Select VCO-1.  10 = Select VCO-2.  11 = Not used. |

## 表5. VCOレジスタ(続き)

| BIT NAME | BIT LOCATION<br>(0 = LSB) | DEFAULT | FUNCTION                                                                                                                                                                                                                                                                                                                   |

|----------|---------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSB[3:0] | 4, 3, 2, 1                | 0100    | Select a particular sub-band for each of the on-chip VCOs. Together with the VCO[1:0] bits a manual selection of a VCO band and a sub-band can be made. This also serves as the starting point for the VCO autoselect mode when VASS = 0.  0000 = Select sub-band 0.  0001 = Select sub-band 1  1111 = Select sub-band 15. |

| VCOB     | 0                         | 1       | Sets the VCO bias mode.  0 = Normal mode.  1 = Low-power mode.                                                                                                                                                                                                                                                             |

## 表6. PDET/RF-FILTレジスタ

| BIT NAME  | BIT LOCATION<br>(0 = LSB) | DEFAULT | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------|---------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PDBM[1:0] | 7, 6                      | 00      | Power detector and buffer mode.  00 = Power detector is enabled, PWRDET buffer is off. On-chip closed-loop RFAGC.  01 = Power detector is enabled, PWRDET buffer is on with detector RMS voltage output at PWRDET pin (RFAGC is open loop with RF gain controlled by voltage applied to GC1).  10 = Unused.  11 = Power detector is enabled; PWRDET buffer is on with the GC1 voltage output at PWRDET pin (on-chip closed loop RFAGC). |

| PDET[2:0] | 5, 4, 3                   | 100     | Sets the AGC attack point.  000 = -66dBm.  001 = -64dBm.  010 = -62dBm.  011 = -60dBm.  100 = -58dBm.  101 = -56dBm.  111 = -52dBm.                                                                                                                                                                                                                                                                                                     |

| RFLT[2:0] | 2, 1, 0                   | 011     | Sets the center frequency of the UHF tracking filter when used.  000 = Minimum frequency (see Table 17).  111 = Maximum frequency (see Table 17).                                                                                                                                                                                                                                                                                       |

### 表7. MODEレジスタ

| BIT NAME | BIT LOCATION<br>(0 = LSB) | DEFAULT | FUNCTION                                                                                                |

|----------|---------------------------|---------|---------------------------------------------------------------------------------------------------------|

| RFVB     | 7                         | 0       | Bypass 3rd-stage RFVGA. 0 = Enables 3rd-stage RFVGA. 1 = Disables the 3rd-stage RFVGA.                  |

| RFFB     | 6                         | 0       | Bypass integrated RF filter.  0 = Enables optional RF filter.  1 = Disables optional RF filter.         |

| HSLS     | 5                         | 0       | Selects between high-side and low-side LO injection.  1 = Low-side injection.  0 = High-side injection. |

| X        | 4, 3, 2, 1, 0             | 0       | Factory use only. Must be programmed to 0 upon power-up.                                                |

## 表8. R分周器MSBレジスタ

| BIT NAME | BIT LOCATION<br>(0 = LSB) | DEFAULT  | FUNCTION                                                                                                              |

|----------|---------------------------|----------|-----------------------------------------------------------------------------------------------------------------------|

| R[8:1]   | 7, 6, 5, 4, 3, 2,<br>1, 0 | 00111111 | Sets the PLL reference divider (R) number. Default R divide value is 126 decimal. R can range from 16 to 511 decimal. |

注:R分周器の値を変更する場合は、R分周器MSBとR分周器LSBの両方のレジスタをロードしなければなりません。それは両方とも、2重にバッファされているからです。

### 表9. R分周器LSB/CPレジスタ

| BIT NAME  | BIT LOCATION<br>(0 = LSB) | DEFAULT | FUNCTION                                                                                                                                                                                                                                                                                                         |

|-----------|---------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CP[1:0]   | 7, 6                      | 00      | Sets the charge-pump current.<br>00 = 1.5mA.<br>01 = 2mA.<br>10 = 2.5mA.<br>11 = 3mA.                                                                                                                                                                                                                            |

| X         | 5                         | 0       | Factory use only. Must be programmed to 0 upon power-up.                                                                                                                                                                                                                                                         |

| DRFD      | 4                         | 1       | Disable RF Detector  0 = Enables the wideband RF overload detector.  1 = Disables the wideband RF overload detector.                                                                                                                                                                                             |

| RFDA[1:0] | 3, 2                      | 11      | Sets the RF overload detector attack point (subtract 6dB to each if PDIQ = 0).  00 = +37dB relative to IF attack point setting.  01 = +34dB relative to IF attack point setting.  10 = +31dB relative to IF attack point setting.  11* = +28dB relative to IF attack point setting.  *Only 11 is factory tested. |

| X         | 1                         | 1       | Factory use only. Must be programmed to 1 upon power-up.                                                                                                                                                                                                                                                         |

| R0        | 0                         | 0       | LSB of reference divider number                                                                                                                                                                                                                                                                                  |

注:R分周器の値を変更する場合は、R分周器MSBとR分周器LSBの両方のレジスタをロードしなければなりません。それは両方とも、2重にバッファされているからです。

### 表10. N分周器MSBレジスタ

| BIT NAME | BIT LOCATION<br>(0 = LSB) | DEFAULT  | FUNCTION                                                                                                                                               |

|----------|---------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| N[11:4]  | 7, 6, 5, 4, 3, 2,<br>1, 0 | 01111010 | Sets the most significant bits of the PLL integer divide number (N). Default integer divider value is N = 1952 decimal. N can range from 1314 to 2687. |

注:N分周器の値を変更する場合は、N分周器MSBとN分周器LSBの両方のレジスタをロードしなければなりません。それは両方とも、2重にバッファされているからです。

## 表11. N分周器LSB/LINレジスタ

| BIT NAME | BIT LOCATION<br>(0 = LSB) | DEFAULT | FUNCTION                                                                                                                                                                                                    |

|----------|---------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N[3:0]   | 7, 6, 5, 4                | 0000    | Sets the least significant bits of the PLL integer divide number (N). Default integer divider value is N = 1952 decimal. N can range from 1314 to 2687.                                                     |

| X        | 3                         | 0       | Factory use only. Must be programmed to 0 upon power-up.                                                                                                                                                    |

| MIX      | 2                         | 0       | Sets linearity mode of mixers.  0 = Selects normal mode for mixer.  1 = Selects high linearity mode for mixer.                                                                                              |

| RFVGA    | 1                         | 0       | Sets linearity mode of 3rd-stage RFVGA.  0 = Selects normal mode for 3rd-stage RFVGA.  1 = Selects high linearity mode for 3rd-stage RFVGA.                                                                 |

| STBY     | 0                         | 0       | Selects standby mode when STBY pin is logic-low.  0 = Normal operation.  1 = Disables the signal path and frequency synthesizer leaving only the serial bus, crystal oscillator, and XTALOUT buffer active. |

注:N分周器の値を変更する場合は、N分周器MSBとN分周器LSBの両方のレジスタをロードしなければなりません。それは両方とも、2重にバッファされているからです。

NIXIN

## 表12. STATUSレジスタ(読取り専用)

| BIT NAME | BIT LOCATION<br>(0 = LSB) | DEFAULT | FUNCTION                                                                                    |

|----------|---------------------------|---------|---------------------------------------------------------------------------------------------|

| X        | 7, 6                      | 1,1     | Unused                                                                                      |

| ADC[2:0] | 5, 4, 3                   |         | Indicates the 3-bit ADC conversion of the VCO tuning voltage (VTUNE).                       |

| VCP[1:0] | 2, 1                      |         | Reflects the charge-pump current setting, when CPS = 1.                                     |

| PWR      | 0                         | 1       | Logic-high indicates power has been cycled. STATUS register read operation resets PWR to 0. |

## 表13. VAS STATUSレジスタ(読取り専用)

| BIT NAME  | BIT LOCATION<br>(0 = LSB) | DEFAULT | FUNCTION                                                                                                                                                                           |

|-----------|---------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VVCO[1:0] | 7, 6                      | _       | Indicates which VCO has been selected by the VCO autoselect state machine. See Table 5 for VCO[1:0] definition.                                                                    |

| VVSB[3:0] | 5, 4, 3, 2                | _       | Indicates which sub-band of a particular VCO has been selected by either the VCO autoselect state machine. See Table 5 for VSB[2:0] definition.                                    |

| VASA      | 1                         | _       | Indicates whether VCO autoselection was successful.  0 = Indicates the autoselect function is disabled or unsuccessful VCO selection.  1 = Indicates successful VCO autoselection. |

| VASE      | 0                         | _       | Status indicator for the VCO autoselect function.  0 = Indicates the VCO autoselect function is active.  1 = Indicates the VCO autoselect function is inactive.                    |

## 表14. Factory Use Onlyレジスタ(OB、OC、OD、OE、OF、10、および11)

| BIT NAME | BIT LOCATION<br>(0 = LSB) | DEFAULT  | FUNCTION                                                 |

|----------|---------------------------|----------|----------------------------------------------------------|

| X        | 7, 6, 5, 4, 3,<br>2, 1, 0 | 00000000 | Factory use only. Must be programmed to 0 upon power-up. |

#### 端子およびビットの真理値表

MAX2163のSTBYはハードウェア端子またはレジスタビットのいずれかで制御することができます。おのおのの真理値表は表15に説明されています。

STBYモードをソフトウェア制御とするためには、STBY 端子をグランドに接続します。

#### 標準および高リニアリティモードの定義

表16は標準および高リニアリティモード用のレジスタ設定を定めます。

#### 2線式シリアルインタフェース

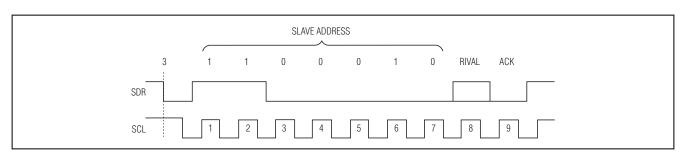

MAX2163はシリアルデータライン(SDA)およびシリアルクロックライン(SCL)で構成される、2線式 $I^2$ C対応シリアルインタフェースを備えています。SDAとSCLによってMAX2163とマスター間で最高400kHzのクロック周波数で双方向の通信が行えます。マスターデバイスはバス上でデータ転送を開始し、SCL信号を生成して、データ転送を許可します。MAX2163は、マスターとの間でデータを送受信する $I^2$ Cのスレーブデバイスとして機能します。正常な $I^2$ C動作のためには、MAX2163の $I^2$ Cの大いでは、MAX2163の $I^2$ Cの大いでは、MAX2163の $I^2$ Cの大いでは、MAX2163の $I^2$ Cがより、では、MAX2163の $I^2$ Cがより、

各SCLのクロックサイクルの間に1ビットが転送されます。MAX2163を入出力する1バイトの転送には最小9クロックサイクル(8ビットとACK/NACK)が必要です。SDA上のデータはSCLクロックパルスがハイの期間、安定でなければなりません。SCLがハイで安定している間のSDAの変化は、制御信号と見なされます(「STARTおよびSTOP条件」の項を参照してください)。バスがビジーでない場合、SDAとSCLの両方はハイのままです。

#### STARTおよびSTOP条件

マスターは、SCLがハイの間にSDAがハイからローに遷移するSTART条件(S)で送信を開始します。SCLがハイの間にSDAがローからハイに遷移するSTOP条件(P)で、マスターは送信を終了します。

#### 表15. スタンバイビットの真理値表

| STBY PIN | STBY BIT | DEVICE STATE           |

|----------|----------|------------------------|

| VCC      | 0        | Device in standby mode |

| VCC      | 1        | Device in standby mode |

| GND      | 0        | Device in normal mode  |

| GND      | 1        | Device in standby mode |

# 表16. 通常および高リニアリティモード用のレジスタ設定

| BIT   | NORMAL<br>MODE | HIGH LINEARITY MODE |

|-------|----------------|---------------------|

| RFVGA | 0              | 1                   |

| MIX   | 0              | 1                   |

#### 肯定応答および否定応答条件

データ転送は、肯定応答ビット(ACK)または否定応答ビット(NACK)で区切られます。マスターとMAX2163 (スレーブ)はともに、肯定応答ビットを生成します。肯定応答を生成するには、受信側デバイスは肯定応答に関係するクロックパルス(第9パルス)の立上りエッジの前にSDAをローに強制し、クロックパルスがハイの間はローに維持する必要があります。

否定応答条件を生成するためには、受信側で肯定応答に 関連するクロックパルスの立上りエッジの前にSDAを ハイに強制して、クロックパルスがハイの期間にSDA のハイを維持します。肯定応答ビットの監視によって、 データ転送の不成功を検出することができます。不成功 なデータ転送は受信するデバイスがビジーか、または システムに障害が起こった場合に生じます。不成功な データ転送が起こった場合に生じます。不成功な データ転送が起こった場合、バスマスターは後に通信 を再試行しなければなりません。

#### スレーブアドレス

MAX2163は、通信を開始するためにSTART条件に続いて、デバイスに送信されなければならない7ビットの $I^2$ Cのスレーブアドレスを備えています。スレーブアドレスはC0またはC2がWRITE用に、C1またはC3がREAD用に内部で設定されます。表2を参照してください。

MAX2163は、START条件とその後に続く自身のスレーブアドレスを常時待機しています。デバイスが自身のスレーブアドレスを認識すると、そのデバイスはSDAラインを1クロック期間の間、ローに強制して肯定応答して、R/Wビットに従ってデータの受信または送信を行うことができます(図1)。

#### 書込みサイクル

書込みコマンド付きでアドレス指定されると、MAX2163は1つまたは連続する複数のレジスタへのマスターからの書込みを許可します。

バスマスターがSTART条件およびそれに続く7ビットのスレーブアドレスビットと1ビットの書込みビット(R/W = 0)を発行すると、書込みサイクルが開始されます。MAX2163は、スレーブアドレスバイトを正常に受信すると、ACKを発行します。次に、バスマスターは、所望の書込み先の先頭レジスタのアドレスを送信する必要があります(レジスタアドレスについては、表1を参照)。スレーブがそのアドレスに対して肯定応答すると、マスターは指定されたアドレスのレジスタに1バイトを書き込むことができます。データは、最上位ビット(MSB)から書き込まれます。データがレジスタに正常に書き込まれると、MAX2163は再びACKを発行します。マスターは、MAX2163が各正常転送に肯定応答すると、連続する内部レジスタにデータを継続して書き込むこと

ができるか、またはSTOP条件を発行して送信を終了することができます。書込みサイクルはマスターがSTOP条件を発行するまでは終了しません。

図2はそのレジスタの0~2にそれぞれ0x0E、0x08、および0xE1が書き込まれる例が示されています。

#### 読取りサイクル

読み取りコマンド付きでアドレス指定されると、MAX2163 はマスターが1つまたは複数の連続するレジスタから読み戻すことを許可します。

バスマスターがSTART条件およびそれに続く7ビットの スレーブアドレスビットと1ビットの書込みビット(R/W = 0)を発行すると、読取りサイクルが開始されます。 MAX2163は、スレーブアドレスバイトを正常に受信 すると、ACKを発行します。次に、バスマスターは、 所望の読取り先の先頭レジスタのアドレスを送信する 必要があります(レジスタアドレスについては、表1を 参照)。スレーブはそのアドレスを肯定応答します。次 に、START条件およびそれに続く7ビットのスレーブア ドレスビットと1ビットの読取りビット $(R/\overline{W} = 1)$ がマ スターによって発行されます。MAX2163は、スレーブ アドレスバイトを正常に受信すると、ACKを発行します。 MAX2163は、SCLクロックサイクルごとに、MSBを 先頭にデータの送信を開始します。9番目のクロックサ イクルで、マスターはACKを発行して連続レジスタの 読取りを続けるか、あるいはNACKを発行して送信を終 了することができます。読取りサイクルはマスターが STOP条件を発行するまでは終了しません。

図3はそのレジスタの0~2が読み戻されている例が示されています。

図1. MAX2163のスレーブアドレスバイト

| START | WRITE 0B/CE<br>ADDRESS | R/W | ACK | WRITE REGISTER<br>ADDRESS | ACK | WRITE DATA TO<br>REGISTER 0x00 | ACK | WRITE DATA TO<br>REGISTER 0x01 | ACK | WRITE DATA TO<br>REGISTER 0x02 | ACK | STOP |

|-------|------------------------|-----|-----|---------------------------|-----|--------------------------------|-----|--------------------------------|-----|--------------------------------|-----|------|

| SIARI | 1100000                | 0   | _   | 0x00                      | _   | 0x0E                           | _   | 0x0E                           | _   | 0xE1                           | _   | 510P |

|       |                        |     |     |                           |     |                                |     |                                |     |                                |     |      |

図2. おのおの0x0E、0x08、および0xE1の0~2の書込みレジスタ。

| S<br>T | DEVICE<br>ADDRESS | R/W | A | REGISTER<br>ADDRESS | A | S<br>T | DEVICE<br>ADDRESS | R/W | A | REG 00<br>DATA | A | REG 01<br>DATA | A | REG 02<br>DATA | N<br>A | S      |

|--------|-------------------|-----|---|---------------------|---|--------|-------------------|-----|---|----------------|---|----------------|---|----------------|--------|--------|

| R      | 1100000           | 0   | K | 00000000            | K | R      | 1100000           | 1   | K | XXXXXXXX       | K | XXXXXXXX       | K | XXXXXXXX       | C<br>K | 0<br>P |

図3. 読取りレジスタからの受信データ

#### アプリケーション情報

#### RF入力(UHFIN)

MAX2163のUHFIN入力は内部で50 $\Omega$ に整合されています。

#### RF利得制御(GC1)

MAX2163は、端子GC1によって制御される多段階のRF可変利得アンプを備え、54dB (typ)を超えるRF利得制御範囲を提供します。電圧制御範囲は、0.3V (最大利得)~2.1V (最小利得)です。RF利得制御は、開ループ制御またはオンチップのIFパワー検出器と組み合わせて閉ループのRF自動利得制御(AGC)用に設定することができます。AGCの応答時間を設定するには、GC1とグランド間にコンデンサを接続してください。詳細については、「閉ループRF利得制御」の項を参照してください。

#### オプションのRFトラッキングフィルタ

MAX2163はRFVGAの第3段の出力にオプションのRFトラッキングフィルタを備えています。このフィルタは MODEレジスタに示されるRFLTビットによって制御されます。表7を参照してください。フィルタをイネーブルにするためには、RFFBビットを0に設定し、フィルタをディセーブルにするためにはRFFBビットを1に設定します。正しい中心周波数の設定のためには表17を参照してください。RFトラッキングフィルタを使用しない場合は、18nHのインダクタを取り付けないでください。

表17. RFLT[2:0]の中心周波数設定

| RFLT | UHF (MHz) |

|------|-----------|

| 000  | 470–488   |

| 001  | 488–512   |

| 010  | 512–542   |

| 011  | 542–572   |

| 100  | 572–608   |

| 101  | 608–656   |

| 110  | 656–710   |

| 111  | 710–806   |

#### RF過負荷検出器

MAX2163はRF過負荷検出を備えています。RF過負荷 検出回路は、表10 (R分周器LSB/CPレジスタ)に示すよ うに、DRFDビットによってイネーブルまたはディセー ブルされます。

#### IF利得制御(GC2)

MAX2163は、65dBを超えるIF利得制御範囲のIF可変利得アンプを備えています。電圧制御VGC2の範囲は、0.3V (最大利得) $\sim$ 2.1V (最小利得)です。IF VGAはチャネルデコーダによって制御されます。

#### IFパワー検出器

MAX2163は真のRMS IFパワー検出器をミキサ出力に可変帯域幅付きで備えています。パワー検出器回路はPDET/RF-FILTレジスタ(表6)のPDBM[1:0]ビットによってイネーブルまたはディセーブルされます。アタックポイントはPDET/RF-FILTレジスタのPDET[2:0]ビットによって設定することができます(アタックポイントの設定の要約は表6を参照してください)。

PWRDET端子はオンチップの閉ループAGCを使用する場合のGC1電圧か、またはオフチップの閉ループAGC方式で使用するIFパワー検出器のRMS電圧のいずれかの低インピーダンスでバッファされ、スケール変換された値を供給するように設定可能です。この端子の出力電圧範囲は0.3V~2.1Vで、2.1Vが最大のRF入力パワーを示します。この出力によってベースバンドプロセッサが受信したRFパワーレベルを監視することが可能です。

オンチップの閉ループAGC機能を使用する場合(PDBM = 11)、PWRDETバッファはGC1電圧の低インピーダンスのバッファされた値を提供します。この出力を復調用LSIが監視してRFフロントエンドの状態を知り、実質的に他の回路(外部のLNA)またはさまざまな復調機能を制御するために使用することができます。PWRDET出力は全体の電力消費を低減するためにディセーブルにすることもできます(PDBM = 00)。

オフチップの閉ループAGC方式に使用するために、PWRDETのバッファ出力はIFパワー検出器のRMS電圧の低インピーダンスのスケール変換された値を提供するように設定可能です(PDBM = 10)。このモードでは、外部電圧はGC1端子に印加されて閉ループを構成します。

#### 閉ループRF利得制御

MAX2163は、GC1端子による開ループのRF利得制御またはオンチップのパワー検出器による閉ループのRF自動利得制御(AGC)のいずれかを提供可能です。自動RF利得制御はPDET/RF-FILTレジスタ(表6)に示すようにPDBM[1:0]ビットを00に設定するとイネーブルになります。PDBM[1:0]ビットを10に設定すると、GC1端子による開ループRF利得制御が可能になります。

RF AGCループがディセーブルされると、RF利得は、GC1 端子に印加される外部電圧によって制御されます。GC1 端子の入力電圧範囲は0.3V~2.1Vで、0.3Vが最大のRF利得を与えます。

RF AGCループがイネーブルされると、IFパワー検出器の出力は、内部でGC1入力に接続され、RF利得はパワー検出器の出力電圧によって制御されます。GC1端子とグランド間に接続された外付けのコンデンサが、AGCループの応答時間を設定します。ループ応答時間は、次式で計算されます。

$t_{SETTLING} = 41.7 \times R \times C_{EXT}$

ここで:

$R = 1k\Omega$

C<sub>EXT</sub>はGC1とグランド間の外付けコンデンサのファラッド値です。

AGCループのアタックポイント(RF入力のことです)は、 $-66dBm\sim-52dBm$ に設定することが可能で、これは PDET/RF-FILTレジスタのPDET[2:0]ビットによって 制御されます(表6)。

#### ハイサイドおよびローサイドの LOインジェクション

MAX2163では、MODEレジスタ(表7)のHSLSビットによって、ハイサイドまたはローサイドのLOインジェクションを選択することができます。ローサイドインジェクションを選択するにはHSLSを1に設定し、ハイサイドインジェクションを選択するには、HSLSを0に設定します。

#### IFフィルタ

IFフィルタの公称の中心周波数と帯域幅は、それぞれ 571kHzと860kHzです。

IFの帯域通過フィルタの中心周波数は出荷時に調整されています。しかし、出荷時調整をバイパスして中心周波数をIFフィルタレジスタのFLTSおよびTUN[2:0]ビットによって調整可能です(表3)。FLTSビットを0に設定すると、フィルタの中心周波数は出荷時の調整値が選択されます。FLTSビットを1に設定すると、フィルタの中心周波数はTUN[2:0]ビットによって調整することができます(表3)。

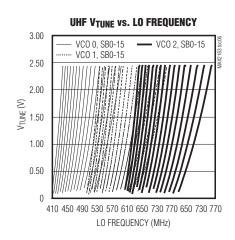

#### VCOの自動選択(VAS)

MAX2163は3つのVCOを備え、VCOごとに16個のサブバンドがあります。所望の局部発振器の周波数に適したVCOとVCOのサブバンドは、VCOレジスタのVCO[1:0] およびVSB[3:0]ビットを設定することによって、手動で選択することができます。選択されたVCOとサブバンドはVAS STATUSレジスタ(読取り専用)に示されています(表13)。

別の方法として、VCOおよびVCOサブバンドを自動的に選択するようにMAX2163を設定することができます。VCOの自動選択は、VASレジスタ(表4)のVASビットを設定するとイネーブルされ、N分周器LSBレジスタワードがロードされると開始されます。R分周器を変更する場合は、R分周器MSBとR分周器LSBの両方のレジスタを再設定しなければなりません。また、R分周器またはN分周器のMSBが変更される場合は、N分周器LSBレジスタも再設定してVCOの自動選択機能を開始しなければなりません。VASS = 0のとき、VCO[1:0]ビットおよびVSB[3:0]ビットで設定されるVCOおよびVCOサブバンドが自動VCO選択プロセスの開始点として機能します。VASS = 1のときは、現行のVCOおよびVCOサブバンドが自動VCO選択プロセスの開始点として機能します。

選択プロセスの間に、VAS STATUSレジスタのVASE ビットはクリアされ、自動選択機能がアクティブであることを示します。正常に終了すると、ビットVASEおよびVASAが設定され、選択されたVCOおよびサブバンドはVAS STATUSレジスタ(表13)に示されます。検出が不成功の場合は、VASAはクリアされ、VASEが設定されます。この処理は、検出は終了したが、VCOが見つからなかったことを示し、VCOの指定周波数範囲外の周波数に同調しようとしているときに発生します。

#### チャージポンプの選択(CPS)

MAX2163はチャージポンプ電流の手動選択(CPS = 0) または自動選択(CPS = 1)が可能です。手動モードでは、チャージポンプ電流は、R分周器のLSBレジスタ(表9)のビットCP[1:0]によって設定されます。自動選択モードでは、チャージポンプ電流は、VTUNE電圧および現行のVCOサブバンドに基づいて自動的に設定されます。ADE、ADL、およびVASの各ビットは1に設定しなければなりません。選択されたチャージポンプ電流は表18に示されています。

表18. CPS = 1 の場合のチャージポンプ 電流の設定値

| VSB[3] | ADC[2] | CP (mA) |  |  |

|--------|--------|---------|--|--|

| 0      | 0      | 2       |  |  |

| 0      | 1      | 3       |  |  |

| 1      | 0      | 1.5     |  |  |

| 1      | 1      | 2.5     |  |  |

#### 3ビットのアナログ-ディジタルコンバータ

MAX2163は3ビットのADCを備えています。その入力はVCOの調整端子(VTUNE)に接続されています。このADCはVCOのロック状態をチェックするために使用することができます。

表19は、ADC[2:0]の値に基づいたフェーズロックループ (PLL)のロック状態を要約したものです。VCOの自動選択 ルーチンでは、VASのロック範囲内にある1つのVCOの みが選択されます。このため、VCOが温度変化でドリフトしても、適正なロック範囲内に留まる余裕が生じます。

VCOの自動選択がディセーブルされているときは、VAS レジスタのADEビットを設定して、ADCを最初にイネーブルする必要があります。ADCの読取り値は、その後で ADCラッチビットを設定することによってラッチされます(ADL = 1)。ADCの値はSTATUSレジスタ(表12)に通知されます。

#### ループの時定数の選択

ループの時定数(LTC)機能によってVCO自動選択モードにある場合にADCの読取りの待機時間が設定されます。この待機時間は、VCOの選択が成功したかどうかを決定する前にPLLのセトリングにVCO自動選択回路がどの位の時間、待機するかを決定します。ループの時定数はVASレジスタ(表4)のLTC[1:0]ビットによって選択可能です。

#### XTALOUTバッファ

リファレンスバッファ/分周器は、外付けデバイスの駆動用に用意されています。内蔵の周波数分周器は2に固定されており、バッファは、 $4k\OmegaII10pF$ の負荷に最小 $500mV_{P-P}$ の信号スイングを $45\%\sim55\%$ の保証されたデューティサイクルで供給することができます。パワーアップまたはシャットダウンからの復帰時に、XTALOUTバッファは、内部タイマ回路によってさらに3ms (typ)の間、シャットダウンの状態に保持されます。これによって水晶発振器が正常に始動するために十分な時間が与えられ、出力バッファからの不要な寄生フィードバックを受けることはありません。

#### 表19. PLLとロック状態

| ADC[2:0] | PLL LOCK STATUS |

|----------|-----------------|

| 000      | Out of lock     |

| 001      | Locked          |

| 010      | Locked          |

| 011      | Not used        |

| 100      | Not used        |

| 101      | Locked          |

| 110      | Locked          |

| 111      | Unlocked        |

#### レイアウトについて

MAX2163の評価キットは、PCBレイアウトのガイドとして役立ちます。損失と放射を最小限に抑えるために、RF信号ラインを可能な限り短くしてください。すべての高周波トレースに対して制御されたインピーダンスを使用してください。RFトレース間に十分なグランドビアを使用して、望ましくないカップリングを最小限に抑えてください。端子の可能な限り近くに配置した $0.1\mu$ Fのコンデンサで、 $\Delta V_{CC}$ 端子をグランドにバイパスしてください。

オプションのUHFトラッキングフィルタを使用する場合は、外付けのインダクタを可能な限りICに近づけて、ICに可能な限り近い上面グランドに戻す接続にしてください。

水晶発振器が正常に起動するためには、水晶をMAX2163のXTAL端子(ピン21)の近くに配置してください。水晶のグランドはXTALに近いMAX2163のグランドパッドにクリアで短い配線で戻してください。XTAL(ピン21)とXTALOUT(ピン22)の基板トレース間の寄生容量を最小限に抑えてください。推奨する基板レイアウトについては、MAX2163の評価キットのデータシートを参照してください。

さらに、VCO、VTUNE、およびチャージポンプのグランドリターンには特別なレイアウトの考察が必要です(「標準アプリケーション回路」を参照してください)。LDOコンデンサ(C66)およびVCCVCOバイパスコンデンサ(C17)のグランドはピン28に近いMAX2163のグランドパッドに戻す配線にしなければなりません。C27、C28、およびC30のループフィルタグランド接続はピン25(GNDSYN)に戻るクリアな経路で全体のグランドプレーンに落とす前に相互に接続しなければなりません。

TQFNパッケージのデバイスを使用する場合は、適正な動作とするために、エクスポーズドパッドは基板のグランドプレーンに均等に半田付けしなければなりません。最大の熱消費とするためにエクスポーズドパッドの下には充分なビアを使用してください。

## 標準アプリケーション回路

### チップ情報

PROCESS: BICMOS

## パッケージ

最新のパッケージ情報とランドパターンは、 japan.maxim-ic.com/packagesをご参照ください。

| パッケージタイプ   | パッケージコード | ドキュメントNo.      |

|------------|----------|----------------|

| 28 TQFN-EP | T2855-8  | <u>21-0140</u> |

MIXIM

## 改訂履歴 \_\_\_\_\_

| 版数 | 改訂日   | 説明                                                                 | 改訂ページ                 |

|----|-------|--------------------------------------------------------------------|-----------------------|

| 0  | 7/08  | 初版                                                                 | _                     |

| 1  | 4/09  | 28ピンのMAX2163ETIをデータシートに加えて更新                                       | すべて                   |

| 2  | 10/09 | すべてのレジスタを設定するよう注意書きを追加。レジスタの表を訂正し、<br>すべてのFactory Use Onlyレジスタを記載。 | 10, 12, 14,<br>15, 16 |

## マキシム・ジャパン株式会社

〒169-0051東京都新宿区西早稲田3-30-16(ホリゾン1ビル) TEL. (03)3232-6141 FAX. (03)3232-6149

Maximは完全にMaxim製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。 Maximは随時予告なく回路及び仕様を変更する権利を留保します。

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_\_\_\_