# 700MHz~1200MHz、高リニアリティ、 ループバックミキサ内蔵、SPI制御DVGA

MAX2058

## 概要

MAX2058は高リニアリティ、デジタル可変利得アンプ(DVGA)で、62dBの総利得範囲と、+32.3dBmの標準出力IP3および+19dBmの出力P1dBレベルを提供するように設計されています。このデバイスは、シングル/マルチキャリア、700MHz~1200MHzのGSM/EDGE、cdma2000®、WCDMA、およびiDEN®基地局のほかに、RFIDハンドヘルドや携帯リーダなどの幅広いアプリケーションに最適です。MAX2058は、2個の5ビット、31dBデジタルアッテネータ、2段ドライバアンプ、ループバックミキサ、およびアッテネータを制御するシリアルインタフェースを内蔵する高水準の部品集積を実現しています。

MAX2058は1800MHz~2200MHzのDVGAであるMAX2059とピンコンパチブルであるため、共通のPCBレイアウトが両周波数帯域に使用されるアプリケーションでデザインインが容易になります。

MAX2058は、エクスポートドパッド付きの40ピンTQFNパッケージで提供されます。電気的性能は、-40°C~+85°Cの温度範囲にわたって保証されています。

## アプリケーション

GSM 850/GSM 900 2Gおよび2.5G EDGE基地局用

トランスマッタおよびパワーアンプ

セルラcdmaOne™、cdma2000、およびIntegrated

Digital Enhanced Network (iDEN)基地局用トランスマッタおよびパワーアンプ

WCDMA 850MHzおよびその他の3G基地局用

トランスマッタおよびパワーアンプ

トランスマッタ利得制御

レシーバ利得制御

ブロードバンドシステム

自動試験機器

デジタルおよびスペクトラム拡散通信システム

マイクロ波地上波リンク

RFIDハンドヘルドおよび携帯リーダ

## 特長

- ◆ 出力IP3 : +32.3dBm (typ)

- ◆ 出力1dB圧縮ポイント : +19dBm (typ)

- ◆ RF周波数範囲 : 700MHz~1200MHz

- ◆ RF周波数範囲 : 1800MHz~2200MHz (MAX2059)

- ◆ 小信号利得 : 10.5dB (typ)

- ◆ 2つの独立した31dBアッテネータ段を内蔵し、1dBステップで62dBの総利得制御範囲を生成

- ◆ 3線式SPI™/MICROWIRE™対応

- ◆ 内蔵ループバックミキサでTx/Rxの自己診断

- ◆ +5Vの単一電源動作

- ◆ 外付け電流設定抵抗器でスケーラブルなデバイス電源

- ◆ 鉛フリーパッケージを提供

## 型番

| PART         | TEMP RANGE     | PIN-PACKAGE                     | PKG CODE |

|--------------|----------------|---------------------------------|----------|

| MAX2058ETL   | -40°C to +85°C | 40 Thin QFN-EP**<br>(6mm x 6mm) | T4066-3  |

| MAX2058ETL-T | -40°C to +85°C | 40 Thin QFN-EP**<br>(6mm x 6mm) | T4066-3  |

| MAX2058ETL+  | -40°C to +85°C | 40 Thin QFN-EP**<br>(6mm x 6mm) | T4066-3  |

| MAX2058ETL+T | -40°C to +85°C | 40 Thin QFN-EP**<br>(6mm x 6mm) | T4066-3  |

\*\*EP = エクスポートドパッド。

+は鉛フリーパッケージを示します。

T = テープ&リール。

ピン配置/ファンクションダイアグラムはデータシートの最後に記載されています。

SPIはMotorola, Inc.の商標です。

MICROWIREはNational Semiconductor Corp.の商標です。

cdma2000はTelecommunications Industry Associationの登録商標です。

iDENはMotorola, Inc.の登録商標です。

cdmaOneはCDMA Development Groupの商標です。

# 700MHz~1200MHz、高リニアリティ、 ループバックミキサ内蔵、SPI制御DVGA

## ABSOLUTE MAXIMUM RATINGS

|                                                       |                                   |

|-------------------------------------------------------|-----------------------------------|

| V <sub>CC</sub> to GND                                | -0.3V to +5.5V                    |

| RSET1, RSET2                                          | +1.2V to +4.0V                    |

| LBBIAS                                                | (V <sub>CC</sub> - 1.5V) to +5.5V |

| LB_EN, DATA, CS, CLK                                  | -0.3V to (V <sub>CC</sub> + 0.3V) |

| ATTEN_INA, ATTEN_INB, ATTEN_OUTA, ATTEN_OUTB          |                                   |

| Input Power                                           | +24dBm                            |

| AMPIN, Differential LO Input Power                    | +12dBm                            |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |                                   |

| 40-Pin TQFN (derated 26.3mW/°C above +70°C)           | 2100mW                            |

|                                      |                 |

|--------------------------------------|-----------------|

| Operating Temperature Range (Note A) | -40°C to +85°C  |

| Junction Temperature                 | +150°C          |

| θ <sub>JC</sub>                      | 10°C/W          |

| θ <sub>JA</sub>                      | 38°C/W          |

| Storage Temperature Range            | -65°C to +150°C |

| Lead Temperature (soldering, 10s)    | +300°C          |

**Note A:** T<sub>C</sub> is the temperature on the exposed paddle of the package.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## DC ELECTRICAL CHARACTERISTICS

(MAX2058 Typical Application Circuit, V<sub>CC</sub> = +4.75V to +5.25V, R<sub>1</sub> = 1.2kΩ, R<sub>2</sub> = 3.92kΩ, R<sub>3</sub> = 2kΩ, T<sub>C</sub> = -40°C to +85°C. Typical values are at V<sub>CC</sub> = +5.0V and T<sub>C</sub> = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                  | SYMBOL          | CONDITIONS                                                                                                                                   | MIN  | TYP | MAX  | UNITS |

|--------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|-------|

| Supply Voltage                             | V <sub>CC</sub> | Reference to V <sub>CC</sub> , V <sub>CC</sub> LB, V <sub>CC</sub> LOGIC, V <sub>CC</sub> BIAS1, V <sub>CC</sub> BIAS2, V <sub>CC</sub> CAMP | 4.75 | 5.0 | 5.25 | V     |

| Total Supply Current                       | I <sub>CC</sub> | LB mixer disabled (LB_EN = 1)                                                                                                                |      | 134 | 156  | mA    |

|                                            |                 | LB mixer enabled (LB_EN = 0)                                                                                                                 |      | 158 | 186  |       |

| <b>LOGIC INPUTS (DATA, CS, CLK, LB_EN)</b> |                 |                                                                                                                                              |      |     |      |       |

| Input High Voltage                         | V <sub>IH</sub> |                                                                                                                                              | 2.4  |     |      | V     |

| Input Low Voltage                          | V <sub>IL</sub> |                                                                                                                                              |      | 0.8 |      | V     |

| Input Current with Logic-High              | I <sub>IH</sub> |                                                                                                                                              | 0.01 |     |      | μA    |

| Input Current with Logic-Low               | I <sub>IL</sub> |                                                                                                                                              | 0.01 |     |      | μA    |

## AC ELECTRICAL CHARACTERISTICS

(MAX2058 Typical Application Circuit, V<sub>CC</sub> = +4.75V to +5.25V, digital attenuators set for maximum gain, 700MHz ≤ f<sub>RF</sub> ≤ 1200MHz, 40MHz ≤ f<sub>LO</sub> ≤ 100MHz, T<sub>C</sub> = -40°C to +85°C. Typical values are at V<sub>CC</sub> = 5.0V, P<sub>IN</sub> = 0dBm, f<sub>RF</sub> = 940MHz, P<sub>LO</sub> = -6dBm, f<sub>LO</sub> = 45MHz, f<sub>LBOUT</sub> = f<sub>RF</sub> - f<sub>LO</sub>, and T<sub>C</sub> = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                          | SYMBOL           | CONDITIONS                                                                                                     | MIN                             | TYP    | MAX  | UNITS |

|------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------|--------|------|-------|

| RF Frequency (Note 2)              |                  | MAX2058                                                                                                        | 700                             | 1200   |      | MHz   |

|                                    |                  | MAX2059                                                                                                        | 1800                            | 2200   |      |       |

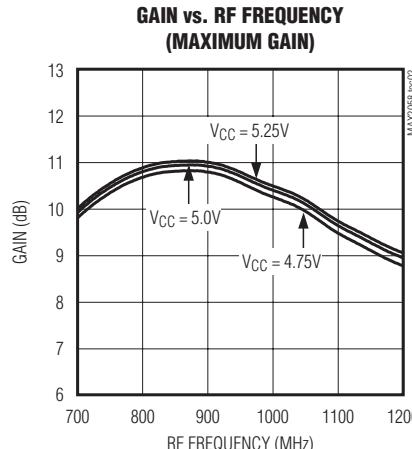

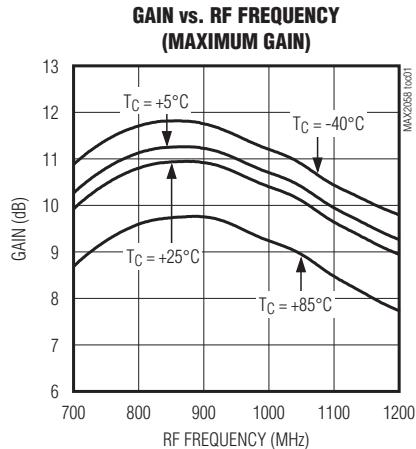

| Small-Signal Gain                  | A <sub>V</sub>   | f <sub>RF</sub> = 940MHz, T <sub>C</sub> = +25°C                                                               | 8.4                             | 10.5   | 12.8 | dB    |

| Gain Variation vs. Temperature     |                  | All attenuation settings                                                                                       | T <sub>C</sub> = -40°C to +25°C | -0.014 |      | dB/°C |

|                                    |                  |                                                                                                                |                                 | -0.021 |      |       |

| Output Power                       | P <sub>OUT</sub> | P <sub>IN</sub> = 0dBm, f <sub>RF</sub> = 940MHz, T <sub>C</sub> = +25°C                                       | 8.4                             | 10.5   | 12.8 | dBm   |

| Output Power Flatness              |                  | P <sub>IN</sub> = 0dBm                                                                                         | 800MHz to 900MHz                | 0.13   |      | dB    |

|                                    |                  |                                                                                                                | 900MHz to 1000MHz               | -0.52  |      |       |

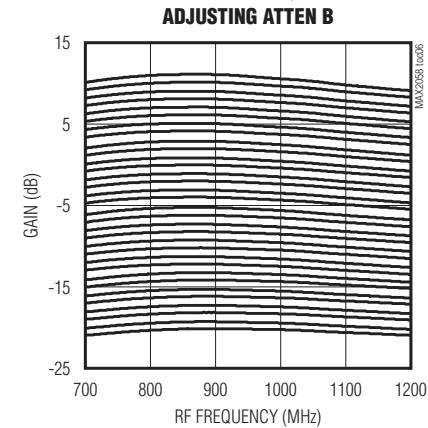

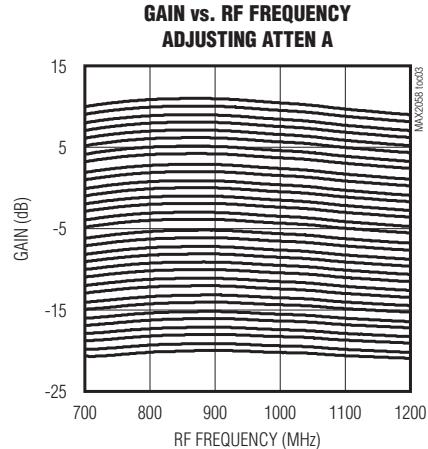

| Attenuation Range                  |                  |                                                                                                                |                                 | 62     |      | dB    |

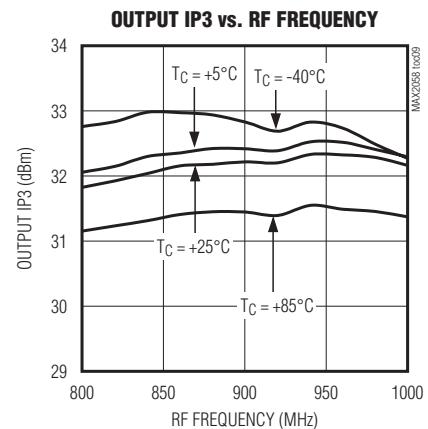

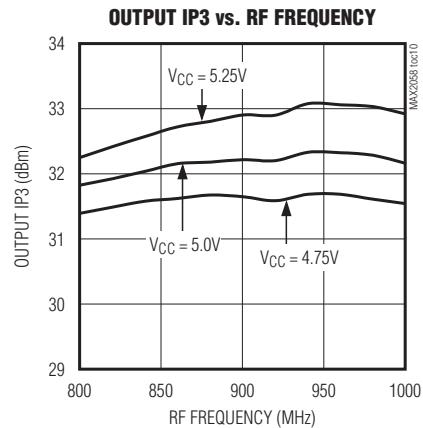

| Output Third-Order Intercept Point | OIP3             | Two tones: f <sub>RF1</sub> = 940MHz, f <sub>RF2</sub> = 941MHz, P <sub>OUT1</sub> = P <sub>OUT2</sub> = +5dBm |                                 | 32.3   |      | dBm   |

# 700MHz~1200MHz、高リニアリティ、 ループバックミキサ内蔵、SPI制御DVGA

MAX2058

## AC ELECTRICAL CHARACTERISTICS (continued)

(MAX2058 Typical Application Circuit,  $V_{CC} = +4.75V$  to  $+5.25V$ , digital attenuators set for maximum gain,  $700MHz \leq f_{RF} \leq 1200MHz$ ,  $40MHz \leq f_{LO} \leq 100MHz$ ,  $T_C = -40^\circ C$  to  $+85^\circ C$ . Typical values are at  $V_{CC} = 5.0V$ ,  $P_{IN} = 0dBm$ ,  $f_{RF} = 940MHz$ ,  $P_{LO} = -6dBm$ ,  $f_{LO} = 45MHz$ ,  $f_{LBOUT} = f_{RF} - f_{LO}$ , and  $T_C = +25^\circ C$ , unless otherwise noted.) (Note 1)

| PARAMETER                                      | SYMBOL            | CONDITIONS                              | MIN           | TYP   | MAX | UNITS |

|------------------------------------------------|-------------------|-----------------------------------------|---------------|-------|-----|-------|

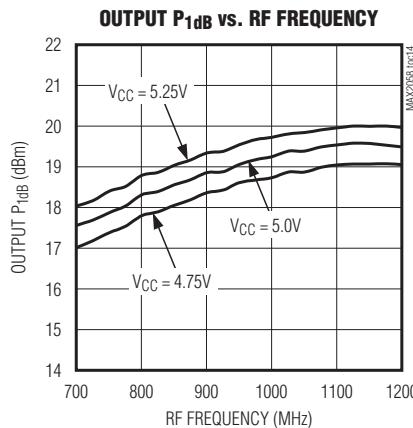

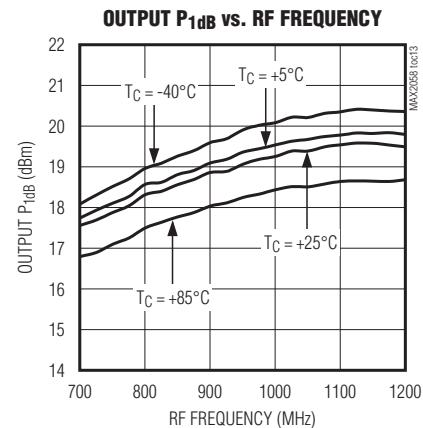

| Output -1dB Compression Point (Note 3)         | OP <sub>1dB</sub> |                                         |               | 19    |     | dBm   |

| RMS Error Vector Magnitude                     | EVM               | $P_{OUT} = +12dBm$ , EDGE modulation    |               | 0.5   |     | %     |

| Spurious Emissions in 30kHz Bandwidth (Note 4) |                   | $P_{OUT} = +12dBm$ , EDGE modulation    | 200kHz offset | -39.2 |     | dBc   |

|                                                |                   |                                         | 400kHz offset | -73.5 |     |       |

|                                                |                   |                                         | 600kHz offset | -82.7 |     |       |

|                                                |                   |                                         | 1.2MHz offset | -85.7 |     |       |

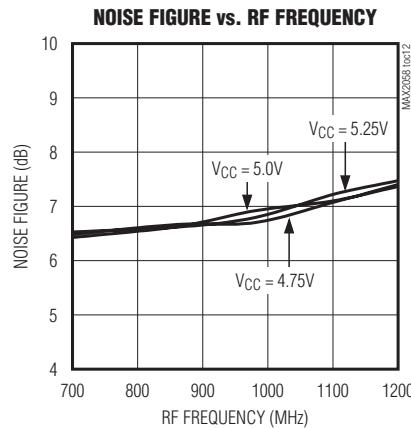

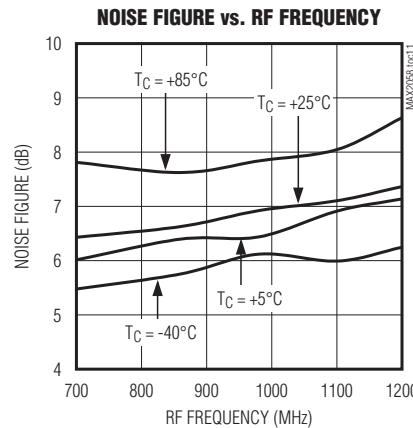

| Noise Figure                                   | NF                |                                         |               | 6.8   |     | dB    |

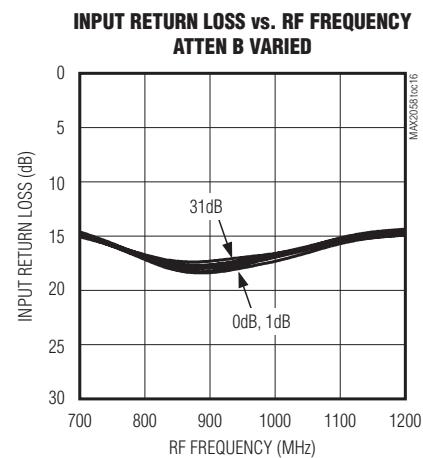

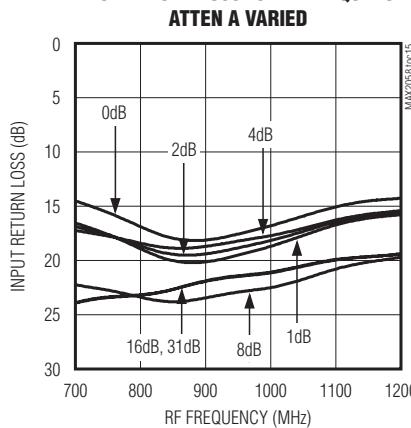

| Input Return Loss                              |                   | 50Ω source, minimum attenuation setting |               | 18    |     | dB    |

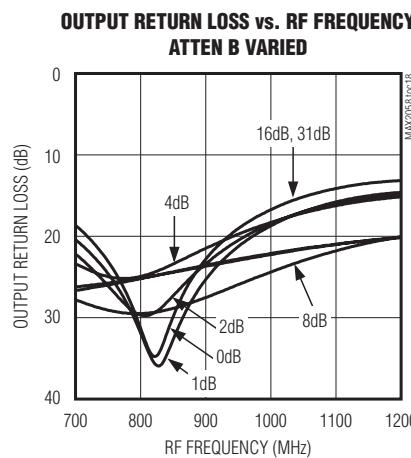

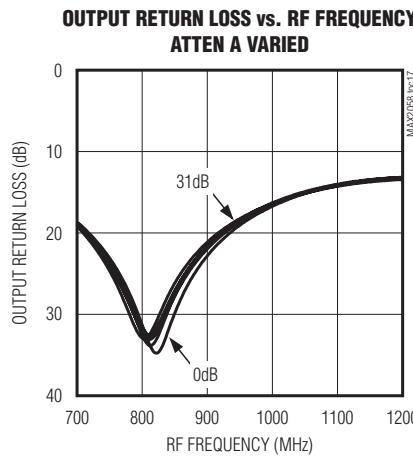

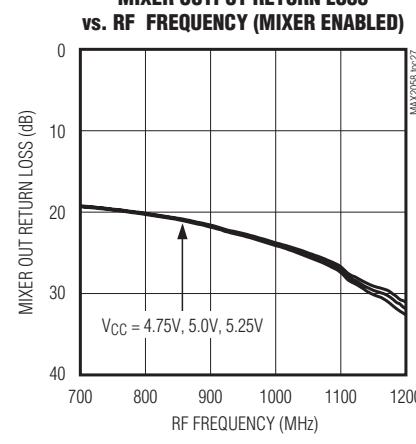

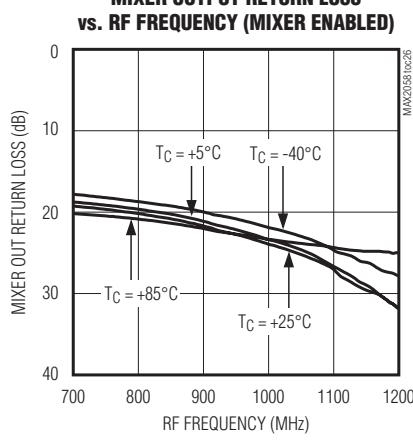

| Output Return Loss                             |                   | 50Ω load, minimum attenuation setting   |               | 20    |     | dB    |

## 5-BIT DIGITAL ATTENUATORS

|                                                 |      |                                                                                                                                                                                                                                             |              |  |       |

|-------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--|-------|

| Insertion Loss                                  |      | Attenuator measured separately $Z_S = Z_L = 50\Omega$                                                                                                                                                                                       | 3.3          |  | dB    |

| Input Third-Order Intercept Point               | IIP3 | Attenuator measured separately $Z_S = Z_L = 50\Omega$ , two tones: $f_{RF1} = 940MHz$ , $f_{RF2} = 941MHz$ , $P_{IN1} = P_{IN2} = +5dBm$                                                                                                    | 44           |  | dBm   |

| Control Range                                   |      |                                                                                                                                                                                                                                             | 31           |  | dB    |

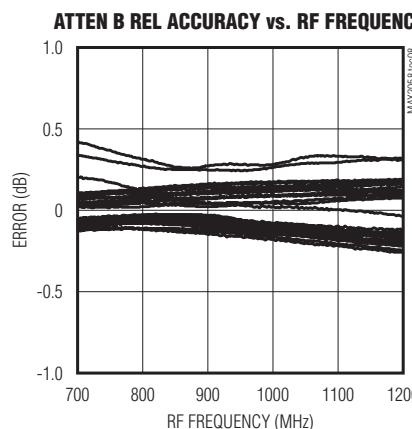

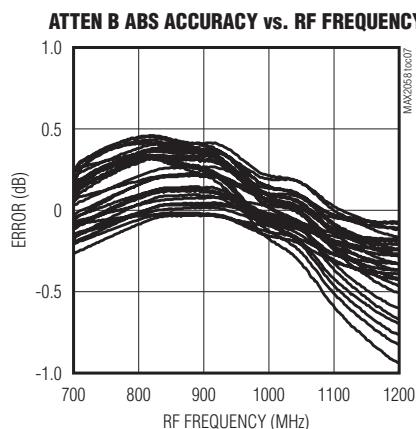

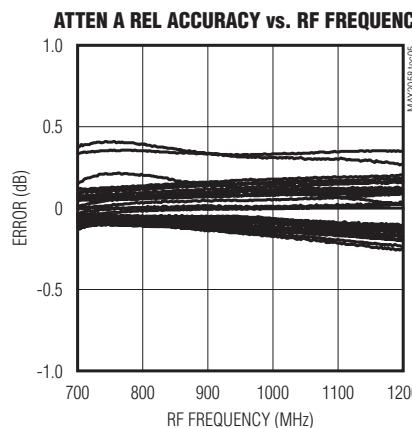

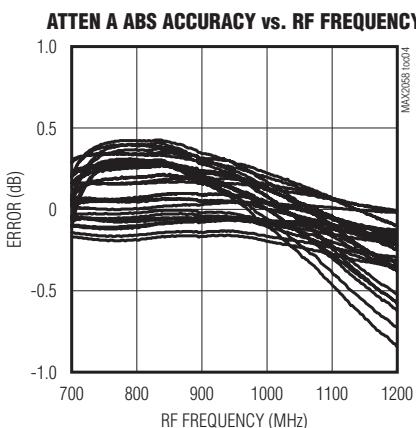

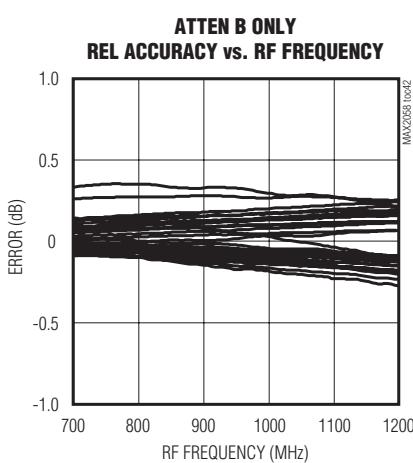

| Attenuation Step Size Variation vs. Frequency   |      | 800MHz to 900MHz                                                                                                                                                                                                                            | $\pm 0.08$   |  | dB    |

|                                                 |      | 900MHz to 1000MHz                                                                                                                                                                                                                           | $\pm 0.06$   |  |       |

| Attenuation Variation vs. Temperature           |      | 800MHz to 1000MHz, $T_C = -40^\circ C$ to $+25^\circ C$                                                                                                                                                                                     | $\pm 0.002$  |  | dB/°C |

|                                                 |      | 800MHz to 1000MHz, $T_C = +25^\circ C$ to $+85^\circ C$                                                                                                                                                                                     | $\pm 0.003$  |  |       |

| Step Size                                       |      |                                                                                                                                                                                                                                             | 1            |  | dB    |

| Relative Step Accuracy                          |      | 800MHz to 1000MHz                                                                                                                                                                                                                           | -0.2<br>+0.4 |  | dB    |

| Absolute Step Accuracy                          |      | 800MHz to 1000MHz                                                                                                                                                                                                                           | -0.2<br>+0.5 |  | dB    |

| Spurious Emissions in 300kHz Bandwidth (Note 5) |      | No RF input, attenuator A stepped from 0 to 2dB, 7dB to 9dB, 15dB to 17dB, 0 to 31dB, 31dB to 0dB, with attenuator B at 0dB; attenuator B stepped from 0 to 2dB, 7dB to 9dB, 15dB to 17dB, 0 to 31dB, 31dB to 0dB, with attenuator A at 0dB | -85          |  | dBm   |

| Switching Speed                                 |      | From chip select transitioning high to the output settling to within 1dB of steady state output                                                                                                                                             | 0.3          |  | μs    |

# 700MHz~1200MHz、高リニアリティ、 ループバックミキサ内蔵、SPI制御DVGA

## AC ELECTRICAL CHARACTERISTICS (continued)

(MAX2058 Typical Application Circuit,  $V_{CC} = +4.75V$  to  $+5.25V$ , digital attenuators set for maximum gain,  $700MHz \leq f_{RF} \leq 1200MHz$ ,  $40MHz \leq f_{LO} \leq 100MHz$ ,  $T_C = -40^\circ C$  to  $+85^\circ C$ . Typical values are at  $V_{CC} = 5.0V$ ,  $P_{IN} = 0dBm$ ,  $f_{RF} = 940MHz$ ,  $P_{LO} = -6dBm$ ,  $f_{LO} = 45MHz$ ,  $f_{LBOUT} = f_{RF} - f_{LO}$ , and  $T_C = +25^\circ C$ , unless otherwise noted.) (Note 1)

| PARAMETER                                   | SYMBOL   | CONDITIONS                                                                                               | MIN               | TYP   | MAX       | UNITS   |

|---------------------------------------------|----------|----------------------------------------------------------------------------------------------------------|-------------------|-------|-----------|---------|

| <b>LOOPBACK MIXER</b>                       |          |                                                                                                          |                   |       |           |         |

| LO Frequency (Note 2)                       | $f_{LO}$ |                                                                                                          | 40                | 100   |           | MHz     |

| LO Input Power                              | $P_{LO}$ |                                                                                                          |                   | -6    | 0         | dBm     |

| Output Power (Note 6)                       |          | $P_{IN} = +5dBm$ , $f_{RF} = 940MHz$ , $T_C = +25^\circ C$                                               | -14.7             | -12.7 | -10.8     | dBm     |

| Gain Accuracy                               |          | $P_{IN} = +5dBm$ , $T_C = -40^\circ C$ to $+25^\circ C$                                                  | 800MHz to 900MHz  |       | $\pm 1.7$ | dB      |

|                                             |          |                                                                                                          | 900MHz to 1000MHz |       | $\pm 1.7$ |         |

| Output Third-Order Intercept Point (Note 6) | OIP3     | Two tones: $f_{RF1} = 940MHz$ , $f_{RF2} = 940.2MHz$ , $P_{IN1} = P_{IN2} = +2dBm$ , $T_C = +25^\circ C$ |                   | 10.6  |           | dBm     |

| Output Noise Floor                          |          | $P_{IN} = +5dBm$                                                                                         |                   | -137  |           | dBc/Hz  |

| ON/OFF Switching Time                       |          | LB_EN enable time                                                                                        |                   | 0.12  |           | $\mu s$ |

|                                             |          | LB_EN disable time                                                                                       |                   | 0.12  |           |         |

| LBOUT to ATTEN_OUTB Isolation               |          | Mixer enabled, attenuators A and B both set to 31dB, $P_{IN} = +5dBm$                                    |                   | 67    |           | dB      |

| ATTEN_OUTB to LBOUT Isolation               |          | Mixer disabled, $P_{IN} = 0dBm$                                                                          |                   | 50    |           | dB      |

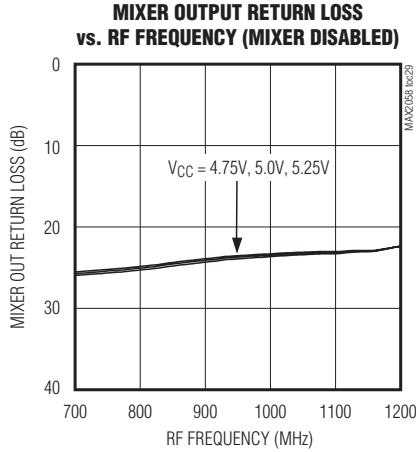

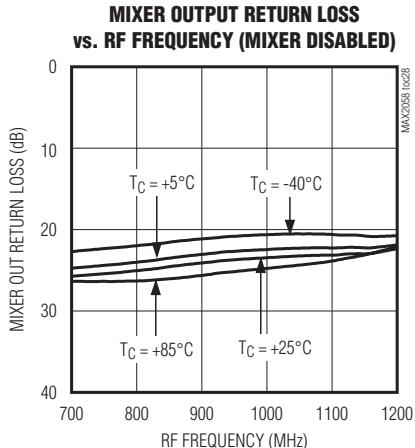

| Output Return Loss                          |          | Mixer enabled, $50\Omega$ load                                                                           |                   | 22    |           | dB      |

|                                             |          | Mixer disabled, $50\Omega$ load                                                                          |                   | 23    |           |         |

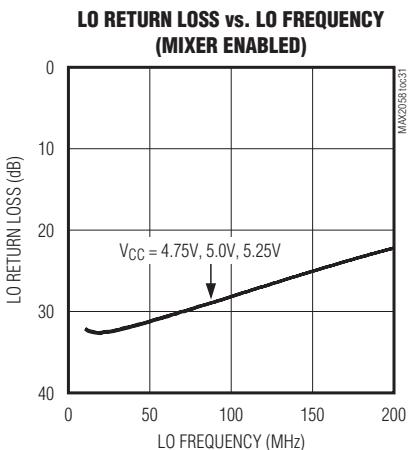

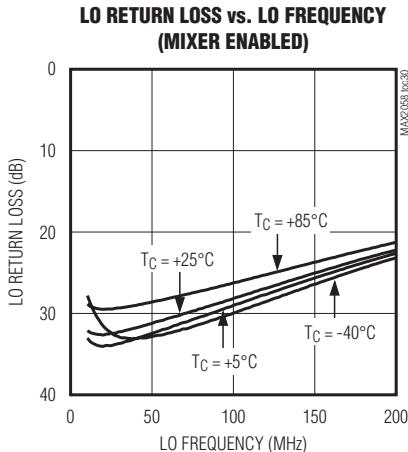

| LO Port Return Loss                         |          | 50 $\Omega$ source                                                                                       |                   | 32    |           | dB      |

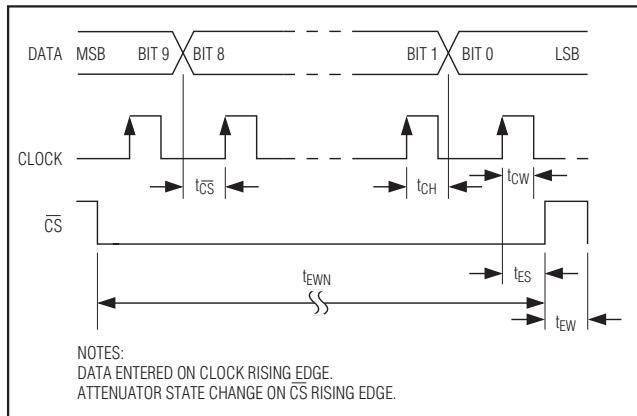

| <b>SERIAL PERIPHERAL INTERFACE (SPI)</b>    |          |                                                                                                          |                   |       |           |         |

| Maximum Clock Speed                         |          |                                                                                                          |                   | 38    |           | MHz     |

| Data to Clock Setup Time                    | tcs      |                                                                                                          |                   | 1     |           | ns      |

| Data to Clock Hold Time                     | tch      |                                                                                                          |                   | 9     |           | ns      |

| Clock to $\overline{CS}$ Setup Time         | tes      |                                                                                                          |                   | 4     |           | ns      |

| $\overline{CS}$ Positive Pulse Width        | tew      |                                                                                                          |                   | 18    |           | ns      |

| $\overline{CS}$ Negative Pulse Width        | tewn     |                                                                                                          |                   | 24    |           | ns      |

| CLOCK Pulse Width                           | tcw      |                                                                                                          |                   | 13    |           | ns      |

**Note 1:** All limits include external component losses. Output measurements taken at RFOUT or LBOUT ports of the *Typical Application Circuit*.

**Note 2:** Operating outside this range is possible, but with degraded performance of some parameters.

**Note 3:** Compression point characterized. It is advisable not to continuously operate the VGA RF input above +15dBm.

**Note 4:** Input RF source contribution to spurious emissions (Agilent ESG 4435B, PSA E4443A): 200kHz = -39.2dBc, 400kHz = -73.5dBc, 600kHz = -83.2dBc, 1.2MHz = -85.7dBc

**Note 5:** No SPI clock input applied.

**Note 6:** Guaranteed by design and characterization.

# 700MHz~1200MHz、高リニアリティ、 ループバックミキサ内蔵、SPI制御DVGA

MAX2058

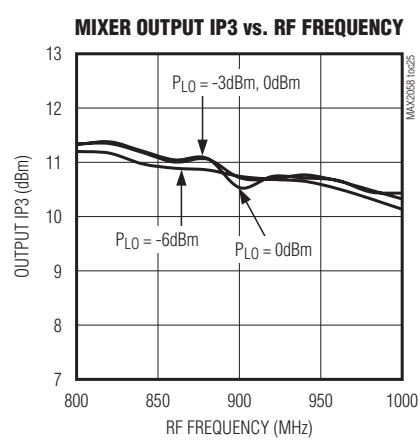

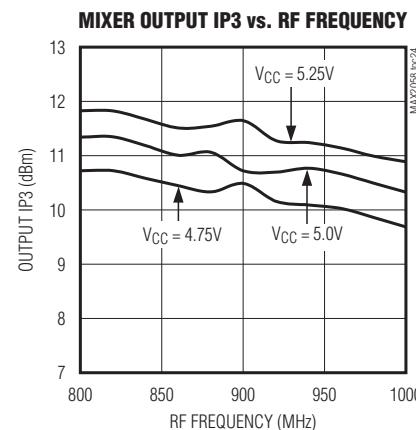

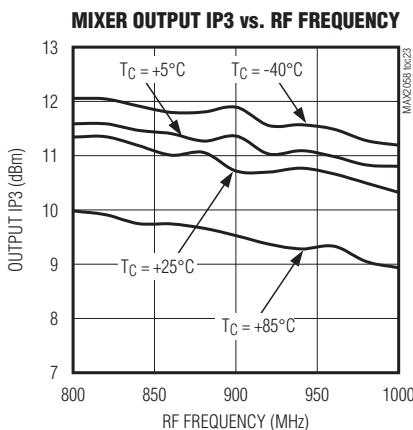

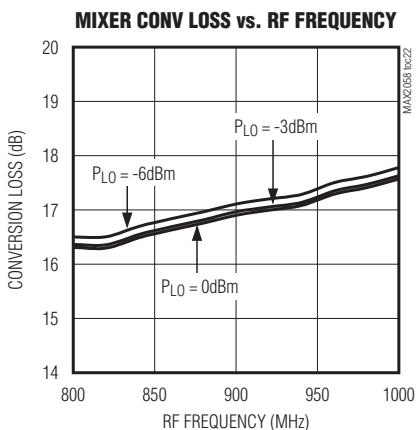

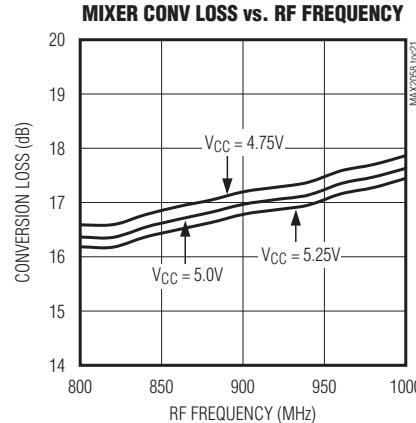

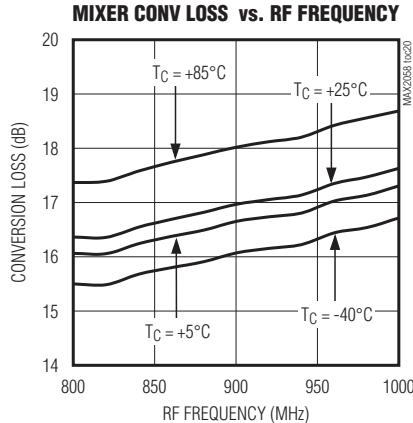

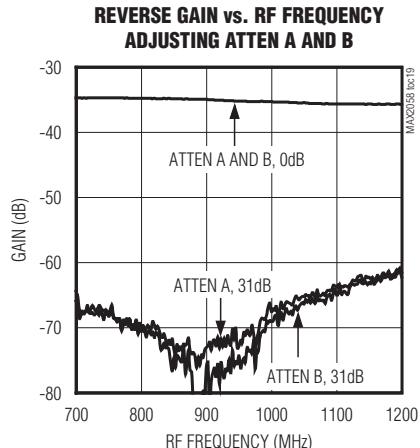

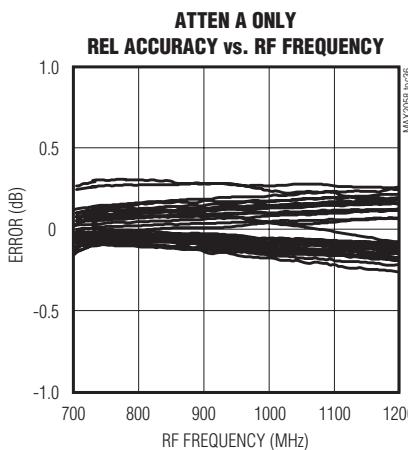

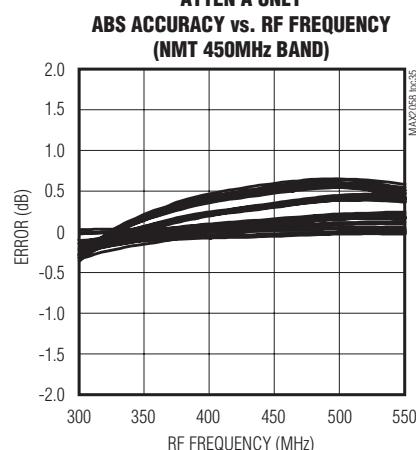

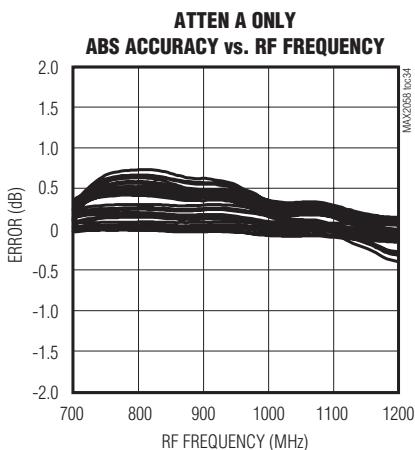

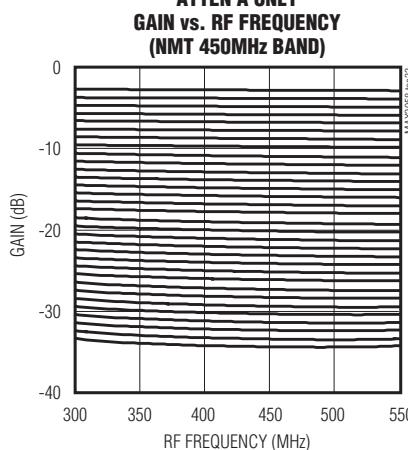

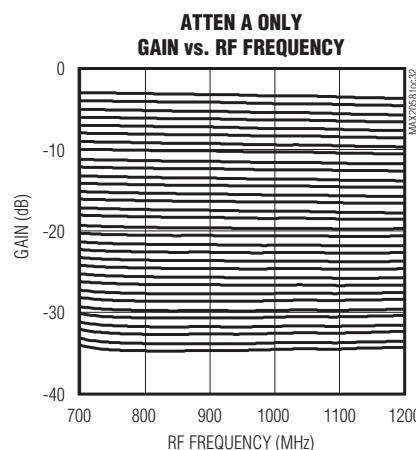

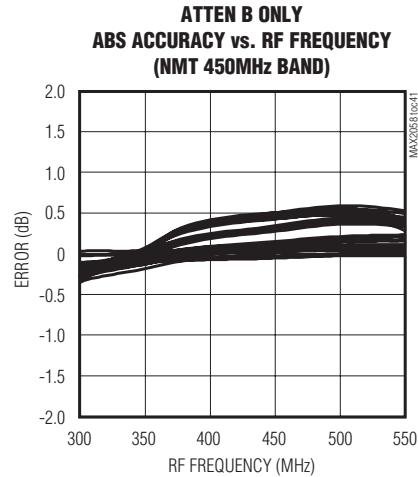

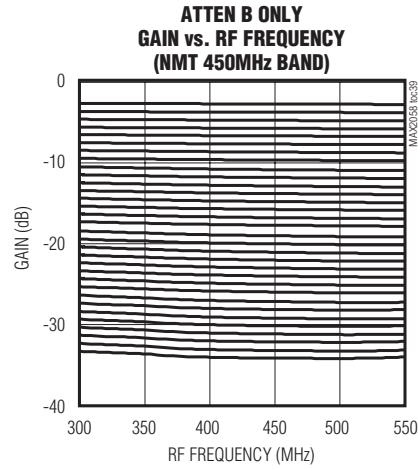

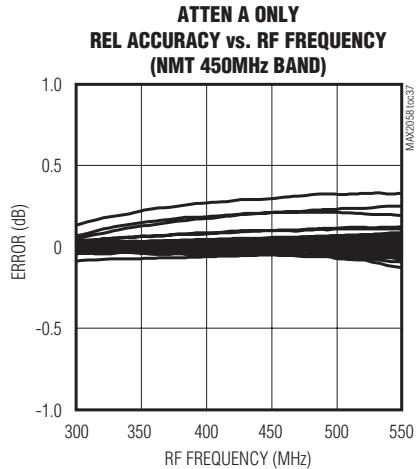

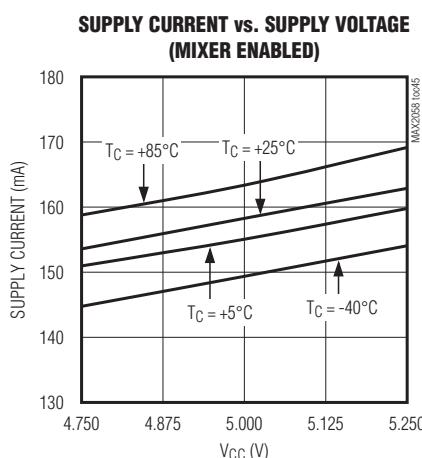

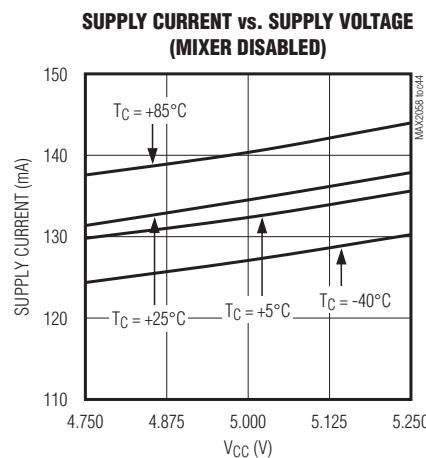

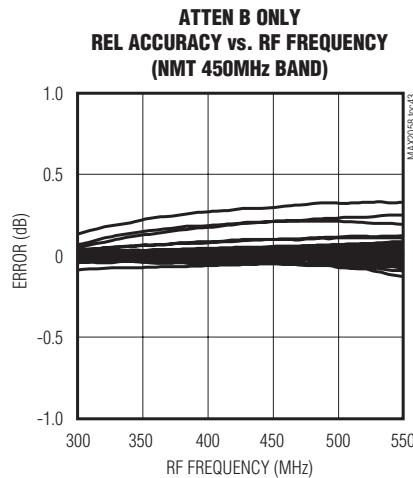

## 標準動作特性

(MAX2058 Typical Application Circuit,  $V_{CC} = +4.75V$  to  $+5.25V$ , digital attenuators set for maximum gain,  $700MHz \leq f_{RF} \leq 1200MHz$ ,  $40MHz \leq f_{LO} \leq 100MHz$ ,  $T_C = -40^{\circ}C$  to  $+85^{\circ}C$ . Typical values are at  $V_{CC} = 5.0V$ ,  $P_{IN} = 0dBm$ ,  $f_{RF} = 940MHz$ ,  $f_{LO} = 45MHz$ ,  $f_{LBOUT} = f_{RF} - f_{LO}$ , and  $T_C = +25^{\circ}C$ , unless otherwise noted.)

# 700MHz~1200MHz、高リニアリティ、 ループバックミキサ内蔵、SPI制御DVGA

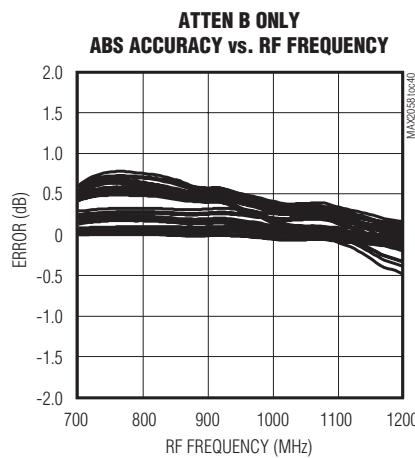

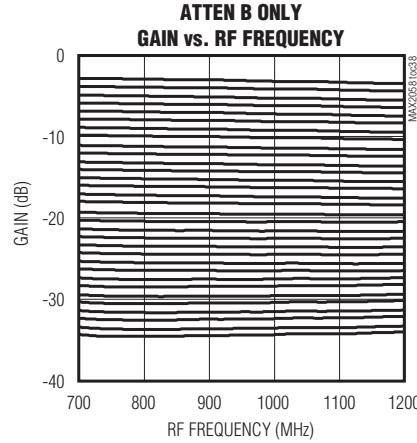

## 標準動作特性(続き)

(MAX2058 Typical Application Circuit,  $V_{CC} = +4.75V$  to  $+5.25V$ , digital attenuators set for maximum gain,  $700MHz \leq f_{RF} \leq 1200MHz$ ,  $40MHz \leq f_{LO} \leq 100MHz$ ,  $T_C = -40^{\circ}C$  to  $+85^{\circ}C$ . Typical values are at  $V_{CC} = 5.0V$ ,  $P_{IN} = 0dBm$ ,  $f_{RF} = 940MHz$ ,  $f_{LO} = 45MHz$ ,  $f_{LBOUT} = f_{RF} - f_{LO}$ , and  $T_C = +25^{\circ}C$ , unless otherwise noted.)

# 700MHz~1200MHz、高リニアリティ、 ループバックミキサ内蔵、SPI制御DVGA

MAX2058

## 標準動作特性(続き)

(MAX2058 Typical Application Circuit,  $V_{CC} = +4.75V$  to  $+5.25V$ , digital attenuators set for maximum gain,  $700MHz \leq f_{RF} \leq 1200MHz$ ,  $40MHz \leq f_{LO} \leq 100MHz$ ,  $T_C = -40^{\circ}C$  to  $+85^{\circ}C$ . Typical values are at  $V_{CC} = 5.0V$ ,  $P_{IN} = 0dBm$ ,  $f_{RF} = 940MHz$ ,  $f_{LO} = 45MHz$ ,  $f_{LBOUT} = f_{RF} - f_{LO}$ , and  $T_C = +25^{\circ}C$ , unless otherwise noted.)

# 700MHz~1200MHz、高リニアリティ、 ループバックミキサ内蔵、SPI制御DVGA

## 標準動作特性(続き)

(MAX2058 Typical Application Circuit,  $V_{CC} = +4.75V$  to  $+5.25V$ , digital attenuators set for maximum gain,  $700MHz \leq f_{RF} \leq 1200MHz$ ,  $40MHz \leq f_{LO} \leq 100MHz$ ,  $T_C = -40^{\circ}C$  to  $+85^{\circ}C$ . Typical values are at  $V_{CC} = 5.0V$ ,  $P_{IN} = 0dBm$ ,  $f_{RF} = 940MHz$ ,  $f_{LO} = 45MHz$ ,  $f_{LBOUT} = f_{RF} - f_{LO}$ , and  $T_C = +25^{\circ}C$ , unless otherwise noted.)

# 700MHz~1200MHz、高リニアリティ、 ループバックミキサ内蔵、SPI制御DVGA

MAX2058

## 標準動作特性(続き)

(MAX2058 Typical Application Circuit,  $V_{CC} = +4.75V$  to  $+5.25V$ , digital attenuators set for maximum gain,  $700MHz \leq f_{RF} \leq 1200MHz$ ,  $40MHz \leq f_{LO} \leq 100MHz$ ,  $T_C = -40^{\circ}C$  to  $+85^{\circ}C$ . Typical values are at  $V_{CC} = 5.0V$ ,  $P_{IN} = 0dBm$ ,  $f_{RF} = 940MHz$ ,  $f_{LO} = 45MHz$ ,  $f_{LBOUT} = f_{RF} - f_{LO}$ , and  $T_C = +25^{\circ}C$ , unless otherwise noted.)

# 700MHz~1200MHz、高リニアリティ、 ループバックミキサ内蔵、SPI制御DVGA

## 標準動作特性(続き)

(MAX2058 Typical Application Circuit,  $V_{CC} = +4.75V$  to  $+5.25V$ , digital attenuators set for maximum gain,  $700MHz \leq f_{RF} \leq 1200MHz$ ,  $40MHz \leq f_{LO} \leq 100MHz$ ,  $T_C = -40^{\circ}C$  to  $+85^{\circ}C$ . Typical values are at  $V_{CC} = 5.0V$ ,  $P_{IN} = 0dBm$ ,  $f_{RF} = 940MHz$ ,  $f_{LO} = 45MHz$ ,  $f_{LBOUT} = f_{RF} - f_{LO}$ , and  $T_C = +25^{\circ}C$ , unless otherwise noted.)

# 700MHz~1200MHz、高リニアリティ、 ループバックミキサ内蔵、SPI制御DVGA

MAX2058

## 端子説明

| 端子                                                                                | 名称         | 機能                                                                              |

|-----------------------------------------------------------------------------------|------------|---------------------------------------------------------------------------------|

| 1                                                                                 | LO+        | ループバックミキサのローカル発振器の正入力                                                           |

| 2                                                                                 | LO-        | ループバックミキサのローカル発振器の負入力                                                           |

| 3                                                                                 | VCCLB      | ループバックミキサの電源電圧。内蔵ループバックミキサの+5V電源。端子にできるだけ近接した0.1μFおよび100pFコンデンサでGNDにバイパスしてください。 |

| 4                                                                                 | LBOUT      | ループバックミキサのRF出力。50Ωに内部で整合されます。コンテンサでAC結合してください。                                  |

| 5                                                                                 | LB_EN      | ループバックミキサのロジック入力。ミキサをイネーブルするには、ロジックローに設定してください。ミキサをアセーブルするには、ロジックハイに設定してください。   |

| 6                                                                                 | DATA       | SPIデジタルデータ入力                                                                    |

| 7                                                                                 | CLK        | SPIクロック入力                                                                       |

| 8                                                                                 | CS         | SPIチップ選択入力                                                                      |

| 9                                                                                 | VCCLOGIC   | ロジック電源電圧。内部ロジック回路の+5V電源。端子にできるだけ近接した0.1μFおよび100pFコンテンサでGNDにバイパスしてください。          |

| 10, 11, 13,<br>14, 16, 17,<br>19, 22, 24,<br>25, 26, 30,<br>32, 34, 35,<br>37, 38 | GND        | グランド                                                                            |

| 12                                                                                | ATTEN_OUTB | アッテネータBの出力。50Ωに内部で整合されます。                                                       |

| 15                                                                                | VCC        | アッテネータBの電源。アッテネータBの+5V電源。端子にできるだけ近接した0.01μFおよび100pFコンテンサでGNDにバイパスしてください。        |

| 18                                                                                | ATTEN_INB  | アッテネータBの入力。50Ωに内部で整合されます。                                                       |

| 20                                                                                | RSET2      | 出力アンプのバイアス電流設定抵抗器。出力アンプ段のバイアス電流を設定します。3.92kΩの抵抗器をグランドに接続してください。                 |

| 21                                                                                | VCCBIAS2   | バイアス回路の電源電圧。内部バイアス回路の+5V電源。端子にできるだけ近接した0.1μFおよび1000pFコンテンサでGNDにバイパスしてください。      |

| 23                                                                                | AMPOUT     | RFアンプ出力。50Ωに内部で整合されます。                                                          |

| 27                                                                                | VCCAMP     | RFアンプの電源電圧。RFアンプの+5V電源。端子にできるだけ近接した0.1μFおよび1000pFコンテンサでGNDにバイパスしてください。          |

| 28                                                                                | AMPIN      | RFアンプ入力。50Ωに内部で整合されます。                                                          |

| 29                                                                                | VCCBIAS1   | バイアス回路の電源電圧。内部バイアス回路の+5V電源。端子にできるだけ近接した0.1μFおよび1000pFコンテンサでGNDにバイパスしてください。      |

| 31                                                                                | RSET1      | 入力アンプのバイアス電流設定抵抗器。入力アンプ段のバイアス電流を設定します。1.2kΩの抵抗器をグランドに接続してください。                  |

| 33                                                                                | ATTEN_OUTA | アッテネータAの出力。50Ωに内部で整合されます。                                                       |

| 36                                                                                | VCC        | アッテネータAの電源電圧。アッテネータAの+5V電源。端子にできるだけ近接した0.01μFおよび100pFコンテンサでGNDにバイパスしてください。      |

| 39                                                                                | ATTEN_INA  | アッテネータAの入力。50Ωに内部で整合されます。                                                       |

| 40                                                                                | LBBIAS     | ループバックミキサのバイアス電流設定抵抗器。ミキサのバイアス電流を設定します。2kΩの抵抗器をグランドに接続してください。                   |

| EP                                                                                | GND        | エクスポートドグランドパッド。複数ビアを使ってエクスポートドパッドをGNDに半田付けしてください。                               |

# 700MHz~1200MHz、高リニアリティ、ループバックミキサ内蔵、SPI制御DVGA

## 詳細

MAX2058は高リニアリティDVGAで、2個の5ビット、31dBデジタルアッテネータ、固定利得の2段ドライバアンプ、ループバックミキサ、およびアッテネータを制御するシリアルインターフェースから構成されています。高水準の部品集積によって、MAX2058は基地局用トランスマッタアプリケーションに最適です。MAX2058は、700MHz~1200MHzの周波数範囲で動作するように設計されています。MAX2058の総カスケード接続性能は、標準で10.5dBの利得、+32.3dBmのOIP3、19dBmのOP1dB、および62dBの総利得制御範囲をもたらします。

## 5ビットアッテネータ

MAX2058は2個の5ビットデジタルアッテネータを内蔵し、高ダイナミックレンジを実現します。各アッテネータはそれぞれ、31dBの制御範囲と1dBのステップサイズを備え、3線式SPIで設定されます。アッテネータ設定の詳細については、「アプリケーション情報」の項と表1を参照してください。これらのアッテネータを静的および動的パワー制御の両方に使用することができます。

表1. アッテネータの設定

| ATTENUATOR A (5 MSBs) | ATTENUATOR B (5 LSBs) |

|-----------------------|-----------------------|

| Bit 9 = 16dB step     | Bit 4 = 16dB step     |

| Bit 8 = 8dB step      | Bit 3 = 8dB step      |

| Bit 7 = 4dB step      | Bit 2 = 4dB step      |

| Bit 6 = 2dB step      | Bit 1 = 2dB step      |

| Bit 5 = 1dB step      | Bit 0 = 1dB step      |

図1. SPIタイミング図

## ドライバアンプ

MAX2058は、17.5dBの固定利得の2段式ミディアムパワー・アンプを内蔵しています。ドライバアンプ回路は、800MHz~1000MHzの周波数範囲の高リニアリティおよび中出力パワー能力に最適化されています。ドライバアンプは、基地局トランスマッタにおいて変調信号を增幅し、ハイパワーアンプを駆動することを目的としています。標準アプリケーションでは、ドライバアンプは2個のデジタルアッテネータ間にカスケード接続されます。「標準動作回路」を参照してください。

デジタルアッテネータやループバックミキサのみが使用されるアプリケーションでは、2段アンプ段をディセーブルすることができます。2段アンプをディセーブルするには、アンプ電源のVCCBIAS2、VCCAMP、VCCBIAS1、さらにアンプバイアス電流の設定用の入力RSET1、RSET2をグランドするか、または未接続状態にしてください。これによって、消費電流が標準状態で約132mA低減します。

## ループバックミキサ

MAX2058のループバックミキサは、700MHz~1200MHzのRF周波数範囲と40MHz~100MHzのLO周波数範囲で動作するように設計されたダブルバランスト、アクティブアーキテクチャを採用しています。ミキサのRFポートは、第1アッテネータ段の入力に(内蔵スイッチによって)内部で接続されています。ミキサのIFポートはシングルエンド50Ωインピーダンスに整合され、またLOポートには100Ωの差動入力インピーダンスが必要です。

ループバックミキサはセルラトランシーバの自己診断モードを容易にするため、ミキサの入力におけるTx帯域の信号を対応するRx帯域の上下に変換することができます。次に、この変換された信号をTx/Rx完全ループ診断用に無線のレシーバに戻すことができます。ループバックミキサは、LB\_ENによってイネーブルまたはディセーブルされます。ミキサをイネーブルするにはLB\_ENをロジックローに設定し、ミキサをディセーブルするにはLB\_ENをロジックハイ1に設定してください。

## アプリケーション情報

### SPIインターフェースおよびアッテネータの設定

2個の5ビットアッテネータは、10ビットワードを使って3線式SPI/MICROWIRE対応シリアルインターフェースを通じて設定されます。10ビットデータのビット9が、CSがハイかローかを問わず、クロックの立上りエッジで残りの全データビットを従えて、最初にシフトインされます。全データビットがシフトインされると、全ビットがCSの立上りエッジでアッテネータに送信されるため、減衰状態が変わります。標準的なSPI動作にするには、有効な10ビットデータセットの間、CSをロー

# 700MHz~1200MHz、高リニアリティ、ループバックミキサ内蔵、SPI制御DVGA

MAX2058

にプルしてください( $t_{EWN}$ )。この $\overline{CS}$ の負パルス幅には、ハイに遷移する $\overline{CS}$ に対する立上りクロックエッジのセットアップ時間が含まれます( $t_{ES}$ )。図1を参照してください。

10ビットワードのMSB側の5ビットでアッテネータAを設定し、10ビットワードのLSB側の5ビットでアッテネータBを設定します。各ビットによって、アッテネータを対応する減衰レベルに設定します。たとえば、アッテネータAおよびBのビット5およびビット0をロジックロー0にすると、それぞれ両アッテネータは1dBに設定されます。00000で両アッテネータは31dBの減衰に設定され、11111で0dBの減衰に設定されます。設定の詳細については、表1を参照してください。

## 外部バイアス

2段アンプとループバックミキサのバイアス電流は、外付け抵抗器によって設定され、最適化されます。抵抗器R1 (ピン31)は入力アンプのバイアス電流を設定し、R2 (ピン20)は出力アンプのバイアス電流を設定し、R3 (ピン40)はループバックミキサのバイアスを設定します。外部バイアス抵抗値を大きくすると、性能を犠牲にして低電流動作にすることができます。詳細については、お問い合わせください。

## 基板レイアウト

MAX2058の端子構成は、デバイスおよびその関連ディスクリート部品の超小型物理レイアウトを容易にするように最適化されています。

MAX2058のTQFN-EPパッケージのエクスポートドパッド(EP)によって、ダイまでの低熱抵抗経路がもたらされます。MAX2058を実装するPCBは、EPから熱を伝導するように設計する必要があります。また、EPから電気的グランドまでを低インダクタンス経路にします。EPは、直接またはメッキ処理されたビアホールのアレイを通じて、PCB上のグランドプレーンに半田付けする必要があります。

表2. 標準動作回路に関連する部品リスト

| COMPONENT             | VALUE          | DESCRIPTION                                     |

|-----------------------|----------------|-------------------------------------------------|

| C1, C4, C10, C13, C16 | 0.1 $\mu$ F    | Microwave capacitors (0603)                     |

| C2, C5, C8, C17       | 100pF          | Microwave capacitors (0402)                     |

| C3, C6, C14, C19      | 47pF           | Microwave capacitors (0402)                     |

| C7, C18               | 0.01 $\mu$ F   | Microwave capacitors (0402)                     |

| C9, C12, C15          | 1000pF         | Microwave capacitors (0402)                     |

| C11                   | 3.9pF          | Microwave capacitor (0402)                      |

| R1                    | 1.2k $\Omega$  | $\pm 1\%$ resistor (0402)                       |

| R2                    | 3.92k $\Omega$ | $\pm 1\%$ resistor (0402)                       |

| R3                    | 2.0k $\Omega$  | $\pm 1\%$ resistor (0402)                       |

| R4                    | 110 $\Omega$   | $\pm 1\%$ resistor (0402)                       |

| T1                    | 2:1            | RF transformer (100:50)<br>Mini-Circuits TC2-1T |

| U1                    | —              | <b>MAX2058 MAXIM IC</b>                         |

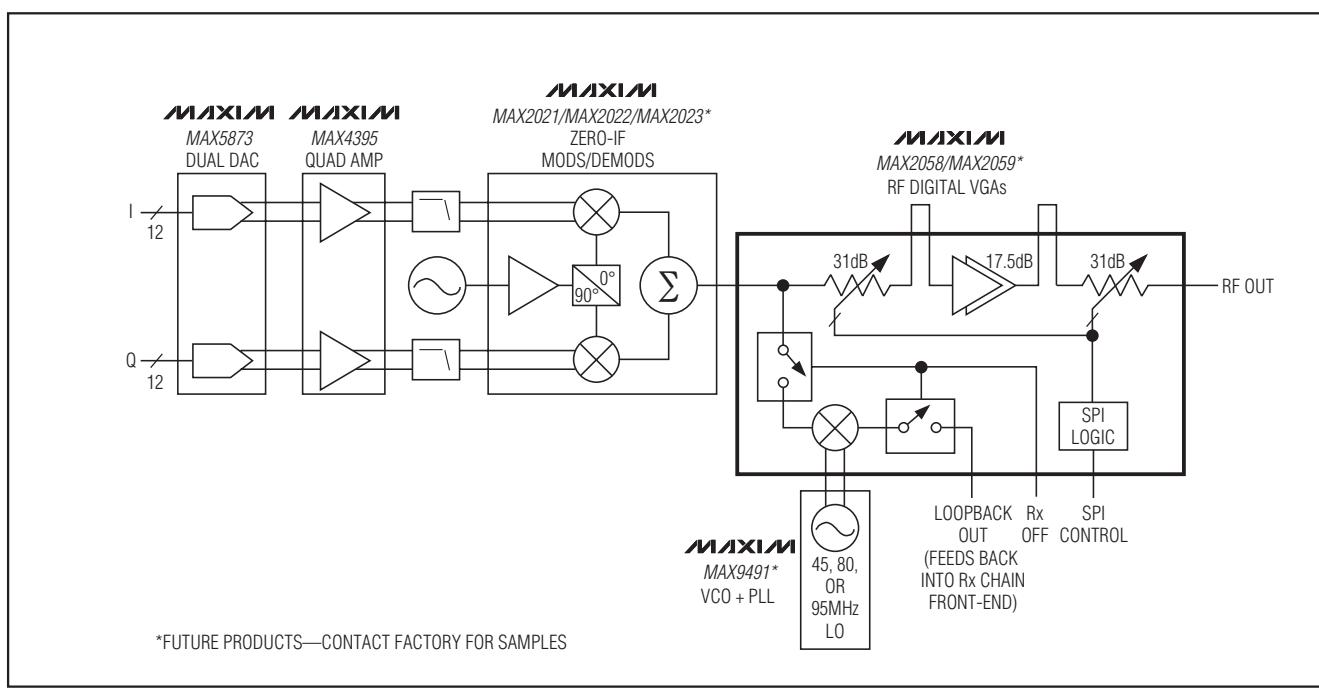

図2. GSM/EDGE基地局用のダイレクトコンバージョントランスマッタ

# 700MHz~1200MHz、高リニアリティ、 ループバックミキサ内蔵、SPI制御DVGA

## 基地局用のダイレクトコンバージョン トランスマッタ

MAX2058/MAX2059は、マキシムのダイレクトコンバージョン直交変調器と高速DACと直接インタフェースし、GSM/EDGE基地局用トランスマッタアプリケーションの完全なソリューションを提供するように設計されています。図2を参照してください。ダイレクトコンバージョン

変調器/復調器のMAX2021/MAX2022/MAX2023\*、デュアルチャネルDACのMAX5873、およびクワッドアンプのMAX4395とともに、MAX2058/MAX2059は、理想的な総合トランスマッタ構成を形成しています。高リニアリティと低ノイズ性能を維持しながら、このシステム全体は高効率で低コストです。

## 標準動作回路

# 700MHz~1200MHz、高リニアリティ、 ループバックミキサ内蔵、SPI制御DVGA

MAX2058

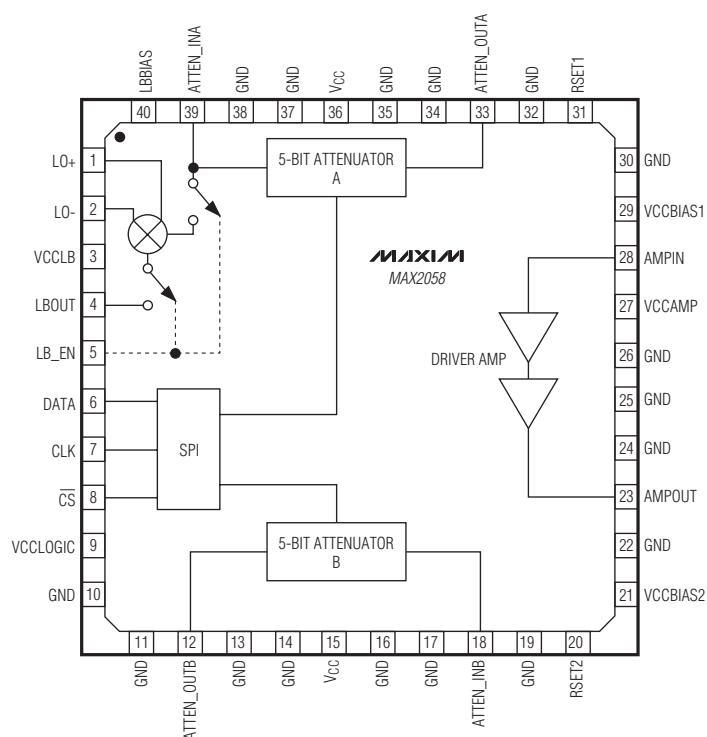

## ピン配置/ファンクションダイアグラム

## チップ情報

PROCESS: SiGe BiCMOS

## パッケージ

最新のパッケージ情報は、[japan.maxim-ic.com/packages](http://japan.maxim-ic.com/packages)をご参照ください。

マキシム・ジャパン株式会社

〒169-0051東京都新宿区西早稲田3-30-16(ホリゾン1ビル)

TEL. (03)3232-6141 FAX. (03)3232-6149

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。マキシムは随时予告なく回路及び仕様を変更する権利を留保します。

**Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600**

15

© 2006 Maxim Integrated Products, Inc. All rights reserved. **MAXIM** is a registered trademark of Maxim Integrated Products, Inc.