# シーケンス/プリバイアス起動及びPOR付 デュアル180°逆位相ステップダウンコントローラ

## 概要

デュアル同期ステップダウンコントローラのMAX1858A/MAX1875A/MAX1876Aは、4.5V～23Vの入力電源から2つの出力を生成します。各出力は1V以下から18Vまでの範囲で可変で、10A以上の負荷を供給します。同期180°逆位相動作によって入力電圧リップルと総RMS入力リップル電流は低減されます。

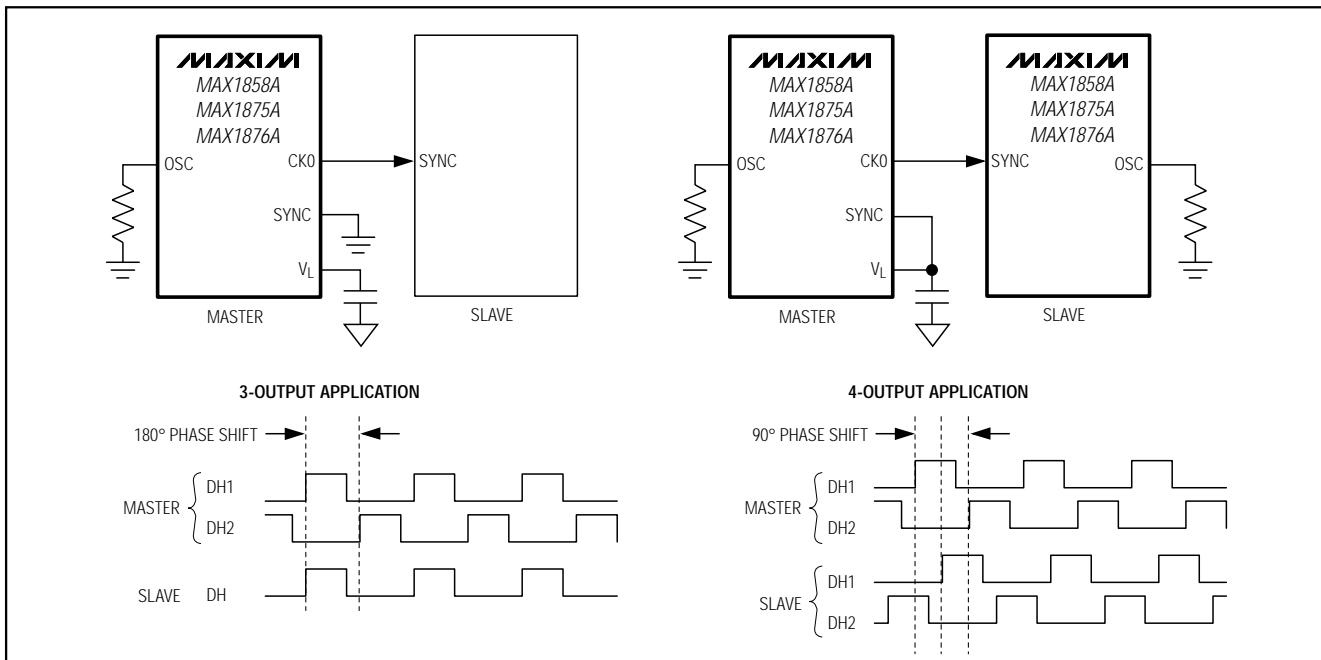

スイッチング周波数は外付け抵抗1本で100kHz～600kHzの間で調整することができます。また別の方法として、他のMAX1858A/MAX1875A/MAX1876Aが発生する外部クロック、またはシステムクロックに同期させることも可能です。他のコントローラと同期を取るために同相または90°位相差があるクロック信号を発生するように1個のMAX1858A/MAX1875A/MAX1876Aを設定することができます。このため、2つのコントローラを用いると、各々が90°位相シフトする交互2相、または4相システムとして動作させることができます。MAX1858A/MAX1875A/MAX1876Aはソフトスタートを備えています。MAX1858Aは、また、ファーストオン/ラストオフの電源シーケンス及びソフトストップ機能も備えています。

MAX1858A/MAX1875A/MAX1876Aは電流検出素子としてローサイドのMOSFETのオン抵抗を利用するため、電流検出用の抵抗が不要です。このため、外付けの電流検出抵抗を必要とせずに、出力が過負荷の場合や短絡の場合にDC-DC用部品の損傷を防ぐことができます。可変フォールドバック型の電流制限によって短絡状態時の電流損失が低減されます。MAX1858A/MAX1876Aはパワーオンリセット(POR)を出力する機能を備え、両出力がレギュレーションに達するとシステムに伝えます。

MAX1858A/MAX1875A/MAX1876Aは、電源入力が印可されない場合またはEN信号をローに設定した場合、出力電圧が負の電圧にならないようになっています。またMAX1875A/MAX1876Aは、出力を放電されることなくプリバイアス起動することができます。

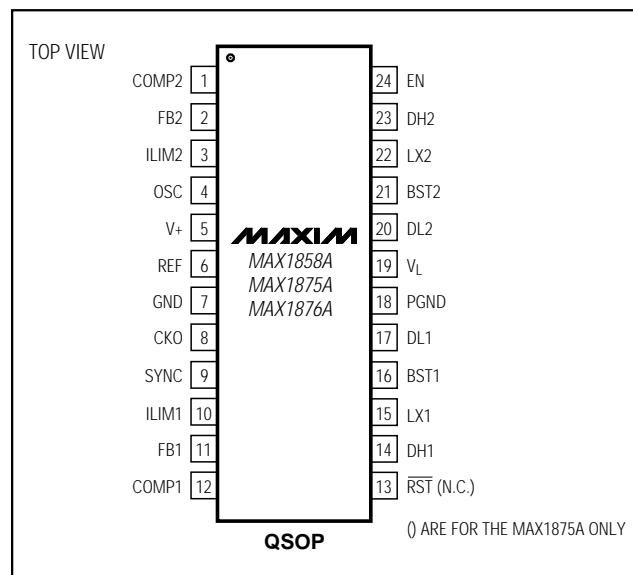

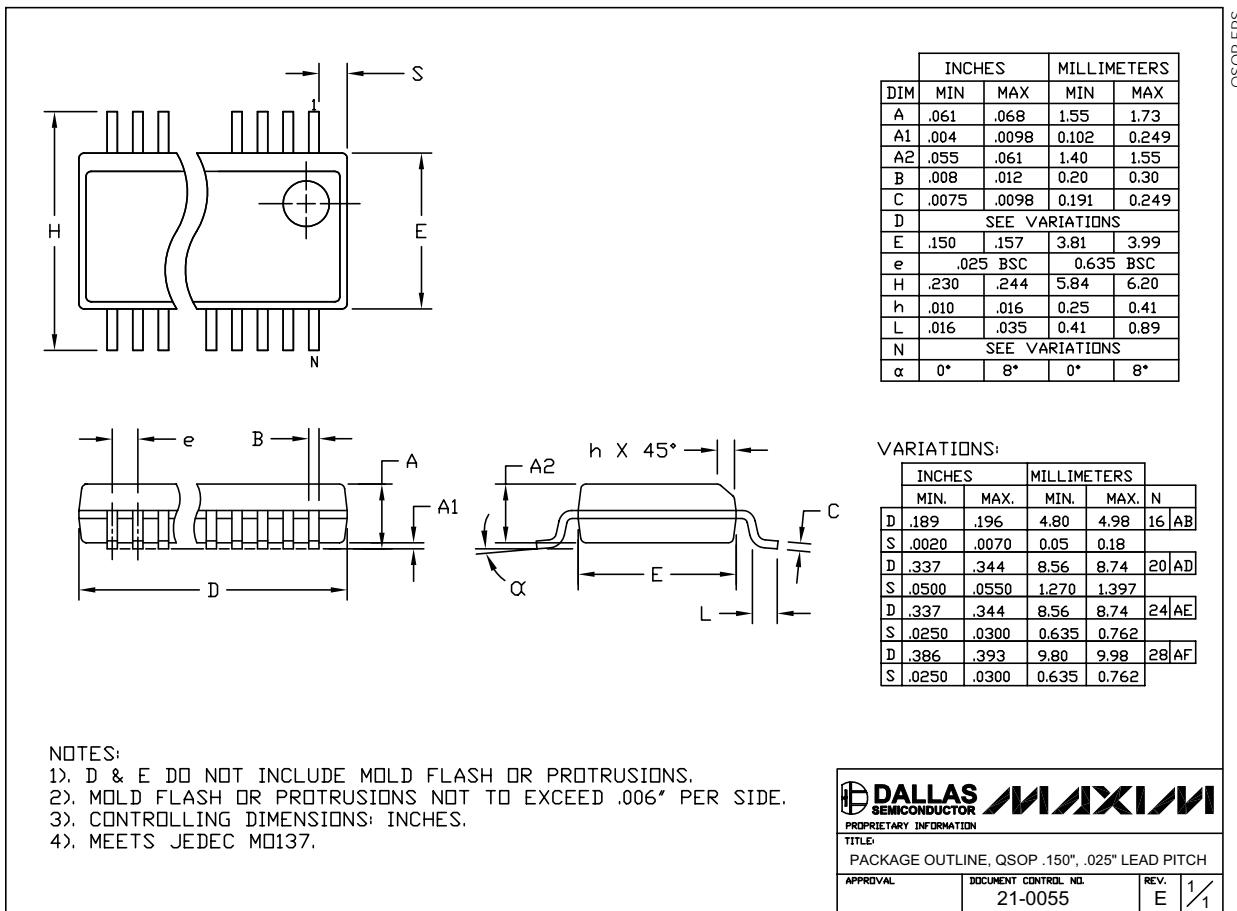

MAX1858A/MAX1875A/MAX1876Aは24ピンのQSOPパッケージで提供されています。MAX1875またはMAX1858の評価キットを使ってMAX1858A/MAX1875A/MAX1876Aを評価することができます。

## アプリケーション

- ネットワーク用電源

- テレコム用電源

- DSP、ASIC、及びFPGA用電源

- セットトップボックス

- ブロードバンド用ルータ

- サーバ

- デスクノート用コンピュータ

## 特長

- ♦ 入力電源範囲：4.5V～23V

- ♦ 出力電圧範囲：0V～18V(最大10A)

- ♦ 調整可能な無損失フォールドバック型電流制限

- ♦ 可変スイッチング周波数：100kHz～600kHz

- ♦ 外部同期を選択可能

- ♦ マスター/スレーブ同期用クロック出力

- ♦ 4相動作(4×90°可能のステップダウンコンバータ(2個のコントローラを使用、図7))

- ♦ プリバイアス起動(MAX1875A/MAX1876A)

- ♦ 電源シーケンス動作(MAX1858A)

- ♦ 140msの最小遅延後のRST出力(MAX1858A/MAX1876A)

- ♦ 固定周波数パルス幅変調(PWM)動作

## 型番

| PART        | TEMP RANGE     | PIN-PACKAGE |

|-------------|----------------|-------------|

| MAX1858AEEG | -40°C to +85°C | 24 QSOP     |

| MAX1875AEEG | -40°C to +85°C | 24 QSOP     |

| MAX1876AEEG | -40°C to +85°C | 24 QSOP     |

## ピン配置

MAX1858A/MAX1875A/MAX1876A

# シーケンス/プリバイアス起動及びPOR付 デュアル180°逆位相ステップダウンコントローラ

## ABSOLUTE MAXIMUM RATINGS

|                                                           |                                                       |

|-----------------------------------------------------------|-------------------------------------------------------|

| V+ to GND .....                                           | -0.3V to +25V                                         |

| PGND to GND .....                                         | -0.3V to +0.3V                                        |

| V <sub>L</sub> to GND .....                               | -0.3V to the lower of +6V and (V <sub>+</sub> + 0.3V) |

| BST1, BST2 to GND .....                                   | -0.3V to +30V                                         |

| LX1 to BST1 .....                                         | -6V to +0.3V                                          |

| LX2 to BST2 .....                                         | -6V to +0.3V                                          |

| DH1 to LX1 .....                                          | -0.3V to (V <sub>BST1</sub> + 0.3V)                   |

| DH2 to LX2 .....                                          | -0.3V to (V <sub>BST2</sub> + 0.3V)                   |

| DL1, DL2 to PGND .....                                    | -0.3V to (V <sub>L</sub> + 0.3V)                      |

| CKO, REF, OSC, ILIM1, ILIM2,<br>COMP1, COMP2 to GND ..... | -0.3V to (V <sub>L</sub> + 0.3V)                      |

|                                                             |                 |

|-------------------------------------------------------------|-----------------|

| FB1, FB2, RST, SYNC, EN to GND .....                        | 0.3V to +6V     |

| VL to GND Short Circuit .....                               | Continuous      |

| REF to GND Short Circuit .....                              | Continuous      |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) ..... | Continuous      |

| 24-Pin QSOP (derate 9.4mW/°C above +70°C) .....             | 762mW           |

| Operating Temperature Range .....                           | -40°C to +85°C  |

| Junction Temperature .....                                  | +150°C          |

| Storage Temperature Range .....                             | -65°C to +150°C |

| Lead Temperature (soldering, 10s) .....                     | +300°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

(V<sub>=</sub> = 12V, EN = ILIM<sub>=</sub> = V<sub>L</sub>, SYNC = GND, I<sub>VL</sub> = 0mA, PGND = GND, C<sub>REF</sub> = 0.22μF, C<sub>VL</sub> = 4.7μF (ceramic), Rosc = 60kΩ, compensation components for COMP<sub>\_</sub> are from Figure 1, T<sub>A</sub> = -40°C to +85°C (Note 1), unless otherwise noted.)

| PARAMETER                                             | CONDITIONS                                                                  | MIN                                | TYP  | MAX  | UNITS        |     |

|-------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------|------|------|--------------|-----|

| <b>GENERAL</b>                                        |                                                                             |                                    |      |      |              |     |

| V <sub>=</sub> Operating Range                        | (Note 2)                                                                    | 4.5                                | 23.0 |      | V            |     |

|                                                       | V <sub>L</sub> = V <sub>=</sub> (Note 2)                                    | 4.5                                | 5.5  |      |              |     |

| V <sub>=</sub> Operating Supply Current               | V <sub>L</sub> unloaded, no MOSFETs connected                               | 3.5                                | 6    |      | mA           |     |

| V <sub>=</sub> Standby Supply Current                 | EN = LX <sub>=</sub> = FB <sub>=</sub> = 0V                                 | 0.3                                | 0.6  |      | mA           |     |

| Thermal Shutdown                                      | Rising temperature, typical hysteresis = 10°C                               | +160                               |      |      | °C           |     |

| Current-Limit Threshold                               | PGND - LX <sub>=</sub>                                                      | ILIM <sub>=</sub> = V <sub>L</sub> | 75   | 100  | 125          | mV  |

|                                                       |                                                                             | R <sub>ILIM</sub> = 100kΩ          | 32   | 50   | 62           |     |

|                                                       |                                                                             | R <sub>ILIM</sub> = 600kΩ          | 225  | 300  | 375          |     |

| <b>V<sub>L</sub> REGULATOR</b>                        |                                                                             |                                    |      |      |              |     |

| Output Voltage                                        | 5.5V < V <sub>=</sub> < 23V, 1mA < I <sub>LOAD</sub> < 50mA                 | 4.75                               | 5    | 5.25 | V            |     |

| V <sub>L</sub> Undervoltage Lockout Rising Trip Level |                                                                             | 4.1                                | 4.2  | 4.3  | V            |     |

| V <sub>L</sub> Undervoltage Lockout Hysteresis        | (Note 3)                                                                    |                                    | 100  |      | mV           |     |

| <b>REFERENCE</b>                                      |                                                                             |                                    |      |      |              |     |

| Output Voltage                                        | I <sub>REF</sub> = 0μA                                                      | 1.98                               | 2.00 | 2.02 | V            |     |

| Reference Load Regulation                             | 0μA < I <sub>REF</sub> < 50μA                                               | 0                                  | 4    | 10   | mV           |     |

| <b>SOFT-START</b>                                     |                                                                             |                                    |      |      |              |     |

| Digital Ramp Period                                   | Internal 6-bit DAC for one converter to ramp from 0V to full scale (Note 4) |                                    | 1024 |      | DC-DC clocks |     |

| Soft-Start Steps                                      |                                                                             |                                    | 64   |      | Steps        |     |

| <b>FREQUENCY</b>                                      |                                                                             |                                    |      |      |              |     |

| Low End of Range                                      | RosC = 60kΩ                                                                 | 0°C to +85°C                       | 84   | 100  | 115          | kHz |

|                                                       |                                                                             | -40°C to +85°C                     | 80   | 100  | 120          |     |

| High End of Range                                     | RosC = 10kΩ                                                                 |                                    | 540  | 600  | 660          | kHz |

| DH <sub>=</sub> Minimum Off-Time                      | RosC = 10kΩ                                                                 |                                    | 250  | 303  | ns           |     |

# シーケンス/プリバイアス起動及びPOR付 デュアル180 °逆位相ステップダウンコントローラ

MAX1858A/MAX1875A/MAX1876A

## ELECTRICAL CHARACTERISTICS (continued)

( $V_+ = 12V$ ,  $EN = ILIM_+ = V_L$ ,  $SYNC = GND$ ,  $I_{VL} = 0mA$ ,  $PGND = GND$ ,  $CREF = 0.22\mu F$ ,  $C_{VL} = 4.7\mu F$  (ceramic),  $Rosc = 60k\Omega$ , compensation components for  $COMP_-$  are from Figure 1,  $T_A = -40^\circ C$  to  $+85^\circ C$  (Note 1), unless otherwise noted.)

| PARAMETER                                             | CONDITIONS                                                                           |      | MIN   | TYP  | MAX   | UNITS  |

|-------------------------------------------------------|--------------------------------------------------------------------------------------|------|-------|------|-------|--------|

| SYNC Range                                            | Switching frequency must be set to half of the SYNC frequency                        |      | 200   |      | 1200  | kHz    |

| SYNC Input Pulse Width                                | (Note 4)                                                                             | High | 100   |      |       | ns     |

|                                                       |                                                                                      | Low  | 100   |      |       |        |

| SYNC Rise/Fall Time                                   | (Note 4)                                                                             |      |       | 100  |       | ns     |

| <b>ERROR AMPLIFIER</b>                                |                                                                                      |      |       |      |       |        |

| FB_- Input Bias Current                               |                                                                                      |      |       | 250  |       | nA     |

| FB_- Input Voltage Set Point                          | 0°C to +85°C                                                                         |      | 0.985 | 1.00 | 1.015 | V      |

|                                                       | -40°C to +85°C                                                                       |      | 0.98  | 1.00 | 1.02  |        |

| FB_- to COMP_- Transconductance                       | 0°C to +85°C                                                                         |      | 1.25  | 1.8  | 2.70  | mS     |

|                                                       | -40°C to +85°C                                                                       |      | 1.2   | 1.8  | 2.9   |        |

| <b>DRIVERS</b>                                        |                                                                                      |      |       |      |       |        |

| DL_, DH_ Break-Before-Make Time                       | CLOAD = 5nF                                                                          |      | 30    |      |       | ns     |

| DH_ On-Resistance                                     | Low                                                                                  |      | 1.5   | 2.5  |       | \Omega |

|                                                       | High                                                                                 |      | 3     | 5    |       |        |

| DL_ On-Resistance                                     | Low                                                                                  |      | 0.6   | 1.5  |       | \Omega |

|                                                       | High                                                                                 |      | 3     | 5    |       |        |

| <b>LOGIC INPUTS (EN, SYNC)</b>                        |                                                                                      |      |       |      |       |        |

| Input Low Level                                       | Typical 15% hysteresis, $V_L = 4.5V$                                                 |      |       | 0.8  |       | V      |

| Input High Level                                      | $V_L = 5.5V$                                                                         |      | 2.4   |      |       | V      |

| Input High/Low Bias Current                           | $V_{EN} = 0$ or $5.5V$                                                               |      | -1    | +0.1 | +1    | \mu A  |

| <b>LOGIC OUTPUTS (CKO)</b>                            |                                                                                      |      |       |      |       |        |

| Output Low Level                                      | $V_L = 5V$ , sinking 5mA                                                             |      |       | 0.4  |       | V      |

| Output High Level                                     | $V_L = 5V$ , sourcing 5mA                                                            |      | 4.0   |      |       | V      |

| <b>COMP_-</b>                                         |                                                                                      |      |       |      |       |        |

| Pulldown Resistance During Shutdown and Current Limit |                                                                                      |      |       | 17   |       | \Omega |

| <b>RST OUTPUT (MAX1858A/MAX1876A ONLY)</b>            |                                                                                      |      |       |      |       |        |

| Output-Voltage Trip Level                             | Both FBs must be over this to allow the reset timer to start; there is no hysteresis |      | 0.87  | 0.9  | 0.93  | V      |

| Output Low Level                                      | $V_L = 5V$ , sinking 3.2mA                                                           |      |       | 0.4  |       | V      |

|                                                       | $V_L = 1V$ , sinking 0.4mA                                                           |      |       | 0.3  |       |        |

| Output Leakage                                        | $V_+ = V_L = 5V$ , $VRST = 5.5V$ , $V_{FB} = 1V$                                     |      |       | 1    |       | \mu A  |

| Reset Timeout Period                                  | $V_{FB_-} = 1V$                                                                      |      | 140   | 315  | 560   | ms     |

| FB_- to Reset Delay                                   | FB_- overdrive from 1V to 0.85V                                                      |      |       | 4    |       | \mu s  |

**Note 1:** Specifications to  $-40^\circ C$  are guaranteed by design and not production tested.

**Note 2:** Operating supply range is guaranteed by  $V_L$  line regulation test. Connect  $V_+$  to  $V_L$  for 5V operation.

**Note 3:** When  $V_L$  falls and UVLO is tripped, the device is latched and  $V_L$  must be discharged below 2.5V before normal operation can resume.

**Note 4:** Guaranteed by design and not production tested.

# シーケンス/プリバイアス起動及びPOR付 デュアル180°逆位相ステップダウンコントローラ

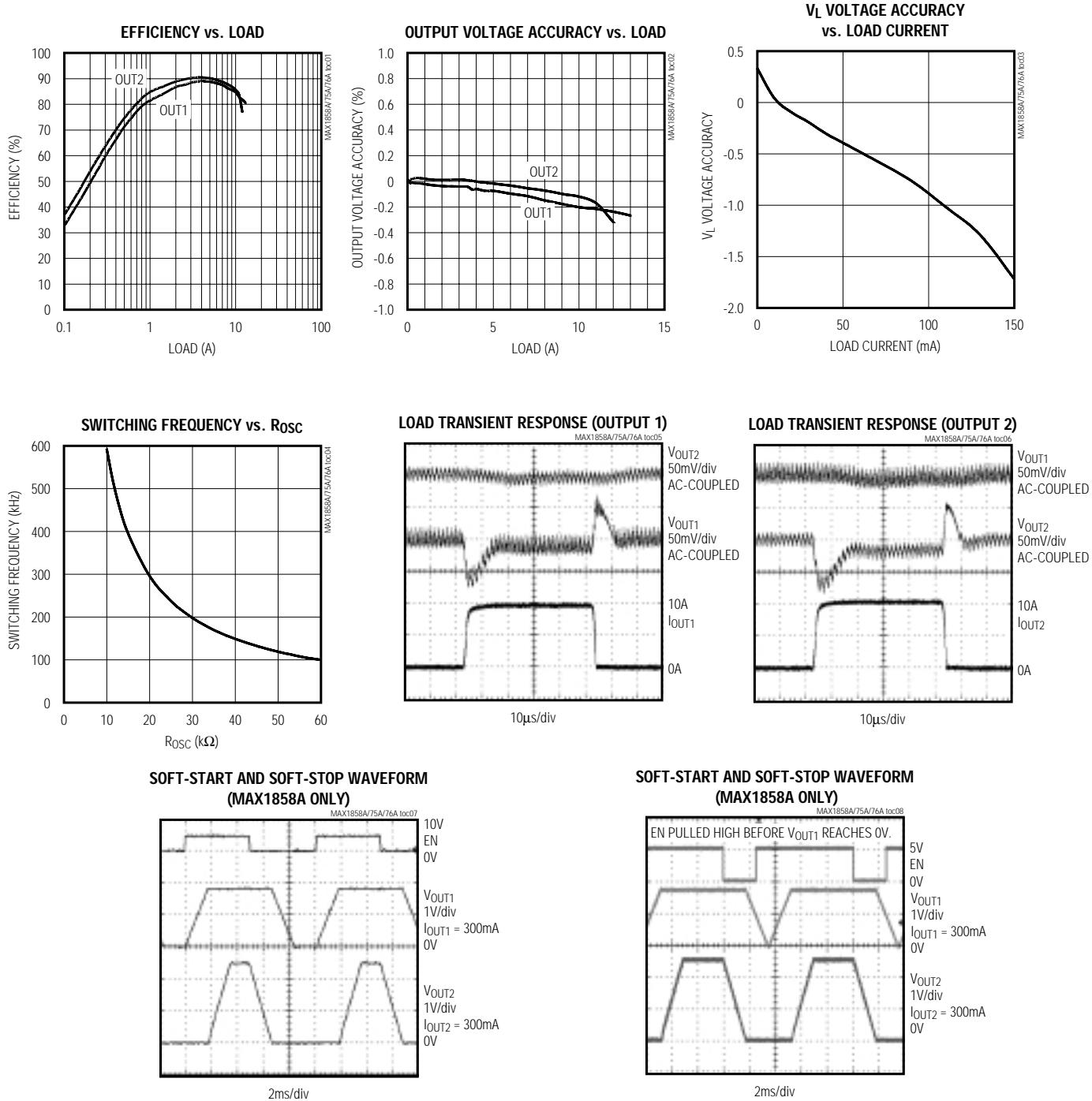

## 標準動作特性

(Circuit of Figure 1,  $V_{IN} = 12V$ ,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted.)

# シーケンス/プリバイアス起動及びPOR付 デュアル180°逆位相ステップダウンコントローラ

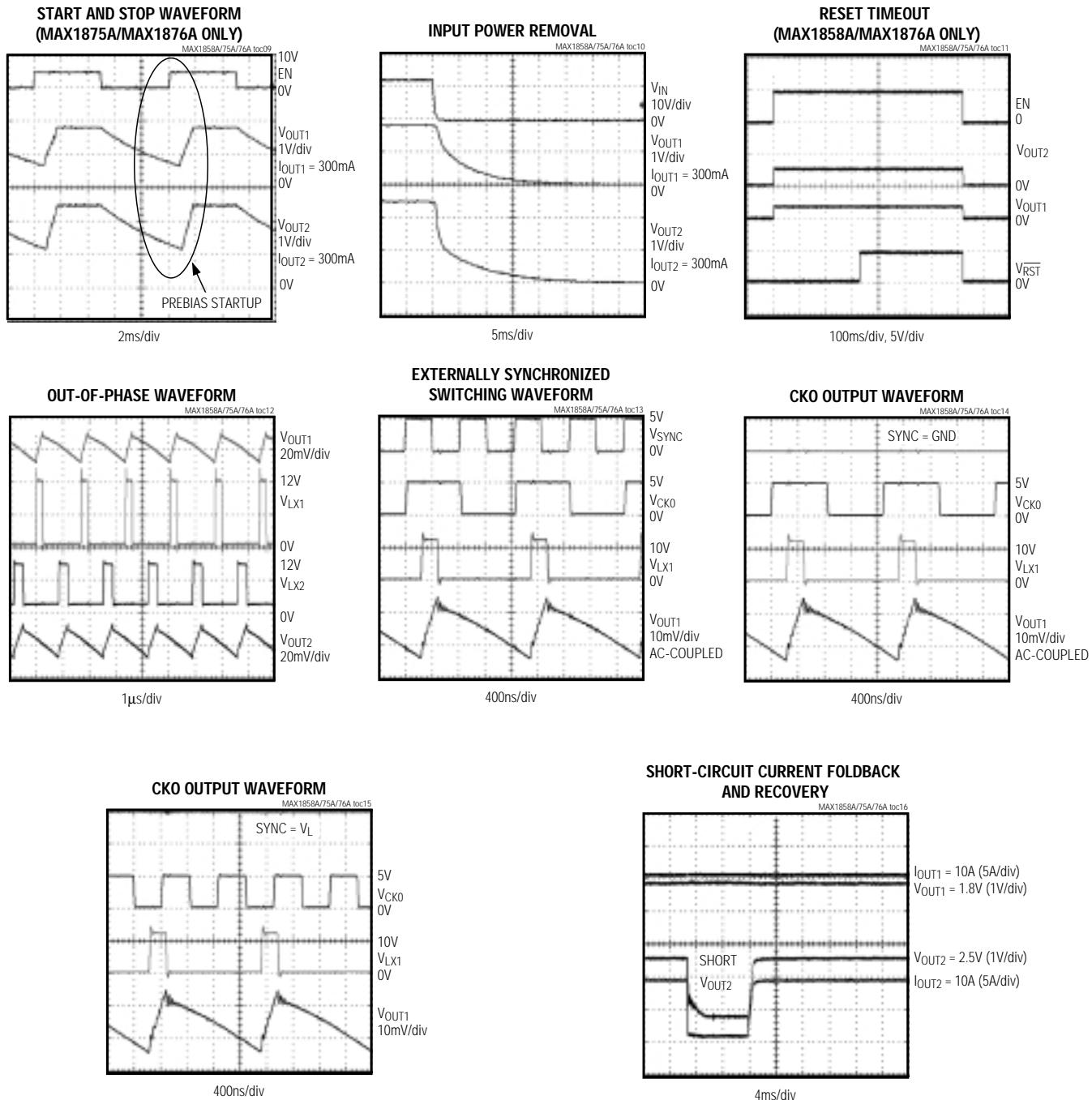

## 標準動作特性(続き)

(Circuit of Figure 1,  $V_{IN} = 12V$ ,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted.)

# シーケンス/プリバイアス起動及びPOR付 デュアル180°逆位相ステップダウンコントローラ

## 端子説明

| 端子 | 名称               | 機能                                                                                                                                                                                                                                                                                                           |

|----|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

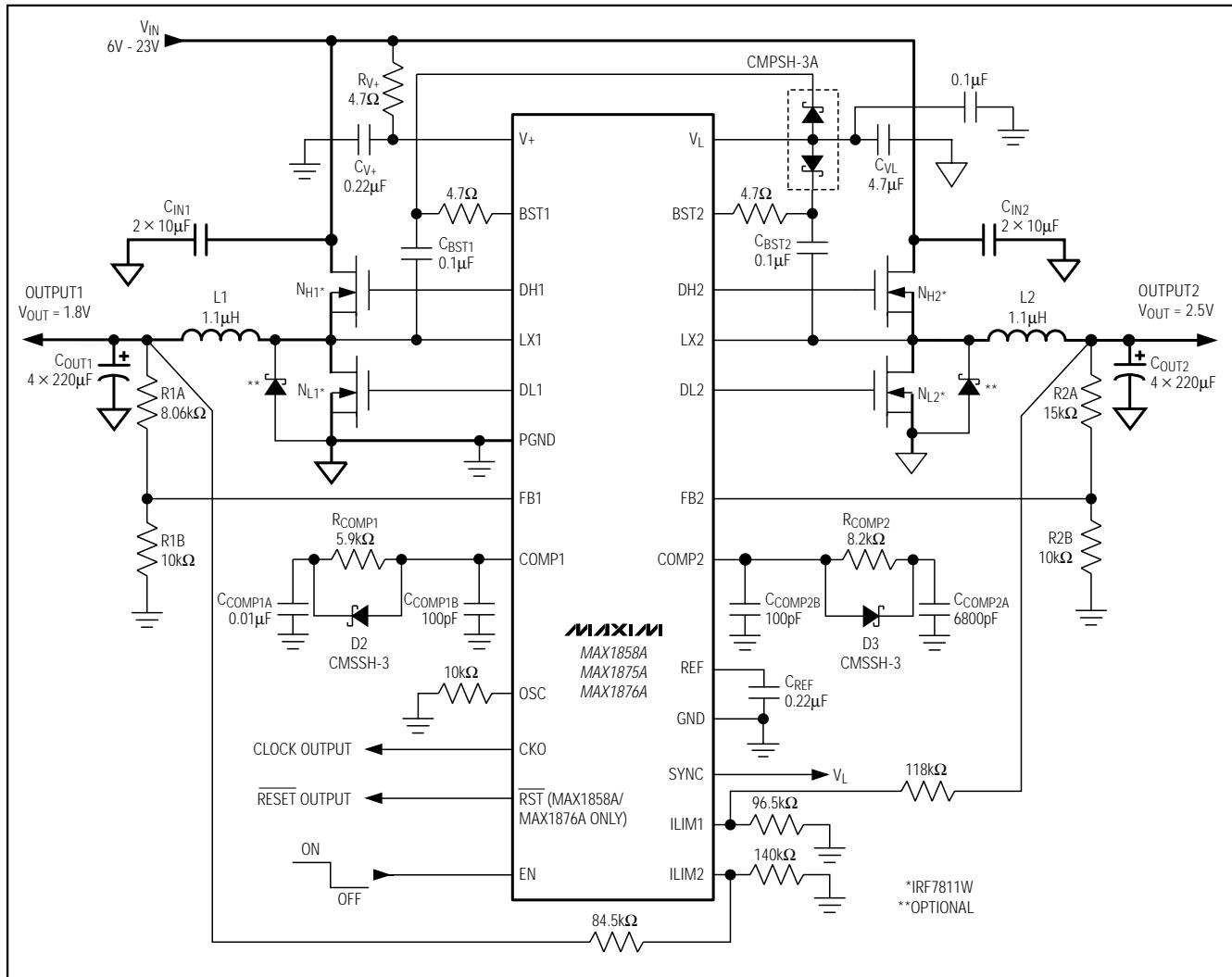

| 1  | COMP2            | レギュレータ2(REG2)用の補償端子。図1に示すように直列に接続した抵抗( $R_{COMP2}$ )とコンデンサ( $C_{COMP2A}$ )をGNDに接続し、それと並列に2番目の補償用コンデンサ( $C_{COMP2B}$ )を接続することによってREG2の制御ループを補償します。                                                                                                                                                            |

| 2  | FB2              | レギュレータ2(REG2)のフィードバック入力端子。FB2にはREG2の出力とGND間に挿入する抵抗分圧された出力を接続して出力電圧を1V~18Vの間に調整します。出力を1V以下に設定するためには、REFとREG2の出力間に挿入する抵抗で分圧された出力を接続してください。「出力電圧の設定」のセクションを参照してください。                                                                                                                                            |

| 3  | ILIM2            | レギュレータ2(REG2)用の電流制限値の調整用端子。ILIM2を $V_L$ に接続するとPGND-LX2の電流制限スレッショルドのデフォルト値は100mVとなります。ILIM2とGND間に抵抗( $R_{ILIM2}$ )を接続するとREG2の電流制限のスレッショルド( $V_{TH2}$ )を50mV( $R_{ILIM2}=100k\Omega$ )~300mV( $R_{ILIM2}=600k\Omega$ )の範囲で調整することができます。「谷(Valley)電流の限界値の設定」を参照してください。                                           |

| 4  | OSC              | 発振器の周波数を設定する入力端子。抵抗( $R_{OSC}$ )をOSCとGND間に接続するとスイッチング周波数を100kHz( $R_{OSC}=60k\Omega$ )~600kHz( $R_{OSC}=10k\Omega$ )の範囲に設定することができます。外部からのクロックがSYNCに接続された場合でも、コントローラには、 $R_{OSC}$ を接続する必要があります。外部クロックを使用する場合、先に述べたように $R_{OSC}$ の値を選択し外部周波数を設定したいスイッチング周波数の2倍に設定してください。                                       |

| 5  | V+               | 4.5V~23Vの電源を接続します。                                                                                                                                                                                                                                                                                           |

| 6  | REF              | 2Vのリファレンス電圧出力端子。GNDとの間に0.22μF以上のセラミックコンデンサを接続してください。                                                                                                                                                                                                                                                         |

| 7  | GND              | アナロググランド端子。                                                                                                                                                                                                                                                                                                  |

| 8  | CKO              | クロック出力端子。2または4相の外部同期用のクロック出力です('クロック同期(SYNC、CKO)'のセクションを参照)。                                                                                                                                                                                                                                                 |

| 9  | SYNC             | 同期入力するか、またはクロック出力するかの選択を行う入力端子。SYNCには3つの動作モードがあります。外部同期とするためにはSYNCを200kHz~1200kHzのクロックに接続してください。2相動作のマスタコントローラとするためにはSYNCをGNDに接続してください。4相動作のマスタコントローラとするためにはSYNCを $V_L$ に接続してください('クロック同期(SYNC、CKO)'のセクションを参照)。                                                                                              |

| 10 | ILIM1            | レギュレータ1(REG1)用の電流制限値の調整用端子。ILIM1を $V_L$ に接続するとPGND-LX1の電流制限スレッショルドのデフォルト値は100mVとなります。ILIM1とGND間に抵抗( $R_{ILIM1}$ )を接続するとREG1の電流制限のスレッショルド( $V_{TH1}$ )を50mV( $R_{ILIM1}=100k\Omega$ )~300mV( $R_{ILIM1}=600k\Omega$ )の範囲に調整することができます。「谷(Valley)電流の限界値の設定」を参照してください。                                           |

| 11 | FB1              | レギュレータ1(REG1)のフィードバック入力端子。FB1にはREG1の出力とGND間に挿入する抵抗分圧された出力を接続して出力電圧を1V~18Vの間に調整します。出力を1V以下に設定するためには、REFとREG1の出力間に挿入する抵抗により分圧された出力を接続してください。「出力電圧の設定」のセクションを参照してください。                                                                                                                                          |

| 12 | COMP1            | レギュレータ1(REG1)用の補償端子。図1に示すように直列に接続した抵抗( $R_{COMP1}$ )とコンデンサ( $C_{COMP1A}$ )をGNDに接続し、それと並列に2番目の補償用コンデンサ( $C_{COMP1B}$ )を接続することによってREG1の制御ループを補償します。                                                                                                                                                            |

| 13 | $\overline{RST}$ | オープンドレイン型のリセット出力端子(MAX1858A/MAX1876Aのみ)。2つの出力電圧のどちらかが、定常調整値より10%以上小さくなると $\overline{RST}$ が低レベルとなります。ソフトスタートが完了し両方の出力がその公称出力値( $V_{FB}>0.9V$ )の90%以上に達すると、140msの遅延の後、 $\overline{RST}$ はハイインピーダンスとなり、両方の出力がレギュレーションを維持している限り、その状態が維持されます。この端子を使って論理レベルの電圧出力を得るために $\overline{RST}$ 端子と論理回路用電源の間に抵抗を接続してください。 |

|    | N.C.             | MAX1875Aでは未使用であり、GNDに接続するか、またはそのままとしてください。                                                                                                                                                                                                                                                                   |

# シーケンス/プリバイアス起動及びPOR付 デュアル180°逆位相ステップダウンコントローラ

MAX1858A/MAX1875A/MAX1876A

## 端子説明(続き)

| 端子 | 名称             | 機能                                                                                                      |

|----|----------------|---------------------------------------------------------------------------------------------------------|

| 14 | DH1            | レギュレータ1(REG1)のためのハイサイドゲートドライバ出力端子。DH1にはLX1からBST1までの電圧振幅があります。DH1はUVLOの間はロー(低)状態です。                      |

| 15 | LX1            | レギュレータ1(REG1)のための外部インダクタの接続端子。LX1をインダクタのスイッチされる側に接続してください。LX1はDH1ハイサイドゲートドライバのためのローサイドの供給電源としての役目も持ちます。 |

| 16 | BST1           | レギュレータ1(REG1)用の昇圧用フライングコンデンサの接続端子。BST1に外部からコンデンサとダイオードを図1に示すように接続してください。                                |

| 17 | DL1            | レギュレータ1(REG1)のローサイドゲートドライバ出力端子。DL1はPGNDからV <sub>L</sub> までの出力振幅となります。DL1はUVLOの間はロー(低)レベルです。             |

| 18 | PGND           | 電源グランド端子。                                                                                               |

| 19 | V <sub>L</sub> | 内蔵の5Vリニアレギュレータ出力端子。この出力は内部の電源供給と、ローサイドゲートドライバ用の電源となり、またハイサイドゲートドライバ用の外部昇圧回路に対する電源となります。                 |

| 20 | DL2            | レギュレータ2(REG2)用のローサイドゲートドライバ出力。DL2はPGNDからV <sub>L</sub> までの出力振幅となります。DL2はUVLOの間はロー(低)状態です。               |

| 21 | BST2           | レギュレータ2(REG2)用の昇圧用フライングコンデンサの接続端子。BST2に外部からコンデンサとダイオードを図1に示すように接続してください。                                |

| 22 | LX2            | レギュレータ2(REG2)用の外部インダクタの接続端子。LX2をインダクタのスイッチされる側に接続してください。LX2はDH2ハイサイドゲートドライバのためのローサイドの供給電源としての役目を持ちます。   |

| 23 | DH2            | レギュレータ2(REG2)用のハイサイドゲートドライバ出力端子。DH2はLX2からBST2までの出力振幅となります。DH2はUVLOの間はロー(低)状態です。                         |

| 24 | EN             | アクティブハイのイネーブル入力端子。論理ゼロを入力すると、両コントローラは不能となります。V <sub>L</sub> に接続すると常にコントローラはオンになります。                     |

## 詳細

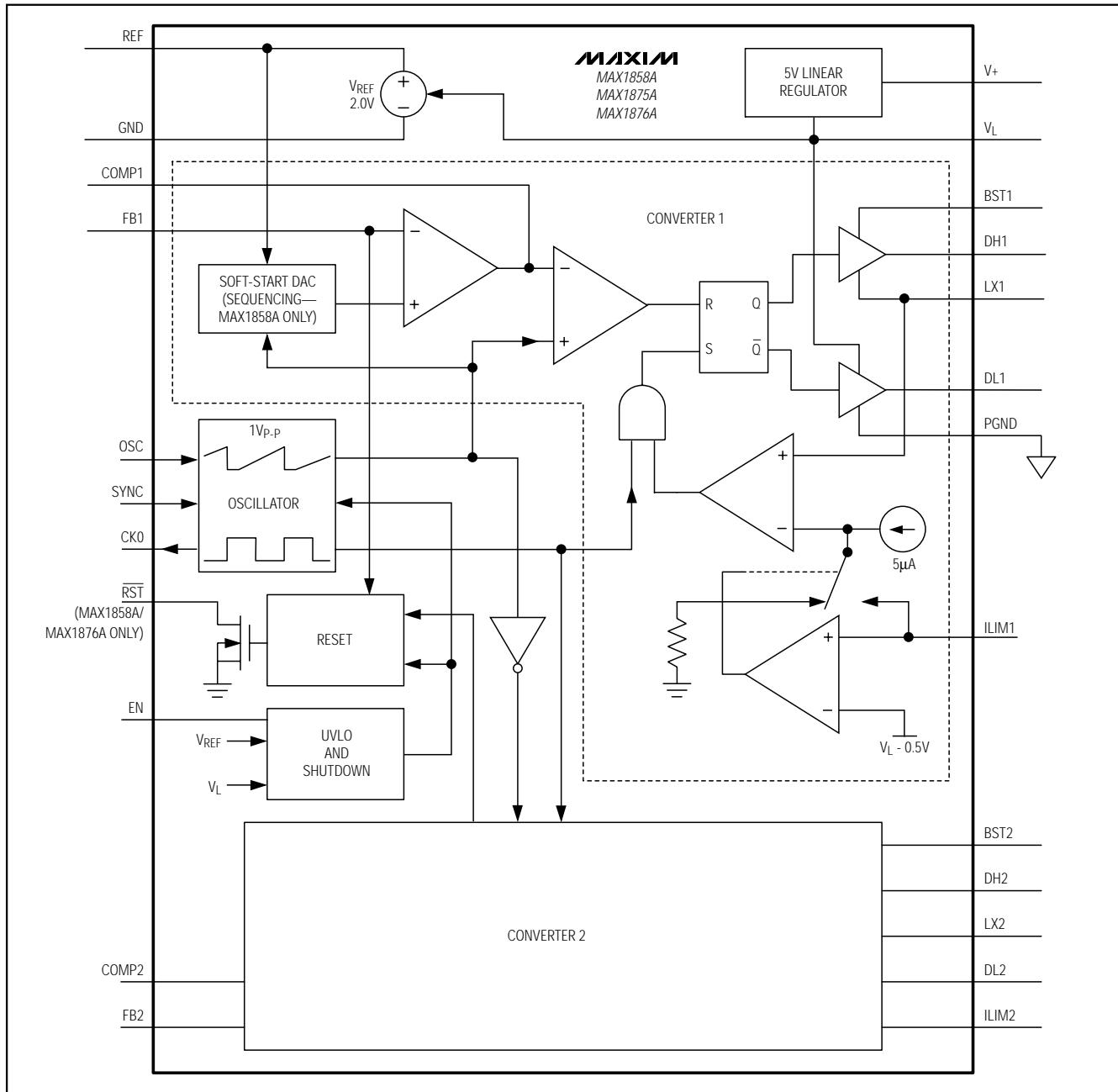

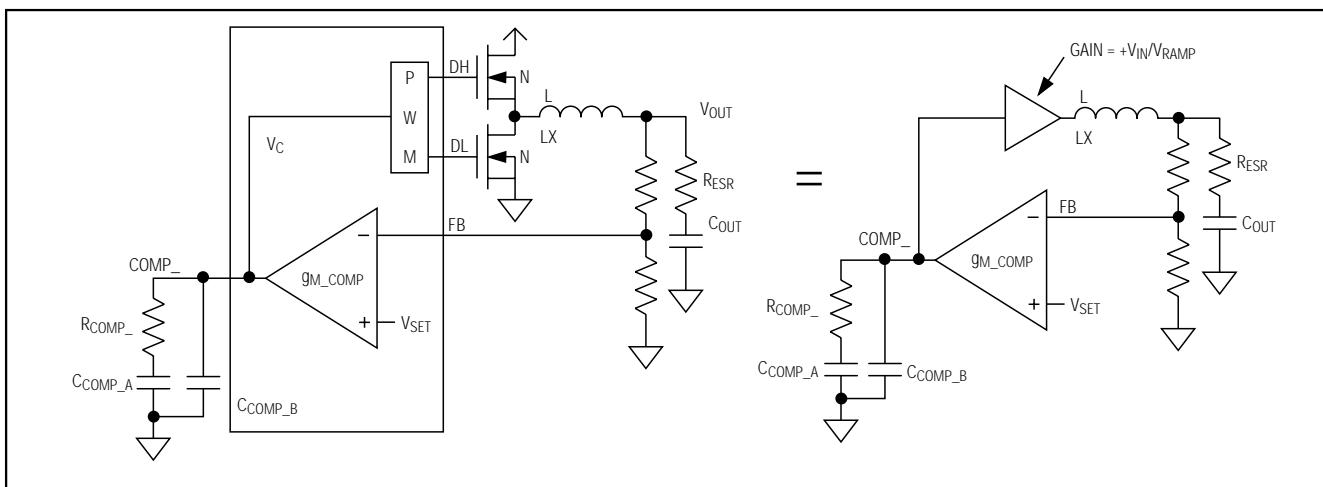

### DC-DC PWMコントローラ

MAX1858A/MAX1875A/MAX1876Aステップダウンコンバータは、各位相シフトコントローラに対してPWM電圧モード制御方式を採用しています(図2)。コントローラは内部の発振器を分周するか、または外部クロックを使用する場合はSYNC入力を分周して、クロック信号を作り出します。したがって、各コントローラのスイッチング周波数は発振器の周波数の半分となります( $f_{SW}=f_{OSC}/2$ )。内部のトランスコンダクタンス型のエラーアンプはCOMP端子において積分誤差電圧を発生させてるので、高精度のDC出力が得られます。COMP端子の電圧はPWMコンパレータとランプ波形を用いてデューティサイクルを設定します。クロックの各立上り時にREG1のハイサイドNチャネルMOSFETはオンとなり、適切なデューティサイクルまたは最大のデューティサイクルに達するまでその状態を維持します。REG2は逆位相で動作します。したがって、クロックの立下り時に2番目のハイサイドMOSFETがオンとなります。各ハイサイドMOSFETがオンの間、それぞれに対応したインダクタ電流が増大します。

スイッチングサイクルの後半において、ハイサイドMOSFETがオフとなり、ローサイドのNチャネルMOSFETがオンとなります。するとインダクタは蓄積したエネルギーを放出して電流が低下し、電流を出力に供給します。

過負荷の状態では、インダクタの電流が選択された谷(valley)電流制限値を超えると(「電流制限回路(ILIM\_)」のセクションを参照)、ハイサイドMOSFETは適切なクロックエッジではオンにならず、ローサイドMOSFETがオンのままでインダクタの電流を低下させます。

### 同期逆位相動作

MAX1858A/MAX1875A/MAX1876A内の2つの独立したレギュレータは180°逆位相した動作をするため、必要な入力フィルタの値を下げ、電磁干渉(EMI)を低下させ、効率を改善します。このことにより、部品のコストを効果的に下げ、ボードの省スペース化が実現し、MAX1858A/MAX1875A/MAX1876Aはコストを重視するアプリケーションに最適です。

通常、デュアルスイッチングレギュレータは両コントローラが同相で動作するので、2つのハイサイドMOSFETを同時にオンとします。その場合、入力コンデンサは両コントローラが要求する電流を同時に供給する必要があります、結果として1個のスイッチングレギュレータに比べて、より大きいリップル電圧と電流を生じることになります。RMSリップル電流は入力コンデンサが持つ等価直列抵抗(ESR)による電力損失のために効率を下げるになります。このため、通常は低いESRを持つ入力コンデンサを、より多く並列に接続して入力電圧リップルとESRに関する損失を下げるか、もしくは必要とされるリップル電流仕様を満足させる必要があります。

# シーケンス/プリバイアス起動及びPOR付 デュアル180°逆位相ステップダウンコントローラ

MAX1858A/MAX1875A/MAX1876A

図1. 600kHzで動作する場合の標準応用回路

MAX1858A/MAX1875A/MAX1876AのハイサイドMOSFETはデュアルの同期型逆位相動作を行うため、180°の逆位相でオンとなります。両レギュレータの瞬時入力の電流ピーク値は、最も早い場合でも、重なることはなく、結果としてRMSリップル電流と入力電圧リップルを減らすことができます。このことにより、入力コンデンサに要求されるリップル電流仕様値を小さくし、またEMIに対するシールド条件を減少させることができます。「標準動作特性」における逆位相波形は180°の逆位相動作を示しています。

## 内部の5Vリニアレギュレータ( $V_L$ )

MAX1858A/MAX1875A/MAX1876Aのすべての回路ブロックはチップに搭載された低ドロップアウト5Vレギュレータから電源供給されます。最大のレギュレータ入力電圧( $V_+$ )は23Vです。レギュレータ出力( $V_L$ )を4.7 $\mu$ FのセラミックコンデンサをPGNDに接続してバイパスしてください。 $V_L$ のドロップ電圧は、標準値で500mVであるため、 $V_+$ が5.5Vよりも高ければ $V_L$ は標準値で5Vを出力します。また、MAX1858A/MAX1875A/MAX1876Aは、 $V_L$ が4.2V以下に低下すると

# シーケンス/プリバイアス起動及びPOR付 デュアル180°逆位相ステップダウンコントローラ

MAX1858A/MAX1875A/MAX1876A

図2. ファンクションダイアグラム

両レギュレータを出力不可とする低電圧ロックアウト回路を採用しています。 $V_L$ は、また、 $0.1\mu F$ のコンデンサをGNDに接続してバイパスしてください。 $V_L$ が低下し、UVLOが動作すると本デバイスはラッピングされ、標準動作に復帰するために、 $V_L$ を2.5V以下にリセットしなければなりません。

内部の $V_L$ リニアレギュレータはIC内部への電源供給、ローサイドゲートドライバへの供給、外部の昇圧用コンデンサを充電し、外部の軽い負荷へ50mA以上の

電流を供給することができます。大きなFETを駆動するための電流は、このレギュレータ出力の場合、ほとんどまたは全く供給することができません。

例えば、600kHzで動作している場合、 $18nC$ の大きな総ゲート容量を持つような大きなFETは $18nC \times 600kHz = 11mA$ を必要とします。より大きなMOSFETを駆動したり、大きな負荷に供給する場合は $V_L$ を4.5V～5.5Vの外部電源に接続してください。

# シーケンス/プリバイアス起動及びPOR付 デュアル180°逆位相ステップダウンコントローラ

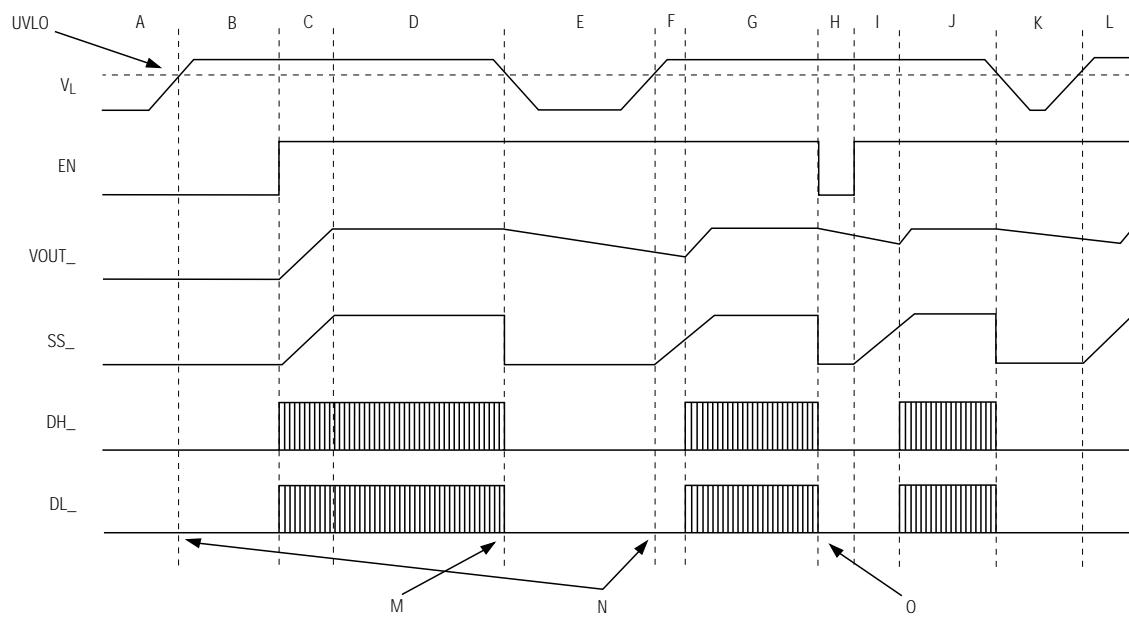

MAX1875A/MAX1876A POWER-ON-OFF SEQUENCING DEFINITIONS

| SYMBOL | DEFINITION                                                                                  |

|--------|---------------------------------------------------------------------------------------------|

| UVLO   | Undervoltage lockout trip level is provided in the <i>Electrical Characteristics</i> table. |

| VL     | Internal 5V Linear-Regulator Output                                                         |

| EN     | Active-High Enable Input                                                                    |

| VOUT_  | Output Voltage                                                                              |

| SS_    | Internal Soft-Start Input Signal into Error Amplifier                                       |

| DH_    | High-Side Gate-Driver Output                                                                |

| DL_    | Low-Side Gate-Driver Output                                                                 |

| A      | $V_L$ rising while below the UVLO threshold, EN is low.                                     |

| B      | $V_L$ is greater than the UVLO threshold, EN is low.                                        |

| C      | EN is pulled high.                                                                          |

| D      | Normal operation                                                                            |

| E      | $V_L$ enters UVLO.                                                                          |

| F      | $V_L$ exits UVLO.                                                                           |

| G      | Resumes normal operation                                                                    |

| H      | EN is pulled low.                                                                           |

| I      | EN is pulled high.                                                                          |

| J      | Resumes normal operation                                                                    |

| K      | $V_L$ drops below UVLO threshold while EN is high.                                          |

| L      | Resumes normal operation                                                                    |

| M      | UVLO is activated and DL_ is latched low.                                                   |

| N      | Exiting UVLO: DL_ remains latched low until the first fall of DH_ is detected.              |

| O      | DL_ is low after EN is pulled low.                                                          |

図3. MAX1875A/MAX1876Aの電源オン/オフシーケンス詳細

# シーケンス/プリバイアス起動及びPOR付 デュアル180°逆位相ステップダウンコントローラ

MAX1858A/MAX1875A/MAX1876A

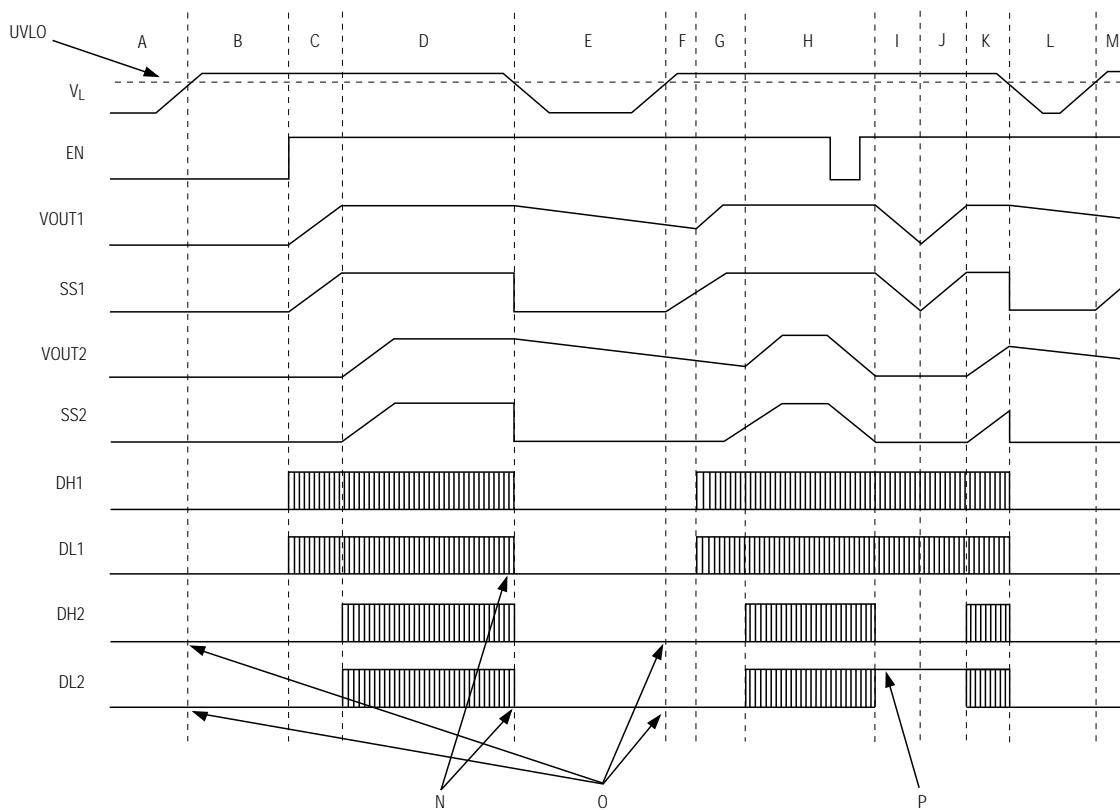

MAX1858A POWER-ON-OFF SEQUENCING DEFINITIONS

| SYMBOL | DEFINITION                                                                               |

|--------|------------------------------------------------------------------------------------------|

| UVLO   | Undervoltage threshold value is provided in the <i>Electrical Characteristics</i> table. |

| $V_L$  | Internal 5V Linear-Regulator Output                                                      |

| EN     | Active-High Enable Input                                                                 |

| VOUT1  | Regulator 1 Output Voltage                                                               |

| SS1    | Regulator 1: Internal Soft-Start Input Signal into Error Amplifier                       |

| VOUT2  | Regulator 2 Output Voltage                                                               |

| SS2    | Regulator 2: Internal Soft-Start Input Signal into Error Amplifier                       |

| DH1    | Regulator 1: High-Side Gate-Driver Output                                                |

| DL1    | Regulator 1: Low-Side Gate-Driver Output                                                 |

| DH2    | Regulator 2: High-Side Gate-Driver Output                                                |

| DL2    | Regulator 2: Low-Side Gate-Driver Output                                                 |

| A      | $V_L$ rising while below the UVLO threshold. EN is low.                                  |

| B      | $V_L$ is greater than the UVLO threshold. EN is low.                                     |

| C      | EN is pulled high. DH1 and DL1 start switching. DH2 and DL2 are off.                     |

| SYMBOL | DEFINITION                                                                                  |

|--------|---------------------------------------------------------------------------------------------|

| D      | Normal operation                                                                            |

| E      | $V_L$ enters UVLO.                                                                          |

| F      | $V_L$ exits UVLO.                                                                           |

| G      | Resumes normal operation. DH1 and DL1 start switching. DH2 and DL2 are off.                 |

| H      | EN is pulled low and then high.                                                             |

| I      | VOUT1 must reach OV before restarting due to the cycling of the enable in region H (above). |

| J      | VOUT1 recovers.                                                                             |

| K      | VOUT2 recovers.                                                                             |

| L      | $V_L$ enters UVLO before VOUT2 fully recovers.                                              |

| M      | $V_L$ exits UVLO.                                                                           |

| N      | UVLO latches DL_low.                                                                        |

| O      | Exiting UVLO: DL_low remains latched low until the first fall of DH_low is detected.        |

| P      | DL_low is high after EN is pulled low and soft-stop is complete.                            |

図4. MAX1858Aの電源オン/オフシーケンス詳細

# シーケンス/プリバイアス起動及びPOR付 デュアル180°逆位相ステップダウンコントローラ

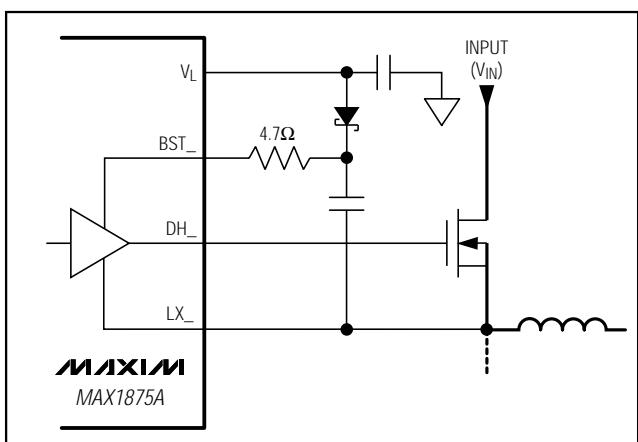

## ハイサイドゲートドライバ用電源(BST\_)

ハイサイドNチャネルスイッチのためのゲート駆動電圧はフライング型のコンデンサ昇圧回路によって発生されます(図5)。昇圧用コンデンサ(BST\_からLX\_への接続)はハイサイドMOSFETドライバの電源を供給します。

動作開始時点で、同期整流器(ローサイドMOSFET)はLX\_をグランドに強制し昇圧用コンデンサを5Vに充電します。ローサイドMOSFETがオフとなった後の2つ目の半サイクルで、BST\_とDH\_の間の内部スイッチを閉じることによってハイサイドMOSFETがオンとなります。このことがハイサイドスイッチをオンとするのに必要なゲートとソース間の電圧を供給することになり、このために5Vのゲート駆動電圧をV<sub>IN</sub>に加算するブースト動作となるのです。ハイサイドMOSFETのゲートを駆動するために必要な電流( $f_{SWITCH} \times Q_G$ )は最終的にはV<sub>L</sub>から供給されます。

## MOSFETのゲートドライバ(DH\_、DL\_)

DHとDLドライバは中程度の大きさのNチャネルハイサイド、及びより大きなローサイドパワーMOSFETを駆動するよう最適化されています。これはV<sub>IN</sub>- V<sub>OUT</sub>の電位差が大きい場合に見られる低いデューティサイクルの場合と矛盾しません。DL\_ローサイド駆動波形は常にDH\_ハイサイド駆動波形の反転波形となっています(クロス伝導または“貫通”を防ぐための制御されたデッドタイム付)。適応型デッドタイム回路がDL\_出力をモニタしDL\_が十分にオフとなるまでハイサイドFETがオンとなることを防ぎます。適応型デッドタイム制御が適切に動作するためにはDL\_ドライバからMOSFETゲートに至る低抵抗、低インダクタンスの経路が存在しなければなりません。そうでなければ、MAX1858A/MAX1875A/MAX1876A内のセンス回路がゲート上に実際に電荷がなお存在しているにもかかわらず、MOSFETが“オフ”となっているとみなしてしまいます。非常に短く幅の広い配線(MOSFETが本デバイスから1インチ離れていれば50ミル~100ミル幅)を使用してください。

図5. スイッティングノードの立上り時間を減らす

DHのオフェッジにおけるデッドタイムは固定された30nsの内部遅延によって決定されます。

同期整流では、通常使われるローサイド側のショットキキャッチダイオードの代わりに低抵抗のMOSFETを使うため、整流器における導電損失を減らすことができます。それに加えて、MAX1858A/MAX1875A/MAX1876Aは同期整流器をブーストゲートドライバ回路の適切な動作開始を保証するために使用し、電流制限用の信号を与えます。

DL\_をロー(低)に駆動する内部のプルダウントランジスタには十分な0.5 (typ)のオン抵抗があります。この低いオン抵抗はLX\_ノードの速い立上りの間にDL\_がプルアップされることを防ぐ働きをします。LX\_ノードの速い立上りはローサイドの同期整流用MOSFETのドレインからゲートへの容量結合により生じるものです。しかし、大電流のアプリケーションでは、ハイ及びローサイドFETの組合わせによっては過剰なゲートとドレイン間の結合が生じ、効率の悪化、EMI、及び貫通電流を生じさせることになります。これはBST\_と直列に抵抗(標準的には5 Ω以下)を挿入することで改善することができます。これはオフになる時間を悪化させることなく、ハイサイドFETのオン時間を改善させることができます(図5)。

## 電流制限回路(ILIM\_)

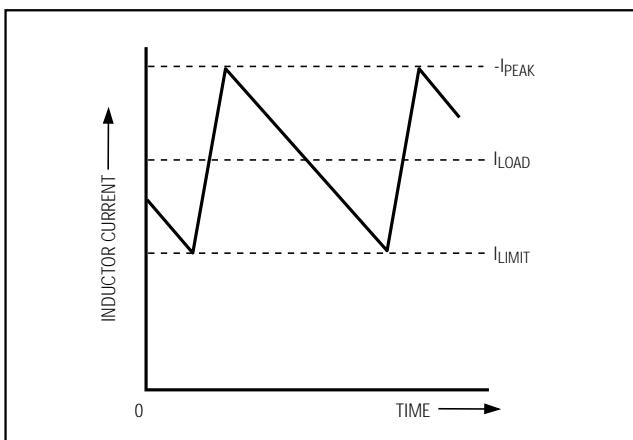

電流制限回路は電流検出素子としてローサイドのMOSFETのオン抵抗を利用する“谷(valley)”電流検出アルゴリズムを採用しています。電流検出信号が電流制限スレッショルドレベルを超えると、MAX1858A/MAX1875A/MAX1876Aは新しいサイクルを開始しません(図6)。谷電流検出が採用されているので、実際のピーク電流はインダクタのリップル電流値だけ電流制限スレッショルドより大きくなります。したがって正確な電流制限特性と最大負荷能力はローサイドMOSFETのオン抵抗、電流制限スレッショルド、インダクタの値、

図6. “谷”電流制限のスレッショルド点

# シーケンス/プリバイアス起動及びPOR付 デュアル180 °逆位相ステップダウンコントローラ

MAX1858A/MAX1875A/MAX1876A

及びオン抵抗の関数となります。この不確定性に対するメリットは、高コストな検出抵抗を必要としない、安定した無損失の電流検出ができます。

電流制限値を調整できることにより、広い範囲のオン抵抗特性を持つMOSFETの使用が可能になります(「設計手法」のセクションを参照)。電流制限スレッショルドはILIM\_に接続した外部抵抗で調整できます(図1)。調整範囲は50mV ~ 300mVであり、これは100 k ~ 600k に対応します。調整可能モードでは、ローサイドMOSFETの電流制限スレッショルドはILIM\_端子に表れる電圧の正確に1/10です。しかし、ILIM\_がVLに接続された場合は電流制限スレッショルドのデフォルト値は100mVとなります。この100mVのデフォルト値に切替わる論理スレッショルドはVL- 0.5Vです。

調整可能なフォールドバック型の電流制限機構によって短絡状態における電力消費が減少します(「設計手法」のセクションを参照)。

LX\_とPGND間に現れる電流検出信号がノイズやDC電圧に影響されないようにプリント基板のレイアウトのガイドラインを守ってください。ICはケルビン接続を行って、意図したローサイドMOSFETのオン抵抗に配線抵抗が加わらないようにし、ローサイドMOSFETの近くに、短く直結された接続となるように実装してください。

## 低電圧ロックアウトと起動

もしVL\_が4.2V以下に低下すると、MAX1858A/MAX1875A/MAX1876Aは、入力電源と基準電圧が低すぎて正しい判断ができないとみなし、低電圧ロックアウト(UVLO)回路を動作させ、スイッチングを禁止するためにDLとDHをラッチします。RSTは同様にUVLOの間はロー(低)に強制されます。ラッチを解除して次のVL\_を立上げるためには、VL\_は2.5V以下に低下させなければなりません。

加えて、正常な起動を行うためには、REFからGNDに接続するコンデンサの値は次の条件を満たす必要があります：

$$C_{REF} > ((8.29 \times 10^{-4}) / V_{+,\text{SLOPE}}) - (1.97 \times 10^{-1} / f_{S,\text{MAX}})$$

ここで、V<sub>+,\text{SLOPE}</sub>は実際の入力電圧の立上り時のスルーレートです。

例えば、もしスイッチング周波数が標準値として600kHzに設定されたとすると、それは660kHz(MAX)であり、入力電圧の立上り時間のスルーレイトを1.6V/mSとするとC<sub>REF</sub>は0.22μF以上の値にする必要があります。ワーストケースのコンデンサ値と温度係数を確認してC<sub>REF</sub>は十分に大きい値となるように選択してください。

イネーブル(EN)、ソフトスタート、及びソフトストップEN端子をハイに設定するとレギュレータを動作可能とし、ローに設定するとシャットダウンします。詳細については、図3、及び図4のタイミング図を参照ください。

## 出力電圧のシーケンス

起動回路がコントローラを動作可能とした後、MAX1858Aは起動シーケンスを開始します。レギュレータ1(OUT1)はソフトスタートがイネーブルとなると電源供給されます。最初のコンバータのソフトスタートが終わると、レギュレータ2(OUT2)の電源がソフトスタートのイネーブルで電源投入されます。最後に両出力電圧がその公称値の90%に達するとリセット出力(RST)がハイとなります(「リセット出力」のセクションを参照)。ソフトトップはENをローに強制することで開始されます。ソフトトップはソフトスタートと反対の順序で行われ、ラストオン/ファーストオフの動作を可能とします。

## リセット出力(RST)

(MAX1858A/MAX1876Aのみ)

RSTはオープンドレイン型の出力です。RSTはどちらかの出力がその公称調整電圧値の90%以下に低下するとローに強制されます。両方の出力がその公称調整電圧値の90%を超えると、RSTはハイインピーダンス状態になります。論理電圧出力を得るためにRSTにプルアップ抵抗を接続し、それを論理電圧電源に接続してください。100k の抵抗を使うとほとんどのアプリケーションに適合します。もし使用しない場合は、RST端子はグランドに接続するか、または開放してください。

## クロック同期(SYNC、CKO)

SYNCは2つの機能を持ちます：SYNCはスレーブコントローラを同期化させるためのクロック出力(CKO)のタイプを選択するか、またはMAX1858A/MAX1875A/MAX1876Aが外部クロック信号に同期することができます。CKOはMAX1858A/MAX1875A/MAX1876Aのスイッチング周波数に同期したクロック信号を供給し、もう一つのDC-DCコントローラの同相(SYNC = GND)または90°位相差(SYNC = VL)を可能とします(図7)。MAX1858A/MAX1875A/MAX1876Aには次に示す3種の動作モードがあります：

- SYNC = GND : CKO出力周波数はREG1のスイッチング周波数( $f_{CKO} = f_{DH1}$ )となり、CKO信号はREG1のスイッチング周波数と同位相となります。この信号を使って2番目のスレーブコントローラと同期させれば2相動作を行わせることができます。

- SYNC = VL : CKO出力周波数はREG1のスイッチング周波数の2倍( $f_{CKO} = 2f_{DH1}$ )となりCKO信号はREG1のスイッチング周波数に対して90°位相差します。これは2つ目のMAX1858A/MAX1875A/MAX1876A(スレーブコントローラ)と同期させると4相動作を可能とします。

# シーケンス/プリバイアス起動及びPOR付 デュアル180°逆位相ステップダウンコントローラ

- 外部発振器でSYNCを駆動する：コントローラはSYNC端子に入力された信号を分周してクロック信号を作るため、スイッチング周波数は同期周波数の半分( $f_{SW} = f_{SYNC}/2$ )となります。REG1の変換サイクルは内部クロック信号の立ち上りエッジで開始されます。CKO出力周波数と位相はREG1のスイッチング周波数と一致( $f_{CKO} = f_{DH1}$ )し、CKOは同相となります。SYNC端子に外部クロックが接続されている場合でもMAX1858A/MAX1875A/MAX1876Aは $R_{OSC}$ を接続する必要があり、内部の発振周波数は同期周波数の50%に設定する( $f_{SW} = 0.5 f_{SYNC}$ )ように注意してください。

## 熱過負荷に対する保護

熱過負荷保護機能によってMAX1858A/MAX1875A/MAX1876A内の総合電力消費が制限されます。デバイスのチップ接合の温度が $T_J = +160$  を超えるとチップに搭載した熱センサがデバイスをシャットダウンし、DL\_とDH\_信号をローに強制し、ICを冷却します。熱センサは接合温度が10°だけ低下すると再びデバイスをオンとします。サーマルシャットダウンの状態ではレギュレータはシャットダウンされ、 $\overline{RST}$ はローとなり、ソフトスタートはリセットされます。もし $V_L$ リニアレギュレータ出力が短絡された場合、熱過負荷保護回路がトリガされます。

## 設計手法

### 実効入力電圧範囲

MAX1858A/MAX1875A/MAX1876Aコントローラは4.5V～23Vの入力電源で動作可能ですが、入力電圧範囲はMAX1858A/MAX1875A/MAX1876Aのデューティサイクル制限により実質的に制限されます。最大入力電圧は最小のオン時間( $t_{ON(MIN)}$ )で制限され、その電圧は次の式で表すことができます：

$$V_{IN(MAX)} \leq \frac{V_{OUT}}{t_{ON(MIN)} f_{SW}}$$

ここで、 $t_{ON(MIN)}$ は100nsです。最小の入力電圧はスイッチング周波数と最小のオフ時間によって制限を受けます。最小のオフ時間は最大のデューティサイクル( $D_{MAX} = 1 - f_{SW} t_{OFF(MIN)}$ )を決定します：

$$V_{IN(MIN)} = \left[ \frac{V_{OUT} + V_{DROP1}}{1 - f_{SW} t_{OFF(MIN)}} \right] + V_{DROP2} - V_{DROP1}$$

ここで、 $V_{DROP1}$ はインダクタの放電経路に存在する寄生電圧降下の合計を表します。これには、同期整流器、インダクタ、及びプリント基板の抵抗が含まれます。 $V_{DROP2}$ は充電経路の抵抗による電圧降下の合計であり、これにはハイサイドスイッチ、インダクタ、及びプリント基板の抵抗が含まれます。

図7. 同期化コントローラ

# シーケンス/プリバイアス起動及びPOR付 デュアル180°逆位相ステップダウンコントローラ

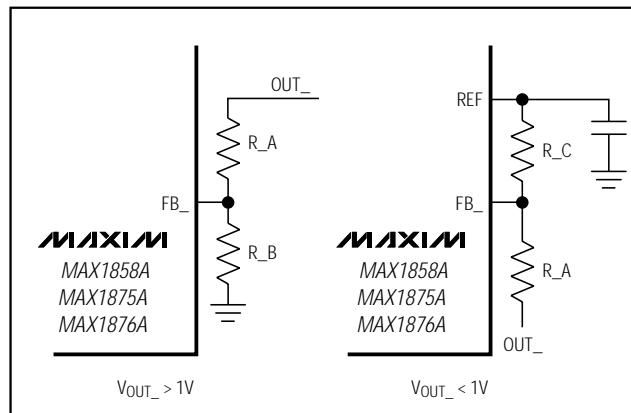

## 出力電圧の設定

1V以上の出力電圧を得るために、MAX1858A/MAX1875A/MAX1876Aの出力端子に電圧分割器を、FB\_を経由してGNDに接続してください(図8)。R\_B(FB\_からGNDへの抵抗)としては1k ~ 10kを選択してください。R\_A(OUT\_とFB\_間の抵抗)を次の式を使って計算してください：

$$R_A = R_B \left[ \left( \frac{V_{OUT}}{V_{SET}} \right) - 1 \right]$$

ここで、 $V_{SET} = 1V$  (「ELECTRICAL CHARACTERISTICS」を参照してください)であり $V_{OUT}$ は $V_{SET} \sim 18V$ の値です。

出力電圧が1Vより低い場合は、電圧分割器を出力からFB\_を経由し、REF間に接続することによってMAX1858A/MAX1875A/MAX1876Aの出力電圧を設定してください(図8)。R\_C(FBとREF間の抵抗)の値は1k ~ 10k の範囲で選択してください。R\_Aの値は次の式にしたがって計算してください：

$$R_A = R_C \left( \frac{V_{SET}-V_{OUT}}{V_{REF}-V_{SET}} \right)$$

ここで、 $V_{SET} = 1V$ 、 $V_{REF} = 2V$ (「ELECTRICAL CHARACTERISTICS」を参照)であり、 $V_{OUT}$ は0から $V_{SET}$ の間の電圧を得ることができます。

## スイッチング周波数の設定

コントローラは内部発振器を分周するか、または外部発振器によって駆動される場合はSYNC入力信号を分周してクロック信号を発生させます。したがってスイッチング周波数は発振器周波数の半分( $f_{SW} = f_{OSC}/2$ )となります。内部の発振器周波数はOSC端子とGND間に接続する抵抗( $R_{OSC}$ )によって設定できます。 $f_{SW}$ と $R_{OSC}$ との関係は次式で表すことができます：

$$R_{OSC} = \frac{6 \times 10^9 (\Omega \cdot Hz)}{f_{SW}}$$

ここで、 $f_{SW}$ はHzであり $R_{osc}$ は の単位で表します。例えば、600kHzのスイッチング周波数は $R_{osc} = 10k$  で設定できます。高い周波数にすると、小さいインダクタ値と出力コンデンサを小さくできます。結果として、ピーク電流と $I^2R$ 損失は高周波に設定するほど少なくなりますが、コアの損失、ゲート電荷電流、及びスイッチング損失は増加します。

SYNC端子の立上りクロックエッジは同期入力として扱われます。もしSYNC信号を喪失すると内部の発振器がスイッチング速度の制御を行い、 $R_{osc}$ の値によって設定されるスイッチング周波数となります。このため、間欠的なSYNC信号の場合でさえ、出力のレギュレーションが行われます。外部同期信号を使う場合は、

図8. 可変出力電圧

スイッチング周波数をSYNC速度( $f_{SYNC}$ )の半分とする $R_{osc}$ の値に設定してください。

## インダクタの選択

MAX1858A/MAX1875A/MAX1876Aを動作させるためには、インダクタの3つの重要なパラメータを決める必要があります：インダクタンスの値(L)、ピークのインダクタ電流( $I_{PEAK}$ )、及びDC抵抗( $R_{DC}$ )です。以下の式はインダクタのピークトゥピークのAC電流のDC平均電流に対する一定の比(LIR)を仮定しています。LIRの値が高すぎるとRMS電流が大きく、したがって $I^2R$ 損失が大きくなります。LIRを小さくするためには、インダクタンスの値を大きくしなければなりません。通常、インダクタンスの値はそれに比例して抵抗を増加させる(同じパッケージの場合)ため、低いLIR値に比べて再び $I^2R$ 損失を増加させることになります。大きさと損失の間での良い妥協は30%のピークトゥピークリップル電流対平均電流の比を選択することです( $LIR = 0.3$ )。スイッチング周波数、入力電圧、出力電圧、及び選定したLIRの値により、インダクタンス値を次の式を用いて求めることができます：

$$L = \frac{V_{OUT}(V_{IN} - V_{OUT})}{V_{IN}f_{SW}I_{OUT}LIR}$$

ここで $V_{IN}$ 、 $V_{OUT}$ 、及び $I_{OUT}$ は標準値です(これは標準的な条件で効率を最適化するためです)。スイッチング周波数は $R_{osc}$ によって設定することができます(「スイッチング周波数の設定」のセクションを参照してください)。正確なインダクタンスの値は重要ではなく、大きさ、コスト、及び効率の間のトレードオフを行うために調整することができます。インダクタンスの値を小さくすると、大きさとコストを下げるができるだけでなく、過渡応答を改善しますが、ピーク電流が大きいことにより、効率を低下させます。一方、インダクタンス値を大きくするとRMS電流を小さくすることができます。しかし、AC電流を小さくできる反面、巻き線数が増えることによる抵抗損失が増す可能性があります。これは、

# シーケンス/プリバイアス起動及びPOR付 デュアル180°逆位相ステップダウンコントローラ

特にサイズを大きくしないでインダクタンス値を大きくする場合に、起こりやすくなります。

許容寸法で、可能な限り小さいDC抵抗を持つ低損失のインダクタを選択してください。インダクタの飽和値の仕様は最大の負荷電流( $I_{LOAD(MAX)}$ )におけるピークのインダクタ電流を超えるなければなりません：

$$I_{PEAK} = I_{LOAD(MAX)} + \left( \frac{L_{IR}}{2} \right) I_{LOAD(MAX)}$$

## 谷(Valley)電流の限界値の設定

最小の電流制限スレッショルド値は、予想される最大の負荷電流におけるローサイドMOSFETのオン抵抗値のワーストケースの場合でも十分に高い値でなければなりません。それはローサイドMOSFETのオン抵抗が電流検出素子として使われるからです。インダクタの谷電流は $I_{LOAD(MAX)}$ からリップル電流の半分を引いた値で起こります。電流検出スレッショルド電圧( $V_{ITH}$ )は、リップル電流が谷状態の時にローサイドMOSFETの電圧降下よりも大きい値としなければなりません：

$$V_{ITH} > R_{DS(ON,MAX)} \times I_{LOAD(MAX)} \times \left( 1 - \frac{L_{IR}}{2} \right)$$

ここで、 $R_{DS(ON)}$ はローサイドMOSFET( $N_L$ )のオン抵抗です。ローサイドMOSFETのデータシートにある $R_{DS(ON)}$ の最大値を使用し、温度による $R_{DS(ON)}$ の増大に対するマージンをさらに持つことを推奨します。一般的にはMOSFETの接合部の温度上昇で1°当たり0.5%の増加を見込むことが良いルールとなります。

電流制限スレッショルドのデフォルト値である100mV(typ)に設定するためにはILIM\_をVLに接続してください。スレッショルド値を変えるためには抵抗( $R_{ILIM_}$ )をILIM\_とGND間に接続してください。電流制限スレッショルド値( $V_{ITH_}$ )と $R_{ILIM_}$ との関係は次の式で与えられます：

$$R_{ILIM_} = \frac{V_{ITH_}}{0.5\mu A}$$

ここで、 $R_{ILIM_}$ はΩ、 $V_{ITH_}$ はVの単位です。

$R_{ILIM}$ を100k~600kの値とすると、電流制限スレッショルド値の50mV~300mVに対応します。電流制限値を調整する場合、1%精度の抵抗を使用すると電流制限スレッショルド値の誤差を最小化できます。

フォールドバック型の電流制限を行うためには、抵抗( $R_{FB1}$ )をILIM端子と出力端子の間に追加します。 $R_{ILIM}$ と $R_{FB1}$ の値は以下のようにして計算することができます：

最初にフォールドバックの%値、 $P_{FB}$ を15%~30%の範囲で選択します。すると：

$$R_{FB1} = \frac{P_{FB} \times V_{OUT}}{5 \times 10^{-6} (1 - P_{FB})}$$

及び

$$R_{ILIM} = \frac{10 \times V_{ITH} (1 - P_{FB}) \times R_{FB1}}{[V_{OUT} - 10 \times V_{ITH} (1 - P_{FB})]}$$

もし $R_{ILIM}$ が負の値になったとすると、より低い $R_{DS(ON)}$ を持つローサイドMOSFETを選択するか、または $P_{FB}$ を大きくするか、または両方を組み合わせてコスト、効率、及び短絡状態における低電力消費の最良の組み合わせを選択してください。

## 入力コンデンサ

入力コンデンサは電源から引き出すピーク電流を減少させ、回路のスイッチングにより生じる入力部のノイズと電圧リップルを減少させます。入力コンデンサは次の式によって決められるスイッチング電流によるリップル電流要件( $I_{RMS}$ )を満足しなければなりません：

$$I_{RMS} = I_{LOAD} \frac{\sqrt{V_{OUT}(V_{IN} - V_{OUT})}}{V_{IN}}$$

$I_{RMS}$ は入力電圧が出力電圧の2倍( $V_{IN} = 2V_{OUT}$ )の場合に最大値を取ります。したがって $I_{RMS(MAX)} = I_{LOAD}/2$ となります。大部分のアプリケーションに対して、入力部には非タンタルコンデンサ(セラミック、アルミニウム、ポリマ、またはOS-CON)を使うことが望まれますが、これは非常に低い電源インピーダンスの場合に起こる、大きな突入電流が流れた場合に堅固性が保たれるからです。加えて、コストを下げるために低ESRを持つ2個(または2個以上)の小さい値のコンデンサを並列に接続することができます。最適な長期間の安定性を確保するためにはRMS入力電流による温度上昇が+10°C以下となる入力コンデンサを選択してください。

## 出力コンデンサ

出力コンデンサの重要な選択パラメータはコンデンサの値、ESR、及び電圧定格です。これらのパラメータは全体の安定性、出力リップル電圧、及び過渡応答に影響を与えます。出力リップルは2つの成分からなります：出力コンデンサに蓄積される電荷の変化、及びコンデンサに入出力する電流によるコンデンサのESRに生じる電圧降下です：

$$V_{RIPPLE} \approx V_{RIPPLE(ESR)} + V_{RIPPLE(C)}$$

# シーケンス/プリバイアス起動及びPOR付 デュアル180°逆位相ステップダウンコントローラ

ESRと出力コンデンサの値による出力電圧リップル値は次の式で求めることができます：

$$V_{\text{RIPPLE}(\text{ESR})} = I_{\text{P-P}} R_{\text{ESR}}$$

$$V_{\text{RIPPLE}(C)} = \frac{I_{\text{P-P}}}{8C_{\text{OUT}} f_{\text{SW}}}$$

$$I_{\text{P-P}} = \left( \frac{V_{\text{IN}} - V_{\text{OUT}}}{f_{\text{SW}}} \right) \left( \frac{V_{\text{OUT}}}{V_{\text{IN}}} \right)$$

ここで、 $I_{\text{P-P}}$ はインダクタ電流のピークトゥピーク値(「インダクタの選択」のセクションを参照)です。これらの式は最初にコンデンサを選択する場合に役に立ちます。しかし、最終的にはプロトタイプまたは評価回路でテストしてから決めるべきです。

一般的には、インダクタのリップル電流を小さくすると出力電圧のリップル電圧は小さくなります。インダクタのリップル電流はインダクタ値と入力電圧に依存するので、出力リップル電圧は、より大きいインダクタンスを使用すると小さくなり、入力電圧を高くすると大きくなります。しかし、インダクタのリップル電流は、過渡応答性能に大きい影響を与えます。それは $V_{\text{IN}} - V_{\text{OUT}}$ が小さい場合に顕著となります。インダクタの値を小さくするとインダクタ電流の変化率が速くなり、突然の負荷変動による出力フィルタコンデンサから奪われる電荷を再充電することができます。出力電圧の低下量は、また、最大デューティサイクルの関数であり、それは最小のオフ時間とスイッチング周波数を用いて計算することができます：

$$V_{\text{SAG}} = \frac{L(I_{\text{LOAD1}} - I_{\text{LOAD2}})^2 \left[ \left( \frac{V_{\text{OUT}}}{V_{\text{IN}} f_{\text{SW}}} \right) + t_{\text{OFF(MIN)}} \right]}{2C_{\text{OUT}} V_{\text{OUT}} \left[ \left( \frac{V_{\text{IN}} - V_{\text{OUT}}}{V_{\text{IN}} f_{\text{SW}}} \right) - t_{\text{OFF(MIN)}} \right]}$$

ここで、 $t_{\text{OFF(MIN)}}$ は最小のオフ時間(「ELECTRICAL CHARACTERISTICS」を参照)であり、 $f_{\text{SW}}$ は $R_{\text{OSC}}$ を使って設定することができます(「スイッチング周波数の設定」のセクションを参照)。

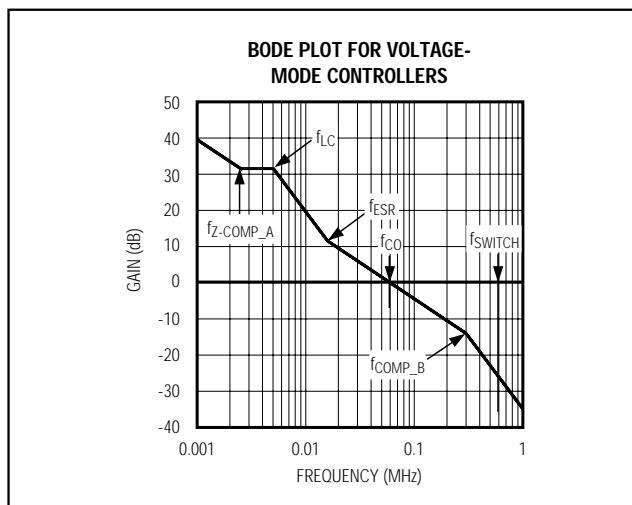

## 補償

各電圧モードコントローラ部はトランスコンダクタ型のエラーアンプを採用しており、その出力は制御ループの補償点となります。制御ループは図9に示されています。ナイキスト周波数よりもかなり低い周波数ではPWMブロックは電圧アンプに簡素化できます。 $R_{\text{COMP}}$ と $C_{\text{COMP\_A}}$ をCOMP端子とGND間に接続してループを補償します(図9)。インダクタ、出力コンデンサ、補償抵抗、及び補償コンデンサがループの安定性を決定します。インダクタと出力コンデンサは性能、大きさ、及びコストによって決定されるので、制御ループの安定性は抵抗とコンデンサを用いて行います。

ループ利得( $A_L$ )を決定するためには、FBからCOMP端子まで( $A_{\text{COMP/FB}}$ )、COMPからLXまで( $A_{\text{LX/COMP}}$ )、及びLXからFBまで( $A_{\text{FB/LX}}$ )の利得を考慮します。すると、総合ループ利得は：

$$A_L = A_{\text{COMP/FB}} \times A_{\text{LX/COMP}} \times A_{\text{FB/LX}}$$

ここで、

$$A_{\text{COMP/FB}} = \frac{V_{\text{COMP}}}{V_{\text{FB}}} \approx \frac{g_{\text{M\_COMP}}}{S C_{\text{COMP}}} \times \frac{1 + S R_{\text{COMP}} C_{\text{COMP\_A}}}{1 + S R_{\text{COMP}} C_{\text{COMP\_B}}}$$

理想的な積分器を仮定し $C_{\text{COMP\_B}}$ が $C_{\text{COMP\_A}}$ よりもかなり小さいと仮定すると：

$$A_{\text{LX/COMP}} = \frac{V_{\text{LX}}}{V_{\text{COMP}}} = \frac{V_{\text{IN}}}{V_{\text{RAMP}}}$$

ここで、 $V_{\text{RAMP}} = 1V_{\text{P-P}}$ として

$$A_{\text{FB/LX}} = \frac{V_{\text{FB}}}{V_{\text{LX}}} = \frac{V_{\text{SET}}}{V_{\text{OUT}}} \frac{1 + S R_{\text{ESR}} C_{\text{OUT}}}{S^2 L C_{\text{OUT}} + S R_{\text{ESR}} C_{\text{OUT}} + 1} \\ \approx \frac{V_{\text{SET}}}{V_{\text{OUT}}} \frac{1 + S R_{\text{ESR}} C_{\text{OUT}}}{V_{\text{OUT}} S^2 L C_{\text{OUT}} + 1}$$

したがって、

$$A_L \approx \frac{g_{\text{M\_COMP}}}{S C_{\text{COMP\_A}}} \times \frac{1 + S R_{\text{COMP}} C_{\text{COMP\_A}}}{1 + S R_{\text{COMP}} C_{\text{COMP\_B}}} \times \frac{V_{\text{IN}}}{V_{\text{RAMP}}} \\ \times \frac{V_{\text{SET}}}{V_{\text{OUT}}} \times \frac{1 + S R_{\text{ESR}} C_{\text{OUT}}}{S^2 L C_{\text{OUT}} + 1}$$

理想的な積分器に対しては、このループ利得はDCにおいて無限大となります。実際には $g_{\text{M}}$ アンプが有限の出力インピーダンスを持つので、利得は有限であるが、大きな値となります。

DC負荷の場合に正確な出力を得ることができるのは、この大きな利得によるためです。この解析をするために主極は積分器により生じ、それはDCで起こると近似することができます。 $R_{\text{COMP}}$ はゼロを発生させ、その周波数は次式となります：

$$f_{Z\_COMP\_A} = \frac{1}{2\pi \times R_{\text{COMP}} C_{\text{COMP\_A}}}$$

インダクタとコンデンサは次式の周波数において二重極を作ります：

$$f_{LC} = \frac{1}{2\pi \sqrt{L C_{\text{OUT}}}}$$

MAX1858A/MAX1875A/MAX1876A

# シーケンス/プリバイアス起動及びPOR付 デュアル180°逆位相ステップダウンコントローラ

ある、より高い周波数において出力コンデンサのインピーダンスはそのESRに比べて無視できる大きさになり、LCシステムはLRシステムに近づき、その結果、二重極を単一極に変えてしまいます。このゼロは次の周波数で起こります：

$$f_{ESR} = \frac{1}{2\pi \times R_{ESR} C_{OUT}}$$

$C_{COMP\_B}$ を用いることにより最後の極を追加することができ、クロスオーバ周波数以上で利得を減じノイズを減衰させます。この極( $f_{COMP\_B}$ )は次の周波数に生じます：

$$f_{COMP\_B} = \frac{1}{2\pi \times R_{COMP} C_{COMP\_B}}$$

図10は相互の位置関係を示した極とゼロ点のボード線図を描いたものです。

クロスオーバの近くでは以下の近似が成立しループ利得の式を簡素化することができます：

- $R_{COMP}$ は $C_{COMP}$ に比べてずっと大きいインピーダンスを持ちます。これはクロスオーバが $f_{Z\_COMP\_A}$ よりも高い周波数で起こる場合にのみ正しく、これが正しければ $C_{COMP\_A}$ は無視することができます(グランドに短絡したのと同じに見なせます)。

- $R_{ESR}$ は $C_{OUT}$ よりもずっと大きいインピーダンスを持ちます。これはクロスオーバ周波数が出力コンデンサのESRによるゼロよりも、ずっと高い周波数で起こる場合にのみ正しく、もしこれが正しければ $C_{OUT}$ はループ利得の中で重要ではない部品となり、無視することができます(グランドに短絡するのと同じです)。

- $C_{COMP\_B}$ は $R_{COMP}$ に比べて、ずっと大きいインピーダンスを持ち無視することができます(オープンに

するのと同じです)。これはクロスオーバが $f_{COMP\_B}$ よりもずっと低い周波数で起こる場合にのみ正しいと言えます。

以下のループ利得の式は、上で述べた近似を図9と共に用いることにより見出すことができます：

$$A_L \approx \frac{V_{IN}}{V_{RAMP}} \times \frac{V_{SET}}{V_{OUT}} \times \frac{gM_{COMP} \times R_{COMP} \times R_{ESR}}{sL}$$

ループ利得を1に設定してクロスオーバ周波数を求める次の式となります：

$$f_{CO} = GBW = \frac{V_{IN}}{V_{RAMP}} \times \frac{V_{SET}}{V_{OUT}} \times \frac{gM_{COMP} \times R_{COMP} \times R_{ESR}}{2\pi \times L}$$

安定性を保証するためには $R_{COMP}$ を次の判別式を満たすように選択します：

- 利得が1となるクロスオーバはスイッチング周波数の1/5以下で起こらなければなりません。

- タイプ1の補償法を用いて適切な位相マージンを得るためにには $f_{CO}$ は $5 \times f_{ESR}$ よりも高くなければなりません。

次の式を用いて $C_{COMP\_A}$ を $f_{Z\_COMP\_A}$ が $f_{LC}$ の半分の周波数になるように選択してください。

$$C_{COMP\_A} = \frac{2 \times \sqrt{LC_{OUT}}}{R_{COMP}}$$

次の式を用いて $C_{COMP\_B}$ を $f_{COMP\_B}$ が $f_{CO}$ の3倍の周波数になるように選択してください。

$$C_{COMP\_B} = \frac{1}{2\pi \times (3 \times f_{CO}) \times R_{COMP}}$$

図9. 周波数固定の場合の電圧モード制御ループ

# シーケンス/プリバイアス起動及びPOR付 デュアル180°逆位相ステップダウンコントローラ

MAX1858A/MAX1875A/MAX1876A

## MOSFETの選択

MAX1858A/MAX1875A/MAX1876A内のステップダウンコントローラはロジックレベルで動作できる2個の外付けNチャネルMOSFETをその回路スイッチ素子として駆動します。その重要な選択パラメータを次に示します：

- ・ オン抵抗( $R_{DS(ON)}$ )

- ・ 最大ドレイン-ソース間電圧( $V_{DS(MAX)}$ )

- ・ 最小のスレッショルド電圧( $V_{TH(MIN)}$ )

- ・ 全ゲート電荷( $Q_g$ )

- ・ 逆方向伝達容量( $C_{RSS}$ )

- ・ 電力消費

4個のNチャネルMOSFETのすべては、オン抵抗の仕様が  $V_{GS} \geq 4.5V$  で保証された論理レベル型でなければなりません。最大の効率を得るために、最適な入力電圧における伝導損失がスイッチング損失に等しいハイサイド MOSFET( $N_H$ )を選択してください。最小入力電圧における伝導損失がMOSFETのパッケージの熱限界を超えないか、または全体の熱マージンを超えることがないかをチェックしてください。また同様に最大入力電圧における伝導損失とスイッチング損失の和がパッケージの定格を超えないか、または全体の熱マージンを超えることがないかをチェックしてください。

MAX1858A/MAX1875A/MAX1876AのDL\_ゲートが  $N_L$  を駆動することができるかチェックしてください。特に、 $N_H$  がオンになるときに起こる  $dv/dt$  が  $N_L$  のドレンとソース間の容量を通して  $N_L$  のゲート電位を引き上げることがないかをチェックしてください。これはクロス伝導問題が最も頻繁に起こる原因です。

ゲート電荷損失はドライバで消費されるのでMOSFETを過熱することはありません。すべてのMOSFETはその全ゲート電荷が十分に小さく、ICを加熱することなく  $V_L$  が4つのすべてのドライバに給電できなければなりません：

$$P_{VL} = V_{IN} \times Q_{G\_TOTAL} \times f_{SW}$$

MOSFETのパッケージの電力消費が主な設計要素となる場合が多いです。 $I^2R$ 損失がハイサイド及びローサイドMOSFETの両方にとて最大の熱消費の原因です。 $I^2R$ 損失は、以下の式に示されるデューティファクタにしたがって  $N_H$  と  $N_L$  との間で分配されます。スイッチング損失はハイサイドのMOSFETにのみ影響します。それはローサイドのMOSFETは降圧型構成の場合、ゼロ電圧で切替わるからです。

パッケージの熱抵抗の仕様にしたがって MOSFET の温度上昇を計算し、両方のMOSFETが高い環境温度でその最高接合部温度以内であるようにしてください。

図10. 電圧モードのループ解析

ハイサイド MOSFET( $P_{NH}$ )に対するワーストケースの消費は入力電圧の両極端値で起こり、ローサイド MOSFET( $P_{NL}$ )のワーストケースの消費は最大の入力電圧で起こります。

$$P_{NH(SWITCHING)} = V_{IN} | LOAD f_{SW} \left( \frac{Q_{GS} + Q_{GD}}{I_{GATE}} \right)$$

$I_{GATE}$ は次の式で決定される平均のDH ドライバ出力の電流能力です：

$$I_{GATE} = \frac{V_L}{2(R_{DS(ON)DH} + R_{GATE} + R_{GMOSFET})}$$

ここで  $R_{DS(ON)DH}$  はハイサイド MOSFET ドライバのオン抵抗(最大 5 ),  $R_{GATE}$  は DH と BST 間に存在する直列抵抗(図 5)、そして  $R_{GMOSFET}$  は外部に接続する MOSFET の内部ゲート抵抗です：

$$P_{NH(CONDUCTION)} = I_{LOAD}^2 R_{DS(ON)NH} \left( \frac{V_{OUT}}{V_{IN}} \right)$$

$$P_{NH(TOTAL)} = P_{NH(SWITCHING)} + P_{NH(CONDUCTION)}$$

$$P_{NL} = I_{LOAD}^2 R_{DS(ON)NL} \left( 1 - \left( \frac{V_{OUT}}{V_{IN}} \right) \right)$$

ここで、 $P_{NH(CONDUCTION)}$  はハイサイド MOSFET 内の伝導電力損失であり  $P_{NL}$  は総合のローサイド電力損失です。

スイッチングノイズによるEMIを減らすためには、ハイサイドスイッチのドレンからローサイドスイッチのソースに  $0.1 \mu F$  のセラミックコンデンサを追加するか、または DL\_ と DH\_ に直列に抵抗を追加し MOSFET のターンオン時間とターンオフ時間を増加させてください。

# シーケンス/プリバイアス起動及びPOR付 デュアル180°逆位相ステップダウンコントローラ

## アプリケーション情報

### ドロップアウト電圧の性能

低い入力電圧で動作させる場合、連続伝導モードで動作させるための出力電圧の調整範囲は最小のオフ時間( $t_{OFF(MIN)}$ )によって制限されます。最良のドロップアウト性能を得るために最低(100kHz)のスイッチング周波数を設定してください。製造誤差と内部の伝播遅延はスイッチング周波数と最小のオフ時間に誤差をもたらします。この誤差は、より高い周波数で大きくなります。また、ドロップアウト電圧に近い値で動作している降圧型のレギュレータの過渡応答は良くないので大きな出力コンデンサを追加する必要があることが多いので注意してください(「設計手法」のセクションの $V_{SAG}$ の式を参照してください)。

ドロップアウトの絶対的な点は、インダクタ電流が最小オフ時間の間に低下する量( $\Delta I_{DOWN}$ )が最大のオン時間に上昇した値( $\Delta I_{UP}$ )と同じになる点です。 $h = \Delta I_{UP} / \Delta I_{DOWN}$ 比はインダクタ電流を、増加した負荷に応答して増加させる指標であり、常に1より大きい値でなければなりません。 $h$ が絶対的な最小ドロップアウト点である1に近づくにつれて、インダクタ電流は各スイッチングサイクルで増加することが出来ず、出力コンデンサを追加しなければ、 $V_{SAG}$ が大きく増加します。

妥当な $h$ の最小値は1.5ですが、これを調整するのは $V_{SAG}$ 、出力コンデンサの値、及び最小の動作電圧の間のトレードオフとなります。 $h$ の値を先に決めると、最小の動作電圧は次の式で計算することができます。

$$V_{IN(MIN)} = \left[ \frac{V_{OUT} + V_{DROP1}}{1 - h f_{SW} t_{OFF(MIN)}} \right] + V_{DROP2} - V_{DROP1}$$

ここで、 $V_{DROP1}$ はインダクタの放電経路における寄生電圧であり、放電経路には同期整流器、インダクタ、及びプリント基板の抵抗が含まれます； $V_{DROP2}$ は充電経路における抵抗の電圧降下の和であり、充電経路にはハイサイドスイッチ、インダクタ、及びプリント基板の抵抗が含まれます； $t_{OFF(MIN)}$ は電気的特性(「ELECTRICAL CHARACTERISTICS」)からくる値です。絶対最小入力電圧は $h = 1$ として計算することができます。

もし、計算された $V_{+}(MIN)$ が、必要とする最小入力電圧よりも高い場合、動作周波数を下げるか、または許容できる $V_{SAG}$ を得るために、出力コンデンサを追加してください。もしドロップアウトに近い動作が予想される場合は $V_{SAG}$ を計算して十分な過渡応答特性が得られるかを確認してください。

### ドロップアウトの計算例：

$$V_{OUT} = 5V$$

$$f_{SW} = 600\text{kHz}$$

$$t_{OFF(MIN)} = 250\text{ns}$$

$$V_{DROP1} = V_{DROP2} = 100\text{mV}$$

$$h = 1.5$$

$$V_{IN(MIN)} = \left[ \frac{5V + 100\text{mV}}{1 - 1.5(600\text{kHz})(250\text{ns})} \right] + 100\text{mV} - 100\text{mV} = 6.58V$$

$h = 1$ として再び計算するとドロップアウトの絶対限界値を得ることができます：

$$V_{IN(MIN)} = \left[ \frac{5V + 100\text{mV}}{1 - (600\text{kHz})(250\text{ns})} \right] + 100\text{mV} - 100\text{mV} = 6V$$

したがって、非常に大きい出力コンデンサを使用したとしても、 $V_{IN}$ は6Vより大きくしなければなりません。そして適度な出力コンデンサを接続したとして、実用的な実際の入力電圧は6.58Vになるでしょう。

### ノイズイミュニティを改善する

MAX1858A/MAX1875A/MAX1876Aをノイズの多い環境で動作させなければならないアプリケーションの場合、コントローラの補償を変えて、システムのノイズイミュニティを改善することができます。特に帰還ループに結合する高周波ノイズはジッタ的なデューティサイクルを生じます。その1つの解はクロスオーバ周波数を下げることです(「補償」のセクションを参照)。

### プリント基板のレイアウトのガイドライン

充分に考慮されたプリント基板のレイアウトはスイッチング損失を低くし、ノイズの無い安定な動作を行わせるために非常に重要です。このことは、特に1つのチャネルが他方に影響を及ぼすデュアルコンバータの場合に有効です。個別のレイアウトの例はMAX1858A EVキットまたはMAX1875 EV キットのデータシートを参照してください。

可能であればボードの上側にすべての電力部品を配置し、それらのグランド端子があ互いに同じ面となるようにしてください。プリント基板のレイアウトを旨く行うためには以下のガイドラインにしたがってください：

- 電力用部品を上側に、アナログ部品は裏側に置いて分離し、グランド面をシールドしてください。OUT1とOUT2側の下に隔離したPGNDを作成して

# シーケンス/プリバイアス起動及びPOR付 デュアル180 °逆位相ステップダウンコントローラ

MAX1858A/MAX1875A/MAX1876A

ください(これをPGND1及びPGND2と言う)。AC電流がPGND1とPGND2のグランド面に流れることを避けてください。電源面のグランド電流を上面側のみに流すようにしてください。

- OUT1とOUT2の間のクロストークを最小化するために電源面上でスター状のグランド接続してください。

- 特にグランド端子の場所で、大電流路を短くしてください。これを実施することは安定でジッタのない動作を行うために必須です。

- ICの近くでGNDとPGNDを接続してください。どこか他の所では接続しないでください。「レイアウトの方法」のセクションに示すステップ4のグランド接続の指示に注意深くしたがってください。

- 電源配線と負荷との接続を短く行ってください。この実施は高い効率を得るために必須なことです。厚い銅を用いたプリント基板(2オンス対1オンス)は最大負荷時の効率を1%以上、高めることができます。

- 電流制限を行うためのLX\_とPGNDの同期整流器との接続は、電流制限の正確さを維持するためにケルビン接続とする必要があります。8ピンのSOP型MOSFETでは、MOSFETへの電源を上側の銅層を用いて行い、一方PGNDとLX\_との接続は8ピンのSOPパッケージの下で行うことが最良です。

- 配線長のトレードオフを必要とする場合はインダクタへの電流を充電する経路は放電経路よりも長くすることができます。ステップダウンコンバータにおいては、平均の入力電流は平均の出力電流よりも小さいので、このことは電力消費とボードの抵抗による電圧降下を最小化します。例えば、インダクタとローサイドMOSFET間、またはインダクタと出力フィルタコンデンサ間の距離よりも、むしろ入力コンデンサとハイサイドMOSFET間の距離を余分に取ります。

- C<sub>OUT</sub>\_へのフィードバック接続は短く直接配線してください。

- 高速度スイッチングを行うノード(BST\_、LX\_、DH\_、及びDL\_)を敏感なアナログ領域(REF、COMP\_、ILIM\_、及びFB\_)から引き離して配線してください。PGND1とPGND2をEMIシールドとして使い、放射するノイズをIC、フィードバック分割器、及びアナログ用のバイパスコンデンサから遠ざけてください。

- 端子をストラップして制御する接続(ILIM\_、SYNC、及びEN)はすべて、電源グランド(PGND)ではなくアナロググランド(GND)に対して行ってください。

## レイアウトの方法

- 電力部品を最初に、隣にはグランド端子を備えて、配置してください(N<sub>L</sub>\_のソース、C<sub>IN</sub>\_、及びC<sub>OUT</sub>\_)。これらの接続は幅の広い銅面(2オンス銅を推奨)を使ってトップ層で行ってください。

- コントローラICを同期整流MOSFET(N<sub>L</sub>\_)の隣に、できれば裏面に配置してください。これはLX\_、PGND\_、及びDL\_の配線を短く、太くなるようにするためです。DL\_のゲート配線は短く、太くしてください。もし、ローサイドMOSFETがコントローラICから1インチ離れていれば、この配線の幅は50ミル~100ミルとしてください。

- ゲートを駆動する部品はコントローラICの近くにまとめて配置してください(BST\_ダイオード及びコンデンサ、及びV<sub>L</sub>のバイパスコンデンサ)。

- DC-DCコントローラのグランド接続は以下のように行ってください：ICの近くに小さいアナロググランド面を作る。この面をGNDに接続し、この面を基準(REF) V+バイパス用コンデンサ、補償用部品、フィードバック分割器、OSC抵抗、及びILIM\_抵抗(使用した場合)のグランド接続用としてください。ICの下でGNDとPGNDを接続してください(これをGNDとPGNDの唯一の接続点としてください)。

- ボードの上側(電源面)には両側間のクロストークを減少させるためのスター状のグランドを作ってください。

## チップ情報

TRANSISTOR COUNT: 6688

PROCESS: BiCMOS

# シーケンス/プリバイアス起動及びPOR付 デュアル180°逆位相ステップダウンコントローラ

## パッケージ

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、<http://japan.maxim-ic.com/packages>をご参照下さい。)

販売代理店

マキシム・ジャパン株式会社

〒169-0051 東京都新宿区西早稲田3-30-16(ホリゾン1ビル)

TEL. (03)3232-6141 FAX. (03)3232-6149

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。

マキシムは随时予告なく回路及び仕様を変更する権利を留保します。

22 Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2003 Maxim Integrated Products

**MAXIM** is a registered trademark of Maxim Integrated Products.