## ダイナミック可変、同期ステップダウンコントローラ

MAX1717

## 概要

MAX1717は、ノートブックコンピュータのコアCPU DC-DCコンバータ用のステップダウンコントローラです。最新のCPUのコア電源に必要なダイナミック可変出力、超高速過渡応答、高DC精度及び高効率の組合せを特長とします。マキシム社独自のQuick-PWM™クイック応答、一定オントライムPWM制御方式は、広い入力/出力電圧比を容易に処理し、比較的一定のスイッチング周波数を維持しながら、負荷トランジエントに対して100ns<sup>†</sup>インスタンット・オン応答を提供します。

出力電圧は、0.925V~2Vの範囲において5ビットのデジタルアナログコンバータ(DAC)入力により動的に調整できます。MAX1717のユニークな特長は、僅か5つのデジタル入力ピンで2つの5ビットDAC設定を受け入れる内部マルチプレクサ(mux)にあります。出力電圧の遷移は、当社独自の高精度スルーレート制御<sup>†</sup>により行われます。これは、バッテリとの間のサージ電流を最小にし、その一方で新しいIDAC設定における「ジャストインタイム」の遷移を保証します。

高いDC精度は、グランドバス及び出力電圧範囲の電圧降下を補償する2線リモート検出方式により強化されています。代わりに、MAX1717の高いDC精度をリモート検出入力と組み合わせることにより、負荷過渡応答を変更して出力コンデンサの条件及び全負荷における電力消費を低減する電圧ポジショニング回路を導入することもできます。

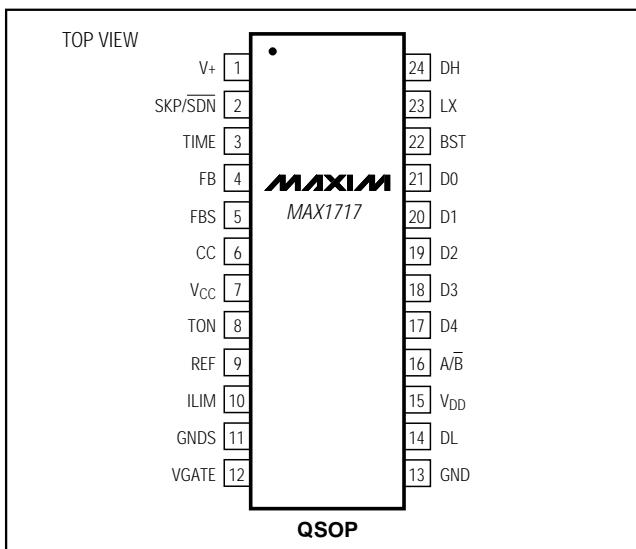

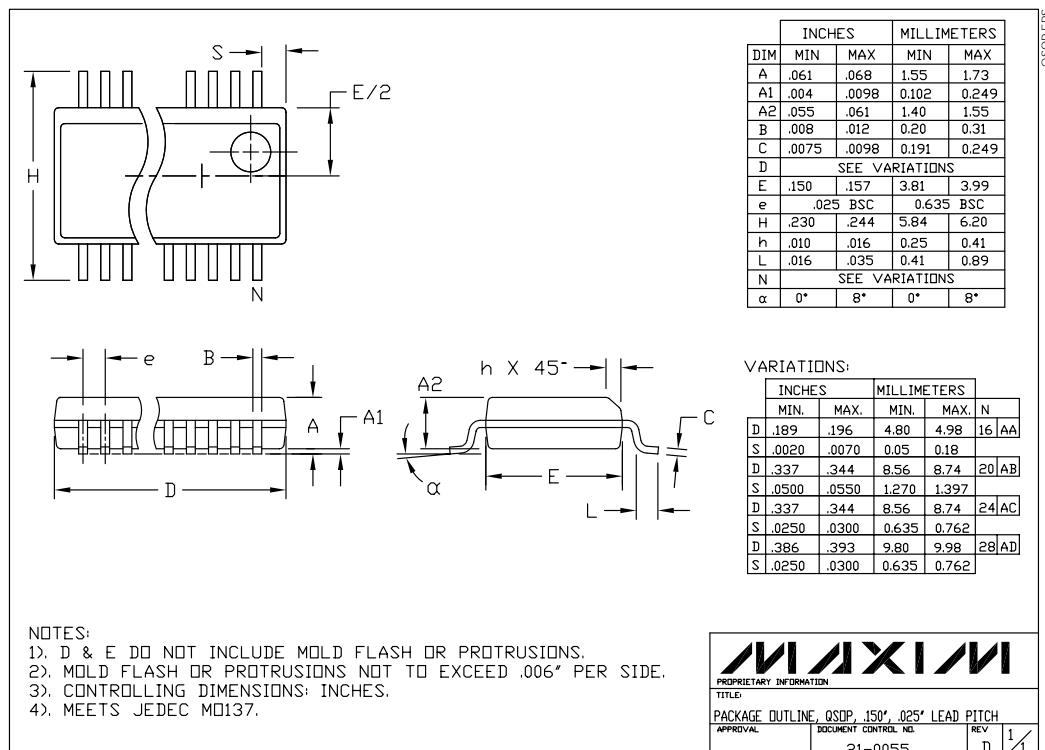

1段バッック変換を使用することにより高圧バッテリを直接ステップダウンし、最高の効率を達成できます。これに対し、高いスイッチング周波数で2段変換(バッテリの代わりに+5Vシステム電源をステップダウン)を使用すると、デバイスのサイズを最小にすることができます。MAX1717は、24ピンのQSOPパッケージで提供されています。

## アプリケーション

SpeedStep™又は他のダイナミック可変プロセッサ付ノートブックコンピュータ

2~4セルLi+バッテリからCPUコア電源へのコンバータ

5VからCPUコア電源へのコンバータ

ピン配置はデータシートの最後に記載されています。

<sup>†</sup>特許申請中

Quick-PWMは、Maxim Integrated Productsの商標です。

SpeedStepは、Intel Corp.の商標です。

## 特長

- ◆ Quick-PWMアーキテクチャ

- ◆ 全入力及び負荷範囲におけるV<sub>OUT</sub>精度： $\pm 1\%$

- ◆ 入力マルチプレクサ付き5ビット内蔵DAC

- ◆ 高精度可変V<sub>OUT</sub>スルーリー制御

- ◆ 可変出力範囲：0.925V~2V

- ◆ 電圧ポジショニングアプリケーションに対応

- ◆ バッテリ入力範囲：2V~28V

- ◆ 個別の+5Vバイアス電源が必要

- ◆ スイッチング周波数：200/300/550/1000kHz

- ◆ 過電圧/低電圧保護

- ◆ 大きな同期整流器FETを駆動

- ◆ I<sub>CC</sub>消費電流：700μA (typ)

- ◆ シャットダウン消費電流：2μA (typ)

- ◆ リファレンス出力：2V±1%

- ◆ VGATE遷移完了インジケータ

- ◆ パッケージ：小型24ピンQSOP

## 型番

| PART       | TEMP RANGE     | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX1717EEG | -40°C to +85°C | 24 QSOP     |

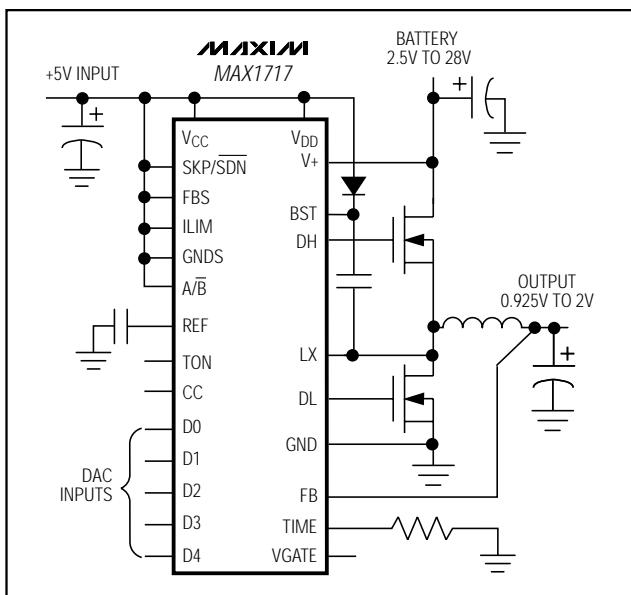

## 最小動作回路

# ノートブックCPU用 ダイナミック可変、同期ステップダウンコントローラ

## ABSOLUTE MAXIMUM RATINGS

|                                                |                                   |

|------------------------------------------------|-----------------------------------|

| V <sub>+</sub> to GND                          | -0.3V to +30V                     |

| V <sub>CC</sub> , V <sub>DD</sub> to GND       | -0.3V to +6V                      |

| D0-D4, A/B, V <sub>GATE</sub> , to GND         | -0.3V to +6V                      |

| SKP/SDN to GND                                 | -0.3V to +16V                     |

| ILIM, FB, FBS, CC, REF, GNDS, TON, TIME to GND | -0.3V to (V <sub>CC</sub> + 0.3V) |

| DL to GND                                      | -0.3V to (V <sub>DD</sub> + 0.3V) |

| BST to GND                                     | -0.3V to +36V                     |

| DH to LX                                       | -0.3V to (BST + 0.3V)             |

|                                           |                 |

|-------------------------------------------|-----------------|

| LX to BST                                 | -6V to +0.3V    |

| REF Short Circuit to GND                  | Continuous      |

| Continuous Power Dissipation              |                 |

| 24-Pin QSOP (derate 9.5mW/°C above +70°C) | 762mW           |

| Operating Temperature Range               | -40°C to +85°C  |

| Junction Temperature                      | +150°C          |

| Storage Temperature                       | -65°C to +150°C |

| Lead Temperature (soldering, 10s)         | +300°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

(Circuit of Figure 1, V<sub>+</sub> = +15V, V<sub>CC</sub> = V<sub>DD</sub> = SKP/SDN = +5V, V<sub>OUT</sub> = 1.6V, T<sub>A</sub> = 0°C to +85°C, unless otherwise noted.)

| PARAMETER                                          | CONDITIONS                                                         | MIN                             | TYP  | MAX  | UNITS |

|----------------------------------------------------|--------------------------------------------------------------------|---------------------------------|------|------|-------|

| <b>PWM CONTROLLER</b>                              |                                                                    |                                 |      |      |       |

| Input Voltage Range                                | Battery voltage, V <sub>+</sub>                                    | 2                               | 28   |      | V     |

|                                                    | V <sub>CC</sub> , V <sub>DD</sub>                                  | 4.5                             | 5.5  |      |       |

| DC Output Voltage Accuracy<br>(Note 1)             | V <sub>+</sub> = 4.5V to 28V,<br>includes load<br>regulation error | DAC codes from 1.3V to 2V       | -1   | 1    | %     |

|                                                    |                                                                    | DAC codes from 0.925V to 1.275V | -1.2 | 1.2  | %     |

| Remote Sense Voltage Error                         | FB to FBS or GNDS to GND = 0 to 25mV                               |                                 | 3    |      | mV    |

| Line Regulation Error                              | V <sub>CC</sub> = 4.5V to 5.5V, V <sub>BATT</sub> = 4.5V to 28V    |                                 | 5    |      | mV    |

| FB Input Resistance                                |                                                                    | 115                             | 180  | 265  | kΩ    |

| FBS Input Bias Current                             |                                                                    | -0.2                            | 0.2  |      | μA    |

| GNDS Input Bias Current                            |                                                                    | -1                              | 1    |      | μA    |

| TIME Frequency Accuracy                            | 150kHz nominal, RTIME = 120kΩ                                      | -8                              | +8   |      | %     |

|                                                    | 380kHz nominal, RTIME = 47kΩ                                       | -12                             | +12  |      |       |

|                                                    | 38kHz nominal, RTIME = 470kΩ                                       | -12                             | +12  |      |       |

| On-Time (Note 2)                                   | V <sub>+</sub> = 5V, FB = 2V, TON = GND (1000kHz)                  | 375                             | 425  | 475  | ns    |

|                                                    | V <sub>+</sub> = 24V, FB = 2V                                      | TON = REF (550kHz)              | 135  | 155  | 173   |

|                                                    |                                                                    | TON = open (300kHz)             | 260  | 289  | 318   |

|                                                    |                                                                    | TON = V <sub>CC</sub> (200kHz)  | 375  | 418  | 461   |

| Minimum Off-Time (Note 2)                          | TON = V <sub>CC</sub> , open, or REF (200kHz, 300kHz, or 550kHz)   |                                 | 400  | 500  | ns    |

| Minimum Off-Time (Note 2)                          | TON = GND (1000kHz)                                                |                                 | 300  | 375  | ns    |

| <b>BIAS AND REFERENCE</b>                          |                                                                    |                                 |      |      |       |

| Quiescent Supply Current (V <sub>CC</sub> )        | Measured at V <sub>CC</sub> , FB forced above the regulation point | 700                             | 1200 |      | μA    |

| Quiescent Supply Current (V <sub>DD</sub> )        | Measured at V <sub>DD</sub> , FB forced above the regulation point | <1                              | 5    |      | μA    |

| Quiescent Battery Supply Current (V <sub>+</sub> ) |                                                                    | 25                              | 40   |      | μA    |

| Shutdown Supply Current (V <sub>CC</sub> )         | SKP/SDN = 0                                                        | 2                               | 5    |      | μA    |

| Shutdown Supply Current (V <sub>DD</sub> )         | SKP/SDN = 0                                                        | <1                              | 5    |      | μA    |

| Shutdown Battery Supply Current (V <sub>+</sub> )  | SKP/SDN = 0, V <sub>CC</sub> = V <sub>DD</sub> = 0 or 5V           | <1                              | 5    |      | μA    |

| Reference Voltage                                  | V <sub>CC</sub> = 4.5V to 5.5V, no REF load                        | 1.98                            | 2    | 2.02 | V     |

ノートブックCPU用

ダイナミック可変、同期ステップダウンコントローラ

**ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_+ = +15V$ ,  $V_{CC} = V_{DD} = \overline{SKP/SDN} = +5V$ ,  $V_{OUT} = 1.6V$ ,  $T_A = 0^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , unless otherwise noted.)

| PARAMETER                                      | CONDITIONS                                                                           | MIN                                                  | TYP          | MAX            | UNITS              |

|------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------|--------------|----------------|--------------------|

| Reference Load Regulation                      | $I_{REF} = 0$ to $50\mu\text{A}$                                                     |                                                      |              | 0.01           | V                  |

| REF Sink Current                               | REF in regulation                                                                    | 10                                                   |              |                | $\mu\text{A}$      |

| <b>FAULT PROTECTION</b>                        |                                                                                      |                                                      |              |                |                    |

| Overvoltage Trip Threshold                     | Measured at FB                                                                       | 2.20                                                 | 2.25         | 2.30           | V                  |

| Overvoltage Fault Propagation Delay            | FB forced 2% above trip threshold                                                    |                                                      | 10           |                | $\mu\text{s}$      |

| Output Undervoltage Fault Protection Threshold | With respect to unloaded output voltage                                              | 65                                                   | 70           | 75             | %                  |

| Output Undervoltage Fault Propagation Delay    | FB forced 2% below trip threshold                                                    |                                                      | 10           |                | $\mu\text{s}$      |

| Output Undervoltage Fault Blanking Time        | From $\overline{SKP/SDN}$ signal going high, clock speed set by RTIME                | 256                                                  |              |                | clks               |

| Current-Limit Threshold (Positive, Default)    | GND - LX, ILIM = $V_{CC}$                                                            | $T_A = +25^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ | 90           | 100            | 110                |

| Current-Limit Threshold (Positive, Adjustable) |                                                                                      | $T_A = 0^{\circ}\text{C}$ to $+85^{\circ}\text{C}$   | 85           | 115            |                    |

| Current-Limit Threshold (Positive, Adjustable) | GND - LX                                                                             | ILIM = 0.5V                                          | 35           | 50             | 65                 |

| Current-Limit Threshold (Negative)             |                                                                                      | ILIM = REF (2V)                                      | 165          | 200            | 230                |

| Current-Limit Threshold (Negative)             | LX - GND, ILIM = $V_{CC}$                                                            | -140                                                 | -110         | -80            | mV                 |

| Current-Limit Threshold (Zero Crossing)        | GND - LX                                                                             |                                                      | 4            |                | mV                 |

| Current-Limit Default Switchover Threshold     |                                                                                      | 3                                                    | $V_{CC} - 1$ | $V_{CC} - 0.4$ | V                  |

| Thermal Shutdown Threshold                     | Hysteresis = $10^{\circ}\text{C}$                                                    |                                                      | 150          |                | $^{\circ}\text{C}$ |

| $V_{CC}$ Undervoltage Lockout Threshold        | Rising edge, hysteresis = 20mV, PWM disabled below this level                        | 4.1                                                  |              | 4.4            | V                  |

| VGATE Lower Trip Threshold                     | Measured at FB with respect to unloaded output voltage, rising edge, hysteresis = 1% | -8                                                   | -6.5         | -5             | %                  |

| VGATE Upper Trip Threshold                     | Measured at FB with respect to unloaded output voltage, rising edge, hysteresis = 1% | +10                                                  | +12          | +14            | %                  |

| VGATE Propagation Delay                        | FB forced 2% outside VGATE trip threshold                                            |                                                      | 10           |                | $\mu\text{s}$      |

| VGATE Transition Delay                         | After $X = Y$ , clock speed set by RTIME                                             |                                                      | 1            |                | clk                |

| VGATE Output Low Voltage                       | $I_{SINK} = 1\text{mA}$                                                              |                                                      |              | 0.4            | V                  |

| VGATE Leakage Current                          | High state, forced to 5.5V                                                           |                                                      |              | 1              | $\mu\text{A}$      |

| <b>GATE DRIVERS</b>                            |                                                                                      |                                                      |              |                |                    |

| DH Gate Driver On-Resistance                   | BST - LX forced to 5V                                                                | 1.0                                                  | 3.5          |                | $\Omega$           |

| DL Gate Driver On-Resistance                   | DL, high state (pullup)                                                              | 1.0                                                  | 3.5          |                | $\Omega$           |

|                                                | DL, low state (pulldown)                                                             | 0.4                                                  | 1.0          |                |                    |

| DH Gate-Driver Source/Sink Current             | DH forced to 2.5V, BST - LX forced to 5V                                             |                                                      | 1.3          |                | A                  |

| DL Gate-Driver Sink Current                    | DL forced to 2.5V                                                                    | 4                                                    |              |                | A                  |

MAX1717

# ノートブックCPU用 ダイナミック可変、同期ステップダウンコントローラ

## ELECTRICAL CHARACTERISTICS (continued)

(Circuit of Figure 1,  $V_+ = +15V$ ,  $V_{CC} = V_{DD} = SKP/SDN = +5V$ ,  $V_{OUT} = 1.6V$ ,  $T_A = 0^\circ C$  to  $+85^\circ C$ , unless otherwise noted.)

| PARAMETER                             | CONDITIONS                                                           |           | MIN            | TYP  | MAX  | UNITS |

|---------------------------------------|----------------------------------------------------------------------|-----------|----------------|------|------|-------|

| DL Gate-Driver Source Current         | DL forced to 2.5V                                                    |           |                | 1.3  |      | A     |

| Dead Time                             | DL rising                                                            |           |                | 35   |      | ns    |

|                                       | DH rising                                                            |           |                | 26   |      |       |

| <b>LOGIC AND I/O</b>                  |                                                                      |           |                |      |      |       |

| Logic Input High Voltage              | D0-D4, A/Ā                                                           |           |                | 2.4  |      |       |

| Logic Input Low Voltage               | D0-D4, A/Ā                                                           |           |                | 0.8  |      |       |

| DAC B-Mode Programming Resistor, Low  | D0-D4, 0 to 0.4V or 2.6V to 5.5V applied through resistor, A/Ā = GND |           |                | 1.05 |      |       |

| DAC B-Mode Programming Resistor, High | D0-D4, 0 to 0.4V or 2.6V to 5.5V applied through resistor, A/Ā = GND |           | 95             |      |      | kΩ    |

| D0-D4 Pullup/Pulldown                 | Entering B mode                                                      | Pull up   |                | 40   |      | kΩ    |

|                                       |                                                                      | Pull down |                | 8    |      |       |

| Logic Input Current                   | D0-D4, A/Ā = 5V                                                      |           | -1             | 1    |      | μA    |

|                                       | A/Ā                                                                  |           | -1             | 1    |      |       |

| TON Input Levels                      | For TON = $V_{CC}$ (200kHz operation)                                |           | $V_{CC} - 0.4$ |      |      | V     |

|                                       | For TON = open (300kHz operation)                                    |           | 3.15           |      | 3.85 |       |

|                                       | For TON = REF (550kHz operation)                                     |           | 1.65           |      | 2.35 |       |

|                                       | For TON = GND (1000kHz operation)                                    |           | 0.5            |      |      |       |

| SKP/SDN and TON Input Current         | SKP/SDN, TON forced to GND or $V_{CC}$                               |           | -3             | 3    |      | μA    |

| SKP/SDN Input Levels                  | SKP/SDN = logic high (SKIP mode)                                     |           | 2.8            | 6    |      | V     |

|                                       | SKP/SDN = open (PWM mode)                                            |           | 1.8            | 2.2  |      |       |

|                                       | SKP/SDN = logic low (shutdown mode)                                  |           |                | 0.5  |      |       |

|                                       | To enable no-fault mode                                              |           | 12             | 15   |      |       |

## ELECTRICAL CHARACTERISTICS

(Circuit of Figure 1,  $V_+ = +15V$ ,  $V_{CC} = V_{DD} = SKP/SDN = +5V$ ,  $V_{OUT} = 1.6V$ ,  $T_A = -40^\circ C$  to  $+85^\circ C$ , unless otherwise noted.) (Note 3)

| PARAMETER                           | CONDITIONS                                                   |                                 | MIN  | TYP | MAX | UNITS |

|-------------------------------------|--------------------------------------------------------------|---------------------------------|------|-----|-----|-------|

| DC Output Voltage Accuracy (Note 1) | V <sub>+</sub> = 4.5V to 28V, includes load regulation error | DAC codes from 1.3V to 2V       | -1.5 | 1.5 |     | %     |

|                                     |                                                              | DAC codes from 0.925V to 1.275V | -1.7 | 1.7 |     |       |

| TIME Frequency Accuracy             | 150kHz nominal, $R_{TIME} = 120k\Omega$                      |                                 | -8   | +8  |     | %     |

|                                     | 380kHz nominal, $R_{TIME} = 47k\Omega$                       |                                 | -12  | +12 |     |       |

|                                     | 38kHz nominal, $R_{TIME} = 470k\Omega$                       |                                 | -12  | +12 |     |       |

| On-Time (Note 2)                    | V <sub>+</sub> = 5V, FB = 2V, TON = GND (1000kHz)            |                                 | 375  | 475 |     | ns    |

| On-Time (Note 2)                    | V <sub>+</sub> = 24V, FB = 2V                                | TON = REF (550kHz)              | 136  | 173 |     | ns    |

|                                     |                                                              | TON = open (300kHz)             | 260  | 318 |     |       |

|                                     |                                                              | TON = $V_{CC}$ (200kHz)         | 365  | 471 |     |       |

| Minimum Off-Time (Note 2)           | TON = $V_{CC}$ , open, or REF (200kHz, 300kHz, or 550kHz)    |                                 |      | 500 |     | ns    |

| Minimum Off-Time (Note 2)           | TON = GND (1000kHz)                                          |                                 |      | 375 |     | ns    |

ノートブックCPU用

ダイナミック可変、同期ステップダウンコントローラ

MAX1717

**ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_+ = +15V$ ,  $V_{CC} = V_{DD} = SKP/\bar{SDN} = +5V$ ,  $V_{OUT} = 1.6V$ ,  $T_A = -40^\circ C$  to  $+85^\circ C$ , unless otherwise noted.) (Note 3)

| PARAMETER                                      | CONDITIONS                                                                            | MIN             | TYP  | MAX  | UNITS     |

|------------------------------------------------|---------------------------------------------------------------------------------------|-----------------|------|------|-----------|

| Quiescent Supply Current ( $V_{CC}$ )          | Measured at $V_{CC}$ , FB forced above the regulation point                           |                 |      | 1200 | $\mu A$   |

| Quiescent Supply Current ( $V_{DD}$ )          | Measured at $V_{DD}$ , FB forced above the regulation point                           |                 |      | 5    | $\mu A$   |

| Quiescent Battery Supply Current ( $V_+$ )     |                                                                                       |                 |      | 40   | $\mu A$   |

| Shutdown Supply Current ( $V_{CC}$ )           | $SKP/\bar{SDN} = 0$                                                                   |                 |      | 5    | $\mu A$   |

| Shutdown Supply Current ( $V_{DD}$ )           | $SKP/\bar{SDN} = 0$                                                                   |                 |      | 5    | $\mu A$   |

| Shutdown Battery Supply Current ( $V_+$ )      | $SKP/\bar{SDN} = 0$ , $V_{CC} = V_{DD} = 0$ or $5V$                                   |                 |      | 5    | $\mu A$   |

| Reference Voltage                              | $V_{CC} = 4.5V$ to $5.5V$ , no REF load                                               | 1.98            | 2.02 |      | V         |

| Overtoltage Trip Threshold                     | Measured at FB                                                                        | 2.20            | 2.30 |      | V         |

| Output Undervoltage Protection Threshold       | With respect to unloaded output voltage                                               | 65              | 75   |      | %         |

| Current-Limit Threshold (Positive, Default)    | GND - LX, ILIM = $V_{CC}$                                                             | 80              | 115  |      | mV        |

| Current-Limit Threshold (Positive, Adjustable) | GND - LX                                                                              | ILIM = 0.5V     | 33   | 65   | mV        |

|                                                |                                                                                       | ILIM = REF (2V) | 160  | 240  |           |

| Current-Limit Threshold (Negative)             | LX - GND, ILIM = $V_{CC}$                                                             | -140            | -80  |      | mV        |

| $V_{CC}$ Undervoltage Lockout Threshold        | Rising edge, hysteresis = 20mV, PWM disabled below this level                         | 4.1             | 4.4  |      | V         |

| DH Gate Driver On-Resistance                   | BST - LX forced to $5V$                                                               |                 |      | 3.5  | $\Omega$  |

| DL Gate Driver On-Resistance                   | DL, high state (pullup)                                                               |                 |      | 3.5  | $\Omega$  |

|                                                | DL, low state (pulldown)                                                              |                 |      | 1.0  | $\Omega$  |

| Logic Input High Voltage                       | D0-D4, A/ $\bar{B}$                                                                   | 2.4             |      |      | V         |

| Logic Input Low Voltage                        | D0-D4, A/ $\bar{B}$                                                                   |                 |      | 0.8  | V         |

| DAC B-Mode Programming Resistor, Low           | D0-D4, 0 to 0.4V or 2.6V to 5.5V applied through resistor, A/ $\bar{B}$ = GND         |                 |      | 1    | $k\Omega$ |

| DAC B-Mode Programming Resistor, High          | D0-D4, 0 to 0.4V or 2.6V to 5.5V applied through resistor, A/ $\bar{B}$ = GND         | 100             |      |      | $k\Omega$ |

| VGATE Lower Trip Threshold                     | Measured at FB with respect to unloaded output voltage, falling edge, hysteresis = 1% | -8.4            | -4.6 |      | %         |

| VGATE Upper Trip Threshold                     | Measured at FB with respect to unloaded output voltage, rising edge, hysteresis = 1%  | +10             | +15  |      | %         |

**Note 1:** Output voltage accuracy specifications apply to DAC voltages from 0.925V to 2V. Includes load-regulation error.

**Note 2:** On-Time specifications are measured from 50% to 50% at the DH pin, with LX forced to 0, BST forced to  $5V$ , and a  $500pF$  capacitor from DH to LX to simulate external MOSFET gate capacitance. Actual in-circuit times may be different due to MOSFET switching speeds.

**Note 3:** Specifications to  $-40^\circ C$  are guaranteed by design and not production tested.

# ノートブックCPU用 ダイナミック可変、同期ステップダウンコントローラ

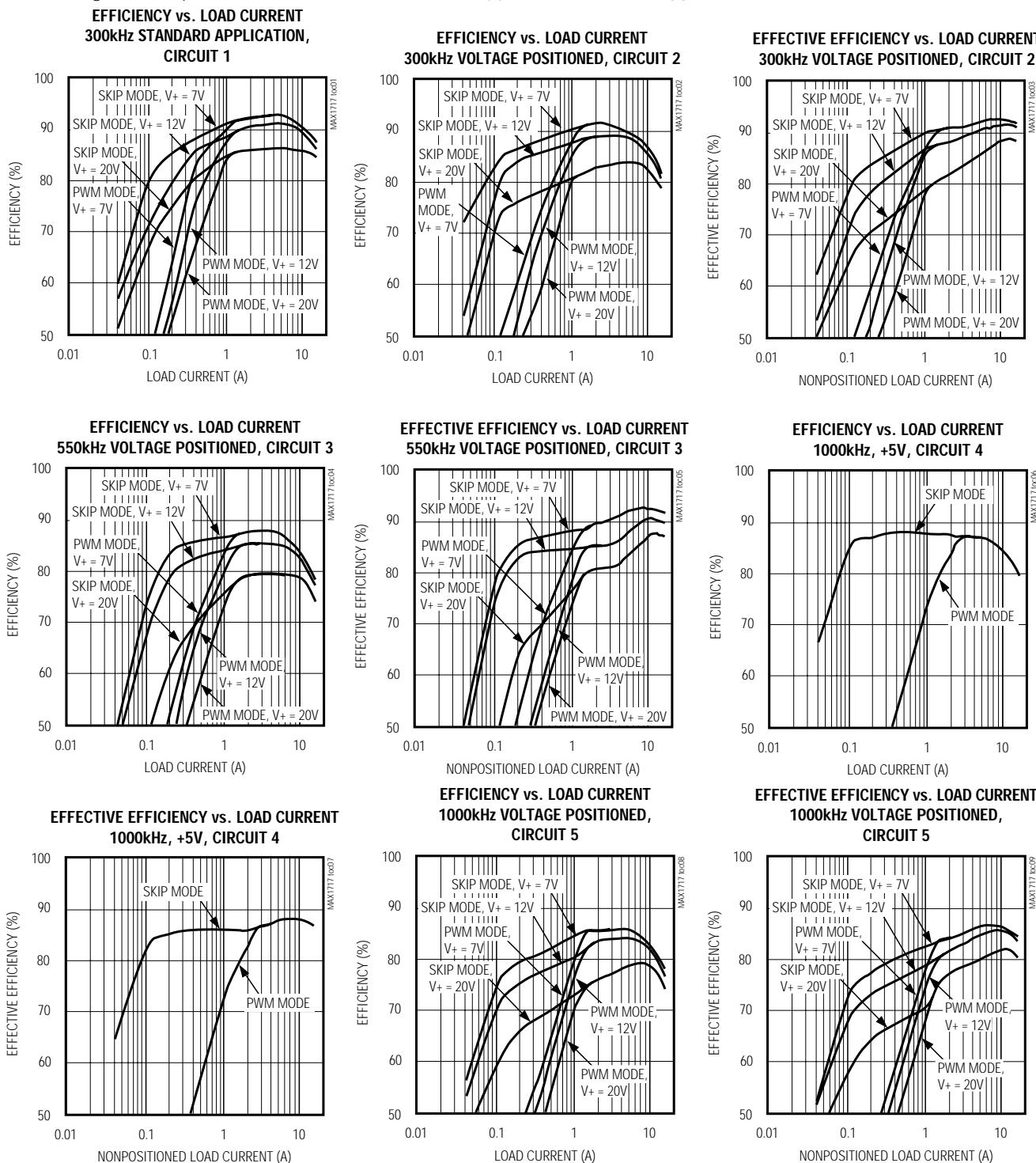

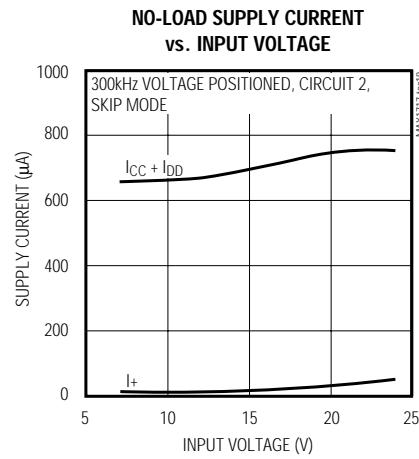

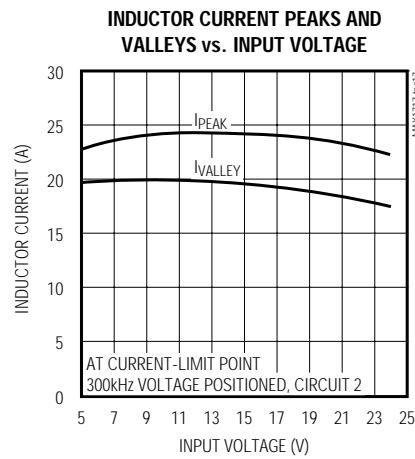

## 標準動作特性

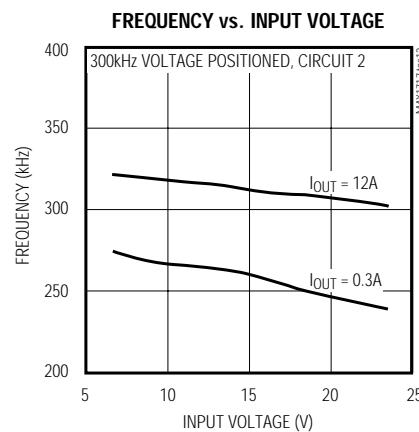

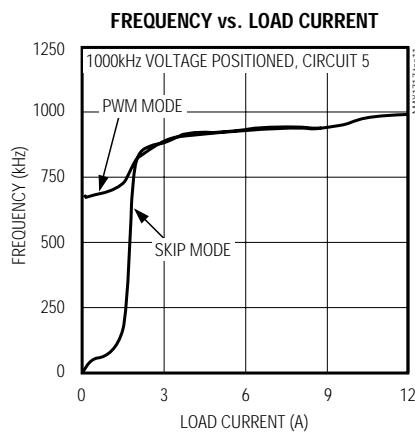

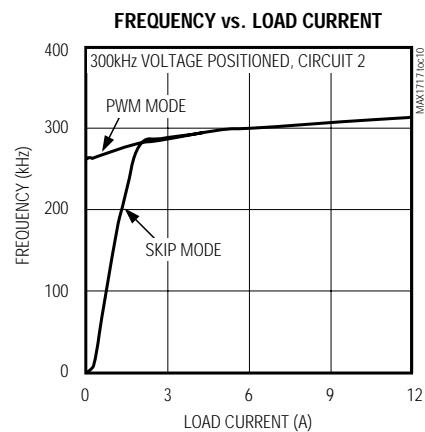

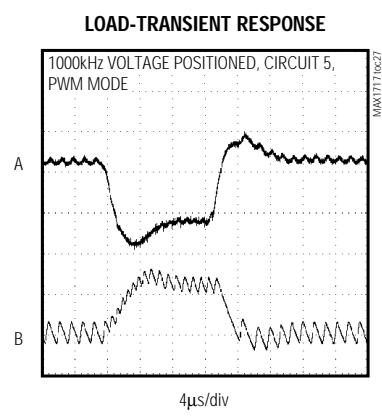

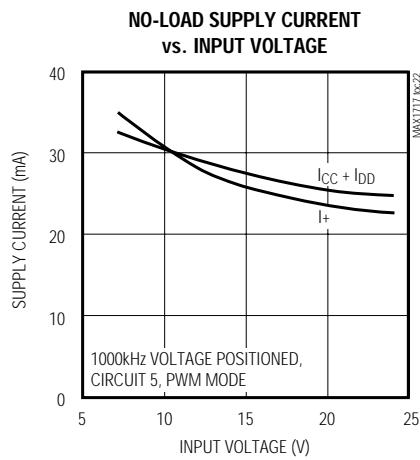

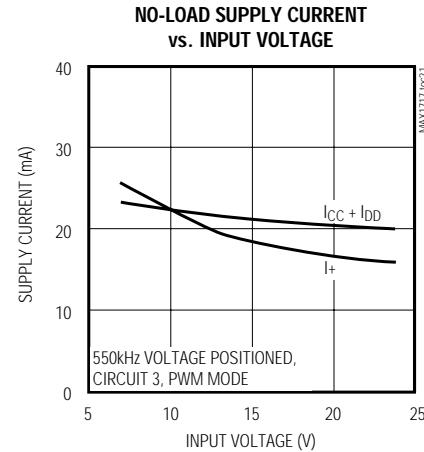

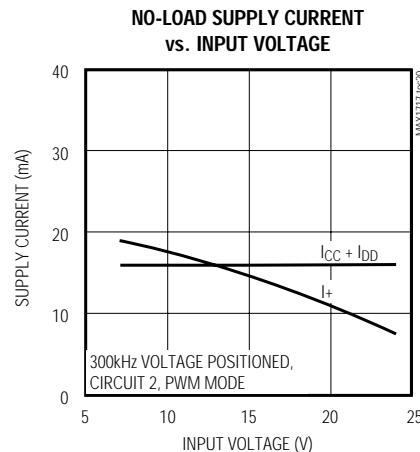

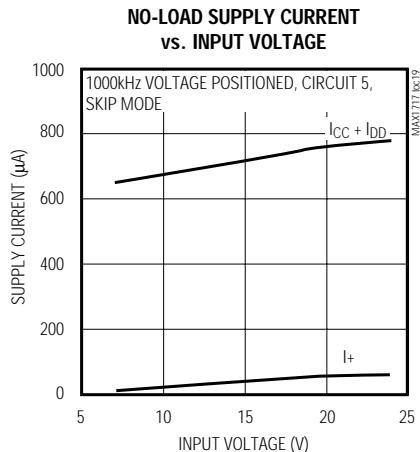

(Circuit of Figure 1, components of Table 1,  $V_+ = +12V$ ,  $V_{DD} = V_{CC} = SKP/SDN = +5V$ ,  $V_{OUT} = 1.6V$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

# ノートブックCPU用 ダイナミック可変、同期ステップダウンコントローラ

MAX1717

## 標準動作特性(続き)

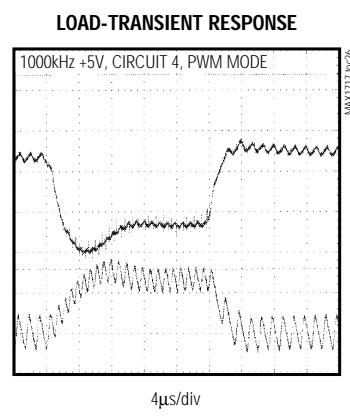

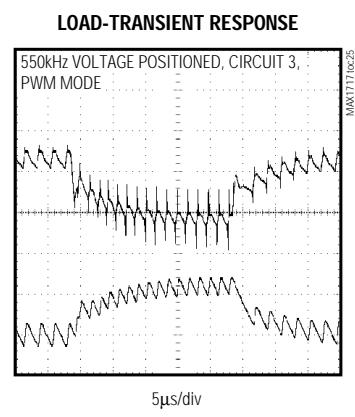

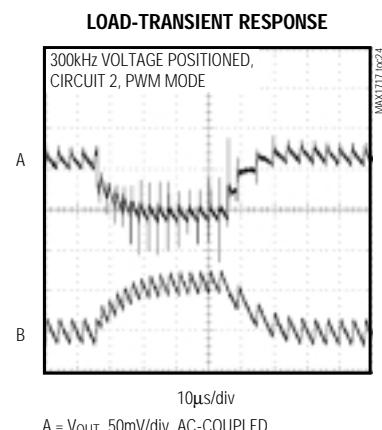

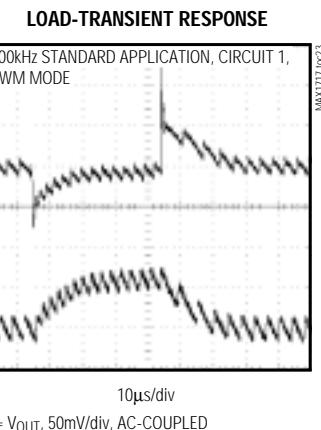

(Circuit of Figure 1, components of Table 1,  $V_+ = +12V$ ,  $V_{DD} = V_{CC} = \text{SKP/SDN} = +5V$ ,  $V_{OUT} = 1.6V$ ,  $T_A = +25^\circ\text{C}$ , unless otherwise noted.)

# ノートブックCPU用 ダイナミック可変、同期ステップダウンコントローラ

## 標準動作特性(続き)

(Circuit of Figure 1, components of Table 1,  $V_+ = +12V$ ,  $V_{DD} = V_{CC} = \text{SKP/SDN} = +5V$ ,  $V_{OUT} = 1.6V$ ,  $T_A = +25^\circ\text{C}$ , unless otherwise noted.)

# ノートブックCPU用 ダイナミック可変、同期ステップダウンコントローラ

## 標準動作特性(続き)

(Circuit of Figure 1, components of Table 1,  $V_+ = +12V$ ,  $V_{DD} = V_{CC} = SKP/SDN = +5V$ ,  $V_{OUT} = 1.6V$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

MAX1717

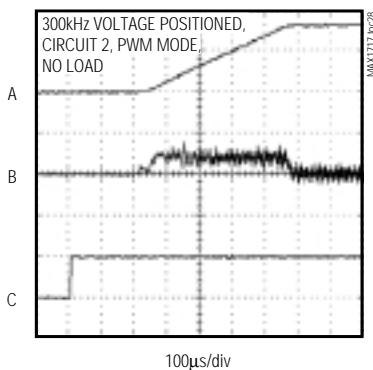

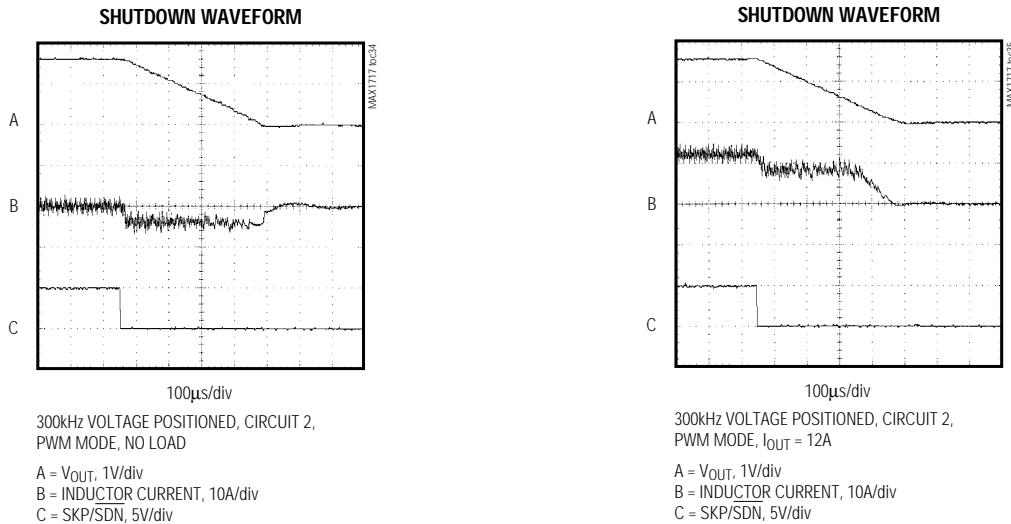

### STARTUP WAVEFORM

A =  $V_{OUT}$ , 1V/div

B = INDUCTOR CURRENT, 10A/div

C =  $SKP/SDN$ , 5V/div

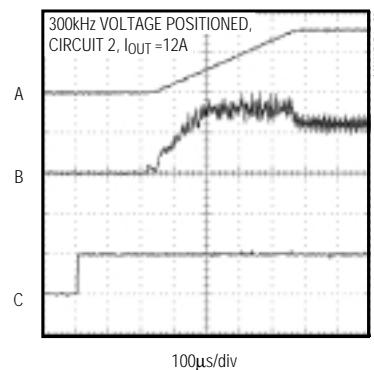

### STARTUP WAVEFORM

A =  $V_{OUT}$ , 1V/div

B = INDUCTOR CURRENT, 10A/div

C =  $SKP/SDN$ , 5V/div

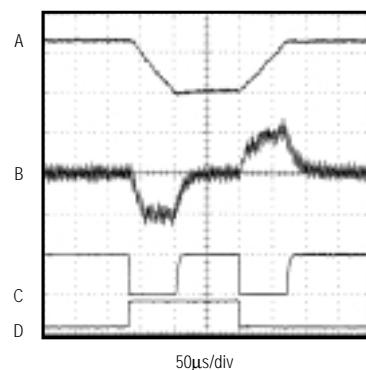

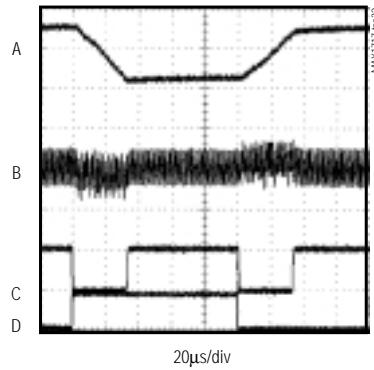

### DYNAMIC OUTPUT VOLTAGE TRANSITION

300kHz STANDARD APPLICATION, CIRCUIT 1,

PWM MODE,  $V_{OUT} = 1.35V$  TO 1.6V,  $I_{OUT} = 0.3A$ ,

$R_{TIME} = 120k\Omega$

A =  $V_{OUT}$ , 200mV/div, AC-COUPLED

B = INDUCTOR CURRENT, 10A/div

C = VGATE, 5V/div

D = A/B, 5V/div

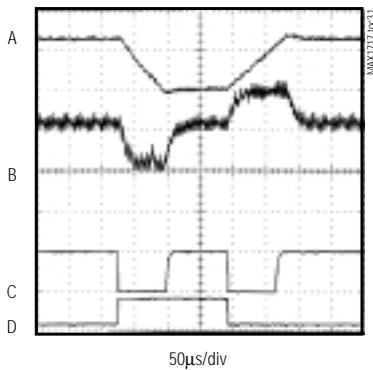

### DYNAMIC OUTPUT VOLTAGE TRANSITION

300kHz STANDARD APPLICATION, CIRCUIT 1,

PWM MODE,  $V_{OUT} = 1.35V$  TO 1.6V,

$I_{OUT} = 12A$ ,  $R_{TIME} = 120k\Omega$

A =  $V_{OUT}$ , 200mV/div, AC-COUPLED

B = INDUCTOR CURRENT, 10A/div

C = VGATE, 5V/div

D = A/B, 5V/div

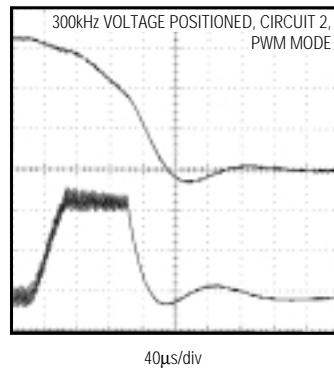

### DYNAMIC OUTPUT VOLTAGE TRANSITION

1000kHz +5V, CIRCUIT 4,

PWM MODE,  $V_{OUT} = 1.35V$  TO 1.6V,

$I_{OUT} = 0.3A$ ,  $R_{TIME} = 51k\Omega$

### OUTPUT OVERLOAD WAVEFORM

A =  $V_{OUT}$ , 500mV/div

B = INDUCTOR CURRENT, 10A/div

# ノートブックCPU用 ダイナミック可変、同期ステップダウンコントローラ

## 標準動作特性(続き)

(Circuit of Figure 1, components of Table 1,  $V_+ = +12V$ ,  $V_{DD} = V_{CC} = SKP/\overline{SDN} = +5V$ ,  $V_{OUT} = 1.6V$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

## 端子説明

| 端子 | 名称                   | 機能                                                                                                                                                                                                                                                                                                                                                                                     |

|----|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | $V_+$                | バッテリ電圧検出接続。 $V_+$ は入力電源に接続して下さい。 $V_+$ は、PWM単安定マルチバイブレータのタイミング専用です。DHオンタイムは、2V ~ 28Vの範囲で $V_+$ 入力電圧に反比例します。                                                                                                                                                                                                                                                                            |

| 2  | $SKP/\overline{SDN}$ | シャットダウン及びスキップモードの組合せ制御。シャットダウンする場合は、 $SKP/\overline{SDN}$ をGNDに駆動します。低ノイズ強制PWMモードの時は $SKP/\overline{SDN}$ をオープンにしておき、通常のパルススキップ動作では $V_{CC}$ に接続します。低ノイズ強制PWMモードは、軽負荷時にインダクタ電流を再循環させ、パルススキップ動作を抑制します。 $SKP/\overline{SDN}$ を使用して、過電圧及び低電圧保護回路の両方をディセーブルし、フォルトラッシュを12V < $SKP/\overline{SDN}$ < 15V(その他の場合は通常のPFM/PWM動作)に強制することによってクリアすることもできます。 $SKP/\overline{SDN}$ を15V以上に接続しないで下さい。 |

| 3  | TIME                 | スルーレート調整端子。TIMEからの抵抗をGNDに接続して内部スルーレートロックを設定して下さい。 $470k \sim 47k$ の抵抗は、クロックを38kHz ~ 380kHz, $f_{SLEW} = 150kHz \cdot 120k / R_{TIME}$ に設定します。                                                                                                                                                                                                                                          |

| 4  | FB                   | 高速フィードバック入力。非電圧ポジショニング回路の場合は、FBを外部インダクタ及び出力コンデンサのジャンクションに接続します(図1)。電圧ポジショニング回路の場合は、FBを外部インダクタ及びポジショニング抵抗のジャンクションに接続します(図3)。                                                                                                                                                                                                                                                            |

| 5  | FBS                  | フィードバックリモート検出入力。非電圧ポジショニング回路の場合は、FBSを負荷側で直接 $V_{OUT}$ に接続します。FBSは、DC出力電圧の微調整用積分器に内部接続されています。電圧ポジショニング回路の場合は、FBSをICの近くでFBに直接接続し、FBSリモート検出積分器アンプをディセーブルします。3つ全部の積分器アンプをディセーブルするには、FBSを $V_{CC}$ に接続します。                                                                                                                                                                                  |

| 6  | CC                   | 積分器コンデンサ接続。積分時定数を設定するには、100pF ~ 1000pF(470pF typ)のコンデンサをCCからGNDに接続します。FBSが $V_{CC}$ に接続されている場合、CCは無接続にしておくことができます。                                                                                                                                                                                                                                                                     |

| 7  | $V_{CC}$             | PWMコアのアナログ電源電圧入力。2.0 の直列抵抗を通じて $V_{CC}$ をシステム電源電圧(4.5V ~ 5.5V)に接続します。0.22µF(min)コンデンサでGNDにバイパスして下さい。                                                                                                                                                                                                                                                                                   |

# ノートブックCPU用 ダイナミック可変、同期ステップダウンコントローラ

## 端子説明(続き)

| 端子    | 名称              | 機能                                                                                                                                                                                                                                    |

|-------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8     | TON             | オンタイム選択制御入力。これは、DHオンタイムを求めるためにKファクタ(表3)を設定する4レベル入力です。各動作に応じて次の端子に接続して下さい。<br>GND = 1000kHz<br>REF = 550kHz<br>Open = 300kHz<br>V <sub>CC</sub> = 200kHz                                                                               |

| 9     | REF             | 2.0Vリファレンス出力。0.22μF(min)コンデンサでGNDにバイパスして下さい。REFは外部負荷に対して50μAを供給できます。REFに負荷を加えると、REF負荷レギュレーション誤差によりRF精度が劣化します。                                                                                                                         |

| 10    | ILIM            | 電流リミット調整。ILIMをV <sub>CC</sub> に接続した場合、GND - LX電流リミットスレッショルドがデフォルト値の+100mVになります。可変モードでは、電流リミットスレッショルド電圧は、0.5V ~ 3.0V範囲におけるILIMの電圧の1/10です。100mVのデフォルト値への切換えのロジックスレッショルドは、約V <sub>CC</sub> - 1Vです。200mVの固定スレッショルドを得るには、ILIMをREFに接続して下さい。 |

| 11    | GNDS            | グランドリモート検出入力。非電圧ポジショニング回路の場合は、GNDSを負荷側で直接グランドに接続します。GNDSは出力電圧を微調整する積分器に内部接続されています。出力電圧はGNDS - GNDの分だけ増加します。電圧ポジショニング回路の場合は、抵抗分圧器を使用してREFからGNDにGNDSをバイアスすることにより、出力電圧(24mV typ)を増加させます。                                                 |

| 12    | VGATE           | オープンドレインパワーゲット出力。出力が安定しているときは通常ハイになっています。VGATEは、DACコードが変化するたびにローになり、スルーレートコントローラが動作を完了し、出力が安定してから1クロック期間後にハイに戻ります。シャットダウン中はローになります。                                                                                                   |

| 13    | GND             | アナログ及び電力グランド。電流リミットコンパレータにも接続します。                                                                                                                                                                                                     |

| 14    | DL              | ローサイドゲートドライバ出力。スイングはGND ~ V <sub>DD</sub> 。                                                                                                                                                                                           |

| 15    | V <sub>DD</sub> | DLゲートドライバ用電源電圧入力。4.5V ~ 5.5V。0.1 μFコンデンサでGNDにバイパスして下さい。                                                                                                                                                                               |

| 16    | A/̄B            | 内部MUX選択入力。A/̄Bがハイの時、DACコードはD0 ~ D4のロジックレベル電圧により決定されます。A/̄Bの立下りエッジ(又はA/̄Bローでのパワーアップ中)では、DACコードはD0 ~ D4の抵抗値により決定されます。                                                                                                                   |

| 17-21 | D4-D0           | DACコード入力。D0は内部5ビットDAC用のLSBで、D4はMSBです(表4参照)。A/̄Bがハイの時、D0 ~ D4はハイ入力インピーダンスロジック入力として機能します。A/̄Bの立下りエッジ(又はA/̄Bローでのパワーアップ中)では、各入力セットの直列抵抗はそのロジック状態を次のように設定します。<br>(直列抵抗 1k ±5%) = ロジックロー<br>(直列抵抗 100k ±5%) = ロジックハイ                        |

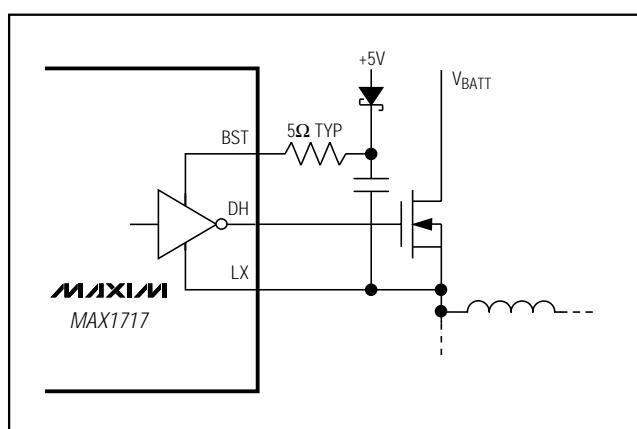

| 22    | BST             | ブーストフライングコンデンサ接続。標準アプリケーション回路の図に示されているように、BSTを外部ブーストダイオードとコンデンサに接続します。BSTと直列接続されたオプションの抵抗を使用すると、DHプルアップ電流を調整できます(図5)。                                                                                                                 |

| 23    | LX              | インダクタ接続。LXは、DHハイサイドゲートドライバの低い方の電源電圧範囲として使用します。又、電流リミットコンパレータ及びスキップモードゼロクロスコンパレータにも接続されています。                                                                                                                                           |

| 24    | DH              | ハイサイドゲートドライバ出力。スイングはLX ~ BSTです。                                                                                                                                                                                                       |

MAX1717

# ノートブックCPU用 ダイナミック可変、同期ステップダウンコントローラ

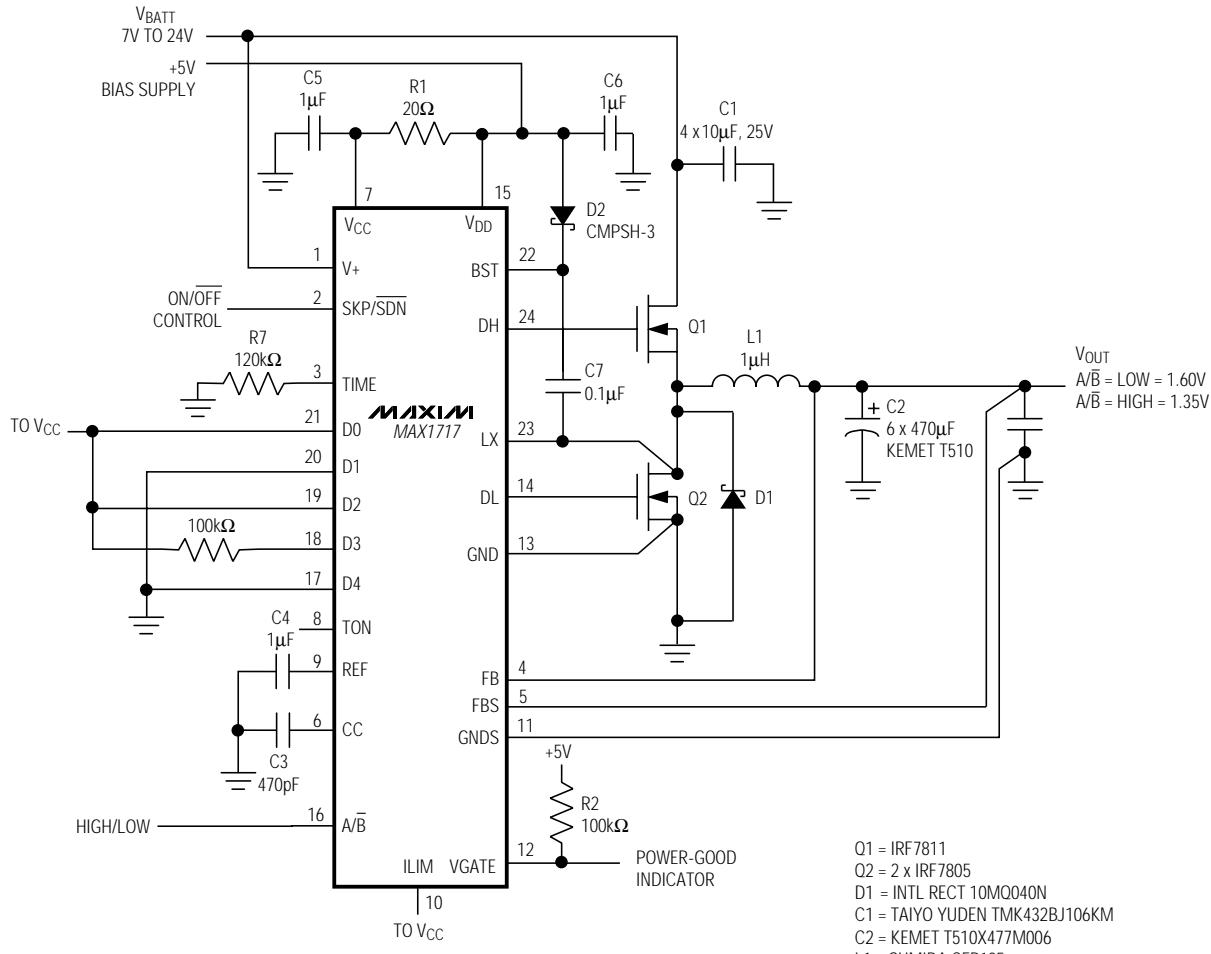

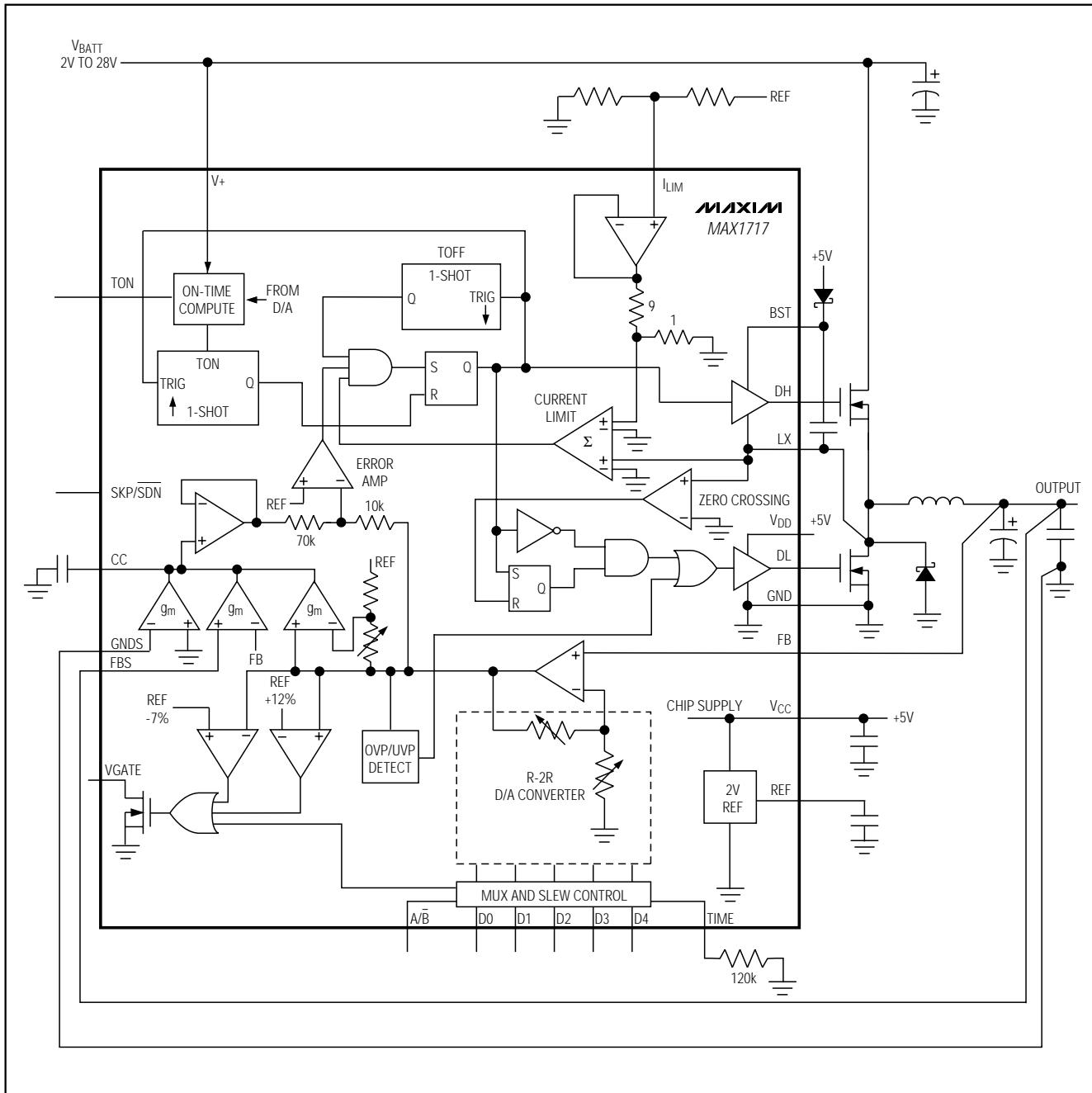

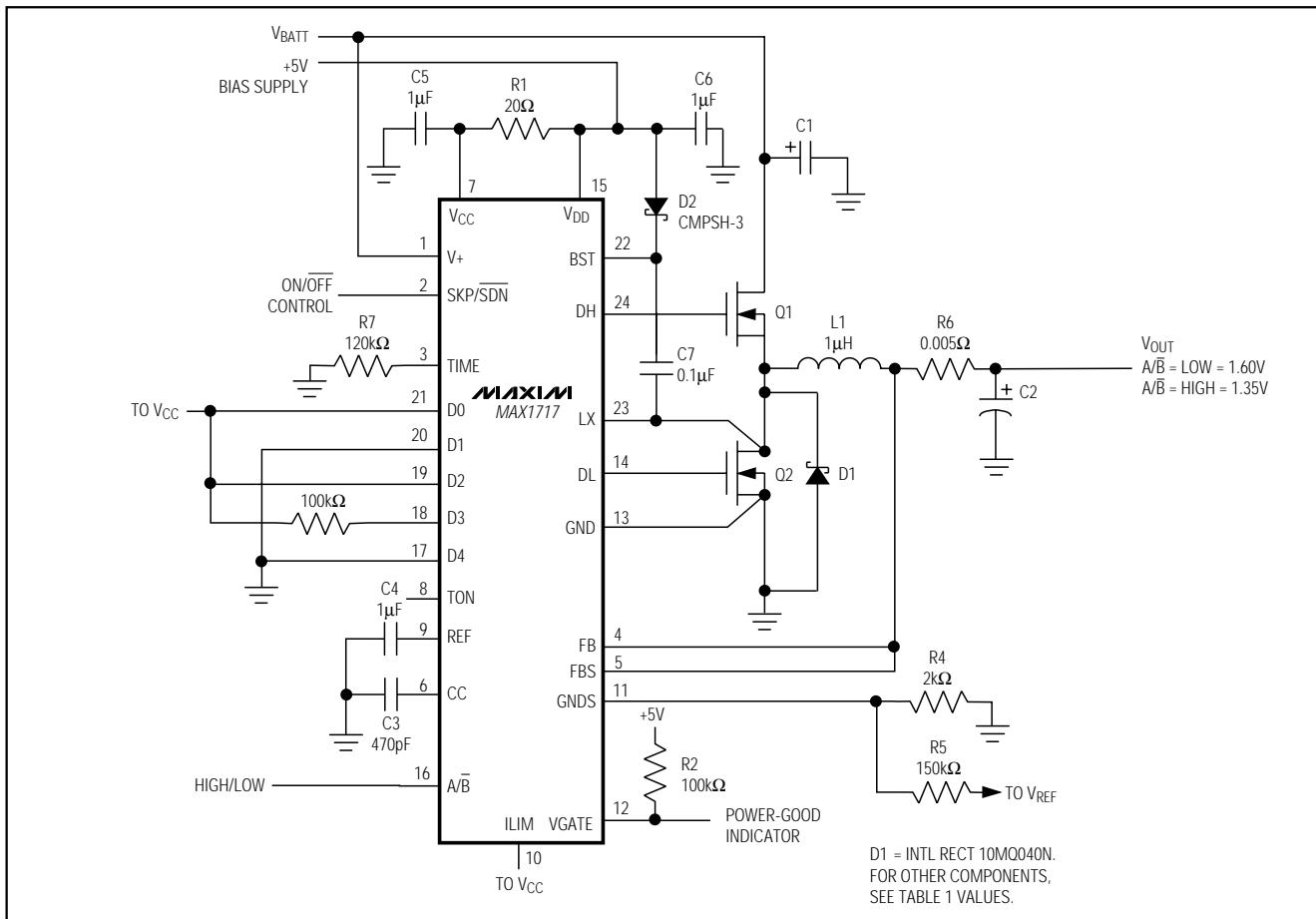

図1. 標準アプリケーション回路

ノートブックCPU用

ダイナミック可変、同期ステップダウンコントローラ

MAX1717

表1. 標準アプリケーションの部品の選択

| COMPONENT                       | 300kHz, STANDARD APPLICATION, CIRCUIT 1                             | 300kHz, VOLTAGE POSITIONED, CIRCUIT 2                                             | 550kHz, VOLTAGE POSITIONED, CIRCUIT 3                                             | 1000kHz, +5V, CIRCUIT 4                                      | 1000kHz, VOLTAGE POSITIONED, CIRCUIT 5                       |

|---------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|

| Figure Number                   | 1                                                                   | 3                                                                                 | 3                                                                                 | 3                                                            | 3                                                            |

| Input Range (VBATT)             | 7V to 24V                                                           | 7V to 24V                                                                         | 7V to 24V                                                                         | 4.5V to 5.5V                                                 | 7V to 24V                                                    |

| Output Current                  | 14A                                                                 | 14A                                                                               | 14A                                                                               | 14A                                                          | 14A                                                          |

| Frequency                       | 300kHz                                                              | 300kHz                                                                            | 550kHz                                                                            | 1000kHz                                                      | 1000kHz                                                      |

| High-Side MOSFET Q1             | International Rectifier IRF7811                                     | International Rectifier IRF7811                                                   | International Rectifier IRF7811                                                   | International Rectifier IRF7811                              | International Rectifier IRF7811                              |

| Low-Side MOSFET Q2              | (2) International Rectifier IRF7805, IRF7811, or IRF7811A           | (2) International Rectifier IRF7805, IRF7811, or IRF7811A                         | (2) International Rectifier IRF7805, IRF7811, or IRF7811A                         | (2) International Rectifier IRF7805, IRF7811, or IRF7811A    | (2) International Rectifier IRF7805, IRF7811, or IRF7811A    |

| Input Capacitor C1              | (4) 10 $\mu$ F, 25V ceramic<br>Taiyo Yuden<br>TMK432BJ106KM         | (4) 10 $\mu$ F, 25V ceramic<br>Taiyo Yuden<br>TMK432BJ106KM                       | (4) 10 $\mu$ F, 25V ceramic<br>Taiyo Yuden<br>TMK432BJ106KM                       | (5) 22 $\mu$ F, 10V ceramic<br>Taiyo Yuden<br>LMK432BJ226KM  | (4) 10 $\mu$ F, 25V ceramic<br>Taiyo Yuden<br>TMK432BJ106KM  |

| Output Capacitor C2             | (6) 470 $\mu$ F, 6.3V tantalum<br>Kemet<br>T510X477M006AS           | (5) 220 $\mu$ F, 2.5V, 25m $\Omega$ specialty polymer<br>Panasonic<br>EEFUE0E221R | (4) 220 $\mu$ F, 2.5V, 25m $\Omega$ specialty polymer<br>Panasonic<br>EEFUE0E221R | (5) 47 $\mu$ F, 6.3V ceramic<br>Taiyo Yuden<br>JMK432BJ476MM | (5) 47 $\mu$ F, 6.3V ceramic<br>Taiyo Yuden<br>JMK432BJ476MM |

| Inductor L1                     | 1 $\mu$ H<br>Sumida<br>CEP125-1R0MC or<br>Panasonic<br>ETQP6F1R1BFA | 1 $\mu$ H<br>Sumida<br>CEP125-1R0MC or<br>Panasonic<br>ETQP6F1R1BFA               | 0.47 $\mu$ H<br>Sumida<br>CEP125-4712-T006                                        | 0.19 $\mu$ H<br>Coilcraft<br>X8357-A                         | 0.3 $\mu$ H<br>Sumida<br>CEP12D38 4713-T001                  |

| Voltage-Positioning Resistor R6 | —                                                                   | 5m $\Omega$ $\pm$ 1%, 1W<br>Dale<br>WSL-2512-R005F                                | 5m $\Omega$ $\pm$ 1%, 1W<br>Dale<br>WSL-2512-R005F                                | 5m $\Omega$ $\pm$ 1%, 1W<br>Dale<br>WSL-2512-R005F           | 5m $\Omega$ $\pm$ 1%, 1W<br>Dale<br>WSL-2512-R005F           |

| Voltage-Positioning Offset      | —                                                                   | 24mV                                                                              | 24mV                                                                              | 24mV                                                         | 24mV                                                         |

| TON Level                       | Float                                                               | Float                                                                             | REF                                                                               | GND                                                          | GND                                                          |

# ノートブックCPU用 ダイナミック可変、同期ステップダウンコントローラ

表2. 部品メーカー

| MANUFACTURER            | USA PHONE    | FACTORY FAX<br>[Country Code] |

|-------------------------|--------------|-------------------------------|

| Coilcraft               | 847-639-6400 | [1] 847-639-1469              |

| Dale-Vishay             | 402-564-3131 | [1] 402-563-6418              |

| International Rectifier | 310-322-3331 | [1] 310-322-3332              |

| Kemet                   | 408-986-0424 | [1] 408-986-1442              |

| Panasonic               | 714-373-7939 | [1] 714-373-7183              |

| Sumida                  | 847-956-0666 | [81] 3-3607-5144              |

| Taiyo Yuden             | 408-573-4150 | [1] 408-573-4159              |

## 詳細

+5Vバイアス電源( $V_{CC}$ 及び $V_{DD}$ )

MAX1717は、バッテリの他にも+5Vの外部バイアス電源を必要とします。通常、この+5Vバイアス電源は、ノートブックコンピュータの95%効率+5Vシステム電源になります。バイアス電源をICの外部に配置すると効率を向上できるだけでなく、PWM回路及びゲートドライバで必要となる+5Vリニアレギュレータのコストを削減することもできます。スタンダードアロン機能が必要な場合は、外部リニアレギュレータで+5V電源を発生させることができます。

+5Vバイアス電源は $V_{CC}$ (PWMコントローラ)及び $V_{DD}$ (ゲート駆動電力)を供給する必要があるため、最大消費電流は次のようになります。

$$I_{BIAS} = I_{CC} + f(Q_{G1} + Q_{G2}) = 10\text{mA to } 40\text{mA (typ)}$$

ここで、 $I_{CC}$ は700 $\mu\text{A}$ (typ)、 $f$ はスイッチング周波数、 $Q_{G1}$ 及び $Q_{G2}$ はMOSFETデータシートの $V_{GS} = 5\text{V}$ における合計ゲートチャージ仕様リミットです。

入力が一定の+4.5V ~ +5.5V電源の場合は、 $V_{+}$ 及び $V_{DD}$ をまとめて接続できます。+5Vバイアス電源をバッテリ電源の前にパワーアップする場合は、起動を補償するバッテリ電圧を得る時点までイネーブル信号(ローからハイ又はオープンの $SKP/\overline{SDN}$ )を遅延させる必要があります。

入力フィードフォワードを備えた

フリーランニング、一定オンタイム

PWMコントローラ

Quick-PWM制御構造は、電圧フィードフォワードを備えた擬似固定周波数の一定オンタイム電流モードタイプです(図2)。この構造は、フィルタコンデンサのESRを電流検出抵抗として利用するため、PWMランプ信号は出力リップル電圧から得ます。制御アルゴリズムは単純です。ハイサイドスイッチのオンタイムは、周期が入力電圧に反比例し、出力電圧に直接的に正比例する単安定マルチバイブレータのみによって決まります。もう1つの単安定マルチバイブレータは、最小オフタイム

(400ns typ)を設定します。オンタイム単安定マルチバイブレータがトリガされるのは、誤差コンパレータがロー、ローサイドスイッチ電流が電流リミットスレッショルド以下で、さらに最小オフタイム単安定マルチバイブレータがタイムアウトになった場合です。

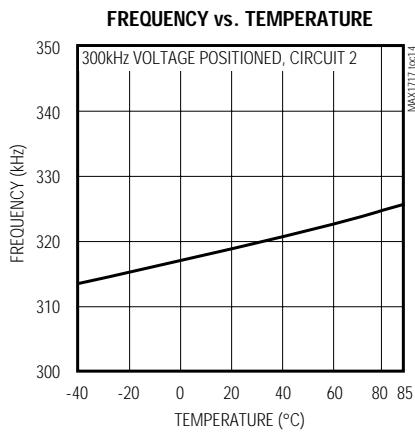

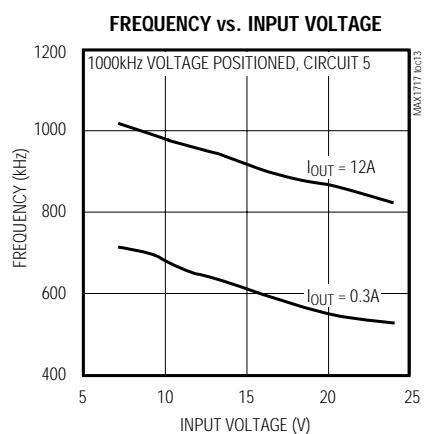

## オンタイム単安定マルチバイブレータ(TON)

PWMコアの心臓部は、ハイサイドスイッチのオンタイムを設定する単安定マルチバイブレータです。この高速、低ジッタ、可変単安定マルチバイブレータには、バッテリ及び出力電圧に応じてオンタイムを変える回路が含まれています。ハイサイドスイッチのオンタイムは、 $V_{+}$ 入力で測定されるバッテリ電圧に反比例し、出力電圧に正比例します。このアルゴリズムは、固定周波数クロックジェネレータが無いにもかかわらず、ほぼ一定のスイッチング周波数を提供します。一定スイッチング周波数の利点は2つありますが、その1つは、周波数を選択することにより、455kHz IF帯域などのノイズに敏感な領域を回避できることです。もう1つは、インダクタリップル電流動作点が比較的一定に保たれるため、設計が容易になるだけでなく、出力電圧リップルを予測できることです。

$$\text{オンタイム} = K (V_{OUT} + 0.075V) / V_{IN}$$

ここで、 $K$ はTONピンストラップ接続で設定される値で、予想されるローサイドMOSFET両端の電圧降下に対応する概算値は0.075Vです(表3)。

オンタイム単安定マルチバイブレータ値は、「電気的特性」の表に示されている動作点において良好な精度を示します(200kHz及び300kHzでは±10%、550kHz及び1000kHzでは±12%)。「電気的特性」の表に示されている条件からかなり離れた動作点におけるオンタイムは、広範囲に渡ります。例えば1000kHzの設定は、入力が+5Vよりもかなり大きい場合に通常10%遅くなります。これは非常に短いオンタイムが要求されるためです。

オンタイムは、非常に大まかにスイッチング周波数に対応します。「電気的特性」の表で保証されているオンタイムは、外部ハイサイドMOSFETのスイッチング遅延の影響を受けます。出力及びグランドにおけるインダクタ、2つのMOSFET、出力コンデンサESR、

表3. Kファクタ誤差の概算

| TON<br>SETTING<br>(kHz) | K<br>FACTOR<br>( $\mu\text{s}$ ) | APPROXIMATE<br>K-FACTOR<br>ERROR (%) | MIN RECOMMENDED<br>VBATT AT $V_{OUT} = 1.6\text{V}$<br>(V) |

|-------------------------|----------------------------------|--------------------------------------|------------------------------------------------------------|

| 200                     | 5                                | ±10                                  | 2.1                                                        |

| 300                     | 3.3                              | ±10                                  | 2.3                                                        |

| 550                     | 1.8                              | ±12.5                                | 3.2                                                        |

| 1000                    | 1.0                              | ±12.5                                | 4.5                                                        |

ノートブックCPU用

ダイナミック可変、同期ステップダウンコントローラ

MAX1717

図2. ファンクションダイアグラム

# ノートブックCPU用 ダイナミック可変、同期ステップダウンコントローラ

及びプリント基板の銅損を含む抵抗損は、大出力電流におけるスイッチング周波数を増加させる傾向にあります。デッドタイム効果は有効オンタイムを増加させ、スイッチング周波数を減少させます。これは、モードがPWMモード( $SKP/\overline{SDN}$  = オープン)であって、インダクタ電流が軽負荷または負の負荷電流において反転する際のダイナミック出力電圧の遷移時に発生します。インダクタ電流が反転すると、インダクタのEMFによって、通常よりも早くLXがハイになり、DH立上りのデッドタイムだけオンタイムが長くなります。

デッドタイム効果が影響を及ぼさない臨界伝導点以上の負荷においては、実際のスイッチング周波数は次のようにになります。

$$f = (V_{OUT} + V_{DROP1}) / t_{ON} (V_{IN} + V_{DROP1} - V_{DROP2})$$

ここで、 $V_{DROP1}$ は、同期整流器、インダクタ、及びプリント基板の抵抗を含めたインダクタ放電経路内の寄生電圧降下の合計値、 $V_{DROP2}$ はハイサイドスイッチ、インダクタ、及びプリント基板の抵抗を含めたインダクタ充電経路内の寄生電圧降下の合計値、 $t_{ON}$ はMAX1717で計算されるオンタイムを示します。

## 積分器アンプ

出力レギュレーション点の微調整を行う3つの積分器アンプが存在します。その1つはGNDSとGNDの間の差を積分し、もう1つはFBSとFBの間の差を積分します。3つ目の積分器アンプは、REFとDAC出力の間の差を積分します。これら3つのトランスコンダクタンスアンプの出力はチップ内で直接合計されるため、積分時定数は1つのコンデンサで容易に設定できます。各アンプの $g_m$ は160 $\mu$ s(typ)です。

この積分器ブロックでは、出力電圧を2%減少または6%増加できます。各アンプでは、DCオフセット及びACリップルを含め、差動入力電圧範囲は合計で少なくとも $\pm 70$ mVです。積分器は有限ゲインにより、合計誤差の約90%を補正します。

FBSアンプは、DC-DCコンバータと負荷の間の出力バス経路に存在するプリント基板トレース及びコネクタのDC電圧降下を補正します。GNDSアンプは、出力グランドバスに対して同様のDC補正処理を行います。3番目の整合器アンプは誤差のあるアンプの小さなオフセットを補正し、 $V_{OUT}$ を出力リップル波形の平均値で強制的に安定化する平均化機能を提供します。

積分器には長所と短所があります。積分器はDCバス抵抗による電圧降下を補正し、ピーク間出力リップルの平均を取ることによってDC出力電圧許容差の限度を強化しますが、最も速い負荷過渡応答を達成する時の支障になります。最も速い負荷過渡応答は、3つ全ての

積分器をディセーブルした時に得ることができます。MAX1717回路をCPUの間近に配置できる場合は、この方法が非常に効果的です。

3つの積分器は、全てFBSを $V_{CC}$ に接続することによりディセーブルできます。整合器がディセーブルされている際は、CCを無接続にしておくことができます。これにより1つの部品が不要となり、GNDSを都合のよいグランドに接続したまま残すことができます。インダクタが連続導電を行っている際、出力電圧のDCレギュレーションはトリップレベルよりもリップルの50%だけ高くなります。断続導電中( $SKP/\overline{SDN}$ オープン、軽負荷)の出力電圧のDCレギュレーションは、スロープの補償によりトリップレベルよりも約1.5%高くなります。

DC-DCコンバータとCPUの間には、大抵コネクタ又は少なくとも何ミリかのプリント基板トレース抵抗が存在します。この場合最良の方法は、大部分のバルクバイパスコンデンサをCPUの近くに配置し、1つのコンデンサだけをコネクタの反対側でMAX1717の近くに配置して、CPUカードのプラグを外した時のリップルを抑制できるようにすることです。これにより、リモート検出ライン(GNDSとFBS)及び積分器が良い結果を生み出します。

MAX1717を電圧ポジショニング回路(図3)で使用する際は、REFからGNDへの抵抗分圧器を使用してGNDSを相殺できます。これにより、GNDS整合器は印可されたオフセット(27mV typ)の90%だけ出力電圧を増加できます。外部インダクタ及び出力コンデンサの間には、低(5m typ)電圧ポジショニング抵抗が直列に接続されます。FBSは、外部インダクタ及び電圧ポジショニング抵抗のジャンクションにおいてFBに直接接続されます。これらの2つの変更により、出力電圧はプログラムされた軽負荷でのDAC電圧よりも若干高くなり、全負荷電流でのDAC電圧よりも若干低くなります。電圧ポジショニングの詳細については、「アプリケーション」の項を参照して下さい。

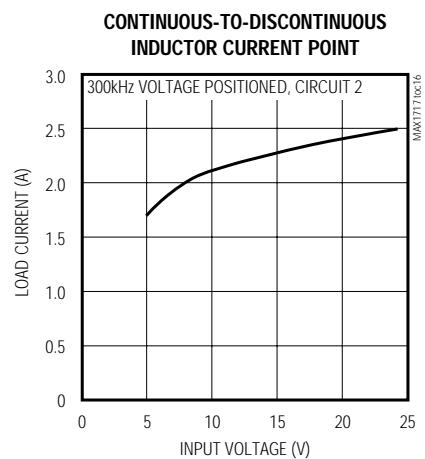

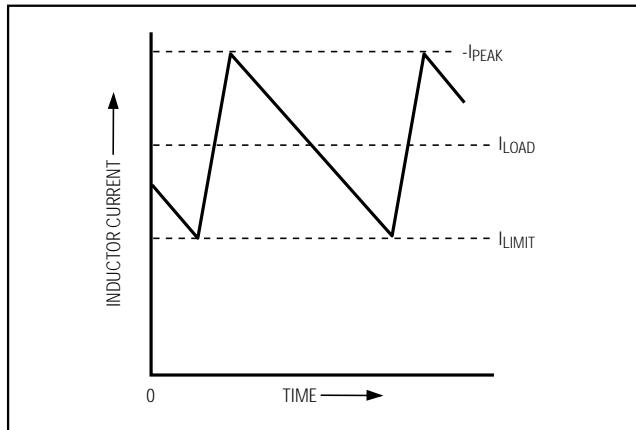

## 自動パルススキップ切換え

スキップモード( $SKP/\overline{SDN}$ ハイ)では、軽負荷で特有のPFMへの自動切換えが発生します(図4)。この切換えは、インダクタ電流のゼロクロスでローサイドスイッチのオンタイムを縮めるコンバレータから影響を受けます。このメカニズムによって、パルススキップPFMと非スキップPFM動作間のスレッショルドが、連続及び断続インダクタ電流動作間の境界と一致します(「標準動作特性」のContinuous-to-Discontinuous Inductor Current Pointのグラフを参照)。7V ~ 24Vのバッテリ範囲におけるこのスレッショルドは、バッテリ電圧に多少依存しますが比較的一定です。

# ノートブックCPU用 ダイナミック可変、同期ステップダウンコントローラ

MAX1717

図3. 電圧ポジショニング回路

$$I_{LOAD(SKIP)} \approx \frac{K \times V_{OUT}}{2 \times L} \times \frac{V_{BATT} - V_{OUT}}{V_{BATT}}$$

ここで、Kはオンタイムスケールファクタを示します(表3)。PFM/PWMクロスオーバーが発生する負荷電流レベル( $I_{LOAD(SKIP)}$ )は、インダクタ値の関数であるピーク間リップル電流の1/2に等しくなります(図4)。例えば、標準のアプリケーション回路では、これは次のようになります。

$$\frac{3.3\mu\text{s} \times 1.6\text{V}}{2 \times 1\mu\text{H}} \times \frac{12\text{V} - 1.6\text{V}}{12\text{V}} = 2.3\text{A}$$

スイング(ソフト飽和)インダクタを使用した場合は、クロスオーバー点がより低い値で発生します。

軽負荷によってパルススキップ動作が発生すると、スイッチング波形はノイズが多く非同期のように見えることもあります。これは軽負荷効率が高くなる正常な動作です。PFMノイズと軽負荷効率間の妥協点は、インダクタ値を変えることによって調整できます。一般に、インダクタ値が低いと効率対負荷曲線がより広くなり、インダクタ値が高いと全負荷効率が高くなり(コイル抵抗が一定の場合)、出力電圧リップルが小さくなります。但し、インダクタ値を高くすると物理的なサイズが増し、(特に低入力電圧レベルにおいて)負荷過渡応答が劣化します。

# ノートブックCPU用 ダイナミック可変、同期ステップダウンコントローラ

図4. パルススキップ/断続クロスオーバ点

## 強制PWMモード(SKP/SDNオープン)

低ノイズ、強制PWMモード(SKP/SDNオープン)においては、ローサイドスイッチのオンタイムを制御するゼロクロスコンパレータがディセーブルされます。これによって、ローサイドゲート駆動波形がハイサイドゲート駆動波形と相補的になります。この結果、PWMループがデューティ比率を $V_{OUT}/V_{IN}$ に維持しようとするため、インダクタ電流は軽負荷で逆転します。強制PWMモードの利点は、スイッチング周波数をほぼ一定に保つことです、この場合外部MOSFET及びスイッチング周波数に応じて無負荷時のバッテリ電流が10mA ~ 40mAになる可能性があります。

強制PWMモードが最も有効となるのは、オーディオ周波数ノイズを低減する場合、及びフライバックトランス又は結合インダクタを使用した複数出力アプリケーションのクロスレギュレーションを向上する場合です。

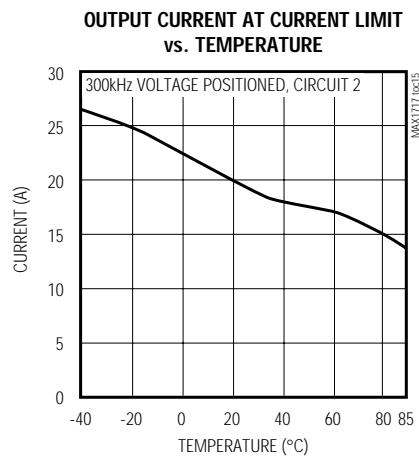

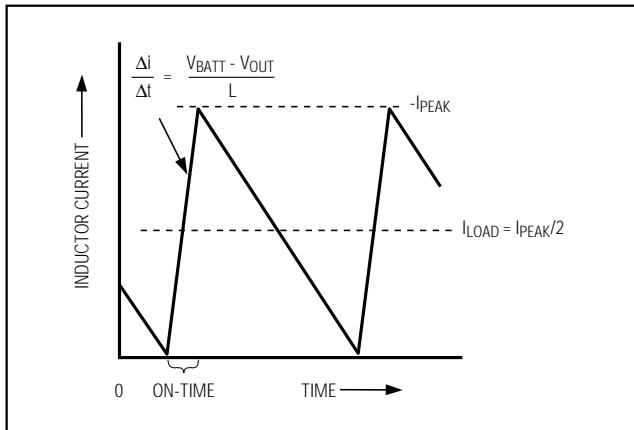

## 電流リミット回路

電流リミット回路は、ローサイドMOSFETのオン抵抗を電流検出素子として使用するユニークな「谷間」電流検出アルゴリズムを採用しています。電流検出信号が電流リミットスレッショルドよりも大きい時、PWMは新しいサイクルを開始できません(図5)。実際のピーク電流は、電流リミットスレッショルドよりもインダクタリップル電流の量だけ大きくなります。従って、正確な電流リミット特性及び最大負荷性能は、MOSFETオン抵抗、インダクタ値、及びバッテリ電圧の関数になります。この不確実性という対価を支払うことにより、損失のない確実な過電流検出を達成できます。低電圧保護回路と組み合わせると、この電流リミット技法は殆どの状況で効果的となります。

又、 $V_{OUT}$ が電流のシンクとなっている時に、過剰な逆インダクタ電流を防止する負の電流リミットも存在します。負の電流リミットスレッショルドは、正の電流

図5. 「谷間」電流リミットスレッショルド点

リミットの約120%に設定されるため、ILIMの調整時に正の電流リミットに追随します。

電流リミットスレッショルドは、ILIMの外付抵抗分圧器で調整できます。電流リミットスレッショルドの調整範囲は50mV ~ 300mVです。可変モードでは、電流リミットスレッショルド電圧は、ILIMの電圧のちょうど1/10です。ILIMを $V_{CC}$ に接続した時のデフォルトスレッショルドは100mVです。この100mVデフォルト値への切換え用ロジックスレッショルドは、約 $V_{CC}$ -1Vです。

可変電流リミットは、幅広い範囲のオン抵抗特性を持つMOSFETへの対応を可能にします(「設計手順」参照)。

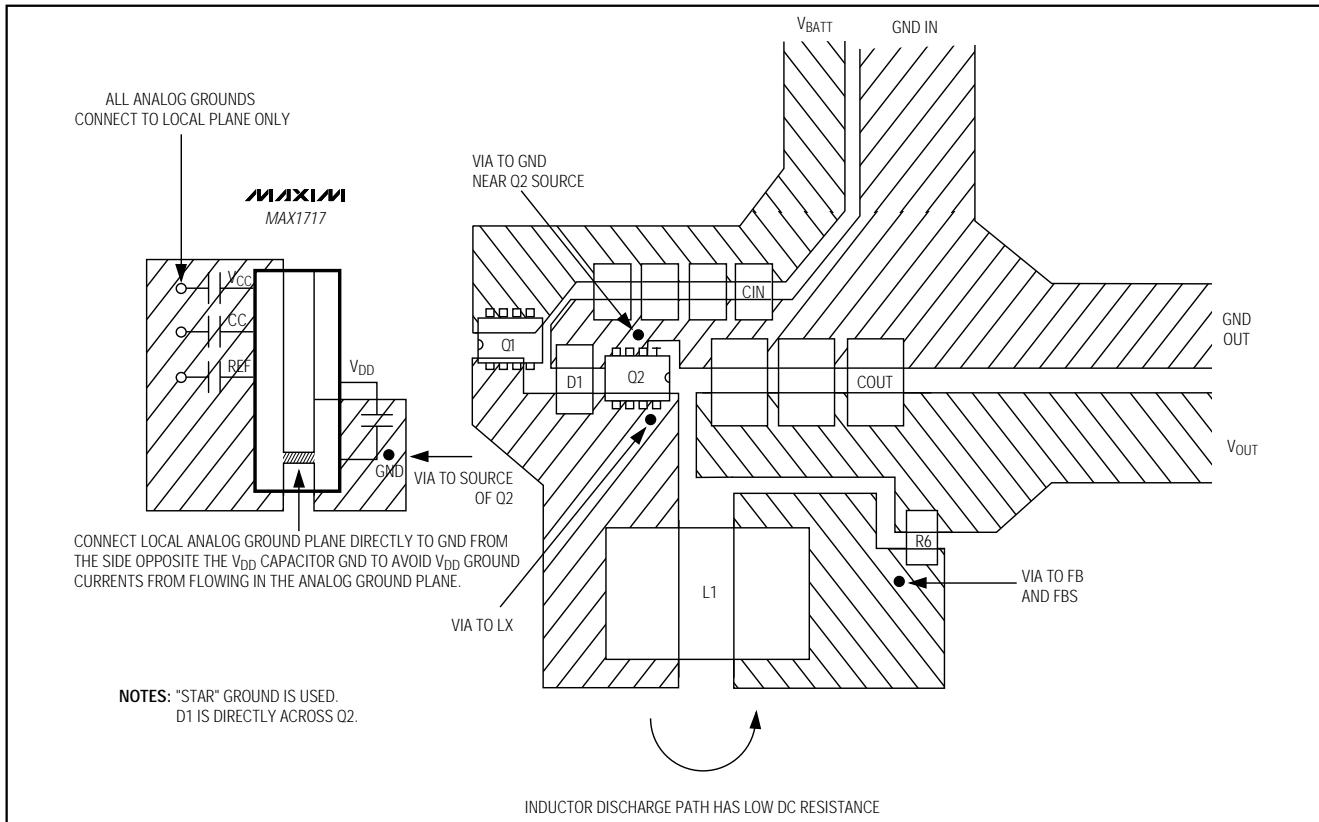

プリント基板レイアウトのガイドラインを厳守し、LX及びGNDから見た電流検出信号が、ノイズ及びDC誤差によって影響を受けないようにして下さい。このICはローサイドMOSFETの近くに取り付け、ソース端子及びドレイン端子へのケルビン検出接続を短くダイレクトなトレースで行う必要があります。

## MOSFETゲートドライバ(DH、DL)

DH及びDLドライバは、中間サイズのハイサイド及びより大きなローサイドパワーMOSFETの駆動用として最適化されています。これは、 $V_{BATT} - V_{OUT}$ の差が大きいノートブックCPU環境に見られる低デューティ係数に適応します。適応型デッドタイム回路はDL出力を監視し、DLが完全にオフになる前にハイサイドFETがオンになるのを防ぎます。この適応型デッドタイム回路を正しく動作させるには、DLドライバからMOSFETゲートへの低抵抗、低インダクタンス経路が必要です。さもないと、MAX1717内の検出回路は、MOSFETゲートに現実にはまだ電荷が残っていても、MOSFETゲートはオフであるものと解釈します。経路には、10 ~ 20平方(MOSFETがMAX1717から2.5cm離れている場合は50 ~ 100mils)の非常に短く太いトレースを使用して下さい。

# ノートブックCPU用 ダイナミック可変、同期ステップダウンコントローラ

MAX1717

反対側のデッドタイム(DHターンオフ)は、固定の35ns(typ)内部遅延によって決まります。DLをローに駆動する内部プルダウントランジスタは、0.5 (typ)のオン抵抗を持つ強力なものです。これは、ローサイド同期整流器MOSFETのドレインからゲートへの容量カップリングによって、インダクタノードの高速立ち上り時間中にDLがプルアップされるのを防ぎます。但し、大電流アプリケーションにおいて、ハイサイドFET及びローサイドFETの組合せによっては、過大なゲートドレインカップリングが起こり、これが原因で効率の低下及びEMIの発生を伴う貫通電流が発生する可能性もあります。この問題は、多くの場合BSTと直列に抵抗を追加することで解決できます。これにより、ターンオフ時間に影響を及ぼすことなくハイサイドFETのターンオン時間を増大できます(図6)。

## POR

$V_{CC}$ が約2Vを越えて上昇するとパワーオンリセット(POR)が発生し、フォルトラッチがリセットされ、PWMが動作可能になります。 $V_{CC}$ 低電圧ロックアウト(UVLO)回路はスイッチングを抑制し、VGATEを強制的にローにし、DLゲートドライバを強制的にハイにします(出力過電圧保護を行うため)。 $V_{CC}$ が4.2V以上になると、DAC入力がサンプリングされ、出力電圧がDAC設定に近づくよう調整されます。

自動起動では、バッテリ電圧が $V_{CC}$ の前に存在する必要があります。バッテリ電圧が存在しないままMAX1717が出力を安定化させようとすると、フォルトラッチがトリップします。SKP/SDNピンは、フォルトラッチをリセットするために切り換えることができます。

## シャットダウン

SKP/SDNがローになると、MAX1717は低電力シャットダウンモードに切り替わります。VGATEは直ちにローになります。出力電圧は、 $R_{TIME}$ で設定されているクロック

速度により20mVステップで0まで低下します。DACが0Vの設定に達するとDLがハイになり、DHがローになり、リファレンスがオフになります。消費電流が約2 $\mu$ Aまで降下します。

SKP/SDNがハイになるかフロートすると、リファレンスがパワーアップし、リファレンスUVLOの通過後に、DACターゲットが評価され、スイッチングが始まります。スルーレートコントローラは25mVステップでゼロから現在選択されているコード値まで(A/Bに基づく)上昇します。従来のソフトスタート(可変電流リミット)回路は存在しないため、全出力電流が直ちに利用可能になります。スルーレートコントローラが停止し、出力電圧が安定すると、VGATEはハイになります。VGATEがハイになると、直ちにフルパワーが利用可能になります。

## UVLO

UVLOコンパレータをトリップする程度まで $V_{CC}$ 電圧がローに降下すると、有効な決断を行うための十分な消費電圧がないものと見なされます。過電圧フォルトから出力を保護するために、このモードではDLが強制的にハイになります。これにより出力が強制的にGNDに送られますが、スルーレートコントローラは使用されません。この結果、大きな負のインダクタ電流が発生し、小さな負の出力電圧が発生することもあります。 $V_{CC}$ がこのようにして降下する可能性がある場合は、GNDへの出力をショットキダイオードでクランプし、負の流れを減少させることができます。

## DAC入力D0 ~ D4

デジタルアナログコンバータ(DAC)は出力電圧をプログラミます。このDACは、CPUモジュールのピンから設定済みのデジタルコードを受け取ります。CPUピンはGNDに接続されているか、無接続になっています。これらをデジタルロジック、汎用I/O、又は外部マルチプレクサによって駆動することもできます。D0 ~ D4はフロートさせたままにしないで下さい。入力がフロートする可能性がある場合は、1M 以下のプルアップを使用して下さい。SMPSがアクティブの時は、D0 ~ D4を変化させて新しい出力電圧レベルへの遷移を開始できます。このモードのDAC制御を使用する場合は、A/Bハイを接続して下さい。D0 ~ D4は一緒に変化させて、ビット間に1 $\mu$ sより大きいスキューが発生しないようにします。さもないと、誤ったDAC測定値により誤った電圧レベルへの部分的遷移が発生し、その後正しい電圧レベルへの意図した遷移が行われるため、全体の遷移時間が長くなります。使用可能なDACコード及び結果の出力電圧(表4)は、IntelのモバイルPentium®IIIの仕様とコンパチブルです。

図6. スイッチングノードの立上り時間の削減

PentiumはIntel Corp.の登録商標です。

# ノートブックCPU用 ダイナミック可変、同期ステップダウンコントローラ

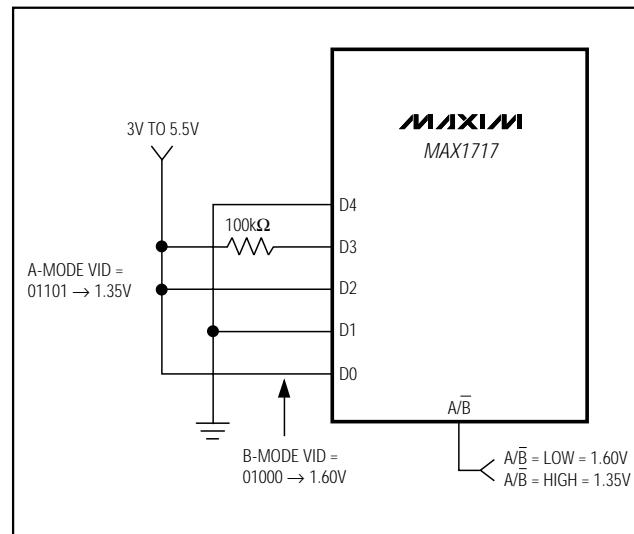

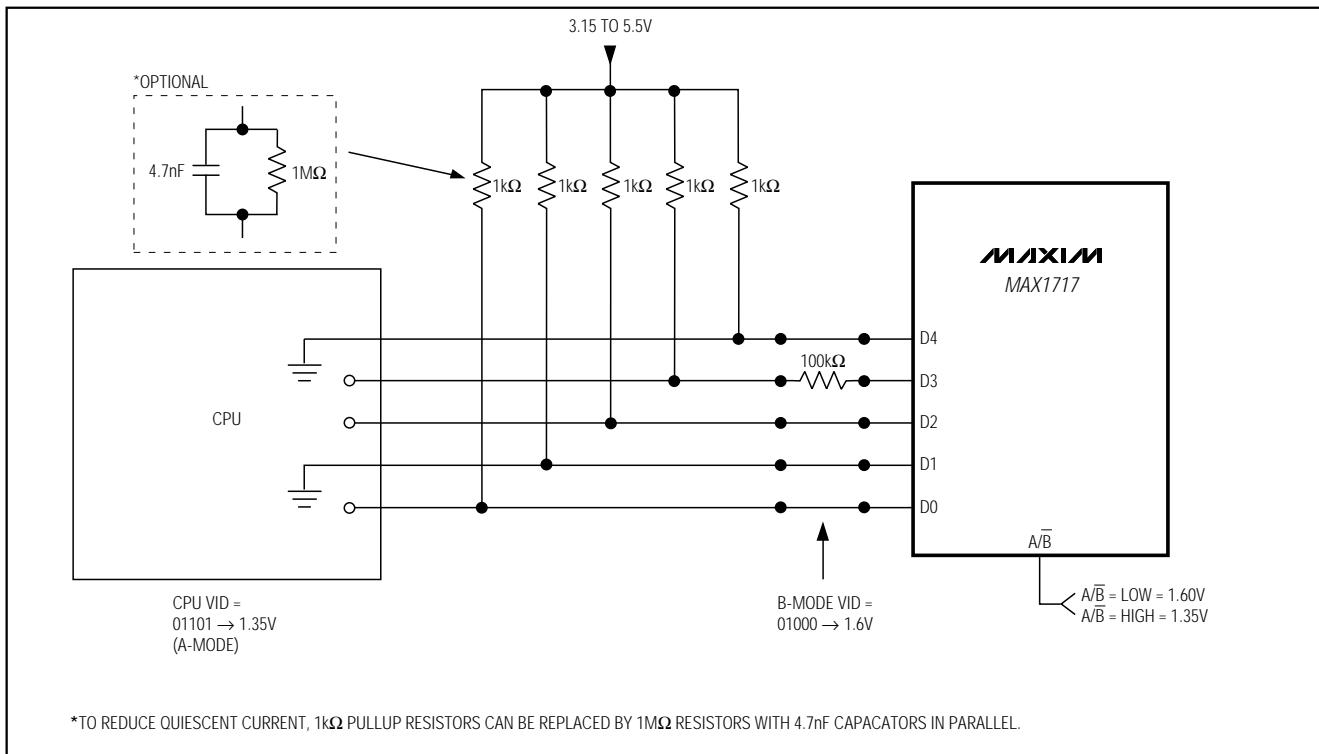

## A/ $\bar{B}$ 内部マルチプレクサ

MAX1717は、2つのプログラムされたDACコードのうちの1つ及び出力電圧を選択するために使用できる内部マルチプレクサを備えています。内部マルチプレクサはA/ $\bar{B}$ ピンで制御されます。このピンは、AモードとBモードの切換えを行います。Aモードでは、D0～D4の電圧レベルは表4に基づいて出力電圧を選択します。D0～D4はフロートさせたままにしないで下さい。内部プルアップ抵抗は存在しません。

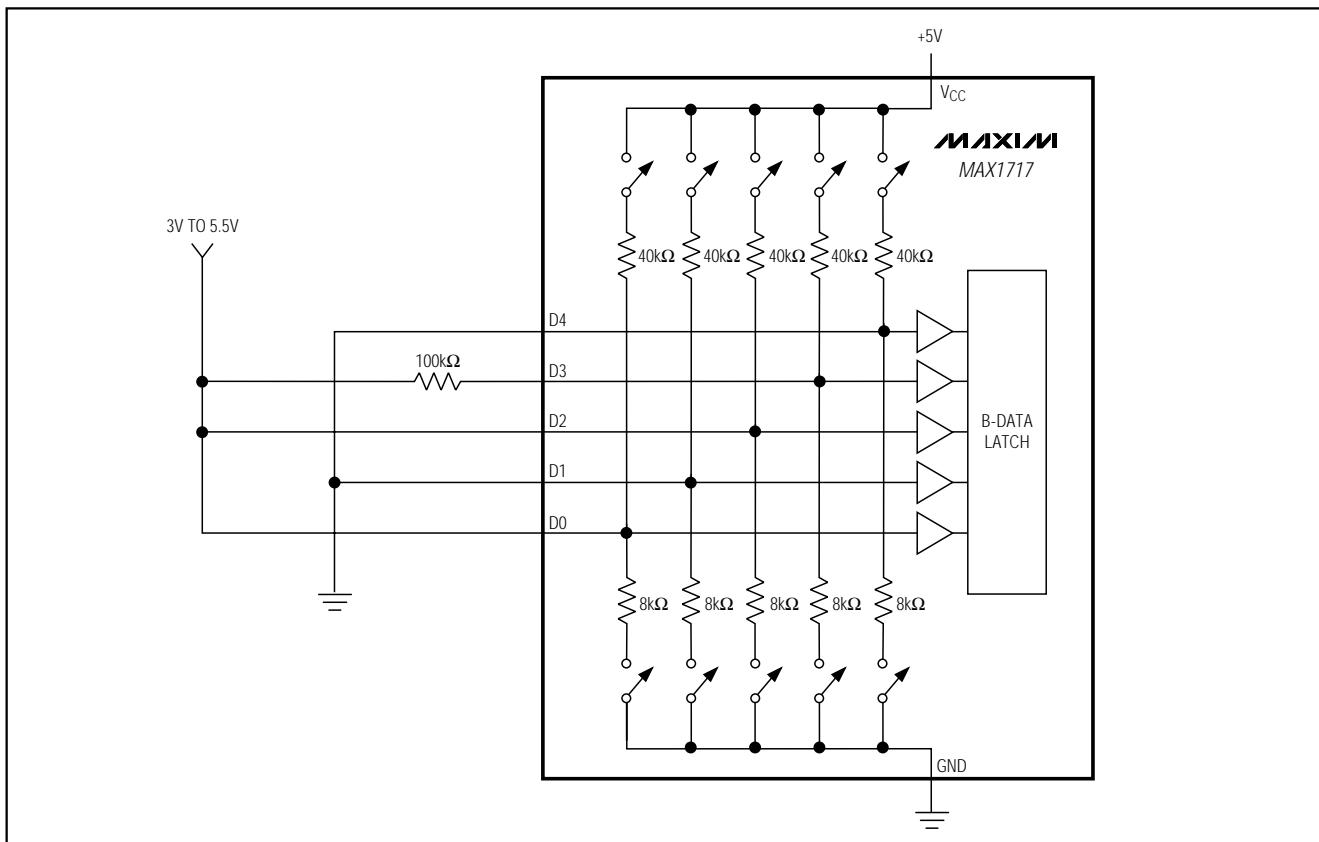

Bモードは、1セットのピンで2セットのデータビットを可能にするユニークな方式を使用して、D0～D4と直列接続された外部抵抗によりプログラムされます(図7)。A/ $\bar{B}$ がローになると(又はA/ $\bar{B}$ がローの状態でのパワーアップ中)、D0～D4のテストが行われ、ピンとの直列接続に大きな抵抗がないかどうかが検査されます。ピンの電圧レベルがロジックローの場合、内部スイッチがピンを内部の40k プルアップに約4 $\mu$ s接続し、ピン電圧を強制的にハイにしようとします(図8)。ピンの電圧をロジックハイにできない場合、このピンのインピーダンスは低く、Bモードのロジック状態はローであると見なされます。ピンをロジックハイにできる場合、インピーダンスは高く、Bモードのロジック状態もハイであると見なされます。同様に、ピンの電圧レベルがロジックハイの場合、内部スイッチはピンを内部の8k プルダウンに接続し、ピン電圧を強制的にローにしようとします。ローになった場合、ピンは高インピーダンスでそのBモードのロジック状態もハイであると見なされます。ローにならない場合、ロジック状態はローであると見なされます。

ピンの高インピーダンス(及びロジックハイ)は100k 以上で、低インピーダンス(及びロジックロー)は1k 以下です。「電気的特性」の表におけるこれらのインピーダンスの保証レベルは95k 及び1.05k で、5%の公差で標準の100k 及び1k の抵抗を使用できるようにしています。

出力電圧コードをプリント基板の設計時に固定する場合は、ピンストラップ接続及び直列レジスタの単純な組合せを使用して両方のコードをプログラムします(図7)。出力電圧コードをプリント基板の組立て時に選択する場合は、抵抗を使用して両方のコードを個別にプログラムできます(図9)。この10の抵抗実装パターンの行列は、僅か5つの抵抗ですべての可能なAモード及びBモードのコードの組合せをプログラムできます。

1つ又は複数の出力電圧コードがCPUのVIDピンにより直接提供される場合がよくあります。CPUが能動的にこれらのピンを駆動する場合は、A/ $\bar{B}$ ハイ(Aモード)を接続し、CPUに出力電圧を判断させて下さい。起動時又は他の理由によりBモードが必要な場合は、抵抗をD0～D4と直列に挿入し、Bモードの電圧をプログラム

表4. 出力電圧及びDACコード

| D4 | D3 | D2 | D1 | D0 | V <sub>OUT</sub> (V) |

|----|----|----|----|----|----------------------|

| 0  | 0  | 0  | 0  | 0  | 2.00                 |

| 0  | 0  | 0  | 0  | 1  | 1.95                 |

| 0  | 0  | 0  | 1  | 0  | 1.90                 |

| 0  | 0  | 0  | 1  | 1  | 1.85                 |

| 0  | 0  | 1  | 0  | 0  | 1.80                 |

| 0  | 0  | 1  | 0  | 1  | 1.75                 |

| 0  | 0  | 1  | 1  | 0  | 1.70                 |

| 0  | 0  | 1  | 1  | 1  | 1.65                 |

| 0  | 1  | 0  | 0  | 0  | 1.60                 |

| 0  | 1  | 0  | 0  | 1  | 1.55                 |

| 0  | 1  | 0  | 1  | 0  | 1.50                 |

| 0  | 1  | 0  | 1  | 1  | 1.45                 |

| 0  | 1  | 1  | 0  | 0  | 1.40                 |

| 0  | 1  | 1  | 0  | 1  | 1.35                 |

| 0  | 1  | 1  | 1  | 0  | 1.30                 |

| 0  | 1  | 1  | 1  | 1  | No CPU               |

| 1  | 0  | 0  | 0  | 0  | 1.275                |

| 1  | 0  | 0  | 0  | 1  | 1.250                |

| 1  | 0  | 0  | 1  | 0  | 1.225                |

| 1  | 0  | 0  | 1  | 1  | 1.200                |

| 1  | 0  | 1  | 0  | 0  | 1.175                |

| 1  | 0  | 1  | 0  | 1  | 1.150                |

| 1  | 0  | 1  | 1  | 0  | 1.125                |

| 1  | 0  | 1  | 1  | 1  | 1.100                |

| 1  | 1  | 0  | 0  | 0  | 1.075                |

| 1  | 1  | 0  | 0  | 1  | 1.050                |

| 1  | 1  | 0  | 1  | 0  | 1.025                |

| 1  | 1  | 0  | 1  | 1  | 1.000                |

| 1  | 1  | 1  | 0  | 0  | 0.975                |

| 1  | 1  | 1  | 0  | 1  | 0.950                |

| 1  | 1  | 1  | 1  | 0  | 0.925                |

| 1  | 1  | 1  | 1  | 1  | No CPU               |

注記：No CPU状態では、DH及びDLはローに維持され、スルーレートコントローラは0.9Vに設定されます。

して下さい。VIDピンは常に能動的に駆動されるようにして下さい。

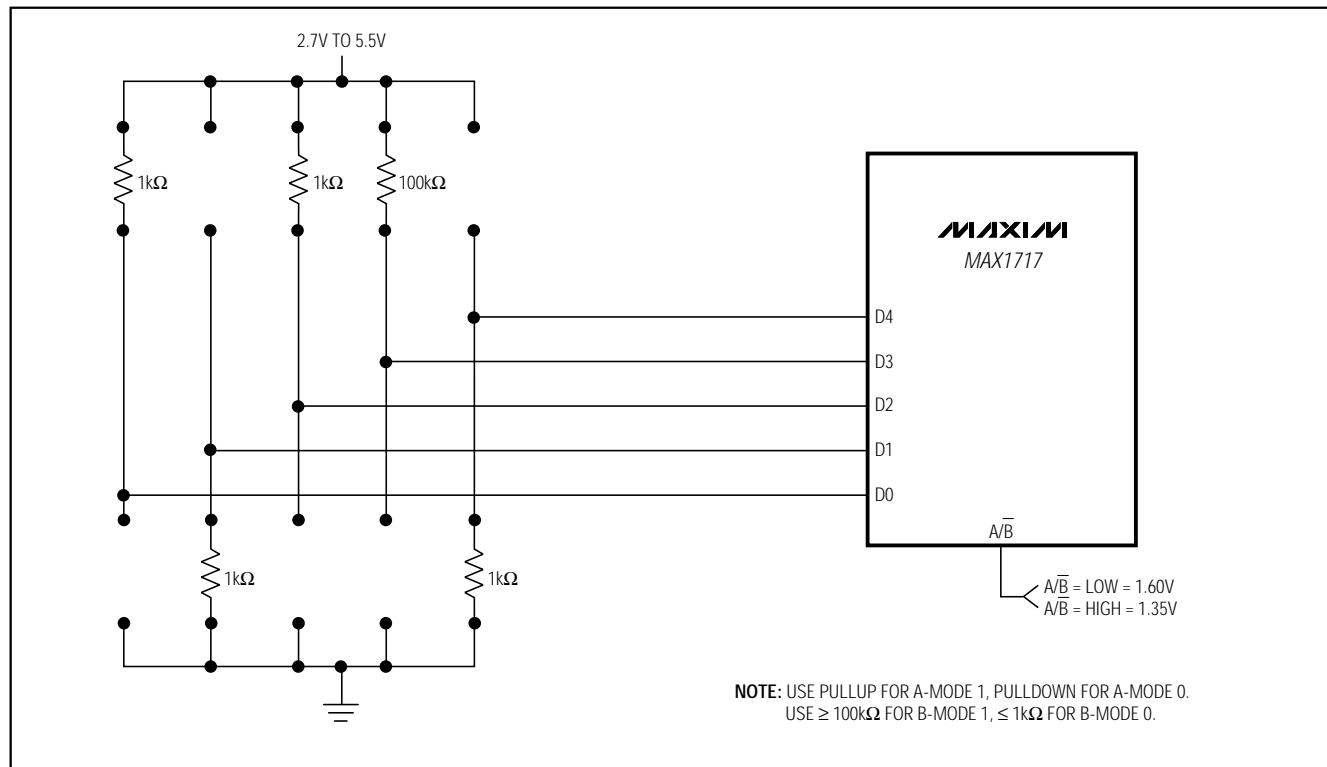

CPUのVIDピンがフローティングにされる場合、この無接続のピンがMAX1717の内部マルチプレクサに問題を発生させることができます。プロセッサのVIDピンは、適切なプルアップ抵抗と組み合わせてAモードの設定に使用できます。但し、BモードのVIDコードはD0～D4と直列に接続された抵抗により設定されており、Bモードが機能するには、Bモードでロジックローになるよう意図されているピンが少なくとも4 $\mu$ sのサンプリング間隔で低インピーダンスになることが必要です。

# ノートブックCPU用 ダイナミック可変、同期ステップダウンコントローラ

これは、次の2種類を含む幾つかの方法で達成できます(図10)。低インピーダンスのプルアップ抵抗をCPUのVIDピンと組み合わせることにより、各ピンはマルチプレクサがBモードの設定を正しく解釈するために必要とする低インピーダンスを提供します。但し、ローの抵抗はグランドに接続されているCPUの各VIDピンに数mAの余分の自己消費電流をもたらします。ここで、D0～D4は連続的ではなく、短時間だけ低インピーダンスになればよいという事実を利用することによってこの自己消費電流を避けることができます。高インピーダンスのプルアップを使用することもできます。この場合、十分な大きさの容量でプルアップをバイパスし、4μsのサンプリング間隔で低インピーダンスに見せかける必要があります。図10に示されるように、4.7nFのコンデンサは1MΩの抵抗でプルアップされても入力を低インピーダンスに見せかけることができます。

図7. ハード配線されたAモード及びBモードの

DACコード付き内部マルチプレクサの使用

MAX1717

図8. 内部マルチプレクサのBモードのデータテスト及びラッチ

# ノートブックCPU用 ダイナミック可変、同期ステップダウンコントローラ

図9. 2つのVIDコード抵抗がプログラムされた内部マルチプレクサの使用

## 出力電圧の遷移タイミング

MAX1717は制御された方法で出力電圧を遷移させ、自動的に入力サージ電流を最小化するよう設計されています。この機能は、回路の設計者が理想的に近い遷移を達成し、任意の出力容量に対する最低限のピーク電流で新しい出力電圧レベルにジャストインタイムで達することを保証します。このため、このICはSpeedStep技術を採用したCPUや、異なるコア電圧レベルを持つ2種類以上のモードで動作するその他のICに最適です。

SpeedStep技術を採用したIntelのモバイルPentium III CPUは、2種類の異なるクロック周波数で動作し、2種類の異なるコア電圧を必要とします。1つのクロック周波数から他方の周波数に遷移する時CPUはまず低電力状態になり、次に出力電力及びクロック周波数が変化します。この変更は100μs以内で行う必要があります。さもないと、システムが停止することがあります。

出力電圧遷移の始めにMAX1717はVGATE出力をローにして、遷移の始まりを示します。VGATEの遷移中はローに留まり、スルーレートコントローラが内部DACを最終値に設定し、さらにもう1つのスルーレートクロック期間が過ぎるとハイになります。スルーレートクロック

周波数(抵抗 $R_{TIME}$ で設定)は、許容されている100μs以内にVGATEがハイになるのに十分な速さに設定する必要があります。一方スルーレートクロックを必要以上に速く設定し、VGATEの立上りエッジを検出して、通常のシステム動作がより早く再開されるようにすることもできます。

出力電圧の遷移は4μsの遅延の後に25mVステップで実行され、その後に追加の1クロック期間が続きます。その後、出力電圧が安定している場合はVGATEがハイになります。遷移に要する時間の合計は、 $R_{TIME}$ 、電圧差、及びMAX1717のスルーレートクロックの精度に依存し、出力容量の合計には依存しません。出力容量が大きいほど遷移に必要なサージ電流が高くなります。MAX1717はサージ電流がILIMの設定した電流リミット以内である限り、算出された時間内に遷移を完了するために必要な最小レベルになるよう電流を自動的に制御します。遷移時間は次式で求めることができます。

$$\leq 4\mu s + \left[ \frac{1}{f_{SLEW}} \left( 1 + \frac{V_{OLD} - V_{NEW}}{25mV} \right) \right]$$

ここで、 $f_{SLEW} = 150\text{kHz} \cdot 120\text{k} / R_{TIME}$ 、 $V_{OLD}$ は元の

# ノートブックCPU用 ダイナミック可変、同期ステップダウンコントローラ

MAX1717

\*TO REDUCE QUIESCENT CURRENT, 1kΩ PULLUP RESISTORS CAN BE REPLACED BY 1MΩ RESISTORS WITH 4.7nF CAPACITORS IN PARALLEL.

図10. AモードのVIDコードを駆動するCPU及び内部マルチプレクサの使用

出力電圧で、 $V_{NEW}$ は新しい出力電圧です。 $f_{SLEW}$ の精度については「電気的特性」のTime Frequency Accuracyを参照して下さい。

$R_{TIME}$ の実用的な範囲は47k ~ 470k で、25mVステップ当たり2.6μs ~ 26μsに対応しています。DACの遷移は別個の25mVのステップで行われますが、出力フィルタによりこの遷移は比較的スムーズになります。出力電圧の遷移に必要な平均インダクタ電流は、次のとあります。

$$I_L \approx C_{OUT} \times 25mV \times f_{SLEW}$$

## 出力過電圧保護

過電圧保護(OVP)回路は、大電流を流してバッテリヒューズを切断することによって、ハイサイドMOSFETの短絡から保護するように設計されています。出力電圧は過電圧状態になつてないか継続的に監視されます。出力が2.25V以上になると、OVPがトリガされ、回路がシャットダウンされます。この結果DLローサイドゲートドライバ出力は、 $SKP/\overline{SDN}$ がトグルされるか $V_{CC}$ 電源が1V以下に一度低下するまでハイにラッチされます。

これによって、同期整流器MOSFETが100%デューティでオンになり、出力フィルタコンデンサが急速に放電され、出力が強制的にグランドレベルになります。過電圧の原因(ハイサイドMOSFETの短絡など)が取り除かれない場合は、バッテリヒューズが切断されます。 $V_{CC}$ UVLOがアクティブの時、及びシャットダウンモードの時にもDLは継続的にハイに保たれます(表5)。過電圧保護は、保護機能なしテストモードで解除できます(「保護機能なしテストモード」参照)。

## 出力低電圧シャットダウン

出力UVLP機能はフの字過電流リミットに似ていますが、可変電流リミットの代わりにタイマーを使用します。MAX1717の出力電圧が標準値の70%以下である場合、PWMがオフにラッチされ、 $V_{CC}$ のパワー切換えが行われるか、 $SKP/\overline{SDN}$ がトグルされるまで再起動しません。起動時の低電圧障害無視期間中(起動後の最初の256サイクルのスルーレート)、UVLPは無視されます。

UVLPは、保護機能なしテストモードで解除できます(「保護機能なしテストモード」参照)。

# ノートブックCPU用 ダイナミック可変、同期ステップダウンコントローラ

表5. 動作モードの真理値表

| SKP/SDN                  | DL        | MODE                            | COMMENT                                                                                                                                                                                 |

|--------------------------|-----------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND                      | High      | Shutdown                        | Low-power shutdown state. DL is forced to V <sub>DD</sub> , enforcing OVP. I <sub>CC</sub> + I <sub>DD</sub> = 2 $\mu$ A (typ).                                                         |

| 12V to 15V               | Switching | No Fault                        | Test mode with faults disabled and fault latches cleared, including thermal shutdown. Otherwise, normal operation, with automatic PWM/PFM switchover for pulse-skipping at light loads. |

| Float                    | Switching | Run (PWM, low noise)            | Low-noise operation with no automatic switchover. Fixed-frequency PWM action is forced regardless of load. Inductor current reverses at light load levels.                              |

| V <sub>CC</sub>          | Switching | Run (PFM/PWM, normal operation) | Normal operation with automatic PWM/PFM switchover for pulse-skipping at light loads.                                                                                                   |

| V <sub>CC</sub> or Float | High      | Fault                           | Fault latch has been set by OVP, UVP, or thermal shutdown. Device will remain in FAULT mode until V <sub>CC</sub> power is cycled or SKP/SDN is forced low.                             |

## 保護機能なしテストモード

過電圧/低電圧保護機能が作動していると、障害を突き止めるための時間が(長くても)数ミリ秒しかないと、プロトタイプブレッドボードのデバッグ処理が難しくなります。従って、OVP、UVP、及びサーマルシャットダウン機能を完全にディセーブルし、すでにフォルトラッチがセットされている場合にこれをクリアするためのテストモードが用意されています。PWMは、SKP/SDNがハイであるかのように動作します(SKIPモード)。保護機能なしテストモードに切り換えるには、SKP/SDNで12Vを強制的に15Vにします。

## 設計手順

入力電圧範囲及び最大負荷電流は、スイッチング周波数及びインダクタ動作点(リップル電流比)を選択する前に確定して下さい。主要な設計妥協点は、良好なスイッチング周波数及びインダクタ動作点の選択によって決まり、その他は次の4つの要因によって決まります。

- 1) 入力電圧範囲。最大値(V<sub>IN(MAX)</sub>)は、ACアダプタのワーストケースの高電圧に対応させる必要があります。最小値(V<sub>IN(MIN)</sub>)は、コネクタ、ヒューズ、及びバッテリセレクタスイッチによる電圧降下後の最低バッテリ電圧に対応させる必要があります。選択が可能な場合は、より低い入力電圧を選択すると、効率が高くなります。

- 2) 最大負荷電流。考慮すべき値は2つあります。ピーク負荷電流(I<sub>LOAD(MAX)</sub>)は瞬時的な素子のストレス及びフィルタリング条件を決定するため、出力コンデンサの選択、インダクタ飽和定格、及び電流リミット回路の設計を左右します。連続負荷電流(I<sub>LOAD</sub>)は熱ストレスを決定するため、入力コンデンサ、MOSFET、及びその他の重要な発熱部品の

選択を左右します。最近のノートブックCPUでは、I<sub>LOAD</sub> = I<sub>LOAD(MAX)</sub> · 80%が一般的です。

- 3) スイッチング周波数。サイズと効率間の基本的な妥協点は、スイッチング周波数によって決まります。MOSFETスイッチング損失は周波数及びV<sub>IN2</sub>に比例するため、最適周波数は主に最大入力電圧の関数になります。又、MOSFET技術の急速な改良によってより高い周波数が実用的になっていることから、最適周波数は変わりつつあります。

- 4) インダクタ動作点。この選択によって、サイズと効率間の妥協点を得ることができます。インダクタ値が低い程リップル電流が大きくなり、サイズが小さになりますが、効率は劣化し出力ノイズが大きくなります。実用的な最小のインダクタ値は、臨界伝導の終端(最大負荷時にインダクタ電流が各サイクルでちょうどゼロに達する点)で回路が動作する値です。インダクタ値をこれ以上小さくしても、サイズ削減の利点はありません。

- 5) MAX1717のパルススキップアルゴリズムは、臨界伝導点でスキップモードを開始します。従って、PFM/PWM切換えが発生する負荷電流値も、インダクタ動作点で決まります。最適な動作点は、通常リップル電流が20%~50%の範囲内になります。

- 6) さらに、インダクタリップル電流は、特にV<sub>IN</sub> - V<sub>OUT</sub>電圧差が小さい場合に過渡応答性能にも影響します。インダクタ値が低いとインダクタ電流のスルーレートがより速くなり、急激な負荷ステップによって出力フィルタコンデンサから放電した電荷が補給されます。出力の落ち込み量は、次に示すようにオンタイム及び最小オフタイムから計算できる最大デューティ係数の関数であります。

# ノートブックCPU用 ダイナミック可変、同期ステップダウンコントローラ

MAX1717

$$V_{SAG} = \frac{(\text{I}_{LOAD1} - \text{I}_{LOAD2})^2 \times L \left( K \frac{V_{OUT}}{V_{IN}} + t_{OFF(MIN)} \right)}{2 \times C_{OUT} \times V_{OUT} \left[ K \left( \frac{V_{IN} - V_{OUT}}{V_{IN}} \right) - t_{OFF(MIN)} \right]}$$

ここで、 $t_{OFF(MIN)}$ は最小オフ時間で(「電気的特性」参照)、 $K$ は表3から得たものです。

## インダクタの選択

インダクタ値は、次に示すようにスイッチング周波数及び動作点(%リップル又はLIR)によって決まります。

$$L = \frac{V_{OUT} (V_{IN} - V_{OUT})}{V_{IN} \times f_{SW} \times LIR \times \text{I}_{LOAD(MAX)}}$$

例： $\text{I}_{LOAD(MAX)} = 14\text{A}$ 、 $V_{IN} = 7\text{V}$ 、 $V_{OUT} = 1.6\text{V}$ 、 $f_{SW} = 300\text{kHz}$ 、30%リップル電流又はLIR = 0.30

$$L = \frac{1.6\text{V}(7\text{V} - 1.6\text{V})}{7\text{V} \times 300\text{kHz} \times 0.30 \times 14\text{A}} = 0.98\mu\text{H}$$

割当てたスペースに収まる最低のDC抵抗を持つ低損失インダクタを使用して下さい。鉄粉コアは安価で200kHzでもうまく動作しますが、通常はフェライトコアが最適です。コアは、ピークインダクタ電流( $I_{PEAK}$ )で飽和しない大きさであることが必要です。

$$I_{PEAK} = \text{I}_{LOAD(MAX)} + (LIR / 2) \text{I}_{LOAD(MAX)}$$

## 電流リミットの設定

最小電流リミットスレッショルドは、電流リミットが最小許容値の時に最大負荷電流に対応できる大きさであることが必要です。インダクタ電流の谷間は $\text{I}_{LOAD(MAX)}$ からリップル電流の半分を差し引いた時点で発生するため、次のようにになります。

$$I_{LIMIT(LOW)} > \text{I}_{LOAD(MAX)} - (LIR / 2) \text{I}_{LOAD(MAX)}$$

ここで、 $I_{LIMIT(LOW)}$ は、最小電流リミットスレッショルド電圧をQ2の $R_{DS(ON)}$ で割った値を示します。MAX1717では、最小電流リミットスレッショルド(100mVデフォルト設定)は90mVです。 $R_{DS(ON)}$ に関しては、MOSFET Q2データシートから最悪の場合の最大値を選択し、温度による $R_{DS(ON)}$ の上昇を考慮したマージンを追加します。一般に、上昇温度1°Cにつき0.5%の抵抗値を追加するのが適切です。

$$T_J = +25^\circ\text{C} \text{ で } Q_2 \text{ 最大 } R_{DS(ON)} = 5.5\text{m}\Omega \text{ 、 } T_J = +100^\circ\text{C}$$

で7.5mΩである図1の例では、次のようにになります。

$$I_{LIMIT(LOW)} = 90\text{mV} / 7.5\text{m}\Omega = 11.9\text{A}$$

必要な谷間電流リミットは次のようにになります。

$$I_{LIMIT(LOW)} > 14\text{A} - (0.3012) 14\text{A} = 11.9\text{A}$$

このため、回路はデフォルトのILIMスレッショルドを使用して全定格14Aを供給できます。

14Aの出力電流を供給する時のQ2の最悪の場合の電力消費は1.48Wです。熱抵抗が60mΩ/Wで各MOSFETの電力消費が0.74Wの時のMOSFETの温度上昇は60mΩ/W × 0.74W = 44.5°Cで、最大周囲温度は+100°C + 44.5°C = +144.5°Cです。より高い周囲温度で動作させるには、より低い $R_{DS(ON)}$ のMOSFETを選択するか、熱抵抗を減少させて下さい。電流リミットスレッショルドを上げて、より高いMOSFETジャンクション温度で動作させることもできます。

デフォルトの100mVの電流リミットスレッショルドの場合は、ILIMを $V_{CC}$ に接続します。調整可能なスレッショルドの場合は、ILIMがセンタタップに接続された状態で、抵抗分圧器をREFからGNDに接続します。0.5V~3.0Vの外部調整範囲は、50mV~300mVの電流リミットスレッショルドに対応します。電流リミットを調整する場合は、1%の許容抵抗及び10μAの分割電流を使用して電流リミット許容差における誤差が大きく増加しないようにして下さい。

## 出力コンデンサの選択

出力フィルタコンデンサの実効直列抵抗(ESR)は、出力リップル及び負荷過渡条件を満足できるように十分に小さい必要がありますが、安定性の条件を満足できる十分な大きさも必要です。又容量値は過電圧保護回路をトリップすることなく、全負荷から無負荷状態になる時のインダクタエネルギーを吸収できる大きさであることが必要です。

出力が急激な負荷遷移にさらされるCPU  $V_{CORE}$ コンバータや他のアプリケーションにおいては、出力コンデンサのサイズは負荷の遷移による過剰な出力低下を防止するために必要なESRの量に依存します。有限容量による電圧の落ち込みを無視すると、次のようにになります。

$$RESR \leq V_{STEP} / \text{I}_{LOAD(MAX)}$$

実際に必要な容量値(マイクロファラッド)は、低ESRを達成するのに必要な物理サイズ及びコンデンサの種類に関係します。従って、コンデンサは通常、容量値ではなく、ESR仕様及び電圧定格によって選択します(これに該当するのはタンタル、OS-CON、及びその他の電解コンデンサです)。

# ノートブックCPU用 ダイナミック可変、同期ステップダウンコントローラ

セラミックやポリマーなどの低容量フィルタコンデンサを使用する場合は、通常、負荷の遷移中に $V_{SAG}$ や $V_{SOAR}$ に問題が発生するのを防ぐために必要な容量を基にしてコンデンサのサイズを決定します。一般に、オーバーシュート条件を満足する容量を追加すれば、負荷の立上りエッジでのアンダーシュートが問題になることはありません(「設計手順」の項の $V_{SAG}$ の式を参照)。インダクタの蓄積エネルギーによるオーバーシュート量は、次のように計算できます。

$$V_{SOAR} \approx \frac{L \times I_{PEAK}^2}{2 \times C \times V_{OUT}}$$

ここで、 $I_{PEAK}$ はピークインダクタ電流を示します。

## 出力コンデンサの安定性

安定性は、スイッチング周波数に対するESRゼロの値によって決まります。このデータシートの電圧ポジショニング回路では、外部抵抗が出力コンデンサESRに直列接続されているため、ESRゼロの周波数を低くして安定性を保証しています。電圧ポジショニング回路の場合、出力コンデンサの最小のESR条件は、電圧ポジショニング抵抗値により削減されます。

非電圧ポジショニング回路の場合は、次の基準を満たす必要があります。不安定性の時点は次式から求めることができます。

$$f_{ESR} \leq f_{SW} / \pi$$

$$\text{ここで、 } f_{ESR} = \frac{1}{2 \times \pi \times R_{ESR} \times C_{OUT}}$$

標準的な300kHzアプリケーションでは、ESRゼロ周波数が95kHzよりもはるかに低くなければならず、望ましいのは50kHz以下です。このデータシートの発行時に広く使用されているタンタルやOS-CONコンデンサは、標準ESRゼロ周波数が15kHzになっています。インダクタの選択で使用した標準アプリケーションでは、50mV<sub>P-P</sub>リップルをサポートするのに必要なESRは50mV/4.2A = 11.9mΩです。低ESRタンタルコンデンサである470μF/4V Kemet T510を6つ並列に接続すると、5mΩ(= 50mV/10A)のESRが得られます。この場合、標準の複合ESRは17kHzでゼロになり、十分安定範囲内に収まります。安定性の保証を考慮せずに、大きな値を持つセラミックコンデンサを高速フィードバック入力(FBからGND)に直接配置することは避けて下さい。値の大きなセラミックコンデンサはESRゼロ周波数が高く、不規則で不安定な

動作になります。但し、インダクタとFBピンの接点から5cm程負荷側にコンデンサを配置するか、電圧ポジショニング回路を使用すると、十分な直列抵抗を容易に追加できます(「電圧ポジショニング及び実効効率」の項参照)。不安定な動作は、ダブルパルシング及び高速フィードバックループ不安定性といった関連性はあっても全く異なる2つの問題として現れます。

ダブルパルシングは、出力のノイズが原因で発生するか、ESRが低すぎて出力電圧信号に十分な電圧ランプが得られないことが原因で発生します。この結果、最小オフタイム期間が経過した直後に、新しいサイクルが誤差コンパレータによって誤って開始されます。ダブルパルシングは有害であるというよりも厄介で、出力リップルの増大を除いて悪影響はありません。但し、ESRが不十分なことに起因してループ不安定性が生じている可能性があります。

ループ不安定性は、ライン又は負荷変動後の出力に振動を起こし、このために出力電圧を許容範囲外に上昇又は低下させることができます。

安定性をチェックする最も簡単な方法は、ゼロから最大への非常に速い負荷遷移を与え、出力電圧リップルエンベロープのオーバーシュート及びリンギングを観察する方法です。この場合、AC電流プローブでインダクタ電流を同時に監視できます。最初のステップ応答アンダーシュート又はオーバーシュート後は、リンギングを1サイクルより多く発生させないで下さい。

## 入力コンデンサの選択

入力コンデンサは、次式で定義されるスイッチング電流に必要なリップル電流条件( $I_{RMS}$ )を満たす必要があります。

$$I_{RMS} = I_{LOAD} \frac{\sqrt{V_{OUT} (V_{IN} - V_{OUT})}}{V_{IN}}$$

ほとんどのアプリケーションでは、タンタル以外のコンデンサ(セラミック、アルミ、又はOS-CON)が適切です。これは、これらのコンデンサには機械的スイッチ付システムや、バッテリに直列接続されたコネクタを持つシステムによく見られる突入サーボ電流への耐性があるためです。MAX1717を2段電力変換システムの第2段として使用する場合は、タンタル入力コンデンサを使用しても問題ありません。どちらの構成にしても、RMS入力電流における温度上昇が+10°C未満の入力コンデンサを選択し、最適な回路寿命を保つようにして下さい。

# ノートブックCPU用 ダイナミック可変、同期ステップダウンコントローラ

MAX1717

## パワーMOSFETの選択

次に示すMOSFETガイドラインの殆どは、高電圧(>20V)ACアダプタを使用した時に、高負荷電流能力(>12A)を得ることに焦点を置いています。低電流アプリケーションでは、通常これ程注意する必要はありません。

最大の効率を得るには、ハイサイドMOSFET(Q1)として最適バッテリ電圧(15V)で伝導損失がスイッチング損失と同じになるものを選択します。この場合、最小入力電圧における伝導損失がパッケージの熱リミットを越えないこと、又は全体的な熱許容量に違反しないことを確認して下さい。さらに、最大入力電圧での伝導損失にスイッチング損失を加えた値がパッケージ定格を越えないこと、又は全体的な熱許容量に違反しないことを確認して下さい。

ローサイドMOSFET(Q2)としては、 $R_{DS(ON)}$ が最低で、適度な小型パッケージ(1つ又は2つのSO-8、DPAK、又はD<sup>2</sup>PAKなど)で提供され、妥当な価格のものを選択します。MAX1717のDLゲートドライバがQ2を駆動できることを確認して下さい。即ち、ドレインとゲート間の寄生容量が原因でQ1のターンオンによって生じるdv/dtがQ2ゲートをブルアップして貫通電流の問題を発生させることのないようにして下さい。ステップダウン構成で使用した場合、ローサイドMOSFETはゼロ電圧スイッチデバイスになるため、スイッチング損失が問題になることはありません。

## MOSFETの電力消費

最悪の場合の伝導損失は、最小あるいは最大デューティで発生します。ハイサイドMOSFETでは、次に示すように最小バッテリ電圧で、抵抗による電力消費が最悪になります。

$$PD(Q1 \text{ Resistive}) = \frac{V_{OUT}}{V_{IN}} \times I_{LOAD}^2 \times R_{DS(ON)}$$

一般に、高い入力電圧でスイッチング損失を低減するには、小さなハイサイドMOSFETが望ましくなります。しかし、MOSFETをどれだけ小さくできるかは、パッケージ電力消費リミットを守るために必要な $R_{DS(ON)}$ によってしばしば制限されます。上でも述べたように、スイッチング損失と伝導( $R_{DS(ON)}$ )損失が等しい時が最適です。通常、入力が約15Vを越えない限り、ハイサイドスイッチング損失が問題になることはありません。

ハイサイドMOSFETのスイッチング損失は、最大ACアダプタ電圧が印可された時に深刻な熱の問題を起こす

ことがあります。これは、 $CV^2f_{SW}$ スイッチング損失の式の二乗項が原因です。低バッテリ電圧で十分な $R_{DS(ON)}$ が得られるように選択したハイサイドMOSFETが、 $V_{IN(MAX)}$ によって極端に熱くなる場合は、MOSFETを選択し直す必要があります。

ターンオン時間及びターンオフ時間に影響する要因は数値化が難しいため、スイッチング損失によるQ1の電力消費を計算するのは困難です。これらの要因としては、内部ゲート抵抗、ゲートチャージ、スレッショルド電圧、ソースインダクタンス、及びプリント基板のレイアウト特性があります。次に示すスイッチング損失の計算式は概算であって、プレッドボード評価に代わるものではありません。プレッドボード評価には、Q1に取り付けた熱電対を使用した検証チェックを行うのが好適です。

$$PD(Q1 \text{ Switching}) = \frac{C_{RSS} \times V_{IN(MAX)}^2 \times f_{SW} \times I_{LOAD}}{I_{GATE}}$$

ここで、 $C_{RSS}$ はQ1の帰還容量、 $I_{GATE}$ はピークゲート駆動ソース/シンク電流(1A typ)を示します。

ローサイドMOSFET(Q2)に関しては、次に示すように常に最大バッテリ電圧で電力消費が最悪になります。

$$PD(Q2) = \left(1 - \frac{V_{OUT}}{V_{IN(MAX)}}\right) I_{LOAD}^2 \times R_{DS(ON)}$$

絶対的に最悪のMOSFET電力消費が発生するのは、 $I_{LOAD(MAX)}$ を超えていても、電流リミットを超えてフォルトランチをトリップする程大きくはない重負荷がかかる場合です。これを回避するには、次の $I_{LOAD}$ に耐える回路を設計することが必要です。

$$I_{LOAD} = I_{LIMIT(HIGH)} + (I_{LIR} / 2) \times I_{LOAD(MAX)}$$

ここで、 $I_{LIMIT(HIGH)}$ はスレッショルド許容値及びオン抵抗変動を含め、電流リミット回路に許される最大谷間電流を示します。これは、MOSFETのヒートシンクをかなり良好に行う必要があることを意味します。過負荷保護は必要なく、短絡保護だけで十分な場合は、通常の $I_{LOAD}$ 値を使用して部品ストレスを計算できます。

デッドタイム中にQ2 MOSFETボディダイオードがオンになるのを防止するには、順方向電圧が十分低いショットキダイオード(D1)を選択して下さい。原則として、DC電流定格が負荷電流の1/3に等しいダイオードで十分です。このダイオードはオプションであるため、効率が重要でない場合は省略できます。

# ノートブックCPU用 ダイナミック可変、同期ステップダウンコントローラ

## アプリケーション情報

### 電圧ポジショニング及び実効効率

新しいモバイルプロセッサの電力供給においてコスト、サイズ、及び電力消費を節約するには、新しい技術が必要です。電圧ポジショニングは出力コンデンサの合計数を減らし、任意の遷移応答条件を満たします。無負荷出力電圧を若干高く設定すると、出力電流が突然増加した時により大きなステップダウンが可能になり、負荷がかかっている時に出力を低電圧で安定化させると、出力電流が突然減少した時により大きなステップアップが可能になります。より大きなステップサイズを得ることは、出力容量を減少し、コンデンサのESRを増加できることを意味します。

無負荷出力電圧は、REFからの抵抗分圧器を通じて一定のオフセットをGNDSに追加することにより引き上げられます。27mVの公称値は1.6Vのアプリケーションに適しています。この27mVは、1.6VのV<sub>OUT</sub>における $0.9 \cdot 27\text{mV} = 24\text{mV} = 1.5\%$ の増加に対応します。電圧ポジショニング回路(図3)では、これは抵抗R4及びR5により実現されます。10μAの抵抗分圧器電流を使用して下さい。

直列出力抵抗を追加すると、全負荷出力電圧がプログラムされている実際のDAC電圧より低くなります。FB及びFBSを電圧ポジショニング抵抗(R6、5mΩ)のインダクタ側に直接接続して下さい。電圧ポジショニング抵抗のもう一方の側は、短く幅の広いプリント基板トレースを使用して出力フィルタコンデンサに直接接続して下さい。14Aの全負荷電流では、R6は70mVのドロップを発生させます。この70mVは-4.4%の誤差になりますが、GNDSオフセットからの+1.5%の誤差で補償されるため、結果として-2.9%の純誤差になります。これは電圧精度の標準仕様範囲に十分収まります。

電圧ポジショニングのもう1つの利点は、高負荷電流における電力消費が削減されることです。出力電圧は負荷が存在する時により低くなるため、CPUはより少ない電流を消費します。その結果、R6で余分な電力が若干消費されますが、CPUの電力消費はより少くなります。公称の1.6V、12Aの出力では、出力電圧が2.9%削減された場合、出力電圧は1.55Vになり、出力電流は11.65Aになります。これらの値のもとでのCPUの電力消費は19.2Wから18.1Wに低減されます。R6の追加の電力消費は次のようになります。

$$5\text{m}\Omega \times 11.65\text{A}^2 = 0.68\text{W}$$

これにより、総合的な電力の節約値は次のようにして求められます。

$$19.2 - (18.1 + 0.68) = 0.42\text{W}$$

実際には、1WのCPU消費が節約され、この節約分のほとんどは電源により消費されますが、純節約分及び加熱したCPUからの消費の移動はどちらも有益です。

実効効率は、非電圧ポジショニング回路に要求される効率として定義され、任意のCPU動作条件下での電圧ポジショニング回路の合計消費と等しくなります。

実効効率は次のようにして計算します。

1) まずポジショニング回路の効率データを使用します (V<sub>IN</sub>、I<sub>IN</sub>、V<sub>OUT</sub>、I<sub>OUT</sub>)。

2) 各データ点の負荷抵抗を次のようにモデル化します。

$$R_{LOAD} = V_{OUT} / I_{OUT}$$

3) 非ポジショニングアプリケーションの各R<sub>LOAD</sub>データ点に存在する出力電流を次のように計算します。

$$I_{NP} = V_{NP} / R_{LOAD}$$

この例では、V<sub>NP</sub>=1.6Vです。

4) 実効効率を次のようにして計算します。

実効効率 =  $(V_{NP} \cdot I_{NP}) / (V_{IN} \cdot I_{IN})$  = 算出した非ポジショニング電力出力を、測定した電圧ポジショニング電力入力で割ったもの。

5) 非ポジショニング電流I<sub>NP</sub>における効率データ点を図に表します。

電圧ポジショニング回路の実効効率は、「標準動作特性」の項に示されています。

図11. 抵抗分圧器によるV<sub>OUT</sub>の調整

# ノートブックCPU用 ダイナミック可変、同期ステップダウンコントローラ

MAX1717

## ドロップアウト性能

連続伝導動作の出力電圧調整範囲は、固定500ns(max)最小オフタイム単安定マルチバイブレータ(1000kHzで375ns(max))によって制限されます。最も優れたドロップアウト性能を得るには、遅い(200kHz)オンタイム設定を使用します。低入力電圧を使用する場合は、オンタイム及びオフタイムとしてワーストケースの値を使用して、デューティ係数リミットを計算する必要があります。製造許容値及び内部伝播遅延は、TON Kファクタに誤差を発生させます。この誤差は、周波数が高い程大きくなります(表3)。又、ドロップアウト付近で動作させた時のバックレギュレータの過渡応答性能は低く、バルク出力容量の追加が必要になることが一般的です(「設計手順」の項の $V_{SAG}$ の式を参照)。

ドロップアウトの絶対点は、インダクタ電流がオンタイム中に上昇する( $\Delta I_{UP}$ )のと同じくらい最小オフタイム中に下降する時点( $\Delta I_{DOWN}$ )になります。 $h = \Delta I_{UP} / \Delta I_{DOWN}$ の比率は、負荷の増加に応じてインダクタの電流を上昇させる能力を示すもので、常に1より大きくなっている必要があります。hが絶対最小ドロップアウト点である1に近づくにつれて、各スイッチングサイクル中にインダクタ電流を増加させることができ難しくなり、追加の出力容量を使用しない限り、 $V_{SAG}$ が大きく増加します。

妥当なhの最小値は1.5ですが、これは上下に調整して $V_{SAG}$ 、出力容量、及び最小動作電圧間で相殺できます。任意のhの値における最小動作電圧は、次のようにして計算できます。

$$V_{IN(MIN)} = \frac{\left( V_{OUT} + V_{DROP1} \right)}{1 - \left( \frac{T_{OFF(MIN)} \times h}{K} \right)} + V_{DROP2} - V_{DROP1}$$

ここで、 $V_{DROP1}$ 及び $V_{DROP2}$ は放電経路及び充電経路における寄生電圧ドロップで(「オンタイム単安定マルチバイブレータ」参照)、 $T_{OFF(MIN)}$ は「電気的特性」の表からの値で、Kは表3からの値です。絶対最小入力電圧は、h=1として計算されます。

算出した $V_{IN(MIN)}$ が必要な最小入力電圧よりも高い場合は、動作周波数を下げるか、出力容量を追加して許容範囲の $V_{SAG}$ を得る必要があります。ドロップアウト付近の動作が予想される場合は、 $V_{SAG}$ を計算して十分な過渡応答が得られるようにして下さい。

## ドロップアウト設計例 :

$$V_{OUT} = 1.6V$$

$$f_{SW} = 550\text{kHz}$$

$$K = 1.8\mu\text{s}、ワーストケース K = 1.58\mu\text{s}$$

$$T_{OFF(MIN)} = 500\text{ns}$$

$$V_{DROP1} = V_{DROP2} = 100\text{mV}$$

$$h = 1.5$$

$$V_{IN(MIN)} = (1.6V + 0.1V) / (1 - 0.5\mu\text{s} \cdot 1.5 / 1.58\mu\text{s}) + 0.1V - 0.1V = 3.2V$$

$h = 1$ で再計算すると、次のようにドロップアウトの絶対リミットを求めることができます。

$$V_{IN(MIN)} = (1.6V + 0.1V) / (1 - 1.0 \times 0.5\mu\text{s} / 1.58\mu\text{s}) - 0.1V + 0.1V = 2.5V$$

このため、出力容量が非常に大きくて $V_{IN}$ は2.5V以上である必要があり、妥当な出力容量での実用的な入力電圧は3.2Vになります。

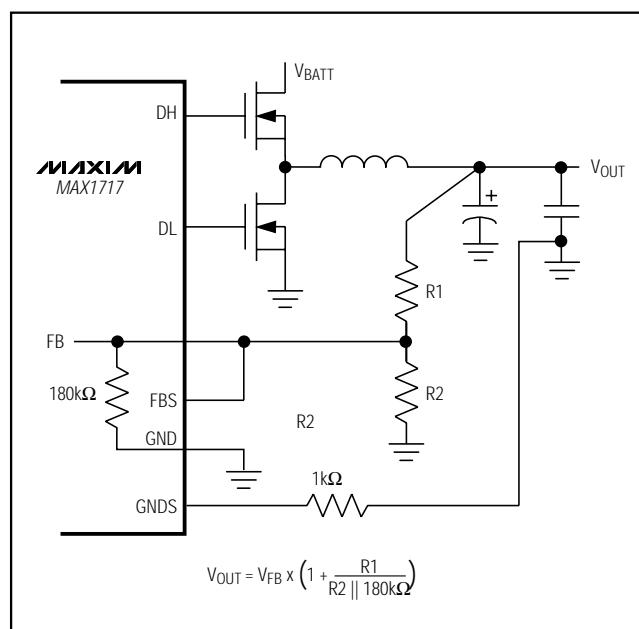

## 抵抗分圧器における $V_{OUT}$ の調整

出力電圧は、必要に応じてDACではなく抵抗分圧器を使用して調整できます(図11)。この方法の短所は、出力電圧レベルの変化に応じてオンタイムを自動的に正しく補償できないことです。この結果、抵抗比の変化に伴ってスイッチング周波数の変化や過剰なスイッチング周波数が発生する場合があります。次に、出力電圧を調整するための式を示します。

$$V_{OUT} = V_{FB} \left( 1 + \frac{R_1}{R_2 || R_{INT}} \right)$$

ここで、 $V_{FB}$ は現在選択されているDAC値で、 $R_{INT}$ はFB入力抵抗です。外部抵抗を使用した場合、FBSリモート検出は奨励できませんが、GNDSリモート検出は可能です。FBSをFBに接続し、GNDSをリモートグランドに接続して下さい。抵抗調整回路では、DACコードを実際の出力電圧にできるだけ近く設定し、スイッチング周波数の変化を最小に留めて下さい。

## $V_{OUT}$ を2V以上に調節

オンタイムをバッテリ電圧に依存させるフィードフォワード回路は、 $V_{IN}$ 、 $I_{LOAD}$ 、及びDACコードが変化してもほぼ一定のスイッチング周波数を維持します。これは、FBを出力に直接接続した場合に非常に良好に動作します。抵抗分圧器を使用して出力を調整すると、スイッチング周波数が分割比と反比例して増加します。

周波数のこの変化は、抵抗分圧器をバッテリ検出入力(V+)に追加することにより補償できます。出力抵抗器と同じ減衰率を使用して、抵抗分圧器をバッテリ電圧からMAX1717のV+に接続して下さい。 $V_{+}$ 入力の公称入力インピーダンスは600k で、抵抗器値を選択する際はこの値を考慮する必要があります。

# ノートブックCPU用 ダイナミック可変、同期ステップダウンコントローラ

## 1段(バッテリ入力)及び2段(5V入力)の アプリケーション