#### 概要

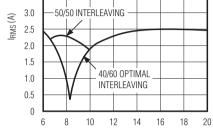

MAX17003A/MAX17004Aは、同期整流を行うデュアル ステップダウン、スイッチモード電源(SMPS)コントローラ で、バッテリ駆動システムにおいて5V/3.3Vのメイン電源 を生成するように設計されています。最適なインタリーブ とした固定周波数動作によって、最小入力電圧から26Vの 最大入力まで入力リップル電流が最低限に抑制されます。 入力電圧が10Vを下回るとデューティサイクルのオーバ ラップが発生する180°逆位相レギュレータに対して、 40/60の最適なインタリーブにより入力電圧が8.3Vに低下 するまでデューティサイクルのオーバラップが発生しま せん。

精度の高い検出抵抗または無損失のインダクタDCR電流検 出を使用する出力電流検出によって、ピーク電流制限保護 が提供されます。低ノイズモードでは、スイッチング周波 数を可聴範囲外に維持しながら、高い軽負荷効率が確保 されます。

内蔵の5V固定、100mAリニアレギュレータは、 MAX17003A/MAX17004Aおよびそのゲートドライバ のほかに、外部キープアライブ負荷に給電します。メイン PWMレギュレータがレギュレーションの範囲内である ときは、自動ブートストラップスイッチは内蔵リニア レギュレータをバイパスし、最大200mAの電流を供給し ます。外付けpnpトランジスタを使用するもう1つの可変 リニアレギュレータドライバは2次巻線を使用して、 12V電源を供給するか、またはメイン出力から直接駆動 して最低1Vの低電圧出力を生成することができます。

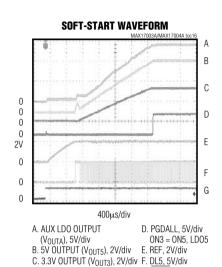

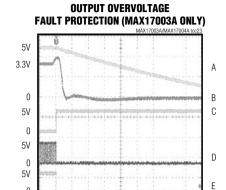

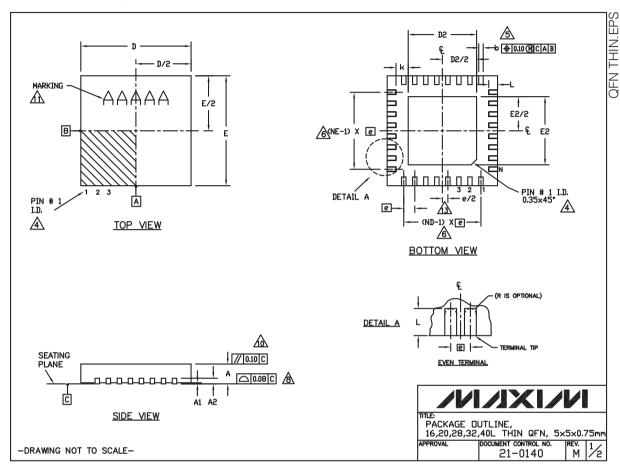

個別のイネーブル制御およびパワーグッド信号によって、 フレキシブルな電源シーケンスが可能です。電圧ソフト スタートは出力電圧を緩やかに上昇させ、突入電流を低減 し、またソフト放電は出力電圧を緩やかに下降させ、負の 電圧降下を防止します。MAX17003A/MAX17004Aは、 出力低電圧保護と過熱保護を備えています。また、 MAX17003Aは出力過電圧フォルト保護も備えています。 MAX17003A/MAX17004Aは、5mm x 5mmの32 ピンTQFNパッケージで提供されます。裏面エクスポー ズドパッドによって、要件の厳しいリニアキープアラ イブアプリケーションの熱特性が向上します。

#### アプリケーション

#### 主雷源

2~4 Li+ (リチウムイオン)セルのバッテリ駆動デバイス ノートブックおよびサブノートブックコンピュータ PDAおよびモバイル通信機器

Dual ModeはMaxim Integrated Products, Inc.の商標です。

#### 特長

- ◆ 固定周波数、電流モード制御

- ◆ 40/60の最適なインタリーブ

- ◆ 内蔵BSTスイッチ

- ◆ 内蔵5V、100mAリニアレギュレータ

- ◆ 補助リニアレギュレータドライバ(12Vまたは 最低1Vまで可変)

- ◆ Dual Mode<sup>™</sup>フィードバック-3.3V/5Vの固定、 または可変出力電圧

- ◆ スイッチング周波数: 200kHz/300kHz/500kHz

- ◆ 低電圧と過熱保護

- ◆ 過電圧フォルト保護(MAX17003Aのみ)

- ◆ 入力範囲:6V~26V

- ◆ リファレンス出力:2V ±0.75%

- ◆ 個別のイネーブル入力およびパワーグッド出力

- ◆ ソフトスタートおよびソフト放電(電圧ランプ)

- ◆ シャットダウン電流:8µA (typ)

#### 型番

| PART                  | TEMP PIN-PACKAGE<br>RANGE |                            | PKG<br>CODE |

|-----------------------|---------------------------|----------------------------|-------------|

| MAX17003AETJ+         | -40°C to<br>+85°C         | 32 Thin QFN<br>(5mm x 5mm) | T3255-4     |

| <b>MAX17004A</b> ETJ+ | -40°C to<br>+85°C         | 32 Thin QFN<br>(5mm x 5mm) | T3255-4     |

+は鉛フリーパッケージを示します。

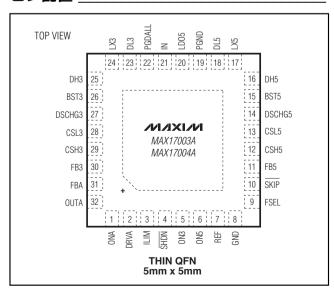

#### ピン配置

####

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| BST3, BST5 to LDO5                                    | 0.3V to +0.3V  |

|-------------------------------------------------------|----------------|

| LDO Short Circuit to GND                              | Momentary      |

| REF Short Circuit to GND                              | Momentary      |

| DRVA Current (sinking)                                | 30mA           |

| OUTA Shunt Current                                    | 30mA           |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

| Multilayer PCB                                        |                |

| 32-Pin, 5mm x 5mm TQFN                                |                |

| (derated 34.5mW/°C above +70°C)                       | 2459mW         |

| Operating Temperature Range                           | 40°C to +85°C  |

| Junction Temperature                                  | +150°C         |

| Storage Temperature Range                             | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 1,  $V_{IN}$  = 12V, both SMPS enabled, FSEL = REF,  $\overline{SKIP}$  = GND, ILIM = LDO5, FBA = LDO5, I<sub>REF</sub> = I<sub>LDO5</sub> = I<sub>OUTA</sub> = no load,  $T_A$  = 0°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.)

| PARAMETER                                | PARAMETER SYMBOL CONDITIONS |                                                                                                                                                                                                   | MIN   | TYP   | MAX   | UNITS |

|------------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| INPUT SUPPLIES (Note 1)                  |                             |                                                                                                                                                                                                   |       |       |       |       |

| Var Input Voltage Denge                  | V/v·                        | LDO5 in regulation                                                                                                                                                                                | 5.4   |       | 26.0  | V     |

| V <sub>IN</sub> Input Voltage Range      | VIN                         | IN = LDO5, V <sub>CSL5</sub> < 4.4V                                                                                                                                                               | 4.5   |       | 5.5   | V     |

| V <sub>IN</sub> Operating Supply Current | I <sub>IN</sub>             | LDO5 switched over to CSL5, either SMPS on                                                                                                                                                        |       | 20    | 36    | μΑ    |

| V <sub>IN</sub> Standby Supply Current   | lin(STBY)                   | $V_{IN}$ = 6V to 26V, both SMPS off, includes $\overline{I_{SHDN}}$                                                                                                                               |       | 65    | 120   | μΑ    |

| V <sub>IN</sub> Shutdown Supply Current  | IN(SHDN)                    | V <sub>IN</sub> = 6V to 26V                                                                                                                                                                       |       | 8     | 20    | μΑ    |

| Quiescent Power Consumption              | PQ                          | Both SMPS on, FB3 = FB5 = LDO5,<br>SKIP = GND, V <sub>CSL3</sub> = 3.5V, V <sub>CSL5</sub> = 5.3V,<br>V <sub>OUTA</sub> = 15V,<br>PIN + P <sub>CSL3</sub> + P <sub>CSL5</sub> + P <sub>OUTA</sub> |       | 3.5   | 4.5   | mW    |

| MAIN SMPS CONTROLLERS                    |                             |                                                                                                                                                                                                   |       |       |       |       |

| 3.3V Output Voltage in Fixed<br>Mode     | V <sub>OUT3</sub>           | V <sub>IN</sub> = 6V to 26V, <del>SKIP</del> = FB3 = LDO5,<br>0 < V <sub>CSH3</sub> - V <sub>CSL3</sub> < 50mV (Note 2)                                                                           | 3.265 | 3.315 | 3.365 | V     |

| 5V Output Voltage in Fixed Mode          | V <sub>OUT5</sub>           | $V_{IN} = 6V$ to 26V, $\overline{SKIP} = FB5 = LDO5$ , $0 < V_{CSH5} - V_{CSL5} < 50mV$ (Note 2)                                                                                                  | 4.94  | 5.015 | 5.09  | V     |

| Feedback Voltage in Adjustable           | \/==                        | V <sub>IN</sub> = 6V to 26V, FB3 or FB5<br>duty factor = 20% to 80%                                                                                                                               | 1.980 | 2.010 | 2.040 | V     |

| Mode (Note 2)                            | V <sub>FB</sub> _           | V <sub>IN</sub> = 6V to 26V, FB3 or FB5<br>duty factor = 50%                                                                                                                                      | 1.990 | 2.010 | 2.030 | V     |

#### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{IN}$  = 12V, both SMPS enabled, FSEL = REF,  $\overline{SKIP}$  = GND, ILIM = LDO5, FBA = LDO5, I<sub>REF</sub> = I<sub>LDO5</sub> = I<sub>OUTA</sub> = no load, **T<sub>A</sub>** = **0°C** to +85°**C**, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                                       | SYMBOL             | CON                                                     | IDITIONS                                                                  | MIN  | TYP                        | MAX                        | UNITS   |

|-------------------------------------------------|--------------------|---------------------------------------------------------|---------------------------------------------------------------------------|------|----------------------------|----------------------------|---------|

| Output Voltage Adjust Range                     |                    | Either SMPS                                             |                                                                           | 2.0  |                            | 5.5                        | V       |

| FB3, FB5 Dual Mode Threshold                    |                    |                                                         |                                                                           |      | V <sub>LOO5</sub><br>- 1.0 | V <sub>LOO5</sub><br>- 0.4 | V       |

| Feedback Input Leakage Current                  |                    | $V_{FB3} = V_{FB5} = 2.1$                               | V                                                                         | -0.1 |                            | +0.1                       | μΑ      |

| DC Load Regulation                              |                    | · ·                                                     | Either SMPS, SKIP = LDO5,<br>0 < V <sub>CSH</sub> V <sub>CSL</sub> < 50mV |      | -0.1                       |                            | %       |

| Line Regulation Error                           |                    | Either SMPS, 6V <                                       | V <sub>IN</sub> < 26V                                                     |      | 0.03                       |                            | %/V     |

|                                                 |                    | FSEL = GND                                              |                                                                           | 170  | 200                        | 230                        |         |

| Operating Frequency (Note 1)                    | fosc               | FSEL = REF                                              |                                                                           | 270  | 300                        | 330                        | kHz     |

|                                                 |                    | FSEL = LDO5                                             |                                                                           | 425  | 500                        | 575                        |         |

| Maximum Duty Factor                             | D <sub>MAX</sub>   | (Note 1)                                                |                                                                           | 97.5 | 99                         |                            | %       |

| Minimum On-Time                                 | tonmin             |                                                         |                                                                           |      | 100                        |                            | ns      |

| SMPS3-to-SMPS5 Phase Shift                      |                    | SMPS5 starts after                                      | CMDC2                                                                     |      | 40                         |                            | %       |

| SIVIFSS-10-SIVIFSS FITASE STILL                 |                    | SIVIF 33 Starts after SIVIF 33                          |                                                                           |      | 144                        |                            | Degrees |

| CURRENT LIMIT                                   |                    |                                                         |                                                                           |      |                            |                            |         |

| ILIM Adjustment Range                           |                    |                                                         |                                                                           | 0.5  |                            | $V_{REF}$                  | V       |

| Current-Sense Input Leakage<br>Current          |                    | CSH3 = CSH5 = GND or LDO5                               |                                                                           | -1   |                            | +1                         | μΑ      |

| Current-Limit Threshold (Fixed)                 | V <sub>LIMIT</sub> | V <sub>CSH</sub> V <sub>CSL</sub> _, ILI                | M = LDO5                                                                  | 45   | 50                         | 55                         | mV      |

| Current-Limit Threshold                         | V <sub>LIMIT</sub> | V <sub>CSH</sub> V <sub>CSL</sub> _                     | VILIM = 2.00V                                                             | 185  | 200                        | 215                        | mV      |

| (Adjustable)                                    | V □MII             | VCSH VCSL_                                              | V <sub>ILIM</sub> = 1.00V                                                 | 94   | 100                        | 106                        | IIIV    |

| Consent Limit Threehold                         |                    | V <sub>CSH</sub> V <sub>CSL</sub> _, SK                 | (IP = ILIM = LDO5                                                         | -67  | -60                        | -53                        | mV      |

| Current-Limit Threshold (Negative)              | VNEG               | VCSH VCSL_, Sk<br>mode, percent of c                    | IP = LDO5, adjustable current limit                                       |      | -120                       |                            | %       |

| Current-Limit Threshold (Zero Crossing)         | V <sub>Z</sub> X   | V <sub>CSH</sub> - V <sub>CSL</sub> , SK<br>ILIM = LDO5 | (IP = GND,                                                                | 0    | 3                          | 6                          | mV      |

|                                                 |                    |                                                         | ILIM = LDO5                                                               | 6    | 10                         | 14                         | mV      |

| Idle Mode™ Threshold                            | VIDLE              | VCSH VCSL_,<br>SKIP = GND                               | With respect to current-limit threshold (VLIMIT)                          |      | 20                         |                            | %       |

|                                                 |                    |                                                         | ILIM = LDO5                                                               | 2.5  | 5                          | 7.5                        | mV      |

| Idle Mode Threshold<br>(Low Audible-Noise Mode) | VIDLE              | VCSH VCSL_,<br>SKIP = REF                               | With respect to current-limit threshold (V <sub>LIMIT</sub> )             |      | 10                         |                            | %       |

| ILIM Leakage Current                            |                    | ILIM = GND or REI                                       | F                                                                         | -1   |                            | +1                         | μΑ      |

| Soft-Start Ramp Time                            | tsstart            | Measured from the full scale                            | e rising edge of ON_ to                                                   |      | 2                          |                            | ms      |

Idle ModeはMaxim Integrated Products, Inc.の商標です。

#### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{IN}$  = 12V, both SMPS enabled, FSEL = REF,  $\overline{SKIP}$  = GND, ILIM = LDO5, FBA = LDO5,  $I_{REF}$  =  $I_{LDO5}$  =  $I_{OUTA}$  = no load,  $T_A$  =  $0^{\circ}$ C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.)

| PARAMETER                                                         | SYMBOL             | CONDITIONS                                                              | MIN   | TYP      | MAX   | UNITS  |

|-------------------------------------------------------------------|--------------------|-------------------------------------------------------------------------|-------|----------|-------|--------|

| INTERNAL FIXED LINEAR REGUI                                       | ATORS              |                                                                         |       |          |       |        |

| LDO5 Output Voltage                                               | V <sub>LDO5</sub>  | ON5 = GND, 6V < V <sub>IN</sub> < 26V,<br>0 < I <sub>LD05</sub> < 100mA | 4.85  | 4.95     | 5.10  | V      |

| LDO5 Undervoltage-Lockout Fault                                   |                    | Rising edge, hysteresis = 1%                                            | 3.7   | 4.0      | 4.1   | mA     |

| Short-Circuit Current (Switched over to CSL5)                     |                    | LDO5 = GND, V <sub>CSL5</sub> > 4.7V                                    | 200   | 425      |       | mA     |

| AUXILIARY LINEAR REGULATOR                                        | ?                  |                                                                         |       |          |       | l.     |

| DRVA Voltage Range                                                | V <sub>DRVA</sub>  |                                                                         | 0.5   |          | 26.0  | V      |

| DDVA Deiter Outmant                                               |                    | V <sub>FBA</sub> = 1.05V, V <sub>DRVA</sub> = 5V                        |       |          | 0.4   | 0      |

| DRVA Drive Current                                                |                    | V <sub>FBA</sub> = 0.965V, V <sub>DRVA</sub> = 5V                       | 10    |          |       | mA     |

| FBA Regulation Threshold                                          | V <sub>FBA</sub>   | V <sub>DRVA</sub> = 5V, I <sub>DRVA</sub> = 1mA (sink)                  | 0.98  | 1.00     | 1.02  | V      |

| FBA Load Regulation                                               |                    | V <sub>DRA</sub> = 5V, I <sub>DRVA</sub> = 0.5mA to 5mA                 |       | -1.2     | -2.2  | %      |

| OUTA Shunt Trip Level                                             |                    | Rising edge                                                             | 25    | 26       | 27    | V      |

| FBA Leakage Current                                               |                    | V <sub>FBA</sub> = 1.035V                                               | 0.1   |          | +0.1  | μΑ     |

| Secondary Feedback-Regulation<br>Threshold                        |                    | VDRVA - VOUTA                                                           |       | 0        |       | V      |

| DL5 Pulse Width                                                   |                    |                                                                         |       | 1/3/fosc |       | μs     |

| OUTA Leakage Current                                              | IOUTA              | V <sub>DRVA</sub> = V <sub>OUTA</sub> = 25V                             |       |          | 50    | μΑ     |

| REFERENCE (REF)                                                   |                    |                                                                         |       |          |       |        |

| Reference Voltage                                                 | V <sub>REF</sub>   | LDO5 in regulation, I <sub>REF</sub> = 0                                | 1.985 | 2.00     | 2.015 | V      |

| Reference Load-Regulation Error                                   | $\Delta V_{REF}$   | I <sub>REF</sub> = -5μA to +50μA                                        | -10   |          | +10   | mV     |

| REF Lockout Voltage                                               | VREF(UVLO)         | Rising edge                                                             |       | 1.8      |       | V      |

| FAULT DETECTION                                                   |                    |                                                                         |       |          |       |        |

| Output Overvoltage Trip<br>Threshold (MAX17003A Only)             |                    | With respect to error-comparator threshold                              | 8     | 11       | 14    | %      |

| Output Overvoltage Fault<br>Propagation Delay<br>(MAX17003A Only) | tovp               | 50mV overdrive                                                          |       | 10       |       | μs     |

| Output Undervoltage Protection<br>Trip Threshold                  |                    | With respect to error-comparator threshold                              | 65    | 70       | 75    | %      |

| Output Undevoltage Fault<br>Propagation Delay                     | tuvp               | 50mV overdrive                                                          |       | 10       |       | μs     |

| Output Undervoltage Protection<br>Blanking Time                   | t <sub>BLANK</sub> | From rising edge of ON_ with respect to fsw                             | 5000  | 6144     | 7000  | 1/fosc |

#### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{IN}$  = 12V, both SMPS enabled, FSEL = REF,  $\overline{SKIP}$  = GND, ILIM = LDO5, FBA = LDO5, I<sub>REF</sub> = I<sub>LDO5</sub> = I<sub>OUTA</sub> = no load,  $T_A$  = 0°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.)

| PARAMETER                              | SYMBOL           | COND                                               | ITIONS                            | MIN                     | TYP  | MAX  | UNITS |

|----------------------------------------|------------------|----------------------------------------------------|-----------------------------------|-------------------------|------|------|-------|

| PGDALL Lower Trip Threshold            |                  | With respect to either S threshold, hysteresis =   | SMPS error-comparator 1% (typ)    | -12                     | -10  | -8   | %     |

| DCDALL Proposition Polari              |                  | Falling edge, 50mV o                               | verdrive                          |                         | 10   |      |       |

| PGDALL Propagation Delay               | tpgdall          | Rising edge, 50mV ov                               | verdrive                          |                         | 1    |      | μs    |

| PGDALL Output Low Voltage              |                  | Isink = 1mA                                        |                                   |                         |      | 0.4  | V     |

| PGDALL Leakage Current                 | IPGDALL          | High state, PGDALL f                               | High state, PGDALL forced to 5.5V |                         |      | 1    | μΑ    |

| Thermal-Shutdown Threshold             | tshdn            | Hysteresis = 15°C                                  |                                   |                         | +160 |      | °C    |

| GATE DRIVERS                           | •                |                                                    |                                   |                         |      |      | •     |

| DH_ Gate-Driver On-Resistance          | RDH              | BST LX_ forced to                                  | 5V                                |                         | 1.3  | 5    | Ω     |

|                                        |                  | DL_, high state                                    |                                   |                         | 1.7  | 5    |       |

| DL_ Gate-Driver On-Resistance RDL      |                  | DL_, low state                                     |                                   |                         | 0.6  | 3    | Ω     |

| DH_ Gate-Driver<br>Source/Sink Current | I <sub>DH</sub>  | DH_ forced to 2.5V, E forced to 5V                 | 3ST LX_                           |                         | 2    |      | А     |

| DL_ Gate-Driver Source Current         | I <sub>DL</sub>  | DL_ forced to 2.5V                                 |                                   |                         | 1.7  |      | А     |

| DL_ Gate-Driver Sink Current           | IDL (SINK)       | DL_ forced to 2.5V                                 |                                   |                         | 3.3  |      | А     |

| Dood Time                              | to               | DH_ low to DL_ high                                |                                   | 15                      | 45   |      | no    |

| Dead Time                              | tDEAD            | DL_ low to DH_ high                                |                                   | 15                      | 44   |      | ns    |

| Internal BST_ Switch On-Resistance     | R <sub>BST</sub> | I <sub>BST</sub> = 10mA                            | I <sub>BST</sub> = 10mA           |                         | 5    |      | Ω     |

| BST_ Leakage Current                   |                  | V <sub>BST</sub> _ = 26V                           |                                   |                         | 2    | 20   | μΑ    |

| INPUTS AND OUTPUTS                     | •                |                                                    |                                   |                         |      |      |       |

|                                        |                  | Rising trip level                                  |                                   | 1.1                     | 1.6  | 2.2  | .,    |

| SHDN Input Trip Level                  |                  | Falling trip level                                 |                                   | 0.96                    | 1    | 1.04 | V     |

|                                        |                  | Hysteresis = 600mV                                 | High                              | 2.4                     |      |      | İ ,,  |

| ONA Logic Input Voltage                |                  | (typ)                                              | Low                               |                         |      | 0.8  | V     |

|                                        |                  | SMPS off level/clear fault level Delay start level |                                   |                         |      | 0.8  |       |

| ON3, ON5 Input Voltage                 |                  |                                                    |                                   | 1.9                     |      | 2.1  | V     |

|                                        |                  | SMPS on level                                      |                                   | 2.4                     |      |      | 1     |

| DSCHG_ Output Low Voltage              |                  | Isink = 1mA                                        |                                   |                         |      | 0.4  | V     |

| DSCHG_ Leakage Current                 |                  | High state, DSCHG_ forced to 5.5V                  |                                   |                         |      | 1    | μΑ    |

|                                        |                  |                                                    | High                              | V <sub>LDO5</sub> - 0.4 |      |      |       |

| Tri-Level Input Logic                  |                  | SKIP, FSEL                                         | REF                               | 1.65                    |      | 2.35 | V     |

|                                        |                  |                                                    | GND                               |                         |      | 0.5  | 1     |

|                                        |                  | SKIP, FSEL forced to GND or LDO5                   |                                   | -1                      |      | +1   |       |

| Input Leakage Current                  |                  | SHDN forced to GND or 26V                          |                                   | -1                      |      | +1   | μΑ    |

#### **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 1,  $V_{IN}$  = 12V, both SMPS enabled, FSEL = REF,  $\overline{SKIP}$  = GND, ILIM = LDO5, FBA = LDO5, I<sub>REF</sub> = I<sub>LDO5</sub> = I<sub>OUTA</sub> = no load,  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 3)

| PARAMETER                                     | SYMBOL             | CONDITIONS                                                                                                                                                                               | MIN   | MAX                     | UNITS |

|-----------------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------|-------|

| INPUT SUPPLIES (Note 1)                       |                    |                                                                                                                                                                                          | •     |                         | •     |

| V Innut Valtage Dange                         | \/                 | LDO5 in regulation                                                                                                                                                                       | 5.4   | 26.0                    | V     |

| V <sub>IN</sub> Input Voltage Range           | VIN                | IN = LDO5, V <sub>CSL5</sub> < 4.4V                                                                                                                                                      | 4.5   | 5.5                     | V     |

| V <sub>IN</sub> Operating Supply Current      | I <sub>IN</sub>    | LDO5 switched over to CSL5, either SMPS on                                                                                                                                               |       | 40                      | μΑ    |

| V <sub>IN</sub> Standby Supply Current        | IIN(STBY)          | V <sub>IN</sub> = 6V to 26V, both SMPS off, includes ISHDN                                                                                                                               |       | 120                     | μΑ    |

| V <sub>IN</sub> Shutdown Supply Current       | IN(SHDN)           | V <sub>IN</sub> = 6V to 26V                                                                                                                                                              |       | 20                      | μΑ    |

| Quiescent Power Consumption                   | PQ                 | Both SMPS on, FB3 = FB5 = LDO5; SKIP = GND, V <sub>CSL3</sub> = 3.5V, V <sub>CSL5</sub> = 5.3V, V <sub>OUTA</sub> = 15V, PIN + P <sub>CSL3</sub> + P <sub>CSL5</sub> + P <sub>OUTA</sub> |       | 4.5                     | mW    |

| MAIN SMPS CONTROLLERS                         |                    |                                                                                                                                                                                          | •     |                         |       |

| 3.3V Output Voltage in Fixed Mode             | V <sub>OUT3</sub>  | V <sub>IN</sub> = 6V to 26V, <del>SKIP</del> = FB3 = LDO5,<br>0 < V <sub>CSH3</sub> - V <sub>CSL3</sub> < 50mV (Note 2)                                                                  | 3.255 | 3.375                   | V     |

| 5V Output Voltage in Fixed Mode               | V <sub>OUT5</sub>  | V <sub>IN</sub> = 6V to 26V, <del>SKIP</del> = FB5 = LDO5,<br>0 < V <sub>CSH5</sub> - V <sub>CSL5</sub> < 50mV (Note 2)                                                                  | 4.925 | 5.105                   | V     |

| Feedback Voltage in<br>Adjustable Mode        | V <sub>FB</sub> _  | V <sub>IN</sub> = 6V to 26V, FB3 or FB5<br>duty factor = 20% to 80% (Note 2)                                                                                                             | 1.974 | 2.046                   | V     |

| Output Voltage-Adjust Range                   |                    | Either SMPS                                                                                                                                                                              | 2.0   | 5.5                     | V     |

| FB3, FB5 Dual Mode Threshold                  |                    |                                                                                                                                                                                          | 3V    | V <sub>LDO5</sub> - 0.4 | V     |

|                                               |                    | FSEL = GND                                                                                                                                                                               | 170   | 230                     | kHz   |

| Operating Frequency (Note 1)                  | fosc               | FSEL = REF                                                                                                                                                                               | 270   | 330                     |       |

|                                               |                    | FSEL = LDO5                                                                                                                                                                              | 425   | 575                     |       |

| Maximum Duty Factor                           | DMAX               |                                                                                                                                                                                          | 97    |                         | %     |

| CURRENT LIMIT                                 |                    |                                                                                                                                                                                          |       |                         |       |

| ILIM Adjustment Range                         |                    |                                                                                                                                                                                          | 0.5   | V <sub>REF</sub>        | V     |

| Current-Limit Threshold (Fixed)               | V <sub>LIMIT</sub> | V <sub>CSH</sub> - V <sub>CSL</sub> , ILIM = LDO5                                                                                                                                        | 44    | 56                      | mV    |

| Current-Limit Threshold                       | VLIMIT             | V <sub>CSH</sub> - V <sub>CSL</sub> V <sub>ILIM</sub> = 2.00V                                                                                                                            | 185   | 215                     | mV    |

| (Adjustable)                                  |                    | V <sub>ILIM</sub> = 1.00V                                                                                                                                                                | 93    | 107                     |       |

| INTERNAL FIXED LINEAR REGU                    | LATORS             |                                                                                                                                                                                          | T     |                         | T     |

| LDO5 Output Voltage                           | V <sub>LDO5</sub>  | ON5 = GND, 6V < V <sub>IN</sub> < 26V,<br>0 < I <sub>LDO5</sub> < 100mA                                                                                                                  | 4.85  | 5.10                    | V     |

| LDO5 Undervoltage-Lockout<br>Fault Threshold  |                    | Rising edge, hysteresis = 1% (typ)                                                                                                                                                       | 3.7   | 4.1                     | V     |

| LDO5 Bootstrap Switch                         |                    | Rising edge of CSL5, hysteresis = 1% (typ)                                                                                                                                               | 4.30  | 4.75                    | V     |

| Short-Circuit Current                         |                    | LDO5 = GND, ON5 = GND                                                                                                                                                                    |       | 450                     | mA    |

| Short-Circuit Current (Switched over to CSL5) |                    | LDO5 = GND, V <sub>CSL5</sub> > 4.7V                                                                                                                                                     | 200   |                         | mA    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{IN} = 12V$ , both SMPS enabled, FSEL = REF,  $\overline{SKIP} = GND$ , ILIM = LDO5, FBA = LDO5, IREF = ILDO5 = IOUTA = no load,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted.) (Note 3)

| PARAMETER                                          | SYMBOL            | CONDI                                                       | TIONS                                      | MIN                     | MAX   | UNITS                                 |

|----------------------------------------------------|-------------------|-------------------------------------------------------------|--------------------------------------------|-------------------------|-------|---------------------------------------|

| AUXILIARY LINEAR REGULATOR                         | 7                 |                                                             |                                            |                         |       |                                       |

| DRVA Voltage Range                                 | V <sub>DRVA</sub> |                                                             |                                            | 0.5                     | 26.0  | V                                     |

| DRVA Drive Current                                 |                   | V <sub>FBA</sub> = 1.05V, V <sub>DRVA</sub> = 5V            |                                            |                         | 0.4   | mA                                    |

| DRVA Drive Current                                 |                   | V <sub>FBA</sub> = 0.965V, V <sub>DRVA</sub> =              | = 5V                                       | 10                      |       | ] ""A                                 |

| FBA Regulation Threshold                           | V <sub>FBA</sub>  | V <sub>DRVA</sub> = 5V, I <sub>DRVA</sub> = 1r              | nA (sink)                                  | 0.98                    | 1.02  | V                                     |

| OUTA Shunt Trip Level                              |                   |                                                             |                                            |                         | 27    | V                                     |

| REFERENCE (REF)                                    |                   |                                                             |                                            | •                       |       |                                       |

| Reference Voltage                                  | V <sub>REF</sub>  | LDO5 in regulation, IRE                                     | F = 0                                      | 1.980                   | 2.020 | V                                     |

| FAULT DETECTION                                    |                   |                                                             |                                            |                         |       |                                       |

| Output Overvoltage Trip Threshold (MAX17003A Only) |                   | With respect to error co                                    | mparator threshold                         | 8                       | 14    | %                                     |

| Output Undervoltage Protection                     |                   | With respect to error co                                    | With respect to error comparator threshold |                         | 75    | %                                     |

| PGDALL Lower Trip Threshold                        |                   | With respect to error comparator threshold, hysteresis = 1% |                                            | -12                     | -8    | %                                     |

| PGDALL Output Low Voltage                          |                   | ISINK = 1mA                                                 |                                            |                         | 0.4   | V                                     |

| GATE DRIVERS                                       | '                 | ,                                                           |                                            | •                       |       | •                                     |

| DH_ Gate-Driver On-Resistance                      | R <sub>DH</sub>   | BST LX_ forced to 5V                                        | 1                                          |                         | 5     | Ω                                     |

| DL Gate-Driver On-Resistance                       | Dec               | DL_, high state                                             |                                            |                         | 5     | Ω                                     |

| DL_Gate-Driver On-Resistance                       | R <sub>DL</sub>   | DL_, low state                                              |                                            |                         | 3     | ] 12                                  |

| INPUTS AND OUTPUTS                                 |                   |                                                             |                                            |                         |       |                                       |

| SHDN Input Trip Level                              |                   | Rising trip level                                           |                                            | 1.0                     | 2.3   | V                                     |

| SHOW INPUT THE Level                               |                   | Falling trip level                                          |                                            | 0.96                    | 1.04  | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

| ONA Logic Input Voltage                            |                   | Hysteresis = 600mV                                          | High                                       | 2.4                     |       | V                                     |

| ONA Logic input voltage                            |                   | Trysteresis = 000mv                                         | Low                                        |                         | 0.8   | , v                                   |

|                                                    |                   | SMPS off level/clear fau                                    | ılt level                                  |                         | 0.8   |                                       |

| ON3, ON5 Input Voltage                             |                   | Delay start level                                           |                                            | 1.9                     | 2.1   | V                                     |

|                                                    |                   | SMPS on level                                               |                                            | 2.4                     |       |                                       |

| DSCHG_ Output Low Voltage                          |                   | I <sub>SINK</sub> = 1mA                                     |                                            |                         | 0.4   | V                                     |

|                                                    |                   |                                                             | High                                       | V <sub>LDO5</sub> - 0.4 |       |                                       |

| Tri-Level Input Logic                              |                   | SKIP, FSEL                                                  | REF                                        | 1.65                    | 2.35  | V                                     |

|                                                    |                   |                                                             | GND                                        |                         | 0.5   |                                       |

- Note 1: The MAX17003A/MAX17004A cannot operate over all combinations of frequency, input voltage (V<sub>IN</sub>), and output voltage. For large input-to-output differentials and high switching-frequency settings, the required on-time may be too short to maintain the regulation specifications. Under these conditions, a lower operating frequency must be selected. The minimum ontime must be greater than 150ns, regardless of the selected switching frequency. On-time and off-time specifications are measured from 50% point to 50% point at the DH\_ pin with LX\_ = GND, VBST\_ = 5V, and a 250pF capacitor connected from DH\_ to LX\_. Actual in-circuit times may differ due to MOSFET switching speeds.

- Note 2: When the inductor is in continuous conduction, the output voltage has a DC-regulation level lower than the error-comparator threshold by 50% of the ripple. In discontinuous conduction (SKIP = GND, light load), the output voltage has a DC regulation level higher than the trip level by approximately 1.1% due to slope compensation.

- Note 3: Specifications from -40°C to +85°C are guaranteed by design, not production tested.

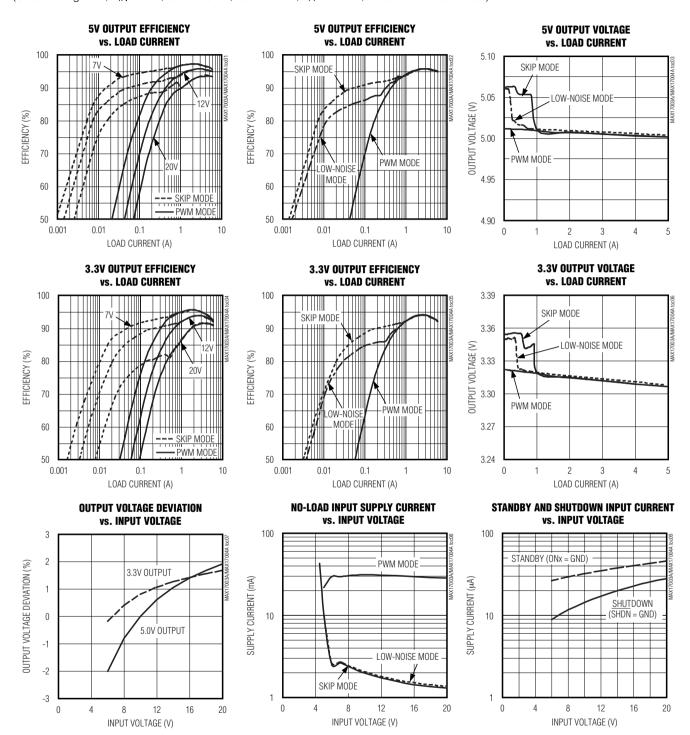

#### 標準動作特性

(Circuit of Figure 1, V<sub>IN</sub> = 12V, SKIP = GND, FSEL = REF, T<sub>A</sub> = +25°C, unless otherwise noted.)

#### 標準動作特性(続き)

(Circuit of Figure 1, V<sub>IN</sub> = 12V, SKIP = GND, FSEL = REF, T<sub>A</sub> = +25°C, unless otherwise noted.)

#### 標準動作特性(続き)

(Circuit of Figure 1,  $V_{IN} = 12V$ ,  $\overline{SKIP} = GND$ , FSEL = REF,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

G. SHDN, 5V/div

#### 標準動作特性(続き)

(Circuit of Figure 1,  $V_{IN} = 12V$ ,  $\overline{SKIP} = GND$ , FSEL = REF,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

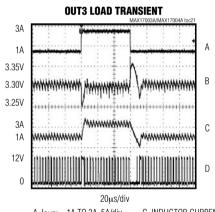

A. SKIP, 5V/div B. 3.3V OUTPUT (V<sub>OUT3</sub>), 100mV/div 0.5A LOAD

$\begin{array}{ccc} & 100\mu s/\text{div} \\ \text{A. 5V OUTPUT (V}_{\text{OUT5})}, 2\text{V/div} & \text{D. DL5, 5V/div} \\ \text{B. 3.3V OUTPUT (V}_{\text{OUT3})}, 2\text{V/div} & \text{E. PGDALL, 5V/div} \\ \text{C. DL3, 5V/div} & \text{R}_{\text{LOAD5}} = 5\Omega \end{array}$

OUTPUT UNDERVOLTAGE

(SHORT-CIRCUIT) FAULT PROTECTION

MAXITOOS/MAXITOOU Inc.24

A B

5V

0

5V

0

0

C

D

A. 3.3V OUTPUT (V<sub>OUT3</sub>), 2V/div C. PGDALL, 5V/div B. 5V OUTPUT (V<sub>OUT5</sub>), 2V/div D. DL3, 5V/div

# LD05 LOAD TRANSIENT MAX17003AM V

2A/div

D. LX3, 10V/div

A. LOAD FET GATE, 5V/div B. AUX LDO INPUT, 0.5V/div 0 TO 150mA LOAD TRANSIENT

# 12.0V 11.9V 20μs/div

C. AUX LDO OUTPUT (V<sub>OUTA</sub>), 0.1V/div

### 端子説明\_

| 端子 | 名称     | 機能                                                                                                                                                                                                                                                                                                                   |

|----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | ONA    | 補助LDOイネーブル入力。ONAがローに駆動されている場合、OUTAはハイインピーダンスになり、<br>2次フィードバック制御がディセーブルされます。ONAがハイに駆動されている場合、コントローラ<br>は補助LDOをイネーブルします。                                                                                                                                                                                               |

| 2  | DRVA   | 補助LDOトランジスタベースドライバ。DRVAをpnpパワートランジスタのベースに接続してください。<br>ベースとエミッタの間に680Ωのプルアップ抵抗を接続してください。                                                                                                                                                                                                                              |

| 3  | ILIM   | ピーク電流制限スレッショルド調整。ILIMがLDO5にプルアップされている場合、電流制限スレッショルドはデフォルトで50mVになります。可変モードの場合、CSH_とCSL_の間の電流制限スレッショルドは0.5V~2.0Vの範囲で正確にILIMの電圧の1/10になります。50mVのデフォルト値への切替えのロジックスレッショルドは約V <sub>LDO5</sub> - 1Vです。                                                                                                                       |

| 4  | SHDN   | シャットダウン制御入力。 $V_{\overline{SHDN}}$ が $\overline{SHDN}$ 入力立下りエッジトリップレベルより低い場合、デバイスは消費電流 $8\mu A$ のシャットダウンモードに移行して、 $V_{\overline{SHDN}}$ が $\overline{SHDN}$ 入力立上りトリップレベルを上回るまで動作を再開しません。自動起動にするには、 $\overline{SHDN}$ を $V_{\overline{IN}}$ に接続してください。抵抗分圧器を介して $\overline{SHDN}$ を $V_{\overline{IN}}$ に接続することができます。 |

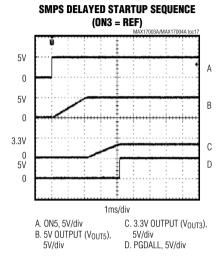

| 5  | ON3    | 3.3V SMPSイネーブル入力。ON3をハイに駆動することで3.3V SMPSがイネーブルされ、ON3をローに駆動することで3.3V SMPSがディセーブルされます。ON3がREFに接続されている場合、5V SMPSがレギュレーションに到達した後で3.3V SMPSが始動します(遅延スタート)。フォルトラッチをリセットするには、ON3をクリアフォルトレベル以下に駆動してください。                                                                                                                     |

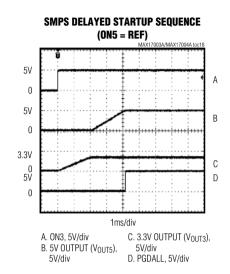

| 6  | ON5    | 5V SMPSイネーブル入力。ON5をハイに駆動することで5V SMPSがイネーブルされ、ON5をローに駆動することで5V SMPSがディセーブルされます。ON5がREFに接続されている場合、3.3V SMPSがレギュレーションに到達した後で5V SMPSが始動します(遅延スタート)。フォルトラッチをリセットするには、ON5をクリアフォルトレベル以下に駆動してください。                                                                                                                           |

| 7  | REF    | 2.0Vリファレンス電圧出力。0.1µF以上のセラミックコンデンサでREFをアナロググランドにバイパスしてください。リファレンスは外部負荷に対して最大50µAをソースします。REFに負荷を接続した場合、REFの負荷レギュレーション誤差にしたがって出力電圧の精度が低下します。システムがSHDNをローに駆動した場合、リファレンスはシャットダウンします。                                                                                                                                      |

| 8  | GND    | アナロググランド。裏面エクスポーズドパッドをGNDに接続してください。                                                                                                                                                                                                                                                                                  |

| 9  | FSEL   | 周波数選択入力。この3レベルのロジック入力によって、コントローラのスイッチング周波数を設定します。LDO5、REF、またはGNDに接続して、以下の標準スイッチング周波数を選択してください:LDO5 = 500kHz、REF = 300kHz、GND = 200kHz。                                                                                                                                                                               |

| 10 | SKIP   | パルススキップ制御入力。低ノイズの強制PWM動作を行わせるには、LDO5に接続してください。軽負荷時に低ノイズの自動パルススキップ動作を行わせるには、REFに接続してください。軽負荷時に高効率の自動パルススキップ動作を行わせるには、GNDに接続してください。起動時には、SKIPの設定に関係なく常に低ノイズのパルススキップモード(すなわち、SKIP = REFに設定した場合と同じ)になります。SKIPの設定は、各SMPSがレギュレーションに到達した時点で有効になります。                                                                         |

| 11 | FB5    | 5V SMPS用のフィードバック入力。プリセットの5V出力の場合、LDO5に接続してください。可変<br>モードでは、FB5は2Vに安定化されます。                                                                                                                                                                                                                                           |

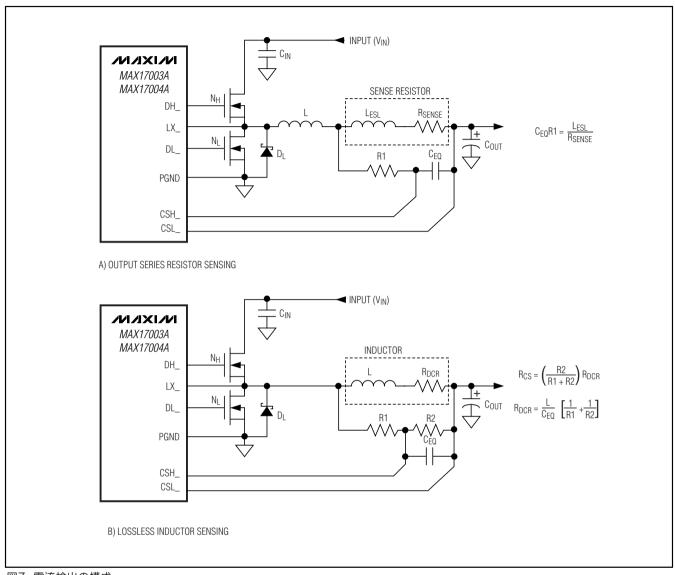

| 12 | CSH5   | 5V SMPS用の正の電流検出入力。電流検出素子の正の端子に接続してください。図7に、高精度の<br>検出抵抗または無損失のインダクタDCR検出を使用する2種類の電流検出方式を示します。                                                                                                                                                                                                                        |

| 13 | CSL5   | 5V SMPS用の出力検出および負の電流検出入力。内蔵のプリセット5Vフィードバック分圧器を使用する場合(FB5 = LDO5)、コントローラはCSL5を使用して出力電圧を検出します。電流検出素子の負の端子に接続してください。CSL5は、LDO5のブートストラップ入力としても機能します。MAX17003Aの場合、CSL5が-7Vを下回るのを防止するために、CSL5とGNDの間にショットキーダイオードを接続してください。                                                                                                  |

| 14 | DSCHG5 | 5V SMPS用のオープンドレインの放電入力。ON5がローの場合DSCHG5はローに駆動されて、SMPS5の出力を放電します。DSCHG5はフォルト条件下でもローになります。DSCHG5とSMPS5の出力の間に47Ω以上の抵抗を接続してください。                                                                                                                                                                                          |

12 \_\_\_\_\_\_ /VI/XI/M

#### 端子説明(続き)

| 端子 | 名称     | 機能                                                                                                                                                                                                                                                                                          |

|----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 | BST5   | 5V SMPSのブーストフライングコンデンサ接続。MAX17003A/MAX17004Aは、LD05とBST5の間に接続されたブーストスイッチを内蔵しています。図1に示すように外付けコンデンサに接続してください。                                                                                                                                                                                  |

| 16 | DH5    | 5V SMPSのハイサイドゲートドライバ出力。DH5のスイング範囲はLX5~BST5です。                                                                                                                                                                                                                                               |

| 17 | LX5    | 5V SMPSのインダクタ接続。LX5をインダクタのスイッチ側に接続してください。LX5はDH5ハイサイドゲートドライバの低圧側電源レイルとして機能します。                                                                                                                                                                                                              |

| 18 | DL5    | 5V SMPSのローサイドゲートドライバ出力。DL5のスイング範囲はPGND~LDO5です。                                                                                                                                                                                                                                              |

| 19 | PGND   | 電源グランド                                                                                                                                                                                                                                                                                      |

| 20 | LD05   | $5$ V内蔵リニアレギュレータ出力。 $4.7$ μF (min、 $1$ μF/ $25$ mA)のコンデンサでバイパスしてください。 DL_ローサイドゲートドライバ、DH_ハイサイドドライバ(BSTスイッチ経由)、PWMコントローラ、ロジック、リファレンス、および外部負荷に対して、少なくとも $100$ mAを供給します。CSL $5$ が $4.5$ Vを上回り、かつソフトスタートが完了している場合、リニアレギュレータがシャットダウンして、定格負荷が最大 $200$ mAの $1$ Ωのスイッチを介してLDO $5$ がCSL $5$ に接続されます。 |

| 21 | IN     | スタートアップ回路およびLDO5内蔵5Vリニアレギュレータの入力。ICの近くに配置した0.22μF<br>以上のセラミックコンデンサでPGNDにバイパスしてください。                                                                                                                                                                                                         |

| 22 | PGDALL | SMPS3およびSMPS5のオープンドレインのパワーグッド出力。SMPS3またはSMPS5の <b>いずれか</b> の出力が正常なレギュレーションポイントを10% (typ)以上下回るか、ON3またはON5の <b>いずれか</b> がローの場合、PGDALLがローに駆動されます。SMPS3とSMPS5の <b>両方</b> がレギュレーション状態の場合、PGDALLはハイインピーダンスになります。                                                                                  |

| 23 | DL3    | 3.3V SMPSのローサイドゲートドライバ出力。DL3のスイング範囲はPGND~LDO5です。                                                                                                                                                                                                                                            |

| 24 | LX3    | 3.3V SMPSのインダクタ接続。LX3をインダクタのスイッチ側に接続してください。LX3はDH3<br>ハイサイドゲートドライバの低圧側電源レイルとして機能します。                                                                                                                                                                                                        |

| 25 | DH3    | 3.3V SMPSのハイサイドゲートドライバ出力。DH3のスイング範囲はLX3~BST3です。                                                                                                                                                                                                                                             |

| 26 | BST3   | 3.3V SMPSのブーストフライングコンデンサ接続。MAX17003A/MAX17004Aは、LD05とBST3 の間に接続されたブーストスイッチを内蔵しています。図1に示すように外付けコンデンサに接続してください。                                                                                                                                                                               |

| 27 | DSCHG3 | 3.3V SMPS用のオープンドレインの放電出力。ON3がローの場合DSCHG3はローに駆動されて、SMPS3の出力を放電します。DSCHG3はフォルト条件下でもローになります。DSCHG3とSMPS3の出力の間に47Ω以上の抵抗を接続してください。                                                                                                                                                               |

| 28 | CSL3   | 3.3V SMPS用の出力検出および負の電流検出。内蔵のプリセット3.3Vフィードバック分圧器を使用する場合(FB3 = LDO5)、コントローラはCSL3を使用して出力電圧を検出します。電流検出素子の負の端子に接続してください。                                                                                                                                                                         |

| 29 | CSH3   | 3.3V SMPS用の正の電流検出入力。電流検出素子の正の端子に接続してください。図7に、高精度の<br>検出抵抗または無損失のインダクタDCR検出を使用する2種類の電流検出方式を示します。                                                                                                                                                                                             |

| 30 | FB3    | 3.3V SMPS用のフィードバック入力。固定の3.3V出力の場合、LDO5に接続してください。可変<br>モードでは、FB3は2Vに安定化されます。                                                                                                                                                                                                                 |

#### 端子説明(続き)

| 端子 | 名称   | 機能                                                                                                                                                                                                                                                                                               |

|----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

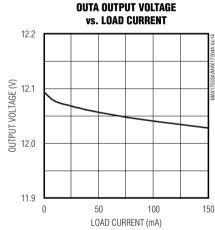

| 31 | FBA  | 補助LDOフィードバック入力。OUTAとアナロググランドの間に抵抗分圧器を接続して、補助リニアレギュレータの出力電圧を調整してください。FBAは1Vに安定化されます。                                                                                                                                                                                                              |

| 32 | OUTA | 可変補助リニアレギュレータ出力。1µF以上(1µF/25mA)のコンデンサでOUTAをGNDにバイパスしてください。DRVA < OUTAの場合、2次フィードバック制御によって1µsの間DL5がトリガされ、コントローラに補助蓄積コンデンサの再充電を強制します。DRVAが25Vを上回った場合、MAX17003A/MAX17004AはOUTAの10mAシャントをイネーブルして、トランスの漏れインダクタンスによって蓄積コンデンサが危険なレベルまで上昇するのを防止します。ONAをハイに駆動することによって、リニアレギュレータドライバと2次フィードバック制御がイネーブルされます。 |

| EP | EP   | エクスポーズドパッド。 <b>裏面エクスポーズドパッドをアナロググランドに接続してください。</b>                                                                                                                                                                                                                                               |

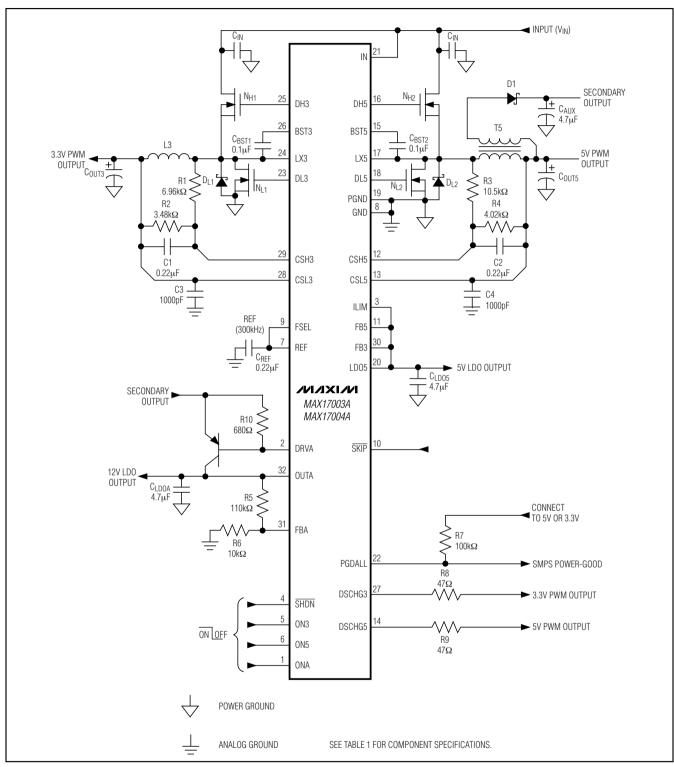

## 表1. 標準アプリケーションの部品の選択

| COMPONENT                            | 300kHz<br>5V AT 5A<br>3.3V AT 5A                                           | 500kHz<br>5V AT 3A<br>3.3V AT 5A                                           |  |

|--------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------|--|

| INPUT VOLTAGE                        | V <sub>IN</sub> = 7V TO 24V                                                | V <sub>IN</sub> = 7V TO 24V                                                |  |

| C <sub>IN</sub> _, Input Capacitor   | (3) 10µF, 25V<br>Taiyo Yuden TMK432BJ106KM                                 | (3) 10µF, 25V<br>Taiyo Yuden TMK432BJ106KM                                 |  |

| 5V OUTPUT                            |                                                                            | •                                                                          |  |

| C <sub>OUT5</sub> , Output Capacitor | 2x 100μF, 6V, 35mΩ<br>SANYO 6TPE100MAZB                                    | 2x 100μF, 6V, 35m $\Omega$<br>SANYO 6TPE100MAZB                            |  |

| L5/T5, Inductor/Transformer          | 6.8μH, 6.4A, 18mΩ (max) 1:2<br>Sumida 4749-T132                            | _                                                                          |  |

| N <sub>H5</sub> , High-Side MOSFET   | Fairchild Semiconductor<br>FDS6612A<br>International Rectifier<br>IRF7807V | Fairchild Semiconductor<br>FDS6612A<br>International Rectifier<br>IRF7807V |  |

| N <sub>L5</sub> , Low-Side MOSFET    | Fairchild Semiconductor FDS6670S International Rectifier IRF7807VD1        | Fairchild Semiconductor FDS6670S International Rectifier IRF7807VD1        |  |

| 3V OUTPUT                            |                                                                            |                                                                            |  |

| C <sub>OUT3</sub> , Output Capacitor | 2x 150μF, 4V, 35mΩ<br>SANYO 4TPE150MAZB                                    | 2x 100μF, 6V, 35m $\Omega$<br>SANYO 6TPE100MAZB                            |  |

| L3, Inductor                         | 5.8μH, 8.6A, 16.2mΩ<br>Sumida CORH127/LD-BR8NC                             | $3.9\mu H, 6.5A, 15m\Omega$<br>Sumida CDRH124-3R9NC                        |  |

| N <sub>H3</sub> , High-Side MOSFET   | Fairchild Semiconductor<br>FDS6612A<br>International Rectifier<br>IRF7807V | Fairchild Semiconductor FDS6612A International Rectifier IRF7807V          |  |

| N <sub>L3</sub> , Low-Side MOSFET    | Fairchild Semiconductor FDS6670S International Rectifier IRF7807VD1        | Fairchild Semiconductor FDS6670S International Rectifier IRF7807VD1        |  |

14 \_\_\_\_\_\_ **/VI/IXI/M**

図1. 標準アプリケーション回路

#### 表2. 部品メーカー

| SUPPLIER                 | WEBSITE                      |

|--------------------------|------------------------------|

| AVX                      | www.avx.com                  |

| Central Semiconductor    | www.centralsemi.com          |

| Fairchild                | www.fairchildsemi.com        |

| International Rectifier  | www.irf.com                  |

| KEMET                    | www.kemet.com                |

| NEC/Tokin                | www.nec-tokin.com            |

| Panasonic                | www.panasonic.com/industrial |

| Philips                  | www.philips.com              |

| Pulse                    | www.pulseeng.com             |

| Renesas                  | www.renesas.com              |

| SANYO                    | www.edc.sanyo.com            |

| Sumida                   | www.sumida.com               |

| Taiyo Yuden              | www.t-yuden.com              |

| TDK                      | www.component.tdk.com        |

| TOKO                     | www.tokoam.com               |

| Vishay (Dale, Siliconix) | www.vishay.com               |

#### 詳細

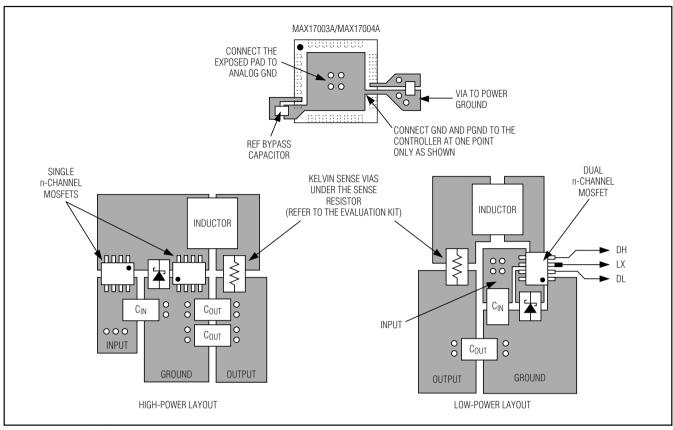

MAX17003A/MAX17004Aの標準アプリケーション回路(図1)は、ノートブックコンピュータのメイン電源で一般に使用される5V/5Aと3.3V/5Aを生成します。入力電源電圧範囲は7V~24Vです。部品の選択については表1を、部品メーカーについては表2をご覧ください。MAX17003A/MAX17004Aは、低電圧電源用に設計された2つのインタリーブされた固定周波数のステップダウンコントローラを内蔵しています。最適なインタリーブを使用するアーキテクチャによって位相差の動作が保証され、入力コンデンサのリップルが軽減されます。1つの内蔵LDOは、キープアライブ用5V電源を生成します。MAX17003A/MAX17004Aは、3.3Vのキープアライブ電源の生成または低電力12Vシステム電源の安定化を行うための可変出力の補助LDOを備えています。

#### 固定5Vリニアレギュレータ(LDO5)

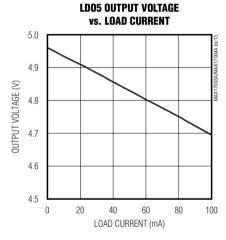

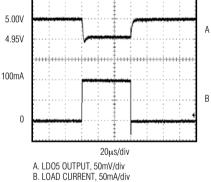

内蔵リニアレギュレータは、プリセットの5V低電流出力を生成します。LDO5は外付けMOSFET用のゲートドライバへの給電を行い、SMPSアナログコントローラ、リファレンス、およびロジックブロックに必要なバイアス電源を提供します。LDO5は、MOSFETゲート駆動を含む外部および内部の負荷に少なくとも100mAを供給します。MOSFETゲート駆動は、スイッチング周波数と外付けMOSFETの選択に応じて、通常は5mA~50mAの範囲で変動します。全負荷状態での安定性を保証するために、LDO5を4.7 $\mu$ F以上のセラミックコンデンサ(負荷25mA当り1 $\mu$ F)でバイパスしてください。

MAX17003A/MAX17004A SMPSコントローラは、 高出力の入力電源(バッテリまたはACアダプタ)に加えて、 5Vのバイアス電源を必要とします。この5Vバイアス電 源は、コントローラの内蔵5Vリニアレギュレータ (LDO5)によって生成されます。このブートストラップ 式LDOによって、コントローラは単独で起動することができます。ゲートドライバの入力電源は、固定5Vの リニアレギュレータ出力(LDO5)に接続されます。その ため、5V LDO電源はLDO5 (PWMコントローラ)およびゲート駆動電力を供給する必要があり、次の最大消費電流が要求されます。

$$I_{BIAS} = I_{CC} + f_{SW} (Q_{G(LOW)} + Q_{G(HIGH)})$$

= 5mA~50mA (typ)

ここで、 $I_{CC}$ は0.7mA(typ)、 $f_{SW}$ はスイッチング周波数、 $Q_{G(LOW)}$ と $Q_{G(HIGH)}$ は、MOSFETのデータシートの $V_{GS}$  = 5Vでの総ゲート電荷量の仕様上の制限値です。

#### SMPSからLDOへのブートストラップ切替え

5Vのメイン出力電圧がLDO5ブートストラップ切替え スレッショルドを上回り、かつソフトスタートが完了 している場合、内蔵の1Ω (typ) pチャネルMOSFETに よってCSL5がLDO5に短絡され、それと同時にLDO5 リニアレギュレータがシャットダウンされます。これ によってデバイスがブートストラップされ、バッテリ からリニアレギュレータを介してではなく5V SMPS出力 (CSL5)から内部回路および外部負荷への給電が行われ ます。ブートストラップは、大幅に効率が低いリニア レギュレータの代わりに効率90%のスイッチモード ソースから給電することによって、ゲート電荷と自己 損失に起因する電力消費を低減します。LDO5出力か らCSL5への切替えで、電流能力は100mAから 200mAに増大します。ON5をローに駆動した場合、 コントローラは直ちにブートストラップスイッチをディ セーブルし、5V LDOを再イネーブルします。

#### リファレンス(REF)

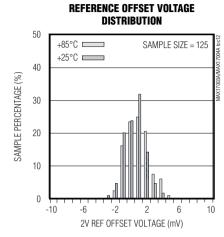

2Vのリファレンスは温度と負荷の変動に対して $\pm 1\%$ の精度を備えているため、REFは高精度のシステムリファレンスとして役立ちます。 $0.1\mu$ F以上のセラミックコンデンサでREFをGNDにバイパスしてください。このリファレンスは、外部負荷に対して最大 $50\mu$ Aのソースおよび $5\mu$ Aのシンクをサポートします。メインSMPSの出力電圧に関して非常に高精度の仕様が要求される場合は、リファレンスに負荷を接続しないでください。リファレンスに負荷を接続した場合、リファレンスの負荷レギュレーション誤差のため、LDO5、CSL5 (OUT5)、CSL3 (OUT3)、およびOUTAの出力電圧がわずかに低下します。

#### システムイネーブル/シャットダウン(SHDN)

MAX17003A/MAX17004Aを低電力シャットダウン 状態にするには、SHDNを正確なSHDN入力立下りエッジ トリップレベルより低い電圧に駆動してください。コン トローラは、シャットダウンモードでは8µAの自己消費

表3. 動作モードの真理値表

| MODE                                               |      | INPUTS* |      | OUTPUTS                                      |                                                    |                                                  |  |  |

|----------------------------------------------------|------|---------|------|----------------------------------------------|----------------------------------------------------|--------------------------------------------------|--|--|

| MODE                                               | SHDN | ON5     | ON3  | LDO5                                         | 5V SMPS                                            | 3V SMPS                                          |  |  |

| Shutdown Mode                                      | Low  | Χ       | Х    | OFF                                          | OFF                                                | OFF                                              |  |  |

| Standby Mode                                       | High | Low     | Low  | ON                                           | OFF, DSCHG5 LOW                                    | OFF, DSCHG3 LOW                                  |  |  |

| Normal Operation                                   | High | High    | High | ON                                           | ON                                                 | ON                                               |  |  |

| 3.3V SMPS Active                                   | High | Low     | High | ON                                           | OFF, DSCHG5 LOW                                    | ON                                               |  |  |

| 5V SMPS Active                                     | High | High    | Low  | OFF<br>LDO5 to CSL5 bypass<br>switch enabled | ON                                                 | OFF, DSCHG3 LOW                                  |  |  |

| Normal Operation<br>(Delayed 5V SMPS<br>Startup)   | High | Ref     | High | OFF<br>LDO5 to CSL5 bypass<br>switch enabled | ON<br>Power-up after 3.3V<br>SMPS is in regulation | ON                                               |  |  |

| Normal Operation<br>(Delayed 3.3V SMPS<br>Startup) | High | High    | Ref  | OFF<br>LDO5 to CSL5 bypass<br>switch enabled | ON                                                 | ON<br>Power-up after 5V<br>SMPS is in regulation |  |  |

\*SHDNは高精度、低電圧のロジック入力で、立下りエッジスレッショルド電圧は1V、立上りエッジスレッショルド電圧は1.6Vです。 ON3およびON5は3レベルのCMOSロジック入力で、0.8Vより低い電圧がロジックロー、2.4Vより高い電圧がロジックハイ、中間ロジックレベルが1.7V~2.3Vです(「ELECTRICAL CHARACTERISTICS (電気的特性)」の表を参照)。

電流のみを消費します。シャットダウンモード作動時、コントローラがシャットダウンシーケンスを完了した後でリファレンスがオフになるため、シャットダウン 終了のスレッショルドの精度が低下します。スタートアップを保証するためには、SHDNを2V(SHDN入力立上りエッジトリップレベル)より高い電圧に駆動してください。自動でシャットダウンおよびスタートアで行うには、SHDNをVINに接続してください。正確に1VのSHDNの立下りエッジスレッショルドを使用して、特定の入力電圧レベルを検出してデバイスをシーの移行後は1.6Vの立上りエッジスレッショルドが有効にならため、ほとんどのアプリケーションにとって十分なヒステリシスが提供されます(表3を参照)。

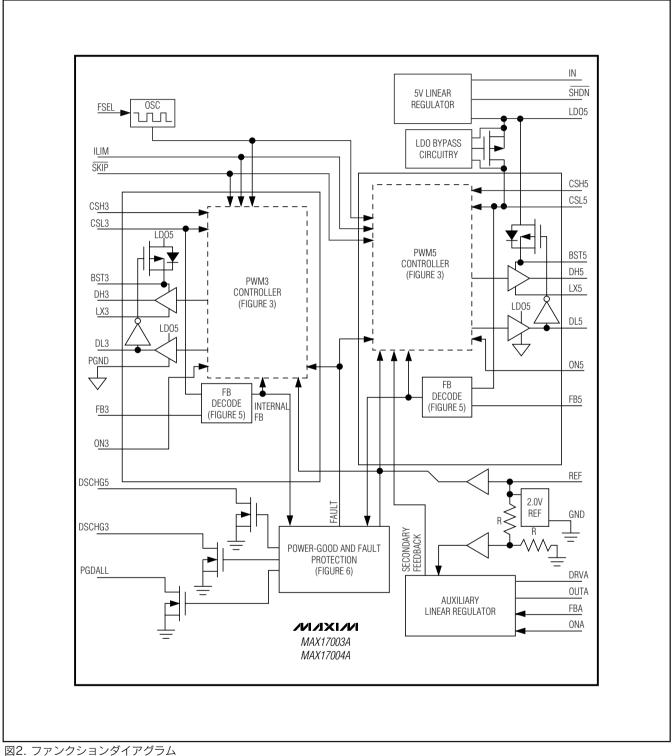

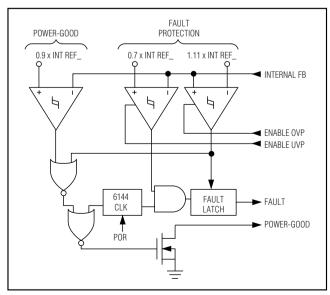

#### SMPSのPOR、UVLO、およびソフトスタート

パワーオンリセット(POR)はLDO5が約1Vを上回った時点で行われ、低電圧、過電圧、およびサーマルシャットダウンの各フォルトラッチがリセットされます。また、POR回路によって、SMPSコントローラが作動するまでローサイドドライバがハイに駆動されることも保証されます。図2に、MAX17003A/MAX17004Aのブロック図を示します。

LDO5の入力低電圧ロックアウト(UVLO)回路は、5Vバイアス電源(LDO5)が4VのUVLOスレッショルドを下回った場合にスイッチングを停止させます。5Vバイアス電源(LDO5)がこの入力UVLOスレッショルドを上回り、SMPSコントローラがイネーブル(ON\_がハイに駆動)された時点で、SMPSコントローラはスイッチングを開始して、ソフトスタートを使用した出力電圧の上昇が開始します。LDO5の電圧がUVLOスレッショルドを下回った

場合、コントローラはスイッチングを停止して、LDO5の電圧が回復するかまたはPORスレッショルドを下回るまで、ローサイドゲートドライバをローに駆動します。内蔵のソフトスタートは、フィードバック電圧を1V/msのスルーレートで徐々に上昇させます。そのため、出力が公称レギュレーション電圧に到達するのはSMPSコントローラのイネーブルから2ms後になります(「標準動作特性」の「SOFT-START WAVEFORM (ソフトスタートの波形)」を参照)。この緩やかなスルーレートによって出力コンデンサの充電に必要な電流( $I_{OUT} = I_{LOAD} + C_{OUT} \times V_{OUT(NOM)}/t_{SLEW}$ )が最小限に抑えられるため、入力サージ電流が効果的に低減されます。

#### SMPSイネーブル制御(ON3、ON5)

ON3およびON5は、SMPSのパワーアップシーケンスを制御します。ON3またはON5が2.4Vを上回った場合に、それぞれの出力がイネーブルされます。ON3またはON5が1.6Vを下回った場合に、それぞれの出力がディセーブルされます。ON\_を0.8V以下に駆動した場合、過電圧、低電圧、および熱フォルトのラッチがクリアされます。

#### SMPSのパワーアップシーケンス

ON3またはON5をREFに接続することによって、それぞれの出力はもう一方の出力がレギュレーションに到達するまで強制的にオフになり、その出力が安定化した後で動作を開始します。第2のSMPSは、第1のSMPSがオフになるか、デバイスがシャットダウンするか、フォルトが発生するか、またはLDO5がUVLOになるまでオンのままになります。第1の電源がオフになった場合、両方の電源が直ちにパワーダウンシーケンスを開始します。

18

#### 出力の放電(ソフト放電)

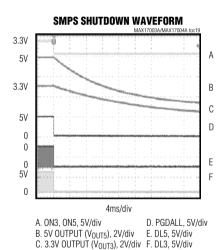

スイッチングレギュレータがディセーブルされた場合 (ON\_またはSHDNがローに駆動された場合、または出力低電圧フォルトが発生した場合)、内蔵のソフト放電がDSCHG\_をローに駆動することによって出力電圧を徐々に低下させます(「標準動作特性」の「SMPS SHUTDOWN WAVEFORM (SMPSシャットダウンの波形)」を参照)。これによって出力の静電容量がゆっくりと放電され、インダクタおよびローサイドMOSFETを通した急速な出力の放電によって生じる負の出力電圧が防止されます。両方のSMPSコントローラが個別のソフトシャットダウン回路を内蔵しています。

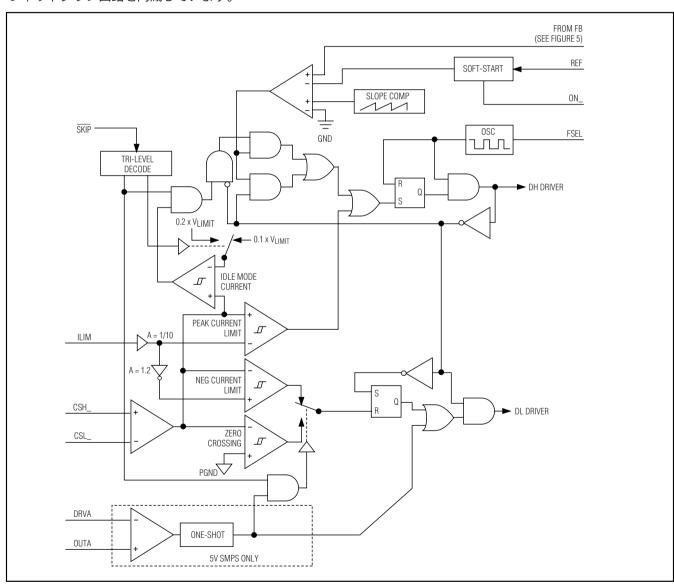

#### 固定周波数、電流モードPWMコントローラ

それぞれの電流モードPWMコントローラの中心部は、リファレンス電圧を基準とする出力電圧の誤差信号とスロープ補償ランプの2つの信号を加算する、マルチ入力、オープンループのコンパレータです(図3)。MAX17003A/MAX17004Aは直接加算構成を使用しており、従来のエラーアンプとそれに付随する位相シフトなしで、理想的なサイクル単位の制御に近い出力電圧の制御を行います。

図3. PWMコントローラのファンクションダイアグラム

#### 表4. FSELの設定の表

| FSEL | SWITCHING FREQUENCY (kHz) |

|------|---------------------------|

| LDO5 | 500                       |

| REF  | 300                       |

| GND  | 200                       |

#### 周波数の選択(FSEL)

FSEL入力で、PWMモードのスイッチング周波数を選択します。表4に、FSELの接続に基づくスイッチング周波数を示します。高周波(500kHz)の動作は、最小の部品サイズ向けにアプリケーションが最適化されますが、スイッチング損失が増大するため効率が低下します。負荷電流が小さいウルトラポータブル機器では、これが許容される場合があります。低周波(200kHz)の動作は、最高の全体的効率が提供されますが、部品サイズと基板スペースが犠牲になります。

#### 強制PWMモード

低ノイズの強制PWMモード(SKIP = LDO5)では、ローサイドスイッチのオン時間を制御するゼロクロスコンパレータがディセーブルされます。これによって、ローサイドのゲート駆動波形が常にハイサイドのゲート駆動波形の相補形に強制されるため、軽負荷時にはインダクタ電流が反転しますが、DH\_のデューティ比はVout/VINに維持されます。強制PWMモードの利点は、スイッチング周波数がほぼ一定に保たれることです。しかし強制PWM動作の欠点として、外付けMOSFETおよびスイッチング周波数に応じて無負荷時にも5Vの消費電流が20mA~50mAのままになります。

強制PWMモードは、オーディオ周波数ノイズの防止と 負荷過渡応答の改善にとって非常に有効です。強制 PWM動作ではゼロクロスコンパレータがディセーブル されるため、軽負荷時にはインダクタ電流が反転します。

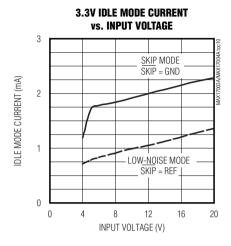

#### 軽負荷時の動作の制御 (SKIP)

MAX17003A/MAX17004Aは軽負荷時の動作モードの制御入力(SKIP)を備えており、両方のスイッチングレギュレータのゼロクロスコンパレータのイネーブルまたはディセーブルに使用します。ゼロクロスコンパレータがイネーブルされている場合、インダクタ電流が0であることを電流検出入力が検出した時点でレギュレータはDL\_をローに強制します。これによって、インダクタは出力コンデンサの放電を行わず、軽負荷状態でレギュレータにパルスのスキップを強制して出力の過充電を防止します。ゼロクロスコンパレータがディセーブルされている場合、レギュレータは軽負荷状態でもPWM動作を維持するように強制されます(強制PWM)。

#### アイドルモード電流検出スレッショルド

パルススキップモードがイネーブルされている場合、 出力電圧がフィードバックスレッショルドを超えた時 点、および電流検出電圧がアイドルモード電流検出ス レッショルドを超えた時点で、ステップダウンコート ローラのオン時間が終了します。軽負荷状態でのオン 時間の長さは、ILIMで設定される全負荷時の電流制限 スレッショルドの20% (SKIP = GND)に相当するアイ ドルモード電流検出スレッショルド、またはILIMで設 定される全負荷時の電流制限スレッショルドの10% (SKIP = REF)に相当する低ノイズ電流検出スレッショ ルドのみに依存します。これによって、コントローラは 各サイクルで最小限の電力を供給します。出力の過充 電を防止するために、出力電圧がフィードバックスレッ ショルドを下回るまで次のオン時間を開始することは できません。ゼロクロスコンパレータによってスイッ チングレギュレータの電流シンクが防止されるため、 コントローラはパルスをスキップする必要があります。 したがって、コントローラは軽負荷状態では出力リッ プルの谷を安定化することになります。

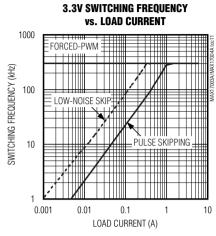

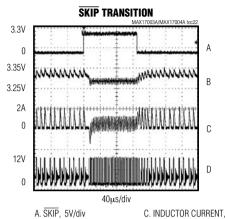

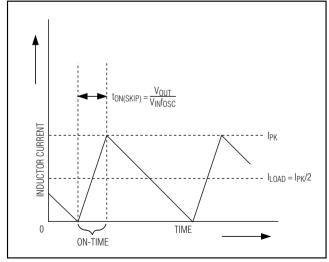

#### 自動パルススキップのクロスオーバー

スキップモードでは、軽負荷時にPFMへの固有の自動切替えが行われます(図4)。この切替えは、インダクタ電流のゼロクロスでローサイドスイッチのオン時間を終了させるコンパレータの影響を受けます。ゼロクロスコンパレータは、CSH\_とCSL\_間のインダクタ電流を検出します。VCSH\_・VCSL\_がゼロクロス電流検出スレッショルドの3mVを下回った時点で、コンパレータはDL\_をローに強制します(図3)。この仕組みによって、パルススキップPFMと非スキップPWM動作の間のスレッショルドは、連続と不連続のインダクタ電流動作の境界(別名「臨界動作」点)と一致します。PFM/PWMのクロス

図4. パルススキップ/不連続クロスオーバーポイント

オーバーが発生する負荷電流レベル $I_{LOAD(SKIP)}$ は、次式で与えられます。

$$I_{LOAD(SKIP)} = \frac{(V_{IN} - V_{OUT})V_{OUT}}{2V_{IN}I_{OSC}L}$$

軽負荷によってパルススキップ動作に移行した場合、スイッチング波形のノイズが増えて非同期のように見える可能性がありますが、これは正常な動作状態であり、結果として軽負荷時に高効率が実現されます。PFMのノイズと軽負荷時の効率の間のトレードオフは、インダクタの値を変えることによって調整します。一般に、インダクタの値が小さい場合は効率と負荷の関係を示す曲線がなだらかになり、インダクタの値が大きい場合は、全負荷時の効率が高くなり(コイルの抵抗は一定と仮定)、出力電圧リップルが減少します。大きい値のインダクタを使用するデメリットとして、物理サイズの増大および(特に低い入力電圧レベルにおける)負荷過渡応答の劣化があります。

#### 出力電圧

「ELECTRICAL CHARACTERISTICS」の表のDC出力精度の仕様は、エラーコンパレータのスレッショルドを基準としています。インダクタが連続的に導通している場合、MAX17003A/MAX17004Aは出力リップルのピークを安定化するため、実際のDC出力電圧は出力リップル電圧の50%だけスロープ補償後のトリップレベルより低くなります。PWM動作(連続動作)の場合、出力電圧は次式によって正確に定義されます。

$$V_{OUT(PWM)} = V_{NOM} \left(1 - \frac{A_{SLOPE}V_{RIPPLE}}{V_{IN}}\right) - \left(\frac{V_{RIPPLE}}{2}\right)$$

ここで、 $V_{NOM}$ は公称出力電圧、 $A_{SLOPE}$ は1.1%、 $V_{RIPPLE}$ は出力リップル電圧です(「出力コンデンサの選択」の項で説明するように、 $V_{RIPPLE}$  =  $ESR \times \Delta I_{INDUC-TOR}$ です)。

不連続動作 (I<sub>OUT</sub> < I<sub>LOAD (SKIP)</sub>) の場合、MAX17003A/MAX17004Aは出力リップルの谷を安定化するため、出力電圧のDCレギュレーションレベルはエラーコンパレータのスレッショルドより高くなります。PFM動作(不連続導通)の場合、出力電圧は次式によって近似的に定義されます。

$$V_{OUT(PFM)} = V_{NOM} + \frac{1}{2} \left( \frac{f_{SW}}{f_{OSC}} \right) I_{IDLE} ESR$$

ここで、 $V_{NOM}$ は公称出力電圧、 $f_{OSC}$ は内蔵発振器によって設定された最大スイッチング周波数、 $f_{SW}$ は実際のスイッチング周波数、 $I_{IDLE}$ はパルススキップ時におけるアイドルモードのインダクタ電流です。

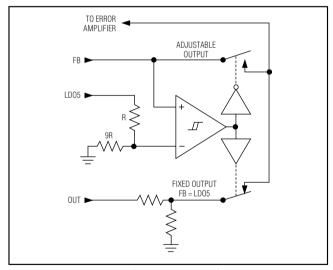

出力(CSL\_)とアナロググランドの間に接続されている プリセットの内蔵抵抗分圧器によって設定される固定 のSMPS出力電圧(それぞれ3.3Vおよび5V)を有効にする場合は、FB3およびFB5をLD05に接続してください。それぞれの出力電圧を2V~5.5Vの範囲で調整する場合は、出力(CSL\_)とGNDの間に接続した抵抗分圧器にFB\_を接続してください(図5)。 $R_{FBLO}$  (FBからGNDまでの抵抗)として約10k $\Omega$ を選択して、次式を使用して $R_{FBHI}$  (出力からFBまでの抵抗)を求めてください。

$$R_{FBHI} = R_{FBLO} \left( \frac{V_{OUT}}{V_{FB}} - 1 \right)$$

ここで、 $V_{FB} = 2V$  (公称)です。

両方の出力電圧を調整する場合、3.3V SMPSを5V SMPSよりも低い値に設定してください。CSL5が LDO5のブートストラップスレッショルド(4.5V)を上回り、CSL5側のソフトスタートシーケンスが完了している場合にのみ、LDO5は内部スイッチを介して5V出力(CSL5)に接続されます。ブートストラップは、固定の出力電圧を使用する場合に最も有効に機能します。CSL5からLDO5のブートストラップが行われた時点で、内蔵の5Vリニアレギュレータがオフになります。これによって内部の電力消費が低減され、高い入力電圧での効率が向上します。

図5. Dual Modeフィードバックデコーダ

#### 電流制限保護(ILIM)

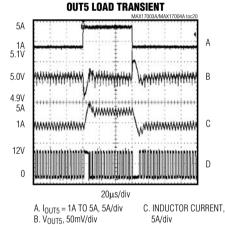

電流制限回路は、差動電流検出入力(CSH\_およびCSL\_)を使用してピークインダクタ電流を制限します。電流検出信号の大きさが電流制限スレッショルドを超えた場合、PWMコントローラはハイサイドのMOSFETをオフにします(図3)。実際の最大負荷電流は、インダクタのリップル電流の半分の量だけピーク電流制限スレッショルドより小さくなります。そのため、最大負荷能力は、電流検出抵抗値、インダクタ値、スイッチング

周波数、およびデューティサイクル( $V_{OUT}/V_{IN}$ )の関数になります。

強制PWMモードでは、 $V_{OUT}$ が電流をシンクしている場合に過度の逆インダクタ電流を防止するために、MAX17003A/MAX17004Aは負の電流制限も実行します。負の電流制限スレッショルドは正の電流制限値の約120%に設定され、ILIMを調整した場合は正の電流制限値に追従します。

ILIMをLDO5に接続してデフォルトのスレッショルドの 50 mVを使用するか、またはILIMに外付けの抵抗分圧器 を接続して電流制限スレッショルドを調整してください。精度およびノイズ耐性のために、分圧器の電流は  $2 \mu \text{A} \sim 20 \mu \text{A}$ を使用してください。電流制限スレッショルドの調整範囲は、 $50 \text{mV} \sim 200 \text{mV}$ です。可変モードの場合、電流制限スレッショルド電圧は正確にILIMの電圧の1/10に等しくなります。デフォルト値への切替えのロジックスレッショルドは、約 $V_{\text{LDO5}}$  - 1Vです。

ノイズとDC誤差によるCSH\_とCSL\_での差動電流検出信号の劣化がないことを保証するため、PCBレイアウトのガイドラインを十分に遵守してください。ICは短い直接的な配線を使用して検出抵抗の近くに配置して、電流検出抵抗にケルビン接続を行ってください。

#### MOSFETゲートドライバ(DH\_、DL\_)