## MAX16928

# 車載用TFT LCD電源、ブーストコンバータ およびゲート電圧レギュレータ内蔵

### 概要

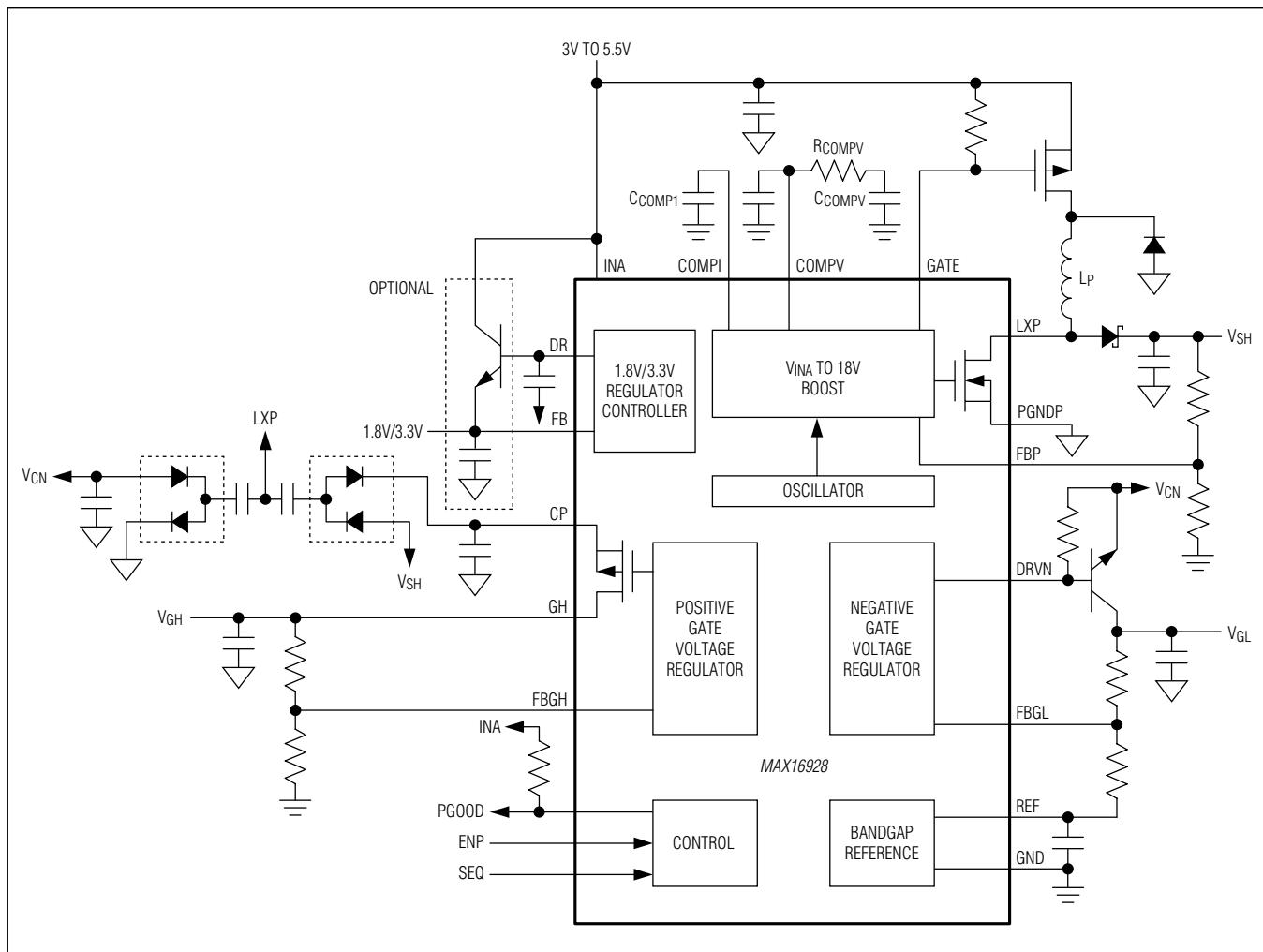

MAX16928は、車載TFT LCDアプリケーション用の高集積電源です。このデバイスは、1つのブーストコンバータ、1つの1.8V/3.3Vレギュレータコントローラ、および2つのゲート電圧レギュレータを内蔵しています。このデバイスは、共通の車載TFT LCD電源要件を満たす複数のバージョンで提供されます(「[型番](#)」の表を参照)。

ブーストコンバータは、スペクトラム拡散変調を使用し、ピーク干渉を低減してEMI性能を最適化します。シーケンス入力(SEQ)によって、正ゲートと負ゲート電圧レギュレータのフレキシブルなシーケンスが可能です。パワーグッドインジケータ(PGOOD)は、任意のコンバータまたはレギュレータ出力における障害を表示します。内蔵サーマルシャットダウン回路は、デバイスを温度過昇から保護します。

MAX16928は、エクスポートドパッドを備えた20ピンTSSOPパッケージで提供され、-40°C～+105°Cの温度範囲で動作します。

### アプリケーション

車載ダッシュボード

車載セントラルインフォメーションディスプレイ

車載用ナビゲーションシステム

### 特長

- ◆ 最大18Vを供給する高出力(最大6W)ブースト出力

- ◆ 1.8Vまたは3.3Vレギュレータは外付けのnpnトランジスタで500mAを供給

- ◆ 1つの正ゲート電圧レギュレータは28Vで20mAを供給可能

- ◆ 1つの負ゲート電圧レギュレータ

- ◆ 2.2MHzの高周波数動作

- ◆ フレキシブルなスタンダロンシーケンス

- ◆ True Shutdown™ ブーストコンバータ

- ◆ ソフトスタート内蔵

- ◆ 温度過昇シャットダウン

- ◆ 動作温度：-40°C～+105°C

- ◆ AEC-Q100認定

[型番](#)はデータシートの最後に記載されています。

[標準動作回路](#)はデータシートの最後に記載されています。

True ShutdownはMaxim Integrated Products, Inc.の商標です。

関連部品およびこの製品とともに使用可能な推奨製品については、[japan.maximintegrated.com/MAX16928.related](http://japan.maximintegrated.com/MAX16928.related)を参照してください。

本データシートは日本語翻訳であり、相違及び誤りのある可能性があります。設計の際は英語版データシートを参照してください。

価格、納期、発注情報についてはMaxim Direct (0120-551056)にお問い合わせいただくか、Maximのウェブサイト([japan.maximintegrated.com](http://japan.maximintegrated.com))をご覧ください。

# 車載用TFT LCD電源、ブーストコンバータ およびゲート電圧レギュレータ内蔵

## ABSOLUTE MAXIMUM RATINGS

|                                                          |                                      |                                                                    |                 |

|----------------------------------------------------------|--------------------------------------|--------------------------------------------------------------------|-----------------|

| INA, COMPV, FBP to GND                                   | -0.3V to +6V                         | GND to PGNDP                                                       | -0.3V to +0.3V  |

| PGOOD to GND                                             | -0.3V to +6V                         | Continuous Power Dissipation ( $T_A = +70^\circ\text{C}$ )         |                 |

| CP, GH to GND                                            | -0.3V to +31V                        | TSSOP (derate 26.5mW/ $^\circ\text{C}$ above $+70^\circ\text{C}$ ) | 2122mW          |

| CP, GH to GND ( $V_{INA} = 3.3\text{V}$ )                | -0.3V to +29V                        | Operating Temperature Range                                        | -40°C to +105°C |

| LXP to GND                                               | -0.3V to +20V                        | Junction Temperature Range                                         | -40°C to +150°C |

| DRVN to GND                                              | -25V to +0.3V                        | Storage Temperature Range                                          | -65°C to +150°C |

| ENP, DR, FB, GATE, COMPI, FBGH,<br>FBGL, REF, SEQ to GND | -0.3V to ( $V_{INA} + 0.3\text{V}$ ) | Lead Temperature (soldering, 10s)                                  | +300°C          |

|                                                          |                                      | Soldering Temperature (reflow)                                     | +260°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## PACKAGE THERMAL CHARACTERISTICS (Note 1)

### TSSOP

|                                                          |       |          |

|----------------------------------------------------------|-------|----------|

| Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) | ..... | 37.7°C/W |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )    | ..... | 2°C/W    |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to [japan.maximintegrated.com/thermal-tutorial](http://japan.maximintegrated.com/thermal-tutorial).

## ELECTRICAL CHARACTERISTICS

( $V_{INA} = 5\text{V}$ ,  $V_{GND} = V_{PGNDP} = 0\text{V}$ ,  $T_A = T_J = -40^\circ\text{C}$  to  $+105^\circ\text{C}$ , typical values are at  $T_A = +25^\circ\text{C}$  unless otherwise noted.) (Note 2)

| PARAMETER                                                        | SYMBOL     | CONDITIONS                                                                         | MIN   | TYP  | MAX   | UNITS         |

|------------------------------------------------------------------|------------|------------------------------------------------------------------------------------|-------|------|-------|---------------|

| <b>BOOST, POSITIVE (GH), NEGATIVE (GL), 1.8V/3.3V CONVERTERS</b> |            |                                                                                    |       |      |       |               |

| INA Input Supply Range                                           |            |                                                                                    | 3     | 5.5  |       | V             |

| INA Undervoltage Lockout Threshold                               |            | $V_{INA}$ rising, hysteresis = 200mV,<br>$T_A = +25^\circ\text{C}$                 | 2.5   | 2.7  | 2.9   | V             |

| INA Supply Current                                               | $I_{INA}$  | $V_{FBP} = V_{FBGH} = 1.3\text{V}$ , $V_{FBGL} = 0\text{V}$ ,<br>LXP not switching |       | 1.5  | 2.0   | mA            |

| INA Shutdown Current                                             | $I_{SHDN}$ | $V_{ENP} = 0\text{V}$ , $T_A = +25^\circ\text{C}$                                  |       | 0.5  |       | $\mu\text{A}$ |

| Thermal Shutdown Temperature                                     | $T_{SHDN}$ | Temperature rising                                                                 |       | +165 |       | °C            |

| Thermal Shutdown Hysteresis                                      | $T_H$      |                                                                                    |       | 15   |       | °C            |

| Duration to Trigger Fault Condition                              |            | $V_{FBP}$ , $V_{FBGH}$ , or $V_{FBGL}$ below its threshold                         |       | 238  |       | ms            |

| Autoretry Time                                                   |            |                                                                                    |       | 1.9  |       | s             |

| <b>REFERENCE (REF)</b>                                           |            |                                                                                    |       |      |       |               |

| REF Output Voltage                                               | $V_{REF}$  | No output current                                                                  | 1.236 | 1.25 | 1.264 | V             |

| REF Load Regulation                                              |            | $0 < I_{REF} < 80\mu\text{A}$ , REF sourcing                                       | -2    | +2   |       | %             |

| REF Undervoltage Lockout Threshold                               |            | Rising edge, hysteresis = 200mV                                                    |       |      | 1.165 | V             |

| <b>OSCILLATOR</b>                                                |            |                                                                                    |       |      |       |               |

| Spread-Spectrum Factor                                           | SSR        | As a percentage of switching frequency,<br>$f_{SW}$                                |       | ±4   |       | %             |

# 車載用TFT LCD電源、ブーストコンバータ およびゲート電圧レギュレータ内蔵

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{INA} = 5V$ ,  $V_{GND} = V_{PGNDP} = 0V$ ,  $T_A = T_J = -40^\circ C$  to  $+105^\circ C$ , typical values are at  $T_A = +25^\circ C$  unless otherwise noted.) (Note 2)

| PARAMETER                                   | SYMBOL            | CONDITIONS                                                                    | MIN                                   | TYP   | MAX     | UNITS            |   |

|---------------------------------------------|-------------------|-------------------------------------------------------------------------------|---------------------------------------|-------|---------|------------------|---|

| <b>BOOST CONVERTER</b>                      |                   |                                                                               |                                       |       |         |                  |   |

| Switching Frequency                         | $f_{SW}$          |                                                                               | 1.98                                  | 2.20  | 2.42    | MHz              |   |

| Maximum Duty Cycle                          |                   |                                                                               | 82                                    |       | 93.5    | %                |   |

| LXP Current Limit                           | $I_{LIM}$         | Duty cycle = 70%,<br>$C_{COMPI} = 220\text{pF}$                               | Low boost current-limit option        | 0.625 | 0.78    | A                |   |

|                                             |                   |                                                                               | High boost current-limit option       | 1.25  | 1.56    | 1.87             |   |

| LXP On-Resistance                           | $R_{DS\_ON(LXP)}$ | $I_{LXP} = 200\text{mA}$                                                      |                                       | 110   | 250     | $\text{m}\Omega$ |   |

| LXP Leakage Current                         | $I_{LK\_LXP}$     | $V_{LXP} = 20V$ , $T_A = +25^\circ C$                                         |                                       | 8.5   | 20      | $\mu\text{A}$    |   |

| Soft-Start Time                             |                   | (Note 3)                                                                      |                                       | 30    |         | ms               |   |

| Output Voltage Range                        | $V_{SH}$          |                                                                               | $V_{INA}$                             |       | 18      | V                |   |

| FBP Regulation Voltage                      | $V_{FBP}$         | $V_{INA} = +3V$ to $+5.5V$ ,<br>$0 < I_{LOAD} <$ full load                    | $T_A = +25^\circ C$                   | 0.985 | 1.0     | 1.015            | V |

|                                             |                   |                                                                               | $T_A = -40^\circ C$ to $+105^\circ C$ | 0.98  | 1.0     | 1.02             |   |

| PGOOD Threshold                             | $V_{PG\_FBP}$     | Measured at FBP                                                               |                                       | 0.74  | 0.85    | 0.96             | V |

| FBP Load Regulation                         |                   | $0 < I_{LOAD} <$ full load                                                    |                                       | -1    |         | %                |   |

| FBP Line Regulation                         |                   | $V_{INA} = +3V$ to $+5.5V$                                                    |                                       | 0.1   |         | %/V              |   |

| FBP Input Bias Current                      |                   | $V_{FBP} = +1V$ , $T_A = +25^\circ C$                                         |                                       |       | $\pm 1$ | $\mu\text{A}$    |   |

| FBP to COMPV<br>Transconductance            |                   | $\Delta I = \pm 2.5\mu\text{A}$ at COMPV, $T_A = +25^\circ C$                 |                                       | 400   |         | $\mu\text{S}$    |   |

| <b>POSITIVE-GATE VOLTAGE REGULATOR (GH)</b> |                   |                                                                               |                                       |       |         |                  |   |

| Output Voltage Range                        | $V_{GH}$          | With external charge pump, $T_A = +25^\circ C$<br>(maximum $V_{CP} = 29.5V$ ) | 5                                     |       | 29      | V                |   |

| CP Overvoltage Threshold                    |                   | $T_A = +25^\circ C$ (Note 4)                                                  | 29.5                                  | 30.5  |         | V                |   |

| FBGH Regulation Voltage                     | $V_{FBGH}$        | $I_{GH} = 1\text{mA}$                                                         | 0.96                                  | 1.0   | 1.034   | V                |   |

| PGOOD Threshold                             | $V_{PG\_FBGH}$    | Measured at FBGH                                                              | 0.83                                  | 0.85  | 0.87    | V                |   |

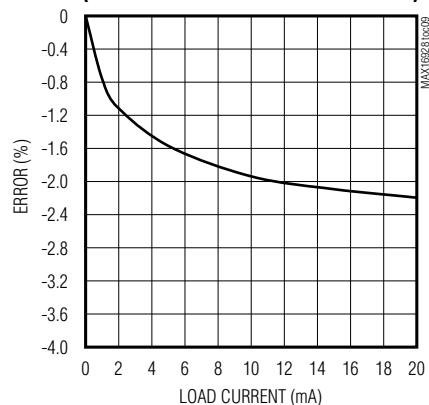

| FBGH Load Regulation                        |                   | $I_{GH} = 0$ to $20\text{mA}$                                                 |                                       | 2     |         | %                |   |

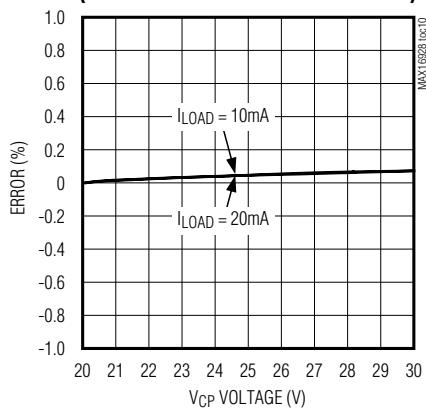

| FBGH Line Regulation                        |                   | $V_{CP} = 12V$ to $20V$ at $V_{GH} = 10V$ ,<br>$I_{GH} = 10\text{mA}$         |                                       | 2     |         | %                |   |

| FBGH Input Bias Current                     |                   | $V_{FBGH} = 1V$ , $T_A = +25^\circ C$                                         |                                       |       | $\pm 1$ | $\mu\text{A}$    |   |

| GH Output Current                           | $I_{GH}$          | $V_{CP} - V_{GH} = 2V$                                                        | 20                                    |       |         | $\text{mA}$      |   |

| GH Current Limit                            | $I_{LIM\_GH}$     |                                                                               | 35                                    | 56    |         | $\text{mA}$      |   |

| GH Soft-Start Time                          |                   |                                                                               |                                       | 7.45  |         | ms               |   |

| <b>NEGATIVE-GATE VOLTAGE REGULATOR (GL)</b> |                   |                                                                               |                                       |       |         |                  |   |

| Output Voltage Range                        | $V_{DRVN}$        |                                                                               | -24                                   |       | -2      | V                |   |

| FBGL Regulation Voltage                     | $V_{FBGL}$        | $I_{DRVN} = 100\mu\text{A}$                                                   | 0.212                                 | 0.242 | 0.271   | V                |   |

| PGOOD Threshold                             | $V_{PG\_FBGL}$    | Measured at FBGL                                                              | 0.38                                  | 0.4   | 0.42    | V                |   |

# 車載用TFT LCD電源、ブーストコンバータ およびゲート電圧レギュレータ内蔵

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{INA} = 5V$ ,  $V_{GND} = V_{PGNDP} = 0V$ ,  $T_A = T_J = -40^\circ C$  to  $+105^\circ C$ , typical values are at  $T_A = +25^\circ C$  unless otherwise noted.) (Note 2)

| PARAMETER                              | SYMBOL       | CONDITIONS                                                                        | MIN                                 | TYP   | MAX                  | UNITS     |

|----------------------------------------|--------------|-----------------------------------------------------------------------------------|-------------------------------------|-------|----------------------|-----------|

| FBGL Input Bias Current                |              | $V_{FBGL} = +0.25V$                                                               |                                     |       | $\pm 1$              | $\mu A$   |

| DRVN Source Current                    |              | $V_{FBGL} = +0.5V$ , $V_{DRVN} = -10V$                                            | 2                                   |       |                      | $mA$      |

| DRVN Source Current Limit              |              |                                                                                   | 2.5                                 | 4     |                      | $mA$      |

| GL Soft-Start Time                     |              |                                                                                   |                                     | 7.45  |                      | $ms$      |

| <b>1.8V/3.3V REGULATOR CONTROLLER</b>  |              |                                                                                   |                                     |       |                      |           |

| Output Voltage                         | $V_{FB}$     | $V_{DR} = V_{FB}$                                                                 | 3.3V regulator option               | 3.18  | 3.3                  | 3.38      |

|                                        |              |                                                                                   | 1.8V regulator option               | 1.746 | 1.8                  | 1.854     |

| FB PGOOD Threshold                     | $V_{PG\_FB}$ | Measured at FB<br>(Notes 4, 6)                                                    | 3.3V regulator option,<br>FB rising | 2.4   | 2.57                 | 2.7       |

|                                        |              |                                                                                   | 1.8V regulator option,<br>FB rising | 1.364 | 1.38                 | 1.396     |

| FB Input Bias Current                  |              | $V_{FB} = 1.8V$                                                                   |                                     | 2.5   |                      |           |

|                                        |              | $V_{FB} = 3.3V$                                                                   |                                     | 4.5   |                      |           |

| DR Drive Current                       |              | $V_{FB} = 1.8V$                                                                   | 4.5                                 | 6     |                      | $mA$      |

| <b>INPUT SERIES SWITCH CONTROL</b>     |              |                                                                                   |                                     |       |                      |           |

| p-Channel FET GATE Sink Current        |              | $V_{GATE} = 0.5V$                                                                 | 33                                  | 55    | 75                   | $\mu A$   |

| GATE Voltage Threshold                 |              | Measured at GATE; below this voltage, the external p-channel FET is considered on |                                     | 1.25  |                      | $V$       |

| <b>DIGITAL LOGIC</b>                   |              |                                                                                   |                                     |       |                      |           |

| ENP, SEQ Input Pulldown Resistor Value | $R_{PD}$     |                                                                                   |                                     | 500   |                      | $k\Omega$ |

| ENP, SEQ Input-Voltage Low             | $V_{IL}$     |                                                                                   |                                     |       | $0.3 \times V_{INA}$ | $V$       |

| ENP, SEQ Input-Voltage High            | $V_{IH}$     |                                                                                   |                                     |       | $0.7 \times V_{INA}$ | $V$       |

| PGOOD Leakage Current                  | $I_{LK\_IN}$ | $T_A = +25^\circ C$                                                               |                                     |       | $\pm 1$              | $\mu A$   |

| PGOOD Output-Voltage Low               | $V_{OL}$     | 2mA sink current, $T_A = +25^\circ C$                                             |                                     | 0.4   |                      | $V$       |

**Note 2:** Specifications over temperature are guaranteed by design and not production tested.

**Note 3:** 50% of the soft-start voltage time is due to the soft-start ramp and the other 50% is due to the settling of the output voltage.

**Note 4:** After the voltage at CP exceeds this overvoltage threshold, the entire circuit switches off and autoretry is started.

**Note 5:** Guaranteed by design; not production tested.

**Note 6:** FB power good is indicated by PGOOD. The condition  $V_{FB} < V_{PG\_FB}$  does not shut down/restart the device.

# 車載用TFT LCD電源、ブーストコンバータ およびゲート電圧レギュレータ内蔵

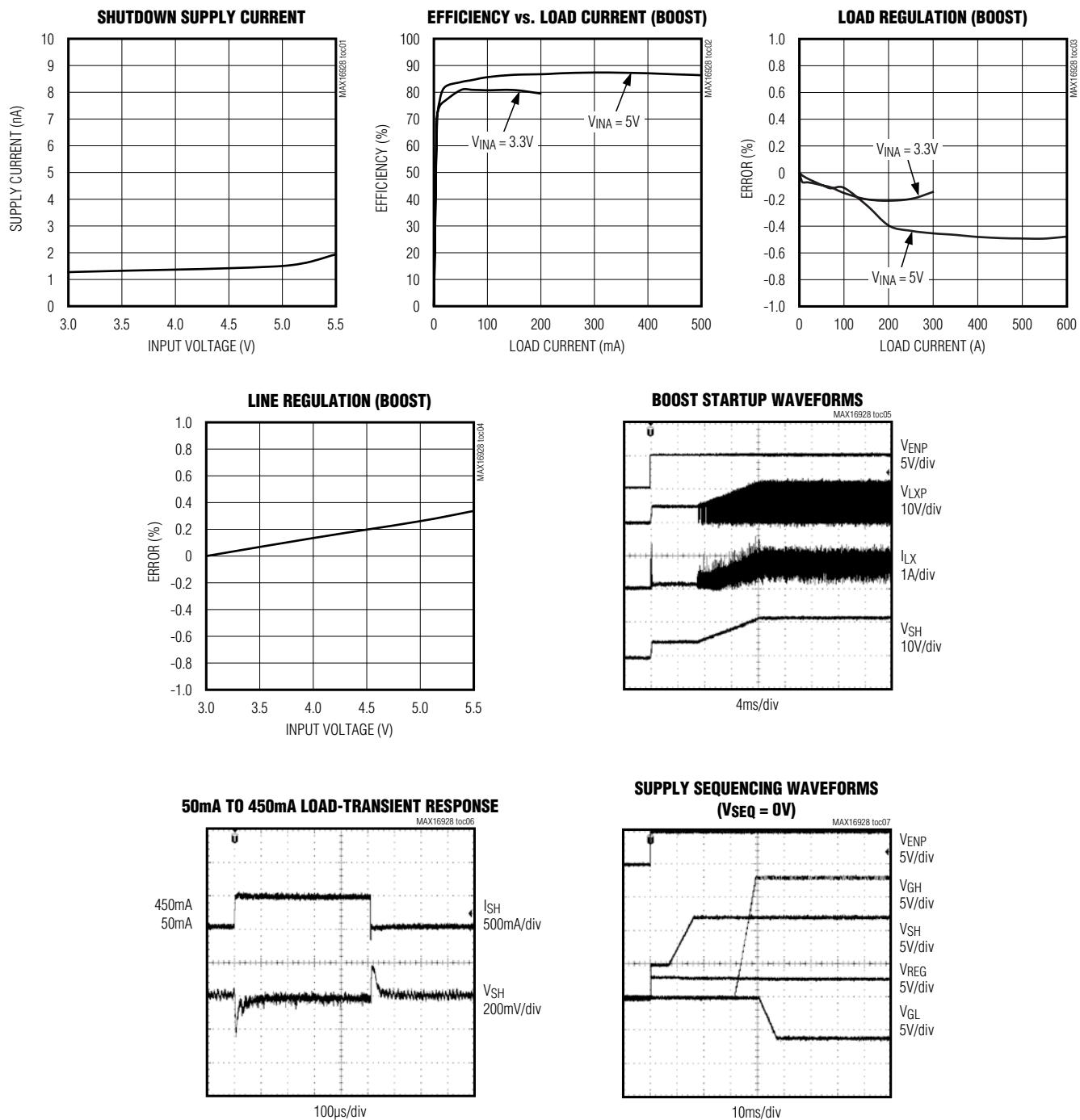

## 標準動作特性

( $V_{INA} = +5V$ ,  $V_{SH} = +12V$ ,  $V_{GH} = +18V$ ,  $V_{GL} = -6V$ ,  $V_{REG} = 3.3V$ ,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted.)

# 車載用TFT LCD電源、ブーストコンバータ およびゲート電圧レギュレータ内蔵

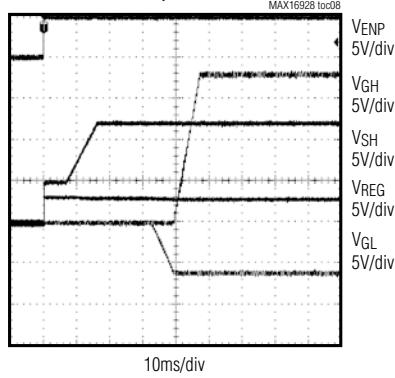

## 標準動作特性(続き)

( $V_{INA} = +5V$ ,  $V_{SH} = +12V$ ,  $V_{GH} = +18V$ ,  $V_{GL} = -6V$ ,  $V_{REG} = 3.3V$ ,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted.)

**SUPPLY SEQUENCING WAVEFORMS**

( $V_{SEQ} = V_{INA}$ )

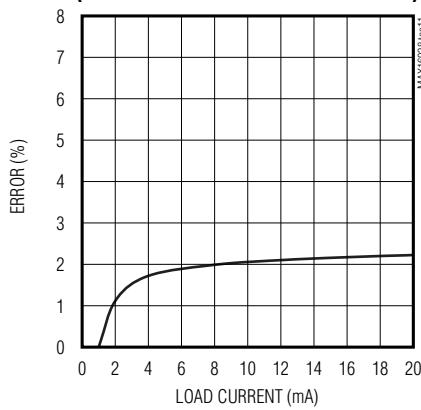

**LOAD REGULATION**

(POSITIVE-GATE VOLTAGE REGULATOR)

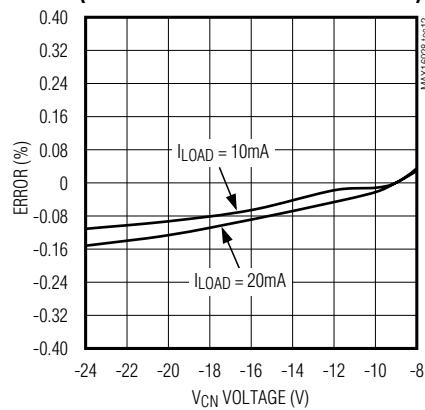

**LINE REGULATION**

(POSITIVE-GATE VOLTAGE REGULATOR)

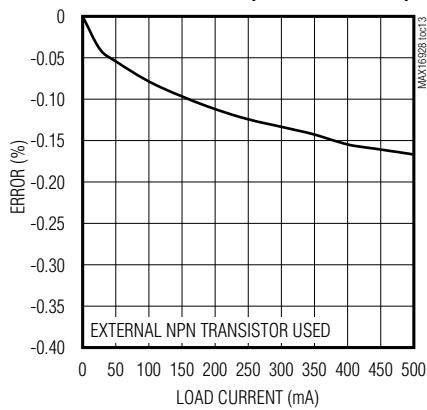

**LOAD REGULATION**

(NEGATIVE-GATE VOLTAGE REGULATOR)

**LINE REGULATION**

(NEGATIVE-GATE VOLTAGE REGULATOR)

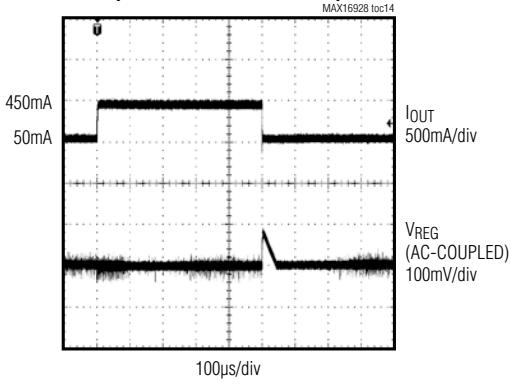

**LOAD REGULATION (3.3V REGULATOR)**

**LOAD-TRANSIENT RESPONSE**

(3.3V LINEAR REGULATOR)

# 車載用TFT LCD電源、ブーストコンバータ およびゲート電圧レギュレータ内蔵

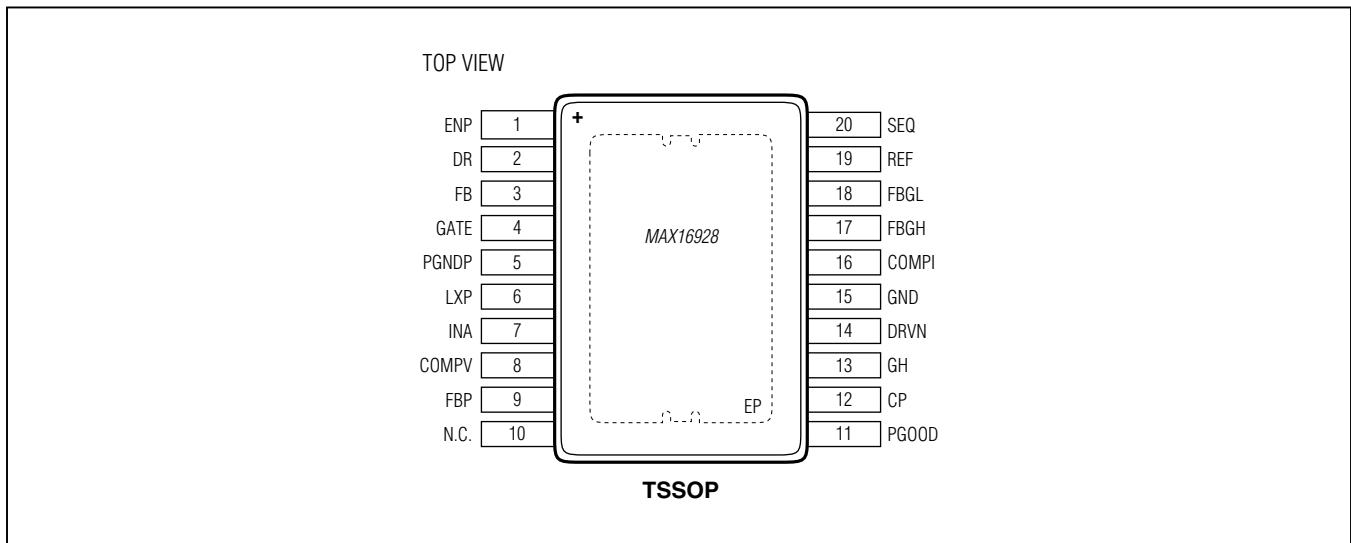

## ピン配置

## 端子説明

| 端子 | 名称    | 機能                                                                                                                                                       |

|----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | ENP   | ブースト回路および1.8V/3.3Vレギュレータコントローラのイネーブル入力。ENPは500kΩのブルダウン抵抗を内蔵しています。通常動作の場合はハイに駆動し、デバイスをシャットダウンするにはローに駆動してください。                                             |

| 2  | DR    | 1.8Vまたは3.3Vレギュレータの出力。DRは4.5mA (min)の駆動能力があります。より大きい出力電流能力を実現するには、外付けのnpnバイポーラトランジスタを使用して、そのベースをDRに接続してください。                                              |

| 3  | FB    | 1.8Vまたは3.3Vレギュレータのフィードバック入力。FBは1.8Vまたは3.3Vに安定化されます。4.5mA以下を必要とする負荷に給電する場合は、FBをDRに接続してください。より大きい出力電流能力を実現するには、外付けのnpnバイポーラトランジスタを使用して、そのエミッタをFBに接続してください。 |

| 4  | GATE  | 外部pチャネルFETのゲート駆動。GATEはオープンドレインのドライバで、外付けの入力直列pチャネルFETのゲートに接続します。GATEとINA間にプルアップ抵抗を接続してください。フォルト状態時、ゲートドライバはオフになり、プルアップ抵抗によってFETがオフになります。                 |

| 5  | PGNDP | ブーストコンバータのパワーグランド                                                                                                                                        |

| 6  | LXP   | ブーストコンバータのスイッチング端子。LXPをブーストコンバータのインダクタおよびキャッチダイオードに接続してください。                                                                                             |

| 7  | INA   | ブースト回路および1.8V/3.3Vレギュレータコントローラの電源入力。INAを3V~5.5Vの電源に接続してください。                                                                                             |

| 8  | COMPV | ブーストエラーアンプ補償接続。COMPVとGND間に補償回路を接続してください。                                                                                                                 |

| 9  | FBP   | ブーストコンバータのフィードバック入力。FBPは1Vに安定化されます。FBPをブースト出力とGND間に接続された抵抗分圧器のセンターに接続してください。                                                                             |

| 10 | N.C.  | 接続なし。内部で接続されていません。                                                                                                                                       |

| 11 | PGOOD | オープンドレインのパワーグッド出力。外付けのプルアップ抵抗を介してPGOODをINAに接続してください。                                                                                                     |

| 12 | CP    | 正のゲート電圧レギュレータの電源入力。CPを外付けチャージポンプの正の出力に接続してください。 $V_{cp}$ が「Electrical Characteristics (電気的特性)」の表に記載されたCPの過電圧閾値を超えないようにしてください。                            |

# 車載用TFT LCD電源、ブーストコンバータ およびゲート電圧レギュレータ内蔵

## 端子説明(続き)

| 端子 | 名称    | 機能                                                                                                                          |

|----|-------|-----------------------------------------------------------------------------------------------------------------------------|

| 13 | GH    | 正のゲート電圧レギュレータの出力                                                                                                            |

| 14 | DRVN  | 負のゲート電圧レギュレータのドライバ出力。DRVNは内蔵pチャネルFETのオープンドレインです。DRVNを外付けnnpnパストランジスタのベースに接続してください。                                          |

| 15 | GND   | アナロググランド                                                                                                                    |

| 16 | COMPI | ブーストスロープ補償接続。COMPIとGND間にコンデンサを接続してスロープ補償を設定してください。                                                                          |

| 17 | FBGH  | 正のゲート電圧レギュレータのフィードバック入力。FBGHは1Vに安定化されます。FBGHをGHとGND間に接続された抵抗分圧器のセンターに接続してください。                                              |

| 18 | FBGL  | 負のゲート電圧レギュレータのフィードバック入力。FBGLは0.25Vに安定化されます。FBGLをREFと負のゲート電圧レギュレータの出力間に接続された抵抗分圧器のセンターに接続してください。                             |

| 19 | REF   | 1.25Vリファレンス出力。0.1μFのセラミックコンデンサでREFをGNDに接続してください。                                                                            |

| 20 | SEQ   | シーケンシング入力。SEQは500kΩのプルダウン抵抗を内蔵しています。SEQは、V <sub>GH</sub> およびV <sub>GL</sub> が起動する順序を決定します。電源シーケンシングのオプションについては、表1を参照してください。 |

| —  | EP    | エクスポートドパッド。放熱を最適化するために、連続した大面積の銅グランドプレーンに接続してください。EPを唯一の電気的グランド接続として使用しないでください。                                             |

## 詳細

MAX16928は、車載TFT LCDアプリケーション用の高集積電源です。このデバイスは、1つのブーストコンバータ、1つの1.8V/3.3Vレギュレータコントローラ、1つの正のゲート電圧レギュレータ、および1つの負のゲート電圧レギュレータを内蔵しています。

このデバイスは、スペクトラム拡散変調を使用してEMI性能を強化します。デジタル入力制御により、デバイスを低電流シャットダウンモードにすることが可能で、ゲート電圧レギュレータのフレキシブルなシーケンシングが提供されます。

内蔵サーマルシャットダウン回路は、デバイスを過熱から保護します。このデバイスは、チップ温度が+165°C(typ)に達するとシャットダウンし、チップ温度が15°C低下すると通常動作を再開するように設計されています。

型番の表に概要を示すように、このデバイスは最も一般的な車載TFT LCDディスプレイの電源要件に適合するさまざまな電源オプションを提供するように出荷時調整されます。

## ブーストコンバータ

ループ帯域幅を最大化し、TFT LCDパネルのソースドライバにおいて標準的なパルス状の負荷に対する高速過渡応答を提供するために、ブーストコンバータは電流モード、固定周波数PWMアーキテクチャを採用しています。2.2MHzのスイッチング周波数によって低プロファイルのインダクタおよびセラミックコンデンサの使用が可能で、LCDパネル設計の厚さを最小限に抑えることができます。内蔵の低オン抵抗MOSFETおよびこのデバイスに組み込まれたデジタルソフトスタート機能により、必要な外付け部品の数が削減されるとともに、突入電流が制御されます。出力電圧は外付けの抵抗分圧器によってV<sub>INA</sub>~18Vに設定可能です。レギュレータは各スイッチングサイクルで内蔵パワーMOSFETのデューティサイクル(D)を変調することによって出力電圧を制御します。MOSFETのデューティサイクルは、次式によって概算することができます。

$$D = 1 - \frac{\eta V_{INA}}{V_O}$$

ここで、V<sub>INA</sub>はINAの電圧、V<sub>O</sub> = V<sub>SH</sub> (ブースト出力電圧)、ηは「標準動作特性」に示されているブーストコンバータの効率です。

# 車載用TFT LCD電源、ブーストコンバータ およびゲート電圧レギュレータ内蔵

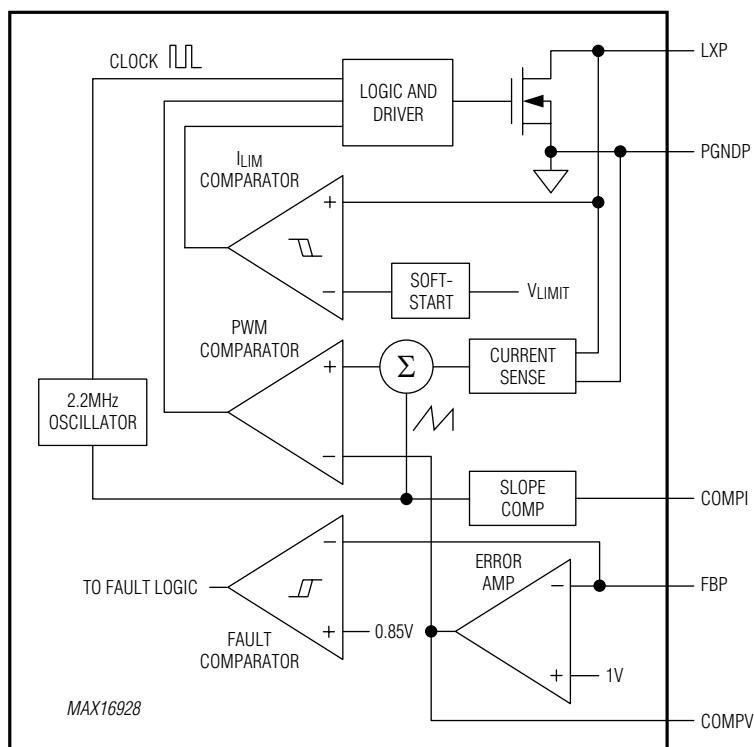

図1は、ブーストレギュレータのファンクション図を示します。エラーアンプはFBPの信号を1Vと比較してCOMPVの出力を変化させます。COMPVの電圧によって、ピークインダクタ電流が設定されます。負荷の変化にともない、エラーアンプはそれに応じてCOMPV出力への電流を供給またはシンクして、負荷への対応に必要なピークインダクタ電流を生成します。高いデューティサイクルでの安定性を維持するために、(COMPIのコンテンツによって設定される)スロープ補償信号が電流検出信号に加算されます。内部クロックの立上りエッジでコントローラはフリップフロップをセットし、nチャネルMOSFETをオンにしてインダクタに入力電圧を印加します。インダクタを流れる電流はリニアに増大して、その磁場にエネルギーを蓄積します。電流フィードバック信号とスロープ補償の合計がCOMPV

の電圧を上回ると、コントローラはMOSFETをオフにします。その後、インダクタ電流がダイオードを通して出力に流れます。クロックサイクルの残り時間は、MOSFETはオフのままになります。

GATEによって制御される外部pチャネルFETは、フォルト状態の間出力を保護し、コンバータのTrue Shutdownを提供します。GATEとINA間にプルアップ抵抗を接続してください(プルアップ抵抗の値の選択については、「[ブーストコンバータ](#)」の項を参照)。通常動作中は、GATEがpチャネルFETをオンにして、電源をブースト入力に接続します。フォルト状態またはシャットダウン中は、GATEはオフになり、プルアップ抵抗がpチャネルFETをオフにして、電源をブースト入力から切断します。

図1. ブーストコンバータのファンクション図

# 車載用TFT LCD電源、ブーストコンバータ およびゲート電圧レギュレータ内蔵

## スペクトラム拡散変調

ブーストコンバータは2.2MHzの高周波数で動作するため、スイッチングノイズはAM帯の範囲外になります。このデバイスはスイッチング周波数を±4%変調させることによってEMI性能の強化を実現します。変調信号は疑似ランダムで、各スイッチング周期で変化します(すなわち、 $f_{SS} = 2.2\text{MHz}$ )。

## スタートアップ

起動の直後、シャットダウンからの復帰時、または自動再試行への移行時、ブーストコンバータは内蔵50Ω抵抗を介して入力(INA)をスイッチング端子(LXP)に接続することにより出力の短絡検出テストを行います。

LXPの電圧の結果が1.2Vを超えた場合、デバイスはGATEをローに駆動することによって外部pMOSスイッチをオンにします。ブースト出力は15msで最終的な値まで増大します。

LXPの電圧の結果が1.2V以下の場合、出力の過負荷または短絡が検出されます。外部pMOSスイッチはオフのまゝになり、コンバータはスイッチングを行いません。238msのフォルトブランкиング時間のあと、デバイスはPGOODをローに駆動して自動再試行タイマーを始動させます。

短絡検出機能によって、入力電圧が3Vのとき出力負荷の下限が約46Ωに制限されます。

## フォルト状態とPGOOD

PGOODは、全レギュレータおよびブーストコンバータが正常に動作しているかどうかを示します。PGOODはオープンドレイン出力で、以下のいずれかのフォルトが発生した場合にローになります。

- 1) ブースト出力電圧が設定値の85%を下回る。

- 2) 正のゲート電圧レギュレータの出力( $V_{GH}$ )が設定値の85%を下回る。

- 3) 負のゲート電圧レギュレータの出力( $V_{GL}$ )が設定値の85%を下回る。

- 4) LXPの電圧が21V (typ)以上。

- 5) 正のチャージポンプ電圧( $V_{CP}$ )が30.5V (typ)以上。

- 6) 1.8V/3.3Vレギュレータの出力電圧が公称値の85%を下回る。

最初の3つのフォルト状態のいずれかが238msのフォルトブランкиング時間より長時間にわたって継続した場合、デバイスはPGOODをローに駆動し、全出力をオフにして、自動再試行タイマーを始動させます。

状態4または5が発生した場合、デバイスは直ちにPGOODをローに駆動して全出力をオフにします。デバイスは

フォルトが解消したあとにのみスタートアップを開始します。

最後の状態が発生した場合、デバイスはPGOODをローに駆動しますが、どの出力もオフにしません。

スタートアップ中はPGOODはマスクされ、1.8V/3.3Vレギュレータコントローラがオンになると同時にハイになります。このレギュレータは、 $V_{INA}$ がINA低電圧ロックアウト閾値を超えると同時にオンになります。

## 自動再試行

1.9秒後に自動再試行カウンタがインクリメントを終了すると、デバイスは表1に示す順序でブーストコンバータおよびゲート電圧レギュレータをオンにしようとします。フォルト状態が継続する限り、デバイスは自動再試行を続けます。1.8V/3.3Vレギュレータの出力でフォルトが発生した場合、PGOODはローになりますが、デバイスはシャットダウンせず自動再試行は行われません。

## 電流制限

ブーストコンバータの実効電流制限は内部で付加されるスロープ補償によって低減され、その量はコンバータのデューティサイクルによって決まります。実効電流制限は、次式で与えられます。

$$I_{LIM(EFF)} = 192 \times 10^{-12} \times I_{LIM\_DC\_0} \times \frac{D}{C_{COMPI}}$$

ここで、 $I_{LIM(EFF)}$ は実効電流制限、 $I_{LIM\_DC\_0} = 1.1\text{A}$ または $2.2\text{A}$ (ブーストコンバータの電流制限オプションによる)、Dはブーストコンバータのデューティサイクル、 $C_{COMPI}$ はCOMPI入力のコンデンサの値です。「[設計手順](#)」の項で示す式を使用して、コンバータのデューティサイクルを概算してください。

## 1.8V/3.3Vレギュレータコントローラ

1.8V/3.3Vレギュレータコントローラは、外部の負荷に4.5mA (min)を供給します。安定化された1.8V/3.3V出力とするには、FBをDRに接続してください。

より高い出力能力を実現するには、「[標準動作回路](#)」に示すように外付けのnpnトランジスタを使用してください。これにより、レギュレータの駆動能力はトランジスタの電流利得( $h_{FE}$ )だけ増大します。外付けトランジスタを使用する場合は、DRをベース駆動として使用し、FBをトランジスタのエミッタに接続してください。0.1μFのセラミックコンデンサでベースをグランドに接続してください。

ブースト出力電流が300mA以上の場合は、DRとGND間に30kΩの抵抗を接続してください。

# 車載用TFT LCD電源、ブーストコンバータ およびゲート電圧レギュレータ内蔵

## 正のゲート電圧レギュレータ(GH)

正のゲート電圧レギュレータは、安定化された5V～( $V_{CP}$ -2V)の出力を生成するためのpチャネルFET出力段を内蔵しています。このレギュレータは、広範なラインおよび負荷の条件にわたって高精度を維持します。少なくとも20mAの出力電流が可能で、電流制限保護を内蔵しています。 $V_{GH}$ は、通常はTFT LCDゲートドライバのゲートオン電圧を供給するために使用されます。

このレギュレータは、非反転チャージポンプから正の電源電圧を得ます。その1段の例を、「[標準動作回路](#)」に示します。「[チャージポンプ](#)」の項で説明するように、多段のチャージポンプを使用してより高い電圧を生成することも可能です。

## 負のゲート電圧レギュレータ(GL)

負のゲート電圧レギュレータは、オープンドレインのpチャネル出力を備えたアナログ利得ブロックです。6.8kΩのベースエミッタ間抵抗を使用して外部npnパストランジスタを駆動します(「[パストランジスタの選択](#)」の項を参照)。ベース駆動供給電流は少なくとも2mAが保証されています。 $V_{GL}$ は、通常はTFT LCDゲートドライバのゲートオフ電圧を供給するために使用されます。

負のゲート電圧レギュレータの出力(すなわち、外付けnpnパストランジスタのコレクタ)は、負荷に応じたバイパスを必要とします。[表3](#)に示す値のセラミックコンデンサを、コレクタとグランド間に接続してください。

このレギュレータは、反転チャージポンプから負の電源電圧を得ます。その1段の例を、「[標準動作回路](#)」に示します。「[チャージポンプ](#)」の項で説明するように、多段のチャージポンプを使用してより大きい負の電圧を生成することも可能です。

外付けnpnトランジスタは、短絡保護されません。外付けnpnトランジスタの適切なプルダウン能力および最適なレギュレーションを維持するために、GLレギュレータの出力の最小負荷を少なくとも500μAとすることを推奨します。

**表1.** 電源シーケンシング

| CONTROL INPUTS |     | SUPPLY SEQUENCING     |          |          |

|----------------|-----|-----------------------|----------|----------|

| ENP            | SEQ | FIRST                 | SECOND   | THIRD    |

| 0              | X   | Device is in shutdown |          |          |

| 1              | 0   | $V_{SH}$              | $V_{GH}$ | $V_{GL}$ |

| 1              | 1   | $V_{SH}$              | $V_{GL}$ | $V_{GH}$ |

## イネーブル(ENP)

イネーブル入力(ENP)を使用して、デバイスのブーストセクションをイネーブルおよびディセーブルしてください。通常動作の場合はENPをINAに接続し、デバイスをシャットダウンするにはGNDに接続してください。シャットダウン中は、INAの消費電流は0.5μAに低減されます。

## ソフトスタートおよび電源シーケンシング(SEQ)

イネーブル時、ブースト出力は $V_{INA}$ から設定電圧に向けて増大します。ブースト出力が設定電圧の85%に達し、ソフトスタートタイマーが終了すると、[表1](#)に示す順序でゲート電圧レギュレータがオンになります。1.8V/3.3Vレギュレータコントローラは、ブーストコンバータのソフトスタートの最初にイネーブルされます。

両方のゲート電圧レギュレータは、7.45msのソフトスタート時間を備えています。第1のレギュレータの出力が設定電圧の85%に達すると同時に、第2のレギュレータがオンになります。

## サーマルシャットダウン

内蔵サーマルシャットダウン回路は、チップ温度が+165°Cを超えると直ちにデバイスをシャットダウンします。15°Cのサーマルシャットダウンヒステリシスは、チップ温度が+150°Cを下回るまでデバイスの通常動作への復帰を防止します。

## 設計手順

### ブーストコンバータ

#### インダクタの選択

このデバイスによる動作のためには、インダクタンス値(L)、インダクタ飽和電流( $I_{SAT}$ )、およびDC抵抗( $R_{DC}$ )の、3つの主要なインダクタのパラメータを指定する必要があります。インダクタンス値を決定するためには、最初にインダクタのピークトゥピークリップ電流と平均出力電流の比率(LIR)を選択する必要があります。LIRの値が大きすぎる場合、RMS電流が大きくなるため、 $I^2R$ 損失が増大します。小さいLIR値を実現するには、大きい値のインダクタを使用してください。通常、特定のパッケージタイプにつ

# 車載用TFT LCD電源、ブーストコンバータ およびゲート電圧レギュレータ内蔵

いてインダクタンスは抵抗値に比例するため、LIR値が非常に小さい場合にも $I^2R$ 損失が大きくなります。サイズと損失の間の適切な妥協点は、ピクトウピークリップル電流と平均電流の比率として30%~60%を選択することです。LCDパネルアプリケーションで一般的に使用される、非常に薄型で高抵抗のインダクタを使用する場合、最良のLIRは0.5~1.0の範囲に増大する可能性があります。インダクタのサイズは次のように決定されます。

$$L = \frac{V_{INA} \times D}{LIR \times I_{INA} \times f_{SW}} \text{ and } I_{INA} = \frac{V_O \times I_O}{\eta V_{INA}}$$

$$D = \frac{1 - \eta V_{INA}}{V_O}$$

ここで、 $V_{INA}$ は入力電圧、 $V_O$ は出力電圧、 $I_O$ は出力電流、 $I_{INA}$ は平均ブースト入力電流、 $\eta$ はブーストコンバータの効率、Dはデューティサイクル、 $f_{SW}$ は2.2MHz (ブーストコンバータのスイッチング周波数)です。ブーストコンバータの効率は「[標準動作特性](#)」から概算することが可能で、内部スイッチ、キャッチダイオード、インダクタの $R_{DC}$ 、およびコンデンサのESRによる損失が含まれます。

## コンデンサの選択

入力および出力フィルタコンデンサは低ESRタイプ(タンタル、セラミック、または低ESR電解)にして、 $I_{RMS}$ の定格が次の値以上のものを使用してください。

$$I_{RMS} = \frac{LIR \times I_{INA}}{\sqrt{12}} \text{ (入力コンデンサの場合)}$$

$$I_{RMS} = I_O \sqrt{\frac{LIR^2}{D + \frac{12}{1-D}}} \text{ (出力コンデンサの場合)}$$

ここで、 $I_{INA}$ およびDは前記の入力電流とデューティサイクルです。

出力電圧に含まれるリップル成分のピクトウピーク値は出力コンデンサのESRの値および容量によって決まり、以下のように概算することができます。

$$\Delta V_{RIPPLE} = \Delta V_{ESR} + \Delta V_{CAP}$$

$$\Delta V_{ESR} = I_{INA} \times \left(1 + \frac{LIR}{2}\right) \times R_{ESR}$$

$$\Delta V_{CAP} = \frac{I_O \times D}{C_{OUT} \times f_{SW}}$$

ここで、 $I_{INA}$ およびDは前記の入力電流とデューティサイクルです。

## 整流ダイオード

電圧降下を最小限に抑え、効率を最大化するために、キャッチダイオードはショットキータイプにしてください。ダイオードは少なくとも $V_{SH}$ の逆電圧に耐えることができる必要があります。ダイオードは平均順方向電流定格が次式以上のものにしてください。

$$I_D = I_{INA} \times (1 - D)$$

ここで、 $I_{INA}$ およびDは前記の入力電流とデューティサイクルです。さらに、ダイオードのピーク電流定格が確実に次式を上回るようにしてください。

$$I_{INA} \times \left(1 + \frac{LIR}{2}\right)$$

## 出力電圧の選択

ブーストコンバータの出力電圧は、 $R_{TOP}$ および $R_{BOTTOM}$ で構成される抵抗分圧器を使用することによって調整可能です。 $R_{TOP}$ を出力とFBP間に接続し、 $R_{BOTTOM}$ をFBPとGND間に接続してください。 $R_{BOTTOM}$ は10kΩ~50kΩの範囲で選択してください。次式を使用して $R_{TOP}$ を計算してください。

$$R_{TOP} = R_{BOTTOM} \times \left(\frac{V_O}{V_{FBP}} - 1\right)$$

ここで、 $V_{FBP}$  (ブーストコンバータのフィードバック設定ポイント)は1Vです。両方の抵抗ができる限りデバイスの近くに配置し、 $R_{BOTTOM}$ をアナロググランドプレーンに接続してください。

## ループ補償

$R_{COMPV}$ の選択によって、高速な過渡応答を得るために高周波積分器の利得を設定してください。 $C_{COMPV}$ の選択によって、ループの安定性を維持するための積分器のゼロを設定してください。低ESRの出力コンデンサの場合、[表2](#)を使用して $R_{COMPV}$ と $C_{COMPV}$ の初期値を選択してください。 $R_{COMPV} + C_{COMPV}$ と並列に、22pFのコンデンサを使用してください。

## 表2. 補償部品の値

|                  |      |      |

|------------------|------|------|

| $V_{SH}$ (V)     | 8    | 18   |

| $I_{SH}$ (mA)    | 200  | 200  |

| $V_{INA}$ (V)    | 3.3  | 5    |

| $P_{IN}$ (W)     | 1.75 | 3.75 |

| $L$ ( $\mu$ H)   | 5    | 5    |

| $R_{COMPV}$ (kΩ) | 33   | 39   |

| $C_{COMPV}$ (pF) | 220  | 180  |

| $C_{COMPI}$ (pF) | 820  | 330  |

# 車載用TFT LCD電源、ブーストコンバータ およびゲート電圧レギュレータ内蔵

過渡応答をさらに最適化するために、過渡応答の波形を観察しながら $R_{COMPV}$ を20%ステップ、 $C_{COMPV}$ を50%ステップで変化させてください。理想的な過渡応答は、オーバーシュートがほとんどあるいはまったく発生せず、出力が短時間で安定するときに得られます。補償回路をアナロググランドプレーンに接続してください。

次式を使用して、 $C_{COMPI}$ の値を計算してください。

$$C_{COMPI} \leq 950 \times 10^{-6} \times L / (V_{SH} + V_{SCHOTTKY} - V_{INA})$$

## pチャネルFETの選択

ブーストコンバータの入力を開閉するために使用するpチャネルFETは、低オン抵抗のものにしてください。FETのソースとゲート間に抵抗( $R_{SG}$ )を接続してください。通常動作時、 $R_{SG}$ には $55\mu A$ のゲート駆動電流が流れ、その結果生じるゲート-ソース間電圧( $V_{GS}$ )によってFETがオンになります。フォルト状態またはシャットダウン時にゲート駆動が除去された場合、 $R_{SG}$ は電荷を放出させてFETをオフにします。FETのターンオンに必要な $V_{GS}$ が生成されるように $R_{SG}$ の大きさを決めてください。

## 1.8V/3.3Vレギュレータコントローラ

### npnバイポーラトランジスタの選択

パスnpnバイポーラトランジスタを選択する場合は、電流利得( $h_{FE}$ )と消費電力という2つの重要な点について考慮する必要があります。適切な駆動能力を確保するために、 $h_{FE}$ が十分に高いトランジスタを選択してください。この条件は、 $I_{DR} \times (h_{FE} + 1)$ が最大負荷電流より大きいときに満たされます。このレギュレータは、 $I_{DR} = 4.5mA$  (min)を供給することができます。トランジスタは、次式の電力を消費可能なものにしてください。

$$P_{NP_N\_REG} = (V_{INA} - V_{REG\_OUT}) \times I_{LOAD(MAX)}$$

ここで、 $V_{REG\_OUT} = 1.8V$ または $3.3V$ です。 $0.1\mu F$ のセラミックコンデンサでDRをグランドに接続してください。ブースト出力電流が $300mA$ を超えるアプリケーションの場合は、DRとグランド間に $30k\Omega$ の抵抗を接続してください。

### 電源について

3.3Vレギュレータが正常に動作するためには、INAは少なくとも $4.5V$ である必要があります。

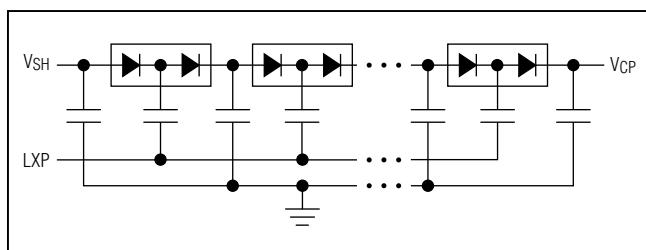

図2. 正の出力電圧用の多段チャージポンプ

## チャージポンプ

### チャージポンプの段数の選択

「[標準動作回路](#)」に示すように、ほとんどのアプリケーションでは1段のチャージポンプで十分です。フライングコンデンサをLXPに接続してください。蓄積コンデンサに生成される出力電圧は、次のようになります。

$$V_{CP} = 2 \times V_{SH} + V_{SCHOTTKY} - 2 \times V_D$$

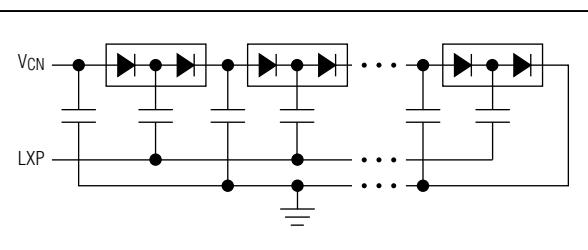

$$V_{CN} = -(V_{SH} + V_{SCHOTTKY} - 2 \times V_D)$$

ここで、 $V_{CP}$ は正のゲート電圧レギュレータ用の正の電源、 $V_{CN}$ は負のゲート電圧レギュレータ用の負の電源です。より大きい出力電圧が必要な場合は、多段のチャージポンプを使用してください(ただし、最大チャージポンプ電圧はCPおよびDRVNの絶対最大定格によって制限されます)。[図2](#)および[図3](#)は、正と負の両方の出力電圧について多段チャージポンプの構成を示します。

多段チャージポンプの場合、出力電圧は次のようになります。

$$V_{CP} = V_{SH} + n \times (V_{SH} + V_{SCHOTTKY} - 2 \times V_D)$$

$$V_{CN} = -n \times (V_{SH} + V_{SCHOTTKY} - 2 \times V_D)$$

最高の効率を実現するために、出力要件に適合する最少のチャージポンプの段数を選択してください。必要な正のチャージポンプの段数は、次式で与えられます。

$$n_{CP} = \frac{V_{GH} + V_{DROPOUT} - V_{SH}}{V_{SH} + V_{SCHOTTKY} - 2 \times V_D}$$

負のチャージポンプの段数は、次式で与えられます。

$$n_{CN} = \frac{|V_{GL}| + V_{DROPOUT}}{V_{SH} + V_{SCHOTTKY} - 2 \times V_D}$$

ここで、 $n_{CP}$ は正のチャージポンプの段数、 $n_{CN}$ は負のチャージポンプの段数、 $V_{GH}$ は正のゲート電圧レギュレータの出力電圧、 $V_{GL}$ は負のゲート電圧レギュレータの出力電圧、 $V_{SH}$ はブーストコンバータの出力電圧、 $V_D$ はチャージポンプダイオードの順電圧降下、 $V_{SCHOTTKY}$ はブーストコンバータのショットキーダイオードの順電圧降下、 $V_{DROPOUT}$ はレギュレータのドロップアウトマージンです。負の電圧レギュレータの場合は $V_{DROPOUT} = 0.3V$ を使用し、正の

図3. 負の出力電圧用の多段チャージポンプ

# 車載用TFT LCD電源、ブーストコンバータ およびゲート電圧レギュレータ内蔵

ゲート電圧レギュレータの場合は20mAで $V_{DROPOUT} = 2V$ を使用してください。

## フライングコンデンサ

フライングコンデンサ( $C_X$ )の値を増大することで、実効ソースインピーダンスが低下し、出力電流能力が増大します。内部スイッチの抵抗とダイオードのインピーダンスによってソースインピーダンスの下限が制限されるため、容量を無限に増大させた場合でも出力電圧能力に対する影響はわずかです。ほとんどの低電流アプリケーションでは、 $0.1\mu F$ のセラミックコンデンサで十分な効果が得られます。正のチャージポンプのフライングコンデンサの電圧定格は $V_{CP}$ を上回り、負のチャージポンプの場合は $V_{CN}$ の大きさを上回るようにしてください。

## チャージポンプの出力コンデンサ

出力容量の増大またはESRの低減によって、出力リップル電圧とピークトゥピーク過渡電圧が減少します。セラミックコンデンサの場合、出力電圧リップルの大部分は容量値によって決定されます。次式を使用して、CPに接続する非反転チャージポンプに必要な出力容量を概算してください。

$$C_{OUT\_CP} \geq \frac{D \times I_{LOAD\_CP}}{f_{SW} \times V_{RIPPLE\_CP}}$$

ここで、 $C_{OUT\_CP}$ はチャージポンプの出力コンデンサ、 $D$ はブーストコンバータのデューティサイクル、 $I_{LOAD\_CP}$ はチャージポンプの負荷電流、 $f_{SW}$ はブーストコンバータのスイッチング周波数、 $V_{RIPPLE\_CP}$ は出力リップルのピークトゥピーク値です。

CNに接続される反転チャージポンプの場合、次式を使用して必要な出力容量を概算してください。

$$C_{OUT\_CN} \geq \frac{(1-D) \times I_{LOAD\_CN}}{f_{SW} \times V_{RIPPLE\_CN}}$$

ここで、 $C_{OUT\_CN}$ はチャージポンプの出力コンデンサ、 $D$ はブーストコンバータのデューティサイクル、 $I_{LOAD\_CN}$ はチャージポンプの負荷電流、 $f_{SW}$ はブーストコンバータのスイッチング周波数、 $V_{RIPPLE\_CN}$ は出力リップルのピークトゥピーク値です。

## チャージポンプの整流ダイオード

平均チャージポンプ入力電流の2倍以上の電流定格を持つ高速シリコンスイッチングダイオードを使用してください。段の追加を避けるために役立つ場合は、一部またはすべてのダイオードを同等の電流定格のショットキーダイオードに置き換えてください。

## 正のゲート電圧レギュレータ

### 出力電圧の選択

正のゲート電圧レギュレータの出力電圧は、 $R_{TOP}$ および $R_{BOTTOM}$ で構成される抵抗分圧器を使用することによって調整可能です。 $R_{TOP}$ を出力と $FBGH$ 間に接続し、 $R_{BOTTOM}$ を $FBGH$ と $GND$ 間に接続してください。 $R_{BOTTOM}$ は $10k\Omega$ ～ $50k\Omega$ の範囲で選択してください。次式を使用して $R_{TOP}$ を計算してください。

$$R_{TOP} = R_{BOTTOM} \times \left( \frac{V_{GH}}{V_{FBGH}} - 1 \right)$$

ここで、 $V_{GH}$ は目的の出力電圧、 $V_{FBGH} = 1V$  (レギュレータの安定化されたフィードバック電圧)です。両方の抵抗ができる限りデバイスの近くに配置してください。

ドレンとソース間の電圧降下に注意することによって、レギュレータの内蔵pMOSデバイス内での過度の消費電力を防止してください。消費電力量は次式で与えられます。

$$P_{GL} = (V_{CP} - V_{GH}) \times I_{LOAD(MAX)}$$

ここで、 $V_{CP}$ はドレンに印加される非反転チャージポンプの出力電圧、 $V_{GH}$ は安定化された出力電圧、 $I_{LOAD(MAX)}$ は最大負荷電流です。

### 安定性の要件

正のゲート電圧レギュレータ(GH)は、安定性のために最小限の出力容量を必要とします。出力電圧が $5V$ ～( $V_{CP} - 2V$ )で出力電流が $10mA$ ～ $15mA$ の場合、最小限の容量として $0.47\mu F$ を使用してください。

## 負のゲート電圧レギュレータ

### 出力電圧の選択

負のゲート電圧レギュレータの出力電圧は、 $R_{TOP}$ および $R_{BOTTOM}$ で構成される抵抗分圧器を使用することによって調整可能です。 $R_{TOP}$ を $REF$ と $FBGL$ 間に接続し、 $R_{BOTTOM}$

# 車載用TFT LCD電源、ブーストコンバータ およびゲート電圧レギュレータ内蔵

をFBGLと外付けnpnトランジスタのコレクタ間に接続してください。負荷によるリファレンス出力の低下を避けるために、 $R_{TOP}$ には $20\text{k}\Omega$ 以上を選択してください。次式を使用して $R_{BOTTOM}$ を計算してください。

$$R_{BOTTOM} = R_{TOP} \times \frac{V_{FBGL} - V_{GL}}{V_{REF} - V_{FBGL}}$$

ここで、 $V_{GL}$ は目的の出力電圧、 $V_{REF} = 1.25\text{V}$ 、 $V_{FBGL} = 0.25\text{V}$  (レギュレータの安定化されたフィードバック電圧)です。

## パストランジスタの選択

パストランジスタは、電流利得( $h_{FE}$ )、入力容量、コレクタ-エミッタ間飽和電圧、および消費電力の仕様に適合する必要があります。トランジスタの電流利得によって、保証最大出力電流が次のように制限されます。

$$I_{LOAD(MAX)} = (I_{DRVN} - \frac{V_{BE}}{R_{BE}}) \times h_{FE(MIN)}$$

ここで、 $I_{DRVN}$ は最小保証ベース駆動電流、 $V_{BE}$ はトランジスタのベースエミッタ間順電圧降下、 $R_{BE}$ はトランジスタのベースとエミッタ間に接続されたプルダウン抵抗です。さらに、トランジスタの電流利得によってレギュレータのDCループ利得が増大するため(「安定性の要件」の項を参照)、過度の利得は出力を不安定にします。

最大出力電流におけるトランジスタの飽和電圧によって、レギュレータがサポート可能な最小入出力間電位差が決まります。また、パッケージの消費電力によって、使用可能な最大入出力間電位差が制限されます。トランジスタのパッケージおよび取付け部の最大消費電力能力は、デバイス内で消費される実際の電力を上回っている必要があります。消費される電力は、最大負荷電流( $I_{LOAD(MAX)_GL}$ )と最大入出力間電位差の積に等しくなります。

$$P_{NP_N\_GL} = (V_{GL} - V_{CN}) \times I_{LOAD(MAX)}$$

ここで、 $V_{GL}$ はトランジスタのコレクタにかかる安定化された出力電圧、 $V_{CN}$ はトランジスタのエミッタに印加される反転チャージポンプの出力電圧、 $I_{LOAD(MAX)}$ は最大負荷電流です。外付けトランジスタは短絡保護されないことに注意してください。

## 安定性の要件

このデバイスの負のゲート電圧レギュレータは、内蔵トランスクンダクタンスアンプを使用して外付けのパストランジスタを駆動します。トランスクンダクタンスアンプ、パストランジスタ、ベースエミッタ間の抵抗、および出力コンデンサによって、ループの安定性が決定します。

トランスクンダクタンスアンプは、パストランジスタのベース

電流を制御することによって出力電圧を安定化します。DCループの総合利得は、次式で概算されます。

$$A_{V_{GL}} \approx \left(\frac{4}{V_T}\right) \times \left(1 + \frac{I_{BIAS} \times h_{FE}}{I_{LOAD}}\right) \times V_{REF}$$

ここで、 $V_T$ は室温において $26\text{mV}$ 、 $I_{BIAS}$ はベースエミッタ間の抵抗( $R_{BE}$ )を通って流れる電流です。このデバイスの場合、負のゲート電圧レギュレータのバイアス電流は $0.1\text{mA}$ です。したがって、 $0.1\text{mA}$ のバイアス電流が設定されるようにベースエミッタ間の抵抗を選択してください。

$$R_{BE} = \frac{V_{BE}}{0.1\text{mA}} = \frac{0.7\text{V}}{0.1\text{mA}} = 7\text{k}\Omega$$

最も近い標準抵抗の値である $6.8\text{k}\Omega$ を使用してください。出力コンデンサおよび負荷抵抗によって、システムのドミナントポールが生成されます。しかし、内蔵アンプの遅延、パストランジスタの入力容量、およびフィードバック端子の浮遊容量によってそれ以外のポールがシステム内に生成され、出力コンデンサのESRによってゼロが生成されます。適正な動作のために、以下の手順を使用してレギュレータの補償が適切であることを確認してください。

- 最初に、レギュレータの出力コンデンサと負荷抵抗によって設定されるドミナントポールを決定してください。

$$f_{POLE\_GL} = \frac{I_{LOAD(MAX)_GL}}{2\pi \times C_{OUT\_GL} \times V_{OUT\_GL}}$$

レギュレータのユニティゲインクロスオーバー周波数は次のようになります。

$$f_{CROSSOVER} = A_{V_{LR}} \times f_{POLE\_LR}$$

- 内蔵アンプの遅延によって生成されるポールは、約 $1\text{MHz}$ です。

$$f_{POLE\_AMP} = 1\text{MHz}$$

- 次に、トランジスタの入力容量、トランジスタの入力抵抗、およびベースエミッタ間のプルアップ抵抗によって設定されるポールを計算してください。

$$f_{POLE\_IN} = \frac{1}{2\pi \times C_{IN} \times (R_{BE}/R_{IN})}$$

ここで、

$$C_{IN} = \frac{g_m}{2\pi f_T}, R_{IN} = \frac{h_{FE}}{g_m}$$

$g_m$ はパストランジスタのトランスクンダクタンス、 $f_T$ は遷移周波数です。どちらのパラメータも、トランジスタのデータシートに記載されています。 $R_{BE}$ は $R_{IN}$ よりは

# 車載用TFT LCD電源、ブーストコンバータ およびゲート電圧レギュレータ内蔵

るかに大きいため、上記の式を次のように簡略化することができます。

$$f_{POLE\_IN} = \frac{1}{2\pi \times C_{IN} \times R_{IN}}$$

$C_{IN}$ と $R_{IN}$ の代入により、次式が得られます。

$$f_{POLE} = \frac{f_T}{h_{FE}}$$

- 4) 次に、レギュレータのフィードバック抵抗およびFBGLとGND間の容量(浮遊容量を含む)によって設定されるポールを計算してください。

$$f_{POLE\_FBGL} = \frac{1}{2\pi \times C_{FBGL} \times (R_{TOP}/R_{BOTTOM})}$$

ここで、 $C_{FBGL}$ はFBGLとGNDの間の容量で30pFに等しく、 $R_{TOP}$ はレギュレータのフィードバック分圧器の上部側抵抗、 $R_{BOTTOM}$ は分圧器の下部側抵抗です。

- 5) 次に、出力コンデンサのESRによって発生するゼロを計算してください。

$$f_{ZERO\_ESR} = \frac{1}{2\pi \times C_{OUT\_LR} \times R_{ESR}}$$

ここで、 $R_{ESR}$ は $C_{OUT\_LR}$ の等価直列抵抗です。安定性を確保するために、 $C_{OUT\_LR}$ を十分に大きくして、ステップ2から5で計算したポールおよびゼロよりはるかに低い位置でクロスオーバーが発生するようにしてください。ステップ3および4のポールは通常は数MHzの位置に発生し、セラミックコンデンサの使用によってESRによるゼロも確実に数MHzの位置に発生させることができます。クロスオーバー周波数を500kHz以下に設定することによってアンプ遅延のポールを十分に回避することが可能で、変則的な部品選択や過剰な容量によって他のポールまたはゼロを1MHz以下に移動させない限り、通常は問題なく動作します。

**表3**に、負のゲート電圧レギュレータの推奨最小出力容量のリストを示します。これらは10mA～15mAの範囲の出力電流に適用可能です。

**表3. 負のゲート電圧レギュレータの最小出力容量と出力電圧範囲の関係 ( $I_{OUT} = 10mA \sim 15mA$ )**

| OUTPUT VOLTAGE RANGE        | MINIMUM OUTPUT CAPACITANCE ( $\mu F$ ) |

|-----------------------------|----------------------------------------|

| -2V $\geq V_{GL} \geq -4V$  | 2.2                                    |

| -5V $\geq V_{GL} \geq -7V$  | 1.5                                    |

| -8V $\geq V_{GL} \geq -13V$ | 1                                      |

## アプリケーション情報

### 消費電力

ICの最大消費電力は、ダイから周囲環境への熱抵抗および周囲温度によって決まります。熱抵抗は、ICのパッケージ、PCBの銅面積、その他の熱容量、およびエアフローによって決まります。PCBの銅面積が広く、周囲の気温が低く、エアフローが大きいほど可能な消費が増大するのに対して、狭い銅面積や高い気温によってICの消費能力が低下します。消費電力の主な要因は、ブーストコンバータ、正のゲート電圧レギュレータ、負のゲート電圧レギュレータ、および1.8V/3.3Vレギュレータコントローラでの消費電力です。

### ブーストコンバータ

ブーストコンバータの消費電力は、主にローサイドFETでの導通損失とスイッチング損失が原因です。導通損失は、オン時間中にインダクタ電流がFETのオン抵抗を通して流れることによって発生します。スイッチング損失はスイッチング遷移中に発生し、FETを完全にオンおよびオフするために必要な有限時間の結果です。ブーストコンバータでの消費電力は、次式を使用して概算することができます。

$$P_{LXP} \approx [(I_{IN(DC,MAX)} \times \sqrt{D})^2 \times R_{DS\_ON}(LXP)] + V_{SH} \times I_{IN(DC,MAX)} \times f_{SW} \times [(t_{R-V} + t_{F-I}) + (t_{R-I} + t_{F-V})]$$

ここで、 $I_{IN(DC,MAX)}$ は最大予想平均入力(すなわち、インダクタ)電流、Dはブーストコンバータのデューティサイクル、 $R_{DS\_ON}(LXP)$ は内蔵ローサイドFETのオン抵抗、 $V_{SH}$ は出力電圧、 $f_{SW}$ はブーストコンバータのスイッチング周波数です。 $R_{DS\_ON}(LXP)$ は110mΩ (typ)で、 $f_{SW}$ は2.2MHzです。

# 車載用TFT LCD電源、ブーストコンバータ およびゲート電圧レギュレータ内蔵

LXP端子の電圧および電流の立上り/立下り時間は、 $t_{R-V}$  (電圧立上り時間)、 $t_{F-V}$  (電圧立下り時間)、 $t_{R-I}$  (電流立上り時間)、および $t_{F-I}$  (電流立下り時間)で、以下のように決定されます。

$$t_{R-V} = \frac{V_{SH} + V_{SCHOTTKY}}{K_{R-V}}$$

$$t_{F-V} = \frac{V_{SH} + V_{SCHOTTKY}}{K_{F-V}}$$

$$t_{R-I} = \frac{I_{IN(DC,MAX)}}{K_{R-I}}$$

$$t_{F-I} = \frac{I_{IN(DC,MAX)}}{K_{F-I}}$$

$K_{R-V}$ 、 $K_{F-V}$ 、 $K_{R-I}$ 、および $K_{F-I}$ はLXP端子の電圧および電流スルーレートで、電源に依存します。[表4](#)を使用して、それぞれの値を決定してください。

## 正のゲート電圧レギュレータ

正の電圧レギュレータへの給電には、可能な限り最少のチャージポンプの段数を使用してください。それによって、内蔵pMOSスイッチのドレン-ソース間電圧および消費電力を最小限に抑えることができます。スイッチの消費電力は、次式で与えられます。

$$P_{GH} = (V_{CP} - V_{GH}) \times I_{LOAD(MAX)}_{GH}$$

CPの電圧が「[Electrical Characteristics](#)」の表に記載されたCPの過電圧閾値を超えないようにしてください。

## 負のゲート電圧レギュレータ

負のゲート電圧レギュレータへの負の電圧の供給には、可能な限り最少のチャージポンプの段数を使用してください。次式を使用して、負のゲート電圧レギュレータの消費電流を概算してください。

**表4. LXPの電圧および電流スルーレートと電源電圧の関係**

| $V_{INA}$ (V) | LXP VOLTAGE AND CURRENT SLEW RATES            |                                                |                                               |                                                |

|---------------|-----------------------------------------------|------------------------------------------------|-----------------------------------------------|------------------------------------------------|

|               | RISING VOLTAGE SLEW RATE,<br>$K_{R-V}$ (V/ns) | FALLING VOLTAGE SLEW RATE,<br>$K_{F-V}$ (V/ns) | RISING CURRENT SLEW RATE,<br>$K_{R-I}$ (A/ns) | FALLING CURRENT SLEW RATE,<br>$K_{F-I}$ (A/ns) |

| 3.3           | 0.52                                          | 1.7                                            | 0.13                                          | 0.38                                           |

| 5             | 1.35                                          | 2                                              | 0.3                                           | 0.44                                           |

$$P_{GL} = (V_{INA} + |V_{CN1}| - V_{BE}) \times I_{DRVN}$$

ここで、 $V_{BE}$ は外付けnpnバイポーラトランジスタのベースエミッタ間電圧、 $I_{DRVN}$ はDRVNからバイアス抵抗 $R_{BE}$ を通してトランジスタのベースに供給される電流で、次式によって与えられます。

$$I_{DRVN} = \frac{V_{BE}}{R_{BE}} + \frac{I_{GL}}{h_{FE} + 1}$$

## 1.8V/3.3Vレギュレータコントローラ

1.8V/3.3Vレギュレータコントローラの消費電力は、次式で与えられます。

$$P_{REG} = (V_{INA} - V_{OUT\_REG} - V_{BE}) \times I_{DR}$$

ここで、 $V_{OUT\_REG} = 1.8V$ または $3.3V$ 、 $V_{BE}$ は外付けnpnバイポーラトランジスタのベースエミッタ間電圧、 $I_{DR}$ はDRからトランジスタのベースに供給される電流です。 $I_{DR}$ は次式によって与えられます。

$$I_{DR} = \frac{I_{LOAD}}{h_{FE} + 1}$$

ここで、 $I_{LOAD}$ は1.8V/3.3Vレギュレータコントローラの負荷電流、 $h_{FE}$ はトランジスタの電流利得です。

## 総消費電力

パッケージの総消費電力は、上記で計算した損失の合計です。したがって、総消費電力は次のように概算することができます。

$$P_T = P_{LXP} + P_{GH} + P_{GL} + P_{REG}$$

エクスポートドパッドをサーマルランディングパッドに接続し、サーマルビアを介してサーマルランディングパッドを大面積のグランドプレーンに接続することによって、最大の熱伝導を実現してください。

# 車載用TFT LCD電源、ブーストコンバータ およびゲート電圧レギュレータ内蔵

## レイアウトについて

安定した最高の性能を実現するためには、注意深いPCBレイアウトが非常に重要です。適切なPCBレイアウトとするために、これらのガイドラインに従ってください。

- 1) デカッピングコンデンサはできる限りデバイスの近くに配置してください。パワーグランドプレーンとアナロググランドプレーンをデバイスに近い一点で相互に接続してください。

- 2) 入力および出力コンデンサは、パワーグランドプレーンに接続してください。その他のすべてのコンデンサは、アナロググランドプレーンに接続してください。

- 3) 大電流の経路は、できる限り短く太くしてください。スイッチング電流の経路は短くしてください。

- 4) フィードバック抵抗はできる限りデバイスの近くに配置してください。抵抗分圧器の負側および補償回路をアナロググランドプレーンに接続してください。

- 5) 高速スイッチング端子のLXPは、敏感なアナログ端子(FB、FBP、FBGH、FBGL、およびREF)から遠ざけて配線してください。

推奨PCBレイアウトについては、MAX16928の評価キットのデータシートを参照してください。

## 型番

| PART            | TEMP RANGE      | REGULATOR V <sub>REG</sub> (V) | BOOST I <sub>LIM</sub> (A) | PIN-PACKAGE  |

|-----------------|-----------------|--------------------------------|----------------------------|--------------|

| MAX16928AGUP/V+ | -40°C to +105°C | 3.3                            | 1.5                        | 20 TSSOP-EP* |

| MAX16928BGUP/V+ | -40°C to +105°C | 1.8                            | 1.5                        | 20 TSSOP-EP* |

| MAX16928CGUP/V+ | -40°C to +105°C | 3.3                            | 0.75                       | 20 TSSOP-EP* |

| MAX16928DGUP/V+ | -40°C to +105°C | 1.8                            | 0.75                       | 20 TSSOP-EP* |

/Vは車載認定製品を表します。

+は鉛(Pb)フリー/RoHS準拠パッケージを表します。

\*EP = エクスポートドパッド

## チップ情報

PROCESS: BiCMOS

## パッケージ

最新のパッケージ図面情報およびランドパターン(フットプリント)は[japan.maximintegrated.com/packages](http://japan.maximintegrated.com/packages)を参照してください。なお、パッケージコードに含まれる「+」、「#」、または「-」はRoHS対応状況を表したものでしかありません。パッケージ図面はパッケージそのものに関するものでRoHS対応状況とは関係がなく、図面によってパッケージコードが異なることがある点を注意してください。

| パッケージタイプ    | パッケージコード | 外形図No.                  | ランドパターンNo.              |

|-------------|----------|-------------------------|-------------------------|

| 20 TSSOP-EP | U20ME+1  | <a href="#">21-0108</a> | <a href="#">90-0114</a> |

**車載用TFT LCD電源、ブーストコンバータ

およびゲート電圧レギュレータ内蔵****標準動作回路**

# 車載用TFT LCD電源、ブーストコンバータ およびゲート電圧レギュレータ内蔵

## 改訂履歴

| 版数 | 改訂日  | 説明                                 | 改訂ページ |

|----|------|------------------------------------|-------|

| 0  | 7/11 | 初版                                 | —     |

| 1  | 1/12 | 「ループ補償」の項のC <sub>COMP1</sub> の式を修正 | 13    |

マキシム・ジャパン株式会社 〒141-0032 東京都品川区大崎1-6-4 大崎ニューシティ 4号館 20F TEL: 03-6893-6600

Maxim Integratedは完全にMaxim Integrated製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。Maxim Integratedは隨時予告なく回路及び仕様を変更する権利を留保します。「Electrical Characteristics (電気的特性)」の表に示すパラメータ値(min、maxの各制限値)は、このデータシートの他の場所で引用している値より優先されます。

**Maxim Integrated 160 Rio Robles, San Jose, CA 95134 USA 1-408-601-1000**

© 2012 Maxim Integrated Products, Inc.

Maxim IntegratedおよびMaxim IntegratedのロゴはMaxim Integrated Products, Inc.の商標です。