# デュアルチャネル、カードバス及びPCMCIA用 パワースイッチ、SMBus<sup>TM</sup>シリアルインターフェース付

**MAX1601/MAX1604**

## 概要

MAX1601 / MAX1604は、2チャネルのカードバス又はPCカードのホストソケットに選択可能なVCC及びVPP電圧を供給する低抵抗MOSFETスイッチのネットワークを備えた、DC電源切換えICです。主な特長としては、超低抵抗スイッチ、小型パッケージ、ソフト切換え動作、及び3V/5V切換えでのPCMCIA規格への適合等が挙げられます。高速32ビットカードバスアプリケーション用の3.3V専用電源切換えが2つの方法でサポートされています。まず、強力な3.3V低抵抗スイッチが3.3Vで高電流(最大1A)を可能にします。さらに、省電力化のために+5V及び+12V電源が切り離してあったりオフになっていても、完全に独立した内部チャージポンプ回路が3.3Vスイッチの正常動作を可能にします。内部チャージポンプは安定化タイプであり、VCCスイッチがスタティック状態のときに入力電流が減少します。また、独立したシャットダウン制御入力を必要とする他の解決法とは異なり、シリアルインターフェースで制御ロジック入力がハイインピーダンス又はGND状態に設定されると、消費電流が自動的に10μA(max)に低減されます。

その他の重要な特長としては、出力電流制限レベルの仕様が保証されていること、及び出力の立上がり/立下がり時間が保証(PCMCIA規格に適合)されていることが挙げられます。サーマル過電流保護、高精度電流制限、過電流障害フラグ出力、低電圧ロックアウト、及びVCC/VPP出力での特別なESD保護が信頼性を高めています。SMBusシリアルインターフェースはフレキシブルで、正電源電圧を超えるロジック入力レベルを許容します。

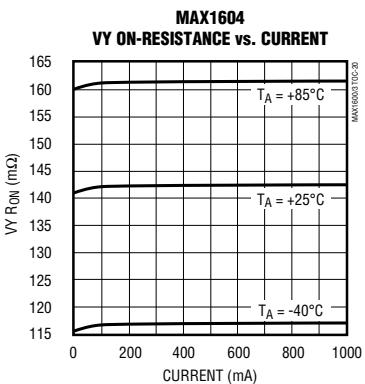

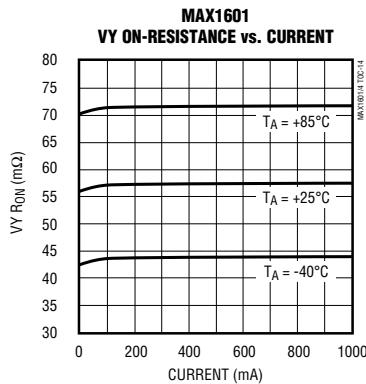

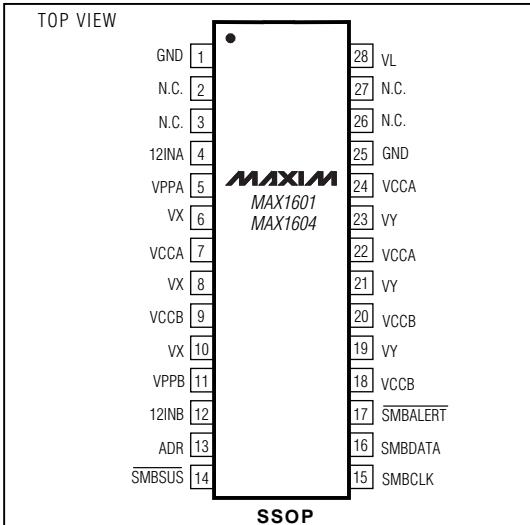

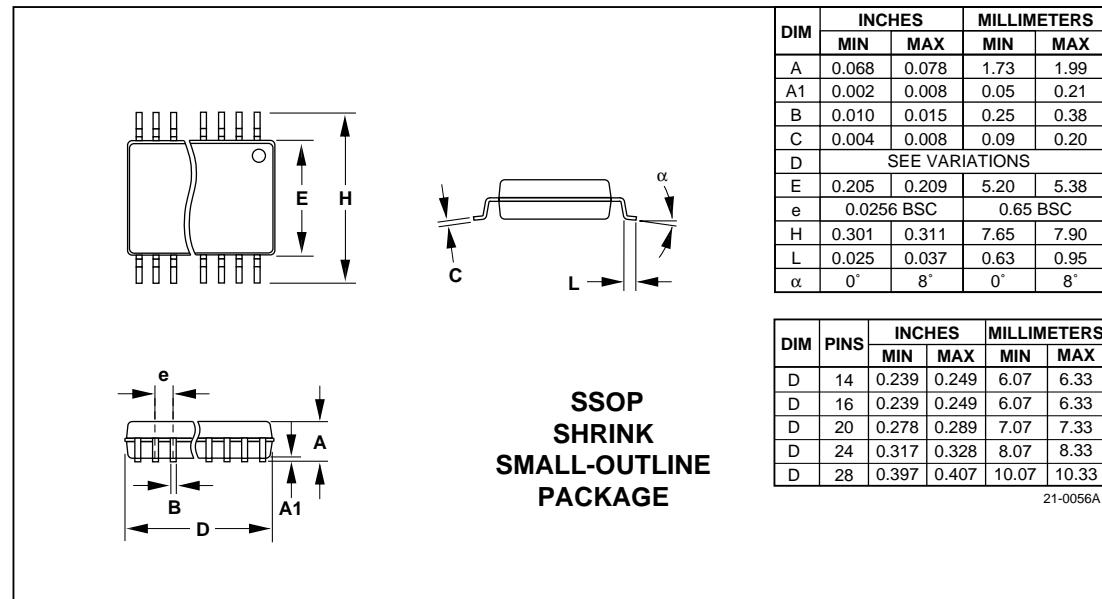

MAX1604及びMAX1601は、MAX1604のVYスイッチのオン抵抗が約3倍(140m typ)である以外は同一です。MAX1601/MAX1604は、2つの完全なカードバス/PCMCIAスイッチを省スペースのナロー(幅5mm)SSOPパッケージに内蔵しています。

## アプリケーション

|              |                  |

|--------------|------------------|

| デスクトップコンピュータ | データロガー           |

| ノート型コンピュータ   | デジタルカメラ          |

| ドッキングステーション  | プリンタ             |

| ハンディターミナル    | PCMCIA 読取/書きドライブ |

ピン配置は最後のページに記載されています。

SMBusは、Intel Corp.の商標です。

## 特長

- ◆ 2つのカードバスソケットをサポート

- ◆ 1A、0.08 (max), VY VCCスイッチ(MAX1601のみ)

1A、0.14 (max), VX VCCスイッチ

- ◆ インラッシュサージ電流を低減するソフト切換え

- ◆ 過電流保護

- ◆ 過電流/熱障害フラグ出力

- ◆  $T_j = +150$  でサーマルシャットダウン

- ◆ 独立した内部チャージポンプ

- ◆ ブレーク・ビフォ・メイクの切換え動作

- ◆ スタンバイ消費電流 : 10μA(max)

- ◆ 低 $R_{DS(ON)}$ での3.3V切換えには5V及び12Vは不要

- ◆ PCMCIA 3V/5V切換え規格に適合

- ◆ 超小型28ピンSSOPパッケージ(幅5mm)

- ◆ システムマネジメントバス(SMBus)

シリアルインターフェース

## 型番

| PART              | TEMP. RANGE    | PIN-PACKAGE |

|-------------------|----------------|-------------|

| <b>MAX1601EAI</b> | -40°C to +85°C | 28 SSOP     |

| <b>MAX1604EAI</b> | -40°C to +85°C | 28 SSOP     |

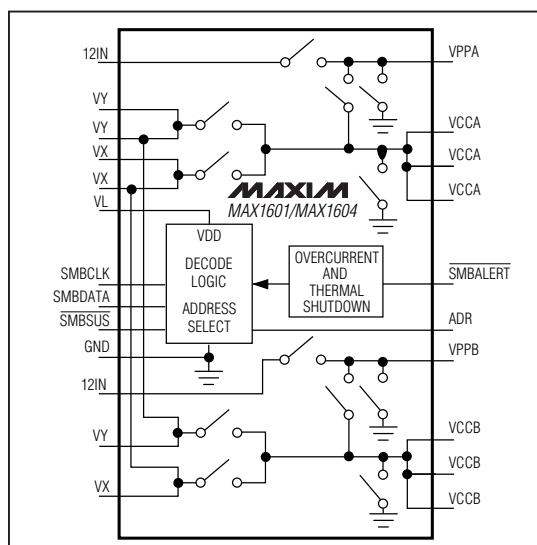

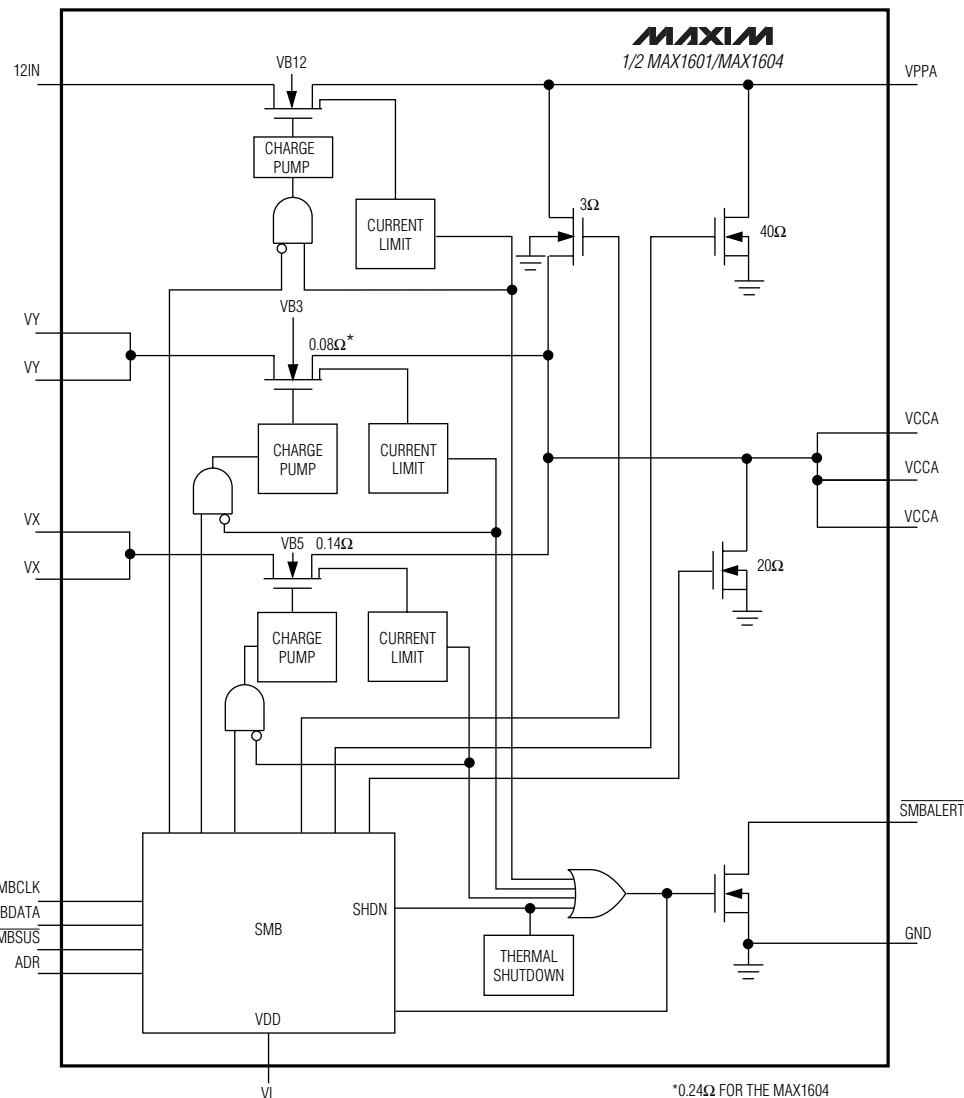

## 簡略ブロック図

# デュアルチャネル、カードバス及びPCMCIA用 パワースイッチ、SMBus™シリアルインターフェース付

## ABSOLUTE MAXIMUM RATINGS

|                                                                           |                    |

|---------------------------------------------------------------------------|--------------------|

| Inputs/Outputs to GND<br>(VL, VX, VY, VCCA, VCCB) (Note 1)                | -0.3V, +6V         |

| VPP Inputs/Outputs to GND<br>(12INA, 12INB, VPPA, VPPB) (Note 1)          | -0.3V, +15V        |

| Inputs and Outputs to GND (SMBCLK, SMBDATA,<br>SMBBUS, SMBALERT) (Note 1) | -0.3V, +6V         |

| ADR Input to GND                                                          | -0.3V, (VL + 0.3V) |

| VCCA, VCCB Output Current (Note 2)                                        | .4A                |

| VPPA, VPPB Output Current (Note 2)                                        | 250mA              |

|                                                                                        |                 |

|----------------------------------------------------------------------------------------|-----------------|

| VCCA, VCCB Short Circuit to GND .....                                                  | Continuous      |

| VPPA, VPPB Short Circuit to GND .....                                                  | Continuous      |

| Continuous Power Dissipation (TA = +70°C)<br>SSOP (derate 9.52mW/°C above +70°C) ..... | 762mW           |

| Operating Temperature Range<br>MAX1601EA1/MAX1604EA1 .....                             | -40°C to +85°C  |

| Storage Temperature Range .....                                                        | -65°C to +160°C |

| Lead Temperature (soldering, 10sec) .....                                              | +300°C          |

**Note 1:** There are no parasitic diodes between any of these pins, so there are no power-up sequencing restrictions (for example, logic input signals can be applied even if all of the supply voltage inputs are grounded).

**Note 2:** VCC and VPP outputs are internally current-limited to safe values. See the *Electrical Characteristics* table.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

(VL = VY = 3.3V, VX = 5V, 12INA = 12INB = 12V, TA = 0°C to +85°C, unless otherwise noted. Typical values are at TA = +25°C.)

| PARAMETER                      | CONDITIONS                                                                                     | MIN     | TYP  | MAX  | UNITS |

|--------------------------------|------------------------------------------------------------------------------------------------|---------|------|------|-------|

| <b>POWER-SUPPLY SECTION</b>    |                                                                                                |         |      |      |       |

| Input Voltage Range            | VX, VY or VL                                                                                   | 3.0     | 5.5  |      | V     |

|                                | 12INA, 12INB                                                                                   | 11      | 13   |      |       |

| Undervoltage Lockout Threshold | VL falling edge                                                                                | 2.4     | 2.5  | 2.8  | V     |

|                                | 12IN falling edge                                                                              | 1.8     | 3.0  |      |       |

|                                | 12IN rising edge                                                                               | 5       | 8    | 10   |       |

|                                | VX, VY falling edge                                                                            | 1.4     | 2.5  | 2.8  |       |

| Standby Supply Current         | VX or VY, all switches 0V or high-Z,<br>control inputs = 0V or VL, TA = +25°C                  |         | 1    |      | µA    |

| VY Quiescent Supply Current    | Any combination of VY switches on,<br>control inputs = 0V or VL, no VCC loads                  | 20      | 100  |      | µA    |

| VX Quiescent Supply Current    | Any combination of VX switches on,<br>control inputs = 0V or high-Z, no VCC loads              | 20      | 100  |      | µA    |

| 12IN_ Standby Supply Current   | 12INA tied to 12INB, all switches 0V or high-Z,<br>control inputs = 0V or VL, TA = +25°C       |         | 1    |      | µA    |

| 12IN_ Quiescent Supply Current | 12INA tied to 12INB, VPPA and VPPB 12V switches on,<br>control inputs = 0V or VL, no VPP loads | 15      | 100  |      | µA    |

| VL Standby Supply Current      | All switches 0V or high-Z, control inputs = 0V or VL,<br>TA = +25°C                            | 4       | 10   |      | µA    |

| VL Quiescent Supply Current    | Any combination of switches on                                                                 | 25      | 150  |      | µA    |

| VL Fall Rate                   | When using VL as shutdown pin (Note 3)                                                         |         | 0.05 |      | V/µs  |

| <b>VCC SWITCHES</b>            |                                                                                                |         |      |      |       |

| Operating Output Current Range | VCCA or VCCB, VX = VY = 3V to 5.5V                                                             | 0       | 1    |      | A     |

| On-Resistance, VY Switches     | 12INA = 12INB = 0V to 13V,<br>VY = 3V, VX = 0V to 5.5V,<br>ISWITCH = 1A, TA = +25°C            | MAX1601 | 0.06 | 0.08 | Ω     |

|                                |                                                                                                | MAX1604 | 0.14 | 0.24 |       |

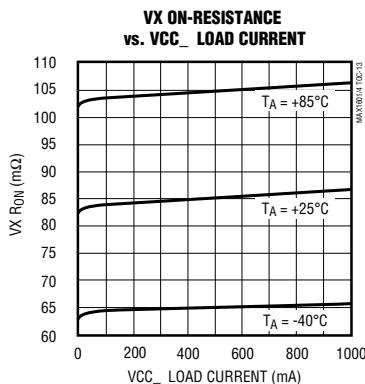

| On-Resistance, VX Switches     | 12INA = 12INB = 0V to 13V, VX = 4.5V, VY = 0V to 5.5V,<br>ISWITCH = 1A, TA = +25°C             |         | 0.10 | 0.14 | Ω     |

# デュアルチャネル、カードバス及びPCMCIA用 パワースイッチ、SMBus<sup>TM</sup>シリアルリンクフェース付

## ELECTRICAL CHARACTERISTICS (continued)

( $V_L = V_Y = 3.3V$ ,  $V_X = 5V$ ,  $12INA = 12INB = 12V$ ,  $T_A = 0^\circ C$  to  $+85^\circ C$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ .)

| PARAMETER                                  | CONDITIONS                                                                                                                                 | MIN  | TYP  | MAX | UNITS      |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|------------|

| Output Current Limit                       | VCCA or VCCB                                                                                                                               | 1.2  |      | 4.0 | A          |

| Output Sink Current                        | VCCA or VCCB < 0.4V, programmed to 0V state                                                                                                | 20   |      |     | mA         |

| Output Leakage Current                     | VCCA or VCCB forced to 0V, high-Z state,<br>$T_A = +25^\circ C$                                                                            |      |      | 10  | $\mu A$    |

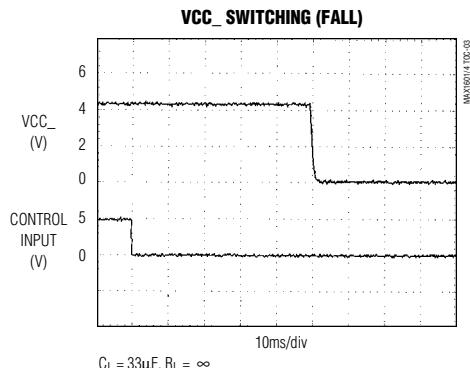

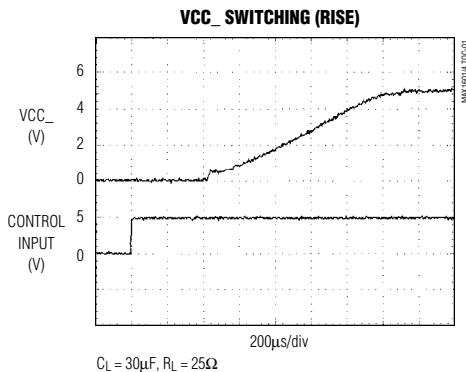

| Output Propagation Delay<br>Plus Rise Time | VCCA or VCCB, 0V to $VX$ or $VY$ , $C_L = 30\mu F$ ,<br>$R_L = 25\Omega$ , 50% of input to 90% of output, $T_A = +25^\circ C$              |      | 2    | 10  | ms         |

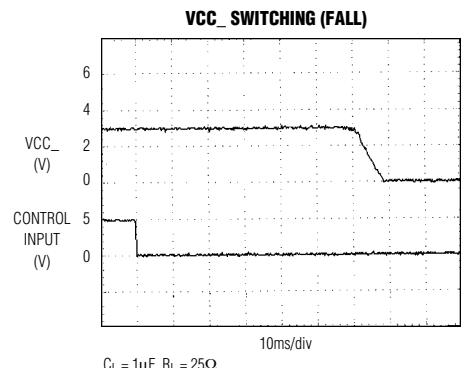

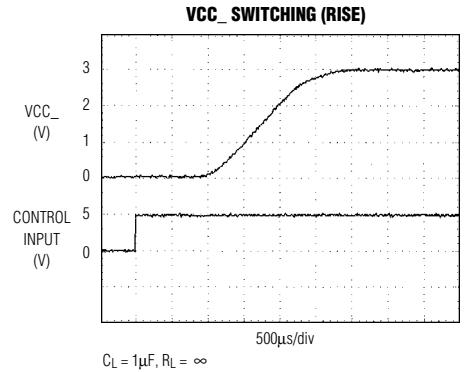

| Output Rise Time                           | VCCA or VCCB, 0V to $VX$ or $VY$ , $C_L = 1\mu F$ ,<br>$R_L = \text{open circuit}$ , 10% to 90% points, $T_A = +25^\circ C$                | 100  | 1200 |     | $\mu s$    |

| Output Propagation Delay<br>Plus Fall Time | VCCA or VCCB, $VX$ or $VY$ to 0V, $C_L = 30\mu F$ ,<br>$R_L = \text{open circuit}$ , 50% of input to 10% of output,<br>$T_A = +25^\circ C$ |      | 60   | 100 | ms         |

| Output Fall Time                           | VCCA or VCCB, $VX$ or $VY$ to 0V, $C_L = 1\mu F$ ,<br>$R_L = 25\Omega$ , 90% to 10% points                                                 |      | 6    |     | ms         |

| <b>VPP SWITCHES</b>                        |                                                                                                                                            |      |      |     |            |

| Operating Output Current Range             | VPPA or VPPB                                                                                                                               | 0    |      | 120 | mA         |

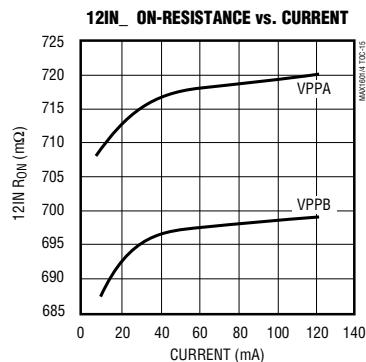

| On-Resistance, 12V Switches                | $12IN = 11.6V$ , $I_{SWITCH} = 100mA$ , $T_A = +25^\circ C$                                                                                |      | 0.70 | 1   | $\Omega$   |

| On-Resistance, VPP = VCC Switches          | Programmed to $VX$ (5V) or $VY$ (3.3V), $T_A = +25^\circ C$                                                                                |      | 1    | 3   | $\Omega$   |

| Output Current Limit                       | VPPA or VPPB, programmed to 12V                                                                                                            | 130  | 200  | 260 | mA         |

| Output Sink Current                        | VPPA or VPPB < 0.4V, programmed to 0V state                                                                                                | 10   |      |     | mA         |

| Output Leakage Current                     | VPPA or VPPB forced to 0V, high-Z state,<br>$T_A = +25^\circ C$                                                                            |      |      | 10  | $\mu A$    |

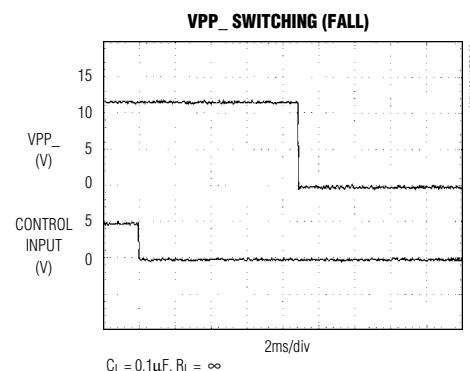

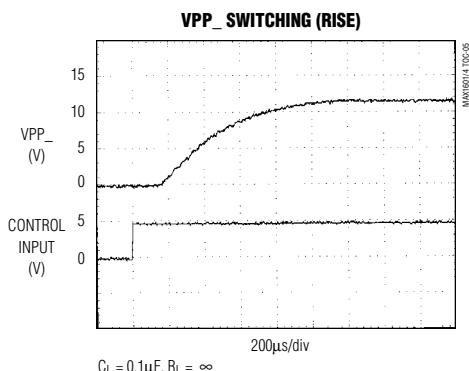

| Output Propagation Delay<br>Plus Rise Time | VPPA or VPPB, 0V to $12IN_-$ , $C_L = 0.1\mu F$ ,<br>50% of input to 90% of output, $T_A = +25^\circ C$                                    |      | 1.2  | 30  | ms         |

| Output Rise Time                           | VPPA or VPPB, 0V to $12IN_-$ , $C_L = 0.1\mu F$ ,<br>10% to 90% points, $T_A = +25^\circ C$                                                | 100  | 800  |     | $\mu s$    |

| Output Propagation Delay<br>Plus Fall Time | VPPA or VPPB, $12IN_-$ to 0V, $C_L = 0.1\mu F$ ,<br>50% of input to 10% of output, $T_A = +25^\circ C$                                     |      | 9    | 60  | ms         |

| Output Fall Time                           | VPPA or VPPB, $12IN_-$ to 0V, $C_L = 0.1\mu F$ ,<br>90% to 10% points                                                                      |      | 1    |     | ms         |

| <b>INTERFACE AND LOGIC SECTION</b>         |                                                                                                                                            |      |      |     |            |

| SMBALERT Signal Propagation Delay          | $VCC_-$ or $VPP_-$ , load step to $\overline{\text{SMBALERT}}$ output,<br>50% point to 50% point (Note 3)                                  |      | 3    |     | $\mu s$    |

| SMBALERT Output Low Voltage                | $I_{SINK} = 1mA$ , low state                                                                                                               |      | 0.4  |     | V          |

| SMBALERT Output Leakage Current            | $V_{SMBALERT} = 5.5V$ , high state                                                                                                         | -0.1 | 0.1  |     | $\mu A$    |

| Thermal Shutdown Threshold                 | Hysteresis = $+20^\circ C$ (Note 4)                                                                                                        |      | 150  |     | $^\circ C$ |

| Logic Input Low Voltage                    | $\overline{\text{SMBSUS}}$ , $\overline{\text{SMBCLK}}$ , $\overline{\text{SMBDATA}}$                                                      |      | 0.8  |     | V          |

| Logic Input High Voltage                   | $\overline{\text{SMBSUS}}$ , $\overline{\text{SMBCLK}}$ , $\overline{\text{SMBDATA}}$                                                      | 2.2  |      |     | V          |

| Logic Output Low Voltage                   | $\overline{\text{SMBDATA}}$ , $I_{SINK} = 4mA$                                                                                             |      | 0.4  |     | V          |

# デュアルチャネル、カードバス及びPCMCIA用 パワースイッチ、SMBus<sup>TM</sup>シリアルインターフェース付

## ELECTRICAL CHARACTERISTICS (continued)

(VL = VY = 3.3V, VX = 5V, 12INA = 12INB = 12V, TA = 0°C to +85°C, unless otherwise noted. Typical values are at TA = +25°C.)

| PARAMETER                                          | CONDITIONS                                          | MIN | TYP  | MAX | UNITS |

|----------------------------------------------------|-----------------------------------------------------|-----|------|-----|-------|

| SMB Input Capacitance                              | SMBUS, SMBCLK, SMBDATA                              |     | 5    |     | pF    |

| SMBCLK Clock Frequency                             | SMBus spec = 10kHz min                              | DC  | 100  |     | KHz   |

| SMBCLK Clock Low Time                              | t <sub>LOW</sub> 10% to 10% points                  | 4.7 |      |     | μs    |

| SMBCLK Clock High Time                             | t <sub>HIGH</sub> 90% to 90% points                 | 4   |      |     | μs    |

| SMB Repeated Start-Condition Setup Time            | tsu:STA 90% to 90% points                           | 250 |      |     | ns    |

| SMB Start-Condition Hold Time                      | t <sub>HD:STA</sub> 10% of SMBDATA to 90% of SMBCLK | 4   |      |     | μs    |

| SMB Stop-Condition Setup Time                      | tsu:STO 90% of SMBCLK to 10% of SMBDATA             | 4   |      |     | μs    |

| SMB Data Valid to SMBCLK Rising-Edge Time          | tsu:DAT 10% or 90% of SMBDATA to 10% of SMBCLK      | 500 |      |     | ns    |

| SMB Data Hold Time                                 | t <sub>HD:DAT</sub> (Note 5)                        | 0   |      |     | ns    |

| Bus Free Time                                      | t <sub>BUF</sub> between start and stop conditions  | 4.7 |      |     | μs    |

| ADR Input Low Voltage                              |                                                     |     | 0.6  |     | V     |

| ADR Input High Voltage                             |                                                     |     | 1.5  |     | V     |

| Logic Input Bias Current                           | ADR, SMBUS, SMBCLK, SMBDATA                         | -1  | 1    |     | μA    |

| SCL Fall to SDA Valid<br>(Master Clocking-In Data) |                                                     | 100 | 1000 |     | ns    |

| Start-Condition Setup                              |                                                     | 4.7 |      |     | μs    |

**Note 3:** Not production tested.

**Note 4:** Thermal limit not active in standby state (all switches programmed to GND or high-Z state).

**Note 5:** A transition must internally provide at least a hold time in order to bridge the undefined region (300ns max) of the falling edge of SMBCLK.

# デュアルチャネル、カードバス及びPCMCIA用 パワースイッチ、SMBus<sup>TM</sup>シリアルリンクフェース付

## ELECTRICAL CHARACTERISTICS

(VL = VY = 3.3V, VX = 5V, 12INA = 12INB = 12V, TA = -40°C to +85°C, unless otherwise noted.)

| PARAMETER                          | CONDITIONS                                                                                  | MIN | TYP | MAX | UNITS |

|------------------------------------|---------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| <b>POWER-SUPPLY SECTION</b>        |                                                                                             |     |     |     |       |

| Input Voltage Range                | VX, VY or VL                                                                                | 3.0 | 5.5 | 13  | V     |

|                                    | 12INA, 12INB                                                                                | 11  | 13  |     |       |

| Undervoltage Lockout Threshold     | VL falling edge, hysteresis = 1%                                                            | 2.3 | 2.9 | 10  | V     |

|                                    | 12IN falling edge                                                                           | 1.8 | 1.8 |     |       |

|                                    | 12IN rising edge                                                                            | 5   | 10  |     |       |

|                                    | VX, VY falling edge                                                                         | 1.4 | 2.9 |     |       |

| Standby Supply Current             | VX or VY, all switches 0V or high-Z, control inputs = 0V or VL                              |     | 15  |     | µA    |

| VY Quiescent Supply Current        | Any combination of VY switches on, control inputs = 0V or VL, no VCC loads                  |     | 100 |     | µA    |

| VX Quiescent Supply Current        | Any combination of VX switches on, control inputs = 0V or high-Z, no VCC loads              |     | 100 |     | µA    |

| 12IN_ Standby Supply Current       | 12INA tied to 12INB, all switches 0V or high-Z, control inputs = 0V or VL                   |     | 15  |     | µA    |

| 12IN_ Quiescent Supply Current     | 12INA tied to 12INB, VPPA and VPPB 12V switches on, control inputs = 0V or VL, no VPP loads |     | 100 |     | µA    |

| VL Standby Supply Current          | All switches 0V or high-Z, control inputs = 0V or VL                                        |     | 15  |     | µA    |

| VL Quiescent Supply Current        | Any combination of switches on                                                              |     | 150 |     | µA    |

| <b>INTERFACE AND LOGIC SECTION</b> |                                                                                             |     |     |     |       |

| SMBALERT Output Low Voltage        | ISINK = 1mA, low state                                                                      |     | 0.4 |     | V     |

| Logic Input Low Voltage            | SMBCLK, SMBDATA, SMBSUS                                                                     |     | 0.8 |     | V     |

| Logic Input High Voltage           | SMBCLK, SMBDATA, SMBSUS                                                                     | 2.2 |     |     | V     |

| Logic Output Low Voltage           | SMBDATA, ISINK = 4mA                                                                        |     | 0.4 |     | V     |

| ADR Input Low Voltage              |                                                                                             |     | 0.6 |     | V     |

| ADR Input High Voltage             |                                                                                             | 1.5 |     |     | V     |

# デュアルチャネル、カードバス及びPCMCIA用 パワースイッチ、SMBus<sup>TM</sup>シリアルインターフェース付

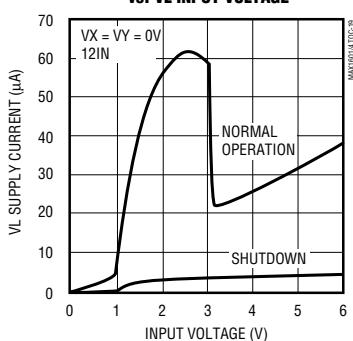

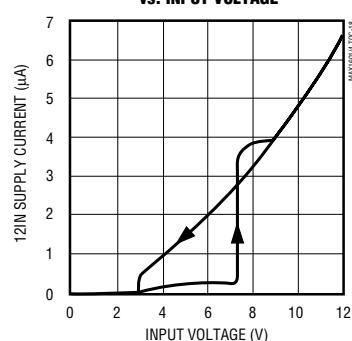

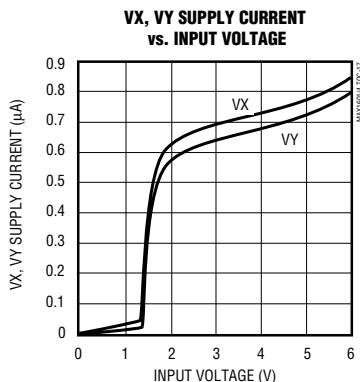

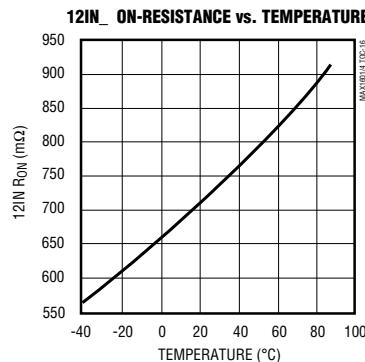

## 標準動作特性

( $V_L = V_Y = 3.3V$ ,  $V_X = 5V$ ,  $12IN$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

# デュアルチャネル、カードバス及びPCMCIA用 パワースイッチ、SMBus<sup>TM</sup>シリアルリンクフェース付

## 標準動作特性( 続き )

( $V_L = V_Y = 3.3V$ ,  $V_X = 5V$ ,  $I_{2IN} = +25^\circ C$ , unless otherwise noted.)

**MAX1601/MAX1604**

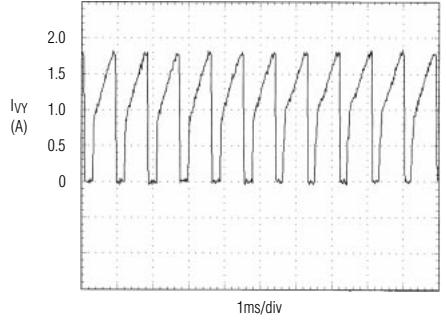

**VCC\_ CURRENT LIMITING**

$C_L = 1\mu F$ , RESISTIVE OVERLOAD,  $R_L = 1\Omega$

**INPUT CURRENT (VCC OUTPUT SHORTED)**

1ms/div

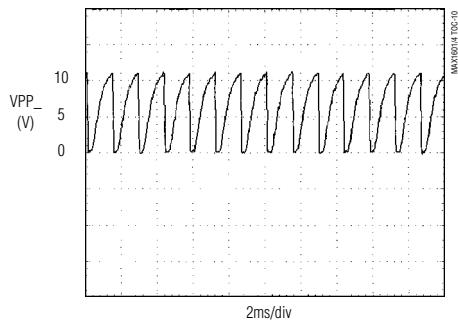

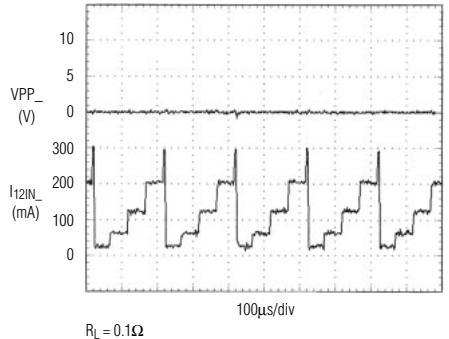

**VPP\_ CURRENT LIMITING**

$C_L = 1\mu F$ ,  $R_L = 50\Omega$

**INPUT CURRENT (VPP OUTPUT SHORTED)**

100μs/div

$R_L = 0.1\Omega$

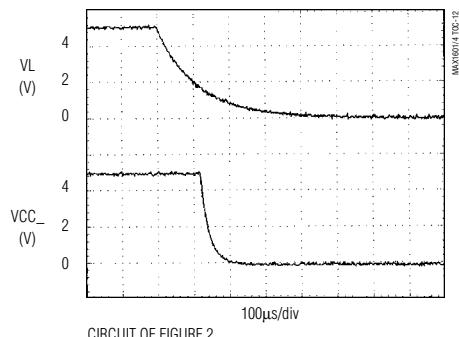

**VCC\_ SHUTDOWN RESPONSE**

CIRCUIT OF FIGURE 2

# デュアルチャネル、カードバス及びPCMCIA用 パワースイッチ、SMBus<sup>TM</sup>シリアルインターフェース付

## 標準動作特性( 続き )

( $V_L = V_Y = 3.3V$ ,  $V_X = 5V$ ,  $12IN$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

# デュアルチャネル、カードバス及びPCMCIA用 パワースイッチ、SMBus<sup>TM</sup>シリアルインターフェース付

## 端子説明

| 端子              | 名称       | 機能                                                                                                                                                                                                                         |

|-----------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 25           | GND      | グランド                                                                                                                                                                                                                       |

| 2, 3,<br>26, 27 | N.C.     | 内部接続なし。                                                                                                                                                                                                                    |

| 4               | 12INA    | +12V電源電圧入力。内部でチャネルA VPPスイッチに接続しています。使用しない場合はVPPAに接続してください。                                                                                                                                                                 |

| 5               | VPPA     | チャネルA VPP出力                                                                                                                                                                                                                |

| 6, 8, 10        | VX       | VX電源電圧入力。VXピン同士をまとめて接続する必要があります。入力範囲は3V～5.5Vです。VXは通常5Vに接続されます。                                                                                                                                                             |

| 7, 22, 24       | VCCA     | チャネルA VCC出力                                                                                                                                                                                                                |

| 9, 18, 20       | VCCB     | チャネルB VCC出力                                                                                                                                                                                                                |

| 11              | VPPB     | チャネルB VPP出力                                                                                                                                                                                                                |

| 12              | 12INB    | +12V電源電圧入力。内部でチャネルB VPPスイッチに接続しています。使用しない場合はVPPBに接続してください。                                                                                                                                                                 |

| 13              | ADR      | アドレス入力。SMBusアドレス位置を設定します。アドレス選択については、表1を参照してください。                                                                                                                                                                          |

| 14              | SMBSUS   | SMBusサスPENDモード制御入力。 <u>SMBSUS</u> がハイの場合、デバイスは以前にノーマルモードレジスタに保存されていたコマンドを実行します。 <u>SMBSUS</u> がローの場合、デバイスは以前にサスPENDモードレジスタに保存されていたコマンドを実行します。                                                                              |

| 15              | SMBCLK   | SMBusクロック入力                                                                                                                                                                                                                |

| 16              | SMBDATA  | SMBusデータ入力/出力、オーブンドレイン                                                                                                                                                                                                     |

| 17              | SMBALERT | 障害検出割込み出力。 <u>SMBALERT</u> は、VCC又はVPPスイッチが電流制限又は低電圧ロックアウトになった場合、あるいはサーマル保護回路が起動された場合にローになります。 <u>SMBALERT</u> はオーブンドレイン出力であり、外部プルアップ抵抗を必要とします。                                                                             |

| 19, 21, 23      | VY       | VY電源電圧入力。VYピン同士と一緒にまとめて接続する必要があります。入力範囲は3V～5.5Vです。VXは通常3Vに接続されます。                                                                                                                                                          |

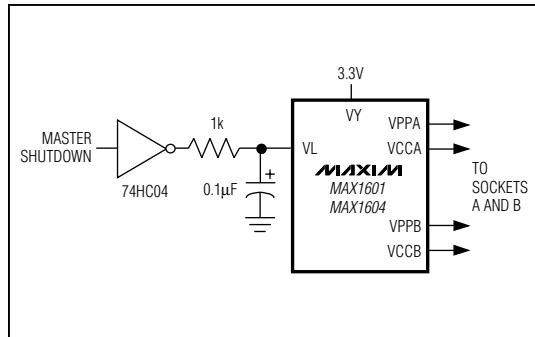

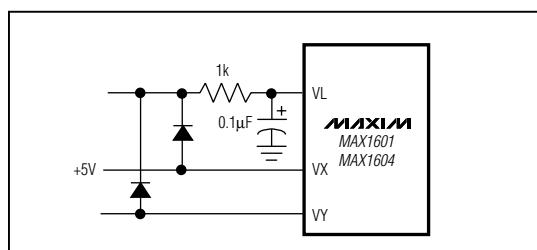

| 28              | VL       | ロジック電源電圧入力。+3.3V又は+5Vのホストシステム電源に接続してください。VLの電源をCMOSロジックゲートの出力を介して供給することにより、オーバーライドシャットダウンを発生させることができます。シャットダウン入力として用いる場合、VLに1kΩの直列抵抗を接続し、0.1μFのコンデンサでグランドに接続してください(図2)。スイッチがターンオンするためには、VLが低電圧ロックアウトよりも高い必要があることに注意してください。 |

デュアルチャネル、カードバス及びPCMCIA用

パワースイッチ、SMBus<sup>TM</sup>シリアルインターフェース付

**MAX1601/MAX1604**

図1. ファンクションダイアグラム(2つのチャネルの内の1つ)

# デュアルチャネル、カードバス及びPCMCIA用 パワースイッチ、SMBus<sup>TM</sup>シリアルインターフェース付

## 詳細

MAX1601/MAX1604は、2つのカードバス又はPCカードのホストソケットに選択可能なVCC及びVPP電圧を供給する低抵抗MOSFETスイッチのネットワークを備えた、DC電源切換えICです。MAX1601とMAX1604の唯一の違いはVYスイッチのオン抵抗にあります。図1に詳細ブロック図を示します。

電源入力ピン(VY、VX、12IN\_)は、完全に独立しています。スイッチの立上がり時間を制御することによって低インラッシュ電流を保証しています。VCCの最小出力立上がり時間である100μsは、1μFの容量性負荷にて100%試験済みです。VPPの最小出力立上り時間である1msは、0.1μFの容量性負荷で保証されています。それぞれの容量性負荷は、ワーストケースのカード挿入パラメータとして選択されています。内部切換え制御機能はVCCとVPPの立上がり時間を制御し、抵抗性負荷及び容量性負荷には依存しません(「標準動作特性」の立上がり時間の写真を参照)。立下がり時間は負荷の関数であり、内部回路で補償されています。

省電力は自動的に行われます。VCCスイッチがスタンバイ状態のときは、内部チャージポンプの消費電流は極めて低くなっています。スイッチの消費電流はスタンバイモードでは、1μAまで低減します。外部ロジックゲート(マスターシャットダウン)でVLピンをローにすると、全消費電流が1μAまで低減します(図2)。

## 動作モード

MAX1601/MAX1604にはノーマル、スタンバイ、及びシャットダウンという3つの動作モードがあります。ノーマルモードでは選択された出力にそれぞれ適した電源電圧が供給されます。スタンバイモードでは全てのスイッチがグランド、ハイインピーダンス、又はこれら2つの組み合わせになります。シャットダウンモードでは全てのスイッチがオフになり、VCC及びVPP出力はハイインピーダンス状態になります。シャットダウンモードとするには、VLをローにします。VLの立下がりレートを0.05V/μsで保証するために、1kの直列抵抗と0.1μFのコンデンサでグランドに接続してください(図2)。

## 過電流保護

ピーク検出回路がVCC及びVPPスイッチの両方を過電流から保護します。いずれかのスイッチを流れる電流が内部電流制限(VCCスイッチの場合4A、VPPスイッチの場合は200mA)を超えると、スイッチは短時間ターン

図2. マスターシャットダウン回路

オフしてから制御された立上がりレートでターンオンします。過電流状態が2μs以上続くとSMBALERT出力がローにラッチされます。短絡状態が継続すると、サーマルシャットダウンに入るまで出力電流はパルス状になります。SMBALERTはオープンドレインのため外部プルアップ抵抗が必要です。

## サーマルシャットダウン

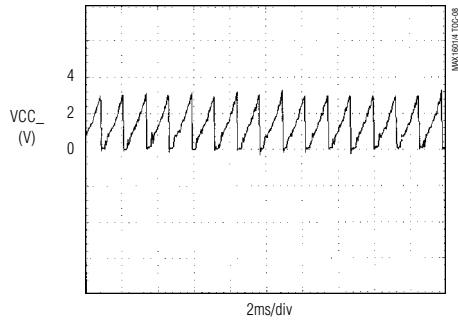

ICのジャンクション温度が+150以上に上昇すると、サーマルシャットダウン回路がGNDスイッチを含む全てのスイッチを開放し、SMBALERTがローになります。温度が+130よりも低い状態に戻ると、スイッチは制御された立上がりレートで再びターンオンします。過電流状態がまだ続いている場合は、サーマルシャットダウンと過電流の状態をサイクルし続けます。

## 低電圧ロックアウト

VX又はVYスイッチの入力電圧が1.5Vよりも低くなると、それに対するスイッチはオフになりSMBALERTがローになります。例えば、VYが3.3V、VXが0VでインターフェースコントローラがVYを選択している場合は、VCCA出力は3.3Vになります。もしここでVXが選択されるとVCCAはハイインピーダンス出力に変わり、SMBALERTがローになります。

電圧を最初に12IN\_に印加するとき、8V以上でないとスイッチは動作しません。いったん動作し始めれば電圧が2V以下になるまで動作し続けます(VPP出力はハイインピーダンス)。

VLが2.3Vよりも低くなると、全てのスイッチがターンオフしてVCC及びVPP出力はハイインピーダンスになります。

# デュアルチャネル、カードバス及びPCMCIA用 パワースイッチ、SMBus™シリアルインターフェース付

**SMBus™インターフェースの動作**

SMBusシリアルインターフェースはマルチマスタリング機能を備えた2線インターフェースであり、低電力のポータブル機器アプリケーションで低速周辺機器を制御するために使用されます。SMBusはI<sup>2</sup>C™及びAccessBusと似ていますが、ロジックスレッシュルド電圧レベルがやや異なり、固定アドレスが異なるとともに、サスペンドモードレジスタ機能を備えている点が違います。SMBusインターフェースの完全な仕様が必要な場合は、Intel社まで製品コードSBS5220を請求してください。

## SMBusのアドレス指定

これらのデュアルチャネルPCカードスイッチデバイスは4つの異なるアドレスの内の2つに応答します。どれに応答するかはADRアドレスピンの状態に依存します。デバイスへの通常の書きを行うには、まず4つのアドレスの内の1つを送信し、それからシングルのデータバイトを送って選択されたチャネルをプログラムします。これらのデバイスでは、割込みポインタアドレスへの書き送信はサポートされていません。デバイスからの読み取りは、Aチャネルアドレス(A及びBの両チャネルの障害に関するデータを提供)又は割込みポインタアドレス

(後述)に対応する2つのアドレスの内の1つを送信することによって行われます。

通常のスタート条件は、SMBCLKがハイのときにSMBDATAがハイからローに遷移することにより成立します。7ビットのアドレスの後に読み取又は書き動作を指定する1ビット(ハイは読み取、ローは書き)が続きます。7ビットアドレスがサポートされている機能アドレスの内の1つに一致すると、ICはSMBDATAラインをローにすることによってアクノレッジパルスを発信します。ICはアドレスが有効でない場合、新しくスタート条件が検出されるまでバスにアクセスせず、バス上のデータを全て無視します。書きビットを含む有効アドレスを受け取ると、ICは次の1バイトのデータを予期します。完全な1バイトのデータがクロックインする前にストップ条件又は新しいスタート条件が検出された場合、ICはエラーが生じたとみなしてすべてのデータを拒絶し、廃棄します。SMBDATA及びSMBCLKはショミットトリガされており、遅いエッジにも対応します。しかし、それでも立ち上りエッジは1μsより早く、立ち下りエッジは300nsより速くしてください。

## SMBusの書き動作

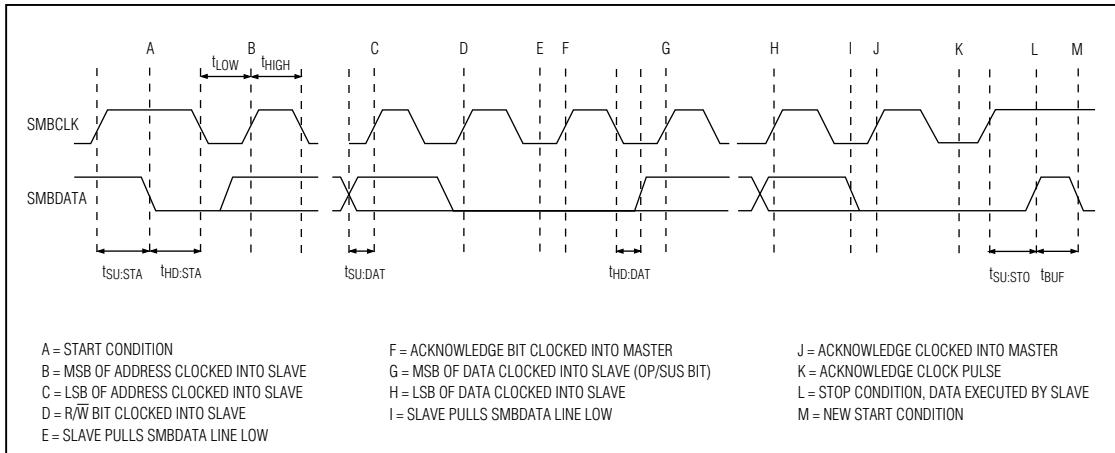

有効なアドレスの直後に書きビットを受け取ると、そのICはスレーブリセーバになります。スレーブICはアドレス及び書きビットの後で最初のアクノレッジを生成し、コマンドバイトの後で2番目のアクノレッジを生成します。コマンド(データ)バイトの次にストップ条件が発生すると、データのSUS/OPビットがローでない限りそのコマンドが直ちに実行されます。データのSUS/OPビットがローである場合、コマンドはサスペンドモードレジスタに保存され、SMBSUSピンがローになったときだけ実行されます(図3)。

表1. SMBusのアドレス指定

| SMB ADDRESS | ADR PIN    | WRITE FUNCTION | READ FUNCTION      |

|-------------|------------|----------------|--------------------|

| 0001100     | Don't care | N/A            | Interrupt Pointer  |

| 1010000     | Grounded   | Channel A      | Channel A/B faults |

| 1010001     | Grounded   | Channel B      | Channel A/B faults |

| 1010010     | Tied to VL | Channel A      | Channel A/B faults |

| 1010011     | Tied to VL | Channel B      | Channel A/B faults |

表2. チャネルA書き動作のコマンドフォーマット(アドレス1010000又は1010010)

| BIT     | NAME    | POR STATE | FUNCTION                                                                                 |

|---------|---------|-----------|------------------------------------------------------------------------------------------|

| 7 (MSB) | OP/SUS  | 0         | Operate/suspend bit. Selects which latch receives data: high = operation, low = suspend. |

| 6       | VCCAON  | 0         | Turns on VCCA when high, pulls VCCA to GND when low.                                     |

| 5       | VCCA3/5 | 0         | If VCCA is on, a high connects VY to VCCA, and a low connects VX to VCCA.                |

| 4       | VCAHIZ  | 0         | Puts VCCA in a high-impedance state when high. Overrides VCCAON.                         |

| 3       | VPPAON  | 0         | Turns on VPPA when high, pulls VPPA to GND when low.                                     |

| 2       | VPPAPGM | 0         | If VPPA is on, a high connects VPPA to 12INA, and a low connects VPPA to VCCA.           |

| 1       | VPPAHIZ | 0         | Puts VPPA in a high-impedance state when high. Overrides VPPAON.                         |

| 0 (LSB) | MASKFLT | 0         | Masks fault interrupts from both channel A and channel B when high.                      |

I<sup>2</sup>Cは、Phillips Corps.の商標です。

SMBusは、Intel Corp.の商標です。

# デュアルチャネル、カードバス及びPCMCIA用 パワースイッチ、SMBus<sup>TM</sup>シリアルインターフェース付

表3. チャネルB書き動作のコマンドフォーマット(アドレス1010001又は1010011)

| BIT     | NAME    | POR STATE | FUNCTION                                                                                 |

|---------|---------|-----------|------------------------------------------------------------------------------------------|

| 7 (MSB) | OP/SUS  | 0         | Operate/suspend bit. Selects which latch receives data: high = operation, low = suspend. |

| 6       | VCCBON  | 0         | Turns on VCCB when high, pulls VCCB to GND when low.                                     |

| 5       | VCCB3/5 | 0         | If VCCB is on, a high connects VY to VCCB, and a low connects VX to VCCB.                |

| 4       | VCCBHIZ | 0         | Puts VCCB in a high-impedance state when high. Overrides VCCBON.                         |

| 3       | VPPBON  | 0         | Turns on VPPB when high, pulls VPPB to GND when low.                                     |

| 2       | VPPBPGM | 0         | If VPPB is on, a high connects VPPB to 12INB, and a low connects VPPB to VCCB.           |

| 1       | VPPBHIZ | 0         | Puts VPPB in a high-impedance state when high. Overrides VPPBON.                         |

| 0 (LSB) | RFU     | 0         | Reserved for future use.                                                                 |

表4. 割込みポインタアドレス(0001100)の読み取りフォーマット

| BIT     | NAME | POR STATE | FUNCTION                                                                                                                                                                                                                                              |

|---------|------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 (MSB) | ADD7 | 0         | ADD7 to ADD1 provide a return address for any interrupt query. For these devices, the return addresses are:<br>1010000 = Channel A, ADD = low<br>1010001 = Channel B, ADD = low<br>1010010 = Channel A, ADD = high<br>1010011 = Channel B, ADD = high |

| 6       | ADD6 | 0         |                                                                                                                                                                                                                                                       |

| 5       | ADD5 | 0         |                                                                                                                                                                                                                                                       |

| 4       | ADD4 | 0         |                                                                                                                                                                                                                                                       |

| 3       | ADD3 | 0         |                                                                                                                                                                                                                                                       |

| 2       | ADD2 | 0         |                                                                                                                                                                                                                                                       |

| 1       | ADD1 | 0         |                                                                                                                                                                                                                                                       |

| 0 (LSB) | ADD0 | 0         |                                                                                                                                                                                                                                                       |

表5. パワースイッチアドレス(1010000又は1010010)の読み取りフォーマット

| BIT     | NAME     | POR STATE | LATCHED? | FUNCTION                                                                  |

|---------|----------|-----------|----------|---------------------------------------------------------------------------|

| 7 (MSB) | CATFAULT | 0         | Y        | Indicates catastrophic (thermal or undervoltage lockout) fault when high. |

| 6       | FAULT1   | 0         | Y        | Indicates VCCA overcurrent/undervoltage lockout when high.                |

| 5       | FAULT2   | 0         | Y        | Indicates VPPA overcurrent/undervoltage lockout when high.                |

| 4       | FAULT3   | 0         | Y        | Indicates VCCB overcurrent/undervoltage lockout when high.                |

| 3       | FAULT4   | 0         | Y        | Indicates VPPB overcurrent/undervoltage lockout when high.                |

| 2       | SIG/DUAL | 0         | N        | Indicates dual part (single-channel devices would read 1).                |

| 1       | RFU      | 0         | N        | Reserved for future use.                                                  |

| 0 (LSB) | RFU      | 0         | N        | Reserved for future use.                                                  |

# デュアルチャネル、カードバス及びPCMCIA用 パワースイッチ、SMBus<sup>TM</sup>シリアルインターフェース付

図3. SMBusの書きタイミング図

## SMBusの読み取り動作

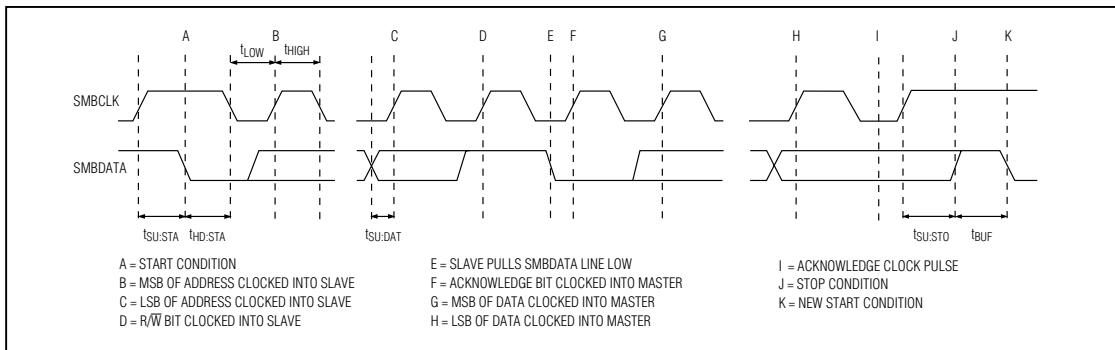

読み取りビットを含む有効なアドレスを受け取ると、そのICはスレーブトランスマッタになります。アドレスデータを受け取った後、ICはアクノレッジクロックパルス中にアクノレッジを生成し、SMBDATAラインをSMBCLKと同期させて駆動します。SMBプロトコルでは、マスターがSMBCLKのアクノレッジビット中にアクノレッジしないことによって読み取り送信を終了する必要があります。これらのPCカードICは、データ転送方向を変更するに際して「繰返しスタート条件法」をサポートしています。これは書き送信の後にストップ条件ではなく、スタートの繰返しによってICのデータ読み取りを準備します(図4)。

## SMBus割込み

これらのPCカードパワースイッチICは、スレーブデバイス専門であり、(SMBALERTをローにして)割込みを発生する場合を除いては決して自ら通信を開始することはできません。割込みを生成するのは、障害条件を報告するときだけです。障害条件としてはVCCA、VCCB、VPPA又はVPPBでの過電流、低電圧ロックアウト及びICの過熱等が挙げられます。割込みの発生はシステム故障の前兆である可能性があります。ホストシステムはサスPENDモードに入るか、あるいはその他の処置により対応することができます。ホストシステムは後で戻ってきて割込みポインタを介してICからステータスを得るか、あるいは修正処置を取ることができます(例えば、短絡したPCカードに接続されているパワースイッチをディセーブルする等)。障害条件に対応して最も速くスイッチをターンオフできるのは、

VLの電圧をサイクルしてパワーオンリセットを生成する方法です(これにより全てのSMBusレジスタがクリアされます)。SMBusレジスタは、たとえメインVX/VY電源がターンオフしていてもVLの電源が入っている限りデータを保持します。

障害が発生すると、SMBALERTが直ちに発生してローにラッチされます。障害が瞬間的でICがサービスを受ける前に消えた場合にも、データは割込みポインタにラッチされたままでSMBALERTは発生状態を維持します。通常はここでマスター(ホストシステム又はPCMCIAデジタルコントローラ)が割込みポインタアドレス(00011000)に続いて読み取りビットを送ります。SMBALERTはクリアされ、PCカードICは自己のアドレスをバスに乗せて応答します。障害が引き続き存在する場合は、SMBALERTが再び発生しますが、障害レジスタのデータは再ロードされません。障害ラッチのデータは最初にSMBALERTが発生したときの状態だけを反映します。

ICが動作モードに入ったときに疑似割込みフラグが発生する場合があります。ユーザは、割込みアドレスを送ってこの疑似割込みをクリアする必要があります。通常はマスターが適切なPCカードスイッチアドレスをバスに送り出し、その後に読み取りビットを送り出します。それから、障害レジスタ内のデータがバスにクロックアウトされます(障害レジスタのクリアもこれで行われます)。障害が引き続き存在する場合は、障害ビット及びSMBALERTが再びラッチされます。

# デュアルチャネル、カードバス及びPCMCIA用 パワースイッチ、SMBus<sup>TM</sup>シリアルインターフェース付

図4. SMBusの読み取りタイミング図

割込みポインタアドレスは、バスマスターになるために必要な複雑で高価なロジックを持たない、単純なスレーブデバイスの障害を迅速に認識する方法を提供します。ホストは割込みポインタを読むことによって、どのデバイスから SMBALERT 割込み信号が発生したかを知ることができます。割込みポインタアドレスは I<sup>2</sup>C ジェネラルコールと同様に、いくつかの異なるスレーブデバイスを同時に起動することができます。割込みを発生したスレーブデバイスは、最初の読み込みバイト中に自分のアドレスをバスに乗せることによって自分がどのデバイスであるかを知らせようとします。2つ以上のスレーブが応答しようとした場合は、バスの仲裁規則により、アドレスコードの低い方のデバイスが応答します。応答できなかった方のデバイスはアクノレッジを発生せず、サービスを受けるまで SMBALERT ラインをローに保持します。このため、ホストの割込み入力がレベル感受性を持っている必要があります。

## アプリケーション情報

### 電源バイパス

VY、VX、及び12IN\_入力は、0.1μFのセラミックコンデンサでバイパスしてください。ノイズ低減とESD保護のために、VCC\_及びVPP\_出力は0.1μFのコンデンサでバイパスしてください。

### パワーアップ

どのスイッチ入力よりも先にVL入力に電源を投入してください。VLが2.8Vを超える前にVY、VX、又は12INに電源を投入すると、消費電流が異常に高くなることがあります(約5mA)。VLの電圧が2.8Vよりも高ければ(動作モード)、消費電流は仕様通り24μAとなります。電源シーケンスを避けるために、VXとVYをダイオードOR接続し、1k の抵抗を通じてVLに接続してください(図5)。VLが最大低電圧ロックアウトのスレッショルドである2.8Vを下回ることがないように注意してください。

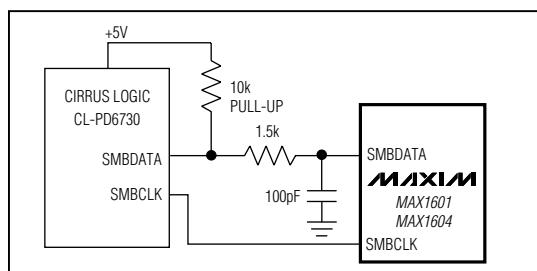

### SMBCLKとSMBDATAの同時変化

MAX1601/MAX1604 状態にデータをクロックインする時は、SMBDATAをSMBCLKより先にローにしないでください。ローにした場合には、MAX1601/MAX1604はスタート状態として解釈してしまいます。SMBDATAとSMBCLKが同時にローになったとしても、2つの信号の異なる立ち下がり時間によって、誤ったスタート状態を発生してしまいます。SMCLKの立ち下がりエッジ後にSMBDATAの遷移を正しく行うために、RCネットワークをSMBDATAに追加します。(図6)

図5. VX又はVYから電源を供給

図6. Cirrus Logicとのインターフェース

# デュアルチャネル、カードバス及びPCMCIA用 パワースイッチ、SMBus<sup>TM</sup>シリアルインターフェース付

## ピン配置

## チップ情報

TRANSISTOR COUNT: 4372

## パッケージ

**マキシム・ジャパン株式会社**〒169 東京都新宿区西早稲田3-30-16(ホリゾン1ビル)

TEL. (03)3232-6141 FAX. (03)3232-6149

マキシム社では全体がマキシム社製品で実現されている回路以外の回路の使用については責任を持ちません。回路特許ライセンスは明言されていません。

マキシム社は隨時予告なしに回路及び仕様を変更する権利を保有します。

16 **Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 (408) 737-7600**

© 1996 Maxim Integrated Products

**MAXIM** is a registered trademark of Maxim Integrated Products.