# ノートブックコンピュータ用 高効率、5出力、メイン電源コントローラ

## 概要

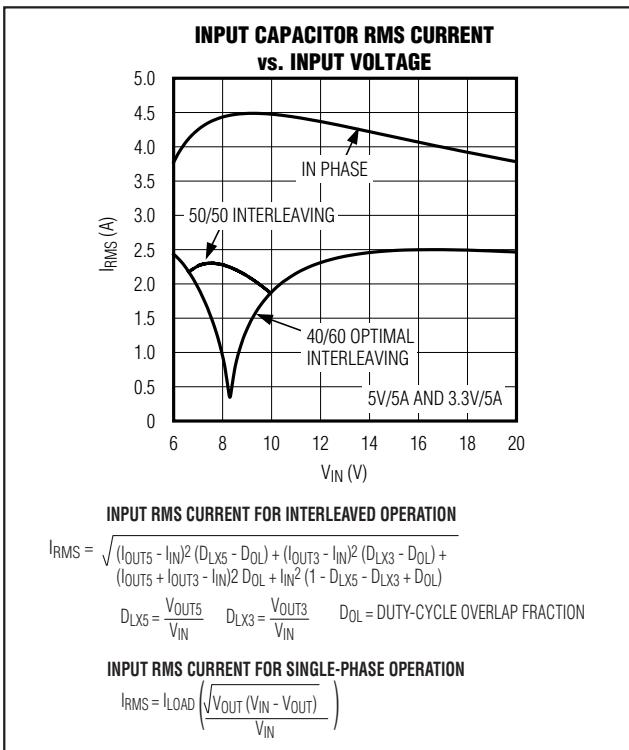

MAX1533/MAX1537は、同期整流を備えたデュアルステップダウン、スイッチモード電源(SMPS)コントローラで、バッテリ駆動システムで5V/3.3Vのメイン電源電圧を生成します。固定周波数で最適にインタリーブして動作するため、最低入力電圧から26Vの最大入力電圧まで、入力リップル電流は最小限に抑えられます。最適な40/60インタリーブによって、入力電圧はデューティサイクルオーバラップが発生する前に8.3Vまで低下させることができます。それに対して180°逆位相レギュレータでは、デューティサイクルオーバラップは入力が10Vを下回ったときに発生します。検出抵抗器を使用する出力電流の検出によって正確に電流を制限することができます。一方、無損失インダクタ電流検出を使用すると、電力損失を減少させることができます。

内蔵の5Vおよび3.3Vリニアレギュレータは、MAX1533/MAX1537とそのゲートドライバ、および外付けのキープアライブ負荷に対して、合計100mAまでの電力を供給します。メインPWMレギュレータがレギュレーション中は、自動ブートストラップスイッチが内蔵のリニアレギュレータへバイパスし、各リニア出力から最大200mAの電流を供給します。もう1つの5V～23V可変の内蔵150mAリニアレギュレータは2次巻線を使って、通常、12V電源を供給します。

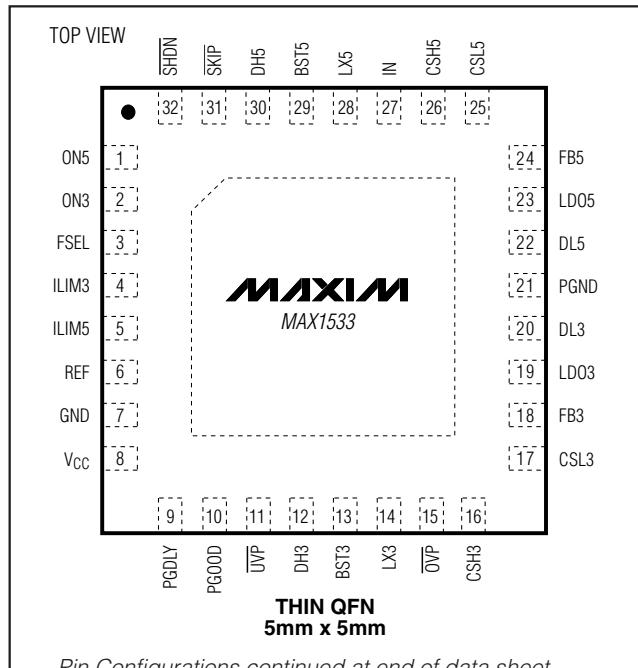

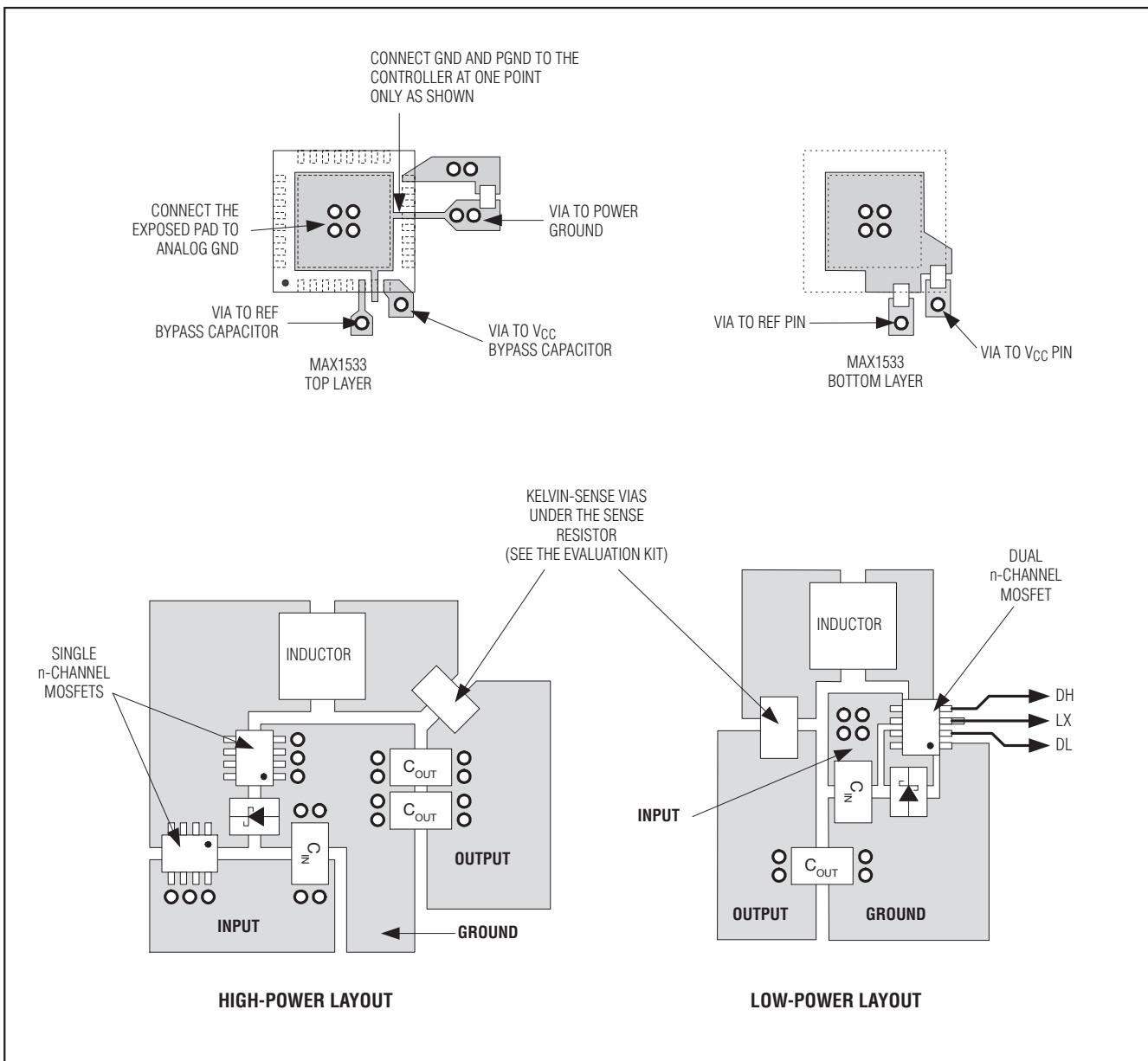

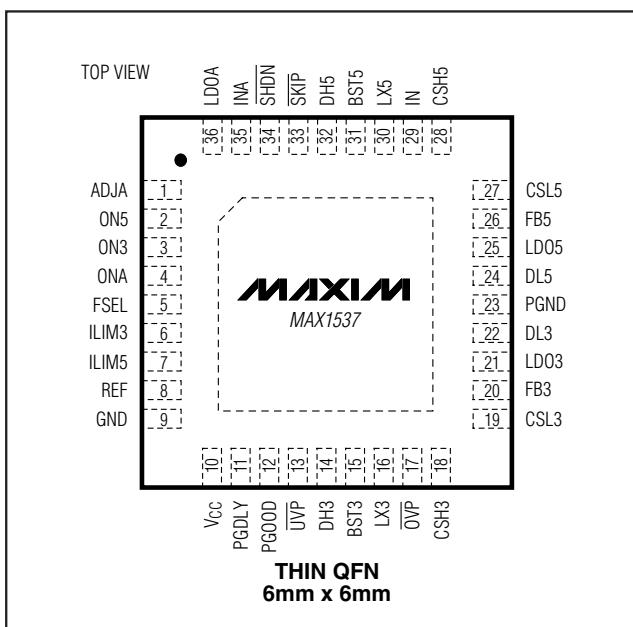

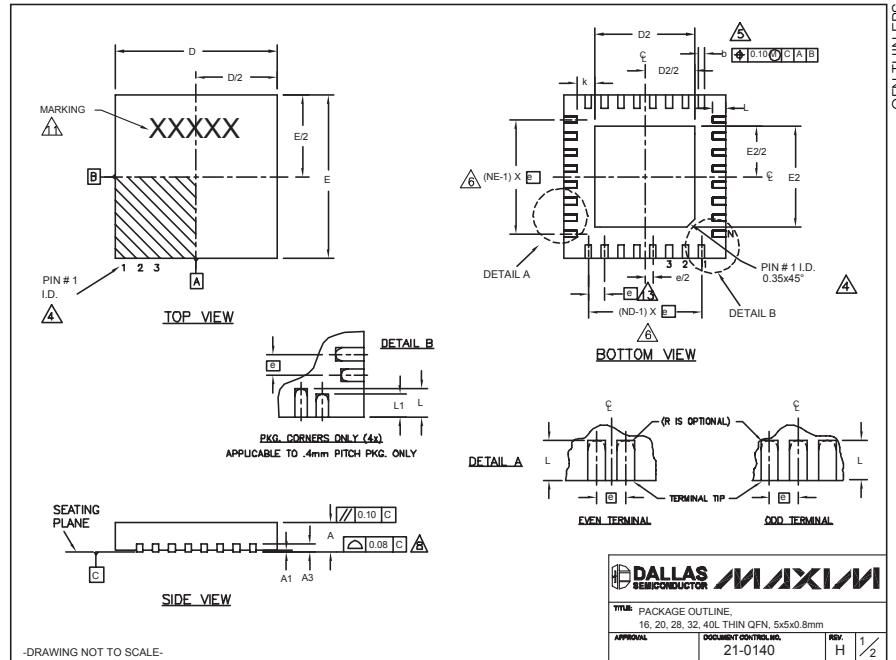

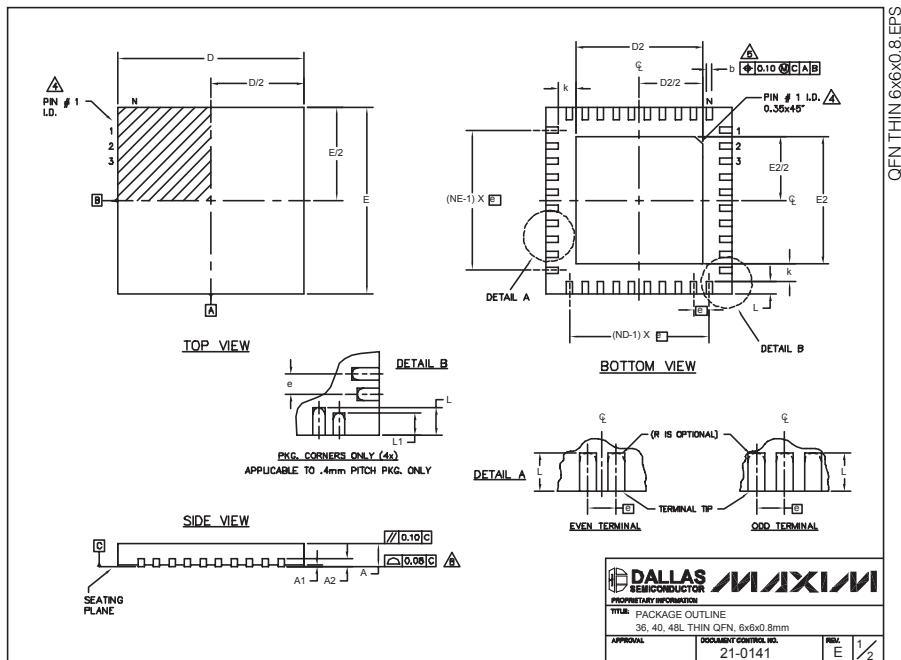

MAX1533/MAX1537は、内蔵のパワーアップシーケンス、パワーグッド(PGOOD)出力、デジタルソフトスタート、およびシャットダウン時の負電圧を防止する内蔵のソフトシャットダウン出力放電を備えています。MAX1533は32ピン薄型QFN(5mm x 5mm)パッケージで提供され、MAX1537は36ピン薄型QFN(6mm x 6mm)パッケージで提供されます。裏面エクスポートド/パッドによって熱特性が向上するため、要件の厳しいリニアキープアライブアプリケーションにも対応します。

## アプリケーション

## 2個～4個のリチウムイオン(Li<sup>+</sup>)セル用バッテリ駆動機器

ノートブックおよびサブノートブックコンピュータ

PDAおよびモバイル通信

## 番型

| PART              | TEMP RANGE     | PIN-PACKAGE           |

|-------------------|----------------|-----------------------|

| <b>MAX1533ETJ</b> | -40°C to +85°C | 32 Thin QFN 5mm x 5mm |

| MAX1533ETJ+       | -40°C to +85°C | 32 Thin QFN 5mm x 5mm |

| <b>MAX1537ETX</b> | -40°C to +85°C | 36 Thin QFN 6mm x 6mm |

| MAX1537ETX+       | -40°C to +85°C | 36 Thin QFN 6mm x 6mm |

+は鉛フリーパッケージを示します。

Dual ModeはMaxim Integrated Products, Inc.の商標です。

## 特長

- ◆ 固定周波数、電流モード制御

- ◆ 40/60の最適なインタリーブ

- ◆ 正確な差動電流検出入力

- ◆ 100mA負荷能力を備えた内蔵の5Vおよび3.3Vリニアレギュレータ

- ◆ 補助の12Vまたは可変150mAリニアレギュレータ(MAX1537のみ)

- ◆ Dual Mode™ フィードバック採用—3.3V/5V固定または可変出力(Dual Mode)電圧

- ◆ スイッチング周波数：200kHz/300kHz/500kHz

- ◆ 汎用パワーアップシーケンス

- ◆ 調整可能な過電圧および低電圧保護

- ◆ 入力電圧範囲：6V～26V

- ◆ リファレンス出力：2V $\pm$ 0.75%

- ◆ パワーグッド出力

- ◆ ソフトシャットダウン

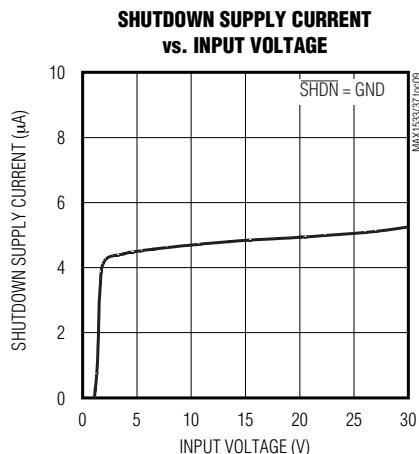

- ◆ シャットダウン電流：5 $\mu$ A(typ)

## ピン配置

*Pin Configurations continued at end of data sheet.*

# ノートブックコンピュータ用 高効率、5出力、メイン電源コントローラ

## ABSOLUTE MAXIMUM RATINGS

|                                                                      |                                    |                                                            |                                    |

|----------------------------------------------------------------------|------------------------------------|------------------------------------------------------------|------------------------------------|

| IN, $\overline{\text{SHDN}}$ , $\text{INA}$ , $\text{LDOA}$ to GND   | -0.3V to +30V                      | LX5 to BST5                                                | -6V to +0.3V                       |

| GND to PGND                                                          | -0.3V to +0.3V                     | DH5 to LX5                                                 | -0.3V to ( $\text{VBST5} + 0.3V$ ) |

| $\text{LDO5}$ , $\text{LDO3}$ , $\text{VCC}$ to GND                  | -0.3V to +6V                       | $\text{LDO3}$ , $\text{LDO5}$ Short Circuit to GND         | Momentary                          |

| $\text{ILIM3}$ , $\text{ILIM5}$ , $\text{PGDLY}$ to GND              | -0.3V to +6V                       | REF Short Circuit to GND                                   | Momentary                          |

| $\text{CSL3}$ , $\text{CSH3}$ , $\text{CSL5}$ , $\text{CSH5}$ to GND | -0.3V to +6V                       | $\text{INA}$ Shunt Current                                 | +15mA                              |

| $\text{ON3}$ , $\text{ON5}$ , $\text{FB3}$ , $\text{FB5}$ to GND     | -0.3V to +6V                       | Continuous Power Dissipation ( $T_A = +70^\circ\text{C}$ ) |                                    |

| $\text{SKIP}$ , $\text{OVP}$ , $\text{UVP}$ to GND                   | -0.3V to +6V                       | 32-Pin TQFN (derate 21.3mW/°C above +70°C)                 | 1702mW                             |

| $\text{PGOOD}$ , $\text{FSEL}$ , $\text{ADJA}$ , $\text{ONA}$ to GND | -0.3V to +6V                       | 36-Pin TQFN (derate 26.3mW/°C above +70°C)                 | 2105mW                             |

| REF to GND                                                           | -0.3V to ( $\text{VCC} + 0.3V$ )   | Operating Temperature Range                                | -40°C to +85°C                     |

| $\text{DL3}$ , $\text{DL5}$ to PGND                                  | -0.3V to ( $\text{VLD05} + 0.3V$ ) | Junction Temperature                                       | +150°C                             |

| $\text{BST3}$ , $\text{BST5}$ to PGND                                | -0.3V to +36V                      | Storage Temperature Range                                  | -65°C to +150°C                    |

| $\text{LX3}$ to $\text{BST3}$                                        | -6V to +0.3V                       | Lead Temperature (soldering, 10s)                          | +300°C                             |

| $\text{DH3}$ to $\text{LX3}$                                         | -0.3V to ( $\text{VBST3} + 0.3V$ ) |                                                            |                                    |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

(Circuit of Figure 1,  $\text{VIN} = 12\text{V}$ , both SMPS enabled,  $\text{VCC} = 5\text{V}$ ,  $\text{FSEL} = \text{REF}$ ,  $\overline{\text{SKIP}} = \text{GND}$ ,  $\text{VILIM}_- = \text{VLD05}$ ,  $\text{VINA} = 15\text{V}$ ,  $\text{VLD0A} = 12\text{V}$ ,  $\text{ILDO5} = \text{ILDO3} = \text{ILDOA} = \text{no load}$ ,  $\text{TA} = 0^\circ\text{C}$  to  $+85^\circ\text{C}$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ\text{C}$ .)

| PARAMETER                           | SYMBOL                       | CONDITIONS                                                                                                                                                                                                                                                                   | MIN   | TYP   | MAX   | UNITS         |

|-------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|---------------|

| <b>INPUT SUPPLIES (Note 1)</b>      |                              |                                                                                                                                                                                                                                                                              |       |       |       |               |

| VIN Input Voltage Range             | $\text{VIN}$                 | LDO5 in regulation                                                                                                                                                                                                                                                           | 6     | 26    |       | V             |

|                                     |                              | $\text{IN} = \text{LDO5}$ , $\text{VOUT5} < 4.43\text{V}$                                                                                                                                                                                                                    | 4.5   | 5.5   |       |               |

| VIN Operating Supply Current        | $\text{I}_{\text{IN}}$       | LDO5 switched over to CSL5                                                                                                                                                                                                                                                   | 15    | 35    |       | $\mu\text{A}$ |

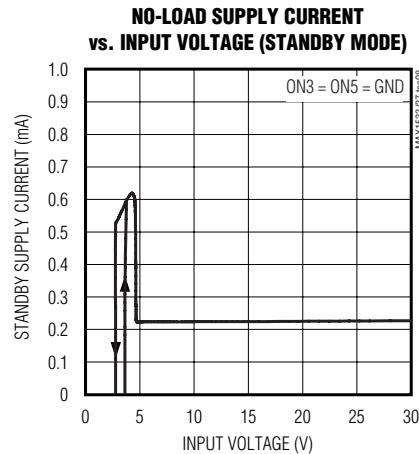

| VIN Standby Supply Current          | $\text{I}_{\text{IN(STBY)}}$ | $\text{VIN} = 6\text{V}$ to $26\text{V}$ , both SMPS off, includes $\overline{\text{SHDN}}$                                                                                                                                                                                  | 100   | 170   |       | $\mu\text{A}$ |

| VIN Shutdown Supply Current         | $\text{I}_{\text{IN(SHDN)}}$ | $\text{VIN} = 6\text{V}$ to $26\text{V}$ , $\overline{\text{SHDN}} = \text{GND}$                                                                                                                                                                                             | 5     | 17    |       | $\mu\text{A}$ |

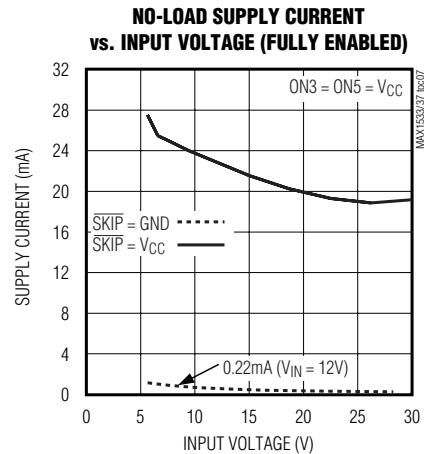

| Quiescent Power Consumption         | $\text{P}_Q$                 | Both SMPS on, $\text{FB3} = \text{FB5} = \overline{\text{SKIP}} = \text{GND}$ , $\text{V}_{\text{CSL3}} = 3.5\text{V}$ , $\text{V}_{\text{CSL5}} = 5.3\text{V}$ , $\text{VINA} = 15\text{V}$ , $\text{ILDOA} = 0$ , $\text{PIN} + \text{PCSL3} + \text{PCSL5} + \text{PINA}$ | 3.5   | 4.5   |       | $\text{mW}$   |

| VCC Quiescent Supply Current        | $\text{I}_{\text{CC}}$       | Both SMPS on, $\text{FB3} = \text{FB5} = \text{GND}$ , $\text{V}_{\text{CSL3}} = 3.5\text{V}$ , $\text{V}_{\text{CSL5}} = 5.3\text{V}$                                                                                                                                       | 1.1   | 2.1   |       | $\text{mA}$   |

| <b>MAIN SMPS CONTROLLERS</b>        |                              |                                                                                                                                                                                                                                                                              |       |       |       |               |

| 3.3V Output Voltage in Fixed Mode   | $\text{VOUT3}$               | $\text{VIN} = 6\text{V}$ to $26\text{V}$ , $\overline{\text{SKIP}} = \text{VCC}$ (Note 2)                                                                                                                                                                                    | 3.280 | 3.33  | 3.380 | V             |

| 5V Output Voltage in Fixed Mode     | $\text{VOUT5}$               | $\text{VIN} = 6\text{V}$ to $26\text{V}$ , $\overline{\text{SKIP}} = \text{VCC}$ (Note 2)                                                                                                                                                                                    | 4.975 | 5.05  | 5.125 | V             |

| Feedback Voltage in Adjustable Mode | $\text{V}_{\text{FB}_-}$     | $\text{VIN} = 6\text{V}$ to $26\text{V}$ , $\text{FB3}$ or $\text{FB5}$ , duty factor = 20% to 80% (Note 2)                                                                                                                                                                  | 0.990 | 1.005 | 1.020 | V             |

| Output-Voltage Adjust Range         |                              | Either SMPS                                                                                                                                                                                                                                                                  | 1.0   | 5.5   |       | V             |

| FB3, FB5 Dual-Mode Threshold        |                              |                                                                                                                                                                                                                                                                              | 0.1   | 0.2   |       | V             |

| Feedback Input Leakage Current      |                              | $\text{V}_{\text{FB3}} = \text{V}_{\text{FB5}} = 1.1\text{V}$                                                                                                                                                                                                                | -0.1  | +0.1  |       | $\mu\text{A}$ |

| DC Load Regulation                  |                              | Either SMPS, $\overline{\text{SKIP}} = \text{VCC}$ , $\text{I}_{\text{LOAD}} = 0$ to full load                                                                                                                                                                               | -0.1  |       |       | %             |

# ノートブックコンピュータ用 高効率、5出力、メイン電源コントローラ

MAX1533/MAX1537

## ELECTRICAL CHARACTERISTICS (continued)

(Circuit of Figure 1,  $V_{IN} = 12V$ , both SMPS enabled,  $V_{CC} = 5V$ ,  $FSEL = REF$ ,  $\overline{SKIP} = GND$ ,  $V_{ILIM\_} = V_{LDO5}$ ,  $V_{INA} = 15V$ ,  $V_{LDOA} = 12V$ ,  $I_{LDO5} = I_{LDO3} = I_{LDOA} = \text{no load}$ ,  $T_A = 0^\circ\text{C to } +85^\circ\text{C}$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ\text{C}$ .)

| PARAMETER                                 | SYMBOL               | CONDITIONS                                                                      | MIN                                                     | TYP       | MAX        | UNITS         |    |

|-------------------------------------------|----------------------|---------------------------------------------------------------------------------|---------------------------------------------------------|-----------|------------|---------------|----|

| Line-Regulation Error                     |                      | Either SMPS, duty cycle = 10% to 90%                                            |                                                         | 1         |            | %             |    |

| Operating Frequency (Note 1)              | fosc                 | FSEL = GND                                                                      | 170                                                     | 200       | 230        | kHz           |    |

|                                           |                      | FSEL = REF                                                                      | 270                                                     | 300       | 330        |               |    |

|                                           |                      | FSEL = $V_{CC}$                                                                 | 425                                                     | 500       | 575        |               |    |

| Maximum Duty Factor (Note 1)              | D <sub>MAX</sub>     | FSEL = GND                                                                      | 91                                                      | 93        |            | %             |    |

|                                           |                      | FSEL = REF                                                                      | 91                                                      | 93        |            |               |    |

|                                           |                      | FSEL = $V_{CC}$                                                                 | 91                                                      | 93        |            |               |    |

| Minimum On-Time                           | t <sub>ON(MIN)</sub> | (Note 3)                                                                        |                                                         |           | 200        | ns            |    |

| SMPS3 to SMPS5 Phase Shift                |                      | SMPS5 starts after SMPS3                                                        |                                                         |           | 40         | %             |    |

|                                           |                      |                                                                                 |                                                         |           | 144        | Deg           |    |

| <b>CURRENT LIMIT</b>                      |                      |                                                                                 |                                                         |           |            |               |    |

| ILIM <sub>_</sub> Adjustment Range        |                      |                                                                                 | 0.5                                                     | $V_{REF}$ |            | V             |    |

| Current-Sense Input Range                 |                      | CSH <sub>_</sub> , CSL <sub>_</sub>                                             | 0                                                       | 5.5       |            | V             |    |

| Current-Sense Input Leakage Current       |                      | CSH <sub>_</sub> , $V_{CSH\_} = 5.5V$                                           | -1                                                      | +1        |            | $\mu\text{A}$ |    |

| Current-Limit Threshold (Fixed)           | $V_{LIMIT\_}$        | $V_{CSH\_} - V_{CSL\_}$ , ILIM <sub>_</sub> = $V_{CC}$                          | 70                                                      | 75        | 80         | mV            |    |

| Current-Limit Threshold (Adjustable)      | $V_{LIMIT\_}$        | $V_{CSH\_} - V_{CSL\_}$                                                         | $V_{ILIM\_} = 2.00V$                                    | 170       | 200        | 230           | mV |

|                                           |                      |                                                                                 | $V_{ILIM\_} = 1.00V$                                    | 91        | 100        | 109           |    |

|                                           |                      |                                                                                 | $V_{ILIM\_} = 0.50V$                                    | 42        | 50         | 58            |    |

| Current-Limit Threshold (Negative)        | $V_{NEG}$            | $V_{CSH\_} - V_{CSL\_}$ , $\overline{SKIP} = V_{CC}$ , percent of current limit |                                                         |           | -120       | %             |    |

| Current-Limit Threshold (Zero Crossing)   | $V_{ZX}$             | $V_{PGND} - V_{LX\_}$ , $\overline{SKIP} = GND$ , ILIM <sub>_</sub> = $V_{CC}$  |                                                         |           | 3          | mV            |    |

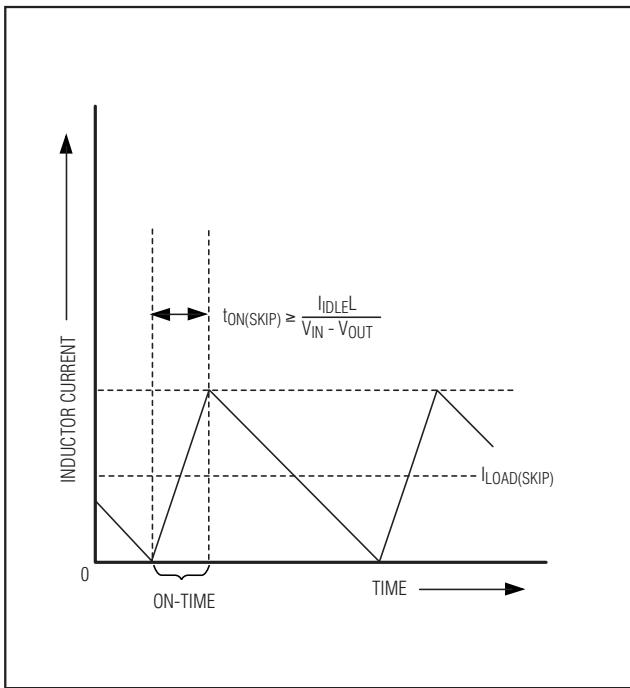

| Idle-Mode™ Threshold                      | VIDLE                | $V_{CSH\_} - V_{CSL\_}$                                                         | ILIM <sub>_</sub> = $V_{CC}$                            | 10        | 16         | 22            | mV |

|                                           |                      |                                                                                 | With respect to current-limit threshold ( $V_{LIMIT}$ ) |           |            | 20            | %  |

| ILIM <sub>_</sub> Leakage Current         |                      | ILIM3 = ILIM5 = GND or $V_{CC}$                                                 | -0.1                                                    |           | +0.1       | $\mu\text{A}$ |    |

| Soft-Start Ramp Time                      | t <sub>SS</sub>      | Measured from the rising edge of ON <sub>_</sub> to full scale                  |                                                         |           | 512 / fosc | s             |    |

| <b>INTERNAL FIXED LINEAR REGULATORS</b>   |                      |                                                                                 |                                                         |           |            |               |    |

| LDO5 Output Voltage                       | $V_{LDO5}$           | ON3 = ON5 = GND, $6V < V_{IN} < 26V$ , $0 < I_{LDO5} < 100\text{mA}$            | 4.80                                                    | 4.95      | 5.10       | V             |    |

| LDO5 Undervoltage-Lockout Fault Threshold |                      | Rising edge, hysteresis = 1%                                                    | 3.75                                                    | 4.0       | 4.25       | V             |    |

| LDO5 Bootstrap Switch Threshold           |                      | Rising edge of CSL5, hysteresis = 1%                                            | 4.41                                                    |           | 4.75       | V             |    |

| LDO5 Bootstrap Switch Resistance          |                      | LDO5 to CSL5, $V_{CSL5} = 5V$ , $I_{LDO5} = 50\text{mA}$                        |                                                         | 0.75      | 3          | $\Omega$      |    |

Idle ModeはMaxim Integrated Products, Inc.の商標です。

# ノートブックコンピュータ用 高効率、5出力、メイン電源コントローラ

## ELECTRICAL CHARACTERISTICS (continued)

(Circuit of Figure 1,  $V_{IN} = 12V$ , both SMPS enabled,  $V_{CC} = 5V$ ,  $FSEL = REF$ ,  $\overline{SKIP} = GND$ ,  $V_{ILIM\_} = V_{LDO5}$ ,  $V_{INA} = 15V$ ,  $V_{LDOA} = 12V$ ,  $I_{LDO5} = I_{LDO3} = I_{LDOA} = \text{no load}$ ,  $T_A = 0^\circ\text{C}$  to  $+85^\circ\text{C}$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ\text{C}$ .)

| PARAMETER                                                  | SYMBOL     | CONDITIONS                                                  | MIN  | TYP  | MAX  | UNITS    |

|------------------------------------------------------------|------------|-------------------------------------------------------------|------|------|------|----------|

| LDO3 Output Voltage                                        | $V_{LDO3}$ | Standby mode, $6V < V_{IN} < 26V$ , $0 < I_{LOAD} < 100mA$  | 3.20 | 3.35 | 3.42 | V        |

| LDO3 Bootstrap Switch Threshold                            |            | Rising edge of CSL3, hysteresis = 1%                        | 2.83 |      | 3.10 | V        |

| LDO3 Bootstrap Switch Resistance                           |            | LDO3 to CSL3, $V_{CSL3} = 3.2V$ , $I_{LDO3} = 50mA$         |      | 1    | 3    | $\Omega$ |

| Short-Circuit Current                                      |            | $LDO3 = LDO5 = GND$ , $CSL3 = CSL5 = GND$                   |      | 150  | 220  | mA       |

| Short-Circuit Current (Switched Over to CSL <sub>—</sub> ) |            | $LDO3 = LDO5 = GND$ , $V_{CSL3} > 3.1V$ , $V_{CSL5} > 4.7V$ | 250  |      |      | mA       |

### AUXILIARY LINEAR REGULATOR (MAX1537 ONLY)

|                                              |                 |                                                                            |      |      |      |         |

|----------------------------------------------|-----------------|----------------------------------------------------------------------------|------|------|------|---------|

| LDOA Voltage Range                           | $V_{LDOA}$      |                                                                            | 5    | 23   | V    |         |

| INA Voltage Range                            | $V_{INA}$       |                                                                            | 6    | 24   | V    |         |

| LDOA Regulation Threshold, Internal Feedback |                 | $ADJA = GND$ , $0 < I_{LDOA} < 120mA$ , $V_{INA} > 13V$                    | 11.4 | 12.0 | 12.4 | V       |

| ADJA Regulation Threshold, External Feedback | $V_{ADJA}$      | $0 < I_{LDOA} < 120mA$ , $V_{LDOA} > 5.0V$ and $V_{INA} > V_{LDOA} + 1V$   | 1.94 | 2.00 | 2.06 | V       |

| ADJA Dual-Mode Threshold                     |                 |                                                                            | 0.1  | 0.15 | 0.2  | V       |

| ADJA Leakage Current                         |                 | $V_{ADJA} = 2.1V$                                                          | -0.1 |      | +0.1 | $\mu A$ |

| LDOA Current Limit                           |                 | $V_{LDOA}$ forced to $V_{INA} - 1V$ , $V_{ADJA} = 1.9V$ , $V_{INA} > 6V$   | 150  |      |      | mA      |

| Secondary Feedback Regulation Threshold      |                 | $V_{INA} - V_{LDOA}$                                                       | 0.65 | 0.8  | 0.95 | V       |

| DL Duty Factor                               |                 | $V_{INA} - V_{LDOA} < 0.7V$ , pulse width with respect to switching period |      | 33   |      | %       |

| INA Quiescent Current                        | $I_{INA}$       | $V_{INA} = 24V$ , $I_{LDOA} = \text{no load}$                              |      | 50   | 165  | $\mu A$ |

| INA Shunt Sink Current                       |                 | $V_{INA} = 28V$                                                            | 10   |      |      | mA      |

| INA Leakage Current                          | $I_{INA(SHDN)}$ | $V_{INA} = 5V$ , LDOA disabled                                             |      |      | 30   | $\mu A$ |

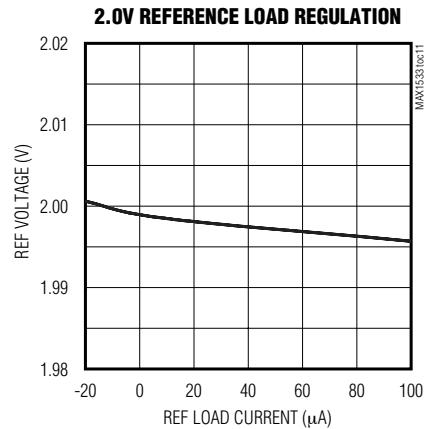

### REFERENCE (REF)

|                           |                 |                                           |       |      |       |   |

|---------------------------|-----------------|-------------------------------------------|-------|------|-------|---|

| Reference Voltage         | $V_{REF}$       | $V_{CC} = 4.5V$ to $5.5V$ , $I_{REF} = 0$ | 1.985 | 2.00 | 2.015 | V |

| Reference Load Regulation |                 | $I_{REF} = -10\mu A$ to $+100\mu A$       | 1.980 |      | 2.020 | V |

| REF Lockout Voltage       | $V_{REF(UVLO)}$ | Rising edge, hysteresis = 350mV           |       | 1.95 |       | V |

### FAULT DETECTION

|                                            |           |                                                                     |   |    |    |         |

|--------------------------------------------|-----------|---------------------------------------------------------------------|---|----|----|---------|

| Output Overvoltage Trip Threshold          |           | $\overline{OVP} = GND$ , with respect to error-comparator threshold | 8 | 11 | 15 | %       |

| Output Overvoltage Fault-Propagation Delay | $t_{OVP}$ | 50mV overdrive                                                      |   | 10 |    | $\mu s$ |

# ノートブックコンピュータ用 高効率、5出力、メイン電源コントローラ

MAX1533/MAX1537

## ELECTRICAL CHARACTERISTICS (continued)

(Circuit of Figure 1,  $V_{IN} = 12V$ , both SMPS enabled,  $V_{CC} = 5V$ ,  $FSEL = REF$ ,  $\overline{SKIP} = GND$ ,  $V_{ILIM\_} = V_{LDO5}$ ,  $V_{INA} = 15V$ ,  $V_{LDOA} = 12V$ ,  $I_{LDO5} = I_{LDO3} = I_{LDOA}$  = no load,  $T_A = 0^\circ C$  to  $+85^\circ C$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ .)

| PARAMETER                                     | SYMBOL          | CONDITIONS                                                  | MIN      | TYP              | MAX      | UNITS      |

|-----------------------------------------------|-----------------|-------------------------------------------------------------|----------|------------------|----------|------------|

| Output Undervoltage-Protection Trip Threshold |                 | With respect to error-comparator threshold                  | 65       | 70               | 75       | %          |

| Output Undervoltage Fault-Propagation Delay   | $t_{UVF}$       | 50mV overdrive                                              |          | 10               |          | $\mu s$    |

| Output Undervoltage-Protection Blanking Time  | $t_{BLANK}$     | From rising edge of $ON\_$                                  |          | 6144 / $f_{OSC}$ |          | s          |

| PGOOD Lower Trip Threshold                    |                 | With respect to error-comparator threshold, hysteresis = 1% | -14      | -10              | -7.5     | %          |

| PGOOD Propagation Delay                       | $t_{PGOOD\_}$   | Falling edge, 50mV overdrive                                |          | 10               |          | $\mu s$    |

| PGOOD Output Low Voltage                      |                 | $I_{SINK} = 4mA$                                            |          |                  | 0.4      | V          |

| PGOOD Leakage Current                         | $I_{PGOOD\_}$   | High state, PGOOD forced to 5.5V                            |          |                  | 1        | $\mu A$    |

| PGDLY Pullup Current                          |                 | $PGDLY = GND$                                               | 4        | 5                | 6        | $\mu A$    |

| PGDLY Pulldown Resistance                     |                 |                                                             |          | 10               | 25       | $\Omega$   |

| PGDLY Trip Threshold                          |                 |                                                             | REF- 0.2 | REF              | REF+ 0.2 | V          |

| Thermal-Shutdown Threshold                    | $T_{SHDN}$      | Hysteresis = $15^\circ C$                                   |          | +160             |          | $^\circ C$ |

| <b>GATE DRIVERS</b>                           |                 |                                                             |          |                  |          |            |

| DH_Gate-Driver On-Resistance                  | $R_{DH}$        | BST_ - LX_ forced to 5V                                     | 1.5      | 5                |          | $\Omega$   |

| DL_Gate-Driver On-Resistance                  | $R_{DL}$        | DL_, high state                                             | 1.7      | 5                |          | $\Omega$   |

|                                               |                 | DL_, low state                                              | 0.6      | 3                |          |            |

| DH_Gate-Driver Source/Sink Current            | $I_{DH}$        | DH forced to 2.5V,<br>BST_ - LX_ forced to 5V               |          | 2                |          | A          |

| DL_Gate-Driver Source Current                 | $I_{DL}$        | DL forced to 2.5V                                           |          | 1.7              |          | A          |

| DL_Gate-Driver Sink Current                   | $I_{DL} (SINK)$ | DL forced to 2.5V                                           |          | 3.3              |          | A          |

| Dead Time                                     | $t_{DEAD}$      | DL_rising                                                   |          | 35               |          | ns         |

|                                               |                 | DH_rising                                                   |          | 26               |          |            |

| LX_, BST_ Leakage Current                     |                 | $V_{BST\_} = V_{LX\_} = 26V$                                | <2       | 20               |          | $\mu A$    |

| <b>INPUTS AND OUTPUTS</b>                     |                 |                                                             |          |                  |          |            |

| Logic Input Voltage                           |                 | $\overline{SKIP}$ , hysteresis = 600mV                      | High     | 2.4              |          | V          |

|                                               |                 |                                                             | Low      |                  | 0.8      |            |

| Fault Enable Logic Input Voltage              |                 | OVP, UVP, ONA                                               | High     | 0.7 x $V_{CC}$   |          | V          |

|                                               |                 |                                                             | Low      |                  | 0.4      |            |

| Logic Input Current                           |                 | OVP, UVP, $\overline{SKIP}$ , ONA                           | -1       |                  | +1       | $\mu A$    |

| SHDN Input Trip Level                         |                 | Rising trip level                                           | 1.10     | 1.6              | 2.20     | V          |

|                                               |                 | Falling trip level                                          | 0.96     | 1                | 1.04     |            |

| ON_ Input Voltage                             |                 | Clear fault level/SMPS off level                            |          |                  | 0.8      | V          |

|                                               |                 | Delay start level (REF)                                     |          | 1.9              | 2.1      |            |

|                                               |                 | SMPS on level                                               |          | 2.4              |          |            |

# ノートブックコンピュータ用 高効率、5出力、メイン電源コントローラ

## ELECTRICAL CHARACTERISTICS (continued)

(Circuit of Figure 1,  $V_{IN} = 12V$ , both SMPS enabled,  $V_{CC} = 5V$ ,  $FSEL = REF$ ,  $\overline{SKIP} = GND$ ,  $V_{ILIM\_} = V_{LDO5}$ ,  $V_{INA} = 15V$ ,  $V_{LDOA} = 12V$ ,  $I_{LDO5} = I_{LDO3} = I_{LDOA} = \text{no load}$ ,  $T_A = 0^\circ\text{C to } +85^\circ\text{C}$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ\text{C}$ .)

| PARAMETER                                               | SYMBOL          | CONDITIONS                                                   | MIN            | TYP | MAX | UNITS         |  |

|---------------------------------------------------------|-----------------|--------------------------------------------------------------|----------------|-----|-----|---------------|--|

| FSEL Three-Level Input Logic                            |                 | High                                                         | $V_{CC} - 0.2$ |     |     | V             |  |

|                                                         |                 | REF                                                          | 1.7            |     |     |               |  |

|                                                         |                 | GND                                                          | 0.4            |     |     |               |  |

| Input Leakage Current                                   |                 | OVP, UV, $\overline{SKIP}$ , ONA, ON3, ON5 = GND or $V_{CC}$ | -1             |     |     | $\mu\text{A}$ |  |

|                                                         |                 | SHDN, 0V or 26V                                              | -1             |     |     |               |  |

|                                                         |                 | $FSEL = GND$ or $V_{CC}$                                     | -3             |     |     |               |  |

| CSL_ Discharge-Mode On-Resistance                       | $R_{DISCHARGE}$ |                                                              | 10             |     |     | $\Omega$      |  |

| CSL_ Synchronous-Rectifier Discharge-Mode Turn-On Level |                 |                                                              | 0.2            | 0.3 | 0.4 | V             |  |

## ELECTRICAL CHARACTERISTICS

(Circuit of Figure 1,  $V_{IN} = 12V$ , both SMPS enabled,  $V_{CC} = 5V$ ,  $FSEL = REF$ ,  $\overline{SKIP} = GND$ ,  $V_{ILIM\_} = V_{LDO5}$ ,  $V_{INA} = 15V$ ,  $V_{LDOA} = 12V$ ,  $I_{LDO5} = I_{LDO3} = I_{LDOA} = \text{no load}$ ,  $T_A = -40^\circ\text{C to } +85^\circ\text{C}$ , unless otherwise noted.) (Note 4)

| PARAMETER                                  | SYMBOL                | CONDITIONS                                                                                                                                                              | MIN   | MAX   | UNITS |  |

|--------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|--|

| <b>INPUT SUPPLIES (Note 1)</b>             |                       |                                                                                                                                                                         |       |       |       |  |

| VIN Input Voltage Range                    | VIN                   | LDO5 in regulation                                                                                                                                                      | 6     | 26    | V     |  |

|                                            |                       | $V_{IN} = LDO5$ , $V_{OUT5} < 4.4V$                                                                                                                                     | 4.5   | 5.5   |       |  |

| VIN Operating Supply Current               | $I_{IN}$              | LDO5 switched over to CSL5, either SMPS on                                                                                                                              | 35    |       |       |  |

| VIN Standby Supply Current                 | $I_{IN(STBY)}$        | $V_{IN} = 6V$ to 26V, both SMPS off, includes $I_{SHDN}$                                                                                                                | 170   |       |       |  |

| VIN Shutdown Supply Current                | $I_{IN(SHDN)}$        | $V_{IN} = 6V$ to 26V                                                                                                                                                    | 17    |       |       |  |

| Quiescent Power Consumption                | PQ                    | Both SMPS on, $FB3 = FB5 = \overline{SKIP} = GND$ , $V_{CSL3} = 3.5V$ , $V_{CSL5} = 5.3V$ , $V_{INA} = 15V$ , $I_{LDOA} = 0$ , $P_{IN} + P_{CSL3} + P_{CSL5} + P_{INA}$ | 4.5   |       |       |  |

| VCC Quiescent Supply Current               | $I_{CC}$              | Both SMPS on, $FB3 = FB5 = GND$ , $V_{CSL3} = 3.5V$ , $V_{CSL5} = 5.3V$                                                                                                 | 2.5   |       |       |  |

| <b>MAIN SMPS CONTROLLERS</b>               |                       |                                                                                                                                                                         |       |       |       |  |

| 3.3V Output Voltage in Fixed Mode          | $V_{OUT3}$            | $V_{IN} = 6V$ to 26V, $\overline{SKIP} = V_{CC}$ (Note 2)                                                                                                               | 3.28  | 3.38  | V     |  |

| 5V Output Voltage in Fixed Mode            | $V_{OUT5}$            | $V_{IN} = 6V$ to 26V, $\overline{SKIP} = V_{CC}$ (Note 2)                                                                                                               | 4.975 | 5.125 | V     |  |

| Feedback Voltage in Adjustable Mode        | $V_{FB3}$ , $V_{FB5}$ | $V_{IN} = 6V$ to 26V, $FB3$ or $FB5$ , duty factor = 20% to 80% (Note 2)                                                                                                | 0.982 | 1.018 | V     |  |

| Output-Voltage Adjust Range                |                       | Either SMPS                                                                                                                                                             | 1.0   | 5.5   | V     |  |

| FB3, FB5 Adjustable-Mode Threshold Voltage |                       | Dual-mode comparator                                                                                                                                                    | 0.1   | 0.2   | V     |  |

# ノートブックコンピュータ用 高効率、5出力、メイン電源コントローラ

## ELECTRICAL CHARACTERISTICS (continued)

(Circuit of Figure 1,  $V_{IN} = 12V$ , both SMPS enabled,  $V_{CC} = 5V$ ,  $FSEL = REF$ ,  $\overline{SKIP} = GND$ ,  $V_{ILIM\_} = V_{LDO5}$ ,  $V_{INA} = 15V$ ,  $V_{LDOA} = 12V$ ,  $I_{LDO5} = I_{LDO3} = I_{LDOA} = \text{no load}$ ,  $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ , unless otherwise noted.) (Note 4)

| PARAMETER                                        | SYMBOL              | CONDITIONS                                                                                            | MIN                        | MAX              | UNITS |    |

|--------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------|----------------------------|------------------|-------|----|

| Operating Frequency (Note 1)                     | fosc                | FSEL = GND                                                                                            | 170                        | 230              | kHz   |    |

|                                                  |                     | FSEL = REF                                                                                            | 240                        | 330              |       |    |

|                                                  |                     | FSEL = V <sub>CC</sub>                                                                                | 375                        | 575              |       |    |

| Maximum Duty Factor (Note 1)                     | D <sub>MAX</sub>    | FSEL = GND                                                                                            | 91                         | %                |       |    |

|                                                  |                     | FSEL = REF                                                                                            | 91                         |                  |       |    |

|                                                  |                     | FSEL = V <sub>CC</sub>                                                                                | 91                         |                  |       |    |

| Minimum On-Time                                  | ton(MIN)            |                                                                                                       |                            | 250              | ns    |    |

| <b>CURRENT LIMIT</b>                             |                     |                                                                                                       |                            |                  |       |    |

| ILIM <sub>_</sub> Adjustment Range               |                     |                                                                                                       | 0.5                        | V <sub>REF</sub> | V     |    |

| Current-Limit Threshold (Fixed)                  | V <sub>LIMIT_</sub> | V <sub>CSH_</sub> - V <sub>CSL_</sub> , ILIM <sub>_</sub> = V <sub>CC</sub>                           | 67                         | 83               | mV    |    |

| Current-Limit Threshold (Adjustable)             | V <sub>LIMIT_</sub> | V <sub>CSH_</sub> - V <sub>CSL_</sub>                                                                 | V <sub>ILIM_</sub> = 2.00V | 170              | 230   | mV |

|                                                  |                     |                                                                                                       | V <sub>ILIM_</sub> = 1.00V | 90               | 110   |    |

|                                                  |                     |                                                                                                       | V <sub>ILIM_</sub> = 0.50V | 40               | 60    |    |

| <b>INTERNAL FIXED LINEAR REGULATORS</b>          |                     |                                                                                                       |                            |                  |       |    |

| LDO5 Output Voltage                              | V <sub>LDO5</sub>   | ON3 = ON5 = GND, 6V < V <sub>IN</sub> < 26V, 0 < I <sub>LDO5</sub> < 100mA                            | 4.8                        | 5.1              | V     |    |

| LDO5 Undervoltage-Lockout Fault Threshold        |                     | Rising edge, hysteresis = 1%                                                                          | 3.75                       | 4.30             | V     |    |

| LDO3 Output Voltage                              | V <sub>LDO3</sub>   | Standby mode, 6V < V <sub>IN</sub> < 28V, 0 < I <sub>LOAD</sub> < 100mA                               | 3.20                       | 3.43             | V     |    |

| <b>AUXILIARY LINEAR REGULATOR (MAX1537 ONLY)</b> |                     |                                                                                                       |                            |                  |       |    |

| LDOA Voltage Range                               | V <sub>LDOA</sub>   |                                                                                                       | 5                          | 23               | V     |    |

| INA Voltage Range                                | V <sub>INA</sub>    |                                                                                                       | 6                          | 24               | V     |    |

| LDOA Regulation Threshold, Internal Feedback     |                     | ADJA = GND, 0 < I <sub>LDOA</sub> < 120mA, V <sub>INA</sub> > 13V                                     | 11.40                      | 12.55            | V     |    |

| ADJA Regulation Threshold, External Feedback     | V <sub>ADJA</sub>   | 0 < I <sub>LDOA</sub> < 120mA, V <sub>LDOA</sub> > 5.0V and V <sub>INA</sub> > V <sub>LDOA</sub> + 1V | 1.94                       | 2.08             | V     |    |

| ADJA Dual-Mode Threshold                         |                     | ADJA                                                                                                  | 0.10                       | 0.25             | V     |    |

| Secondary Feedback Regulation Threshold          |                     | V <sub>INA</sub> - V <sub>LDOA</sub>                                                                  | 0.63                       | 0.97             | V     |    |

| INA Quiescent Current                            | I <sub>INA</sub>    | V <sub>INA</sub> = 24V, I <sub>LDOA</sub> = no load                                                   |                            | 165              | µA    |    |

| <b>REFERENCE (REF)</b>                           |                     |                                                                                                       |                            |                  |       |    |

| Reference Voltage                                | V <sub>REF</sub>    | V <sub>CC</sub> = 4.5V to 5.5V, I <sub>REF</sub> = 0                                                  | 1.97                       | 2.03             | V     |    |

MAX1533/MAX1537

# ノートブックコンピュータ用 高効率、5出力、メイン電源コントローラ

## ELECTRICAL CHARACTERISTICS (continued)

(Circuit of Figure 1,  $V_{IN} = 12V$ , both SMPS enabled,  $V_{CC} = 5V$ ,  $FSEL = REF$ ,  $\overline{SKIP} = GND$ ,  $V_{ILIM\_} = V_{LDO5}$ ,  $V_{INA} = 15V$ ,  $V_{LDOA} = 12V$ ,  $I_{LDO5} = I_{LDO3} = I_{LDOA} = \text{no load}$ ,  $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ , unless otherwise noted.) (Note 4)

| PARAMETER                                     | SYMBOL   | CONDITIONS                                                          | MIN            | MAX                 | UNITS    |

|-----------------------------------------------|----------|---------------------------------------------------------------------|----------------|---------------------|----------|

| <b>FAULT DETECTION</b>                        |          |                                                                     |                |                     |          |

| Output Overvoltage Trip Threshold             |          | $\overline{OVP} = GND$ , with respect to error-comparator threshold | +8             | +15                 | %        |

| Output Undervoltage-Protection Trip Threshold |          | With respect to error-comparator threshold                          | +65            | +75                 | %        |

| PGOOD Lower Trip Threshold                    |          | With respect to error-comparator threshold, hysteresis = 1%         | -14.0          | -7.0                | %        |

| PGOOD Output Low Voltage                      |          | $I_{SINK} = 4mA$                                                    |                | 0.4                 | V        |

| PGDLY Pulldown Resistance                     |          |                                                                     |                | 25                  | $\Omega$ |

| PGDLY Trip Threshold                          |          |                                                                     | REF-<br>0.2    | REF+<br>0.2         | V        |

| <b>GATE DRIVERS</b>                           |          |                                                                     |                |                     |          |

| DH_Gate-Driver On-Resistance                  | $R_{DH}$ | BST_- LX_ forced to 5V                                              |                | 5                   | $\Omega$ |

| DL_Gate-Driver On-Resistance                  | $R_{DL}$ | DL_, high state                                                     |                | 5                   | $\Omega$ |

|                                               |          | DL_, low state                                                      |                | 3                   |          |

| <b>INPUTS AND OUTPUTS</b>                     |          |                                                                     |                |                     |          |

| Logic Input Voltage                           |          | $\overline{SKIP}$ , hysteresis = 600mV                              | High           | 2.4                 | V        |

|                                               |          |                                                                     | Low            | 0.8                 |          |

| Fault Enable Logic Input Voltage              |          | $\overline{OVP}$ , $\overline{UVP}$ , $ONA$                         | High           | $0.7 \times V_{CC}$ | V        |

|                                               |          |                                                                     | Low            | 0.4                 |          |

| SHDN Input Trip Level                         |          | Rising trip level                                                   | 1.1            | 2.2                 | V        |

|                                               |          | Falling trip level                                                  | 0.95           | 1.05                |          |

| ON_ Input Voltage                             |          | Clear fault level                                                   |                | 0.8                 | V        |

|                                               |          | SMPS off level                                                      |                | 1.6                 |          |

|                                               |          | Delay start level (REF)                                             | 1.9            | 2.1                 |          |

|                                               |          | SMPS on level                                                       |                | 2.4                 |          |

| FSEL Three-Level Input Logic                  |          | High                                                                | $V_{CC} - 0.2$ |                     | V        |

|                                               |          | REF                                                                 | 1.7            | 2.3                 |          |

|                                               |          | GND                                                                 | 0.4            |                     |          |

**Note 1:** The MAX1533/MAX1537 cannot operate over all combinations of frequency, input voltage ( $V_{IN}$ ), and output voltage. For large input-to-output differentials and high-switching frequency settings, the required on-time may be too short to maintain the regulation specifications. Under these conditions, a lower operating frequency must be selected. The minimum on-time must be greater than 150ns, regardless of the selected switching frequency. On-time and off-time specifications are measured from 50% point to 50% point at the DH\_ pin with  $LX_ = GND$ ,  $V_{BST\_} = 5V$ , and a 250pF capacitor connected from DH\_ to LX\_. Actual in-circuit times may differ due to MOSFET switching speeds.

**Note 2:** When the inductor is in continuous conduction, the output voltage has a DC regulation level lower than the error-comparator threshold by 50% of the ripple. In discontinuous conduction ( $\overline{SKIP} = GND$ , light load), the output voltage has a DC regulation level higher than the trip level by approximately 1% due to slope compensation.

**Note 3:** Specifications are guaranteed by design, not production tested.

**Note 4:** Specifications to  $-40^{\circ}\text{C}$  are guaranteed by design, not production tested.

# ノートブックコンピュータ用 高効率、5出力、メイン電源コントローラ

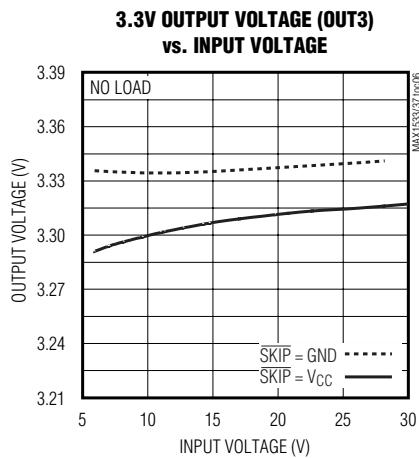

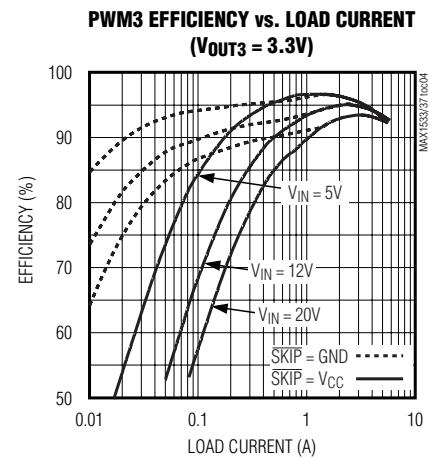

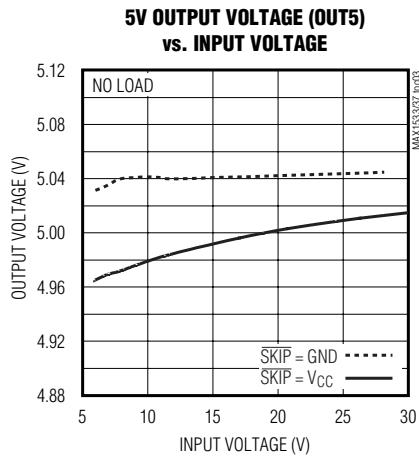

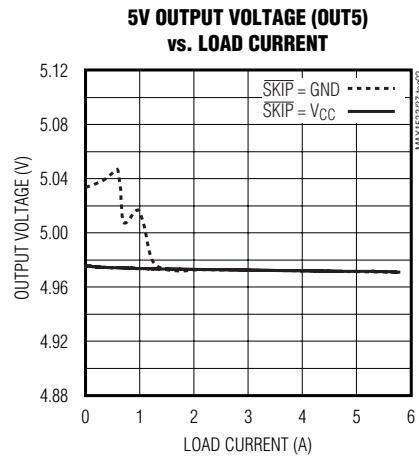

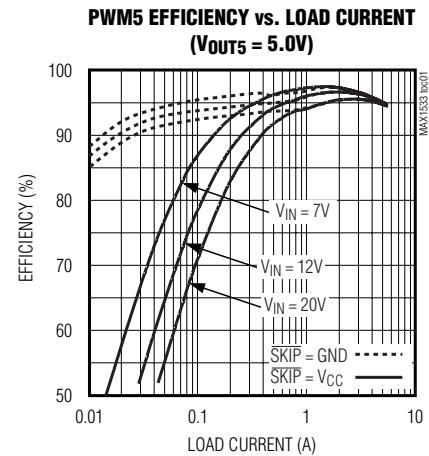

## 標準動作特性

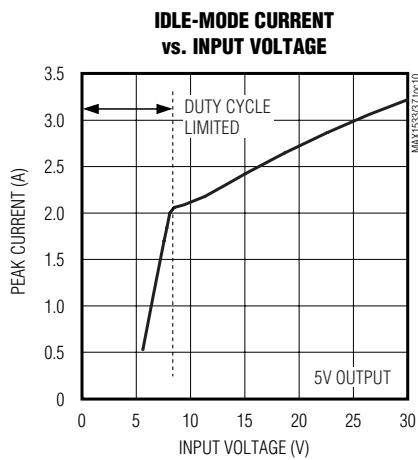

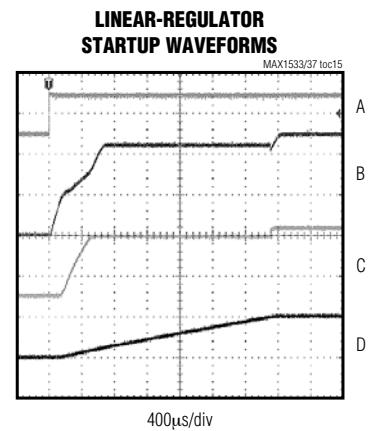

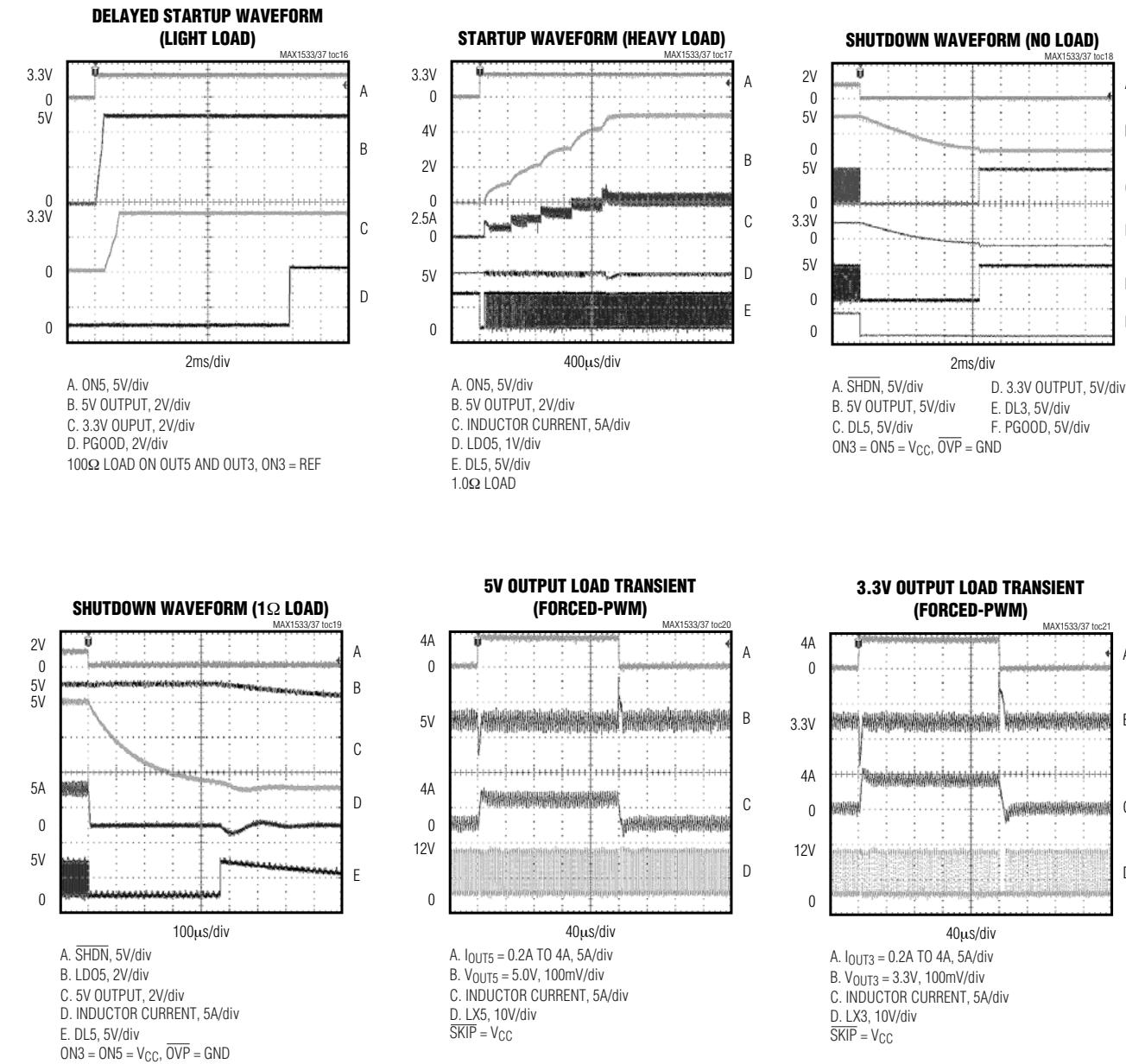

(MAX1537 circuit of Figure 1,  $V_{IN} = 12V$ ,  $LDO5 = V_{CC} = 5V$ ,  $\overline{SKIP} = GND$ ,  $FSEL = REF$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

# ノートブックコンピュータ用 高効率、5出力、メイン電源コントローラ

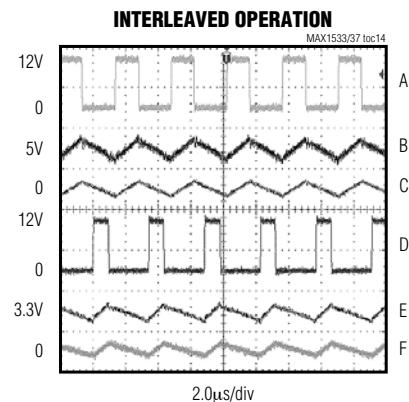

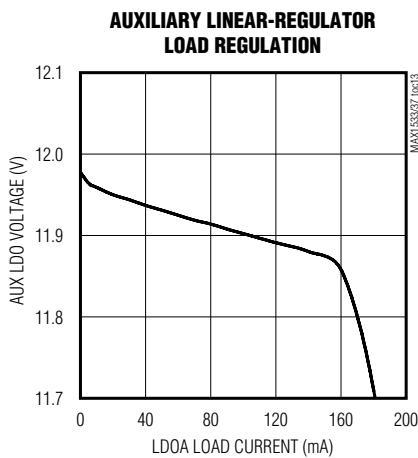

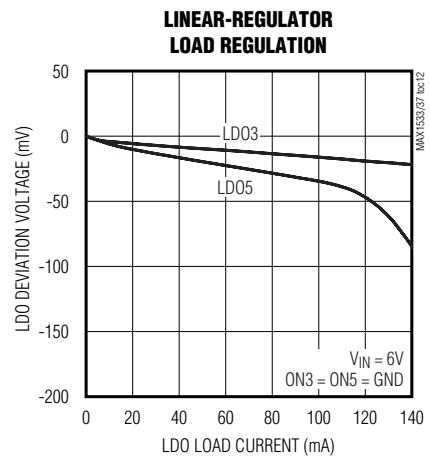

## 標準動作特性(続き)

(MAX1537 circuit of Figure 1,  $V_{IN} = 12V$ ,  $LDO5 = V_{CC} = 5V$ ,  $\overline{SKIP} = GND$ ,  $FSEL = REF$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

- A. LX5, 10V/div

- B. 5V OUTPUT, 100mV/div

- C. PWM5 INDUCTOR CURRENT, 5A/div

- D. LX3, 10V/div

- E. 3.3V OUTPUT, 100mV/div

- F. PWM3 INDUCTOR CURRENT, 5A/div

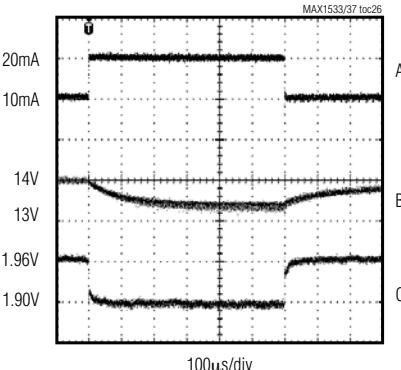

- A. SHDN, 5V/div

- B. LDO5, 2V/div

- C. LD03, 2V/div

- D. REF, 2V/div

- 100Ω LOAD ON LD05 AND LD03

# ノートブックコンピュータ用 高効率、5出力、メイン電源コントローラ

## 標準動作特性(続き)

(MAX1537 circuit of Figure 1,  $V_{IN} = 12V$ ,  $LDO5 = V_{CC} = 5V$ ,  $\overline{SKIP} = GND$ ,  $FSEL = REF$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

# ノートブックコンピュータ用 高効率、5出力、メイン電源コントローラ

## 標準動作特性(続き)

(MAX1537 circuit of Figure 1,  $V_{IN} = 12V$ ,  $LDO5 = V_{CC} = 5V$ ,  $\overline{SKIP} = GND$ ,  $FSEL = REF$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

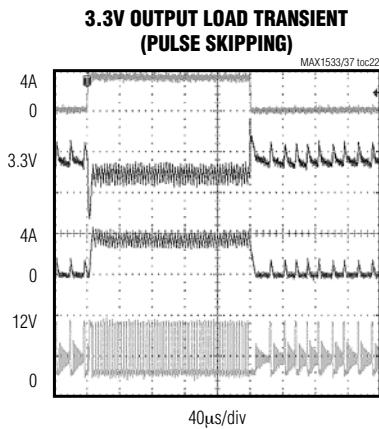

- A.  $I_{OUT3} = 0.2A$  TO 4A, 5A/div

B.  $V_{OUT3} = 3.3V$ , 100mV/div

C. INDUCTOR CURRENT, 5A/div

D. LX3, 10V/div

$\overline{SKIP} = GND$

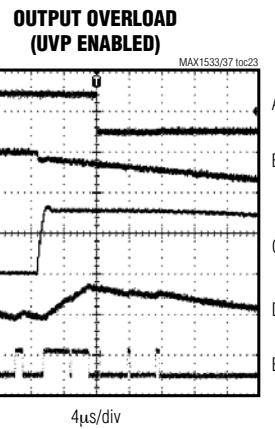

- A. PGOOD2, 5V/div

B. 3.3V OUTPUT, 3.3V/div

C. LOAD (0 TO 30A), 20A/div

D. INDUCTOR CURRENT, 10A/div

E. LX3, 20V/div

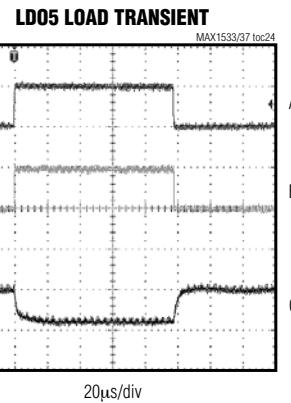

- A. CONTROL SIGNAL, 5V/div

B.  $I_{LDO5} = 1mA$  TO 100mA, 100mA/div

C. LDO5, 50mV/div

ON3 = ON5 = GND

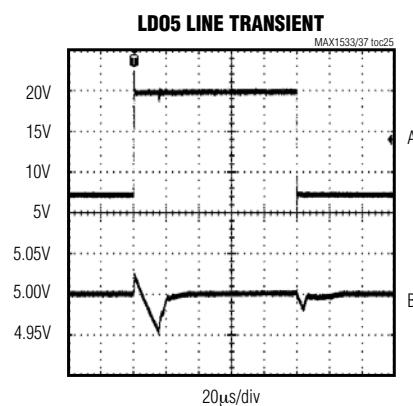

- A. INPUT VOLTAGE ( $V_{IN} = 7V$  TO 20V), 5V/div

B. LDO5 OUTPUT VOLTAGE, 50mV/div

ON3 = ON5 = GND,  $I_{LDO5} = 20mA$

## AUXILIARY LINEAR-REGULATOR LOAD TRANSIENT

- A.  $I_{LDOA} = 10mA$  TO 100mA, 100mA/div

B. INA, 1V/div

C. LDOA, 50mV/div

INA = VOLTAGE GENERATED BY SECONDARY

TRANSFORMER WINDING

# ノートブックコンピュータ用 高効率、5出力、メイン電源コントローラ

## 端子説明

| 端子      |         | 名称              | 機能                                                                                                                                                                                                             |

|---------|---------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX1533 | MAX1537 |                 |                                                                                                                                                                                                                |

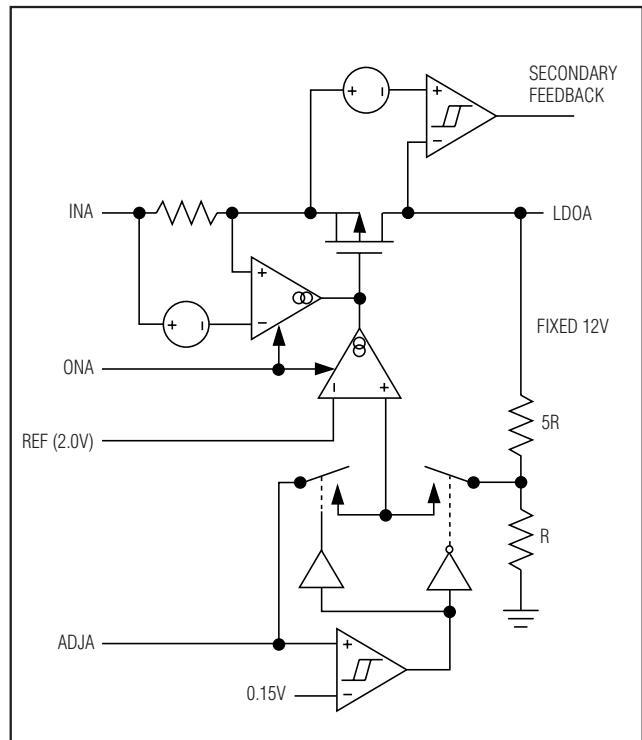

| —       | 1       | ADJA            | 補助フィードバック入力。補助リニアレギュレータ出力電圧を調整するためには、抵抗分圧器をLDOAからアナロググランドに接続してください。ADJAは2Vに安定化されます。内部フィードバックを使って定格12V出力を得るには、ADJAをGNDに接続してください。                                                                                |

| 1       | 2       | ON5             | 5V SMPSイネーブル入力。5V SMPSは、ON5がSMPSのオンレベルよりも大きくなるとイネーブルされ、ON5がSMPSのオフレベルよりも小さくなるとディセーブルされます。ON5をREFに接続すると、3.3V SMPSが安定状態に達してから5V SMPSが始動します(遅延始動)。障害ラッチをリセットするためには、ON5をクリア障害レベル以下に駆動してください。                       |

| 2       | 3       | ON3             | 3.3V SMPSイネーブル入力。3.3V SMPSは、ON3がSMPSのオンレベルよりも大きくなるとイネーブルされ、ON3がSMPSのオフレベルよりも小さくなるとディセーブルされます。ON3をREFに接続すると、5V SMPSが安定状態に達してから3.3V SMPSが始動します(遅延始動)。障害ラッチをリセットするためには、ON3をクリア障害レベル以下に駆動してください。                   |

| —       | 4       | ONA             | LDOAイネーブル入力。ONAがローのとき、LDOAはハイインピーダンスで2次巻線制御がオフになります。ONAがハイのときLDOAはオンになります。所望の自動スタートアップシーケンスが得られるよう、LDO3、LDO5、CSL3、CSL5などの出力に接続してください。                                                                          |

| 3       | 5       | FSEL            | 周波数選択入力。この3レベルロジック入力はコントローラのスイッチング周波数を設定します。下記の標準スイッチング周波数を選択するためには、GND、REF、またはV <sub>CC</sub> に接続してください：<br>V <sub>CC</sub> = 500kHz、REF = 300kHz、GND = 200kHz                                                |

| 4       | 6       | ILIM3           | 3.3V SMPSピーク電流制限スレッショルド調整。ILIM3をV <sub>CC</sub> に接続すると、電流制限スレッショルドがデフォルトの75mVになります。可変モードでは、CSH3とCSL3の間の電流制限スレッショルドが500mV~2.0Vの範囲でILIM3の電圧のちょうど1/10になります。75mVデフォルト値への切替え用ロジクスレッショルドは、およそV <sub>CC</sub> - 1Vです。 |

| 5       | 7       | ILIM5           | 5V SMPSピーク電流制限スレッショルド調整。ILIM5をV <sub>CC</sub> に接続すると、電流制限スレッショルドがデフォルトの75mVになります。可変モードでは、CSH5とCSL5の間の電流制限スレッショルドが500mV~2.0Vの範囲でILIM5の電圧のちょうど1/10になります。75mVデフォルト値への切替え用ロジクスレッショルドは、およそV <sub>CC</sub> - 1Vです。   |

| 6       | 8       | REF             | 2.0Vリファレンス電圧出力。REFを0.1μF以上のセラミックコンデンサでアナロググランドにバイパスしてください。リファレンスは、最大100μAを外部負荷にソースすることができます。REFに負荷が接続されると、REF負荷レギュレーション誤差によって出力電圧精度が低下します。SHDNがローのとき、リファレンスがシャットダウンします。                                        |

| 7       | 9       | GND             | アナロググランド。裏面のパッドをGNDに接続してください。                                                                                                                                                                                  |

| 8       | 10      | V <sub>CC</sub> | アナログ電源入力。20Ωの直列抵抗を介してシステム電源電圧(+4.5V~+5.5V)に接続してください。V <sub>CC</sub> を1μF以上のセラミックコンデンサでアナロググランドにバイパスしてください。                                                                                                     |

| 9       | 11      | PGDLY           | パワーグッドワンショット遅延。PGOODがハイになるのを遅延するためには、PGDLYにタイミングコンデンサを取り付けてください。PGDLYはプルアップ電流が5μAでプルダウン抵抗が10Ωです。プルダウンは、パワーが正常でないとき駆動されます。パワーが正常なとき、プルダウンは切り離されて5μAのプルアップが駆動されます。PGDLYがREFを超ると、PGOODはイネーブルされます。                 |

MAX1533/MAX1537

# ノートブックコンピュータ用 高効率、5出力、メイン電源コントローラ

## 端子説明(続き)

| 端子      |         | 名称              | 機能                                                                                                                                                                                                                                                                                                          |

|---------|---------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX1533 | MAX1537 |                 |                                                                                                                                                                                                                                                                                                             |

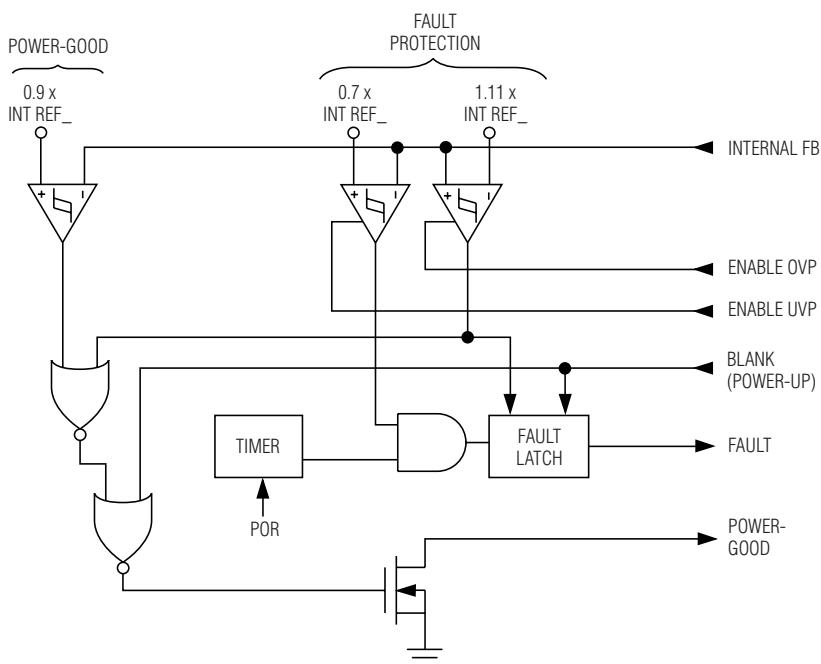

| 10      | 12      | PGOOD           | オープンドレインパワーグッド出力。いずれかの出力がソフトスタートの際またはシャットダウン中に、通常のレギュレーションポイントよりも10%(typ)を超えて低くなるとPGOODはローになります。PGOODは、PGDLYワンショットタイマによって立上りエッジで遅延されます。両方のSMPS出力が安定状態にあるとき、PGOODはハイインピーダンスになります。                                                                                                                            |

| 11      | 13      | UV <sub>P</sub> | 低電圧障害保護制御。定格の70%のデフォルト過電圧スレッショルドを選択するためには、UV <sub>P</sub> をGNDに接続してください。低電圧保護をディセーブルして低電圧障害ラッチをクリアするためには、V <sub>CC</sub> に接続してください。                                                                                                                                                                         |

| 12      | 14      | DH3             | 3.3V SMPSのハイサイドゲートドライバ出力。DH3はLX3からBST3までスイングします。                                                                                                                                                                                                                                                            |

| 13      | 15      | BST3            | 3.3V SMPSのブーストフライングコンデンサ接続部。図6に示すように、外部のコンデンサとダイオードに接続してください。BST3と直列のオプションの抵抗器によって、DH3ブルアップ電流を調整することができます。                                                                                                                                                                                                  |

| 14      | 16      | LX3             | 3.3V SMPSのインダクタ接続部。LX3をインダクタの切替え側に接続してください。LX3は、DH3ハイサイドゲートドライバの下側電源レイルとして働きます。                                                                                                                                                                                                                             |

| 15      | 17      | OV <sub>P</sub> | 過電圧フォルト保護制御。定格よりも+11%高いデフォルト過電圧スレッショルドを選択するためには、OV <sub>P</sub> をGNDに接続してください。過電圧保護をディセーブルして過電圧障害ラッチをクリアするためには、V <sub>CC</sub> に接続してください。                                                                                                                                                                   |

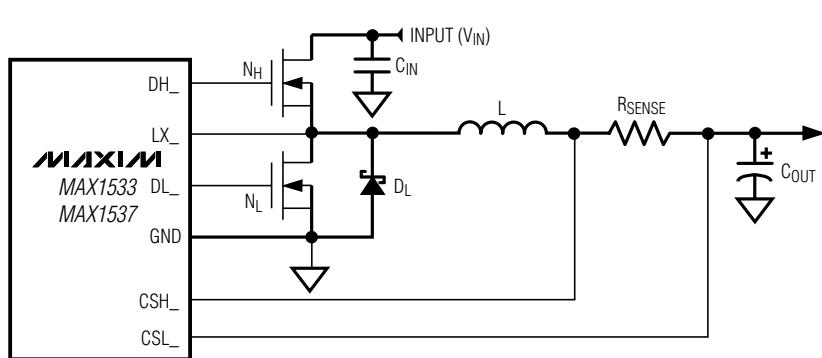

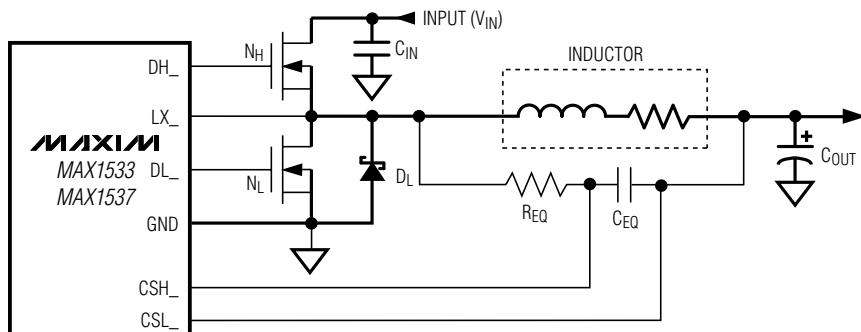

| 16      | 18      | CSH3            | 3.3V SMPSの正電流検出入力。電流検出エレメントの正端子に接続してください。図9に2種類の電流検出オプションを示します。                                                                                                                                                                                                                                             |

| 17      | 19      | CSL3            | 3.3V SMPSの負電流検出入力。電流検出エレメントの負端子に接続してください。図9に2種類の電流検出オプションを示します。CSL3もLDO3のブーストアップ入力として働きます。                                                                                                                                                                                                                  |

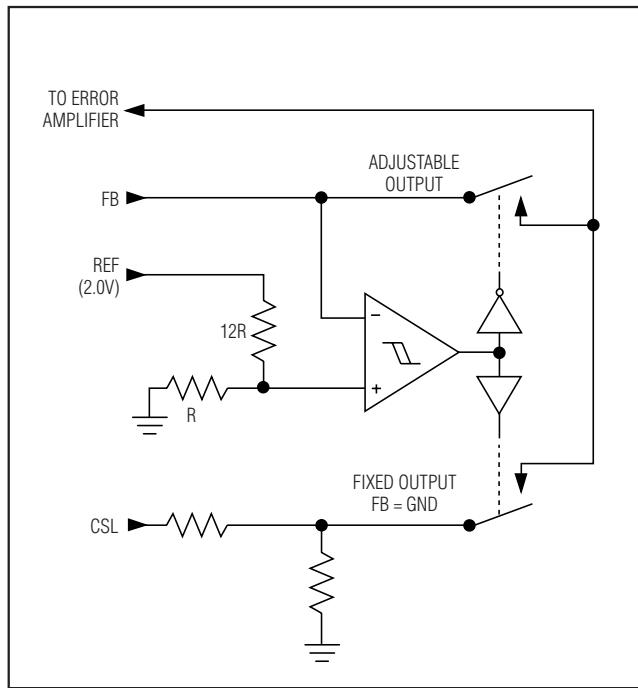

| 18      | 20      | FB3             | 3.3V SMPSのフィードバック入力。固定3.3V出力の場合はGNDに接続してください。可変モードでは、FB3が1Vに安定化されます。                                                                                                                                                                                                                                        |

| 19      | 21      | LDO3            | 3.3V内部リニアレギュレータ出力。2.2μF(min)(1μF/20mA)でバイパスしてください。100mA(min)を供給します。電源はLDO5から供給されます。CSL3が3Vよりも高くなると、リニアレギュレータはシャットダウンして、LDO3は定格負荷が最大200mAの1Ωスイッチを介してCSL3に接続されます。                                                                                                                                             |

| 20      | 22      | DL3             | 3.3V SMPSのローサイドゲートドライバ出力。DL3はPGNDからLDO5までスイングします。                                                                                                                                                                                                                                                           |

| 21      | 23      | PGND            | 電源グランド                                                                                                                                                                                                                                                                                                      |

| 22      | 24      | DL5             | 5V SMPSのローサイドゲートドライバ出力。DL5はPGNDからLDO5までスイングします。                                                                                                                                                                                                                                                             |

| 23      | 25      | LDO5            | 5V内部リニアレギュレータ出力。2.2μF(min)(1μF/20mA)でバイパスしてください。LDO3内部3.3Vリニアレギュレータと同様に、BSTダイオードを介してDL_ローサイドゲートドライバ、DH_ハイサイドドライバに電源を供給し、V <sub>CC</sub> ピンを介してPWMコントローラ、ロジック、およびリファレンスに電源を供給します。外部負荷に対して100mA(min)を供給します(ゲートドライバに対して+25mA)。CSL5が4.5Vよりも高ければ、リニアレギュレータはシャットダウンして、LDO5は定格負荷が最大200mAの0.75Ωスイッチを介してCSL5に接続されます。 |

| 24      | 26      | FB5             | 5V SMPSのフィードバック入力。固定5V出力の場合はGNDに接続してください。可変モードでは、FB5が1Vに安定化されます。                                                                                                                                                                                                                                            |

# ノートブックコンピュータ用 高効率、5出力、メイン電源コントローラ

## 端子説明(続き)

| 端子      |         | 名称   | 機能                                                                                                                                                                                                                                                               |

|---------|---------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX1533 | MAX1537 |      |                                                                                                                                                                                                                                                                  |

| 25      | 27      | CSL5 | 5V SMPSの負電流検出入力。電流検出エレメントの負端子に接続してください。図9に2種類の電流検出オプションを示します。CSL5もLDO5のブートストラップ入力として働きます。                                                                                                                                                                        |

| 26      | 28      | CSH5 | 5V SMPSの正電流検出入力。電流検出エレメントの正端子に接続してください。図9に2種類の電流検出オプションを示します。                                                                                                                                                                                                    |

| 27      | 29      | IN   | スタートアップ回路およびLDO5内部5Vリニアレギュレータの入力。ICの近くにおいて0.22μFでPGNDにバイパスしてください。                                                                                                                                                                                                |

| 28      | 30      | LX5  | 5V SMPSのインダクタ接続部。LX5をインダクタの切替え側に接続してください。LX5は、DH5ハイサイドゲートドライバの下側電源レイルとして働きます。                                                                                                                                                                                    |

| 29      | 31      | BST5 | 5V SMPSのブーストフライングコンデンサ接続部。図6に示すように、外部のコンデンサとダイオードに接続してください。BST5と直列のオプションの抵抗器によって、DH5プレアップ電流を調整することができます。                                                                                                                                                         |

| 30      | 32      | DH5  | 5V SMPSのハイサイドゲートドライバ出力。DH5はLX5からBST5までスイングします。                                                                                                                                                                                                                   |

| 31      | 33      | SKIP | パルススキッピング制御入力。低ノイズ強制PWMモードの場合はV <sub>CC</sub> に接続してください。軽負荷の高効率パルススキッピングモードの場合はGNDに接続してください。                                                                                                                                                                     |

| 32      | 34      | SHDN | シャットダウン制御入力。V <sub>SHDN</sub> がSHDN入力の立下りエッジトリップレベルよりも低い場合、デバイスは消費電流が5μAのシャットダウンモードに入り、また、V <sub>SHDN</sub> がSHDN入力の立上りエッジトリップレベルよりも高くなるまで再始動しません。自動スタートアップの場合は、SHDNをV <sub>IN</sub> に接続してください。SHDNは、抵抗分圧器を介してV <sub>IN</sub> に接続してプログラマブル低電圧ロックアウトを実行することができます。 |

| —       | 35      | INA  | 補助LDOAリニアレギュレータの電源電圧入力。INAは、内蔵シャントによって26Vにクランプされます。                                                                                                                                                                                                              |

| —       | 36      | LDOA | 可変(12V定格)150mA補助リニアレギュレータ出力。入力電源はINAから取り込まれます。LDOAを2.2μF(min)(1μF/20mA)でGNDにバイパスしてください。2次フィードバックスレッショルドは、INA - LDOA = 0.8Vに設定され、5V SMPSのみでDL5をトリガします。ONAをハイにすると、レギュレータ出力と2次レギュレーションがイネーブルされます。PGOODは、LDOAの状態によって影響されません。                                         |

MAX1533/MAX1537

# ノートブックコンピュータ用 高効率、5出力、メイン電源コントローラ

表1. 標準アプリケーション用の部品選択

| COMPONENT                                   | 5A/300kHz                                                                                   | 5A/500kHz                                                                               |

|---------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Input Voltage                               | $V_{IN} = 7V$ to 24V                                                                        | $V_{IN} = 7V$ to 24V                                                                    |

| $C_{IN\_}$ , Input Capacitor                | (2) 10 $\mu$ F, 25V<br>Taiyo Yuden TMK432BJ106KM                                            | (2) 10 $\mu$ F, 25V<br>Taiyo Yuden TMK432BJ106KM                                        |

| $C_{OUT5}$ , Output Capacitor               | 150 $\mu$ F, 6.3V, 40m $\Omega$ , low-ESR capacitor<br>Sanyo 6TPB150ML                      | 150 $\mu$ F, 6.3V, 40m $\Omega$ , low-ESR capacitor<br>Sanyo 6TPB150ML                  |

| $C_{OUT3}$ , Output Capacitor               | 220 $\mu$ F, 4V, 40m $\Omega$ , low-ESR capacitor<br>Sanyo 4TPB220ML                        | 220 $\mu$ F, 4V, 40m $\Omega$ , low-ESR capacitor<br>Sanyo 4TPB220ML                    |

| $N_{H\_}$ High-Side MOSFET                  | Fairchild Semiconductor FDS6612A<br>International Rectifier IRF7807V                        | Fairchild Semiconductor FDS6612A<br>International Rectifier IRF7807V                    |

| $N_{L\_}$ Low-Side MOSFET                   | Fairchild Semiconductor FDS6670S<br>International Rectifier IRF7807VD1                      | Fairchild Semiconductor FDS6670S<br>International Rectifier IRF7807VD1                  |

| $D_{L\_}$ Schottky Rectifier<br>(if needed) | 2A, 30V, 0.45V <sub>f</sub><br>Nihon EC21QS03L                                              | 2A, 30V, 0.45V <sub>f</sub><br>Nihon EC21QS03L                                          |

| Inductor/Transformer                        | $T_1 = 6.8\mu$ H, 1:2 turns Sumida 4749-T132<br>$L_1 = 5.8\mu$ H, 8.6A Sumida CDRH127-5R8NC | 3.9 $\mu$ H<br>Sumida CDRH124-3R9NC                                                     |

| $R_{CS}$                                    | 10m $\Omega$ $\pm 1\%$ , 0.5W resistor<br>IRC LR2010-01-R010F or<br>Dale WSL-2010-R010F     | 10m $\Omega$ $\pm 1\%$ , 0.5W resistor<br>IRC LR2010-01-R010F or<br>Dale WSL-2010-R010F |

表2. 部品メーカー

| SUPPLIER                | WEBSITE                                                          | SUPPLIER                 | WEBSITE                                                                        |

|-------------------------|------------------------------------------------------------------|--------------------------|--------------------------------------------------------------------------------|

| AVX                     | <a href="http://www.avx.com">www.avx.com</a>                     | Panasonic                | <a href="http://www.panasonic.com/industrial">www.panasonic.com/industrial</a> |

| Central Semiconductor   | <a href="http://www.centralsemi.com">www.centralsemi.com</a>     | Sanyo                    | <a href="http://www.secc.co.jp">www.secc.co.jp</a>                             |

| Coilcraft               | <a href="http://www.coilcraft.com">www.coilcraft.com</a>         | Sumida                   | <a href="http://www.sumida.com">www.sumida.com</a>                             |

| Coiltronics             | <a href="http://www.coiltronics.com">www.coiltronics.com</a>     | Taiyo Yuden              | <a href="http://www.t-yuden.com">www.t-yuden.com</a>                           |

| Fairchild Semiconductor | <a href="http://www.fairchildsemi.com">www.fairchildsemi.com</a> | TDK                      | <a href="http://www.component.tdk.com">www.component.tdk.com</a>               |

| International Rectifier | <a href="http://www.irf.com">www.irf.com</a>                     | TOKO                     | <a href="http://www.tokoam.com">www.tokoam.com</a>                             |

| Kemet                   | <a href="http://www.kemet.com">www.kemet.com</a>                 | Vishay (Dale, Siliconix) | <a href="http://www.vishay.com">www.vishay.com</a>                             |

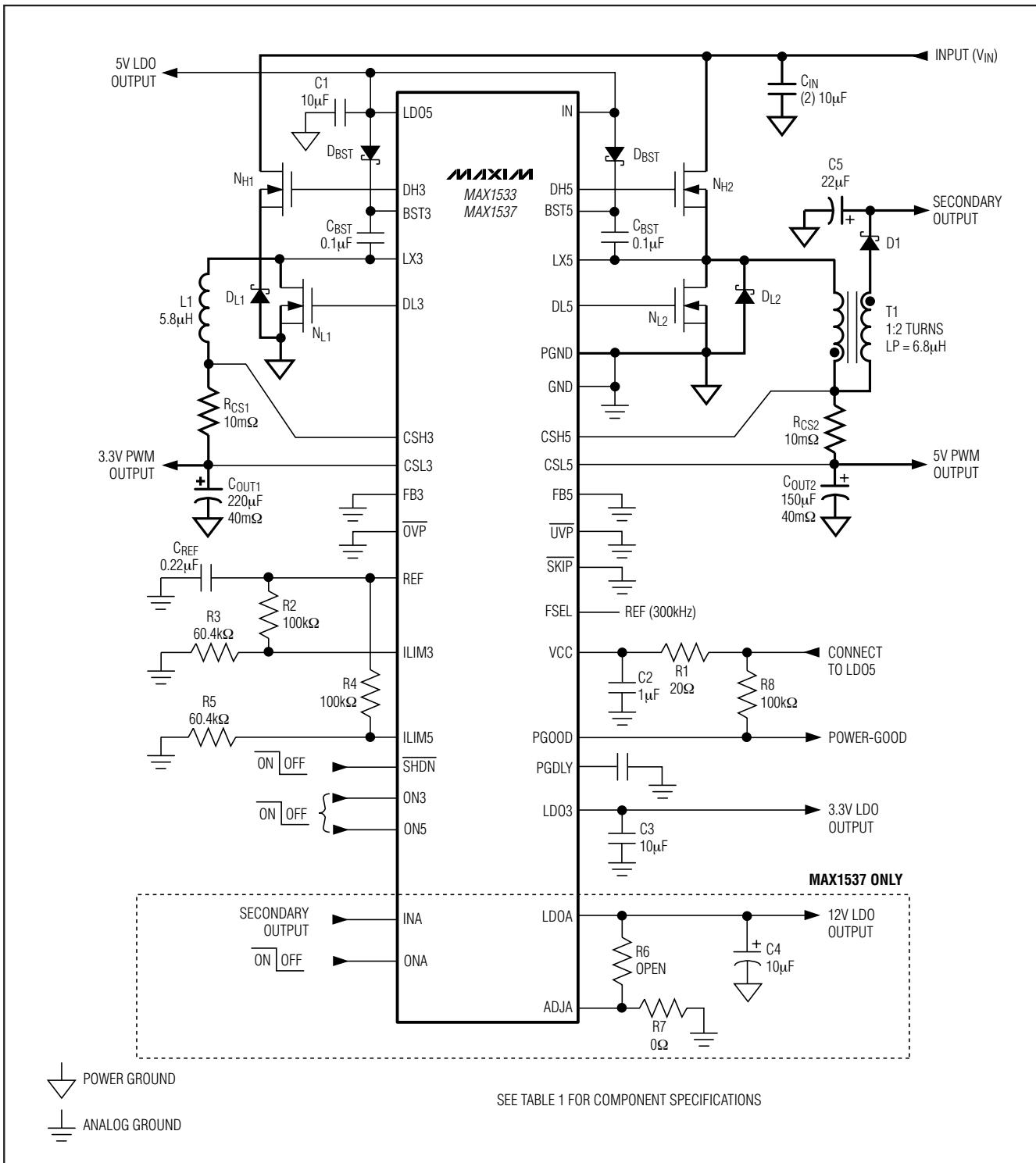

## 詳細

MAX1533/MAX1537の標準動作回路(図1)は、ノートブックコンピュータのメイン電源特有の5V/5Aと3.3V/5Aを生成します。入力電源電圧範囲は7V～24Vです。部品の選択については表1を、部品メーカーについては表2をご覧ください。

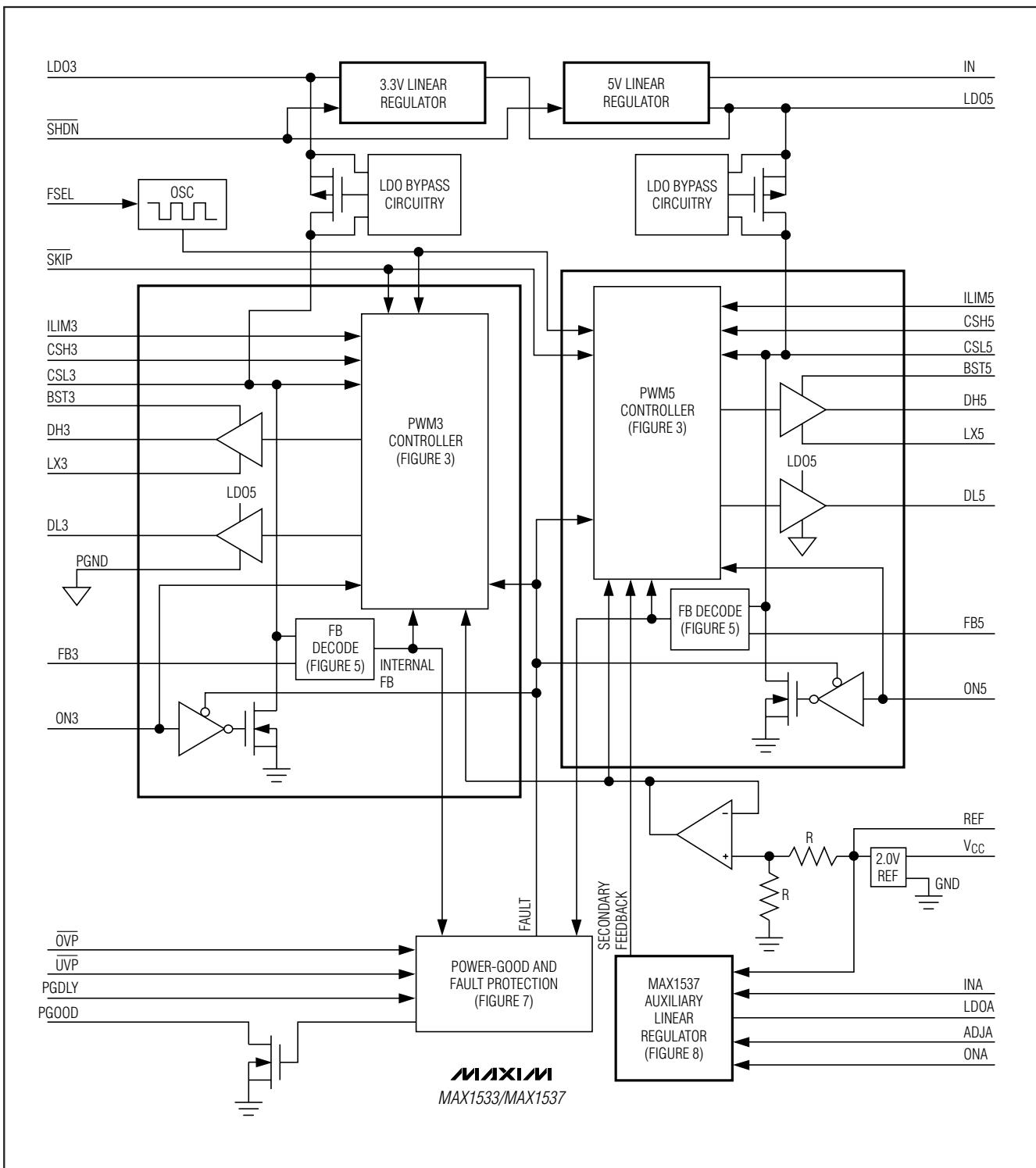

MAX1533/MAX1537は、低電圧電源用に設計された2つのインタリーブ固定周波数ステップダウンコントローラを内蔵しています。最適なインタリーブアーキテクチャは逆位相動作を保証しており、入力コンデンサリップルを抑制します。2つの内蔵LDOは、5Vおよび3.3Vのキープアライブ電源を生成します。MAX1537は、固定12V出力または可変出力に設定可能な補助LDOを備えています。

## 固定リニアレギュレータ(LDO5とLDO3)

2つの内部リニアレギュレータは、固定5V(LDO5)および3.3V(LDO3)の低電力出力を生成します。LDO5は、LDO3、外付けMOSFETのゲートドライバに給電し、SMPSアナログ制御、リファレンス、およびロジックブロックに必要なバイアス電源( $V_{CC}$ )を提供します。LDO5は、MOSFETゲート駆動を含む外部および内部負荷に100mA以上を供給します。MOSFETゲート駆動は、選択されたスイッチング周波数と外付けMOSFETに応じて、通常、5mA～50mAの範囲で変動します。LDO3も、外部負荷に100mA以上を供給します。LDO5とLDO3を2.2 $\mu$ F以上の出力コンデンサでバイパスしてください。ただし、内部および外部負荷電流が20mA増えるごとにこのコンデンサ容量を1.0 $\mu$ Fずつ増やしてください。

# ノートブックコンピュータ用 高効率、5出力、メイン電源コントローラ

MAX1533/MAX1537

図1. MAX1533/MAX1537の標準動作回路

# ノートブックコンピュータ用 高効率、5出力、メイン電源コントローラ

## SMPSからLDOブートストラップへの切替え

5Vのメイン出力電圧がLDO5のブートストラップ切替えスレッショルドよりも高くなると、 $0.75\Omega$ (typ)の内蔵pチャネルMOSFETがCSL5をLDO5に短絡し、同時にLDO5リニアレギュレータをシャットダウンします。同様に、3.3Vのメイン出力電圧がLDO3のブートストラップ切替えスレッショルドよりも高くなると、 $1\Omega$ (typ)の内蔵pチャネルMOSFETがCSL3をLDO3に短絡し、同時にLDO3リニアレギュレータをシャットダウンします。これらの動作によって、デバイスが始動し、内部回路と外部負荷にはバッテリからリニアレギュレータを経由してではなく、出力SMPS電圧から給電されます。ブートストラップは、きわめて低い効率のリニアレギュレータからでなく90%効率のスイッチモードソースからの給電によって、ゲート電荷と自己損失に起因する電力損失を抑制します。LDO\_出力が切替えられると、出力電流制限値は200mAに増加します。

## SMPS 5Vバイアス電源(LDO5とV<sub>CC</sub>)

Aスイッチモード電源(SMPS)には、高電力入力電源(バッテリまたはACアダプタ)のほかに5Vバイアス電源が必要です。この5Vバイアス電源は、MAX1533/MAX1537の内部5Vリニアレギュレータ(LDO5)によって生成されます。始動したこのLDOによって、MAX1533/MAX1537は単独でパワーアップすることができます。ゲートドライバの入力電源は、固定5Vのリニアレギュレータ出力(LDO5)に接続されています。したがって、5V LDO電源はV<sub>CC</sub>(PWMコントローラ)とゲートドライバ電源を供給する必要があるため、必要な最大消費電流は次のようにになります：

$$\begin{aligned} I_{BIAS} &= I_{CC} + f_{SW} (Q_{G(LOW)} + Q_{G(HIGH)}) \\ &= 5\text{mA to } 50\text{mA (typ)} \end{aligned}$$

ここで、I<sub>CC</sub>は1mA(typ)、f<sub>SW</sub>はスイッチング周波数、Q<sub>G(LOW)</sub>とQ<sub>G(HIGH)</sub>はMOSFETのデータシートのV<sub>GS</sub> = 5Vにおける全ゲート電荷仕様制限値です。

## リファレンス(REF)

2Vリファレンスは温度と負荷に対する精度が $\pm 1\%$ であるため、REFは高精度システムリファレンスとして利用されます。REFを $0.22\mu\text{F}$ 以上のセラミックコンデンサでGNDにバイパスしてください。リファレンスは、外部負荷に対して最大 $100\mu\text{A}$ をソースし $10\mu\text{A}$ をシンクすることができます。非常に高い精度の仕様( $\pm 0.5\%$ )がメインSMPS出力電圧に求められる場合、リファレンスには負荷がかかるないようにすべきです。リファレンスに負荷がかかると、LDO5、LDO3、OUT5、およびOUT3の各出力電圧がリファレンスの負荷レギュレーション誤差によってわずかに低下します。

## システムイネーブル/シャットダウン(SHDN)

MAX1533/MAX1537を低電力シャットダウン状態にするためには、SHDNを高精度のSHDN入力立下りエッジトリップレベル以下に駆動してください。シャットダウンモードにあるMAX1533/MAX1537は、自己消費電流がわずか $5\mu\text{A}$ です。シャットダウンモードがアクティブになると、リファレンスはオフとなるため、シャットダウンから抜け出るためのスレッショルドの精度が低下します。スタートアップを確実に行うために、SHDNを2.2V(SHDN入力立上りエッジトリップレベル)以上に駆動してください。自動シャットダウンおよびスタートアップの場合、SHDNをV<sub>IN</sub>に接続してください。特定の入力電圧レベルを検出してデバイスをシャットダウンするために、SHDNに対して正確な1Vの立下りエッジスレッショルドを使用することができます。シャットダウン状態では、1.6Vの立上りエッジスレッショルドがアクティブになり、ほとんどのアプリケーションにとって十分なヒステリシスが得られます。

## SMPS詳細

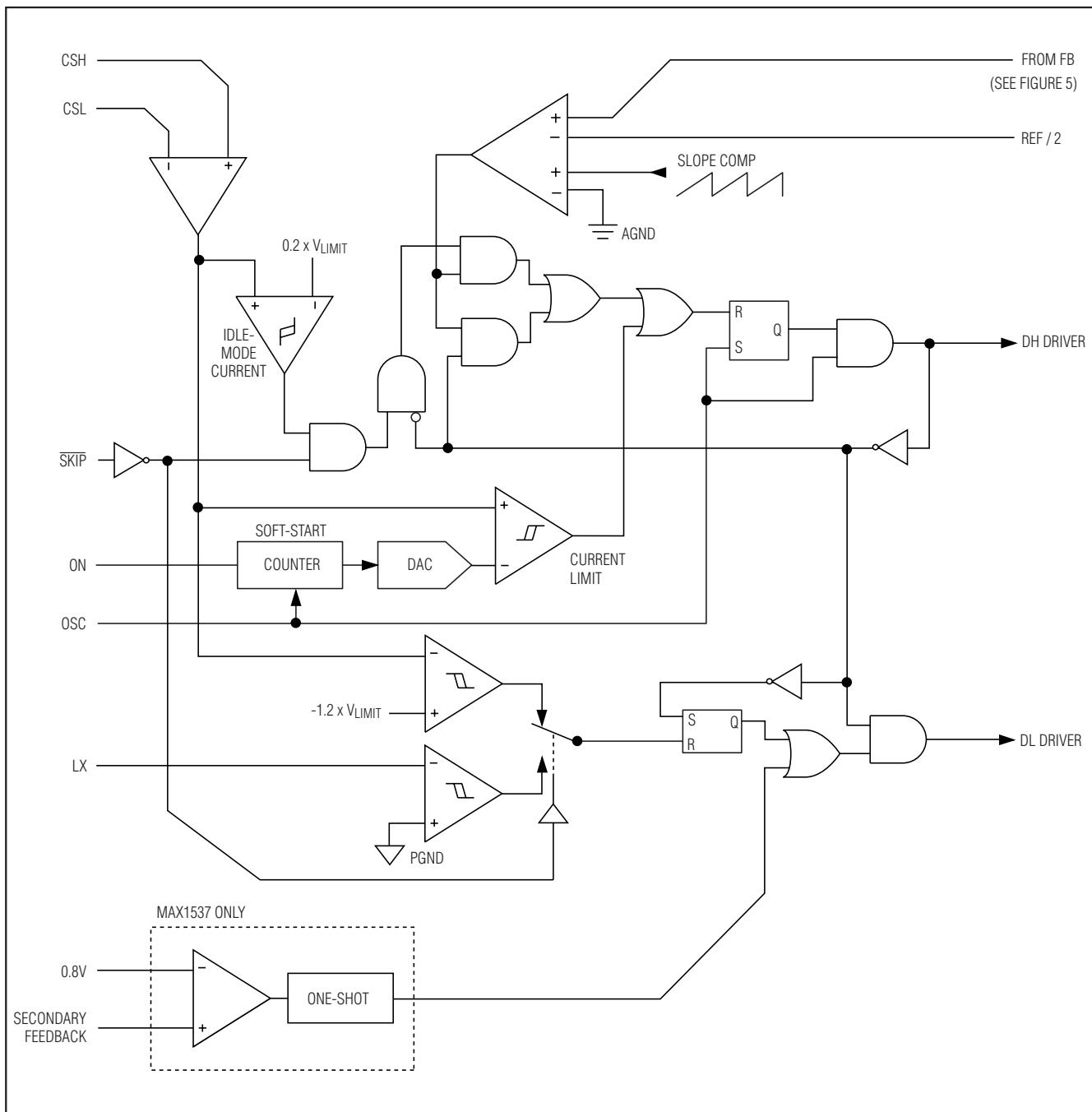

### SMPS POR、UVLO、およびソフトスタート

パワーオンリセット(POR)は、V<sub>CC</sub>が約1Vを超えた時に動作して、低電圧、過電圧、およびサーマルシャットダウンの各障害ラッチをリセットします。また、POR回路は、OVPがデイセーブルされていると(OVP = V<sub>CC</sub>)、ローサイドドライバがローに駆動され、またOVPがイネーブルされていると(OVP = GND)、SMPSコントローラがアクティブになるまでローサイドドライバがハイに駆動されることを保証します。

V<sub>CC</sub>入力の低電圧ロックアウト(UVLO)回路は、5Vバイアス電源(LDO5)が4Vの入力UVLOスレッショルドを下回るとスイッチングを阻止します。5Vバイアス電源(LDO5)がこの入力UVLOスレッショルドを超えて上昇し、コントローラがイネーブルされると、SMPSコントローラはスイッチングを開始し、出力電圧がソフトスタート状態でランプアップを開始します。

内蔵のデジタルソフトスタートは、スタートアップ中に内部の電流制限レベルを徐々に上昇させて入力サージ電流を抑えます。MAX1533/MAX1537では、ソフトスタート期間が5段階に分割されています。最初の段階では、各コントローラがその電流制限値を最大電流制限値のわずか20%に制限します。出力が128クロックサイクル(1/f<sub>OSC</sub>)以内にレギュレーションに達しなければ、ソフトスタートは第2段階に入り電流制限値がさらに20%増加されます。このプロセスは、512クロックサイクル(1/f<sub>OSC</sub>)後に最大電流制限値に達するまで、または出力が定格レギュレーション電圧に達するまでの

ノートブックコンピュータ用

高効率、5出力、メイン電源コントローラ

MAX1533/MAX1537