**MAX14949****5kVRMS絶縁型500kbpsハーフデュプレックス

RS-485/RS-422トランシーバ、±30kV ESD保護および

トランジストライバ内蔵****概要**

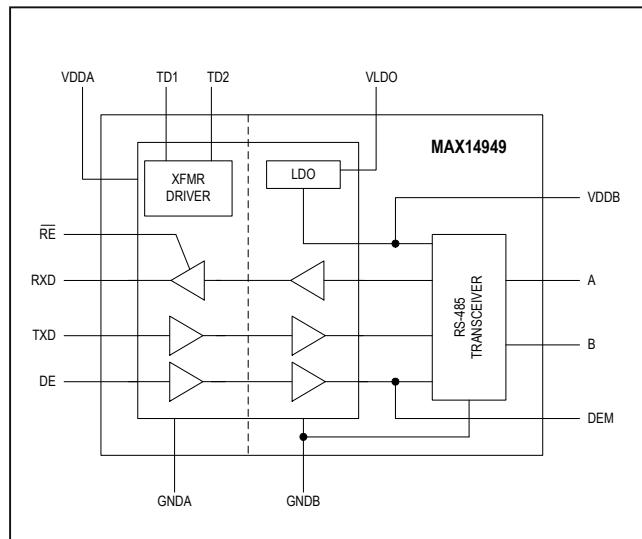

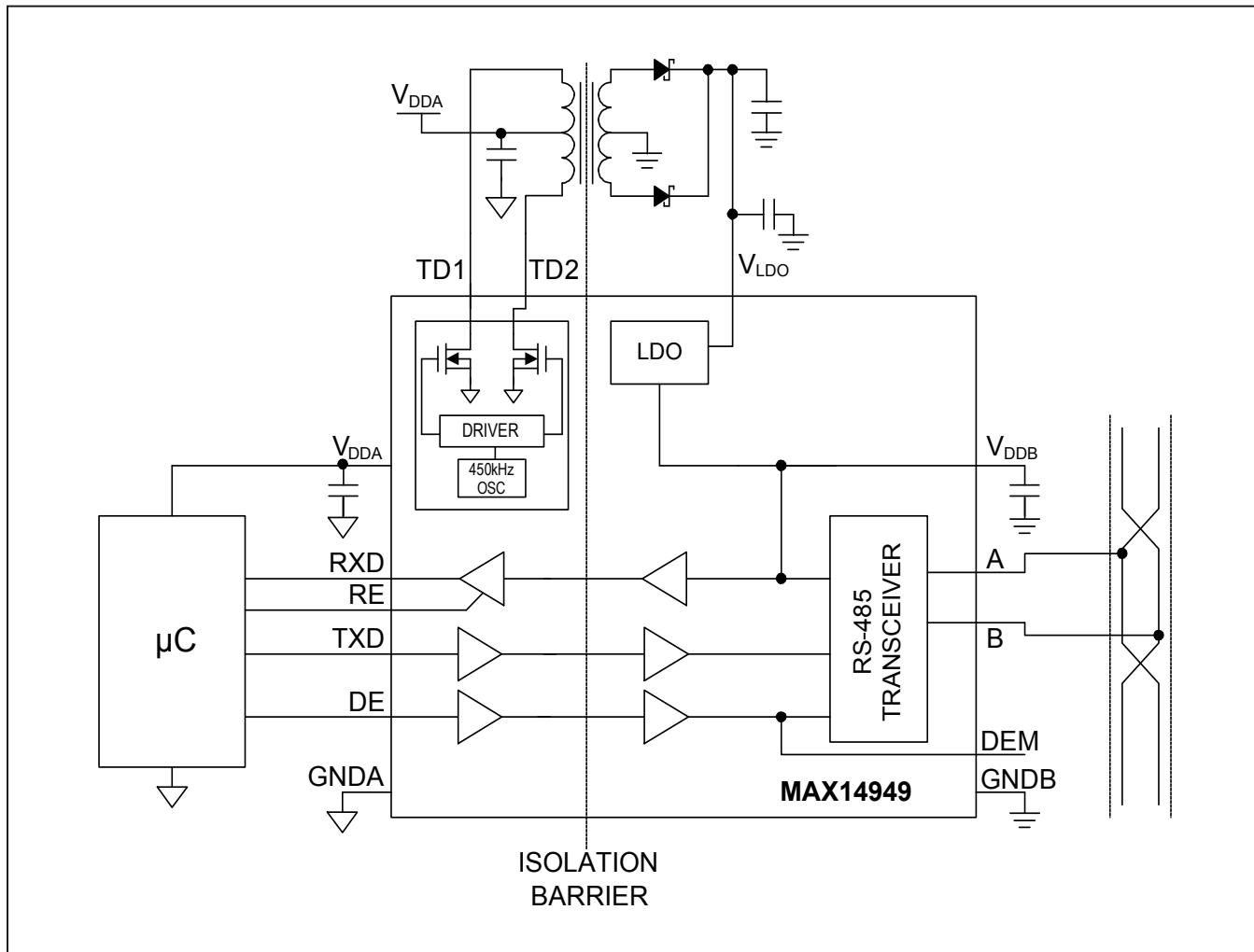

絶縁型RS-485/RS-422トランシーバのMAX14949は、5000VRMS (60秒)のガルバニック絶縁をデバイスのケーブル側(RS-485/RS-422ドライバ/レシーバ側)とUART側の間に提供します。絶縁は、ポート間に大きいグランド電位の差がある場合に、グランドループを切断しノイズを低減することで通信を改善します。このデバイスは、最大500kbpsの堅牢な通信を実現します。

このデバイスは、外部のトランスを使用してトランシーバのケーブル側に電力を伝送するために、450kHzのトランジストライバを内蔵しています。内蔵LDOは、ICのケーブル側に給電するための簡素でスペース効率の良いアーキテクチャを提供します。

このデバイスは、1つのハーフデュプレックスドライバ/レシーバチャネルを内蔵しています。レシーバは1/8ユニット負荷で、共通のバス上に最大256のトランシーバを接続可能です。

内蔵の真のフェイルセーフ回路は、入力が短絡またはオープンの場合に、レシーバ出力がロジックハイになることを確保します。低電圧ロックアウトは、ケーブル側またはUART側の電源が動作レベル以下の場合に、ドライバをディセーブルします。

ドライバ出力/レシーバ入力は、ヒューマンボディモデル(HBM)によって規定されているとおり、ケーブル側のGNDBに対する±30kVの静電気放電(ESD)から保護されています。

MAX14949はワイドボディ16ピンSOICパッケージで提供され、-40°C～+85°Cの温度範囲で動作します。

**アプリケーション**

- 産業オートメーション機器

- プログラマブルロジックコントローラ

- HVAC

- パワーメータ

**申請中の安全規格認定**

- UL (UL1577に準拠)

- cUL (CSA公告5Aに準拠)

- VDE 0884-10

型番はデータシートの最後に記載されています。

**主な特長**

- 高集積によって設計を簡素化

- ケーブル側電源用のLDO内蔵

- ケーブル側への電力伝送用トランジストライバ内蔵：最大80%の効率(150mA負荷時)

- 高性能トランシーバによって柔軟な設計を実現

- RS-485 EIA/TIA-485規格に準拠

- データレート：500kbps (max)

- バス上のデバイス数：最大256

- 内蔵の保護によって堅牢な通信を実現

- ドライバ出力/レシーバ入力のESD保護：±30kV (HBM)

- 絶縁耐圧(V<sub>ISO</sub>)：5kVRMS (60秒)

- 最大繰り返しピーク絶縁電圧(V<sub>IORM</sub>)：1200V<sub>PEAK</sub>

- 最大動作絶縁電圧(V<sub>IOWM</sub>)：848V<sub>RMS</sub>

- 寿命：30年以上(定格動作電圧時)

- IEC 61000-4-5適合サージ耐圧：±10kV

- サーマルシャットダウン

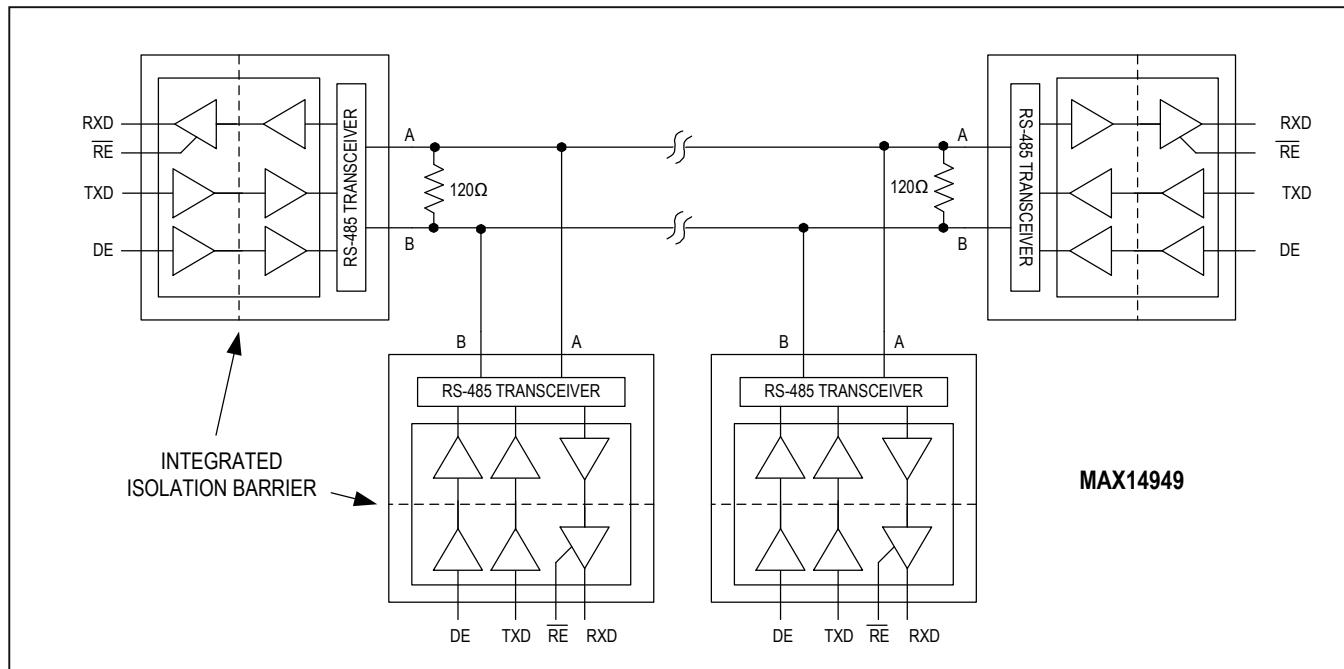

**ファンクションダイアグラム**

**Absolute Maximum Ratings**

|                                                                    |               |                                                            |

|--------------------------------------------------------------------|---------------|------------------------------------------------------------|

| $V_{DDA}$ to GNDA                                                  | -0.3V to +6V  | Continuous Power Dissipation ( $T_A = +70^\circ\text{C}$ ) |

| $V_{DDB}$ to GNDB                                                  | -0.3V to +6V  | 16-pin Wide SOIC                                           |

| $V_{LDO}$ to GNDB                                                  | -0.3V to +16V | (derate 14.1mW/°C above +70°C) 1126.8mW                    |

| TD1, TD2 to GNDA                                                   | -0.3V to +12V | Operating Temperature Range -40°C to +85°C                 |

| TXD, DE, $\bar{RE}$ , RXD to GNDA                                  | -0.3V to +6V  | Junction Temperature +150°C                                |

| DEM to GNDB                                                        | -0.3V to +6V  | Storage Temperature Range -65°C to +150°C                  |

| A, B to GNDB                                                       | -8V to +13V   | Lead Temperature (soldering, 10s) +300°C                   |

| TD1, TD2 Continuous Current                                        | ±1.4A         | Soldering Temperature (reflow) +260°C                      |

| Short-Circuit Duration (RXD to GNDA, A, B, DEM, $V_{DDB}$ to GNDB) | Continuous    |                                                            |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Package Thermal Characteristics (Note 1)**

|                                                          |        |                                                       |        |

|----------------------------------------------------------|--------|-------------------------------------------------------|--------|

| Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) | 71°C/W | Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) | 23°C/W |

|----------------------------------------------------------|--------|-------------------------------------------------------|--------|

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to [www.maximintegrated.com/jp/thermal-tutorial](http://www.maximintegrated.com/jp/thermal-tutorial).

**DC Electrical Characteristics**

( $V_{DDA} - V_{GNDA} = 3.0\text{V}$  to  $5.5\text{V}$ ,  $V_{DDB} - V_{GNDB} = 4.5\text{V}$  to  $5.5\text{V}$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $V_{DDA} - V_{GNDA} = 3.3\text{V}$ ,  $V_{DDB} - V_{GNDB} = 5\text{V}$ ,  $V_{GNDA} = V_{GNDB}$ , and  $T_A = +25^\circ\text{C}$ .) (Note 2, 3)

| PARAMETER                                 | SYMBOL        | CONDITIONS                                                                                                   | MIN  | TYP  | MAX  | UNITS    |

|-------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------|------|------|------|----------|

| <b>POWER</b>                              |               |                                                                                                              |      |      |      |          |

| Supply Voltage                            | $V_{DDA}$     |                                                                                                              | 3.0  | 5.5  |      | V        |

|                                           | $V_{DDB}$     |                                                                                                              | 4.5  | 5.5  |      |          |

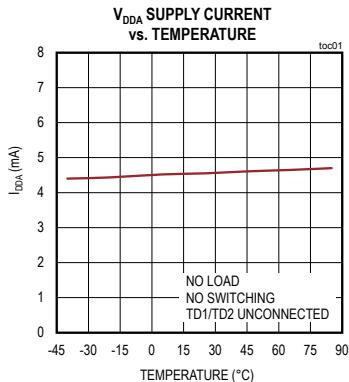

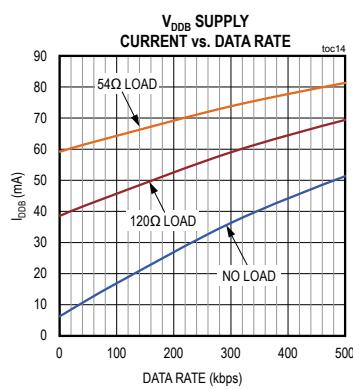

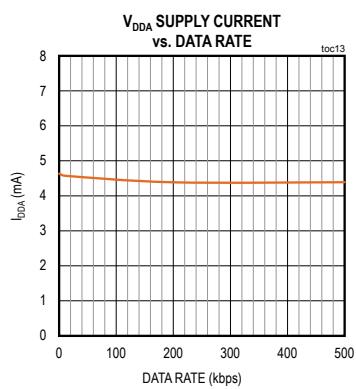

| Supply Current                            | $I_{DDA}$     | $V_{DDA} = 5\text{V}$ , DE = high, $\bar{RE}$ = TXD = low, RXD unconnected, no bus load, TD1/TD2 unconnected |      | 4.7  | 7.7  | mA       |

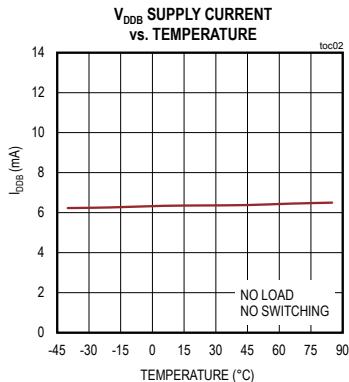

|                                           | $I_{DDB}$     | DE = high, $\bar{RE}$ = TXD = low, RXD unconnected, no bus load, $V_{DDB} = 5\text{V}$                       |      | 6.3  | 12.5 |          |

| Undervoltage-Lockout Threshold            | $V_{UVLOA}$   | $\bar{RE}$ , RXD, DE, TXD, $V_{DDA}$ rising                                                                  | 1.50 | 1.58 | 1.65 | V        |

|                                           | $V_{UVLOB}$   | TD1/TD2 driver, $V_{DDA}$ rising                                                                             | 2.55 | 2.7  | 2.85 |          |

| Undervoltage-Lockout-Threshold Hysteresis | $V_{UVHYSTA}$ | $\bar{RE}$ , RXD, DE, TXD                                                                                    |      | 50   |      | mV       |

|                                           |               | TD1/TD2 driver                                                                                               |      | 200  |      |          |

|                                           | $V_{UVHYSTB}$ |                                                                                                              |      | 200  |      |          |

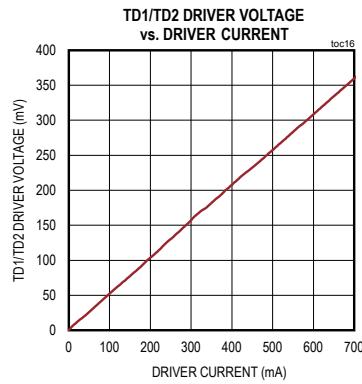

| <b>TRANSFORMER DRIVER</b>                 |               |                                                                                                              |      |      |      |          |

| Output Resistance                         | $R_O$         | TD1/TD2 = low, $I_{OUT} = 300\text{mA}$                                                                      | 0.6  | 1.5  |      | $\Omega$ |

| TD1, TD2 Current Limit                    | $I_{LIM}$     | $4.5\text{V} \leq V_{DDA} \leq 5.5\text{V}$                                                                  | 540  | 785  | 1300 | mA       |

|                                           |               | $3.0\text{V} \leq V_{DDA} \leq 3.6\text{V}$                                                                  | 485  | 730  | 1170 |          |

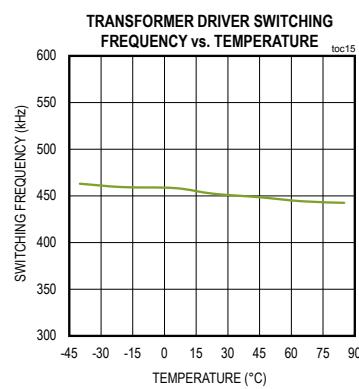

| Switching Frequency                       | $f_{SW}$      |                                                                                                              | 350  | 450  | 550  | kHz      |

| Duty Cycle                                | D             |                                                                                                              |      | 50   |      | %        |

| Crossover Dead Time                       | $t_{DEAD}$    |                                                                                                              |      | 50   |      | ns       |

## DC Electrical Characteristics (continued)

( $V_{DDA} - V_{GNDA} = 3.0V$  to  $5.5V$ ,  $V_{DDB} - V_{GNDB} = 4.5V$  to  $5.5V$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $V_{DDA} - V_{GNDA} = 3.3V$ ,  $V_{DDB} - V_{GNDB} = 5V$ ,  $V_{GNDA} = V_{GNDB}$ , and  $T_A = +25^\circ C$ .) (Note 2, 3)

| PARAMETER                                                         | SYMBOL       | CONDITIONS                                                                      | MIN                | TYP  | MAX  | UNITS |

|-------------------------------------------------------------------|--------------|---------------------------------------------------------------------------------|--------------------|------|------|-------|

| <b>LDO</b>                                                        |              |                                                                                 |                    |      |      |       |

| LDO Supply Voltage                                                | $V_{LDO}$    | Relative to GNDB, LDO is on (Note 4)                                            | 4.68               | 14   |      | V     |

| LDO Supply Current                                                | $I_{LDO}$    | $DE = \text{high}$ , $TXD = \text{low}$ , no bus load,<br>$V_{LDO} = 5.5V$      |                    | 6.4  | 12.9 | mA    |

| LDO Output Voltage                                                | $V_{DDB}$    |                                                                                 | 4.5                | 5    | 5.5  | V     |

| LDO Current Limit                                                 |              |                                                                                 |                    | 300  |      | mA    |

| Load Regulation                                                   |              | $V_{LDO} = 5.68V$ , $I_{LOAD} = 20mA$ to<br>$40mA$                              |                    | 0.19 | 1.7  | mV/mA |

| Line Regulation                                                   |              | $V_{LDO} = 5.68V$ to $14V$ , $I_{LOAD} = 20mA$                                  |                    | 0.12 | 1.8  | mV/V  |

| Dropout Voltage                                                   |              | $V_{LDO} = 4.68V$ , $I_{DDB} = 120mA$                                           |                    | 100  | 180  | mV    |

| Load Capacitance                                                  |              | Nominal value (Note 5)                                                          | 1                  |      | 10   | μF    |

| <b>LOGIC INTERFACE (TXD, RXD, DE, <math>\bar{RE}</math>, DEM)</b> |              |                                                                                 |                    |      |      |       |

| Input High Voltage                                                | $V_{IH}$     | $\bar{RE}$ , TXD, DE to GNDA                                                    | 0.7 x<br>$V_{DDA}$ |      |      | V     |

| Input Low Voltage                                                 | $V_{IL}$     | $\bar{RE}$ , TXD, DE to GNDA                                                    |                    | 0.8  |      | V     |

| Input Hysteresis                                                  | $V_{HYS}$    | $\bar{RE}$ , TXD, DE to GNDA                                                    |                    | 220  |      | mV    |

| Input Capacitance                                                 | $C_{IN}$     | $\bar{RE}$ , TXD, DE, $f = 1MHz$                                                |                    | 2    |      | pF    |

| Input Pullup Current                                              | $I_{PU}$     | TXD                                                                             | -10                | -4.5 | -1.5 | μA    |

| Input Pulldown Current                                            | $I_{PD}$     | DE, $\bar{RE}$                                                                  | 1.5                | 4.5  | 10   | μA    |

| Output Voltage High                                               | $V_{OH}$     | RXD to GNDA, $I_{OUT} = -4mA$                                                   | $V_{DDA}$<br>-0.4  |      |      | V     |

|                                                                   |              | DEM to GNDB, $I_{OUT} = -4mA$                                                   | $V_{DDB}$<br>-0.4  |      |      |       |

| Output Voltage Low                                                | $V_{OL}$     | RXD to GNDA, $I_{OUT} = 4mA$                                                    |                    | 0.40 |      | V     |

|                                                                   |              | DEM to GNDB, $I_{OUT} = 4mA$                                                    |                    | 0.40 |      |       |

| Short-Circuit Output Pullup Current                               | $I_{SH\_PU}$ | $0V \leq V_{RXD} \leq V_{DDA}$ , $V_A - V_B > -50mV$ , $\bar{RE} = \text{low}$  |                    | -42  |      | mA    |

|                                                                   |              | $0V \leq V_{DEM} \leq V_{DDB}$ , $DE = \text{high}$                             |                    | -42  |      |       |

| Short-Circuit Output Pulldown Current                             | $I_{SH\_PD}$ | $0V \leq V_{RXD} \leq V_{DDA}$ , $V_A - V_B < -200mV$ , $\bar{RE} = \text{low}$ |                    | +40  |      | mA    |

|                                                                   |              | $0V \leq V_{DEM} \leq V_{DDB}$ , $DE = \text{low}$                              |                    | +40  |      |       |

| Three-State Output Current                                        | $I_{OZ}$     | $0V \leq V_{RXD} \leq V_{DDA}$ , $\bar{RE} = \text{high}$                       | -1                 | +1   |      | μA    |

## DC Electrical Characteristics (continued)

( $V_{DDA} - V_{GNDA} = 3.0V$  to  $5.5V$ ,  $V_{DDB} - V_{GNDB} = 4.5V$  to  $5.5V$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $V_{DDA} - V_{GNDA} = 3.3V$ ,  $V_{DDB} - V_{GNDB} = 5V$ ,  $V_{GNDA} = V_{GNDB}$ , and  $T_A = +25^\circ C$ .) (Note 2, 3)

| PARAMETER                                                 | SYMBOL            | CONDITIONS                                                       | MIN             | TYP         | MAX  | UNITS |    |

|-----------------------------------------------------------|-------------------|------------------------------------------------------------------|-----------------|-------------|------|-------|----|

| <b>DRIVER</b>                                             |                   |                                                                  |                 |             |      |       |    |

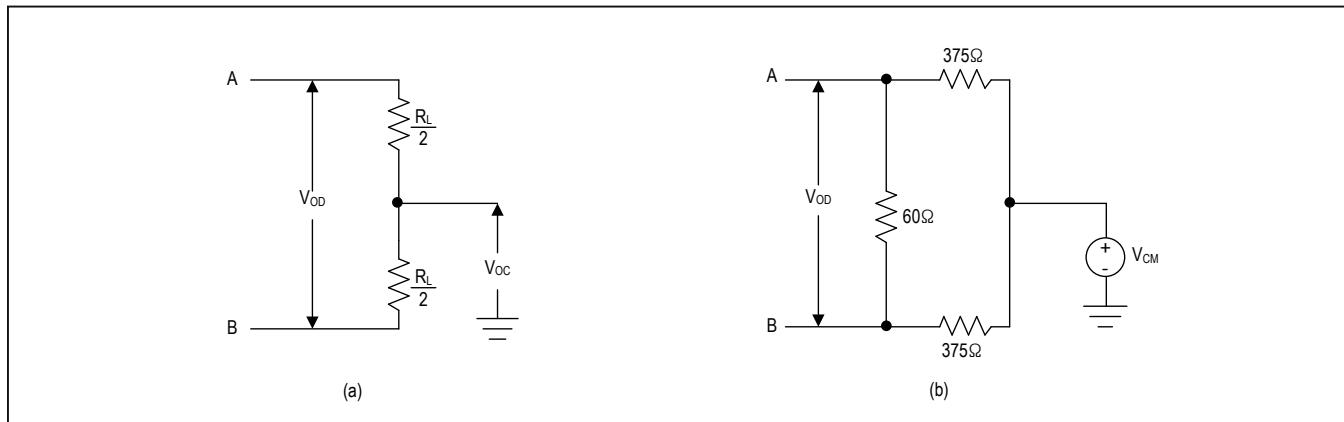

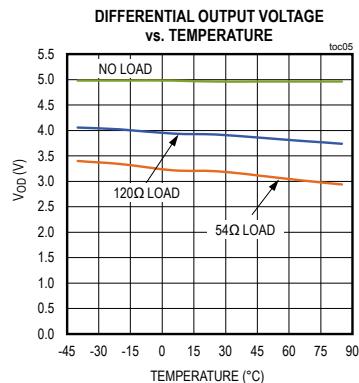

| Differential-Driver Output                                | V <sub>O</sub>    | $R_L = 54\Omega$ , TXD = high or low, DE = high, Figure 1a       | 2               |             |      | V     |    |

|                                                           |                   | $R_L = 100\Omega$ , TXD = high or low, DE = high, Figure 1a      | 3               |             |      |       |    |

|                                                           |                   | $-7V \leq V_{CM} \leq +12V$ , Figure 1b                          | 1.5             |             | 5    |       |    |

| Change in Magnitude of Differential-Driver Output Voltage | $\Delta V_{OD}$   | $R_L = 100\Omega$ or $54\Omega$ , Figure 1b (Note 6)             |                 | 0.2         |      | V     |    |

| Driver Common-Mode Output Voltage                         | $V_{OC}$          | $R_L = 100\Omega$ or $54\Omega$ , Figure 1a                      |                 | $V_{DDB}/2$ | 3    | V     |    |

| Change in Magnitude of Common-Mode Voltage                | $\Delta V_{OC}$   | $R_L = 100\Omega$ or $54\Omega$ , Figure 1a (Note 6)             |                 | 0.2         |      | V     |    |

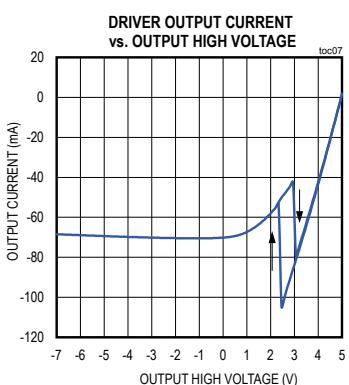

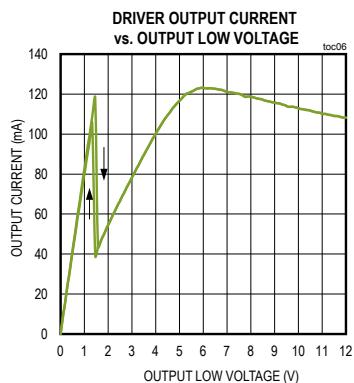

| Driver Short-Circuit Output Current                       | I <sub>OSD</sub>  | $GNDB \leq V_{OUT} \leq +12V$ , output low (Note 7)              |                 |             | +250 | mA    |    |

|                                                           |                   | $-7V \leq V_{OUT} \leq V_{DDB}$ , output high (Note 7)           |                 | -250        |      |       |    |

| Driver Short-Circuit Foldback Output Current              | I <sub>OSDF</sub> | $(V_{DDB} - 1V) \leq V_{OUT} \leq +12V$ , output low (Note 5, 7) | +20             |             |      | mA    |    |

|                                                           |                   | $-7V \leq V_{OUT} \leq +1V$ , output high (Note 5, 7)            |                 |             | -20  |       |    |

| <b>RECEIVER</b>                                           |                   |                                                                  |                 |             |      |       |    |

| Input Current (A and B)                                   | I <sub>A,B</sub>  | DE = GNDA, $V_{DDB} = GNDB$ or $+5.5V$                           | $V_{IN} = +12V$ |             | +125 | μA    |    |

|                                                           |                   |                                                                  | $V_{IN} = -7V$  |             | -100 |       |    |

| Receiver Differential-Threshold Voltage                   | V <sub>TH</sub>   | $-7V \leq V_{CM} \leq +12V$                                      |                 | -200        | -125 | -50   | mV |

| Receiver Input Hysteresis                                 | $\Delta V_{TH}$   | $V_{CM} = 0V$                                                    |                 |             | 15   |       | mV |

| Receiver Input Resistance                                 | R <sub>IN</sub>   | $-7V \leq V_{CM} \leq +12V$ , DE = low                           |                 | 96          |      |       | kΩ |

| <b>PROTECTION</b>                                         |                   |                                                                  |                 |             |      |       |    |

| Thermal-Shutdown Threshold                                | T <sub>SHDN</sub> | Temperature rising                                               |                 | +160        |      | °C    |    |

| Thermal-Shutdown Hysteresis                               | T <sub>HYST</sub> |                                                                  |                 | 15          |      | °C    |    |

| ESD Protection (A and B Pins to GNDB)                     |                   | Human Body Model                                                 |                 | ±30         |      | kV    |    |

|                                                           |                   | IEC 61000-4-2 Air-Gap Discharge                                  |                 | ±15         |      |       |    |

|                                                           |                   | IEC 61000-4-2- Contact Discharge                                 |                 | ±10         |      |       |    |

| ESD Protection (All Other Pins)                           |                   | Human Body Model                                                 |                 | ±4          |      | kV    |    |

**Switching Electrical Characteristics**

( $V_{DDA} - V_{GNDA} = 3.0V$  to  $5.5V$ ,  $V_{DDB} - V_{GNDB} = 4.5V$  to  $5.5V$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $V_{DDA} - V_{GNDA} = 3.3V$ ,  $V_{DDB} - V_{GNDB} = 5V$ ,  $V_{GNDA} = V_{GNDB}$ , and  $T_A = +25^{\circ}C$ .) (Note 5)

| PARAMETER                                               | SYMBOL               | CONDITIONS                                           | MIN | TYP  | MAX | UNITS |

|---------------------------------------------------------|----------------------|------------------------------------------------------|-----|------|-----|-------|

| <b>DYNAMIC</b>                                          |                      |                                                      |     |      |     |       |

| Common-Mode Transient Immunity                          | CMTI                 | (Note 8)                                             |     | 35   |     | kV/μs |

| Glitch Rejection                                        |                      | TXD, DE, RXD                                         | 10  | 17   | 29  | ns    |

| <b>DRIVER</b>                                           |                      |                                                      |     |      |     |       |

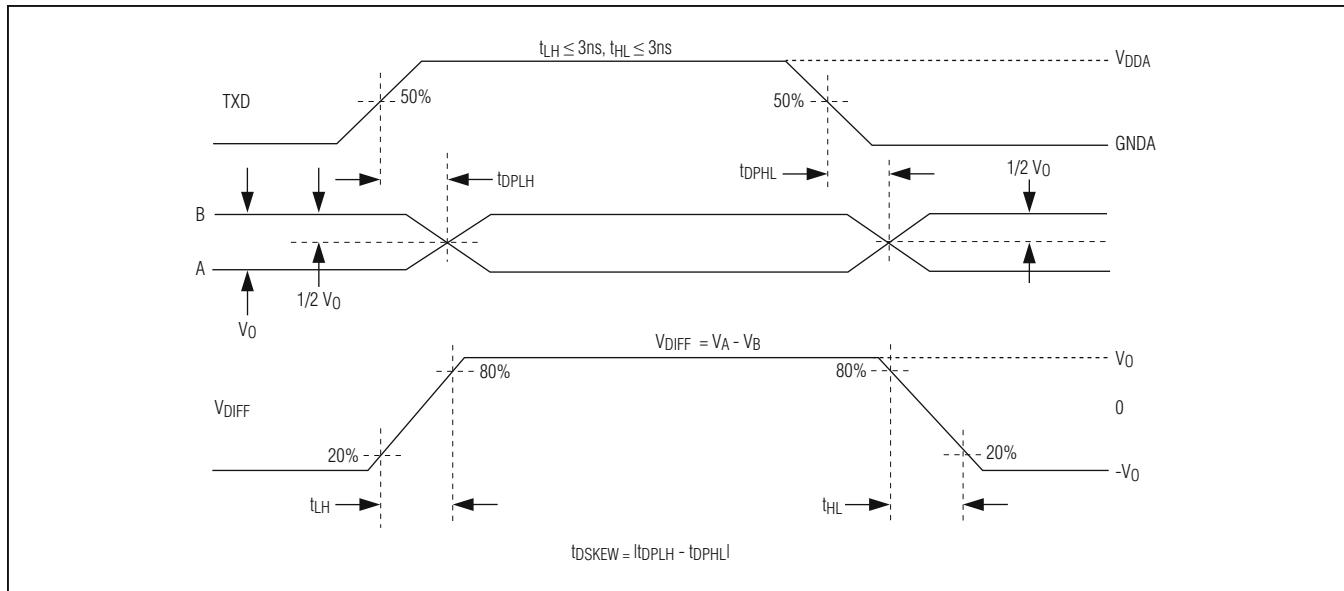

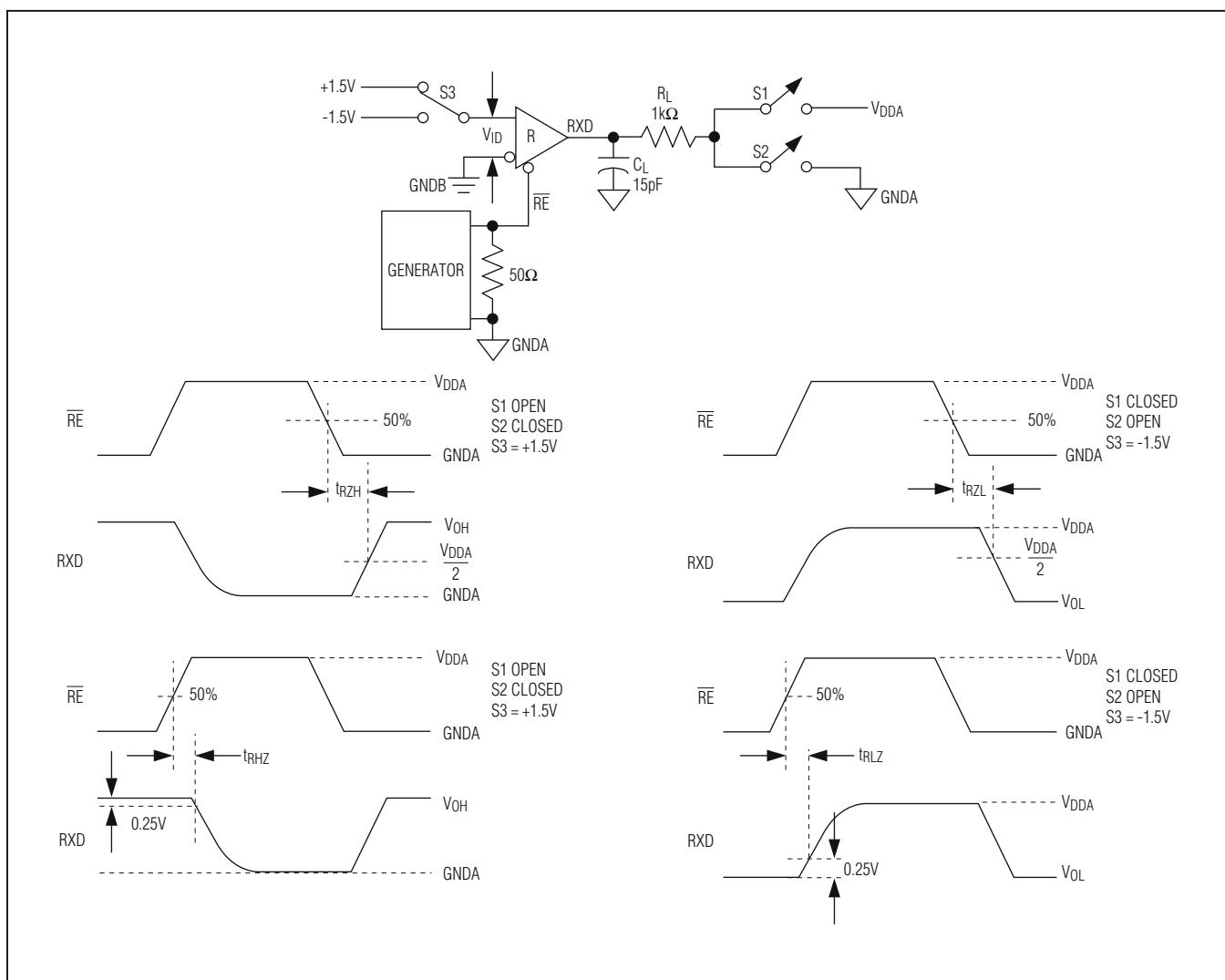

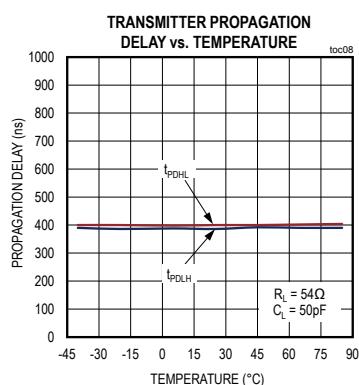

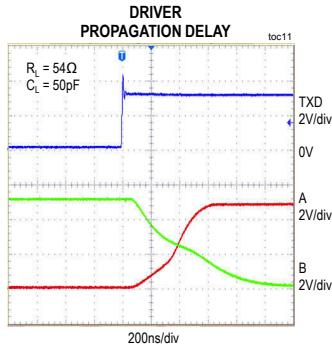

| Driver Propagation Delay                                | $t_{DPLH}, t_{DPHL}$ | $R_L = 54\Omega, C_L = 50pF$ , Figure 2 and Figure 3 |     | 1040 |     | ns    |

| Differential Driver Output Skew $ t_{DPLH} - t_{DPHL} $ | $t_{DSKEW}$          | $R_L = 54\Omega, C_L = 50pF$ , Figure 2 and Figure 3 |     | 144  |     | ns    |

| Driver Differential-Output Rise or Fall Time            | $t_{LH}, t_{HL}$     | $R_L = 54\Omega, C_L = 50pF$ , Figure 2 and Figure 3 |     | 900  |     | ns    |

| Maximum Data Rate                                       | DR <sub>MAX</sub>    |                                                      | 500 |      |     | kbps  |

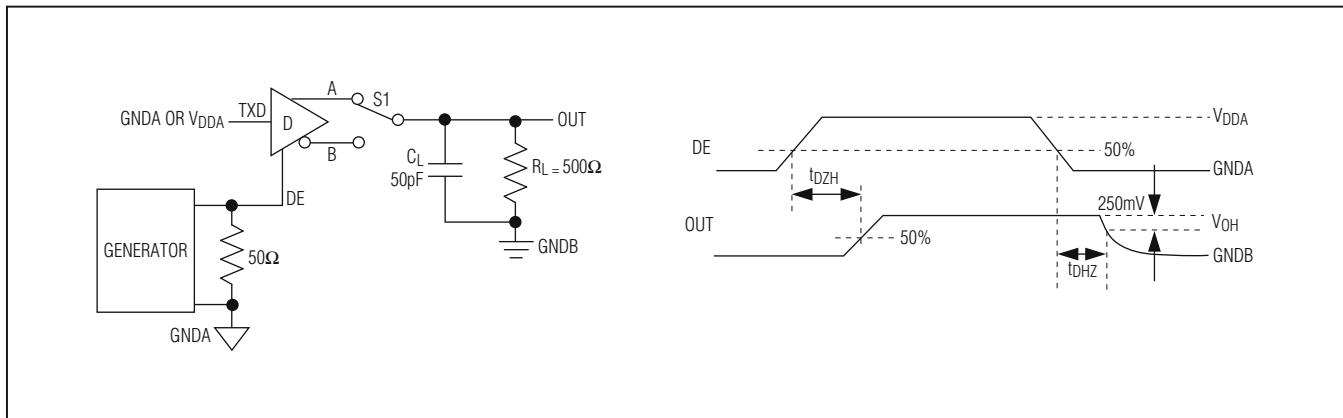

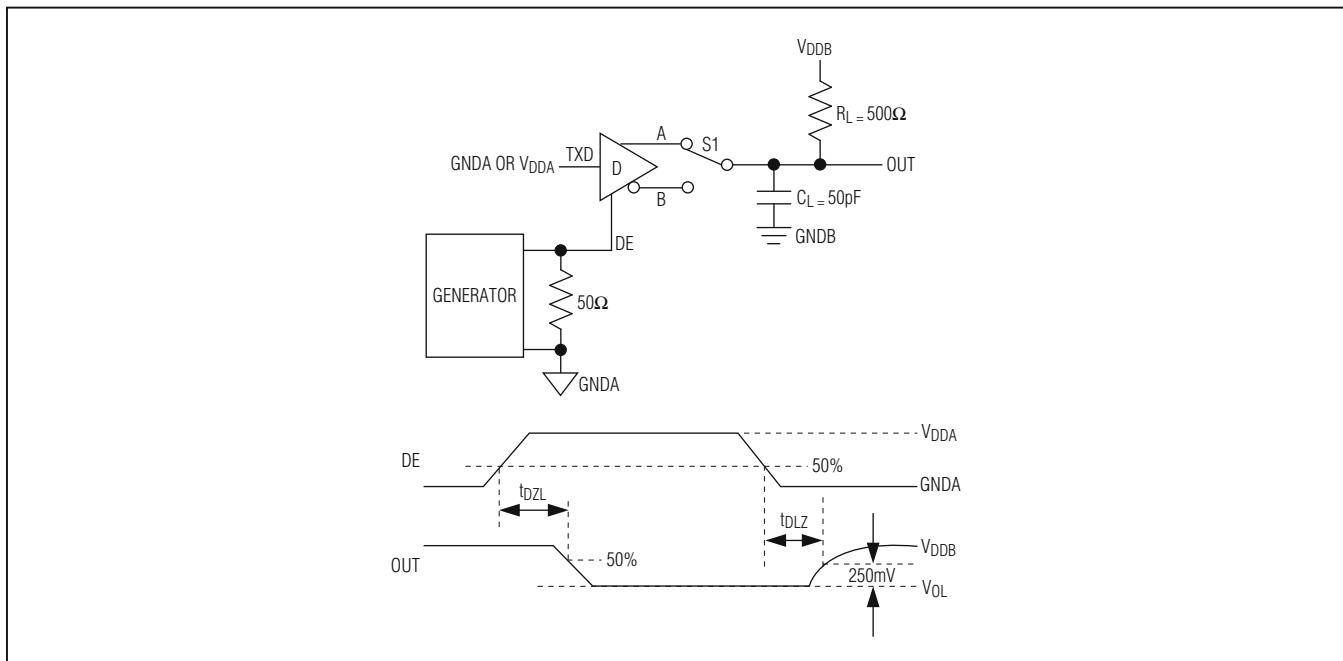

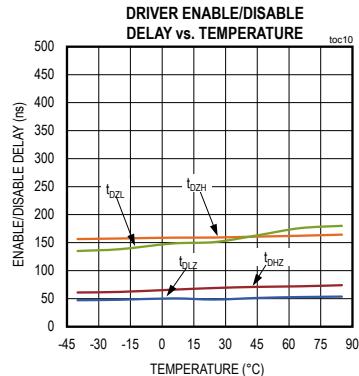

| Driver Enable to Output High                            | $t_{DZH}$            | $R_L = 500\Omega, C_L = 50pF$ , Figure 4             |     | 2540 |     | ns    |

| Driver Enable to Output Low                             | $t_{DZL}$            | $R_L = 500\Omega, C_L = 50pF$ , Figure 5             |     | 2540 |     | ns    |

| Driver Disable Time From Low                            | $t_{DLZ}$            | $R_L = 500\Omega, C_L = 50pF$ , Figure 5             |     | 140  |     | ns    |

| Driver Disable Time From High                           | $t_{DHZ}$            | $R_L = 500\Omega, C_L = 50pF$ , Figure 4             |     | 140  |     | ns    |

| <b>RECEIVER</b>                                         |                      |                                                      |     |      |     |       |

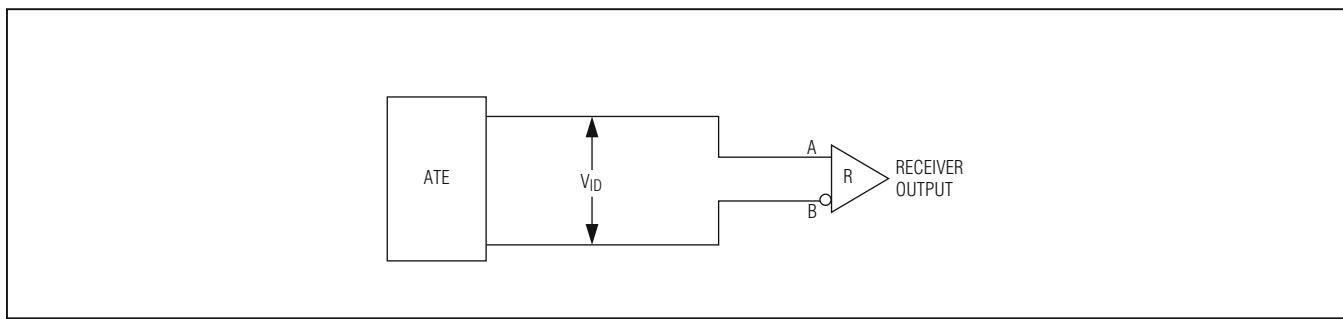

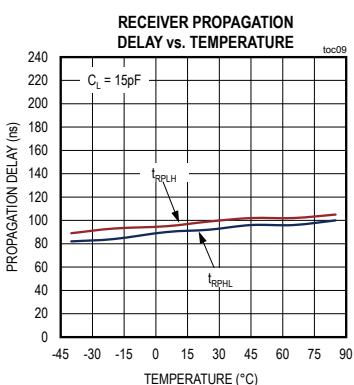

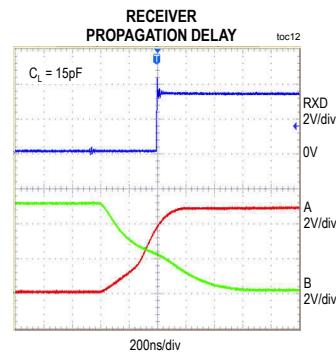

| Receiver Propagation Delay                              | $t_{RPLH}, t_{RPHL}$ | $C_L = 15pF$ , Figure 6 and Figure 7 (Note 9)        |     | 240  |     | ns    |

| Receiver Output Skew                                    | $t_{RSKEW}$          | $C_L = 15pF$ , Figure 6 and Figure 7 (Note 9)        |     | 34   |     | ns    |

| Maximum Data Rate                                       | DR <sub>MAX</sub>    |                                                      | 500 |      |     | kbps  |

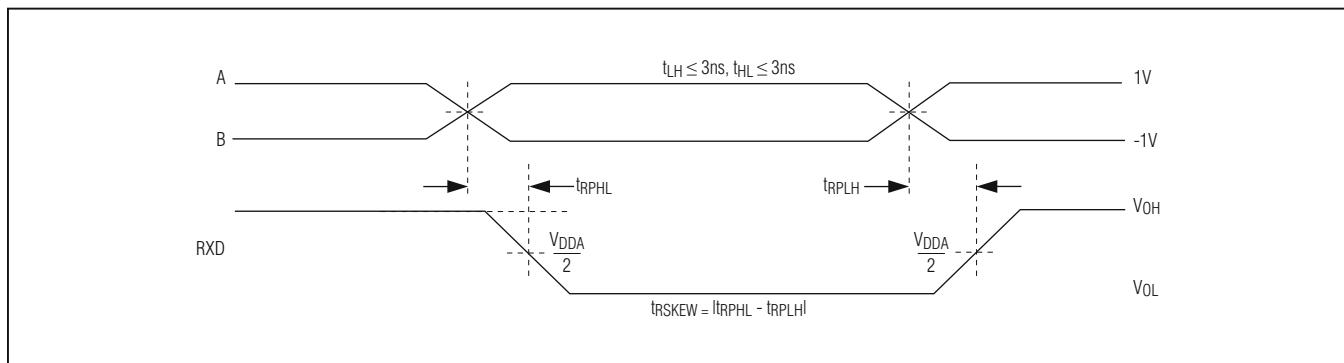

| Receiver Enable to Output High                          | $t_{RZH}$            | $R_L = 1k\Omega, C_L = 15pF$ , S2 closed, Figure 8   |     | 20   |     | ns    |

| Receiver Enable to Output Low                           | $t_{RZL}$            | $R_L = 1k\Omega, C_L = 15pF$ , S1 closed, Figure 8   |     | 30   |     | ns    |

| Receiver Disable Time from Low                          | $t_{RLZ}$            | $R_L = 1k\Omega, C_L = 15pF$ , S1 closed, Figure 8   |     | 20   |     | ns    |

| Receiver Disable Time from High                         | $t_{RHZ}$            | $R_L = 1k\Omega, C_L = 15pF$ , S2 closed, Figure 8   |     | 20   |     | ns    |

**Note 2:** All devices are 100% production tested at  $T_A = +25^{\circ}C$ . Specifications over temperature are guaranteed by design.

**Note 3:** All currents into the device are positive. All currents out of the device are negative. All voltages are referenced to their respective ground (GNDA or GNDB), unless otherwise noted.

**Note 4:**  $V_{LDO}$  max indicates voltage capability of the circuit. Power-dissipation requirements may limit  $V_{LDO}$  max to a lower value.

**Note 5:** Not production tested. Guaranteed by design.

**Note 6:**  $\Delta V_{OD}$  and  $\Delta V_{OC}$  are the changes in  $V_{OD}$  and  $V_{OC}$ , respectively, when the TXD input changes state.

**Note 7:** The short-circuit output current applies to the peak current just prior to foldback-current limiting. The short-circuit foldback output current applies during current limiting to allow a recovery from bus contention. See TOC 6 and TOC 7 in the *Typical Operating Characteristics* section.

**Note 8:** CMTI is the maximum sustainable common-mode voltage slew rate while maintaining the correct output states. CMTI applies to both rising and falling common-mode voltage edges. Tested with the transient generator connected between GNDA and GNDB.  $\Delta V_{CM} = 1kV$ .

**Note 9:** Capacitive load includes test probe and fixture capacitance.

## Insulation Characteristics

| PARAMETER                                 | SYMBOL     | CONDITIONS                                                                  | VALUE     | UNITS     |

|-------------------------------------------|------------|-----------------------------------------------------------------------------|-----------|-----------|

| Partial Discharge Test Voltage            | $V_{PR}$   | Method B1 = $V_{IORM} \times 1.875$ ( $t = 1s$ , partial discharge $<5pC$ ) | 2250      | $V_P$     |

| Maximum Repetitive Peak Withstand Voltage | $V_{IORM}$ | (Note 10)                                                                   | 1200      | $V_P$     |

| Maximum Working-Isolation Voltage         | $V_{IOWM}$ | (Note 10)                                                                   | 848       | $V_{RMS}$ |

| Maximum Transient Isolation Voltage       | $V_{IOTM}$ | $t = 1s$                                                                    | 8400      | $V_P$     |

| Maximum Withstand-Isolation Voltage       | $V_{ISO}$  | $t = 60s, f = 60Hz$ (Notes 10, 11)                                          | 5000      | $V_{RMS}$ |

| Maximum Surge Isolation Voltage           | $V_{IOSM}$ | Basic insulation                                                            | 10        | kV        |

| Insulation Resistance                     | $R_S$      | $T_A = +150^\circ C, V_{IO} = 500V$                                         | $>10^9$   | $\Omega$  |

| Barrier Capacitance Input to Output       | $C_{IO}$   | $f = 1MHz$                                                                  | 2         | pF        |

| Minimum Creepage Distance                 | $CPG$      | Wide SOIC                                                                   | 8         | mm        |

| Minimum Clearance Distance                | $CLR$      | Wide SOIC                                                                   | 8         | mm        |

| Internal Clearance                        |            | Distance through insulation                                                 | 0.015     | mm        |

| Comparative Tracking Resistance Index     | $CTI$      | Material Group II (IEC 60112)                                               | 575       |           |

| Climatic Category                         |            |                                                                             | 40/125/21 |           |

| Pollution Degree (DIN VDE 0110, Table 1)  |            |                                                                             | 2         |           |

**Note 10:**  $V_{IORM}$ ,  $V_{IOWM}$ ,  $V_{ISO}$  are defined by the IEC 60747-5-5 standard

**Note 11:** Product is qualified  $V_{ISO}$  for 60s. 100% production tested at 120% of  $V_{ISO}$  for 1s.

## Safety Regulatory Approvals (Pending)

|                                                                             |

|-----------------------------------------------------------------------------|

| <b>UL</b>                                                                   |

| The MAX14949 is certified under UL1577. For more details, see File E351759. |

| Rate up to 5000VRMS isolation voltage for basic insulation.                 |

| <b>cUL</b>                                                                  |

| Pending                                                                     |

| <b>VDE</b>                                                                  |

| Pending                                                                     |

| <b>TUV</b>                                                                  |

| Pending                                                                     |

図 1. ドライバの DC 試験負荷

図 2. ドライバのタイミング試験回路

図 3. ドライバ伝播遅延

図4. ドライバのイネーブルおよびディセーブル時間 ( $t_{DZH}$ 、 $t_{DHZ}$ )図5. ドライバのイネーブルおよびディセーブル時間 ( $t_{DZL}$ 、 $t_{DLZ}$ )

図6. レシーバの伝播遅延試験回路

図 7. レシーバの伝播遅延

図 8. レシーバのイネーブルおよびディセーブル時間

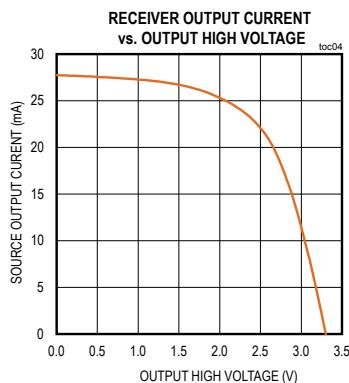

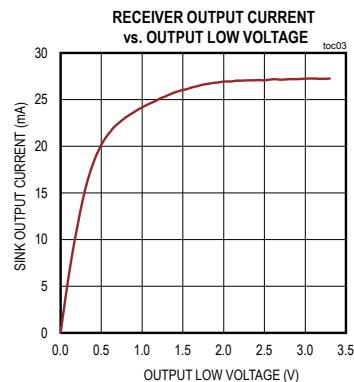

### 標準動作特性

( $V_{DDA} - V_{GNDA} = 3.3V$ ,  $V_{DDB} - V_{GNDB} = 5V$ ,  $V_{GNDA} = V_{GNDB}$ , and  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted.)

### 標準動作特性(続き)

( $V_{DDA} - V_{GNDA} = 3.3\text{V}$ ,  $V_{DDB} - V_{GNDB} = 5\text{V}$ ,  $V_{GNDA} = V_{GNDB}$ , and  $T_A = +25^\circ\text{C}$ , unless otherwise noted.)

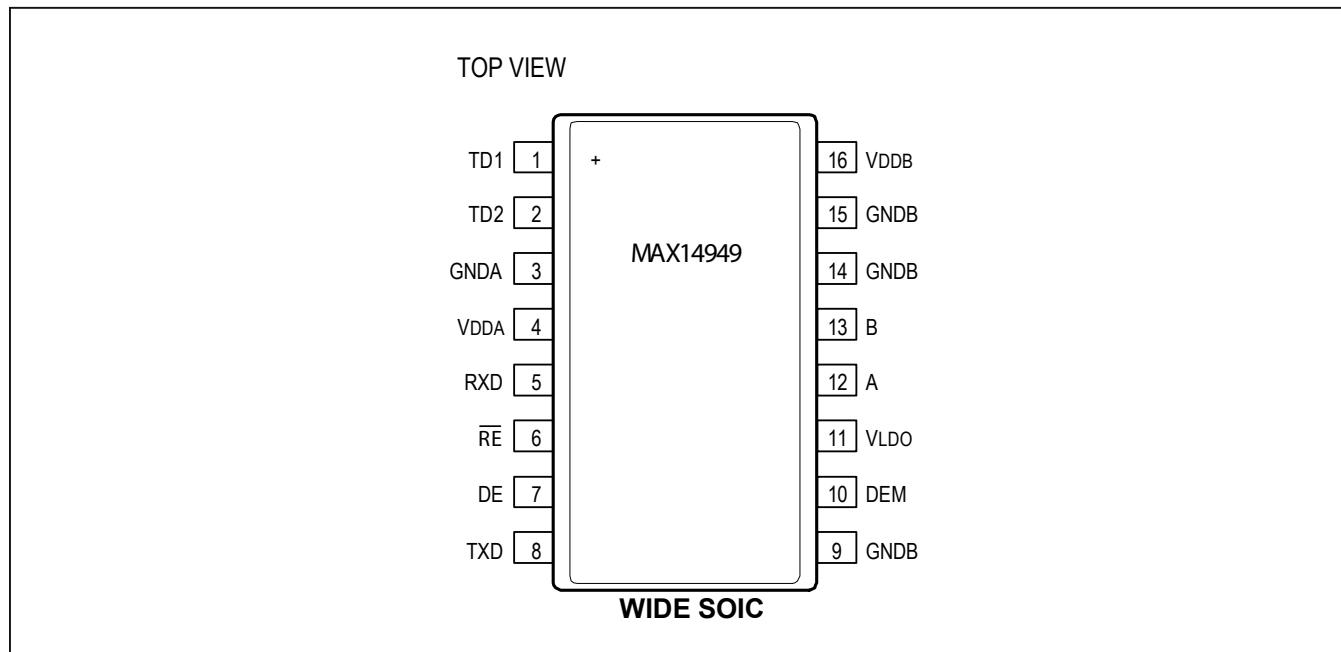

## ピン配置

## 端子説明

| 端子 | 名称   | 基準   | 機能                                                                                                                                                                                                                 |

|----|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | TD1  | GNDA | トランスドライバ出力1                                                                                                                                                                                                        |

| 2  | TD2  | GNDA | トランスドライバ出力2                                                                                                                                                                                                        |

| 3  | GNDA | —    | UART/ロジック側グランド。GNDAはデジタル信号およびトランスドライバのグランド基準です。                                                                                                                                                                    |

| 4  | VDDA | GNDA | ロジック側電源入力。できる限りデバイスの近くに配置した0.1μFと1μFの両方のコンデンサで、VDDAをGNDAに接続してください。                                                                                                                                                 |

| 5  | RXD  | GNDA | レシーバデータ出力。RXDをイネーブルする場合は、REをローに駆動してください。REがローの場合、RXDは(V <sub>A</sub> - V <sub>B</sub> ) > -50mVのときハイになります、(V <sub>A</sub> - V <sub>B</sub> ) < -200mVのときローになります。VDDAがUVLOB以下の場合、RXDはハイです。REがハイの場合、RXDはハイインピーダンスです。 |

| 6  | RE   | GNDA | レシーバ出力イネーブル。RXDをイネーブルする場合は、REをローに駆動するか、GNDAに接続してください。RXDをディセーブルする場合は、REをハイに駆動してください。REがハイの場合、RXDはハイインピーダンスです。REはGNDAへの4.5μAのプルダウンを内蔵しています。                                                                         |

### 端子説明(続き)

| 端子        | 名称               | 基準   | 機能                                                                                                                                                                                                                                              |

|-----------|------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7         | DE               | GNDA | ドライバ出力イネーブル。バスドライバ出力AおよびBをイネーブルする場合は、DEをハイに駆動してください。AおよびBをディセーブルする場合は、DEをローに駆動するか、GNDAに接続してください。DEがローの場合、AおよびBはハイインピーダンスです。DEはGNDAへの4.5μAのプルダウンを内蔵しています。                                                                                        |

| 8         | TXD              | GNDA | ドライバ入力。DEがハイの場合、TXDをローにすると強制的に非反転出力(A)がローになり反転出力(B)がハイになります。同様に、TXDをハイにすると強制的に非反転出力がハイになり反転出力がローになります。TXDはV <sub>DDA</sub> への4.5μAのプルアップを内蔵しています。                                                                                               |

| 9, 14, 15 | GNDB             | —    | ケーブル側グランド。GNDBは内蔵LDO、DEM出力、およびRS-485/RS-422バス信号のグランド基準です。                                                                                                                                                                                       |

| 10        | DEM              | GNDB | ドライバイネーブル監視出力。トランスマッタがイネーブルされている場合、DEMはハイです。詳細については「機能表」を参照してください。                                                                                                                                                                              |

| 11        | V <sub>LDO</sub> | GNDB | LDO電源入力。トランシーバのケーブル側に給電するため、4.68V (min)の電圧をV <sub>LDO</sub> に接続してください。できる限りデバイスの近くに配置した0.1μFと1μFの両方のコンデンサで、V <sub>LDO</sub> をGNDBに接続してください。内蔵LDOをディセーブルする場合は、V <sub>LDO</sub> を未接続のままにするか、GNDBに接続してください。                                        |

| 12        | A                | GNDB | 非反転レシーバ入力および非反転ドライバ出力                                                                                                                                                                                                                           |

| 13        | B                | GNDB | 反転レシーバ入力および反転ドライバ出力                                                                                                                                                                                                                             |

| 16        | V <sub>DDB</sub> | GNDB | ケーブル側電源入力/絶縁型LDO電源出力。できる限りデバイスの近くに配置した0.1μFと1μFの両方のコンデンサで、V <sub>DDB</sub> をGNDBに接続してください。V <sub>LDO</sub> に電力が印加されている場合、V <sub>DDB</sub> は内蔵LDOの出力です。内蔵LDOが未使用の場合(V <sub>LDO</sub> が未接続またはGNDBに接続されている場合)、V <sub>DDB</sub> はICのケーブル側の正の電源入力です。 |

## 機能表

| TRANSMITTING     |                  |     |     |         |        |     |

|------------------|------------------|-----|-----|---------|--------|-----|

| INPUTS           |                  |     |     | OUTPUTS |        |     |

| $V_{DDA}$        | $V_{DDB}$        | DE* | TXD | A       | B      | DEM |

| $\geq V_{UVLOA}$ | $\geq V_{UVLOB}$ | 1   | 1   | 1       | 0      | 1   |

| $\geq V_{UVLOA}$ | $\geq V_{UVLOB}$ | 1   | 0   | 0       | 1      | 1   |

| $\geq V_{UVLOA}$ | $\geq V_{UVLOB}$ | 0   | X   | High-Z  | High-Z | 0   |

| $< V_{UVLOA}$    | $\geq V_{UVLOB}$ | X   | X   | High-Z  | High-Z | 0   |

| $\geq V_{UVLOA}$ | $< V_{UVLOB}$    | X   | X   | High-Z  | High-Z | 0   |

| $< V_{UVLOA}$    | $< V_{UVLOB}$    | X   | X   | High-Z  | High-Z | 0   |

\*トランシット出力をディセーブルする場合は、DEをローに駆動してください。トランシット出力をイネーブルする場合は、DEをハイに駆動してください。DEはGNDへのプルダウンを内蔵しています。

X = 任意

| RECEIVING        |                  |                   |               |         |

|------------------|------------------|-------------------|---------------|---------|

| INPUTS           |                  |                   |               | OUTPUTS |

| $V_{DDA}$        | $V_{DDB}$        | $\overline{RE}^*$ | $(V_A - V_B)$ | RXD     |

| $\geq V_{UVLOA}$ | $\geq V_{UVLOB}$ | 0                 | $> -50mV$     | 1       |

| $\geq V_{UVLOA}$ | $\geq V_{UVLOB}$ | 0                 | $< -200mV$    | 0       |

| $\geq V_{UVLOA}$ | $\geq V_{UVLOB}$ | 0                 | Open/Short    | 1       |

| $\geq V_{UVLOA}$ | $\geq V_{UVLOB}$ | 1                 | X             | High-Z  |

| $< V_{UVLOA}$    | $\geq V_{UVLOB}$ | X                 | X             | High-Z  |

| $\geq V_{UVLOA}$ | $< V_{UVLOB}$    | 0                 | X             | 1       |

| $< V_{UVLOA}$    | $< V_{UVLOB}$    | X                 | X             | High-Z  |

\*レシーバ出力をディセーブルする場合は、 $\overline{RE}$ をハイに駆動してください。レシーバ出力をイネーブルする場合は、 $\overline{RE}$ をローに駆動してください。 $\overline{RE}$ はGNDへのプルダウンを内蔵しています。

X = 任意。

## 詳細

絶縁型RS-485/RS-422トランシーバのMAX14949は、5000VRMS (60秒)のガルバニック絶縁をトランシーバのRS-485/RS-422ケーブル側とUART側の間に提供します。このデバイスは、絶縁障壁のそれぞれの側のグランド間に大きい電位差が存在する場合に、絶縁障壁越しに最大500kbpsの通信を実現します。

## 絶縁

データおよび電源の両方を絶縁障壁越しに送信することができます。データ絶縁は内蔵の容量性絶縁を使用して実現され、トランシーバのUART側とケーブル側間のデータ送信が可能です。

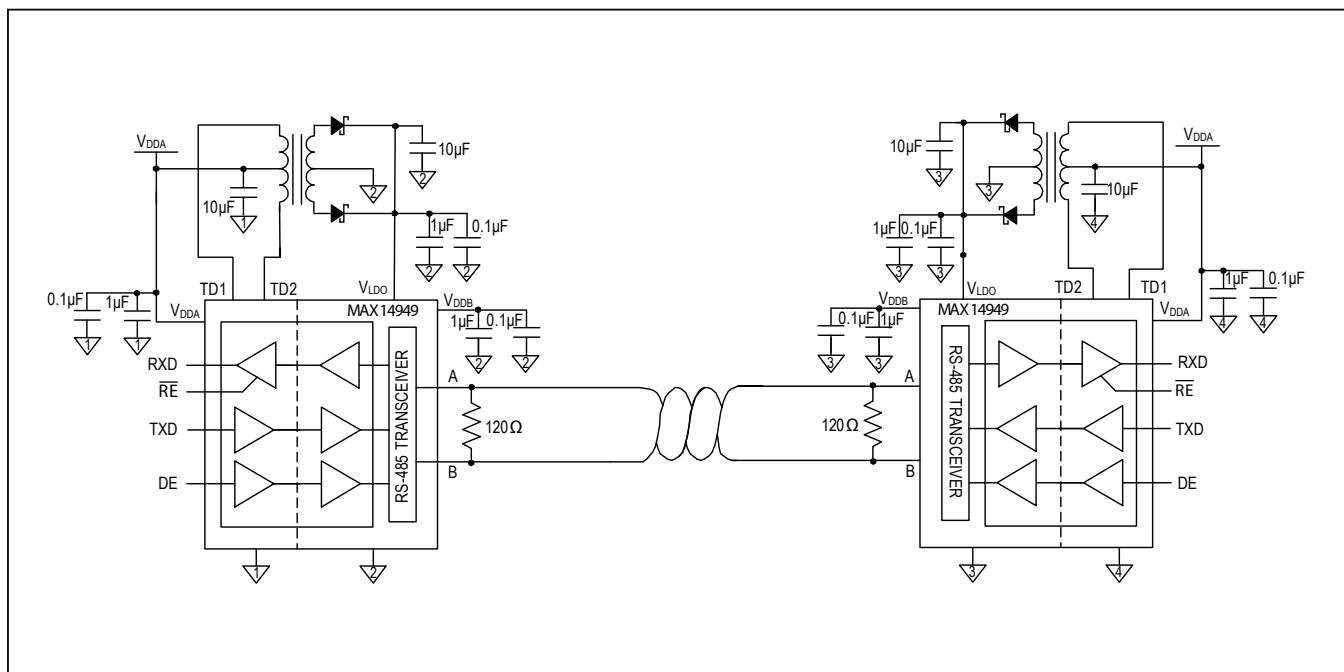

電源の絶縁を実現するため、このデバイスはセンタータップを備えた外付けトランスを駆動するためのトранスドライバを内蔵し、UART側から絶縁障壁を超えてケーブル側に動作電源を伝送することができます。外付けトランスの1次側を、デバイスのトランスドライバ出力(TD1およびTD2)に接続してください。1次側センタータップをV<sub>DDA</sub>に接続してください。

## 内蔵LDO

このデバイスは、ICのケーブル側への給電に使用される、5V (typ)出力に設定された低ドロップアウトレギュレータを内蔵しています。LDOの出力はV<sub>DDB</sub>です。LDOは300mA (typ)の電流制限を備えています。LDOを使用しない場合、V<sub>LDO</sub>をGNDBに接続し、V<sub>DDB</sub>に+5Vを直接印加してください。

## 真のフェイルセーフ

このデバイスは、レシーバ入力が短絡またはオープン状態の場合、または終端処理された伝送ラインに接続され全ドライバがディセーブルされている場合に、レシーバ出力がロジックハイになることを保証します。レシーバのスレッショルドは-50mV~-200mVの間に固定されています。差動レシーバ入力電圧(V<sub>A</sub> - V<sub>B</sub>)が-50mVまたはそれ以上の場合、RXDはロジックハイになります。終端処理されたバスで全トランスマッタがディセーブルされている場合、レシーバの差動入力電圧は終端抵抗によってゼロにブリダウンされます。このデバイスのレシーバスレッショルドによって、その結果RXDはロジックハイになります。

## ドライバ出力の保護

障害またはバス競合によって発生する過大な出力電流および消費電力を防ぐため、2つの仕組みを備えています。第1の仕組みは出力段のフォールドバックモード電流制限で、

全コモンモード電圧範囲にわたって短絡に対する保護を瞬時に提供します。第2の仕組みはサーマルシャットダウン回路で、チップ温度が+160°C (typ)を超えるとドライバ出力を強制的にハイインピーダンス状態にします。

## サーマルシャットダウン

このデバイスはサーマルシャットダウン回路によって過熱の損傷から保護されます。接合部温度(T<sub>J</sub>)が+160°C (typ)を超えると、ドライバ出力はハイインピーダンスになります。T<sub>J</sub>が+145°C (typ)を下回ると、デバイスは通常動作に戻ります。

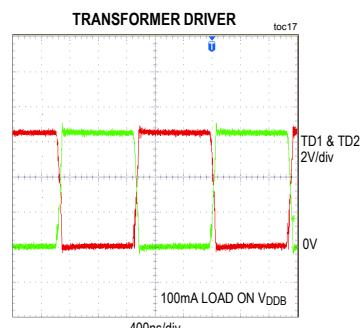

## トランスドライバ

### 過電流制限

このデバイスは過電流制限を備え、大きい容量性負荷の充電時または短絡状態の駆動時に内蔵トランスドライバを過大な電流から保護します。電流制限は、2段階で実現されます。内部回路は出力電流を監視し、ピーク電流が1.2Aを上回ったことを検出します。1.2Aのスレッショルドを超えると、内部回路は出力電流を730mAの電流制限に低減します。このデバイスはサイクル単位でドライバ電流を監視し、短絡が除去されるまで電流を制限します。

デバイスのトランスドライバは、過電流制限時に大量の電力を消費し、ICがサーマルシャットダウンに移行する可能性があります。ドライバの接合部温度がサーマルシャットダウンの閾値を超えると、TD1およびTD2ドライバ出力がディセーブルされます。温度がサーマルシャットダウンのヒステリシスを下回ると、ドライバは通常動作を再開します。

## トランスの選択

内蔵プッシュプルトランスドライバは、UART側から(絶縁障壁越しに)デバイスの絶縁されたケーブル側への動作電源の伝送を可能にします。450kHzのトランスドライバは、センタータップを備えた1次側トランスとの組合せで動作します。トランスが飽和状態に移行しないことを確実にするため、ET積がドライバのETと等しいかそれ以上のトランスを選択してください。Eはトランスに印加される電圧で、Tは任意の1サイクル中にそれが印加される最大時間です。トランス1次側の最小ET積は、次のように計算します。

$$ET = V_{MAX}/(2 \times f_{MIN})$$

ここで、V<sub>MAX</sub>はV<sub>DDA</sub>のワーストケースの最大電源電圧、f<sub>MIN</sub>はその電源電圧での最小周波数です。たとえば、5.5Vおよび350kHzを使用する場合、必要な最小ET積は7.9Vμsです。[表1](#)に、推奨トランスのリストが記載されています。

## アプリケーション情報

### バス上の256のトランシーバ

標準RS-485レシーバの入力インピーダンスは1ユニット負荷で、標準ドライバは最大32ユニット負荷を駆動することができます。デバイスのトランシーバは1/8ユニット負荷のレシーバを備えているため、1つの通信ラインに最大256のトランシーバを並列に接続可能です。最大32ユニット負荷までの範囲で、これらのデバイス(および/または他のRS-485/RS-422デバイス)を任意に組み合わせてラインに接続してください。

### 標準アプリケーション

トランシーバは、マルチポイントバス伝送ライン上での双方向データ通信用に設計されています。[図9](#)および[図10](#)は、標準的なネットワークアプリケーション回路を示します。反射を最小限に抑えるため、バスの両端をその特性インピーダンスで終端処理し、主ラインから分岐するスタブ長をできる限り短くしてください。

### レイアウトについて

絶縁またはキープアウトチャネルは、グランドプレーンおよび信号プレーンに接続されていないアイソレータの下に設計することが推奨されます。ケーブル側とUART側間に何らかのガルバニック接続または金属接続があると、絶縁が無効になります。

インダクタンスを最小限に抑えるため、VDDAとGNDA間およびVLDO/VDBBとGNDB間のデカップリングコンデンサができる限りICの近くに配置されていることを確認してください。

外部の影響の可能性を最小限に抑えるため、重要な信号ラインはグランドプレーンの近くに配線してください。デバイスのケーブル側では、バスコネクタおよび終端抵抗ができる限りAおよびB端子の近くに配置するのが良い手法です。

表1.推奨トランス

| MANUFACTURER PART NUMBER | APPLICATION  | CONFIGURATION | ISOLATION (VRMS) | DIMENSIONS           |

|--------------------------|--------------|---------------|------------------|----------------------|

| HALO TGMR-1450V6LF       | 5V to 3.3V   | 1CT:1CT       | 5000             | 9.45 x 10.87 x 10.03 |

| HALO TGMR-1455V6LF       | 3.3V to 3.3V | 1CT:1.5CT     | 5000             | 9.45 x 10.87 x 10.03 |

| WURTH 750315229          | 5V to 3.3V   | 1CT:1.1CT     | 5000             | 9.14 x 8.00 x 7.62   |

| WURTH 750315230          | 3.3V to 3.3V | 1CT:1.3CT     | 5000             | 9.14 x 8.00 x 7.62   |

| WURTH 750315231          | 3.3V to 3.3V | 1CT:1.7CT     | 5000             | 9.14 x 8.00 x 7.62   |

MAX14949

5kVRMS絶縁型500kbpsハーフデュプレックス

RS-485/RS-422トランシーバ、±30kV ESD保護および

トランスドライバ内蔵

図 9. 標準的な絶縁型ハーフデュプレックス RS-485 アプリケーション

図 10. 内蔵トランスドライバを使用する標準的な絶縁型ハーフデュプレックス RS-485 アプリケーション

### 拡張ESD保護

取扱い中や組立て中に発生する静電気放電に対する保護のために、すべての端子にESD保護構造が組み込まれています。MAX14949のドライバ出力とレシーバ入力は、静電気に対する保護が強化されています。このESD構造は、通常動作時およびパワーダウン時に高ESDに耐えることができます。ESDの発生後、デバイスはラッチアップや損傷なしに動作を継続します。

最大のESD保護を確保するため、 $0.1\mu\text{F}$ と $1\mu\text{F}$ のコンデンサで $V_{DDA}$ を $GNDA$ に接続し、 $V_{DDB}$ および $V_{LDO}$ を $GNDB$ に接続してください。

ESD保護は、さまざまな方法で試験を行うことができます。デバイスのトランスマッタ出力およびレシーバ入力は、ケーブル側グランド( $GNDB$ )に対して以下の限界値までの保護特性となっています。

- ±30kV HBM

- ±15kV (IEC 61000-4-2で規定されている気中放電法を使用した場合)

- ±10kV (IEC 61000-4-2で規定されている接触放電法を使用した場合)

### ESD試験条件

ESD性能は、各種の条件に依存します。試験のセットアップ、試験方法、および試験結果が記載された信頼性レポートについては、マキシムまでお問い合わせください。

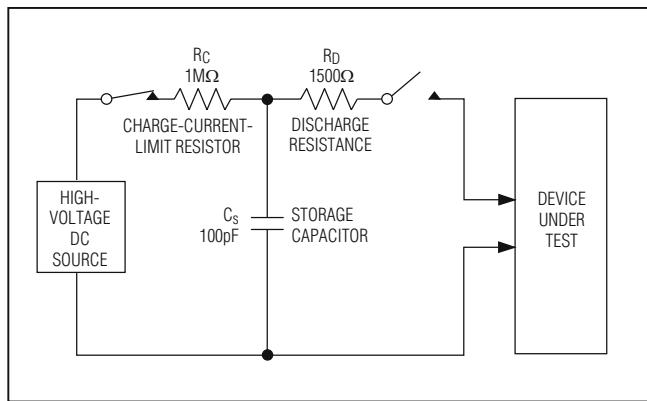

### ヒューマンボディモデル(HBM)

図11はHBM試験モデルを示し、図12はローインピーダンス状態に対して放電した場合に生成される電流波形を示します。このモデルは、目的のESD電圧まで充電された $100\text{pF}$ のコンデンサで構成され、それが $1.5\text{k}\Omega$ の抵抗を介して試験デバイスに放電されます。

### IEC 61000-4-2

IEC 61000-4-2規格は、完成した機器のESD試験およびESD性能を対象としています。しかし、ICについては特に対象としません。このデバイスは、ESD保護部品を追加しなくてもIEC 61000-4-2に適合する機器の設計に役立ちます。

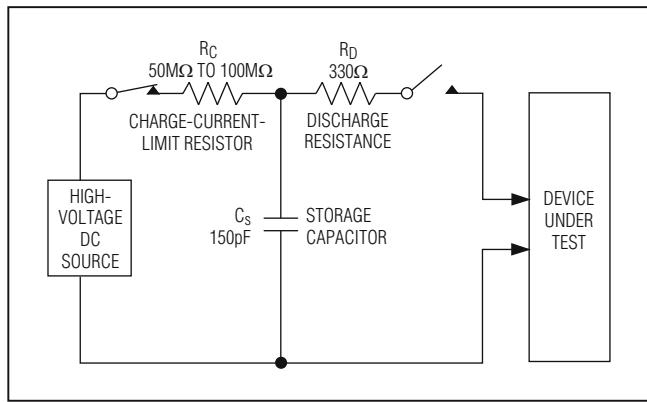

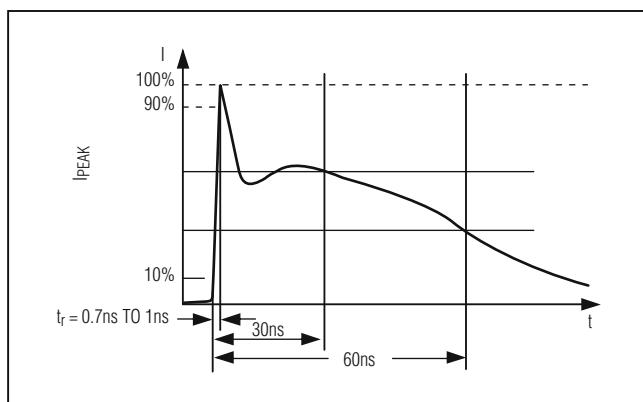

HBMとIEC 61000-4-2を使用して行われた試験の主な違いは、IEC 61000-4-2モデルの方が直列抵抗が小さいため、IEC 61000-4-2のピーク電流が大きくなるという点です。そのため、IEC 61000-4-2に従って測定されたESD耐電圧は、HBMを使用して測定された値よりも一般的に低くなります。

図13はIEC 61000-4-2のモデルを示し、図14はIEC 61000-4-2 ESD接触放電試験の電流波形を示します。

図 11. ヒューマンボディ ESD 試験モデル

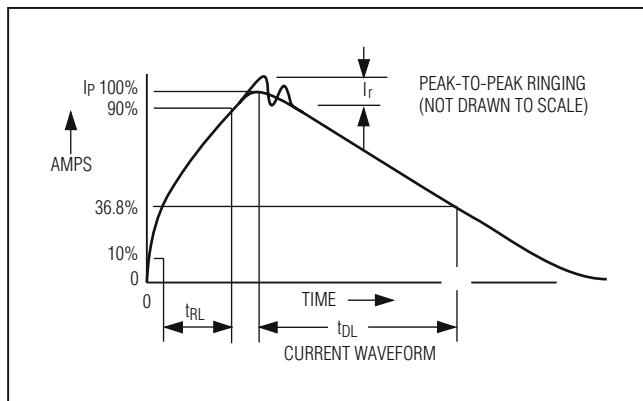

図 12. ヒューマンボディの電流波形

図 13. IEC 61000-4-2 ESD 試験モデル

図 14. IEC 61000-4-2 ESD 発生器の電流波形

## 標準アプリケーション回路

## パッケージ

最新のパッケージ図面情報およびランドパターン(フットプリント)は [www.maximintegrated.com/jp/packaging](http://www.maximintegrated.com/jp/packaging) を参照してください。なお、パッケージコードに含まれる「+」、「#」、または「-」はRoHS対応状況を表したものでしかありません。パッケージ図面はパッケージそのものに関するものでRoHS対応状況とは関係がなく、図面によってパッケージコードが異なることがある点を注意してください。

| パッケージ<br>タイプ | パッケージ<br>コード | 外形図<br>No.              | ランド<br>パターンNo.          |

|--------------|--------------|-------------------------|-------------------------|

| 16 SOIC      | W16M+10      | <a href="#">21-0042</a> | <a href="#">90-0107</a> |

## 型番

| PART          | TEMP RANGE     | PIN-PACKAGE |

|---------------|----------------|-------------|

| MAX14949EWE+  | -40°C to +85°C | 16 SOIC (W) |

| MAX14949EWE+T | -40°C to +85°C | 16 SOIC (W) |

+は鉛(Pb)フリー/RoHS準拠パッケージを表します。

T = テープ&リール。

## チップ情報

PROCESS: BiCMOS

## 改訂履歴

| 版数 | 改訂日  | 説明 | 改訂ページ |

|----|------|----|-------|

| 0  | 6/15 | 初版 | —     |

マキシム・ジャパン株式会社 〒141-0032 東京都品川区大崎1-6-4 大崎ニューシティ 4号館 20F TEL: 03-6893-6600

Maxim Integratedは完全にMaxim Integrated製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。Maxim Integratedは隨時予告なく回路及び仕様を変更する権利を留保します。「Electrical Characteristics (電気的特性)」の表に示すパラメータ値(min、maxの各制限値)は、このデータシートの他の場所で引用している値より優先されます。