EVALUATION KIT

AVAILABLE**MAXIM****シリアルLVDS出力付き、オクタル、

12ビット、50Msps、1.8V ADC****概要**

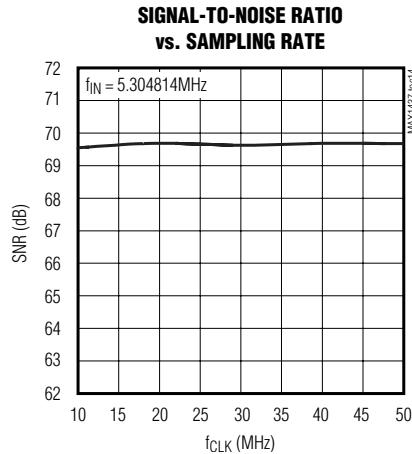

MAX1437はオクタル、12ビット、アナログ-デイジタルコンバータ(ADC)で、完全差動入力、パイプラインアーキテクチャ、およびディジタルエラー補正を備え、完全差動信号経路を採用しています。このADCは、医療用画像処理装置およびディジタル通信アプリケーションにおいて低電力、高ダイナミック性能に最適化されています。MAX1437は1.8Vの単一電源で動作し、消費電力はわずか768mW(1チャネル当たり96mW)ながら、5.3MHzの入力周波数で69.9dB(typ)の信号対ノイズ比(SNR)を実現しています。MAX1437は低動作電力に加えて、アイドル時のパワーダウンモードを備えています。

1.24Vの高精度内蔵バンドギャップリファレンスによって、ADCのフルスケール範囲を設定します。リファレンス構造がフレキシブルであるため、高い精度または別の入力電圧範囲が必要なアプリケーション用に外部リファレンスを使用することができます。リファレンスアーキテクチャは低ノイズに最適化されています。

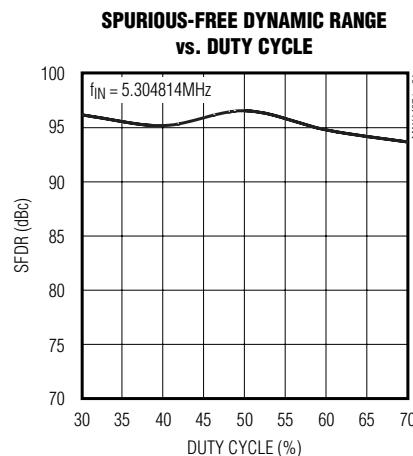

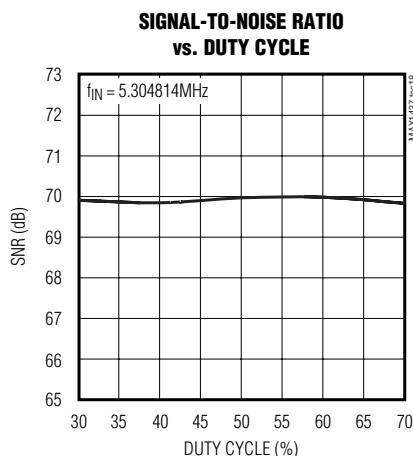

シングルエンドクロックがデータ変換プロセスを制御します。内蔵デューティサイクルイコライザによって、クロックデューティサイクルの幅広い変動が補償されます。内蔵PLL(位相ロックループ)は、高速シリアル低電圧差動信号(LVDS)クロックを生成します。

MAX1437は、データ、クロック、およびフレーム整列信号に対して自動整列されるシリアルLVDS出力を備えています。出力データは、2の補数またはバイナリ形式で提供されます。

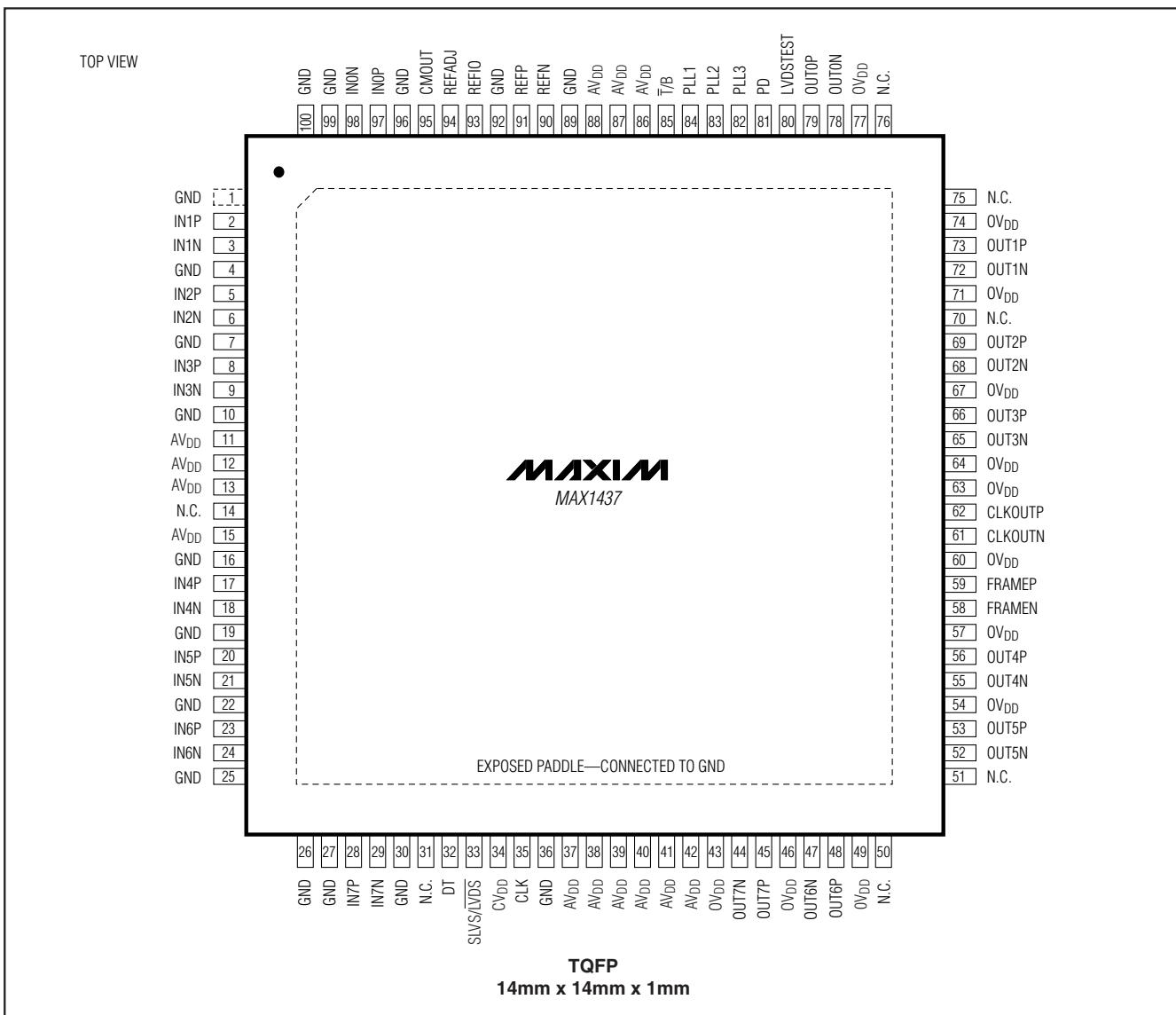

MAX1437の最高サンプルレートは50Mspsです。これより速い速度と遅い速度のバージョンについては、「ピンコンパチブルバージョン」の表を参照してください。このデバイスは14mm x 14mm x 1mmのエクスポートドパッド付き小型100ピンTQFPパッケージで提供され、工業用拡張温度範囲(-40°C ~ +85°C)での動作が保証されています。

**アプリケーション**

超音波および医療用画像処理

計測

マルチチャネル通信

**機能**

- ◆ 優れたダイナミック性能

SNR : 69.9dB(5.3MHzにおいて)

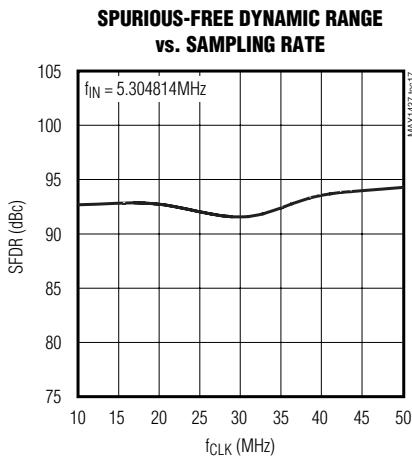

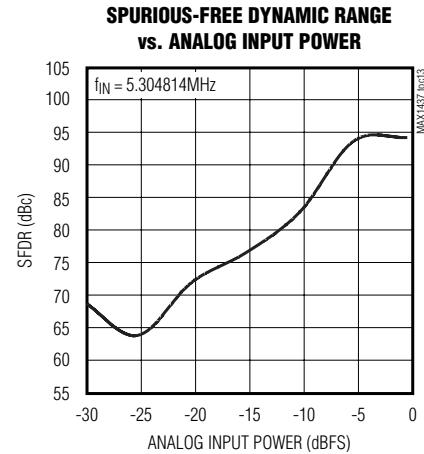

SFDR : 96dBc(5.3MHzにおいて)

チャネルアイソレーション : 95dB

- ◆ 超低電力

1チャネル当たり96mW(通常動作時)

- ◆ シリアルLVDS出力

- ◆ 端子選択可能なLVDS/SLVS

(スケーラブル低電圧信号)モード

- ◆ LVDS出力は最長30インチのFR-4

バックプレーン接続をサポート

- ◆ ディジタル信号の完全性のためのテストモード

- ◆ 完全差動アナログ入力

- ◆ 広差動入力電圧範囲 : 1.4V<sub>P-P</sub>

- ◆ 1.24Vの高精度バンドギャップリファレンス内蔵

- ◆ クロックデューティサイクルイコライザ

- ◆ エクスポートドパッド付き小型100ピン

TQFNパッケージ

- ◆ 評価キットを提供(MAX1437EVKITを

注文してください)

**型番**

| PART       | TEMP RANGE     | PIN-PACKAGE                         |

|------------|----------------|-------------------------------------|

| MAX1437ECQ | -40°C to +85°C | 100 TQFP-EP*<br>(14mm x 14mm x 1mm) |

\*EP = エクスポートドパッド。

**ピンコンパチブルバージョン**

| PART      | SAMPLING RATE<br>(Msps) | RESOLUTION<br>(BITS) |

|-----------|-------------------------|----------------------|

| MAX1434   | 50                      | 10                   |

| MAX1436   | 40                      | 12                   |

| MAX1438** | 65                      | 12                   |

\*\* 開発中の製品。入手性についてはお問い合わせください。

ピン配置はデータシートの最後に記載されています。

**MAXIM****Maxim Integrated Products** 1

本データシートに記載された内容はMaxim Integrated Productsの公式な英語版データシートを翻訳したものです。翻訳により生じる相違及び誤りについては責任を負いかねます。正確な内容の把握には英語版データシートをご参照ください。

無料サンプル及び最新版データシートの入手には、マキシムのホームページをご利用ください。<http://japan.maxim-ic.com>

**MAX1437**

# シリアルLVDS出力付き、オクタル、 12ビット、50MspS、1.8V ADC

## ABSOLUTE MAXIMUM RATINGS

|                                                                    |                        |                                                 |

|--------------------------------------------------------------------|------------------------|-------------------------------------------------|

| AVDD to GND                                                        | -0.3V to +2.0V         | Continuous Power Dissipation (TA = +70°C)       |

| CVDD to GND                                                        | -0.3V to +3.6V         | 100-Pin TQFP 14mm x 14mm x 1mm                  |

| OVDD to GND                                                        | -0.3V to +2.0V         | (derated 47.6mW/°C above +70°C).....3809.5mW    |

| IN_P, IN_N to GND                                                  | -0.3V to (AVDD + 0.3V) | Operating Temperature Range .....-40°C to +85°C |

| CLK to GND                                                         | -0.3V to (CVDD + 0.3V) | Maximum Junction Temperature .....+150°C        |

| OUT_P, OUT_N, FRAME_                                               |                        | Storage Temperature Range .....-65°C to +150°C  |

| CLKOUT_ to GND                                                     | -0.3V to (OVDD + 0.3V) | Lead Temperature (soldering, 10s) .....+300°C   |

| DT, SLVS/LVDS, LVDSTEST, PLL_, T/B,<br>REFIO, REFADJ, CMOUT to GND | -0.3V to (AVDD + 0.3V) |                                                 |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

(AVDD = 1.8V, OVDD = 1.8V, CVDD = 3.3V, GND = 0, external VREFIO = 1.24V, CREFIO to GND = 0.1 $\mu$ F, CREFP to GND = 10 $\mu$ F, CREFN to GND = 10 $\mu$ F, fCLK = 50MHz (50% duty cycle), VDT = 0, TA = TMIN to TMAX, unless otherwise noted. Typical values are at TA = +25°C.) (Note 1)

| PARAMETER                                                                     | SYMBOL            | CONDITIONS                            | MIN  | TYP        | MAX       | UNITS            |

|-------------------------------------------------------------------------------|-------------------|---------------------------------------|------|------------|-----------|------------------|

| <b>DC ACCURACY (Note 2)</b>                                                   |                   |                                       |      |            |           |                  |

| Resolution                                                                    | N                 |                                       | 12   |            |           | Bits             |

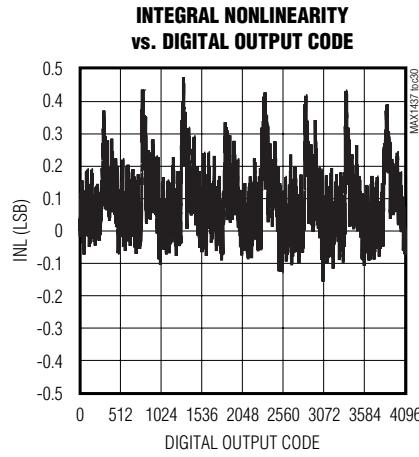

| Integral Nonlinearity                                                         | INL               |                                       |      | $\pm 0.4$  | $\pm 2.5$ | LSB              |

| Differential Nonlinearity                                                     | DNL               | No missing codes over temperature     |      | $\pm 0.25$ | $\pm 1$   | LSB              |

| Offset Error                                                                  |                   |                                       |      |            | $\pm 0.5$ | %FS              |

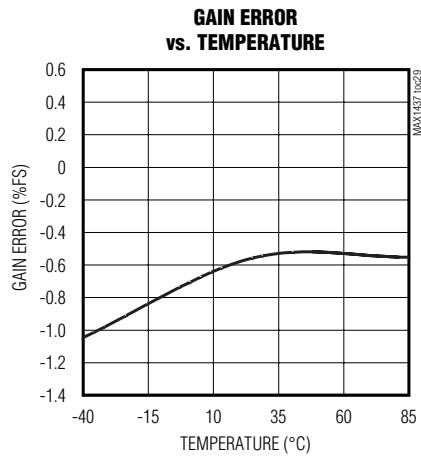

| Gain Error                                                                    |                   |                                       | -3   |            | +2        | %FS              |

| <b>ANALOG INPUTS (IN_P, IN_N)</b>                                             |                   |                                       |      |            |           |                  |

| Input Differential Range                                                      | V <sub>ID</sub>   | Differential input                    | 1.4  |            |           | V <sub>P-P</sub> |

| Common-Mode Voltage Range                                                     | V <sub>CMO</sub>  |                                       | 0.76 |            |           | V                |

| Common-Mode Voltage Range Tolerance                                           |                   | (Note 3)                              |      | $\pm 50$   |           | mV               |

| Differential Input Impedance                                                  | R <sub>IN</sub>   | Switched capacitor load               | 2    |            |           | k $\Omega$       |

| Differential Input Capacitance                                                | C <sub>IN</sub>   |                                       | 12.5 |            |           | pF               |

| <b>CONVERSION RATE</b>                                                        |                   |                                       |      |            |           |                  |

| Maximum Conversion Rate                                                       | f <sub>SMAX</sub> |                                       | 50   |            |           | MHz              |

| Minimum Conversion Rate                                                       | f <sub>SMIN</sub> |                                       | 4.0  |            |           | MHz              |

| Data Latency                                                                  |                   |                                       | 6.5  |            |           | Cycles           |

| <b>DYNAMIC CHARACTERISTICS (differential inputs, 4096-point FFT) (Note 2)</b> |                   |                                       |      |            |           |                  |

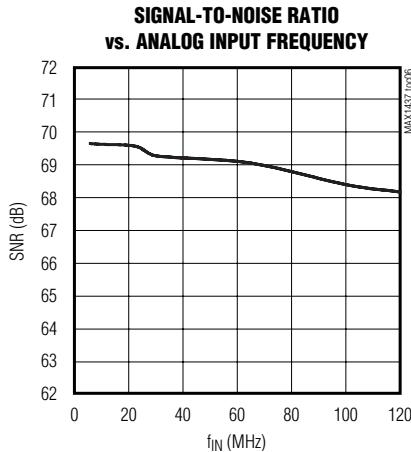

| Signal-to-Noise Ratio                                                         | SNR               | f <sub>IN</sub> = 5.3MHz at -0.5dBFS  | 69.9 |            |           | dB               |

|                                                                               |                   | f <sub>IN</sub> = 19.3MHz at -0.5dBFS | 66.5 | 69.7       |           |                  |

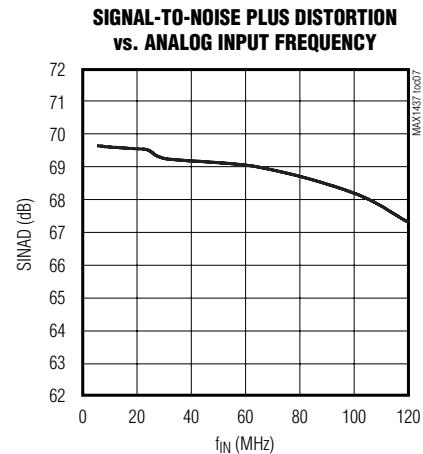

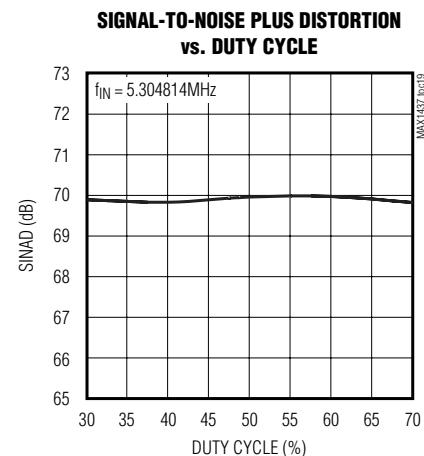

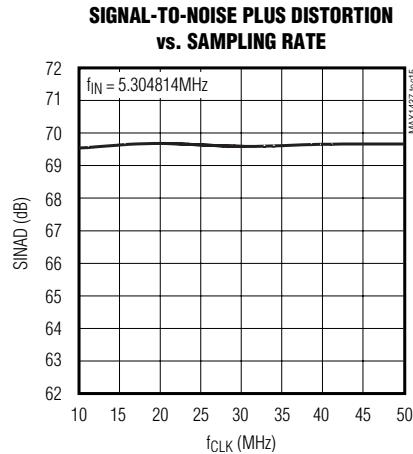

| Signal-to-Noise and Distortion (First 4 Harmonics)                            | SINAD             | f <sub>IN</sub> = 5.3MHz at -0.5dBFS  | 69.9 |            |           | dB               |

|                                                                               |                   | f <sub>IN</sub> = 19.3MHz at -0.5dBFS | 66.5 | 69.7       |           |                  |

| Effective Number of Bits                                                      | ENOB              | f <sub>IN</sub> = 5.3MHz at -0.5dBFS  | 11.3 |            |           | dB               |

|                                                                               |                   | f <sub>IN</sub> = 19.3MHz at -0.5dBFS | 11.3 |            |           |                  |

| Spurious-Free Dynamic Range                                                   | SFDR              | f <sub>IN</sub> = 5.3MHz at -0.5dBFS  | 96   |            |           | dBc              |

|                                                                               |                   | f <sub>IN</sub> = 19.3MHz at -0.5dBFS | 79   | 94         |           |                  |

# シリアルLVDS出力付き、オクタル、 12ビット、50MspS、1.8V ADC

MAX1437

## ELECTRICAL CHARACTERISTICS (continued)

(AV<sub>DD</sub> = 1.8V, OV<sub>DD</sub> = 1.8V, CV<sub>DD</sub> = 3.3V, GND = 0, external V<sub>REFIO</sub> = 1.24V, C<sub>REFIO</sub> to GND = 0.1μF, C<sub>REFP</sub> to GND = 10μF, C<sub>REFN</sub> to GND = 10μF, f<sub>CLK</sub> = 50MHz (50% duty cycle), V<sub>DT</sub> = 0, TA = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at TA = +25°C.) (Note 1)

| PARAMETER                                     | SYMBOL              | CONDITIONS                                                                 | MIN                     | TYP  | MAX  | UNITS       |

|-----------------------------------------------|---------------------|----------------------------------------------------------------------------|-------------------------|------|------|-------------|

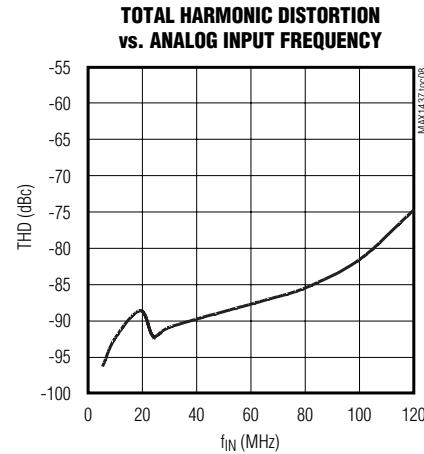

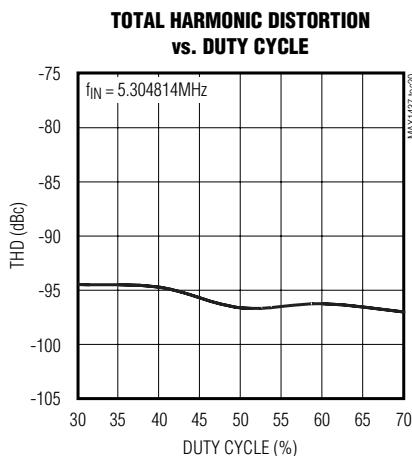

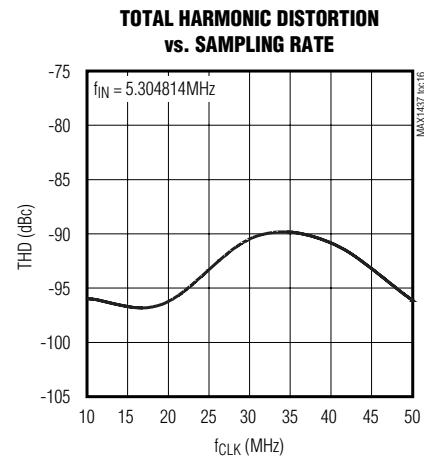

| Total Harmonic Distortion                     | THD                 | f <sub>IN</sub> = 5.3MHz at -0.5dBFS                                       |                         | -96  |      | dBc         |

|                                               |                     | f <sub>IN</sub> = 19.3MHz at -0.5dBFS                                      |                         | -90  | -79  |             |

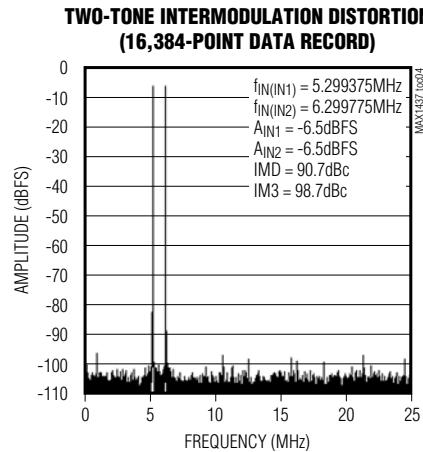

| Intermodulation Distortion                    | IMD                 | f <sub>1</sub> = 5.3MHz at -6.5dBFS<br>f <sub>2</sub> = 6.3MHz at -6.5dBFS |                         | 90.7 |      | dBc         |

| Third-Order Intermodulation                   | IM3                 | f <sub>1</sub> = 5.3MHz at -6.5dBFS<br>f <sub>2</sub> = 6.3MHz at -6.5dBFS |                         | 98.7 |      | dBc         |

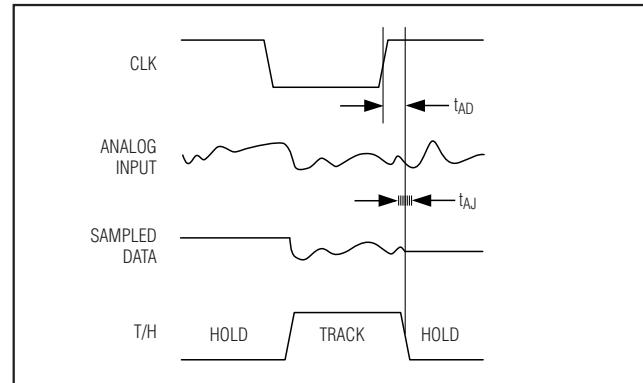

| Aperture Jitter                               | t <sub>AJ</sub>     | Figure 11                                                                  |                         | <0.4 |      | psRMS       |

| Aperture Delay                                | t <sub>AD</sub>     | Figure 11                                                                  |                         | 1    |      | ns          |

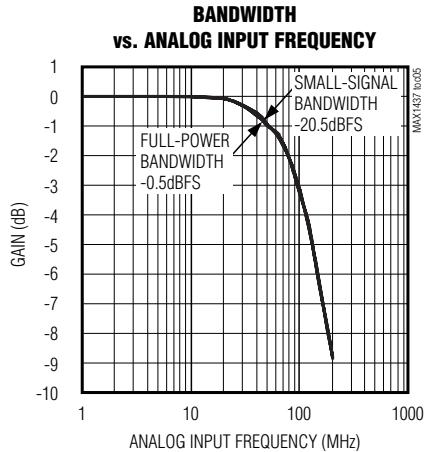

| Small-Signal Bandwidth                        | SSBW                | Input at -20dBFS                                                           |                         | 100  |      | MHz         |

| Full-Power Bandwidth                          | LSBW                | Input at -0.5dBFS                                                          |                         | 100  |      | MHz         |

| Output Noise                                  |                     | IN_P = IN_N                                                                |                         | 0.44 |      | LSBRMS      |

| Over-Range Recovery Time                      | t <sub>OR</sub>     | R <sub>S</sub> = 25Ω, C <sub>S</sub> = 50pF                                |                         | 1    |      | Clock cycle |

| <b>INTERNAL REFERENCE</b>                     |                     |                                                                            |                         |      |      |             |

| REFADJ Internal Reference-Mode Enable Voltage |                     | (Note 4)                                                                   |                         | 0.1  |      | V           |

| REFADJ Low-Leakage Current                    |                     |                                                                            |                         | 1.5  |      | mA          |

| REFIO Output Voltage                          | V <sub>REFIO</sub>  |                                                                            | 1.18                    | 1.24 | 1.30 | V           |

| Reference Temperature Coefficient             | T <sub>CREFIO</sub> |                                                                            |                         | 120  |      | ppm/°C      |

| <b>EXTERNAL REFERENCE</b>                     |                     |                                                                            |                         |      |      |             |

| REFADJ External Reference-Mode Enable Voltage |                     | (Note 4)                                                                   | AV <sub>DD</sub> - 0.1V |      |      | V           |

| REFADJ High-Leakage Current                   |                     |                                                                            | 200                     |      |      | μA          |

| REFIO Input Voltage                           |                     |                                                                            | 1.24                    |      |      | V           |

| REFIO Input Voltage Tolerance                 |                     |                                                                            | ±5                      |      |      | %           |

| REFIO Input Current                           | I <sub>REFIO</sub>  |                                                                            | <1                      |      |      | μA          |

| <b>COMMON-MODE OUTPUT (CMOUT)</b>             |                     |                                                                            |                         |      |      |             |

| CMOUT Output Voltage                          | V <sub>CMOUT</sub>  |                                                                            | 0.76                    |      |      | V           |

| <b>CLOCK INPUT (CLK)</b>                      |                     |                                                                            |                         |      |      |             |

| Input High Voltage                            | V <sub>CLKH</sub>   |                                                                            | 0.8 x CV <sub>DD</sub>  |      |      | V           |

| Input Low Voltage                             | V <sub>CLKL</sub>   |                                                                            | 0.2 x CV <sub>DD</sub>  |      |      | V           |

| Clock Duty Cycle                              |                     |                                                                            | 50                      |      |      | %           |

| Clock Duty-Cycle Tolerance                    |                     |                                                                            | ±30                     |      |      | %           |

| Input Leakage                                 | D <sub>IN</sub>     | Input at GND                                                               | 5                       |      |      | μA          |

|                                               |                     | Input at AV <sub>DD</sub>                                                  | 80                      |      |      |             |

| Input Capacitance                             | D <sub>CIN</sub>    |                                                                            | 5                       |      |      | pF          |

# シリアルLVDS出力付き、オクタル、 12ビット、50MspS、1.8V ADC

## ELECTRICAL CHARACTERISTICS (continued)

(AV<sub>DD</sub> = 1.8V, OV<sub>DD</sub> = 1.8V, CV<sub>DD</sub> = 3.3V, GND = 0, external V<sub>REFIO</sub> = 1.24V, C<sub>REFIO</sub> to GND = 0.1μF, C<sub>REFP</sub> to GND = 10μF, C<sub>REFN</sub> to GND = 10μF, f<sub>CLK</sub> = 50MHz (50% duty cycle), V<sub>DT</sub> = 0, TA = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at TA = +25°C.) (Note 1)

| PARAMETER                                                                                   | SYMBOL               | CONDITIONS                                                                            | MIN                                   | TYP                    | MAX | UNITS |

|---------------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------|---------------------------------------|------------------------|-----|-------|

| <b>DIGITAL INPUTS (PLL<sub>—</sub>, LVDSTEST, DT, SLVS, PD, T/B)</b>                        |                      |                                                                                       |                                       |                        |     |       |

| Input High Threshold                                                                        | V <sub>IH</sub>      |                                                                                       | 0.8 x AV <sub>DD</sub>                |                        |     | V     |

| Input Low Threshold                                                                         | V <sub>IL</sub>      |                                                                                       |                                       | 0.2 x AV <sub>DD</sub> |     | V     |

| Input Leakage                                                                               | DI <sub>IN</sub>     | Input at GND                                                                          |                                       | 5                      |     | μA    |

|                                                                                             |                      | Input at AV <sub>DD</sub>                                                             |                                       | 80                     |     |       |

| Input Capacitance                                                                           | DC <sub>IN</sub>     |                                                                                       |                                       | 5                      |     | pF    |

| <b>LVDS OUTPUTS (OUT_P, OUT_N), SLVS/LVDS = 0</b>                                           |                      |                                                                                       |                                       |                        |     |       |

| Differential Output Voltage                                                                 | V <sub>OHDIFF</sub>  | RTERM = 100Ω                                                                          | 250                                   | 450                    |     | mV    |

| Output Common-Mode Voltage                                                                  | V <sub>OCM</sub>     | RTERM = 100Ω                                                                          | 1.125                                 | 1.375                  |     | V     |

| Rise Time (20% to 80%)                                                                      | t <sub>RL</sub>      | RTERM = 100Ω, C <sub>LOAD</sub> = 5pF                                                 | 350                                   |                        |     | ps    |

| Fall Time (80% to 20%)                                                                      | t <sub>FL</sub>      | RTERM = 100Ω, C <sub>LOAD</sub> = 5pF                                                 | 350                                   |                        |     | ps    |

| <b>SLVS OUTPUTS (OUT_P, OUT_N, CLKOUTP, CLKOUTN, FRAMEP, FRAMEN), SLVS/LVDS = 1, DT = 1</b> |                      |                                                                                       |                                       |                        |     |       |

| Differential Output Voltage                                                                 | V <sub>OHDIFF</sub>  | RTERM = 100Ω                                                                          | 205                                   |                        |     | mV    |

| Output Common-Mode Voltage                                                                  | V <sub>OCM</sub>     | RTERM = 100Ω                                                                          | 220                                   |                        |     | V     |

| Rise Time (20% to 80%)                                                                      | t <sub>RS</sub>      | RTERM = 100Ω, C <sub>LOAD</sub> = 5pF                                                 | 320                                   |                        |     | ps    |

| Fall Time (80% to 20%)                                                                      | t <sub>FS</sub>      | RTERM = 100Ω, C <sub>LOAD</sub> = 5pF                                                 | 320                                   |                        |     | ps    |

| <b>POWER-DOWN</b>                                                                           |                      |                                                                                       |                                       |                        |     |       |

| PD Fall to Output Enable                                                                    | t <sub>ENABLE</sub>  | (Note 5)                                                                              | 100                                   |                        |     | ms    |

| PD Rise to Output Disable                                                                   | t <sub>DISABLE</sub> |                                                                                       | 20                                    |                        |     | ns    |

| <b>POWER REQUIREMENTS</b>                                                                   |                      |                                                                                       |                                       |                        |     |       |

| AV <sub>DD</sub> Supply Voltage Range                                                       | AV <sub>DD</sub>     |                                                                                       | 1.7                                   | 1.8                    | 1.9 | V     |

| OV <sub>DD</sub> Supply Voltage Range                                                       | OV <sub>DD</sub>     |                                                                                       | 1.7                                   | 1.8                    | 1.9 | V     |

| CV <sub>DD</sub> Supply Voltage Range                                                       | CV <sub>DD</sub>     |                                                                                       | 1.7                                   | 1.8                    | 3.6 | V     |

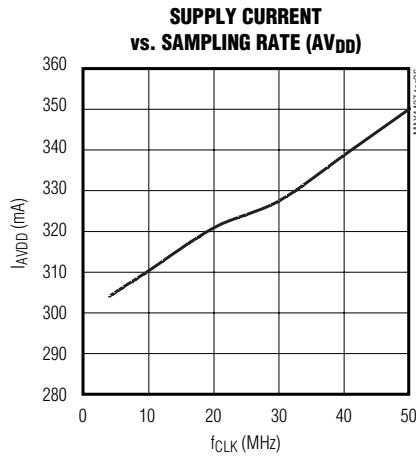

| AV <sub>DD</sub> Supply Current                                                             | I <sub>AVDD</sub>    | f <sub>IN</sub> = 19.3MHz<br>at -0.5dBFS                                              | PD = 0                                | 348                    | 390 | mA    |

|                                                                                             |                      |                                                                                       | PD = 0, DT = 1                        | 348                    |     |       |

|                                                                                             |                      |                                                                                       | PD = 1, power-down,<br>no clock input | 1.16                   |     | mA    |

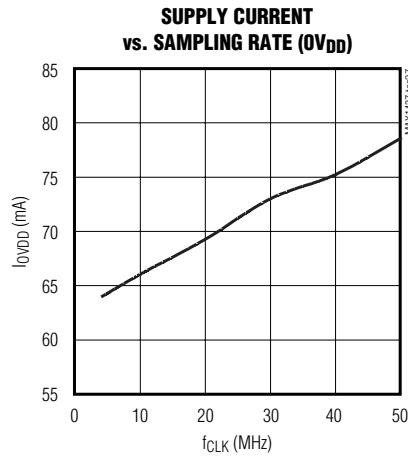

| OV <sub>DD</sub> Supply Current                                                             | I <sub>OVDD</sub>    | f <sub>IN</sub> = 19.3MHz<br>at -0.5dBFS                                              | PD = 0                                | 79                     | 100 | mA    |

|                                                                                             |                      |                                                                                       | PD = 0, DT = 1                        | 103                    |     |       |

|                                                                                             |                      |                                                                                       | PD = 1, power-down,<br>no clock input | 960                    |     | μA    |

| CV <sub>DD</sub> Supply Current                                                             | I <sub>CVDD</sub>    | CV <sub>DD</sub> is used only to bias ESD-protection<br>diodes on CLK input, Figure 2 |                                       | 0                      |     | mA    |

| Power Dissipation                                                                           | P <sub>DISS</sub>    | f <sub>IN</sub> = 19.3MHz at -0.5dBFS                                                 |                                       | 769                    | 882 | mW    |

# シリアルLVDS出力付き、オクタル、 12ビット、50MspS、1.8V ADC

## ELECTRICAL CHARACTERISTICS (continued)

(AV<sub>DD</sub> = 1.8V, OV<sub>DD</sub> = 1.8V, CV<sub>DD</sub> = 3.3V, GND = 0, external V<sub>REFIO</sub> = 1.24V, C<sub>REFIO</sub> to GND = 0.1 $\mu$ F, C<sub>REFP</sub> to GND = 10 $\mu$ F, C<sub>REFN</sub> to GND = 10 $\mu$ F, f<sub>CLK</sub> = 50MHz (50% duty cycle), V<sub>DT</sub> = 0, TA = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at TA = +25°C.) (Note 1)

| PARAMETER                              | SYMBOL          | CONDITIONS                        | MIN                               | TYP                               | MAX | UNITS   |

|----------------------------------------|-----------------|-----------------------------------|-----------------------------------|-----------------------------------|-----|---------|

| <b>TIMING CHARACTERISTICS (Note 6)</b> |                 |                                   |                                   |                                   |     |         |

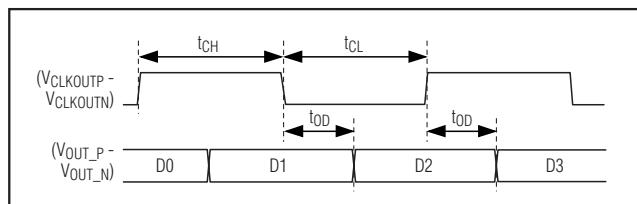

| Data Valid to CLKOUT Rise/Fall         | t <sub>OD</sub> | Figure 5 (Note 7)                 | (t <sub>SAMPLE</sub> / 24) - 0.15 | (t <sub>SAMPLE</sub> / 24) + 0.15 |     | ns      |

| CLKOUT Output-Width High               | t <sub>CH</sub> | Figure 5                          |                                   | t <sub>SAMPLE</sub> / 12          |     | ns      |

| CLKOUT Output-Width Low                | t <sub>CL</sub> | Figure 5                          |                                   | t <sub>SAMPLE</sub> / 12          |     | ns      |

| FRAME Rise to CLKOUT Rise              | t <sub>CF</sub> | Figure 4 (Note 7)                 | (t <sub>SAMPLE</sub> / 24) - 0.15 | (t <sub>SAMPLE</sub> / 24) + 0.15 |     | ns      |

| Sample CLK Rise to FRAME Rise          | t <sub>SF</sub> | Figure 4 (Note 7)                 | (t <sub>SAMPLE</sub> / 2) + 1.1   | (t <sub>SAMPLE</sub> / 2) + 2.6   |     | ns      |

| Crosstalk                              |                 | (Note 2)                          |                                   | -95                               |     | dB      |

| Gain Matching                          | C <sub>GM</sub> | f <sub>IN</sub> = 5.3MHz (Note 2) |                                   | $\pm 0.1$                         |     | dB      |

| Phase Matching                         | C <sub>PM</sub> | f <sub>IN</sub> = 5.3MHz (Note 2) |                                   | $\pm 0.25$                        |     | Degrees |

**Note 1:** Specifications at TA  $\geq$  +25°C are guaranteed by production testing. Specifications at TA < +25°C are guaranteed by design and characterization and not subject to production testing.

**Note 2:** See definition in the *Parameter Definition* section at the end of this data sheet.

**Note 3:** See the *Common-Mode Output (CMOUT)* section.

**Note 4:** Connect REFADJ to GND directly to enable internal reference mode. Connect REFADJ to AV<sub>DD</sub> directly to disable the internal bandgap reference and enable external reference mode.

**Note 5:** Measured using C<sub>REFP</sub> to GND = 1 $\mu$ F and C<sub>REFN</sub> to GND = 1 $\mu$ F. t<sub>ENABLE</sub> time may be lowered by using smaller capacitor values.

**Note 6:** Data valid to CLKOUT rise/fall timing is measured from 50% of data output level to 50% of clock output level.

**Note 7:** Guaranteed by design and characterization. Not subject to production testing.

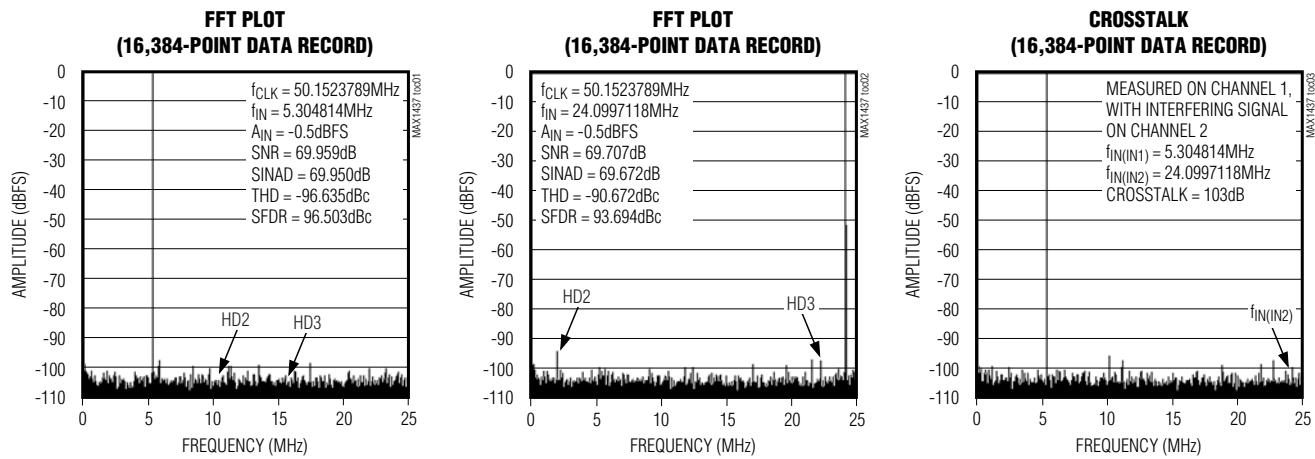

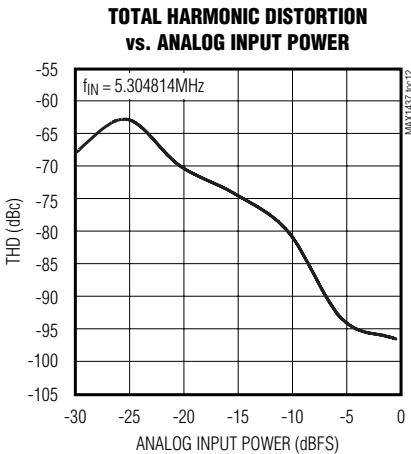

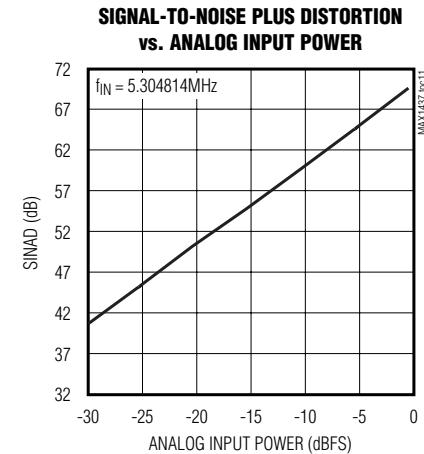

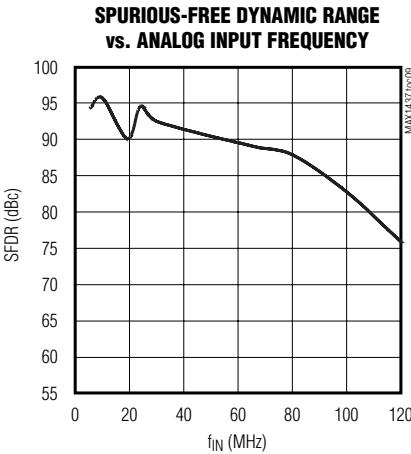

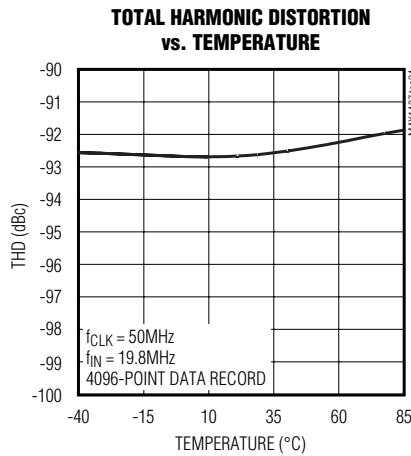

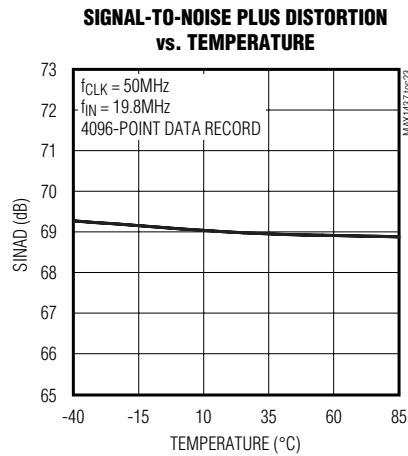

## 標準動作特性

(AV<sub>DD</sub> = 1.8V, OV<sub>DD</sub> = 1.8V, CV<sub>DD</sub> = 3.3V, GND = 0, internal reference, differential input at -0.5dBFS, f<sub>IN</sub> = 5.3MHz, f<sub>CLK</sub> = 50MHz (50% duty cycle), V<sub>DT</sub> = 0, C<sub>LOAD</sub> = 10pF, TA = +25°C, unless otherwise noted.)

MAX1437

# シリアルLVDS出力付き、オクタル、 12ビット、50Msps、1.8V ADC

## 標準動作特性(続き)

(AVDD = 1.8V, OVDD = 1.8V, CVDD = 3.3V, GND = 0, internal reference, differential input at -0.5dBFS, fIN = 5.3MHz, fCLK = 50MHz (50% duty cycle), VDT = 0, CLOAD = 10pF, TA = +25°C, unless otherwise noted.)

# シリアルLVDS出力付き、オクタル、 12ビット、50Msps、1.8V ADC

## 標準動作特性(続き)

(AV<sub>DD</sub> = 1.8V, OV<sub>DD</sub> = 1.8V, CV<sub>DD</sub> = 3.3V, GND = 0, internal reference, differential input at -0.5dBFS, f<sub>IN</sub> = 5.3MHz, f<sub>CLK</sub> = 50MHz (50% duty cycle), V<sub>DT</sub> = 0, C<sub>LOAD</sub> = 10pF, T<sub>A</sub> = +25°C, unless otherwise noted.)

# シリアルLVDS出力付き、オクタル、 12ビット、50Msps、1.8V ADC

## 標準動作特性(続き)

(AV<sub>DD</sub> = 1.8V, OV<sub>DD</sub> = 1.8V, CV<sub>DD</sub> = 3.3V, GND = 0, internal reference, differential input at -0.5dBFS, f<sub>IN</sub> = 5.3MHz, f<sub>CLK</sub> = 50MHz (50% duty cycle), V<sub>DT</sub> = 0, C<sub>LOAD</sub> = 10pF, T<sub>A</sub> = +25°C, unless otherwise noted.)

# シリアルLVDS出力付き、オクタル、 12ビット、50MspS、1.8V ADC

## 標準動作特性(続き)

(AV<sub>DD</sub> = 1.8V, OV<sub>DD</sub> = 1.8V, CV<sub>DD</sub> = 3.3V, GND = 0, internal reference, differential input at -0.5dBFS, f<sub>IN</sub> = 5.3MHz, f<sub>CLK</sub> = 50MHz (50% duty cycle), V<sub>DT</sub> = 0, C<sub>LOAD</sub> = 10pF, T<sub>A</sub> = +25°C, unless otherwise noted.)

# シリアルLVDS出力付き、オクタル、 12ビット、50MspS、1.8V ADC

## 端子説明

| 端子                                                               | 名称        | 機能                                                                                                                                                                                                                |

|------------------------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 4, 7, 10, 16, 19, 22, 25, 26, 27, 30, 36, 89, 92, 96, 99, 100 | GND       | グラウンド。すべてのGND端子を同じ電位に接続してください。                                                                                                                                                                                    |

| 2                                                                | IN1P      | チャネル1の正アナログ入力                                                                                                                                                                                                     |

| 3                                                                | IN1N      | チャネル1の負アナログ入力                                                                                                                                                                                                     |

| 5                                                                | IN2P      | チャネル2の正アナログ入力                                                                                                                                                                                                     |

| 6                                                                | IN2N      | チャネル2の負アナログ入力                                                                                                                                                                                                     |

| 8                                                                | IN3P      | チャネル3の正アナログ入力                                                                                                                                                                                                     |

| 9                                                                | IN3N      | チャネル3の負アナログ入力                                                                                                                                                                                                     |

| 11, 12, 13, 15, 37–42, 86, 87, 88                                | AVDD      | アナログ電源入力。AV <sub>DD</sub> を+1.7V～+1.9Vの電源に接続してください。デバイスに可能な限り近接した0.1μFコンデンサでAV <sub>DD</sub> をGNDにバイパスしてください。2.2μF以上の大容量コンデンサでAV <sub>DD</sub> 電源プレーンをGNDプレーンにバイパスしてください。すべてのAV <sub>DD</sub> 端子を同じ電位に接続してください。   |

| 14, 31, 50, 51, 70, 75, 76                                       | N.C.      | 接続なし。内部で接続されていません。                                                                                                                                                                                                |

| 17                                                               | IN4P      | チャネル4の正アナログ入力                                                                                                                                                                                                     |

| 18                                                               | IN4N      | チャネル4の負アナログ入力                                                                                                                                                                                                     |

| 20                                                               | IN5P      | チャネル5の正アナログ入力                                                                                                                                                                                                     |

| 21                                                               | IN5N      | チャネル5の負アナログ入力                                                                                                                                                                                                     |

| 23                                                               | IN6P      | チャネル6の正アナログ入力                                                                                                                                                                                                     |

| 24                                                               | IN6N      | チャネル6の負アナログ入力                                                                                                                                                                                                     |

| 28                                                               | IN7P      | チャネル7の正アナログ入力                                                                                                                                                                                                     |

| 29                                                               | IN7N      | チャネル7の負アナログ入力                                                                                                                                                                                                     |

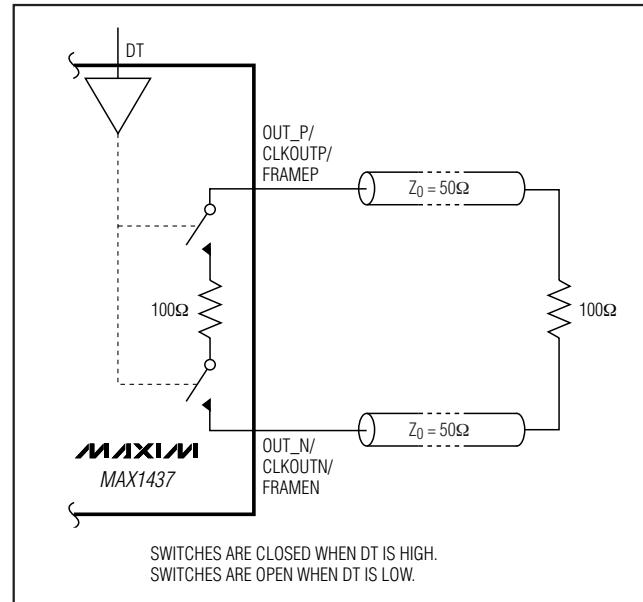

| 32                                                               | DT        | 2重終端の選択。差動出力ペア間の100Ωの内部終端を選択するには、DTをハイにしてください。出力終端を選択しない場合は、DTをローにしてください。                                                                                                                                         |

| 33                                                               | SLVS/LVDS | 差動出力信号形式の選択入力。SLVS出力を選択するには、SLVS/LVDSをハイにしてください。LVDS出力を選択するには、SLVS/LVDSをローにしてください。                                                                                                                                |

| 34                                                               | CVDD      | クロック電源入力。CV <sub>DD</sub> を+1.7V～+3.6Vの電源に接続してください。2.2μF以上のコンデンサと並列に0.1μFのコンデンサでCV <sub>DD</sub> をGNDにバイパスしてください。デバイスにできるだけ近接してバイパスコンデンサを実装してください。                                                                |

| 35                                                               | CLK       | シングルエンドCMOSクロック入力                                                                                                                                                                                                 |

| 43, 46, 49, 54, 57, 60, 63, 64, 67, 71, 74, 77                   | OVDD      | 出力ドライバ電源入力。OV <sub>DD</sub> を+1.7V～+1.9Vの電源に接続してください。デバイスにできる限り近接した0.1μFコンデンサでOV <sub>DD</sub> をGNDにバイパスしてください。2.2μF以上の大容量コンデンサでOV <sub>DD</sub> 電源プレーンをGNDプレーンにバイパスしてください。すべてのOV <sub>DD</sub> 端子を同じ電位に接続してください。 |

| 44                                                               | OUT7N     | チャネル7の負LVDS/SLVS出力                                                                                                                                                                                                |

| 45                                                               | OUT7P     | チャネル7の正LVDS/SLVS出力                                                                                                                                                                                                |

| 47                                                               | OUT6N     | チャネル6の負LVDS/SLVS出力                                                                                                                                                                                                |

| 48                                                               | OUT6P     | チャネル6の正LVDS/SLVS出力                                                                                                                                                                                                |

| 52                                                               | OUT5N     | チャネル5の負LVDS/SLVS出力                                                                                                                                                                                                |

| 53                                                               | OUT5P     | チャネル5の正LVDS/SLVS出力                                                                                                                                                                                                |

| 55                                                               | OUT4N     | チャネル4の負LVDS/SLVS出力                                                                                                                                                                                                |

| 56                                                               | OUT4P     | チャネル4の正LVDS/SLVS出力                                                                                                                                                                                                |

# シリアルLVDS出力付き、オクタル、 12ビット、50MspS、1.8V ADC

## 端子説明(続き)

| 端子 | 名称       | 機能                                                                                                                                                                  |

|----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 58 | FRAMEN   | 負フレーム整列LVDS/SLVS出力。差動フレーム出力の立上りエッジが出力データストリームの正しいD0位置に整列します。                                                                                                        |

| 59 | FRAMEP   | 正フレーム整列LVDS/SLVS出力。差動フレーム出力の立上りエッジが出力データストリームの正しいD0位置に整列します。                                                                                                        |

| 61 | CLKOUTN  | 負のLVDS/SLVSシリアルクロック出力                                                                                                                                               |

| 62 | CLKOUTP  | 正のLVDS/SLVSシリアルクロック出力                                                                                                                                               |

| 65 | OUT3N    | チャネル3の負LVDS/SLVS出力                                                                                                                                                  |

| 66 | OUT3P    | チャネル3の正LVDS/SLVS出力                                                                                                                                                  |

| 68 | OUT2N    | チャネル2の負LVDS/SLVS出力                                                                                                                                                  |

| 69 | OUT2P    | チャネル2の正LVDS/SLVS出力                                                                                                                                                  |

| 72 | OUT1N    | チャネル1の負LVDS/SLVS出力                                                                                                                                                  |

| 73 | OUT1P    | チャネル1の正LVDS/SLVS出力                                                                                                                                                  |

| 78 | OUT0N    | チャネル0の負LVDS/SLVS出力                                                                                                                                                  |

| 79 | OUT0P    | チャネル0の正LVDS/SLVS出力                                                                                                                                                  |

| 80 | LVDSTEST | LVDSテストパターンのイネーブル。出力テストパターンをイネーブルするには、LVDSTESTをハイにしてください(0000 1011 1101 MSB→LSB)。アナログ変換結果と同様に、テストパターンデータはLSBを先頭とした出力です。通常動作にするには、LVDSTESTをローにしてください。                |

| 81 | PD       | パワーダウンの入力。すべてのチャネルとリファレンスをパワーダウンするには、PDをハイにしてください。通常動作にするには、PDをローにしてください。                                                                                           |

| 82 | PLL3     | PLL制御入力3。詳細については、表1を参照してください。                                                                                                                                       |

| 83 | PLL2     | PLL制御入力2。詳細については、表1を参照してください。                                                                                                                                       |

| 84 | PLL1     | PLL制御入力1。詳細については、表1を参照してください。                                                                                                                                       |

| 85 | TB       | 出力形式の選択入力。バイナリ出力形式を選択するには、TBをハイしてください。2の補数出力形式を選択するには、TBをローにしてください。                                                                                                 |

| 90 | REFN     | 負リファレンスバイパス出力。1μF以上のコンデンサ(10μF, typ)をREFPとREFNの間に接続し、1μF以上のコンデンサ(10μF, typ)をREFNとGNDの間に接続してください。これらのコンデンサはプリント(PC)基板の同じ面にデバイスにできる限り近接して配置してください。                    |

| 91 | REFP     | 正リファレンスバイパス出力。1μF以上のコンデンサ(10μF, typ)をREFPとREFNの間に接続し、1μF以上のコンデンサ(10μF, typ)をREFPとGNDの間に接続してください。これらのコンデンサはプリント(PC)基板の同じ面にデバイスにできる限り近接して配置してください。                    |

| 93 | REFIO    | リファレンス入力/出力。内部リファレンス動作(REFADJ = GND)の場合は、リファレンス出力電圧は1.24Vです。外部リファレンス動作(REFADJ = AVDD)の場合は、REFIOに安定したリファレンス電圧を印加してください。0.1μF以上でGNDにバイパスしてください。                       |

| 94 | REFADJ   | 内部または外部リファレンスマードの選択およびリファレンス調整の入力。内部リファレンスマードの場合は、REFADJをGNDに直接接続してください。外部リファレンスマードの場合は、REFADJをAVDDに直接接続してください。リファレンス調整モードの場合は、「内部リファレンスによるフルスケール範囲の調整」の項を参照してください。 |

| 95 | CMOUT    | コモンモードリファレンス電圧出力。CMOUTは、DC結合アプリケーション用に入力コモンモード電圧を出力します。0.1μF以上のコンデンサでCMOUTをGNDにバイパスしてください。                                                                          |

| 97 | INOP     | チャネル0の正アナログ入力                                                                                                                                                       |

| 98 | INON     | チャネル0の負アナログ入力                                                                                                                                                       |

| —  | EP       | エクスポートドパッド。EPはGNDに内部で接続されています。EPをGNDに接続してください。                                                                                                                      |

MAX1437

# シリアルLVDS出力付き、オクタル、 12ビット、50MspS、1.8V ADC

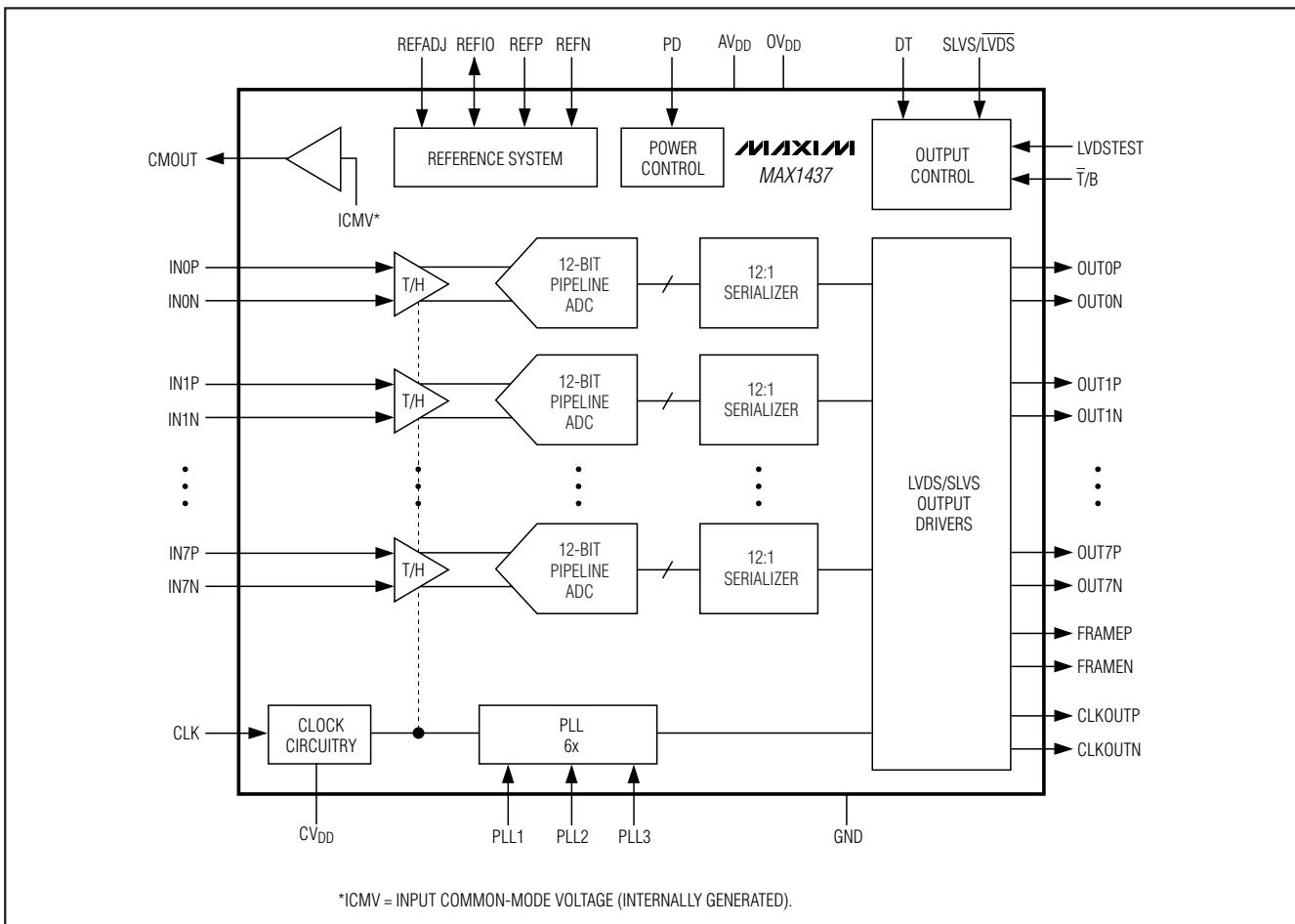

## ファンクションダイアグラム

## 詳細

ADCのMAX1437は、高速度信号変換のために完全差動入力、パイプラインアーキテクチャ、およびデジタルエラー補正を備えています。ADCパイプラインアーキテクチャによって、入力で取り込まれたサンプルは半クロックサイクルごとに各パイプライン段を進行します。変換されたデジタル結果はシリアル化され、LVDS/SLVS出力ドライバを通じて送出されます。入力から出力までの総クロックサイクル遅延は、6.5クロックサイクルです。

MAX1437は、入力と出力が同期した8つの個別の完全差動チャネルを備えています。T/Bデジタル入力によって、出力をバイナリまたは2の補数に設定してください。グローバルパワーダウンによって、電力消費が最小限に抑制されます。

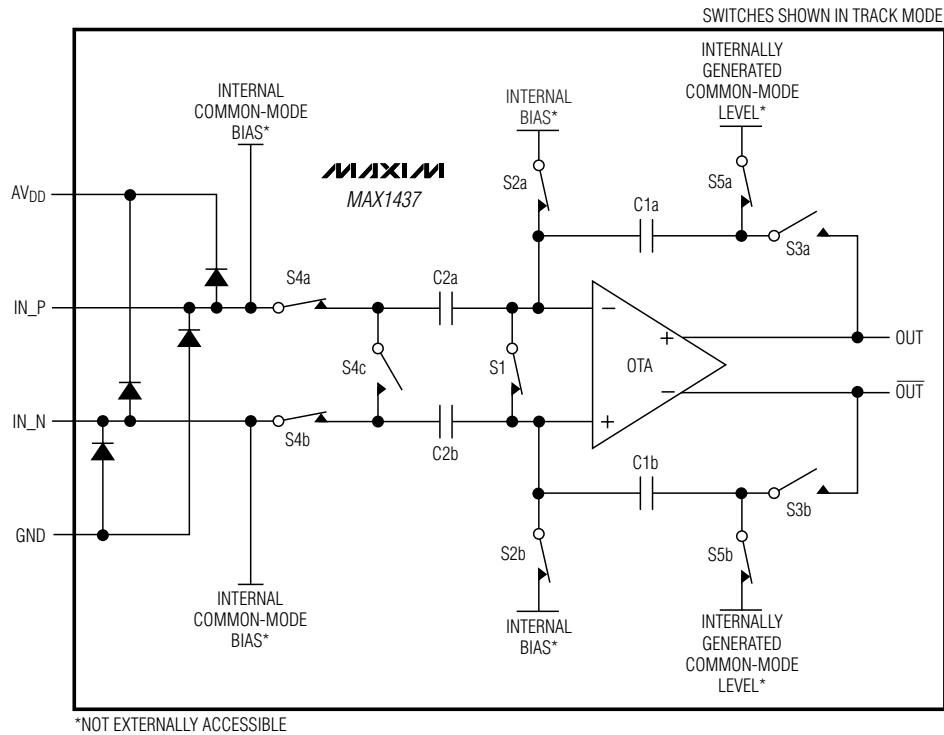

## 入力回路

図1は、入力T/H回路の簡略図を示しています。トラックモードでは、スイッチS1、S2a、S2b、S4a、S4b、S5a、およびS5bは閉じています。完全差動回路は、スイッチS4aおよびS4bを通じて2個のコンデンサ(C2aおよびC2b)に入力信号をサンプルします。S2aとS2bはトランスクンダクタンスオペアンプ(OTA)のコモンモードを設定し、S1と同時に開かれて入力波形をサンプリングします。次に、スイッチS4a、S4b、S5a、およびS5bが開かれた後に、スイッチS3aとS3bはコンデンサC1aおよびC1bをアンプの出力と接続し、スイッチS4cが閉じられます。得られた差動電圧は、コンデンサC2aとC2bに保持されます。アンプは、コンデンサC2aとC2bに当初保持されていた値まで、コンデンサC1aとC1bを充電します。次に、これらの値は第1段の量子化器に送られ、高速変動する入力からパイプラインが分離されます。

# シリアルLVDS出力付き、オクタル、12ビット、50MspS、1.8V ADC

MAX1437

図1. 内部入力回路

IN\_P～IN\_N間のアナログ入力は、差動駆動されます。差動入力の場合は、性能を最適化するために、IN\_PおよびIN\_Nの入力インピーダンスをバランスさせてください。

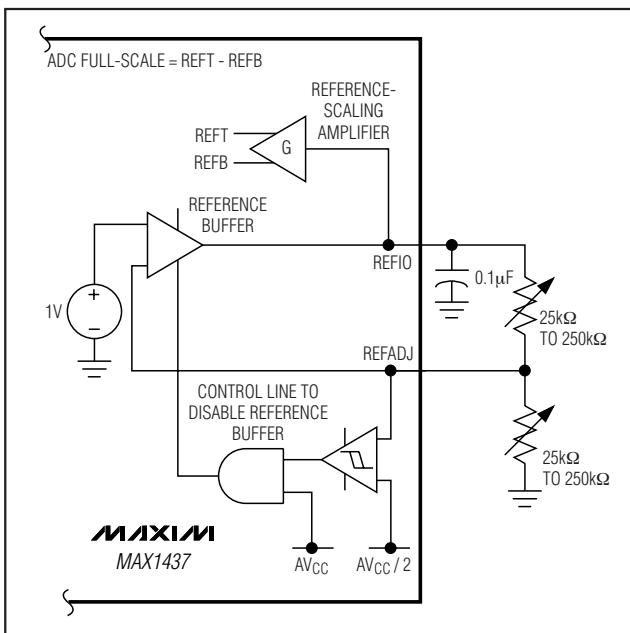

## リファレンス構成(REFIO、REFADJ、REFP、およびREFN)

MAX1437は1.24Vの内部バンドギャップリファレンスを備えていますが、外部リファレンス電圧で駆動することもできます。フルスケールアナログ差動入力範囲は $\pm$ FSRです。FSR(フルスケール範囲)は、次式から求められます。

$$FSR = \frac{(0.700 \times V_{REFIO})}{1.24V}$$

ここで、 $V_{REFIO}$ は、内部または外部で生成されるREFIOの電圧です。 $V_{REFIO} = 1.24V$ の場合は、フルスケール入力範囲は $\pm 700mV$ ( $1.4V_{P-P}$ )です。

## 内部リファレンスマード

内部バンドギャップリファレンスを直接使用するには、REFADJをGNDに接続してください。内部バンドギャップリファレンスは、内部リファレンスマードの場合、温度係数が $120ppm/^\circ C$ の1.24Vの $V_{REFIO}$ を生成します。安定化させるには、 $0.1\mu F$ 以上の外付けバイパスコンデンサをREFIOとGNDの間に接続してください。REFIOは外部回路に対して最大 $200\mu A$ までソースし、シンクします。REFIOの負荷レギュレーションは $75mV/mA$ です。MAX1437がパワーダウンモードのときは、REFIOはGNDに対して $1M\Omega$ を超える抵抗を備えています。電源がMAX1437に印加された場合またはPDがハイからローに遷移する場合、内部リファレンス回路は起動とセトリングに $100ms$ ( $C_{REFP} \sim GND = C_{REFN} \sim GND = 1\mu F$ の場合)が必要です。

利得誤差を補償するか、またはADCのFSRの拡大や縮小を行うには、REFADJとGNDの間またはREFADJとREFIOの間に外付け抵抗器を追加してください。この抵抗器によって、MAX1437の内部リファレンス値をその公称値の最大 $\pm 5\%$ まで調整します。「内部リファレンスによるフルスケール範囲の調整」の項を参照してください。

# シリアルLVDS出力付き、オクタル、 12ビット、50MspS、1.8V ADC

GNDへの1 $\mu$ F以上のコンデンサ(10 $\mu$ F, typ)をREFPおよびREFNとの間に接続し、1 $\mu$ F以上のコンデンサ(10 $\mu$ F, typ)をREFPとREFNの間にデバイスとプリント基板の同じ面でデバイスにできる限り近接して接続してください。

## 外部リファレンスマード

外部リファレンスマードでは、MAX1437のリファレンスマート電圧に優る制御を可能とし、複数のコンバータが共通リファレンスを使用することができます。内部リファレンスをディセーブルするには、REFADJをAV<sub>DD</sub>に接続してください。REFIOに安定した1.18V~1.30Vの電源を印加してください。0.1 $\mu$ F以上のコンデンサでREFIOをGNDにバイパスしてください。REFIOの入力インピーダンスは1M $\Omega$ を超えます。

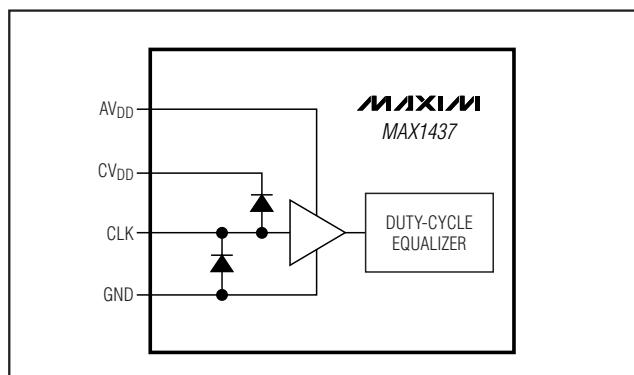

## クロック入力(CLK)

MAX1437は、入力クロックデューティサイクルが20%~80%と広範囲のCMOSコンパチブルクロック信号を受け付けます。外付けシングルエンドクロック信号でCLKを駆動してください。図2は、簡略化されたクロック入力回路を示しています。

MAX1437の規定のSNR性能を得るには、低クロックジッタが必要です。アナログ入力サンプリングはCLKの立上りエッジで行われるため、このエッジのジッタは可能な限り小さくする必要があります。ジッタはADCの最大SNR性能に限界を与え、それは次の式によります：

$$SNR = 20 \times \log \left( \frac{1}{2 \times \pi \times f_{IN} \times t_J} \right)$$

ここで、f<sub>IN</sub>はアナログ入力周波数を表し、t<sub>J</sub>は総システムクロックジッタです。

## PLL入力(PLL1、PLL2、PLL3)

MAX1437は、入力クロックの6倍の周波数の出力クロック信号を生成するPLLを備えています。出力クロック信号は、MAX1437からデータをクロックアウトする

図2. クロック入力回路

表1. PLL1、PLL2、およびPLL3の構成表

| PLL1 | PLL2 | PLL3 | INPUT CLOCK RANGE (MHz) |      |

|------|------|------|-------------------------|------|

|      |      |      | MIN                     | MAX  |

| 0    | 0    | 0    | 45.0                    | 50.0 |

| 0    | 0    | 1    | 32.5                    | 45.0 |

| 0    | 1    | 0    | 22.5                    | 32.5 |

| 0    | 1    | 1    | 16.3                    | 22.5 |

| 1    | 0    | 0    | 11.3                    | 16.3 |

| 1    | 0    | 1    | 8.1                     | 11.3 |

| 1    | 1    | 0    | 5.6                     | 8.1  |

| 1    | 1    | 1    | 4.0                     | 5.6  |

ために使われます(「システムタイミング要件」の項を参照)。表1に記載の入力クロック範囲に従って、PLL1、PLL2、およびPLL3ビットを設定してください。

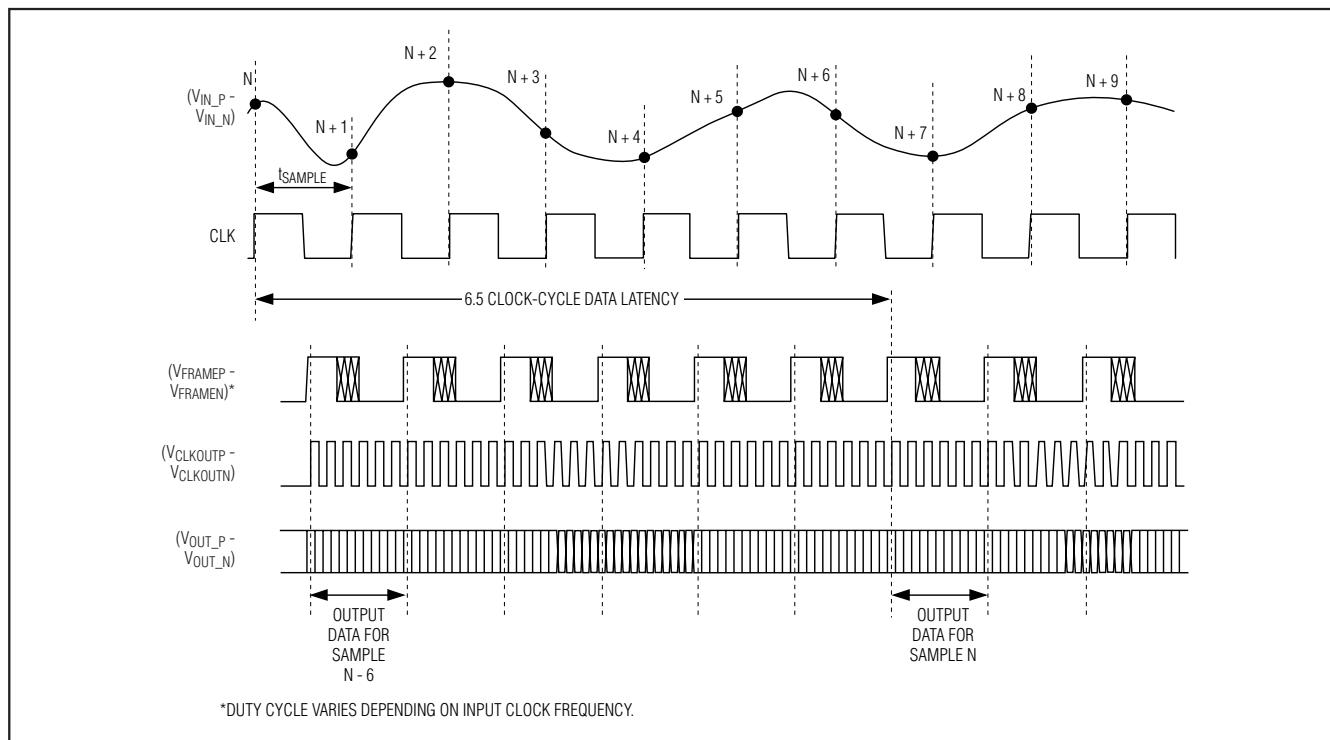

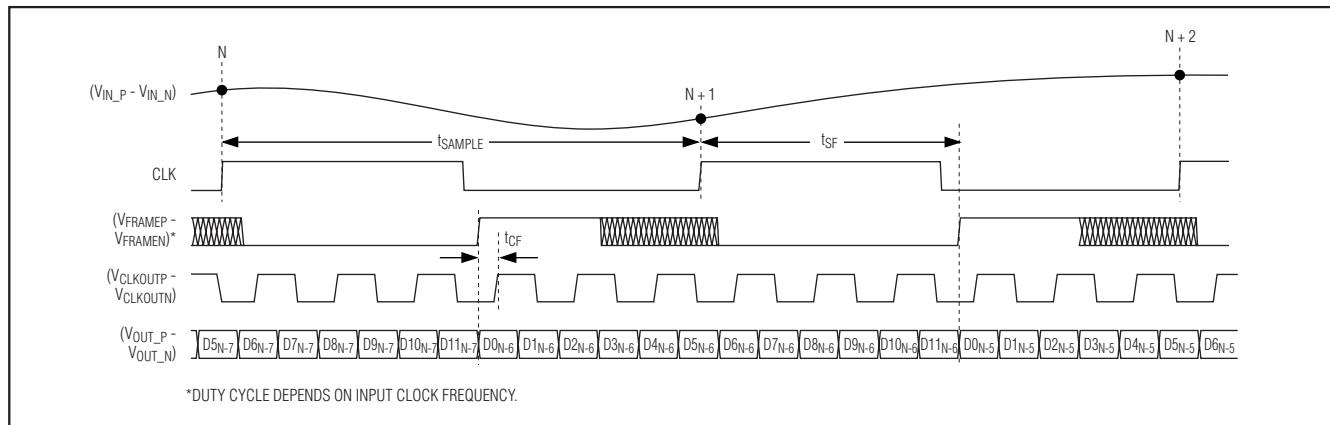

## システムタイミング要件

図3は、アナログ入力、入力クロック、フレーム整列出力、シリアルクロック出力、およびシリアルデータ出力間の関係を示しています。差動アナログ入力(IN\_PおよびIN\_N)はCLK信号の立上りエッジでサンプリングされ、変換結果のデータは6.5クロックサイクル後にデジタル出力に現れます。図4は、入力と出力間の関係についての詳細な2変換のタイミング図を示しています。

## クロック出力(CLKOUTP、CLKOUTN)

MAX1437は、CLKOUTPとCLKOUTNから構成される差動クロック出力を備えています。図4に示すように、シリアル出力データはクロック出力の両エッジでMAX1437からクロックアウトされます。出力クロックの周波数は、CLKの周波数の6倍です。

## フレーム整列出力(FRAMEP、FRAMEN)

MAX1437は、FRAMEPとFRAMENから構成される差動フレーム整列信号を備えています。図4に示すように、フレーム整列信号の立上りエッジは、12ビットシリアルデータストリームの先頭ビット(D0)に対応しています。フレームアライメント信号の周波数は、入力クロックの周波数と同じです。

## シリアル出力データ(OUT\_P、OUT\_N)

MAX1437は、OUT\_PとOUT\_Nから構成される各差動出力を通じて変換結果を提供します。変換結果は、サンプルが取得されてから6.5入力クロックサイクル後に得られます。図3に示すように、出力データは、出力クロックの両エッジでLSB(D0)を先頭にクロックアウトされます。図5は、詳細なシリアル出力タイミング図を示しています。

# シリアルLVDS出力付き、オクタル、12ビット、50MspS、1.8V ADC

MAX1437

図3. グローバルタイミング図

図4. 2変換タイミング詳細図

図5. シリアル化出力タイミング詳細図

# シリアルLVDS出力付き、オクタル、 12ビット、50MspS、1.8V ADC

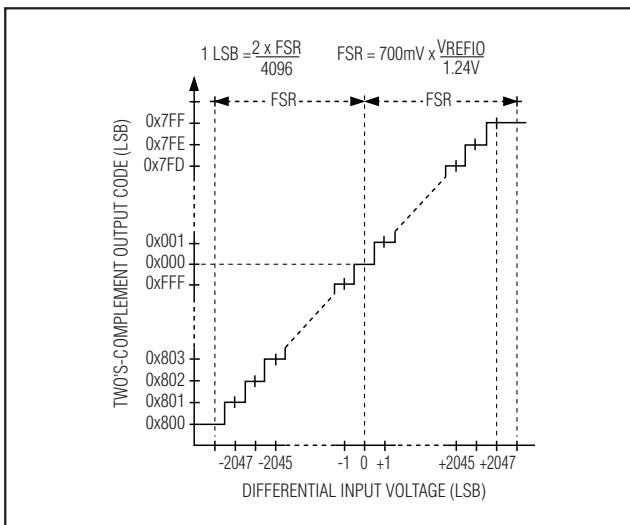

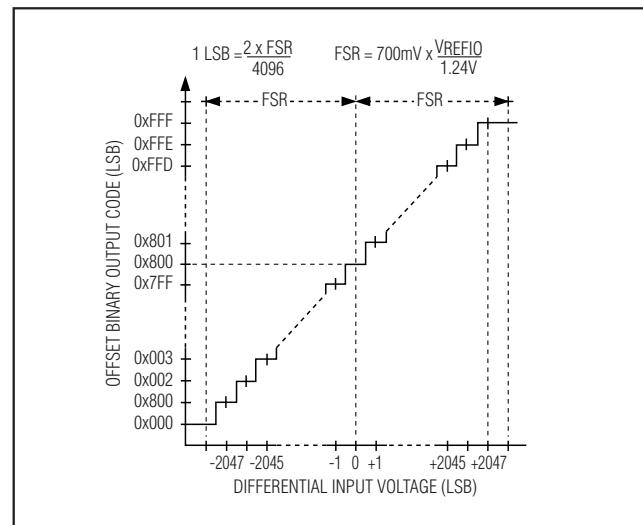

表2. 出力コード表( $V_{REFIO} = 1.24V$ )

| TWO'S-COMPLEMENT DIGITAL OUTPUT CODE<br>( $\bar{T}/B = 0$ ) |                                                          |                                                      | OFFSET BINARY DIGITAL OUTPUT CODE<br>( $\bar{T}/B = 1$ ) |                                                          |                                                      | $V_{IN\_P} - V_{IN\_N}$ (mV)<br>( $V_{REFIO} = 1.24V$ ) |

|-------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------|

| BINARY<br>$D_{11} \rightarrow D_0$                          | HEXADECIMAL<br>EQUIVALENT<br>OF $D_{11} \rightarrow D_0$ | DECIMAL<br>EQUIVALENT<br>OF $D_{11} \rightarrow D_0$ | BINARY<br>$D_{11} \rightarrow D_0$                       | HEXADECIMAL<br>EQUIVALENT<br>OF $D_{11} \rightarrow D_0$ | DECIMAL<br>EQUIVALENT<br>OF $D_{11} \rightarrow D_0$ |                                                         |

| 0111 1111 1111                                              | 0x7FF                                                    | +2047                                                | 1111 1111 1111                                           | 0FFF                                                     | +4095                                                | +699.66                                                 |

| 0111 1111 1110                                              | 0x7FE                                                    | +2046                                                | 1111 1111 1110                                           | 0FFE                                                     | +4094                                                | +699.32                                                 |

| 0000 0000 0001                                              | 0x001                                                    | +1                                                   | 1000 0000 0001                                           | 0x801                                                    | +2049                                                | +0.34                                                   |

| 0000 0000 0000                                              | 0x000                                                    | 0                                                    | 1000 0000 0000                                           | 0x800                                                    | +2048                                                | 0                                                       |

| 1111 1111 1111                                              | 0xFFFF                                                   | -1                                                   | 0111 1111 1111                                           | 0x7FF                                                    | +2047                                                | -0.34                                                   |

| 1000 0000 0001                                              | 0x801                                                    | -2047                                                | 0000 0000 0001                                           | 0x001                                                    | +1                                                   | -699.66                                                 |

| 1000 0000 0000                                              | 0x800                                                    | -2048                                                | 0000 0000 0000                                           | 0x000                                                    | 0                                                    | -700.00                                                 |

図6. 2の補数の伝達関数( $\bar{T}/B = 0$ )

図7. バイナリの伝達関数( $\bar{T}/B = 1$ )

## 出力データ形式( $\bar{T}/B$ )、伝達関数

MAX1437の出力データ形式は、ロジック入力 $\bar{T}/B$ に応じて、オフセットバイナリか、または2の補数のいずれかの形式になります。 $\bar{T}/B$ がローの場合は、出力データ形式は2の補数です。 $\bar{T}/B$ がハイの場合は、出力データ形式はオフセットバイナリです。次式、表2、図6および図7によって、デジタル出力とアナログ入力との関係が定義されます。2の補数( $\bar{T}/B = 0$ )の場合は：

$$V_{IN\_P} - V_{IN\_N} = FSR \times 2 \times \frac{CODE_{10}}{4096}$$

オフセットバイナリ( $\bar{T}/B = 1$ )の場合は、

$$V_{IN\_P} - V_{IN\_N} = FSR \times 2 \times \frac{CODE_{10} - 2048}{4096}$$

ここで、 $CODE_{10}$ は、表2に示すようにデジタル出力コードの10進数に相当します。

MAX1437のデジタル出力の容量性負荷は、可能な限り小さくしてください。

# シリアルLVDS出力付き、オクタル、12ビット、50MspS、1.8V ADC

MAX1437

## LVDSおよびSLVS信号(SLVS/LVDS)

MAX1437の出力(OUT\_P、OUT\_N、CLKOUTP、CLKOUTN、FRAMEP、およびFRAMEN)をLVDSレベルとする場合はSLVS/LVDSをローにして、SLVSレベルとする場合はSLVS/LVDSをハイにしてください。SLVSレベルの場合は、DTをハイに駆動して、2重終端をイネーブルしてください。LVDSおよびSLVSの出力電圧レベルについては、「Electrical Characteristics(電気的特性)」の表を参照してください。

## LVDSテストパターン(LVDSTEST)

すべてのLVDSまたはSLVS出力チャネルで出力テストパターンをイネーブルするには、LVDSTESTをハイにしてください。出力テストパターンは、0000 1011 1101です。通常動作にするには、LVDSTESTをローに駆動してください(テストパターンをディセーブルとする)。

## コモンモード出力(CMOUT)

CMOUTは、DC結合アナログ入力用のコモンモードリファレンスを備えています。入力がDC結合される場合は、MAX1437を駆動する回路の出力コモンモード電圧と $V_{CMOUT}$ の出力電圧を $\pm 50\text{mV}$ 以内に一致させてください。駆動回路の出力コモンモード電圧はCMOUTを取り出して使うことを推奨します。

## 2重終端(DT)

MAX1437は、差動出力ペア(OUT\_PとOUT\_N、CLKOUTPとCLKOUTN、FRAMEPとFRAMEN)の間にオプションの100 $\Omega$ 終端を内蔵しています。ラインの遠端部の終端のほかに出力部に直接配置される終端も、ライン上の望ましくない反射を排除するのに役立ちます。トレース長が長く(5インチ以上)、またはインピーダンスが不整合のアプリケーションでは、この機能は有効です。2重終端を選択するにはDTをハイにし、また内蔵終端抵抗器を切断する(单一終端)にはDTをローにしてください。2重終端を選択すると、 $0V_{DD}$ の消費電流が増大します(図8を参照)。

## パワーダウンモード(PD)

MAX1437は、変換が不要なときに低電力状態に遷移して、電力を効率的に使用するパワーダウンモードを備えています。

PDはすべてのチャネルと内部リファレンス回路のパワーダウンモードを制御します。パワーダウンをイネーブルするには、PDをハイにしてください。パワーダウンモードでは、DTがローの場合は、LVDS/SLVSのすべての出力の出力インピーダンスは約342 $\Omega$ です。差動LVDS/SLVS出力の出力インピーダンスは、DTがハイの場合は、100 $\Omega$ です。パワーダウン時の標準的な消費電流については、「Electrical Characteristics(電気的特性)」の表を参照してください。以下は、パワーダウンモードにおけるアナログ入力とデジタル出力の状態を示しています。

図8. 2重終端

- IN\_P、IN\_Nのアナログ入力は内部入力アンプから切断。

- REFIOは、GNDに対して1M $\Omega$ を超える抵抗を保持。

- OUT\_P、OUT\_N、CLKOUTP、CLKOUTN、FRAMEP、およびFRAMENは、DTがローの場合は出力ペア間に約342 $\Omega$ を保持。DTがハイの場合は、差動出力ペアは各ペア間に100 $\Omega$ を保持。

内部リファレンスで動作している場合は、パワーダウンからのウェイクアップ時間は100ms(typ)です( $C_{REFP}$ とGND間に、および $C_{REFN}$ とGND間に1 $\mu\text{F}$ を接続)。外部リファレンスを使用している場合は、ウェイクアップ時間は外部リファレンスドライバに依存します。

## アプリケーション情報

### 内部リファレンスによるフルスケール範囲の調整

MAX1437は、10%( $\pm 5\%$ )のフルスケール調整範囲をサポートしています。フルスケール範囲を縮小するには、25k $\Omega$ ～250k $\Omega$ の外付け抵抗器またはポテンショメータ( $R_{ADJ}$ )をREFADJとGNDの間に接続してください。フルスケール範囲を拡大するには、25k $\Omega$ ～250k $\Omega$ の抵抗器をREFADJとREFIOの間に接続してください。図9は、2つの可能な構成を示しています。

次式は、 $R_{ADJ}$ とアナログフルスケール範囲の変更との関係を示しています：

$$FSR = 0.7V \left(1 + \frac{1.25k\Omega}{R_{ADJ}}\right)$$

REFADJとREFIOの間に接続された $R_{ADJ}$ の場合は：

# シリアルLVDS出力付き、オクタル、 12ビット、50MspS、1.8V ADC

図9. ADCのフルスケール範囲を調整する回路案

$$FSR = 0.7V \left(1 - \frac{1.25k\Omega}{R_{ADJ}}\right)$$

REFADJとGNDの間に接続されたR<sub>ADJ</sub>の場合

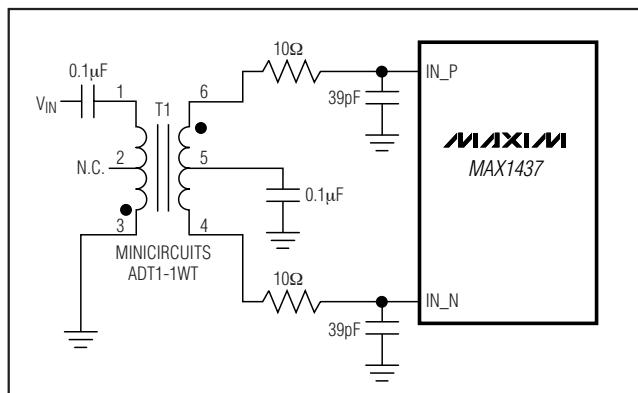

## トランス結合の使用

RFトランス(図10)は、シングルエンド入力源信号を完全差動信号に変換する卓越したソリューションを提供します。MAX1437の入力コモンモード電圧は、f<sub>CLK</sub> = 50MHzの場合、0.76V(typ)に内部でバイアスされます。ここでは1:1のトランスが示されていますが、ステップアップトランスを選択すると、駆動要件を緩和することができます。また、オペアンプなどの入力ドライバからの信号振幅が低減すると、全体的な歪みを改善することもできます。

## グランド、バイパス、および基板レイアウト

MAX1437には、高速基板レイアウトの設計方法が必要です。基板レイアウトのリファレンスについては、MAX1434/MAX1436/MAX1437/MAX1438のEVキットのデータシートを参照してください。インダクタンスを最小限に抑えるために、表面実装デバイスを使って、すべてのバイパスコンデンサをデバイスにできるだけ近接して、できればADCと同じ面に配置してください。0.1μFのセラミックコンデンサと並列に、0.1μFのセラミックコンデンサでAV<sub>DD</sub>をGNDにバイパスしてください。2.2μF以上のセラミックコンデンサと並列に0.1μFのコンデンサでOV<sub>DD</sub>をGNDにバイパスしてください。2.2μF以上のセラミックコンデンサと並列

図10. トランス結合クロック入力駆動

に0.1μFのセラミックコンデンサでCV<sub>DD</sub>をGNDにバイパスしてください。

広いグランドプレーンと電源プレーンの多層基板は、最高レベルの信号完全性を実現します。MAX1437のグランドピンと裏面エクスポートドパッドを同じグランドプレーンに接続してください。MAX1437は、低インダクタンスのグランド接続については裏面エクスポートドパッドの接続に依存しています。グランドプレーンは、ノイズの多いデジタルシステムのグランドプレーンから分離してください。

高速デジタル信号トレースは、敏感なアナログトレースから遠ざけて配線してください。すべての信号ラインは短くして、直角に曲げないでください。

差動アナログ入力回路のレイアウトを対称にして、すべての寄生要素を均等に平衡させてください。対称的な入力レイアウト例については、MAX1434/MAX1436/MAX1437/MAX1438のEVキットのデータシートを参照してください。

## パラメータ定義

### Integral Nonlinearity(積分非直線性)(INL)

積分非直線性は、実際の伝達関数の値の、直線からの偏差です。MAX1437の場合、この直線は、オフセット誤差および利得誤差がヌルにされた後の伝達関数の端点間に引かれます。INLの偏差は全ステップで測定され、ワーストケースの偏差は「Electrical Characteristics(電気的特性)」の表に示されています。

### Differential Nonlinearity(微分非直線性)(DNL)

微分非直線性は、1 LSBの実際のステップの幅と理想値との差です。1 LSB以下のDNL誤差規格は、ミッキングコードのない単調伝達関数を保証しています。MAX1437の場合は、DNLの偏差は全ステップで測定され、ワーストケースの偏差は「Electrical Characteristics(電気的特性)」の表に示されています。

# シリアルLVDS出力付き、オクタル、12ビット、50Msps、1.8V ADC

MAX1437

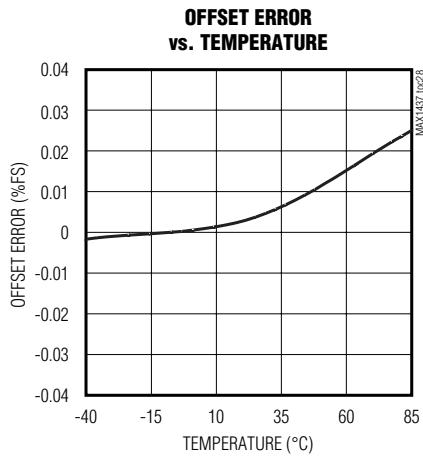

## Offset Error(オフセット誤差)

オフセット誤差は、実際の伝達関数がシングルポイントで理想的な伝達関数と一致している程度を示す性能指数です。MAX1437の場合は、アナログ入力全体にわたって-1/2の LSBがあると、理想的なミッドスケールデジタル出力遷移が行われます(図6および図7)。バイポーラオフセット誤差は、測定したミッドスケール遷移点と理想的なミッドスケール遷移点との偏差の大きさです。

## Gain Error(利得誤差)

利得誤差は、実際の伝達関数の傾きが理想的な伝達関数の傾きと一致している程度を示す性能指数です。MAX1437の場合は、測定されたフルスケール遷移点とゼロスケール遷移点との差から、理想的なフルスケール遷移点とゼロスケール遷移点との差を引いたものが利得誤差です。

バイポーラデバイス(MAX1437)の場合は、フルスケール遷移点は2の補数出力形式では0x7FE～0x7FFで(オフセットバイナリでは0xFFE～0xFFFF)、ゼロスケール遷移点は2の補数で0x800～0x801です(オフセットバイナリでは0x000～0x001)。

## Crosstalk(クロストーク)

クロストークは、各アナログ入力が他のアナログ入力から分離されている程度を示します。MAX1437の場合は、24.1MHz、-0.5dBFSのアナログ信号が1つのチャネルに印加され、別のチャネルに5.3MHz、-0.5dBFSのアナログ信号が印加されます。5.3MHzのアナログ信号が印加されたチャネルで、FFTが実行されます。このFFTから、クロストークは5.3MHzと24.1MHzの振幅の差として測定されます。

## Aperture Delay(アパー チャ 遅延)

アパー チャ 遅延( $t_{AD}$ )は、サンプリングクロックの立ち上がりエッジから、実際のサンプルの取得時点までの時間です。図11を参照してください。

## Aperture Jitter(アパー チャ ジッタ)

アパー チャ ジッタ( $t_{AJ}$ )は、アパー チャ 遅延におけるサンプル間のばらつきです。図11を参照してください。

## Signal-to-Noise Ratio(SNR)(信号 対 ノイズ比)

デジタルサンプルから完全に再生された波形の場合、理論的最大SNRは、RMS量子化誤差(残留誤差)に対するフルスケールアナログ入力(RMS値)の比です。理想的な理論上の最小のアナログ-デジタル変換ノイズは量子化誤差によってのみもたらされ、ADCの分解能(Nビット)から次式によって直接的求められます：

$$SNR_{dB}[\max] = 6.02dB \times N \times 1.76dB$$

実際には、量子化ノイズのほかに、熱雑音、リファレンスノイズ、クロックジッタなどのその他のノイズ源があります。

図11. アパー チャ ジッタ/遅延の仕様

MAX1437の場合は、SNRを算出するには、RMSノイズに対するRMS信号の比を取ります。RMSノイズには、基本波、最初から6つの高調波(HD2～HD7)、およびDCオフセットを除く、ナイキスト周波数までの全スペクトル成分が含まれます。

## Signal-to-Noise Plus Distortion(SINAD) (信号 対 ノイズ + 歪み)

SINADを算出するには、RMSノイズ+歪みに対するRMS信号の比を取ります。RMSノイズ+歪みには、基本波とDCオフセットを除く、ナイキスト周波数までの全スペクトル成分が含まれます。

## Effective Number of Bits(ENOB) (有効ビット数)

ENOBによって、特定の入力周波数とサンプリングレートにおけるADCのダイナミック性能を規定します。理想的なADCのエラーは、量子化ノイズのみで構成されます。フルスケール正弦波入力波形に対するENOBは、次式から算出されます：

$$ENOB = \left( \frac{SINAD - 1.76}{6.02} \right)$$

## Total Harmonic Distortion(THD)(全高調波歪み)

THDは、基本波そのものに対する、入力信号の先頭から6つの高調波RMS合計の比です。これは、次式のように表されます：

$$THD = 20 \times \log \left( \frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + V_5^2 + V_6^2 + V_7^2}}{V_1} \right)$$

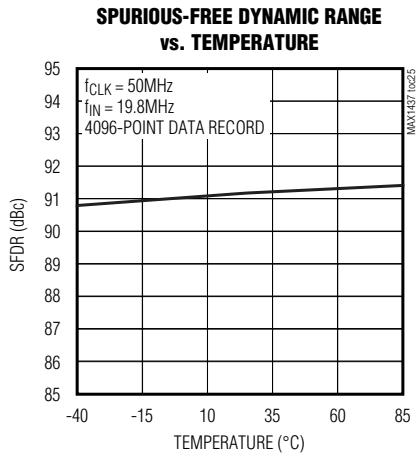

## Spurious-Free Dynamic Range(SFDR) (スピアスフリー、ダイナミックレンジ)

SFDRは、2番目に大きなスピアス成分(DCオフセットを除く)のRMS値に対する、基本波(最大信号成分)のRMS振幅の比をデシベルで表したものです。

# シリアルLVDS出力付き、オクタル、 12ビット、50Msps、1.8V ADC

SFDRは、キャリアに対するデシベル値で表されます(dBc)。

## Intermodulation Distortion(IMD)(相互変調歪み)

IMDは、2つの入力トーン $f_1$ および $f_2$ の総入力パワーに対する、ナイキスト周波数までのIM2からIM5の相互変調積の総パワーです。各入力トーンレベルは、-6.5dBFSです。相互変調積は、以下のとおりです。

- 2次相互変調積(IM2) :  $f_1 + f_2$ 、 $f_2 - f_1$

- 3次相互変調積(IM3) :  $2 \times f_1 - f_2$ 、 $2 \times f_2 - f_1$ 、 $2 \times f_1 + f_2$ 、 $2 \times f_2 + f_1$

- 4次相互変調積(IM4) :  $3 \times f_1 - f_2$ 、 $3 \times f_2 - f_1$ 、 $3 \times f_1 + f_2$ 、 $3 \times f_2 + f_1$

- 5次相互変調積(IM5) :  $3 \times f_1 - 2 \times f_2$ 、 $3 \times f_2 - 2 \times f_1$ 、 $3 \times f_1 + 2 \times f_2$ 、 $3 \times f_2 + 2 \times f_1$

## Third-Order Intermodulation(IM3)

### (3次相互変調)

IM3は、2つの入力トーン $f_1$ および $f_2$ の総入力パワーに対する、ナイキスト周波数までの3次相互変調積の総パワーです。各入力トーンレベルは、-6.5dBFSです。3次相互変調積は、 $2 \times f_1 - f_2$ 、 $2 \times f_2 - f_1$ 、 $2 \times f_1 + f_2$ 、 $2 \times f_2 + f_1$ です。

## Small-Signal Bandwidth(小信号帯域幅)

信号のスルーレートがADCの性能を制限しないように、-20.5BFSのアナログ入力小信号がADCに印加されます。次に、デジタル変換結果の振幅が-3dB低減する点まで入力周波数がスイープされます。

## Full-Power Bandwidth(フルパワー帯域幅)

-0.5dBFSのアナログ入力大信号がADCに印加され、デジタル変換結果の振幅が-3dB小さくなる点まで入力周波数がスイープされます。この点が、フルパワー入力帯域幅周波数として定義されます。

## Gain Matching(利得マッチング)

利得マッチングは、8つの全ADCチャネルの利得が互いに一致している程度を示す性能指数です。MAX1437の場合は、同じ5.3MHz、-0.5dBFSのアナログ信号をすべてのアナログ入力チャネルに印加して、利得マッチングが測定されます。これらのアナログ入力は50Mspsでサンプリングされ、振幅の最大偏差は「Electrical Characteristics(電気的特性)」の表に利得マッチングとしてdB単位で示されています。

## Phase Matching(位相マッチング)

位相マッチングは、8つの全ADCチャネルの位相が互いに一致している程度を示す性能指数です。MAX1437の場合は、同じ5.3MHz、-0.5dBFSのアナログ信号をすべてのアナログ入力チャネルに印加して、位相マッチングが測定されます。これらのアナログ入力は50Mspsでサンプリングされ、位相の最大偏差は「Electrical Characteristics(電気的特性)」表に位相マッチングとして度の単位で示されています。

# シリアルLVDS出力付き、オクタル、 12ビット、50Msps、1.8V ADC

## ピン配置

# シリアルLVDS出力付き、オクタル、 12ビット、50MspS、1.8V ADC

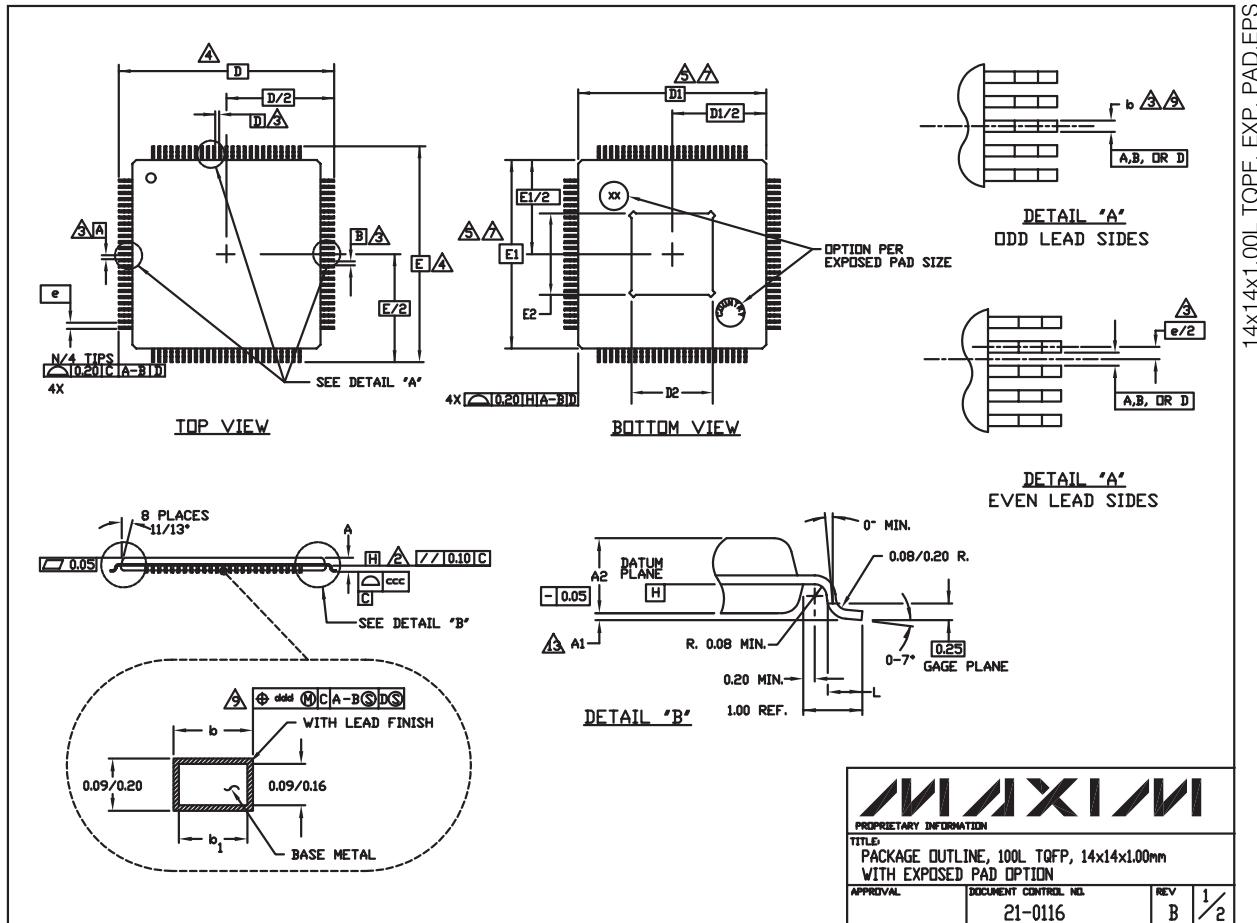

## パッケージ

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、[japan.maxim-ic.com/packages](http://japan.maxim-ic.com/packages)をご参照下さい。)

For the MAX1437 exposed paddle variation, the package code is C100E-2.

# シリアルLVDS出力付き、オクタル、 12ビット、50MspS、1.8V ADC

## パッケージ(続き)

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、[japan.maxim-ic.com/packages](http://japan.maxim-ic.com/packages)をご参照下さい。)

For the MAX1437 exposed paddle variation, the package code is C100E-2.

### NOTES:

- ALL DIMENSIONING AND TOLERANCING CONFORM TO ASME Y14.5M-1994.

- DATUM PLANE **[H]** LOCATED AT MOLD PARTING LINE AND COINCIDENT WITH LEAD, WHERE LEAD EXITS PLASTIC BODY AT BOTTOM OF PARTING LINE.

- DATUM **[A-B]** AND **[D]** TO BE DETERMINED AT CENTERLINE BETWEEN LEADS WHERE LEADS EXITS PLASTIC BODY AT DATUM PLANE **[H]**.

- TO BE DETERMINED AT SEATING PLANE **[C]**.

- DIMENSIONS D1 AND E1 DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE MOLD PROTRUSION IS 0.254mm ON D1 AND E1 DIMENSIONS.

- "N" IS THE TOTAL NUMBER OF TERMINALS.

- THESE DIMENSIONS TO BE DETERMINED AT DATUM PLANE **[H]**.

- THE TOP OF PACKAGE IS SMALLER THAN THE BOTTOM OF PACKAGE BY 0.15mm.

- DIMENSIONS **b** DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08mm TOTAL IN EXCESS OF THE **b** DIMENSION AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT.

- CONTROLLING DIMENSION: MILLIMETER

- MAXIMUM ALLOWABLE DIE THICKNESS TO BE ASSEMBLED IN THIS PACKAGE FAMILY IS 0.50mm.

- THIS OUTLINE IS NOT YET JEDEC REGISTERED.

- A1 IS DEFINED AS THE DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT OF THE PACKAGE BODY.

- EXPOSED DIE PAD SHALL BE COPLANAR WITH BOTTOM OF PACKAGE WITHIN 0.05mm.

- METAL AREA OF EXPOSED DIE PAD SHALL BE WITHIN 0.30mm OF THE NOMINAL DIE PAD SIZE.

- COUNTRY OF ORIGIN MUST BE MARKED ON THE PACKAGE.

| S<br>Y<br>M<br>B<br>D<br>L | ALL DIMENSIONS ARE IN MILLIMETERS |      |      |       |

|----------------------------|-----------------------------------|------|------|-------|

|                            | MIN.                              | NOM. | MAX. | NOTES |

| A                          | ~                                 | ~    | 1.20 |       |

| A <sub>1</sub>             | 0.05                              | ~    | 0.15 | 13    |

| A <sub>2</sub>             | 0.95                              | 1.00 | 1.05 |       |

| D                          | 16.00                             | BSC. |      | 4     |

| D <sub>1</sub>             | 14.00                             | BSC. |      | 7,8   |

| E                          | 16.00                             | BSC. |      | 4     |

| E <sub>1</sub>             | 14.00                             | BSC. |      | 7,8   |

| L                          | 0.45                              | 0.60 | 0.75 |       |

| N                          | 100                               |      |      |       |

| e                          | 0.50                              | BSC. |      |       |

| b                          | 0.17                              | 0.22 | 0.27 | 9     |

| b <sub>1</sub>             | 0.17                              | 0.20 | 0.23 |       |

| ccc                        | ~                                 | ~    | 0.08 |       |

| ddd                        | ~                                 | ~    | 0.08 |       |

| EXPOSED PAD VARIATIONS |      |      |      |      |      |      |

|------------------------|------|------|------|------|------|------|

| PKG. CODE              | D2   |      |      | E2   |      |      |

|                        | MIN. | NOM. | MAX. | MIN. | NOM. | MAX. |

| C100E-2                | 7.7  | 8.0  | 8.3  | 7.7  | 8.0  | 8.3  |

| C100E-3                | 6.2  | 6.5  | 6.8  | 6.2  | 6.5  | 6.8  |

| C100E-6                | 4.7  | 5.0  | 5.3  | 4.7  | 5.0  | 5.3  |

**MAXIM**

PROPRIETARY INFORMATION

TITLE: PACKAGE OUTLINE, 100L TQFP, 14x14x1.00mm

WITH EXPOSED PAD OPTION

|          |                      |           |

|----------|----------------------|-----------|

| APPROVAL | DOCUMENT CONTROL NO. | REV       |

|          | 21-0116              | B / 2 / 2 |

マキシム・ジャパン株式会社

〒169-0051 東京都新宿区西早稲田3-30-16(ホリゾン1ビル)

TEL. (03)3232-6141 FAX. (03)3232-6149

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。マキシムは隨時予告なく回路及び仕様を変更する権利を留保します。

**Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600**

© 2005 Maxim Integrated Products, Inc. All rights reserved. **MAXIM** is a registered trademark of Maxim Integrated Products, Inc.

MAX1437