# IFアプリケーション用の15ビット、80Msps、 -78.4dBFSのノイズフロアを持つADC

**MAX1428**

## 概要

MAX1428は5V、高速、高性能のアナログ-デジタルコンバータ(ADC)であり、完全差動広帯域トラックアンドホールド(T/H)及び15ビットの変換コアを備えています。MAX1428はADCに対して非常に厳しいダイナミック性能要件を満たすことを要求する多チャネル、多モード受信器として最適化されています。MAX1428は-78.4dBFSのノイズフロアを持ち、優れた感度を備えた受信器の設計を可能とします。

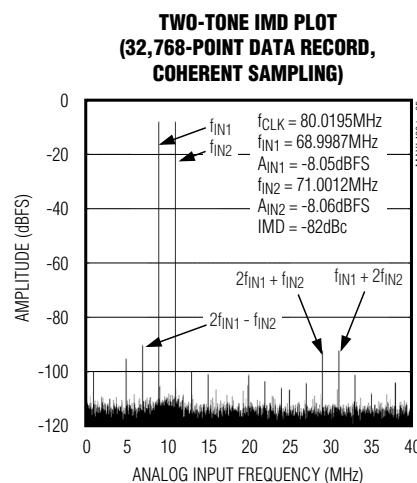

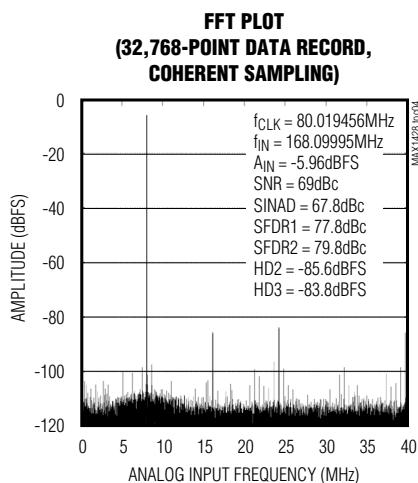

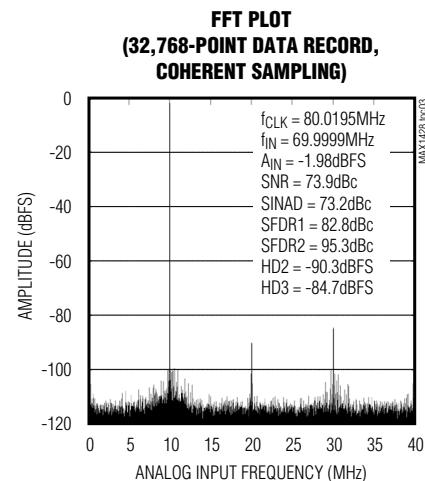

MAX1428は69MHzと71MHzの入力トーンに対して、-82dBcのスプリアスフリーダイナミックレンジ(SFDR)を達成しています。73.9dBというその優れた信号対ノイズ比(SNR)、及び $f_{IN} = 70\text{MHz}$ 及び80Mspsのサンプリング速度における83dBc/91dBcというシングルトーンSFDR性能(SFDR1/SFDR2)を持つことが、この製品を高性能のデジタルレシーバ用として理想的にしています。

MAX1428はアナログ5V及びデジタル3V電源で動作し、2.56V<sub>P-P</sub>のフルスケール入力範囲を備え、最高80Mspsのサンプリング速度を可能とします。入力T/Hは260MHzの-1dBフルパワー帯域幅で動作します。

MAX1428は2の補数形式のCMOS対応パラレル出力を備えています。広範なロジックデバイスとのインターフェースを可能とするために、このADCは2.3V~3.5Vの独立した出力ドライバ電源を備えています。MAX1428は8mm x 8mmの56ピン、低熱抵抗を得るためにエクスポートドパッドを持つ薄型QFNパッケージで製造され、拡張温度範囲(-40°C~+85°C)での動作が保証されています。

IF用部品であるMAX1418、MAX1428、及びMAX1430(「ピンコンパチブルの高速/低速バージョン選択表」を参照)が、 $f_{CLK}/3$ より高い入力周波数に対して高いダイナミック性能を必要とするアプリケーション用に推奨されること注記しておきます。ベースバンド用の相当品であるMAX1427と異なり、MAX1428は $f_{CLK}/3$ を超える入力周波数に対して最適化されています。

## アプリケーション

- 携帯電話基地局用トランシーバシステム(BTS)

- ワイヤレスローカルループ(WLL)

- シングル及びマルチキャリア受信器

- マルチ標準受信器

- E911口케ーションレシーバ

- パワーアンプのリニアリティ補正

- アンテナアレイ処理

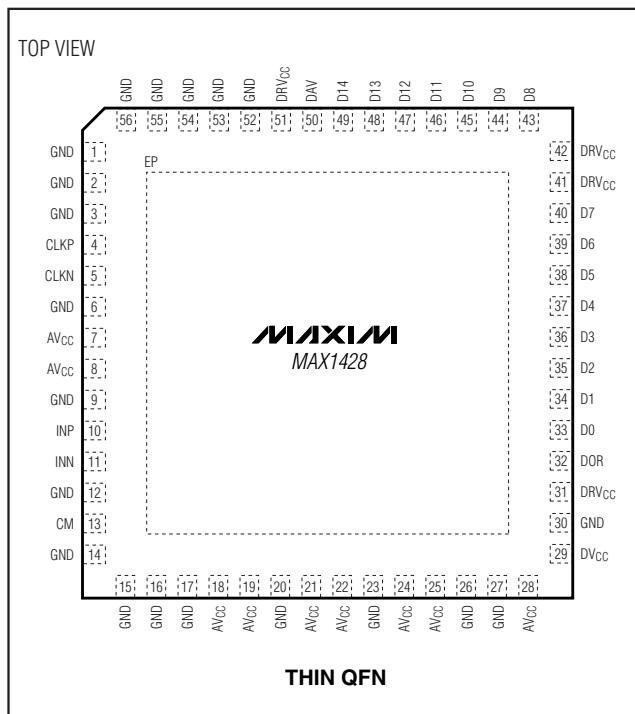

ピン配置はデータシートの最後に記載されています。

## 特長

- ◆ 最低サンプリング速度：80Msps

- ◆ ノイズフロア：-78.4dBFS

- ◆ 優れたダイナミック性能

- SNR : 73.9dB

- ( $f_{IN} = 70\text{MHz}$ 及び $A_{IN} = -2\text{dBFS}$ において)

- シングルトーンSFDR1/SFDR2 : 83dBc/91dBc

- ( $f_{IN} = 70\text{MHz}$ 及び $A_{IN} = -2\text{dBFS}$ において)

- マルチトーンSFDR : -82dB

- ( $f_{IN1} = 69\text{MHz}$ 及び $f_{IN2} = 71\text{MHz}$ において)

- ◆ サンプリングジッタ：0.25ps未満

- ◆ 完全差動アナログ入力範囲：2.56V<sub>P-P</sub>

- ◆ CMOS対応の2の補数データ出力

- ◆ データ有効クロックとオーバレンジ出力が独立

- ◆ フレキシブルな入力のクロックバッファ

- ◆ MAX1428用のEVキットが利用可能

(MAX1427EVKITを注文してください)

## 型番

| PART       | TEMP RANGE     | PIN-PACKAGE     |

|------------|----------------|-----------------|

| MAX1428ETN | -40°C to +85°C | 56 Thin QFN-EP* |

\* EP = エクスポートドパッド。

## ピンコンパチブルの高速/低速 バージョン選択表

| PART    | SPEED GRADE (Msps) | TARGET APPLICATION |

|---------|--------------------|--------------------|

| MAX1418 | 65                 | IF                 |

| MAX1419 | 65                 | Baseband           |

| MAX1427 | 80                 | Baseband           |

| MAX1428 | 80                 | IF                 |

| MAX1429 | 100                | Baseband           |

| MAX1430 | 100                | IF                 |

# IFアプリケーション用の15ビット、80Msps、-78.4dBFSのノイズフロアを持つADC

## ABSOLUTE MAXIMUM RATINGS

AV<sub>CC</sub>, DV<sub>CC</sub>, DRV<sub>CC</sub> to GND.....-0.3V to +6V

INP, INN, CLK<sub>P</sub>, CLK<sub>N</sub>, CM to GND.....-0.3V to (AV<sub>CC</sub> + 0.3V)

D0-D14, DAV, DOR to GND.....-0.3V to (DRV<sub>CC</sub> + 0.3V)

Continuous Power Dissipation (T<sub>A</sub> = +70°C)

56-Pin Thin QFN (derate 47.6mW/°C above +70°C)...3809.5mW

Operating Temperature Range .....-40°C to +85°C

Thermal Resistance θ<sub>JA</sub> .....21°C/W

Junction Temperature .....+150°C

Storage Temperature Range .....-60°C to +150°C

Lead Temperature (soldering, 10s) .....+300°C

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

(AV<sub>CC</sub> = 5V, DV<sub>CC</sub> = DRV<sub>CC</sub> = 2.5V, GND = 0, INP and INN driven differentially with -2dBFS, CLK<sub>P</sub> and CLK<sub>N</sub> driven differentially with a 2V<sub>P-P</sub> sinusoidal input signal, C<sub>L</sub> = 5pF at digital outputs, f<sub>CLK</sub> = 80MHz, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.  $\geq +25^{\circ}\text{C}$  guaranteed by production test,  $< +25^{\circ}\text{C}$  guaranteed by design and characterization.)

| PARAMETER                                             | SYMBOL                   | CONDITIONS                                                                               | MIN           | TYP  | MAX | UNITS            |

|-------------------------------------------------------|--------------------------|------------------------------------------------------------------------------------------|---------------|------|-----|------------------|

| <b>DC ACCURACY</b>                                    |                          |                                                                                          |               |      |     |                  |

| Resolution                                            |                          |                                                                                          | 15            |      |     | Bits             |

| Integral Nonlinearity                                 | INL                      | f <sub>IN</sub> = 15MHz                                                                  |               | ±1.5 |     | LSB              |

| Differential Nonlinearity                             | DNL                      | f <sub>IN</sub> = 70MHz, no missing codes guaranteed                                     |               | ±0.4 |     | LSB              |

| Offset Error                                          |                          |                                                                                          | -12           |      | +12 | mV               |

| Gain Error                                            |                          |                                                                                          | -4            |      | +4  | %FS              |

| <b>ANALOG INPUT (INP, INN)</b>                        |                          |                                                                                          |               |      |     |                  |

| Differential Input Voltage Range                      | V <sub>DIFF</sub>        | Fully differential inputs drive, V <sub>DIFF</sub> = V <sub>INP</sub> - V <sub>INN</sub> | 2.56          |      |     | V <sub>P-P</sub> |

| Common-Mode Input Voltage                             | V <sub>CM</sub>          | Self-biased                                                                              | 4.163         |      |     | V                |

| Differential Input Resistance                         | R <sub>IN</sub>          |                                                                                          | 1<br>±15%     |      |     | kΩ               |

| Differential Input Capacitance                        | C <sub>IN</sub>          |                                                                                          | 1             |      |     | pF               |

| Full-Power Analog Bandwidth                           | F <sub>PBW</sub><br>-1dB | -1dB rolloff for a full-scale input                                                      | 260           |      |     | MHz              |

| <b>CONVERSION RATE</b>                                |                          |                                                                                          |               |      |     |                  |

| Maximum Clock Frequency                               | f <sub>CLK</sub>         |                                                                                          | 80            |      |     | MHz              |

| Minimum Clock Frequency                               | f <sub>CLK</sub>         |                                                                                          | 20            |      |     | MHz              |

| Aperture Jitter                                       | t <sub>AJ</sub>          |                                                                                          | 0.21          |      |     | psRMS            |

| <b>CLOCK INPUT (CLK<sub>P</sub>, CLK<sub>N</sub>)</b> |                          |                                                                                          |               |      |     |                  |

| Full-Scale Differential Input Voltage                 | V <sub>DIFFCLK</sub>     | Fully differential input drive, V <sub>CLKP</sub> - V <sub>CLKN</sub>                    | 0.5 to<br>3.0 |      |     | V                |

| Common-Mode Input Voltage                             | V <sub>CM</sub>          | Self-biased                                                                              | 2.4           |      |     | V                |

| Differential Input Resistance                         | R <sub>INCLK</sub>       |                                                                                          | 2<br>±15%     |      |     | kΩ               |

| Differential Input Capacitance                        | C <sub>INCLK</sub>       |                                                                                          | 1             |      |     | pF               |

| <b>DYNAMIC CHARACTERISTICS</b>                        |                          |                                                                                          |               |      |     |                  |

| Thermal + Quantization Noise Floor                    | NF                       | Analog input <-35dBFS                                                                    | -78.4         |      |     | dBFS             |

# IFアプリケーション用の15ビット、80MspS、-78.4dBFSのノイズフロアを持つADC

MAX1428

## ELECTRICAL CHARACTERISTICS (continued)

(AV<sub>CC</sub> = 5V, DV<sub>CC</sub> = DRV<sub>CC</sub> = 2.5V, GND = 0, INP and INN driven differentially with -2dBFS, CLK<sub>P</sub> and CLK<sub>N</sub> driven differentially with a 2Vp-p sinusoidal input signal, C<sub>L</sub> = 5pF at digital outputs, f<sub>CLK</sub> = 80MHz, TA = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.  $\geq +25^{\circ}\text{C}$  guaranteed by production test,  $< +25^{\circ}\text{C}$  guaranteed by design and characterization.)

| PARAMETER                                             | SYMBOL             | CONDITIONS                                                                                                                              | MIN  | TYP  | MAX | UNITS |

|-------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|-------|

| Signal-to-Noise Ratio (Note 1)                        | SNR                | f <sub>IN</sub> = 5MHz at -2dBFS                                                                                                        | 75.3 |      |     | dB    |

|                                                       |                    | f <sub>IN</sub> = 15MHz at -2dBFS                                                                                                       | 75.3 |      |     |       |

|                                                       |                    | f <sub>IN</sub> = 35MHz at -2dBFS                                                                                                       | 74.8 |      |     |       |

|                                                       |                    | f <sub>IN</sub> = 70MHz at -2dBFS                                                                                                       | 72.0 | 73.9 |     |       |

|                                                       |                    | f <sub>IN</sub> = 170MHz at -6dBFS                                                                                                      | 69.0 |      |     |       |

| Signal-to-Noise and Distortion (Note 1)               | SINAD              | f <sub>IN</sub> = 5MHz at -2dBFS                                                                                                        | 74.9 |      |     | dB    |

|                                                       |                    | f <sub>IN</sub> = 15MHz at -2dBFS                                                                                                       | 74.9 |      |     |       |

|                                                       |                    | f <sub>IN</sub> = 35MHz at -2dBFS                                                                                                       | 74.4 |      |     |       |

|                                                       |                    | f <sub>IN</sub> = 70MHz at -2dBFS                                                                                                       | 71.0 | 73.4 |     |       |

|                                                       |                    | f <sub>IN</sub> = 170MHz at -6dBFS                                                                                                      | 68.2 |      |     |       |

| Spurious-Free Dynamic Range (HD2 and HD3) (Note 1)    | SFDR1              | f <sub>IN</sub> = 5MHz at -2dBFS                                                                                                        | 88.0 |      |     | dBc   |

|                                                       |                    | f <sub>IN</sub> = 15MHz at -2dBFS                                                                                                       | 88.0 |      |     |       |

|                                                       |                    | f <sub>IN</sub> = 35MHz at -2dBFS                                                                                                       | 87.0 |      |     |       |

|                                                       |                    | f <sub>IN</sub> = 70MHz at -2dBFS                                                                                                       | 78.0 | 83.0 |     |       |

|                                                       |                    | f <sub>IN</sub> = 170MHz at -6dBFS                                                                                                      | 78.0 |      |     |       |

| Spurious-Free Dynamic Range (HD4 and Higher) (Note 1) | SFDR2              | f <sub>IN</sub> = 5MHz at -2dBFS                                                                                                        | 95.0 |      |     | dBc   |

|                                                       |                    | f <sub>IN</sub> = 15MHz at -2dBFS                                                                                                       | 95.0 |      |     |       |

|                                                       |                    | f <sub>IN</sub> = 35MHz at -2dBFS                                                                                                       | 95.0 |      |     |       |

|                                                       |                    | f <sub>IN</sub> = 70MHz at -2dBFS                                                                                                       | 83.9 | 91.0 |     |       |

|                                                       |                    | f <sub>IN</sub> = 170MHz at -6dBFS                                                                                                      | 80.0 |      |     |       |

| Two-Tone Intermodulation Distortion                   | TTIMD              | f <sub>IN1</sub> = 69MHz at -8dBFS,<br>f <sub>IN2</sub> = 71MHz at -8dBFS                                                               |      | -82  |     | dBc   |

| Two-Tone Spurious-Free Dynamic Range                  | SFDR <sub>TT</sub> | f <sub>IN1</sub> = 69MHz at -12dBFS < f <sub>IN1</sub> < -100dBFS,<br>f <sub>IN2</sub> = 71MHz at -12dBFS < f <sub>IN2</sub> < -100dBFS |      | -95  |     | dBFS  |

## DIGITAL OUTPUTS (D0–D14, DAV, DOR)

|                             |                 |  |                         |   |

|-----------------------------|-----------------|--|-------------------------|---|

| Digital Output-Voltage Low  | V <sub>OL</sub> |  | 0.5                     | V |

| Digital Output-Voltage High | V <sub>OH</sub> |  | DRV <sub>CC</sub> - 0.5 | V |

## TIMING CHARACTERISTICS (DV<sub>CC</sub> = DRV<sub>CC</sub> = 2.5V)

|                                               |                      |          |             |              |

|-----------------------------------------------|----------------------|----------|-------------|--------------|

| CLK <sub>P</sub> /CLK <sub>N</sub> Duty Cycle | Duty Cycle           |          | 50<br>±5    | %            |

| Effective Aperture Delay                      | t <sub>AD</sub>      |          | 230         | ps           |

| Output Data Delay                             | t <sub>DAT</sub>     | (Note 3) | 3.0 4.5 7.5 | ns           |

| Data Valid Delay                              | t <sub>DAV</sub>     | (Note 3) | 5.3 6.5 8.7 | ns           |

| Pipeline Latency                              | t <sub>LATENCY</sub> |          | 3           | Clock Cycles |

# IFアプリケーション用の15ビット、80Msps、-78.4dBFSのノイズフロアを持つADC

## ELECTRICAL CHARACTERISTICS (continued)

(AV<sub>CC</sub> = 5V, DV<sub>CC</sub> = DRV<sub>CC</sub> = 2.5V, GND = 0, INP and INN driven differentially with -2dBFS, CLK<sub>P</sub> and CLK<sub>N</sub> driven differentially with a 2V<sub>p-p</sub> sinusoidal input signal, C<sub>L</sub> = 5pF at digital outputs, f<sub>CLOCK</sub> = 80MHz, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.  $\geq +25^\circ\text{C}$  guaranteed by production test,  $< +25^\circ\text{C}$  guaranteed by design and characterization.)

| PARAMETER                                                                 | SYMBOL                                 | CONDITIONS                                       | MIN                     | TYP                     | MAX                     | UNITS        |

|---------------------------------------------------------------------------|----------------------------------------|--------------------------------------------------|-------------------------|-------------------------|-------------------------|--------------|

| CLK <sub>P</sub> Rising Edge to DATA Not Valid                            | t <sub>TDNV</sub>                      | (Note 3)                                         | 2.6                     | 3.8                     | 5.7                     | ns           |

| CLK <sub>P</sub> Rising Edge to DATA Valid (Guaranteed)                   | t <sub>DGV</sub>                       | (Note 3)                                         | 3.4                     | 5.2                     | 8.6                     | ns           |

| DATA Setup Time (Before DAV Rising Edge)                                  | t <sub>SETUP</sub>                     | (Note 3)                                         | t <sub>CLKP</sub> - 0.5 | t <sub>CLKP</sub> + 1.3 | t <sub>CLKP</sub> + 2.4 | ns           |

| DATA Hold Time (After DAV Rising Edge)                                    | t <sub>HOLD</sub>                      | (Note 3)                                         | t <sub>CLKN</sub> - 3.6 | t <sub>CLKN</sub> - 2.8 | t <sub>CLKN</sub> - 2.0 | ns           |

| <b>TIMING CHARACTERISTICS (DV<sub>CC</sub> = DRV<sub>CC</sub> = 3.3V)</b> |                                        |                                                  |                         |                         |                         |              |

| CLK <sub>P</sub> /CLK <sub>N</sub> Duty Cycle                             | Duty                                   |                                                  | 50 $\pm$ 5              |                         |                         | %            |

| Effective Aperture Delay                                                  | t <sub>AD</sub>                        |                                                  | 230                     |                         |                         | ps           |

| Output Data Delay                                                         | t <sub>DAT</sub>                       | (Note 3)                                         | 2.8                     | 4.1                     | 6.5                     | ns           |

| Data Valid Delay                                                          | t <sub>DAV</sub>                       | (Note 3)                                         | 5.3                     | 6.3                     | 8.6                     | ns           |

| Pipeline Latency                                                          | t <sub>LATENCY</sub>                   |                                                  | 3                       |                         |                         | Clock Cycles |

| CLK <sub>P</sub> Rising Edge to DATA Not Valid                            | t <sub>TDNV</sub>                      | (Note 3)                                         | 2.5                     | 3.4                     | 5.2                     | ns           |

| CLK <sub>P</sub> Rising Edge to DATA Valid (Guaranteed)                   | t <sub>DGV</sub>                       | (Note 3)                                         | 3.2                     | 4.4                     | 7.4                     | ns           |

| DATA Setup Time (Before DAV Rising Edge)                                  | t <sub>SETUP</sub>                     | (Note 3)                                         | t <sub>CLKP</sub> + 0.2 | t <sub>CLKP</sub> + 1.7 | t <sub>CLKP</sub> + 2.8 | ns           |

| DATA Hold Time (After DAV Rising Edge)                                    | t <sub>HOLD</sub>                      | (Note 3)                                         | t <sub>CLKN</sub> - 3.5 | t <sub>CLKN</sub> - 2.7 | t <sub>CLKN</sub> - 2.0 | ns           |

| <b>POWER REQUIREMENTS</b>                                                 |                                        |                                                  |                         |                         |                         |              |

| Analog-Supply Voltage Range                                               | AV <sub>CC</sub>                       |                                                  | 5 $\pm$ 3%              |                         |                         | V            |

| Digital-Supply Voltage Range                                              | DV <sub>CC</sub>                       | (Note 2)                                         | 2.3 to 3.5              |                         |                         | V            |

| Output-Supply Voltage Range                                               | DRV <sub>CC</sub>                      | (Note 2)                                         | 2.3 to 3.5              |                         |                         | V            |

| Analog Supply Current                                                     | I <sub>AVCC</sub>                      |                                                  | 400                     | 450                     | mA                      |              |

| Digital + Output Supply Current                                           | I <sub>DVCC</sub> + I <sub>DRVCC</sub> | f <sub>CLOCK</sub> = 80MHz, C <sub>L</sub> = 5pF | 38                      | 44                      | mA                      |              |

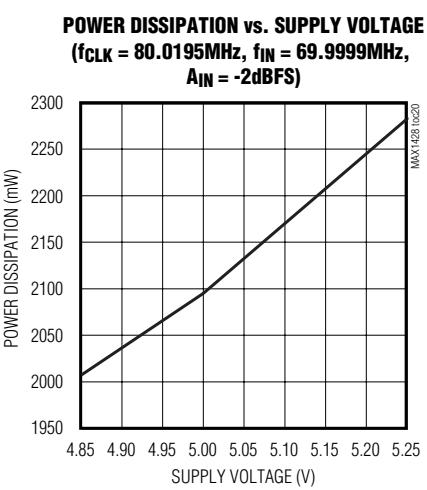

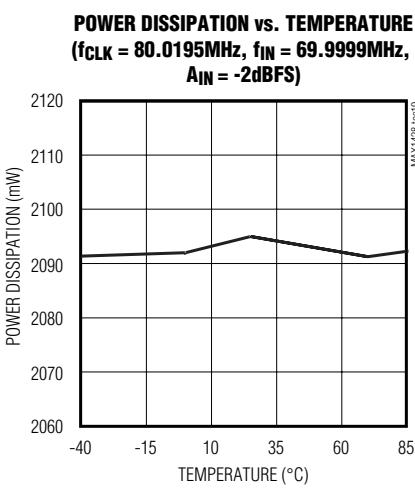

| Total Power Dissipation                                                   | PDISS                                  |                                                  | 2095                    |                         |                         | mW           |

**Note 1:** Dynamic performance is based on a 32,768-point data record with a sampling frequency of f<sub>SAMPLE</sub> = 80.019456MHz, an input frequency of f<sub>IN</sub> = f<sub>SAMPLE</sub> x (28667/32768) = 70.004814MHz, and a frequency bin size of 2442Hz. Close-in (f<sub>IN</sub>  $\pm$ 29.3kHz) and low-frequency (DC to 58.6kHz) bins are excluded from the spectrum analysis.

**Note 2:** Apply the same voltage levels to DV<sub>CC</sub> and DRV<sub>CC</sub>.

**Note 3:** Guaranteed by design and characterization.

# IFアプリケーション用の15ビット、80MspS、-78.4dBFSのノイズフロアを持つADC

MAX1428

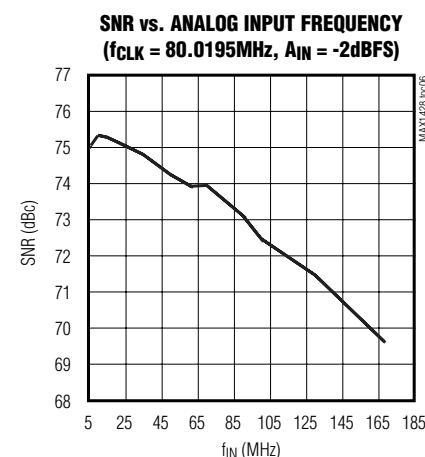

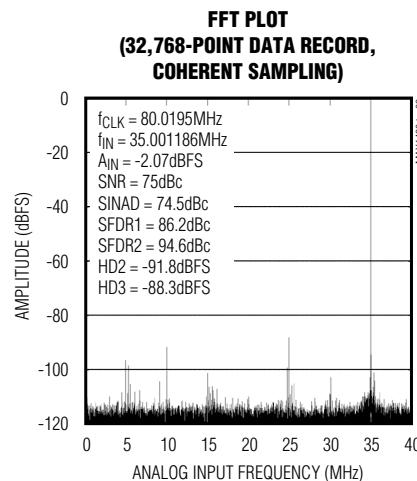

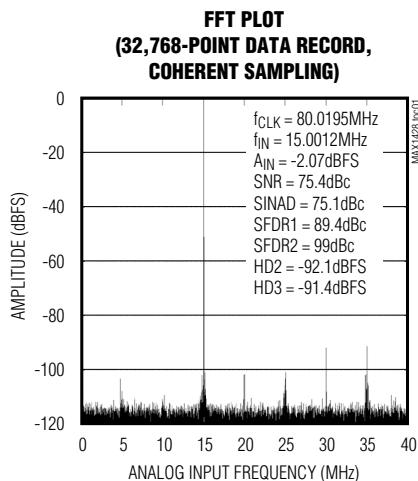

## 標準動作特性

(AV<sub>CC</sub> = 5V, DV<sub>CC</sub> = DRV<sub>CC</sub> = 2.5V, INP and INN driven differentially with a -2dBFS amplitude, CLKP and CLKN driven differentially with a 2Vp-p sinusoidal input signal, C<sub>L</sub> = 5pF at digital outputs, f<sub>CLK</sub> = 80MHz, T<sub>A</sub> = 25°C. All AC data is based on a 32k-point FFT record and under coherent sampling conditions.)

# IFアプリケーション用の15ビット、80Msps、-78.4dBFSのノイズフロアを持つADC

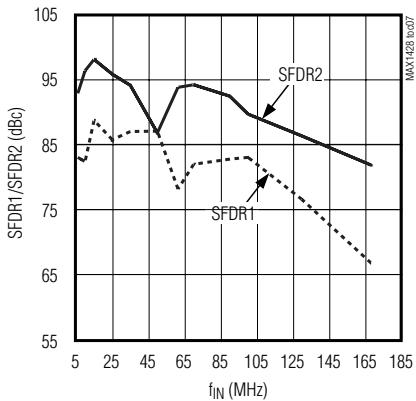

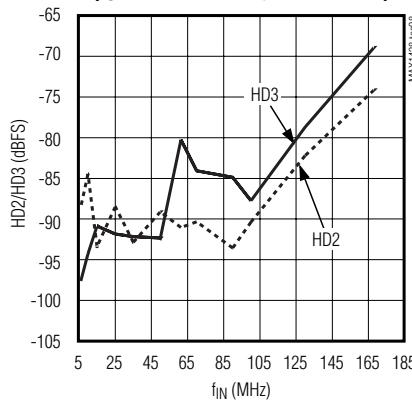

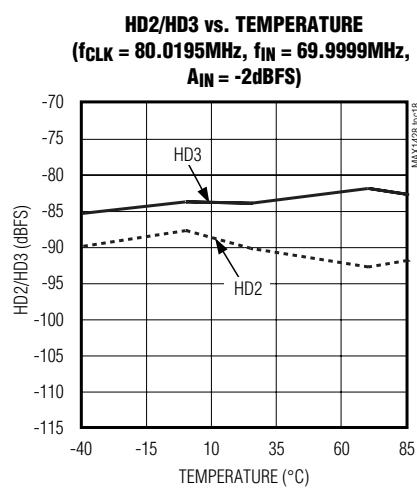

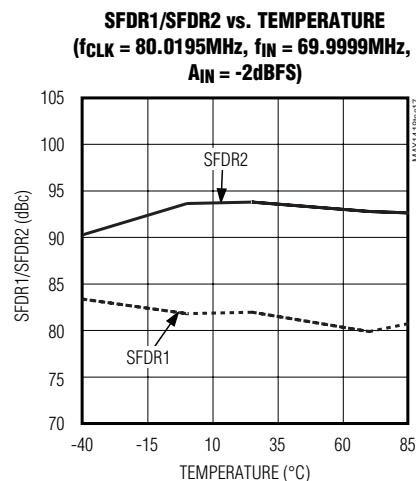

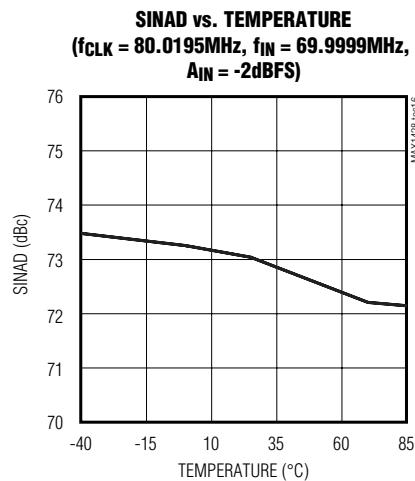

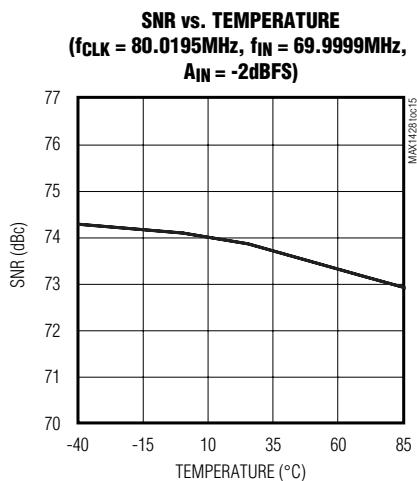

## 標準動作特性(続き)

(AV<sub>CC</sub> = 5V, DV<sub>CC</sub> = DRV<sub>CC</sub> = 2.5V, INP and INN driven differentially with a -2dBFS amplitude, CLKP and CLKN driven differentially with a 2Vp-p sinusoidal input signal, C<sub>L</sub> = 5pF at digital outputs, f<sub>CLK</sub> = 80MHz, T<sub>A</sub> = 25°C. All AC is data based on a 32k-point FFT record and under coherent sampling conditions.)

**SFDR1/SFDR2 vs. ANALOG INPUT FREQUENCY**

(f<sub>CLK</sub> = 80.0195MHz, A<sub>IN</sub> = -2dBFS)

**HD2/HD3 vs. ANALOG INPUT FREQUENCY**

(f<sub>CLK</sub> = 80.0195MHz, A<sub>IN</sub> = -2dBFS)

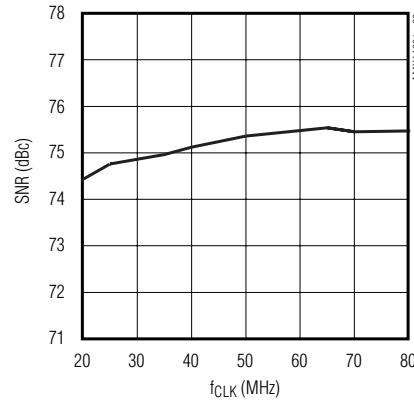

**SNR vs. SAMPLING FREQUENCY**

(f<sub>IN</sub> = 70MHz, A<sub>IN</sub> = -2dBFS)

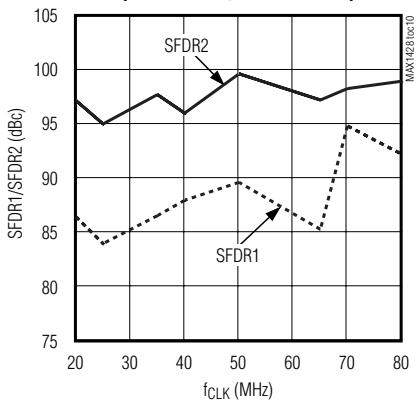

**SFDR1/SFDR2 vs. SAMPLING FREQUENCY**

(f<sub>IN</sub> = 70MHz, A<sub>IN</sub> = -2dBFS)

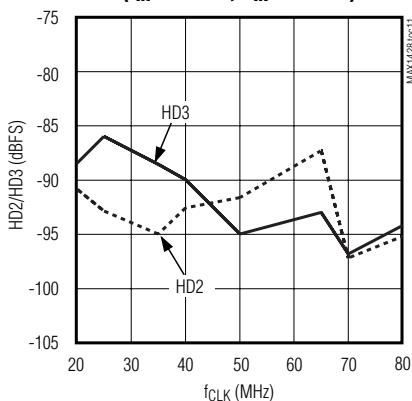

**HD2/HD3 vs. SAMPLING FREQUENCY**

(f<sub>IN</sub> = 70MHz, A<sub>IN</sub> = -2dBFS)

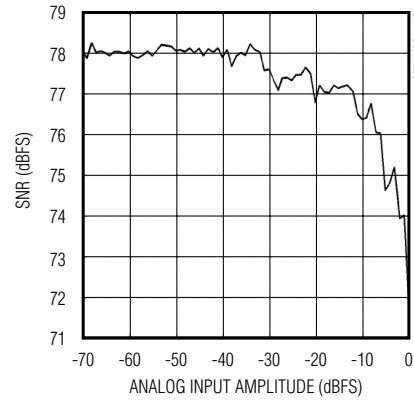

**SNR vs. ANALOG INPUT AMPLITUDE**

(f<sub>CLK</sub> = 80.0195MHz, f<sub>IN</sub> = 69.9999MHz)

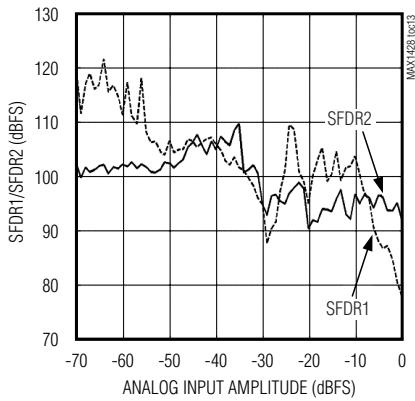

**SFDR1/SFDR2 vs. ANALOG INPUT AMPLITUDE**

(f<sub>CLK</sub> = 80.0195MHz, f<sub>IN</sub> = 69.9999MHz)

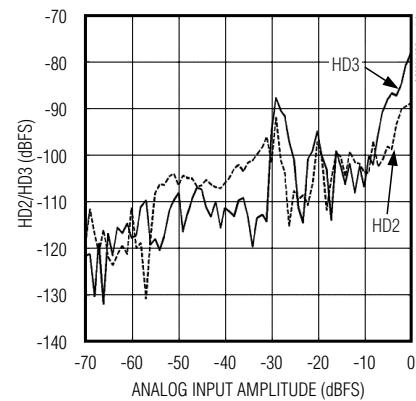

**HD2/HD3 vs. ANALOG INPUT AMPLITUDE**

(f<sub>CLK</sub> = 80.0195MHz, f<sub>IN</sub> = 69.9999MHz)

# IFアプリケーション用の15ビット、80Mps、-78.4dBFSのノイズフロアを持つADC

MAX1428

## 標準動作特性(続き)

(AV<sub>CC</sub> = 5V, DV<sub>CC</sub> = DRV<sub>CC</sub> = 2.5V, INP and INN driven differentially with a -2dBFS amplitude, CLKP and CLKN driven differentially with a 2Vp-p sinusoidal input signal, C<sub>L</sub> = 5pF at digital outputs, f<sub>CLK</sub> = 80MHz, T<sub>A</sub> = 25°C. All AC is data based on a 32k-point FFT record and under coherent sampling conditions.)

# IFアプリケーション用の15ビット、80MspS、-78.4dBFSのノイズフロアを持つADC

## 端子説明

| 端子                                                      | 名称    | 機能                                                                                                                                      |

|---------------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 3, 6, 9, 12, 14–17, 20, 23, 26, 27, 30, 52–56, EP | GND   | コンバータのグランド。アナログ、デジタル、及び出力ドライバのグランドは内部で同じ電位に接続されています。コンバータのEPをGNDに接続してください。                                                              |

| 4                                                       | CLKP  | 差動クロックの正入力端子。                                                                                                                           |

| 5                                                       | CLKN  | 差動クロックの負入力端子。                                                                                                                           |

| 7, 8, 18, 19, 21, 22, 24, 25, 28                        | AVCC  | アナログ電源電圧。0.1 $\mu$ Fと0.22 $\mu$ Fのコンデンサを使ってグランドにローカルバイパスしてください。                                                                         |

| 10                                                      | INP   | 差動アナログ入力の正端子。                                                                                                                           |

| 11                                                      | INN   | 差動アナログ入力の負端子/コンプリメンタリ端子。                                                                                                                |

| 13                                                      | CM    | コモンモードのリファレンス端子。                                                                                                                        |

| 29                                                      | DVCC  | デジタル電源電圧。0.1 $\mu$ Fと0.22 $\mu$ Fのコンデンサを使ってグランドにローカルバイパスしてください。                                                                         |

| 31, 41, 42, 51                                          | DRVCC | デジタル出力ドライバの電源電圧。0.1 $\mu$ Fと0.22 $\mu$ Fのコンデンサを使ってグランドにローカルバイパスしてください。                                                                  |

| 32                                                      | DOR   | データのオーバレンジビット。この制御線はADCのオーバレンジ状態を知らせ(flag)します。DORがハイに遷移した場合、オーバレンジ状態が検出されたことになります。DORがロー状態に留まっている場合は、ADCは許容されるフルスケールの範囲内で動作していることになります。 |

| 33                                                      | D0    | デジタルCMOS出力ビット0 (LSB)。                                                                                                                   |

| 34                                                      | D1    | デジタルCMOS出力ビット1。                                                                                                                         |

| 35                                                      | D2    | デジタルCMOS出力ビット2。                                                                                                                         |

| 36                                                      | D3    | デジタルCMOS出力ビット3。                                                                                                                         |

| 37                                                      | D4    | デジタルCMOS出力ビット4。                                                                                                                         |

| 38                                                      | D5    | デジタルCMOS出力ビット5。                                                                                                                         |

| 39                                                      | D6    | デジタルCMOS出力ビット6。                                                                                                                         |

| 40                                                      | D7    | デジタルCMOS出力ビット7。                                                                                                                         |

| 43                                                      | D8    | デジタルCMOS出力ビット8。                                                                                                                         |

| 44                                                      | D9    | デジタルCMOS出力ビット9。                                                                                                                         |

| 45                                                      | D10   | デジタルCMOS出力ビット10。                                                                                                                        |

| 46                                                      | D11   | デジタルCMOS出力ビット11。                                                                                                                        |

| 47                                                      | D12   | デジタルCMOS出力ビット12。                                                                                                                        |

| 48                                                      | D13   | デジタルCMOS出力ビット13                                                                                                                         |

| 49                                                      | D14   | デジタルCMOS出力ビット14 (MSB)。                                                                                                                  |

| 50                                                      | DAV   | データ有効出力。この出力はクロック制御線として使用することができ、外部バッファまたはデータ収集システムを駆動します。コンバタクロックの立下りエッジとDAVの立上りエッジの間の遅延時間の標準値は6.5nsです。                                |

# IFアプリケーション用の15ビット、80MspS、-78.4dBFSのノイズフロアを持つADC

MAX1428

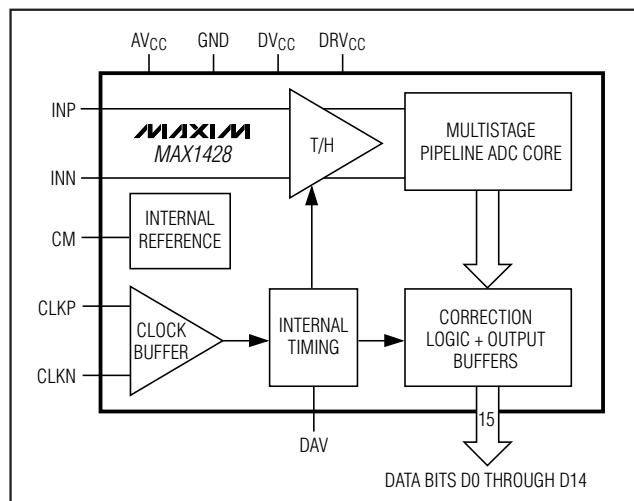

## 詳細

図1はMAX1428のアーキテクチャの全体図を示しています。MAX1428は入力にT/Hアンプを採用しており、それは低い熱ノイズ及び小さい歪となるように最適化されています。T/Hアンプ(INP及びINN)に接続するハイインピーダンスの差動入力は4.163Vに自己バイアスされており、2.56V<sub>P-P</sub>のフルスケール差動入力をサポートしています。T/Hアンプの出力はマルチステージのパイプラインADCコアに供給されます。ADCコアも非常に低い熱ノイズフロアと小さい歪を達成するように最適化されています。

クロックバッファは差動クロック入力波形を受信して入力T/H用の低ジッタクロック信号を生成します。アナログ入力部の信号は差動クロック波形の立上りエッジでサンプルされます。差動クロック入力(CLKP及びCLKN)はハイインピーダンス入力であり、2.4Vに自己バイアスされており、0.5V<sub>P-P</sub>~3.0V<sub>P-P</sub>の差動クロック波形をサポートします。

マルチステージのパイプラインADCコアからの出力は誤差補正及びフォーマット化ロジックに渡され、その後、2の補数形式の15ビット出力コードをデジタル出力ドライバに受け渡します。出力ドライバは2.3V~3.5Vの範囲で設定可能なレベルを持つCMOS対応出力を供給します。

## アナログ入力及びコモンモード(INP、INN、CM)

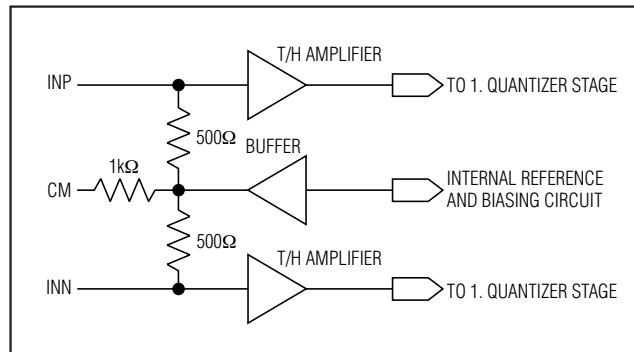

MAX1428に対する信号入力(INPとINN)は平衡型差動入力です。差動構成はコモンモードノイズ結合に対する不感性及び偶数次の高調波項の排除を可能とします。MAX1428に対する差動信号はAC結合として最良のダイナミック性能が得られるように注意深くバランスさせてください(さらに詳細については「アプリケーション情報」の項を参照ください)。入力信号のAC結合は、MAX1428の入力が図2に示すように自己バイアスされているため、容易に達成されます。T/Hはハイインピーダンスですが、実際の差動入力インピーダンスは公称で1kΩです。これはコモンモードリファレンスに対して各入力には2つの500Ωのバイアス抵抗器が接続されているためです。

図1. 簡略化したMAX1428のダイアグラム

図2. 簡略化したアナログ及びコモンモード入力のアーキテクチャ

CM端子は入力コモンモードの自己バイアス電位のモニタ端子を備えています。ほとんどアプリケーションにおいて、入力信号はAC結合され、この端子は無接続となります。入力信号のDC結合が必要となった場合、この端子は入力コモンモードレベルを制御するためのDCサーボループを構成するために使用することができます。さらに詳細は「アプリケーション情報」の項を参照してください。

# IFアプリケーション用の15ビット、80MspS、-78.4dBFSのノイズフロアを持つADC

## チップ搭載のリファレンス回路

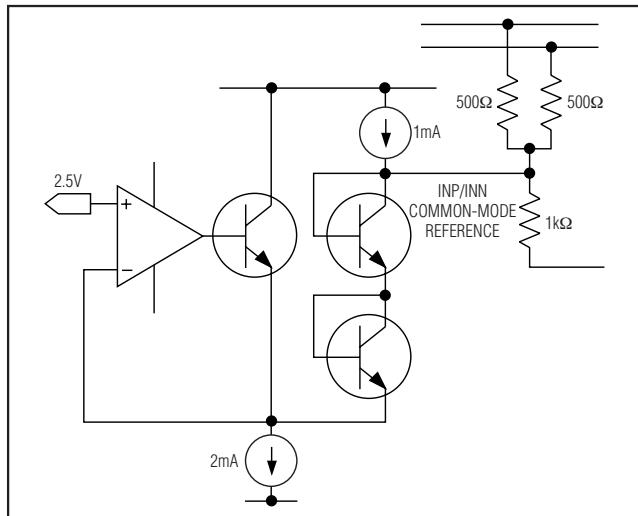

MAX1428は2.5Vの低ドリフトバンドギャップリファレンスをチップに搭載しています。このリファレンスの電位がコンバータのフルスケール範囲を決定し、それは公称で2.56V<sub>P-P</sub>差動です。内蔵のリファレンス電位はユーザからアクセスすることはできないため、MAX1428ではフルスケール範囲を外部から調整することはできません。

図3にはこのリファレンスからアナログ入力のコモンモードバイアス電圧を生成する方法が示されています。コモンモードの入力バイアスはバンドギャップリファレンスよりも、ダイオード2個分の電位だけ高く設定されており、従って温度で変化します。

図3. 簡略化したリファレンスの構造

## クロック入力(CLKP、CLKN)

MAX1428の差動クロックバッファはAC結合されたクロック波形を受け取るように設計されています。信号入力と同様に、クロック入力は自己バイアスされています。この場合のコモンモードバイアス電位は2.4Vであり、各入力はこのリファレンス電位に1kΩの抵抗を通して接続されています。その結果、クロック入力に関わる差動入力抵抗は2kΩです。差動クロック信号はクロック入力を駆動するために最低0.5V<sub>P-P</sub>まで使用可能ですが、最良のダイナミック性能はクロック入力電圧レベルが2V<sub>P-P</sub>～3V<sub>P-P</sub>の場合に得ることができます。クロック信号にジッタが存在すると、それは、直接、サンプルされる信号のジッタ(ノイズ)となります。従って、クロック源は低ジッタ(小さい位相ノイズ)源としてください。クロック入力を駆動するための詳細については「アプリケーション情報」の項を参照してください。

## システムタイミング要件

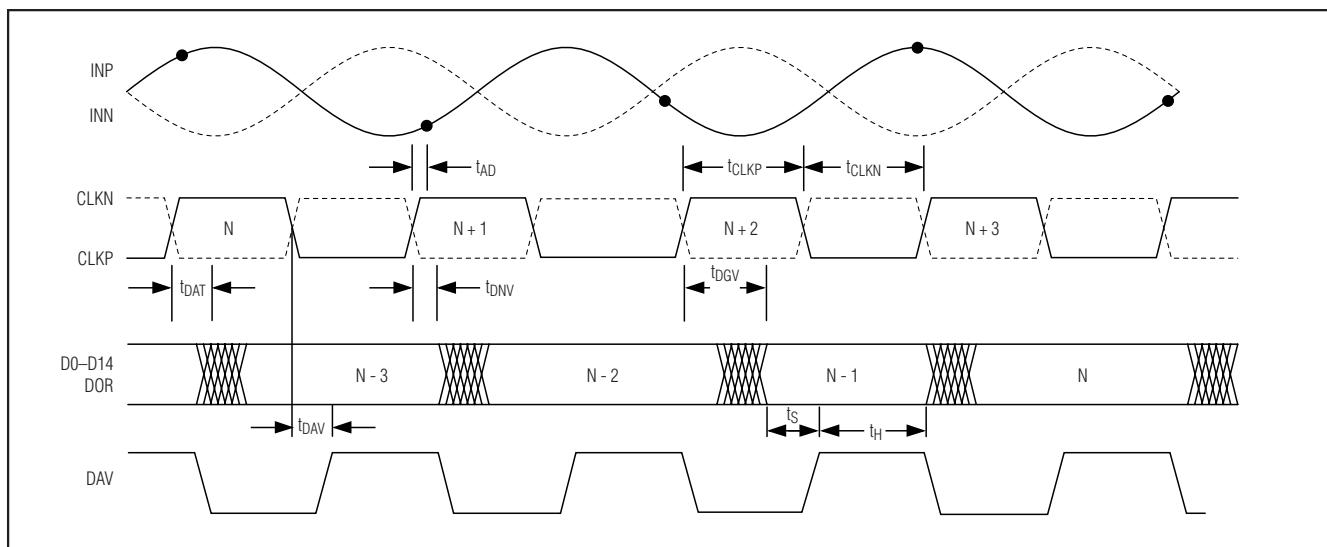

図4は信号入力、クロック入力、データ出力、及びDAV出力のタイミング関係を示しています。図に示された変数は「Electrical Characteristics」(電気的特性)表の種々のタイミング特性に対応しています。その中には以下のものがあります：

- $t_{DAT}$ ：クロックの立上りエッジから出力データ遷移の50%ポイントまでの遅延

- $t_{DAV}$ ：クロックの立下りエッジからDAVの立上りエッジの50%ポイントまでの遅延

- $t_{DNV}$ ：クロックの立上りエッジからデータが有効でなくなるまでの時間

図4. システム及び出力のタイミング図

# IFアプリケーション用の15ビット、80Mps、-78.4dBFSのノイズフロアを持つADC

MAX1428

- $t_{DGV}$  : クロックの立上りエッジからデータが有効となるまでの時間

- $t_{SETUP}$  : データが有効となるDAVの立上りエッジまでの時間

- $t_{HOLD}$  : DAVの立上りエッジからデータが有効でなくなるまでの時間

- $t_{CLKP}$  : クロック信号の立上りエッジの50%ポイントから立下りエッジの50%ポイントまでの時間

- $t_{CLKN}$  : クロック信号の立下りエッジの50%ポイントから立上りエッジの50%ポイントまでの時間

MAX1428は入力クロックの立上りエッジで入力信号をサンプルします。3クロック周期のデータ待ち時間の後、出力データはDAV信号の立上りで有効となります。正常動作のためには、クロックのデューティサイクルは50%  $\pm 5\%$ としなければならないことに注意してください。

## デジタル出力(D0-D14、DAV、DOR)

CMOS対応のデジタル出力(D0-D14、DAV、及びDOR)のロジックハイのレベルは2.3V~3.5Vの範囲で設定することができます。これはDV<sub>CC</sub>及びDRV<sub>CC</sub>のピンの電圧を所望のロジックハイレベルに設定することによって行われます。DV<sub>CC</sub>とDRV<sub>CC</sub>の電圧は同じ値にしなければならないことを注意しておきます。

最良の性能を得るためにMAX1428のデジタル出力への容量性負荷は可能な限り小さくしてください

(10pF未満とする)。容量性負荷が大きいと、データの遷移時に大きい充電電流が流れ、それはADCのアナログ部にフィードバックされて、歪項を生じさせる可能性があります。

負荷容量は出力トレースを短くすること、及び単体のCMOSバッファまたはラッチ入力(複数のCMOS入力ではなく)を駆動することによって小さく抑えられます。小さい直列抵抗(220Ω以下)をMAX1428の出力とデジタル負荷との間で、可能な限り出力端子の近くに配置して挿入すると、データ遷移の間の充電電流の大きさを制御することに役立ち、ダイナミック性能が向上します。負荷と抵抗器の間のトレース長は可能な限り短くするとトレース容量を小さくすることができます。

出力データは表1に示すように2の補数形式です。

データはDAVの立上りエッジで有効となり(図4)、DAVは出力データをラッチするためのクロック信号として使うことができます。DAV出力はデータ出力の2倍の駆動能力を持ち、従って複数のデータラッチを駆動するために使うことができます。

DOR出力はオーバレンジ状態を確認するために使われます。入力信号がMAX1428の正または負のフルスケール範囲を超えた場合、DORがハイとして出力されます。DORのタイミングはデータ出力のタイミングと同じであり、従って、DORは1サンプルごとにオーバレンジ指示を行います。

表1. MAX1428のデジタル出力符号方式

| INP<br>ANALOG VOLTAGE LEVEL | INN<br>ANALOG VOLTAGE LEVEL | D14-D0<br>TWO'S COMPLEMENT CODE                                                                    |

|-----------------------------|-----------------------------|----------------------------------------------------------------------------------------------------|

| V <sub>REF</sub> + 0.64V    | V <sub>REF</sub> - 0.64V    | 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1<br>(positive full scale)                                             |

| V <sub>REF</sub>            | V <sub>REF</sub>            | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0<br>(midscale + δ)<br>1 1 1 1 1 1 1 1 1 1 1 1 1 1 1<br>(midscale - δ) |

| V <sub>REF</sub> - 0.64V    | V <sub>REF</sub> + 0.64V    | 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0<br>(negative full scale)                                             |

# IFアプリケーション用の15ビット、80MspS、-78.4dBFSのノイズフロアを持つADC

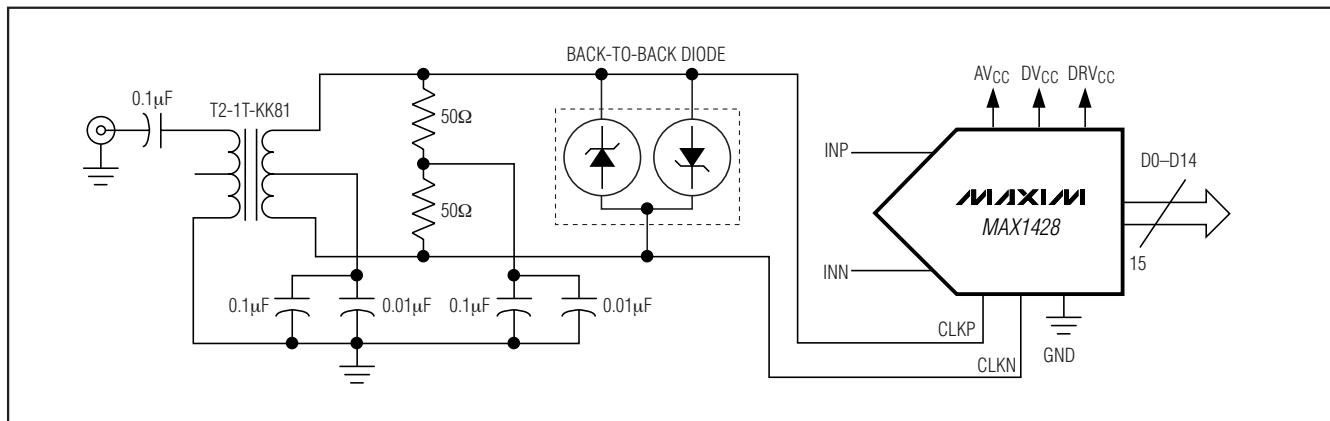

図5. トランス結合したクロック入力構成

## アプリケーション情報

### 差動、AC結合クロック入力

MAX1428に対するクロック入力はAC結合の差動信号で駆動されるように設計されており、この条件で使用すると最良の性能が得られます。しかし、使用可能なクロック源がシングルエンドであるケースが多く存在します。図5にはシングルエンドのクロック入力信号を、トランスを使って差動信号に変換する1つの方法が示されています。この例では、1次と2次間の巻線比は1:1.414です。1次と2次間のインピーダンス比は巻数比の2乗となるため、この場合、それは1:2です。これはトランスの一次側からみて50Ωとなるように2次側を100Ω差動抵抗で終端するためです。この例における終端抵抗は共通ノードをAC結合してグランドに落とした2つの50Ω抵抗器の直列接続で構成されています。その代わりに、コモンモード接続を行わないで、2つの入力間に1個の100Ω抵抗器を接続する方法を採用することができます。

図5の例では、トランスの2次側は直接、クロック入力に接続されています。クロック入力は自己バイアスされているため、トランスのセンタタップはAC結合してグランドに落とすか、または無接続としなければなりません。もし、2次側のセンタタップがDC結合でグランドに接続される場合、クロック入力と直列にプロッキングコンデンサを追加する必要があります。

クロックジッタは、一般に、クロック信号がゼロ交差時に高いスルーレイ特を有する改善されます。従って、クロック入力を駆動するため、正弦波のソースが使われる場合は、クロックの振幅は可能な限り大きくして、ゼロ交差時のスルーレイ特を最大化することが望されます。図5に示したように、バウクトゥバウク接続したショットキダイオードは入力信号が3V<sub>P-P</sub>以下

の値に維持される限りは不要です。大振幅の信号が与えられた場合(ゼロ交差のスルーレイ特を最大化するため)、前述のダイオードはクロック入力端における差動信号振幅を制限する働きをします。

クロック入力に結合する差動モードノイズはすべて、クロックジッタに変換されてMAX1428のSNR性能を悪化させます。クロック入力へのアナログ入力信号の、どのような差動モード結合も高調波歪をもたらします。このため、クロックラインはアナログ入力及びデジタル出力から十分にアイソレートされていることが重要です。ノイズ結合に関する詳細については「プリント基板のレイアウトについて」の項を参照してください。

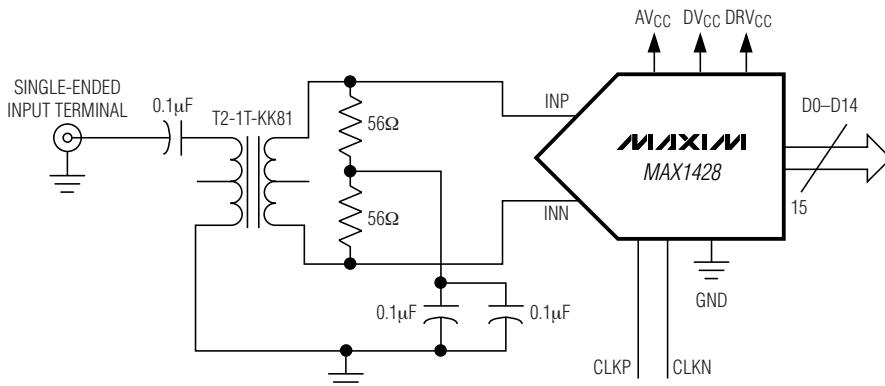

### 差動、AC結合のアナログ入力

アナログ入力(INP及びINN)は差動AC結合の信号で駆動されるように設計されています。これらの信号が正確にバランスしていることが、特に重要です。これらの入力に印加されるいかなるコモンモード信号も偶数次の歪項を悪化させます。従って、シングルエンドの方法でこれらの入力を駆動しようとするなどの試みも大きい偶数次の歪項を生じる結果となります。

図6はトランスを用いて、シングルエンド信号をバランスした差動信号に変換する1つの方法を示しています。この例における1次と2次のトランスの巻線比は1:1.414です。インピーダンス比は巻線比の2乗となるため、この例ではインピーダンス比は1:2となります。トランスの一次側で50Ωの入力インピーダンスを達成するためには、2次側は112Ωの差動負荷で終端されます。この負荷抵抗は、MAX1428の差動入力抵抗と並列となって2次側の差動負荷は100Ωとなります。より大きく信号を昇圧するためには、より大きいトランスの巻線比を使用することが妥当であり、これはMAX1428を駆動する回路の駆動要件を緩和するためには望ましいと

# IFアプリケーション用の15ビット、80MspS、-78.4dBFSのノイズフロアを持つADC

MAX1428

図6. トランス結合のアナログ入力構成

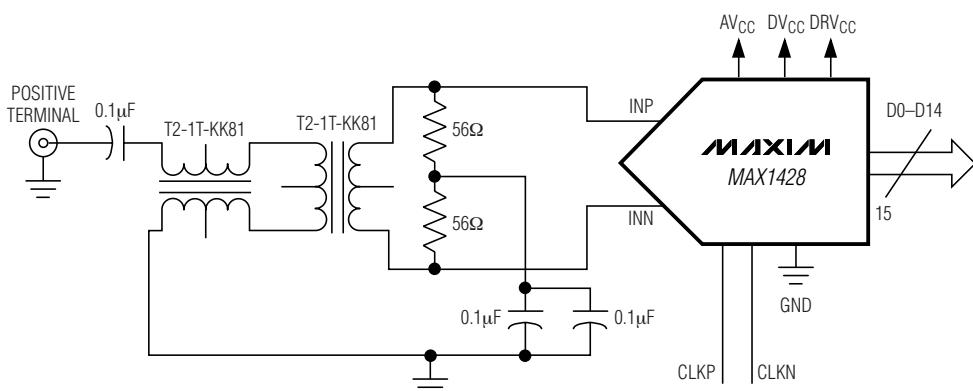

図7. 1次側トランスを用いるトランス結合のアナログ入力構成

言えます。しかし、巻数比を大きくすると、MAX1428の差動入力抵抗が1次側に換算した入力抵抗に大きい影響を与えます。巻数比を1:4.47とすると、MAX1428の1kΩの入力抵抗はそれだけで1次側に換算した入力抵抗は50Ωとなります。

図6ではトランスのセンタタップが無接続として示されていますが、その点はAC結合してグランドに落とすことができます。しかし、経験によればセンタタップを無接続とする方がより良いバランスを得ることができます。

前に述べたように、MAX1428への信号入力は最良の偶数次の歪性能を得るためにには正確にバランスしな

ければなりません。図7はトランスの1次側にバランスを挿入することによって図6に優る、改善されたバランスを得ることができます。図6に比べて偶数次の歪項において著しい改善を達成することができます。

トランスに関するもう1つ重要な注意があります。トランスの1次または2次を流れるいかなるDC電流もトランスのコアに磁気的なバイアスを与えることです。このことが起こると、トランスは、もはや、正確にバランスされず、MAX1428の歪の悪化として観測される可能性があります。バランスした状態に復帰させるためには、コアを消磁する必要があります。

# IFアプリケーション用の15ビット、80MspS、-78.4dBFSのノイズフロアを持つADC

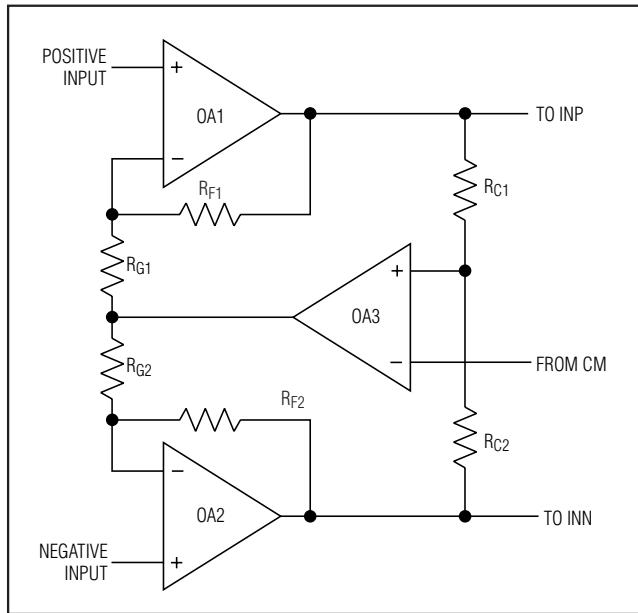

図8. DC結合したアナログ入力構成

## DC結合したアナログ入力

入力信号をAC結合とすることが最良のダイナミック性能を得るために適切な方法ですが、CM電位を利用して入力をDC結合とすることが可能です。図8はDC結合を行う1つの方法が示されています。アンプOA1とOA2のコモンモード電位を、アンプOA3の動作によってMAX1428のCM電位に等しくするように「サーボ」制御が行われます。この場合、コモンモードループが安定であることを保証する注意が必要であり、両半回路の $R_F/R_G$ の比はバランスを保証するために十分にマッチさせなければなりません。

## プリント基板のレイアウトについて

プリント基板のレイアウトが悪いと、どのような広ダイナミックレンジ、高サンプリングのコンバータも性能を損ないます。MAX1428は、このルールに対して例外ではなく、規定された性能を得るために注意深いレイアウト技術を守らなければなりません。レイアウト問題は次に示すカテゴリに分かれます：

- 1) 層の割当て

- 2) 信号経路

- 3) グランド接続

- 4) 電源経路及びバイパス方法

MAX1427の評価ボード(MAX1427の評価キット)は基板のレイアウトを行うための優れた参考基準(frame)を提供し、以下に続く内容は評価ボードにおいて実施されている方法と一致しています。

## 層の割当て

MAX1427のEVキットは6層基板であり、その層の割当てはこの前提で説明します。信号配線層と電源配線層の間にグランドプレーンを1層割り当てる 것을 推奨します。この方法は電源ラインから信号ラインへの結合を防ぎます。MAX1427のEVキットのPC基板は信号ラインを表面(部品)層に置き、グランド層を層2に置いています。信号配線として使われない表面層の領域はグランドプレーンで覆い、ビアを使って層2と接続しています。層3と4は電源配線専用です。層5はもう1つのグランドプレーンであり、層6は部品及び信号配線用のもう1つの層として使われています。

4層基板実装では、層1を信号ライン、層2をグランドプレーン、層3を電源供給、及び層4をもう1つの信号配線とする方法も可能です。しかし、クロックと信号ラインが相互に、また、電源ラインからアイソレートされていることが確実に行われなければなりません。

## 信号配線

偶数次の歪を良好に保つためには、信号ライン(INPとINN入力を伝える配線)は注意深くバランスさせなければなりません。これを達成するためには、信号配線は可能な限り対称としなければなりません。これは2つの信号配線は同じ長さと寄生成分が同じとなる状態を与える必要があることを意味します。前に述べたように、信号ラインは電源ラインからアイソレートして電源からアナログ入力への結合を防がなければなりません。このためには、前節で述べた必要とする層の割当てを行うことによって達成されます。さらに、クロックラインは信号ラインからアイソレートされていることが重要です。MAX1427のEVキットでは、これはクロックラインを最下層(層6)に走らせることによって行われています。クロックラインは、そこから、デバイスの近くに置かれたビアを通してADCに接続されています。クロックラインは電源ラインからは層5のグランドプレーンによってアイソレートされています。

デジタル出力配線は容量性の結合を最小化するために可能な限り短くしてください。これらの配線の下の層2のグランドプレーンは除去してはなりません。それはデジタルグランドのリターン電流がバイパスコンデンサへ返るのに遮られない経路を与えるためです。

# IFアプリケーション用の15ビット、80MspS、-78.4dBFSのノイズフロアを持つADC

MAX1428

## グラウンド接続

デジタルグラウンドのリターン電流を閉じ込める目的で分割グラウンドを用いる方法がADCのアプリケーションに関する文献において推奨されていることが多く存在します。しかし、MAX1428のようなコンバータに対しては、単一で、遮られることのないグラウンドプレーンを強く推奨します。MAX1427のEVキットはそのようなグラウンドプレーンを用いて優れたダイナミック性能を達成しています。

MAX1428のEPは層2のグラウンドプレーンにビア接続した層1のグラウンドパッドに直接半田付けしてください。これがプリント基板への優れた電気的及び熱的接続を与えます。

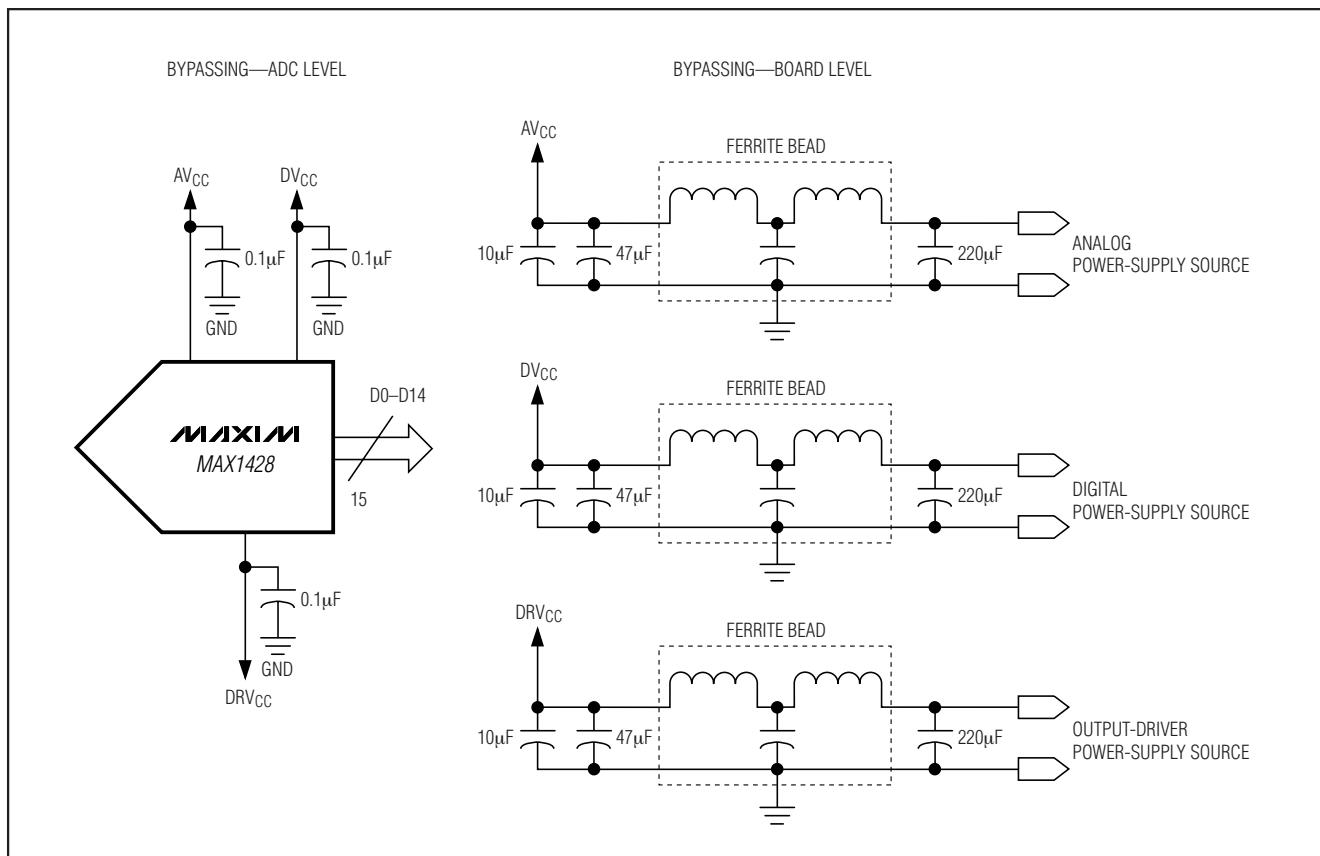

## 電源バイパス

MAX1427のEVキットは各電源ライン( $AV_{CC}$ 、 $DV_{CC}$ 、 $DRV_{CC}$ )に220 $\mu$ Fのコンデンサを使用して、低周波のバイパスを与えています。これらのコンデンサが持つ損失(直列抵抗)は、現実的にはQが高いことによる共振

を抑える利点となります。フェライトビーズもまた、各電源ラインに使用して電源バイパス能力を高めることができます(図9)。

小さい値(0.01 $\mu$ F~0.1 $\mu$ F)の表面実装型のコンデンサを各電源端子または電源端子をまとめた点に配置することによって、高周波の電源ノイズを減衰させるようしてください(図9)。これらのコンデンサはデバイスに可能な限り近い位置で基板の上面に配置し、グラウンドプレーンへの接続は可能な限りの最短とすることを推奨します。

## スタティックなパラメータの定義

### Integral Nonlinearity(積分非直線性)(INL)

積分非直線性は、実際の伝達関数値の直線からの偏差です。この直線はいったん、オフセットと利得誤差をゼロにした後は、最近似直線フィット法または伝達関数の端点間に引かれた直線の何れかとすることができます。しかし、MAX1428に対するスタティックリニアリティパラメータは入力周波数を15MHzとしたヒストグラム法を用いて測定されます。

図9. MAX1428に対する推奨するグラウンド接続、バイパス、及びデカッピング法

# IFアプリケーション用の15ビット、80Msps、-78.4dBFSのノイズフロアを持つADC

## Differential Nonlinearity(微分非直線性)(DNL)

微分非直線性は、1 LSBの実際のステップの幅と、理想値との差です。DNLエラー規格が1 LSB以下の場合は、ミッキングコードがないことと、伝達関数が単調性であることが保証されます。MAX1428のDNLは、15MHzの入力トーンに基づいたヒストグラム法を使って測定されます。

## ダイナミックパラメータの定義

### Aperture Delay(アーチャ遅延)

アーチャ遅延( $t_{AD}$ )は、サンプリングクロックの立上りエッジから、実際のサンプル取得時点までの時間です(図4)。

### Aperture Jitter(アーチャジッタ)

アーチャジッタ( $t_{AJ}$ )は、アーチャ遅延におけるサンプル間の時間間隔のばらつきです。

### Signal-to-Noise Ratio(信号対ノイズ比)(SNR)

デジタルサンプルから完璧に再生された波形の場合、理論上の最大SNRは、RMS量子化エラー(残留エラー)に対するフルスケールアナログ入力(RMS値)の比です。理想的な理論上の最小のアナログ-ディジタル変換ノイズは量子化エラーのみによってたらされ、ADCの分解能(Nビット)に直接依存します：

$$SNR_{dB}[\max] = 6.02dB \times N + 1.76dB$$

実際には、量子化ノイズのほかに、サーマルノイズ、クロックジッタ、信号位相ノイズ、及び伝達関数の非線形性が、同様にSNRの計算に寄与し、ADCのSNRを決定するときは考慮に入れる必要があります。フルスケールに近いアナログ入力信号(-0.5dBFS~-1dBFS)に対して、熱及び量子化ノイズは周波数範囲にわたって均一に分布しています。一方、伝達関数の非線形性に基づく誤差のエネルギーは均一には分布しておらず、最初の数百の奇数次の高調波に限定されます。

MAX1428の主要なターゲットとしているアプリケーションであるBTSアプリケーションではキャリアまたはDCに近い過剰のノイズ及び誤差エネルギーには、通常、注意を払いません。これらの低周波及び側帯波エラーはテストシステムの副作用であり、BTSチャネルの感度に対してなんら影響を与えません。従って、それらはSNRの計算から除外されます。

### Signal-to-Noise Plus Distortion (信号対ノイズ + 歪み)(SINAD)

SINADはRMSで表した信号の、基本波とDCオフセットを除いたすべてのスペクトラム成分に対する比をとて算出されます。

## Single-Tone Spurious-Free Dynamic Range (シングルトーンのスピアスのない ダイナミックレンジ)(SFDR)

SFDRは、2番目に大きなノイズまたは高調波歪成分のRMS値に対する、キャリア周波数(最大信号成分)のRMS振幅の比です。SFDRは通常、キャリア周波数振幅に対するdBc、またはADCのフルスケール範囲に対するdBFSで測定されます。

## Two-Tone Spurious-Free Dynamic Range (2トーンスピアスフリーダイナミックレンジ) (SFDR<sub>TT</sub>)

SFDR<sub>TT</sub>はパワースペクトラムにおけるピークのスピアス成分のRMS値に対するどちらかのトーンのRMS値の比として表されます。このピークススピアスは2つの入力テストトーンの相互変調積となるものです。

## Two-Tone Intermodulation Distortion (2トーン相互変調歪)(IMD)

2トーンIMDは最悪の3次(またはさらに高次の)相互変調積に対するどちらかの入力トーンの比をデシベルで表したものです。個々の入力トーンのレベルは-8dBフルスケールとします。

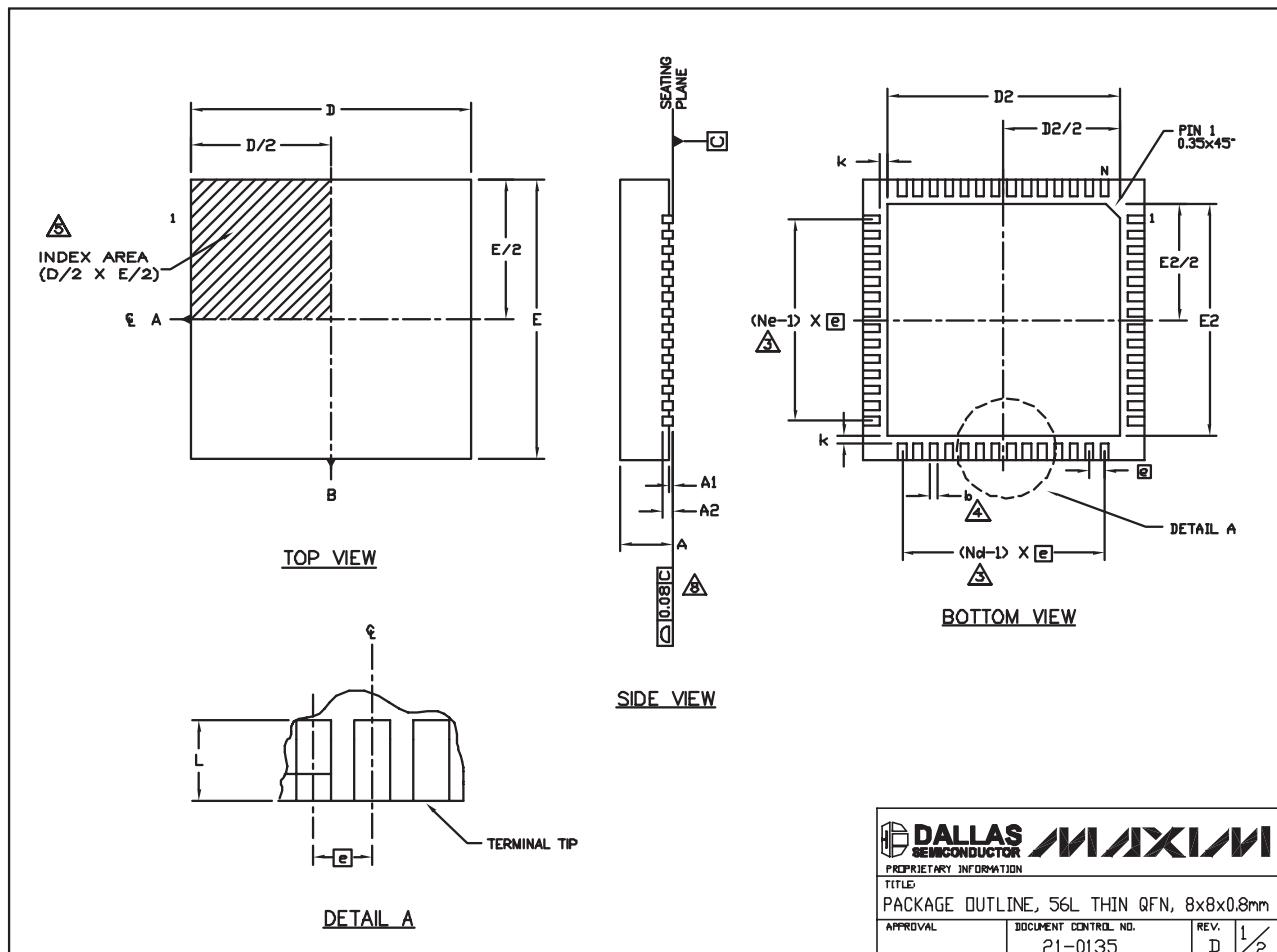

## ピン配置

# IFアプリケーション用の15ビット、80MspS、 -78.4dBFSのノイズフロアを持つADC

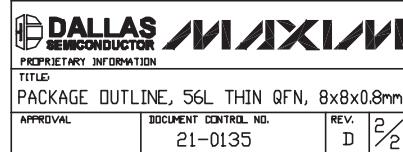

## パッケージ

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、[japan.maxim-ic.com/packages](http://japan.maxim-ic.com/packages)をご参照下さい。)

MAX1428

56L THIN QFN, EPS

|                                          |                             |       |

|------------------------------------------|-----------------------------|-------|

|                                          | <b>DALLAS SEMICONDUCTOR</b> |       |

| PROPRIETARY INFORMATION                  |                             |       |

| TITLE:                                   |                             |       |

| PACKAGE OUTLINE, 56L THIN QFN, 8x8x0.8mm |                             |       |

| APPROVAL                                 | DOCUMENT CONTROL NO.        | REV.  |

|                                          | 21-0135                     | D 1/2 |

# IFアプリケーション用の15ビット、80MspS、-78.4dBFSのノイズフロアを持つADC

## パッケージ(続き)

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、[japan.maxim-ic.com/packages](http://japan.maxim-ic.com/packages)をご参照下さい。)

### NOTES:

1. DIE THICKNESS ALLOWABLE IS 0.225mm MAXIMUM (0.009 INCHES MAXIMUM).

2. DIMENSIONING & TOLERANCES CONFORM TO ASME Y14.5M. - 1994.

3. **N** IS THE NUMBER OF TERMINALS.

**N<sub>d</sub>** IS THE NUMBER OF TERMINALS IN X-DIRECTION &

**N<sub>e</sub>** IS THE NUMBER OF TERMINALS IN Y-DIRECTION.

4. DIMENSION **b** APPLIES TO PLATED TERMINAL AND IS MEASURED

BETWEEN 0.20 AND 0.25mm FROM TERMINAL TIP.

5. THE PIN #1 IDENTIFIER MUST BE LOCATED ON THE TOP SURFACE OF THE

PACKAGE WITHIN HATCHED AREA AS SHOWN.

EITHER AN INDENTATION MARK OR INK/LASER MARK IS ACCEPTABLE.

6. ALL DIMENSIONS ARE IN MILLIMETERS.

7. PACKAGE WARPAGE MAX 0.01mm.

8. APPLIES TO EXPOSED PAD AND TERMINALS.

EXCLUDES INTERNAL DIMENSION OF EXPOSED PAD.

9. MEETS JEDEC NO220.

| S<br>Y<br>B<br>O<br>L | 56L 8x8  |      |      | N <sub>o</sub> <sub>T</sub> <sub>E</sub> |

|-----------------------|----------|------|------|------------------------------------------|

|                       | MIN.     | NOM. | MAX. |                                          |

| A                     | 0.70     | 0.75 | 0.80 |                                          |

| b                     | 0.20     | 0.25 | 0.30 | 4                                        |

| D                     | 7.90     | 8.00 | 8.10 |                                          |

| E                     | 7.90     | 8.00 | 8.10 |                                          |

| ④                     | 0.50 BSC |      |      |                                          |

| N                     | 56       |      |      | 3                                        |

| N <sub>d</sub>        | 14       |      |      | 3                                        |

| N <sub>e</sub>        | 14       |      |      | 3                                        |

| L                     | 0.30     | 0.40 | 0.50 |                                          |

| A1                    | 0.00     | 0.02 | 0.05 |                                          |

| A2                    | 0.20 REF |      |      |                                          |

| k                     | 0.25     | --   | --   |                                          |

| PKG.<br>CODE | EXPOSED PAD VARIATION |      |      |      |      |      | DOWN<br>BONDS<br>ALLOWED |  |

|--------------|-----------------------|------|------|------|------|------|--------------------------|--|

|              | D2                    |      |      | E2   |      |      |                          |  |

|              | MIN.                  | NOM. | MAX. | MIN. | NOM. | MAX. |                          |  |

| T5688-1      | 6.50                  | 6.65 | 6.70 | 6.50 | 6.65 | 6.70 | WLDD-5 NO                |  |

| T5688-2      | 6.50                  | 6.65 | 6.70 | 6.50 | 6.65 | 6.70 | WLDD-5 YES               |  |

| T5688-3      | 6.50                  | 6.65 | 6.70 | 6.50 | 6.65 | 6.70 | WLDD-5 NO                |  |

マキシム・ジャパン株式会社

〒169-0051 東京都新宿区西早稲田3-30-16 (ホリゾン1ビル)

TEL. (03)3232-6141 FAX. (03)3232-6149

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。マキシムは随时予告なく回路及び仕様を変更する権利を留保します。

18 Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2004 Maxim Integrated Products, Inc. All rights reserved.

MAXIM is a registered trademark of Maxim Integrated Products.