# 12ビット、20Msps、3.3V、低電力ADC 内部リファレンス付

MAX1422

## 概要

3.3V、12ビットA/Dコンバータ(ADC) MAX1422は、完全差動入力を特長とし、パイプラインされた12ステージのADCアーキテクチャで、完全差動信号バス構成の、広帯域トラックアンドホールド(T/H)及びディジタル誤差補正を備えています。MAX1422は、イメージング装置及びディジタル通信などの低電源、高ダイナミック性能のアプリケーション用として最適です。このコンバータは3.3Vの単一電源で動作し、消費電力は僅か137mWです。5MHzの入力周波数及び20Mspsサンプル周波数における標準信号対ノイズ比(SNR)は67dB(typ)です。完全差動入力ステージは400MHzの小信号-3dB帯域をもち、シングルエンド入力を使用した動作も可能です。

内部+2.048V精度のバンドギャップリファレンスがADCのフルスケール範囲を設定します。フレキシブルなリファレンス構造で、内部リファレンス又は外部からのバッファされた、又はバッファされていないリファレンスを使用することが可能なため、精度の高い、又は異なる入力電圧範囲を必要とするアプリケーションに最適です。

低動作電力に加えて、MAX1422はリファレンスパワーダウン及びシャットダウンモードの2つのパワーダウンモードを備えています。リファレンスパワーダウンモードでは、内部バンドギャップリファレンスが停止され、結果として標準消費電流が2mA低減されます。アイドル期間中に電力の節約を最大化するフルシャットダウンモードも備えています。

MAX1422は、パラレル、オフセットバイナリ、CMOSコンパチブルのスリーステート出力を特長としています。

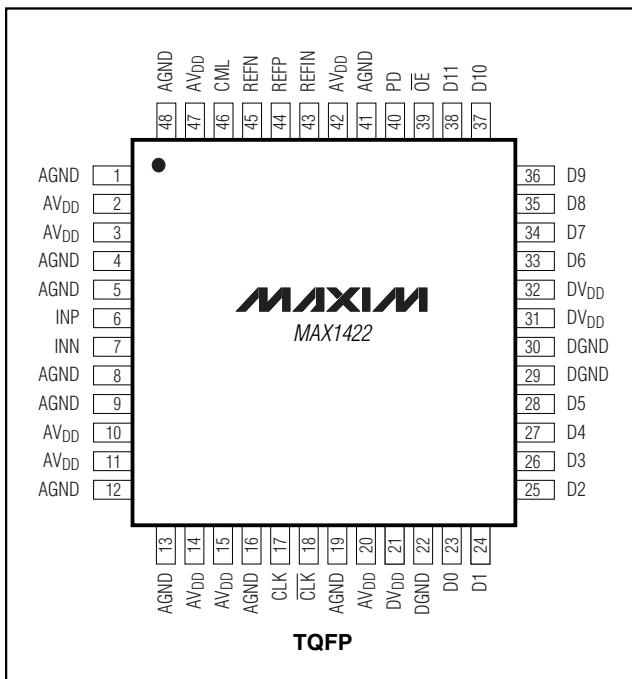

MAX1422は、7mm x 7mm x 1.4mm、48ピンTQFPパッケージで提供され、商業用温度範囲(0°C ~ +70°C)及び工業用拡大温度範囲(-40°C ~ +85°C)の仕様となっています。

ピンコンパチブル、高速バージョンのMAX1422も提供しています。40MspsについてはMAX1421のデータシートを、60MspsについてはMAX1420のデータシートを参照して下さい。

## アプリケーション

医療用超音波イメージング

CCDピクセル処理

データ取得

レーダ

IF及びベースバンドデジタル化

*Functional Diagram appears at end of data sheet.*

## 特長

- ◆ 単一電源：3.3V

- ◆ SNR@f<sub>IN</sub>=5MHz : 67dB

- ◆ 内部2.048V精度バンドギャップリファレンス

- ◆ 差動広帯域入力T/Hアンプ

- ◆ パワーダウンモード：

- 130mW(リファレンスシャットダウンモード)

- 10μW(シャットダウンモード)

- ◆ パッケージ：省スペースの48ピンTQFP

## 型番

| PART       | TEMP RANGE     | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX1422CCM | 0°C to +70°C   | 48 TQFP     |

| MAX1422ECM | -40°C to +85°C | 48 TQFP     |

## ピン配置

本データシートに記載された内容はMaxim Integrated Productsの公式な英語版データシートを翻訳したものです。翻訳により生じる相違及び誤りについては責任を負いかねます。正確な内容の把握には英語版データシートをご参照ください。

無料サンプル及び最新版データシートの入手には、マキシムのホームページをご利用ください。<http://japan.maxim-ic.com>

# 12ビット、20Msps、3.3V、低電力ADC 内部リファレンス付

## ABSOLUTE MAXIMUM RATINGS

|                                                                                                  |                                     |                |

|--------------------------------------------------------------------------------------------------|-------------------------------------|----------------|

| AVDD, DVDD to AGND                                                                               | .....                               | -0.3V to +4V   |

| DVDD, AVDD to DGND                                                                               | .....                               | -0.3V to +4V   |

| DGND to AGND                                                                                     | .....                               | -0.3V to +0.3V |

| INP, INN, REFP, REFN, REFIN,<br>CML, CLK, $\overline{CLK}$ , .....(AGND - 0.3V) to (AVDD + 0.3V) | .....                               | .....          |

| D0-D11, $\overline{OE}$ , PD                                                                     | .....(DGND - 0.3V) to (DVDD + 0.3V) | .....          |

| Continuous Power Dissipation (TA = +70°C)                                                        |                                     |                |

|                                            |       |                 |

|--------------------------------------------|-------|-----------------|

| 48-Pin TQFP (derate 12.5mW/°C above +70°C) | ..... | 1000mW          |

| Operating Temperature Ranges               |       |                 |

| MAX1422CCM                                 | ..... | 0°C to +70°C    |

| MAX1422ECM                                 | ..... | -40°C to +85°C  |

| Maximum Junction Temperature               | ..... | +150°C          |

| Storage Temperature Range                  | ..... | -65°C to +150°C |

| Lead Temperature (soldering, 10s)          | ..... | +300°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

( $V_{AVDD} = V_{DVDD} = +3.3V$ ,  $AGND = DGND = 0$ ,  $V_{IN} = \pm 1.024V$ , differential input voltage at -0.5dB FS, internal reference,  $f_{CLK} = 20MHz$  (50% duty cycle), digital output load  $C_L \approx 10pF$ ,  $TA = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $TA = +25^\circ C$ .)

| PARAMETER                                                             | SYMBOL           | CONDITIONS                                                        | MIN  | TYP                     | MAX | UNITS   |

|-----------------------------------------------------------------------|------------------|-------------------------------------------------------------------|------|-------------------------|-----|---------|

| <b>DC ACCURACY</b>                                                    |                  |                                                                   |      |                         |     |         |

| Resolution                                                            | RES              |                                                                   |      | 12                      |     | Bits    |

| Differential Nonlinearity                                             | DNL              | TA = +25°C, no missing codes                                      | -1   | 1                       |     | LSB     |

|                                                                       |                  | TA = TMIN to TMAX                                                 |      | ±0.5                    |     |         |

| Integral Nonlinearity                                                 | INL              | TA = TMIN to TMAX                                                 |      | ±2                      |     | LSB     |

| Mid-scale Offset                                                      | MSO              |                                                                   | -3   | ±.75                    | 3   | %FSR    |

| Mid-scale Offset Temperature Coefficient                              | MSOTC            |                                                                   |      | 3 × 10 <sup>-4</sup>    |     | %/°C    |

| Gain Error                                                            | GE               | Internal reference (Note 1)                                       | -5   | ±0.1                    | 5   | %FSR    |

|                                                                       |                  | External reference applied to REFIN, (Note 2)                     | -5   | ±0.2                    | 5   |         |

|                                                                       |                  | External reference applied to REFP, CML, and REFN (Note 3)        | -1.5 |                         | 1.5 |         |

| Gain Error Temperature Coefficient                                    | GETC             | External reference applied to REFP, CML, and REFN (Note 3)        |      | 15 × 10 <sup>-6</sup>   |     | %/°C    |

| <b>DYNAMIC PERFORMANCE</b> (f <sub>CLK</sub> = 20MHz, 4096-point FFT) |                  |                                                                   |      |                         |     |         |

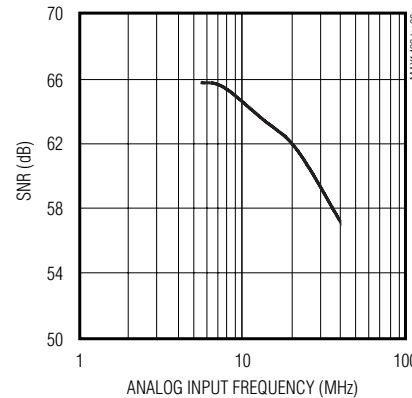

| Signal-to-Noise Ratio                                                 | SNR              | f <sub>IN</sub> = 5MHz, TA = +25°C                                | 63   | 67                      |     | dB      |

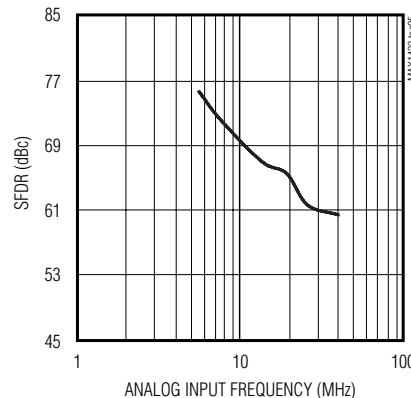

| Spurious-Free Dynamic Range                                           | SFDR             | f <sub>IN</sub> = 5MHz, TA = +25°C                                | 64   | 74                      |     | dBc     |

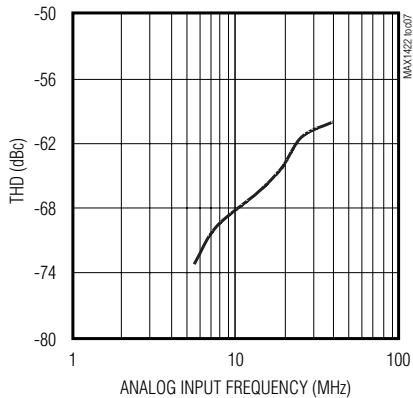

| Total Harmonic Distortion                                             | THD              | f <sub>IN</sub> = 5MHz, TA = +25°C                                |      | -72                     | -63 | dBc     |

| Signal-to-Noise and Distortion                                        | SINAD            | f <sub>IN</sub> = 5MHz, TA = +25°C                                | 60   | 65                      |     | dB      |

| Effective Number of Bits                                              | ENOB             | f <sub>IN</sub> = 5MHz                                            |      | 10.5                    |     | Bits    |

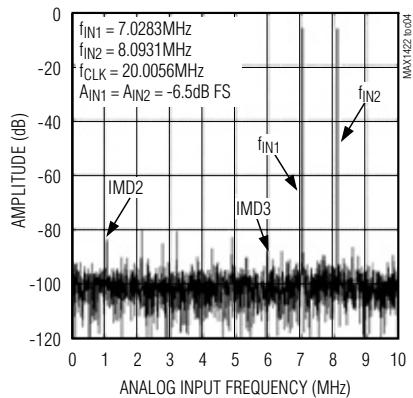

| Two-Tone Intermodulation Distortion                                   | IMD              | f <sub>IN1</sub> = 7.028MHz, f <sub>IN2</sub> = 8.093MHz (Note 4) |      | -77                     |     | dBc     |

| Differential Gain                                                     | DG               |                                                                   |      | ±1                      |     | %       |

| Differential Phase                                                    | DP               |                                                                   |      | ±0.25                   |     | Degrees |

| <b>ANALOG INPUTS</b> (INP, INN, CML)                                  |                  |                                                                   |      |                         |     |         |

| Input Resistance                                                      | R <sub>IN</sub>  | Either input to ground                                            |      | 61                      |     | kΩ      |

| Input Capacitance                                                     | C <sub>IN</sub>  | Either input to ground                                            |      | 4                       |     | pF      |

| Common-Mode Input Level (Note 5)                                      | V <sub>CML</sub> |                                                                   |      | V <sub>AVDD</sub> × 0.5 |     | V       |

# 12ビット、20MspS、3.3V、低電力ADC 内部リファレンス付

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{AVDD} = V_{DVDD} = +3.3V$ ,  $AGND = DGND = 0$ ,  $V_{IN} = \pm 1.024V$ , differential input voltage at  $-0.5dB$  FS,  $+2.048V$  internal reference,  $f_{CLK} = 20MHz$  (50% duty cycle), digital output load  $C_L \approx 10pF$ ,  $TA = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $TA = +25^\circ C$ .)

| PARAMETER                                                                                       | SYMBOL        | CONDITIONS                   | MIN                       | TYP                       | MAX | UNITS           |

|-------------------------------------------------------------------------------------------------|---------------|------------------------------|---------------------------|---------------------------|-----|-----------------|

| Common-Mode Input Voltage Range (Note 5)                                                        | $V_{CMVR}$    |                              | $V_{CML}$<br>$\pm 5\%$    |                           |     | V               |

| Differential Input Range                                                                        | $V_{IN}$      | $V_{INP} - V_{INN}$ (Note 6) | $\pm V_{DIFF}$            |                           |     | V               |

| Small-Signal Bandwidth                                                                          | $BW_{-3dB}$   | (Note 7)                     | 400                       |                           |     | MHz             |

| Large-Signal Bandwidth                                                                          | $FPBW_{-3dB}$ | (Note 7)                     | 150                       |                           |     | MHz             |

| Overvoltage Recovery                                                                            | OVR           | $1.5 \times FS$ input        | 1                         |                           |     | Clock cycles    |

| <b>INTERNAL REFERENCE</b> ( $REFIN$ bypassed with $0.22\mu F$ in parallel with $1nF$ )          |               |                              |                           |                           |     |                 |

| Common-Mode Reference Voltage                                                                   | $V_{CML}$     | At CML                       | $V_{AVDD} \times 0.5$     |                           |     | V               |

| Positive Reference Voltage                                                                      | $V_{REFP}$    | At REFP                      | $V_{CML} + 0.512$         |                           |     | V               |

| Negative Reference Voltage                                                                      | $V_{REFN}$    | At REFN                      | $V_{CML} - 0.512$         |                           |     | V               |

| Differential Reference Voltage                                                                  | $V_{DIFF}$    | (Note 6)                     | $1.024$<br>$\pm 5\%$      |                           |     | V               |

| Differential Reference Temperature Coefficient                                                  | $REFTC$       |                              | $\pm 100$                 |                           |     | ppm/ $^\circ C$ |

| <b>EXTERNAL REFERENCE</b> ( $V_{REFIN} = 2.048V$ )                                              |               |                              |                           |                           |     |                 |

| REFIN Input Resistance                                                                          | $R_{IN}$      | (Note 8)                     | 5                         |                           |     | k $\Omega$      |

| REFIN Input Capacitance                                                                         | $C_{IN}$      |                              | 10                        |                           |     | pF              |

| REFIN Reference Input Voltage Range                                                             | $V_{REFIN}$   |                              | $2.048$<br>$\pm 10\%$     |                           |     | V               |

| Differential Reference Voltage Range                                                            | $V_{DIFF}$    | (Note 6)                     | $0.92 \times V_{REFIN}/2$ | $1.08 \times V_{REFIN}/2$ |     | V               |

| <b>EXTERNAL REFERENCE</b> ( $V_{REFIN} = 0$ , reference voltage applied to REFP, REFN, and CML) |               |                              |                           |                           |     |                 |

| REFP, REFN, CML Input Current                                                                   | $I_{IN}$      |                              | -200                      | 200                       |     | $\mu A$         |

| REFP, REFN, CML Input Capacitance                                                               | $C_{IN}$      |                              | 15                        |                           |     | pF              |

| Differential Reference Voltage Range                                                            | $V_{DIFF}$    | (Note 6)                     | $1.024$<br>$\pm 10\%$     |                           |     | V               |

| CML Input Voltage Range                                                                         | $V_{CML}$     |                              | $1.65$<br>$\pm 10\%$      |                           |     | V               |

| REFP Input Voltage Range                                                                        | $V_{REFP}$    |                              | $V_{CML} + V_{DIFF}/2$    |                           |     | V               |

| REFN Input Voltage Range                                                                        | $V_{REFN}$    |                              | $V_{CML} - V_{DIFF}/2$    |                           |     | V               |

| <b>DIGITAL INPUTS</b> (CLK, $\bar{CLK}$ , PD, $\bar{OE}$ )                                      |               |                              |                           |                           |     |                 |

| Input Logic High                                                                                | $V_{IH}$      |                              | $0.7 \times V_{DVDD}$     |                           |     | V               |

| Input Logic Low                                                                                 | $V_{IL}$      |                              | $0.3 \times V_{DVDD}$     |                           |     | V               |

MAX1422

# 12ビット、20MspS、3.3V、低電力ADC 内部リファレンス付

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{AVDD} = V_{DVDD} = +3.3V$ ,  $AGND = DGND = 0$ ,  $V_{IN} = \pm 1.024V$ , differential input voltage at  $-0.5dB$  FS,  $+2.048V$  internal reference,  $f_{CLK} = 20MHz$  (50% duty cycle), digital output load  $C_L \approx 10pF$ ,  $TA = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $TA = +25^\circ C$ .)

| PARAMETER                                                 | SYMBOL     | CONDITIONS                  | MIN              | TYP        | MAX   | UNITS        |

|-----------------------------------------------------------|------------|-----------------------------|------------------|------------|-------|--------------|

| Input Current                                             |            | CLK, $\overline{CLK}$       |                  | $\pm 330$  |       | $\mu A$      |

|                                                           |            | PD                          | -20              | 20         |       |              |

|                                                           |            | OE                          | -20              | 20         |       |              |

| Input Capacitance                                         |            |                             |                  | 10         |       | pF           |

| <b>DIGITAL OUTPUTS (D0–D11)</b>                           |            |                             |                  |            |       |              |

| Output Logic High                                         | $V_{OH}$   | $I_{OH} = 200\mu A$         | $V_{DVDD} - 0.5$ | $V_{DVDD}$ |       | V            |

| Output Logic Low                                          | $V_{OL}$   | $I_{OL} = -200\mu A$        | 0                | 0.5        |       | V            |

| Three-State Leakage                                       |            |                             | -10              | 10         |       | $\mu A$      |

| Three-State Capacitance                                   |            |                             |                  | 2          |       | pF           |

| <b>POWER REQUIREMENTS</b>                                 |            |                             |                  |            |       |              |

| Analog Supply Voltage                                     | $V_{AVDD}$ |                             | 3.138            | 3.3        | 3.465 | V            |

| Digital Supply Voltage                                    | $V_{DVDD}$ |                             | 2.7              | 3.3        | 3.63  | V            |

| Analog Supply Current                                     | $I_{AVDD}$ |                             | 39               | 46         |       | mA           |

| Analog Supply Current with Internal Reference in Shutdown |            | $V_{REFIN} = 0$             | 37               | 44         |       | mA           |

| Analog Shutdown Current                                   |            | $PD = DVDD$                 |                  | 20         |       | $\mu A$      |

| Digital Supply Current                                    | $I_{DVDD}$ |                             | 3                |            |       | mA           |

| Digital Shutdown Current                                  |            | $PD = DVDD$                 |                  | 20         |       | $\mu A$      |

| Power Dissipation                                         | $P_{DISS}$ | Analog power dissipation    | 137              | 152        |       | mW           |

| Power-Supply Rejection Ratio                              | PSRR       | (Note 9)                    |                  | $\pm 1$    |       | mV/V         |

| <b>TIMING CHARACTERISTICS</b>                             |            |                             |                  |            |       |              |

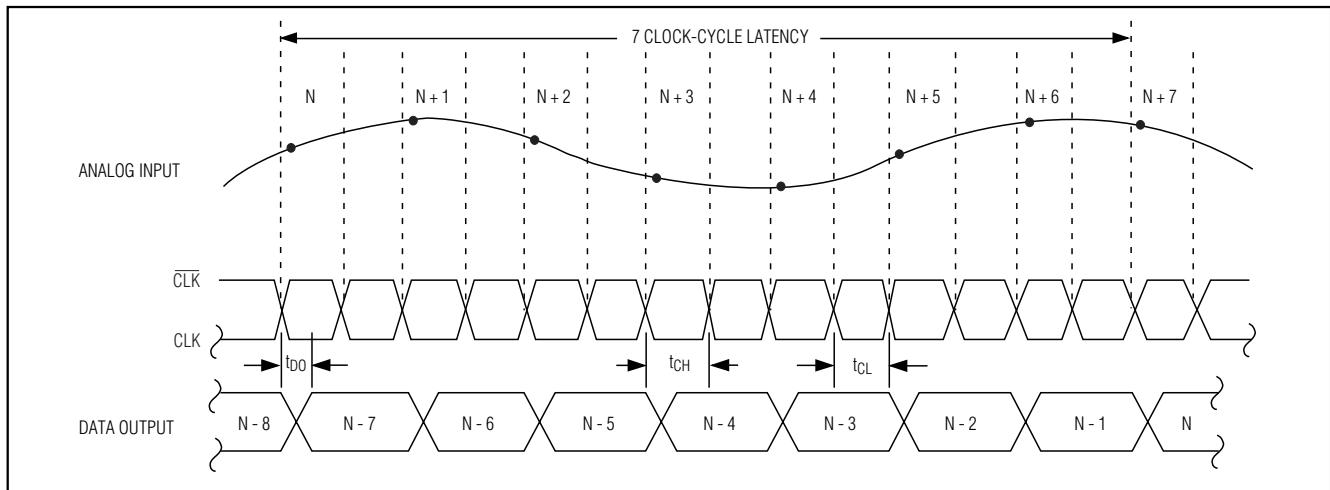

| Maximum Clock Frequency                                   | $f_{CLK}$  | Figure 6                    | 20               |            |       | MHz          |

| Clock High                                                | $t_{CH}$   | Figure 6, clock period 50ns | 25               |            |       | ns           |

| Clock Low                                                 | $t_{CL}$   | Figure 6, clock period 50ns | 25               |            |       | ns           |

| Pipeline Delay (Latency)                                  |            | Figure 6                    | 7                |            |       | Clock cycles |

| Aperture Delay                                            | $t_{AD}$   | Figure 10                   | 2                |            |       | ns           |

| Aperture Jitter                                           | $t_{AJ}$   | Figure 10                   | 2                |            |       | ps           |

| Data Output Delay                                         | $t_{OD}$   | Figure 6                    | 5                | 10         | 14    | ns           |

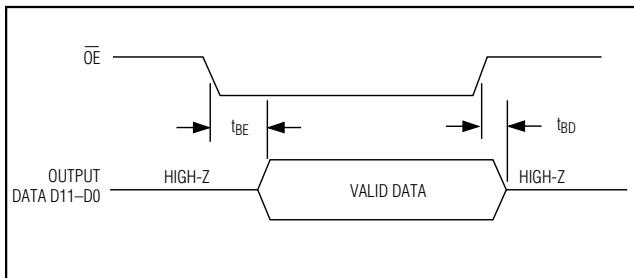

| Bus Enable Time                                           | $t_{BE}$   | Figure 5                    | 5                |            |       | ns           |

| Bus Disable Time                                          | $t_{BD}$   | Figure 5                    | 5                |            |       | ns           |

**Note 1:** Internal reference,  $REFIN$  bypassed to  $AGND$  with a combination of  $0.22\mu F$  in parallel with  $1nF$  capacitor.

**Note 2:** External  $+2.048V$  reference applied to  $REFIN$ .

**Note 3:** Internal reference disabled.  $V_{REFIN} = 0$ ,  $V_{REFP} = +2.162V$ ,  $V_{CML} = +1.65V$ , and  $V_{REFN} = +1.138V$ .

**Note 4:** IMD is measured with respect to either of the fundamental tones.

**Note 5:** Specifies the common-mode range of the differential input signal supplied to the MAX1422.

**Note 6:**  $V_{DIFF} = V_{REFP} - V_{REFN}$ .

**Note 7:** Input bandwidth is measured at a  $3dB$  level.

**Note 8:**  $REFIN$  is internally biased to  $+2.048V$  through a  $10k\Omega$  resistor.

**Note 9:** Measured as the ratio of the change in mid-scale offset voltage for a  $\pm 5\%$  change in  $V_{AVDD}$ , using the internal reference.

# 12ビット、20Msps、3.3V、低電力ADC 内部リファレンス付

MAX1422

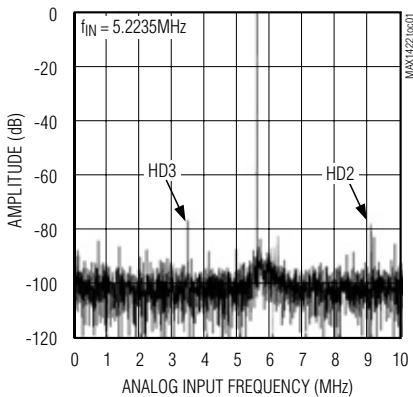

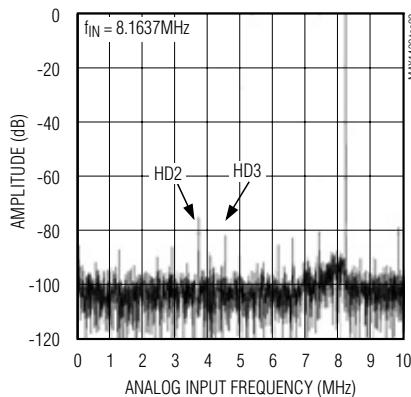

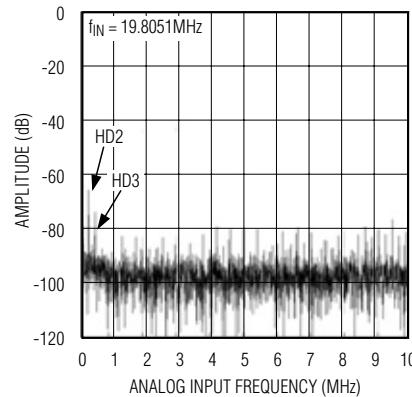

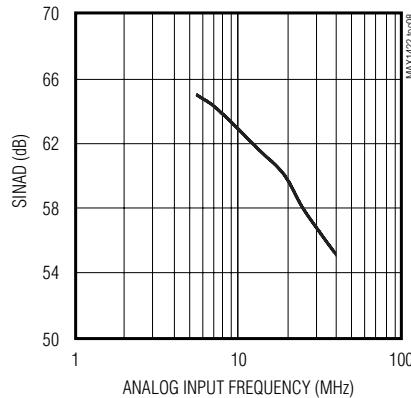

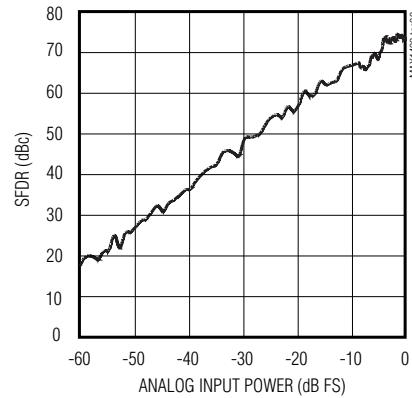

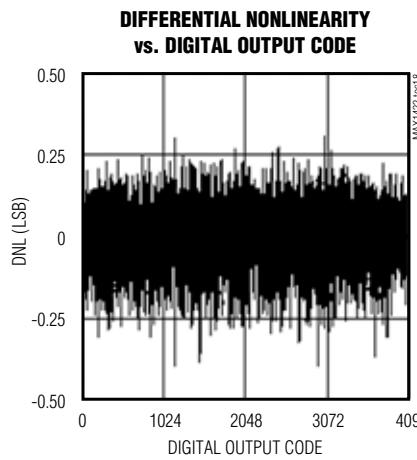

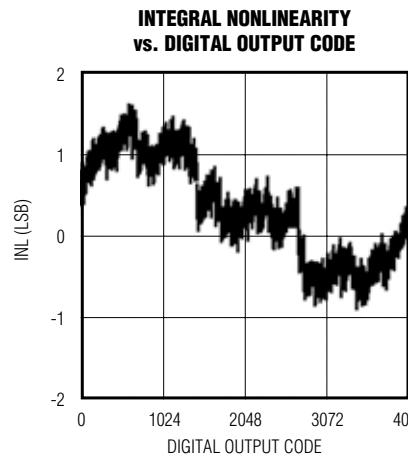

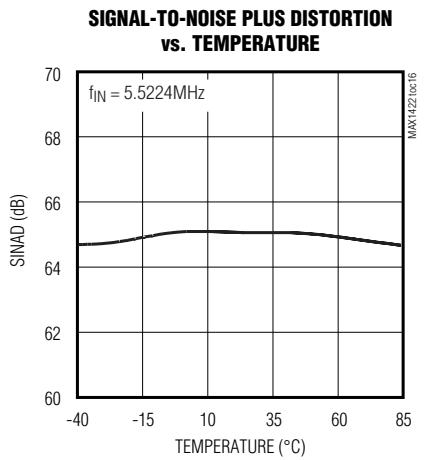

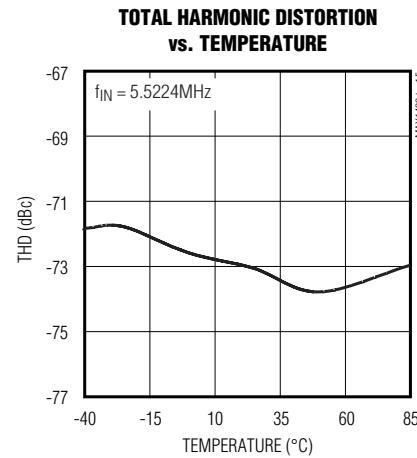

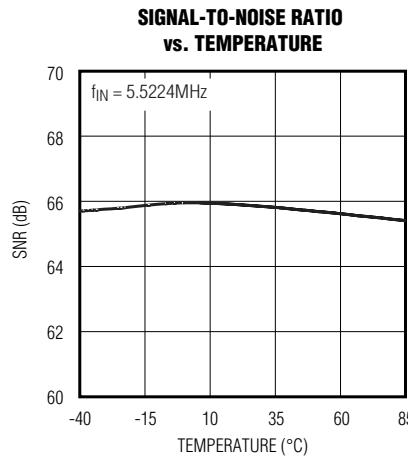

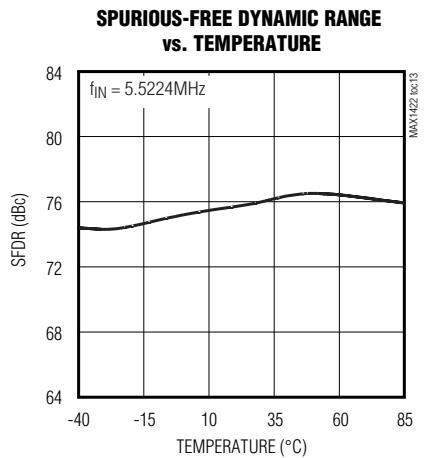

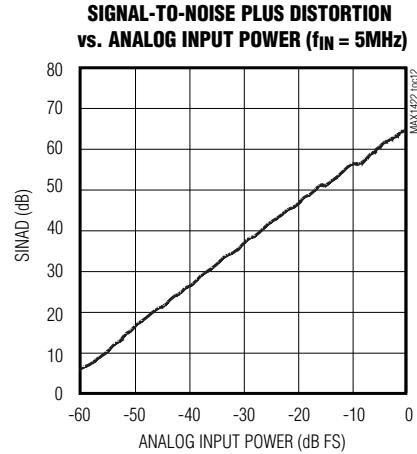

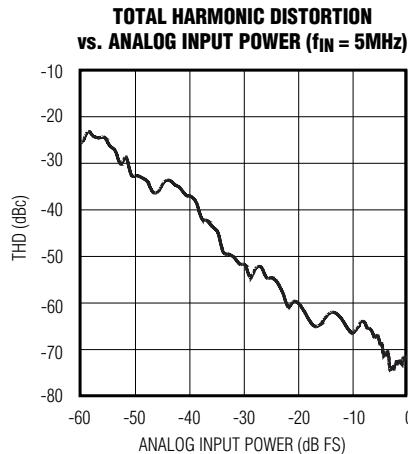

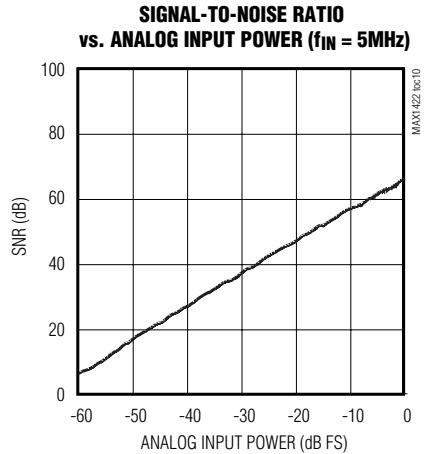

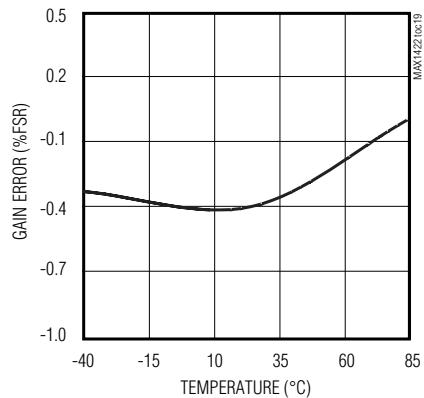

## 標準動作特性

( $V_{AVDD} = V_{DVDD} = +3.3V$ ,  $AGND = DGND = 0$ ,  $V_{IN} = \pm 1.024V$ , differential input voltage,  $f_{CLK} = 20MHz$  (50% duty cycle) digital output load  $C_L = 10pF$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

FFT PLOT (4096-POINT DATA RECORD)

FFT PLOT (4096-POINT DATA RECORD)

FFT PLOT (4096-POINT DATA RECORD)

TWO-TONE IMD PLOT

(4096-POINT DATA RECORD)

SPURIOUS-FREE DYNAMIC RANGE vs.

ANALOG INPUT FREQUENCY

SIGNAL-TO-NOISE RATIO vs.

ANALOG INPUT FREQUENCY

TOTAL HARMONIC DISTORTION vs.

ANALOG INPUT FREQUENCY

SIGNAL-TO-NOISE PLUS DISTORTION

vs. ANALOG INPUT FREQUENCY

SPURIOUS-FREE DYNAMIC RANGE

vs. ANALOG INPUT POWER ( $f_{IN} = 5MHz$ )

# 12ビット、20Msps、3.3V、低電力ADC 内部リファレンス付

## 標準動作特性(続き)

( $V_{AVDD} = V_{DVDD} = +3.3V$ ,  $AGND = DGND = 0$ ,  $V_{IN} = \pm 1.024V$ , differential input voltage,  $f_{CLK} = 20MHz$  (50% duty cycle) digital output load  $C_L = 10pF$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

# 12ビット、20Msps、3.3V、低電力ADC 内部リファレンス付

MAX1422

## 標準動作特性(続き)

( $V_{AVDD} = V_{DVDD} = +3.3V$ ,  $AGND = DGND = 0$ ,  $V_{IN} = \pm 1.024V$ , differential input voltage,  $f_{CLK} = 20MHz$  (50% duty cycle) digital output load  $C_L = 10pF$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

GAIN ERROR vs. TEMPERATURE,

EXTERNAL REFERENCE ( $V_{REFIN} = 2.048V$ )

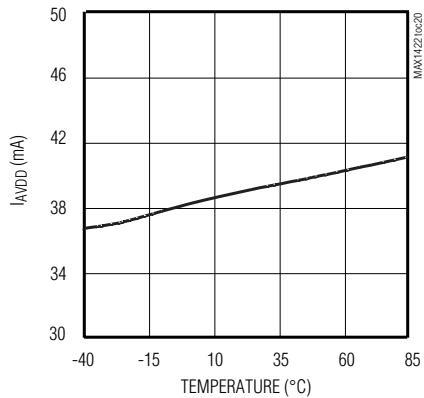

ANALOG SUPPLY CURRENT

vs. TEMPERATURE

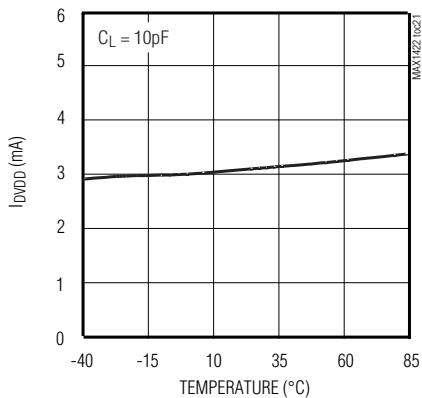

DIGITAL SUPPLY CURRENT

vs. TEMPERATURE

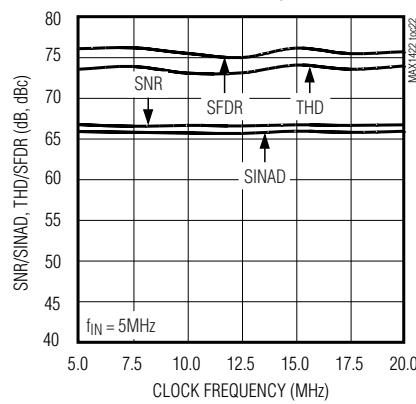

SNR/SINAD, THD/SFDR

vs. CLOCK FREQUENCY

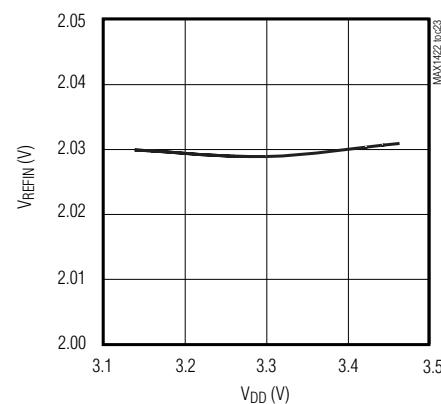

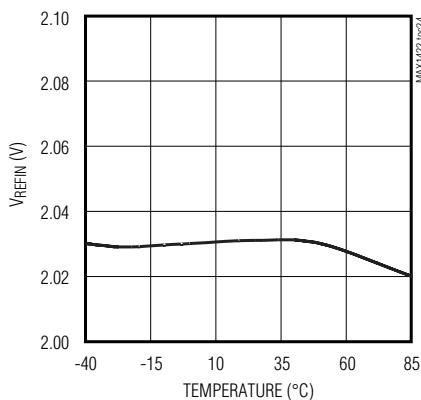

INTERNAL REFERENCE VOLTAGE

vs. ANALOG SUPPLY VOLTAGE

INTERNAL REFERENCE VOLTAGE

vs. TEMPERATURE

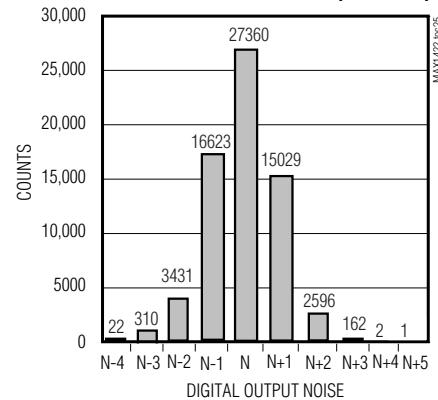

OUTPUT NOISE HISTOGRAM (DC-INPUT)

# 12ビット、20Msps、3.3V、低電力ADC

## 内部リファレンス付

### 端子説明

| 端子                                          | 名称               | 機能                                                                                                                                                   |

|---------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 4, 5, 8, 9,<br>12, 13, 16,<br>19, 41, 48 | AGND             | アナロググランド。アナログ信号用の全てのリターンパスをAGNDへ接続して下さい。                                                                                                             |

| 2, 3, 10, 11,<br>14, 15, 20,<br>42, 47      | AV <sub>DD</sub> | アナログ電源電圧。最適な性能を得るには、0.1μFと1nFのコンデンサを並列に組み合わせて近くのAGNDにバイパスして下さい。シングル10μFと1μFコンデンサの組み合わせで、AV <sub>DD</sub> とAGND間を接続して下さい。                             |

| 6                                           | INP              | 正アナログ信号入力                                                                                                                                            |

| 7                                           | INN              | 負アナログ信号入力                                                                                                                                            |

| 17                                          | CLK              | クロック周波数入力。クロック周波数入力範囲は100kHz～20MHzです。                                                                                                                |

| 18                                          | CLK              | コンプリメンタリクロック周波数入力。この入力は差動クロック入力に使われます。ADCがシングルエンドクロックで駆動される場合は、0.1μFコンデンサでCLKをAGNDへバイパスして下さい。                                                        |

| 21, 31, 32                                  | DV <sub>DD</sub> | デジタル電源電圧。最適な性能を得るには、0.1μFと1nFのコンデンサを並列に組み合わせて近接のDGNDにバイパスして下さい。シングル10μFと1μFコンデンサの組み合わせで、DV <sub>DD</sub> とDGND間を接続して下さい。                             |

| 22, 29, 30                                  | DGND             | デジタルグランド                                                                                                                                             |

| 23-28                                       | D0-D5            | デジタルデータ出力。データビットはD0からD5で、この場合D0がLSB(最下位ビット)です。                                                                                                       |

| 33-38                                       | D6-D11           | デジタルデータ出力。D6からD11で、この場合D11がMSB(最上位のビット)です。                                                                                                           |

| 39                                          | OE               | 出力イネーブル入力。OE上のロジック「1」は出力D0-D11を高インピーダンス状態にします。ロジック「0」は出力からデータビットを読み取る事を可能にします。                                                                       |

| 40                                          | PD               | シャットダウン入力。PD上のロジック「1」はADCをシャットダウンモードにします。                                                                                                            |

| 43                                          | REFIN            | 外部リファレンス入力。コンデンサ0.22μFと1nFを並列に組み合わせてAGNDへバイパスして下さい。REFINは、リファレンスレベルを調整しフルスケール誤差をキャリブレーションするために外部からバイアスすることができます。内部リファレンスをディセーブルするにはREFINをAGNDへ接続します。 |

| 44                                          | REFP             | 正リファレンスI/O。0.22μFと1nFのコンデンサを並列に組み合わせてAGNDへバイパスして下さい。内部リファレンスがディセーブルされている場合(REFIN=AGND)、REFNはV <sub>CML</sub> +V <sub>DIFF</sub> /2にバイアスして下さい。        |

| 45                                          | REFN             | 負リファレンスI/O。0.22μFと1nFのコンデンサを並列に組み合わせてAGNDへバイパスして下さい。内部リファレンスがディセーブルされている場合(REFIN=AGND)、REFNはV <sub>CML</sub> -V <sub>DIFF</sub> /2にバイアスして下さい。        |

| 46                                          | CML              | コモンモードレベル入力。0.22μFと1nFのコンデンサを並列に組み合わせてAGNDへバイパスしてください。内部リファレンスがディセーブルされている場合(REFIN=AGND)、CMLは1.65V ±10%の外部電圧を受け入れます。                                 |

### 詳細

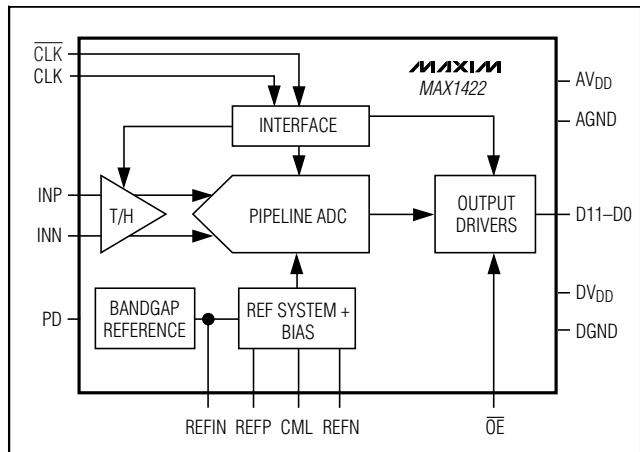

MAX1422は、12ステージ、完全差動、パイプラインアーキテクチャ(図1)によって、電力消費を最小に抑えながら、高速変換を可能にします。各サンプルは、ハーフクロックサイクル毎にパイプラインステージを通って前方に移動します。出力ラッチによる遅延も含み待ち時間は7クロックサイクルです。

2ビット(2コンバーティ)フラッシュADCは、ホールドされた入力電圧をデジタルコードに変換します。次に

続くD/Aコンバータ(DAC)は、デジタル化された結果をアナログ電圧に戻し、その後最初にホールドされていた入力信号から差し引かれます。結果的に生じた誤差信号は2倍に積算され、その積は次のパイプラインステージに渡されます。このプロセスは信号が全12ステージによって処理されるまで繰り返されます。各ステージは1ビット分解能を提供します。デジタル誤差補正是、それぞれのパイプラインステージにおいてADCコンバーティオフセットを補償し、ミッシングコードがないことを確実にします。

# 12ビット、20Msps、3.3V、低電力ADC 内部リファレンス付

MAX1422

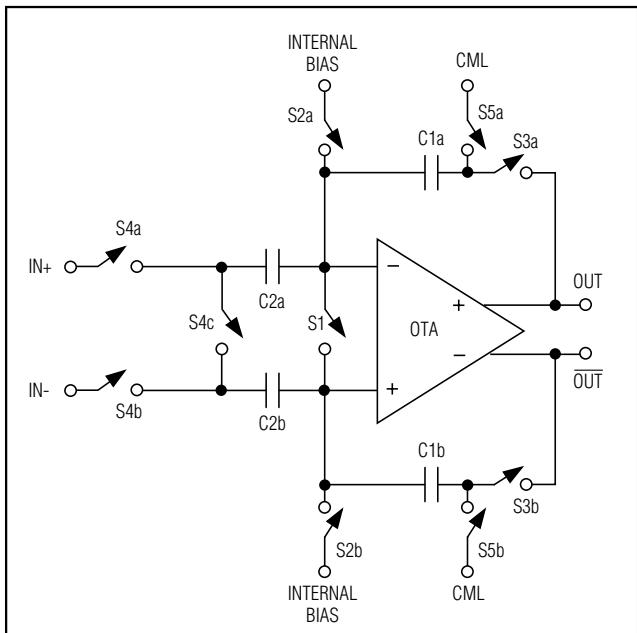

## 入力トラックアンドホールド回路

図2は両トラックアンドホールドのモードにおける入力トラックアンドホールド(T/H)回路を簡素化したファンクションダイアグラムです。トラックモードでは、スイッチS1、S2a、S2b、S4a、S4b、S5a、及びS5bが閉じています。完全差動回路は、入力信号をスイッチS4a及びS4bを介して、2つのコンデンサC2a及びC2bへサンプルします。スイッチS2a及びS2bは、トランスコンダクタンスアンプ(OTA)入力をコモンモードに設定すると同時に、S1を使ってオープンにし、入力波形をサンプルします。結果的に生じた差動電圧は、コンデンサC2a及びC2b上でホールドされます。スイッチS4a、S4bは、スイッチS3aとS3bがコンデンサC1aとC1bをアンプ出力に接続し、スイッチS4cが閉じられる前にオープンになります。OTAは、C2a及びC2bに最初にホールドされた同一の値にコンデンサC1a及びC1bを荷電するために使われます。これらの値は、次に第1ステージの量子化器に表示され、高速変化入力からパイプラインを隔離します。広域入力帯域T/Hアンプは、MAX1422が高周波数(ナイキスト以上)のアナログ入力をトラックしサンプル/ホールドすることを可能にします。INPからINNのアナログ入力は、差動又はシングルエンドのいずれかで駆動が可能です。性能の最適化には、INP及びINNのインピーダンスをマッチさせ、コモンモード電圧を中間電源( $AV_{DD}/2$ )に設定して下さい。

図1. パイプラインアーキテクチャ —

ステージブロック図

## アナログ入力及びリファレンス電圧の構成

MAX1422のフルスケール範囲は、内部で発生される $REFP(AV_{DD}/2 + V_{REFIN}/4)$ 及び $REFN(AV_{DD}/2 - V_{REFIN}/4)$ 間の電圧差によって決定されます。MAX1422のフルスケール範囲は、この調整を目的として高入力インピーダンスを提供するために備えられた $REFIN$ ピンを使って調整可能です。 $REFP$ 、 $CML(AV_{DD}/2)$ 及び $REFN$ は内部でバッファされ低インピーダンス出力です。

MAX1422はリファレンス動作に関して次の3つのモードを提供します。

- 内部リファレンスモード

- バッファされた外部リファレンスモード

- バッファされていない外部リファレンスモード

内部リファレンスモードでは内部2.048Vのバンドギャップリファレンスは有効で、 $REFIN$ 、 $REFP$ 、 $CML$ 及び $REFN$ は浮動の状態です。安定化するためには $0.22\mu F$ と $1nF$ のコンデンサを並列に組み合わせて $REFIN$ 、 $REFP$ 、 $REFN$ 及び $CML$ を $AGND$ へバイパスして下さい。

バッファされた外部リファレンスモードでは、安定した正確な電圧を $REFIN$ に加え、リファレンス電圧レベルを外部から調整することが可能です。

図2. 内部トラックアンドホールド回路

# 12ビット、20MspS、3.3V、低電力ADC 内部リファレンス付

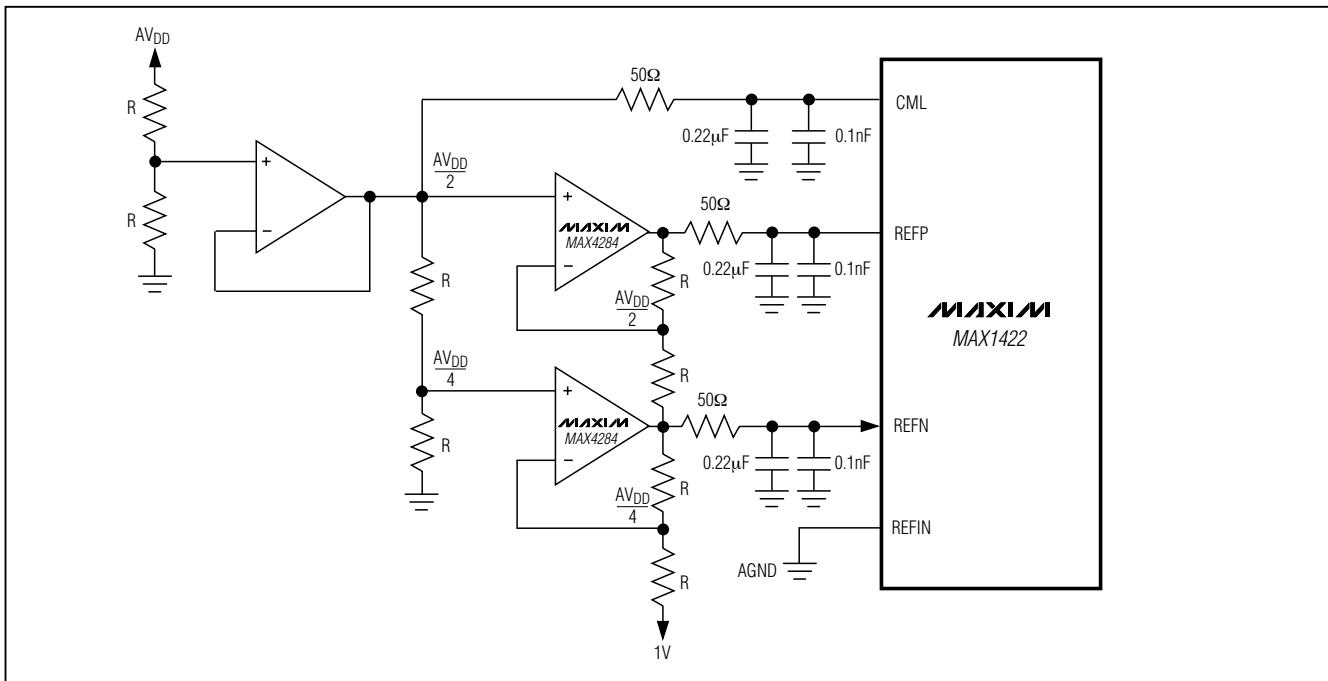

図3. バッファされていない外部リファレンス駆動 — 内部リファレンスはディセーブルされています。

バッファされていない外部リファレンスモードでは、REFINをAGNDに接続して下さい。これはREFP、CML、及びREFNの内部リファレンスバッファを停止します。バッファがシャットダウンされると、これらのノードは高インピーダンスになり、図3に示されているように、別の外部リファレンス電圧源を介して駆動することができます。

## クロック入力(CLK, $\overline{CLK}$ )

MAX1422のCLKと $\overline{CLK}$ 入力は、差動及びシングルエンド入力動作の両方を受け入れ、CMOSコンパチブルのクロック信号を許容します。CLKがシングルエンドクロック信号で駆動される場合は、0.1 $\mu$ Fコンデンサを使って $\overline{CLK}$ をAGNDへバイパスして下さい。デバイスのステージ間変換は、外部クロックの立上りと立下りエッジの反復精度に依存するので、低ジッタと高速立上り及び立下り時間(2ns以下)のクロックを使って下さい。サンプリングはクロック信号の立上りエッジで発生するので、このエッジはできる限り低いジッタとなる必要があります。大きなアーチャジッタは、以下の関係に示されるようにADCのSNR性能を制限します。

$$SNR_{dB} = 20 \times \log_{10} \left( \frac{1}{2\pi \times f_{IN} \times t_{AJ}} \right)$$

この場合 $f_{IN}$ はアナログ入力周波数を $t_{AJ}$ はアーチャジッタを示しています。

クロックジッタは高入力周波数のアプリケーションで特に重要となります。クロック入力は常にアナログ信号とみなされるべきで、アナログ又はデジタル信号ラインから離れて経路されるべきです。

MAX1422のクロック入力はAVDD/2に設定された電圧スレッショルドで動作します。クロック入力は、ハイ及びローの期間に関して「電気的特性」の中で述べられているような仕様に適合しなければなりません。

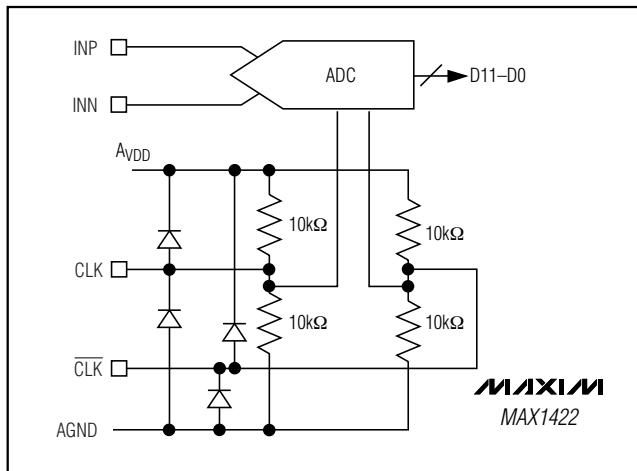

図4はクロック入力回路を簡素化したモデルです。この回路は各入力のコモンモードレベルをバイアスする2つの10k $\Omega$ 抵抗から構成されます。この回路はシステムクロック信号をMAX1422クロック入力へAC結合するのに使うことができます。

## 出カイネーブル( $\overline{OE}$ )、パワーダウン(PD) 及び出力データ(D0-D11)

$\overline{OE}$ がハイになると、デジタル出力は高インピーダンス状態になります。PDがハイで、同時に $\overline{OE}$ がローに保持されると、出力はパワーダウン前の最後のデジタル出力コードでラッチされます。全データ出力、D0(LSB)からD11(MSB)は、TTL/CMOSロジックコンパチブルです。いかなる特定のサンプルとその有効出力データ

# 12ビット、20Msps、3.3V、低電力ADC 内部リファレンス付

MAX1422

図4. クロック入力回路の簡略図

間には7つのクロックサイクル待ち時間があります。出力コードはオフセットバイナリのフォーマットです(表1)。デジタル出力D0からD11の容量負荷は、MAX1422のアナログ部分にフィードバックするような大デジタル電流を避け、性能の劣化を防ぐためにできる限り低く(10pF以下に)保持されるべきです。ADCのデジタル出力上にバッファを使用(例74LVCH16244)することで、デジタル出力を大容量負荷からさらに隔離することが可能です。MAX1422のダイナミック性能をより向上するには、ADCの近くのデジタル出力経路に100Ωの小型直列抵抗を加えて下さい。図5は出力イネーブルとデータ出力のタイミング関係を記したものです。

## システムタイミング条件

図6はクロック入力、アナログ入力、及びデータ出力間の関係を示したものです。MAX1422はCLKの立上りエッジ(CLKの立下りエッジ)のアナログ入力信号をサンプルし、出力データは7つのクロックサイクル後(待ち時間)に有効となります。

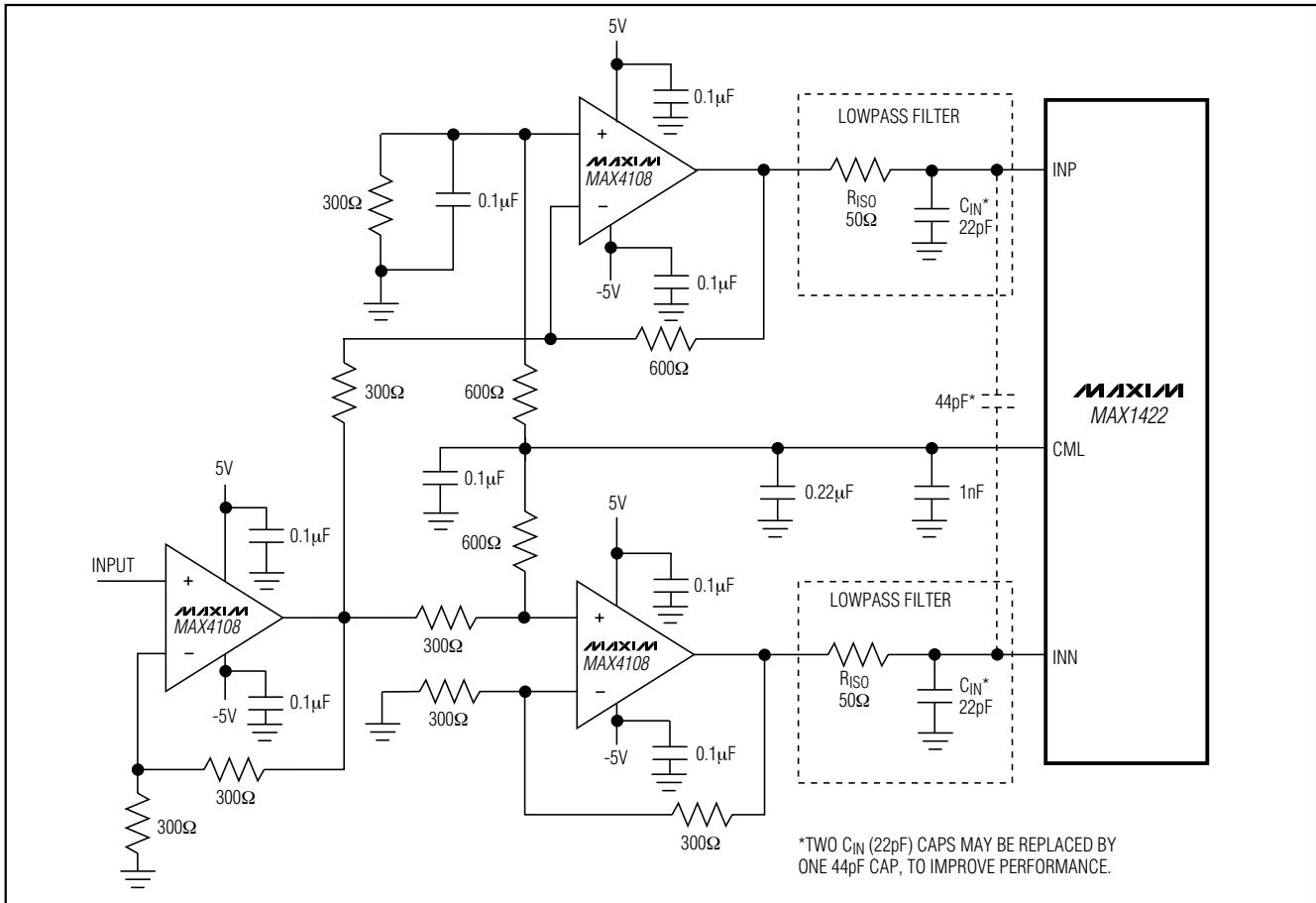

## アプリケーション情報

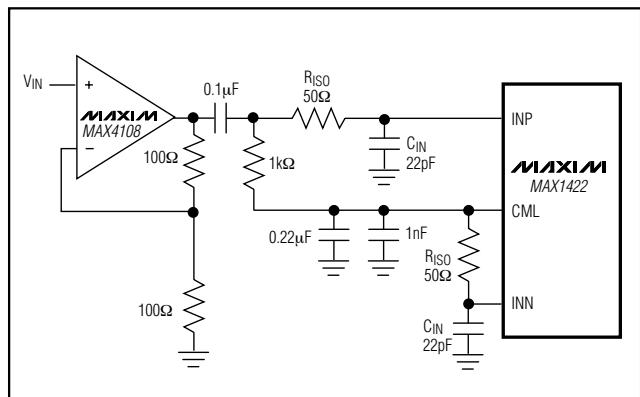

図7はシングルエンドから差動への変換を含む標準アプリケーション回路を示しています。内部リファレンスはレベルシフトの目的としてAV<sub>DD</sub>/2出力電圧を提供します。入力はバッファされ、次に電圧フォロワとインバータに分離されます。ローパスフィルタが高速オペアンプに関連する一部の広帯域ノイズを抑制します。特定なアプリケーションに適するようにフィルタ性能を

図5. 出力イネーブルタイミング

表1. 差動入力のための

MAX1422出力コード

| DIFFERENTIAL INPUT VOLTAGE*   | DIFFERENTIAL INPUT | OFFSET BINARY  |

|-------------------------------|--------------------|----------------|

| V <sub>REF</sub> × 2047/2048  | +FULL SCALE - 1LSB | 1111 1111 1111 |

| V <sub>REF</sub> × 2046/2048  | +FULL SCALE - 2LSB | 1111 1111 1110 |

| V <sub>REF</sub> × 1/2048     | +1 LSB             | 1000 0000 0001 |

| 0                             | Bipolar Zero       | 1000 0000 0000 |

| -V <sub>REF</sub> × 1/2048    | -1 LSB             | 0111 1111 1111 |

| -V <sub>REF</sub> × 2046/2048 | -FULL SCALE +1 LSB | 0000 0000 0001 |

| -V <sub>REF</sub> × 2047/2048 | -FULL SCALE        | 0000 0000 0000 |

\* $V_{REF} = V_{REFP} - V_{REFN}$

最適化するため、R<sub>ISO</sub>及びC<sub>IN</sub>値を選択することができます。図7のアプリケーションにはリンクギング及び振動を防止するために50Ωのアイソレーション抵抗(R<sub>ISO</sub>)が容量負荷の前に設置されています。22pFのC<sub>IN</sub>コンデンサが小型バイパスコンデンサとして動作します。INNからINPへC<sub>IN</sub>を接続することにより、ダイナミック性能がさらに向上します。

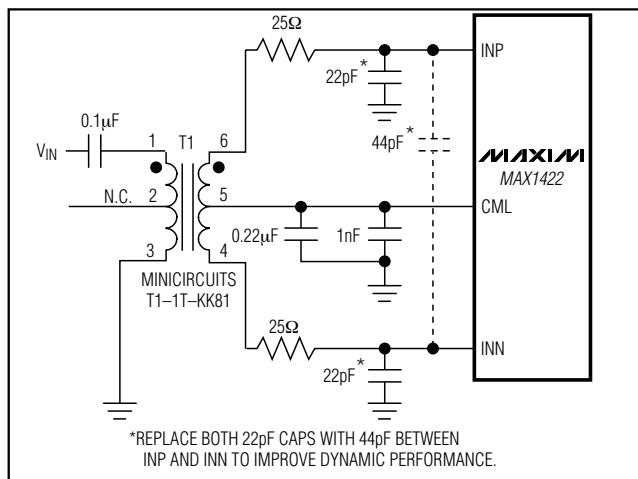

## トランスフォーマ結合の使用

RFトランスフォーマ(図8)はMAX1422の最適な特性を得るために必要な、シングルエンド信号を完全な差動信号に変換する優れた解決法を提供します。トランスフォーマの中央タップをCMLに接続することによって、入力をAV<sub>DD</sub>/2DCレベルにシフトします。1:1のトランスフォーマが示されていますが、駆動条件を低減するために1:2又は1:4の昇圧トランスフォーマを選択することも可能です。

# 12ビット、20MspS、3.3V、低電力ADC 内部リファレンス付

図6. システム及び出力タイミングダイアグラム

通常MAX1422は、特に高い入力周波数においてはシングルエンド駆動よりも、完全差動入力信号のほうが優れたSFDR及びTHDを提供します。差動入力モードでは、偶数位の高調波は低くなり、各入力はシングルエンドモードに比べて僅か半分の信号スイングを必要とするだけになります。

## シングルエンドAC結合入力信号

図9はMAX4108オペアンプを使ったAC結合のシングルエンドアプリケーションを示しています。この構成は入力信号の完全性を維持するための、高速、高帯域幅、低ノイズ、及び低歪みを提供します。

## 接地、バイパス及び 基板のレイアウト

MAX1422は、高速基板レイアウト設計の技術を必要とします。全てのバイパスコンデンサは、インダクタンスが最小となるように表面実装のデバイスを使い、デバイスにできる限り近接して、できればADCと同じ側に配置します。0.22 $\mu$ Fコンデンサ及び1nFを並列に組み合わせてREFP、REFN、REFIN、及びCMLをAGNDへバイパスします。AV<sub>DD</sub>は10 $\mu$ Fバイポーラコンデンサを1nF及び0.1 $\mu$ Fの2つのセラミックコンデンサを並列に、同様なネットワークを使ってバイパスします。同じルールに従って、デジタル電源DV<sub>DD</sub>をDGNDへバイパスして下さい。グランドとパワープレーンが分離した多層基板は信号の完全性を最高レベルにします。ADCのパッケージ上でアナロググランド(AGND)とデジタルグランド

(DGND)の物理的な位置が一致するように配置されたスプリットグランドプレーンを使用することを考慮して下さい。ノイズの多いグランド電流がアナロググランドプレーンと干渉しないように、2つのグランドプレーンを一点で接合します。代替として、グランドプレーンがノイズの多いデジタルシステムグランドプレーン(例えば、ダウンストリームの出力バッファ又はDSPグランドプレーン)から十分に隔離されている場合、全てのグランドピンが同じグランドプレーンを共有することができます。高速デジタル信号のトレースを敏感なアナログトレースから離して経路して、デジタルグランド及びパワープレーンをデジタル出力の下から外して下さい。全ての信号ラインを短くして90度回転しないようにして下さい。

## スタティックパラメーターの定義

### 積分非直線性(INL)

積分非直線性は直線からの実際の伝達関数上の偏差値です。この直線はオフセットと利得誤差が調整された後の最もフィットするベスト・ストレートラインか、又は伝達関数の最終点を結んだエンドポイントラインである可能性があります。MAX1422のためのスタティック直線性パラメータはベストストレートライン・フィット法を使って計測されます。

### 微分非直線性(DNL)

微分非直線性は実際のステップ幅と1 LSBの理想値との差です。1 LSB以下のDNL誤差規格は、ミッシングコードが無いことを保証します。

# 12ビット、20Msps、3.3V、低電力ADC 内部リファレンス付

MAX1422

図7. シングルエンドから差動への変換標準アプリケーション回路

## ダイナミックパラメータの定義

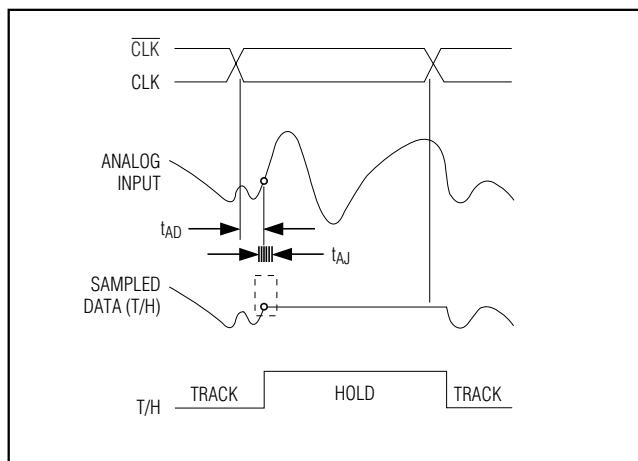

### アパーーチャジッタ

図10はアパーーチャ遅延のサンプル間の変動であるアパーーチャジッタ( $t_{AJ}$ )を示しています。

### アパーーチャ遅延

アパーーチャ遅延( $t_{AD}$ )はサンプリングクロックの立下りエッジと実際のサンプルが取得される瞬間の時間を意味します(図10)。

### 信号対ノイズ比(SNR)

デジタルサンプルから完璧に再構築された波形の場合、理論的な最高SNRはフルスケールアナログ入力(RMS値)とRMS量子化誤差(残余誤差)の比率です。理想的で理論的な最小アナログトゥディジタルノイズは量子化誤差のみに起因し、ADC分解能(Nビット)の直接な結果として生じます。

$$SNR(MAX) = (6.02 \times N + 1.76) \text{dB}$$

実際には、量子化ノイズの他にもサーマルノイズ、リファレンス電圧ノイズ、クロックジッタなどのノイズ源があります。SNRを計算するには基本波、最初の4つの高調波、及びDCオフセットを差し引いた全てのスペクトラム成分を含むRMS信号のRMSノイズに対する比率をとります。

### 信号対ノイズプラス歪み(SINAD)

SINADは基本周波数とDCオフセットを差し引いた全てのスペクトラム成分とRMS信号の比率で計算されます。

### 有効ビット数(ENOB)

ENOBは特定の入力周波数及びサンプリングレートでのADCのダイナミック性能を規定します。理想的なADC誤差は量子化ノイズのみから構成されています。ENOBは次のように計算されます：

$$ENOB = \frac{SINAD - 1.76}{6.02}$$

# 12ビット、20MspS、3.3V、低電力ADC 内部リファレンス付

## 全高調波歪み(THD)

THDは標準的に入力信号の最初の4つの高調波のRMS和と基本波そのものの比率です。これは次のように表されます：

$$\left( THD = 20 \times \log_{10} \frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + V_5^2}}{V_1} \right)$$

この場合、V1は基本波の振幅で、V2からV5は2次から5次の高調波の振幅です。

図8. AC結合にトランスフォーマを使用

## スプリアスフリーダイナミックレンジ(SFDR)

SFDRは基本波(最大信号成分)のRMS振幅と次に大きいスプリアス成分(DCオフセットを除く)のRMS値をデシベルで表した比率です。

## 相互変調歪み(IMD)

ツートーンIMDは最悪3次(又はそれ以上)の相互変調歪みの積に対するいづれかの入力トーンをデシベルで表した比率です。個別の入力トーンのレベルは-6.5dBフルスケールです。

図9. シングルエンドAC結合入力信号

図10. T/Hアバーチャタイミング

## ファンクションダイアグラム

# 12ビット、20MspS、3.3V、低電力ADC 内部リファレンス付

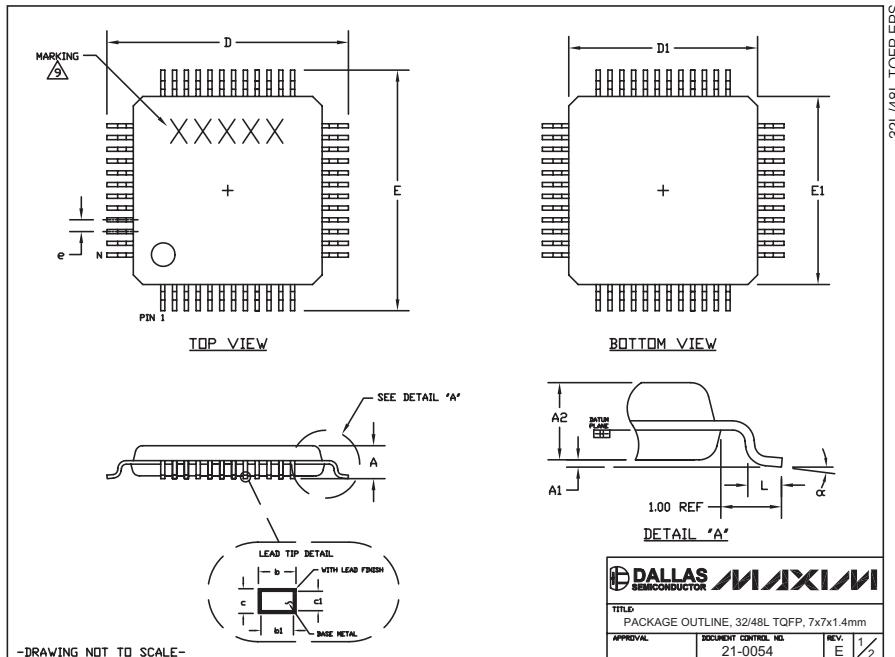

## パッケージ

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、[japan.maxim-ic.com/packages](http://japan.maxim-ic.com/packages)をご参照下さい。)

### NOTES:

- ALL DIMENSIONING AND TOLERANCING CONFORM TO ANSI Y14.5-1982.

- DATUM PLANE  $\text{E}_1$  IS LOCATED AT MOLD PARTING LINE AND COINCIDENT WITH LEAD, WHERE LEAD EXITS PLASTIC BODY AT BOTTOM OF PARTING LINE.

- DIMENSIONS  $D_1$  AND  $E_1$  DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE MOLD PROTRUSION IS 0.25 MM ON  $D_1$  AND  $E_1$  DIMENSIONS.

- THE TOP OF PACKAGE IS SMALLER THAN THE BOTTOM OF PACKAGE BY 0.05 MILLIMETERS.

- DIMENSION  $b$  DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 MM TOTAL IN EXCESS OF THE  $b$  DIMENSION AT MAXIMUM MATERIAL CONDITION.

- ALL DIMENSIONS ARE IN MILLIMETERS.

- THIS OUTLINE CONFORMS TO JEDEC PUBLICATION 95, REGISTRATION MS-026.

- LEADS SHALL BE COPLANAR WITHIN .004 INCH.

- MARKING SHOWN IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

- NUMBER OF LEADS ARE SHOWN FOR REFERENCE ONLY.

| JEDEC VARIATION |          |          |      |      |

|-----------------|----------|----------|------|------|

|                 | BBA      |          | BBC  |      |

|                 | MIN.     | MAX.     | MIN. | MAX. |

| A               | --       | 1.60     | --   | 1.60 |

| $A_1$           | 0.05     | 0.15     | 0.05 | 0.15 |

| $A_2$           | 1.35     | 1.45     | 1.35 | 1.45 |

| D               | 8.90     | 9.10     | 8.90 | 9.10 |

| $D_1$           | 6.90     | 7.10     | 6.90 | 7.10 |

| E               | 8.90     | 9.10     | 8.90 | 9.10 |

| $E_1$           | 6.90     | 7.10     | 6.90 | 7.10 |

| e               | 0.8 BSC. | 0.5 BSC. |      |      |

| L               | 0.45     | 0.75     | 0.45 | 0.75 |

| b               | 0.30     | 0.45     | 0.17 | 0.27 |

| $b_1$           | 0.30     | 0.40     | 0.17 | 0.23 |

| c               | 0.09     | 0.20     | 0.09 | 0.20 |

| $c_1$           | 0.09     | 0.16     | 0.09 | 0.16 |

| N               | 32       |          | 48   |      |

| $\alpha$        | 0°       | 7°       | 0°   | 7°   |

-DRAWING NOT TO SCALE-

| DALLAS SEMICONDUCTOR MAXIM                     |                      |      |     |

|------------------------------------------------|----------------------|------|-----|

| TITLE: PACKAGE OUTLINE, 32/48L TQFP, 7x7x1.4mm |                      |      |     |

| APPROVAL                                       | DOCUMENT CONTROL NO. | REV. | 2/2 |

|                                                | 21-0054              | E    |     |

マキシム・ジャパン株式会社

〒169-0051 東京都新宿区西早稲田3-30-16(ホリゾン1ビル)

TEL. (03)3232-6141 FAX. (03)3232-6149

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。マキシムは隨時予告なく回路及び仕様を変更する権利を留保します。

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

15

© 2004 Maxim Integrated Products, Inc. All rights reserved. MAXIM is a registered trademark of Maxim Integrated Products, Inc.

MAX1422