# 内部直列抵抗付き/なし、 3線式インターフェースフルスピードUSBトランシーバ

## 概要

MAX13342E/MAX13345Eは、USB対応トランシーバで、低電圧ASICをUSBにインターフェースするための面積と外付け部品を最低限に抑制するように設計されています。これらの製品は、フルスピード専用(12Mbps)動作のUSB 2.0規格に準拠しています。これらのトランシーバは3.3Vのレギュレータ、1.5kΩのD+プルアップ抵抗器、および±15kV ESD保護回路を内蔵し、USB I/Oポート(D+、D-)を保護します。また、MAX13345Eは、直列抵抗器も内蔵し、これらの部品をUSBコネクタにじかにワイヤ接続することができます。

これらのデバイスは最低+2.3Vのロジック電源電圧で動作し、低電圧ASIC互換です。低電力モードでは、消費電流は45μA以下に低減します。エニュメレート機能はD+プルアップ抵抗器を制御し、デバイスがプラグインされている間もこれらを論理的に切断することができます。

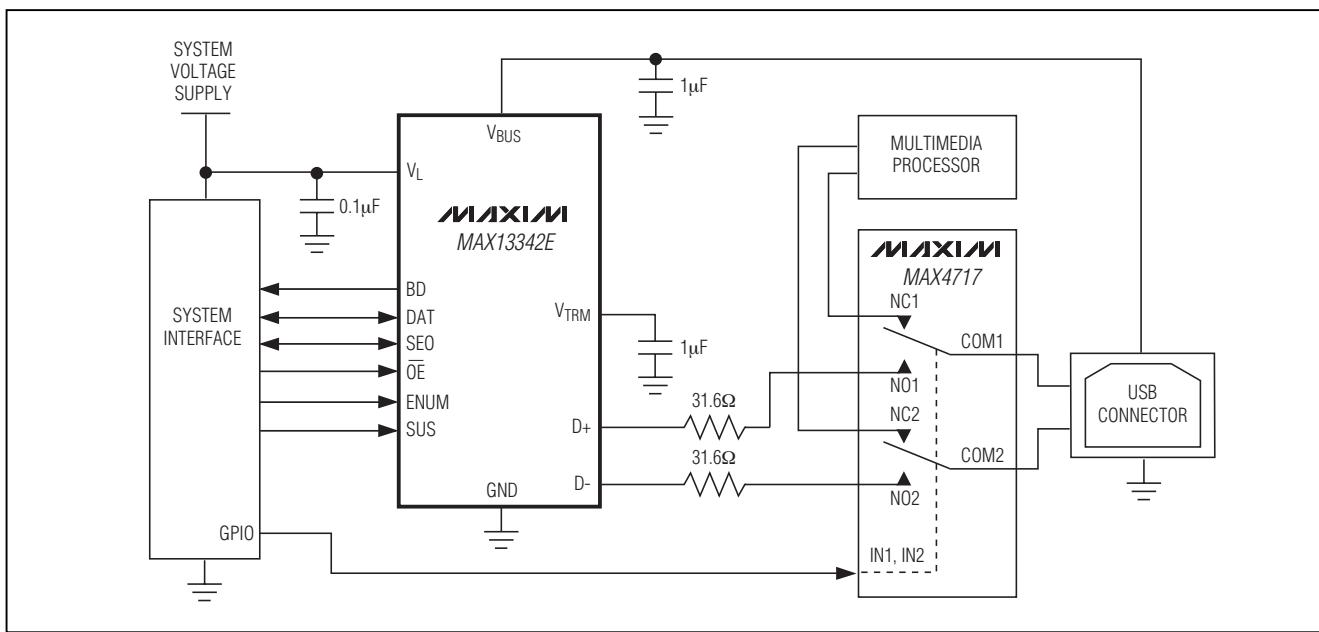

MAX13342EのD+/D-の出力インピーダンスは制御されるため、外付けスイッチを使って、2種類のUSBデバイスを単一のUSBコネクタにマルチプレックスすることができます。MAX13345Eは、USBコネクタとの直接接続用としてD+/D-に43.5Ω (max)の抵抗器を内蔵しています。

MAX13342E/MAX13345Eは、DATおよびSEOインターフェース信号を備えています。これらのトランシーバは、USB V<sub>BUS</sub>の有無を監視してイベントを通知するUSB検出機能を搭載しています。

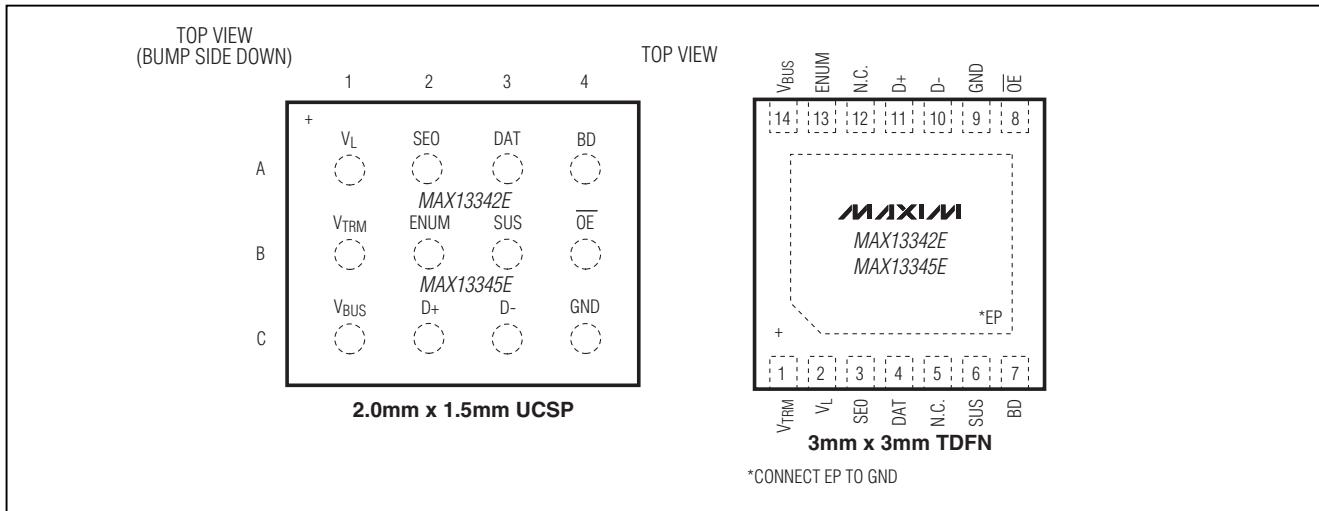

これらのデバイスは拡張温度範囲(-40°C ~ +85°C)で動作し、UCSP™ (2.0mm x 1.5mm)および14ピンTDFN (3mm x 3mm)パッケージで提供されます。

UCSP™はMaxim Integrated Products, Inc.の商標です。

## アプリケーション

- PDA

- PC周辺機器

- 携帯電話

- データクレードル

- MP3プレーヤ

ピン配置はデータシートの最後に記載されています。

## 特長

- ◆ USB 2.0 (フルスピード、12Mbps)準拠トランシーバ

- ◆ プルアップ抵抗器内蔵

- ◆ V<sub>BUS</sub>検出

- ◆ 直列抵抗器内蔵(MAX13345E)

- ◆ D+、D-、およびV<sub>BUS</sub>の±15kV (HBM) ESD保護

- ◆ エニュメレーション入力でD+プルアップ抵抗器を制御

- ◆ 3線式DAT/SEOインターフェースをサポート

- ◆ インタフェース電圧(V<sub>L</sub>) : +2.3V~+3.6V

- ◆ 電源シーケンス不要

- ◆ 低USB出力インピーダンス(MAX13342E)

## 型番

| PART           | PIN-PACKAGE                | TOP MARK | PKG CODE |

|----------------|----------------------------|----------|----------|

| MAX13342EETD+  | 14 TDFN-EP<br>(3mm x 3mm)  | ACZ      | T1433-2  |

| MAX13342EEBC+* | 12 UCSP<br>(2.0mm x 1.5mm) | ACU      | B12-3    |

| MAX13345EETD+  | 14 TDFN-EP<br>(3mm x 3mm)  | ADA      | T1433-2  |

| MAX13345EEBC+* | 12 UCSP<br>(2.0mm x 1.5mm) | ACX      | B12-3    |

\*開発中の製品。入手性についてはお問い合わせください。

+は鉛フリーパッケージを示します。

EP = エクスポートドパッド

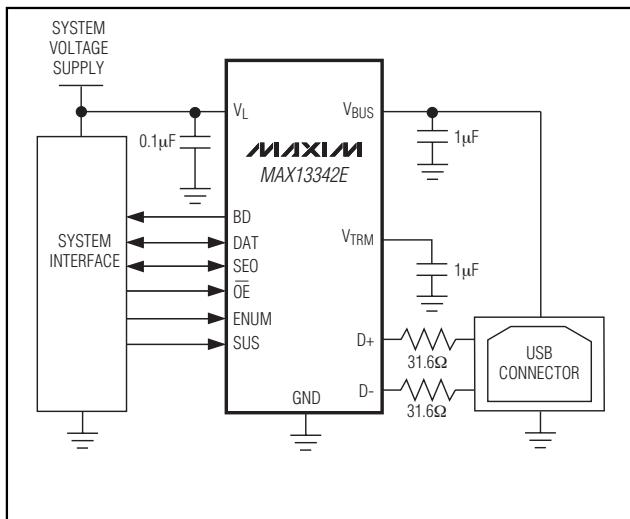

## 標準動作回路

# 内部直列抵抗付き/なし、 3線式インターフェースフルスピードUSBトランシーバ

## ABSOLUTE MAXIMUM RATINGS

(All voltages refer to GND unless otherwise noted.)

|                                                           |                                    |

|-----------------------------------------------------------|------------------------------------|

| Supply Voltage (V <sub>BUS</sub> )                        | -0.3V to +6V                       |

| System Supply Voltage (V <sub>L</sub> )                   | -0.3V to +6V                       |

| Output of Internal Regulator (V <sub>TRM</sub> )          | -0.3V to (V <sub>BUS</sub> + 0.3V) |

| Input Voltage (D+, D-)                                    | -0.3V to +6V                       |

| SUS, BD                                                   | -0.3V to (V <sub>L</sub> + 0.3V)   |

| ENUM, SEO, DAT                                            | -0.3V to (V <sub>L</sub> + 0.3V)   |

| Short-Circuit Current to V <sub>BUS</sub> or GND (D+, D-) | ±150mA                             |

| Maximum Continuous Current (all other pins)               | ±15mA                              |

|                                                       |                      |

|-------------------------------------------------------|----------------------|

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |                      |

| 14-Pin TDFN (derate 18.5mW/°C above +70°C)            | .....1482mW          |

| 4mm x 3mm UCSP                                        |                      |

| (derate 6.5mW/°C above +70°C)                         | .....518mW           |

| Operating Temperature Range                           | .....-40°C to +85°C  |

| Junction Temperature                                  | .....+150°C          |

| Storage Temperature Range                             | .....-65°C to +150°C |

| Bump Soldering                                        | .....+235°C          |

| Lead Soldering (10s)                                  | .....+300°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

(V<sub>BUS</sub> = +4.0V to +5.5V, V<sub>L</sub> = +2.3V to +3.6V, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at V<sub>BUS</sub> = +5.0V, V<sub>L</sub> = +2.5V, T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                                                              | SYMBOL                   | CONDITIONS                                                                                                            | MIN | TYP | MAX | UNITS |

|------------------------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| <b>SUPPLY INPUTS (V<sub>BUS</sub>, V<sub>TRM</sub>, V<sub>L</sub>)</b> |                          |                                                                                                                       |     |     |     |       |

| V <sub>BUS</sub> Input Range                                           | V <sub>BUS</sub>         |                                                                                                                       | 4.0 | 5.5 |     | V     |

| V <sub>L</sub> Input Range                                             | V <sub>L</sub>           |                                                                                                                       | 2.3 | 3.6 |     | V     |

| Regulated Supply-Voltage Output                                        | V <sub>TRM</sub>         |                                                                                                                       | 3.0 | 3.3 | 3.6 | V     |

| Operating V <sub>BUS</sub> Supply Current                              | I <sub>VBUS</sub>        | Full-speed transmitting/receiving at 12Mbps, C <sub>L</sub> = 50pF on D+ and D-                                       |     |     | 10  | mA    |

| Operating V <sub>L</sub> Supply Current                                | I <sub>VL</sub>          | Full-speed transmitting/receiving at 12Mbps, C <sub>L</sub> = 15pF receiver outputs, V <sub>L</sub> = 2.5V            |     | 1.5 |     | mA    |

| Full-Speed Idle and SEO Supply Current                                 | I <sub>VBUS(IDLE)</sub>  | Full-speed idle, V <sub>D+</sub> > 2.7V, V <sub>D-</sub> < 0.3V<br>SEO: V <sub>D-</sub> < 0.3V, V <sub>D+</sub> < 0.3 |     |     | 500 | µA    |

| Static V <sub>L</sub> Supply Current                                   | I <sub>VL(STATIC)</sub>  | Full-speed idle, SEO or suspend mode                                                                                  |     |     | 10  | µA    |

| Suspend Supply Current                                                 | I <sub>VBUS(SUSP)</sub>  | SEO = DAT = open;<br>SUS = OE = high                                                                                  |     | 30  | 45  | µA    |

| Disable-Mode Supply Current                                            | I <sub>VBUS(DIS)</sub>   | V <sub>L</sub> = GND or open                                                                                          |     |     | 25  | µA    |

| Sharing-Mode V <sub>L</sub> Supply Current                             | I <sub>VL(SHARING)</sub> | V <sub>BUS</sub> = GND or open, OE = low,<br>SEO = DAT = low or high, SUS = high                                      |     |     | 5   | µA    |

| D+/D- Supply Current                                                   | I <sub>D+/D-</sub>       | V <sub>BUS</sub> = GND or open                                                                                        |     |     | 20  | µA    |

| V <sub>BUS</sub> Power-Supply Detection Threshold                      | V <sub>TH_VBUS</sub>     | V <sub>L</sub> > 2.3V                                                                                                 | 0.8 | 3.6 |     | V     |

| V <sub>BUS</sub> Power-Supply Detection Hysteresis                     | V <sub>VBUSHYS</sub>     |                                                                                                                       |     | 100 |     | mV    |

| V <sub>L</sub> Power-Supply Threshold                                  | V <sub>TH_VL</sub>       |                                                                                                                       |     | 850 |     | mV    |

# 内部直列抵抗付き/なし、 3線式インターフェースフルスピードUSBトランシーバ

## ELECTRICAL CHARACTERISTICS (continued)

(V<sub>BUS</sub> = +4.0V to +5.5V, V<sub>L</sub> = +2.3V to +3.6V, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at V<sub>BUS</sub> = +5.0V, V<sub>L</sub> = +2.5V, T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                                                       | SYMBOL            | CONDITIONS                                                                              | MIN                  | TYP                  | MAX   | UNITS |

|-----------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------|----------------------|----------------------|-------|-------|

| <b>DIGITAL INPUTS AND OUTPUTS (DAT, SE0, OE, ENUM, SUS, BD)</b> |                   |                                                                                         |                      |                      |       |       |

| Input-High Voltage                                              | V <sub>IH</sub>   |                                                                                         | 0.7 × V <sub>L</sub> |                      |       | V     |

| Input-Low Voltage                                               | V <sub>IL</sub>   |                                                                                         |                      | 0.3 × V <sub>L</sub> |       | V     |

| Output-Voltage High                                             | V <sub>OH</sub>   | I <sub>SOURCE</sub> = 2mA                                                               | V <sub>L</sub> - 0.4 |                      |       | V     |

| Output-Voltage Low                                              | V <sub>OL</sub>   | I <sub>SINK</sub> = 2mA                                                                 |                      | 0.4                  |       | V     |

| Input Leakage Current                                           | I <sub>LKG</sub>  |                                                                                         | -1                   | +1                   |       | µA    |

| Input Capacitance                                               |                   | Measured from input to GND                                                              |                      | 10                   |       | pF    |

| <b>ANALOG INPUTS AND OUTPUTS (D+/D-)</b>                        |                   |                                                                                         |                      |                      |       |       |

| Differential Input Sensitivity                                  | V <sub>ID</sub>   | V <sub>D+</sub> - V <sub>D-</sub>                                                       | 200                  |                      |       | mV    |

| Differential Common-Mode Voltage Range                          | V <sub>CM</sub>   | Includes V <sub>ID</sub> range                                                          | 0.8                  | 2.5                  |       | V     |

| Single-Ended Input Voltage High                                 | V <sub>IHSE</sub> |                                                                                         | 2.0                  |                      |       | V     |

| Single-Ended Input Voltage Low                                  | V <sub>ILSE</sub> |                                                                                         |                      | 0.8                  |       | V     |

| Receiver Single-Ended Hysteresis                                | V <sub>HYS</sub>  |                                                                                         |                      | 200                  |       | mV    |

| Output-Voltage Low                                              | V <sub>OLD</sub>  | R <sub>L</sub> = 1.5kΩ from D+ or D- to 3.6V                                            |                      | 0.3                  |       | V     |

| Output-Voltage High                                             | V <sub>OH</sub>   | R <sub>L</sub> = 15kΩ from D+ or D- to GND                                              | 2.8                  | 3.6                  |       | V     |

| Off-State Leakage Current                                       |                   | Tri-state driver                                                                        | -1                   | +1                   |       | µA    |

| Transceiver Capacitance                                         | C <sub>IND</sub>  | Measured from D+ or D- to GND                                                           |                      | 20                   |       | pF    |

| Driver Output Impedance                                         | R <sub>OUT</sub>  | MAX13342E                                                                               | 4                    | 14                   |       | Ω     |

|                                                                 |                   | MAX13345E                                                                               | 28                   | 43                   |       |       |

| Internal Pullup Resistor                                        | R <sub>PU</sub>   |                                                                                         | 1.425                | 1.500                | 1.575 | kΩ    |

| Input Impedance                                                 | Z <sub>IN</sub>   | Drivers off, tri-state driver, ENUM = 0, V <sub>D+</sub> , V <sub>D-</sub> = 0 OR +3.6V | 1                    |                      |       | MΩ    |

| <b>LINEAR REGULATOR</b>                                         |                   |                                                                                         |                      |                      |       |       |

| External Capacitor                                              | C <sub>OUT</sub>  | Compensation of linear regulator                                                        | 1                    |                      |       | µF    |

| <b>ESD PROTECTION (D+, D-)</b>                                  |                   |                                                                                         |                      |                      |       |       |

| Human Body Model                                                |                   |                                                                                         |                      | ±15                  |       | kV    |

| IEC 61000-4-2 Air-Gap Discharge                                 |                   |                                                                                         |                      | ±8                   |       | kV    |

| IEC 61000-4-2 Contact Discharge                                 |                   |                                                                                         |                      | ±8                   |       | kV    |

# 内部直列抵抗付き/なし、 3線式インターフェースフルスピードUSBトランシーバ

## TIMING CHARACTERISTICS

( $V_{BUS} = +4V$  to  $+5.5V$ ,  $V_L = +2.3V$  to  $+3.6V$ ,  $ENUM = V_L$ ,  $TA = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $V_{BUS} = +5V$ ,  $V_L = +2.5V$ ,  $TA = +25^\circ C$ .) (Note 1)

| PARAMETER                                      | SYMBOL                   | CONDITIONS                                                                                                |              | MIN | TYP | MAX | UNITS |

|------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------|--------------|-----|-----|-----|-------|

| <b>TRANSMITTER ( <math>C_L = 50pF</math> )</b> |                          |                                                                                                           |              |     |     |     |       |

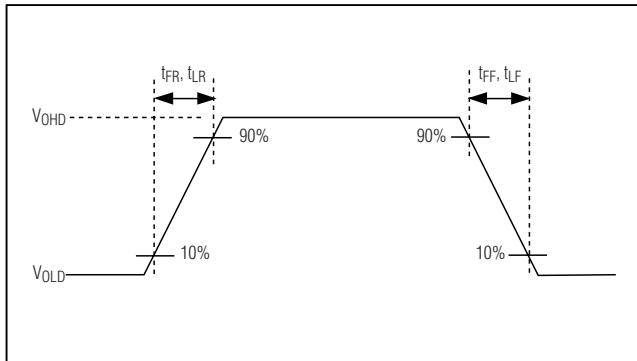

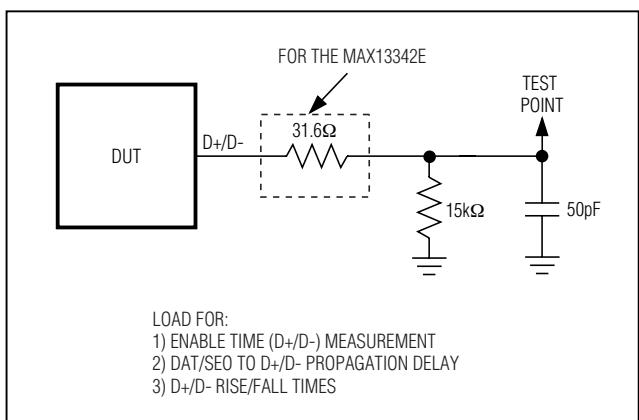

| Rise Time                                      | $t_{PR}$                 | 10% to 90% of $ V_{OHD}-V_{OLD} $ with an external $31.6\Omega$ series resistor (MAX13342E), Figures 3, 8 |              | 4   | 20  |     | ns    |

| Fall Time                                      | $t_{PF}$                 | 10% to 90% of $ V_{OHD}-V_{OLD} $ with an external $31.6\Omega$ series resistor (MAX13342E), Figures 3, 8 |              | 4   | 20  |     | ns    |

| Rise-and-Fall Time Matching (Note 1)           | $t_{LR}/t_{LF}$          | Figures 3, 8                                                                                              |              | 90  | 110 |     | %     |

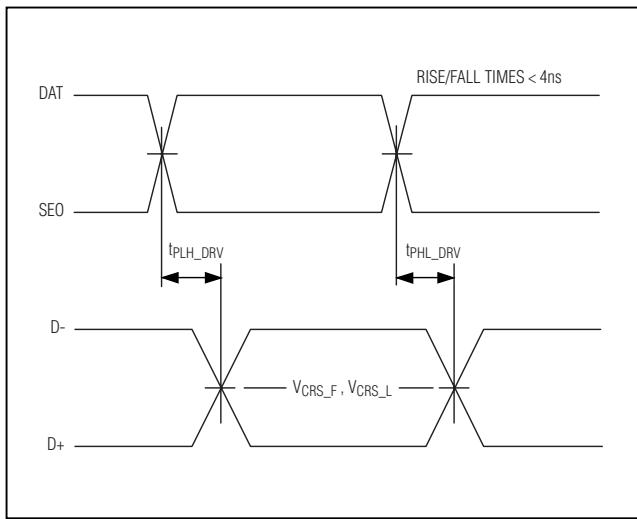

| Output Signal Crossover (Note 2)               | $V_{CRS\_L}, V_{CRS\_F}$ | Figure 4                                                                                                  |              | 1.3 | 2   |     | V     |

| Driver Propagation Delay                       | $t_{PLH\_DRV}$           | Low-to-high transition, Figures 4, 8                                                                      | $V_L > 2.3V$ |     | 20  |     | ns    |

|                                                | $t_{PHL\_DRV}$           | High-to-low transition, Figures 4, 8                                                                      | $V_L > 2.3V$ |     | 20  |     |       |

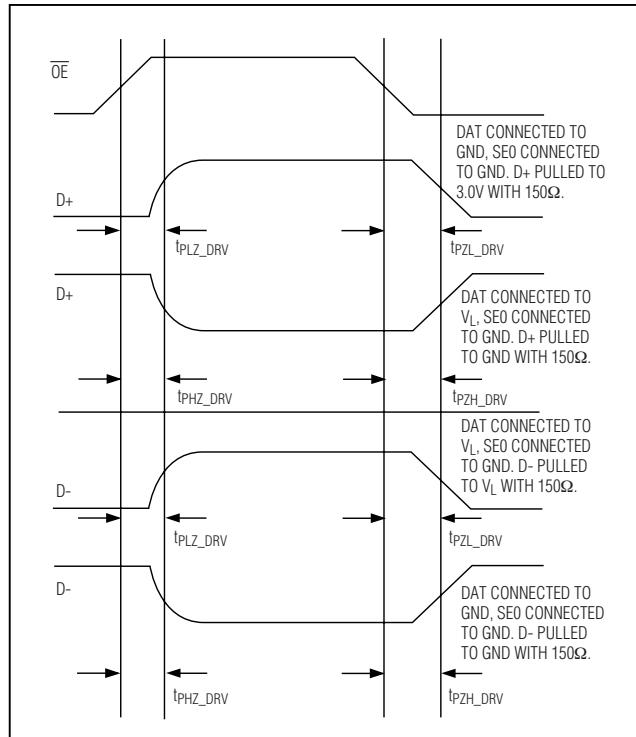

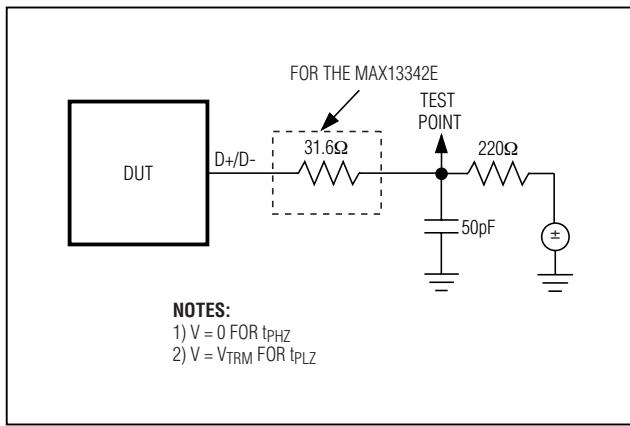

| Driver-Enabled Delay Time                      | $t_{PZH\_DRV}$           | Off-to-high transition, Figures 5, 8                                                                      | $V_L > 2.3V$ |     | 18  |     | ns    |

|                                                | $t_{PZL\_DRV}$           | Off-to-low transition, Figures 5, 8                                                                       | $V_L > 2.3V$ |     | 18  |     |       |

| Driver Disable Delay                           | $t_{PHZ\_DRV}$           | High-to-off transition, Figure 5, 9                                                                       | $V_L > 2.3V$ |     | 18  |     | ns    |

|                                                | $t_{PLZ\_DRV}$           | Low-to-off transition, Figures 5, 9                                                                       | $V_L > 2.3V$ |     | 18  |     |       |

| <b>RECEIVER ( <math>C_L = 15pF</math> )</b>    |                          |                                                                                                           |              |     |     |     |       |

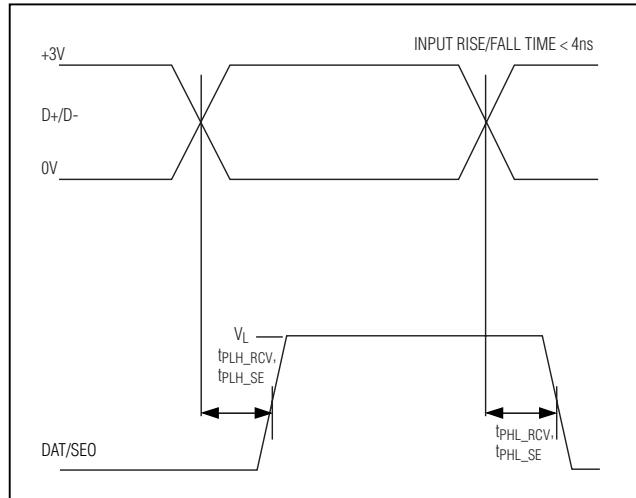

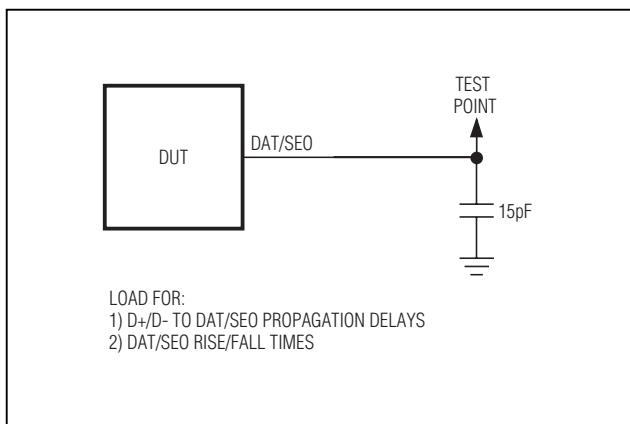

| Differential Receiver Propagation Delay        | $t_{PLH\_RCV}$           | Low-to-high transition, Figures 6, 10                                                                     | $V_L > 2.3V$ |     | 20  |     | ns    |

|                                                | $t_{PHL\_RCV}$           | High-to-low transition, Figures 6, 10                                                                     | $V_L > 2.3V$ |     | 20  |     |       |

| Single-Ended Receiver Propagation Delay        | $t_{PLH\_SE}$            | Low-to-high transition, Figures 6, 10                                                                     |              |     | 18  |     | ns    |

|                                                | $t_{PHL\_SE}$            | High-to-low transition, Figures 6, 10                                                                     |              |     | 18  |     |       |

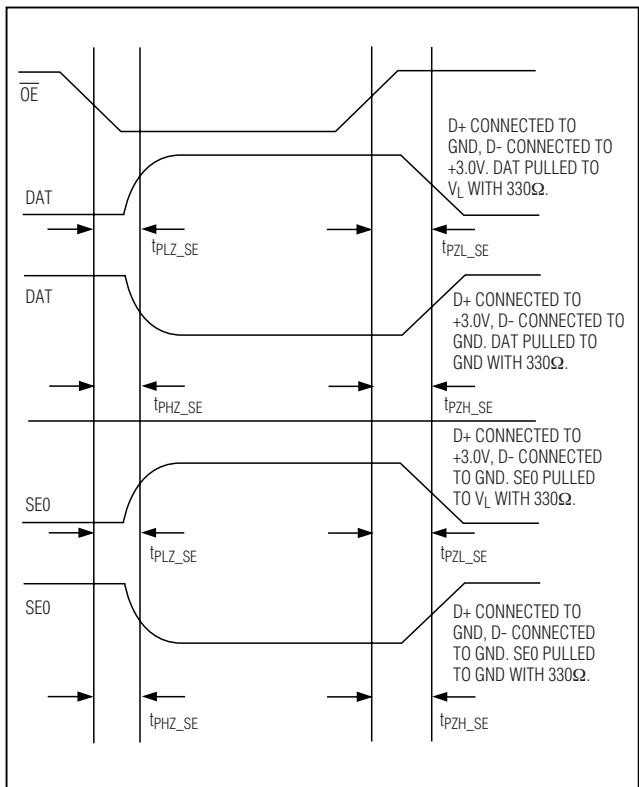

| Single-Ended Receiver Disable Delay            | $t_{PHZ\_SE}$            | High-to-off transition, Figure 7                                                                          | $V_L > 2.3V$ |     | 20  |     | ns    |

|                                                | $t_{PLZ\_SE}$            | Low-to-off transition, Figure 7                                                                           | $V_L > 2.3V$ |     | 20  |     |       |

| Single-Ended Receiver Enable Delay             | $t_{PZH\_SE}$            | Off-to-high transition, Figure 7                                                                          | $V_L > 2.3V$ |     | 22  |     | ns    |

|                                                | $t_{PZL\_SE}$            | Off-to-low transition, Figure 7                                                                           | $V_L > 2.3V$ |     | 22  |     |       |

**Note 1:** Parameters are 100% production tested at  $+25^\circ C$ , unless otherwise noted. Limits over temperature are guaranteed by design.

# 内部直列抵抗付き/なし、 3線式インターフェースフルスピードUSBトランシーバ

**MAX13342E/MAX13345E**

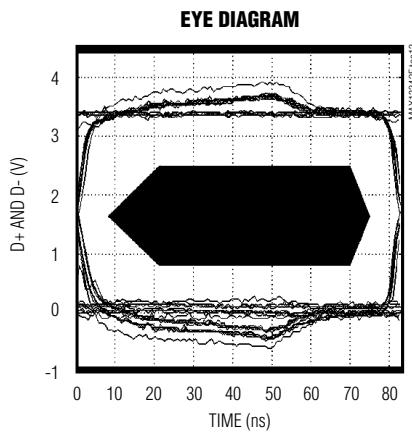

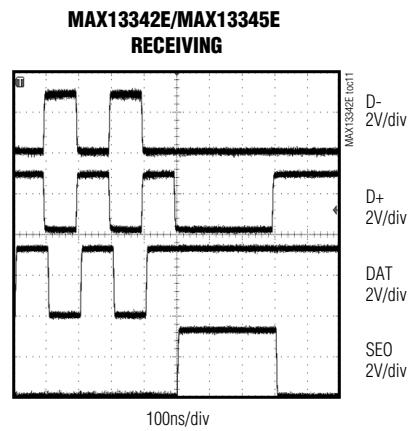

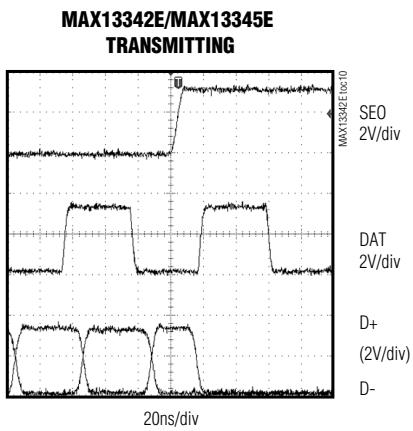

## 標準動作特性

( $V_{BUS} = +5V$ ,  $V_L = +3.3V$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

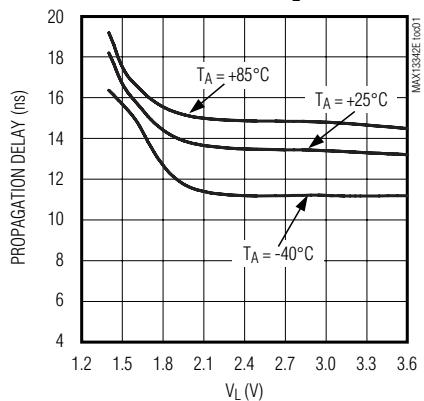

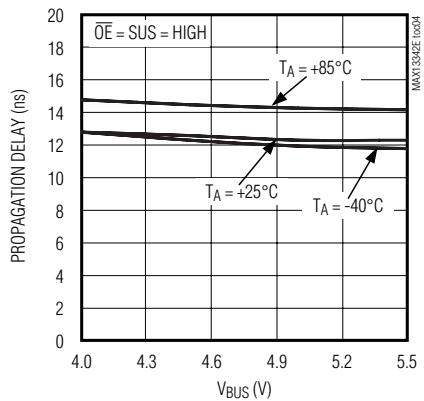

**DIFFERENTIAL RECEIVER PROPAGATION

DELAY vs.  $V_L$**

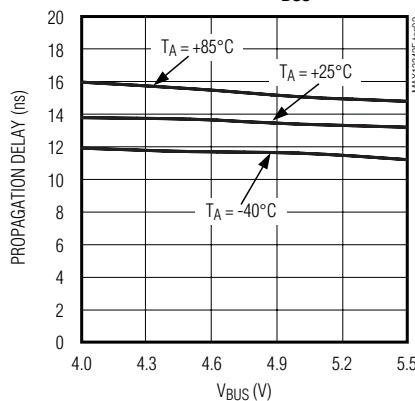

**DIFFERENTIAL RECEIVER PROPAGATION

DELAY vs.  $V_{BUS}$**

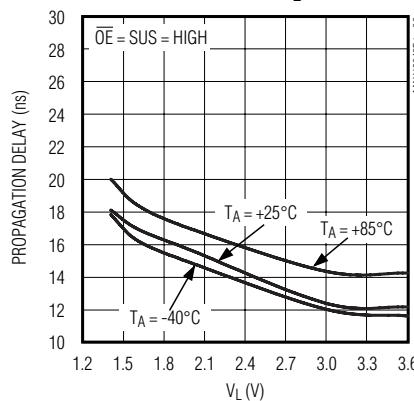

**SINGLE-ENDED RECEIVER PROPAGATION

DELAY vs.  $V_L$**

**SINGLE-ENDED RECEIVER PROPAGATION

DELAY vs.  $V_{BUS}$**

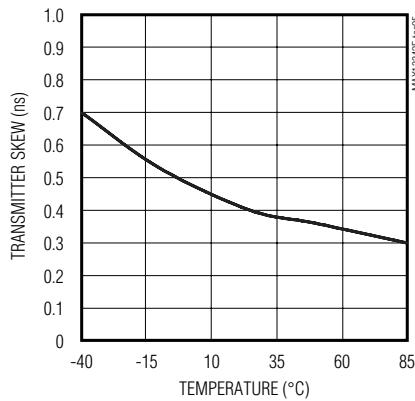

**TRANSMITTER SKEW

vs. TEMPERATURE**

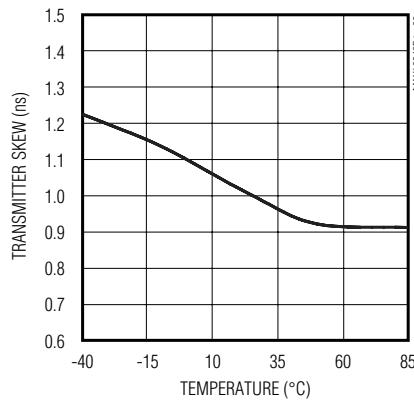

**RECEIVER SKEW

vs. TEMPERATURE**

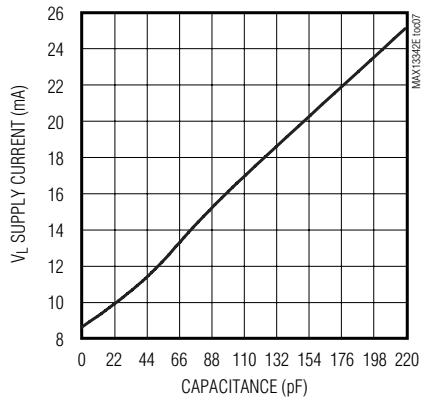

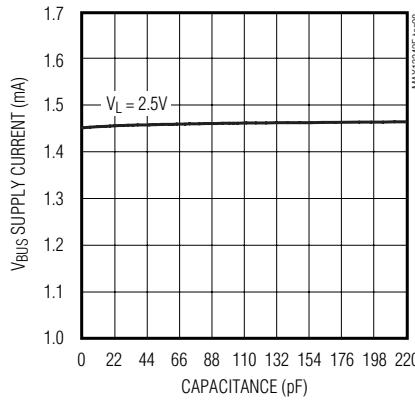

**$V_L$  SUPPLY CURRENT

vs. D+/D- CAPACITANCE**

**$V_{BUS}$  SUPPLY CURRENT vs. D+/D- CAPACITANCE**

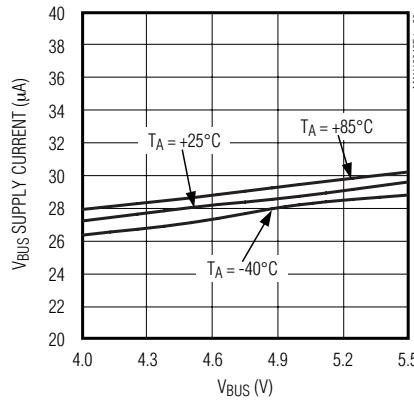

**$V_{BUS}$  SUSPEND CURRENT

vs.  $V_{BUS}$  SUPPLY VOLTAGE**

# 内部直列抵抗付き/なし、 3線式インターフェースフルスピードUSBトランシーバ

## 標準動作特性(続き)

(VBUS = +5V, VL = +3.3V, TA = +25°C, unless otherwise noted.)

# 内部直列抵抗付き/なし、 3線式インターフェースフルスピードUSBトランシーバ

## 端子説明

| 端子    |      | 名称               | 機能                                                                                                                                                                                                                                                                                                                 |

|-------|------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDFN  | UCSP |                  |                                                                                                                                                                                                                                                                                                                    |

| 1     | B1   | V <sub>TRM</sub> | 安定化出力電圧。V <sub>TRM</sub> は、V <sub>BUS</sub> から得られる3.3V出力を供給します。V <sub>TRM</sub> をセラミックまたはプラスチックフィルムタイプなどの1μF (min)の低ESRコンデンサでGNDにバイパスしてください。V <sub>TRM</sub> は、内部回路と内蔵D+ブルアップ抵抗器に電源を供給します。V <sub>TRM</sub> を外部回路への給電に使用しないでください。これらのUSBトランシーバは、V <sub>BUS</sub> とV <sub>TRM</sub> の両方に接続された外部の安定化3.3V電源からの給電が可能です。 |

| 2     | A1   | V <sub>L</sub>   | システム側電源入力。V <sub>L</sub> をシステムのロジックレベル電源に接続してください。V <sub>L</sub> を0.1μF (min)の低ESRセラミックコンデンサでGNDにバイパスしてください。                                                                                                                                                                                                       |

| 3     | A2   | SEO              | ロジック側データ入力/出力。SEOは、 $\overline{OE}$ がローのとき入力として動作し、 $\overline{OE}$ がハイのとき出力として動作します。入力としてのSEOがアクティブハイのとき、D+とD-はともにローに駆動されます。D+とD-がともにローのとき、出力としてのSEOはアクティブハイになります(表3と4参照)。                                                                                                                                        |

| 4     | A3   | DAT              | ロジック側データ入力/出力。 $\overline{OE}$ がローのとき、DATはD+/D-のデータ入力として動作します。 $\overline{OE}$ がハイのとき、DATはD+/D-のデータに関する差動レシーバ出力として動作します(表3と4参照)。                                                                                                                                                                                   |

| 5, 12 | —    | N.C.             | 接続なし。N.C.を無接続のままにしてください。N.C.は内部で接続されていません。                                                                                                                                                                                                                                                                         |

| 6     | B3   | SUS              | サスPEND入力。通常のトランシーバ動作の場合はSUSをローに駆動してください。低電力状態の場合はSUSをハイに駆動してください。                                                                                                                                                                                                                                                  |

| 7     | A4   | BD               | USB検出器出力。BDがハイの状態はV <sub>BUS</sub> が存在することを示します。                                                                                                                                                                                                                                                                   |

| 8     | B4   | $\overline{OE}$  | 出力イネーブル。USBモードでは、 $\overline{OE}$ はUSBトランスマッタ出力(D+/D-)とインターフェース信号(DAT、SEO)を制御します。D+/D-を入力として動作させ、ロジックインターフェース信号を出力として動作させるためには、 $\overline{OE}$ をハイに駆動してください。D+/D-を出力として動作させ、ロジックインターフェース信号を入力として動作させるためには、 $\overline{OE}$ をローに駆動してください。                                                                          |

| 9     | C4   | GND              | グランド                                                                                                                                                                                                                                                                                                               |

| 10    | C3   | D-               | USB差動データの負の入力/出力。D-は、じかに(MAX13345E)、もしくは直列抵抗器を通じて(MAX13342E) USBコネクタに結線接続されています。D-は、 $\overline{OE}$ がハイのとき入力として動作し、 $\overline{OE}$ がローのとき出力として動作します。                                                                                                                                                             |

| 11    | C2   | D+               | 正のUSB差動データ入力/出力。D+は、じかに(MAX13345E)、もしくは直列抵抗器を通じて(MAX13342E) USBコネクタに結線接続されています。D+は、 $\overline{OE}$ がハイのとき入力として動作し、 $\overline{OE}$ がローのとき出力として動作します。                                                                                                                                                              |

| 13    | B2   | ENUM             | エニュメレーション。内蔵の1.5kΩの抵抗器をD+からV <sub>TRM</sub> に接続する場合は、ENUMをハイに駆動してください。内蔵の1.5kΩの抵抗器を切断する場合は、ENUMをローに駆動してください。                                                                                                                                                                                                       |

| 14    | C1   | V <sub>BUS</sub> | USB側電源入力。V <sub>BUS</sub> を入力USB電源に接続してください。V <sub>BUS</sub> を1μFのセラミックコンデンサでGNDにバイパスしてください。                                                                                                                                                                                                                       |

| EP    | —    | EP               | エクスポートドパッド。EPをGNDに接続してください。                                                                                                                                                                                                                                                                                        |

**MAX13342E/MAX13345E**

# 内部直列抵抗付き/なし、 3線式インターフェースフルスピードUSBトランシーバ

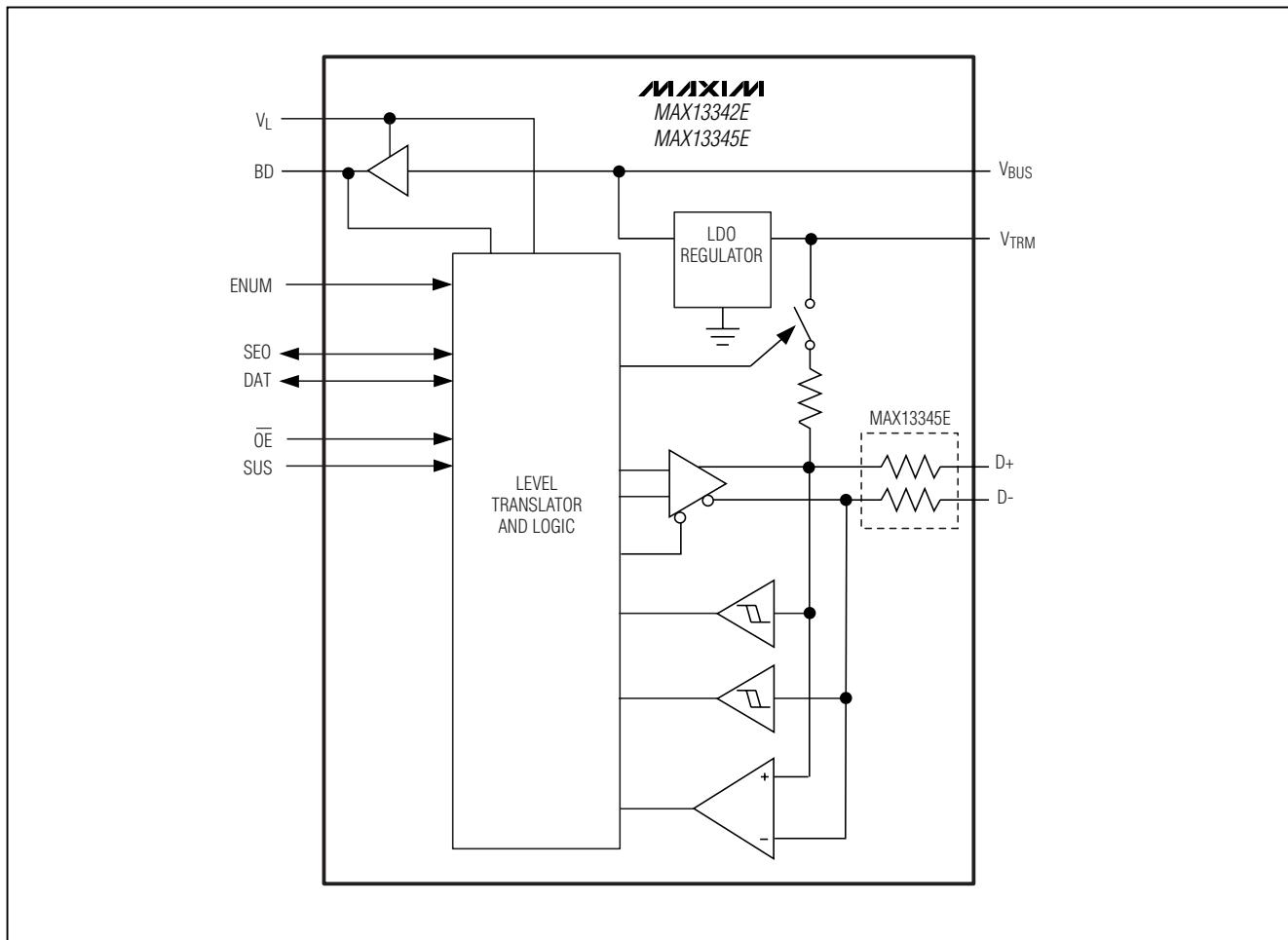

図1. MAX13342E/MAX13345Eのファンクションダイアグラム

## 詳細

MAX13342E/MAX13345Eは、USB対応トランシーバで、低電圧ASICをUSBにインターフェースするために面積と外付け部品を最低限に抑制するように設計されています。これらのデバイスは、フルスピード用(12Mbps)動作のUSB 2.0規格に準拠しています。これらのトランシーバは3.3Vのレギュレータ、1.5kΩのD+プルアップ抵抗器、および±15kV (HBM) ESD保護回路を内蔵し、D+とD-を保護します。図1はMAX13342E/MAX13345Eのファンクションダイアグラムです。

MAX13342EのD+/D-の出力インピーダンスは制御されるため、外付けスイッチを使って、2種類のUSBデバイスを单一のUSBコネクタにマルチプレックスすることができます。

MAX13345Eは、USBコネクタとの直接接続が可能な直列抵抗器をD+/D-に内蔵しています。低電力モードでは、消費電流は45µA以下に低減します。イニュメレート機能が内蔵D+プルアップ抵抗器の接続を制御します。

MAX13342E/MAX13345Eは、DATおよびSEOインターフェース信号を備えており、3線式USBトランシーバインターフェースに対応しています。3線式インターフェースは、一般にUSB On-the-Goトランシーバと関連していますが、MAX13342E/MAX13345EはUSB周辺機器のみをサポートしています。これらのトランシーバは、USB V<sub>BUS</sub>の有無を監視してイベントを通知するUSB V<sub>BUS</sub>検出機能を搭載しています。

# 内部直列抵抗付き/なし、 3線式インターフェースフルスピードUSBトランシーバ

## インターフェース

MAX13342E/MAX13345Eの制御信号は、USB D+/D-ラインの制御に使用されます。V<sub>L</sub>は、ロジック側のインターフェースに給電して、これらの信号入力と出力のスレッショルドを設定します。MAX13342EとMAX13345Eの制御信号は、DAT、SEO、およびOEです。

## 電源の構成

### 通常動作モード

各種電源の構成については表1をご覧ください。

V<sub>BUS</sub>電源はUSBトランシーバに給電します。V<sub>BUS</sub>を+4V～+5.5Vの電源に接続してください。V<sub>L</sub>を+2.3V～+3.6Vの電源に接続してください。V<sub>BUS</sub>は通常USBコネクタにじかに接続されます。内蔵レギュレータは、内蔵D+プルアップ抵抗器への給電のほかに、3.3Vを内部回路に供給し、3.3Vの安定化電圧をV<sub>TRM</sub>に出力します。MAX13342EとMAX13345Eへの給電は、V<sub>BUS</sub>とV<sub>TRM</sub>の両方を3.3Vの外部レギュレータに接続することによって行います。

### 低電力モード

低電力モードでは、SUSをハイにすることによってトランシーバを動作させてください。低電力モードでは、USB

差動レシーバがオフになり、V<sub>BUS</sub>の消費電流が45μA以下になります。シングルエンドのD+およびD-レシーバは、SUSをハイに駆動したときもアクティブのままです。

## 共有モード

V<sub>L</sub>をシステム電源に接続し、V<sub>BUS</sub>（または、V<sub>BUS</sub>とV<sub>TRM</sub>）を無接続のままにするか、またはGNDに接続したままにしてください。D+とD-はトライステートであるため、他の回路がUSBのD+およびD-ラインを共有することができます。V<sub>L</sub>は消費電流が5μA以下です。トランシーバを共有モードで動作させるときは、SUS入力が無視され、インターフェース信号(SEO、DAT)がハイインピーダンスになります。

## ディセーブルモード

V<sub>BUS</sub>をシステム電源に接続し、V<sub>L</sub>を無接続のままにするか、またはグランドに接続してください。ディセーブルモードでは、D+とD-はトライステートで、V<sub>BUS</sub>および/またはV<sub>TRM</sub>（または、V<sub>BUS</sub>とV<sub>TRM</sub>）は消費電流が25μA以下です。トランシーバをディセーブルモードで動作させるときは、OE、SUS、およびインターフェース制御信号への入力が無視されます（表2参照）。

**表1. 電源の構成**

| V <sub>BUS</sub> (V) | V <sub>TRM</sub> (V) | V <sub>L</sub> (V) | CONFIGURATION | NOTES   |

|----------------------|----------------------|--------------------|---------------|---------|

| +4.0 to +5.5         | +3.0 to +3.6 output  | +2.3 to +3.6       | Normal mode   | —       |

| +4.0 to +5.5         | +3.0 to +3.6 output  | GND or floating    | Disable mode  | Table 2 |

| GND or Floating      | High Z               | +2.3 to +3.6       | Sharing mode  | Table 2 |

**表2. ディセーブルモードと共有モードの接続**

| INPUTS/OUTPUTS                      | DISABLE MODE                 | SHARING MODE                 |

|-------------------------------------|------------------------------|------------------------------|

| V <sub>BUS</sub> / V <sub>TRM</sub> | 4V to 5.5V                   | Floating or connected to GND |

| V <sub>L</sub>                      | Floating or connected to GND | 2.3V to 3.6V input           |

| D+ and D-                           | High impedance               | High impedance               |

| DAT, SEO                            | High impedance               | High impedance               |

| SUS                                 | High impedance               | High impedance               |

| BD                                  | Low                          | Low                          |

# 内部直列抵抗付き/なし、 3線式インターフェースフルスピードUSBトランシーバ

## 3線式DAT/SE0インターフェース

MAX13342E/MAX13345Eでは、データまたはシングルエンドゼロをD+/D-ライン上で駆動するのにDATとSE0が使用されます。 $\overline{OE}$ がローのときは、SE0は入力であり、シングルエンドゼロドライバとして働きます。SE0がハイのときは、D+とD-はいずれもローに駆動されます。SE0がローに駆動されると、D+/D-出力はDATによって制御されます。

$\overline{OE}$ とSE0がいずれもローのとき、DATはD+/D-のデータの送信に使用されます。DATがハイのとき、D+はハイに駆動されD-はローに駆動されます。DATがローのとき、D+はローに駆動されD-はハイに駆動されます。

受信モード( $\overline{OE} = \text{ハイ}$ )では、DATはD+とD-に接続された差動レシーバの出力です。D+とD-の両方がローのとき、SE0のみがアクティブハイになります。

## 制御信号

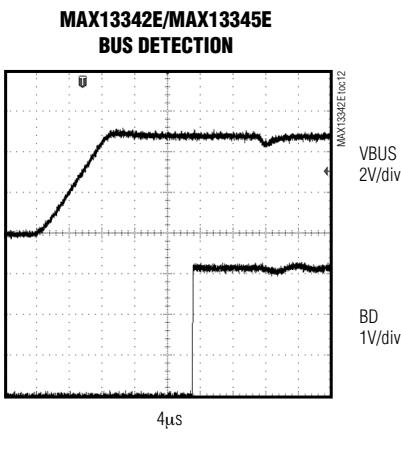

### USB検出

MAX13342E/MAX13345EのUSB検出機能は、 $V_{BUS}$ の有無を示します。MAX13342E/MAX13345Eのプッシュプルバス検出出力(BD)は、 $V_{BUS}$ を監視し、 $V_{BUS}$ と $V_L$ が存在するときハイをアサートします。 $V_{BUS}$ が+3.6V以下で共有モードに入ると、BDはローにアサートされます。

## $\overline{OE}$

$V_L$ と $V_{BUS}$ がいずれも存在するとき $\overline{OE}$ は通信の方向を制御します。 $\overline{OE}$ がローのとき、DATとSE0はロジック入力として動作し、D+/D-は出力となります。 $\overline{OE}$ がハイのとき、DATとSE0はロジック出力として動作し、D+/D-は入力となります。

## SUS

SUSは、MAX13342E/MAX13345Eを通常モードまたはサスPENDモードのいずれで動作させるかを決定します。通常モードの場合はSUSをローに駆動してください。サスPENDモードをイネーブルする場合はSUSをハイに駆動してください。サスPENDモードでは、シングルエンドレシーバ(D+/D-)がアクティブになりウェイクアップイベントを検出します。このモードでは、消費電流が45 $\mu$ A以下に減少します。

MAX13342E/MAX13345Eは、サスPENDモードにある間にD+とD-のデータを送信することができます。この機能はリモートウェイクアップイベントを通知するのに使用されます。

## ENUM

D+の1.5k $\Omega$ プルアップ抵抗器は、フルスピード(12Mbps)動作を示すのに使用されます。D+に接続の内蔵プルアップ抵抗器を $V_{TRM}$ に接続する場合は、ENUMをハイに駆動してください。D+の内蔵プルアップ抵抗器を $V_{TRM}$ から切斷する場合は、ENUMをローに駆動してください。

## D+とD-

D+とD-は双方向信号で、±15kV (HBM)に対してESD保護されます。USBの通常モードにあるとき、 $\overline{OE}$ はD+とD-の方向を制御します(表3と4)。

## $V_{TRM}$

内蔵のリニアレギュレータは $V_{TRM}$ 電圧(+3.3V、typ)を発生します。 $V_{TRM}$ は $V_{BUS}$ から給電されます(「電源の構成」の項参照)。 $V_{TRM}$ は内部のUSB回路に給電し内蔵の1.5k $\Omega$ 抵抗器用のプルアップ電圧を供給します。 $V_{TRM}$ を1 $\mu$ Fのセラミックコンデンサで(デバイスのできる限り近くで) GNDにバイパスしてください。外部回路への給電に $V_{TRM}$ を使用しないでください。

表3. 送信の真理値表

| $(\overline{OE} = 0, SUS = 0)$ |     |         |    |

|--------------------------------|-----|---------|----|

| INPUTS                         |     | OUTPUTS |    |

| DAT                            | SE0 | D+      | D- |

| 0                              | 0   | 0       | 1  |

| 0                              | 1   | 0       | 0  |

| 1                              | 0   | 1       | 0  |

| 1                              | 1   | 0       | 0  |

## アプリケーション情報

## USBデータ転送

## 送信データ

$\overline{OE}$ がローのとき、MAX13342E/MAX13345Eは、D+およびD-でUSBデータをUSBに差動送信します。D+/D-出力は、SE0とDATによって決定されます(表3参照)。

## 受信データ

D+/D-でデータを受信する際は、 $\overline{OE}$ をハイに駆動しSUSをローに駆動してください。D+とD-で受信された差動データはDATに現れます。D+とD-がいずれもローのときに限り、SE0はハイになります(表4)。

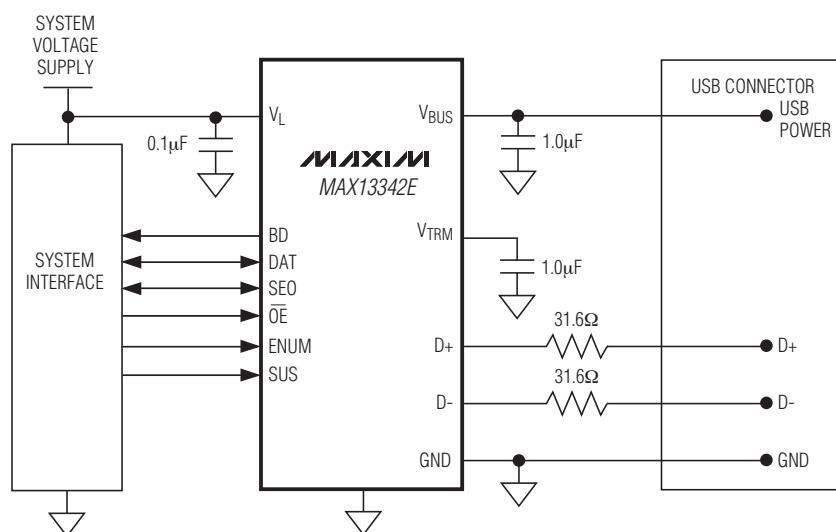

外付け抵抗器

(MAX13342E)

MAX13342Eでは、D+/D-の内部抵抗が低くなっています。USBには、インピーダンス整合用の2個の外付け直列抵抗器が必要です。これらの抵抗器をMAX13342EとUSBコネクタの間に配置してください(図2参照)。

表4. 受信の真理値表

| $(\overline{OE} = 1, SUS = 0)$ |    |         |     |

|--------------------------------|----|---------|-----|

| INPUTS                         |    | OUTPUTS |     |

| D+                             | D- | DAT     | SE0 |

| 0                              | 0  | *DAT    | 1   |

| 0                              | 1  | **0     | 0   |

| 1                              | 0  | **1     | 0   |

| 1                              | 1  | X       | 0   |

\*最終状態

\*\*D+/D-差動レシーバ出力

X = 未定義

## 外付けコンテンツ

デバイスが正しく動作するよう3個のコンテンツを外付けしてください。 $V_L$ を $0.1\mu F$ のセラミックコンデンサでGNDにバイパスしてください。 $V_{BUS}$ を $1\mu F$ のセラミックコンデンサでGNDにバイパスしてください。 $V_{TRM}$ を $1\mu F$  (min)のセラミックまたはプラスチックフィルムコンデンサでGNDにバイパスしてください。これらのコンデンサはすべてデバイスのできる限り近くに配置してください。

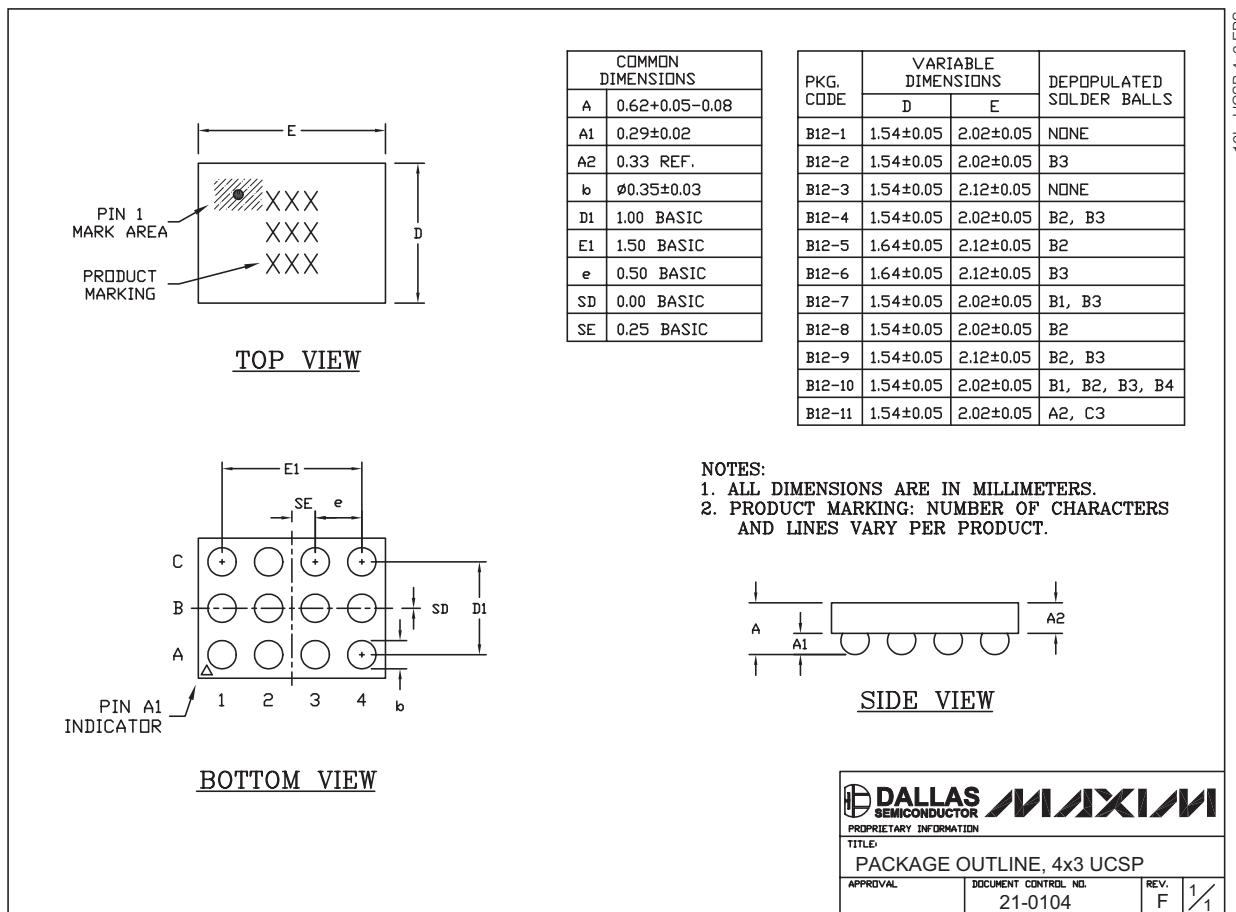

## UCSPのアプリケーション情報

UCSP構成、寸法、テープキャリア情報、PCB技術、バンブパッドレイアウト、および推奨リフロー温度プロファイルに関する最新アプリケーションの詳細、ならびに信頼性試験結果に関する最新情報については、マキシムのウェブサイト[japan.maxim-ic.com/ucsp](http://japan.maxim-ic.com/ucsp)に掲載されたアプリケーションノート1891「UCSP—ウェハレベルチップスケールパッケージ」を参照してください。

# 内部直列抵抗付き/なし、 3線式インターフェースフルスピードUSBトランシーバ

## ESD保護

MAX13342E/MAX13345Eは、D+とD-に±15kV (HBM) ESD保護を備えています。このESD構造は、通常動作、サスPEND、およびパワーダウンのすべての状態で高いESDに耐えます。±15kVのESD構造を正常に機能させるためには、1μF以上のコンデンサをV<sub>TRM</sub>からGNDに接続する必要があります。V<sub>BUS</sub>とD+/D-は、下記の制限値に対する保護特性が評価されます。

- ヒューマンボディモデルの場合は、±15kV

- IEC 61000-4-2接触放電の場合は、±8kV

- IEC 61000-4-2エアギャップ放電の場合は、±8kV

## ESD試験条件

ESD性能は様々な条件に左右されます。試験のセットアップ、試験方法、および試験結果を記載した信頼性報告書については、マキシムにお問い合わせください。

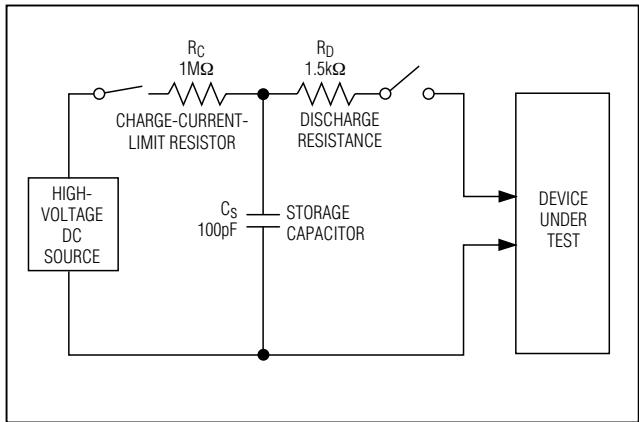

## ヒューマンボディモデル

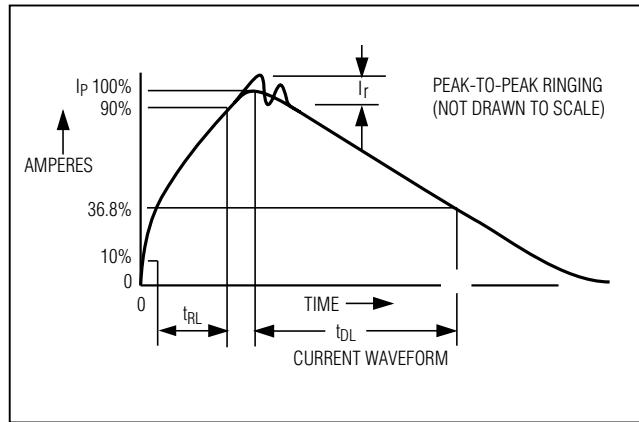

図11はヒューマンボディモデルを示し、図12はこのモデルが低インピーダンスに対して放電するときに発生する電流波形を示します。このモデルは測定するESD

電圧まで充電された100pFのコンデンサで構成され、このコンデンサはその後1.5kΩの抵抗器を通じて被試験デバイスに放電されます。

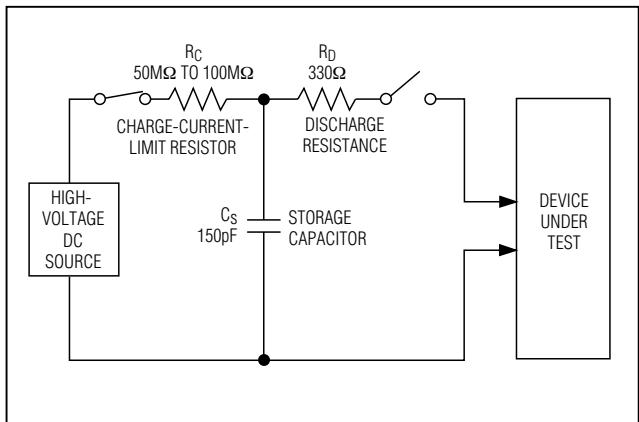

## IEC 61000-4-2

IEC 61000-4-2規格は、ESD試験および完成品の性能については規定していますが、集積回路については特に言及していません。MAX13342E/MAX13345Eでは、ユーザはESD保護部品を追加しなくてもIEC 61000-4-2のレベル4を満たす機器を設計することができます。ヒューマンボディモデルによる試験とIEC 61000-4-2による試験の大きな違いは、IEC 61000-4-2の方がピーク電流が大きいことです。これは、IEC 61000-4-2モデルの方が、直列抵抗が低いためです。このため、IEC 61000-4-2にしたがって測定されたESD耐圧は、ヒューマンボディモデルによって測定された耐圧よりも一般に低くなっています。図13はIEC 61000-4-2モデルを示します。エアギャップ放電法では、充電されたプローブにデバイスを近づける必要があります。接触放電法では、プローブをデバイスに接触した後でプローブを充電します。

図2. MAX13342E用USBコネクタへの外付け抵抗器の接続

# 内部直列抵抗付き/なし、 3線式インターフェースフルスピードUSBトランシーバ

## タイミング図/試験回路

図3. 立上りおよび立下り時間

図4. DAT/SEO～D+/D-のタイミング

図5. イネーブルとディセーブルのタイミング、トランスマッタ

図6. D+/D-～DAT/SEOの伝播遅延

**MAX13342E/MAX13345E**

## 内部直列抵抗付き/なし、 3線式インターフェースフルスピードUSBトランシーバ

図7. レシーバのイネーブルとディセーブルのタイミング

図9. ディセーブル時間測定用負荷

図10. レシーバの伝播遅延およびレシーバの立上り/立下り時間測定用負荷

図8. トランスマッタの伝播遅延、イネーブル時間、トランスマッタの立上り/立下り時間測定用負荷

# 内部直列抵抗付き/なし、 3線式インターフェースフルスピードUSBトランシーバ

**MAX13342E/MAX13345E**

図11. ヒューマンボディによるESD試験モデル

図12. ヒューマンボディモデルによる電流波形

図13. IEC 61000-4-2規格によるESD試験モデル

# 内部直列抵抗付き/なし、 3線式インターフェースフルスピードUSBトランシーバ

## 標準アプリケーション回路

## ピン配置

## チップ情報

PROCESS: BiCMOS

# 内部直列抵抗付き/なし、 3線式インターフェースフルスピードUSBトランシーバ

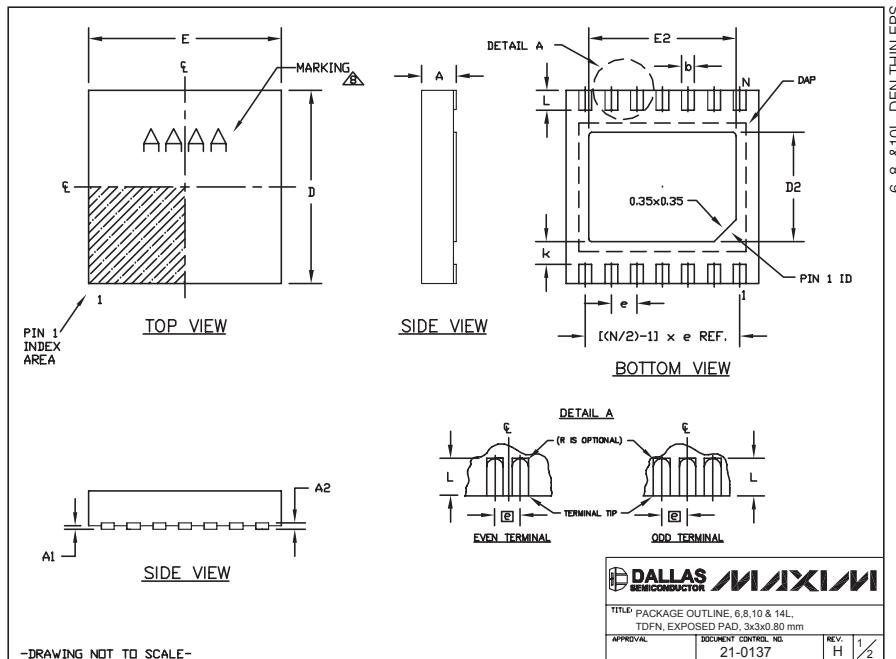

## パッケージ

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、[japan.maxim-ic.com/packages](http://japan.maxim-ic.com/packages)をご参照下さい。)

| COMMON DIMENSIONS |           |      | PACKAGE VARIATIONS |    |           |           |          |                |           |               |

|-------------------|-----------|------|--------------------|----|-----------|-----------|----------|----------------|-----------|---------------|

| SYMBOL            | MIN.      | MAX. | PKG. CODE          | N  | D2        | E2        | e        | JEDEC SPEC     | b         | [(N/2)-1] x e |

| A                 | 0.70      | 0.80 | T633-1             | 6  | 1.50±0.10 | 2.30±0.10 | 0.95 BSC | MO229 / WEEA   | 0.40±0.05 | 1.90 REF      |

| D                 | 2.90      | 3.10 | T633-2             | 6  | 1.50±0.10 | 2.30±0.10 | 0.95 BSC | MO229 / WEEA   | 0.40±0.05 | 1.90 REF      |

| E                 | 2.90      | 3.10 | T833-1             | 8  | 1.50±0.10 | 2.30±0.10 | 0.65 BSC | MO229 / WEEC   | 0.30±0.05 | 1.95 REF      |

| A1                | 0.00      | 0.05 | T833-2             | 8  | 1.50±0.10 | 2.30±0.10 | 0.65 BSC | MO229 / WEEC   | 0.30±0.05 | 1.95 REF      |

| L                 | 0.20      | 0.40 | T833-3             | 8  | 1.50±0.10 | 2.30±0.10 | 0.65 BSC | MO229 / WEEC   | 0.30±0.05 | 1.95 REF      |

| k                 | 0.25 MIN. |      | T1033-1            | 10 | 1.50±0.10 | 2.30±0.10 | 0.50 BSC | MO229 / WEED-3 | 0.25±0.05 | 2.00 REF      |

| A2                | 0.20 REF. |      | T1033-2            | 10 | 1.50±0.10 | 2.30±0.10 | 0.50 BSC | MO229 / WEED-3 | 0.25±0.05 | 2.00 REF      |

|                   |           |      | T1433-1            | 14 | 1.70±0.10 | 2.30±0.10 | 0.40 BSC | -----          | 0.20±0.05 | 2.40 REF      |

|                   |           |      | T1433-2            | 14 | 1.70±0.10 | 2.30±0.10 | 0.40 BSC | -----          | 0.20±0.05 | 2.40 REF      |

NOTES:

1. ALL DIMENSIONS ARE IN mm. ANGLES IN DEGREES.

2. COPLANARITY SHALL NOT EXCEED 0.08 mm.

3. WARPAGE SHALL NOT EXCEED 0.10 mm.

4. PACKAGE LENGTH/PACKAGE WIDTH ARE CONSIDERED AS SPECIAL CHARACTERISTIC(S).

5. DRAWING CONFORMS TO JEDEC MO229, EXCEPT DIMENSIONS "D2" AND "E2", AND T1433-1 & T1433-2.

6. "N" IS THE TOTAL NUMBER OF LEADS.

7. NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY.

8. MARKING IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

DRAWING NOT TO SCALE

DALLAS MAXIM SEMICONDUCTOR

NOTES: 6.0 & 10L DFN THIN FEET

**MAX13342E/MAX13345E**

# 内部直列抵抗付き/なし、 3線式インターフェースフルスピードUSBトランシーバ

## パッケージ(続き)

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、[japan.maxim-ic.com/packages](http://japan.maxim-ic.com/packages)をご参照下さい。)

マキシム・ジャパン株式会社

〒169-0051 東京都新宿区西早稲田3-30-16(ホリゾン1ビル)

TEL. (03)3232-6141 FAX. (03)3232-6149

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。マキシムは隨時予告なく回路及び仕様を変更する権利を留保します。

18 Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2006 Maxim Integrated Products, Inc. All rights reserved. MAXIM is a registered trademark of Maxim Integrated Products, Inc.