# 超低電圧レベルトランスレータ

**MAX13000E-MAX13005E**

## 概要

MAX13000E～MAX13005Eの6チャネルレベルトランスレータは、マルチ電圧システムにおいてデータ転送に必要なレベルシフトを行なえるようにします。外部印加電圧のV<sub>CC</sub>およびV<sub>L</sub>によって、このデバイスの入出力側にロジックレベルを設定します。デバイスのV<sub>L</sub>側にあるロジック信号は、デバイスのV<sub>CC</sub>側により高い電圧ロジック信号として現れ、逆もまた同様になります。

MAX13000E～MAX13005Eは、4μA以下の低いV<sub>CC</sub>およびV<sub>L</sub>の自己消費電流を特徴としています。また、MAX13000E～MAX13005EはI/O V<sub>CC</sub>側に±15kVのESD保護も備え、信号を外部で引き回すアプリケーションでの保護を向上しています。このESD保護は、ヒューマンボディモデル(HBM)を使用して規定されています。MAX13000E/MAX13001E/MAX13002Eは、230kbpsの保証データレートで動作します。MAX13003E/MAX13004E/MAX13005Eは、V<sub>CC</sub>が+1.65Vを上回る場合は20Mbpsの保証データレートで動作します。

MAX13000E/MAX13003Eは双方向レベルトランスレータであり、DIRECTION入力をすることなく任意の單一データライン上において双方向(V<sub>L</sub> ↔ V<sub>CC</sub>)のデータ変換が可能です。MAX13001E/MAX13002E/MAX13004E/MAX13005Eは1方向レベルトランスレータで、任意の单一データライン上において1方向(V<sub>L</sub> → V<sub>CC</sub>、またはV<sub>CC</sub> → V<sub>L</sub>)でデータをレベルシフトします。1方向トランスレータのMAX13001E/MAX13002E/MAX13004E/MAX13005Eの入力は、CMOSおよびオープンドレイン(OD)出力とインターフェースする能力を備えています。詳細については、「型番」、「選択ガイド」、および「入力ドライバ要件」の項を参照してください。

MAX13000E～MAX13005Eは、+0.9V～+3.6VのV<sub>L</sub>電圧と+1.5V～+3.6VのV<sub>CC</sub>電圧で動作します。MAX13000E～MAX13005Eは16バンプUCSP™/パッケージおよび16ピンTSSOPパッケージで提供され、-40°C～+85°Cの拡張動作温度範囲での動作が保証されています。

## アプリケーション

- CMOSロジックレベル変換

- オープンドレインI/O変換

- ODからCMOS信号への変換

- 低電圧ASICレベル変換

- 携帯電話

- SPI™およびMICROWIRE™レベル変換

- スマートカードリーダ

- ポータブルPOSシステム

- ポータブル通信機器

- 低コストシリアルインターフェース

- テレコム機器

## 特長

- ♦ 保証済みデータレートのオプション

230kbps(MAX13000E/MAX13001E/

MAX13002E)

20Mbps(MAX13003E/MAX13004E/

MAX13005E)

- ♦ DIRECTION入力不要の双方向レベル変換

- ♦ V<sub>L</sub>で最低+0.9V、V<sub>CC</sub>で最低+1.5Vの動作

- ♦ HBMによるI/O V<sub>CC</sub>ライン上の±15kVのESD保護

- ♦ 低自己消費電流で4μA以下

- ♦ イネーブル/シャットダウン制御

- ♦ 2mm × 2mmの16バンプUCSPおよび

有鉛パッケージのオプション

- ♦ CMOSまたはオープンドレイン出力インターフェース

機能

UCSPはMaxim Integrated Products, Inc.の商標です。

SPIはMotorola, Inc.の商標です。

MICROWIREはNational Semiconductor Corp.の商標です。

## 型番

| PART        | TEMP RANGE     | PIN-PACKAGE |

|-------------|----------------|-------------|

| MAX13000EUE | -40°C to +85°C | 16 TSSOP    |

型番はデータシートの最後へ続いています。

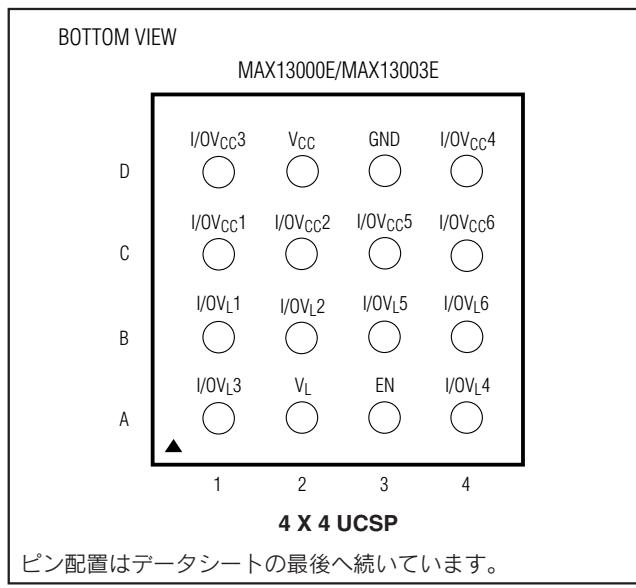

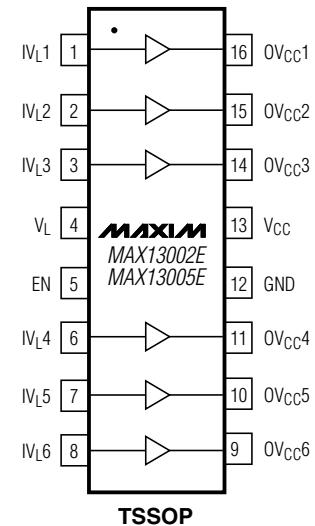

## ピン配置

標準動作回路および選択ガイドはデータシートの最後に記載されています。

# 超低電圧レベルトランスレータ

## ABSOLUTE MAXIMUM RATINGS

Voltages referenced to GND.

|                                                           |                             |

|-----------------------------------------------------------|-----------------------------|

| $V_{CC}$                                                  | -0.3V to +4V                |

| $V_L$                                                     | -0.3V to +4V                |

| $I/O_{VCC\_}$                                             | -0.3V to ( $V_{CC}$ + 0.3V) |

| $I/O_{V_L}$                                               | -0.3V to ( $V_L$ + 0.3V)    |

| EN                                                        | -0.3V to ( $V_L$ + 0.3V)    |

| Short-Circuit Duration $I/O_{V_L}$ , $I/O_{VCC\_}$ to GND | Continuous                  |

|                                                           |                 |

|-----------------------------------------------------------|-----------------|

| Continuous Power Dissipation ( $T_A = +70^\circ C$ )      |                 |

| 16-Pin TSSOP (derate 9.4mW/ $^\circ C$ at $+70^\circ C$ ) | 755mW           |

| 16-Bump UCSP (derate 8.2mW/ $^\circ C$ at $+70^\circ C$ ) | 659mW           |

| Operating Temperature Range                               | -40°C to +85°C  |

| Junction Temperature                                      | +150°C          |

| Storage Temperature Range                                 | -65°C to +150°C |

| Lead Temperature (soldering, 10s)                         | +300°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

( $V_{CC} = +1.5V$  to  $+3.6V$ ,  $V_L = +0.9V$  to  $V_{CC}$ ,  $C_I/OVL \leq 15pF$ ,  $C_I/OVCC \leq 50pF$ ,  $T_A = -40^\circ C$  to  $+85^\circ C$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ .) (Notes 1, 4)

| PARAMETER                                        | SYMBOL         | CONDITIONS                                                      |                                       | MIN | TYP      | MAX | UNITS   |

|--------------------------------------------------|----------------|-----------------------------------------------------------------|---------------------------------------|-----|----------|-----|---------|

| $V_L$ Supply Range                               | $V_L$          | $V_L \leq V_{CC}$ (Note 2)                                      |                                       | 0.9 | $V_{CC}$ |     | V       |

| $V_{CC}$ Supply Range                            | $V_{CC}$       | (Note 2)                                                        |                                       | 1.5 | 3.6      |     | V       |

| Supply Current from $V_{CC}$ (Note 3)            | $I_{QVCC}$     | $T_A = +25^\circ C$                                             |                                       |     | 4        |     | $\mu A$ |

|                                                  |                | $T_A = +85^\circ C$                                             |                                       |     | 40       |     |         |

| Supply Current from $V_L$ (Note 3)               | $I_{QVL}$      | $T_A = +25^\circ C$                                             | (Note 3)                              | 1   | 5        |     | $\mu A$ |

|                                                  |                |                                                                 | $V_L < V_{CC} - 0.2V$                 |     | 2        |     |         |

|                                                  |                | $T_A = +85^\circ C$                                             | (Note 3)                              | 4   | 40       |     |         |

|                                                  |                |                                                                 | $V_L < V_{CC} - 0.2V$                 |     | 20       |     |         |

| V <sub>CC</sub> Shutdown Supply Current (Note 3) | $I_{SHDN-VCC}$ | $EN = GND, T_A = +25^\circ C$                                   |                                       |     | 2        |     | $\mu A$ |

|                                                  |                | $EN = GND, T_A = +85^\circ C$                                   |                                       |     | 20       |     |         |

| V <sub>L</sub> Shutdown Supply Current (Note 3)  |                | $T_A = +25^\circ C$                                             | $V_L < V_{CC} - 0.2V$ ,<br>$EN = GND$ |     | 2        |     | $\mu A$ |

|                                                  |                |                                                                 | $EN = GND$                            | 1   | 4        |     |         |

|                                                  |                | $T_A = +85^\circ C$                                             | $V_L < V_{CC} - 0.2V$ ,<br>$EN = GND$ |     | 20       |     |         |

|                                                  |                |                                                                 | $EN = GND$                            |     | 40       |     |         |

| I/O Tri-State Output Leakage Current             |                | $I/O V_L, I/O V_{CC\_}$ ,<br>$EN = GND$                         | $T_A = +25^\circ C$                   |     | 0.35     |     | $\mu A$ |

|                                                  |                |                                                                 | $T_A = +85^\circ C$                   |     | 1        |     |         |

| I/O Tri-State Output Leakage Current             |                | $V_L < V_{CC} - 0.2V$ , $I/O V_L, I/O V_{CC\_}$ ,<br>$EN = GND$ | $T_A = +25^\circ C$                   |     | 0.2      |     | $\mu A$ |

|                                                  |                |                                                                 | $T_A = +85^\circ C$                   |     | 0.5      |     |         |

| EN Input Leakage Current                         |                | $T_A = +25^\circ C$                                             |                                       |     | 0.35     |     | $\mu A$ |

|                                                  |                |                                                                 | $T_A = +85^\circ C$                   |     | 1        |     |         |

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{CC} = +1.5V$  to  $+3.6V$ ,  $V_L = +0.9V$  to  $V_{CC}$ ,  $C_I/OVL \leq 15pF$ ,  $C_I/OVCC \leq 50pF$ ,  $T_A = -40^\circ C$  to  $+85^\circ C$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ .) (Notes 1, 4)

| PARAMETER                                                   | SYMBOL            | CONDITIONS                                                                       | MIN | TYP                    | MAX                   | UNITS |

|-------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------|-----|------------------------|-----------------------|-------|

| <b>LOGIC-LEVEL THRESHOLDS</b>                               |                   |                                                                                  |     |                        |                       |       |

| I/OVL <sub>_</sub> Input-Voltage-High Threshold             | V <sub>IHL</sub>  |                                                                                  |     |                        | 2/3 × V <sub>L</sub>  | V     |

| I/OVL <sub>_</sub> Input-Voltage-Low Threshold              | V <sub>IIL</sub>  |                                                                                  |     | 1/3 × V <sub>L</sub>   |                       | V     |

| I/OVCC <sub>_</sub> Input-Voltage-High Threshold            | V <sub>IHC</sub>  |                                                                                  |     |                        | 2/3 × V <sub>CC</sub> | V     |

| I/OVCC <sub>_</sub> Input-Voltage-Low Threshold             | V <sub>IIC</sub>  |                                                                                  |     | 1/3 × V <sub>CC</sub>  |                       | V     |

| EN Input-Voltage-High Threshold                             | V <sub>IHEN</sub> |                                                                                  |     |                        | 2/3 × V <sub>L</sub>  | V     |

| EN Input-Voltage-Low Threshold                              | V <sub>ILEN</sub> |                                                                                  |     | 1/3 × V <sub>L</sub>   |                       | V     |

| I/OVL <sub>_</sub> Output-Voltage High                      | V <sub>OHL</sub>  | I/OVL <sub>_</sub> source current = 20µA                                         |     | V <sub>L</sub> - 0.25  |                       | V     |

| I/OVL <sub>_</sub> Output-Voltage Low                       | V <sub>OLL</sub>  | MAX13002E/MAX13005E, OVL <sub>_</sub> sink current = 1µA                         |     | 0.3                    |                       | V     |

|                                                             |                   | MAX13000E/MAX13001E/MAX13003E/MAX13004E, I/OVL <sub>_</sub> sink current = 20µA  |     | 0.25                   |                       |       |

| I/OVCC <sub>_</sub> Output-Voltage High                     | V <sub>OHC</sub>  | I/OVCC <sub>_</sub> source current = 20µA                                        |     | V <sub>CC</sub> - 0.25 |                       | V     |

| I/OVCC <sub>_</sub> Output-Voltage Low                      | V <sub>OCL</sub>  | MAX13001E/MAX13004E, OVCC <sub>_</sub> sink current = 1µA                        |     | 0.3                    |                       | V     |

|                                                             |                   | MAX13000E/MAX13002E/MAX13003E/MAX13005E, I/OVCC <sub>_</sub> sink current = 20µA |     | 0.25                   |                       |       |

| <b>OUTPUT CURRENTS</b>                                      |                   |                                                                                  |     |                        |                       |       |

| Output Sink Current During Transient (V <sub>CC</sub> Side) |                   | V <sub>CC</sub> = +1.65V, MAX13003E/MAX13004E/MAX13005E                          | 25  |                        |                       | mA    |

|                                                             |                   | V <sub>CC</sub> = +1.65V, MAX13000E/MAX13001E/MAX13002E                          | 1   |                        |                       |       |

| Output Sink Current During Transient (V <sub>L</sub> Side)  |                   | V <sub>L</sub> = +1.2V, V <sub>CC</sub> = +1.65V, MAX13003E/MAX13004E/MAX13005E  | 30  |                        |                       | mA    |

|                                                             |                   | V <sub>L</sub> = +1.2V, V <sub>CC</sub> = +1.65V, MAX13000E/MAX13001E/MAX13002E  | 1   |                        |                       |       |

# 超低電圧レベルトランスレータ

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{CC} = +1.5V$  to  $+3.6V$ ,  $V_L = +0.9V$  to  $V_{CC}$ ,  $C_I/OV_L \leq 15pF$ ,  $C_I/OV_{CC} \leq 50pF$ ,  $T_A = -40^\circ C$  to  $+85^\circ C$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ .) (Notes 1, 4)

| PARAMETER                                               | SYMBOL | CONDITIONS                                                        | MIN | TYP      | MAX | UNITS |

|---------------------------------------------------------|--------|-------------------------------------------------------------------|-----|----------|-----|-------|

| Output Source Current During Transient ( $V_{CC}$ Side) |        | $V_{CC} = +1.65V$ , MAX13003E/MAX13004E/MAX13005E                 | 22  |          |     | mA    |

|                                                         |        | $V_{CC} = +1.65V$ , MAX13000E/MAX13001E/MAX13002E                 | 1   |          |     |       |

| Output Source Current During Transient ( $V_L$ Side)    |        | $V_L = +1.2V$ , $V_{CC} = +1.65V$ , MAX13003E/MAX13004E/MAX13005E | 25  |          |     | mA    |

|                                                         |        | $V_L = +1.2V$ , $V_{CC} = +1.65V$ , MAX13000E/MAX13001E/MAX13002E | 1   |          |     |       |

| <b>ESD PROTECTION</b>                                   |        |                                                                   |     |          |     |       |

| I/OVCC_                                                 |        | Human Body Model                                                  |     | $\pm 15$ |     | kV    |

|                                                         |        | Air-Gap Discharge (IEC61000-4-2)                                  |     | $\pm 10$ |     |       |

|                                                         |        | Contact Discharge (IEC61000-4-2)                                  |     | $\pm 8$  |     |       |

## TIMING CHARACTERISTICS

( $V_{CC} = +1.5V$  to  $+3.6V$ ,  $V_L = +0.9V$  to  $V_{CC}$ ,  $C_I/OV_L \leq 15pF$ ,  $C_I/OV_{CC} \leq 50pF$ ,  $T_A = -40^\circ C$  to  $+85^\circ C$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ .) (Notes 1, 4)

| PARAMETER         | SYMBOL | CONDITIONS                                                                               | MIN | TYP | MAX  | UNITS |

|-------------------|--------|------------------------------------------------------------------------------------------|-----|-----|------|-------|

| I/OVCC_ Rise Time | tRVCC  | $C_I/OV_{CC} = 50pF$ , MAX13003E/MAX13004E/MAX13005E, $V_{CC} = +1.65V$ , Figures 1a, 1b |     |     | 15   | ns    |

|                   |        | $C_I/OV_{CC} = 50pF$ , MAX13003E/MAX13004E/MAX13005E, $V_{CC} = +1.5V$ , Figures 1a, 1b  |     |     | 15   |       |

|                   |        | $C_I/OV_{CC} = 50pF$ , MAX13000E/MAX13001E/MAX13002E, Figures 1a, 1b                     | 400 |     | 1400 |       |

| I/OVCC_ Fall Time | tFVCC  | $C_I/OV_{CC} = 50pF$ , MAX13003E/MAX13004E/MAX13005E, $V_{CC} = +1.65V$ , Figures 1a, 1b |     |     | 15   | ns    |

|                   |        | $C_I/OV_{CC} = 50pF$ , MAX13003E/MAX13004E/MAX13005E, $V_{CC} = +1.5V$ , Figures 1a, 1b  |     |     | 15   |       |

|                   |        | $C_I/OV_{CC} = 50pF$ , MAX13000E/MAX13001E/MAX13002E, Figures 1a, 1b                     | 400 |     | 1400 |       |

## TIMING CHARACTERISTICS (continued)

( $V_{CC} = +1.5V$  to  $+3.6V$ ,  $V_L = +0.9V$  to  $V_{CC}$ ,  $C_I/OVL \leq 15pF$ ,  $C_I/OVCC \leq 50pF$ ,  $T_A = -40^\circ C$  to  $+85^\circ C$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ .) (Notes 1, 4)

| PARAMETER                                                      | SYMBOL              | CONDITIONS                                                                                 | MIN | TYP  | MAX  | UNITS   |

|----------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------|-----|------|------|---------|

| I/OVL_Rise Time                                                | t <sub>RVL</sub>    | $C_I/OVL = 50pF$ ,<br>MAX13003E/MAX13004E/MAX13005E,<br>$V_{CC} = +1.65V$ , Figures 2a, 2b |     | 15   |      | ns      |

|                                                                |                     | $C_I/OVL = 15pF$ ,<br>MAX13003E/MAX13004E/MAX13005E,<br>$V_{CC} = +1.5V$ , Figures 2a, 2b  |     | 15   |      |         |

|                                                                |                     | $C_I/OVL = 50pF$ ,<br>MAX13000E/MAX13001E/MAX13002E,<br>Figures 2a, 2b                     | 300 |      | 1200 |         |

| I/OVL_Fall Time                                                | t <sub>FVL</sub>    | $C_I/OVL = 50pF$ ,<br>MAX13003E/MAX13004E/MAX13005E,<br>$V_{CC} = +1.65V$ , Figures 2a, 2b |     | 15   |      | ns      |

|                                                                |                     | $C_I/OVL = 15pF$ ,<br>MAX13003E/MAX13004E/MAX13005E,<br>$V_{CC} = +1.5V$ , Figures 2a, 2b  |     | 15   |      |         |

|                                                                |                     | $C_I/OVL = 50pF$ ,<br>MAX13000E/MAX13001E/MAX13002E,<br>Figures 2a, 2b                     | 300 |      | 1200 |         |

| Propagation Delay<br>(Driving I/OVL_)                          | I/OVL-VCC           | $C_I/OVCC = 50pF$ ,<br>MAX13003E/MAX13004E/MAX13005E,<br>Figures 1a, 1b                    |     | 20   |      | ns      |

|                                                                |                     | $C_I/OVCC = 50pF$ ,<br>MAX13000E/MAX13001E/MAX13002E,<br>Figures 1a, 1b                    |     | 1000 |      |         |

| Propagation Delay<br>(Driving I/OVCC_)                         | I/OVCC-VL           | $V_{CC} > +1.65V$ , $C_I/OVL = 50pF$ ,<br>MAX13003E/MAX13004E/MAX13005E,<br>Figures 2a, 2b |     | 20   |      | ns      |

|                                                                |                     | $V_{CC} = 1.5V$ , $C_I/OVL = 15pF$ ,<br>MAX13003E/MAX13004E/MAX13005E,<br>Figures 2a, 2b   |     | 20   |      |         |

|                                                                |                     | $C_I/OVL = 50pF$ ,<br>MAX13000E/MAX13001E/MAX13002E,<br>Figures 2a, 2b                     |     | 1000 |      |         |

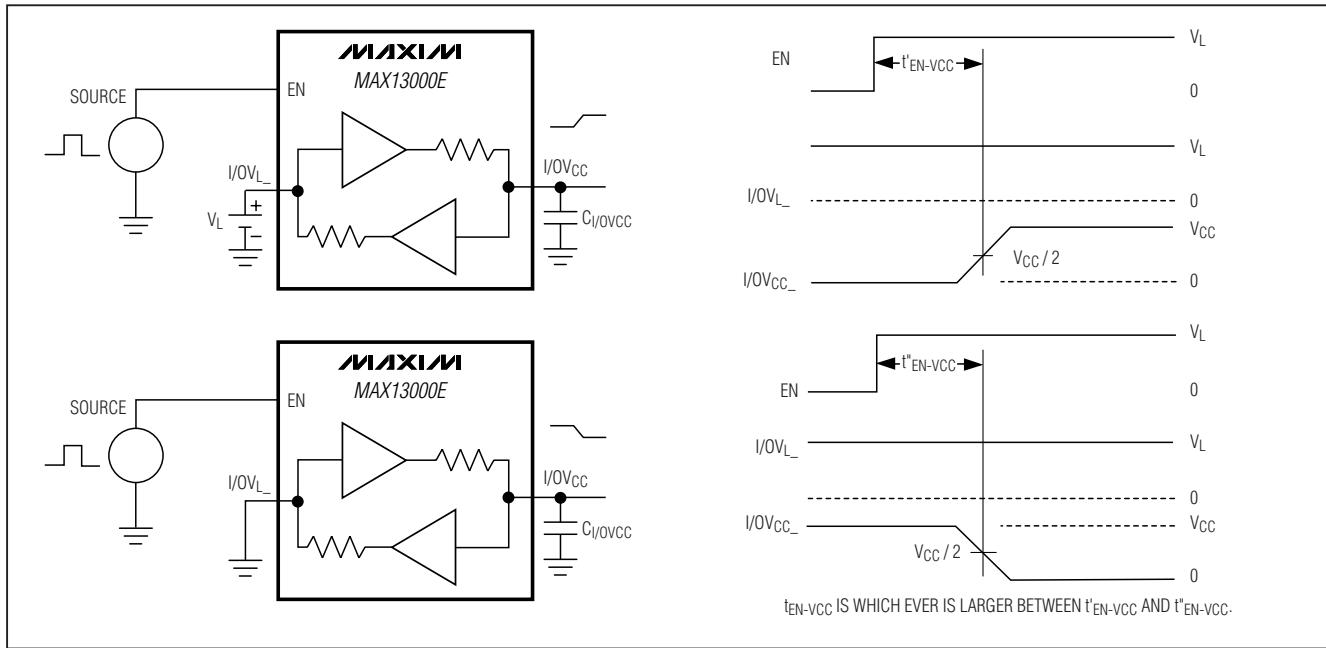

| Propagation Delay from<br>I/OVL to I/OVCC_after EN<br>(Note 5) | t <sub>EN-VCC</sub> | $C_I/OVCC = 50pF$ , CMOS output, Figure 3                                                  |     | 2    |      | $\mu s$ |

|                                                                |                     | $C_I/OVCC = 50pF$ , OD output, Figure 3                                                    |     | 6    |      |         |

# 超低電圧レベルトランスレータ

## TIMING CHARACTERISTICS (continued)

( $V_{CC} = +1.5V$  to  $+3.6V$ ,  $V_L = +0.9V$  to  $V_{CC}$ ,  $C_I/OV_L \leq 15pF$ ,  $C_I/OVCC \leq 50pF$ ,  $T_A = -40^\circ C$  to  $+85^\circ C$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ .) (Notes 1, 4)

| PARAMETER                                                | SYMBOL       | CONDITIONS                                                                                                                       | MIN | TYP | MAX       | UNITS   |

|----------------------------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------|---------|

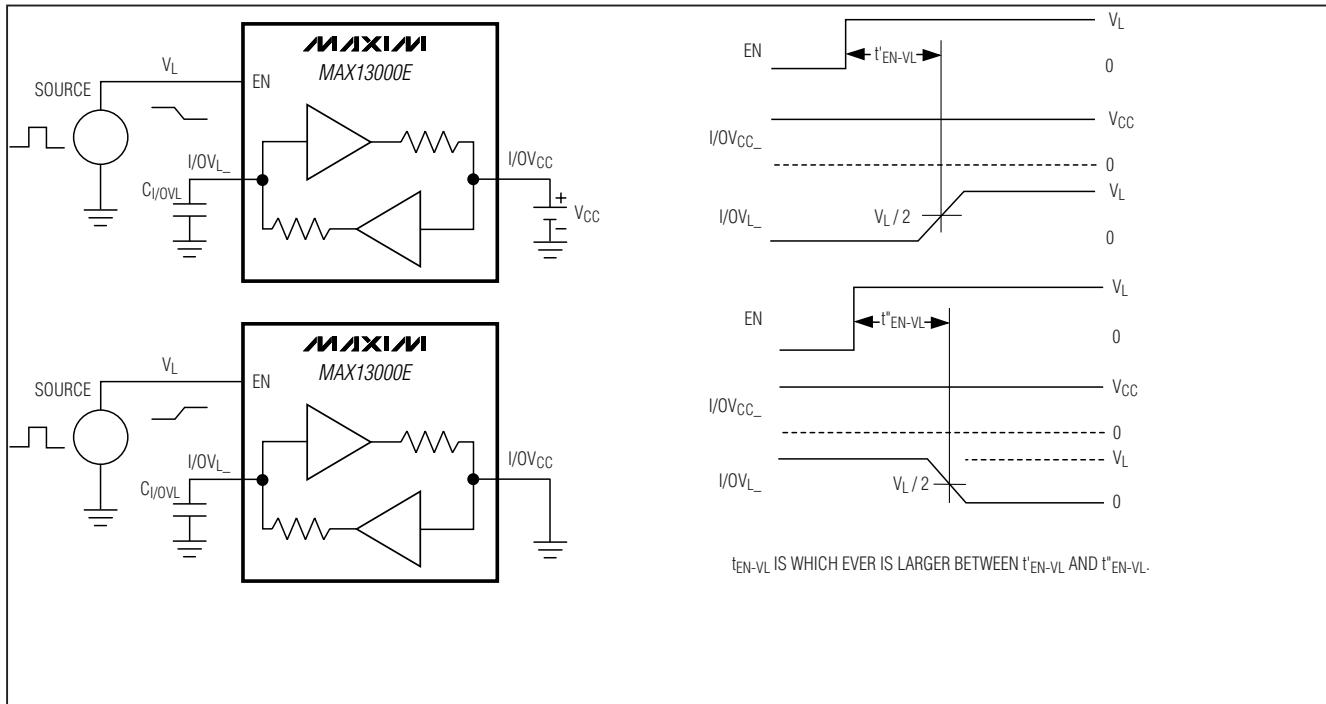

| Propagation Delay from I/OVcc to I/OVL after EN (Note 5) | $t_{EN-VL}$  | $C_I/OV_L = 50pF$ , CMOS output, Figure 4                                                                                        |     | 2   |           | $\mu s$ |

|                                                          |              | $C_I/OV_L = 50pF$ , OD output, Figure 4                                                                                          |     | 6   |           |         |

| Channel-to-Channel Skew                                  | $t_{SKew}$   | Each translator equally loaded, MAX13003E/MAX13004E/MAX13005E                                                                    |     |     | $\pm 5$   | ns      |

|                                                          |              | Each translator equally loaded, MAX13000E/MAX13001E/MAX13002E                                                                    |     |     | $\pm 250$ |         |

| Part-to-Part Skew (Note 6)                               | $t_{PPSKew}$ | $C_I/OV_L = 15pF$ , $C_I/OVCC = 15pF$ , $V_L = +1.8V$ , $V_{CC} = +2V$ , $\Delta T = +5^\circ C$ , MAX13003E/MAX13004E/MAX13005E |     | 10  |           | ns      |

| Maximum Data Rate                                        |              | MAX13003E/MAX13004E/MAX13005E<br>$V_{CC} > +1.65V$ , $C_I/OV_L = 50pF$ , $C_I/OVCC = 50pF$                                       |     | 20  |           | Mbps    |

|                                                          |              | MAX13000E/MAX13001E/MAX13002E<br>$C_I/OV_L = 50pF$ , $C_I/OVCC = 50pF$                                                           |     | 230 |           | kbps    |

**Note 1:** All devices are 100% production tested at  $T_A = +25^\circ C$ . Limits are guaranteed by design over the entire temperature range.

**Note 2:**  $V_L$  must be less than or equal to  $V_{CC}$  during normal operation. However,  $V_L$  can be greater than  $V_{CC}$  during startup and shutdown conditions.

**Note 3:** This consumption is referred to as no signal transmission.

**Note 4:** Guaranteed by design with an input signal full swing, rise/fall time  $\leq 3\text{ns}$ , source resistance is  $50\Omega$ .

**Note 5:** Enable input signal full swing and rise/fall time  $\leq 50\text{ns}$ .

**Note 6:** Guaranteed by design, not production tested.

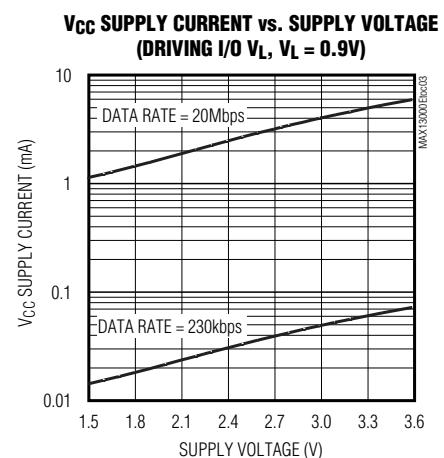

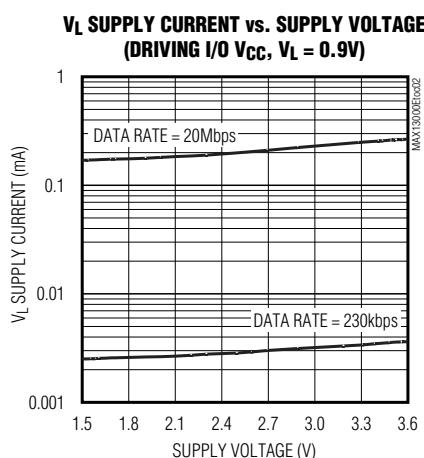

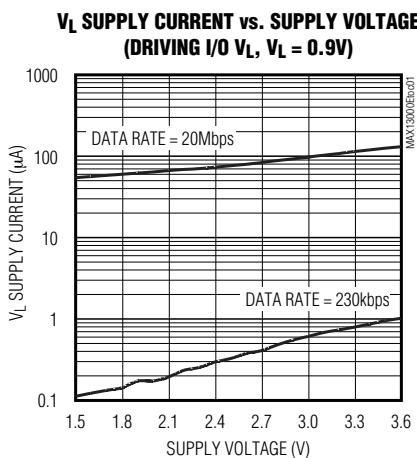

## 標準動作特性

( $V_{CC} = +3.3V$ ,  $V_L = +0.9V$ ,  $T_A = +25^\circ C$ , MAX13003E.)

# 超低電圧レベルトランスレータ

MAX13000E-MAX13005E

## 標準動作特性(続き)

( $V_{CC} = +3.3V$ ,  $V_L = +0.9V$ ,  $T_A = +25^\circ C$ , MAX13003E.)

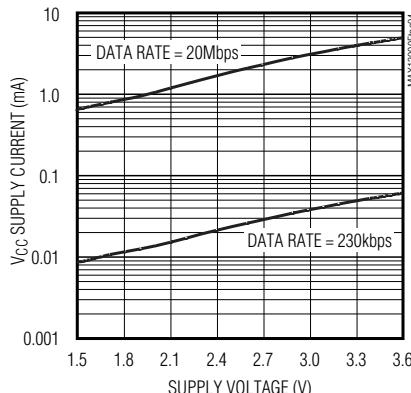

**$V_{CC}$  SUPPLY CURRENT vs. SUPPLY VOLTAGE

(DRIVING I/O $V_{CC}$ ,  $V_L = +0.9V$ )**

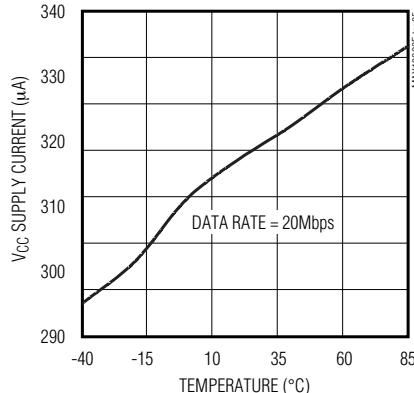

**$V_L$  SUPPLY CURRENT vs. TEMPERATURE

(DRIVING I/O $V_{CC}$ ,  $V_{CC} = +3.3V$ ,  $V_L = +0.9V$ )**

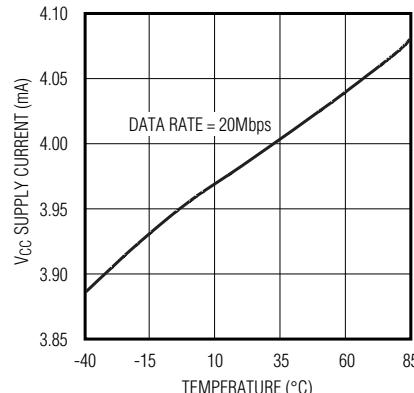

**$V_{CC}$  SUPPLY CURRENT vs. TEMPERATURE

(DRIVING I/O $V_{CC}$ ,  $V_{CC} = +3.3V$ ,  $V_L = +0.9V$ )**

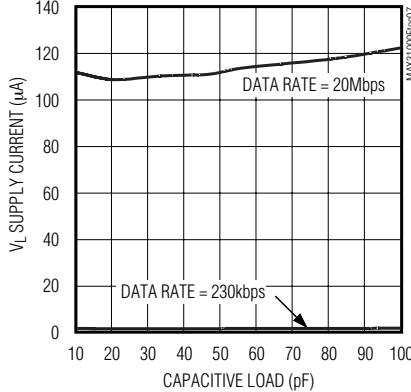

**$V_L$  SUPPLY CURRENT vs.

CAPACITIVE LOAD ON I/O  $V_{CC}$

(DRIVING I/O $V_L$ ,  $V_{CC} = 3.3V$ ,  $V_L = +0.9V$ )**

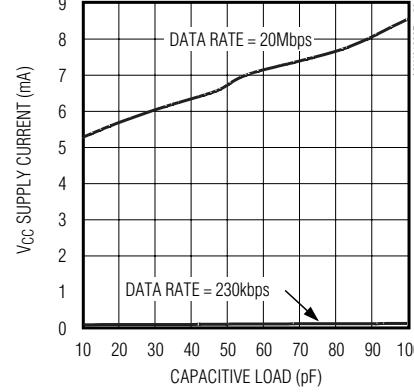

**$V_{CC}$  SUPPLY CURRENT vs.

CAPACITIVE LOAD ON I/O  $V_{CC}$

(DRIVING I/O $V_L$ ,  $V_{CC} = 3.3V$ ,  $V_L = +0.9V$ )**

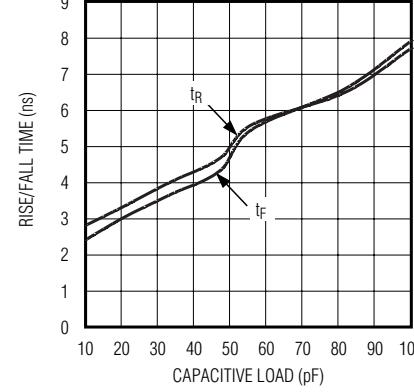

**RISE/FALL TIME vs.

CAPACITIVE LOAD ON I/O  $V_{CC}$

(DRIVING I/O $V_L$ ,  $V_{CC} = 3.3V$ ,  $V_L = +0.9V$ )**

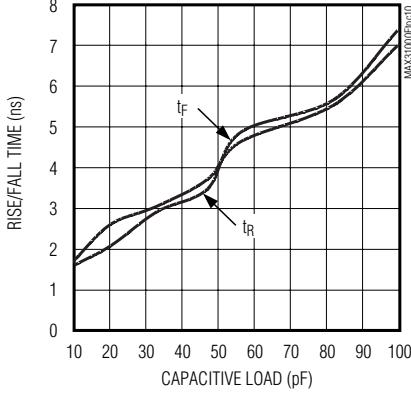

**RISE/FALL TIME vs.

CAPACITIVE LOAD ON I/O  $V_L$

(DRIVING I/O $V_{CC}$ ,  $V_{CC} = 3.3V$ ,  $V_L = +0.9V$ )**

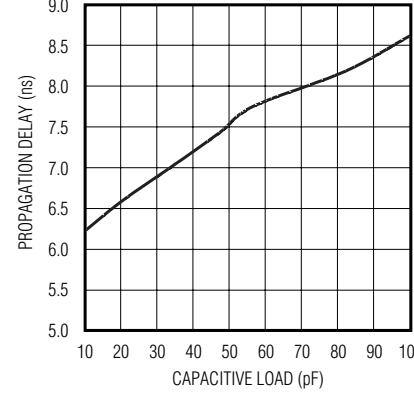

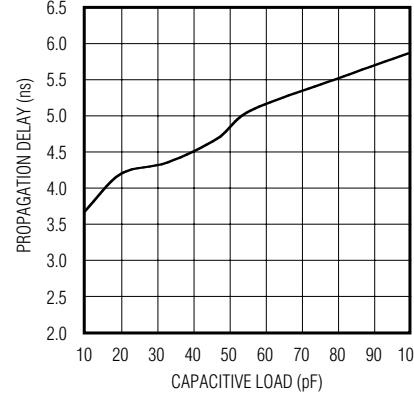

**PROPAGATION DELAY vs.

CAPACITIVE LOAD ON I/O  $V_{CC}$

(DRIVING I/O $V_L$ ,  $V_{CC} = 3.3V$ ,  $V_L = +0.9V$ )**

**PROPAGATION DELAY vs.

CAPACITIVE LOAD ON I/O  $V_L$

(DRIVING I/O $V_{CC}$ ,  $V_{CC} = 3.3V$ ,  $V_L = +0.9V$ )**

# 超低電圧レベルトランスレータ

## 標準動作特性(続き)

( $V_{CC} = +3.3V$ ,  $V_L = +0.9V$ ,  $T_A = +25^\circ C$ , MAX13003E.)

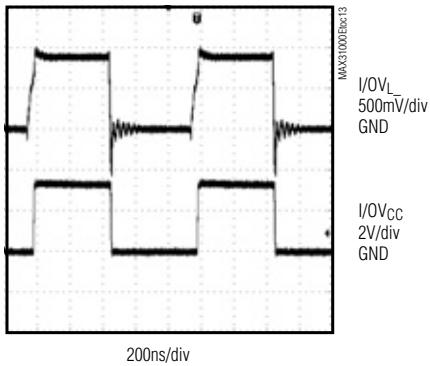

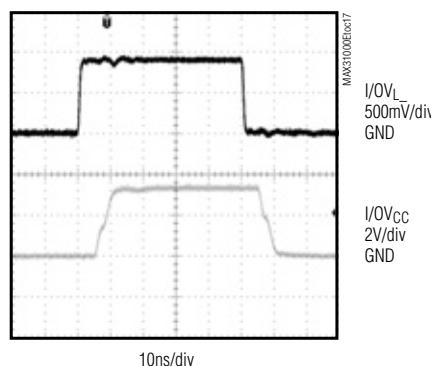

### OD RAIL-TO-RAIL DRIVING (MAX13005E)

(DRIVING I/OV<sub>L</sub>,  $V_{CC} = +3.3V$ ,

$V_L = +0.9V$ ,  $C_{I/OVCC} = 56pF$ ,

DATA RATE = 230Mbps,  $R_{PULLUP} = 1k\Omega$ )

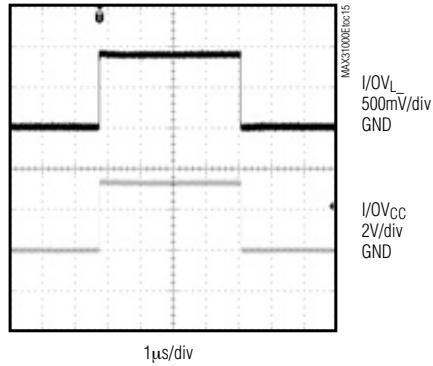

### OD RAIL-TO-RAIL DRIVING (MAX13002E)

(DRIVING I/OV<sub>L</sub>,  $V_{CC} = +3.3V$ ,

$V_L = +0.9V$ ,  $C_{I/OVCC} = 56pF$ ,

DATA RATE = 230kbps,  $R_{PULLUP} = 15k\Omega$ )

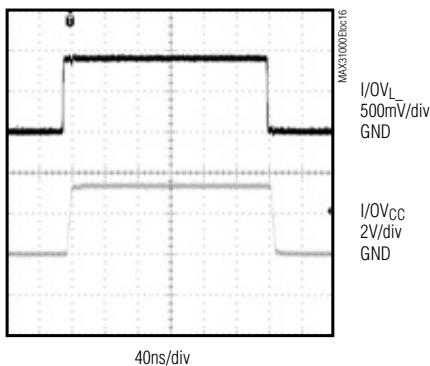

### RAIL-TO-RAIL DRIVING

(DRIVING I/OV<sub>L</sub>,  $V_{CC} = +3.3V$ ,  $V_L = +0.9V$ ,

$C_{I/OVCC} = 50pF$ , DATA RATE = 230kbps)

### RAIL-TO-RAIL DRIVING

(DRIVING I/OV<sub>L</sub>,  $V_{CC} = +3.3V$ ,  $V_L = +0.9V$ ,

$C_{I/OVCC} = 50pF$ , DATA RATE = 4Mbps)

### RAIL-TO-RAIL DRIVING

(DRIVING I/OV<sub>L</sub>,  $V_{CC} = +3.3V$ ,  $V_L = +0.9V$ ,

$C_{I/OVCC} = 50pF$ , DATA RATE = 20Mbps)

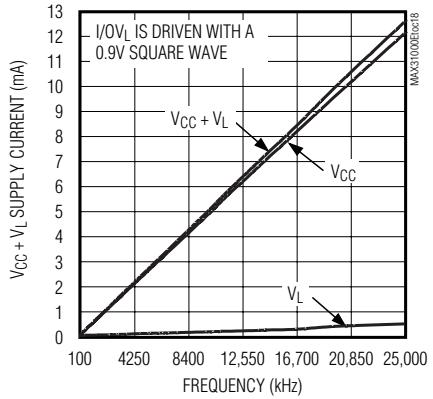

### $V_{CC} + V_L$ SUPPLY CURRENT vs. FREQUENCY

(DRIVING I/OV<sub>L</sub>,  $V_{CC} = +3.3V$ ,  $V_L = +0.9V$ )

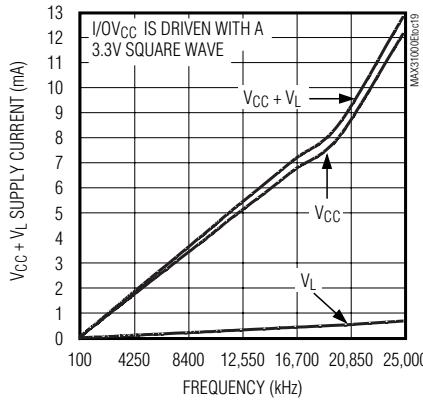

### $V_{CC} + V_L$ SUPPLY CURRENT vs. FREQUENCY

(DRIVING I/OV<sub>CC</sub>,  $V_{CC} = +3.3V$ ,  $V_L = +0.9V$ )

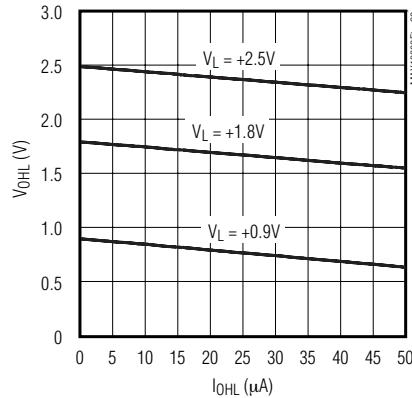

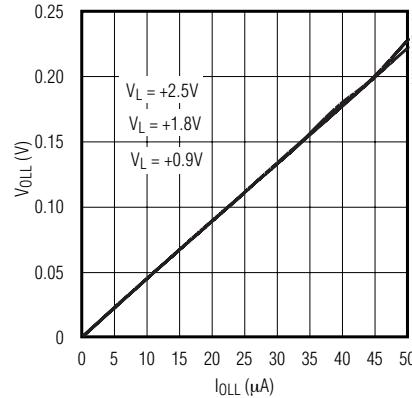

### $V_{OHL}$ vs. $I_{OHL}$ FOR $V_L$ SIDE

( $V_{CC} = 3.3V$ )

### $V_{OLL}$ vs. $I_{OLL}$ FOR $V_L$ SIDE

( $V_{CC} = 3.3V$ )

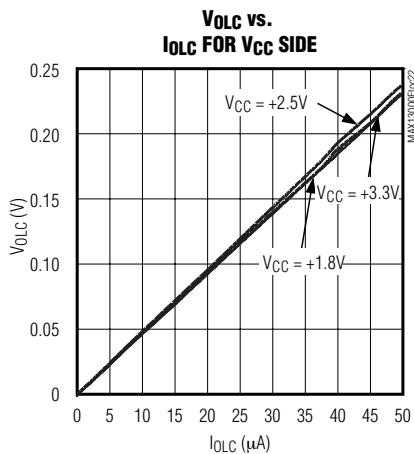

## 標準動作特性(続き)

( $V_{CC} = +3.3V$ ,  $V_L = +0.9V$ ,  $T_A = +25^\circ C$ , MAX13003E.)

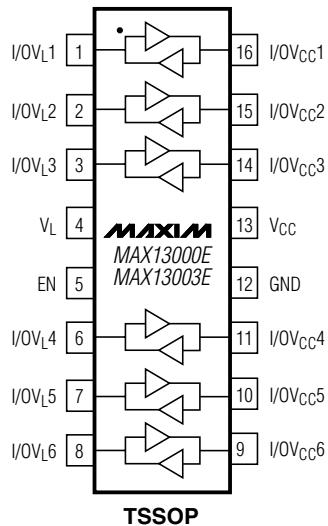

## 端子説明

### MAX13000E/MAX13003E

| 端子    |      | 名称            | 機能                                                                                                                                        |

|-------|------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| TSSOP | UCSP |               |                                                                                                                                           |

| 1     | B1   | I/O $V_L$ 1   | $V_L$ 基準のCMOS入力/出力1                                                                                                                       |

| 2     | B2   | I/O $V_L$ 2   | $V_L$ 基準のCMOS入力/出力2                                                                                                                       |

| 3     | A1   | I/O $V_L$ 3   | $V_L$ 基準のCMOS入力/出力3                                                                                                                       |

| 4     | A2   | $V_L$         | ロジック入力電圧、 $+0.9V \leq V_L \leq V_{CC}$ 。 $0.1\mu F$ のコンデンサで $V_L$ をGNDにバイパスします。                                                           |

| 5     | A3   | EN            | イネーブル入力。ENがローに引き下げられると、I/O $V_{CC}1$ からI/O $V_{CC}6$ とI/O $V_L$ 1からI/O $V_L$ 6がトライステートになります。通常動作には、ENをハイ( $V_L$ )にします。                    |

| 6     | A4   | I/O $V_L$ 4   | $V_L$ 基準のCMOS入力/出力4                                                                                                                       |

| 7     | B3   | I/O $V_L$ 5   | $V_L$ 基準のCMOS入力/出力5                                                                                                                       |

| 8     | B4   | I/O $V_L$ 6   | $V_L$ 基準のCMOS入力/出力6                                                                                                                       |

| 9     | C4   | I/O $V_{CC}6$ | $V_{CC}$ 基準のCMOS入力/出力6                                                                                                                    |

| 10    | C3   | I/O $V_{CC}5$ | $V_{CC}$ 基準のCMOS入力/出力5                                                                                                                    |

| 11    | D4   | I/O $V_{CC}4$ | $V_{CC}$ 基準のCMOS入力/出力4                                                                                                                    |

| 12    | D3   | GND           | グラウンド                                                                                                                                     |

| 13    | D2   | $V_{CC}$      | $V_{CC}$ 入力電圧、 $+1.5V \leq V_{CC} \leq 3.6V$ 。 $0.1\mu F$ のコンデンサで $V_{CC}$ をGNDにバイパスします。完全なESD保護には、 $V_{CC}$ に $1\mu F$ のバイパスコンデンサを接続します。 |

| 14    | D1   | I/O $V_{CC}3$ | $V_{CC}$ 基準のCMOS入力/出力3                                                                                                                    |

| 15    | C2   | I/O $V_{CC}2$ | $V_{CC}$ 基準のCMOS入力/出力2                                                                                                                    |

| 16    | C1   | I/O $V_{CC}1$ | $V_{CC}$ 基準のCMOS入力/出力1                                                                                                                    |

# 超低電圧レベルトランスレータ

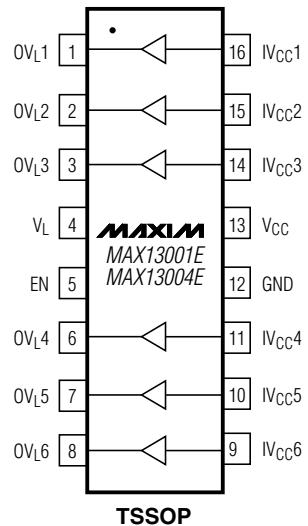

## 端子説明(続き)

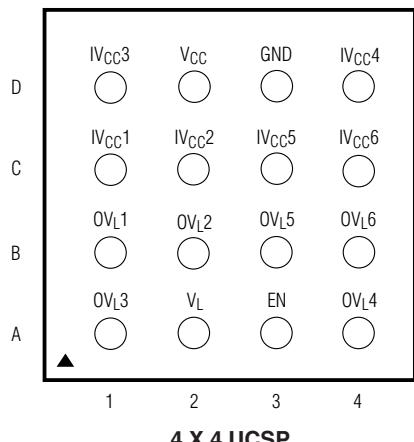

### MAX13001E/MAX13004E

| 端子    |      | 名称                 | 機能                                                                                                                                                 |

|-------|------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| TSSOP | UCSP |                    |                                                                                                                                                    |

| 1     | B1   | OV <sub>L</sub> 1  | V <sub>L</sub> 基準のCMOS出力1                                                                                                                          |

| 2     | B2   | OV <sub>L</sub> 2  | V <sub>L</sub> 基準のCMOS出力2                                                                                                                          |

| 3     | A1   | OV <sub>L</sub> 3  | V <sub>L</sub> 基準のCMOS出力3                                                                                                                          |

| 4     | A2   | V <sub>L</sub>     | ロジック入力電圧、+0.9V ≤ V <sub>L</sub> ≤ V <sub>CC</sub> 。0.1μFのコンデンサでV <sub>L</sub> をGNDにバイパスします。                                                        |

| 5     | A3   | EN                 | イネーブル入力。ENがローに引き下げられると、OV <sub>CC</sub> 1からOV <sub>CC</sub> 6とIV <sub>L</sub> 1からIV <sub>L</sub> 6がトライステートになります。通常動作には、ENをハイ(V <sub>L</sub> )にします。 |

| 6     | A4   | OV <sub>L</sub> 4  | V <sub>L</sub> 基準のCMOS出力4                                                                                                                          |

| 7     | B3   | OV <sub>L</sub> 5  | V <sub>L</sub> 基準のCMOS出力5                                                                                                                          |

| 8     | B4   | OV <sub>L</sub> 6  | V <sub>L</sub> 基準のCMOS出力6                                                                                                                          |

| 9     | C4   | IV <sub>CC</sub> 6 | V <sub>CC</sub> 基準のオープンドレイン対応入力6                                                                                                                   |

| 10    | C3   | IV <sub>CC</sub> 5 | V <sub>CC</sub> 基準のオープンドレイン対応入力5                                                                                                                   |

| 11    | D4   | IV <sub>CC</sub> 4 | V <sub>CC</sub> 基準のオープンドレイン対応入力4                                                                                                                   |

| 12    | D3   | GND                | グラウンド                                                                                                                                              |

| 13    | D2   | V <sub>CC</sub>    | V <sub>CC</sub> 入力電圧、+1.5V ≤ V <sub>CC</sub> ≤ 3.6V。0.1μFのコンデンサでV <sub>CC</sub> をGNDにバイパスします。完全なESD保護には、V <sub>CC</sub> に1μFのバイパスコンデンサを接続します。      |

| 14    | D1   | IV <sub>CC</sub> 3 | V <sub>CC</sub> 基準のオープンドレイン対応入力3                                                                                                                   |

| 15    | C2   | IV <sub>CC</sub> 2 | V <sub>CC</sub> 基準のオープンドレイン対応入力2                                                                                                                   |

| 16    | C1   | IV <sub>CC</sub> 1 | V <sub>CC</sub> 基準のオープンドレイン対応入力1                                                                                                                   |

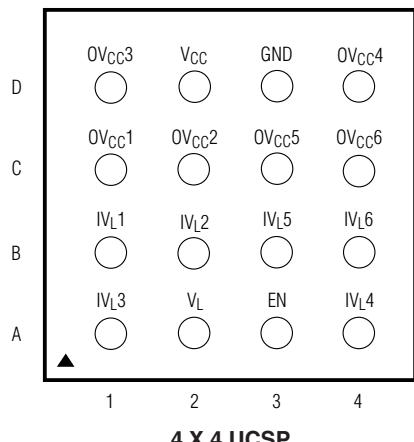

### 端子説明(続き)

#### MAX13002E/MAX13005E

| 端子    |      | 名称                 | 機能                                                                                                                                                 |

|-------|------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| TSSOP | UCSP |                    |                                                                                                                                                    |

| 1     | B1   | IV <sub>L</sub> 1  | V <sub>L</sub> 基準のオープンドレイン対応入力1                                                                                                                    |

| 2     | B2   | IV <sub>L</sub> 2  | V <sub>L</sub> 基準のオープンドレイン対応入力2                                                                                                                    |

| 3     | A1   | IV <sub>L</sub> 3  | V <sub>L</sub> 基準のオープンドレイン対応入力3                                                                                                                    |

| 4     | A2   | V <sub>L</sub>     | ロジック入力電圧、+0.9V ≤ V <sub>L</sub> ≤ V <sub>CC</sub> 。0.1μFのコンデンサでV <sub>L</sub> をGNDにバイパスします。                                                        |

| 5     | A3   | EN                 | イネーブル入力。ENがローに引き下げられると、OV <sub>CC</sub> 1からOV <sub>CC</sub> 6とIV <sub>L</sub> 1からIV <sub>L</sub> 6がトライステートになります。通常動作には、ENをハイ(V <sub>L</sub> )にします。 |

| 6     | A4   | IV <sub>L</sub> 4  | V <sub>L</sub> 基準のオープンドレイン対応入力4                                                                                                                    |

| 7     | B3   | IV <sub>L</sub> 5  | V <sub>L</sub> 基準のオープンドレイン対応入力5                                                                                                                    |

| 8     | B4   | IV <sub>L</sub> 6  | V <sub>L</sub> 基準のオープンドレイン対応入力6                                                                                                                    |

| 9     | C4   | OV <sub>CC</sub> 6 | V <sub>CC</sub> 基準のCMOS出力6                                                                                                                         |

| 10    | C3   | OV <sub>CC</sub> 5 | V <sub>CC</sub> 基準のCMOS出力5                                                                                                                         |

| 11    | D4   | OV <sub>CC</sub> 4 | V <sub>CC</sub> 基準のCMOS出力4                                                                                                                         |

| 12    | D3   | GND                | グランド                                                                                                                                               |

| 13    | D2   | V <sub>CC</sub>    | V <sub>CC</sub> 入力電圧、+1.5V ≤ V <sub>CC</sub> ≤ 3.6V。0.1μFのコンデンサでV <sub>CC</sub> をGNDにバイパスします。完全なESD保護には、V <sub>CC</sub> に1μFのバイパスコンデンサを接続します。      |

| 14    | D1   | OV <sub>CC</sub> 3 | V <sub>CC</sub> 基準のCMOS出力3                                                                                                                         |

| 15    | C2   | OV <sub>CC</sub> 2 | V <sub>CC</sub> 基準のCMOS出力2                                                                                                                         |

| 16    | C1   | OV <sub>CC</sub> 1 | V <sub>CC</sub> 基準のCMOS出力1                                                                                                                         |

# 超低電圧レベルトランスレータ

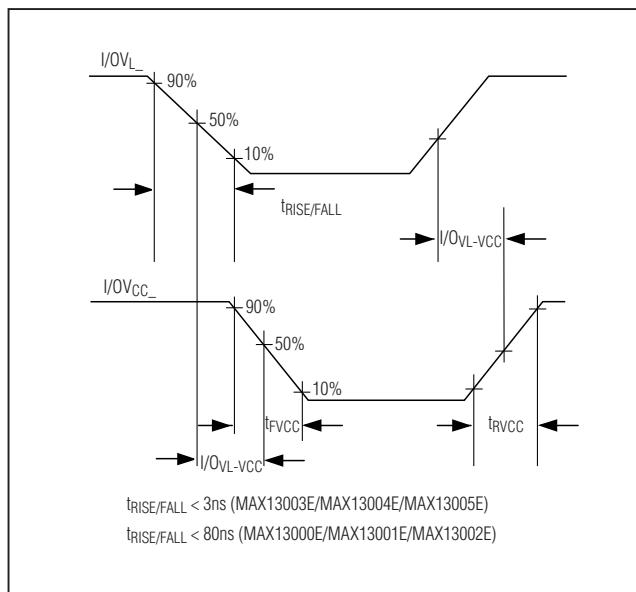

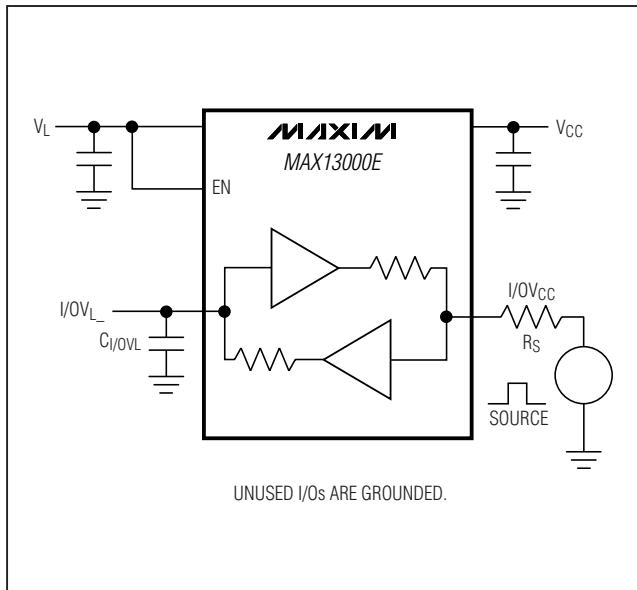

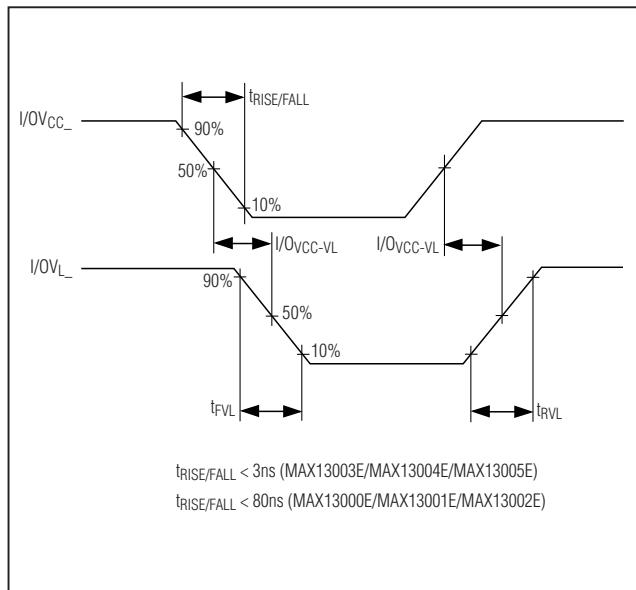

## 試験回路/タイミング図

図1a.  $I/OV_L$ の駆動図1b.  $I/OV_L$ 駆動のタイミング図2a.  $I/OV_{CC}$ の駆動図2b.  $I/OV_{CC}$ 駆動のタイミング

# 超低電圧レベルトランスレータ

**MAX13000E-MAX13005E**

## 試験回路/タイミング図(続き)

図3. EN後のI/OV<sub>L</sub>からI/OV<sub>CC</sub>までの伝搬遅延

図4. EN後のI/OV<sub>CC</sub>からI/OV<sub>L</sub>までの伝搬遅延

# 超低電圧レベルトランスレータ

## 詳細

ロジックレベルトランスレータのMAX13000E～MAX13005Eはマルチ電圧システムであり、データ転送に必要なレベルシフトを行います。外部印加電圧のV<sub>CC</sub>およびV<sub>L</sub>が、このデバイスの入出力側のロジックレベルを設定します。デバイスのV<sub>L</sub>側にあるロジック信号は、デバイスのV<sub>CC</sub>側により高い電圧ロジック信号として現れ、逆もまた同様となります。

MAX13000E/MAX13003Eは双方向レベルトランスレータで、DIRECTION入力を使用せずに任意の單一データライン上において両方向(V<sub>L</sub> ↔ V<sub>CC</sub>)のデータ変換を可能にします。MAX13001E/MAX13002E/MAX13004E/MAX13005Eは1方向レベルトランスレータで、任意の單一データライン上において1方向(V<sub>L</sub> → V<sub>CC</sub>、またはV<sub>CC</sub> → V<sub>L</sub>)でデータをレベルシフトします。1方向トランスレータのMAX13001E/MAX13002E/MAX13004E/MAX13005Eの入力は、CMOSおよびオープンドレイン(OD)出力とインタフェースする能力を備えています。詳細については、「型番」および「入力ドライバ要件」の項を参照してください。

MAX13000E～MAX13005Eは、+0.9V～+3.6VのV<sub>L</sub>を受け付けます。全デバイスは+1.5V～+3.6VのV<sub>CC</sub>範囲を持っているため、低電圧ASIC/PLDなどとこれらより高い電圧システム間のデータ転送に最適です。

MAX13000E～MAX13005Eは、シャットダウン時には4μA以下の低V<sub>CC</sub>自己消費電流と、2μA以下のV<sub>L</sub>自己消費電流を備えています。MAX13000E～MAX13005Eは、信号を外部で引き回すアプリケーションでの保護を向上するために、V<sub>CC</sub>側で±15kVのESD保護を備えています。このESD保護は、ヒューマンボディモデル(HBM)を使用して規定されています。MAX13000E/MAX13001E/MAX13002Eは、230kbpsの保証データレートで動作します。MAX13003E/MAX13004E/MAX13005Eは、V<sub>CC</sub>が+1.65Vを上回る場合は20Mbpsの保証データレートで動作します。

## レベル変換

通常動作には、+1.5V ≤ V<sub>CC</sub> ≤ +3.6V、および+0.9V ≤ V<sub>L</sub> ≤ V<sub>CC</sub>にします。電源投入のシーケンス時には、V<sub>L</sub>が絶対最大定格以内であれば、V<sub>L</sub> ≥ V<sub>CC</sub>でもデバイスに損傷を与えるません(「絶対最大定格(Absolute Maximum Ratings)」の項を参照)。電源シーケンス時には、V<sub>CC</sub>が無投入状態でV<sub>L</sub>が投入されると、1mAの電流をV<sub>L</sub>側の各負荷にソースすることができますが、デバイスはラッチャップしません。

MAX13000E～MAX13005Eは、常にV<sub>CC</sub>がV<sub>L</sub>以上になるように設計されていますが、V<sub>CC</sub>が遮断されても製品は損傷を受けず、ラッチャップしません。I/Oまた

は電源ライン上への過度のリーク電流を防止するには、V<sub>L</sub>側のI/Oをハイ状態に維持しておく必要があります。

MAX13000E～MAX13005Eの最高データレートは、負荷容量(「標準動作特性」を参照)、ドライバの出力インピーダンス、および動作電圧範囲に大きく依存します(「タイミング特性(Timing Characteristics)」表を参照)。

## オープンドレイン動作

MAX13001E/MAX13002E/MAX13004E/MAX1305Eは、外付けオープンドレインドライバに対応するよう専用設計された入力段を備えています。オープンドレインドライバの使用時には、MAX13001E/MAX13002E/MAX13004E/MAX13005Eは1方向専用モードで動作し、OD側からCMOS側に変換します。性能を向上するために、立上り/立下り時間アクセラレータがCMOS側とOD側の両側に配置されています。「入力ドライバ要件」の項を参照してください。正常に動作させるために、15kΩ以上のプルアップ抵抗を使用しないでください。また、動作を高速化するには、より低いプルアップ抵抗が必要になる場合があります。

## 入力ドライバ要件

MAX13000E～MAX13005Eは、トランスレータがCMOSからCMOSへのトランスレータまたはODからCMOSへのトランスレータであることに加え、製品の速度に基づいた4種類のアーキテクチャを装備しています。

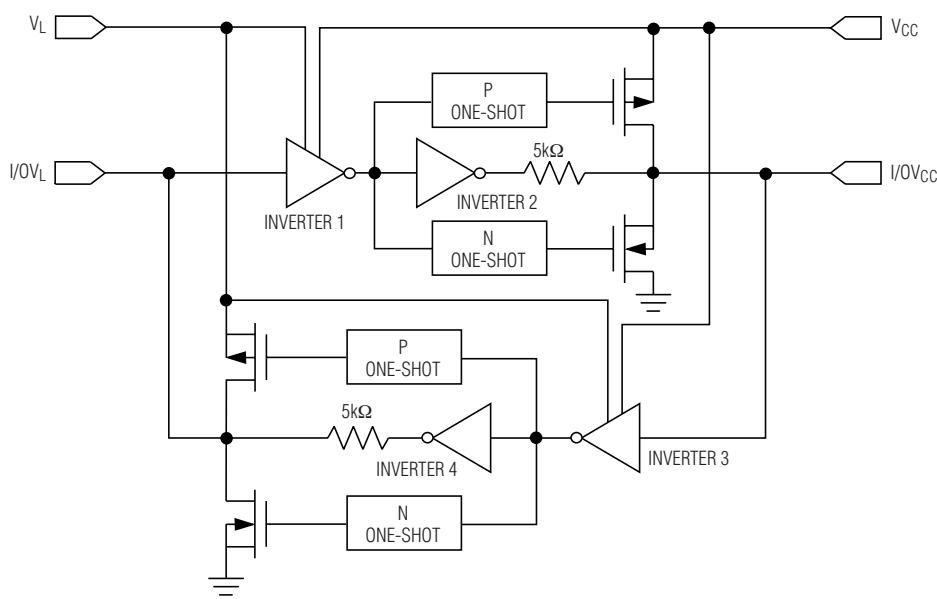

### 20MbpsのCMOSとCMOS間の双方向トランスレータ(MAX13003E)

MAX13003Eのアーキテクチャは、ワンショットアクセラレータ出力段に基づいています(図5)。アクセラレータ出力段は、I/OV<sub>L</sub>またはI/OV<sub>CC</sub>の入力側のいずれかのトランスレータに状態変化がある場合を除き、常にトライステート状態です。ワンショット出力段がアクティブになり、I/Oの容量を充/放電する期間には、ショートパルスが発生します。

双方向性であることから、I/OV<sub>CC</sub>およびI/OV<sub>L</sub>のアクセラレータ段は、ローからハイまたはハイからローへのI/Oの遷移時にアクティブになります。このため、トランスレータを駆動中の外部ソースに一部の電流が流れる場合があります。ただし、この動作によって被駆動側の遷移が高速化されます。

MAX13003Eの入力を駆動するデバイスのタイプは、通常、出力駆動電流能力(I<sub>OUT</sub>)によって規定されます。MAX13003Eの入力を駆動する時には、最高到達速度は、外付けドライバの駆動電流によって制約されます。20Mbpsの最高可能スループットを実現するには、外付けドライバが以下の要件に適合する必要があります。

$$I_{OUT} \geq 1.67 \times 10^8 \times V \times (C_{IN} + C_P)$$

# 超低電圧レベルトランスレータ

図5. 20MbpsのCMOSとCMOS間の双方向トランスレータのアーキテクチャ

ここで、 $C_p$ は配線の寄生容量、 $V$ は被駆動側の電源電圧(すなわち $V_L$ または $V_{CC}$ )、および $C_{IN}$ は被駆動側の入力容量です( $V_L$ 側は $C_{IN} = 10\text{pF}$ 、 $V_{CC}$ 側は $C_{IN} = 20\text{pF}$ )。

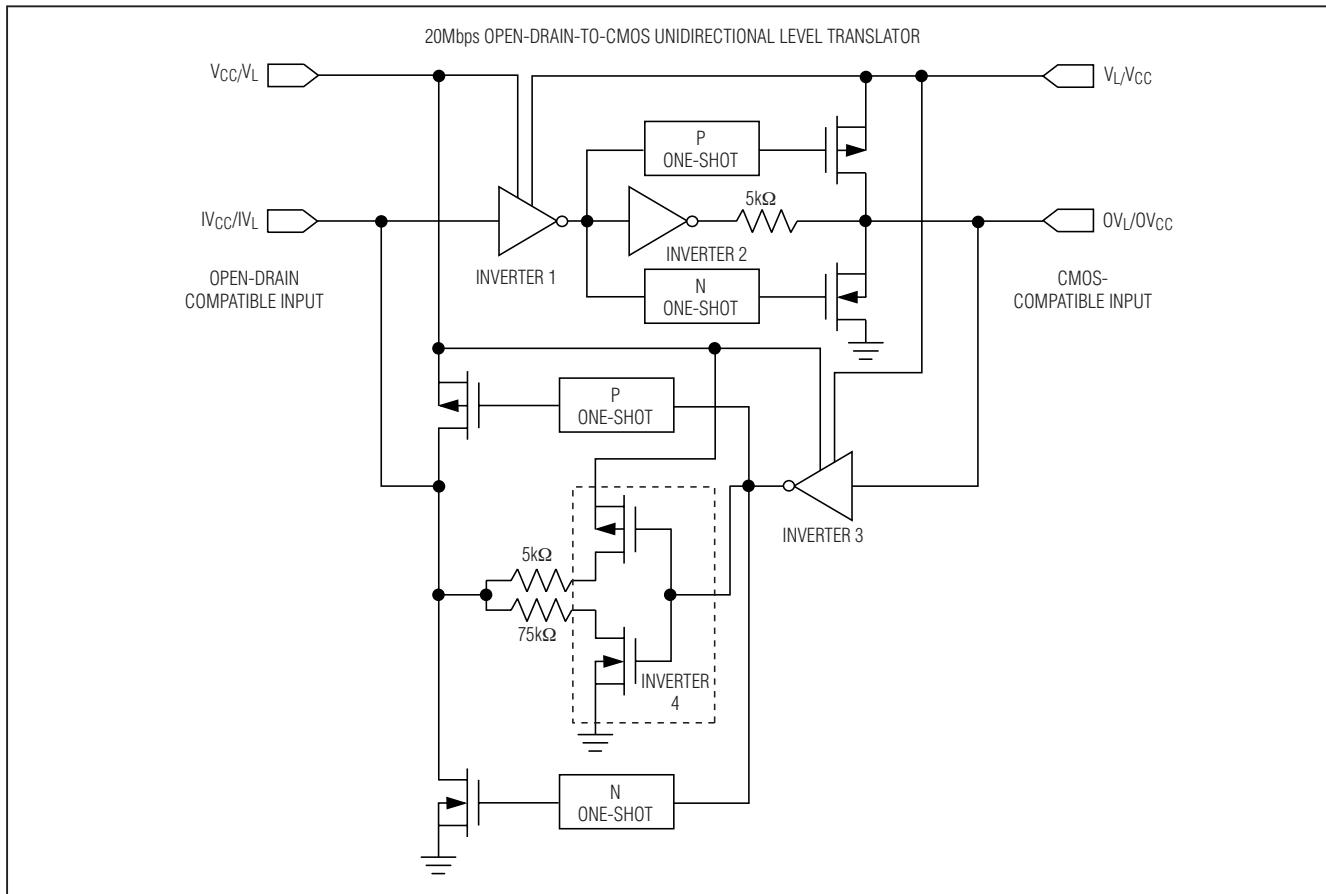

## 20MbpsのODからCMOSへの1方向トランスレータ(MAX13004E/MAX13005E)

MAX13004E/MAX13005Eのアーキテクチャは、双方向のCMOSとCMOS間のトランスレータのアーキテクチャとほぼ同じで、唯一の違いは、駆動側の出力インバータ(インバータ4)がオープンドレイン出力の駆動能力に対応することです(図6)。

正常に動作させるには、プルアップ抵抗をオープンドレイン出力から駆動側の電源に接続する必要があります。15kΩ以下のプルアップ抵抗を使用します。

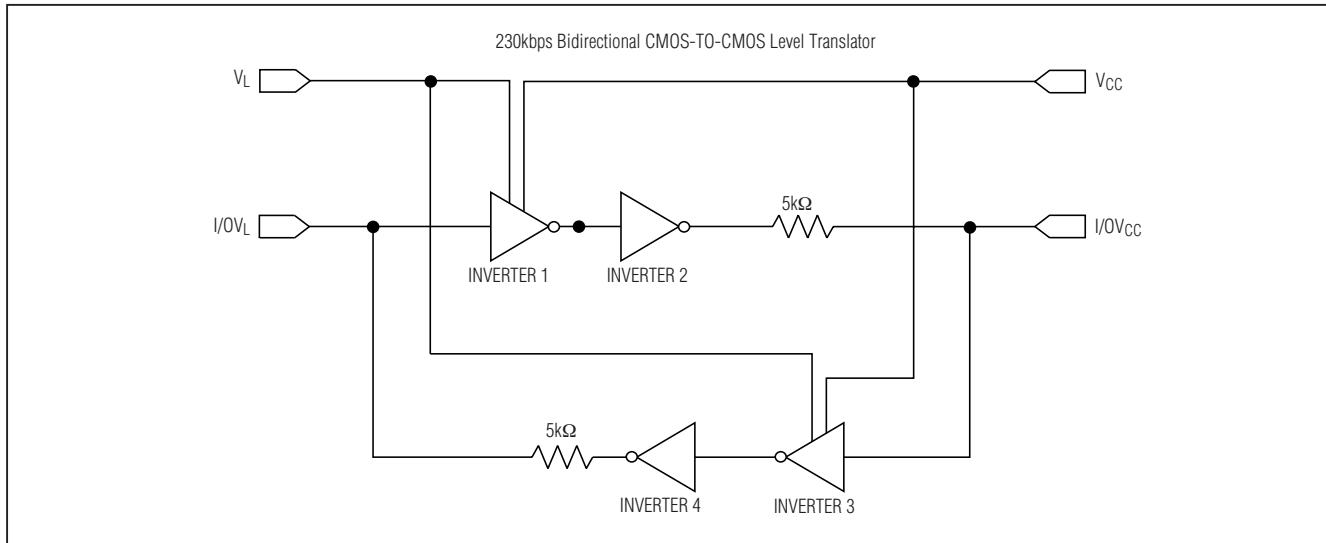

## 230kbpsのCMOSとCMOS間の双方向トランスレータ(MAX13000E)

このデバイスが処理する遷移は230kbpsのデータレートで制限されるため、MAX13000Eのアーキテクチャにはワンショットアクセラレータ出力段がありません(図7)。

正常に動作させるには、ドライバは次の条件、すなわち、出力インピーダンスは最大1kΩで、1mAの最小出力電流を満たす必要があります。

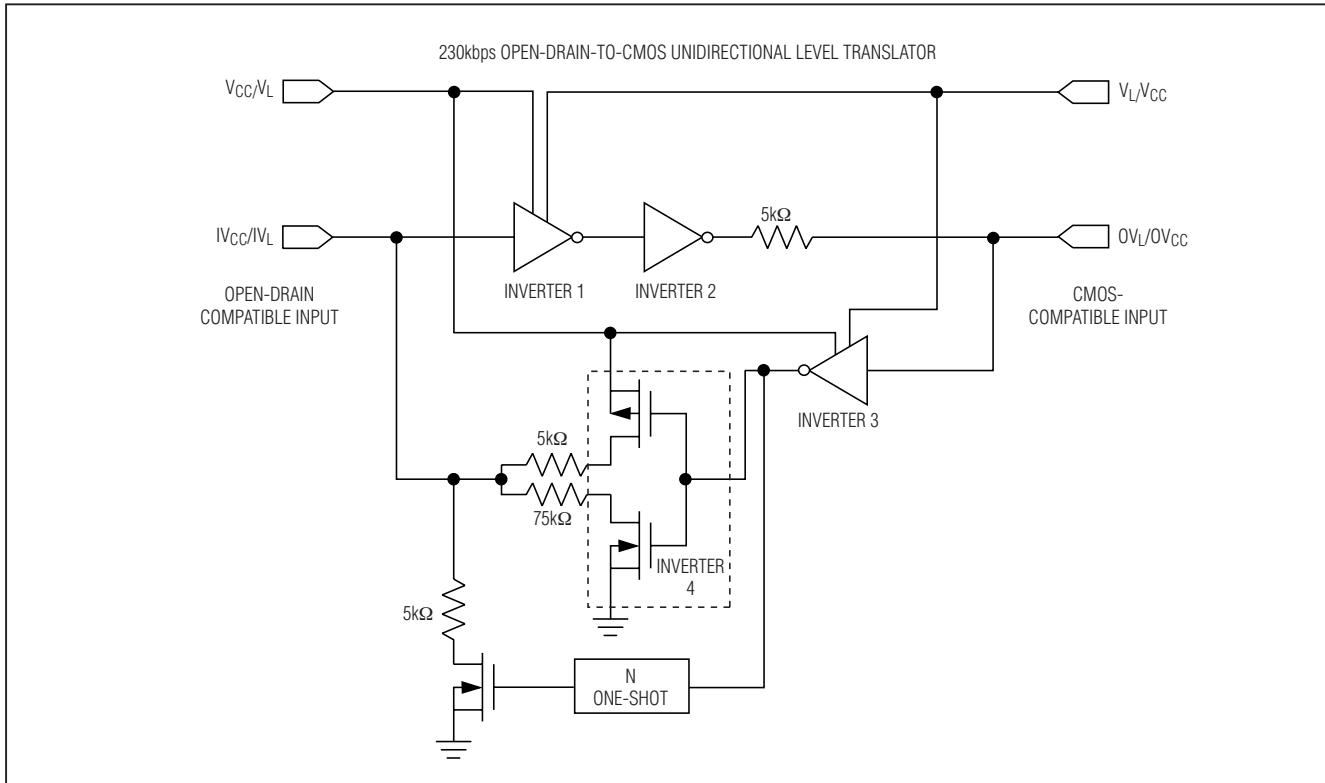

## 230kbpsのODからCMOSへの1方向トランスレータ(MAX13001E/MAX13002E)

MAX13001E/MAX13002Eのアーキテクチャは230kbpsのCMOS-CMOS製品のアーキテクチャとほぼ同じですが、駆動側のオープンドレイン出力の駆動能力に対応し、また1つだけワンショット出力段を備えている点が異なります(図8)。

正常に動作させるには、プルアップ抵抗をオープンドレイン出力から駆動側の電源に接続する必要があります。15kΩ以下のプルアップ抵抗を使用します。

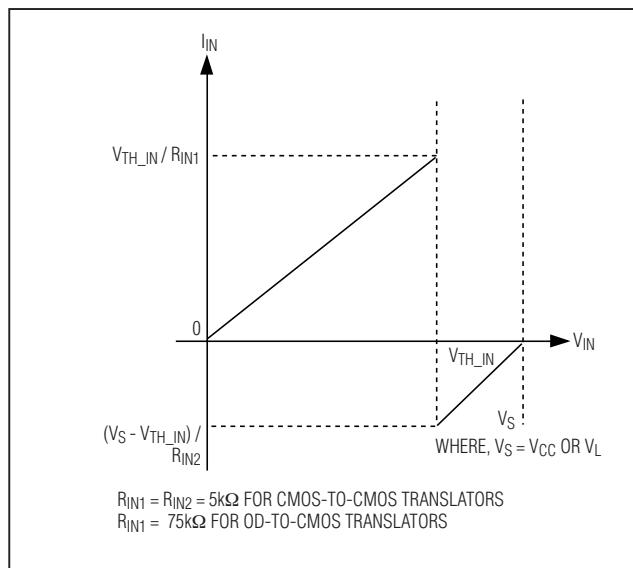

図9は、上記の構成のすべてに対する標準入力電流対入力電圧のグラフを示しています。

## 出力モードのイネーブル(EN)

MAX13000E～MAX13005Eは、イネーブル(EN)入力を備えています。MAX13000E～MAX13005EのI/Oをトライステートモードに設定するには、ENをローにします。通常動作には、ENをハイ( $V_L$ )にします。

## ±15kVのESD保護

マキシムの全デバイスと同様に、取り扱いと組立て時に発生する静電放電から保護するために、ESD保護構造がすべての端子に採用されています。I/OV<sub>CC</sub>ラインは、静電放電から特別に保護されています。マキシムの技術者は、損傷を受けずに±15kVのESDから端子を保護する最先端の構造を開発しました。このESD構造は、標準動作、トライステート出力モード、およびパ

# 超低電圧レベルトランスレータ

図6. 20MbpsのODからCMOSへの1方向トランスレータのアーキテクチャ

図7. 230kbpsのCMOSとCMOS間の双方向トランスレータのアーキテクチャ

図8. 230kbpsのODからCMOSへの1方向トランスレータのアーキテクチャ

図9. 標準的な  $I_{IN}$  対  $V_{IN}$

ワーダウンのどの状態でもESDに対する高耐性を備えています。ESDが発生しても、マキシムのEバージョンはラッチアップなしで動作し続けますが、競合製品はラッチする場合があり、ラッチアップを解消するためにはパワーダウンする必要があります。

ESD保護を様々な方法で試験することができます。MAX13000E～MAX13005EのI/OV<sub>CC</sub>ラインは、ヒューマンボディモデルを用いた±15kVまでの保護が特徴です。

ESD試験条件

ESD性能は、各種条件に依存します。試験のセットアップ、試験方法、および試験結果を記載した信頼性レポートについては、マキシムにお問い合わせください。

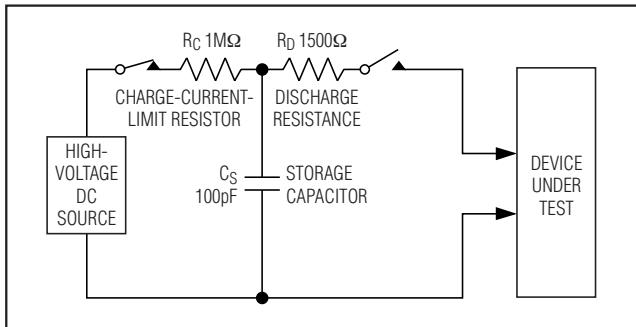

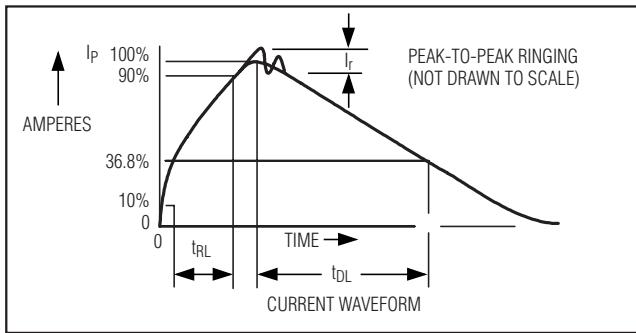

## ヒューマンボディモデル

図10はヒューマンボディモデルを示し、図11は低インピーダンスに放電されると発生する電流波形を示しています。このモデルは、測定対象のESD電圧まで充電された100pFのコンデンサから構成されており、この電圧は $1.5\text{k}\Omega$ の抵抗を通じて試験デバイスに放電されます。

# 超低電圧レベルトランスレータ

図10. ヒューマンボディによるESD試験モデル

図12. IEC 61000-4-2による接触放電試験モデル

図11. ヒューマンボディモデルによる電流波形

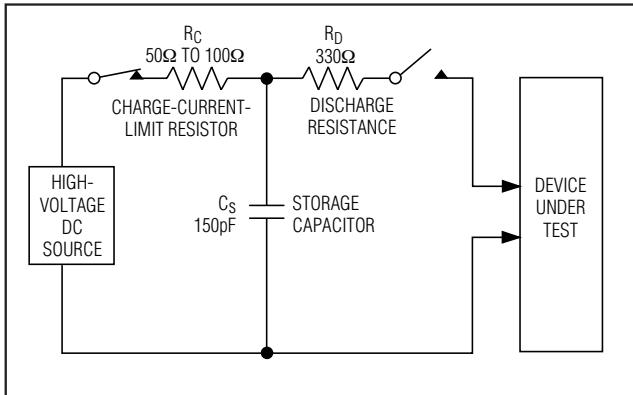

## IEC 61000-4-2規格のESD保護

IEC 61000-4-2規格(図12)は、電子システムのESD耐久性を規定しています。IEC 61000-4-2モデルは、330Ωの抵抗を通じてデバイスに放電される150pFのコンデンサを規定しています。V<sub>CC</sub>側のMAX13000E～MAX13005EのI/Oは、IEC 61000-4-2規格に対する定格です(8kVの接触放電および±10kVのエアギャップ放電)。

IEC 61000-4-2モデルは、より小さい直列抵抗とコンデンサの大容量化のため、HBM(ヒューマンボディモデル)に比べて高いピーク電流とより多くのエネルギーを放電します。

## アプリケーション情報

### 電源のデカップリング

リップルと不適切データの伝送が起きることを低減するには、0.1μFのコンデンサでV<sub>L</sub>およびV<sub>CC</sub>をグランドにバイパスします。完全な±15kV ESD保護を実現するには、1μFのコンデンサでV<sub>CC</sub>をグランドにバイパスします。すべてのコンデンサを電源入力にできるだけ近接して配置します。

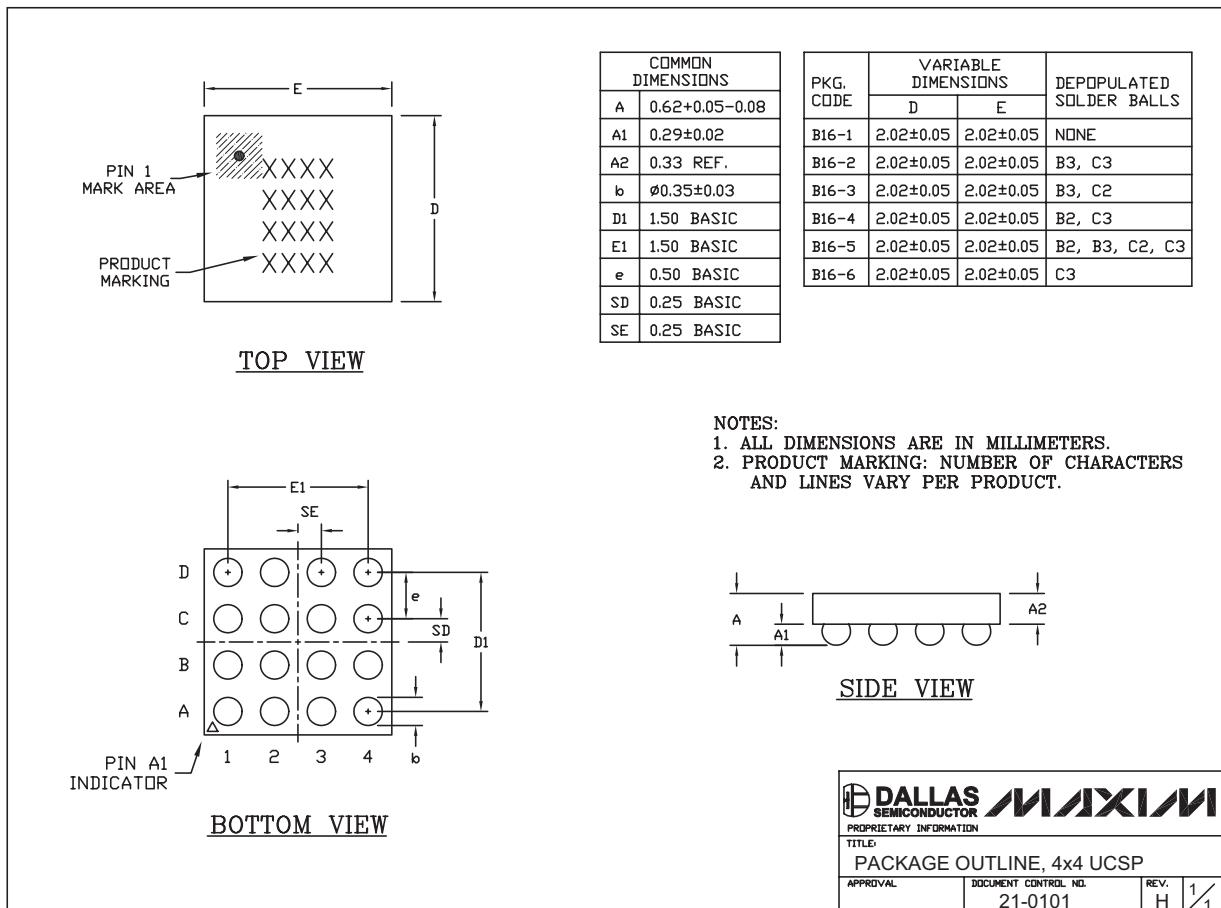

## UCSPパッケージについて

基本的なUCSPパッケージ情報とプリント回路のレイアウトに関しては、マキシムアプリケーションノート『ウェハレベルチップスケールパッケージ』を参照してください。

## UCSPの信頼性

チップスケールパッケージ(UCSP)は、従来の機械的信頼性試験を通じてパッケージされた製品に対して、同様に機能しない場合もある独自のパッケージングフォームファクタです。UCSPの信頼性は、ユーザの組立て方法、回路基板の材料、および使用環境などに全体的に関連しています。UCSPパッケージの使用を検討する際には、こうした面を十分に検討する必要があります。動作寿命試験と耐湿性による性能は、ウェーハ製造プロセスで基本的に決まるため、有意差はありません。

機械的ストレス性能は、UCSPパッケージの大きな検討事項です。UCSPはユーザのプリント基板に直接半田接合によって取り付けられ、パッケージ製品のリードフレームの固有応力緩和より劣っています。半田接合の完全性を検討する必要があります。マキシムの認定計画、試験データ、および推奨事項に関する情報は、japan.maxim-ic.comのマキシムのウェブサイトにあるUCSPアプリケーションノートで詳しく説明されています。

# 超低電圧レベルトランスレータ

**MAX13000E-MAX13005E**

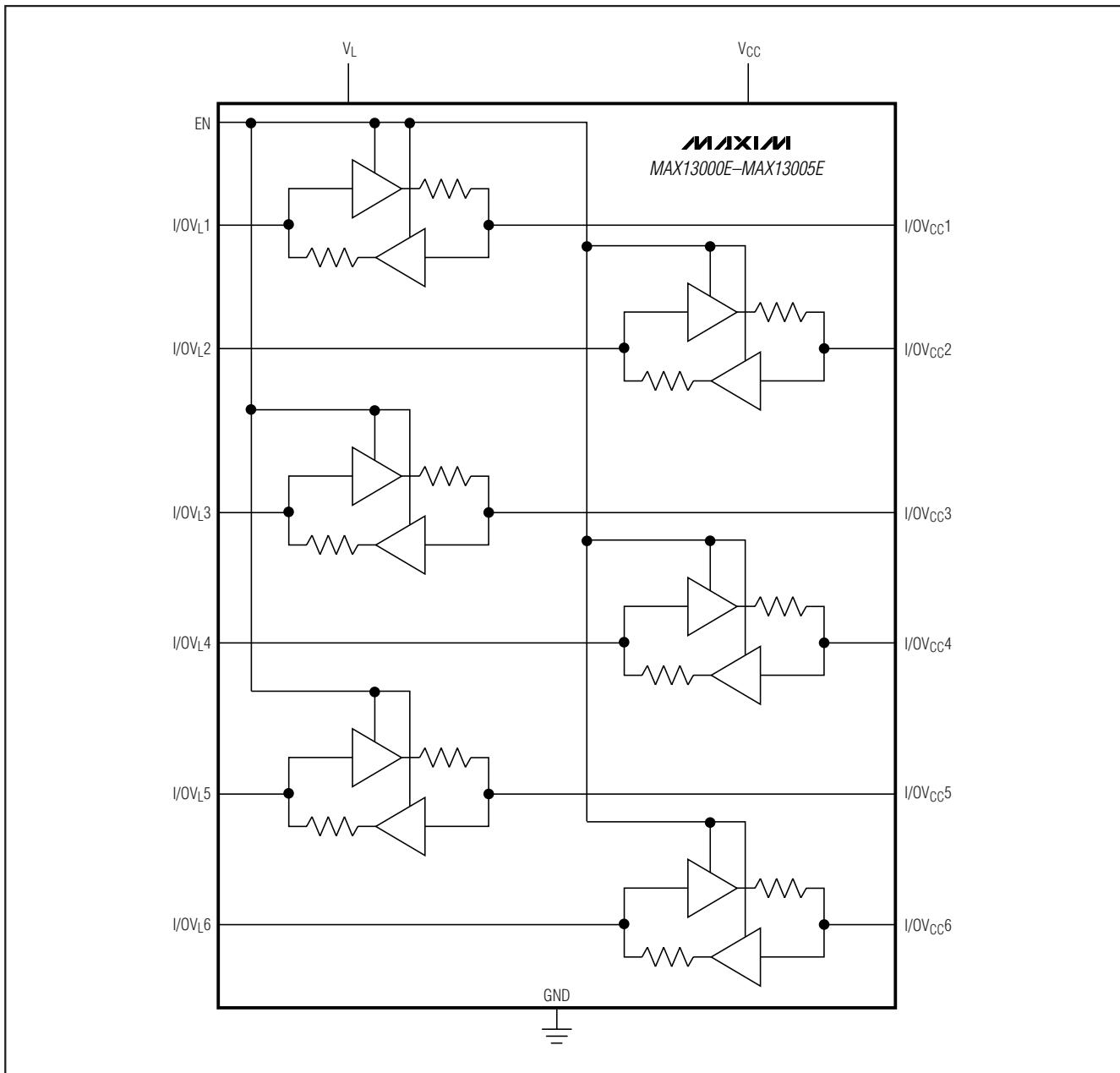

## ファンクションダイアグラム

# 超低電圧レベルトランスレータ

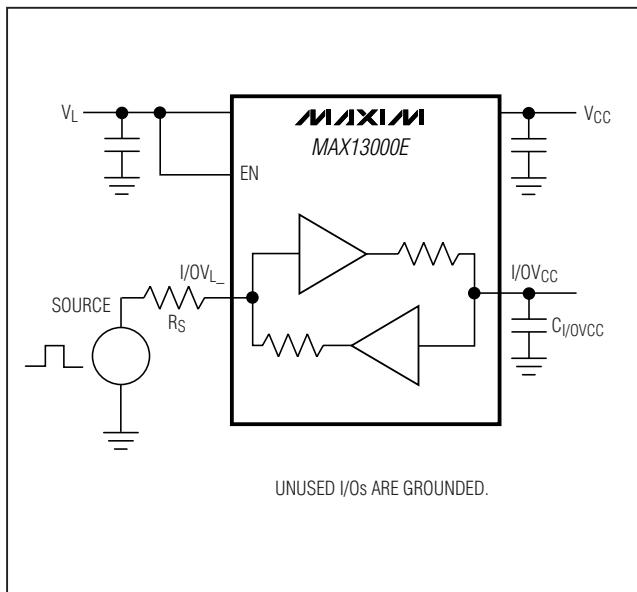

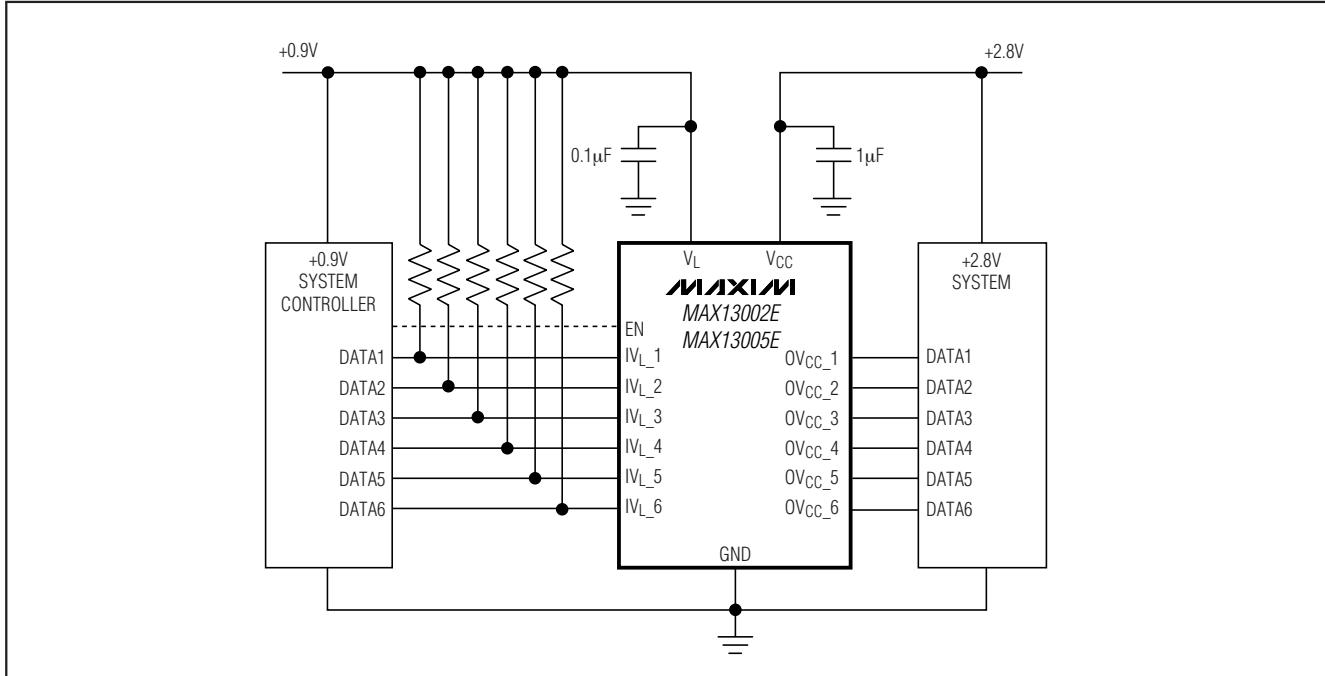

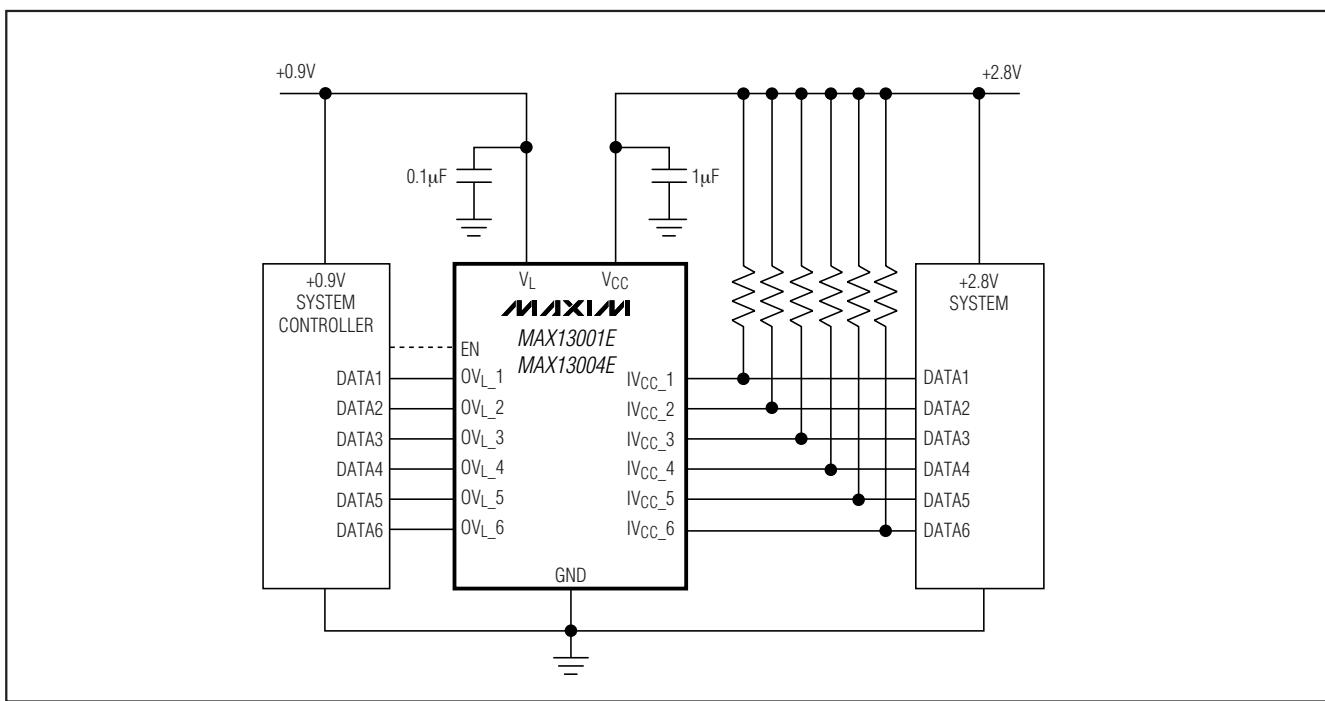

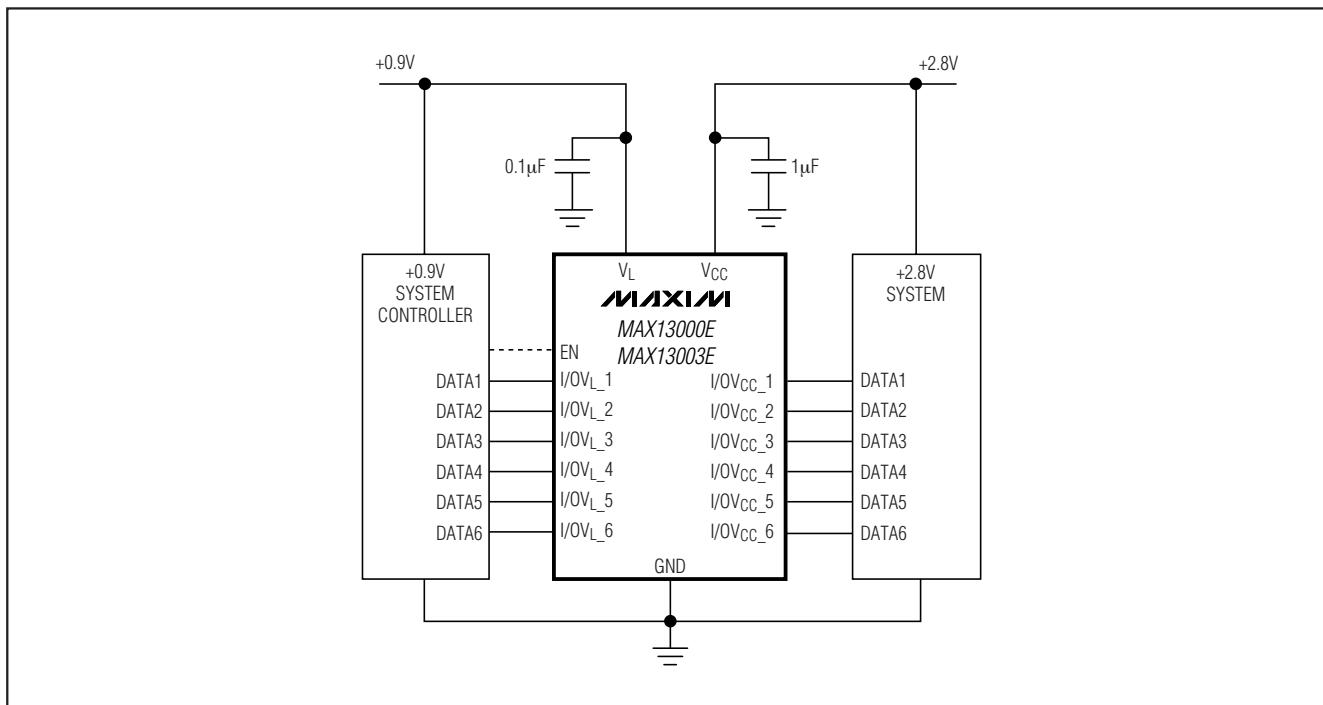

## 標準動作回路

### 標準動作回路(続き)

### 選択ガイド

| PART      | DATA RATE<br>(bps) | NUMBER OF<br>BIDIRECTIONAL<br>TRANSLATORS | NUMBER OF<br>$V_L \rightarrow V_{CC}$<br>TRANSLATORS | NUMBER OF<br>$V_{CC} \rightarrow V_L$<br>TRANSLATORS | TRANSLATOR<br>CONFIGURATION |

|-----------|--------------------|-------------------------------------------|------------------------------------------------------|------------------------------------------------------|-----------------------------|

| MAX13000E | 230k               | 6                                         | —                                                    | —                                                    | CMOS-to-CMOS                |

| MAX13001E | 230k               | —                                         | —                                                    | 6                                                    | OD-to-CMOS                  |

| MAX13002E | 230k               | —                                         | 6                                                    | —                                                    | OD-to-CMOS                  |

| MAX13003E | 20M                | 6                                         | —                                                    | —                                                    | CMOS-to-CMOS                |

| MAX13004E | 20M                | —                                         | —                                                    | 6                                                    | OD-to-CMOS                  |

| MAX13005E | 20M                | —                                         | 6                                                    | —                                                    | OD-to-CMOS                  |

# 超低電圧レベルトランスレータ

## ピン配置(続き)

BOTTOM VIEW

MAX13001E/MAX13004E

4 X 4 UCSP

MAX13002E/MAX13005E

4 X 4 UCSP

TOP VIEW

TSSOP

TSSOP

TSSOP

# 超低電圧レベルトランスレータ

MAX13000E-MAX13005E

## 型番(続き)

| PART                | TEMP RANGE     | PIN-PACKAGE               |

|---------------------|----------------|---------------------------|

| MAX13000EEBE-T*     | -40°C to +85°C | 16 UCSP-16<br>(4mm × 4mm) |

| <b>MAX13001EEUE</b> | -40°C to +85°C | 16 TSSOP                  |

| MAX13001EEBE-T*     | -40°C to +85°C | 16 UCSP-16<br>(4mm × 4mm) |

| <b>MAX13002EEUE</b> | -40°C to +85°C | 16 TSSOP                  |

| MAX13002EEBE-T*     | -40°C to +85°C | 16 UCSP-16<br>(4mm × 4mm) |

| <b>MAX13003EEUE</b> | -40°C to +85°C | 16 TSSOP                  |

| MAX13003EEBE-T*     | -40°C to +85°C | 16 UCSP-16<br>(4mm × 4mm) |

| <b>MAX13004EEUE</b> | -40°C to +85°C | 16 TSSOP                  |

| MAX13004EEBE-T*     | -40°C to +85°C | 16 UCSP-16<br>(4mm × 4mm) |

| <b>MAX13005EEUE</b> | -40°C to +85°C | 16 TSSOP                  |

| MAX13005EEBE-T*     | -40°C to +85°C | 16 UCSP-16<br>(4mm × 4mm) |

## チップ情報

PROCESS: BiCMOS

\*開発中の製品。入手性についてはお問い合わせください。

# 超低電圧レベルトランスレータ

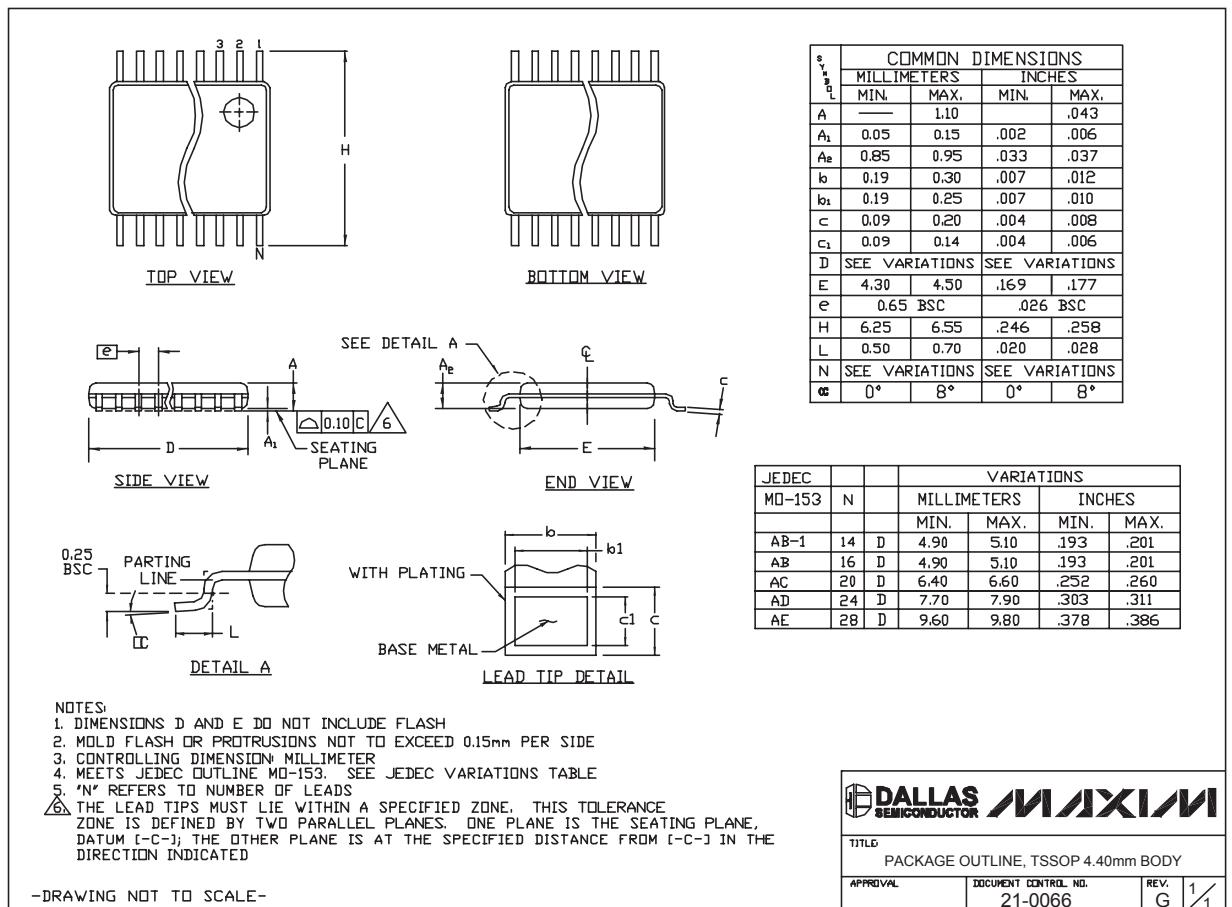

## パッケージ

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、[japan.maxim-ic.com/packages](http://japan.maxim-ic.com/packages)をご参照下さい。)

# 超低電圧レベルトランスレータ

**MAX13000E-MAX13005E**

## パッケージ(続き)

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、[japan.maxim-ic.com/packages](http://japan.maxim-ic.com/packages)をご参照下さい。)

**マキシム・ジャパン株式会社**

〒169-0051 東京都新宿区西早稲田3-30-16(ホリゾン1ビル)

TEL. (03)3232-6141 FAX. (03)3232-6149

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。マキシムは隨時予告なく回路及び仕様を変更する権利を留保します。

**Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600**

25

© 2005 Maxim Integrated Products, Inc. All rights reserved. **MAXIM** is a registered trademark of Maxim Integrated Products, Inc.