# +2.375V、低電力、8チャネル、シリアル12ビットADC

**MAX1245**

## 概要

MAX1245は、8チャネルマルチプレクサ、広帯域幅トラック/ホールド、シリアルインターフェースの機能を備えた、高速変換で超低消費電力の12ビットデータ収集システムです。+2.375V～+3.3Vの単一電源で動作し、アナログ入力はソフトウェアによりユニポーラ/バイポーラ、およびシングルエンド/差動動作に設定することができます。

4線式シリアルインターフェースは、外部ロジックを使用せずに直接SPI™、QSPI™、およびMICROWIRE™機器に接続することができます。シリアルストローブ出力により、TMS320ファミリのデジタル信号プロセッサに直接接続することができます。MAX1245は外部リファレンスで動作し、内部クロックまたは外部シリアルインターフェースクロックを用いることで、逐次比較型のアナログ-ディジタル変換を行います。

このデバイスは、ハード配線されたSHDNピンおよびソフトウェア選択によるパワーダウン機能を備えており、また変換終了時に自動的にシャットダウンするように設定することも可能です。MAX1245はシリアルインターフェースにアクセスすることでパワーアップし、ターンオンが速いため、変換と変換の間にシャットダウンすることができます。これにより、サンプリングレートが低い場合には消費電流を10μA以下に抑えることができます。

MAX1245は20ピンDIPパッケージ、および8ピンDIPよりも30%小さいSSOPパッケージで提供されます。電源電圧が+2.7V～+5.25Vの動作には、ピンコンパチブルのMAX147を使用してください。

## アプリケーション

|              |       |

|--------------|-------|

| ポータブルデータロギング | 医療機器  |

| バッテリ駆動機器     | データ収集 |

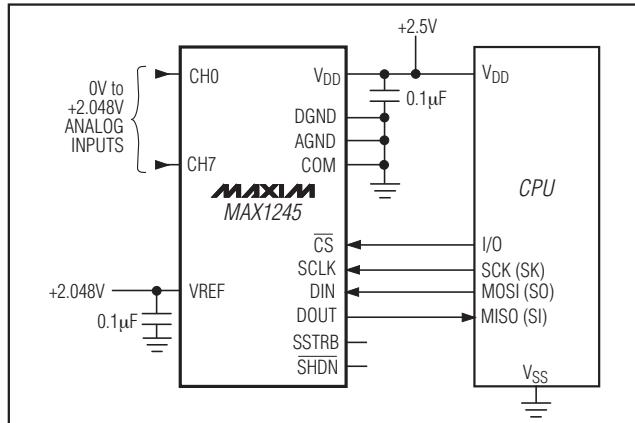

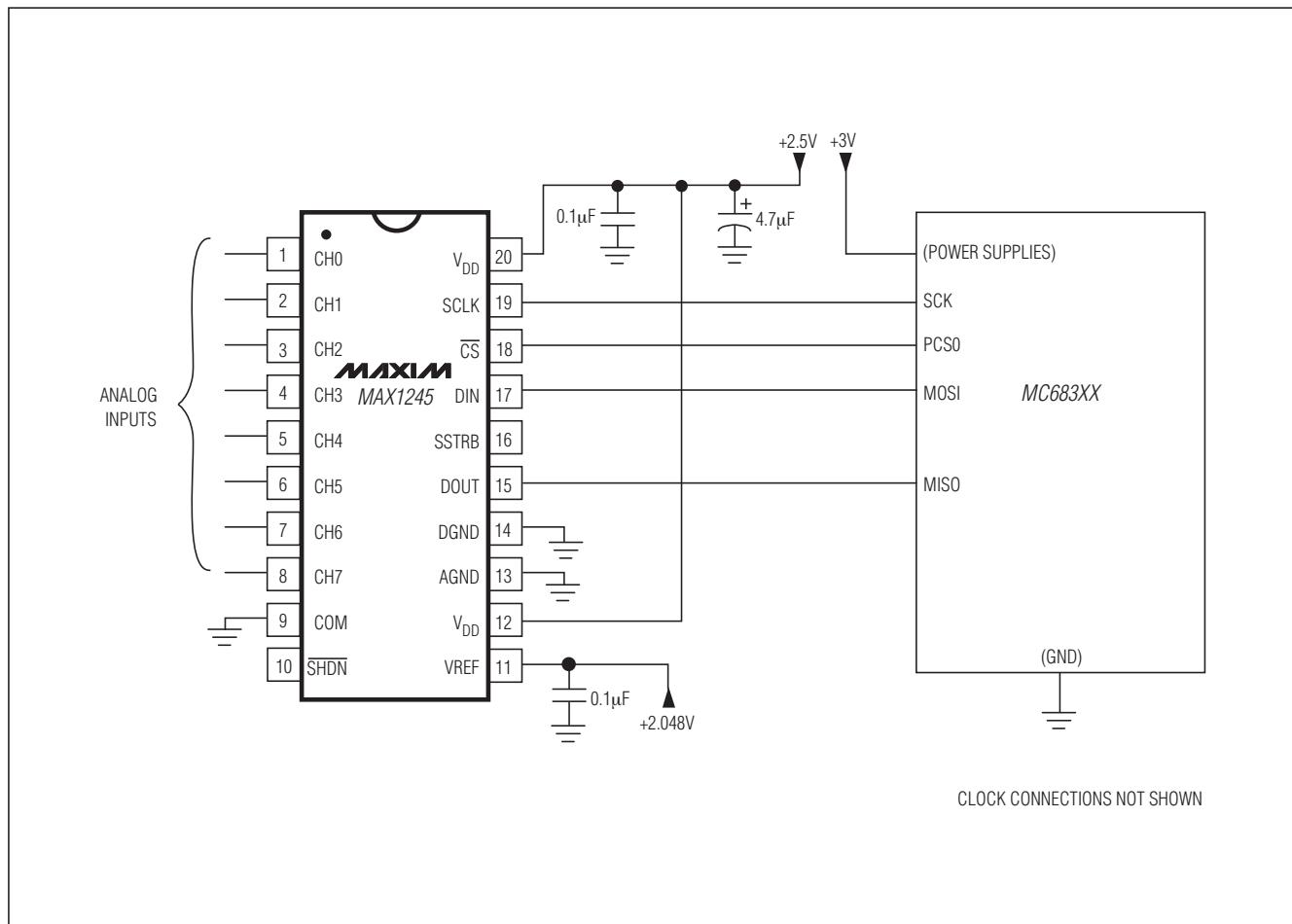

## 標準動作回路

SPIおよびQSPIは、Motorola, Inc.の商標です。MICROWIREはNational Semiconductor Corp.の商標です。

## 特長

- ◆ 単一電源 : +2.375V～+3.3V

- ◆ アナログ入力 : 8チャネルシングルエンドまたは4チャネル差動

- ◆ 低電力 : 0.8mA (100ksps)

10μA (1ksps)

1μA (パワーダウンモード)

- ◆ 内部トラック/ホールドサンプリングレート : 100kHz

- ◆ 4線式シリアルインターフェース : SPI/QSPI/MICROWIRE/TMS320コンパチブル

- ◆ ユニポーラまたはバイポーラ入力 : ソフトウェアで設定

- ◆ パッケージ : 20ピンDIP/SSOP

## 型番

| PART*       | TEMP RANGE     | PIN-PACKAGE    | INL (LSB) |

|-------------|----------------|----------------|-----------|

| MAX1245ACPP | 0°C to +70°C   | 20 Plastic DIP | ±1/2      |

| MAX1245BCPP | 0°C to +70°C   | 20 Plastic DIP | ±1        |

| MAX1245ACAP | 0°C to +70°C   | 20 SSOP        | ±1/2      |

| MAX1245BCAP | 0°C to +70°C   | 20 SSOP        | ±1        |

| MAX1245AEPP | -40°C to +85°C | 20 Plastic DIP | ±1/2      |

| MAX1245BEPP | -40°C to +85°C | 20 Plastic DIP | ±1        |

| MAX1245AEAP | -40°C to +85°C | 20 SSOP        | ±1/2      |

| MAX1245BEAP | -40°C to +85°C | 20 SSOP        | ±1        |

\*その他の表面実装パッケージについてはお問い合わせください。

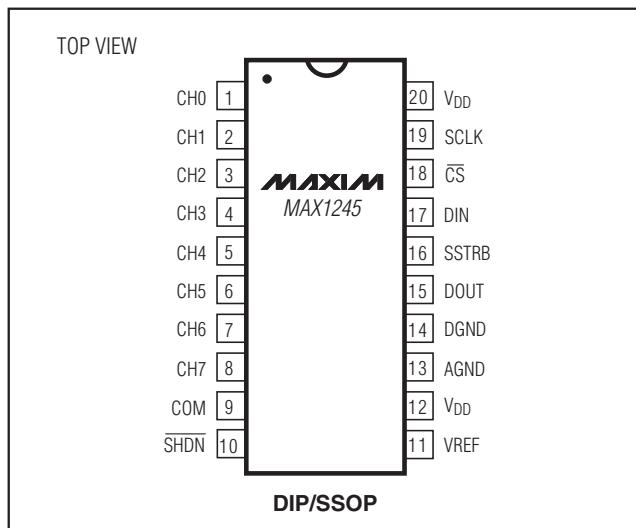

## ピン配置

# +2.375V、低電力、8チャネル、 シリアル12ビットADC

## ABSOLUTE MAXIMUM RATINGS

|                                                             |                                   |

|-------------------------------------------------------------|-----------------------------------|

| V <sub>DD</sub> to AGND, DGND .....                         | -0.3V to +6V                      |

| AGND to DGND .....                                          | -0.3V to +0.3V                    |

| CH0–CH7, COM to AGND, DGND .....                            | -0.3V to (V <sub>DD</sub> + 0.3V) |

| VREF to AGND .....                                          | -0.3V to (V <sub>DD</sub> + 0.3V) |

| Digital Inputs to DGND .....                                | -0.3V to +6V                      |

| Digital Outputs to DGND .....                               | -0.3V to (V <sub>DD</sub> + 0.3V) |

| Digital Output Sink Current .....                           | .25mA                             |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) ..... | 889mW                             |

| Plastic DIP (derate 11.11mW/°C above +70°C) .....           | 889mW                             |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

(V<sub>DD</sub> = +2.375V to +3.3V, V<sub>COM</sub> = 0V, f<sub>CLK</sub> = 1.5MHz, external clock (50% duty cycle), 15 clocks/conversion cycle (100ksps), VREF = 2.048V applied to VREF pin, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted.)

| PARAMETER                                                                                                                     | SYMBOL            | CONDITIONS                                                      | MIN   | TYP   | MAX | UNITS  |

|-------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------------|-------|-------|-----|--------|

| <b>DC ACCURACY (Note 1)</b>                                                                                                   |                   |                                                                 |       |       |     |        |

| Resolution                                                                                                                    |                   |                                                                 | 12    |       |     | Bits   |

| Relative Accuracy (Note 2)                                                                                                    | INL               | MAX1245A                                                        |       | ±0.5  |     | LSB    |

|                                                                                                                               |                   | MAX1245B                                                        |       | ±1.0  |     |        |

| Differential Nonlinearity                                                                                                     | DNL               | No missing codes over temperature                               |       | ±1    |     | LSB    |

| Offset Error                                                                                                                  |                   |                                                                 |       | ±0.5  | ±4  | LSB    |

| Gain Error (Note 3)                                                                                                           |                   |                                                                 |       | ±0.5  | ±4  | LSB    |

| Gain Temperature Coefficient                                                                                                  |                   |                                                                 |       | ±0.25 |     | ppm/°C |

| Channel-to-Channel Offset Matching                                                                                            |                   |                                                                 |       | ±0.2  |     | LSB    |

| <b>DYNAMIC SPECIFICATIONS</b> (10kHz sine-wave input, 0Vp-p to 2.048Vp-p, 100ksps, 1.5MHz external clock, bipolar input mode) |                   |                                                                 |       |       |     |        |

| Signal-to-Noise + Distortion Ratio                                                                                            | SINAD             |                                                                 | 68    |       |     | dB     |

| Total Harmonic Distortion                                                                                                     | THD               | Up to the 5th harmonic                                          |       |       | -76 | dB     |

| Spurious-Free Dynamic Range                                                                                                   | SFDR              |                                                                 | 76    |       |     | dB     |

| Channel-to-Channel Crosstalk                                                                                                  |                   | 50kHz, 2V <sub>p-p</sub> (Note 4)                               |       | -85   |     | dB     |

| Small-Signal Bandwidth                                                                                                        |                   | -3dB rolloff                                                    | 2.25  |       |     | MHz    |

| Full-Power Bandwidth                                                                                                          |                   |                                                                 | 1.0   |       |     | MHz    |

| <b>CONVERSION RATE</b>                                                                                                        |                   |                                                                 |       |       |     |        |

| Conversion Time (Note 5)                                                                                                      | t <sub>CONV</sub> | Internal clock, $\overline{\text{SHDN}} = \text{open}$          | 5.5   | 7.5   |     | μs     |

|                                                                                                                               |                   | Internal clock, $\overline{\text{SHDN}} = \text{V}_{\text{DD}}$ | 35    | 65    |     |        |

|                                                                                                                               |                   | External clock = 1.5MHz, 12 clocks/conversion                   | 8     |       |     |        |

| Track/Hold Acquisition Time                                                                                                   | t <sub>ACQ</sub>  | External clock = 1.5MHz                                         |       | 2.0   |     | μs     |

| Aperture Delay                                                                                                                |                   |                                                                 |       | 40    |     | ns     |

| Aperture Jitter                                                                                                               |                   |                                                                 |       | <50   |     | ps     |

| Internal Clock Frequency                                                                                                      |                   | $\overline{\text{SHDN}} = \text{open}$                          | 1.5   |       |     | MHz    |

|                                                                                                                               |                   | $\overline{\text{SHDN}} = \text{V}_{\text{DD}}$                 | 0.225 |       |     |        |

| External Clock Frequency                                                                                                      |                   |                                                                 | 0.1   | 1.5   |     | MHz    |

|                                                                                                                               |                   | Data transfer only                                              | 0     | 1.5   |     |        |

# +2.375V、低電力、8チャネル、シリアル12ビットADC

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{DD} = +2.375V$  to  $+3.3V$ ,  $V_{COM} = 0V$ ,  $f_{CLK} = 1.5MHz$ , external clock (50% duty cycle), 15 clocks/conversion cycle (100ksps),  $V_{REF} = 2.048V$  applied to VREF pin,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                                                   | SYMBOL     | CONDITIONS                                                                    | MIN              | TYP              | MAX             | UNITS      |

|-------------------------------------------------------------|------------|-------------------------------------------------------------------------------|------------------|------------------|-----------------|------------|

| <b>ANALOG/COM INPUTS</b>                                    |            |                                                                               |                  |                  |                 |            |

| Input Voltage Range, Single-Ended and Differential (Note 6) |            | Unipolar, $V_{COM} = 0V$                                                      |                  |                  | 0 to $V_{REF}$  | V          |

|                                                             |            | Bipolar, $V_{COM} = V_{REF}/2$                                                |                  |                  | $\pm V_{REF}/2$ |            |

| Multiplexer Leakage Current                                 |            | On/off leakage current, $V_{IN} = 0V$ or $V_{DD}$                             |                  | $\pm 0.01$       | $\pm 1$         | $\mu A$    |

| Input Capacitance                                           |            | (Note 7)                                                                      |                  |                  | 16              | pF         |

| <b>EXTERNAL REFERENCE</b>                                   |            |                                                                               |                  |                  |                 |            |

| VREF Input Voltage Range (Note 8)                           |            |                                                                               | 1.0              | $V_{DD} + 50mV$  |                 | V          |

| VREF Input Current                                          |            | $V_{REF} = 2.048V$                                                            |                  | 82               | 120             | $\mu A$    |

| VREF Input Resistance                                       |            |                                                                               | 18               | 25               |                 | k $\Omega$ |

| Shutdown VREF Input Current                                 |            |                                                                               |                  | 0.01             | 10              | $\mu A$    |

| <b>DIGITAL INPUTS (DIN, SCLK, CS, SHDN)</b>                 |            |                                                                               |                  |                  |                 |            |

| DIN, SCLK, CS Input High Voltage                            | $V_{INH}$  |                                                                               | 2.0              |                  |                 | V          |

| DIN, SCLK, CS Input Low Voltage                             | $V_{INL}$  |                                                                               |                  |                  | 0.8             | V          |

| DIN, SCLK, CS Input Hysteresis                              | $V_{HYST}$ |                                                                               |                  |                  | 0.2             | V          |

| DIN, SCLK, CS Input Leakage                                 | $I_{IN}$   | $V_{IN} = 0V$ or $V_{DD}$                                                     |                  | $\pm 0.01$       | $\pm 1$         | $\mu A$    |

| DIN, SCLK, CS Input Capacitance                             | $C_{IN}$   | (Note 7)                                                                      |                  |                  | 15              | pF         |

| SHDN Input High Voltage                                     | $V_{INH}$  |                                                                               | $V_{DD} - 0.4$   |                  | V               |            |

| SHDN Input Low Voltage                                      | $V_{INL}$  |                                                                               |                  |                  | 0.4             | V          |

| SHDN Input Current                                          | $I_{IN}$   | $\overline{SHDN} = 0V$ or $V_{DD}$                                            |                  |                  | $\pm 4.0$       | $\mu A$    |

| SHDN Input Mid Voltage                                      | $V_{IM}$   |                                                                               | $V_{DD}/2 - 0.3$ | $V_{DD}/2 + 0.3$ |                 | V          |

| SHDN Voltage, Open                                          | $V_{FLT}$  | $\overline{SHDN} = \text{open}$                                               | $V_{DD}/2$       |                  | V               |            |

| SHDN Maximum Allowed Leakage, Mid Input                     |            | $\overline{SHDN} = \text{open}$                                               |                  |                  | $\pm 80$        | nA         |

| <b>DIGITAL OUTPUTS (DOUT, SSTRB)</b>                        |            |                                                                               |                  |                  |                 |            |

| Output Voltage Low                                          | $V_{OL}$   | $I_{SINK} = 5mA$                                                              |                  |                  | 0.4             | V          |

|                                                             |            | $I_{SINK} = 16mA$                                                             |                  |                  | 0.5             |            |

| Output Voltage High                                         | $V_{OH}$   | $I_{SOURCE} = 0.5mA$                                                          | $V_{DD} - 0.375$ |                  | V               |            |

| Three-State Leakage Current                                 | $I_L$      | $\overline{CS} = V_{DD}$                                                      |                  | $\pm 0.01$       | $\pm 10$        | $\mu A$    |

| Three-State Output Capacitance                              | $C_{OUT}$  | $\overline{CS} = V_{DD}$ (Note 7)                                             |                  |                  | 15              | pF         |

| <b>POWER REQUIREMENTS</b>                                   |            |                                                                               |                  |                  |                 |            |

| Positive Supply Voltage                                     | $V_{DD}$   |                                                                               | 2.375            | 3.3              |                 | V          |

| Positive Supply Current                                     | $I_{DD}$   | Operating mode, full-scale input                                              |                  | 0.8              | 1.3             | mA         |

|                                                             |            | Power-down                                                                    |                  | 1.2              | 10              | $\mu A$    |

| Supply Rejection (Note 9)                                   | $PSR$      | $V_{DD} = 2.375V$ to $3.3V$ , full-scale input, external reference = $2.048V$ |                  |                  | $\pm 0.3$       | mV         |

**MAX1245**

# +2.375V、低電力、8チャネル、シリアル12ビットADC

## TIMING CHARACTERISTICS

( $V_{DD} = +2.375V$  to  $+3.3V$ ,  $V_{COM} = 0V$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                       | SYMBOL      | CONDITIONS                         | MIN | TYP | MAX | UNITS |

|---------------------------------|-------------|------------------------------------|-----|-----|-----|-------|

| Acquisition Time                | $t_{ACQ}$   |                                    | 2.0 |     |     | μs    |

| DIN to SCLK Setup               | $t_{DS}$    |                                    | 200 |     |     | ns    |

| DIN to SCLK Hold                | $t_{DH}$    |                                    |     | 0   |     | ns    |

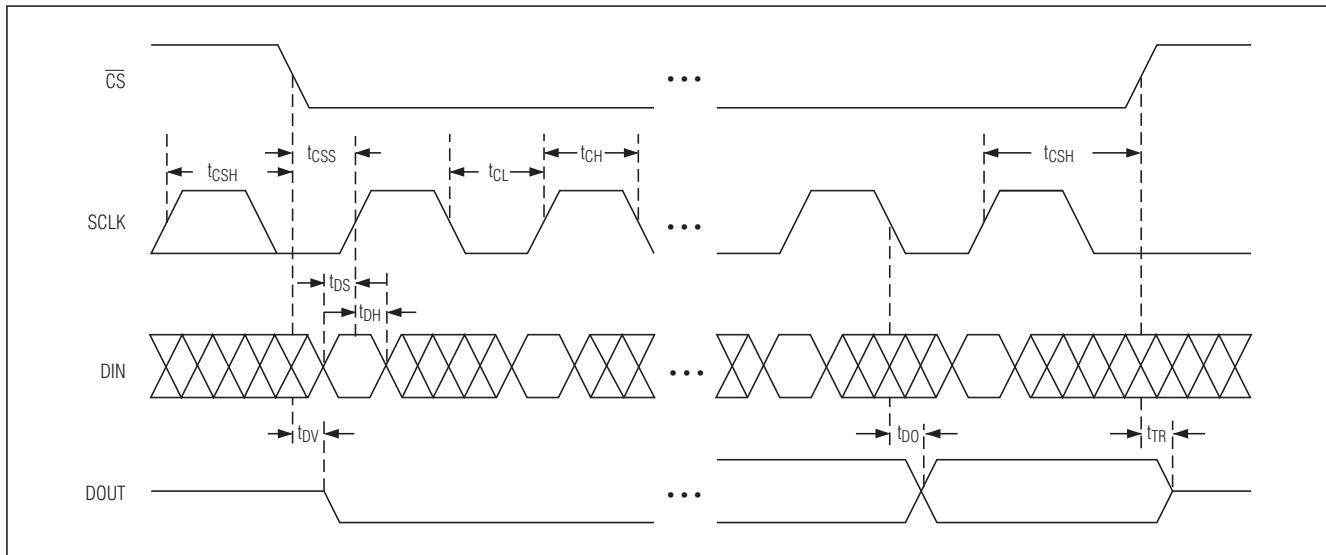

| SCLK Fall to Output Data Valid  | $t_{DO}$    | Figure 1                           | 20  | 260 |     | ns    |

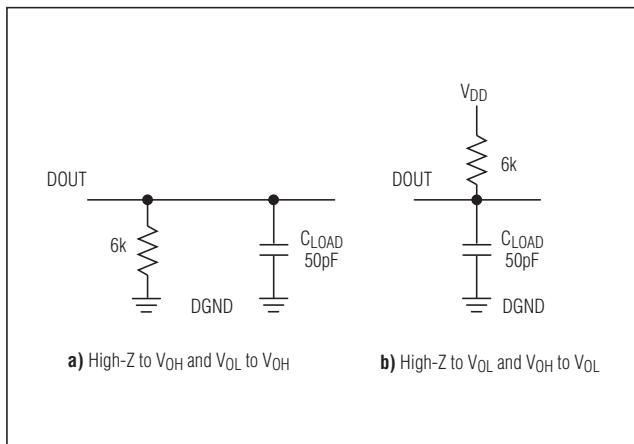

| CS Fall to Output Enable        | $t_{DV}$    | Figure 1                           |     | 240 |     | ns    |

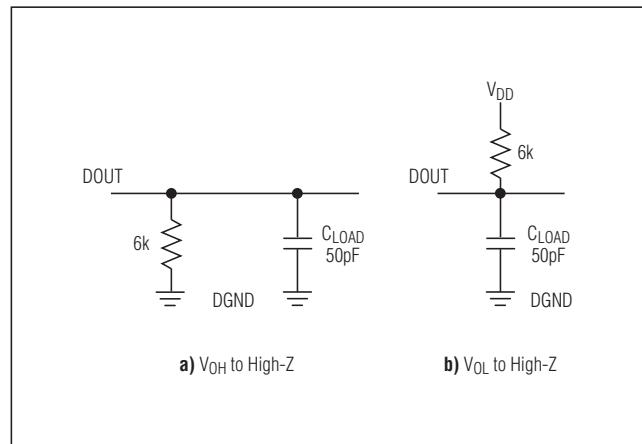

| CS Rise to Output Disable       | $t_{TR}$    | Figure 2                           |     | 400 |     | ns    |

| CS to SCLK Rise Setup           | $t_{CSS}$   |                                    | 200 |     |     | ns    |

| CS to SCLK Rise Hold            | $t_{CSH}$   |                                    | 0   |     |     | ns    |

| SCLK Pulse Width High           | $t_{CH}$    |                                    | 300 |     |     | ns    |

| SCLK Pulse Width Low            | $t_{CL}$    |                                    | 300 |     |     | ns    |

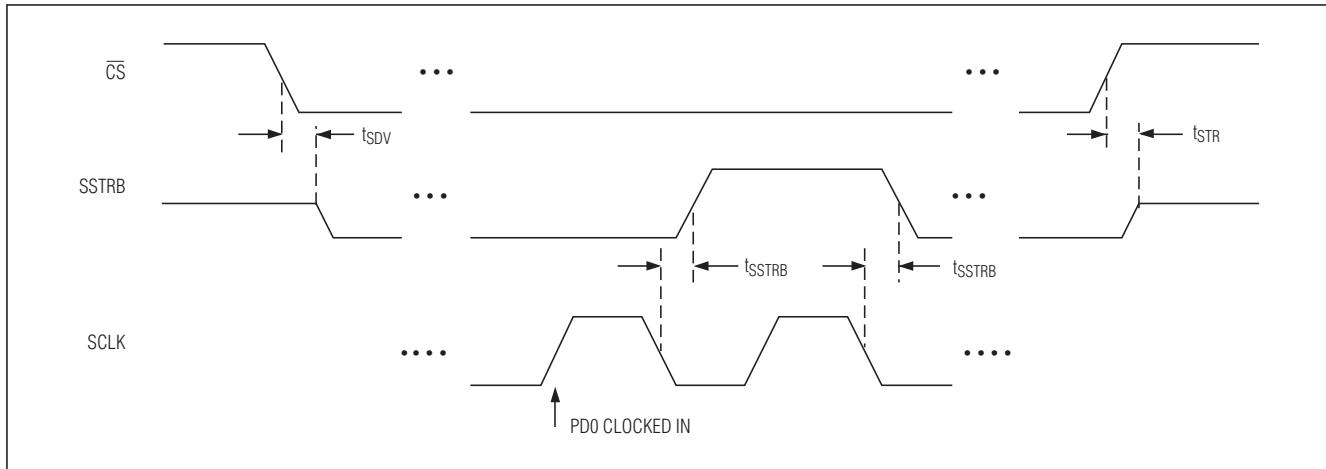

| SCLK Fall to SSTRB              | $t_{SSTRB}$ | Figure 1                           |     | 260 |     | ns    |

| CS Fall to SSTRB Output Enable  | $t_{SDV}$   | External clock mode only, Figure 1 |     | 240 |     | ns    |

| CS Rise to SSTRB Output Disable | $t_{STR}$   | External clock mode only, Figure 2 |     | 400 |     | ns    |

| SSTRB Rise to SCLK Rise         | $t_{SCK}$   | Internal clock mode only (Note 7)  | 0   |     |     | ns    |

**Note 1:** Tested at  $V_{DD} = +2.375V$ ;  $V_{COM} = 0V$ ; unipolar single-ended input mode.

**Note 2:** Relative accuracy is the deviation of the analog value at any code from its theoretical value after the full-scale range has been calibrated.

**Note 3:** External reference ( $V_{REF} = +2.048V$ ), offset nulled.

**Note 4:** Ground “on” channel; sine wave applied to all “off” channels.

**Note 5:** Conversion time defined as the number of clock cycles multiplied by the clock period; clock has 50% duty cycle.

**Note 6:** The common-mode range for the analog inputs is from AGND to  $V_{DD}$ .

**Note 7:** Guaranteed by design. Not subject to production testing.

**Note 8:** ADC performance is limited by the converter’s noise floor, typically  $300\mu V_{p-p}$ .

**Note 9:** Measured as  $|V_{FS}(2.375V) - V_{FS}(3.3V)|$ .

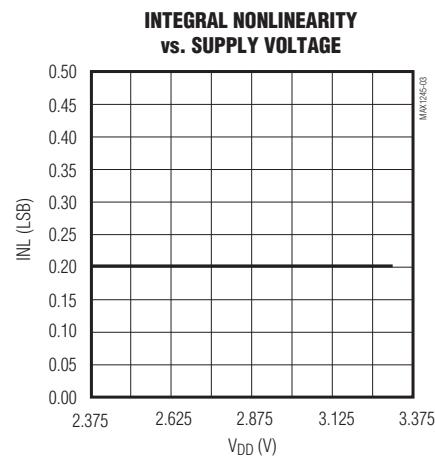

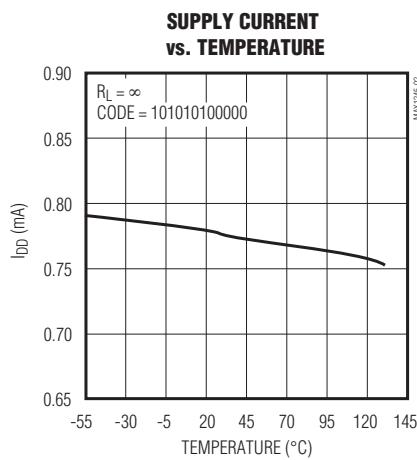

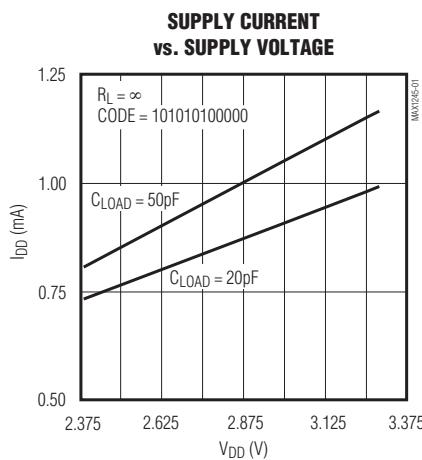

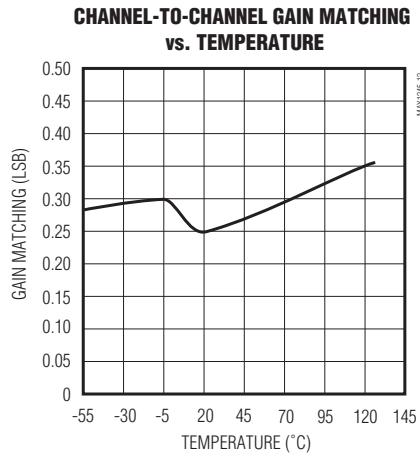

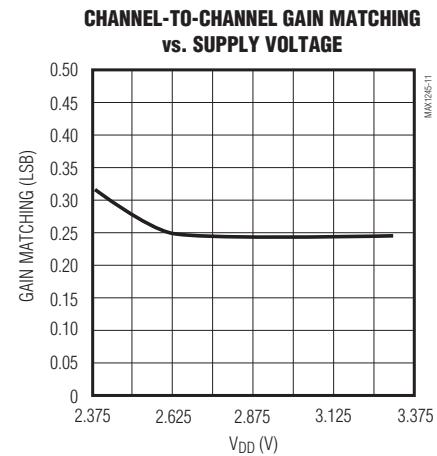

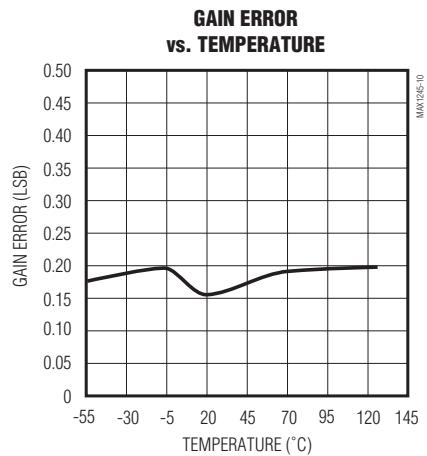

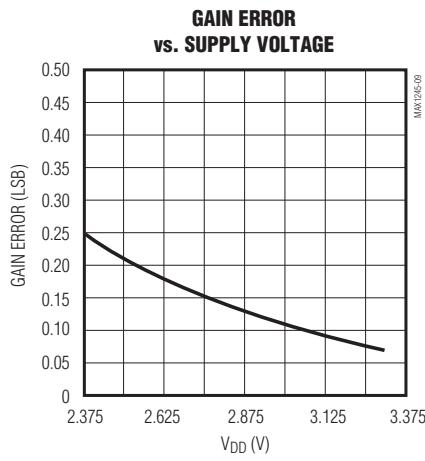

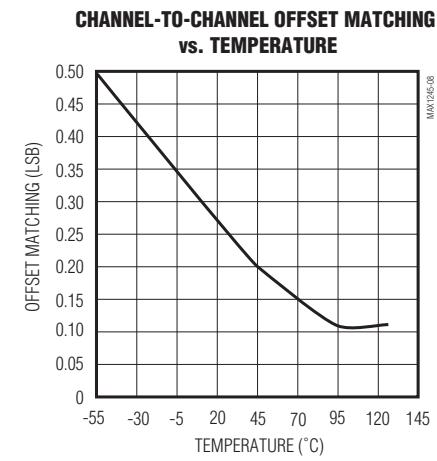

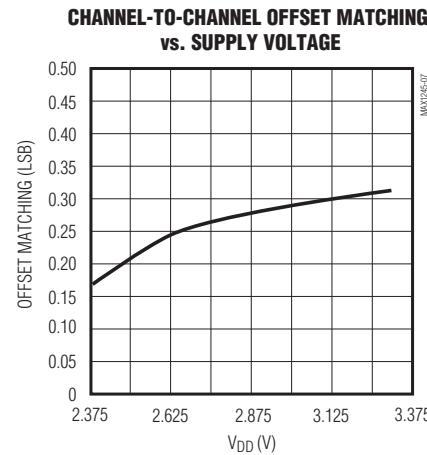

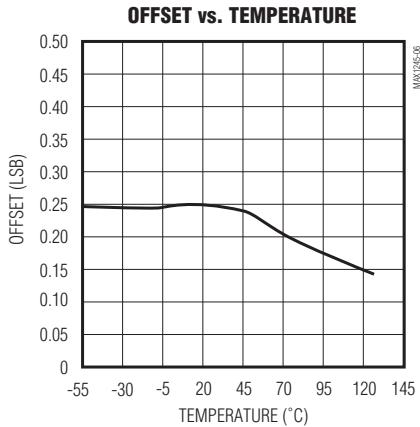

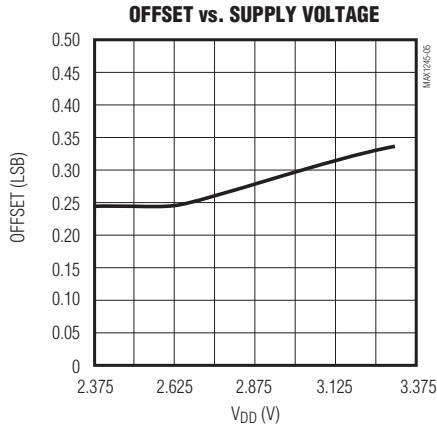

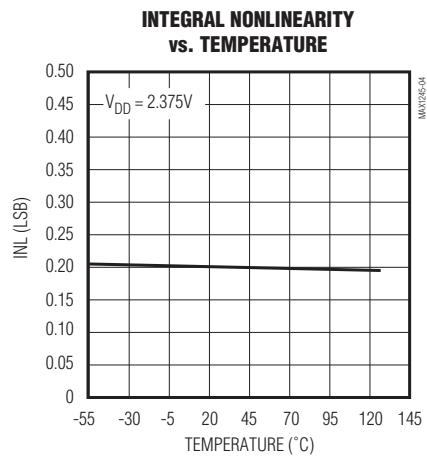

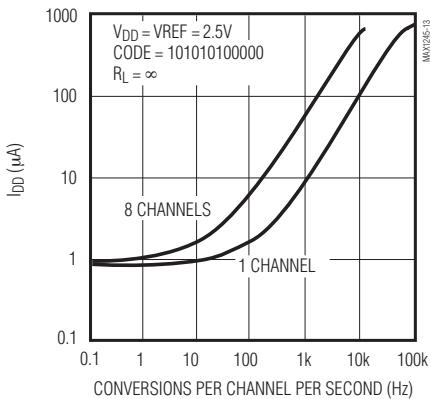

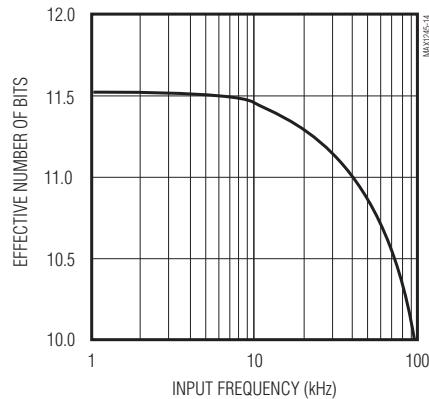

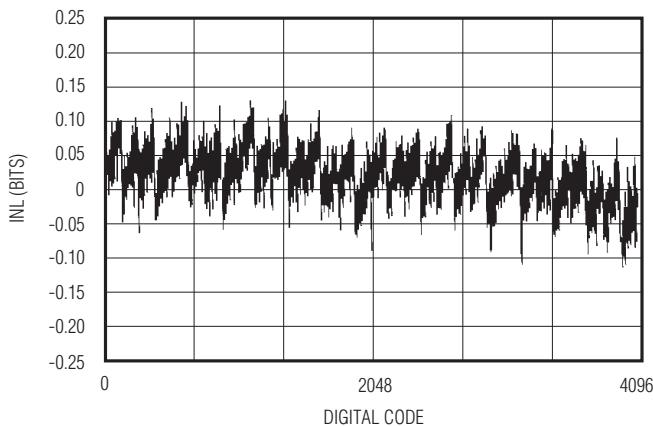

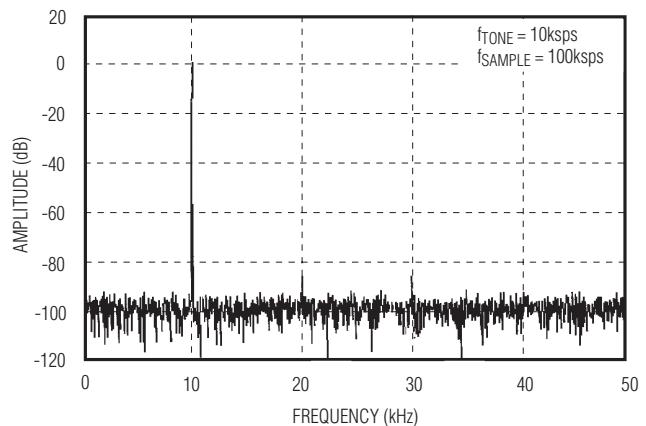

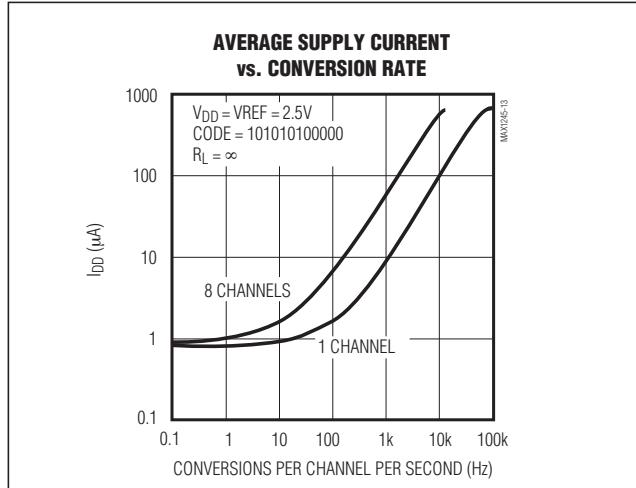

## 標準動作特性

( $V_{DD} = 2.5V$ ,  $V_{REF} = 2.048V$ ,  $f_{CLK} = 1.5MHz$ ,  $C_{LOAD} = 20pF$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

# +2.375V、低電力、8チャネル、シリアル12ビットADC

**MAX1245**

## 標準動作特性(続き)

( $V_{DD} = 2.5\text{V}$ ,  $V_{REF} = 2.048\text{V}$ ,  $f_{CLK} = 1.5\text{MHz}$ ,  $C_{LOAD} = 20\text{pF}$ ,  $T_A = +25^\circ\text{C}$ , unless otherwise noted.)

# +2.375V、低電力、8チャネル、 シリアル12ビットADC

## 標準動作特性(続き)

( $V_{DD} = 2.5V$ ,  $V_{REF} = 2.048V$ ,  $f_{CLK} = 1.5MHz$ ,  $C_{LOAD} = 20pF$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

AVERAGE SUPPLY CURRENT

vs. CONVERSION RATE

EFFECTIVE NUMBER OF BITS

vs. INPUT FREQUENCY

INTEGRAL NONLINEARITY

FFT PLOT

# +2.375V、低電力、8チャネル、シリアル12ビットADC

**MAX1245**

## 端子説明

| 端子     | 名称              | 機能                                                                                                                                                                                                           |

|--------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-8    | CHO-CH7         | サンプリングアナログ入力                                                                                                                                                                                                 |

| 9      | COM             | アナログ入力の基準となるグランド。シングルエンドモードでのゼロコード電圧を設定します。 $\pm 0.5$ LSBの安定性が必要です。                                                                                                                                          |

| 10     | SHDN            | 3レベルシャットダウン入力。SHDNをローにするとMAX1245はシャットダウンして消費電流が $10\mu A$ (max)に低減されます。それ以外の場合は、MAX1245は完全動作状態です。SHDNを開放にすると内部クロック周波数が $1.5MHz$ に設定されます。SHDNをハイにすると内部クロック周波数が $225kHz$ に設定されます。「ハードウェアによるパワーダウン」の項を参照してください。 |

| 11     | VREF            | アナログデジタル変換用の外部リファレンス電圧入力。                                                                                                                                                                                    |

| 12, 20 | V <sub>DD</sub> | 正電源電圧                                                                                                                                                                                                        |

| 13     | AGND            | アナロググランド                                                                                                                                                                                                     |

| 14     | DGND            | デジタルグランド                                                                                                                                                                                                     |

| 15     | DOUT            | シリアルデータ出力。データはSCLKの立下りエッジでクロック出力されます。 $\overline{CS}$ がハイのとき、ハイインピーダンスになります。                                                                                                                                 |

| 16     | SSTRB           | シリアルストローブ出力。内部クロックモードでは、SSTRBはMAX1245がA/D変換を開始したときにローになり、変換終了時にハイになります。外部クロックモードでは、SSTRBはMSBの決定前に1クロック期間だけハイになります。 $\overline{CS}$ がハイ(外部クロックモード)のときは、ハイインピーダンスになります。                                        |

| 17     | DIN             | シリアルデータ入力。データはSCLKの立上りエッジでクロック入力されます。                                                                                                                                                                        |

| 18     | $\overline{CS}$ | アクティブローのチップセレクト。 $\overline{CS}$ がローでない限り、データはDINにクロック入力されません。 $\overline{CS}$ がハイのとき、DOUTはハイインピーダンスになります。                                                                                                   |

| 19     | SCLK            | シリアルクロック入力。シリアルインターフェースのデータをクロック入力または出力します。外部クロックモードではSCLKは変換速度も設定します。(デューティサイクルは40%~60%でなければなりません。)                                                                                                         |

図1. イネーブル時間用の負荷回路

図2. デイセーブル時間用の負荷回路

# +2.375V、低電力、8チャネル、シリアル12ビットADC

## 詳細

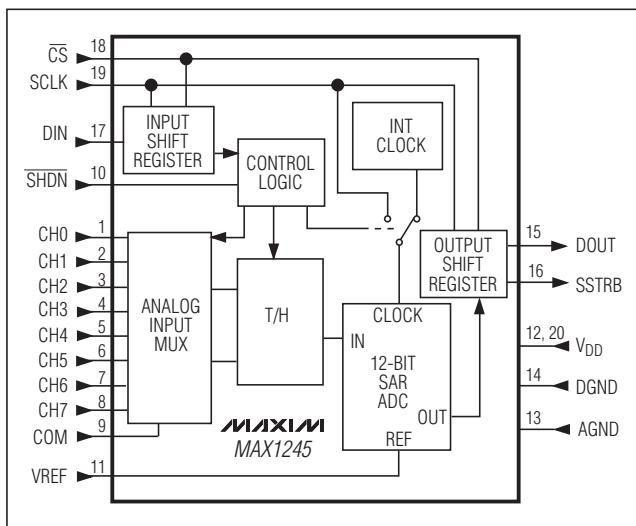

MAX1245アナログ-ディジタルコンバータ(ADC)は逐次比較型の変換技法と入力トラック/ホールド(T/H)回路を用いることで、アナログ信号を12ビットのデジタル出力に変換します。フレキシブルなシリアルインターフェースがマイクロプロセッサ( $\mu$ P)とのインターフェースを容易にしています。外部ホールドコンデンサは必要としません。図3にMAX1245のブロックダイアグラムを示します。

## 疑似差動入力

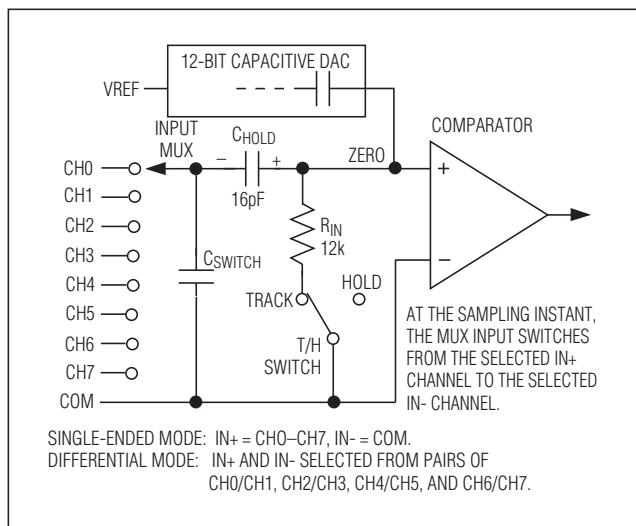

このADCのアナログコンバータのサンプリング構造は入力等価回路(図4)に図解されています。シングルエンドモードでは、IN+は内部でCH0~CH7にスイッチされ、IN-はCOMにスイッチされます。差動モードでは、IN+とIN-は、CH0/CH1、CH2/CH3、CH4/CH5とCH6/CH7の組み合わせから選択されます。チャネルの設定は表2と表3を使用して行ってください。

差動モードでは、IN-とIN+は内部でアナログ入力のいずれかにスイッチされます。この構成ではIN+の信号のみがサンプリングされる意味で疑似差動です。リターン側(IN-)は、変換中AGNDに対して $\pm 0.5$  LSB(最良の結果を得るために $\pm 0.1$  LSB)以内で安定していかなければなりません。これを実現するためにはIN-(選択されたアナログ入力)とAGND間に0.1 $\mu$ Fのコンデンサを接続してください。

アクイジョン期間中は、正入力(IN+)として選択されたチャネルがコンデンサC<sub>HOLD</sub>を充電します。アクイジョン期間は3 SCLKサイクル間だけ続き、入力制御ワードの最後のビットが入力された後のSCLKの立下りエッジで完了します。アクイジョン期間の終了時にT/Hスイッチが開き、C<sub>HOLD</sub>の電荷をIN+の信号のサンプルとして保持します。

図3. ブロックダイアグラム

変換期間は、入力マルチプレクサがC<sub>HOLD</sub>を正入力(IN+)から負入力(IN-)にスイッチしたときから始まります(シングルエンドモードではIN-はCOMです)。このため、コンバレータの入力でのノードZEROが不均衡になります。変換サイクルの残りの時間で、容量性DACがノードZEROを12ビット分解能の制限範囲でOVに調整されます。この動作は $16\text{pF} \times [(V_{IN+}) - (V_{IN-})]$ の電荷をC<sub>HOLD</sub>からバイナリ荷重の容量性DACに移動するのと等価です。この結果、アナログ入力信号のデジタル表現が生成されます。

## トラック/ホールド

T/Hは、8ビット制御ワードの5番目のビットがシフトインされた後の立下りクロックエッジでトラッキングモードに入り、制御ワードの8番目のビットがシフトインされた後の立下りクロックエッジでホールドモードに入ります。コンバータがシングルエンド入力用に設定されている場合はIN-がCOMに接続され、コンバータは「+」入力をサンプリングします。コンバータが差動入力用に設定されている場合はIN-が「-」入力に接続され、|IN+ - IN-|の差がサンプリングされます。変換終了時に正入力が再びIN+に接続され、C<sub>HOLD</sub>は入力信号電圧まで充電されます。

T/Hが入力信号を取り込むのに要する時間は、入力容量が充電される速さの関数になっています。入力信号のソースインピーダンスが大きいとアクイジョン時間は長くなるため、変換と変換の間の時間を長くしなければなりません。アクイジョン時間t<sub>ACQ</sub>はデバイスが信号を取り込むために要する最大時間であり、信号の取込みに必要な最低時間でもあります。t<sub>ACQ</sub>は次式で計算されます。

$$t_{ACQ} = 9 \times (R_S + R_{IN}) \times 16\text{pF}$$

図4. 入力等価回路

# +2.375V、低電力、8チャネル、シリアル12ビットADC

MAX1245

ここで、 $R_{IN} = 12\text{k}\Omega$ 、 $R_S$  = 入力信号のソースインピーダンス、そして $t_{ACQ}$ は $2.0\mu\text{s}$ 以下になってはいけません。ソースインピーダンスが $1\text{k}\Omega$ 以下であれば、ADCのAC性能に大きく影響を与えません。これより大きいソースインピーダンスの場合には、アナログ入力に入力コンデンサを接続してください(図5を参照)。入力コンデンサと入力ソースインピーダンスによってRCフィルタが形成されるため、ADCの信号帯域幅が制限されることに注意してください。

## 入力帯域幅

ADCの入力トラッキング回路の小信号帯域幅は $2.25\text{MHz}$ であるため、アンダーサンプリング技法を用いることによって、高速トランジエント現象をデジタル化して帯域幅がADCのサンプリングレート以上の周期信号を測定することができます。高周波信号が計測したい周波数帯域にエイリアシングされることを防ぐために、アンチエイリアシングフィルタの使用を推奨します。

## アナログ入力保護

内蔵保護ダイオードがアナログ入力を $V_{DD}$ とAGNDにクランプするため、チャネル入力ピンは( $AGND - 0.3\text{V}$ )～( $V_{DD} + 0.3\text{V}$ )の範囲で、損傷を起こすことなくスイッチング可能です。しかし、フルスケール付近で正確な変換を行うためには、入力が $V_{DD}$ を $50\text{mV}$ 以上超えないように、またAGNDを $50\text{mV}$ 以上下回らないようにしてください。

アナログ入力が電源を $50\text{mV}$ 以上超える場合には、オフチャネルの保護ダイオードに $2\text{mA}$ 以上の順方向バイアスをかけないでください。この電流が過剰の場合、オンチャネルの変換精度が劣化します。

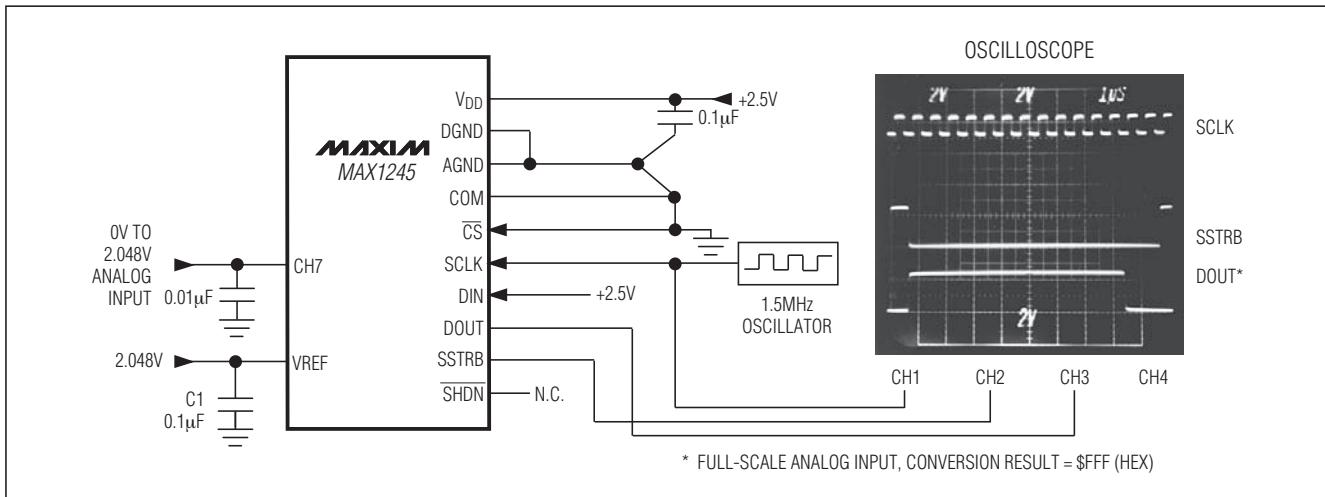

## クイックルック

MAX1245のアナログ性能を簡単に評価するには、図5の回路を使用してください。MAX1245では各変換の前

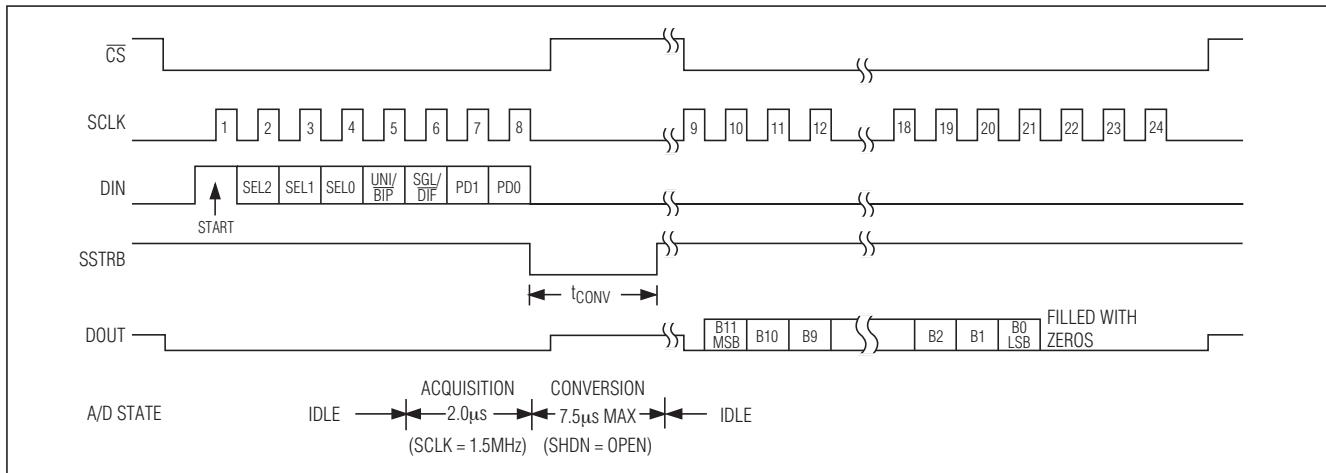

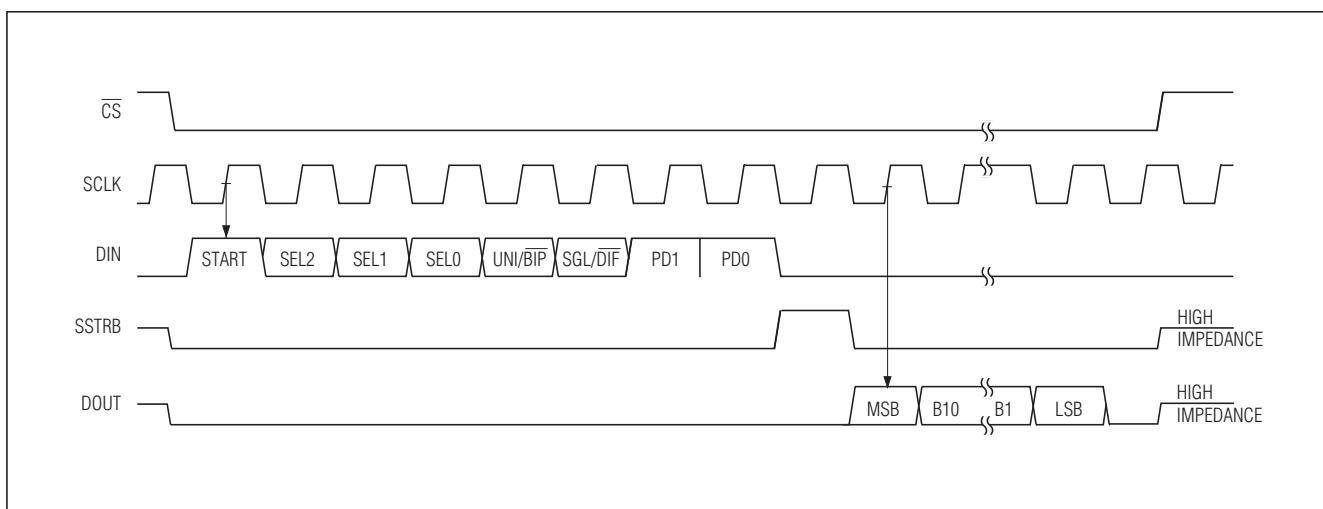

に、制御バイトをDINに書き込む必要があります。DINを $V_{DD}$ に接続すると、\$FF (HEX)という制御バイトが書き込まれます。このことによって、各変換の間にパワーダウンしない外部クロックモードでのCH7のシングルエンドユニポーラ変換が設定されます。外部クロックモードでは、12ビット変換結果の最上位ビットがDOUTからシフトアウトされる前に、SSTRB出力が1クロックだけハイになります。CH7へのアナログ入力を変化させると、DOUTからのビットシーケンスが変わります。1変換当たり合計15クロックサイクルが必要です。SSTRBとDOUT出力の遷移はすべてSCLKの立下りエッジで起こります。

## 変換開始方法

変換は、制御バイトをDINにクロックインすることで始まります。 $\overline{CS}$ をローにすると、SCLKの各立上りエッジで、DINからMAX1245の内部シフトレジスタへビットがクロックインされます。 $\overline{CS}$ がローに低下した後に最初に到来したロジック「1」のビットが制御バイトのMSBとして定義されます。この最初の「スタート」ビットが到来するまでは、ロジック「0」のビットがいくつDINにクロックインされたとしても一切影響はありません。表1に制御バイトのフォーマットを示します。

MAX1245はMICROWIRE、SPIおよびQSPI機器とコンパチブルです。SPIの場合は、SPI制御レジスタによって正しいクロック極性とサンプリングエッジを選択してください(CPOL = 0、およびCPHA = 0に設定してください)。MICROWIRE、SPI、およびQSPIはいずれもバイトの送信とバイトの受信を同時に行います。「標準動作回路」を用いた場合、最もシンプルなソフトウェアインターフェースでは8ビット転送をわずか3回行うだけで変換が行えます(1回の8ビット転送でADCを設定し、残り2回の8ビット転送では12ビット変換結果をクロックアウトします)。MAX1245のQSPI接続法については図17を参照してください。

図5. クイックルック回路

# +2.375V、低電力、8チャネル、シリアル12ビットADC

表1. 制御バイトフォーマット

| BIT 7<br>(MSB) | BIT 6      | BIT 5                                                                                                                                                                                                                                                  | BIT 4 | BIT 3   | BIT 2   | BIT 1 | BIT 0<br>(LSB) |

|----------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|---------|-------|----------------|

| START          | SEL2       | SEL1                                                                                                                                                                                                                                                   | SEL0  | UNI/BIP | SGL/DIF | PD1   | PDO            |

| BIT            | NAME       | DESCRIPTION                                                                                                                                                                                                                                            |       |         |         |       |                |

| 7(MSB)         | START      | The first logic “1” bit after CS goes low defines the beginning of the control byte.                                                                                                                                                                   |       |         |         |       |                |

| 6              | SEL2       | These three bits select which of the eight channels are used for the conversion (Tables 2 and 3).                                                                                                                                                      |       |         |         |       |                |

| 5              | SEL1       |                                                                                                                                                                                                                                                        |       |         |         |       |                |

| 4              | SEL0       |                                                                                                                                                                                                                                                        |       |         |         |       |                |

| 3              | UNI/BIP    | 1 = unipolar, 0 = bipolar. Selects unipolar or bipolar conversion mode. In unipolar mode, an analog input signal from 0V to VREF can be converted; in bipolar mode, the signal can range from -VREF/2 to +VREF/2.                                      |       |         |         |       |                |

| 2              | SGL/DIF    | 1 = single ended, 0 = differential. Selects single-ended or differential conversions. In single-ended mode, input signal voltages are referred to COM. In differential mode, the voltage difference between two channels is measured (Tables 2 and 3). |       |         |         |       |                |

| 1<br>0(LSB)    | PD1<br>PDO | Selects clock and power-down modes.<br>PD1      PDO      Mode<br>0            0      Power-down ( $I_Q = 1.2\mu A$ )<br>0            1      Unassigned<br>1            0      Internal clock mode<br>1            1      External clock mode           |       |         |         |       |                |

表2. シングルエンドモードでのチャネル選択(SGL/DIF = 1)

| SEL2 | SEL1 | SEL0 | CH0 | CH1 | CH2 | CH3 | CH4 | CH5 | CH6 | CH7 | COM |

|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0    | 0    | 0    | +   |     |     |     |     |     |     |     | -   |

| 1    | 0    | 0    |     | +   |     |     |     |     |     |     | -   |

| 0    | 0    | 1    |     |     | +   |     |     |     |     |     | -   |

| 1    | 0    | 1    |     |     |     | +   |     |     |     |     | -   |

| 0    | 1    | 0    |     |     |     |     | +   |     |     |     | -   |

| 1    | 1    | 0    |     |     |     |     |     | +   |     |     | -   |

| 0    | 1    | 1    |     |     |     |     |     |     | +   |     | -   |

| 1    | 1    | 1    |     |     |     |     |     |     |     | +   | -   |

表3. 差動モードでのチャネル選択(SGL/DIF = 0)

| SEL2 | SEL1 | SEL0 | CH0 | CH1 | CH2 | CH3 | CH4 | CH5 | CH6 | CH7 |

|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0    | 0    | 0    | +   | -   |     |     |     |     |     |     |

| 0    | 0    | 1    |     |     | +   | -   |     |     |     |     |

| 0    | 1    | 0    |     |     |     |     | +   | -   |     |     |

| 0    | 1    | 1    |     |     |     |     |     |     | +   | -   |

| 1    | 0    | 0    | -   | +   |     |     |     |     |     |     |

| 1    | 0    | 1    |     |     | -   | +   |     |     |     |     |

| 1    | 1    | 0    |     |     |     |     | -   | +   |     |     |

| 1    | 1    | 1    |     |     |     |     |     |     | -   | +   |

# +2.375V、低電力、8チャネル、シリアル12ビットADC

MAX1245

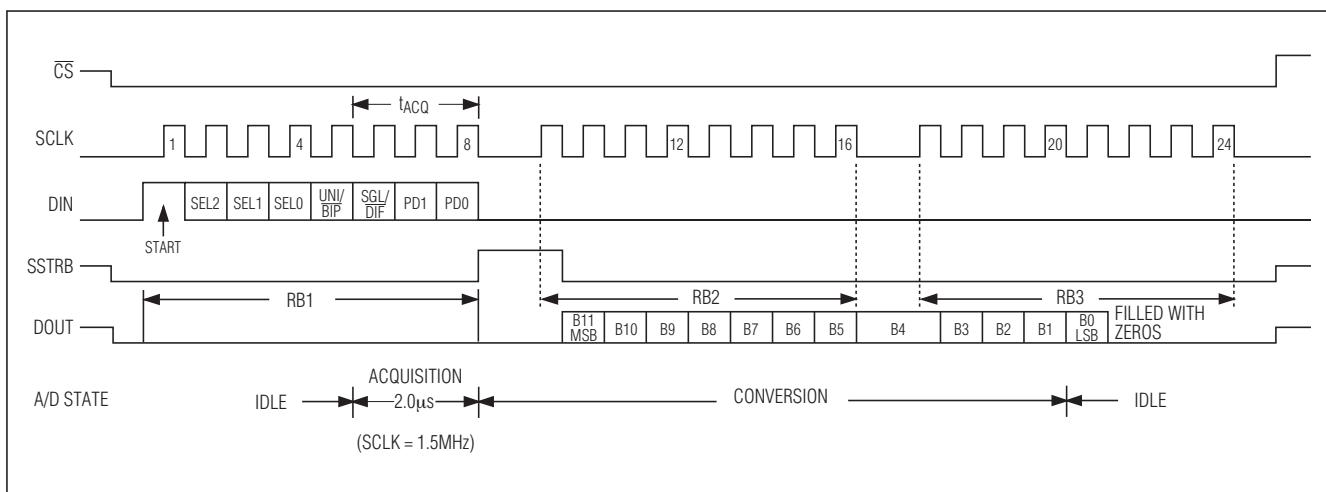

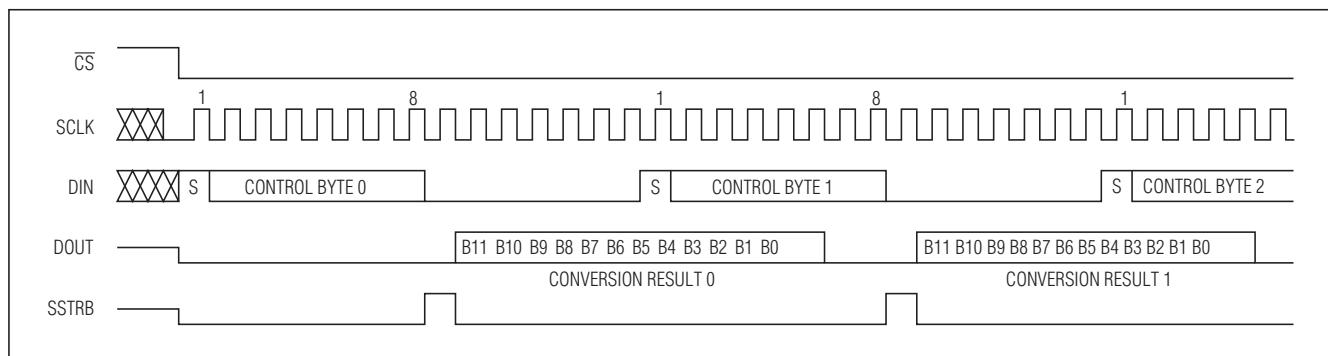

## シンプルなソフトウェアインターフェース

CPUにシリアルクロックを発生させるために、CPUのシリアルインターフェースがマスター modeで動作していることを確認してください。クロック周波数は100kHz～1.5MHzの範囲から選択してください。

- 1) 制御バイトを外部クロックモードに設定し、これをTB1と呼びます。TB1はバイナリの1XXXXX11というフォーマットにしてください。ここで、Xは選択された特定のチャネルと変換モードを表します。

- 2) CPUの汎用I/Oラインを用いて $\overline{CS}$ をローにします。

- 3) TB1を送信し、同時にバイトを受信します。受信したバイトをRB1と呼びます。RB1は無視します。

- 4) すべてゼロで構成されるバイト(\$00 HEX)を送信し、同時にバイトRB2を受信します。

- 5) すべてゼロで構成されるバイト(\$00 HEX)を送信し、同時にバイトRB3を受信します。

- 6)  $\overline{CS}$ をハイにします。

図6にこのシーケンスのタイミングを示します。バイトRB2とRB3は、先頭のゼロ1個と最後の3つのゼロに挟まれた変換結果を含んでいます。総変換時間はシリアルクロック周波数と8ビット転送間のアイドル時間の関数です。T/Hが過剰にドループするのを防ぐために、総変換時間が120μsを超えないようにしてください。

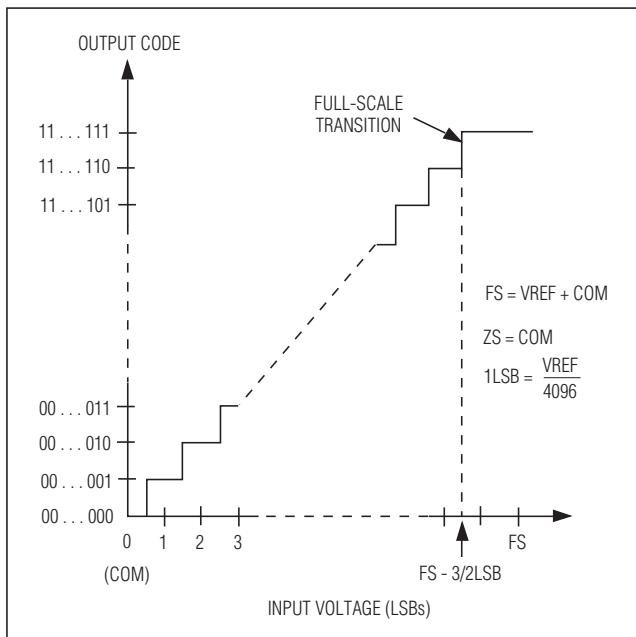

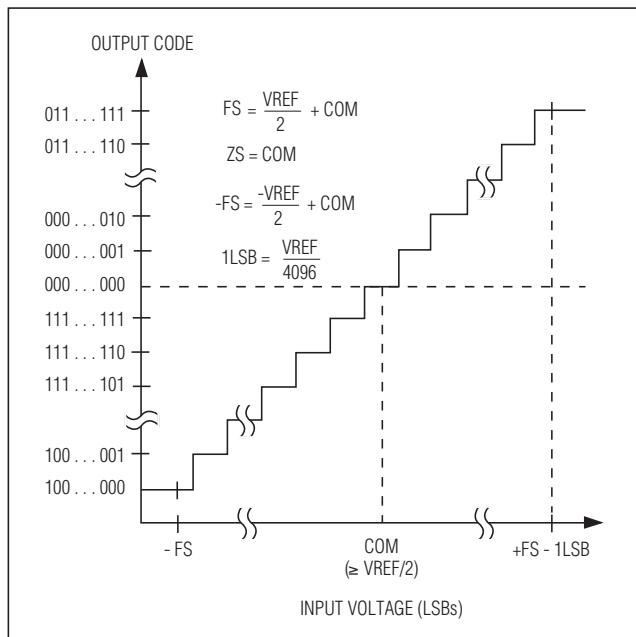

## デジタル出力

ユニポーラ入力モードでは出力はストレートバイナリです(図14)。バイポーラ入力の場合、出力は2の補数形式になります(図15)。データはSCLKの立下りエッジで、MSBを先頭にクロックアウトされます。

## クロックモード

MAX1245は外部シリアルクロック、または内部クロックを用いて、逐次比較型変換を行うことができます。いずれのクロックモードの場合も、外部クロックがMAX1245からデータをシフトイン/アウトします。T/Hは制御バイトの最後の3ビットがDINにクロックインされるときに入力信号を取り込みます。制御バイトのビットPD1とPD0がクロックモードをプログラムします。図7～10に両方のモードに共通するタイミング特性を示します。

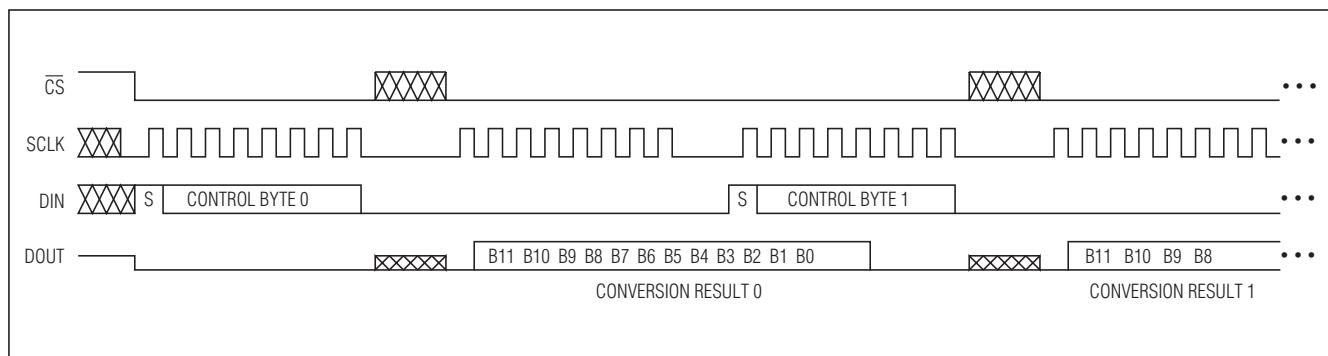

## 外部クロック

外部クロックモードでは、外部クロックはデータをシフトイン/アウトするだけでなく、アナログデジタル変換の駆動も行います。SSTRBは制御バイトの最後のビットの後で、1クロック期間だけハイになります。逐次比較用のビット決定はそれに続く12個のSCLKの立下りエッジでそれぞれ行われ、DOUTに出力されます(図6)。 $\overline{CS}$ がハイになると、SSTRBとDOUTはハイインピーダンス状態になります。そして、その次の $\overline{CS}$ の立下りエッジでSSTRBがロジックローを出力します。図8に外部クロックモードでのSSTRBのタイミングを示します。

変換は一定の最小時間内に完了しなければなりません。完了しない場合は、サンプルアンドホールドコンデンサのドループが変換結果を劣化させます。シリアルクロック周波数が100kHz以下の場合、あるいはシリアルクロックの途切れにより変換期間が120μsを超える可能性がある場合は、内部クロックモードを使用してください。

図6. 24クロック外部クロックモードの変換タイミング(MICROWIREおよびSPIコンパチブル、 $f_{CLK} \leq 1.5\text{MHz}$ でQSPIコンパチブル)

# +2.375V、低電力、8チャネル、シリアル12ビットADC

図7. シリアルインターフェースのタイミングの詳細

図8. 外部クロックモードでのSSTRBのタイミングの詳細

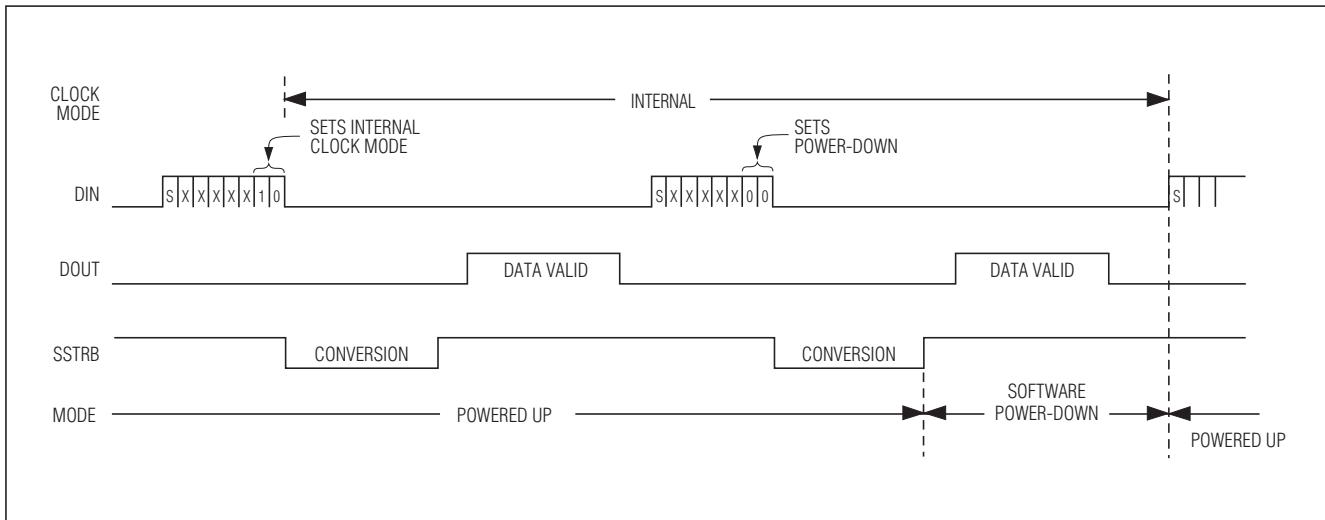

## 内部クロック

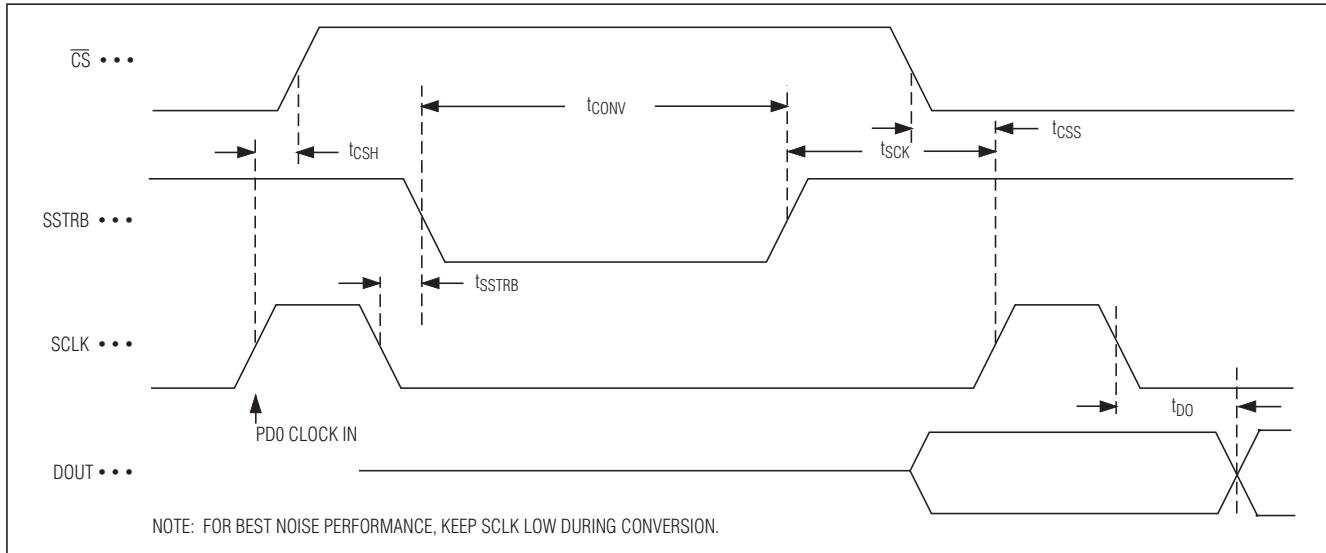

内部クロックモードでは、MAX1245自体が変換クロックを内部で発生します。この結果、μPはSAR変換クロックを発生させる役目から解放され、変換結果はプロセッサの都合のよいときに、0~1.5MHzの任意のクロックレートで読み取ることができます。SSTRBは変換開始時にローになり、変換が完了するとハイになります。SSTRBは最大7.5μs間ローに留まりますが(SHDN = open)、最高のノイズ性能を得るために、その間SCLKをローに保つようにしてください。

変換中は内部レジスタがデータを保存します。変換の終了後、任意の時点で、SCLKによってこのレジスタから

データをクロックアウトします。SSTRBがハイになった後、次の立下りクロックエッジで変換のMSBがDOUTに出力され、続いて残りのビットがMSBを先頭にしたフォーマットで出力されます(図9)。いったん変換が開始されれば、CSをローに保持する必要はありません。CSをハイにするとデータがMAX1245にクロックインされなくなり、DOUTがスリーステートになりますが、すでに進行中の内部クロックモードの変換に悪影響を与えることはありません。内部クロックモードが選択されている場合、CSがハイになってもSSTRBはハイインピーダンス状態にはなりません。

# +2.375V、低電力、8チャネル、シリアル12ビットADC

**MAX1245**

図9. 内部クロックモードのタイミング

図10. 内部クロックモードでのSSTRBのタイミングの詳細

図10に内部クロックモードでのSSTRBのタイミングを示します。このモードでは、最小アクイジションタイム( $t_{ACQ}$ )が $2.0\mu s$ 以上に保たれている限り、1.5MHz以上のクロックレートでデータをMAX1245にシフトインとシフトアウトすることができます。

## データフレーミング

MAX1245では $\overline{CS}$ の立下りエッジでは変換が開始されません。DINにクロックインされる最初のロジックハイはスタートビットとして解釈され、これにより制御バイトの最初のビットが定義されます。変換は、制御バイトの8番目のビット(PDOビット)がDINにクロックインされた後のSCLKの立下りエッジで開始されます。スタートビットの定義は以下のとおりです。

コンバータがアイドル状態である任意の時間(例えば、 $V_{DD}$ が印加された後)に $\overline{CS}$ がローの状態でDINにクロックインされた最初のハイビット。

または

進行中の変換のビット5がDOUTピンにクロックアウトされた後にDINにクロックインされた最初のハイビット。

進行中の変換が完了する前に $\overline{CS}$ がトグルされると、その次にDINにクロックインされるハイビットがスタートビットと見なされます。この場合には進行中の変換は中止され、新しい変換が開始されます。

# +2.375V、低電力、8チャネル、シリアル12ビットADC

MAX1245

MAX1245が動作可能な最高速度は、変換と変換の間で $\overline{CS}$ をローに維持することで15クロック/変換になります。図11aに、外部クロックモードで15 SCLKサイクル毎に変換を実行するために必要なシリアルインターフェースタイミングを示します。 $\overline{CS}$ がローでSCLKが連続的である場合は、最初に16個のゼロをクロックインしてスタートビットを保証してください。

ほとんどのマイクロコントローラの場合、変換は8 SCLKクロックの倍数で起きなければなりません。したがって、マイクロコントローラがMAX1245を動作可能な最高速度は通常16クロック/変換という事になります。図11bに、外部クロックモードで16 SCLKサイクル毎に変換を実行するために必要なシリアルインターフェースタイミングを示します。

## アプリケーション情報

### パワーオンリセット

最初に電源が印加されたときに $\overline{SHDN}$ がローに強制されなければ、パワーオンリセット回路がMAX1245を内部クロックモードにし、SSTRB = ハイで変換を開始可能な状態になります。電源が安定した後、内部リセット時間が10 $\mu$ sあり、この間は変換を行わないでください。SSTRBがパワーアップ時にはハイで $\overline{CS}$ がローの場合は、DINの最初のロジック1がスタートビットと見なされます。変換が行われるまではDOUTはゼロをシフトアウトします。

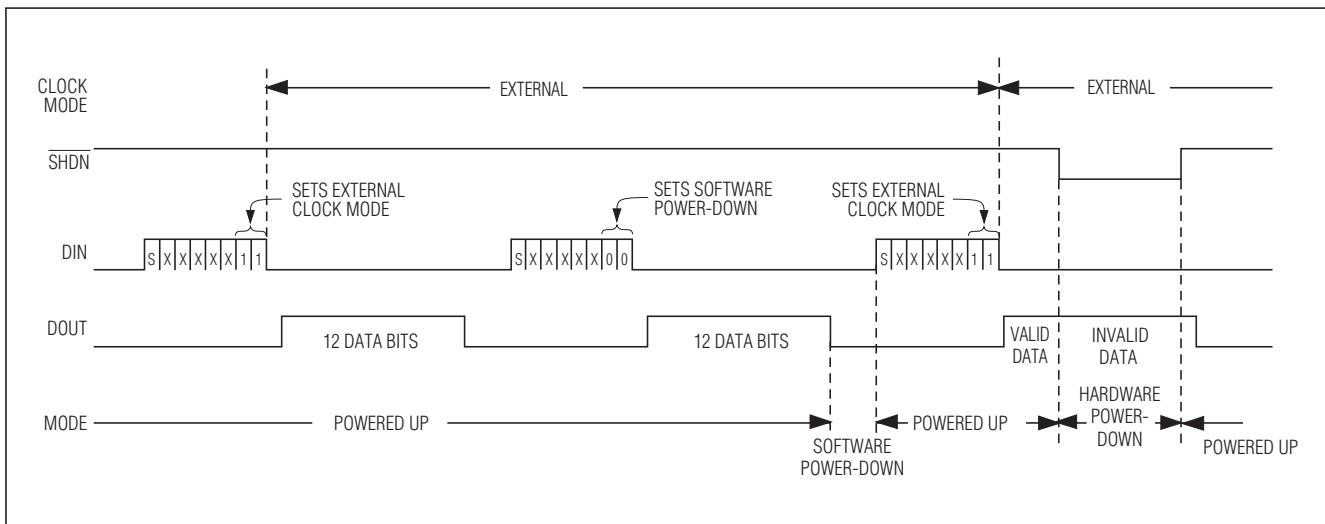

### パワーダウン

最大サンプリングレートよりも遅い速度で動作している場合、MAX1245を自動パワーダウンモードに設定することで、大幅に電力を節約することができます。図13に平均消費電流をサンプリングレートの関数として示します。各変換の間でコンバータを低電流のシャットダウン状態にすることによって、電力を節約できます。

パワーダウンを選択するには、 $\overline{SHDN}$ をハイにしてDIN制御バイトのビット1とビット0を使用します(表1と表4)。 $\overline{SHDN}$ をローに強制すると、いつでもコンバータを完全にシャットダウンすることができます。 $\overline{SHDN}$ は制御バイトのビット1とビット0に優先します(表5)。

パワーダウンモード時、自己消費電流を必要とするすべてのチップ機能がターンオフし、 $I_{DD}$ が1.2 $\mu$ A (typ)まで低下します。

図12aと図12bに、外部および内部クロックモード時のさまざまなパワーダウンシーケンスを示します。

### ソフトウェアによるパワーダウン

制御バイトのビットPD1とPD0を使用してソフトウェアのパワーダウンをアクティブにすることができます。表4に示すように、PD1とPD0はクロックモードを指定するためにも使用されます。ソフトウェアによるシャットダウンになると、変換が終了するまでADCは最後に指定されたクロックモードで動作し続けます。その後、ADCはパワーダウンし、低自己消費電流状態になります。

図11a. 外部クロックモード、15クロック/変換のタイミング

図11b. 外部クロックモード、16クロック/変換のタイミング

# +2.375V、低電力、8チャネル、シリアル12ビットADC

**MAX1245**

図12a. パワーダウンモードのタイミング図(外部クロック)

図12b. パワーダウンモードのタイミング図(内部クロック)

表4. ソフトウェアパワーダウンとクロックモード

| PD1 | PD0 | DEVICE MODE    |

|-----|-----|----------------|

| 1   | 1   | External Clock |

| 1   | 0   | Internal Clock |

| 0   | 1   | Unassigned     |

| 0   | 0   | Power-Down     |

表5. ハード配線のパワーダウンと内部クロック周波数

| SHDN STATE | DEVICE MODE | INTERNAL CLOCK FREQUENCY |

|------------|-------------|--------------------------|

| 1          | Enabled     | 225kHz                   |

| Open       | Enabled     | 1.5MHz                   |

| 0          | Power-Down  | N/A                      |

# +2.375V、低電力、8チャネル、シリアル12ビットADC

表6. フルスケールとゼロスケール

| UNIPOLAR MODE |            | BIPOLAR MODE        |            |                     |

|---------------|------------|---------------------|------------|---------------------|

| Full Scale    | Zero Scale | Positive Full Scale | Zero Scale | Negative Full Scale |

| VREF + COM    | COM        | VREF/2 + COM        | COM        | -VREF/2 + COM       |

内部クロックモードでは、MAX1245がソフトウェアによるパワーダウンに入った後でもインターフェースはアクティブ状態を保ち、変換結果をクロックアウトすることができます。

DINの最初のロジック1がスタートビットと見なされ、これによってMAX1245はパワーアップします。スタートビットに続いて、データ入力ワードまたは制御バイトによってもクロックモードとパワーダウン状態が決定されます。例えば、DINワードがPD1 = 1を含んでいると、MAX1245はパワーアップ状態に留まります。PD0 = PD1 = 0のときは、1回だけ変換が行われ、その後再びパワーダウンします。

## ハードウェアによるパワーダウン

SHDNをローにすると、コンバータはハードウェアによるパワーダウン状態に入ります。ソフトウェアによるパワーダウンモードとは異なり、変換は終了せずに、SHDNがローになったときに停止します。SHDNは、内部クロックモードでのクロック周波数も制御します。SHDNをオープン状態にすると、内部クロック周波数が1.5MHzに設定されます。SHDNがオープン状態で通常動作に戻った場合、約 $2M\Omega \times C_L$ の $t_{RC}$ 遅延時間があります(ここで $C_L$ はSHDNピンでの容量負荷です)。SHDNをハイにすると、内部クロック周波数が225kHzに設定されます。この機能はリファレンス電圧のセッティング時間の必要条件を緩和します。

## 外部リファレンス

MAX1245は外部リファレンスを必要とします。リファレンスの電圧範囲は1V~V<sub>DD</sub>です。

VREFの入力インピーダンスは、DC電流に対して最小18kΩです。変換時には、リファレンスは最大250μAのDC負荷電流を供給する能力を持ち、また出力インピーダンスは10Ω以下でなければなりません。リファレンスの出力インピーダンスがこれより大きい場合やノイズが多い場合は、VREFピンを0.1μFのコンデンサによってピン近くでバイパスしてください。

## 伝達関数

表6に、2.048Vリファレンスを使用した場合のユニポーラとバイポーラモードでのフルスケール電圧範囲を示します。

民生用温度範囲(0°C~+70°C)で1 LSB以下の精度を達成するためには、外部リファレンスの温度係数は4ppm/°C以下にしてください。

図13. 平均消費電流 対 変換レート

図14は通常のユニポーラ入力/出力(I/O)伝達関数を示しています。図15はバイポーラ入力/出力(I/O)伝達関数です。コード遷移は隣り合う整数のLSB値の中間点で起こります。出力コーディングはバイナリで、ユニポーラ動作では1 LSB = 500μV (2.048V / 4096)、バイポーラ動作では1 LSB = 500μV[(2.048V / 2 - -2.048V / 2) / 4096]となります。

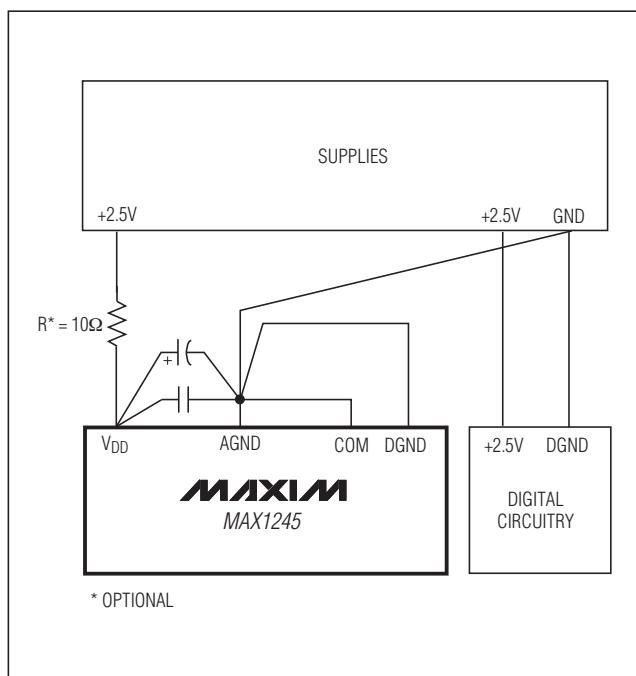

## レイアウト、グランド、およびバイパス

最高の性能を得るためにプリント回路基板を使用してください。ワイヤラップボードは推奨しません。ボードレイアウトはデジタル信号ラインとアナログ信号ラインが分離するようにしてください。アナログとデジタル(特にクロック)ラインを互いに並行に走らせないでください。また、デジタルラインをADCパッケージの下に配線しないようにしてください。

図16に、推奨するシステムグランド接続法を示します。1点アナロググランド(「スター」グランドポイント)をAGNDに設定し、ロジックグランドとは分離してください。その他すべてのアナロググランドとDGNDをスター型グランドにしてください。このグランドに他のデジタルシステムグランドを接続しないでください。ノイズを排除するために、スターグランドから電源へのグランドリターンは可能な限り短くするとともに低インピーダンスにしてください。

# +2.375V、低電力、8チャネル、シリアル12ビットADC

**MAX1245**

図14. ユニポーラの伝達関数、フルスケール(FS) = VREF + COM、ゼロスケール(ZS) = COM

$V_{DD}$ 電源内の高周波ノイズはADC内の高速コンパレータに影響を与える可能性があります。この電源はMAX1245のピン20に近いところで、 $0.1\mu F$ と $4.7\mu F$ コンデンサを使用してスターグランドにバイパスしてください。最高の電源ノイズ除去を得るために、コンデンサのリード線を可能な限り短くしてください。 $+2.5V$ 電源のノイズが特に大きい場合は、 $10\Omega$ 抵抗をローパスフィルタとして接続することができます(図16)。

図15. バイポーラの伝達関数、フルスケール(FS) = VREF / 2 + COM、ゼロスケール(ZS) = COM

図16. 電源グランド接続図

# +2.375V、低電力、8チャネル、 シリアル12ビットADC

図17. MAX1245のQSPI接続図

## QSPIとの高速ディジタルインタフェース

図17の回路を用いると、MAX1245をQSPIとインターフェースすることができます( $f_{SCLK} = 1.5\text{MHz}$ 、CPOL = 0、CPHA = 0)。このQSPI回路は各8個のチャネルで変換を行うようにプログラムすることができます。QSPIはそれ自体がマイクロシーケンサを備えているため、変換結果はCPUに負担をかけることなくメモリに記憶されます。

最大外部クロック周波数が1.5MHzのため、MAX1245は1.5MHzまでQSPIとコンパチブルです。

# +2.375V、低電力、8チャネル、シリアル12ビットADC

**MAX1245**

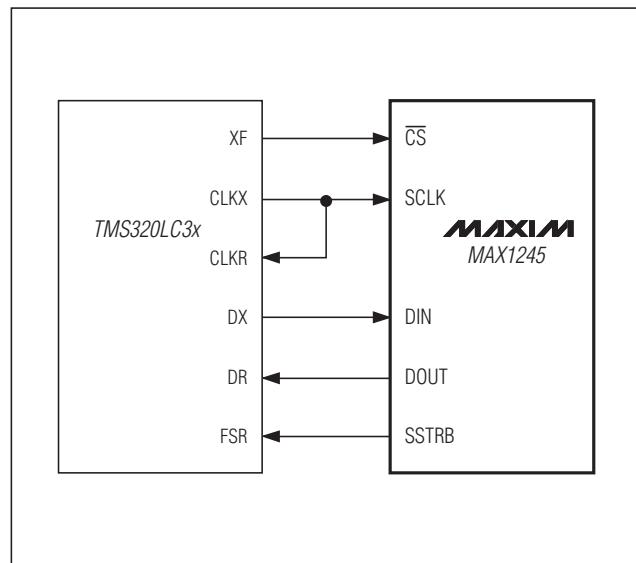

## TMS320LC3xからMAX1245へのインターフェース

図18に示すのは、外部クロックモードでMAX1245をTMS320にインターフェースするためのアプリケーション回路です。このインターフェースのタイミング図を図19に示します。

MAX1245の変換を開始し、結果を読み取るための手順は以下のとおりです。

- 1) TMS320はCLKX(送信クロック)がアクティブハイ出力クロック、CLKR(TMS320受信クロック)がアクティブハイ入力クロックとなるように設定してください。TMS320のCLKXとCLKRはMAX1245のSCLK入力と相互に接続します。

- 2) MAX1245のCSピンはTMS320のXF\_I/Oポートによってローに駆動し、MAX1245のDINにデータがクロックインすることができるようになります。

- 3) 変換を開始するために8ビットワード(1XXXXX11)をMAX1245に書き込み、デバイスを外部クロックモードに設定します。表1を参照して、ユーザのアプリケーションに適したXXXXXビットを選択してください。

- 4) MAX1245のSSTRB出力はTMS320のFSR入力により監視されます。SSTRB出力での立下りエッジは、変換が進行中であることを示し、データをMAX1245から受け取る準備ができていることを示します。

- 5) TMS320は、次に続くSCLK 16個の各立上りエッジで1データビットずつ読み取ります。これらのデータビットは12ビットの変換結果を表しています。この後に続く4ビットは無視してください。

- 6) 次の変換が開始されるまではCSをハイにして、MAX1245をディセーブルします。

図18. MAX1245からTMS320へのシリアルインターフェース

図19. TMS320のシリアルインターフェースタイミング図

# +2.375V、低電力、8チャネル、 シリアル12ビットADC

## チップ情報

TRANSISTOR COUNT: 2554

## パッケージ

最新のパッケージ図面情報およびランドパターンは、[japan.maxim-ic.com/packages](http://japan.maxim-ic.com/packages)を参照してください。なお、パッケージコードに含まれる「+」、「#」、または「-」はRoHS対応状況を表したものでしかありません。パッケージ図面はパッケージそのものに関するものでRoHS対応状況とは関係がなく、図面によってパッケージコードが異なることがある点を注意してください。

| パッケージタイプ | パッケージコード | ドキュメントNo.      |

|----------|----------|----------------|

| 20 PDIP  | A20-1    | <b>21-0056</b> |

| 20 SSOP  | P20-4    | <b>21-0043</b> |

# +2.375V、低電力、8チャネル、 シリアル12ビットADC

## 改訂履歴

| 版数 | 改訂日   | 説明                 | 改訂ページ |

|----|-------|--------------------|-------|

| 0  | 6/96  | 初版                 | —     |

| 1  | 11/09 | 「型番」表からダイスパッケージを削除 | 1     |

MAX1245

マキシム・ジャパン株式会社

〒169-0051 東京都新宿区西早稲田3-30-16(ホリゾン1ビル)

TEL. (03)3232-6141 FAX. (03)3232-6149

Maximは完全にMaxim製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。Maximは隨時予告なく回路及び仕様を変更する権利を留保します。

**Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600** 21