## MAX1127の評価キット

**Evaluates: MAX1126/MAX1127**

### 概要

MAX1127の評価キット(EVキット)は、クワッド、12ビットアナログ-ディジタルコンバータ(ADC) MAX1126/MAX1127の性能評価に必要な全部品を内蔵した完全実装および試験済みの基板です。MAX1126/MAX1127は差動アナログ入力信号で動作します。このEVキットは、これらの信号をユーザが用意するシングルエンド入力ソースから生成します。ADCが生成するデジタル出力は、ユーザが用意する高速ロジックアナライザまたはデータ収集システムによって容易にサンプリングすることができます。また、このEVキットは、標準的なロジック解析システムとの統合を容易にするデシリアルライザを内蔵しています。このEVキットは、1.8V~3.3Vの電源(オプションのFPGAの場合は1.5V)で動作し、ユーザが用意するAC信号からクロック信号を発生する回路を内蔵しています。このEVキットはMAX1127を搭載した状態で提供されます。MAX1126を評価するためには、ピンコンパチブルなMAX1126の無料サンプルをご請求ください。

### デバイス選択表

| PART       | SPEED (MspS) |

|------------|--------------|

| MAX1126EGK | 40           |

| MAX1127EGK | 65           |

### 特長

- ◆ 最大サンプリングレート : 65MspS (MAX1127)

- ◆ 低電圧および低電力動作

- ◆ オプションのクロック整形回路を内蔵

- ◆ シリアルSLVS/LVDS出力

- ◆ LVPECL差動出力ドライバを内蔵

- ◆ デシリアルライザを内蔵

- ◆ LVDSテストモード

- ◆ 実装および試験済み

- ◆ MAX1126も評価可能

### 型番

| PART         | TEMP RANGE   | IC PACKAGE |

|--------------|--------------|------------|

| MAX1127EVKIT | 0°C to +70°C | 68 QFN     |

注: MAX1126を評価するためには、MAX1127EVKITとともにMAX1126EGKの無料サンプルをご請求ください。

### 部品メーカー

| SUPPLIER              | PHONE        | FAX          | WEBSITE               |

|-----------------------|--------------|--------------|-----------------------|

| AVX                   | 843-946-0238 | 843-626-3123 | www.avxcorp.com       |

| Central Semiconductor | 631-435-1110 | 631-435-1824 | www.ctralsemi.com     |

| Diodes Inc            | 805-446-4800 | 805-446-4850 | www.diodes.com        |

| Panasonic             | 714-373-7366 | 714-737-7323 | www.panasonic.com     |

| TDK                   | 847-803-6100 | 847-390-4405 | www.component.tdk.com |

| Vishay/Vitramon       | 203-268-6261 | 203-452-5670 | www.vishay.com        |

| Zetex USA             | 631-543-7100 | 631-864-7630 | www.zetex.com         |

注: これらの部品メーカーにお問い合わせする際には、MAX1127を使用していることをお知らせください。

Maxim Integrated Products 1

本データシートに記載された内容はMaxim Integrated Productsの公式な英語版データシートを翻訳したものです。翻訳により生じる相違及び誤りについては責任を負いかねます。正確な内容の把握には英語版データシートをご参照ください。

無料サンプル及び最新版データシートの入手には、マキシムのホームページをご利用ください。<http://japan.maxim-ic.com>

# MAX1127の評価キット

## 部品リスト

| DESIGNATION                        | QTY | DESCRIPTION                                                                                                                |

|------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------|

| C1-C12,<br>C59-C64,<br>C81-C85     | 23  | 0.1 $\mu$ F $\pm$ 20%, X5R 10V ceramic capacitors (0402)<br>TDK C1005X5R1A104M                                             |

| C13-C20                            | 0   | Not installed (0603)                                                                                                       |

| C21-C28                            | 8   | 39pF $\pm$ 5%, 50V C0G ceramic capacitors (0402)<br>TDK C1005C0G1H390J                                                     |

| C29-C44,<br>C77-C80,<br>C92, C93   | 20  | 1.0 $\mu$ F $\pm$ 20%, X5R 6.3V ceramic capacitors (0402)<br>TDK C1005X5R0J105M                                            |

| C45, C46, C47,<br>C55,<br>C86-C89  | 8   | 220 $\mu$ F $\pm$ 20%, 6.3V tantalum capacitors (C case)<br>AVX TPSC227M006R0250                                           |

| C48, C49, C50,<br>C56              | 0   | Not installed (C case)                                                                                                     |

| C51, C52, C53,<br>C57,<br>C90, C91 | 6   | 10 $\mu$ F $\pm$ 20%, X5R 10V ceramic capacitors (1210)<br>TDK C3225X5R1A106M                                              |

| C54                                | 1   | 2.2 $\mu$ F $\pm$ 20%, X5R 6.3V ceramic capacitor (0603)<br>TDK C1608X5R0J225M                                             |

| C58, C65-C76                       | 13  | 0.01 $\mu$ F $\pm$ 5%, 25V C0G ceramic capacitors (0603)<br>TDK C1608C0G1E103J                                             |

| C94-C121                           | 28  | 0.1 $\mu$ F $\pm$ 20%, X5R 6.3V ceramic capacitors (0201)<br>TDK C0603X5R0J104M                                            |

| D1                                 | 1   | Dual Schottky diode (SOT23)<br>Zetex BAS70-04<br>Central Semiconductor CMPD6263S<br>Vishay BAS70-04<br>Diodes Inc BAS70-04 |

| D2, D3                             | 2   | Green surface-mount LEDs (SS)<br>Panasonic LNJ308G8LRA                                                                     |

| J1-J5                              | 5   | SMA PC-mount connectors                                                                                                    |

| J6, J7,<br>J12-J15                 | 6   | Dual row, 40-pin headers                                                                                                   |

| J8-J11                             | 4   | 2-pin headers                                                                                                              |

| J16                                | 0   | Not installed                                                                                                              |

| DESIGNATION                          | QTY | DESCRIPTION                                                                            |

|--------------------------------------|-----|----------------------------------------------------------------------------------------|

| JU1-JU9, JU11,<br>JU12,<br>JU15-JU18 | 15  | Jumper, 3-pin headers                                                                  |

| JU10                                 | 0   | Not installed (SIP-3)                                                                  |

| JU13                                 | 1   | Jumper, dual row, 8-pin header                                                         |

| N1                                   | 1   | Digital logic n-channel MOSFET (SOT23), top mark = 702<br>Central Semiconductor 2N7002 |

| R1-R16,<br>R22-R25,<br>R82-R93       | 0   | Not installed (0603)                                                                   |

| R17-R21,<br>R58-R75                  | 23  | 49.9 $\Omega$ $\pm$ 1% resistors (0603)                                                |

| R26-R36,<br>R76-R81                  | 0   | Not installed (0402)                                                                   |

| R37-R44                              | 8   | 10 $\Omega$ $\pm$ 1% resistors (0402)                                                  |

| R45-R50                              | 6   | 100 $\Omega$ $\pm$ 1% resistors (0603)                                                 |

| R51                                  | 1   | 100k $\Omega$ potentiometer, 19 turn, 3/8in                                            |

| R52, R53, R56                        | 3   | 4.02k $\Omega$ $\pm$ 1% resistors (0603)                                               |

| R54                                  | 1   | 5k $\Omega$ potentiometer, 19 turn, 3/8in                                              |

| R55                                  | 1   | 2k $\Omega$ $\pm$ 1% resistor (0603)                                                   |

| R57                                  | 1   | 13.0k $\Omega$ $\pm$ 1% resistor (0603)                                                |

| R94, R95                             | 2   | 4.7k $\Omega$ $\pm$ 5% resistors (0603)                                                |

| R96, R97                             | 2   | 330 $\Omega$ $\pm$ 5% resistors (1206)                                                 |

| R98                                  | 1   | 10k $\Omega$ $\pm$ 5% resistor (0603)                                                  |

| SW1                                  | 1   | Momentary pushbutton switch                                                            |

| T1-T4                                | 4   | 1:1 800MHz RF transformers<br>Mini-Circuits ADT1-1WT                                   |

| TP1-TP9                              | 9   | Test points (black)                                                                    |

| TP10-TP12                            | 0   | Not installed                                                                          |

| U1                                   | 1   | Maxim MAX1127EGK (68-pin QFN)                                                          |

| U2                                   | 1   | Maxim MAX9111ESA (8-pin SO)                                                            |

| U3-U8                                | 6   | Maxim MAX9375EUA (8-pin $\mu$ MAX)                                                     |

| U9                                   | 1   | Xilinx XC2V80-5FG256C (FGBGA-256) or<br>Xilinx XC2V80-5FG256I (FGBGA-256)              |

| U10                                  | 1   | Xilinx XC18V01SO20C (20-pin SO)                                                        |

| None                                 | 16  | Shunts                                                                                 |

| None                                 | 1   | MAX1127 PC board                                                                       |

## クイックスタート

### 推奨機器

- DC電源：

|             |             |

|-------------|-------------|

| クロック(CVDD)  | 1.8V, 100mA |

| アナログ(AVDD)  | 1.8V, 500mA |

| デジタル(OVDD)  | 1.8V, 150mA |

| バツファ(VPECL) | 3.3V, 350mA |

- オプション

- デシリアルライザコア(VD1.5) 1.5V, 200mA

- デシリアルライザI/O (VD3.3) 3.3V, 200mA

- 信号発生器、低位相ノイズおよび低ジッタ、クロック入力信号用(HP 8662A, HP 8644Bなど)

- 信号発生器、4台、アナログ入力信号用(HP 8662A, HP 8644Bなど)

- ロジックアナライザまたはデータ収集システム(HP 16500C, TLA621など)

- アナログバンドパスフィルタ、入力信号およびクロック信号用(Allen Avionics, K&L Microwaveなど)

- デジタル電圧計

### 手順

MAX1127のEVキットは、完全実装および試験済みの表面実装基板です。以下の手順で基板の動作を確認してください。すべての接続が終了するまでは電源をオンにしたり信号発生器をイネーブルしたりしないでください。

- シャントが下記の位置に取り付けられていることを確認してください。

JU1～JU5 (1～2)→全チャネルイネーブル

JU6 (2～3)→ 単一終端

JU7 (2～3)→ LVDS出力

JU8 (2～3)→ 2の補数出力

JU9 (2～3)→ 通常動作

JU10、JU11、JU12 (2～3)→ クロック周波数範囲48.75MHz～65MHz

JU13 (3～4)→ 内部リファレンスイネーブル

JU15～JU18 (2～3)→ デシリアルライザ出力イネーブル

- クロック信号発生器をクロックバンドパスフィルタの入力に接続してください。

- クロックバンドパスフィルタの出力をJ5と表示されたSMAコネクタに接続してください。

- アナログ信号入力発生器を所望のアナログバンドパスフィルタの入力に接続してください。

- アナログバンドパスフィルタの出力をJ1～J4と表示されたSMAコネクタに接続してください。アナログ入力信号はJ8～J11で監視することができます。

注：4チャネルすべてを独立または同時に動作させることができます。

- ロジックアナライザをヘッダJ6 (SLVSまたはLVDS対応信号)、またはJ12～J15(デシリアルライズされた3.3V COMS対応信号)のいずれかに接続してください。ヘッダの接続については、「出力ビット位置」の項をご覧ください。

- 1.8V、500mA電源をAVDDに接続してください。この電源のグランド端子をGNDに接続してください。

- 1.8V、150mA電源をOVDDに接続してください。この電源のグランド端子をGNDに接続してください。

- 1.8V、100mA電源をCVDDに接続してください。この電源のグランド端子をGNDに接続してください。

注：MAX9111を使用するときは、CVDDを3.3Vとする必要があります。

- 3.3V、350mAの電源をVPECLに接続してください。この電源のグランド端子をGNDに接続してください。

- 1.5V、200mAの電源をVD1.5に接続してください。この電源のグランド端子をGNDに接続してください。

- 3.3V、200mAの電源をVD3.3に接続してください。この電源のグランド端子をGNDに接続してください。

- すべての電源をオンにしてください。

- 信号発生器をイネーブルしてください。振幅が2.6V<sub>P-P</sub>以上の48.75MHz～65MHzの信号を出力するようにクロック信号発生器を設定してください。振幅が1V<sub>P-P</sub>以下の所望の周波数を出力するようにアナログ入力信号発生器を設定してください。すべての信号発生器は位相ロックしているものとします。

- ロジックアナライザをイネーブルしてください。

- ロジックアナライザを使ってデータを収集してください。

### 詳細

MAX1127のEVのキットは、12ビット、シリアルSLVS/LVDS出力ADCのMAX1126 (40Msps)またはMAX1127 (65Msps)の性能評価に必要な全部品を内蔵した完全実装および試験済みの基板です。このEVキットはMAX1127を搭載した状態で提供され、最大クロック周波数( $f_{CLK}$ ) 65MHzで評価することができます。

MAX1127は差動入力信号で動作しますが、内蔵のトランジスタ(T1～T4)は利用し易いシングルエンドソース出力を所要の差動信号に変換します。MAX1127の入力信号は、差動オシロスコーププローブを使ってヘッダJ8～J11で測定することができます。

# MAX1127の評価キット

出力レベルトランスレータ(U3～U8)は、MAX1127のSLVS/LVDS出力信号をバッファし、種々のロジックアナライザによって取り込むことが可能なより高い電圧のLVPECL信号に変換します。SLVS/LVDS出力にはヘッダJ6でアクセスすることができ、LVPECL出力にはヘッダJ7でアクセスすることができます。

このEVキットは、MAX1127の性能を最適化する4層プリント基板として設計されています。アナログ、デジタル、クロック、およびバッファの各電源プレーンを分離することによって、アナログ信号とデジタル信号の間のノイズ結合を最小化しています。すなわち、50Ωのコプラナ伝送ラインがアナログおよびクロック入力に使用され、100Ωの差動コプラナ伝送ラインがすべてのデジタルLVDS出力に使用されています。すべての差動出力は、真のデジタル出力と相補型デジタル出力の間で100Ω終端抵抗器を用いて適正に終端されています。レイアウトに依存するデータスキューを最小にするために、100Ω差動SLVS/LVDSラインの配線長は、千分の数インチ以内に合わせてあります。

## 電源

最適な性能を得るために、MAX1127のEVキットではアナログ、デジタル、クロック、およびバッファの各電源を分離する必要があります。MAX1127のアナログ部とデジタル部への給電には2個の1.8V電源を使用します。クロック回路には1.8V電源から給電します(MAX9111を使用する場合は、「オプションのクロック整形回路」の項をご覧ください)。EVキットの出力バッファ(U3～U8)への給電には独立した3.3V電源を使用します。

## MAX1127のパワーダウン

MAX1127は複数の電源管理機能を備えています。MAX1127は、グローバルデバイスパワーダウンピンに加えて、ADCの各チャネル用に独立のパワーダウン

表1. パワーダウンシャントの設定(JU1～JU5)

| JUMPER         | SHUNT POSITION | POWER-DOWN CONNECTIONS | CHANNEL      | DESCRIPTION           |

|----------------|----------------|------------------------|--------------|-----------------------|

| JU1<br>(PD0)   | 1-2            | AVDD                   | 0            | Channel 0 disabled    |

|                | 2-3*           | GND                    |              | Channel 0 enabled     |

| JU2<br>(PD1)   | 1-2            | AVDD                   | 1            | Channel 1 disabled    |

|                | 2-3*           | GND                    |              | Channel 1 enabled     |

| JU3<br>(PD2)   | 1-2            | AVDD                   | 2            | Channel 2 disabled    |

|                | 2-3*           | GND                    |              | Channel 2 enabled     |

| JU4<br>(PD3)   | 1-2            | AVDD                   | 3            | Channel 3 disabled    |

|                | 2-3*           | GND                    |              | Channel 3 enabled     |

| JU5<br>(PDALL) | 1-2            | AVDD                   | ALL CHANNELS | All channels disabled |

|                | 2-3*           | GND                    |              | All channels enabled  |

\*デフォルト設定: JU1～JU5 (2～3)

ピンを備えています。ジャンパJU1～JU5は、データコンバータの電源管理機能を制御します。シャントの位置については表1をご覧ください。

## クロック

デフォルトでは、MAX1127のEVキットはユーザが用意するAC結合クロック信号をMAX1127のクロック入力にじかに接続するようになっています。このモードでは、ダイオードD1がクロック信号の振幅を制限します。クロック入力(J5)をオーバードライブすると、差動信号のスルーレートが増大するためクロックジッタが減少します。また、MAX1127のEVキットは、クロックSMAコネクタ(J5)に印加されるAC結合正弦波信号から可変デューティサイクルのクロック信号を生成するクロック整形回路(オプション)を内蔵しています。この回路を使用するためには、プリント回路(PC)基板上のR78で配線を切断し、R77とR35に0Ω抵抗器を取り付けてください。信号の周波数は、MAX1127の場合、65MHzを超えないものとします。正弦波入力信号周波数( $f_{CLK}$ )はADCのサンプリングレートを決定します。

## オプションのクロック整形回路

差動ラインレシーバ(U2)は、クロック入力信号を処理し、所要のCMOSクロック信号を生成します。この回路を使用するとき、CVDDパッドの電圧は3.3V以上でなければなりません。信号のデューティサイクルはポテンショメータR54によって調整することができます。3.3Vのクロック電源電圧(CVDD)の場合は、デューティサイクルが50% (推奨)のクロック信号を得るためにR54を調整してTP6とTP7のテストポイントで1.32Vの電圧が生成されるようにします。クロック信号はTP8で観察することができます。

## PLL周波数モードの選択

MAX1127のEVキットをデフォルトの65MHzクロック信号以外で駆動するとき、MAX1127のフェーズロッ

クループ(PLL)回路を状況に応じて設定する必要があります。

内蔵PLLの動作の詳細については、MAX1127のデータシートを参照してください。ジャンパJU10、JU11、およびJU12はMAX1127のPLLモードを制御します。シャントの位置については表2をご覧ください。

所望のクロック周波数が表2の最大/最小許容値内に入るようにしてください。

**表2. PLLシャントの設定(JU10～JU12)**

|                | JUMPER |      | INPUT CLOCK RANGE (MHz) |        |

|----------------|--------|------|-------------------------|--------|

|                | JU11   | JU12 | MIN                     | MAX    |

| SHUNT POSITION | 2-3*   | 2-3* | 48.750                  | 65.000 |

|                | 2-3    | 1-2  | 32.500                  | 48.750 |

|                | 1-2    | 2-3  | 24.375                  | 32.500 |

|                | 1-2    | 1-2  | 16.000                  | 24.375 |

\*デフォルト設定：JU10、JU11、JU12 (2～3)

### 入力信号

MAX1127は差動アナログ入力信号で動作しますが、EVキットに必要なのはユーザが用意する振幅1.4V<sub>P-P</sub>未満のシングルエンドアナログ入力信号のみです。内蔵のトランス(T1～T4)がシングルエンドアナログ入力信号を変換してADCの差動入力ピンに差動アナログ信号を生成します。

### リファレンス電圧

MAX1127のEVキットでは、設定によって、MAX1127内部のリファレンス、または安定した低ノイズの外部リファレンスを使用することができます。所望のリファレンスマードを設定するためには、ジャンパJU13を使用してください。シャントの設定については表3をご覧ください。

**表3. リファレンスシャントの設定(JU13)**

| SHUNT POSITION | DESCRIPTION                                                                        |

|----------------|------------------------------------------------------------------------------------|

| 1-2            | Internal reference disabled. Apply an external reference voltage at the REFIO pad. |

| 3-4*           | Internal reference enabled.                                                        |

| 5-6            | RESERVED. DO NOT USE.                                                              |

| 7-8            |                                                                                    |

\*デフォルト設定：JU13 (3～4)

### 出力信号

MAX1127は4つのシリアル、LVDS対応デジタル出力を備えています。各出力はチャネル0～3の変換済みアナログ入力信号を送出します。データ同期用として2つの

出力(CLKOUTとFRAME)が追加されています。詳しくはMAX1127のデータシートを参照してください。

### 出力形式

ジャンパJU3の設定によって、デジタル出力コードとして2の補数またはストレートオフセットバイナリのいずれかを選択することができます。ジャンパの設定については表4をご覧ください。

**表4. 出力形式シャントの設定(JU8)**

| SHUNT POSITION | TB PIN | DESCRIPTION                                                                                 |

|----------------|--------|---------------------------------------------------------------------------------------------|

| 1-2*           | AVDD   | <b>Straight offset binary selected.</b><br>Digital output in straight offset binary format. |

| 2-3            | GND    | <b>Two's complement selected.</b><br>Digital output in two's complement format.             |

\*デフォルト設定：JU8 (1～2)

### 二重終端の設定

MAX1127は、各出力(D0～D3、CLK、およびFRAME)の正(真)と負(相補)のラインの間にトリミングされた100Ωの終端抵抗器を内蔵しています。抵抗器を回路に接続する(二重終端)か、または抵抗器を回路から切り離す(单一終端)ためには、ジャンパJU6を使用してください。シャントの位置については表5をご覧ください。

**表5. 二重終端シャントの設定(JU6)**

| SHUNT POSITION | DT PIN | DESCRIPTION                                                           |

|----------------|--------|-----------------------------------------------------------------------|

| 1-2            | AVDD   | <b>Double termination selected.</b><br>Outputs are double terminated. |

| 2-3*           | GND    | <b>Single termination selected.</b><br>Outputs are single terminated. |

\*デフォルト設定：JU6 (2～3)

### SLVS出力

MAX1127は、その出力に低電圧差動信号(LVDS)またはスケーラブル低電圧信号(SLVS)を生成することができます。ジャンパJU7はMAX1127のこの機能を制御します。シャントの位置については表6をご覧ください。選択される出力信号のタイプに関係なく、出力バッファ(U3～U8)はデータをLVPECLロジックレベルに変換します。

# MAX1127の評価キット

表6. SLVSシャントの設定(JU7)

| SHUNT POSITION | SLVS/LVDS PIN    | DESCRIPTION  |

|----------------|------------------|--------------|

| 1-2            | AV <sub>DD</sub> | SLVS outputs |

| 2-3*           | GND              | LVDS outputs |

\*デフォルト設定: JU7 (2~3)

## LVDSテストパターン

信号完全性の問題のデバッグ用として、MAX1127はすべてのSLVS/LVDS出力チャネルに出荷時のデフォルトテストパターンを生成することができます。ジャンパJU9はこの機能を制御します。シャントの位置については表7をご覧ください。

表7. LVDSテストパターンシャントの設定(JU9)

| SHUNT POSITION | LVDSTEST PIN     | DESCRIPTION                                                                    |

|----------------|------------------|--------------------------------------------------------------------------------|

| 1-2            | AV <sub>DD</sub> | Test pattern (0000 1011 1101) transmitted, LSB first, on all SLVS/LVDS outputs |

| 2-3*           | GND              | Normal operation                                                               |

\*デフォルト設定: JU9 (2~3)

表8. 出力ビット位置

| SIGNAL |   | UNBUFFERED (LVDS OR SLVS) | BUFFERED (LVPECL) | DESCRIPTION |

|--------|---|---------------------------|-------------------|-------------|

| CH0    | P | J6-5                      | J7-5              | Channel 0   |

|        | N | J6-6                      | J7-6              |             |

| CH1    | P | J6-11                     | J7-11             | Channel 1   |

|        | N | J6-12                     | J7-12             |             |

| CLKOUT | P | J6-17                     | J7-17             | Clock       |

|        | N | J6-18                     | J7-18             |             |

| FRAME  | P | J6-23                     | J7-23             | Frame       |

|        | N | J6-24                     | J7-24             |             |

| CH2    | P | J6-29                     | J7-29             | Channel 2   |

|        | N | J6-30                     | J7-30             |             |

| CH3    | P | J6-35                     | J7-35             | Channel 3   |

|        | N | J6-36                     | J7-36             |             |

P: 真

N: 相補

## 出力ビット位置

MAX1127のデジタル出力は40ピンヘッダ(J6)に接続されます。プリント基板の配線長は、データスキューが最小になるようにかつデバイスのダイナミック性能全体が向上するように、整合されています。さらに、6個のドライバ(U3~U8)は、デジタル出力をバッファしてLVPECL対応信号にレベル変換します。ドライバは差動電圧振幅を増大させ、ロジックアナライザとの接続部に存在する大きな容量性負荷を駆動することができます。バッファの出力は40ピンヘッダ(J7)に接続されます。ヘッダJ6~J7のビット位置については表8をご覧ください。

## 内蔵デシリアルライザ

MAX1127のEVキットは、MAX1127のシリアル出力をパラレルデータストリームに変換するデシリアルライザを内蔵しています。デシリアルライザでは、これ自身を受信シリアルデータストリームに同期させる遅延ロックループ(DLL)が使用されます。ADCクロック周波数を変更するたびに、必ずSW1を押してDLLをリセットしてください。LED D3が点灯しない場合は、シリアルデータストリームが同期しておらず、デシリアルライザの出力は有効ではありません。

チャネル0～チャネル3のデータは、ヘッダJ12～J15で取り込まれます。ビット位置については表9をご覧ください。

**表9. 出力ビット位置(J12～J15)**

| BIT | POSITION |        |        |        |

|-----|----------|--------|--------|--------|

|     | CH0      | CH1    | CH2    | CH3    |

| CLK | J12-38   | J13-38 | J14-38 | J15-38 |

| D11 | J12-26   | J13-26 | J14-26 | J15-26 |

| D10 | J12-24   | J13-24 | J14-24 | J15-24 |

| D9  | J12-22   | J13-22 | J14-22 | J15-22 |

| D8  | J12-20   | J13-20 | J14-20 | J15-20 |

| D7  | J12-18   | J13-18 | J14-18 | J15-18 |

| D6  | J12-16   | J13-16 | J14-16 | J15-16 |

| D5  | J12-14   | J13-14 | J14-14 | J15-14 |

| D4  | J12-12   | J13-12 | J14-12 | J15-12 |

| D3  | J12-10   | J13-10 | J14-10 | J15-10 |

| D2  | J12-8    | J13-8  | J14-8  | J15-8  |

| D1  | J12-6    | J13-6  | J14-6  | J15-6  |

| D0  | J12-4    | J13-4  | J14-4  | J15-4  |

注：奇数番号が付いたピンはグランドに接続されます。残りのピンは接続なしです。

### デシリアルライザ出力イネーブル

ジャンパJU15～JU18は、デシリアルライザのCH0～CH3の各出力イネーブルを制御します。シャントの位置については表10をご覧ください。

### MAX1126の評価

MAX1127のEVキットはMAX1126の性能確認にも使用することができます。MAX1126を評価するためには、MAX1127をMAX1126EGKの無料サンプルと交換してください。

**表10. デシリアルライザ出力イネーブル

(JU15～JU18)**

| SHUNT POSITION | DESCRIPTION                  |

|----------------|------------------------------|

| 1-2            | Deserializer output disabled |

| 2-3*           | Deserializer output enabled  |

\*デフォルト設定：JU15～JU18 (2～3)

## MAX1127の評価キット

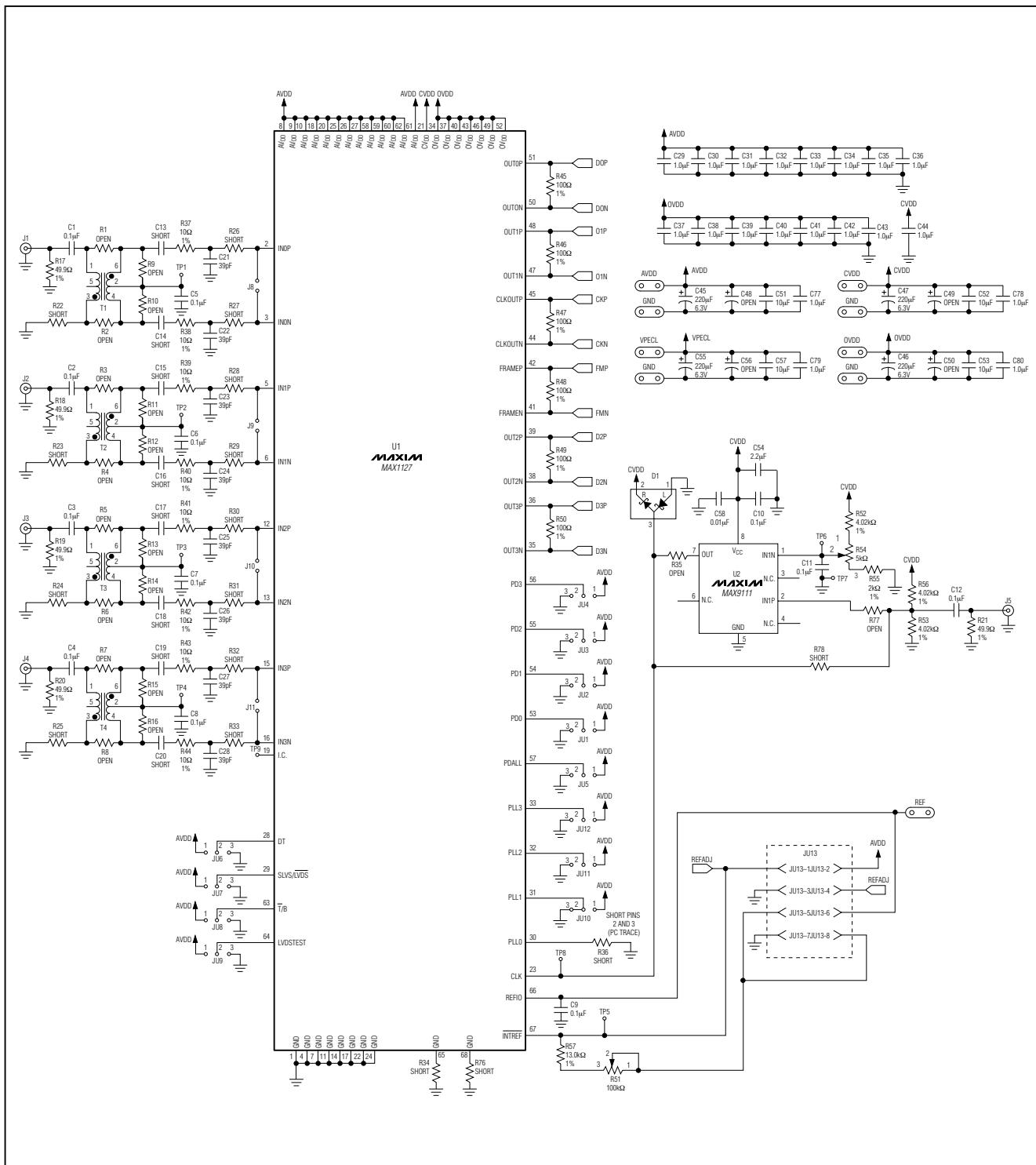

図1. MAX1127のEVキット回路図(1/4)

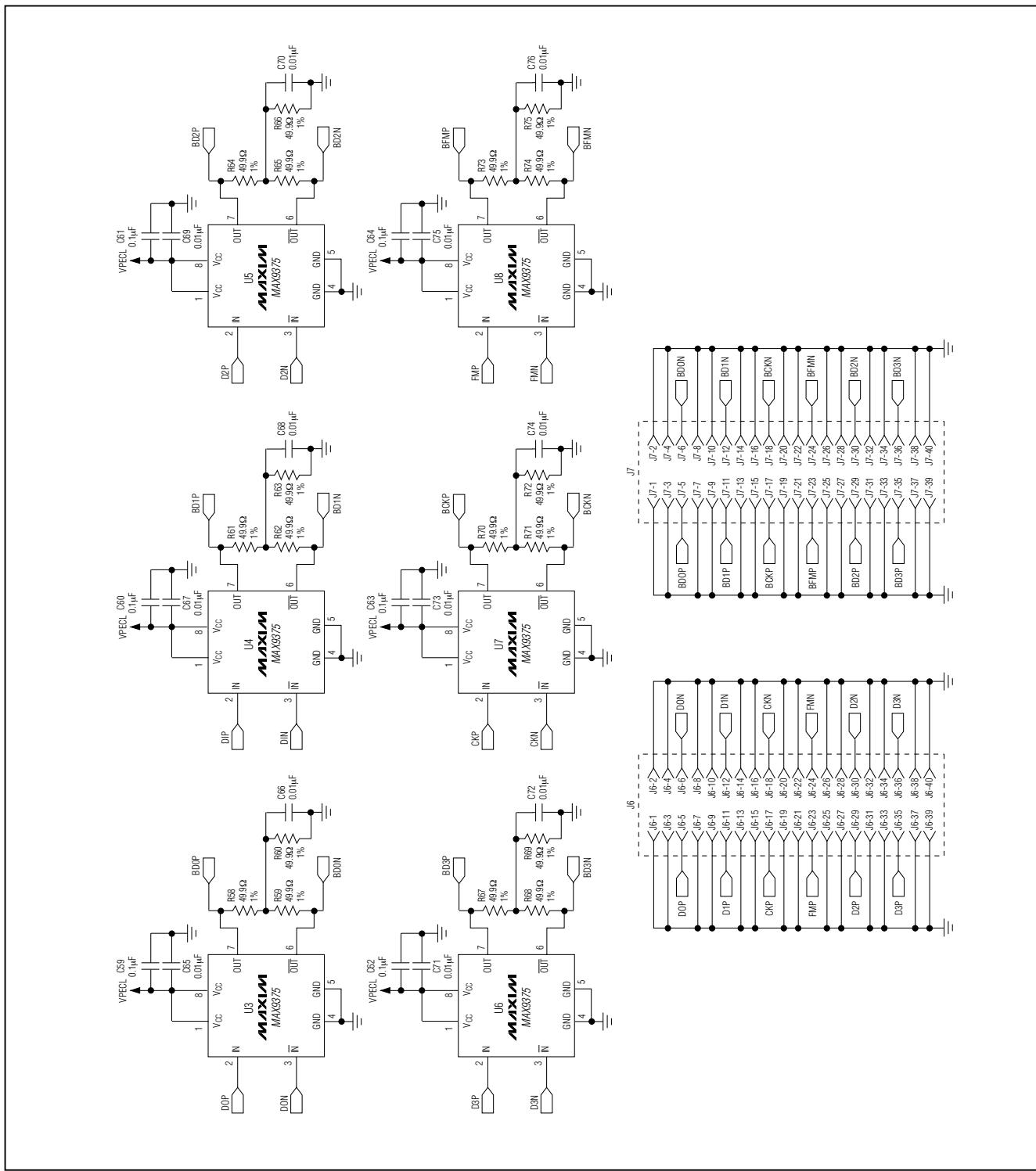

図1. MAX1127のEVキット回路図(2/4)

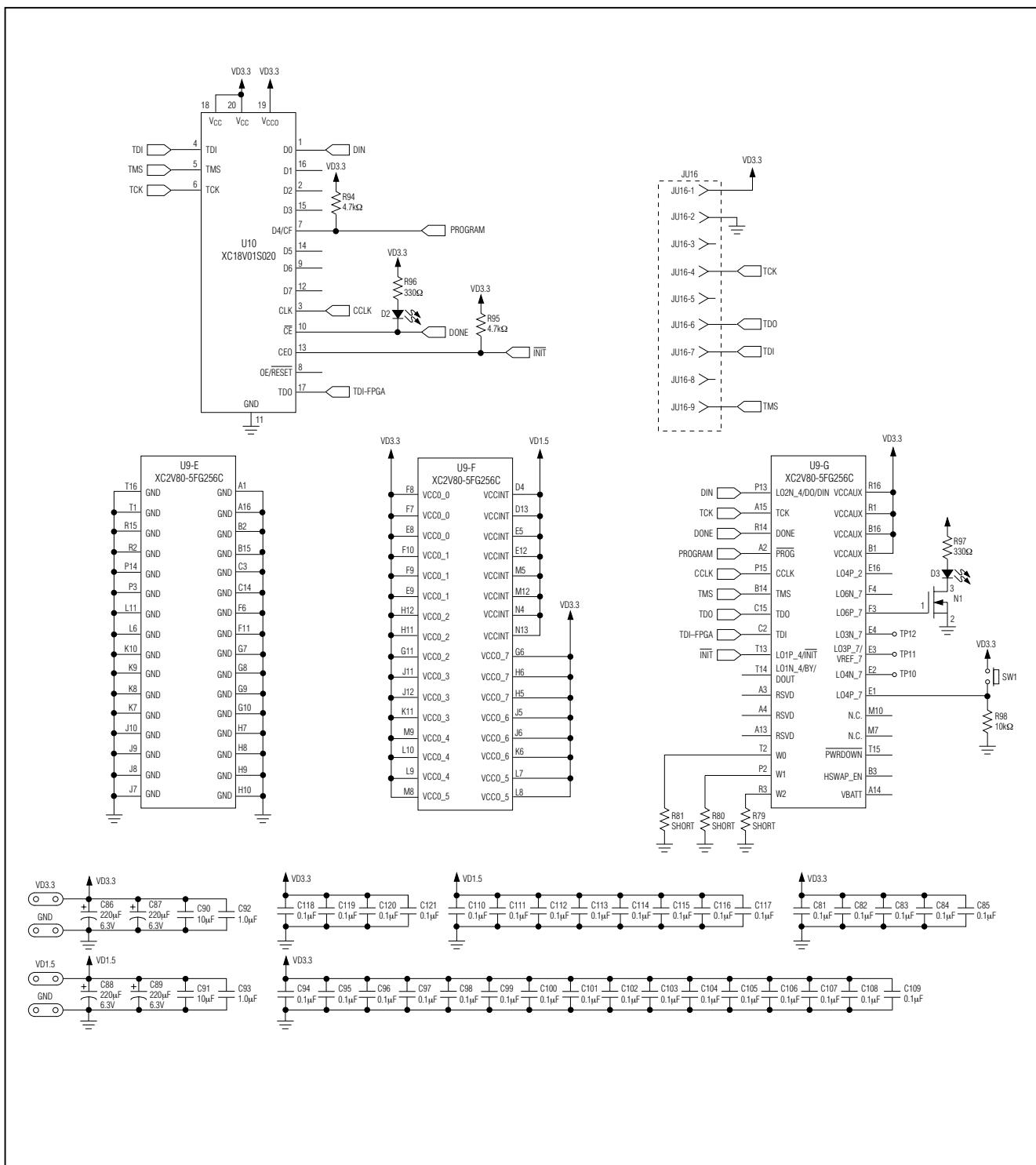

# Evaluates: MAX1126/MAX1127

## MAX1127の評価キット

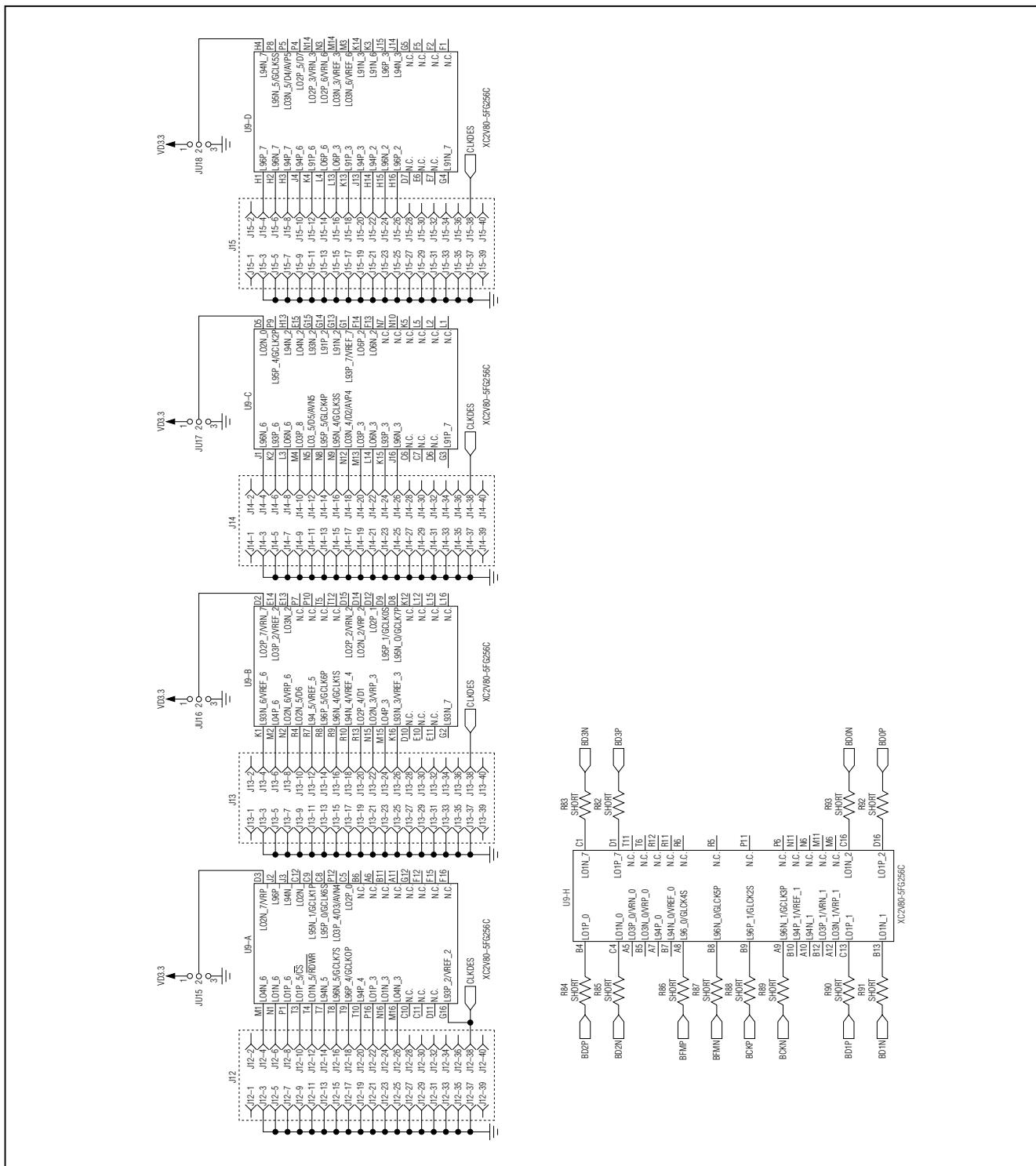

図1. MAX1127のEVキット回路図(4/4)

## MAX1127の評価キット

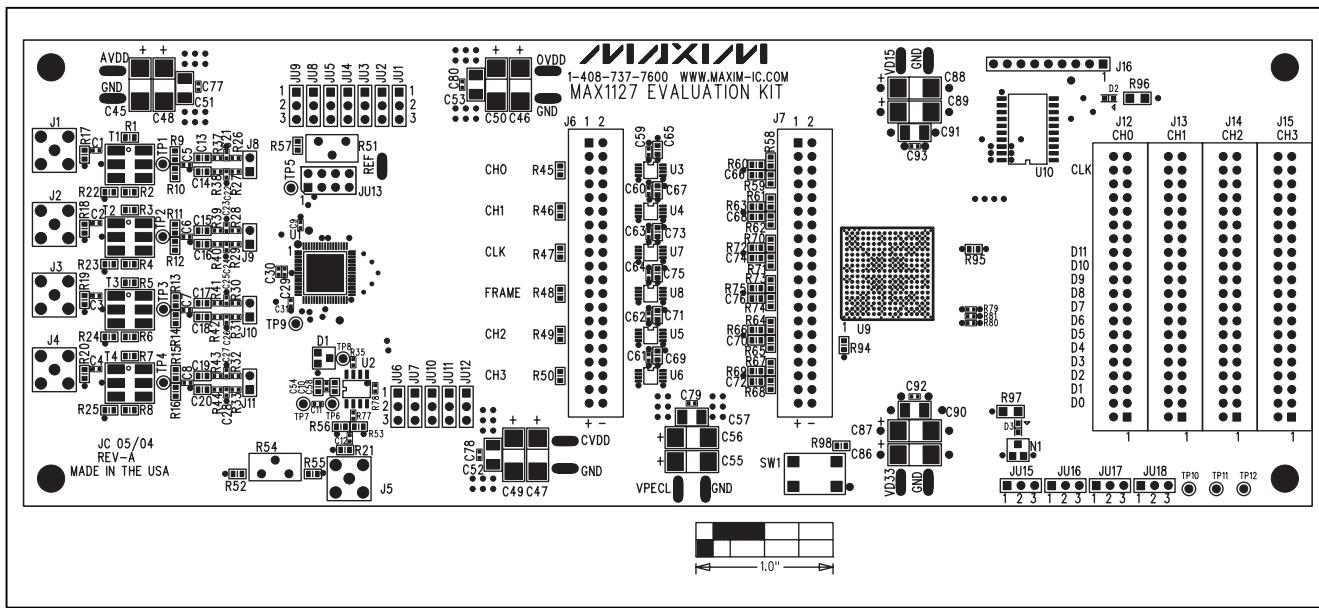

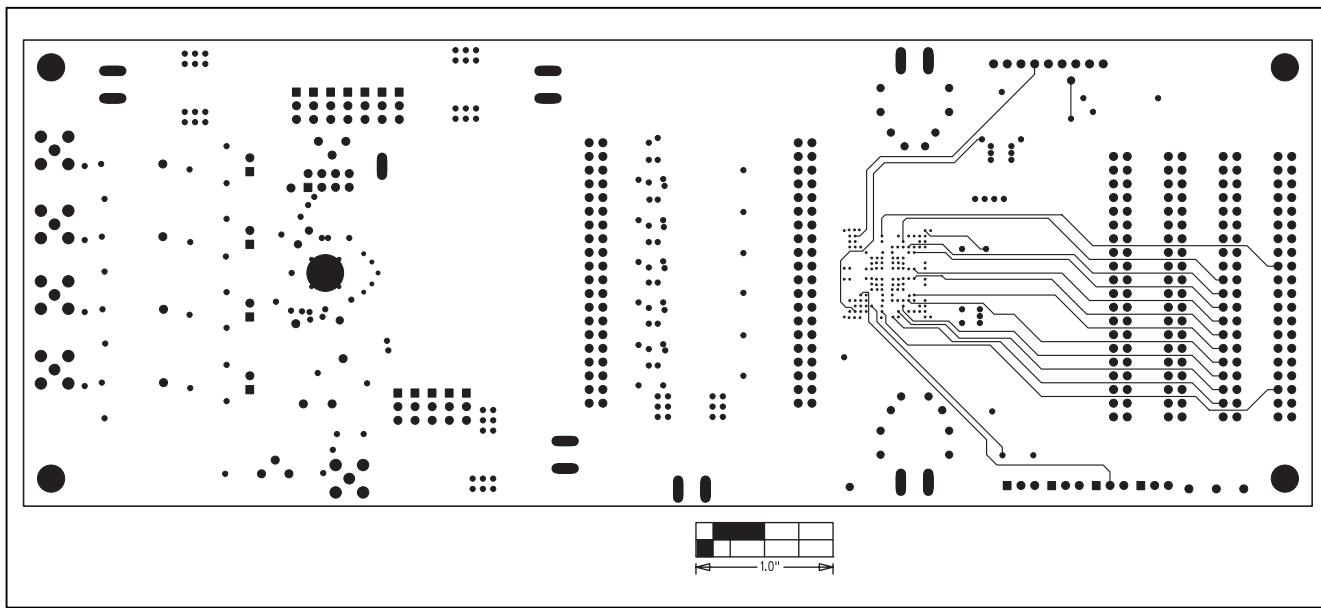

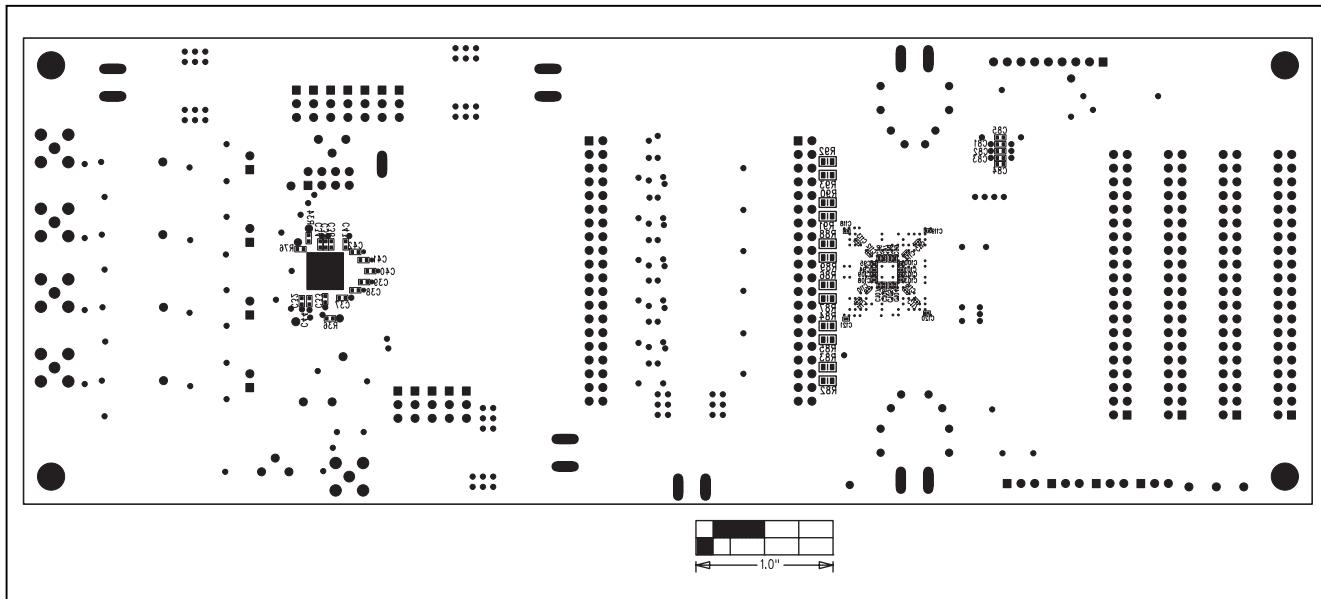

図2. MAX1127のEVキット部品配置ガイド-部品面

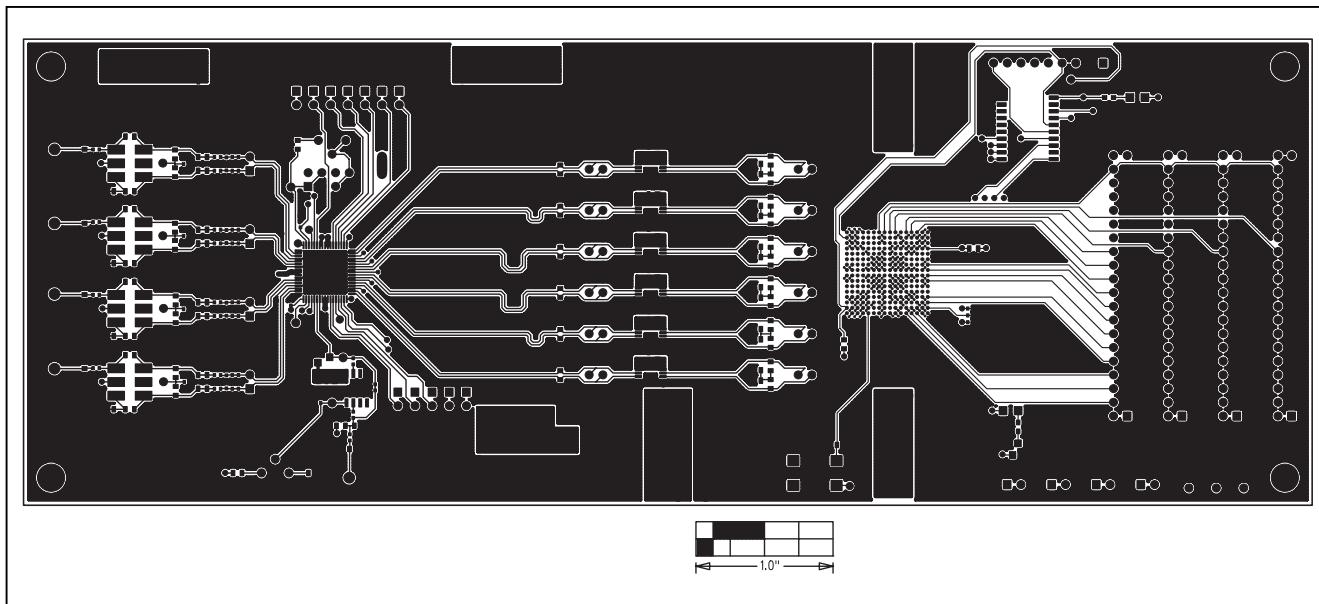

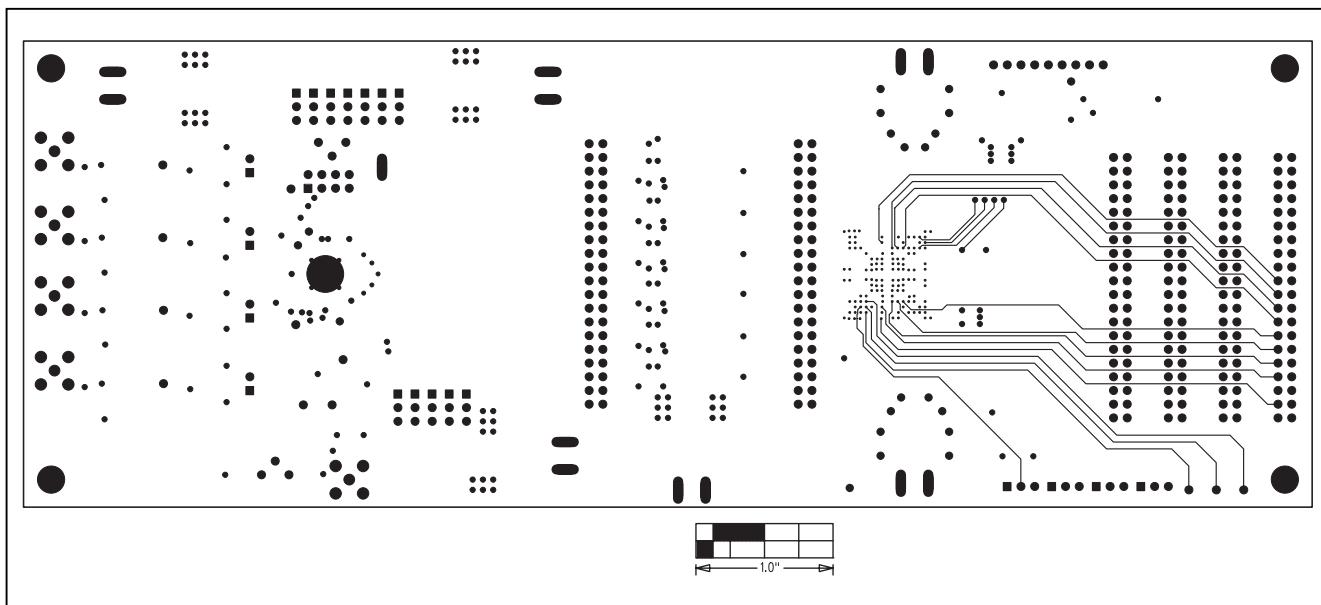

図3. MAX1127のEVキットプリント基板レイアウト-部品面

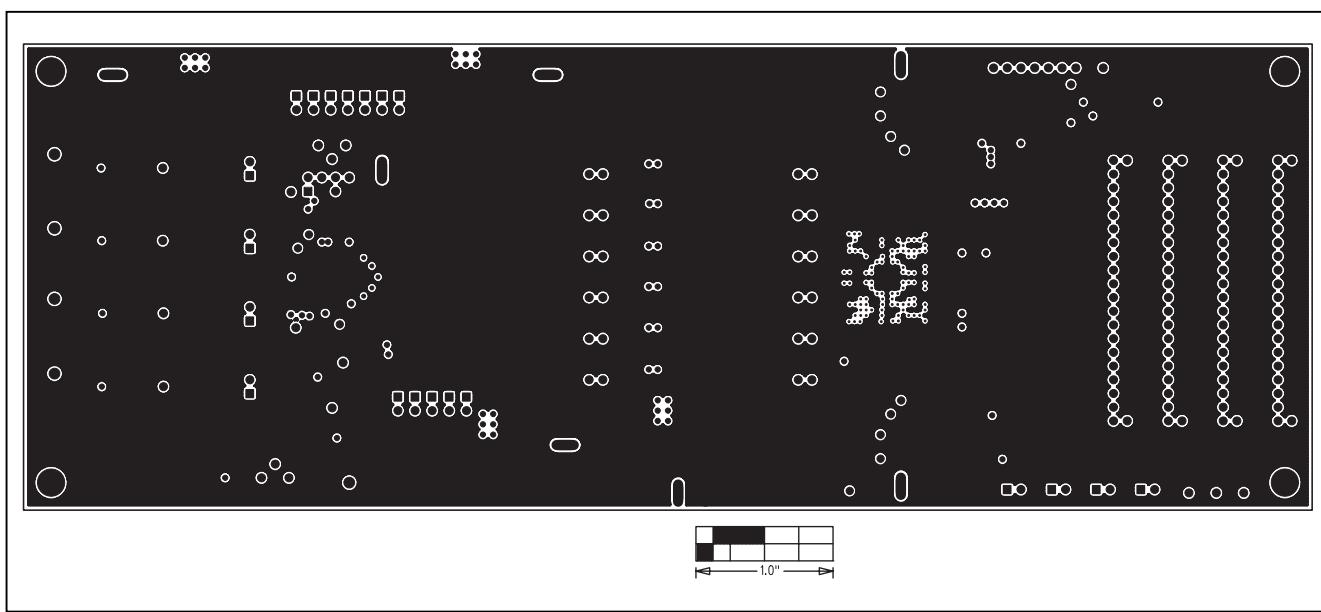

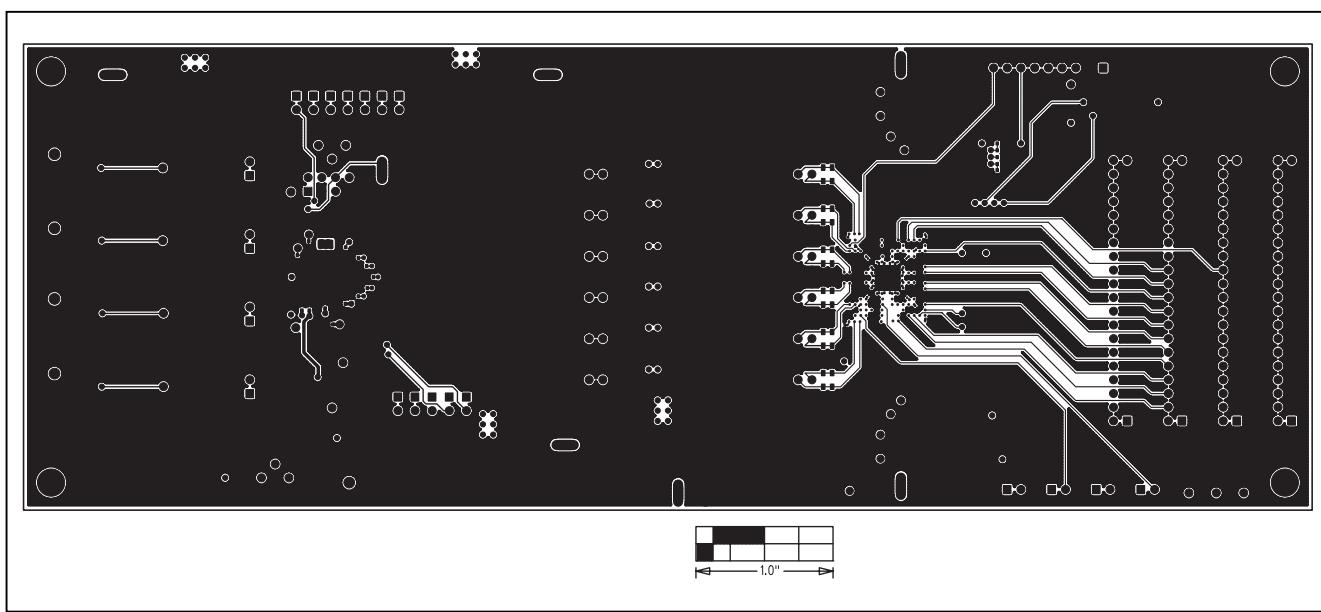

図4. MAX1127のEVキットプリント基板レイアウト(内層2)-グランドプレーン

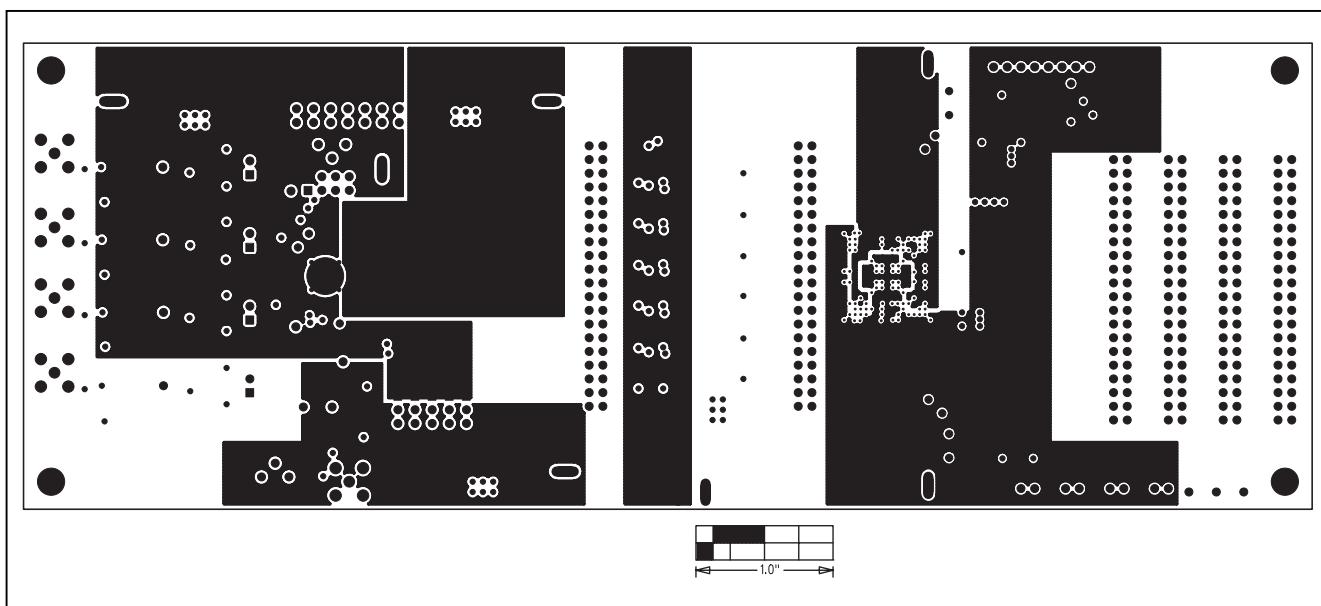

図5. MAX1127のEVキットプリント基板レイアウト(内層3)-電源プレーン

## MAX1127の評価キット

図6. MAX1127のEVキットプリント基板レイアウト(内層4)-信号層

図7. MAX1127のEVキットプリント基板レイアウト(内層5)-信号層

図8. MAX1127のEVキットプリント基板レイアウト-半田面

図9. MAX1127のEVキット部品配置ガイド-半田面

**マキシム・ジャパン株式会社**

〒169-0051 東京都新宿区西早稲田3-30-16(ホリゾン1ビル)

TEL. (03)3232-6141 FAX. (03)3232-6149

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。マキシムは隨時予告なく回路及び仕様を変更する権利を留保します。

**Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600**

15

© 2004 Maxim Integrated Products, Inc. All rights reserved. **MAXIM** is a registered trademark of Maxim Integrated Products, Inc.