## 降圧コンバーター対応の ゲート・ドライバ内蔵4フェーズDC/DCエクスパンダ

### 特長

- 1つのチップあたり最大4フェーズまで拡張可能

- 入力/出力電圧: 最大80V

- 複数のチップをカスケード接続して大電流アプリケーションに対応

- 20°~180°の範囲の最大18の異なるフェーズをサポート

- 各フェーズは位相角を共有可能

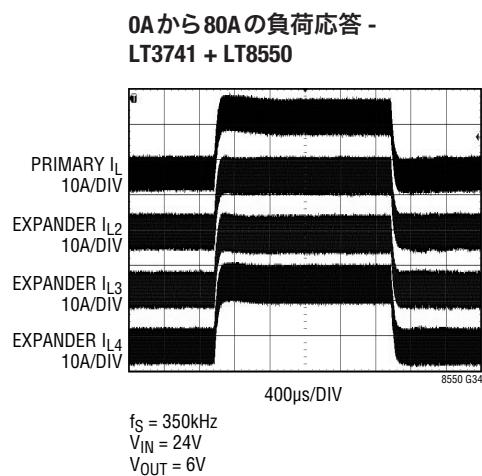

- 優れたDCおよび過渡電流分担

- 位相同期可能な固定周波数: 125kHz~1MHz

- 双方向電流をサポート

- RSENSEまたはDCRによる電流検出

- ノイズにセンシティブな帰還信号と制御信号の配線は不要

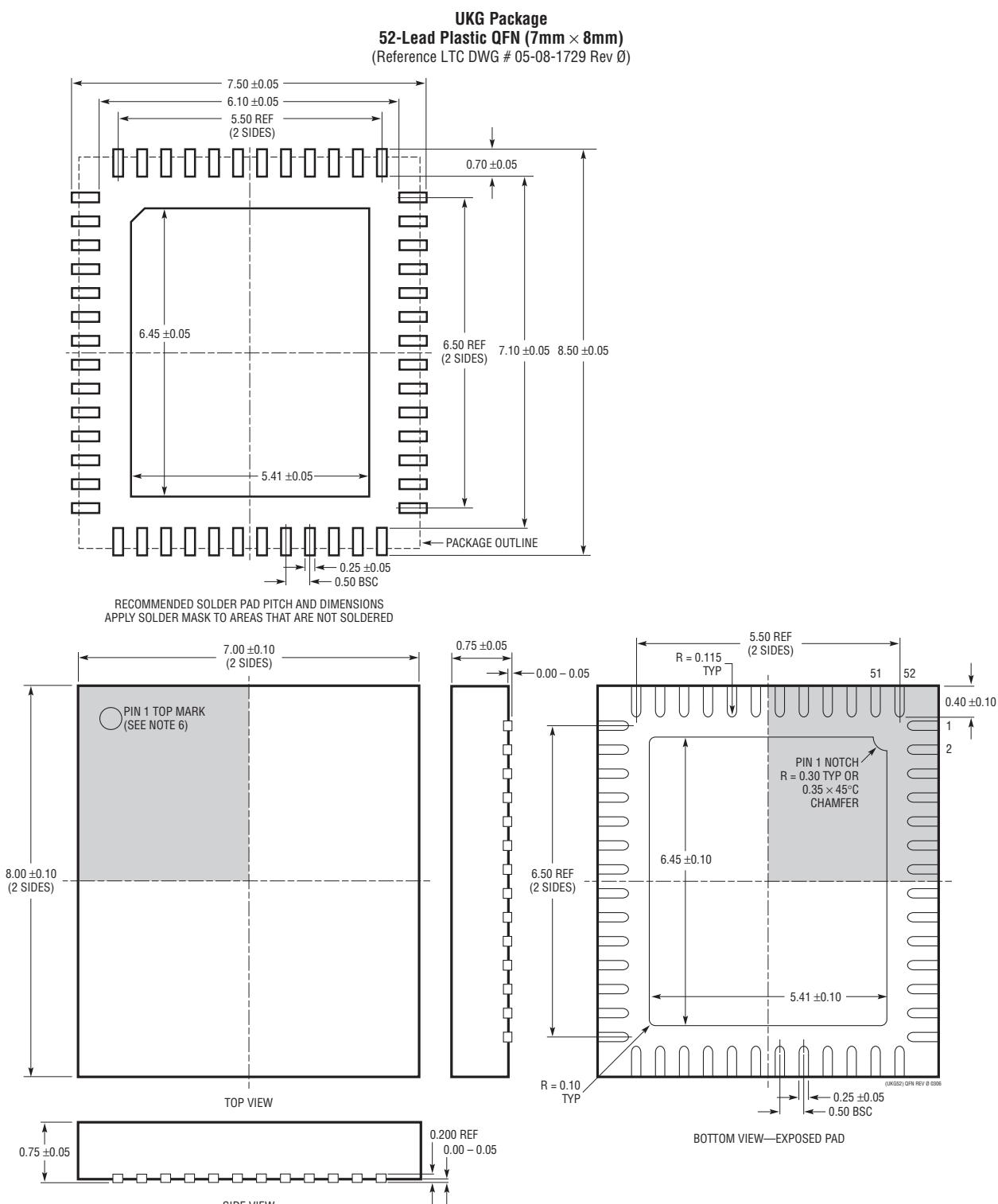

- 52ピン(7mm × 8mm) QFNパッケージ

### アプリケーション

- 大電流の分散給電システム

- 通信システム、データ通信システム、およびストレージ・システム

- 産業用および自動車用機器

### 概要

LT<sup>®</sup>8550は、同期整流式降圧DC/DCコンバータ用のマルチフェーズ・エクスパンダです。このデバイスは任意の降圧DC/DCコンバータと連携して動作し、フェーズを追加することによって負荷電流の供給能力を増強します。各フェーズの位相をずらしてクロッキングして、リップル電流とフィルタリング容量を低減します。簡単にフェーズを追加することができ、ノイズにセンシティブな帰還信号と制御信号を配線する必要はありません。

LT8550はゲート・ドライバを内蔵しており、1デバイスあたり最大4相の降圧フェーズをサポートします。複数のLT8550を使用して、最大18フェーズを提供できます。各チャンネルの電流を正確に監視および調整し、優れたDCおよび過渡電流分担を実現します。

LT8550は100kHz~1MHzの範囲の固定スイッチング周波数で動作しますが、外部クロックに同期させることもできます。

全ての登録商標および商標の所有権は、それぞれの所有者に帰属します。9077244を含む米国特許によって保護されています。

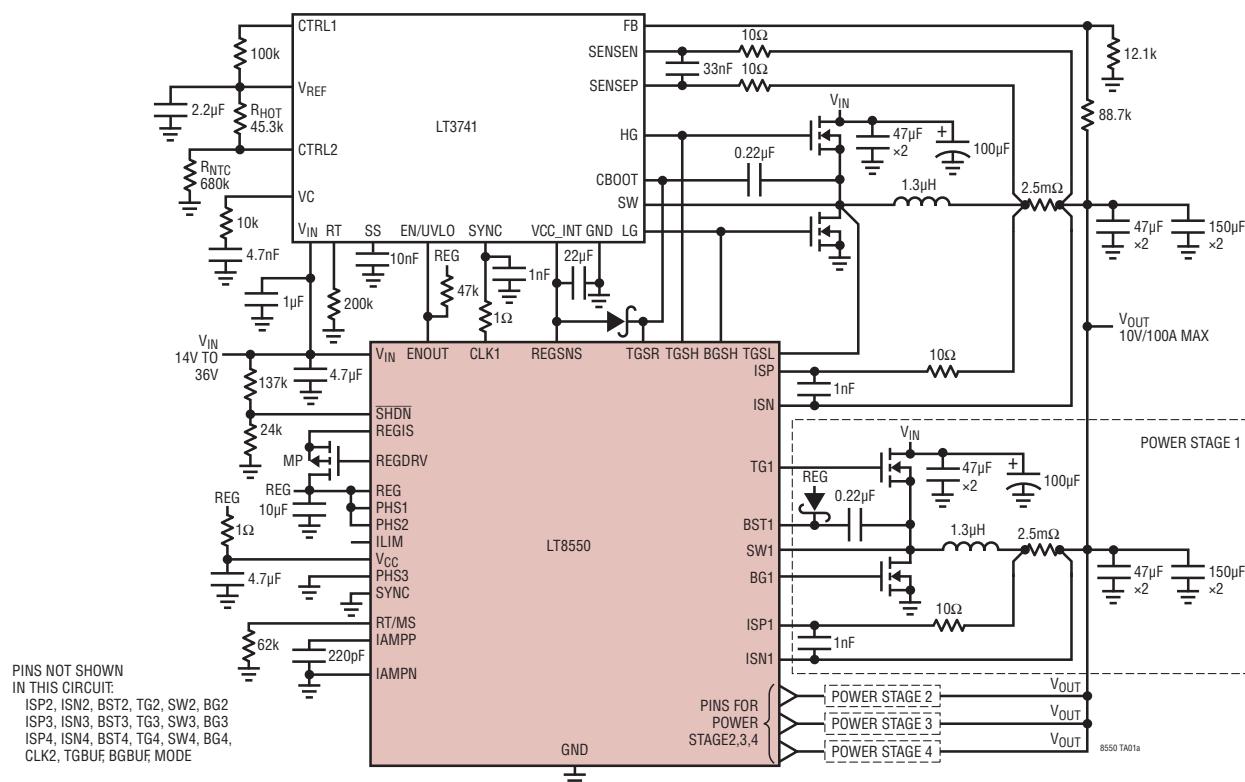

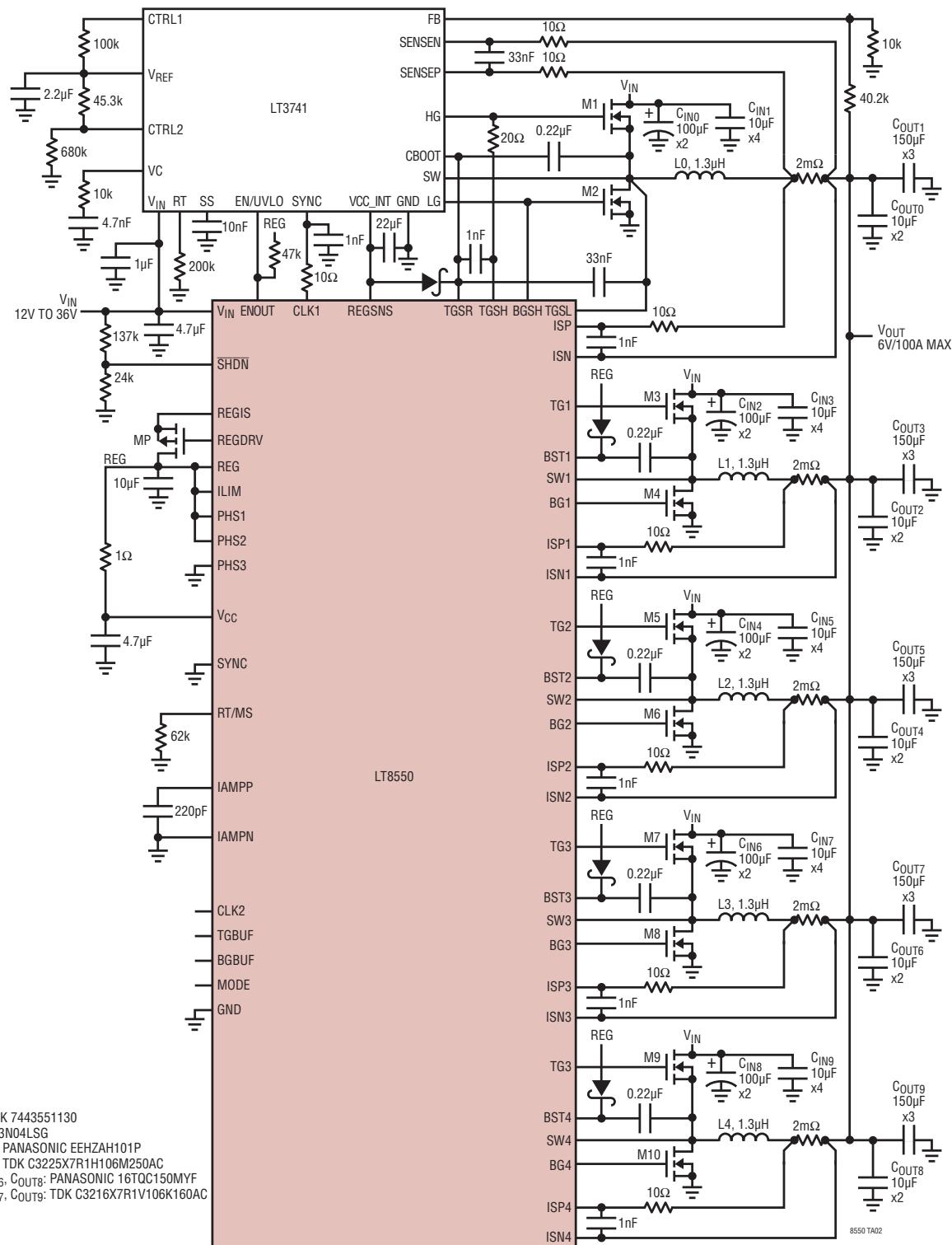

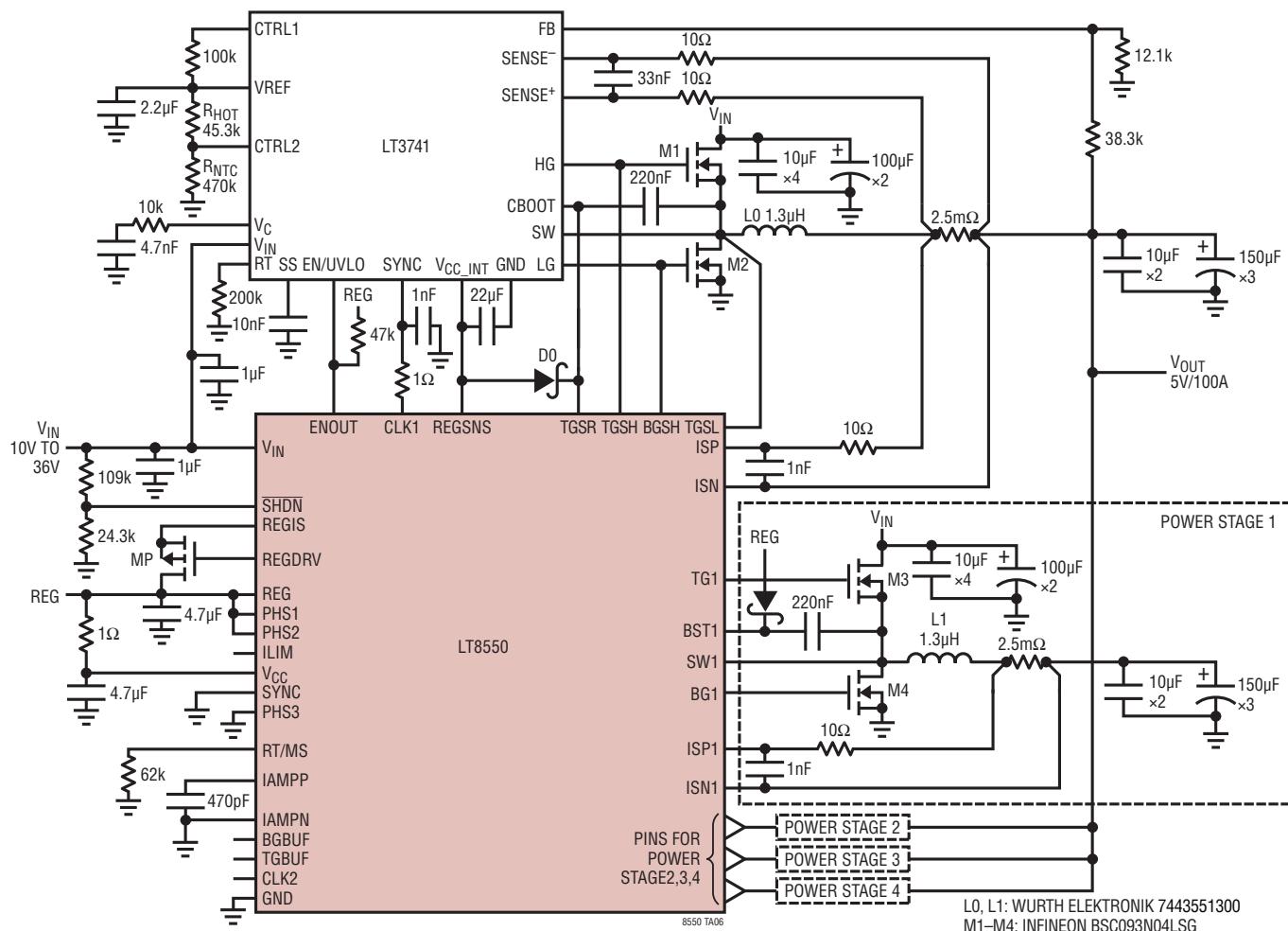

### 標準的応用例

10V/100A 降圧位相エクスパンダ・システム

## 絶対最大定格

### (Note 1)

|                                                 |              |

|-------------------------------------------------|--------------|

| SW1/2/3/4.....                                  | 80V (Note 5) |

| ISP1/2/3/4、ISN1/2/3/4、ISP、ISN、                  |              |

| V <sub>IN</sub> 、REGIS、REGDRVの電圧 (Note 2) ..... | -0.3V～80V    |

| SHDNの電圧.....                                    | -0.3V～70V    |

| TGSLの電圧.....                                    | -3V～80V      |

| TGSHの電圧.....                                    | -3V～86V      |

| TG1/2/3/4、BST1/2/3/4、TGSRの電圧.....               | -0.3V～86V    |

| BG1/2/3/4、RT/MS、SYNC、PHS1/2/3、                  |              |

| CLK1/2、REGSNS、IAMPP、ILIM、BGSH、                  |              |

| BGBUF、TGBUF、ENOUT、MODE、V <sub>CC</sub> 、        |              |

| REG、(BST-SW) 1/2/3/4、(TG-SW) 1/2/3/4、           |              |

| (V <sub>IN</sub> -REGDRV)、(TGSR-TGSL)、          |              |

| (TGSH-TGSL)の電圧.....                             | -0.3V～6.0V   |

| IAMPNの電圧.....                                   | -0.6V～0.6V   |

| (ISP-ISN) 1/2/3/4、(ISP-ISN)の電圧.....             | -0.3V～0.3V   |

| 動作ジャンクション温度範囲 (Note 3)                          |              |

| LT8550E.....                                    | -40°C～125°C  |

| LT8550I.....                                    | -40°C～125°C  |

| 保存温度範囲.....                                     | -65°C～150°C  |

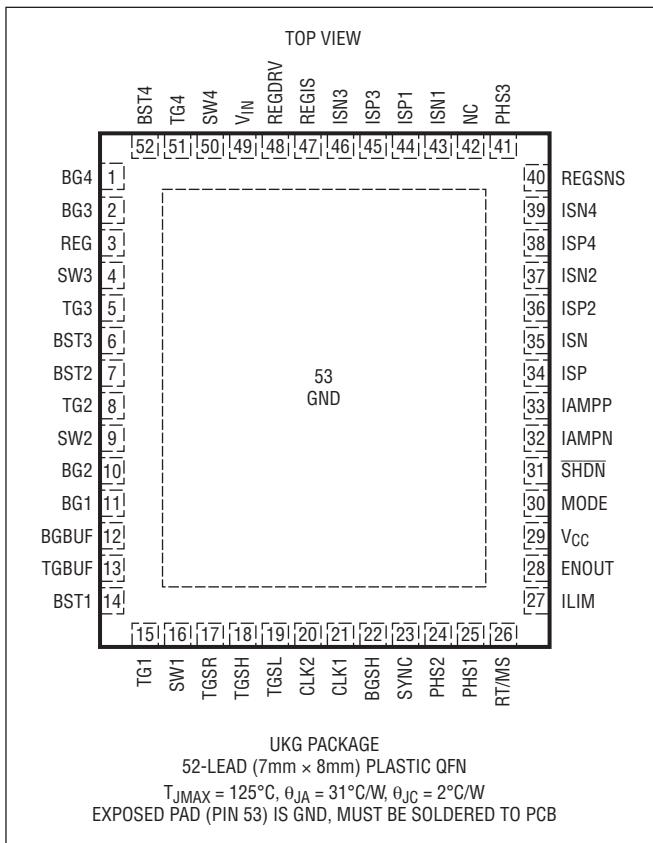

## ピン配置

## 発注情報

| 鉛フリー仕上げ        | テープ&リール          | 製品マーキング* | パッケージ                          | 温度範囲           |

|----------------|------------------|----------|--------------------------------|----------------|

| LT8550EUKG#PBF | LT8550EUKG#TRPBF | 8550     | 52-PIN (7mm x 8mm) Plastic QFN | -40°C to 125°C |

| LT8550IUKG#PBF | LT8550IUKG#TRPBF | 8550     | 52-PIN (7mm x 8mm) Plastic QFN | -40°C to 125°C |

更に広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\*温度グレードは出荷時のコンテナのラベルで識別されます。

**テープ&リールの仕様。**一部のパッケージは、#TRMPBF接尾部の付いた指定の販売経路を通じて500個入りのリールで供給可能です。

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{IN} = 12\text{V}$ 、 $\text{REG} = 5\text{V}$ 、 $V_{CC} = 5\text{V}$ 、 $\text{SHDN} = \text{'H'}$ 。

| PARAMETER                                   | CONDITIONS                                                                              | MIN | TYP      | MAX     | UNITS         |   |

|---------------------------------------------|-----------------------------------------------------------------------------------------|-----|----------|---------|---------------|---|

| $V_{IN}$ Operating Voltage Range            | For Min Spec $V_{CC}$ , $\text{REG} = 0\text{V}$                                        | ●   | 3.6      | 80      | V             |   |

| $V_{IN}$ Quiescent Current                  | $\text{REG} = V_{CC} = 5\text{V}$ , $\text{REGDRV REGIS Floating}$                      |     | 800      |         | $\mu\text{A}$ |   |

| $V_{IN}$ Quiescent Current in Shutdown      |                                                                                         |     | 2        |         | $\mu\text{A}$ |   |

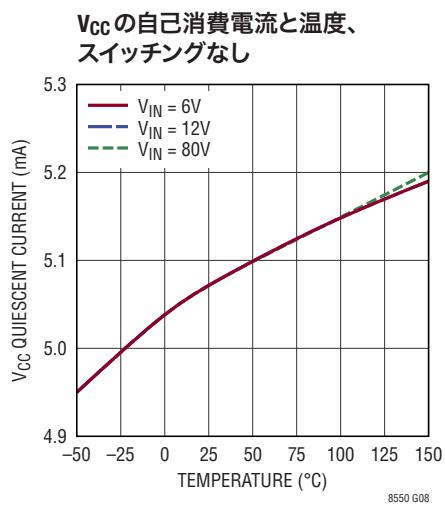

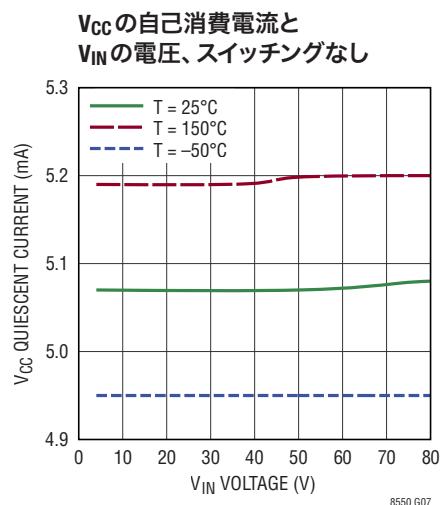

| $V_{CC}$ Quiescent Current                  | Not Switching                                                                           |     | 5        |         | mA            |   |

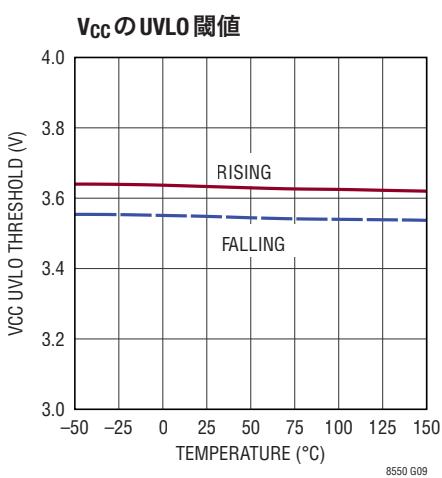

| $V_{CC}$ Undervoltage Lockout               | $V_{CC}$ Falling, $\text{REG} = V_{CC}$                                                 | ●   | 3.3      | 3.55    | 3.8           | V |

| $V_{CC}$ Undervoltage Lockout Hysteresis    | $\text{REG} = V_{CC}$                                                                   |     | 0.1      |         | V             |   |

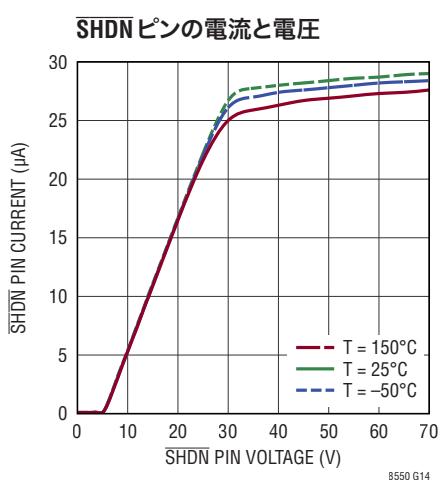

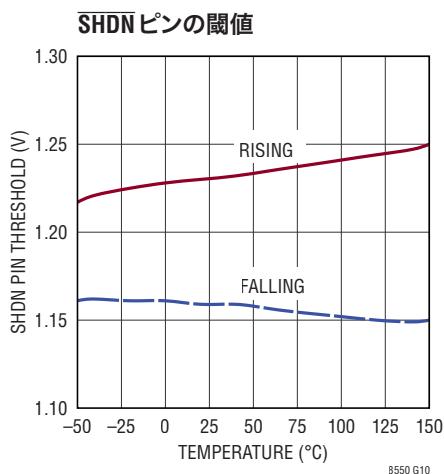

| $\text{SHDN}$ Input Voltage High            | $\text{SHDN}$ Falling                                                                   | ●   | 1.05     | 1.15    | 1.25          | V |

| $\text{SHDN}$ Input Voltage High Hysteresis |                                                                                         |     | 60       |         | mV            |   |

| $\text{SHDN}$ Input Voltage Low             | Device Disabled, Low Quiescent Current, $V_{CC} = 3\text{V}$ , $\text{REG} = 3\text{V}$ | ●   |          | 0.3     | V             |   |

| $\text{SHDN}$ Pin Bias Current              | $V_{SHDN} = 3\text{V}$<br>$V_{SHDN} = 12\text{V}$                                       |     | 0<br>8.5 | 1<br>20 | $\mu\text{A}$ |   |

| MODE Low Falling Threshold                  | Slave LT8550                                                                            | ●   | 0.5      |         | V             |   |

| MODE High Rising Threshold                  | Slave LT8550                                                                            | ●   |          | 4.5     | V             |   |

| MODE Output Voltage Low                     | Master LT8550, 200 $\mu\text{A}$ into MODE Pin                                          |     | 50       |         | mV            |   |

| MODE Output Voltage High                    | Master LT8550, 20 $\mu\text{A}$ Out of MODE Pin                                         |     | 4.8      |         | V             |   |

| MODE Pin Impedance in Middle State          | Master LT8550                                                                           |     | 9        |         | k $\Omega$    |   |

| ENOUT Output Voltage Low                    | Master LT8550, 1mA into ENOUT Pin, $V_{CC}$ , $\text{REG}$ in UVLO                      |     | 60       |         | mV            |   |

| ENOUT Leakage Current                       | $\text{ENOUT} = 5\text{V}$ , $\text{REG}$ , $V_{CC} = 3\text{V}$                        |     | 0.2      | 1       | $\mu\text{A}$ |   |

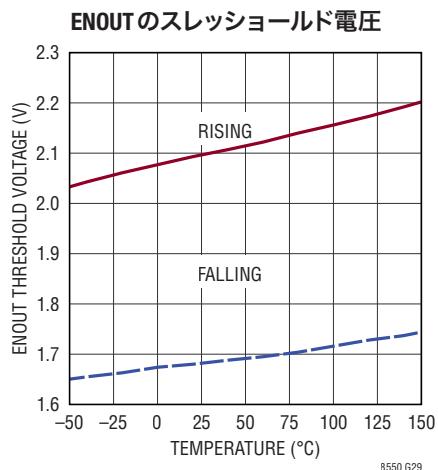

| ENOUT Rising Threshold                      |                                                                                         |     | 2.1      |         | V             |   |

| ENOUT Threshold Hysteresis                  |                                                                                         |     | 0.4      |         | V             |   |

### 電流検出

|                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           |                                                                      |                                                                      |                                                                      |            |   |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|------------|---|

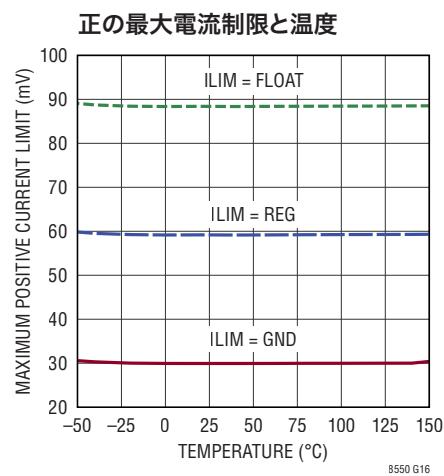

| Maximum Positive Current Sense Voltage, (ISPn-ISNn) | ILIM = 0V, ISNn = 12V, ISPn Rising<br>ILIM = REG, ISNn = 12V, ISPn Rising<br>ILIM = Float, ISNn = 12V, ISPn Rising                                                                                                                                                                                                                                                                                                                                                                                                                        | ●<br>●<br>●                               | 27<br>56<br>84.5                                                     | 30<br>60<br>90                                                       | 32.5<br>64<br>95.5                                                   | mV         |   |

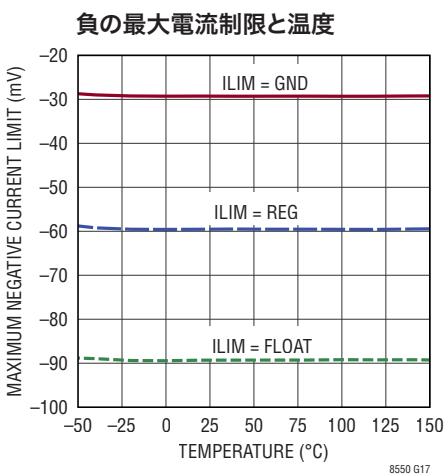

| Maximum Negative Current Sense Voltage, (ISNn-ISPn) | ILIM = 0V, ISNn = 12V, ISPn Falling<br>ILIM = REG, ISNn = 12V, ISPn Falling<br>ILIM = Float, ISNn = 12V, ISPn Falling                                                                                                                                                                                                                                                                                                                                                                                                                     | ●<br>●<br>●                               | 26.5<br>55.5<br>84                                                   | 30<br>60<br>90                                                       | 33<br>64.5<br>96                                                     | mV         |   |

| ISP, ISN Common Mode Operating Voltage Range        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ●                                         | 0                                                                    | 80                                                                   |                                                                      | V          |   |

| ISPn, ISNn Common Mode Operating Voltage Range      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ●                                         | 0                                                                    | 80                                                                   |                                                                      | V          |   |

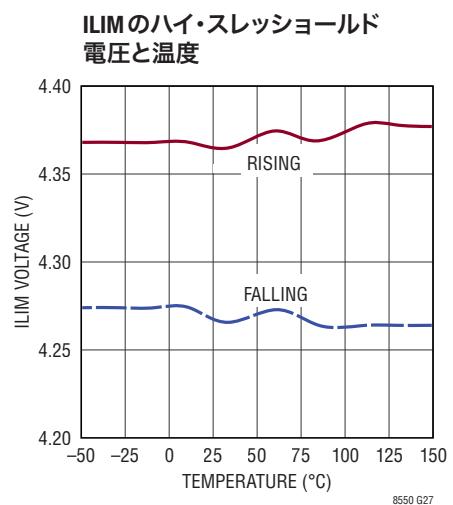

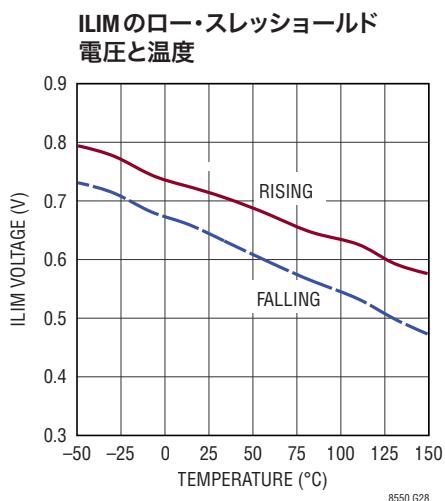

| ILIM High Rising Threshold                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ●                                         |                                                                      | 4.65                                                                 |                                                                      | V          |   |

| ILIM High Threshold Hysteresis                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           |                                                                      | 90                                                                   |                                                                      | mV         |   |

| ILIM Low Falling Threshold                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ●                                         | 0.3                                                                  |                                                                      |                                                                      | V          |   |

| ILIM Low Threshold Hysteresis                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           |                                                                      | 80                                                                   |                                                                      | mV         |   |

| ILIM Impedance at Floating                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           |                                                                      | 11                                                                   |                                                                      | k $\Omega$ |   |

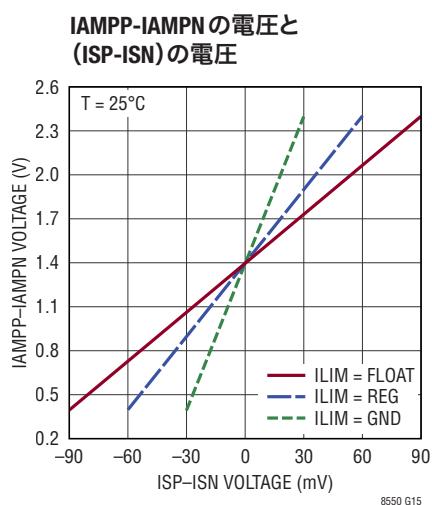

| IAMPP Output Voltage                                | (ISP-ISN) = 30mV, ILIM = 0V, Master LT8550, ISN = 12V<br>(ISP-ISN) = 0mV, ILIM = 0V, Master LT8550, ISN = 12V<br>(ISP-ISN) = -30mV, ILIM = 0V, Master LT8550, ISN = 12V<br>(ISP-ISN) = 60mV, ILIM = REG, Master LT8550, ISN = 12V<br>(ISP-ISN) = 0mV, ILIM = REG, Master LT8550, ISN = 12V<br>(ISP-ISN) = -60mV, ILIM = REG, Master LT8550, ISN = 12V<br>(ISP-ISN) = 90mV, ILIM = Float, Master LT8550, ISN = 12V<br>(ISP-ISN) = 0mV, ILIM = Float, Master LT8550, ISN = 12V<br>(ISP-ISN) = -90mV, ILIM = Float, Master LT8550, ISN = 12V | ●<br>●<br>●<br>●<br>●<br>●<br>●<br>●<br>● | 2.33<br>1.33<br>0.33<br>2.33<br>1.35<br>0.34<br>2.33<br>1.35<br>0.34 | 2.40<br>1.40<br>0.40<br>2.40<br>1.40<br>0.40<br>2.40<br>1.40<br>0.40 | 2.47<br>1.47<br>0.47<br>2.47<br>1.45<br>0.46<br>2.47<br>1.45<br>0.46 |            | V |

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{IN} = 12\text{V}$ 、 $\text{REG} = 5\text{V}$ 、 $V_{CC} = 5\text{V}$ 、 $\text{SHDN} = \text{H}_1$ 。

| PARAMETER                                                                | CONDITIONS                                                                                                                                                                                                                                                                                                                   |                            | MIN                                                 | TYP                                                 | MAX                                                 | UNITS |

|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|-------|

| (ISPn-ISNn) Voltage In Regulation                                        | IAMPP = 2.20V, IAMPN = 0V, ILIM = 0V, ISNn = 12V<br>IAMPP = 0.60V, IAMPN = 0V, ILIM = 0V, ISNn = 12V<br>IAMPP = 2.20V, IAMPN = 0V, ILIM = REG, ISNn = 12V<br>IAMPP = 0.60V, IAMPN = 0V, ILIM = REG, ISNn = 12V<br>IAMPP = 2.20V, IAMPN = 0V, ILIM = Float, ISNn = 12V<br>IAMPP = 0.60V, IAMPN = 0V, ILIM = Float, ISNn = 12V | ●<br>●<br>●<br>●<br>●<br>● | 21.25<br>-26.75<br>45.0<br>-51.0<br>67.25<br>-76.75 | 26.75<br>-21.25<br>51.0<br>-45.0<br>76.75<br>-67.25 | 26.75<br>-21.25<br>51.0<br>-45.0<br>76.75<br>-67.25 | mV    |

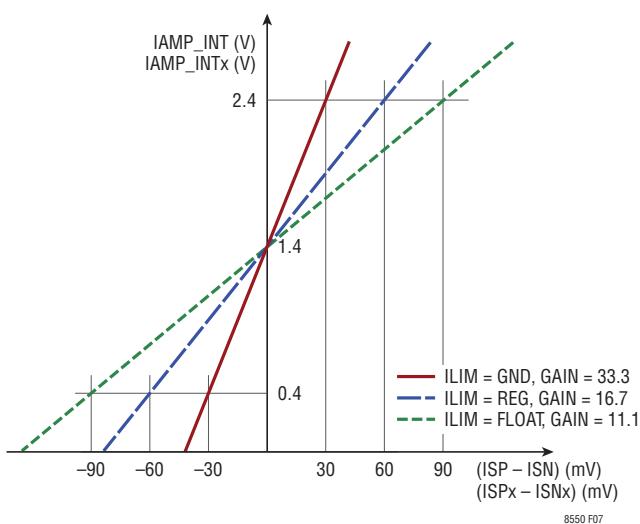

| (ISP-ISN) to IAMPP Voltage Gain                                          | ILIM = 0V, Master LT8550, ISN = 0V<br>ILIM = REG, Master LT8550, ISN = 0V<br>ILIM = FLOAT, Master LT8550, ISN = 0V                                                                                                                                                                                                           |                            |                                                     | 33.3<br>16.7<br>11.1                                |                                                     |       |

| IAMPP Sourcing Current Limit                                             | (ISP-ISN) = 0mV, Master LT8550                                                                                                                                                                                                                                                                                               | ●                          | 250                                                 |                                                     |                                                     | μA    |

| IAMPP Sinking Current Limit                                              | (ISP-ISN) = 0mV, Master LT8550                                                                                                                                                                                                                                                                                               | ●                          | 60                                                  |                                                     |                                                     | μA    |

| IAMPP Load Regulation                                                    | $I_{LOAD} = -200\mu\text{A}$ to $50\mu\text{A}$ , Master LT8550                                                                                                                                                                                                                                                              |                            |                                                     | 1                                                   |                                                     | mV    |

| IAMPP Pin Bias Current                                                   | IAMPP = 1.2V, Slave LT8550<br>IAMPP = 2.4V, Slave LT8550                                                                                                                                                                                                                                                                     |                            |                                                     | 3<br>6                                              |                                                     | μA    |

| Mismatch Between (ISPn-ISNn) and Master LT8550's (ISP-ISN) in Regulation | ILIM = REG                                                                                                                                                                                                                                                                                                                   | ●                          | -6<br>-4.75                                         | 6<br>4.75                                           |                                                     | %     |

| Mismatch Between (ISPn-ISNn) and Master LT8550's (ISP-ISN) in Regulation | ILIM = FLOAT                                                                                                                                                                                                                                                                                                                 | ●                          | -6<br>-5.5                                          | 6<br>5.5                                            |                                                     | %     |

| Mismatch Between (ISPn-ISNn) and Master LT8550's (ISP-ISN) in Regulation | ILIM = 0V                                                                                                                                                                                                                                                                                                                    | ●                          | -10<br>-8                                           | 10<br>8                                             |                                                     | %     |

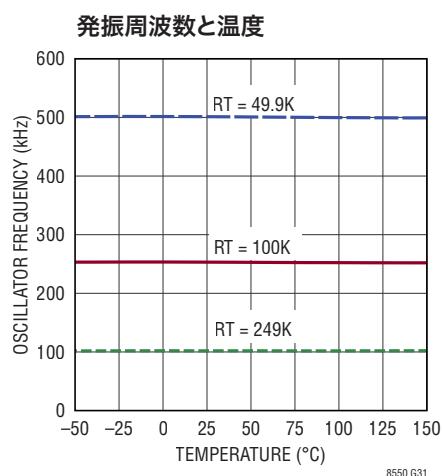

| <b>発振器</b>                                                               |                                                                                                                                                                                                                                                                                                                              |                            |                                                     |                                                     |                                                     |       |

| CLK1 Frequency                                                           | RT/MS = $24.3\text{k}\Omega$ , Master LT8550<br>RT/MS = $100\text{k}\Omega$ , Master LT8550<br>RT/MS = $249\text{k}\Omega$ , Master LT8550                                                                                                                                                                                   | ●<br>●<br>●                | 900<br>236<br>90                                    | 1000<br>250<br>100                                  | 1100<br>264<br>110                                  | kHz   |

| Switching Frequency Range                                                | Free-Running<br>Synchronizing                                                                                                                                                                                                                                                                                                | ●<br>●                     | 100<br>125                                          | 1000<br>1000                                        |                                                     | kHz   |

| SYNC High Level for Synchronization                                      |                                                                                                                                                                                                                                                                                                                              | ●                          | 1.2                                                 |                                                     |                                                     | V     |

| SYNC Low Level for Synchronization                                       |                                                                                                                                                                                                                                                                                                                              | ●                          |                                                     | 0.8                                                 |                                                     | V     |

| CLK1, CLK2 Rise Time                                                     | $C_{LOAD} = 220\text{pF}$ , Master LT8550 (Note 4)                                                                                                                                                                                                                                                                           |                            |                                                     | 7                                                   |                                                     | ns    |

| CLK1, CLK2 Fall Time                                                     | $C_{LOAD} = 220\text{pF}$ , Master LT8550 (Note 4)                                                                                                                                                                                                                                                                           |                            |                                                     | 5                                                   |                                                     | ns    |

| CLK2 Rising Threshold                                                    | Slave LT8550                                                                                                                                                                                                                                                                                                                 | ●                          |                                                     | 4.0                                                 |                                                     | V     |

| CLK2 Falling Threshold                                                   | Slave LT8550                                                                                                                                                                                                                                                                                                                 | ●                          | 1.0                                                 |                                                     |                                                     | V     |

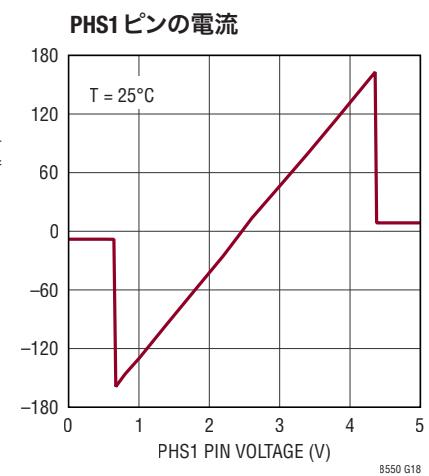

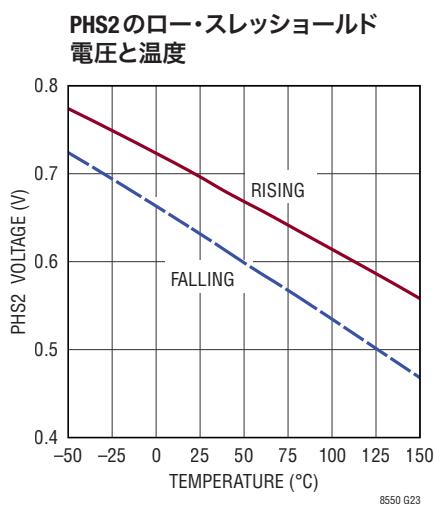

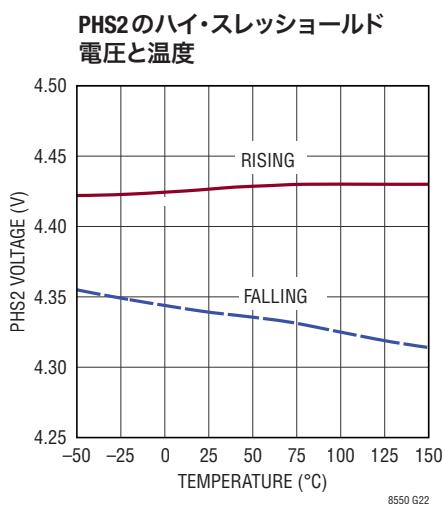

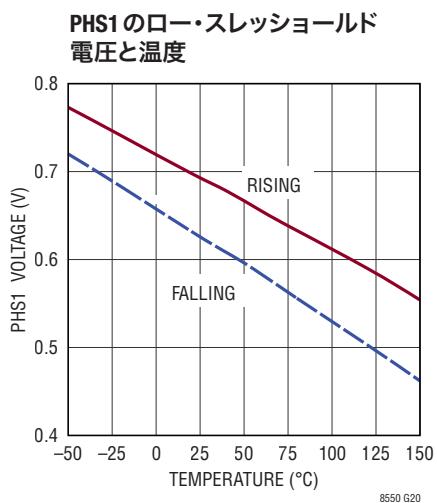

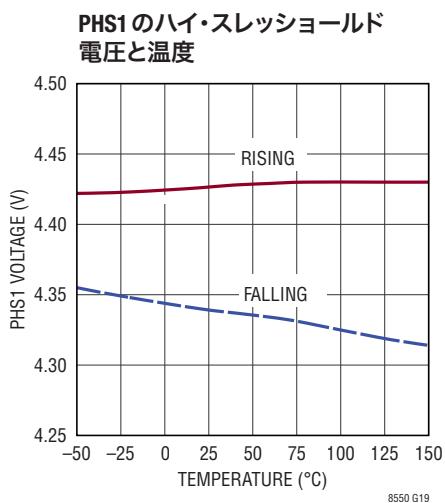

| PHS1, PHS2 High Rising Threshold                                         |                                                                                                                                                                                                                                                                                                                              | ●                          |                                                     | 4.65                                                |                                                     | V     |

| PHS1, PHS2 High Threshold Hysteresis                                     |                                                                                                                                                                                                                                                                                                                              |                            | 80                                                  |                                                     |                                                     | mV    |

| PHS1, PHS2 Low Falling Threshold                                         |                                                                                                                                                                                                                                                                                                                              | ●                          | 0.3                                                 |                                                     |                                                     | V     |

| PHS1, PHS2 Low Threshold Hysteresis                                      |                                                                                                                                                                                                                                                                                                                              |                            | 80                                                  |                                                     |                                                     | mV    |

| PHS1, PHS2 Impedance at Floating                                         |                                                                                                                                                                                                                                                                                                                              |                            | 11                                                  |                                                     |                                                     | kΩ    |

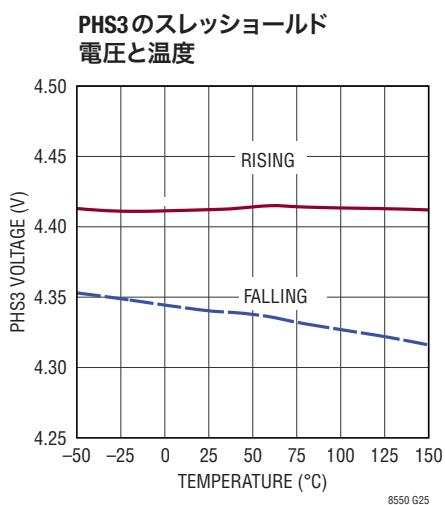

| PHS3 Rising Threshold                                                    |                                                                                                                                                                                                                                                                                                                              | ●                          |                                                     | 4.65                                                |                                                     | V     |

| PHS3 Threshold Hysteresis                                                |                                                                                                                                                                                                                                                                                                                              |                            | 80                                                  |                                                     |                                                     | mV    |

| <b>REG LDO</b>                                                           |                                                                                                                                                                                                                                                                                                                              |                            |                                                     |                                                     |                                                     |       |

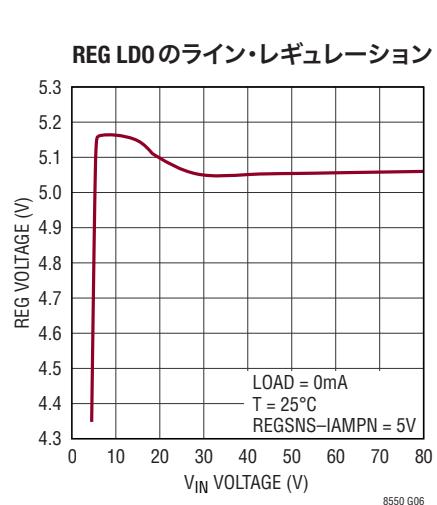

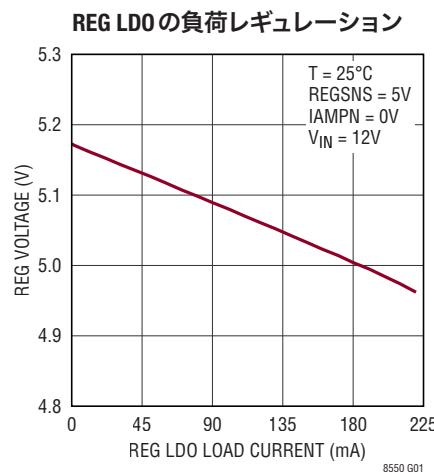

| REG Voltage                                                              | REGSNS = 5V, IAMPN = 0V, $I_{LOAD} = 45\text{mA}$                                                                                                                                                                                                                                                                            | ●                          | 4.9                                                 | 5.1                                                 | 5.3                                                 | V     |

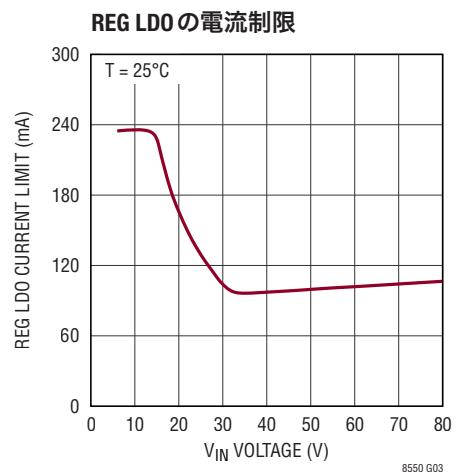

| REG LDO Current Limit                                                    | $V_{IN} = 12\text{V}$ , REGSNS = 5V, REG, $V_{CC} = 4\text{V}$<br>$V_{IN} = 24\text{V}$ , REGSNS = 5V, REG, $V_{CC} = 4\text{V}$                                                                                                                                                                                             |                            |                                                     | 250<br>145                                          |                                                     | mA    |

| REG LDO Gate Drive Clamp Voltage                                         | $(V_{IN} - \text{REGDRV})$ Voltage, REG, $V_{CC} = 4.5\text{V}$                                                                                                                                                                                                                                                              |                            |                                                     | 5.3                                                 |                                                     | V     |

| REG Load Regulation                                                      | $I_{LOAD} = 0$ to $100\text{mA}$ , REGSNS = 5V, IAMPN = 0V                                                                                                                                                                                                                                                                   |                            |                                                     | 90                                                  |                                                     | mV    |

| REGSNS Pin Bias Current                                                  | REGSNS = 5V                                                                                                                                                                                                                                                                                                                  |                            |                                                     | 12                                                  |                                                     | μA    |

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{IN} = 12\text{V}$ 、 $\text{REG} = 5\text{V}$ 、 $V_{CC} = 5\text{V}$ 、 $\overline{\text{SHDN}} = \text{'H'}$ 。

| PARAMETER                          | CONDITIONS                                                                                                                 | MIN | TYP      | MAX | UNITS |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----|----------|-----|-------|

| <b>ゲート・ドライバ</b>                    |                                                                                                                            |     |          |     |       |

| TG1, TG2, TG3, TG4 Rise Time       | $C_{LOAD} = 3.3\text{nF}$ , $SWx = 0\text{V}$ , $BSTx = 5\text{V}$ (Note 4)                                                |     | 30       |     | ns    |

| TG1, TG2, TG3, TG4 Fall Time       | $C_{LOAD} = 3.3\text{nF}$ , $SWx = 0\text{V}$ , $BSTx = 5\text{V}$ (Note 4)                                                |     | 20       |     | ns    |

| BG1, BG2, BG3, BG4 Rise Time       | $C_{LOAD} = 3.3\text{nF}$ (Note 4)                                                                                         |     | 50       |     | ns    |

| BG1, BG2, BG3, BG4 Fall Time       | $C_{LOAD} = 3.3\text{nF}$ (Note 4)                                                                                         |     | 27       |     | ns    |

| Bottom & Top Gate Non-Overlap Time | TG Falling to BG Rising, $C_{LOAD} = 3.3\text{nF}$ (Note 4)<br>BG Falling to TG Rising, $C_{LOAD} = 3.3\text{nF}$ (Note 4) |     | 85<br>80 |     | ns    |

| Bottom & Top Gate Minimum Off-Time | $C_{LOAD} = 3.3\text{nF}$ (Note 4)                                                                                         |     | 140      |     | ns    |

| <b>プライマリ・ゲート・センシング</b>             |                                                                                                                            |     |          |     |       |

| BGSH Rising Threshold              |                                                                                                                            | ●   | 4.0      |     | V     |

| BGSH Falling Threshold             |                                                                                                                            | ●   | 1.0      |     | V     |

| BGSH Threshold Hysteresis          |                                                                                                                            |     | 1.4      |     | V     |

| BGSH to BGBUF Delay                | $C_{LOAD} = 220\text{pF}$ , Master LT8550 (Note 4)                                                                         |     | 45       |     | ns    |

| BGBUF Rise Time                    | $C_{LOAD} = 220\text{pF}$ , Master LT8550 (Note 4)                                                                         |     | 8        |     | ns    |

| BGBUF Fall Time                    | $C_{LOAD} = 220\text{pF}$ , Master LT8550 (Note 4)                                                                         |     | 6        |     | ns    |

| TGSH Rising Threshold              | TGSR = 5V, TGSL = 0V                                                                                                       | ●   | 4.0      |     | V     |

| TGSH Falling Threshold             | TGSR = 5V, TGSL = 0V                                                                                                       | ●   | 1.0      |     | V     |

| TGSH Threshold Hysteresis          |                                                                                                                            |     | 1.4      |     | V     |

| TGSH to TGBUF Delay                | $C_{LOAD} = 220\text{pF}$ , Master LT8550 (Note 4)                                                                         |     | 45       |     | ns    |

| TGBUF Rise Time                    | $C_{LOAD} = 220\text{pF}$ , Master LT8550 (Note 4)                                                                         |     | 8        |     | ns    |

| TGBUF Fall Time                    | $C_{LOAD} = 220\text{pF}$ , Master LT8550 (Note 4)                                                                         |     | 6        |     | ns    |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。また、長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える恐れがある。

**Note 2:** REGDRV, BG1, BG2, BG3, BG4, TG1, TG2, TG3 および TG4 ピンには正または負の電圧源または電流源を印加してはならない。印加すると、永続的な損傷が生じる場合がある。

**Note 3:** LT8550Eは、 $0^\circ\text{C}\sim125^\circ\text{C}$ の動作ジャンクション温度で性能仕様に適合することが確認されている。 $-40^\circ\text{C}\sim125^\circ\text{C}$ の動作ジャンクション温度範囲での仕様は、設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。LT8550Iは、 $-40^\circ\text{C}\sim125^\circ\text{C}$ のジャンクション温度で性能仕様に適合することが確認されている。

**Note 4:** 立上がり時間と立下り時間は10%と90%のレベルを使用して測定されている。遅延時間は50%レベルを使用して測定されている。

**Note 5:** SW1/2/3/4ピンの負電圧は、アプリケーションでは外付けNMOSデバイスのボディ・ダイオードまたは並列ショットキー・ダイオード(存在する場合)によって制限される。SW1/2/3/4ピンは、グラウンドからダイオードの電圧降下分を超えたこれらの負電圧に耐性を持つことが設計により確認されている。

## 代表的な性能特性

特に指定がない限り、 $T_A = 25^\circ\text{C}$ 。

## 代表的な性能特性

特に指定がない限り、 $T_A = 25^\circ\text{C}$ 。

## 代表的な性能特性

特に指定がない限り、 $T_A = 25^\circ\text{C}$ 。

## 代表的な性能特性

特に指定がない限り、 $T_A = 25^\circ\text{C}$ 。

## ピン機能 (QFN)

**REG(ピン3)**: REG LDOの出力。ゲート・ドライバの電源。このピンは、4.7 $\mu$ F以上の低ESRセラミック・コンデンサを使用してグラウンドにデカップリングします。このピンは外部PMOSのドレイン側に接続します。

**BG1、BG2、BG3、BG4(ピン11、10、2、1)**: 下側のゲート・ドライバ出力。これらのピンは、下側NチャンネルMOSFETのゲートを駆動します。これらのピンの電圧振幅はグラウンドからREGまでです。

**BGBUF(ピン12)**: ロジック出力ピン。このピンは、BGSFがロジック・ハイのときはREGに引上げられ、BGSFがロジック・ローのときはグラウンドに引き下げられます。スレーブLT8550では、このピンはフロート状態のままにしておきます。詳細については、アプリケーション情報のセクションを参照してください。

**TGBUF(ピン13)**: ロジック出力ピン。マスタLT8550では、このピンは、(TGSF-TGSL)がロジック・ハイのときはREGの電圧に引上げられ、(TGSF-TGSL)がロジック・ローのときはグラウンドに引き下げられます。スレーブLT8550では、このピンはフロート状態のままにしておきます。詳細については、アプリケーション情報のセクションを参照してください。

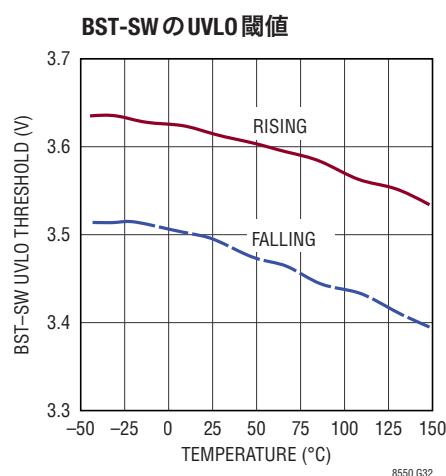

**BST1、BST2、BST3、BST4(ピン14、7、6、52)**: フロート・ドライバの昇圧電源。ブートストラップ・コンデンサの(+)端子をこのピンに接続します。このピンは、REGよりもダイオードの電圧降下分だけ低い電圧からVIN + REGまで振幅します。

**TG1、TG2、TG3、TG4(ピン15、8、5、51)**: 上側のゲート・ドライバ出力。このピンは、スイッチ・ノード電圧にREGを重畠した電圧に等しい電圧振幅を持つフローティング・ドライバ出力です。

**SW1、SW2、SW3、SW4(ピン16、9、4、50)**: スイッチ・ノード。これらのピンの電圧振幅は、グラウンドよりダイオードの電圧降下分だけ低い電圧からVINまでです。

**TGSR(ピン17)**: プライマリ・チャンネルの上側ゲート検出回路のレール。マスタLT8550では、このピンはプライマリ・チャンネルの上側ゲート・ドライバの昇圧ノードに接続します。このピンとTGSFピン、TGSLピンを組み合わせて、プライマリ・チャンネルの上側MOSFETの状態を検出します。スレーブLT8550では、このピンはREGに接続します。

**TGSH(ピン18)**: プライマリ・チャンネルの上側ゲート検出回路の入力。マスタLT8550では、このピンはプライマリ・チャンネルの上側MOSFETのゲートに接続します。このピンと

TGSRピン、TGSLピンを組み合わせて、プライマリ・チャンネルの上側MOSFETの状態を検出します。スレーブLT8550では、このピンはマスタLT8550のTGBUFピンに接続します。

**TGSL(ピン19)**: プライマリ・チャンネルの上側ゲート検出回路の下側レール。マスタLT8550では、このピンはプライマリ・チャンネルの上側MOSFETのソースに接続します。このピンとTGSFピン、TGSHピンを組み合わせて、プライマリ・チャンネルの上側MOSFETの状態を検出します。スレーブLT8550では、このピンはグラウンドに接続します。

**CLK1、CLK2(ピン21、20)**: クロック・ピン。これらの2本のピンを使用して、プライマリ・チャンネルと他の全てのチャンネルを同期させます。詳細については、アプリケーション情報のセクションを参照してください。

**BGSF(ピン22)**: プライマリ・チャンネルの下側ゲート検出回路のロジック入力。マスタLT8550では、このピンはプライマリ・チャンネルの下側MOSFETのゲートに接続します。このピンを使用して、プライマリ・チャンネルの下側MOSFETの状態を検出します。スレーブLT8550では、このピンはマスタLT8550のBGBUFピンに接続します。

**SYNC(ピン23)**: スイッチング周波数を外部クロックに同期させるには、単にこのピンをクロックで駆動します。クロックの電圧ハイ・レベルは1.2Vを超えないければならず、電圧ロー・レベルは0.8Vより低くなければなりません。このピンを0.8V未満にすると、内部自走クロックに戻ります。代表的なアプリケーションのセクションを参照してください。

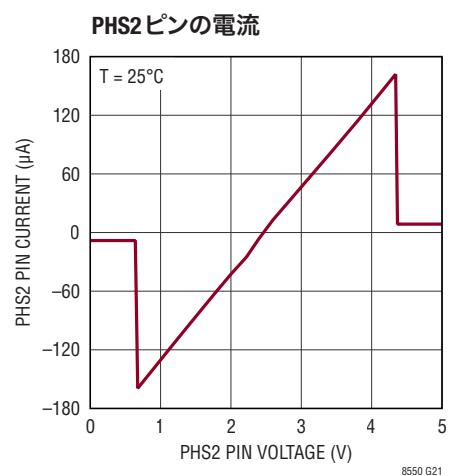

**PHS1、PHS2(ピン25、24)**: フェーズ選択ピン。これらのピンとPHS3およびRT/MSピンを組み合わせて、各チャンネルのスイッチング周波数と位相を設定します。PHS1とPHS2は3レベル入力ピンであり、フロート状態、REG、またはグラウンドに設定できます。PHS1/PHS2がフロート状態のときは、PHS1/PHS2とグラウンドの間に1nFコンデンサを追加します。詳細については、動作のセクションを参照してください。

**RT/MS(ピン26)**: タイミング抵抗ピンおよびマスタ・スレーブ選択ピン。このピンとPHS1、PHS2およびPHS3ピンを組み合わせて、各チャンネルのスイッチング周波数と位相を設定します。このピンとグラウンドの間に抵抗を接続すると、チップはマスタLT8550として設定されます。このピンをREGピンに接続すると、チップはスレーブLT8550として設定されます。詳細については、アプリケーション情報のセクションを参照してください。

## ピン機能 (QFN)

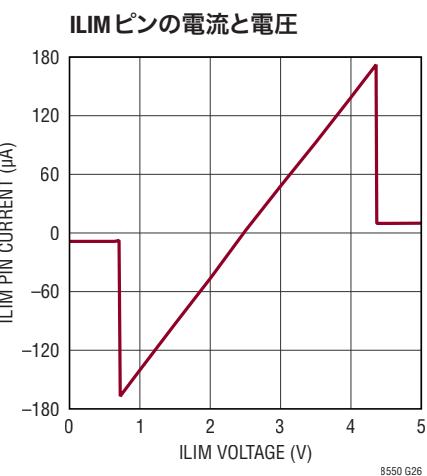

**ILIM(ピン27)**: 最大電流検出電圧プログラミング・ピン。このピンを使用して、プライマリ・チャンネルの電流検出アンプと拡張チャンネルの電流検出アンプの最大検出電圧を設定します。これは3レベル入力ピンです。このピンをグラウンドに接続するか、REGに接続するか、フロート状態のままにしておくと、最大電流検出電圧はそれぞれ30mV、60mV、90mVに設定されます。ILIMがフロート状態のときは、ILIMとグラウンドの間に1nFコンデンサを追加します。

**ENOUT(ピン28)**: マスタLT8550では、このピンはオーブンドレインのロジック出力ピンです。スレーブLT8550では、このピンは入力ピンです。詳細については、ENOUTの接続のセクションを参照してください。

**V<sub>CC</sub>(ピン29)**: 制御回路用の電源。このピンは、1μF以上の低ESRセラミック・コンデンサを使用してグラウンドにデカップリングします。V<sub>CC</sub>とREGは1Ω抵抗を介して接続する必要があります。

**MODE(ピン30)**: ステージ・シェディング選択ピン。このピンをGNDに接続すると、ステージ・シェディング機能が無効になります。詳細については、動作のセクションを参照してください。

**SHDN(ピン31)**: シャットダウン・ピン。このピンを使用して、チップをイネーブル／ディスエーブルします。チップをディスエーブルするには、0.3Vより低い電圧で駆動します。チップを起動するには、1.2V(標準)より高い電圧で駆動します。このピンはフロート状態にしないでください。

**IAMPN(ピン32)**: マスタLT8550では、このピンはローカル・グラウンドに接続します。スレーブLT8550では、このピンはマスタLT8550のIAMPNに接続します。詳細については、アプリケーション情報のセクションを参照してください。

**IAMPP(ピン33)**: マスタLT8550では、このピンは出力ピンです。これはプライマリ・チャンネルの電流検出アンプ出力のバッファリングされた信号です。スレーブLT8550では、このピンは入力ピンです。複数のLT8550を使用する場合は、全てのIAMPPピンと一緒に接続します。詳細については、アプリケーション情報のセクションを参照してください。

**ISP(ピン34)**: プライマリ・チャンネルの電流検出アンプの入力。電流検出アンプへの(+)入力は、通常はDCR検出回路ネットワークまたは電流検出抵抗に接続されます。このピンはマスタLT8550でのみ使用されます。スレーブLT8550では、このピンはグラウンドに接続します。

**ISN(ピン35)**: プライマリ・チャンネルの電流検出アンプの入力。電流検出アンプへの(-)入力は、通常はDCR検出回路ネットワークまたは電流検出抵抗に接続されます。このピンはマスタLT8550でのみ使用されます。スレーブLT8550では、このピンはグラウンドに接続します。

**REGSNS(ピン40)**: REG LDOの電圧検出ピン。このピンはプライマリ・チャンネルのゲート・ドライバ電源ピンに接続します。

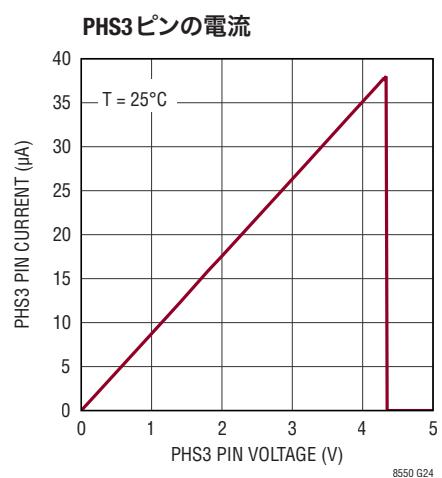

**PHS3(ピン41)**: フェーズ選択ピン。このピンとPHS1、PHS2、およびRT/MSピンを組み合わせて、各チャンネルのスイッチング周波数と位相を設定します。PHS3はREGまたはグラウンドに接続します。詳細については、動作のセクションを参照してください。

**NC(ピン42)**: 未接続。このピンはフロート状態のままにしておくか、隣接するピンに接続します。

**ISN1、ISN2、ISN3、ISN4(ピン43、37、46、39)**: 拡張チャンネルの電流検出アンプの(-)入力。電流検出アンプへの(-)入力は、通常はDCR検出回路ネットワークまたは電流検出抵抗に接続されます。

**ISP1、ISP2、ISP3、ISP4(ピン44、36、45、38)**: 拡張チャンネルの電流検出アンプの(+)入力。電流検出アンプへの(+)入力は、通常はDCR検出回路ネットワークまたは電流検出抵抗に接続されます。

**REGIS(ピン47)**: REG LDOの電流検出ピン。このピンは外部PMOSのソース側に接続します。

**REGDRV(ピン48)**: REG LDOのゲート・ドライバ出力。このピンは外部PMOSのゲートに接続します。

**V<sub>IN</sub>(ピン49)**: 入力電源ピン。このピンは、短距離でグラウンドにバイパスする必要があります。

**GND(露出パッド・ピン53／ピン27)**: グラウンド。このピンは、近くのグラウンド・プレーンに直接接続します。

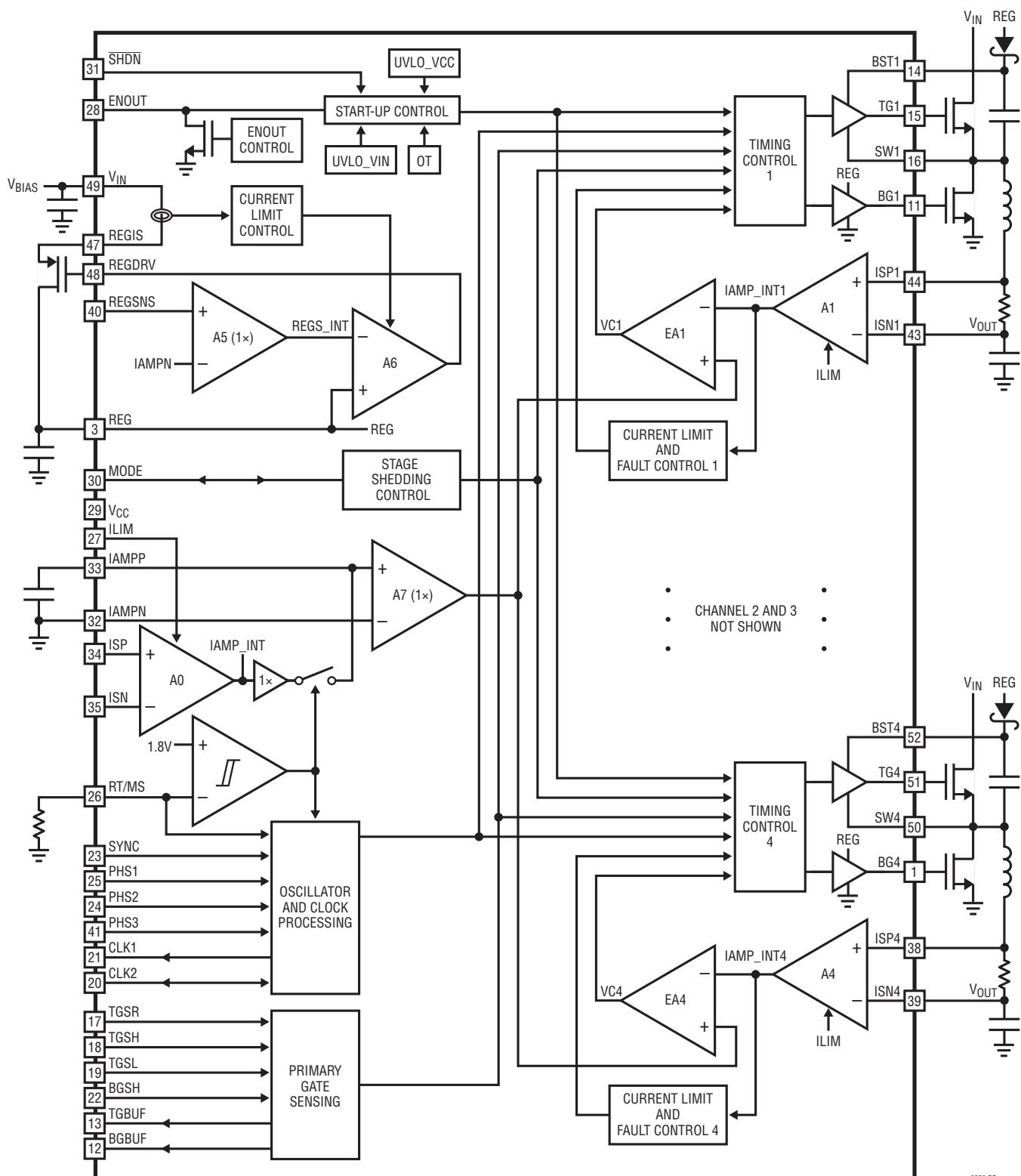

## ブロック図

## 動作

### はじめに

LT8550は、同期整流式降圧コントローラ用のマルチフェーズ・エクスパンダです。各LT8550が8つのゲート・ドライバを内蔵し、最大4フェーズまで拡張可能です。複数のLT8550を1つのシステムに使用した場合、最大18の異なるフェーズをサポートします。更に、このデバイスは1つの位相角につき2フェーズ以上をサポートします。

アナログ・デバイセズ独自の制御アーキテクチャにより、LT8550は(プライマリ・コントローラと呼ばれる)降圧コントローラの動作をサイクルごとに複製します。LT8550は、プライマリ・コントローラのインダクタ電流とプライマリ・コントローラのゲート・ドライバの動作タイミングを測定し、それと同時に各拡張チャンネルの電流を正確に監視および調整して、優れたDCおよび過渡電流分担を実現します。電流分担の精度は、ILIMをREGに接続した場合は全温度範囲で $\pm 6\%$ 、フロート状態にした場合は $\pm 6\%$ 、GNDに接続した場合は $\pm 10\%$ です。

通常動作では、EA(ブロック図のEA1/2/3/4)により、プライマリ降圧レギュレータのスイッチ電流と拡張チャンネルのスイッチ電流が比較されます。プライマリ・チャンネルの電流が増えると、VC(ブロック図のVC1/2/3/4)の電圧も高くなります。これによって拡張チャンネルのスイッチが制御され、プライマリ・チャンネルの電流に一致するまで、拡張チャンネルの電流を増加させます。

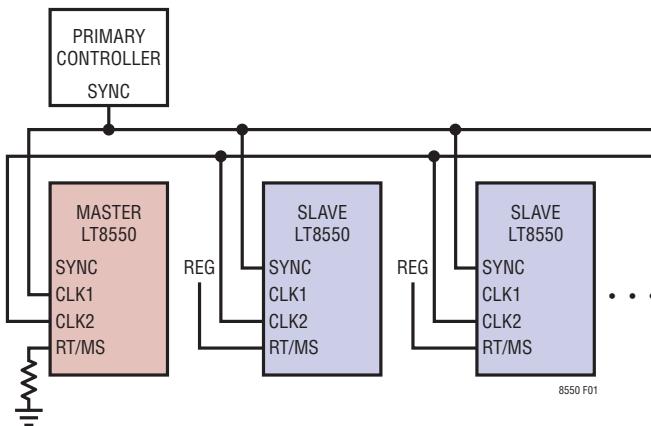

### 複数のLT8550を使用するシステム

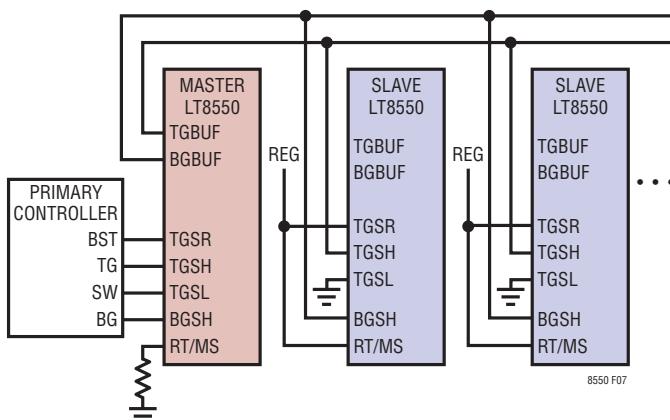

1個のLT8550は最大4チャンネルまで拡張可能です。この構成により、ほとんどの大電流アプリケーションに十分な電力を供給できます。更に大電力のアプリケーションでは、LT8550をマルチチップ動作に構成できます。1つのシステムに2つ以上のLT8550を使用する場合、1つのLT8550がマスターになり、他のLT8550がスレーブになります。RT/MSピンとグラウンドの間に抵抗を接続すると、そのチップはマスターとして設定されます。RT/MSピンをREGに接続すると、そのチップはスレーブとして設定されます。LT8550を1つだけ使用するシステムでは、そのLT8550をマスターとして設定する必要があります。

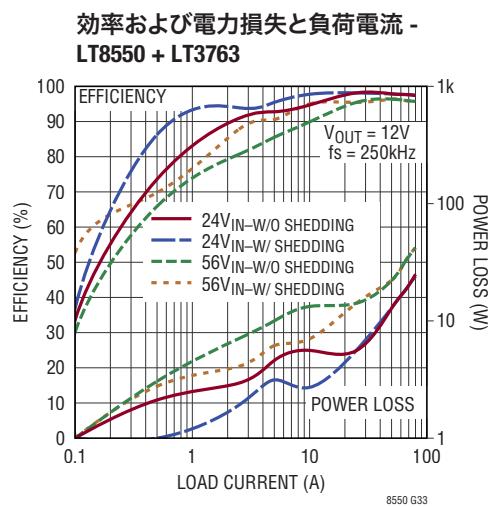

### ステージ・シェディング・モード

MODEピンはステージ・シェディング機能専用です。MODEピンは、マスタLT8550では出力ピンになり、スレーブLT8550では入力ピンになります。

マスタLT8550では、MODEピンがフロート状態になっている場合、LT8550は軽負荷時にステージ・シェディング・モードで動作します。この場合、(ISP-ISN)のピーク電圧が、ある時間の間、特定の値より低いと、デバイスはチャンネル1と3をオフにして全体的な効率を向上させます。チャンネル1と3をオフにした後、(ISP-ISN)のピーク電圧が、ある時間の間、特定の値より低いと、デバイスはチャンネル4もオフにして、チャンネル2だけを動作させます。双方向アプリケーションでは、電流が逆方向で調整されるときにステージ・シェディングを無効にする必要があります。MODEピンの電圧を0.5Vより低くすると、ステージ・シェディング機能は無効になります。

複数のLT8550を使用するシステムでステージ・シェディング機能を使用する場合は、全てのLT8550のMODEピンと一緒に接続して、フロート状態のままにする必要があります。マスタLT8550は、(ISP-ISN)の電圧を検出し、適切な動作を決定します。スレーブLT8550は、若干の遅延の後、マスタLT8550のステージ・シェディング動作に追従します。全てのLT8550のMODEピンの電圧を0.5Vより低くすると、ステージ・シェディング機能は無効になります。

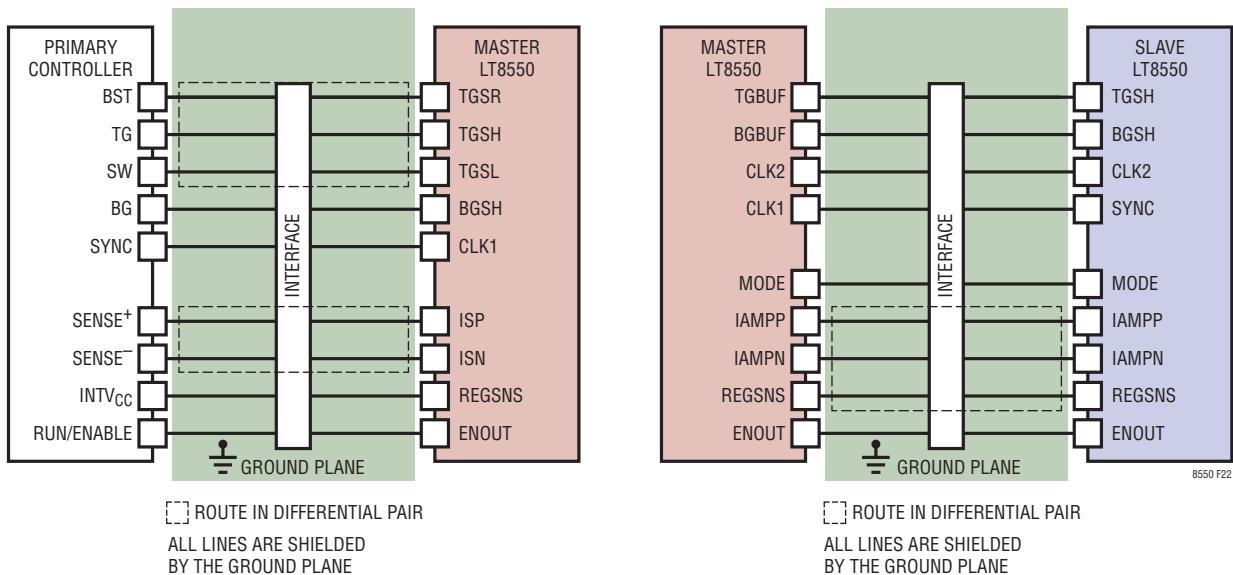

### クロック方式

ここでは、複数のLT8550を使用するシステムでのLT8550のクロック方式を説明します。スレーブLT8550を無視することにより、このクロック方式は、LT8550が1つのシステムにも簡単に応用できます。

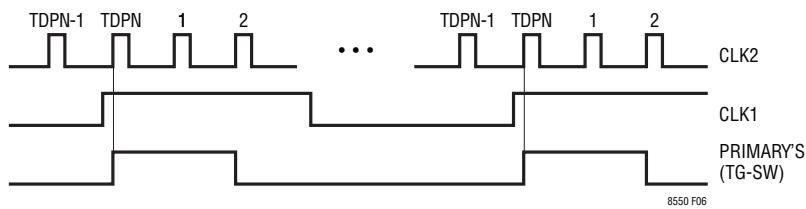

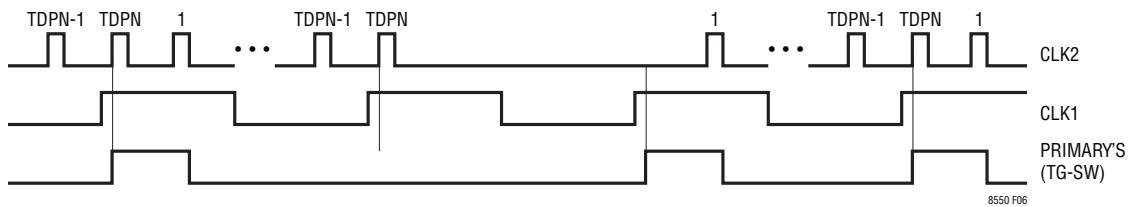

マスタLT8550は、CLK1とCLK2の2つのクロック信号を生成します。複数のLT8550を使用するシステムでは、図1に示すように、全てのLT8550のCLK2ピンを一緒に接続する必要があります。CLK1信号の周波数は基本スイッチング周波数です(詳細については、内部発振器とSYNCピンとクロック同期のセクションを参照してください)。この信号を使用して、プライマリ降圧コントローラとスレーブを同期させます(図1)。通常動作では、CLK2の周波数は、図2に示すように、CLK1の周波数に、異なる位相の総数(TDPN: Total Distinct Phase Number)を掛けた値になります。図2でCLK2パルスの上に示した数は、位相角番号(PAN: Phase Angle Number)と呼ばれます。

## 動作

異なる位相の総数は、表1に従って、マスタLT8550のPHS1、PHS2、およびPHS3ピンによって設定されます。チップ内には遅延ロック・ループ(DLL)があり、プライマリ・コントローラの(TG-SW)の立上がりエッジを、位相角番号がTDPNに等しいパルスに強制的に揃えます(図2)。

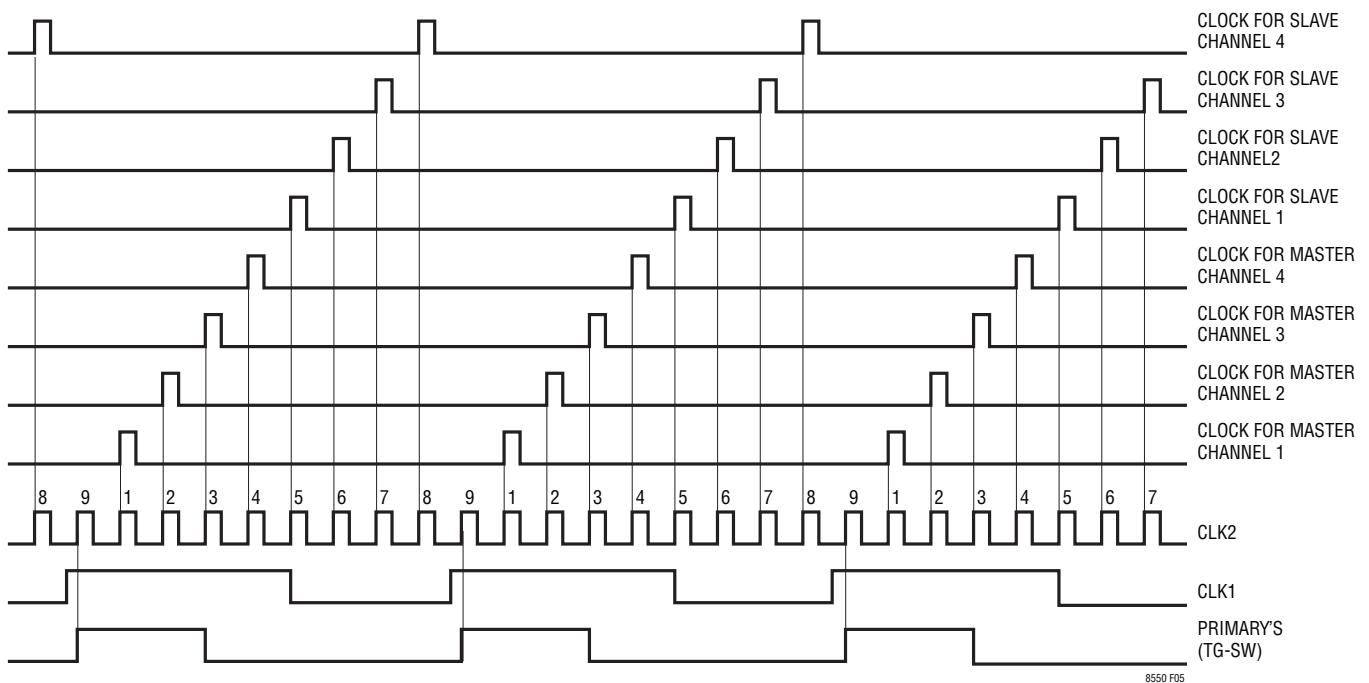

各拡張チャンネルは、CLK1の1クロック・サイクルの中でCLK2から1つのパルスを選択します。この選択されたパルスの立上がりエッジは、非常に短い遅延で、対応するチャンネルの上側ゲートのターンオン・エッジに揃えられます。マスタLT8550のチャンネル1～チャンネル4は、それぞれ位相角番号が1～4に等しいパルスを常に選択します。スレーブLT8550の4つのチャンネルは、4つの連続する位相角番号のパルスを選択します。スレーブLT8550のチャンネル1のパルスの位相角番号は、表1に従って、PHS1、PHS2およびPHS3ピンでも設定されます。スレーブLT8550のチャンネル2、チャンネル3およびチャンネル4は、次の連続する3つの位相角番号のパルスを使用します。

図1. 複数のLT8550を使用するシステムのクロック構成

例として、表2に、2つのLT8550を使用するシステムのPHS1、PHS2およびPHS3の接続を示します。このシステムは、プライマリ・コントローラの位相を含めて合計9フェーズを提供します。プライマリ・コントローラはCLK1信号を使用します。8つの拡張チャンネルが使用するクロックを図3に示します。

プライマリ・コントローラが1つ以上のパルスをスキップすると、拡張チャンネルも同じ数のパルスをスキップします。この機能はCLK2によって実現されます。図4に示すように、プライマリ・コントローラが1つの(TG-SW)パルスをスキップすると、CLK2も1～TDPNの位相番号を持つパルスのグループをスキップします。

表1. 異なる位相の総数(TDPN)と位相角番号(PAN)の設定表

| PHS3 | PHS2     | PHS1     | マスタのTDPN | スレーブのチャンネル1パルスのPAN |

|------|----------|----------|----------|--------------------|

| GND  | GND      | GND      | NA       | 1                  |

| GND  | GND      | REG      | 2        | 2                  |

| GND  | GND      | Floating | 3        | 3                  |

| GND  | REG      | GND      | 4        | 4                  |

| GND  | REG      | REG      | 5        | 5                  |

| GND  | REG      | Floating | 6        | 6                  |

| GND  | Floating | GND      | 7        | 7                  |

| GND  | Floating | REG      | 8        | 8                  |

| GND  | Floating | Floating | 9        | 9                  |

| REG  | GND      | GND      | 10       | 10                 |

| REG  | GND      | REG      | 11       | 11                 |

| REG  | GND      | Floating | 12       | 12                 |

| REG  | REG      | GND      | 13       | 13                 |

| REG  | REG      | REG      | 14       | 14                 |

| REG  | REG      | Floating | 15       | 15                 |

| REG  | Floating | GND      | 16       | 16                 |

| REG  | Floating | REG      | 17       | 17                 |

| REG  | Floating | Floating | 18       | 18                 |

表2.9 フェーズ・アプリケーションの設計例

|               | PHS3 | PHS2     | PHS1     | チャンネル1、2、3、4のPAN |

|---------------|------|----------|----------|------------------|

| Master LT8550 | GND  | Floating | Floating | 1,2,3,4          |

| Slave LT8550  | GND  | REG      | REG      | 5,6,7,8          |

## 動作

図2. CLK1、CLK2およびプライマリ・コントローラの(TG-SW)

図3. 2つのLT8550を使用するシステムのクロック波形

図4. パルスをスキップした場合のCLK1、CLK2およびプライマリ・コントローラの(TG-SW)波形

## 動作

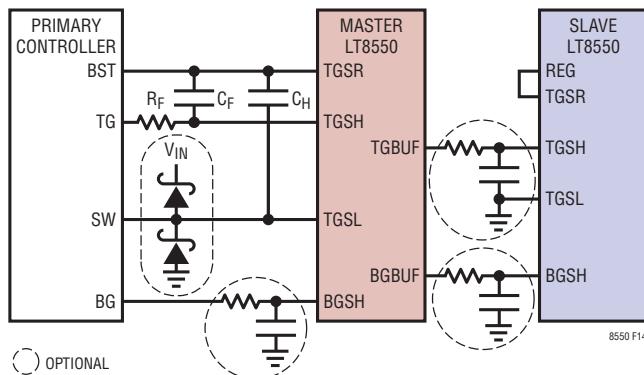

### プライマリ・コントローラのスイッチ状態の検出

ここでは、複数のLT8550を使用するシステムについて説明します。1つのLT8550を使用するシステムでは、この説明のスレーブLT8550を無視してください。

プライマリ・コントローラのスイッチの状態はマスタLT8550によって検出され、マスタLT8550とスレーブLT8550の両方がこの情報を使用します。

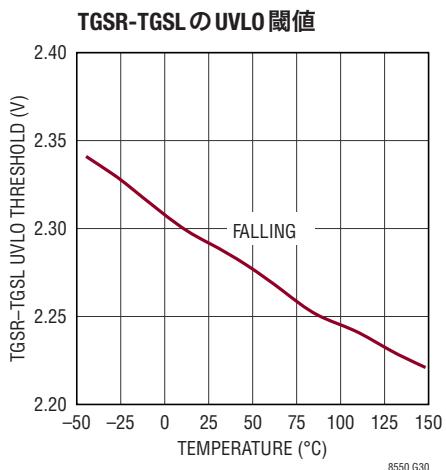

プライマリ・コントローラの上側スイッチの状態は、図5に示すように、マスタLT8550のTGSR、TGSH、およびTGSLピンによって検出されます。このトップ・ゲートのフローティング・ロジック信号は、グラウンド・ベースのロジック信号に変換され、TGBUFピンに出力されます。マスタLT8550のTGBUFは、図5に示すように、下流のスレーブのTGSHに接続されます。スレーブのTGSRとTGSLは、それぞれREGとGNDに接続されます。(TGSR-TGSL)の電圧が2.3V（代表値）より低い場合は、マスタLT8550とスレーブLT8550の両方のTGBUFピンが強制的にグラウンドに引き下げられます。詳細については、アプリケーション情報のセクションを参照してください。

プライマリ・コントローラの下側スイッチの状態の検出にも、図5に示すと同様の手法が使用されます。プライマリ・コントローラのBGはグラウンド・ベースの信号であるため、プライマリ・コントローラのBGの検出に必要なピン(BGSH)は1本だけです。

マスタLT8550がプライマリ・コントローラのスイッチ状態をスレーブに渡すため、プライマリ・コントローラのBST、TG、SWおよびBGのノイズの多い信号を基板上で転送する必要はありません。

図5. 複数のLT8550を使用するシステムのゲート・センシング

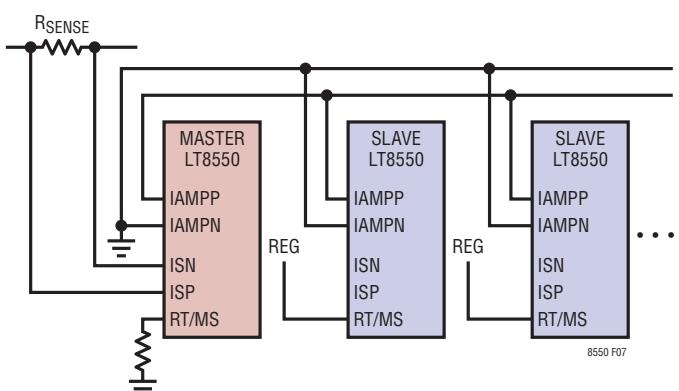

### プライマリ・コントローラのインダクタ電流の検出

ここでは、複数のLT8550を使用するシステムについて説明します。1つのLT8550を使用するシステムでは、この説明のスレーブLT8550を無視してください。

プライマリ・コントローラのインダクタ電流はマスタLT8550によって検出され、マスタLT8550とスレーブLT8550の両方がこの情報を使用します。

図6に示すように、プライマリ・コントローラのインダクタ電流は、マスタLT8550のISPピンとISNピンによって検出されます。この信号は増幅され、マスタLT8550のIAMPPピンに出力されます。安定性を維持するために、IAMPPとGND間にコンデンサが必要です。総容量は100pF～470pFの範囲内にします。スレーブLT8550では、ISPピンとISNピンは使用されず、グラウンドに接続する必要があります。IAMPPは入力ピンになります。プライマリ・コントローラのインダクタ電流の情報をマスタLT8550からスレーブLT8550に渡すために、全てのLT8550のIAMPPピンとIAMPNピンはそれぞれ一緒に接続されます。IAMPNピンは、マスタLT8550のロード・グラウンドに接続されます。IAMPPピンとIAMPNピンは、ユニティ・ゲイン差動検出アンプ(ブロック図のA7)の入力に接続されます。詳細については、アプリケーション情報のセクションを参照してください。

プライマリ・コントローラのインダクタ電流検出抵抗両端の信号は、わずか数十mVです。増幅された電流信号がマスタからスレーブに渡されるため、ノイズにセンシティブな小信号を基板上で転送する必要はなくなります。

図6. 複数のLT8550を使用するシステムでのプライマリ・レギュレータのスイッチ電流の検出

## 動作

### 電流の検出ゲイン、制限、および障害

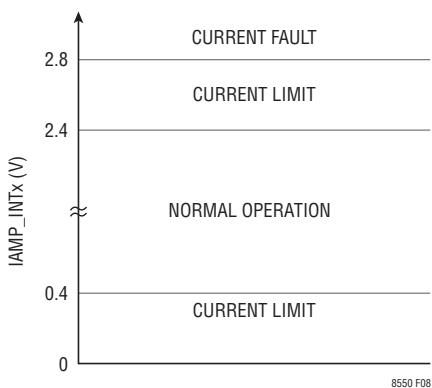

5つの電流アンプ(ブロック図のA0～A4)のゲインには、ILIMピンによって設定される3つのゲイン・レベルがあります。ILIMピンをGND／REG／フロート状態に接続すると、ゲインはそれぞれ33.3/16.7/11.1に設定されます。これらのアンプの出力は(ブロック図の) IAMP\_INT/IMAP\_INTxと呼ばれます。IAMP\_INT/IAMP\_INTxと(ISP-ISN)/(ISPx-ISNx)の関係を図7に示します。1.4Vのオフセットがあります。拡張チャンネルについては、図8に示すように、IAMP\_INTxの値によって電流制限と電流障害が決まります。

図7. 3つの異なるゲインでの電流検出アンプの出力と入力

図8. IAMP\_INTxの電圧と電流制限および電流障害

IAMP\_INTxが2.4Vに達したが2.8Vより低い場合、または0.4V未満に低下した場合、対応するチャンネルは電流制限状態に移行します。電流制限状態が検出されると、対応するチャンネルのBGxとTGxは両方とも直ちにローに引き下げられます。電流制限状態の解消後、次のクロックの立上がりエッジで、チャンネルはスイッチングを再開します。電流制限に対応する(ISPx-ISNx)の電圧を図7に示します。

IAMP\_INTxが2.8Vに達すると、対応するチャンネルは電流障害状態に移行します。電流障害状態が検出されると、対応するチャンネルは障害シーケンスに移行します。詳細については、障害シーケンスのセクションを参照してください。

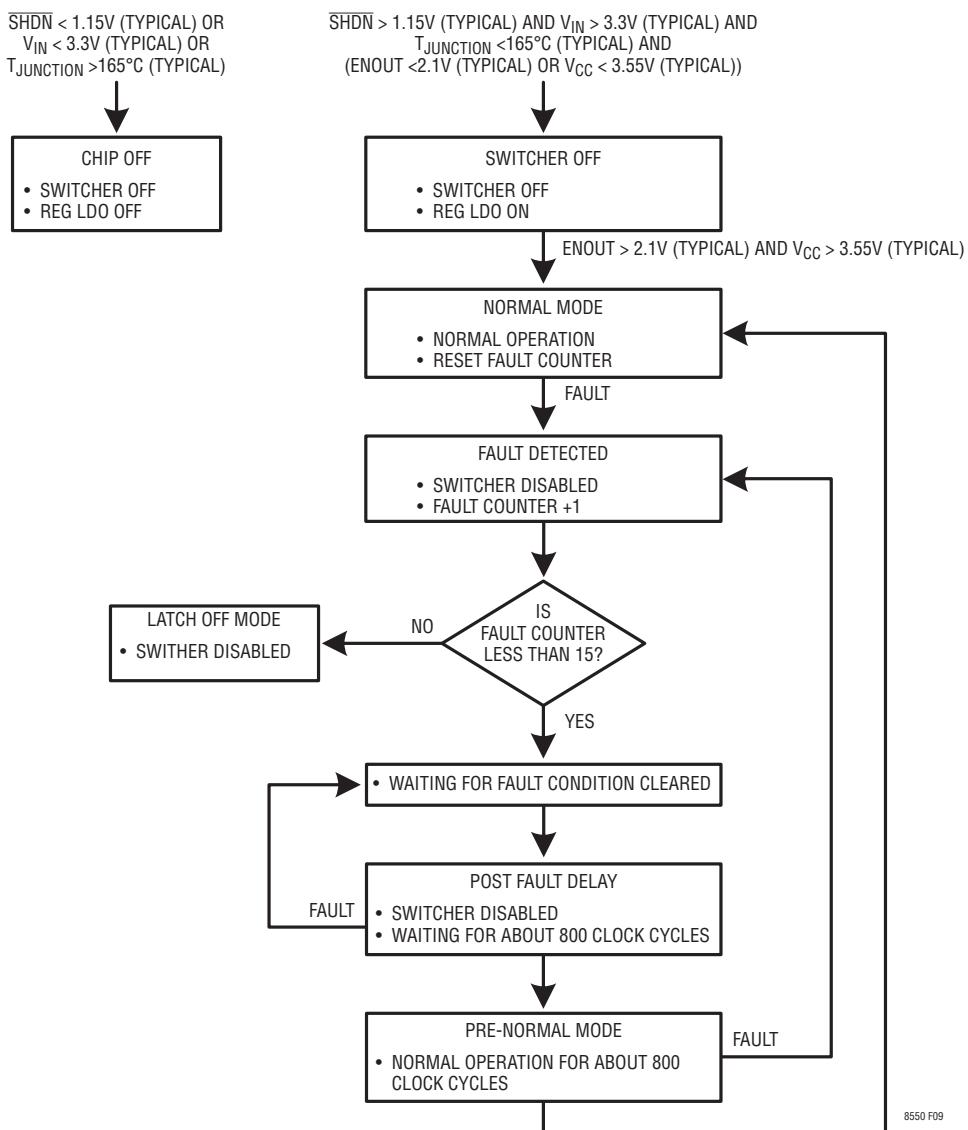

### シャットダウンと起動

図9は、LT8550の起動シーケンスを示しています。このチップのシャットダウン・ピンはSHDNです。このピンの電圧を0.3Vより低くすると、チップはディスエーブルされ(チップ・オフ・ステート)、自己消費電流が最小になります。SHDNの電圧を高くすると自己消費電流は増えますが、REG LDOがイネーブルされた後、SHDNが1.15V(代表値)より高くなるまで、チップはイネーブルされません(スイッチャ・オフ・ステート)。

V<sub>CC</sub>が3.55V(代表値)を超えて上昇し、ENOUTが2.1V(代表値)より高くなった後、スイッキング・レギュレータが起動します。マスタ LT8550 では、ENOUT はオープンドレイン・ピンです。V<sub>CC</sub>が3.55Vより低くなると、ENOUT はGNDに引き下げられ、スイッキングはディスエーブルされます。スレーブ LT8550 では、ENOUT は常に高インピーダンス入力ピンです。

### 障害シーケンス

IAMP\_INTxが2.8Vより高くなると(LT8550の障害条件)、LT8550は障害シーケンスを開始します(図9を参照)。障害イベントはチャンネルに依存しません。つまり、1つのチャンネルで発生した障害状態は、他のチャンネルに直接影響を与えません。特定のチャンネルでいずれかの障害条件が発生すると、対応するチャンネルのゲート・ドライバの出力がローに引き下げられます。LT8550のいずれかのチャンネルがラッチ・オフ・モード(図9を参照)に移行した場合、そのチャンネルを再アクティブ化するには、チップ全体を再起動する必要があります。

## 動作

図9. 起動シーケンスと障害シーケンス

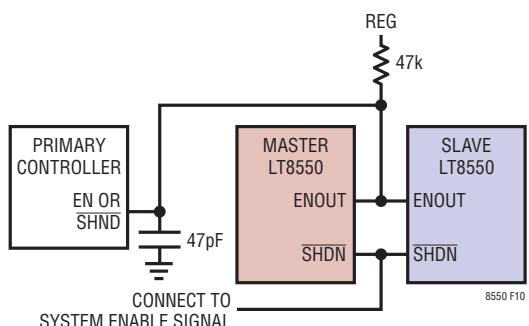

## ENOUTの接続

マスタLT8550では、このピンはオープンドレインのロジック出力ピンです。マスタLT8550のENOUTピンは、スイッチングの準備が完了していないときはグラウンドに引き下げられます。スレーブLT8550では、このピンは入力ピンです。マスタLT8550とスレーブLT8550のいずれも、ENOUTピンが2.1V(代表値)より低くなると、ゲート・ドライバのスイッチング動作はディスエーブルされます。

マスタLT8550のスイッチングの準備が完了していないときは、プライマリ・コントローラとスレーブLT8550のスイッチング動作をディスエーブルすることを推奨します。図10に推奨構成の例を示します。

図10. 推奨されるENOUTの接続

## アプリケーション情報

### REG LDOとV<sub>CC</sub>の電力

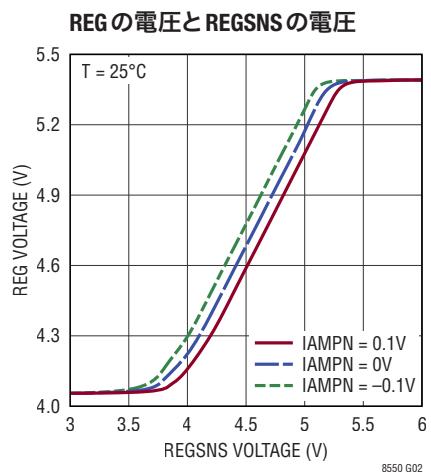

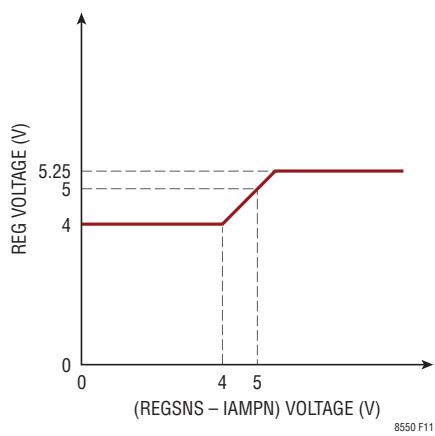

REG LDOは、ゲート・ドライバとCLK1、CLK2、TGBUFおよびBGBUFの出力段に電力を供給します。SHDNピンの電圧が1.15Vより高くなると、図11に示すように、(REGSNS - IAMPN)の電圧が4Vより低い場合、4Vより高いが5.25Vより低い場合、または5.25Vより高い場合、REGの電圧は、それぞれ4V（代表値）、(REGSNS - IAMPN)の電圧、V<sub>IN</sub>から5.25V（代表値）に安定化されます。REGピンは、REGピンの近くに配置される少なくとも4.7μF以上のX5RまたはX7Rセラミック・コンデンサを使用して、電源グラウンドにバイパスする必要があります。

図11. REGの電圧とREGSNSの電圧

V<sub>CC</sub>はほとんどの内部回路の電源であり、図12に示すように、REGのスイッチング・ノイズを除去するための外部フィルタ(R<sub>F</sub>, C<sub>F</sub>)を介してREGに接続されます。このフィルタはV<sub>CC</sub>ピンの近くに配置する必要があり、R<sub>F</sub> = 1Ω、C<sub>F</sub> = 1μF（代表値）が推奨されます。V<sub>CC</sub>が3.55V（代表値）より低くなると、内部UVLOコンパレータがLT8550のスイッチング動作をディスエーブルします。

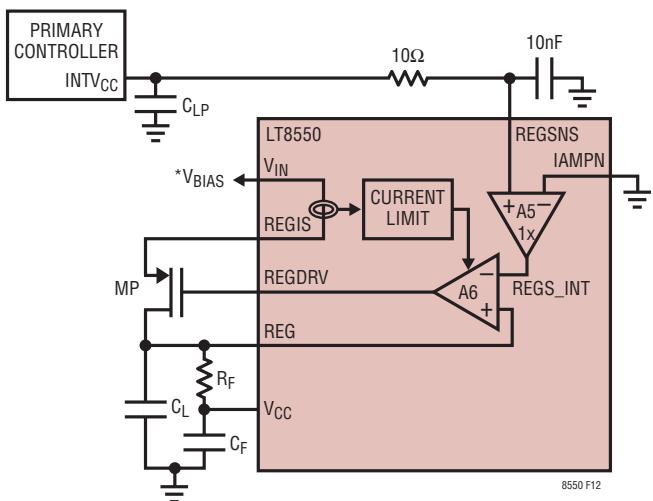

### プライマリ・コントローラのINTV<sub>CC</sub>の検出

図12に示すように、プライマリ・コントローラのゲート・ドライバの電源はINTV<sub>CC</sub>です。

プライマリ・コントローラのINTV<sub>CC</sub>の電圧は、フィルタリング後に図12の差動ユニティ・ゲイン・アンプA5によって検出され、REG LDOのリファレンス電圧としてREGS\_INTにバッファリングされます。

A5の(-)がIAMPNに接続されることに注意してください。プライマリ・コントローラのインダクタ電流の検出のセクションで説明したように、マスタLT8550のIAMPNとスレーブLT8550のIAMPNは、いずれもマスタLT8550のローカル・グラウンドに接続されます。マスタのローカル・グラウンドとプライマリ・コントローラのローカル・グラウンドの電圧にはわずかに差があるため、若干の誤差が生じことがあります。この誤差を最小限に抑えるために、マスタLT8550はプライマリ・コントローラの近くに配置する必要があります。

\*LOWER VOLTAGE (V<sub>BIAS</sub>) CAN BE USED FOR V<sub>IN</sub> PIN TO REDUCE THERMAL STRESS INSTEAD OF USING THE SUPPLY FOR THE POWER STAGE

図12. REG LDOの構成

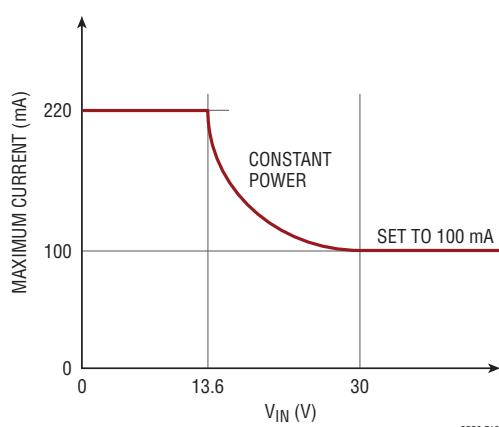

### REG LDOの電流制限と外部パワーPMOSの選択

過電流保護回路は、REG LDOから流れる最大電流を制限します。起動時または過負荷状態でV<sub>CC</sub>の電圧が3.3Vより低い場合、電流制限値は標準で約110mAです。

REGの電圧が3.55Vより高い場合は、図13に示すように、電流制限値はV<sub>IN</sub>の電圧によって決まります。V<sub>IN</sub>の電圧が13.6Vより低い場合、電流制限値は約220mAです。30Vより高い場合、電流制限値は約100mAです。V<sub>IN</sub>の電圧が13.6V～30Vの場合、電流制限値はV<sub>IN</sub>の電圧に反比例し、外部パワーPMOSの最大消費電力を制限します。

外部PMOSの消費電力は次式で計算できます。

$$P = (V_{BIAS} - REG) \cdot I_{LDO}$$

## アプリケーション情報

ここで、 $V_{BIAS}$ ( $V_{IN}$ ピンの電圧)はLT8550のチップ電源、ILDOは特定のアプリケーションでREG LDOから流れる電流です。

次式を使用してPMOSのジャンクション温度を計算し、 $T_J$ の計算値とメーカーのデータシートを比較して、PMOSが過熱しないように適切なPMOSを選択します。

$$T_J = T_A + P \cdot R_{TH(JA)} \quad (1)$$

ここで、

$T_J$ はPMOSのジャンクション温度、

$T_A$ は周囲温度、

$P$ はPMOSの消費電力です。

$R_{TH(JA)}$ は接合部から周囲の空気までのMOSFETの熱抵抗です。該当メーカーのデータシートを参照してください。

外部PMOSの消費電力を削減するために、特に高入力電圧アプリケーションでは、パワー段と同じ電源を共有する代わりに、低電圧の補助電源( $V_{BIAS}$ )を使用してチップに電源を投入することを推奨します。熱ストレスを緩和するには、基板上にPMOS用の十分に大きい銅領域が必要です。

また、ループの安定性を確保するために、 $Q_g < 40nC$ のPMOSを選択することを推奨します。

図13. REG LDOの電流制限と $V_{BIAS}$ の電圧

## 動作周波数の選択

エクスパンダ・システム(プライマリ・コントローラとLT8550)は、マスタ LT8550 によって決定される 100kHz~1MHz の範囲の固定周波数を採用します。図1に示すように、マスタ LT8550 の CLK1 ピンとプライマリ・コントローラおよびスレーブ LT8550 の SYNC ピンを接続することにより、プライマリ・コントローラとスレーブ LT8550 はマスタ LT8550 に同期します。ノイズを最小限に抑えるために、マスタの CLK1 と各プライマリ・コントローラまたはスレーブの SYNC ピンの間に RC フィルタを追加することを推奨します。 $R = 10\Omega$ 、 $C = 220pF$ (代表値)の RC フィルタを SYNC ピンの近くに配置します。

周波数は内部発振器によって設定するか、外部クロック信号源に同期させることができます。スイッチング周波数を選択する際は、効率と部品サイズの兼ね合いを考慮に入れます。低周波数動作は、MOSFET のスイッチング損失を低減して効率を向上させますが、出力リップル電圧を低く保つにはより大きなインダクタンスや容量(あるいは両方)が必要になります。スイッチング周波数を設定するには、RT/MS ピンとグラウンドの間に適切な抵抗を配置し、SYNC ピンをローまたはハイに接続します。この周波数は SYNC ピンを駆動する外部クロック信号源に同期させることもできます。以降のセクションでは詳細を説明します。

## 内部発振器

マスタ LT8550 の自走スイッチング周波数は、RT/MS ピンとグラウンドの間に抵抗を接続し、SYNC ピンをロー(<0.8V)またはハイ(>1.2V)にすることにより、内部発振器を使用して設定できます。発振周波数は次式を使って計算されます。

$$f_{OSC} = \frac{25,000}{R_T + 0.15} \text{kHz} \quad (2)$$

ここで、 $f_{OSC}$  の単位は kHz、 $R_T$  の単位は kΩ です。逆に、 $R_T$ (単位 kΩ) は次式を使って目的の周波数(kHz)から計算できます。

$$R_T = \frac{25,000}{f_{OSC}} \text{k}\Omega - 0.15 \text{k}\Omega \quad (3)$$

## アプリケーション情報

### SYNCピンとクロック同期

LT8550はフェーズ・ロック・ループ(PLL)を備えており、内部発振器を外部クロック信号に同期させることができます。このPLLはエッジに反応するデジタル・タイプで、外部クロックと内部発振器の位相シフトを $0^\circ$ にします。

外部クロック源に適切に同期させるには、外部クロック源の周波数が次の2つの基準を満たしている必要があります。

1. 外部クロック源の周波数が125kHz～1MHzの範囲内である場合にのみ、PLLが正常に動作することが確認されている。

2. 外部クロックの周波数が、RT抵抗によって設定される自走周波数より高い場合にのみ、外部クロックへの同期が可能となる。外部クロックの周波数が、RTによって設定されるf<sub>OSC</sub>より低い場合は、内部発振器はf<sub>OSC</sub>で発振する。

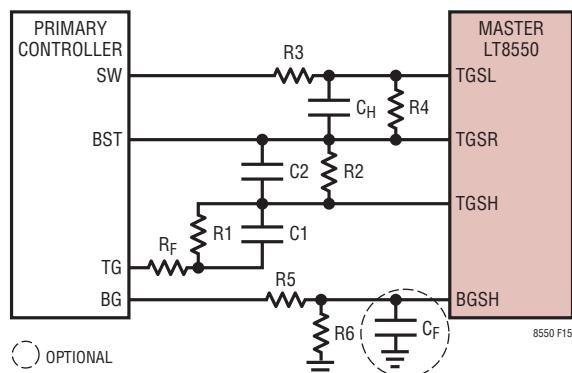

### プライマリ・コントローラのゲート・センシング・フィルタと分圧器

動作のセクションで説明したように、プライマリ・コントローラの上側および下側スイッチの状態は、マスタLT8550のゲート検出ピン(TGSR、TGSH、TGSL、およびBGSH)によって検出されます。検出された上側ゲート信号と下側ゲート信号は、それぞれマスタLT8550のTGBUFとBGBUFにバッファリングされます。

プライマリ・コントローラのSWノードは高速で遷移するため、プライマリ・コントローラの上側MOSFETの状態を誤って検出しないように、図14に示すように、RCフィルタR<sub>F</sub>、C<sub>F</sub>およびバイパス・コンデンサC<sub>H</sub>を接続する必要があります。長いパターンを使用して上側ゲートを検出する場合は、TGSLピンがグラウンドより低い電圧でリンクングしたり、ピンの絶対最大定格を超えたないように、LT8550のTGSLピンの近くにオプションのショットキー・クランプを追加することを推奨します。図14に示すように、プライマリ・コントローラの下側ゲート検出ピンとスレーブLT8550のゲート検出ピンの両方に、オプションのフィルタを追加することも推奨します。これらのフィルタの時定数は30ns未満にする必要があります、R<sub>F</sub> = 20Ω、C = 1nFの代表値を推奨します。

LT8550は、ゲート駆動レールの電圧が5.5Vより低いプライマリ・コントローラと連携させることを推奨します。プライマリ・コントローラのゲート駆動レールの電圧が5.5Vより高い場合は、図15に示すように、抵抗分圧器が必要となります。

図14. TGSL上のフィルタとショットキー・クランプを使用したゲート・センシング構成

図15. プライマリ・コントローラのゲート駆動レールの電圧が5.5Vより高い場合のゲート・センシング構成

次式を使用してゲート・センシングに必要な分圧器とフィルタを設計するか、表3の推奨値を参照してください。

$$\frac{R_F C_1 C_2}{C_1 + C_2} \leq 30\text{ns}$$

$$\frac{C_F R_5 R_6}{R_5 + R_6} \leq 30\text{ns}$$

$$\frac{R_2}{R_1 + R_2} = \frac{R_4}{R_3 + R_4} = \frac{R_6}{R_5 + R_6} = \frac{5.5\text{V}}{\text{Primary's } V_{\text{INTVCC}}}$$

$$R_1 C_1 = R_2 C_2$$

## アプリケーション情報

表3. ゲート・センシング・フィルタの推奨値

| プライマリ・コントローラの<br>INTV <sub>CC</sub> の電圧<br>(V) | R1 = R3 = R5<br>(kΩ) | R2 = R4 = R6<br>(kΩ) | C1<br>(nF) | C2<br>(nF) | R <sub>F</sub><br>(Ω) |

|------------------------------------------------|----------------------|----------------------|------------|------------|-----------------------|

| 6.0                                            | 4.7                  | 47                   | 1.0        | 1.0        | 22                    |

| 6.5                                            | 10                   | 33                   | 3.3        | 1.0        | 27                    |

| 7.0                                            | 10                   | 22                   | 2.2        | 1.0        | 30                    |

| 7.5                                            | 10                   | 15                   | 1.0        | 0.68       | 47                    |

| 8.0                                            | 10                   | 15                   | 1.0        | 0.68       | 47                    |

| 9.0                                            | 10                   | 13                   | 1.0        | 0.68       | 47                    |

| 9.5                                            | 9.1                  | 13                   | 1.0        | 0.68       | 47                    |

| 10                                             | 10                   | 10                   | 1.0        | 1.0        | 43                    |

更に、R1～R6はkΩレンジまたはそれ以上にして、自己消費電流を低減する必要があります。また、SWノードの遷移中にプライマリ・コントローラの上側ゲートの状態を正確に検出できるように、C1とC2の容量を1nF～100nFの範囲内にして、C<sub>H</sub>の容量を4.7nFより大きくすることを推奨します。これらの分圧器とフィルタは、基板上でマスタLT8550の近くに配置する必要があります。

### パワーワン部品の選択ガイドライン

パワーワン部品には、入力および出力コンデンサ、インダクタ、パワーNチャンネルMOSFET、およびオプションのショットキー・ダイオードが含まれます。LT8550の各拡張チャンネルは、常にプライマリ・コントローラと全く同じパワーワン部品を使用します。以降のセクションで、パワー・デバイスの選択の簡単なガイドラインを示します。詳細については、プライマリ・コントローラのデータシートを参照してください。

### インダクタの選択

高効率を実現するには、フェライトなど、コア損失の小さなインダクタを選択します。また、I<sup>2</sup>R損失を減らすため、インダクタはDC抵抗が低く、飽和せずにピーク・インダクタ電流を扱えるものにします。放射ノイズを最小限に抑えるため、トロイド、ポットコア、またはシールド付きボビン・インダクタを使用します。

インダクタの選択は、最大平均負荷電流およびインダクタの電流リップルと相互に関連しています。すなわち、インダクタは飽和しないようピーク電流より大きな規格と、電流リップルを要求に抑えられる大きさが必要です。これによりピーク・インダクタ電流に制限される、最大平均負過電流を取り出すことができます。

### パワー MOSFET およびショットキー・ダイオード (オプション) の選択と効率に関する検討事項

パワー MOSFETを選択する際の重要なパラメータには、オン抵抗(R<sub>DS(ON)</sub>)、ミラー容量(C<sub>MILLER</sub>)、BV<sub>DSS</sub>(すなわち、ドレイン-ソース・ブレークダウン電圧)、最大出力電流などがあります。これらのパラメータは全てメーカーのデータシートに記載されています。ゲート駆動電圧はREG LDOによって設定されます(代表値5V)。したがって、LT8550にはロジック・レベル(5V)のMOSFETを使用する必要があります。

パワー MOSFETの選択では、消費電力を考慮することが非常に重要です。最も効率の高い回路には、消費電力が最小のMOSFETが採用されます。デバイスを損傷する可能性がある過熱を防止するため、消費電力を制限する必要があります。LT8550が連続モードで動作しているとき、上側MOSFETと下側MOSFETのデューティ・サイクルは、以下の式で与えられます。

$$\text{Main Switch Duty Cycle} = \frac{V_{\text{OUT}}}{V_{\text{IN}}}$$

$$\text{Sync Switch Duty Cycle} = \frac{V_{\text{IN}} - V_{\text{OUT}}}{V_{\text{IN}}}$$

最大出力電流でのメイン・スイッチと同期スイッチの消費電力は、以下の式で与えられます。

$$\begin{aligned} P_{\text{MAIN}} &= \frac{V_{\text{OUT}}}{V_{\text{IN}}} I_{\text{MAX}}^2 (1 + \delta) R_{\text{DS(ON)}} \\ &\quad + V_{\text{IN}}^2 \left( \frac{I_{\text{MAX}}}{2} \right) (R_{\text{DR}})(C_{\text{MILLER}}) \\ &\quad \cdot \left[ \frac{1}{V_{\text{REG}} - V_{\text{TH(MIN)}}} + \frac{1}{V_{\text{TH(MIN)}}} \right] \cdot f_{\text{OSC}} \end{aligned}$$

$$P_{\text{SYNC}} = \frac{V_{\text{IN}} - V_{\text{OUT}}}{V_{\text{IN}}} I_{\text{MAX}}^2 (1 + \delta) R_{\text{DS(ON)}}$$

ここで、 $\delta$ はR<sub>DS(ON)</sub>の温度依存性、R<sub>DR</sub>はMOSFETのミラー閾値電圧でのゲート・ドライバの実効抵抗、V<sub>TH(MIN)</sub>はMOSFETの最小閾値電圧の代表値、f<sub>OSC</sub>はスイッチング周波数です。

I<sup>2</sup>Rの損失は両方のMOSFETに共通していますが、メイン・スイッチの式には遷移損失の項が追加されています。この項は入力電圧が高いときの電力損失に大きな影響を与えます。V<sub>IN</sub> < 20Vでは、大電流での効率は一般的にMOSFETが大きいほど向上します。一方、V<sub>IN</sub> > 20Vでは、遷移損失

## アプリケーション情報

が急速に増加し、ミラー容量が小さく  $R_{DS(ON)}$  が高いデバイスを使った方が高い効率が得られるポイントに達します。同期 MOSFET の損失は、メイン・スイッチのデューティ・サイクルが最低のときに最高の入力電圧で最も大きくなります。この場合、複数の MOSFET を並列接続すると、各デバイスでの消費電力を低減することができます。

消費電力に基づいて、REG LDO の電流制限と外部パワー PMOS の選択のセクションの式(1)を使用して MOSFET のジャンクション温度を計算し、過熱が発生しない適切な MOSFET を選択します。

下側スイッチに対して並列に接続されたオプションのショットキー・ダイオードは、メイン・スイッチと同期スイッチの導通の間のデッド・タイム中に導通します。これによって、同期スイッチのボディ・ダイオードがオンして電荷を蓄積するのを防止し、逆回復時間を不要にします。逆回復時間があると、 $V_{IN}$  が高いために効率が最大 3% 低下することがあります。ショットキー・ダイオードを使用すると、効率は向上しますが、特に高温では、シリコン・ダイオードよりもはるかに大きな逆もれ電流が発生します。高い逆電圧と大きな逆電流が組み合わされると、ダイオードが自己加熱することがあります。熱抵抗( $\theta_{JA}$ )の低いパッケージを選択して、ダイオードの自己発熱を最小限に抑えてください。

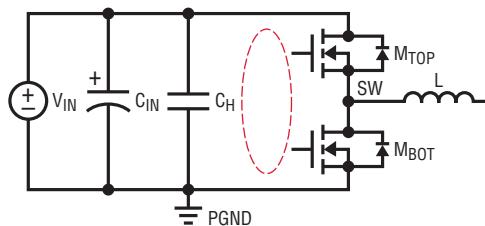

### $C_{IN}$ の容量

連続モードでは、上側 N チャンネル MOSFET のソース電流は、デューティ・サイクルが  $(V_{OUT}/V_{IN})$  の方形波になります。大きな過渡電圧の発生を防止するには、最大 RMS 電流に対応できるサイズの低 ESR (等価直列抵抗) 入力コンデンサを使用する必要があります。コンデンサの最大 RMS 電流は次式で与えられます。

$$C_{IN} \text{ Required } I_{RMS} \approx \frac{I_{MAX}}{V_{IN}} \left[ (V_{OUT})(V_{IN} - V_{OUT}) \right]^{1/2}$$

この式は  $V_{IN} = 2V_{OUT}$  のときに最大になります。ここで、 $I_{RMS} = I_{O(MAX)}/2$  です。設計ではこの単純で最も厳しい条件がよく使用されます。条件を大きく変化させても状況がそれほど改善されないからです。コンデンサ・メーカーの規定するリップル電流定格は多くの場合 2000 時間の寿命試験のみに基づいているので、コンデンサを更にディレーティングする、つまり要求されている温度より高い温度定格のコンデンサを選択することを推奨します。条件を満たすために、複数のコンデンサを並列で使用することもできます。通常は、

複数の X5R または X7R セラミック・コンデンサと、導電性ポリマー・タイプまたはアルミ電解タイプのバルク・コンデンサを並列に接続します。セラミック・コンデンサは ESR が低いため、RMS リップル電流の大部分を吸収します。各ベンダーはセラミック・コンデンサのリップル電流定格について一貫した仕様規定を行っていませんが、セラミック・コンデンサは過剰なリップル電流が原因で故障することもあります。疑問点があれば、該当メーカーにお問い合わせください。

### $C_{OUT}$ の容量

ESR が非常に小さい出力コンデンサを使用して、出力電圧リップルを小さく抑える必要があります。ESR と RMS 電流処理の条件を満たすために、複数のコンデンサを並列に配置しなければならない場合があります。乾式タンタル、特殊ポリマー、アルミ電解およびセラミックの各コンデンサは、全て表面実装パッケージで入手できます。特殊ポリマー・コンデンサは ESR が非常に低く、他のタイプに比べて容量密度が低くなります。タンタル・コンデンサは容量密度が最も高く、スイッチング電源にはサージ・テスト実施済みのタイプを使用する必要があります。アルミ電解コンデンサは ESR がかなり大きく、コスト重視のアプリケーションに使用できます。通常、 $C_{OUT}$  が ESR の条件を満たしていれば、必要な値をはるかに超える RMS 電流定格が確保されます。ほとんどの設計では、少なくとも 20  $\mu\text{F}/\text{A}$  の負荷コンデンサの使用を推奨します。

### 上側 MOSFET ドライバの電源 ( $C_{BX}$ 、 $D_{BX}$ )

外付けブートストラップ・コンデンサ  $C_{BX}$  は、上側スイッチのゲート駆動電圧を供給します。このコンデンサは  $BST_x$  と  $SW_x$  の間に接続され、 $SW_x$  ピンがローのときにショットキー・ダイオード  $D_{BX}$  を介して REG から充電されます。上側のスイッチがオンになると、 $SW_x$  の電圧は上昇して  $V_{IN}$  に電力を供給し、 $BST_x$  の電圧は  $V_{IN} + REG$  まで上昇します。昇圧コンデンサは、上側スイッチが必要とするゲート電荷の約 100 倍の電荷を蓄積する必要があります。大半のアプリケーションでは、0.1  $\mu\text{F}$  ~ 0.47  $\mu\text{F}$  の X5R または X7R 誘電体コンデンサで十分です。REG と GND の間のバイパス容量は、ブートストラップ・コンデンサの容量の少なくとも 10 倍にする必要があります。更に、ショットキー・ダイオードの逆ブレークダウン電圧は、最大電力の  $V_{IN}$  電圧より大きなければなりません。

## アプリケーション情報

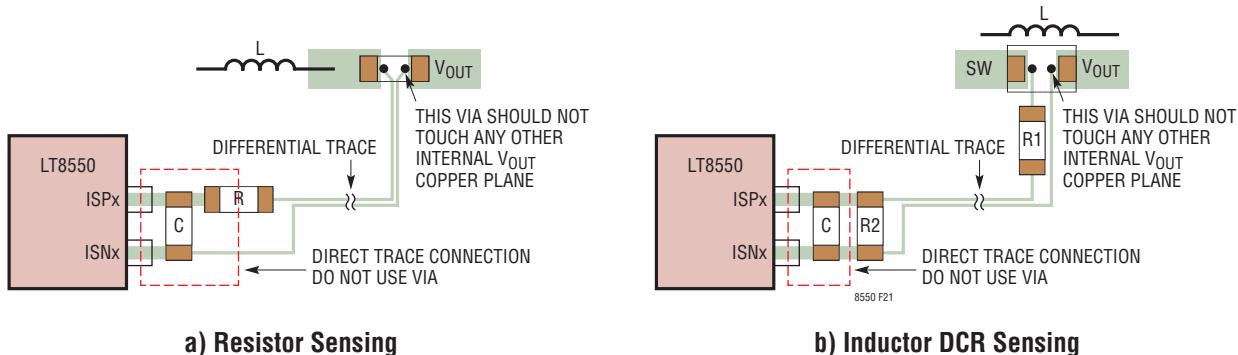

### インダクタ電流の検出

LT8550は、小さな値の直列電流検出抵抗( $R_{SENSE}$ )またはインダクタDC抵抗(DCR)のいずれかでインダクタ電流を検出するように構成できます。2つの電流検出方式のどちらを選択するかは、主にコスト、精度、消費電力の兼ね合いによって決まります。DCRによる検出は、高価な電流検出抵抗が不要となり、特に大電流のアプリケーションで電力効率が高いため、広く普及しつつあります。一方、電流検出抵抗を使用すると、コントローラの非常に正確な電流制限値が得られます。

ISPx/ISNx(すなわち、ISP、ISP1/2/3/4、ISN、ISN1/2/3/4)ピンは、電流検出アンプへの入力です。電流検出アンプのコンモンモード入力電圧範囲は、0V～80Vです。電流検出抵抗は、通常はインダクタと直列にしてLT8550の出力に接続します。

通常動作中、各ISNxピンには $0\mu A$ ～ $100\mu A$ の電流が流れます。ISPxピンの電流は $1\mu A$ 未満です。電流アンプへのISPx入力は高インピーダンスなので、DCRによる高精度の電流検出が可能となります。

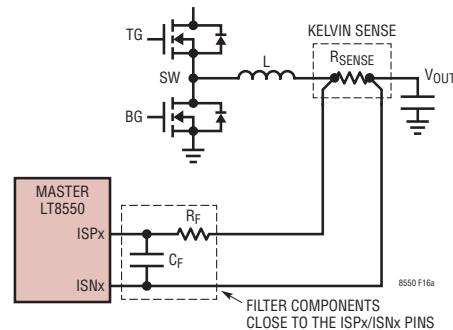

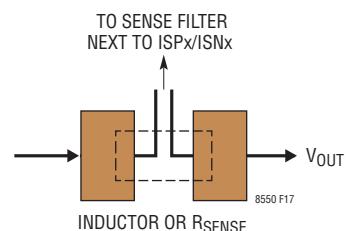

**値の小さな抵抗による電流検出：**標準的な $R_{SENSE}$ によるインダクタ電流検出を図16aに示します。フィルタ部品( $R_F$ 、 $C_F$ )をLT8550の近くに配置する必要があります。 $R_F$ の値が $100\Omega$ より大きいと、オフセット電圧が高くなる可能性があるため、これより大きな抵抗は避ける必要があります。フィルタの時定数( $R_F \cdot C_F$ )は30ns以内にする必要があります。図17に示すように、正と負の検出パターンは差動ペアとして並べて配線し、検出抵抗の下でケルビン(4線式)接続する必要があります。

$R_{SENSE}$ は最大出力電流に基づいて選択します。与えられた最大出力電流 $I_{OUT(MAX)}$ 、最大検出電圧 $V_{SENSE(MAX)}$ 、およびインダクタ最大リップル電流 $\Delta I_L(MAX)$ で、外付け部品の値のばらつきに対して20%のマージンを確保する場合、 $R_{SENSE}$ の値は次の式から選択できます。

$$R_{SENSE} = 0.8 \cdot \frac{V_{SENSE(MAX)}}{I_{OUT(MAX)} + \Delta I_L(MAX) / 2}$$

a)

b)

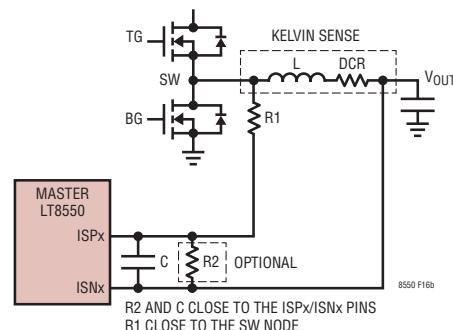

図16. インダクタ電流検出フィルタ

図17. DCRによる検出または抵抗による検出の場合の検出ラインの配置

**DCRによるインダクタ電流の検出：**できるだけ高い効率が要求されるアプリケーションでは、図16bに示すように、LT8550はインダクタのDCR両端の電圧降下を検出できます。インダクタのDCRのDC巻線抵抗は非常に小さく、値の小さな最近の大電流インダクタでは $1m\Omega$ 未満のこともあります。このようなインダクタを必要とする大電流アプリケーションで検出抵抗を使用すると、DCRによる検出に比べて、導通損失によって効率が数ポイント低下することがあります。

## アプリケーション情報

インダクタのDCRは、インダクタの両端にRCフィルタを接続することによって検出されます。このフィルタは、通常は1個または2個の抵抗(R1およびR2)と1個のコンデンサ(C)で構成されます。外付けフィルタの時定数( $R1||R2 \cdot C$ )を、L/DCRの時定数と全く同じになるように選択した場合、Cの両端の電圧降下は次の式で表されます。

$$V_{SENSE} = I_L \cdot DCR \cdot \frac{R2}{R1+R2}$$

したがって、目的の検出抵抗よりDCRの方が大きい場合は、R2を使用してセンス端子両端の電圧をスケーリングできます。ILIMピンを使用して電流制限値を設定する機能があるので、R2の使用はオプションです。Cは通常、 $0.01\mu F \sim 0.47\mu F$ の範囲で選択します。これにより、 $R1||R2$ はほぼkΩレンジに収まります。

DCRによる電流検出では、図17に示すように、検出ラインを並べて配線し、インダクタの下でケルビン接続します。ノイズにセンシティブな小信号ノードにノイズがカップリングしないように、図16bに示すように、抵抗R1はインダクタの近くに配置し、R2とCはLT8550の近くに配置します。

### サーマル・シャットダウン

ダイのジャンクション温度が約 $165^{\circ}C$ に達すると、LT8550はサーマル・シャットダウン状態になります。全てのパワー・スイッチはオフします。マスタLT8550では、ENOUTピンがグラウンドに引き下げられ、システムの全てのスイッチング動作がシャットダウンされます。LT8550は、ダイの温度が約 $5^{\circ}C$ (公称)低下すると再インープルされます。

### 効率に関する検討事項

LT8550のパーセント表示での効率は、出力電力を入力電力で割って100%を掛けたものに等しくなります。多くの場合、個々の損失を分析して、効率を制限する要素が何であり、また何が変化すれば最も効率が改善されるかを判断することが有益です。パーセント表示の効率は、次式で表すことができます。

$$\%Efficiency = 100\% - (L1 + L2 + L3 + \dots)$$

ここで、L1、L2などは入力電力に対するパーセント値で表した個々の損失です。回路内の電力を消費する全ての素子で損失が生じますが、LT8550の回路内の損失の大部分は、通常は次のいくつかの要因によって生じます。

1.  $I^2R$  損失。 $I^2R$  損失は、MOSFET、インダクタ、および電流検出抵抗のDC抵抗から発生します。大出力電流の条件では、電力損失の大部分がこの損失です。連続モードでは、インダクタと $R_{SENSE}$ に平均出力電流が流れますが、上側MOSFETと下側MOSFETの間で細かく分割されます。2つのMOSFETの $R_{DS(ON)}$ がほぼ同じ場合は、一方のMOSFETの抵抗にインダクタのDCR、 $R_{SENSE}$ 、および基板上のパターンを加算するだけで、 $I^2R$ 損失を求めるることができます。

2. 遷移損失。この損失は、スイッチング・ノードの遷移中に上側MOSFETが短時間だけ飽和(ミラー)領域に留まることから生じます。この損失は、入力電圧、負荷電流、ドライバの強度、およびMOSFETの容量によって決まります。この遷移は、高入力電圧または高スイッチング周波数で大きな影響を与えることがあります。

3. REG電流：これはMOSFETドライバ電流とREG制御電流の和です。MOSFETドライバ電流は、パワーMOSFETのゲート容量のスイッチングの結果生じます。MOSFETのゲートがローからハイ、更に再びローに切り替わるたびに、一定量の電荷 $dQ$ がREGからグラウンドに移動します。それによって生じる $dQ/dt$ はREGから流れ出る電流であり、通常は制御回路の電流よりも大きくなります。連続モードでは、 $I_{GATECHG} = f \cdot [Q_T + Q_B]$ です。ここで、 $Q_T$ と $Q_B$ は上側MOSFETと下側MOSFETのゲート電荷です。

4.  $C_{IN}$ の損失。入力コンデンサは、LT8550に流れる大きな方形波入力電流をフィルタリングし、電源からの平均DC電流に変換します。このコンデンサ自体の平均DC電流は0ですが、このコンデンサにはAC電流が流れます。したがって、ESRが非常に低い入力コンデンサを使用して、ESRに起因するRMS電流損失を最小限に抑える必要があります。また、上流のケーブル配線、ヒューズ、またはバッテリ内のRMS損失を防ぐために、入力コンデンサには、入力電流のAC成分を除去するのに十分な容量が必要です。LT8550のマルチフェーズ・アーキテクチャは、ESR損失の軽減に貢献します。

## アプリケーション情報

5. ボディ・ダイオードの導通損失。デッド・タイムの間、下側 MOSFET の損失は  $I_L \cdot V_F$  です。ここで、 $V_F$  は約 0.7V です。スイッチング周波数が高くなると、デッド・タイムがスイッチング・サイクル期間の高い割合を占めるようになり、効率が低下します。

6.  $V_{IN}$  の電流は、 $V_{IN}$  ピンから直接デバイスに流れ込む DC 電源電流です。これは電気的特性の表に仕様規定

されています。 $V_{IN}$  の電流による損失は通常小さな値です (0.1%未満)。

銅パターン、ヒューズおよびバッテリの抵抗など、その他の隠れた損失が、更なる効率低下の原因になる可能性があります。システム設計の段階でこれらの要因を考慮に入れることが重要です。

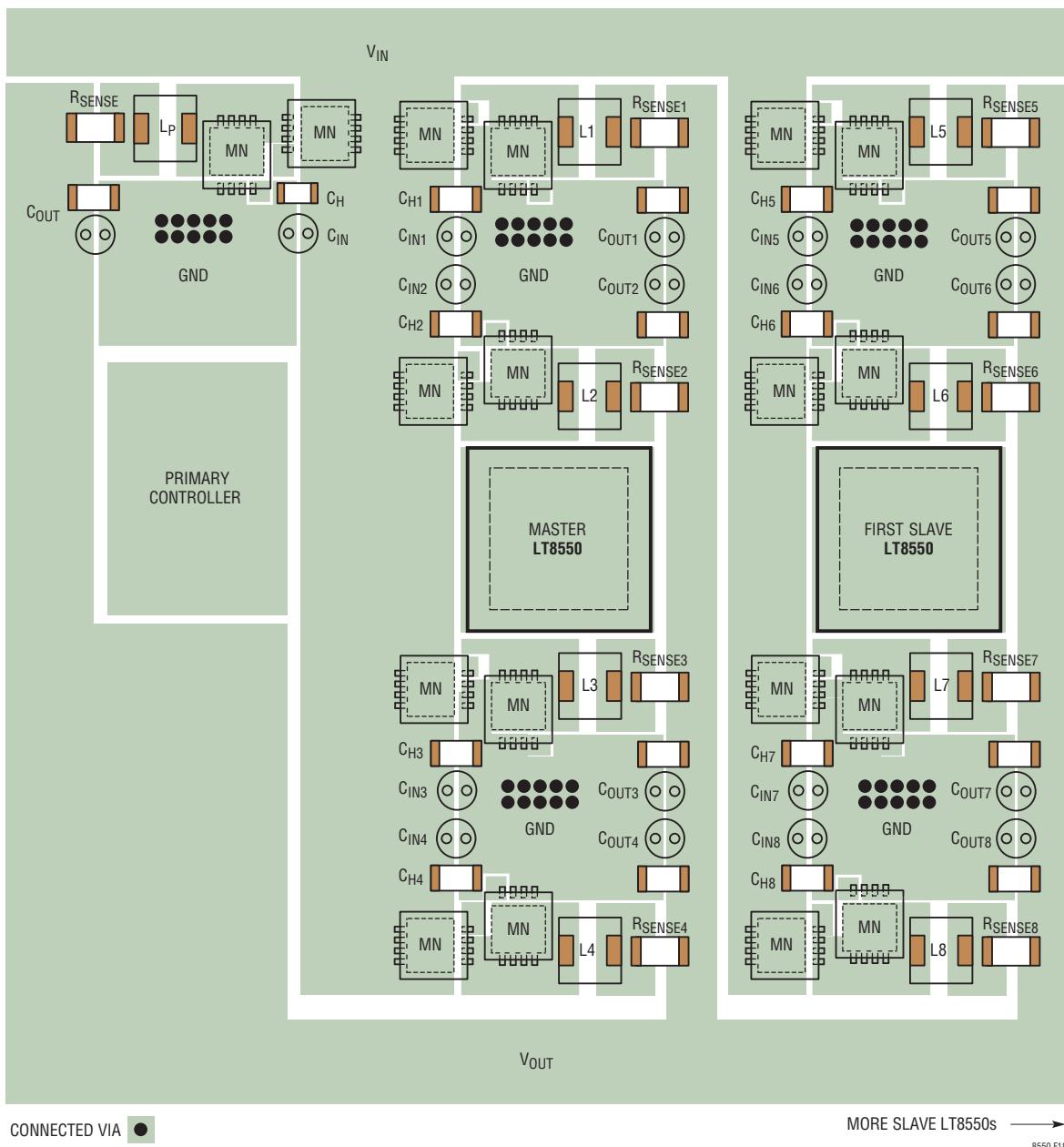

図 18.9 フェーズ・システムの推奨回路基板設計

## アプリケーション情報

### 回路基板レイアウトのチェックリスト

9フェーズ・システム、プライマリ・コントローラ、および2つのLT8550を使用したプリント回路基板の推奨設計例を図18に示します。必要に応じてこの設計のフェーズ/チャンネル数を拡張できます。マルチフェーズ・システムが正常に動作するように、次の一般的なチェックリストに従ってください。

- 専用のグラウンド・プレーンを持つ多層基板を使用して、ノイズ・カップリングを軽減し、放熱性能を向上させます。グラウンド・プレーンは、部品(すなわち、MOSFET、インダクタ、検出抵抗、入力および出力コンデンサなど)の配線層に隣接させます。

- 小信号グラウンド(SGND)と電源グラウンド(PGND)を分離します。SGNDとPGNDの間に必要な接続点は1つだけになります。SGNDはPGNDプレーン上のクリーンなポイントに帰還させることを推奨します。小信号部品のグラウンドを、PGNDを介してSGNDに帰還させないでください。全てのパワー供給系部品は、PGNDをリファレンスにする必要があります。直接ビアを使用して、電源部品をPGNDに接続します。各電源部品に複数のビアが必要です。

- 電源部品( $C_{IN}$ 、 $C_{OUT}$ 、インダクタ、MOSFETなど)は1つの小さな領域にまとめて配置します。この領域の大電流経路( $V_{IN}$ 、 $V_{OUT}$ 、PGNDなど)には、幅が広く、できるだけ短いパターンを使用して、銅損失を最小限に抑えます。

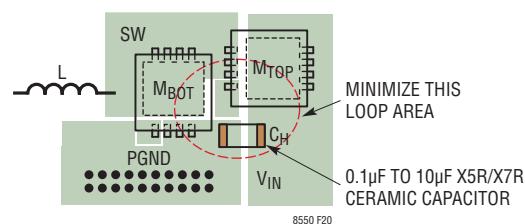

- $BST_x/SW_x$ ノードの電圧は、高いdV/dtレートで振幅します。これらのノード部品は高周波ノイズが多いため、EMIノイズの強力な発生源になります。これらのノードとノイズにセンシティブな他のパターンの間のカップリングを最小限に抑えるため、銅領域は最小限に抑える必要があります。ただし一方では、大きなインダクタ電流を流し、パワーMOSFETを放熱するために、 $SW_x$ ノードにはある程度の実装面積が必要です。通常は $SW_x$ ノードの下にグラウンド銅領域を配置して、シールドを強化することを推奨します。

a) High  $di/dt$  Loop

図20. 回路基板レイアウトの高  $di/dt$  ループ領域を最小限に抑える

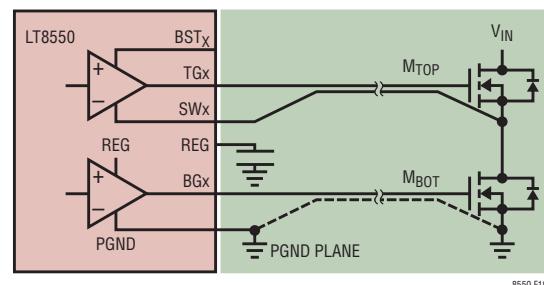

$BST_x/SW_x$ 以外に、 $TG_x$ と $BG_x$ も高  $dV/dt$ 信号であり、ノイズにセンシティブなパターンから離して配線する必要があります。ゲート駆動経路のインピーダンスを最小限に抑えるために、ゲート駆動信号は、幅が広く短いパターンを使って伝達することを強く推奨します。 $TG_x$ と $SW_x$ は最小限のループ領域を使用して一緒に配線し、インダクタンスと高い  $dV/dt$  ノイズを最小限に抑える必要があります。同様に、図19に示すように、 $BG_x$ は PGND のパターンの近くに配線する必要があります。 $TG_x$ 、 $SW_x$ 、 $BG_x$ のパターンはできるだけ1つの層のみに配線してください。

図19. ゲート・ドライバの配線例

- 図20に示すように、上側MOSFET、下側MOSFET、およびセラミック・コンデンサ $C_H$ で構成される高  $di/dt$  ループはできるだけ短くして、パルスを発生するループのインダクタンスを最小限に抑え、スイッチング・ノイズを吸収します。

- REG、V<sub>CC</sub>、V<sub>IN</sub>、および電流検出ピンなどのデカップリング・コンデンサは、それぞれのピンの近くに配置します。REGのデカップリング・コンデンサはPGNDに接続し、V<sub>IN</sub>とV<sub>CC</sub>のデカップリング・コンデンサはSGNDに接続します。接続インピーダンスを最小限に抑えるために、デカップリング・コンデンサは、ビアを使用せずにピンに直接接続することを推奨します。

- 全ての小信号パターンの中で、電流検出パターンは最もノイズにセンシティブです。図21に示すように、電流検

b) Recommended Layout Example

## アプリケーション情報

出パターンは最小限の間隔で差動ペアとして配線し、ノイズを拾う可能性を最小限に抑える必要があります。更に、電流検出パターンのフィルタ抵抗およびコンデンサは、ISPx/ISNxピンのできるだけ近くに配置する必要があります。DCR検出とR/Cネットワークを組み合わせる場合、DCR検出抵抗R1はインダクタの近くに配置し、R2とCはLT8550の近くに配置する必要があります。

図21に示すように、ISPx/ISNxラインを接続するビアは、電流検出抵抗またはインダクタの端子に直接接続します。

- マスタLT8550、プライマリ・コントローラ、スレーブLT8550間のインターフェース信号を配線する際は、小信号ラインはノイズの多いラインから離して配線し、グラウンド・プレーンでシールドします。信号線の推奨配置を図22に示します。

図21. 電流検出用の回路基板設計

図22. 回路基板上の信号線の推奨配置

## 代表的なアプリケーション

5フェーズ6V/100A降圧エクスパンダ

L0-L4: WURTH ELEKTRONIK 7443551130

M1-M10: INFINEON BSC093N04LSG

C<sub>IN0</sub>, C<sub>IN2</sub>, C<sub>IN4</sub>, C<sub>IN6</sub>, C<sub>IN8</sub>: PANASONIC EEHZAH101P

C<sub>IN1</sub>, C<sub>IN3</sub>, C<sub>IN5</sub>, C<sub>IN7</sub>, C<sub>IN9</sub>: TDK C3225X7R1H106M250AC

C<sub>OUT0</sub>, C<sub>OUT2</sub>, C<sub>OUT4</sub>, C<sub>OUT6</sub>, C<sub>OUT8</sub>: PANASONIC 16TQC150MYF

C<sub>OUT1</sub>, C<sub>OUT3</sub>, C<sub>OUT5</sub>, C<sub>OUT7</sub>, C<sub>OUT9</sub>: TDK C3216X7R1V106K160AC

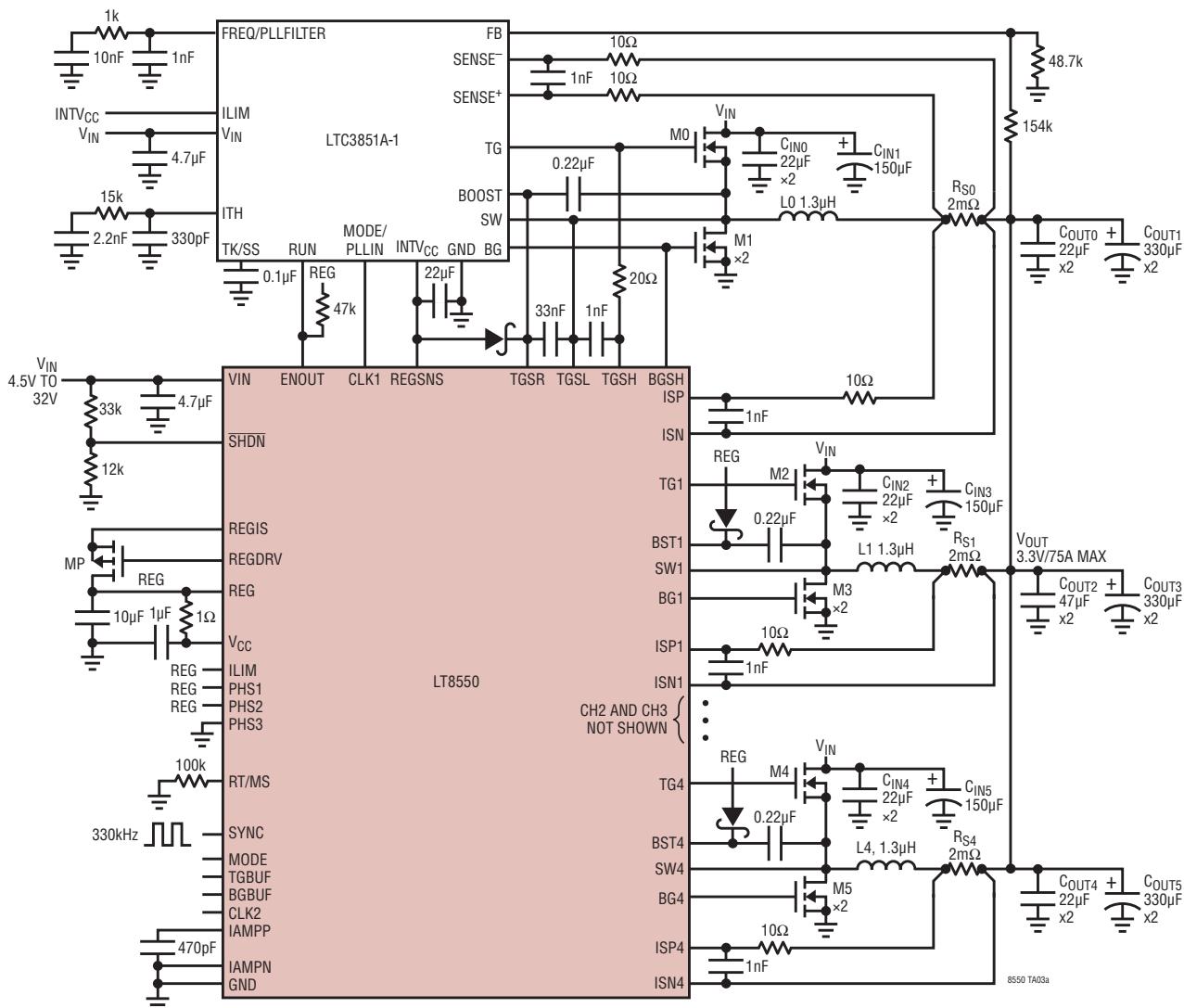

## 代表的なアプリケーション

## 5フェーズ3.3V/75A降圧エクスパンダ・システム

L1-L4: WURTH ELEKTRONIK 7443556130

M1-M6: INFINEON BSC093N04LSG

C<sub>IN0</sub>: C<sub>IN2</sub>: C<sub>IN4</sub>: TDK C4532X7R1E226M250KC

C<sub>IN1</sub>: C<sub>IN3</sub>: C<sub>IN5</sub>: PANASONIC EEUF1V151

C<sub>OUT0</sub>: C<sub>OUT2</sub>: C<sub>OUT4</sub>: TDK C3216JB1E476M160AC

C<sub>OUT1</sub>: C<sub>OUT3</sub>: C<sub>OUT5</sub>: PANASONIC EEUFM1E331

R<sub>S0</sub>-R<sub>S4</sub>: PANASONIC ERJMP3PF2MOU

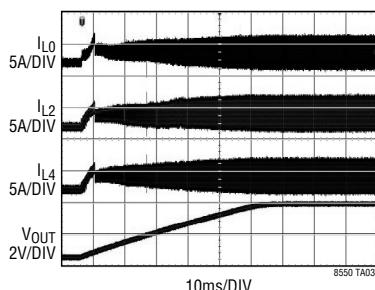

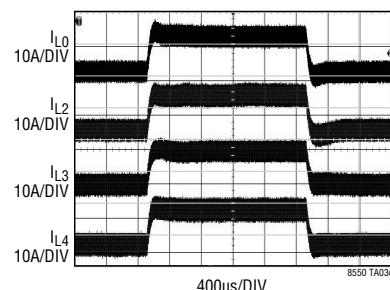

負荷電流10Aでの起動波形

20Aから70Aの出力負荷ステップに対する過渡応答

## 代表的なアプリケーション

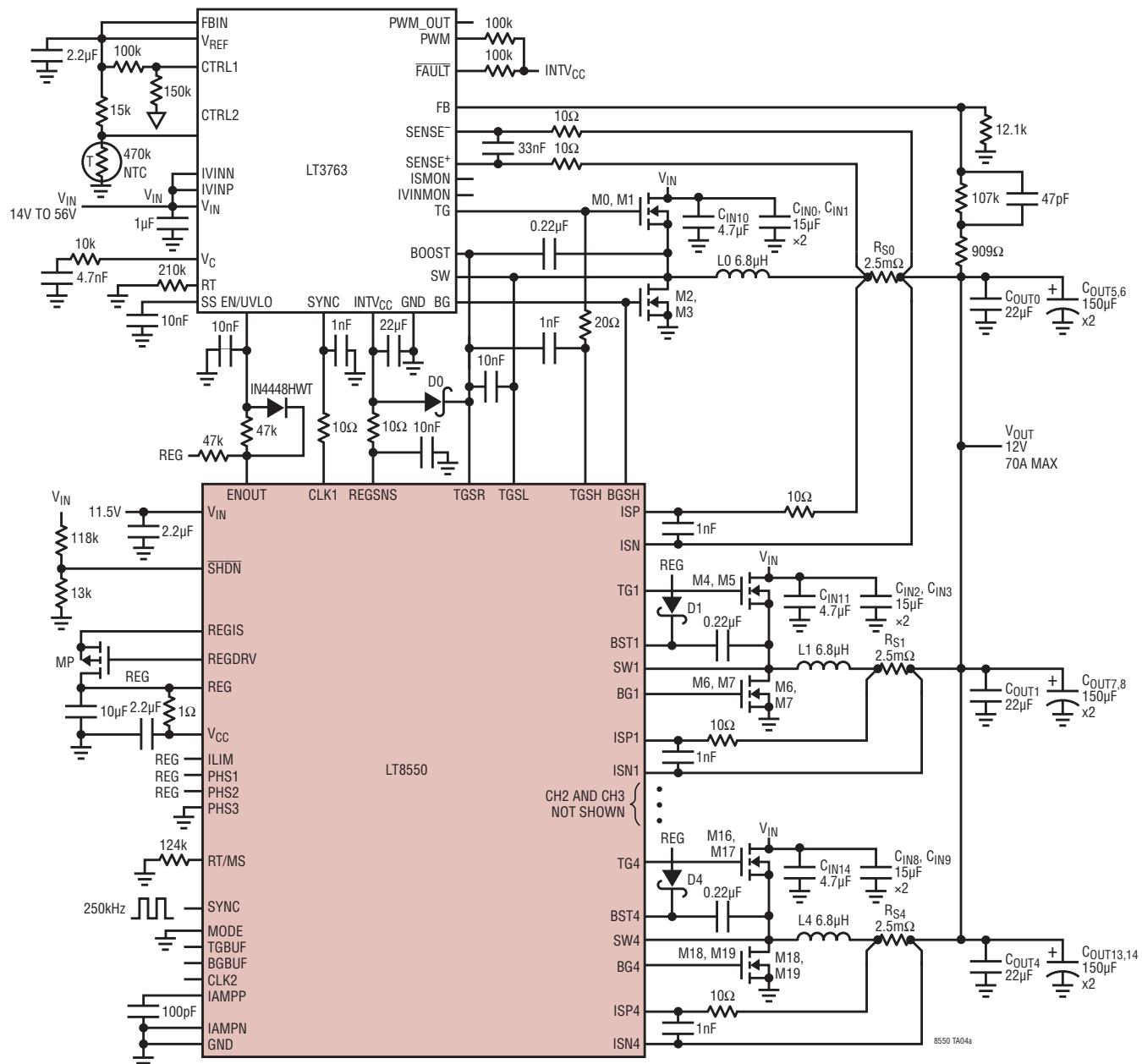

## 5フェーズ12V/70A降圧エクスパンダ・システム

L0-L4: COILCRAFT SER2915L-682KL

M0-M19: INFINEON BSC100N06LS3

MP: ZETEX ZXMP10A18G

C<sub>IN0</sub>-C<sub>IN9</sub>: MURATA KRM55WR72A156MH01K

C<sub>IN10</sub>-C<sub>IN14</sub>: MURATA GRJ32DC72A475KE11L

C<sub>OUT0</sub>-C<sub>OUT4</sub>: MURATA GRM32R71C226MEA8L

C<sub>OUT5</sub>-C<sub>OUT14</sub>: PANASONIC 16SVP150M

R<sub>S0</sub>-R<sub>S4</sub>: PANASONIC ERJMP4PF2M5U

D0-D4: BAT46WJ

## 代表的なアプリケーション

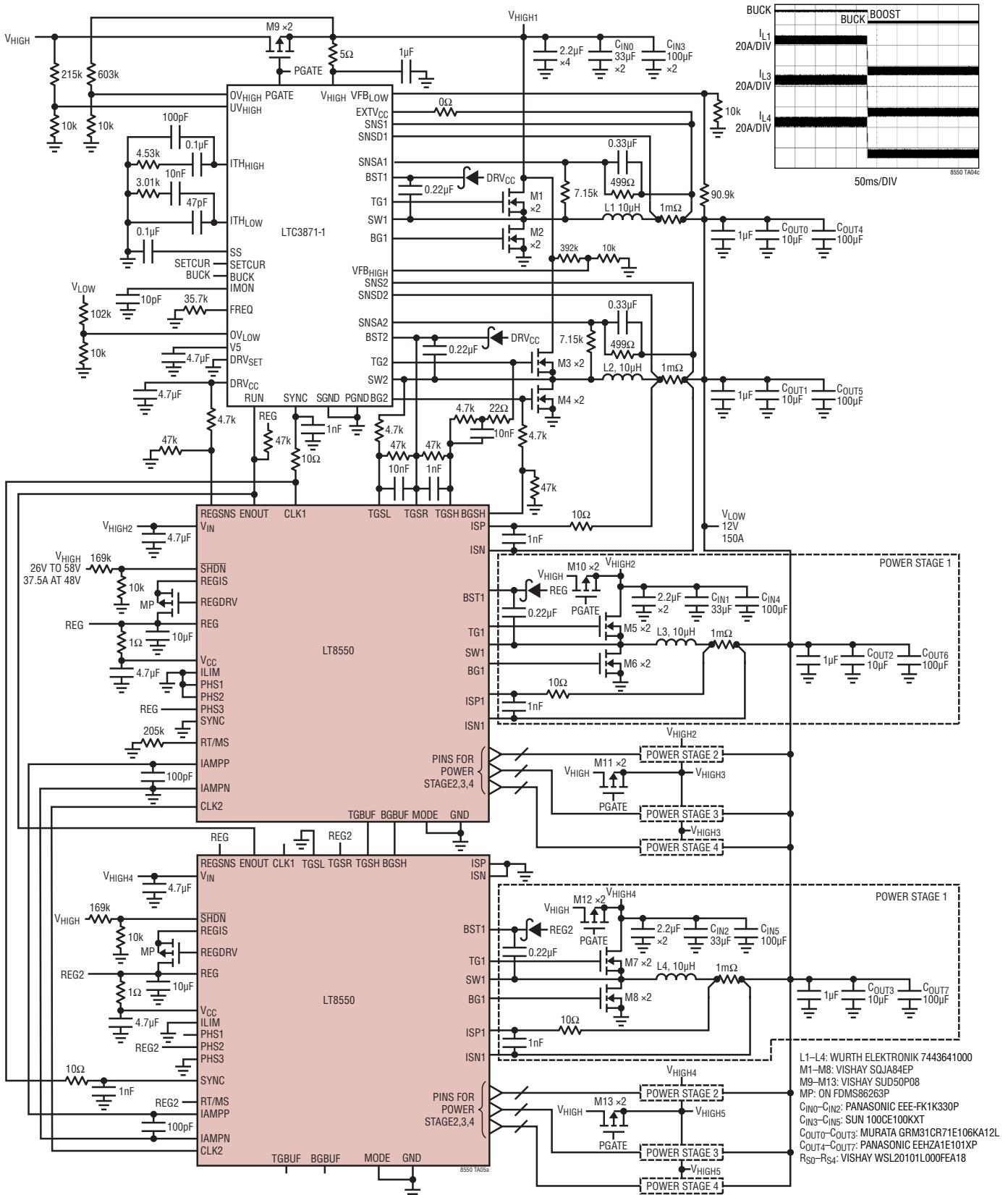

#### 10フェーズ双方向エクスパンダ・システム

降圧から昇圧への切り替え

(1フェーズあたり15A)

## パッケージ

## 代表的なアプリケーション

## 5フェーズ 5V/100A 降圧フェーズ・エクスパンダ・システム

## 関連製品

| 製品番号             | 説明                                                | 注釈                                                                                                                       |

|------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| LT3741           | 大電力、定電流、定電圧、降圧コントローラ                              | 固定動作周波数: 200kHz~1MHz、電流レギュレーション: ±6%、6V ≤ V <sub>IN</sub> ≤ 36V、V <sub>OUT</sub> : 最大で (V <sub>IN</sub> - 2V)            |

| LTC3851A-1       | RSENSE™不要、広いV <sub>IN</sub> 範囲の同期整流式降圧DC/DCコントローラ | 位相同期可能な固定周波数: 250kHz~750kHz、4V ≤ V <sub>IN</sub> ≤ 38V、0.8V ≤ V <sub>OUT</sub> ≤ 5.25V、MSOP-16E、3mm × 3mm QFN-16、SSOP-16 |

| LT3763           | 60V大電流降圧LEDドライバ・コントローラ                            | 固定動作周波数: 200kHz~1MHz、電流レギュレーション: ±6%、電圧レギュレーション精度: ±1.5%、6V ≤ V <sub>IN</sub> ≤ 60V、V <sub>OUT</sub> : 最大 55V            |

| LTC3871          | 双方向PolyPhase®同期整流式降圧／昇圧コントローラ                     | 位相同期可能な固定動作周波数: 60kHz~460kHz、最大効率: 97%、V <sub>HIGH</sub> : 最大 100V、V <sub>LOW</sub> : 最大 30V、電圧レギュレーション精度: 全温度範囲で ±1.5%  |

| LTC7801/ LTC3895 | 低静止電流の150V、同期整流式降圧DC/DCコントローラ                     | 広い入力電圧範囲: 4V~140V、広い出力電圧範囲: 0.8V~60V、24ピン 4mm × 5mm QFN、TSSOP-24、TSSOP-38(31)                                            |