# LTPoE++/IEEE 802.3bt PD インターフェース・コントローラ

## 特長

- LTPoE++®/IEEE 802.3bt 受電デバイス(PD)コントローラ

- 最大 90W の PD をサポート

- LTPoE++ PSE と IEEE 802.3bt PSE を識別

- 5 イベントの分類検出

- 優れたサージ保護(絶対最大定格: 100V)

- 広いジャンクション温度範囲(-40°C ~ 125°C)

- 過熱保護

- シグネチャ抵抗を内蔵

- ホット・スワップ用の N チャンネル MOSFET を外付けすることにより、最小の消費電力および最高のシステム効率を達成

- 最小 9V の構成可能な補助電源をサポート

- LT4275A/B/C および LT4294 とピン互換

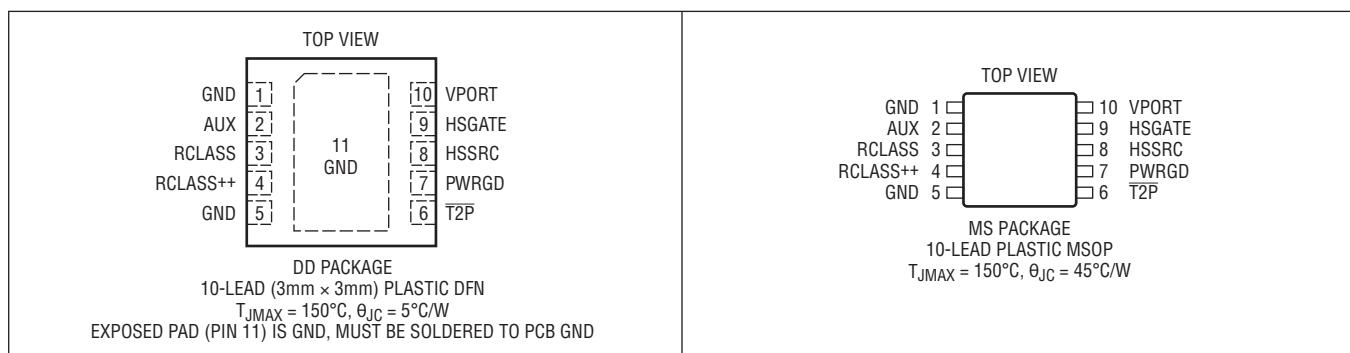

- 10 ピン MSOP パッケージおよび 3mm × 3mm DFN パッケージで供給可能

## アプリケーション

- 高出力の無線データ・システム

- 屋外防犯カメラ装置

- 商用情報および公開情報の表示装置

- 高温での産業用機器アプリケーション

## 概要

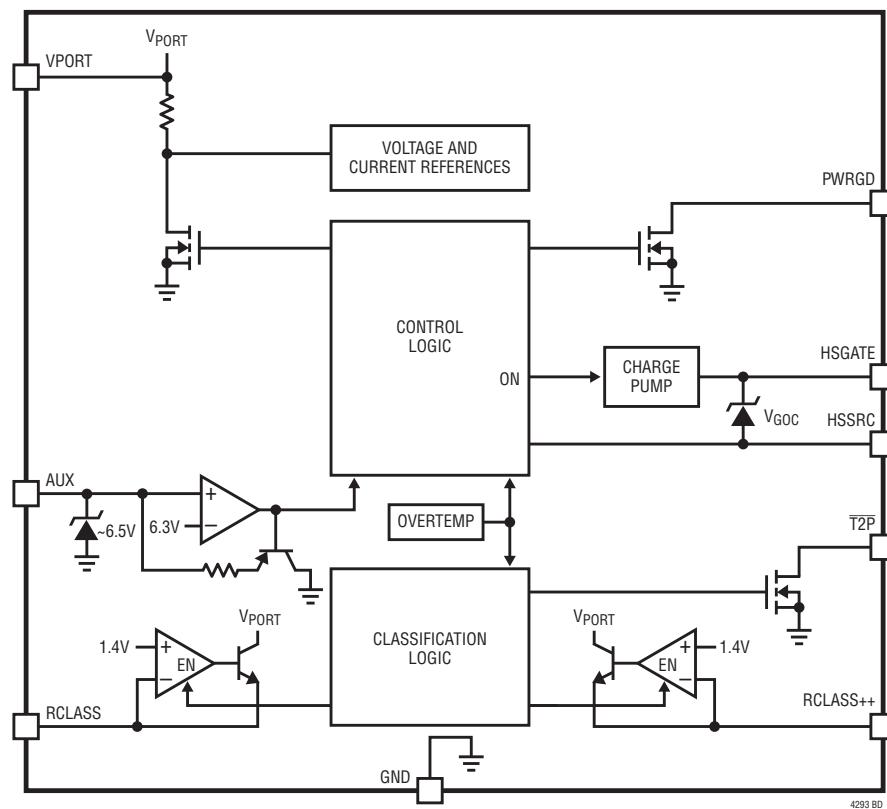

LT<sup>®</sup>4293 は、LTPoE++/IEEE 802.3af/at/bt 準拠の受電デバイス(PD)インターフェース・コントローラです。T2P 出力は、相互識別時および供給可能な電力のネゴシエーション時に、LTPoE++ と IEEE 802.3bt の 2 種類の給電デバイス(PSE)を識別します。

LT4293 は、低 R<sub>DSON</sub> の外付け N チャンネル、ホット・スワップ MOSFET を使用し、LT4320/LT4321 理想ダイオード・ブリッジをサポートして、エンド-to-エンド の電力供給効率を高め、高価なヒートシンクの必要性をなくします。LT4293 には、パワーグッド出力、シグネチャ抵抗、低電圧ロックアウト回路、および熱保護回路も内蔵されています。起動時の突入電流は外付けコンデンサで調整可能です。AUX ピンにより、補助電源の変更機能が最小 9V までサポートされています。

LT4293 は、外付け部品の変更により、LTPoE++、802.3bt、802.3at、および 802.3af の可能な全ての電力レベルをサポートするように構成できます。PD インターフェース・コントローラの LT4275 および LT4294 ファミリとピン互換なので、LTPoE++ PD から IEEE 802.3bt 準拠の PD へ容易に移行することができます。

全ての登録商標および商標の所有権は、それぞれの所有者に帰属します。

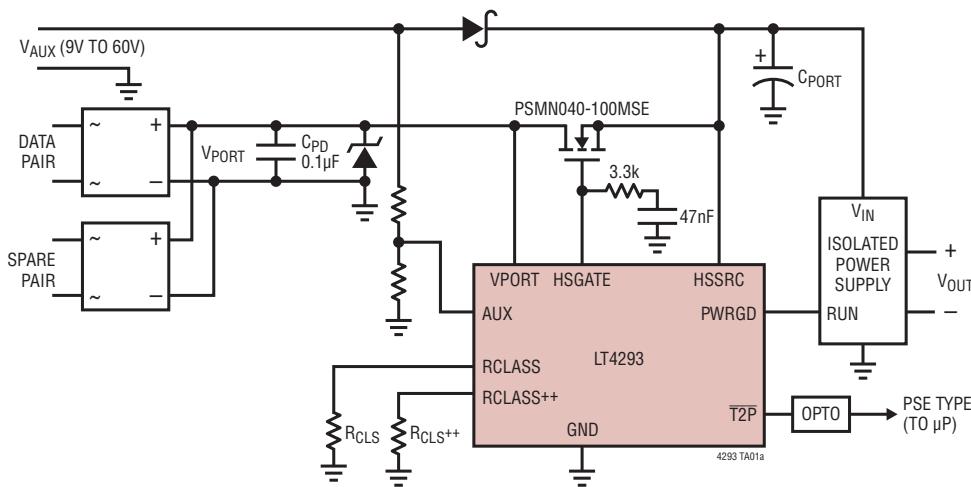

## 標準的応用例

LTPoE++/IEEE 802.3bt シングル・シグネチャ受電デバイス・インターフェース

| クラス | シングル・シグネチャの電力分類(PD 入力基準) |              |

|-----|--------------------------|--------------|

|     | LTPoE++                  | IEEE 802.3bt |

| 0   | 13W                      | 13W          |

| 1   | 3.84W                    | 3.84W        |

| 2   | 6.49W                    | 6.49W        |

| 3   | 13W                      | 13W          |

| 4   | 25.5W                    | 25.5W        |

| 5   | 38.7W                    | 40W          |

| 6   | 52.7W                    | 51W          |

| 7   | 70W                      | 62W          |

| 8   | 90W                      | 71.3W        |

## 絶対最大定格

(Notes 1, 3)

|                     |                           |

|---------------------|---------------------------|

| VPORT、HSSRCの電圧      | -0.3V~100V                |

| HSGATEの電流           | ±20mA                     |

| RCLASS、RCLASS++ の電圧 | -0.3V~8V(かつ $\leq$ VPORT) |

| AUX の電流             | ±1.4mA                    |

| T2P、PWRGD の電圧       | -0.3V~100V                |

| T2P、PWRGD の電流       | 5mA                       |

動作ジャンクション温度範囲 (Note 4)

LT4293I ..... -40°C~85°C

LT4293H ..... -40°C~125°C

保存温度範囲 ..... -65°C~150°C

ピン温度

(ハンダ処理、10秒) ..... 300°C (MSOPのみ)

## ピン配置

## 発注情報

| チューブ          | テープ&リール         | 製品マーキング* | パッケージ                           | 温度範囲           |

|---------------|-----------------|----------|---------------------------------|----------------|

| LT4293IDD#PBF | LT4293IDD#TRPBF | LHJX     | 10-Lead (3mm x 3mm) Plastic DFN | -40°C to 85°C  |

| LT4293HDD#PBF | LT4293HDD#TRPBF | LHJX     | 10-Lead (3mm x 3mm) Plastic DFN | -40°C to 125°C |

| LT4293IMS#PBF | LT4293IMS#TRPBF | LTHJY    | 10-Lead Plastic MSOP            | -40°C to 85°C  |

| LT4293HMS#PBF | LT4293HMS#TRPBF | LTHJY    | 10-Lead Plastic MSOP            | -40°C to 125°C |

更に広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\*温度グレードは出荷時のコンテナのラベルで識別されます。

**テープ&リールの仕様。**一部のパッケージは、#TRMPBF接尾部の付いた指定の販売経路を通じて500個入りのリールで供給可能です。

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値 (Note 3)。

| SYMBOL      | PARAMETER                         | CONDITIONS                            | MIN | TYP  | MAX | UNITS |

|-------------|-----------------------------------|---------------------------------------|-----|------|-----|-------|

|             | VPORT Operating Input Voltage     | At VPORT Pin                          | ●   |      | 60  | V     |

| $V_{SIG}$   | VPORT Signature Range             | At VPORT Pin                          | ●   | 1.5  | 10  | V     |

| $V_{CLASS}$ | VPORT Classification Range        | At VPORT Pin                          | ●   | 12.5 | 21  | V     |

| $V_{MARK}$  | VPORT Mark Range                  | At VPORT Pin, Preceded by $V_{CLASS}$ | ●   | 5.6  | 10  | V     |

|             | VPORT Aux Mode Range              | At VPORT Pin, $AUX > V_{AUXT}$        | ●   | 8    | 60  | V     |

|             | Signature/Class Hysteresis Window |                                       | ●   | 1.0  |     | V     |

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値 (Note 3)。

| SYMBOL      | PARAMETER                         | CONDITIONS                            | MIN   | TYP | MAX | UNITS |

|-------------|-----------------------------------|---------------------------------------|-------|-----|-----|-------|

| $V_{RESET}$ | Reset Threshold                   | At VPORT Pin, Preceded by $V_{CLASS}$ | ● 2.6 |     | 5.6 | V     |

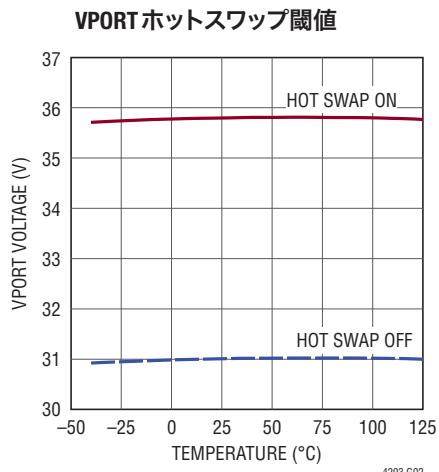

| $V_{HSON}$  | Hot Swap Turn-On Voltage          |                                       | ●     | 35  | 37  | V     |

| $V_{HSOFF}$ | Hot Swap Turn-Off Voltage         |                                       | ● 30  | 31  |     | V     |

|             | Hot Swap On/Off Hysteresis Window |                                       | ● 3   |     |     | V     |

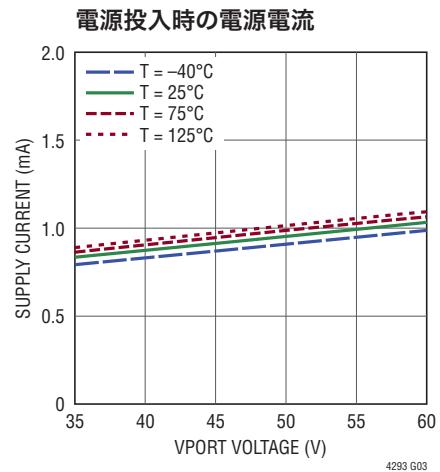

### 電源電流

|                                      |                                                       |       |     |     |    |

|--------------------------------------|-------------------------------------------------------|-------|-----|-----|----|

| Supply Current                       | $V_{VPORT} = V_{HSSRC} = 57\text{V}$                  | ●     | 2   | mA  |    |

| Supply Current During Classification | $V_{VPORT} = 17.5\text{V}$ , RCLASS and RCLASS++ Open | ● 0.4 | 0.7 | 0.9 | mA |

| Supply Current During Mark Event     | $V_{VPORT} = V_{MARK}$ After 1st Classification Event | ● 0.5 | 2.2 |     | mA |

### 検出シグネチャと分類シグネチャ

|                                         |                                                                            |        |      |      |            |

|-----------------------------------------|----------------------------------------------------------------------------|--------|------|------|------------|

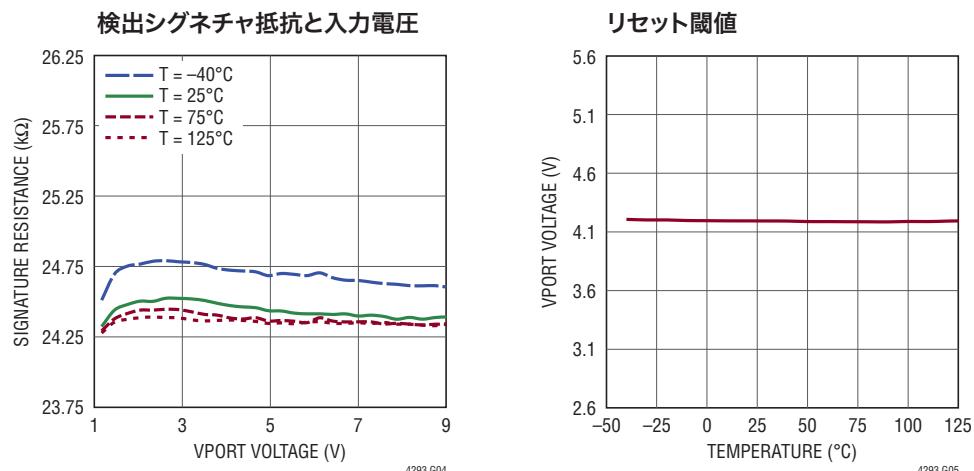

| Detection Signature Resistance          | $V_{SIG}$ (Note 2)                                                         | ● 23.7 | 24.4 | 25.2 | k $\Omega$ |

| Resistance During Mark Event            | $V_{MARK}$ (Note 2)                                                        | ● 5.8  | 8.3  | 11   | k $\Omega$ |

| RCLASS/RCLASS++ Operating Voltage       | $-10\text{mA} \geq I_{RCLASS} \geq -36\text{mA}$ , $V_{CLASS}$             | ● 1.32 | 1.40 | 1.43 | V          |

| Classification Signature Stability Time | $V_{VPORT}$ Step to 17.5V,<br>34.8 $\Omega$ from RCLASS or RCLASS++ to GND | ●      |      | 2    | ms         |

### アナログ／デジタル・インターフェース

|                       |                            |                         |       |     |     |               |

|-----------------------|----------------------------|-------------------------|-------|-----|-----|---------------|

| $V_{AUXT}$            | AUX Threshold              |                         | ● 6.1 | 6.3 | 6.5 | V             |

| $I_{AUXH}$            | AUX Pin Hysteresis Current | $V_{AUX} = 6.1\text{V}$ | ● 3.2 | 5   | 7   | $\mu\text{A}$ |

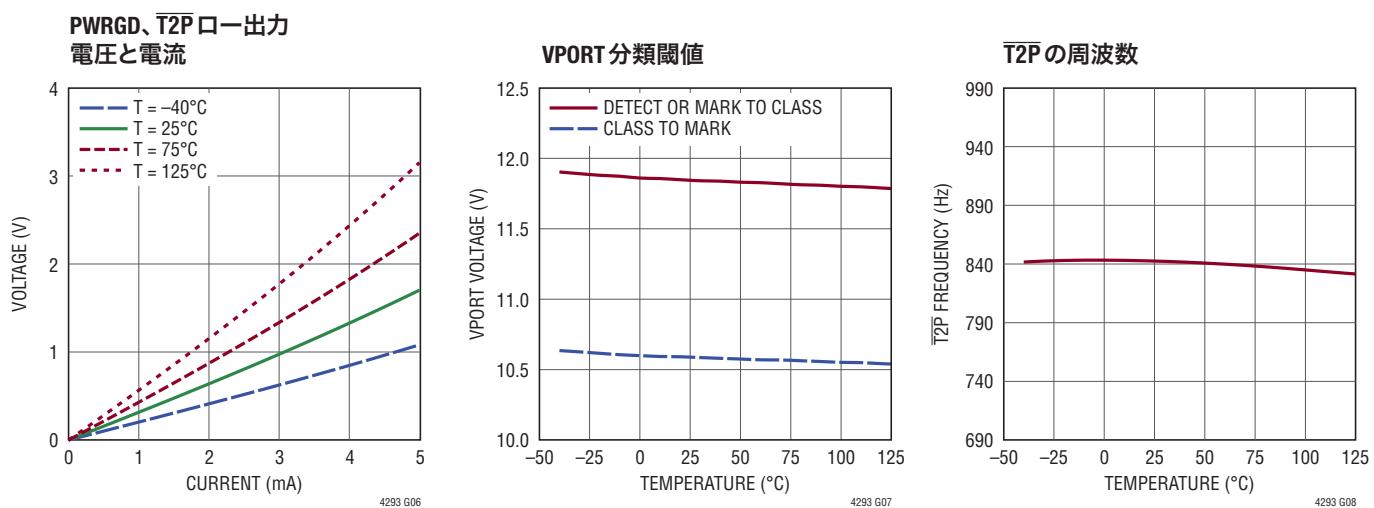

| $T2P$ Output Low      | 1mA Load                   |                         | ●     |     | 0.8 | V             |

| PWRGD Output Low      | 1mA Load                   |                         | ●     |     | 0.8 | V             |

| PWRGD Leakage Current | $V_{PWRGD} = 60\text{V}$   | ●                       |       | 5   |     | $\mu\text{A}$ |

| $T2P$ Leakage Current | $T2P = 60\text{V}$         | ●                       |       | 5   |     | $\mu\text{A}$ |

### 活線挿抜制御

|           |                             |                                               |       |     |     |               |

|-----------|-----------------------------|-----------------------------------------------|-------|-----|-----|---------------|

| $I_{GPU}$ | HSGATE Pull-Up Current      | $V_{HSGATE} - V_{HSSRC} = 5\text{V}$ (Note 6) | ● -27 | -22 | -18 | $\mu\text{A}$ |

| $V_{GOC}$ | HSGATE Open Circuit Voltage | -10 $\mu\text{A}$ Load, with Respect to HSSRC | ● 10  |     | 18  | V             |

|           | HSGATE Pull-Down Current    | $V_{HSGATE} - V_{HSSRC} = 5\text{V}$          | ● 200 |     |     | $\mu\text{A}$ |

### タイミング

|                                                       |                                                                                                                                        |       |     |     |    |

|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-----|----|

| T2Pの周波数                                               | $V_{AUX} > V_{AUXT}$ , and RCLASS++ Has Resistor to GND                                                                                | ● 690 | 840 | 990 | Hz |

| T2P Duty Cycle in PoE Operation (Note 5)              | After LTPoE++ 3-Event Classification<br>After 4-Event Classification<br>After 5-Event Classification<br>(RCLASS++ Has Resistor to GND) |       | 75  | 50  | 25 |

| T2P Duty Cycle in Auxiliary Supply Operation (Note 5) | $V_{AUX} > V_{AUXT}$ , and RCLASS++ Has Resistor to GND                                                                                |       | 75  |     | %  |

| 1st Classification Event Timing Threshold             |                                                                                                                                        | ● 31  | 87  |     | ms |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。また、長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える恐れがある。

**Note 2:** シグネチャ抵抗の仕様には、ポート抵抗を最大1.1k增加させる可能性がある外付けダイオード・ブリッジの抵抗が含まれていない。

**Note 3:** 全ての電圧値は(注記がない限り)GNDを基準にしている。注記がない限り、正電流はピンに流れ込み、負電流はピンから流れ出す。

**Note 4:** このデバイスには、短時間の過負荷状態の間デバイスを保護するための過熱保護機能が備わっている。過熱保護機能がアクティブなときジャンクション温度は150°Cを超える。規定された最大動作ジャンクション温度を超えた状態で動作が継続すると、デバイスの信頼性を損なう可能性がある。

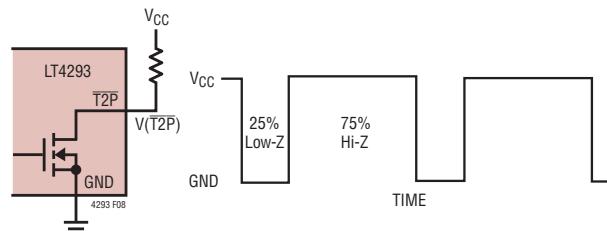

**Note 5:** T2PがGNDに対して低インピーダンスである時間の割合(%)として規定されている。PWRGDが有効になった後に現れる。

**Note 6:** PoE受電動作時に流れる  $I_{GPU}$  つまり、 $V_{VPORT}$  が  $V_{HSOFF} \sim 60\text{V}$  の範囲で、 $V_{VPORT} > V_{HSOFF}$ かつ  $V_{AUX} < V_{AUXT}$  となった後に流れる電流。

## 代表的な性能特性

## ピン機能

**GND(ピン1、5、DFN露出パッドのピン11)**: デバイスのグラウンド。露出パッドは、ピン5、およびPCBのGNDに電気的および熱的に接続する必要があります。

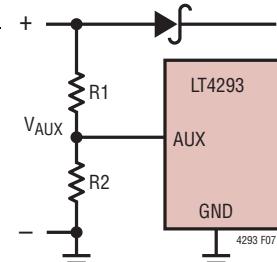

**AUX(ピン2)**: 補助検出ピン。補助電源入力とAUXの間に抵抗分割器を接続して、補助電源が引き継ぐ電圧を設定します。補助電源の動作時は、HSGATEの電圧が低下し、シグネチャ抵抗が切り離され、分類が無効になり、PWRGDピンが高インピーダンスになって、T2Pは供給可能な最大電力を示します。AUXピンは、その電圧がスレッショルド電圧 $V_{AUXT}$ より低くなると、 $I_{AUXH}$ が流れ込んでヒステリシス特性を示します。使用しない場合は、GNDに接続します。

**RCLASS(ピン3)**: 構成可能なPoE分類抵抗用のピン。表2を参照してください。

**RCLASS++(ピン4)**: 構成可能なPoE分類抵抗用のピン。表2を参照してください。

**T2P(ピン6)**: PSEのタイプを示すオープンドレイン出力ピン。ピンの動作については、アプリケーション情報のT2P出力のセクションを参照してください。

**PWRGD(ピン7)**: パワーグッド・インジケータ用のオープンドレイン出力ピン。 $V_{CLASS}$ および突入電流モードではGNDまで低下します。

**HSSRC(ピン8)**: ホットスワップ用の外付けMOSFETのソース。外付けMOSFETのソースに接続します。

**HSGATE(ピン9)**: ホットスワップ用の外付けMOSFETのゲート制御、出力。外付けMOSFETのゲートに接続します。

**VPORT(ピン10)**: PDインターフェースの上側電源レールと、ホットスワップ用の外付けMOSFETのドレイン接続。

## ブロック図

## アプリケーション情報

### 概要

Power over Ethernet (PoE) 製品は、RJ45 コネクタ 1 つで、DC 電力と高速のデータという 2 つのメリットを得られることから、ますます普及が進んでいます。しかし、受電 (PD) 装置のベンダの前には、IEEE 802.3at 規格によって設定された、25.5W という電力制限の壁が立ちはだかります。

LT4293 は LTPoE++/IEEE 802.3bt 準拠の PD インターフェース・コントローラであり、最大 90W の動作が可能である上に、既存の PSE システムとの下位互換性を維持しています。T2P 出力は、相互識別時および供給可能な電力のネゴシエーション時に、LTPoE++ と IEEE 802.3bt の 2 種類の給電装置 (PSE) を識別します。LT4293 は、低  $R_{DS(ON)}$  の N チャンネル MOSFET を制御して、効率と供給電力を最大限に高めます。

また、アナログ・デバイセズは、PSE、PD、および理想ダイオード・ブリッジ・ソリューションの全機能内蔵型ファミリも提供しています。このデータシートの巻末に記載している関連製品のセクションを参照してください。

### 動作モード

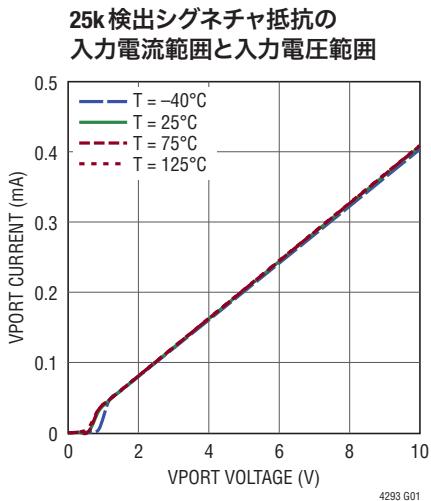

#### 検出シグネチャ

検出モードでは、PSE はデバイスを PD として識別する 25k のシグネチャ抵抗を探します。PSE は 2.7V ~ 10.1V の範囲の 2 つの電圧を印加して、対応する電流を測定します。図 1 に検出電圧を示します。PSE は  $\Delta V/\Delta I$  の測定手法により、シグネチャ抵抗を計算します。

LT4293 は、VPORT と GND ピンの間に温度補償された高精度の  $24.4\text{k}\Omega$  の抵抗値を示すことで、PD が存在して電源印加を要求していることを PSE に認識させます。LT4293 のシグネチャ抵抗は、IEEE が要求するブリッジまたは LT4321 ベースの理想ダイオード・ブリッジによって増加する直列抵抗を補うために、25k よりも小さな値になっています。

#### IEEE 802.3bt のシングル・シグネチャ PD と デュアル・シグネチャ PD

IEEE 802.3bt は、シングル・シグネチャとデュアル・シグネチャという 2 つの PD トポロジを規定しています。LT4293 は主にシングル・シグネチャ PD トポロジを対象にしているので、別

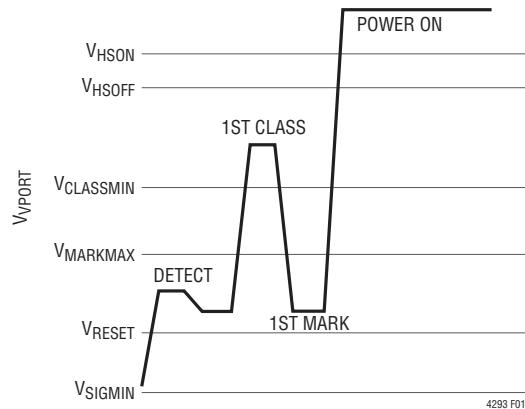

図 1. タイプ 3 またはタイプ 4 PSE、1 イベント・クラスのシーケンス

の PD コントローラは必要ありません。このデータシートでの PD の説明および IEEE 802.3 規格の参考文献は、全てシングル・シグネチャ PD の範囲内に限られます。

LT4293 は、デュアル・シグネチャ PD アプリケーションに採用することもできます。詳細については、弊社にお問い合わせください。

#### 分類シグネチャおよびマーク

分類／マークのプロセスは、PSE のタイプによって異なります。PSE は、検出に成功すると、14.5V ~ 20.5V の分類プローブ電圧を印加して、PD 分類シグネチャ電流を測定します。PSE は、いったん分類プローブ電圧を印加すると、PD の電圧をマーク電圧の範囲内に戻してから、別の分類プローブ電圧を印加するか、または PD に電力を供給します。

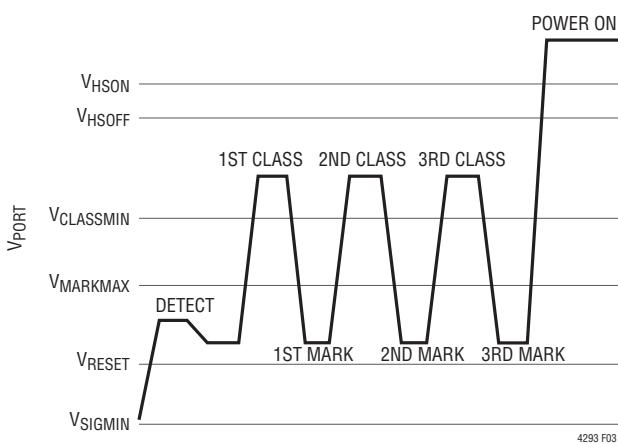

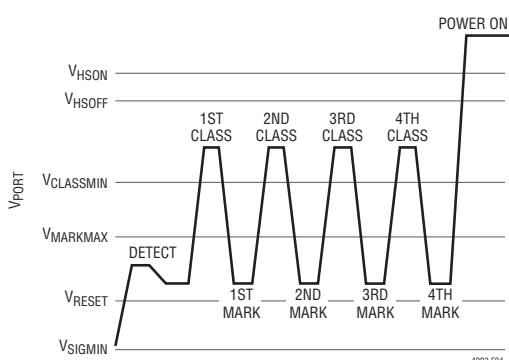

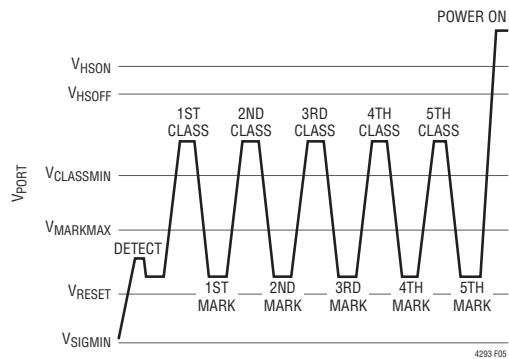

1 イベント分類の一例を図 1 に示します。2 イベント分類では、PSE は、図 2 に示すように電力分類のプロービングを 2 回行います。IEEE 802.3bt PSE は、PD に電力を供給する前に、最大で 5 つのイベントを適用することができます。

#### IEEE 802.3bt の物理的な分類と格下げ

IEEE 802.3bt は、物理的な分類を定義して、PD がその電力割り当て量を接続先の PSE から要求し、PSE がその供給可能電力を PD に通知することができます。PD の要求電力レベルを PSE が供給できない場合は、格下げが行われます。格下げされると、PD はより低い電力状態で動作する必要があります。

## アプリケーション情報

図2. タイプ2 PSE、2イベント・クラスのシーケンス

図3. タイプ3またはタイプ4 PSE、3イベント・クラスのシーケンス

PSEが発行した分類／マークのイベント数は、PDに割り当てられた電力を端的に示します(表1に要約を示します)。

IEEE 802.3btは、表2に示すように、9つのPDクラスと4つのPDタイプを規定しています。LT4293のクラスは、R<sub>CLS</sub>とR<sub>CLS++</sub>の抵抗値を設定することによって構成されます。

IEEE 802.3bt PSEは、クラス0～3のPDに1つの分類イベント(図1参照)を示します。クラス0～3のPDは、そのクラス・シグネチャをPSEに提示し、十分な電力が得られる場合は電源が投入されます。電力が制限されたIEEE 802.3bt PSEは、クラス4以上のPDをクラス3(13W)に格下げするために、これらのPDに対して1つのイベントを発行することができます。

表1. IEEE 802.3bt PSE割り当て電力

| PD要求クラス | PSEクラス/マークのイベント数 |       |       |       |       |

|---------|------------------|-------|-------|-------|-------|

|         | 1                | 2     | 3     | 4     | 5     |

| 0       |                  |       |       | 13W   |       |

| 1       |                  |       |       | 3.84W |       |

| 2       |                  |       |       | 6.49W |       |

| 3       |                  |       |       | 13W   |       |

| 4       | 13W              |       |       | 25.5W |       |

| 5       | 13W              |       | 25.5W |       | 40W   |

| 6       | 13W              | 25.5W |       |       | 51W   |

| 7       | 13W              | 25.5W | 51W   |       | 62W   |

| 8       | 13W              | 25.5W | 51W   | 51W   | 71.3W |

注記: 太字はPDが格下げされていることを示す。

表2. LTPoE++/IEEE802.3btシングル・シグネチャ分類、電力レベル、および抵抗の選択

| PD要求クラス            | PDの要求電力<br>LTPoE++/IEEE802.3bt | PDタイプ<br>LTPoE++/IEEE802.3bt | クラスの公称電流    | 抵抗(1%)           |                    |

|--------------------|--------------------------------|------------------------------|-------------|------------------|--------------------|

|                    |                                |                              |             | R <sub>CLS</sub> | R <sub>CLS++</sub> |

| 0                  | 13W                            | Type 1                       | 2.5mA       | 1.00kΩ           | Open               |

| 1                  | 3.84W                          | Type 1 or 3                  | 10.5mA      | 140Ω             | Open               |

| 2                  | 6.49W                          | Type 1 or 3                  | 18.5mA      | 76.8Ω            | Open               |

| 3                  | 13W                            | Type 1 or 3                  | 28mA        | 49.9Ω            | Open               |

| 4                  | 25.5W                          | Type 2 or 3                  | 40mA        | 34.8Ω            | Open               |

| LTPoE++ 38.7W or 5 | 38.7W                          | 40W                          | 40mA/2.5mA  | 1.00kΩ           | 37.4Ω              |

| LTPoE++ 52.7W or 6 | 52.7W                          | 51W                          | 40mA/10.5mA | 140Ω             | 46.4Ω              |

| LTPoE++ 70W or 7   | 70W                            | 62W                          | 40mA/18.5mA | 76.8Ω            | 64.9Ω              |

| LTPoE++ 90W or 8   | 90W                            | 71.3W                        | 40mA/28mA   | 49.9Ω            | 118Ω               |

## アプリケーション情報

IEEE 802.3bt PSEは、クラス4のPDに対して最大3つの分類イベントを示します(図3参照)。クラス4のPDは、全てのイベントにクラス・シグネチャ4を示します。第3のイベントにより、クラス4のPDは上位クラスのPDと区別されます。電力が制限されたIEEE 802.3bt PSEは、クラス5以上のPDをクラス4(25.5W)に格下げするために、これらのPDに対して3つのイベントを発行することができます。

IEEE 802.3bt PSEは、クラス5および6のPDに4つの分類イベント(図4参照)を示します。クラス5および6のPDは、最初の2つのイベントでクラス・シグネチャ4を示し、残りのイベントでそれぞれクラス・シグネチャ0または1を示します。電力が制限されたIEEE 802.3bt PSEは、クラス7以上のPDをクラス6(51W)に格下げするために、これらのPDに対して4つのイベントを発行することができます。

IEEE 802.3bt PSEは、クラス7および8のPDに5つの分類イベント(図5参照)を示します。クラス7および8のPDは、最初の2つのイベントでクラス・シグネチャ4を示し、残りのイベントでそれぞれクラス・シグネチャ2または3を示します。

図4. タイプ3またはタイプ4 PSE、4イベント・クラスのシーケンス

図5. タイプ4 PSE、5イベント・クラスのシーケンス

クラス／マークのイベント数は、LT4293のT2Pピンを介して伝達されます。詳細については、T2P出力のセクションを参照してください。

### LTPoE++の格下げと拒否

PDの要求電力がPSEの供給可能電力を超えると、LTPoE++ PSEとIEEE 802.3 PSEは、両方とも、PDをより低い電力状態に格下げすることができます。更に、電力が制限されたLTPoE++ PSEは、クラス6以上を要求するPDへの電力を拒否することができます。受け取ったクラス／マーク・イベント数が2以下の場合、PDが割り当てた電力は25.5W以下であり、表5に示すように、LTPoE++ PSEはIEEE 802.3 PSEと同等であるとみなされます。

表3. LTPoE++ PSE割り当て電力

| PD要求クラス | PSEクラス／マークのイベント数 |       |       |

|---------|------------------|-------|-------|

|         | 1                | 2     | 3     |

| 0       |                  | 13W   |       |

| 1       |                  | 3.84W |       |

| 2       |                  | 6.49W |       |

| 3       |                  | 13W   |       |

| 4       | 13W              |       | 25.5W |

| 5       | 13W              | 25.5W | 38.7W |

| 6       | 13W              | 25.5W | 52.7W |

| 7       | 13W              | 25.5W | 70W   |

| 8       | 13W              | 25.5W | 90W   |

注記:太字はPDが格下げされていることを示す。

### 分類抵抗(RCLS および RCLS++)

抵抗RCLSおよびRCLS++は、PDの電力分類に対応した分類電流を設定します。RCLSおよびRCLS++を表2から選択し、RCLASSピン、RCLASS++ピンとGNDの間に許容誤差1%の抵抗をそれぞれ接続します。

### マーク・イベント時の検出シグネチャ波形の乱れ

マーク・イベント時に、LT4293は、LTPoE++/IEEE 802.3規格で要求されているように、ポートに対して11kΩより低い値を示します。

### 突入電流および電源投入

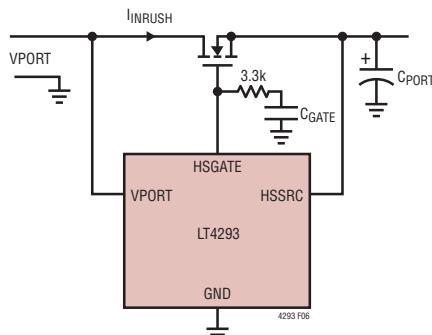

PSEは、検出およびPDの分類が完了すると、PDに電源を投入します。ポート電圧がVHSONの閾値を超えると、HSGATEピンからIGPUを供給はじめます。この電流は外付けコン

## アプリケーション情報

デンサ(図6のC<sub>GATE</sub>)に流れ込み、外付けMOSFETのゲート電圧を高くする電圧を発生します。外付けのMOSFETはソース・フォロワとして機能し、出力バルク・コンデンサC<sub>PORT</sub>の電圧を上昇させてるので、これによって突入電流I<sub>INRUSH</sub>が決まります。I<sub>INRUSH</sub>が約100mAになるように設計します。次式を参照してください。

$$I_{INRUSH} = I_{GPU} \cdot \frac{C_{PORT}}{C_{GATE}}$$

図6. INRUSHの設定

LT4293では、内蔵のチャージ・ポンプによってNチャンネルMOSFETによる解決策を実現できるので、より大型で高価なPチャンネルMOSFETを使用せずに済みます。 $R_{DS(ON)}$ の低いMOSFETにより、電力供給と電力効率が最高になり、消費電力と熱放散が減少して、熱設計が容易になります。

パワーグッド

PWRGD ピンは、HSGATE が HSSRC より約 7V 高い電圧に充電されるまで、オープンドレイン出力によって Low に保持されます。PWRGD ピンは、突入電流が流れ終わって外付け MOSFET が完全にオンするまで、下流の回路をオフ状態に維持するために使用します。HSGATE ピンはハイのままであり、ポートの電圧が  $V_{HSOFF}$  より低くなるまで PWRGD ピンはオープンドレイン状態が維持されます。

遅延後の起動

PSEがポートの電源を投入する場合、PDアプリケーションはIEEE 802.3規格に準拠するため、80msの間350mAを超える電流を流さないようにします。

#### 補助電源への切り換え(オーバーライド)

AUXピンをV<sub>AUXT</sub>より高く保持すると、LT4293は補助電源オーバーライド・モードに移行します。このモードでは、シグネチャ抵抗が切り離され、分類が無効になり、HSGATEは電圧が低下し、PWRGDピンはオープンドレインになって、T2<sub>P</sub>ピンは供給可能な最大電力を示します。

AUXピンによって、補助電源のターンオン電圧閾値( $V_{AUXON}$ )とターンオフ電圧閾値( $V_{AUXOFF}$ )をそれぞれ設定できます。補助電源のヒステリシス電圧 $V_{AUXHYS}$ はシンク電流 $I_{AUXH}$ を流すことによって発生させます。また、AUXピンの電圧が $V_{AUXT}$ より低い場合に限って有効になります。 $V_{AUXON}$ と $V_{AUXOFF}$ は、図7のR1とR2により、次式に従って設定します。内部の6.5VツエナーによってAUXピンの電圧が制限されることに注意してください。

$$R1 = \frac{V_{AUXON} - V_{AUXOFF}}{I_{AUXH}}$$

$$R2 = \frac{R1}{\left( \frac{V_{AUXOFF}}{V_{AUXT}} - 1 \right)}$$

$$R1 \geq \frac{V_{AUX(MAX)} - V_{AUXT}}{1.4mA}$$

図7. AUXの閾値とヒステリシスの計算

最大1000pFのコンデンサをAUXピンとGNDの間に接続して、ノイズ耐性を改善することができます。VAUXONはVHSOFFより低くする必要があります。

T2P出力

LT4293は、PSEが割り当てた電力をT2Pピンを介してPDアプリケーションに伝達します。T2Pピンの状態は、AUXピン、RCLASS++ピン、および分類イベントの数によって決まります。LT4293は、T2P出力に対して5ステートのエンコーディングを使用します。T2Pの状態と関連のPSE割り当て電力を表4および表5に示します。

表4. 補助電源動作時のT2Pの応答

| PD 要求クラス | T2P*  |

|----------|-------|

| 0 – 4    | Low-Z |

| 5 – 8    | 75%   |

\* $\overline{T2P}$ がGNDに対して低インピーダンスである時間の割合(%)として規定されている。

## アプリケーション情報

表5. PoE動作時のT2Pの応答

| 電源         | クラス/マークのイベント数 | T2P*  | PSE割り当て電力                       |

|------------|---------------|-------|---------------------------------|

| LTPoE++    | 1             | Hi-Z  | Min (PD Requested Power, 13W)   |

|            | 2             | Low-Z | 25.5W                           |

|            | 3             | 75%   | LTPoE++ PD Requested Power      |

| IEEE 802.3 | 1             | Hi-Z  | Min (PD Requested Power, 13W)   |

|            | 2 or 3        | Low-Z | 25.5W                           |

|            | 4             | 50%   | Min (PD Requested Power, 51W)   |

|            | 5             | 25%   | Min (PD Requested Power, 71.3W) |

\*T2PがGNDに対して低インピーダンスである時間の割合(%)として規定されている。

最も優先順位の高い入力はAUXピンです。AUXがアサートされると補助電源状態に入り、デアサートされるとPoE状態に入ります。補助電源状態では、T2Pピンは、PD要求クラスに基づいて、供給可能な最大の電力を示します。補助電源は、少なくともPD要求クラスの電力を供給できる規模のものにする必要があります。

第2に、PD要求クラスとPD要求電力は、RCLASSピンとRCLASS++ピンを使用して設定します。RCLASS++ピンを

図8. Low-Zが25%、Hi-Zが75%の場合の応答例

単独で使用して、表2に示すように、PDクラスが0~4、5~8、LTPoE++のいずれであるかを判別できます。

最後に、表1と表3で説明しているように、PSEによって割り当たされた電力の大きさがPSEタイプと分類イベントの数によって決まります。

### 各種のPSEと補助電源間の相互運用性

表6に、LT4293のT2Pの予想される応答、PSE割り当電力、分類イベントの数を示します。結果は、PD要求クラスと電源(補助電源またはPoE)に応じて変わります。

表6. LT4293の相互運用性(T2Pの応答\*、割り当電力、クラス/マークのイベント数)

| PD要求クラス<br>(要求電力) | PSEのタイプ、クラス(電力)              |                              |                              |                              |                              |                              |                              |                              |                              |                              | 補助電源**                    |

|-------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|---------------------------|

|                   | IEEE 802.3<br>タイプ1           |                              | IEEE 802.3<br>タイプ2           |                              | IEEE 802.3<br>タイプ3           |                              | IEEE 802.3<br>タイプ4           |                              | LTPoE++                      |                              |                           |

|                   | クラス3<br>(13W)                | クラス4<br>(25.5W)              | クラス4<br>(25.5W)              | クラス5<br>(40W)                | クラス6<br>(51W)                | クラス7<br>(62W)                | クラス8<br>(71.3W)              | (38.7W)                      | (52.7W)                      | (70W)                        | (90W)                     |

| クラス0~3<br>(最大13W) | Hi-Z<br>Up to 13W<br>1-Event | Low-Z<br>Aux.Power<br>N/A |

| クラス4<br>(25.5W)   | Hi-Z<br>13W<br>1-Event       | Low-Z<br>25.5W<br>2-Event    | Low-Z<br>25.5W<br>3-Event    | Low-Z<br>25.5W<br>3-Event    | Low-Z<br>25.5W<br>3-Event    | Low-Z<br>25.5W<br>3-Event    | Low-Z<br>25.5W<br>2-Event    | Low-Z<br>25.5W<br>2-Event    | Low-Z<br>25.5W<br>2-Event    | Low-Z<br>25.5W<br>2-Event    | Low-Z<br>Aux.Power<br>N/A |

| クラス5<br>(40W)     | Hi-Z<br>13W<br>1-Event       | Low-Z<br>25.5W<br>2-Event    | Low-Z<br>25.5W<br>3-Event    | 50%<br>40W<br>4-Event        | 50%<br>40W<br>4-Event        | 50%<br>40W<br>4-Event        | 75%<br>38.7W<br>3-Event      | 75%<br>38.7W<br>3-Event      | 75%<br>38.7W<br>3-Event      | 75%<br>38.7W<br>3-Event      | 75%<br>Aux.Power<br>N/A   |

| クラス6<br>(51W)     | Hi-Z<br>13W<br>1-Event       | Low-Z<br>25.5W<br>2-Event    | Low-Z<br>25.5W<br>3-Event    | 50%<br>51W<br>4-Event        | 50%<br>51W<br>4-Event        | 50%<br>DENIED                | 75%<br>52.7W<br>3-Event      | 75%<br>52.7W<br>3-Event      | 75%<br>52.7W<br>3-Event      | 75%<br>52.7W<br>3-Event      | 75%<br>Aux.Power<br>N/A   |

| クラス7<br>(62W)     | Hi-Z<br>13W<br>1-Event       | Low-Z<br>25.5W<br>2-Event    | Low-Z<br>25.5W<br>3-Event    | 50%<br>51W<br>4-Event        | 25%<br>62W<br>5-Event        | DENIED                       | DENIED                       | 75%<br>70W<br>3-Event        | 75%<br>70W<br>3-Event        | 75%<br>70W<br>3-Event        | 75%<br>Aux.Power<br>N/A   |

| クラス8<br>(71.3W)   | Hi-Z<br>13W<br>1-Event       | Low-Z<br>25.5W<br>2-Event    | Low-Z<br>25.5W<br>3-Event    | 50%<br>51W<br>4-Event        | 25%<br>71.3W<br>5-Event      | DENIED                       | DENIED                       | DENIED                       | 75%<br>90W<br>3-Event        | 75%<br>90W<br>3-Event        | 75%<br>Aux.Power<br>N/A   |

↓

|                    |

|--------------------|

| T2Pの応答* →          |

| PSE割り当電力 →         |

| 分類イベントの数 →         |

| 75%<br>90W 3-Event |

Note 1: 青の網掛けはPDが格下げされたか電力を拒否されたことを示す。

\* T2PがGNDに対して低インピーダンスである時間の割合(%)として規定されている。

\*\* 補助電源はPDの要求電力を供給できる規模のものにする必要があります。

## アプリケーション情報

### 過熱保護

IEEE 802.3規格は、PDが0V～57Vの範囲の任意の印加電圧に無期限で耐えることを要求しています。しかし、分類動作モードにおけるLT4293の消費電力は1.5Wに達することがあります。LT4293はIEEE分類の最大時間であってもこの電力を十分に許容することができますが、この状態が異常に長く続ければ過熱状態になります。

LT4293は、瞬間的な過負荷状態の間デバイスを保護するための過熱保護機能を備えています。ジャンクション温度が過熱閾値を超えると、LT4293はHSGATEピンの電圧を引き下げて分類を無効にします。

### 外部インターフェースと部品の選択

#### PoE入力ダイオード・ブリッジ

PDはその入力電圧の極性を補正することが必要です。ブリッジ整流器には、いくつかの異なるオプションがあります。それは、シリコン・ダイオード、ショットキー・ダイオード、および理想ダイオードです。シリコン・ダイオード・ブリッジまたはショットキー・ダイオード・ブリッジを使用する場合は、ダイオードの順方向電圧降下がVPORTピンの電圧に影響します。LT4293は、これらの電圧降下を許容できるように設計されています。電気的特性に示す電圧パラメータは、LT4293のパッケージのピンで規定されていることに注意してください。

シリコン・ダイオード・ブリッジは、供給電力の最大4%を消費します。更に、シリコン・ダイオード・ブリッジは、ペアセット間の不平衡性能が劣っています。シリコン・ダイオード・ブリッジの各分岐はソース電流／戻り電流を分担しており、熱暴走が発生すると、ペアセット間に大きく不適合な電流不平衡が生じる可能性があります。

ショットキー・ダイオードを使用すると、電力損失を低減しつつ順方向電圧を小さくするのに役立ちますが、ショットキー・ダイオード・ブリッジは高温のPDアプリケーションには適さないことがあります。ショットキー・ダイオード・ブリッジには、温度が原因のリーク電流が流れます。リーク電流には電圧依存性があり、測定された検出シグネチャを無効化することができます。更に、これらのリーク電流が未給電

の分岐や未使用のブリッジを介して逆方向に流れ、IEEE 802.3の仕様を満たさなくなることがあります。

効率の高いアプリケーション向けに、LT4293はLT4321ベースのPoE理想ダイオード・ブリッジをサポートしています。このダイオード・ブリッジは、ダイオード1個当たりの順方向電圧降下を0.7Vから20mVに低減しつつ、IEEE 802.3の準拠を維持します。LT4321は熱設計を簡略化し、高価なヒートシンクを省いて、スペースに制約のあるアプリケーションで動作できます。

#### 補助入力ダイオード・ブリッジ

一部のPDは、AC電力またはDC電力を補助電源から受ける必要があります。電圧の整流と極性の補正に対応するには、一般的にはダイオード・ブリッジが必要です。

効率の高いアプリケーションや補助電源の入力電圧が低いアプリケーションでは、整流器の両端での電圧降下を許容することができません。LT4293は、LT4320ベースの理想ダイオード・ブリッジと組み合わせて構成し、ダイオードの電圧降下分を補って、熱設計を容易にすることができます。

補助電源の入力電圧が10Vより低いアプリケーションでは、LT4293をLT4320ベースの理想ダイオード・ブリッジと組み合わせて構成して電圧降下を補償し、電気的特性の表で規定しているように、VPORTの最小電圧がVPORT AUXモードの電圧範囲内に収まることを確保する必要があります。

#### 入力コンデンサ

IEEE 802.3の入力インピーダンス要件を満たし、LT4293を適切にバイパスするには、VPORTとGNDの間に0.1 $\mu$ Fのコンデンサが必要です。LT4321と組み合わせて動作させる場合は、0.047 $\mu$ Fのコンデンサをそれぞれデバイスの近くに接続してバイパスし、ポートの全容量が仕様の範囲内に収まるようにします。

#### トランジエント電圧抑圧素子

LT4293の絶対最大定格電圧は100Vと規定されており、イーサネット・ケーブルのサージに起因する短時間の過電圧を許容するように設計されています。LT4293を過電圧か

## アプリケーション情報

ら保護するため、SMAJ58Aなどの单方向トランジエント電圧抑圧素子(TVS)をVPORTピンとGNDピンの間に取り付けます。補助電源入力が必要なPDアプリケーションの場合は、TVSをV<sub>IN</sub>とGNDの間に取り付けます。TVSの配置については、レイアウトに関する検討事項を参照してください。

ケーブル放電が著しく大きい場合やサージ保護については、弊社にお問い合わせください。

### 露出パッド

LT4293のDFNパッケージには、内部でGNDに接続された露出パッドがあります。露出パッドは、プリント回路基板上のGNDにのみ接続できます。

### レイアウトに関する検討事項

RCLASSピンとRCLASS++ピンの寄生容量が大きくなりすぎないようにしてください。また、抵抗R<sub>CLS</sub>とR<sub>CLS++</sub>はLT4293の近くに配置してください。

デバイスを最大限保護するには、0.1μFの入力コンデンサC<sub>PD</sub>とトランジエント電圧抑圧素子をLT4293のできるだけ近くに配置することが不可欠です。LT4293とLT4321を組み合わせて動作させる場合は、0.047μFのコンデンサC<sub>PD1</sub>をLT4293のVPORTピンとGNDピン(それぞれピン10とピン5)にできるだけ近づけて配置し、0.047μFのコンデンサC<sub>PD2</sub>をLT4321のOUTPピンとOUTNピンにできるだけ近づけて配置します。

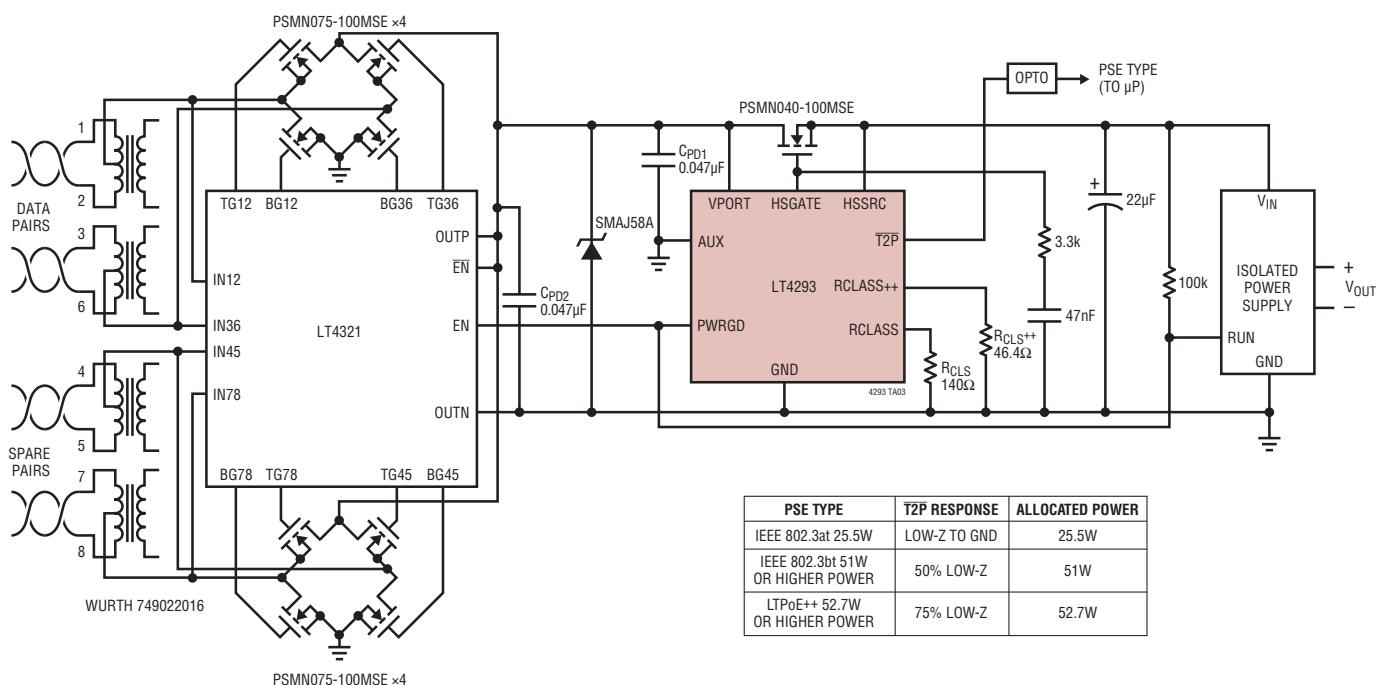

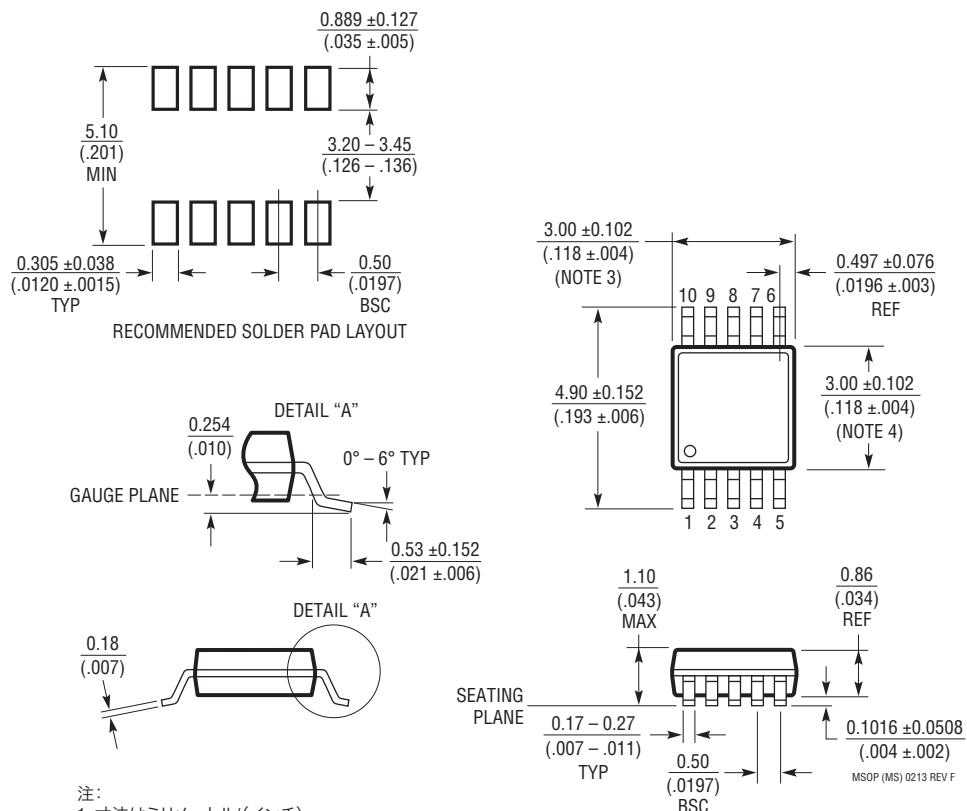

## 代表的なアプリケーション

LTPoE++/IEEE 802.3bt準拠、効率99%超の51W受電デバイス

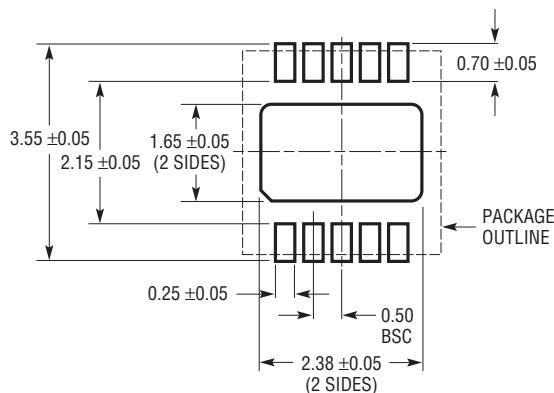

## パッケージ

**DD Package

10-Lead Plastic DFN (3mm × 3mm)**

(Reference LTC DWG # 05-08-1699 Rev C)

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS

注:

1. 図はJEDECのパッケージ外形MO-229のバリエーション(WEED-2)に含めるよう提案されている。

バリエーション割り当ての最新の状況については、弊社Webサイトのデータシートを確認すること

2. 図は実寸とは異なる

3. 全ての寸法はミリメートル

4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない。モールドのバリは(もしあれば)

各サイドで0.15mmを超えないこと

5. 露出パッドはハンダ・メッキとする

6. 灰色の部分はパッケージの上面と底面の1番ピンの位置の参考に過ぎない

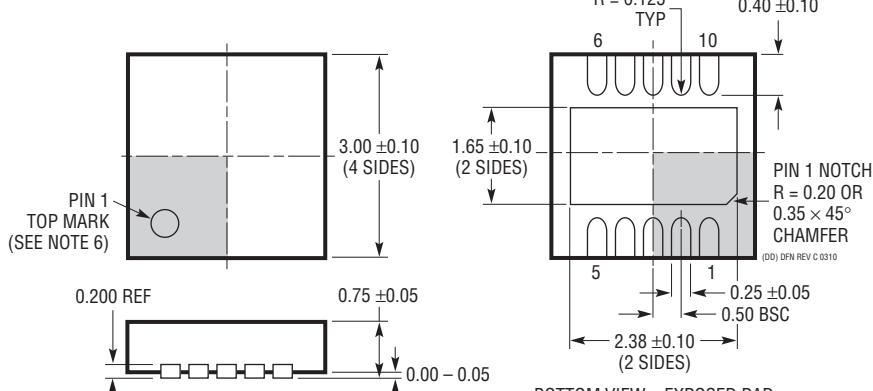

## パッケージ

**MS Package

10-Lead Plastic MSOP**

(Reference LTC DWG # 05-08-1661 Rev F)

注:

- 寸法はミリメートル/(インチ)

- 図は実寸とは異なる

- 寸法にはモールドのバリ、突出部、またはゲートのバリを含まない。

モールドのバリ、突出部、またはゲートのバリは、各サイドで $0.152\text{mm}$  ( $0.006"$ ) を超えないこと

- 寸法には、リード間のバリまたは突出部を含まない。

- リード間のバリまたは突出部は、各サイドで $0.152\text{mm}$  ( $0.006"$ ) を超えないこと

- リードの平坦度(整形後のリードの底面)は最大 $0.102\text{mm}$  ( $0.004"$ ) であること

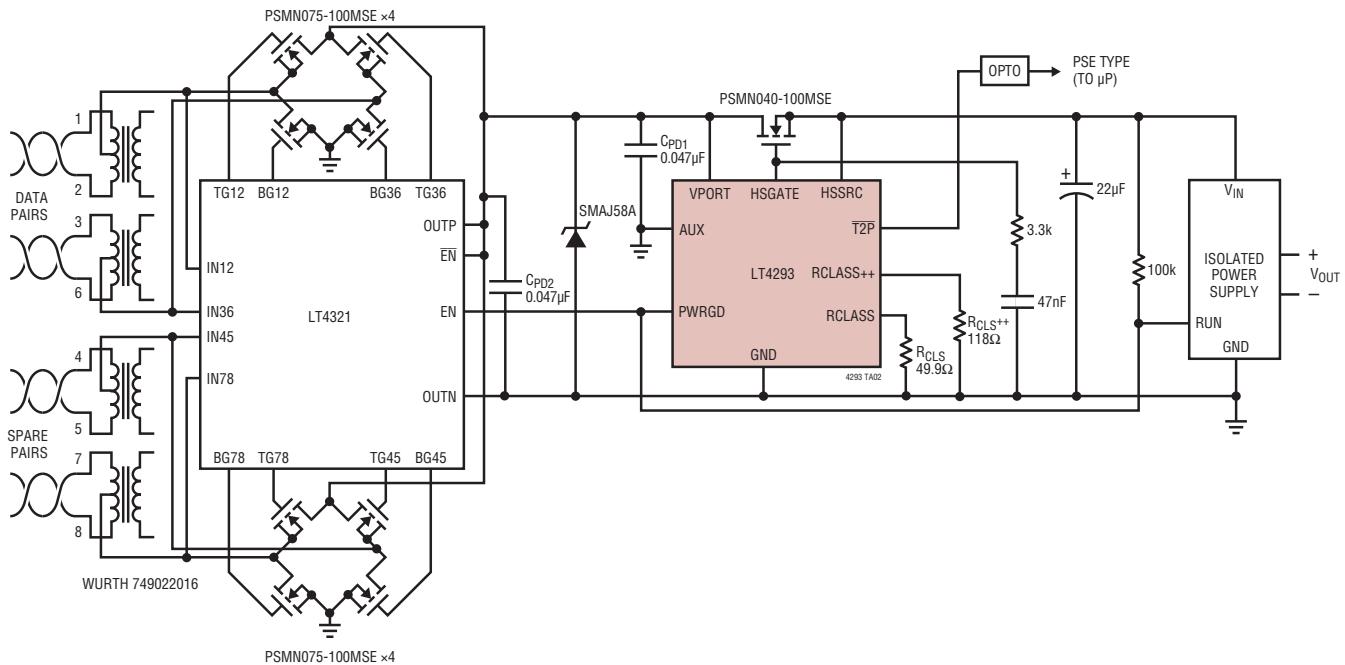

## 代表的なアプリケーション

LTPoE++/IEEE 802.3bt、効率99%超の71.3W受電デバイス

## 関連製品

| 製品番号                            | 説明                                                               | 注釈                                                                                                                          |

|---------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| LT4295                          | フォワード／フライバック・スイッチング・レギュレータ・コントローラ付きIEEE 802.3bt PD               | 外部スイッチ、IEEE 802.3btのサポート、構成可能なクラス、フォワード動作またはNo-Optoフライバック構成動作、周波数、PG/SG遅延、ソフトスタート、および最小9Vの補助電源サポート、(ハウスキーピング降圧電源、スロープ補償を含む) |

| LT4294                          | IEEE 802.3bt PD コントローラ                                           | 外部スイッチ、IEEE 802.3bt、および補助電源をサポート                                                                                            |

| LT4321                          | PoE理想ダイオード・ブリッジ・コントローラ                                           | IEEE規定のPD向けに8つのNMOSFETを制御、ダイオードの電圧降下がない電圧の整流                                                                                |

| LT4320/LT4320-1                 | 理想ダイオード・ブリッジ・コントローラ                                              | 入力:9V~72V、DC~600Hz。4つのNMOSFETを制御、ダイオードの電圧降下がない電圧の整流                                                                         |

| LTC4292/LTC4291-1               | 4ポート IEEE 802.3bt PSE コントローラ                                     | トランスによる絶縁、IEEE 802.3bt PDをサポート                                                                                              |

| LTC4279                         | シングル PoE/PoE+/LTPoE++ PSE コントローラ                                 | IEEE 802.3af、IEEE 802.3at、LTPoE++、および独自PDをサポート                                                                              |

| LT4276A/B/C                     | フォワード／フライバック・スイッチング・レギュレータ・コントローラを内蔵したLTPoE++/PoE+/PoE PD コントローラ | 外部スイッチ、LTPoE++のサポート、ユーザが構成可能なクラス、フォワード動作またはNo-Optoフライバック動作、周波数、PG/SG遅延、ソフトスタート、および最小9Vの補助電源サポート、(ハウスキーピング降圧電源、スロープ補償を含む)    |

| LT4275A/B/C                     | LTPoE++/PoE+/PoE PD コントローラ                                       | 外部スイッチ、LTPoE++をサポート                                                                                                         |

| LTC4269-1                       | フライバック・スイッチング・レギュレータ内蔵のIEEE 802.3at PD インターフェース                  | 2イベント分類、プログラマブルなクラス、同期整流式No-Optoフライバック・コントローラ、スイッチング周波数:50kHz~250kHz、補助電源サポート                                               |

| LTC4269-2                       | フォワード・スイッチング・レギュレータ内蔵のIEEE 802.3at PD インターフェース                   | 2イベント分類、プログラマブルなクラス、同期整流式フォワード・コントローラ、スイッチング周波数:100kHz~500kHz、補助電源サポート                                                      |

| LTC4278                         | フライバック・スイッチング・レギュレータ内蔵のIEEE 802.3at PD インターフェース                  | 2イベント分類、プログラマブルなクラス、同期整流式No-Optoフライバック・コントローラ、スイッチング周波数:50kHz~250kHz、12V補助電源サポート                                            |

| LTC4267/LTC4267-1/<br>LTC4267-3 | スイッチング・レギュレータ内蔵のIEEE 802.3af PD インターフェース                         | 100V、400mAスイッチを内蔵、プログラム可能なクラス、200kHz/300kHzの固定周波数PWM                                                                        |

| LTC4290/LTC4271                 | 8ポート PoE/PoE+/LTPoE++ PSE コントローラ                                 | トランスによる絶縁、IEEE802.3af、IEEE802.3at、およびLTPoE++ PDに対応                                                                          |