## **DS28CZ04**

## 不揮発性PIO付き、4kビットI<sup>2</sup>C/SMBus EEPROM

#### iapan.maxim-ic.com

#### 概要

DS28CZ04 は、4 本のPIOライン付き 4kビット(512 x 8) EEPROMです。デバイスとの通信は、業界標準の $l^2$ Cおよび SMBus<sup>TM</sup>インタフェースによって行われます。メモリは、単一バイトおよび最大 16 バイトのブロック書込み機能を備えた 2 セグメントの 256 バイトで構成されます。各PIO ラインは、入力または出力として構成することができます。出力として設定されたPIOの電源投入時の状態は、不揮発性メモリに保存されます。すべてのPIOは、シリアルインタフェースを通じてユーザが設定変更することができます。

### アプリケーション

- 4G SFP 銅モジュール

- SFF-8472、SFP ファイバモジュール

- RAID システム

- サーバ

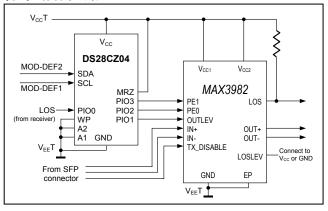

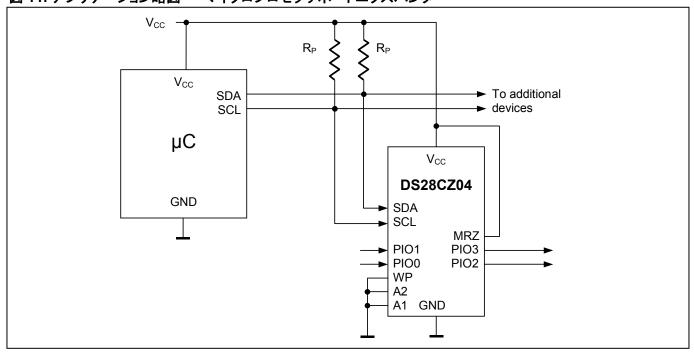

### 標準動作回路

スモールフォームファクタプラガブル(SFP)回路

SMBus は Intel Corp. の商標です。

### 特長

- 2 セグメントの 256 バイトブロックで構成される 4k ビット (512 x 8) EEPROM

- 単一バイトおよび最大 16 バイトの EEPROM 書込み シーケンス

- すべての EEPROM アレイ用の書込み保護制御端子

- 25°Cでブロック当り 200k サイクルの耐久性;10ms (max)の EEPROM 書込みサイクル

- 4本のPIOライン

- 各 PIO ラインは、保存された値によって起動時に入力 または出力モードに構成

- すべての PIO が起動後に構成変更可能

- I<sup>2</sup>CバスおよびSMBus対応のためにユーザープログラ マブルなシリアルインタフェース

- 100kHzおよび 400kHzのI<sup>2</sup>C通信速度をサポート

- 動作範囲:2.0V~5.25V、-40°C~+85°C

- 4mm x 4mm、12ピン TQFN パッケージ

### 型番

| PART         | TEMP RANGE     | PIN-PACKAGE                    |

|--------------|----------------|--------------------------------|

| DS28CZ04-4+  | -40°C to +85°C | TQFN12 4x4mm <sup>2</sup>      |

| DS28CZ04-4+T | -40°C to +85°C | TQFN12 4x4mm²<br>Tape-and-Reel |

<sup>+</sup>は鉛フリーパッケージを示します。

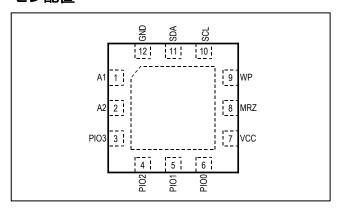

### ピン配置

注: この製品の改訂版の中には仕様が公表されたデータシートの仕様と異なり、正誤表として扱われている場合があります。様々な販売チャネルを通し、 製品に複数の改訂版が同時に存在することがあります。デバイスの正誤表に関しては、japan.maxim-ic.com/errataをご覧ください。

1 of 22 REV: 073106

### **ABSOLUTE MAXIMUM RATINGS**

Voltage Range on Any Pin Relative to Ground -0.5V, +6V Maximum Current SDA, SCL, A2, A1, WP, MRZ Pin  $\pm 20 mA$ Maximum Current each PIO Pin ±20mA Maximum GND and V<sub>CC</sub> Current 100mA -40°C to +85°C **Operating Temperature Range** Junction Temperature +150°C Storage Temperature Range -55°C to +85°C Soldering Temperature See IPC/JEDEC J-STD-020

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to the absolute maximum rating conditions for extended periods may affect device.

### **ELECTRICAL CHARACTERISTICS**

(-40°C to +85°C, see Note 1)

| PARAMETER                                                                   | SYMBOL             | CONDITIONS                             | MIN                       | TYP | MAX                       | UNITS |

|-----------------------------------------------------------------------------|--------------------|----------------------------------------|---------------------------|-----|---------------------------|-------|

| Supply Voltage                                                              | V <sub>CC</sub>    |                                        | 2.0                       |     | 5.25                      | V     |

| Standby Current (Note 2)                                                    | I <sub>CCS</sub>   | Bus idle, $V_{CC} = 5.25V$             |                           | 1.5 | 4                         | μA    |

| Operating Current                                                           | I <sub>CCA</sub>   | Bus active at 400kHz, $V_{CC} = 5.25V$ |                           | 250 | 500                       | μΑ    |

| Programming Current                                                         | I <sub>PROG</sub>  | V <sub>CC</sub> = 5.25V                |                           | 500 | 1000                      | μΑ    |

| Power-up Wait Time                                                          | t <sub>POIP</sub>  | (Note 3)                               |                           |     | 100                       | μs    |

| EEPROM                                                                      |                    |                                        |                           |     |                           |       |

| Programming Time                                                            | t <sub>PROG</sub>  |                                        |                           |     | 10                        | ms    |

| Endurance                                                                   | N <sub>CYCLE</sub> | At +25°C (Notes 4, 5)                  | 200k                      |     |                           | _     |

| Data Retention                                                              | t <sub>RET</sub>   | At +85°C (Note 5)                      | 50                        |     |                           | years |

| PIO Pins, See Figures 8, 9                                                  |                    |                                        |                           |     |                           |       |

| LOW-Level Output Voltage                                                    | V <sub>OL</sub>    | 1mA sink current                       | 0                         |     | 0.4                       | V     |

| HIGH-Level Output Voltage                                                   | V <sub>OH</sub>    | 500µA source current                   | V <sub>CC</sub> - 0.5V    |     |                           | V     |

| LOW-Level Input Voltage                                                     | $V_{IL}$           |                                        | -0.3                      |     | 0.3 × V <sub>CC</sub>     | V     |

| HIGH-Level Input Voltage                                                    | V <sub>IH</sub>    |                                        | 0.7 ×<br>V <sub>CC</sub>  |     | V <sub>CC</sub> + 0.3V    | V     |

| Output Data Valid Time                                                      | t <sub>PV</sub>    |                                        |                           |     | 1                         | μs    |

| PIO Read Setup Time                                                         | t <sub>PS</sub>    | (Note 5)                               | 150                       |     |                           | ns    |

| PIO Read Hold Time                                                          | t <sub>PH</sub>    | (Note 5)                               | 150                       |     |                           | ns    |

| Leakage Current                                                             | IL                 | High Impedance, at V <sub>CCMAX</sub>  | -1                        |     | +1                        | μΑ    |

| SCL, SDA, A2, A1, WP, MRZ Pi                                                | ns (Note 6), \$    |                                        | •                         |     |                           |       |

| LOW Level Input Voltage                                                     | V <sub>IL</sub>    |                                        | -0.3                      |     | 0.3 × V <sub>CC</sub>     | V     |

| HIGH Level Input Voltage                                                    | V <sub>IH</sub>    | (Note 7)                               | 0.7 ×<br>V <sub>CC</sub>  |     | V <sub>CCmax</sub> + 0.3V | V     |

| Hysteresis of Schmitt Trigger Inputs                                        | V <sub>hys</sub>   | (Notes 5, 8)                           | 0.05 ×<br>V <sub>CC</sub> |     |                           | V     |

| LOW Level Output Voltage                                                    | V <sub>OL</sub>    | At 4mA Sink Current, open drain        |                           |     | 0.4                       | V     |

| Output Fall Time from V <sub>Ihmin</sub> to V <sub>ILmax</sub> (Notes 5, 9) | t <sub>of</sub>    | Bus Capacitance from 10pF to 400pF     | 20 +<br>0.1C <sub>B</sub> |     | 250                       | ns    |

| Pulse Width of Spikes that are<br>Suppressed by the Input Filter            | t <sub>SP</sub>    | SDA and SCL pins only (Note 5)         |                           |     | 50                        | ns    |

| PARAMETER                                                                                      | SYMBOL               | CONDITIONS                                                         | MIN        | TYP | MAX | UNITS |

|------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------|------------|-----|-----|-------|

| Input Current with an Input<br>Voltage Between 0.1V <sub>CC</sub> and<br>0.9V <sub>CCmax</sub> | I <sub>I</sub>       | (Note 10)                                                          | -10        |     | 10  | μA    |

| Input Capacitance                                                                              | Cı                   | (Notes 5, 8)                                                       |            |     | 10  | pF    |

| SCL Clock Frequency                                                                            | $f_{SCL}$            | (Note 11)                                                          |            |     | 400 | kHz   |

| Bus Time-Out                                                                                   | t <sub>TIMEOUT</sub> | (Note 11)                                                          | 25         |     | 75  | ms    |

| Hold Time (Repeated) START Condition. After this Period, the First Clock Pulse is Generated.   | t <sub>HD:STA</sub>  | (Note 12)                                                          | 0.6        |     |     | μs    |

| LOW Period of the SCL Clock (Note 12)                                                          | $t_{LOW}$            | $ \begin{array}{c} V_{CC} \geq 2.7V \\ V_{CC} < 2.7V \end{array} $ | 1.3<br>1.5 |     |     | μs    |

| HIGH Period of the SCL Clock                                                                   | t <sub>HIGH</sub>    | (Note 12)                                                          | 0.6        |     |     | μs    |

| Setup Time for a Repeated START Condition                                                      | t <sub>su:sta</sub>  | (Note 12)                                                          | 0.6        |     |     | μs    |

| Data Hold Time (Notes 13, 14)                                                                  | +                    | $V_{CC} \ge 2.7V$                                                  | 0.3        |     | 0.9 | 116   |

| Data Hold Time (Notes 13, 14)                                                                  | t <sub>HD:DAT</sub>  | V <sub>CC</sub> < 2.7V                                             | 0.3        |     | 1.1 | μs    |

| Data Setup Time                                                                                | t <sub>SU:DAT</sub>  | (Notes 12, 15)                                                     | 100        |     |     | ns    |

| Setup Time for STOP Condition                                                                  | t <sub>su:sto</sub>  | (Note 12)                                                          | 0.6        |     |     | μs    |

| Bus Free Time Between a STOP and START Condition                                               | t <sub>BUF</sub>     | (Note 12)                                                          | 1.3        |     |     | μs    |

| Capacitive Load for Each Bus Line                                                              | Св                   | (Notes 5, 12)                                                      |            |     | 400 | pF    |

- **Note 1:** Specifications at -40°C are guaranteed by design and characterization only and not production tested.

- **Note 2:** To the first order, this current is independent of the supply voltage value.

- **Note 3:** All PIO are tri-stated at beginning of reset prior to setting to Power-On values.

- **Note 4:** This specification is valid for each 16-byte memory block.

- **Note 5:** Not production tested. Guaranteed by design or characterization.

- **Note 6:** All values are referenced to  $V_{IHmin}$  and  $V_{ILmax}$  levels.

- **Note 7:** The maximum specification value is guaranteed by design, not production tested.

- **Note 8:** Applies to SDA and SCL.

- **Note 9:** C<sub>B</sub> = total capacitance of one bus line in pF. If mixed with HS-mode devices, faster fall-times according to I<sup>2</sup>C-Bus Specification v2.1 are allowed.

- Note 10: The DS28CZ04 does not obstruct the SDA and SCL lines if V<sub>CC</sub> is switched off.

- **Note 11:** The minimum SCL clock frequency is limited by the bus timeout feature. If the CM bit is 1 AND SCL stays at the same logic level or SDA stays low for this interval, the DS28CZ04 behaves as though it has sensed a STOP condition.

- Note 12: System Requirement

- **Note 13:** The DS28CZ04 provides a hold time of at least 300ns for the SDA signal (referred to the V<sub>IHmin</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- Note 14: The maximum  $t_{\text{HD:DAT}}$  has only to be met if the device does not stretch the low period  $(t_{\text{LOW}})$  of the SCL signal.

- Note 15: A Fast-mode I²C-bus device can be used in a standard-mode I²C-bus system, but the requirement  $t_{SU:DAT} \ge 250$ ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line  $t_{max} + t_{SU:DAT} = 1000 + 250 = 1250$ ns (according to the standard-mode I²C-bus specification) before the SCL line is released.

### 端子説明

| 端子 | 名称       | 機能                                                                           |

|----|----------|------------------------------------------------------------------------------|

| 1  | A1       | デバイスアドレスビット 1                                                                |

| 2  | A2       | デバイスアドレスビット 2                                                                |

| 3  | PIO3     | PIO ライン#3                                                                    |

| 4  | PIO2     | PIO ライン#2                                                                    |

| 5  | PIO1     | PIO ライン#1                                                                    |

| 6  | PIO0     | PIO ライン#0                                                                    |

| 7  | $V_{CC}$ | 電源入力                                                                         |

| 8  | MRZ      | マスタリセット(アクティブロー)。 デバイスの電源をサイクリングしないでシリアルインタフェースと PIO                         |

|    |          | をリセットします。                                                                    |

| 9  | WP       | 書込み保護入力。 $V_{CC}$ またはGNDに接続します。 $V_{CC}$ に接続すると、EEPROMアレイ全体が書込み              |

|    |          | 保護されます。GNDに接続すると通常の読取り/書込みアクセスが行われます。書込みアクセス中に                               |

|    |          | 端子状態を変更すると、結果の予測です。                                                          |

| 10 | SCL      | $I^2$ C/SMBusシリアルクロック入力。プルアップ抵抗を通して $V_{CC}$ に接続する必要があります。                   |

| 11 | SDA      | I <sup>2</sup> C/SMBus双方向シリアルデータライン。プルアップ抵抗を通してV <sub>CC</sub> に接続する必要があります。 |

| 12 | GND      | デバイスのグランド供給                                                                  |

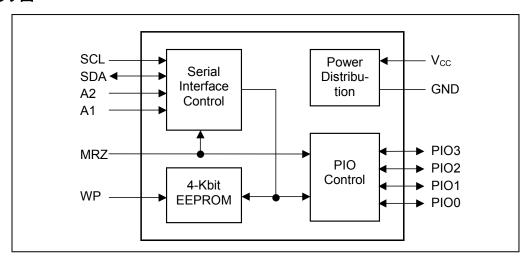

### 概要

DS28CZ04 は、図 1 のブロック図に示すように、シリアルI<sup>2</sup>C/SMBusインタフェース、4kビットのEEPROM、および 4 つの双方向 PIOチャネルで構成されます。このデバイスは、I<sup>2</sup>Cバスインタフェースを通じて、標準モードまたはファーストモードでホストプロセッサと通信します。またユーザはインタフェースをI<sup>2</sup>CバスからSMBusに切り替えることができます。2 つのアドレス端子によって、4 個のDS28CZ04 を同じバスセグメント上に置くことができます。マスタリセット端子によって、電源サイクリングなしで完全なデバイスリセットが可能です。

このデバイスは、2 セグメント(下位半分、上位半分)の 256 バイトで構成された 512 バイトのメモリを備えています(図 2)。メモリマップとデバイスアドレス指定は、SFF-8472 ディジタル診断アドレス割当に対応しています。EEPROM全体は、WP端子をVccに接続することによって書込み保護されます。PIO端子は、1 つのアドレス(= シングルアドレスモード)または個別アドレス(= マルチアドレスモード)によってアクセスされます。PIO直接アクセスアドレス指定によって、データパターンの高速生成と高速サンプリングが可能です。

DS28CZ04 は、ユーザがデバイスを SFF モードで電源投入するかどうかを選択して、個々の PIO の出力状態(出力モードでのハイ、ロー)、個々の PIO のデータ方向(入力、出力)、個々の PIO の出力タイプ(プッシュ/プル、オープンドレイン)、個々の PIO 読取りビットの反転(真、偽)に関する電源投入時のデフォルトを定義することができる複数の EEPROM レジスタを内蔵しています。いったん電源が投入されると、PIO 設定値は電源投入時のデフォルトに影響を与えることなく SRAM レジスタによって上書きすることができます。

## 図 1. ブロック図

## 図 2A. メモリマップ(デバイスアドレス = A0h)

| ADDRESS    | TYPE   | ACCESS | DESCRIPTION                                                                   |

|------------|--------|--------|-------------------------------------------------------------------------------|

| 00h to 74h | EEPROM | R/W    | User memory                                                                   |

| 75h        | EEPROM | R/W    | Special function/user memory; controls whether device powers-up into SFF Mode |

| 76h        | EEPROM | R/W    | Power-on default for PIO output state and direction for all PIOs              |

| 77h        | EEPROM | R/W    | Power-on default for PIO output type and read-<br>inversion for all PIOs      |

| 78h to 79h | _      | R      | Reserved (reads FFh)                                                          |

| 7Ah        | SRAM   | R/W    | Direction setting for all PIOs and device control/status register             |

| 7Bh        | SRAM   | R/W    | PIO read-inversion and PIO output type for all PIOs                           |

| 7Ch to 7Fh | SRAM   | R/W    | PIO Read/Write Access Registers                                               |

| 80h to FFh | EEPROM | R/W    | User memory                                                                   |

# 図 2B. メモリマップ(デバイスアドレス = A2h)

| ADDRESS    | TYPE   | ACCESS | DESCRIPTION                               |

|------------|--------|--------|-------------------------------------------|

| 00h to 6Dh | EEPROM | R/W    | User memory                               |

| 6Eh        | EEPROM | R/W    | SFF Mode off: User memory                 |

| OEII       |        | R      | SFF Mode on: SFF Optional Status Register |

| 6Fh to EFh | EEPROM | R/W    | User memory                               |

| F0h to FFh | _      | R      | Reserved (reads FFh)                      |

#### レジスタの詳細

### 特別機能/ユーザメモリ(デバイスアドレス = A0h)

| ADDR | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

|------|----|----|----|----|----|----|----|----|

| 75h  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  |

このアドレスに対しては一般的な読取りと書込みが行われます。AAhに設定すると、前記のビットパターンに示されるように、メモリアドレス 7Ah (デバイスアドレス = A0h)のSFFモードビットは<u>次の電源投入後に</u>1 に設定され、SFFオプションステータスレジスタとして働くメモリアドレス 6Eh (デバイスアドレス = A2h)のSFFモードをアクティブにします。

#### 出荷時デフォルト:00h

### PIO 出力状態と方向に関する電源投入時のデフォルト(デバイスアドレス = A0h)

| ADDR | b7   | b6   | b5   | b4   | b3   | b2   | b1   | b0   |

|------|------|------|------|------|------|------|------|------|

| 76h  | POD3 | POD2 | POD1 | POD0 | POV3 | POV2 | POV1 | POV0 |

### このアドレスに対しては一般的な読取りと書込みが行われます。出荷時デフォルト:F0h

| ビット説明                   | ビット | 定義                                 |  |  |

|-------------------------|-----|------------------------------------|--|--|

| POV0:電源投入時の<br>PIO0の状態  | b0  | PIO0 の電源投入時のデフォルト出力状態              |  |  |

| POV1:電源投入時の<br>PIO1 の状態 | b1  | PIO1 の電源投入時のデフォルト出力状態              |  |  |

| POV2:電源投入時の<br>PIO2の状態  | b2  | PIO2 の電源投入時のデフォルト出力状態              |  |  |

| POV3:電源投入時の<br>PIO3の状態  | b3  | PIO3 の電源投入時のデフォルト出力状態              |  |  |

| POD0:電源投入時の<br>PIO0の方向  | b4  | PIO0 の電源投入時のデフォルトの方向;0 ⇒ 出力、1 ⇒ 入力 |  |  |

| POD1:電源投入時の<br>PIO1の方向  | b5  | PIO1 の電源投入時のデフォルトの方向;0 ⇒ 出力、1 ⇒ 入力 |  |  |

| POD2:電源投入時の<br>PIO2の方向  | b6  | PIO2 の電源投入時のデフォルトの方向;0 ⇒ 出力、1 ⇒ 入力 |  |  |

| POD3:電源投入時の<br>PIO3の方向  | b7  | PIO3 の電源投入時のデフォルトの方向;0 ⇒ 出力、1 ⇒ 入力 |  |  |

### PIO 出力タイプと読取り反転に関する電源投入時のデフォルト(デバイスアドレス = A0h)

| ADDR | b7   | b6   | b5   | b4   | b3   | b2   | b1   | b0   |

|------|------|------|------|------|------|------|------|------|

| 77h  | РОТ3 | POT2 | POT1 | POT0 | PIM3 | PIM2 | PIM1 | PIM0 |

このアドレスに対しては一般的な読取りと書込みが行われます。出荷時デフォルト:F0h

| ビット説明                      | ビット | 定義                                                  |

|----------------------------|-----|-----------------------------------------------------|

| PIM0:電源投入時の PIO0<br>の読取り反転 | b0  | PIO0 の読取り反転ビットの電源投入時のデフォルト状態:0 ⇒ 反転なし、<br>1 ⇒ 反転    |

| PIM1:電源投入時の PIO1<br>の読取り反転 | b1  | PIO1 の読取り反転ビットの電源投入時のデフォルト状態:0 ⇒ 反転なし、<br>1 ⇒ 反転    |

| PIM2:電源投入時の PIO2<br>の読取り反転 | b2  | PIO2 の読取り反転ビットの電源投入時のデフォルト状態:0 ⇒ 反転なし、<br>1 ⇒ 反転    |

| PIM3:電源投入時の PIO3<br>の読取り反転 | b3  | PIO3 の読取り反転ビットの電源投入時のデフォルト状態:0 ⇒ 反転なし、<br>1 ⇒ 反転    |

| POT0:電源投入時の PIO0 の出力タイプ    | b4  | PIO0 の電源投入時のデフォルト出力タイプ;0 ⇒ プッシュ/プル、<br>1 ⇒ オープンドレイン |

| POT1:電源投入時の PIO1 の出力タイプ    | b5  | PIO1 の電源投入時のデフォルト出力タイプ;0 ⇒ プッシュ/プル、<br>1 ⇒ オープンドレイン |

| POT2:電源投入時の PIO2<br>の出力タイプ | b6  | PIO2 の電源投入時のデフォルト出力タイプ;0 ⇒ プッシュ/プル、<br>1 ⇒ オープンドレイン |

| POT3:電源投入時の PIO3<br>の出力タイプ | b7  | PIO3 の電源投入時のデフォルト出力タイプ;0 ⇒ プッシュ/プル、<br>1 ⇒ オープンドレイン |

### 方向および制御/ステータスレジスタ(デバイスアドレス = A0h)

| ADDR | b7   | b6 | b5   | b4  | b3   | b2   | b1   | b0   |

|------|------|----|------|-----|------|------|------|------|

| 7Ah  | ADMD | CM | BUSY | SFF | DIR3 | DIR2 | DIR1 | DIR0 |

このアドレスに対しては一般的な読取りと書込みが行われます。ビット 5 は読取り専用です。ビット 0~3 の電源投入時のデフォルトは、メモリアドレス 76h (デバイスアドレス = A0h)のビット 4~7 からそれぞれコピーされます。

| ビット説明                     | ビット | 定義                                                                                                                                                              |

|---------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIR0:PIO0 の方向             | b0  | PIO0 の方向; 0 ⇒ 出力、1 ⇒ 入力                                                                                                                                         |

| DIR1:PIO1 の方向             | b1  | PIO1 の方向; 0 ⇒ 出力、1 ⇒ 入力                                                                                                                                         |

| DIR2:PIO2 の方向             | b2  | PIO2 の方向; 0 ⇒ 出力、1 ⇒ 入力                                                                                                                                         |

| DIR3:PIO3 の方向             | b3  | PIO3 の方向; 0 ⇒ 出力、1 ⇒ 入力                                                                                                                                         |

| SFF:SFF モードビット            | b4  | SFFモード制御;0 ⇒ SFFモードオフ、1 ⇒ SFFモードオン<br>詳しくは、メモリマップ(デバイスアドレス = A2h)とSFFオプションステータスレジス<br>タの説明を参照してください。SFFモードビットは、1 に設定されたときPIOO と<br>PIO1 の <u>方向を入力に変更しません</u> 。 |

| ビジー: EEPROM ビジーイ<br>ンジケータ | b5  | このビットが 1を示す場合は、EEPROM書込みサイクル(デバイスアドレス = A0hまたはA2h)が進行中です。(SMBusモードのみ; l <sup>2</sup> Cバスモードでは読み取ると 0 です)                                                        |

| CM:通信モード                  | b6  | シリアル通信インタフェース用のモードを選択します。<br>0:l <sup>2</sup> Cバスモード(電源投入時のデフォルト)<br>1:SMBusモード                                                                                 |

| ADMD: PIO アドレスモード         | b7  | PIO 読取り/書込みアクセス用のアドレスモードを選択します。詳しくは PIO 読取り/書込みアクセスレジスタを参照してください。 0:マルチアドレスモード(電源投入時のデフォルト) 1:シングルアドレスモード                                                       |

### PIO 読取り反転および出力タイプ(デバイスアドレス = A0h)

| ADDR | b7  | b6  | b5  | b4  | b3    | b2    | b1    | b0    |

|------|-----|-----|-----|-----|-------|-------|-------|-------|

| 7Bh  | ОТ3 | OT2 | OT1 | ОТ0 | IMSK3 | IMSK2 | IMSK1 | IMSK0 |

このアドレスに対しては一般的な読取りと書込みが行われます。電源時のデフォルトは、メモリアドレス 77h (デバイスアドレス = A0h) からコピーされます。

| ビット説明                  | ビット | 定義                                 |

|------------------------|-----|------------------------------------|

| IMSK0:PIO0の読取り反転<br>制御 | b0  | 0 ⇒ 反転なし、1 ⇒ PIOO からの読取りデータが反転されます |

| IMSK1:PIO1の読取り反転<br>制御 | b1  | 0 ⇒ 反転なし、1 ⇒ PIO1 からの読取りデータが反転されます |

| IMSK2:PIO2の読取り反転<br>制御 | b2  | 0 ⇒ 反転なし、1 ⇒ PIO2 からの読取りデータが反転されます |

| IMSK3:PIO3の読取り反転<br>制御 | b3  | 0 ⇒ 反転なし、1 ⇒ PIO3 からの読取りデータが反転されます |

| OT0:PIO0 の出力タイプ        | b4  | 0 ⇒ プッシュ/プル、1 ⇒ オープンドレイン           |

| OT1:PIO1 の出力タイプ        | b5  | 0 ⇒ プッシュ/プル、1 ⇒ オープンドレイン           |

| OT2:PIO2の出力タイプ         | b6  | 0 ⇒ プッシュ/プル、1 ⇒ オープンドレイン           |

| OT3:PIO3 の出力タイプ        | b7  | 0 ⇒ プッシュ/プル、1 ⇒ オープンドレイン           |

### PIO 読取り/書込みアクセスレジスタ(デバイスアドレス = A0h)

| ADDR  | b7  | b6                | b5  | b4     | b3  | b2  | b1  | b0  | PIO アドレスモード        |

|-------|-----|-------------------|-----|--------|-----|-----|-----|-----|--------------------|

| 7Ch   | IV3 | IV2               | IV1 | IV0    | OV3 | OV2 | OV1 | OV0 | Single             |

| 7011  | 1   | 1                 | 1   | IV0    | 1   | 1   | 1   | OV0 | <mark>Multi</mark> |

| 7Dh   |     |                   |     | Single |     |     |     |     |                    |

| ווטו  | 1   | 1                 | 1   | IV1    | 1   | 1   | 1   | OV1 | <mark>Multi</mark> |

| 7Eh   |     | 00h (no function) |     |        |     |     |     |     | Single             |

| / [[] | 1   | 1                 | 1   | IV2    | 1   | 1   | 1   | OV2 | <mark>Multi</mark> |

| 7Fh   |     |                   |     | Single |     |     |     |     |                    |

| 7.511 | 1   | 1                 | 1   | IV3    | 1   | 1   | 1   | OV3 | <mark>Multi</mark> |

これらのレジスタに対しては一般的な読取りと書込みが行われます。1 と示したビットには機能がなく、これらの状態を変更することはできません。

| ビット説明         | ビット | 定義                                |

|---------------|-----|-----------------------------------|

| OV0:PIO0 の出力値 | _   | DIR0 = 0 (出力)の場合の PIO0 のロジック出力状態  |

| OV1:PIO1 の出力値 | _   | DIR1 = 0 (出力)の場合の PIO1 のロジック出力状態  |

| OV2:PIO2の出力値  |     | DIR2 = 0 (出力)の場合の PIO2 のロジック出力状態  |

| OV3:PIO3 の出力値 |     | DIR3 = 0 (出力)の場合の PIO3 のロジック出力状態  |

| IV0:PIO0 の入力値 | _   | IMSK0とPIO0の排他論理和から読み取られたロジック状態    |

| IV1:PIO1 の入力値 |     | IMSK1 と PIO1 の排他論理和から読み取られたロジック状態 |

| IV2:PIO2 の入力値 |     | IMSK2 と PIO2 の排他論理和から読み取られたロジック状態 |

| IV3:PIO3 の入力値 |     | IMSK3とPIO3の排他論理和から読み取られたロジック状態    |

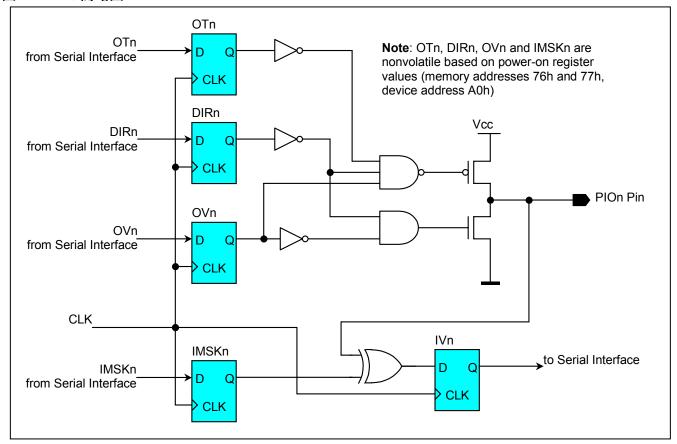

図 3 は PIO の簡略図を示します。フリップフロップは、PIO R/W アクセスレジスタおよびメモリアドレス 7Ah と 7Bh (デバイス アドレス = A0h)によってアクセスされます。これらは、メモリアドレス 76h と 77h (デバイスアドレス = A0h)に保存されたデータに 従って、電源投入時またはリセット中に初期化されます。PIO が入力として構成されると、PIO 出力はトライステート(ハイインピー ダンス)になります。PIO が出力として構成されると、PIO 入力は対応する読取り反転ビットと XOR (排他論理和)された出力状態 と同じになります。

## 図 3. PIO の簡略図

#### SFF オプションステータスレジスタ(デバイスアドレス = A2h、SFF モードがオンの場合のみ)

|   | ADDR | b7 | b6 | b5 | b4 | b3 | b2  | b1  | b0 |

|---|------|----|----|----|----|----|-----|-----|----|

| Ī | 6Eh  | 0  | 0  | 0  | 0  | 0  | TXF | LOS | 0  |

このレジスタは読取り専用です。各ビットの機能割当てを下表で説明します。ビット 0 と 3~7 には機能がありません。これらは常に 0 を示し 1 に設定することはできません。

| ビット説明 ビット 定義 |    | 定義                                                                  |

|--------------|----|---------------------------------------------------------------------|

| LOS:ロスオブシグナル | b1 | PIO0 のロジック状態を通知します。SFF-8472 対応モジュールでは、PIO0 はロスオブシグナルインジケータに接続されます。  |

| TXF:TX_FAULT | b2 | PIO1 のロジック状態を通知します。SFF-8472 対応モジュールでは、PIO1 はTX_FAULT インジケータに接続されます。 |

### デバイスの動作

アプリケーションにおけるDS28CZ04 の標準的な用法には、メモリに対する書込みと読取り、およびPIOへのアクセスが含まれます。 これらすべてのアクティビティは、I<sup>2</sup>C/SMBusシリアルインタフェースを通じて制御されます。DS28CZ04 はさまざまな特性のメモリ 領域とレジスタを備えているため、検討すべき特別な事例がいくつかあります。詳しくは*読取りと書込み*の項を参照してください。

### シリアル通信インタフェース

#### 一般的な特性

シリアルインタフェースでは、通信にデータライン(SDA)とクロック信号(SCL)が使われます。SDA と SCL はいずれも双方向ラインで、プルアップ抵抗を介して正電源電圧に接続されます。通信が行われないとき両ラインはハイになります。バスに接続されたデバイスの出力段は、ワイヤド AND 機能を実行するオープンドレインまたはオープンコレクタを備えている必要があります。データは、標準モードでは最高 100kbps、ファーストモードでは最高 400kbps のレートで転送されます。DS28CZ04 はこの両モードで動作します。

バス上でデータを送信するデバイスはトランスミッタ、データを受信するデバイスはレシーバと定義されます。通信を制御するデバイスは「マスタ」と呼ばれます。マスタによって制御されるデバイスは「スレーブ」です。DS28CZ04 はスレーブデバイスです。

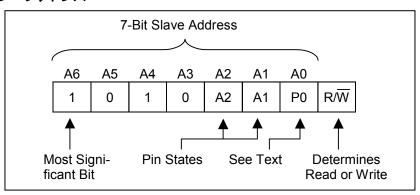

#### スレーブアドレス/方向バイト

個別にアクセスされるためには、各デバイスはバス上の他のデバイスと競合しないスレーブアドレスを備えている必要があります。DS28CZ04 が応答の対象とするスレーブアドレスを、図 4 に示します。スレーブアドレスはスレーブアドレス/方向バイトの一部です。DS28CZ04 のスレーブアドレスの上位 4 ビットは、1010b に設定されています。ビット A1 と A2 は A1 端子と A2 端子に対応します。すなわち、これを選択するためには、A1 ビットと A2 ビットを各ピンのロジック状態に合わせてデバイスをアドレス指定する必要があります。

#### 図 4. DS28CZ04 のスレーブアドレス

512 バイトメモリデバイスの DS28CZ04 は、メモリ位置にアクセスするのに 9 アドレスビットを必要とします。A0 アドレスビットの代りに送信された P0 ビットは、メモリの「下位半分」(0b)または「上位半分」(1b)のいずれをアドレス指定するかを指定します。このため、DS28CZ04 は、メモリの各半分に対して 1 つずつ、すなわち 2 つのロジックスレーブアドレスを専有することになります。本書では、メモリの下位半分をデバイスアドレス A0h と呼び、上位半分をデバイスアドレス A2h と呼びます。A1 端子と A2 端子をロジック 0 に接続すると、A0h と A2h は正しいアドレスになります。これらのピンの条件が異なる場合は、それに応じてスレーブアドレスが変化します。

スレーブアドレス/方向バイトの最終ビット(R/W)によって、データの方向が規定されます。このビットを 0 に設定すると後続データはマスタからスレーブに流れ(書込みアクセスモード)、1 に設定するとデータはスレーブからマスタに流れます(読取りアクセスモード)。 読取りモードでDS28CZ04 にアクセスしてもP0 ビットは送信されますが、その値は無視され(任意でよい)、代りに、<u>最新の**書込み**アクセスで送信された値が適用されます。</u>

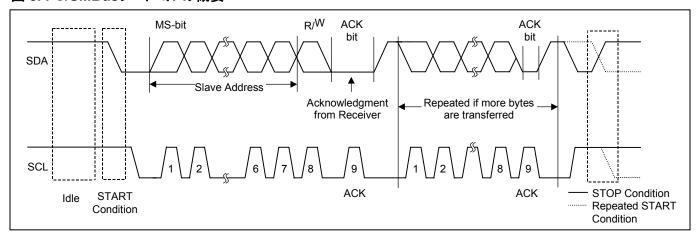

#### I<sup>2</sup>C/SMBusプロトコル

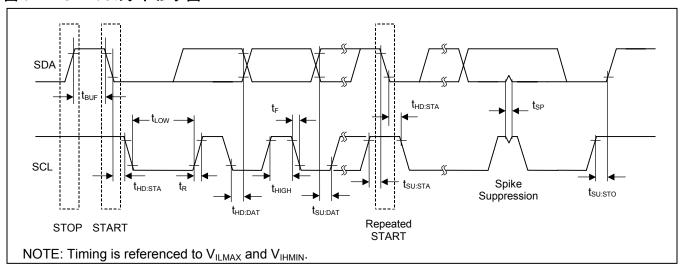

データ転送は、バスがビジーでないときにのみ開始することができます。マスタは、シリアルクロック(SCL)の生成、バスアクセスの制御、START および STOP 条件の生成、および START と STOP の間にデータライン(SDA)上で転送されるバイト数の決定を行います。データは、最上位ビットを先頭にバイト単位で転送されます。各バイトの後に、マスタとスレーブの間の同期を可能にする確認ビットが続きます。データ転送の間、クロックラインがハイのときは SDA が安定に保たれる必要があります。 SCL がハイの間に SDA ラインが変化すると、この変化は START または STOP と解釈されます。プロトコルを図 5 に示します。詳細なタイミングリファレンズについては図 6 を参照してください。

### 図 5. I<sup>2</sup>C/SMBusプロトコルの概要

#### バスアイドルまたは非ビジー

SDAとSCL はともに非アクティブ、すなわちロジックハイ状態にあります。

#### START 条件

スレーブとの通信を開始するために、マスタは START 条件を生成する必要があります。START 条件は、SCL がハイに保たれている間に SDA がハイからローになる状態変化と定義されます。

#### STOP 条件

スレーブとの通信を終了するために、マスタは STOP 条件を生成する必要があります。STOP 条件は、SCL がハイに保たれている間に SDA がローからハイになる状態変化と定義されます。

#### 反復 START 条件

反復 START は、一般に直前の書込みアクセスで読み取るメモリアドレスを指定してから読取りアクセスに利用されます。マスタは、 データ転送の最後に反復 START 条件を使用して、現在のデータ転送に続いて新たなデータ転送を直ちに開始することができます。 反復 START 条件は、通常の START 条件と同様に生成されますが、STOP 条件の後にバスアイドル状態がありません。

#### データ有効

STARTおよびSTOP条件を除くと、SDAの遷移はSCLがロー状態の間にのみ発生します。SDAのデータは、SCLがハイの全パルス期間と必要なセットアップおよびホールド時間(SCLの立下りエッジ後のthodate SCLの立上りエッジ前のtsudat、図 6 参照)にわたって、有効かつ不変の状態を保つものとします。データの 1 ビットにつき 1 クロックパルスが生成されます。データは、SCLパルスの立上りエッジの間に受信デバイスにシフト入力されます。

書込みを終了すると、マスタは読取りを開始するSCLの次の立上りエッジ前に十分なセットアップ時間(図 6 の最小t<sub>SU:DAT</sub> + t<sub>R</sub>)の間 SDAラインを解放する必要があります。スレーブは直前のSCLパルスの立下りエッジでSDAの各データビットをシフト出力し、データ ビットは現在のSCLパルスの立上りエッジで有効になります。マスタは、スレーブから読み取る必要のあるクロックパルスを含む、すべてのSCLクロックパルスを生成します。

#### スレーブによる確認応答

通常、アドレスを指定されたスレーブデバイスは、各バイトの受信後に確認応答を生成しなければなりません。マスタはこの確認 応答ビットに関連するクロックパルスを生成する必要があります。確認に関係するクロックパルスのハイ期間と必要なセットアップ およびホールド時間(SCLの立下りエッジ後のt<sub>HD:DAT</sub>とSCLの立上りエッジ前のt<sub>SU:DAT</sub>)の間SDAがローで安定するように、確認 応答するデバイスは確認応答パルスの間にSDAをローに駆動する必要があります。

#### マスタによる確認応答

スレーブから読取りを続けるために、マスタは各バイトの受信後に確認応答を生成しなければなりません。マスタは、各確認応答ビットに対してクロックパルスを生成する必要があり、確認に関係したクロックパルスのハイ期間中にSDAがローで安定するように、確認クロックパルスの間にSDAをローに駆動します。セットアップおよびホールド時間(SCLの立下りエッジ後のt<sub>HD:DAT</sub>とSCLの立上りエッジ前のt<sub>SU:DAT</sub>)もマスタに適用されます。

### スレーブによる非確認応答

スレーブデバイスは、ビジーであるなどの理由で、データを送受信することができない場合があります。DS28CZ04 は、SMBus モードでは常にそのスレーブアドレスを確認します。しかし、しばらく経って、アクセスモードが不正である、EEPROM 書込みサイクルが進行中であるなどの理由でデバイスがデータの受入れを拒否する場合があります。この場合、DS28CZ04 は拒否するバイトのいずれも確認せずに、確認に関係したクロックパルスのハイ期間中 SDA をハイに保ちます。DS28CZ04 が確認応答しない状況の詳細リストについては、読取りと書込みの項を参照してください。

#### マスタによる非確認応答

データを受信しているある時期に、マスタはスレーブデバイスにデータの終了を通知する必要があります。これを実行する際、マスタはスレーブから受信した最終バイトを確認しません。これに応じて、スレーブは SDA を解放するため、マスタは STOP 条件を生成することができます。

### 図 6. I<sup>2</sup>C/SMBusのタイミング図

#### 読取りと書込み

マスタ側から見ると、DS28CZ04 はアドレス範囲が 512 バイトのメモリデバイスのように動作します。図 2 のメモリマップに示すように、DS28CZ04 は SRAM、EEPROM、および読取り専用領域といった複数のタイプのメモリを備えています。書込み動作は、メモリタイプとアドレス指定される場所の特性によって異なります。SRAM レジスタには、一度に 1 バイトから複数バイトを書き込むことができます。EEPROM には、メモリ位置に応じて一度に 1 バイトから 16 または 8 バイトを書き込むことができます。

DS28CZ04 に書き込むためには、マスタは書込みアクセスモードでデバイスをアドレス指定する必要があります。すなわち、方向 ビットを 0 に設定してスレーブアドレスを送信する必要があります。また、スレーブアドレスは、メモリのいずれの半分がアクセス されているかを判断します。書込みアクセスモードで送信される次のバイトは、書き込まれるメモリ位置(「書込みポインタ」)、または データを送信せずに書込みアクセスを終了する(「ダミー書込み」)場合は読取りを開始するメモリ位置(「読取りポインタ」)のアドレスです。追加バイトは、アドレス指定されたメモリ位置のデータと判断されます。

DS28CZ04 から読み取るためには、マスタは読取りアクセスモードでデバイスをアドレス指定する必要があります。すなわち、方向 ビットを 1 に設定してスレーブアドレスを送信する必要があります。読取りポインタは、マスタが読取りを開始する位置を決定します。 ポインタを設定するためには、前記のように、DS28CZ04を書込みアクセスモードでアドレス指定する必要があります。

#### 書込みアクセス

各種のメモリタイプ、特別機能レジスタ、PIO アクセスレジスタ、およびアドレスモードによって、下記のさまざまな事例があります。

通常の EEPROM 16 バイトの EEPROM ブロック

ショート EEPROM 8 バイトの EEPROM ブロック

● 特別 EEPROM 少なくとも 1 つの書込み不可能なバイトを有する 16 バイトの EEPROM ブロック

● 予備 16 の書込み不可能なバイトのブロック

● SRAM 書込み PIO 読取り/書込みアクセスレジスタを含む SRAM バイト

● PIO 直接アクセス PIO 読取り/書込みアクセスレジスタのみ

表 1A では、さまざまな事例を適切なメモリアドレスにマップしてデバイスの動作を詳しく説明します。すべての EEPROM 書込みは WP ピンの状態によって異なります。EEPROM が書込み保護されていないとき(WP ピン状態 = 0)のみ、データが受け付けられて EEPROM に転送されます。PIO 読取り/書込みレジスタのアドレス範囲に書き込むか、またはアドレスをじかに指定してこれらの レジスタに書き込むとき、PIO マルチアドレスモードと PIO シングルアドレスモードをさらに区別する必要があります。アドレス モードは、アドレス 7Ah の方向および制御/ステータスレジスタ(デバイスアドレス = A0h)の ADMD ビットによって選択されます。 マルチアドレスモードでは、各 PIO が 1 つのメモリアドレスを専有しますが、シングルアドレスモードではすべての PIO が 1 つの アドレスを共有します。詳しくは PIO 読取り/書込みアクセスレジスタの説明を参照してください。PIO アドレスモードは、EEPROM セクションに書き込む際にデバイスの動作に影響を与えません。

#### EEPROM 位置への書込み

DS28CZ04 が書込みアクセスモードでアドレス指定されると、アドレスに続くデータバイトは宛先アドレスの 4 つの最下位ビットによって決まるオフセットで始まる 16 バイトバッファに書き込まれます。このバッファは、アドレス指定された 16 バイトEEPROM ブロックのデータで初期化(プリロード)されます。受信データはプリロードされたデータに置き代わります。すべてのバイトを受信すると、バッファの書込みポインタと読取りポインタがインクリメントされます。バッファの書込みポインタが 1111b (通常のEEPROMと特殊EEPROM)または 0111b (ショートEEPROM)の最大値に達して追加データが受信されると、ポインタはラップアラウンド(ロールオーバ)して受信データはEEPROM書込みバッファの最初に書き込まれ、以後書込みが継続されます。同じラップアラウンドは、読取りポインタの 4 つの最下位ビットにも適用されます。こうして、読取りポインタは、1 だけインクリメントされて書込み動作中にアクセスされた最終アドレスを維持します。バッファからEEPROMへの転送は、マスタがSTOP条件を生成したときに始まります。書込みサイクルが終了するまで、DS28CZ04 はterogの期間、ビジーです。

#### 表 1A. 書込みアクセス

|                   | WRITING WHILE DEVICE IS NOT BUSY                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PIO Mode          | Starting Address                                                                                                                                                   | SMBus or I <sup>2</sup> C Bus Mode                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                   | Device address = A0h,<br>any 16-byte block except<br>70h to 7Fh;<br>Device address = A2h,<br>any 16-byte block except<br>60h to 6Fh, F0h to FFh<br>(normal EEPROM) | If WP pin is tied to GND: Slave address is acknowledged; memory address is acknowledged, data is acknowledged; write pointer increments and wraps around from end of block to beginning of block, read pointer = write pointer +1.  If WP pin is tied to V <sub>cc</sub> : data is not acknowledged, no EEPROM write cycle takes place; everything else remains the same. |  |  |  |

|                   | Device address = A0h,<br>memory address from<br>70h to 77h (short<br>EEPROM)                                                                                       | Same as "normal EEPROM" <b>except</b> that <b>write</b> pointer wraps around from <b>77h to 70h</b> .                                                                                                                                                                                                                                                                     |  |  |  |

| Multi-<br>Address | Device address = A2h,<br>memory address from<br>60h to 6Fh (special<br>EEPROM)                                                                                     | SFF mode off: same as "normal EEPROM". SFF mode on: data for address 6Eh is not acknowledged; everything else is the same as with "normal EEPROM".                                                                                                                                                                                                                        |  |  |  |

|                   | Device address = A2h,<br>memory address from<br>F0h to FFh (reserved)                                                                                              | Same as "normal EEPROM" <b>except</b> that data is <b>not</b> acknowledged.                                                                                                                                                                                                                                                                                               |  |  |  |

|                   | Device address = <b>A0h</b> ,<br>memory address from<br><b>78h to 7Bh</b> (SRAM write)                                                                             | Slave address is acknowledged; memory address is acknowledged, data for address <b>78h and 79h</b> is <b>not</b> acknowledged; <b>write</b> pointer increments and wraps around from <b>7Fh to 7Ah</b> , <b>read</b> pointer = write pointer +1.                                                                                                                          |  |  |  |

|                   | Device address = <b>A0h</b> ,<br>memory address from<br><b>7Ch to 7Fh</b> (PIO direct)                                                                             | Slave address is acknowledged; memory address is acknowledged, data is acknowledged; write pointer increments and wraps around from 7Fh to 7Ch, read pointer = write pointer +1.                                                                                                                                                                                          |  |  |  |

| Single-           | Device address = A0h,<br>memory address from<br>78h to 7Fh excluding<br>7Ch (SRAM write)                                                                           | Slave address is acknowledged; memory address is acknowledged, data for addresses <b>7Dh to 7Fh and 78h to 79h</b> is <b>not</b> acknowledged; <b>write</b> pointer increments and wraps around from <b>7Fh to 7Ah</b> , <b>read</b> pointer = write pointer +1.                                                                                                          |  |  |  |

| Address           | Device address = <b>A0h</b> ,<br>memory address = <b>7Ch</b><br>(PIO direct)                                                                                       | Slave address is acknowledged; memory address is acknowledged, data is acknowledged; write pointer stays at 7Ch; read pointer stays at 7Ch.                                                                                                                                                                                                                               |  |  |  |

|                   | All other cases                                                                                                                                                    | Same as in PIO Multi-Address Mode.                                                                                                                                                                                                                                                                                                                                        |  |  |  |

#### ビジーポーリング

ビジーの間、DS28CZ04の動作は、アドレス 7Ahの方向および制御ステータスレジスタ(デバイスアドレス = A0h)の CM ビットによって選択される通信モードで決まります。表 1Bと 2Bは詳細を示します。PIO アドレスモードは、ビジーのときデバイスの動作に影響を与えません。

I<sup>2</sup>Cバスモードでは、ビジーのとき、書込みサイクルが終了するまでDS28CZ04 はそのスレーブアドレスに確認応答しません。 マスタは、スレーブアドレス/方向バイトを送信し、アドレスが確認されたかどうかを判断してデバイスにアクセスすることができます。 DS28CZ04 が確認応答するとすぐに、マスタはデバイスが後続のアクティビティの準備が整ったことを認識します。

**SMBus モード**では、DS28CZ04 はそのスレーブアドレスを必ず確認します。マスタが書込みサイクルの終了を検出するためには、 方向および制御/ステータスレジスタ(デバイスアドレス = A0h)のビジービットによるしか方法はありません。このビットにアクセスするために、マスタは書込みアクセスモードの DS28CZ04 (デバイスアドレス = A0h)にまずアクセスして、メモリアドレスを 7Ah に設定する必要があります(表 1B 参照)。ここで、マスタは読取りアクセスモードの DS28CZ04 のアドレスを指定して SCL にパルス を生成し、STOPを送出せずにデータを 1 バイトずつ読み取ることができます(表 2B 参照)。 最終的に、ビジービットは 1 から 0 に変化して書込みサイクルの終了を知らせます。ビジービットは、読み取られる前のバイトの送信中にサンプリングされるため、 読み取られた状態は必然的に、実際の状態ではなくサンプリング時点の状態を表します。ビジービットの実際の状態は、マスタが a) 最大データレートを読み取るか、b) 2 バイトを順番に遅延なしで読み取って 2 番目のバイトのビジービットを使用するか、または c) ループ内で 1 バイトを読み取り、STOP を送出し、待機し、読取りポインタを移動し、読み取りモードの DS28CZ04 をアドレス指定して別のステータスバイトを得るか、のいずれかによって実現します。

### 表 1B. ビジーポーリングの準備

| WRITING WHILE DEVICE IS BUSY |                                                              |                                                                                                                                                     |                                                                                                   |  |

|------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--|

| PIO Mode                     | Starting Address                                             | SMBus Mode                                                                                                                                          | I <sup>2</sup> C Bus Mode                                                                         |  |

| Either<br>Address<br>Mode    | Device Address = <b>A0h</b> ,<br>memory address = <b>7Ah</b> | Slave address is acknowledged; memory address is acknowledged; data is not acknowledged; write pointer keeps its last position; read pointer = 7Ah. | Slave address is NOT ac-<br>knowledged; memory ad-<br>dress is not acknowledged;                  |  |

|                              | Device Address = A0h,<br>any memory address<br>except 7Ah    | Slave address is acknowledged;<br>memory address is not acknowl-<br>edged; data is not acknowledged;                                                | data is not acknowledged; write pointer keeps its last position; read pointer = write pointer +1. |  |

|                              | Device Address = <b>A2h</b> , any memory address             | write pointer keeps its last position; read pointer = write pointer +1.                                                                             |                                                                                                   |  |

### 表 2B. ビジーポーリング

| READING WHILE DEVICE IS BUSY |                                                              |                                                                              |                                                                                    |  |

|------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|

| PIO Mode                     | Read Pointer                                                 | SMBus Mode                                                                   | I <sup>2</sup> C Bus Mode                                                          |  |

| Either<br>Address<br>Mode    | Device Address = <b>A0h</b> ,<br>memory address = <b>7Ah</b> | Slave address is acknowledged; data is delivered; read pointer stays at 7Ah. | Slave address is NOT acknowledged; no data is delivered; read pointer stays as is. |  |

|                              | Device Address = A0h,<br>excluding memory<br>address 7Ah     | Slave address is acknowledged; no data is delivered; <b>read</b> pointer     |                                                                                    |  |

|                              | Device Address = <b>A2h</b> , any memory address             | = last write pointer +1.                                                     |                                                                                    |  |

### SRAM および PIO 位置への書込み

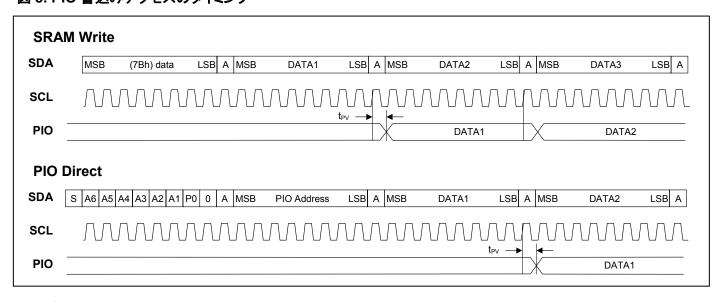

DS28CZ04 を書込みアクセスモードでアドレス指定する場合、アドレスに続くデータバイトはこれらの各メモリ位置にじかに書き込まれます。PIO アドレスモードは、PIO 読取り/書込みアクセスレジスタに書き込む際にデバイスの動作を制御します。PIO アドレス範囲に書き込むかどうか(SRAM 書込み)や PIO アドレスで開始するかどうか(PIO 直接アクセス)に応じて、ポインタおよびデータ確認動作は異なります。表 1A は詳細を示します。PIO アドレスモードは、ポインタの動作に影響を与えるもう 1 つのパラメータです。図 7 は、考えられる事例とアドレスにアクセスする順番を示します。

両 SRAM 書込み事例に共通する特徴は、**PIO アクセスに使用されるアドレスを除く**、SRAM ブロック(アドレス範囲 = 78h~7Fh) の先頭アドレスです。書込み可能なレジスタ(7Ah、7Bh および PIO 読取り/書込みアクセスの有効アドレス)のデータは確認されます。 すなわち、書込みポインタはインクリメントし、アドレス 7Fh の後、7Ah にロールオーバします。

両 PIO 直接アクセス事例に共通する特徴は、**PIO アクセスに使用されるアドレス範囲内の**先頭アドレスです。PIO マルチアドレス モードでは、こうしたアドレスが 4 つ(7Ch~7Fh)あり、各 PIO は独自のアドレスを専有しています。データは必ず確認されます。 すなわち、書込みポインタは次の PIO にインクリメントし、その後 7Ch にラップアラウンドします。PIO シングルアドレスモードでは、 すべての PIO が共有するただ 1 つのアドレス(7Ch)があります。 データは必ず確認され、書込みポインタは 7Ch に留まります。

#### 図 7. SRAM および PIO 書込み

|               | Memory     | Location | PIO Multi-Ad | dress Mode | PIO Single-Address Mode |            |

|---------------|------------|----------|--------------|------------|-------------------------|------------|

|               | Address    | Function | SRAM Write   | PIO Direct | SRAM Write              | PIO Direct |

|               | 00h to 77h | Memory   |              |            |                         |            |

|               | 78h        | Reserved |              |            |                         |            |

|               | 79h        | Reserved |              |            |                         |            |

| <b>_</b>      | 7Ah        | Register |              |            |                         |            |

| Lower Half    | 7Bh        | Register |              |            |                         |            |

| owe           | 7Ch        | PIO R/W  |              | 7          |                         | ••         |

|               | 7Dh        | PIO R/W  |              |            |                         |            |

|               | 7Eh        | PIO R/W  |              |            |                         |            |

|               | 7Fh        | PIO R/W  |              |            |                         |            |

|               | 80h to FFh | Memory   |              |            |                         |            |

| Upper<br>Half | 00h to FFh | Memory   |              |            |                         |            |

PIOに書き込むとき、図8に示すように、状態変化はPIO読取り/書込みアクセスレジスタに書き込まれるバイトの確認応答ビット用にマスタが生成するSCLパルスによってトリガされます。出力の遷移時間 $t_{PV}$ が経過すると、状態変化が終了します。PIOシングルアドレスモードでは、すべてのPIOの状態がほぼ同時に変化します。このモードでは、PIOの状態変化の最速レートは $f_{SCL}/9$ です。PIOマルチアドレスモードでは、APIOが個別にアクセスされます。永久ループで書き込むこのモードでは、PIOの状態変化の最速レートは $f_{SCL}/36$ です。データの転送は、STOP条件によって随時停止されます。このとき、最新確認段階で存在するデータは有効です。

### 図 8. PIO 書込みアクセスのタイミング

#### メモリ読取りと PIO

DS28CZ04 が読取りアクセスモードでアドレス指定されると、読取りポインタはマスタが読取りを開始する位置を決定します。読取りポインタは DS28CZ04 がデータ書込みのためやダミー書込みによって書込みアクセスモードでアクセスされるとき設定されます。

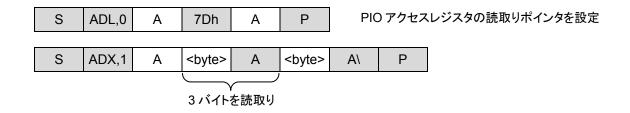

電源投入時、読取りポインタはメモリの下位半分のアドレス 00h にリセットされます。読取りポインタが書込みアクセス中にどのような影響を受けるかについて表 1A に説明されています。メモリが 8 または 16 バイトの小ブロックで更新される書込みアクセスとは対照的に、512 バイトすべてが 1 回の読取りアクセスで読取り可能です。通常読取りと PIO 直接アクセスの 2 つの事例のみを区別する必要があります。表 2A はこれらの事例を詳しく示します。

### 表 2A. 読取りアクセス

|          | READING WHILE DEVICE IS NOT BUSY                                                      |                                                                                                                                                                                                     |  |  |  |

|----------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PIO Mode | Read Pointer                                                                          | SMBus or I <sup>2</sup> C Bus Mode                                                                                                                                                                  |  |  |  |

| Multi-   | Anywhere excluding device address = A0h, memory address from 7Ch to 7Fh (normal read) | Slave address is acknowledged; data is delivered; read pointer increments, eventually crossing from lower half to upper half of the memory, and wraps around from upper half FFh to lower half 00h. |  |  |  |

| Address  | Device address = A0h,<br>memory address from<br>7Ch to 7Fh (PIO direct)               | Slave address is acknowledged; data is delivered; read pointer increments and wraps around from 7Fh to 7Ch, staying in the lower half of memory.                                                    |  |  |  |

| Single-  | Anywhere excluding device address = A0h, memory address = 7Ch (normal read)           | Slave address is acknowledged; data is delivered; read pointer increments, eventually crossing from lower half to upper half of the memory, and wraps around from upper half FFh to lower half 00h. |  |  |  |

| Address  | Device address = A0h,<br>memory address = 7Ch<br>(PIO direct)                         | Slave address is acknowledged; data is delivered; read pointer stays at 7Ch.                                                                                                                        |  |  |  |

PIO アドレスモードは、初期の読取りポインタ位置でアドレスがアクセスされる順序を決定します。図 9 は考えられる事例を示します。

### 図 9. メモリと PIO 読取り

|               | Memory     | Location | PIO Multi-Ad | Idress Mode | PIO Single-Address Mode |            |  |

|---------------|------------|----------|--------------|-------------|-------------------------|------------|--|

|               | Address    | Function | Normal Read  | PIO Direct  | Normal Read             | PIO Direct |  |

|               | 00h to 77h | Memory   |              |             |                         |            |  |

|               | 78h        | Reserved | > •          |             | > •                     |            |  |

|               | 79h        | Reserved |              |             |                         |            |  |

| f             | 7Ah        | Register |              |             |                         |            |  |

| Lower Half    | 7Bh        | Register |              |             |                         |            |  |

| owe           | 7Ch        | PIO R/W  |              |             |                         | ••         |  |

|               | 7Dh        | PIO R/W  |              |             |                         |            |  |

|               | 7Eh        | PIO R/W  |              |             |                         |            |  |

|               | 7Fh        | PIO R/W  |              |             |                         |            |  |

|               | 80h to FFh | Memory   |              |             |                         |            |  |

| Upper<br>Half | 00h to FFh | Memory   |              |             |                         |            |  |

2 つの通常読取り事例に共通する特徴は、PIO アクセスに使用されるアドレスを除く、メモリの任意の場所における先頭アドレスです。読取りポインタは各バイトの読取り後にインクリメントします。こうして、一連の読取りアクセスによって重複したり途切れたりすることのない連続アドレスのメモリデータが実現します。予備領域から読み取る際は、マスタが FFh バイトを受信します。メモリの上位半分(デバイスアドレス = A2h、アドレス = FFh)の最後に達すると、読取りポインタはメモリの下位半分(デバイスアドレス = A0h、アドレス = 00h)の先頭にラップアラウンドします。メモリの下半分の最後に達すると、読取りポインタはメモリの上半分の最初から読取りを続けます。読取りアドレスを変更するためには、マスタは書込みアクセスモードで DS28CZ04 をアドレス指定して新しいメモリアドレスを指定する必要があります。

2つの PIO 直接アクセス事例に共通する特徴は、PIO アクセスに使用されるアドレス範囲内の先頭アドレスです。PIO マルチアドレスモードでは、こうしたアドレスが 4 つ(7Ch~7Fh)あり、各 PIO は独自のアドレスを専有しています。1 つのバイトがマスタに送信されると、読取りポインタは次の PIO にインクリメントし、その後 7Ch にラップアラウンドします。PIO シングルアドレスモードでは、すべての PIO が共有するただ 1 つのアドレス(7Ch)があります。その結果、マスタは読取りを続けることができますが読取りポインタは 7Ch に留まります。

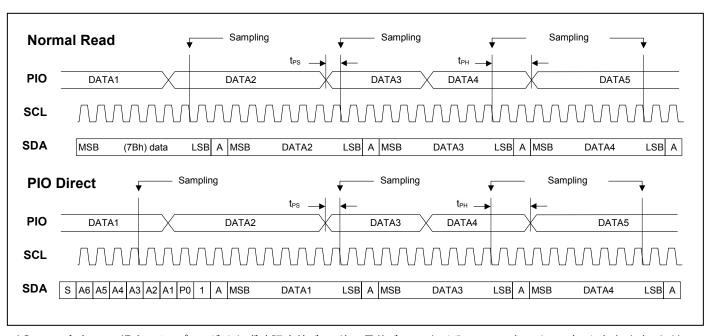

PIOから読み取る際は、図10に示すように、確認応答ビット前の第2最終ビットにおけるSCLの立下りエッジでサンプリングが行われます。PIO直接アクセスモードの場合、最初のサンプルは3 SCLサイクル早く、すなわち、スレーブアドレスの3Aビットを送信する間に採取されます。正しく評価するためには、PIOの状態が $t_{PS}$ と $t_{PH}$ の間に変化してはなりません。PIOシングルアドレスモードでは、すべてのPIOが同時にサンプリングされます。すなわち、PIO直接アクセスのこのモードでは、PIOに関する最速のサンプリングレートが $f_{SCL}$ /9です。PIOマルチアドレスモードでは、各PIOが個別にサンプリングされます。すなわち、PIO直接アクセスのこのモードでは、PIOに関する最速のサンプリングレートが $f_{SCL}$ /36です。データの転送はSTOP条件によって随時停止されます。このとき、最終サンプリング段階のデータは失われます。

#### 図 10. PIO 読取りアクセスのタイミング

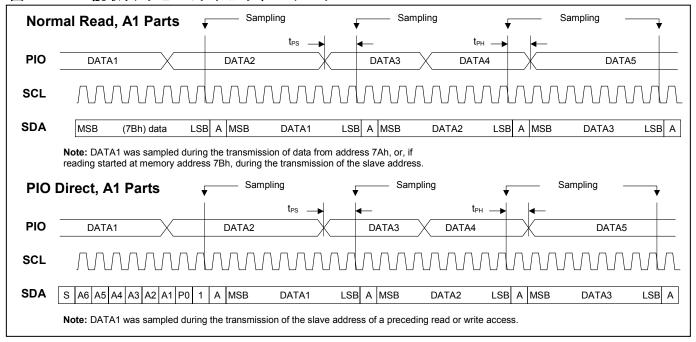

改訂 A1 デバイスの場合、サンプリングは必ず確認応答ビット前の最終ビットにおける SCL の立下りエッジで行われます。ただし、サンプリングされたデータは、図 10A に示すように、1 バイト後にマスタに通知されます。PIO 直接アクセスでマスタが受信する PIO データの最初のサンプルは、破棄される必要があります。これは、スレーブアドレスの送信を基準とする PIO データのタイミングが未定義であるためです。改訂 A1 デバイス用に開発されたアプリケーションファームウェアは、これよりも新しいデバイスに完全対応しています。

### 図 10A. PIO 読取りアクセスのタイミング、A1 デバイス

## I<sup>2</sup>C/SMBus通信 — 凡例

| 記号    | 説明                 |  |  |

|-------|--------------------|--|--|

| S     | START 条件           |  |  |

| ADL,0 | 下位半分に対する書込みアクセスの選択 |  |  |

| ADH,0 | 上位半分に対する書込みアクセスの選択 |  |  |

| ADX,1 | 読取りアクセスの選択         |  |  |

| ADX,X | 任意アクセスの選択          |  |  |

| А     | 確認応答               |  |  |

| 記号        | 説明              |  |  |  |  |

|-----------|-----------------|--|--|--|--|

| xx0xx1xxb | 特定ビットのみを規定するバイト |  |  |  |  |

| Р         | STOP 条件         |  |  |  |  |

| A\        | 非確認応答           |  |  |  |  |

| <br>byte> | 1 バイトの転送        |  |  |  |  |

| AMA       | 任意の8ビットメモリアドレス  |  |  |  |  |

| Sr        | 反復 START 条件     |  |  |  |  |

### コマンド固有の通信―カラーコード

| Master-to-Slave Slave-to-Master | Programming |

|---------------------------------|-------------|

|---------------------------------|-------------|

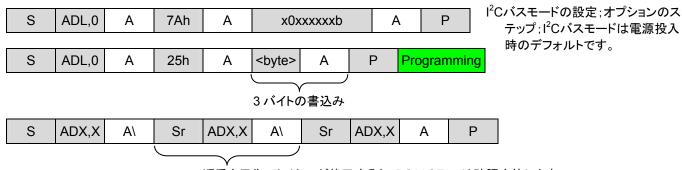

#### 通信の例

#### I<sup>2</sup>Cモードの設定、アドレス 25hで始まる 3 バイトの書込み、メモリの下位半分、サイクル終了の試験

#### SMBus モードの設定、アドレス 25h で始まる 3 バイトの書込み、メモリの上位半分、サイクル終了の試験 SMBus モードを設定;モード設定 S ADL,0 Р 7Ah Α x1xxxxxxb は、次の電源投入または MRZリセットまで有効です。 S Ρ ADH,0 Α 25h Α <byte> **Programming** 3 バイトの書込み ビジービットのポーリング用読取りポインタの設定 7Ah Р S ADL.0 Α Α <byte> S ADX,1 Α <byte> Α Ρ Α <byte> A١ この順序を反復;サイクルが終了すると、ビジービットは0です。 すべてのメモリを読取り、メモリの下位半分で開始 ADL,0 S AMA Α Sr ADX,1 Α <byte> Α <byte> A١ Ρ 読取りポインタを設定 最終バイト 下位半分を選択 511 バイトを読取り SFF モードをオンに設定、SFF オプションステータスレジスタを読取り SFF をオンに設定 S ADL,0 xxx1xxxxb Ρ Α 7Ah Α Α Р オプションステータスレジスタの読取りポインタを設定 S ADH,0 Α 6Eh Α Р S ADX.1 <br/>bvte> A١ マルチアドレスモードで4つのPIO すべてに書込み、PIO0で開始 方向を設定、PIO アドレスモード S ADL,0 7Ah Α 0xxx0000b Α Ρ Α Ρ S ADL.0 Α 7Ch Α <byte> Α 4 バイトを書込み シングルアドレスモードで 4 つの PIO すべてに書込み 方向を設定、PIO アドレスモード S ADL,0 1xxx0000b Р 7Ah Α Α Α Р ADL,0 7Ch <byte> Α マルチアドレスモードで4つの PIO すべてから読取り、PIO1で開始

Α

0xxx1111b

S

ADL,0

7Ah

Р

方向を設定、PIO アドレスモード

#### シングルアドレスモードで 4 つの PIO すべてから読取り

| S | ADL,0 | Α | 7Ah       | Α  | 1xxx1111b |  | Α    | Р     | 方向を設定、PIO アドレスモード |

|---|-------|---|-----------|----|-----------|--|------|-------|-------------------|

| S | ADL,0 | Α | 7Ch       | Α  | P PIO     |  | クセスレ | ジスタの割 | 読取りポインタを設定        |

| S | ADX,1 | Α | <br>byte> | A۱ | Р         |  |      |       |                   |

### アプリケーション情報

#### SDA および SCL のプルアップ抵抗

SDA は DS28CZ04 のオープンドレイン出力であるため、ハイロジックレベルを実現するにはプルアップ抵抗(図 11)が必要です。 DS28CZ04 では SCL を入力としてのみ使用するため(クロック伸縮なし)、マスタはプルアップ抵抗付きのオープンドレイン/コレクタ 出力またはプッシュ/プル出力のいずれかによって SCL を駆動することができます。

### プルアップ抵抗R<sub>P</sub>の大きさ

$I^2$ C仕様によると、スレーブデバイスは 0.4Vの $V_{\text{OL}}$ で少なくとも 3mAをシンクする必要があります。SMBus仕様では、0.4Vで 4mAの電流シンク能力を必要とします。DS28CZ04 は、全動作電圧範囲にわたって 0.4Vの $V_{\text{OL}}$ で少なくとも 4mAをシンクすることができます。CMC この CMC この CMC この CMC ことができます。CMC この CMC この CMC によってプルアップ抵抗の最小値は 1.2k $\Omega$  です。CMC の CMC です。CMC の CMC です。CMC でかいます。CMC でかいます。CMC でかいます。CMC でかいます。CMC です。CMC です。CMC でかいます。CMC でかいます。CMC では、CMC です。CMC です。CMC でかいます。CMC では、CMC でかいます。CMC では、CMC でかいます。CMC でかいます。CMC では、CMC では、CMC でかいます。CMC でかいます

### 図 11. アプリケーション略図 -- マイクロプロセッサポートエクスパンダ

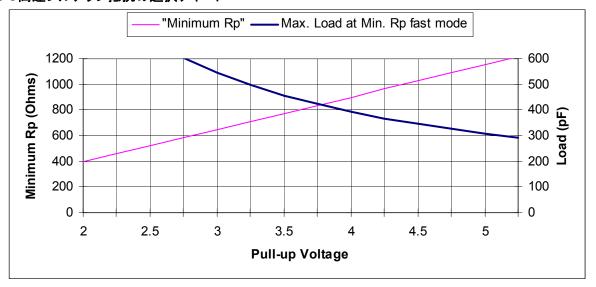

$I^2$ Cシステムでは、立上り時間と立下り時間はプルアップ電圧の 30%~70%で測定されます。最大バス容量 $C_B$ は 400pFです。 最大立上り時間が 300nsを超えてはなりません。最大立上り時間を仮定すると、所定の容量 $C_B$ における最大抵抗値は  $R_{PMAX}$  = 300ns/( $C_B$ \*In(7/3))として求められます。400pFのバス容量では、最大プルアップ抵抗が 885 $\Omega$ となります。

立上り時間仕様と 400pFのバス容量を満たす必要がある 885Ωのプルアップ抵抗は、5.25VにおけるR<sub>PMIN</sub>よりも小さいため、異なる アプローチが必要です。図 12 の「Max. Load」ラインは、所定の動作電圧における最小プルアップ抵抗(「Minimum R<sub>P</sub>」ライン)を計算 した後、300nsの立上り時間を生じるそれぞれのバス容量を計算することによって生成されます。

プルアップ電圧が 4V以下の場合にのみ、400pFの最大許容バス容量を維持することができます。バス容量を 300pFに低減すると、動作電圧の全範囲で受け入れられます。各電圧に対応するプルアップ抵抗の値を「Minimum R<sub>P</sub>」ラインで示しています。

### 図 12. I<sup>2</sup>C高速プルアップ抵抗の選択チャート

#### パッケージ

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、japan.maxim-ic.com/DallasPackInfoをご参照下さい。)