# XFPレーザ制御およびデジタル診断IC

DS1862A

## 概要

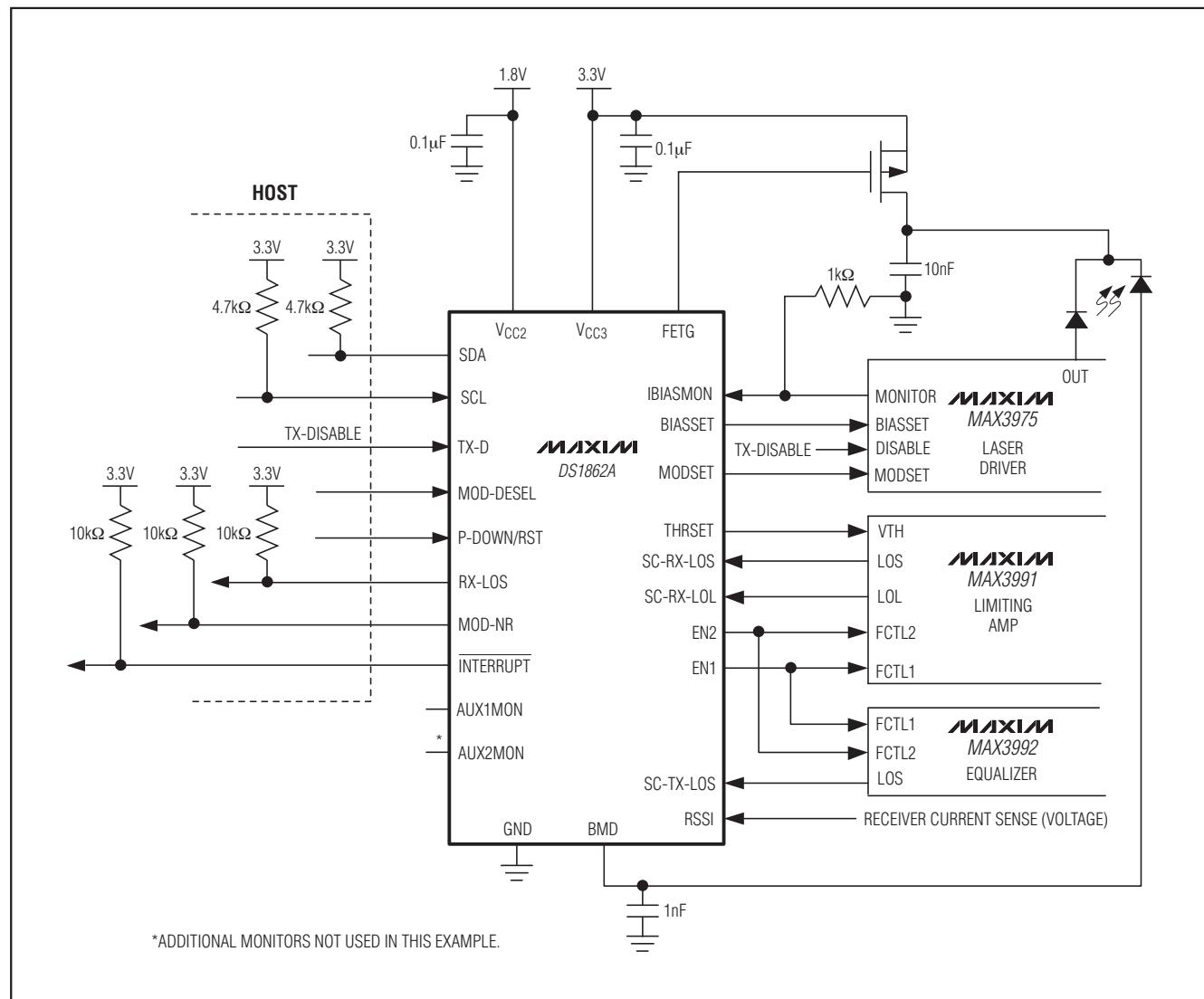

DS1862Aは、XFP MSA用に設計されたデジタル診断を内蔵する閉ループレーザドライバ制御ICです。レーザ制御機能は、自動パワー制御(APC)を搭載し、温度指標付きルックアップテーブル(LUT)によって消光比を制御することができます。DS1862Aは、温度やモニタダイオード(MD)電流などの最大7個のアナログ入力を監視し、これらの入力を使って、レーザバイアス電流および消光比をレギュレートします。監視対象の信号が許容値を上回ると割込みを生成するように、警告/警報スレッショルドをプログラムすることができます。また、監視対象のアナログ信号ごとに独立した、利得およびオフセットスケーリングレジスタによるキャリブレーションも内蔵しています。プログラムされたキャリブレーションデータなどの設定値は、パスワード保護されたEEPROMメモリに保存されます。プログラミングは、I<sup>2</sup>C対応インターフェースを通じて行われ、このインターフェースを使って診断機能にアクセスすることもできます。

## アプリケーション

10Gbps光トランシーバモジュール(XFP)

の

レーザ制御および監視

レーザ制御および監視

光伝送のデジタル診断

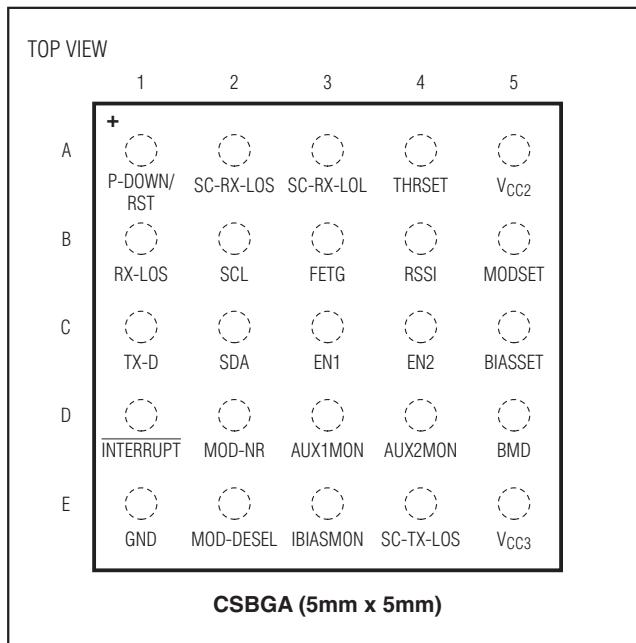

## ピン配置

## 特長

- ◆ デジタル診断、シリアルID、およびユーザメモリのXFP MSA要件を実装

- ◆ I<sup>2</sup>C対応シリアルインターフェース

- ◆ 自動パワー制御(APC)

- ◆ ルックアップテーブルによる消光比制御

- ◆ デジタル診断用の7個の監視対象チャネル(5個の基本および2個の補助チャネル)

- ◆ 監視対象チャネルの内部キャリブレーション(温度、V<sub>CC2/3</sub>、バイアス電流、送受信パワー)

- ◆ 眼の安全に配慮してレーザをオフするプログラマブルな高速トリップロジック

- ◆ 監視およびID情報にアクセス可能

- ◆ プログラマブルな警報/警告スレッショルド

- ◆ 動作電源：3.3Vまたは5V

- ◆ 5mm x 5mmの25ピンCSBGAパッケージ

- ◆ 内部/外部温度センサ

- ◆ 動作温度範囲：-40°C～+100°C

- ◆ 1個のバッファ付き8ビットDAC

## 型番

| PART         | TEMP RANGE      | PIN-PACKAGE |

|--------------|-----------------|-------------|

| DS1862AB+    | -40°C to +100°C | 25 CSBGA    |

| DS1862AB+T&R | -40°C to +100°C | 25 CSBGA    |

+は鉛フリー/RoHS準拠パッケージを示します。

T&R = テープ&リール

標準動作回路はデータシートの最後に記載されています。

# XFPレーザ制御およびデジタル診断IC

DS1862A

## ABSOLUTE MAXIMUM RATINGS

Voltage Range on Any Open-Drain Pin

Relative to Ground ..... -0.5V to +6.0V

Voltage Range on MOD-DESEL, SDA, SCL,

FETG, THRSET, TX-D, AUX1MON, AUX2MON,

IBIASMON, RSSI, BIASSET, MODSET,

EN1, EN2 ..... -0.5V to (VCC3 + 0.5V)\*

Voltage Range on SC-RX-LOS,

SC-RX-LOL, RX-LOS, SC-TX-LOS,

MOD-NR, EN1, EN2 ..... -0.5V to (VCC2 + 0.5V)\*

Operating Temperature Range ..... -40°C to +100°C

EEPROM Programming Temperature Range ..... 0°C to +70°C

Storage Temperature Range ..... -55°C to +125°C

Soldering Temperature ..... Refer to the IPC JEDEC

J-STD-020 Specification.

\*Not to exceed +6.0V.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## RECOMMENDED OPERATING CONDITIONS

(VCC3 = +2.9V to +5.5V, TA = -40°C to +100°C, unless otherwise noted.)

| PARAMETER                                                             | SYMBOL | CONDITIONS                       | MIN           | TYP  | MAX           | UNITS |

|-----------------------------------------------------------------------|--------|----------------------------------|---------------|------|---------------|-------|

| Main Supply Voltage                                                   | VCC3   | (Note 1)                         | +2.9          | +5.5 |               | V     |

| Secondary Supply Voltage                                              | VCC2   | VCC2 not to exceed VCC3 (Note 2) | +1.6          | +3.6 |               | V     |

| High-Level Input Voltage<br>(SDA, SCL)                                | VIH    | I <sub>IIH</sub> (max) = 10µA    | 0.7 x<br>VCC3 |      | VCC3 +<br>0.5 | V     |

| Low-Level Input Voltage<br>(SDA, SCL)                                 | VIL    | I <sub>ILI</sub> (max) = -10µA   | GND -<br>0.3  |      | 0.3 x<br>VCC3 | V     |

| High-Level Input Voltage<br>(TX-D, MOD-DESEL,<br>P-DOWN/RST) (Note 3) | VIH    | I <sub>IIH</sub> (max) = 10µA    | 2             |      | VCC3 +<br>0.3 | V     |

| Low-Level Input Voltage<br>(TX-D, MOD-DESEL,<br>P-DOWN/RST) (Note 3)  | VIL    | I <sub>ILI</sub> (max) = -10µA   | -0.3          |      | +0.8          | V     |

# XFPレーザ制御およびディジタル診断IC

DS1862A

## DC ELECTRICAL CHARACTERISTICS

(V<sub>CC3</sub> = +2.9V to +5.5V, V<sub>CC2</sub> = +1.6V to +3.6V, TA = -40°C to +100°C, unless otherwise noted.)

| PARAMETER                                               | SYMBOL           | CONDITIONS                   | MIN                    | TYP | MAX | UNITS |

|---------------------------------------------------------|------------------|------------------------------|------------------------|-----|-----|-------|

| Supply Current                                          | I <sub>CC3</sub> | P-DOWN/RST = 1               |                        | 3   | 5   | mA    |

| High-Level Output Voltage (FETG)                        | V <sub>OH</sub>  | I <sub>OH</sub> (max) = -2mA | V <sub>CC3</sub> - 0.5 |     |     | V     |

| Low-Level Output Voltage (MOD-NR, INTERRUPT, SDA, FETG) | V <sub>OL</sub>  | I <sub>OL</sub> (max) = 3mA  | 0                      | 0.4 |     | V     |

| Resistor (Pullup)                                       | R <sub>PU</sub>  |                              | 9                      | 12  | 15  | kΩ    |

| I/O Capacitance                                         | C <sub>I/O</sub> | (Note 4)                     |                        | 10  |     | pF    |

| Leakage Current                                         | I <sub>L</sub>   |                              | -10                    | +10 |     | μA    |

| Leakage Current (SCL, SDA)                              | I <sub>L</sub>   |                              | -10                    | +10 |     | μA    |

| Digital Power-On Reset                                  | POD              |                              | 1.0                    | 2.2 |     | V     |

| Analog Power-On Reset                                   | POA              |                              | 2.0                    | 2.6 |     | V     |

## DC ELECTRICAL CHARACTERISTICS — INTERFACE SIGNALS TO SIGNAL CONDITIONERS

(V<sub>CC2</sub> = +1.6V to +3.6V, V<sub>CC3</sub> = +2.9V to +5.5V, TA = -40°C to +100°C, unless otherwise noted.)

| PARAMETER                                                  | SYMBOL           | CONDITIONS                                                    | MIN                    | TYP                    | MAX | UNITS |

|------------------------------------------------------------|------------------|---------------------------------------------------------------|------------------------|------------------------|-----|-------|

| High-Level Input Voltage (SC-RX-LOS, SC-RX-LOL, SC-TX-LOS) | V <sub>IH</sub>  | I <sub>IH</sub> (max) = 100μA                                 | 0.7 x V <sub>CC2</sub> | V <sub>CC2</sub> + 0.1 |     | V     |

| Low-Level Input Voltage (SC-RX-LOS, SC-RX-LOL, SC-TX-LOS)  | V <sub>IL</sub>  | I <sub>IL</sub> (max) = -100μA                                | 0                      | 0.3 x V <sub>CC2</sub> |     | V     |

| High-Level Output Voltage (EN1, EN2)                       | V <sub>OH</sub>  | I <sub>OH</sub> (max) = -0.7mA                                | V <sub>CC2</sub> - 0.2 | V                      |     |       |

|                                                            | V <sub>OH2</sub> | V <sub>CC2</sub> = 2.5V to 3.6V, I <sub>OH</sub> (max) = -2mA | V <sub>CC2</sub> - 0.4 |                        |     |       |

|                                                            | V <sub>OH3</sub> | V <sub>CC2</sub> = 1.6V, I <sub>OH</sub> (max) = -0.7mA       | V <sub>CC2</sub> - 0.2 |                        |     |       |

| Low-Level Output Voltage (EN1, EN2, RX-LOS)                | V <sub>OL</sub>  | I <sub>OL</sub> (max) = 0.7mA                                 |                        | 0.20                   |     | V     |

|                                                            | V <sub>OL2</sub> | V <sub>CC2</sub> = 2.5V to 3.6V, I <sub>OL</sub> (max) = 2mA  |                        | 0.40                   |     |       |

| Leakage Current (SC-RX-LOS, SC-RX-LOL, SC-TX-LOS, RX-LOS)  | I <sub>L</sub>   |                                                               | -10                    | +10                    |     | μA    |

# XFPレーザ制御およびデジタル診断IC

**DS1862A**

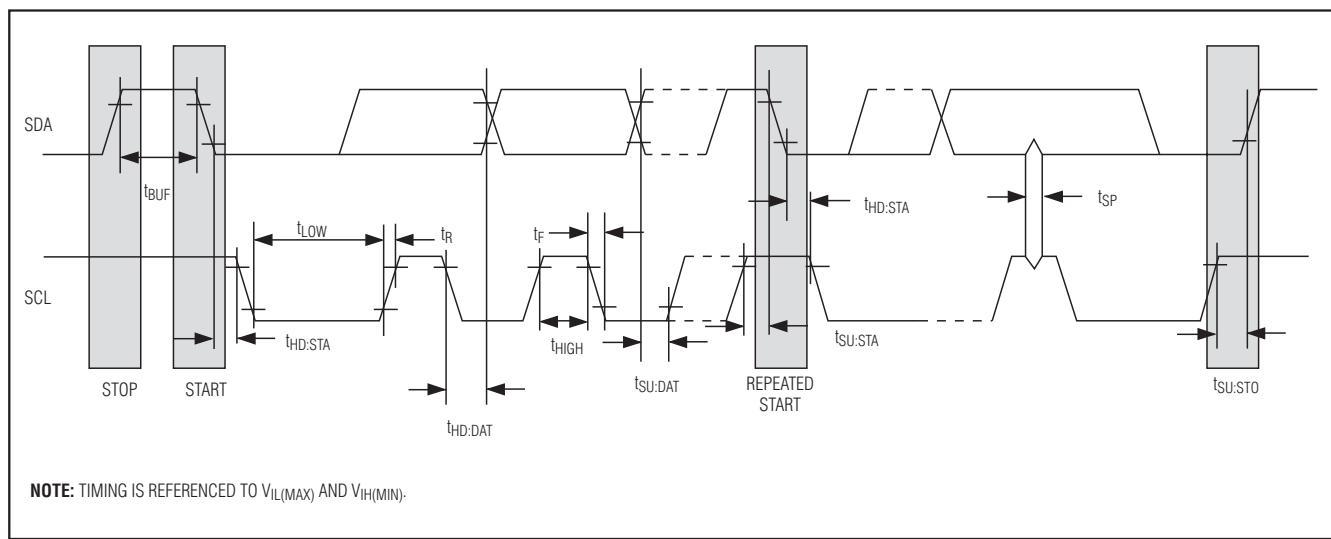

## I<sup>2</sup>C AC ELECTRICAL CHARACTERISTICS

(V<sub>CC3</sub> = +2.9V to +5.5V, T<sub>A</sub> = -40°C to +100°C, unless otherwise noted.)

| PARAMETER                                       | SYMBOL                         | CONDITIONS              | MIN                    | TYP | MAX | UNITS |

|-------------------------------------------------|--------------------------------|-------------------------|------------------------|-----|-----|-------|

| SCL Clock Frequency                             | f <sub>SCI</sub>               |                         | 0                      |     | 400 | kHz   |

| Clock Pulse-Width Low                           | t <sub>LOW</sub>               |                         | 1.3                    |     |     | μs    |

| Clock Pulse-Width High                          | t <sub>HIGH</sub>              |                         | 0.6                    |     |     | μs    |

| Bus Free Time Between STOP and START Conditions | t <sub>BUF</sub>               |                         | 1.3                    |     |     | μs    |

| START Hold Time                                 | t <sub>HD:SDA</sub>            |                         | 0.6                    |     |     | μs    |

| START Setup Time                                | t <sub>SU:SDA</sub>            |                         | 0.6                    |     |     | μs    |

| Data In Hold Time                               | t <sub>HD:DAT</sub>            |                         | 0                      |     | 0.9 | μs    |

| Data In Setup Time                              | t <sub>SU:DAT</sub>            |                         | 100                    |     |     | ns    |

| Rise Time of Both SDA and SCL Signals           | t <sub>R</sub>                 | (Note 5)                | 20 + 0.1C <sub>B</sub> |     | 300 | ns    |

| Fall Time of Both SDA and SCL Signals           | t <sub>F</sub>                 | (Note 5)                | 20 + 0.1C <sub>B</sub> |     | 300 | ns    |

| STOP Setup Time                                 | t <sub>SU:STO</sub>            |                         | 0.6                    |     |     | μs    |

| MOD-DESEL Setup Time                            | t <sub>HOST_SELECT_SETUP</sub> |                         | 2                      |     |     | ms    |

| MOD-DESEL Hold Time                             | t <sub>HOST_SELECT_HOLD</sub>  |                         | 10                     |     |     | μs    |

| Aborted Sequence Bus Release                    | t <sub>MOD-DESEL_ABORT</sub>   |                         |                        |     | 2   | ms    |

| Capacitive Load for Each Bus                    | C <sub>B</sub>                 | (Note 5)                |                        |     | 400 | pF    |

| EEPROM Write Time                               | t <sub>W</sub>                 | ≤ 4-byte write (Note 6) |                        |     | 16  | ms    |

## ANALOG OUTPUT CHARACTERISTICS

(V<sub>CC3</sub> = +2.9V to +5.5V, V<sub>CC2</sub> = +1.6V to +3.6V, T<sub>A</sub> = -40°C to +100°C, unless otherwise noted.)

| PARAMETER                                               | SYMBOL               | CONDITIONS                                     | MIN  | TYP | MAX  | UNITS |

|---------------------------------------------------------|----------------------|------------------------------------------------|------|-----|------|-------|

| I <sub>BIASSET</sub>                                    | I <sub>BIASSET</sub> |                                                | 0.01 |     | 1.50 | mA    |

| I <sub>BIASSET</sub> (Off-State Current)                | I <sub>BIASSET</sub> | Shutdown                                       |      | ±10 | ±100 | nA    |

| I <sub>MODSET</sub>                                     | I <sub>MODSET</sub>  |                                                | 0.01 |     | 1.20 | mA    |

| I <sub>MODSET</sub> (Off-State Current)                 | I <sub>MODSET</sub>  | Shutdown                                       |      | ±10 | ±100 | nA    |

| Voltage on I <sub>BIASSET</sub> and I <sub>MODSET</sub> | V <sub>MAX</sub>     | (Note 7)                                       | 0.7  |     | 3.0  | V     |

| V <sub>THRSET</sub>                                     | V <sub>THRSET</sub>  | I <sub>MAX</sub> = 100μA                       | 50   |     | 1000 | mV    |

| V <sub>THRSET</sub> Drift                               |                      | Across temperature (Note 8)                    | -5   |     | +5   | %     |

| V <sub>THRSET</sub> Capacitance Load                    | C <sub>THRSET</sub>  |                                                |      |     | 1    | nF    |

| APC Calibration Accuracy                                |                      | +25°C                                          |      |     | 25   | μA    |

| APC Temp Drift                                          |                      | 0.200mA to 1.5mA<br>50μA to 200μA              | -5   |     | +5   | %     |

| I <sub>BMD</sub> DNL                                    |                      | Sink, SRC_SINK_B = 0<br>Source, SRC_SINK_B = 1 | -0.9 |     | +0.9 | LSB   |

| I <sub>BMD</sub> INL                                    |                      | Sink, SRC_SINK_B = 0<br>Source, SRC_SINK_B = 1 | -0.9 |     | +0.9 |       |

| I <sub>BMD</sub> Voltage Drift                          |                      |                                                | -4.0 |     | +4.0 | LSB   |

| I <sub>BMD</sub> FS Accuracy                            |                      |                                                | -4.0 |     | +4.0 |       |

# XFPレーザ制御およびディジタル診断IC

## ANALOG OUTPUT CHARACTERISTICS (continued)

( $V_{CC3} = +2.9V$  to  $+5.5V$ ,  $V_{CC2} = +1.6V$  to  $+3.6V$ ,  $T_A = -40^\circ C$  to  $+100^\circ C$ , unless otherwise noted.)

| PARAMETER                         | SYMBOL | CONDITIONS                                     | MIN  | TYP | MAX  | UNITS |

|-----------------------------------|--------|------------------------------------------------|------|-----|------|-------|

| I <sub>MODSET</sub> Accuracy      |        | +25°C, I <sub>MODSET</sub> = 0.04mA to 1.2mA   | -1.5 |     | +1.5 | %     |

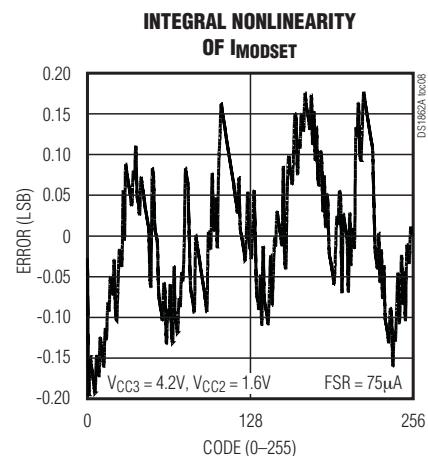

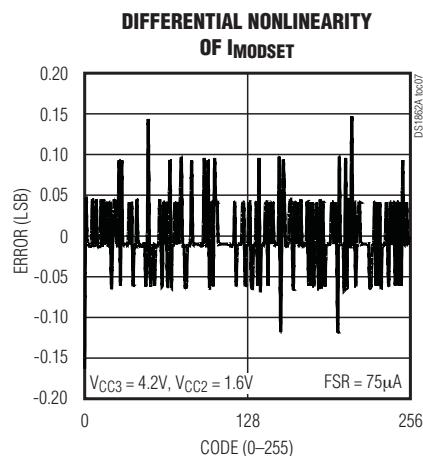

| I <sub>MODSET</sub> DNL           |        | 75µA range                                     | -0.9 |     | +0.9 | LSB   |

|                                   |        | 150µA range                                    | -0.9 |     | +0.9 |       |

|                                   |        | 300µA range                                    | -0.9 |     | +0.9 |       |

|                                   |        | 600µA range                                    | -0.9 |     | +0.9 |       |

|                                   |        | 1200µA range                                   | -0.9 |     | +0.9 |       |

| I <sub>MODSET</sub> INL           |        | 75µA range                                     | -1.5 |     | +1.5 | LSB   |

|                                   |        | 150µA range                                    | -1.5 |     | +1.5 |       |

|                                   |        | 300µA range                                    | -1.0 |     | +1.0 |       |

|                                   |        | 600µA range                                    | -1.0 |     | +1.0 |       |

|                                   |        | 1200µA range                                   | -1.0 |     | +1.0 |       |

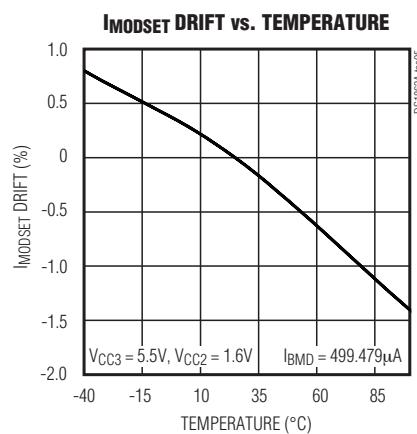

| I <sub>MODSET</sub> Temp Drift    |        |                                                |      |     | 5    | %     |

| I <sub>MODSET</sub> Voltage Drift |        |                                                |      |     | 1.2  | %/V   |

| I <sub>MODSET</sub> FS Accuracy   |        |                                                |      |     | 1.5  | %     |

| APC Bandwidth                     |        | I <sub>MD</sub> /I <sub>APC</sub> = 1 (Note 4) | 6    | 10  | 30   | kHz   |

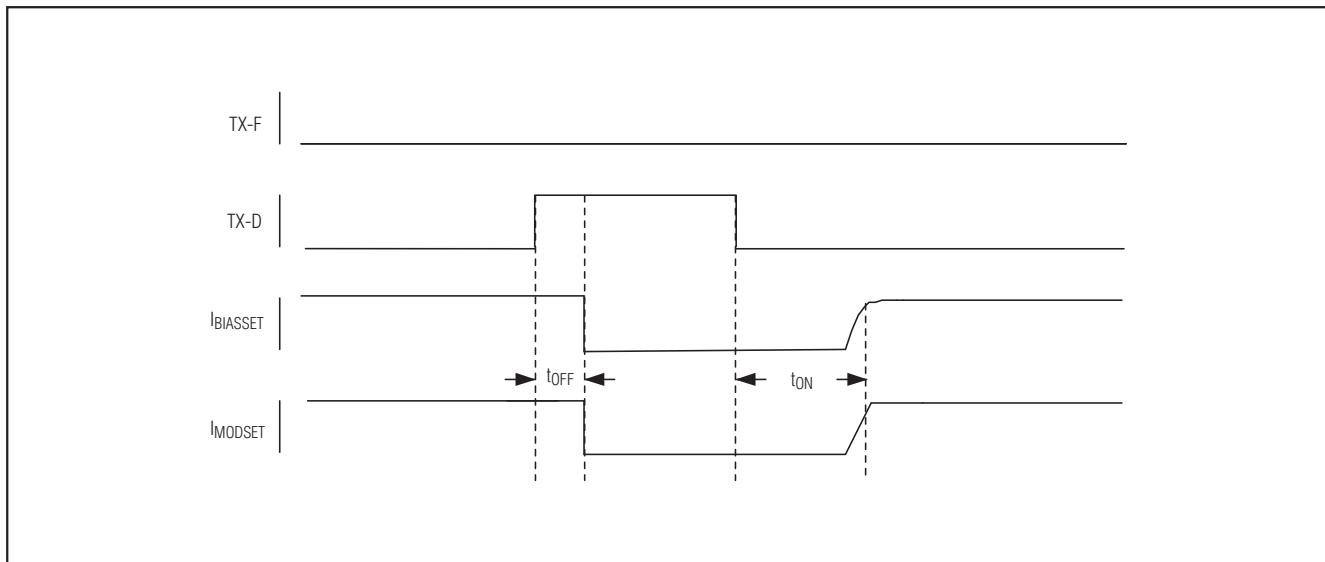

## AC ELECTRICAL CHARACTERISTICS — XFP CONTROLLER

( $V_{CC3} = +2.9V$  to  $+5.5V$ ,  $V_{CC2} = +1.6V$  to  $+3.6V$ ,  $T_A = -40^\circ C$  to  $+100^\circ C$ , unless otherwise noted.)

| PARAMETER                | SYMBOL                  | CONDITIONS                                                                                     | MIN | TYP | MAX | UNITS |

|--------------------------|-------------------------|------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

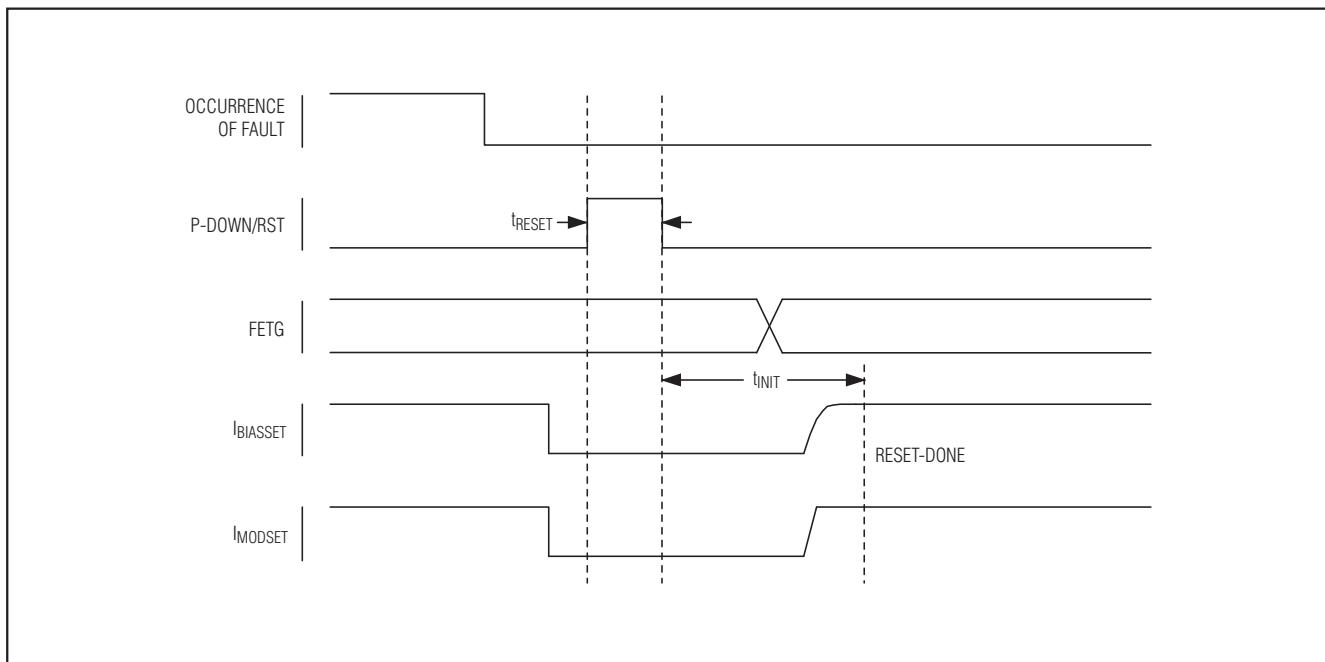

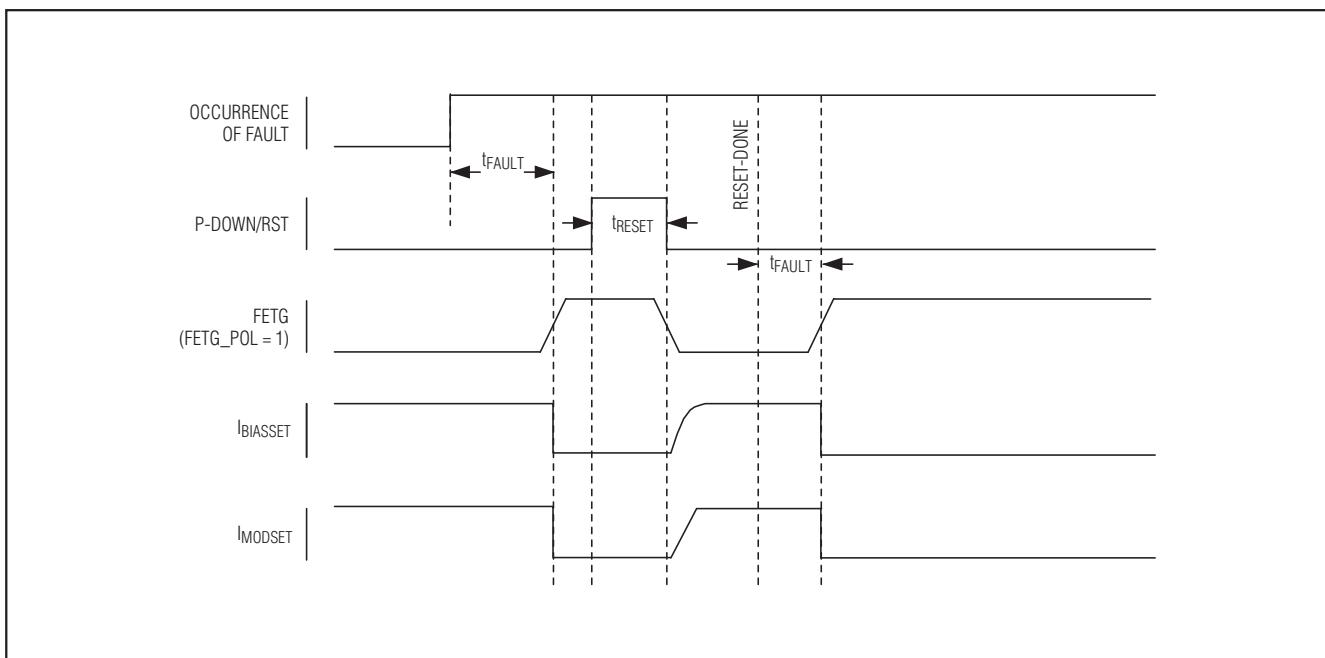

| Time to Initialize       | t <sub>INIT</sub>       | $V_{CC3}$ within $\pm 5\%$ of nominal                                                          | 30  | 200 |     | ms    |

| TX-D Assert Time         | t <sub>OFF</sub>        | I <sub>BIAS</sub> and I <sub>MOD</sub> below 10% of nominal                                    |     | 5   |     | µs    |

| TX-D Deassert Time       | t <sub>ON</sub>         | I <sub>BIAS</sub> and I <sub>MOD</sub> above 90% of nominal                                    |     | 1   |     | ms    |

| P-DOWN/RST Assert Time   | t <sub>PDR-ON</sub>     | I <sub>BIAS</sub> and I <sub>MOD</sub> below 10% of nominal                                    |     | 100 |     | µs    |

| P-DOWN/RST Deassert Time | t <sub>PDR-OFF</sub>    | I <sub>BIAS</sub> and I <sub>MOD</sub> above 90% of nominal                                    |     | 200 |     | ms    |

| MOD-DESEL Deassert Time  | t <sub>MOD-DESEL</sub>  | Time until proper response to I <sup>2</sup> C communication                                   |     | 2   |     | ms    |

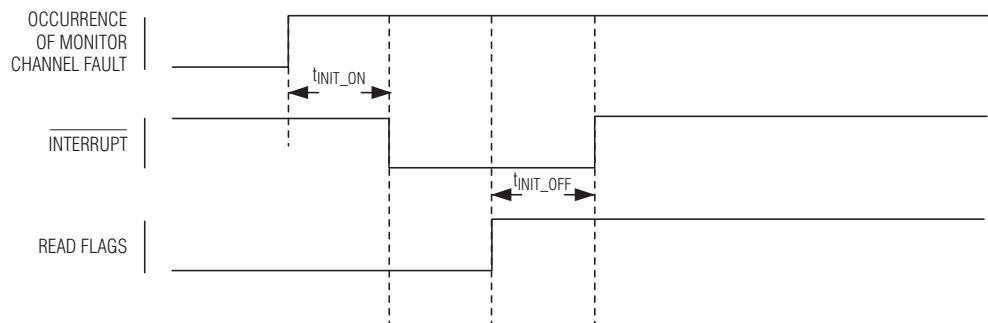

| INTERRUPT Assert Delay   | t <sub>INIT_ON</sub>    | Time from fault to interrupt assertion                                                         |     | 100 |     | ms    |

| INTERRUPT Deassert Delay | t <sub>INIT_OFF</sub>   | Time from read (clear flags) to interrupt deassertion                                          |     | 500 |     | µs    |

| MOD-NR Assert Delay      | t <sub>MOD-NR-ON</sub>  | Time from fault to MOD-NR assertion                                                            |     | 0.5 |     | ms    |

| MOD-NR Deassert Delay    | t <sub>MOD-NR-OFF</sub> | Time from read (clear flags) to MOD-NR deassertion                                             |     | 0.5 |     | ms    |

| RX-LOS Assert Time       | t <sub>LOS-ON</sub>     | Time from SC-RX-LOS assertion to RX-LOS assertion                                              |     | 100 |     | ns    |

| RX-LOS Deassert Time     | t <sub>LOS-OFF</sub>    | Time from SC-RX-LOS deassertion to RX-LOS deassertion                                          |     | 100 |     | ns    |

| P-DOWN/RST Reset Time    | t <sub>RESET</sub>      | Time from P-DOWN/RST assertion to initial reset                                                | 10  |     |     | µs    |

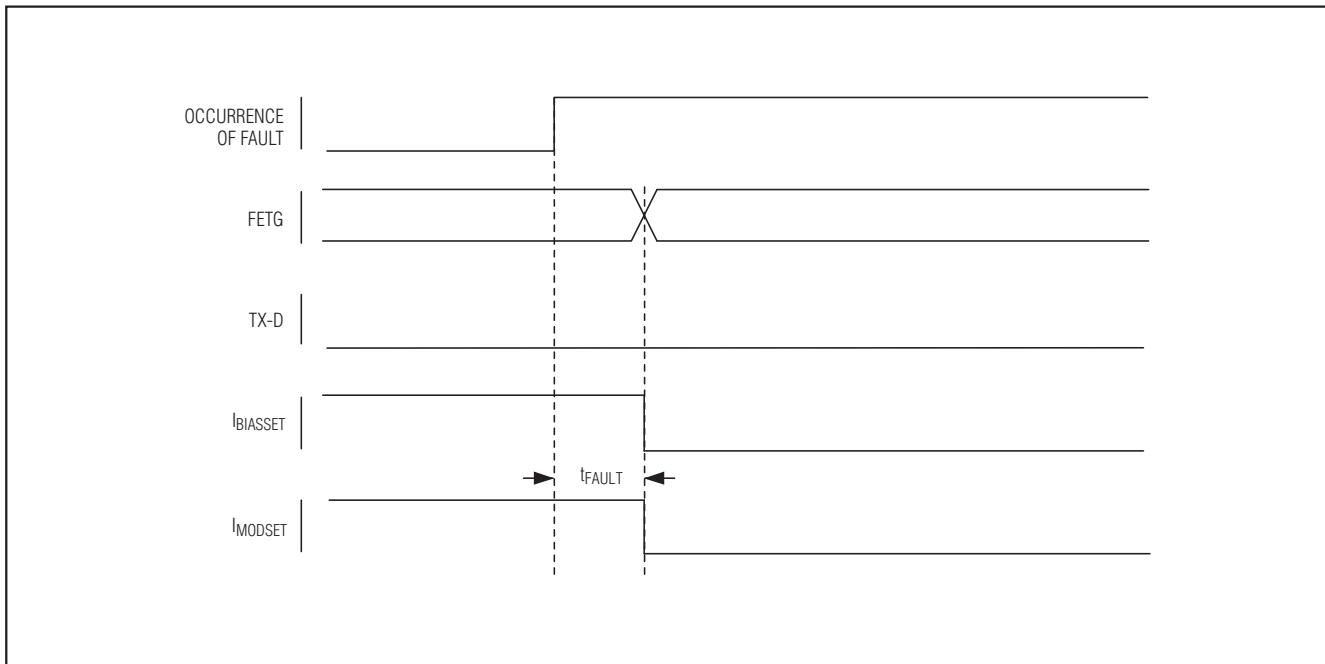

| Shutdown Time            | t <sub>FAULT</sub>      | Time from fault to I <sub>BIASSET</sub> , I <sub>MODSET</sub> , and I <sub>BMD</sub> below 10% |     | 30  |     | µs    |

# XFPレーザ制御およびデジタル診断IC

## AC ELECTRICAL CHARACTERISTICS – SOFT\* CONTROL AND STATUS

(V<sub>CC3</sub> = +2.9V to +5.5V, V<sub>CC2</sub> = +1.6V to +3.6V, T<sub>A</sub> = -40°C to +100°C, unless otherwise noted.)

| PARAMETER                             | SYMBOL                       | CONDITIONS                                                  | MIN | TYP | MAX | UNITS |

|---------------------------------------|------------------------------|-------------------------------------------------------------|-----|-----|-----|-------|

| SOFT TX-D Assert Time                 | t <sub>OFF_SOFT</sub>        | I <sub>BIAS</sub> and I <sub>MOD</sub> below 10% of nominal |     | 50  |     | ms    |

| SOFT TX-D Deassert Time               | t <sub>ON_SOFT</sub>         | I <sub>BIAS</sub> and I <sub>MOD</sub> above 90% of nominal |     | 50  |     | ms    |

| SOFT P-DOWN/RST Assert Time           | t <sub>PDR-ON_SOFT</sub>     | I <sub>BIAS</sub> and I <sub>MOD</sub> below 10% of nominal |     | 50  |     | ms    |

| SOFT P-DOWN/RST Deassert Time         | t <sub>PDR-OFF_SOFT</sub>    | I <sub>BIAS</sub> and I <sub>MOD</sub> above 90% of nominal |     | 200 |     | ms    |

| Soft MOD-NR Assert Delay              | t <sub>MOD-NR-ON_SOFT</sub>  | Time from fault to MOD-NR assertion                         |     | 50  |     | ms    |

| Soft MOD-NR Deassert Delay            | t <sub>MOD-NR-OFF_SOFT</sub> | Time from read (clear flags) to MOD-NR deassertion          |     | 50  |     | ms    |

| Soft RX_LOS Assert Time               | t <sub>LOS-ON_SOFT</sub>     | Time from SC-RX-LOS assertion to RX-LOS assertion           |     | 50  |     | ms    |

| Soft RX_LOS Deassert Time             | t <sub>LOS-OFF_SOFT</sub>    | Time from SC-RX-LOS deassertion to RX-LOS deassertion       |     | 50  |     | ms    |

| Analog Parameter Data Ready (DATA-NR) |                              |                                                             |     | 500 |     | ms    |

\*All SOFT timing specifications are measured from the falling edge of STOP signal during I<sup>2</sup>C communication.

## ANALOG INPUT CHARACTERISTICS

(V<sub>CC3</sub> = +2.9V to +5.5V, T<sub>A</sub> = -40°C to +100°C, unless otherwise noted.)

| PARAMETER                                          | SYMBOL           | CONDITIONS  |                                   | MIN  | TYP | MAX  | UNITS |

|----------------------------------------------------|------------------|-------------|-----------------------------------|------|-----|------|-------|

| I <sub>BMD</sub> Configurable Source or Sink (+/-) |                  |             |                                   | 0.05 |     | 1.50 | mA    |

| I <sub>BMD</sub> Voltage (I <sub>BMD</sub> - 0μA)  | V <sub>BMD</sub> | Source mode | I <sub>BMD</sub> range 0 to 1.5mA | 2.0  |     | V    |       |

|                                                    |                  | Sink mode   |                                   | 1.2  |     |      |       |

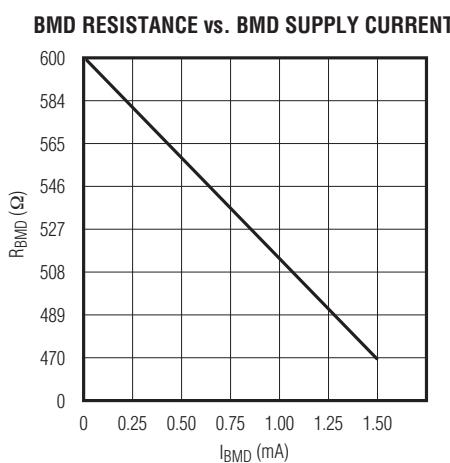

| I <sub>BMD</sub> Input Resistance                  | R <sub>BMD</sub> |             |                                   | 400  | 550 | 700  | Ω     |

## A/D INPUT VOLTAGE MONITORING (IBIASMON, AUX2MON, AUX1MON, RSSI, BMD)

(V<sub>CC3</sub> = +2.9V to +5.5V, T<sub>A</sub> = -40°C to +100°C, unless otherwise noted.)

| PARAMETER                                                                 | SYMBOL              | CONDITIONS                   |  | MIN    | TYP    | MAX    | UNITS |

|---------------------------------------------------------------------------|---------------------|------------------------------|--|--------|--------|--------|-------|

| Input Resolution                                                          | ΔV <sub>MON</sub>   |                              |  |        | 610    |        | μV    |

| Supply Resolution                                                         | ΔV <sub>CC2/3</sub> |                              |  |        | 1.6    |        | mV    |

| Input/Supply Accuracy                                                     | ACC                 | At factory setting           |  | 0.25   | 0.5    |        | %FS   |

| Update Rate                                                               | t <sub>FRAME1</sub> | AUX1MON and AUX2MON disabled |  | 48     | 52     | ms     |       |

|                                                                           | t <sub>FRAME2</sub> | All channels enabled         |  | 64     | 75     |        |       |

| Input/Supply Offset                                                       | V <sub>OS</sub>     | (Note 4)                     |  | 0      | 5      |        | LSB   |

| Full-Scale Input (IBIASMON and RSSI)                                      |                     | At factory setting           |  | 2.4875 | 2.5    | 2.5125 | V     |

| Full-Scale Input (AUX1MON, AUX2MON, V <sub>CC2</sub> , V <sub>CC3</sub> ) |                     | At factory setting (Note 9)  |  | 6.5208 | 6.5536 | 6.5864 | V     |

| BMD (Monitor) (TX-P)                                                      |                     | FS setting                   |  | 1.5    |        |        | mA    |

# XFPレーザ制御およびデジタル診断IC

## FAST ALARMS AND V<sub>CC</sub> FAULT CHARACTERISTICS

(V<sub>CC3</sub> = +2.9V to +5.5V, V<sub>CC2</sub> = +1.6V to +3.6V, TA = -40°C to +100°C, unless otherwise noted.)

| PARAMETER                                            | SYMBOL | CONDITIONS                        | MIN   | TYP   | MAX   | UNITS |

|------------------------------------------------------|--------|-----------------------------------|-------|-------|-------|-------|

| HIGH BIAS and TX-P Threshold FS                      |        | (Note 10)                         | 2.48  | 2.5   | 2.52  | mA    |

| V <sub>CC2/3</sub> Fault Asserted Falling Edge Delay |        | ↓ V <sub>CC2/3</sub><br>(Note 11) |       |       | 75    | ms    |

| QT Temperature Coefficient                           |        |                                   | -3    |       | +3    | %     |

| QT Voltage Coefficient                               |        |                                   |       |       | 0.5   | %/V   |

| QT FS Trim Accuracy (4.2V, +25°C)                    |        |                                   | 2.480 | 2.500 | 2.520 | mA    |

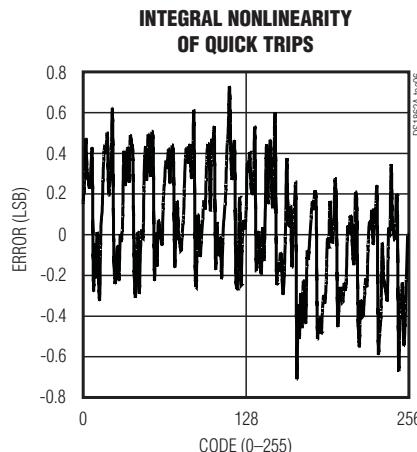

| QT Accuracy (Trip) (INL)                             |        |                                   | -2    | 0     | +2    | LSB   |

| QT Voltco                                            |        |                                   |       |       | 0.5   | %/V   |

| QT Tempco                                            |        |                                   |       | 1.5   | 3     | %     |

## NONVOLATILE MEMORY CHARACTERISTICS

(V<sub>CC3</sub> = +2.9V to +5.5V, unless otherwise noted.)

| PARAMETER               | SYMBOL | CONDITIONS | MIN  | TYP | MAX | UNITS  |

|-------------------------|--------|------------|------|-----|-----|--------|

| Endurance (Write Cycle) |        | +70°C      | 50k  |     |     | Cycles |

| Endurance (Write Cycle) |        | +25°C      | 200k |     |     | Cycles |

**Note 1:** All voltages are referenced to ground. Current into the IC is positive, and current out of the IC is negative.

**Note 2:** Secondary power supply is used to support optional variable power-supply feature of the XFP module. If V<sub>CC2</sub> is not used (i.e., signal conditioners using 3.3V supply), V<sub>CC2</sub> should be connected to the V<sub>CC3</sub>.

**Note 3:** Input signals (i.e., TX-D, MOD-DESEL, and P-DOWN/RST) have internal pullup resistors.

**Note 4:** Guaranteed by design. Simulated over process and 50µA < I<sub>BMD</sub> < 1500µA.

**Note 5:** C<sub>B</sub>—total capacitance of one bus line in picofarads.

**Note 6:** EEPROM write begins after a STOP condition occurs.

**Note 7:** This is the maximum and minimum voltage on the MODSET and BIASSSET pins required to meet accuracy and drift specifications.

**Note 8:** For V<sub>THRSET</sub>, offset may be as much as 10mV.

**Note 9:** This is the uncalibrated offset provided by the factory; offset adjustment is available on this channel.

**Note 10:** %FS refers to calibrated FS in case of internal calibration, and uncalibrated FS in the case of external calibration. Uncalibrated FS is set in the factory and specified in this data sheet as FS (factory). Calibrated FS is set by the user, allowing a change in any monitored channel scale.

**Note 11:** See the *Monitor Channels* section for more detail on V<sub>CC2</sub> and V<sub>CC3</sub> selection.

# XFPレーザ制御およびデジタル診断IC

**DS1862A**

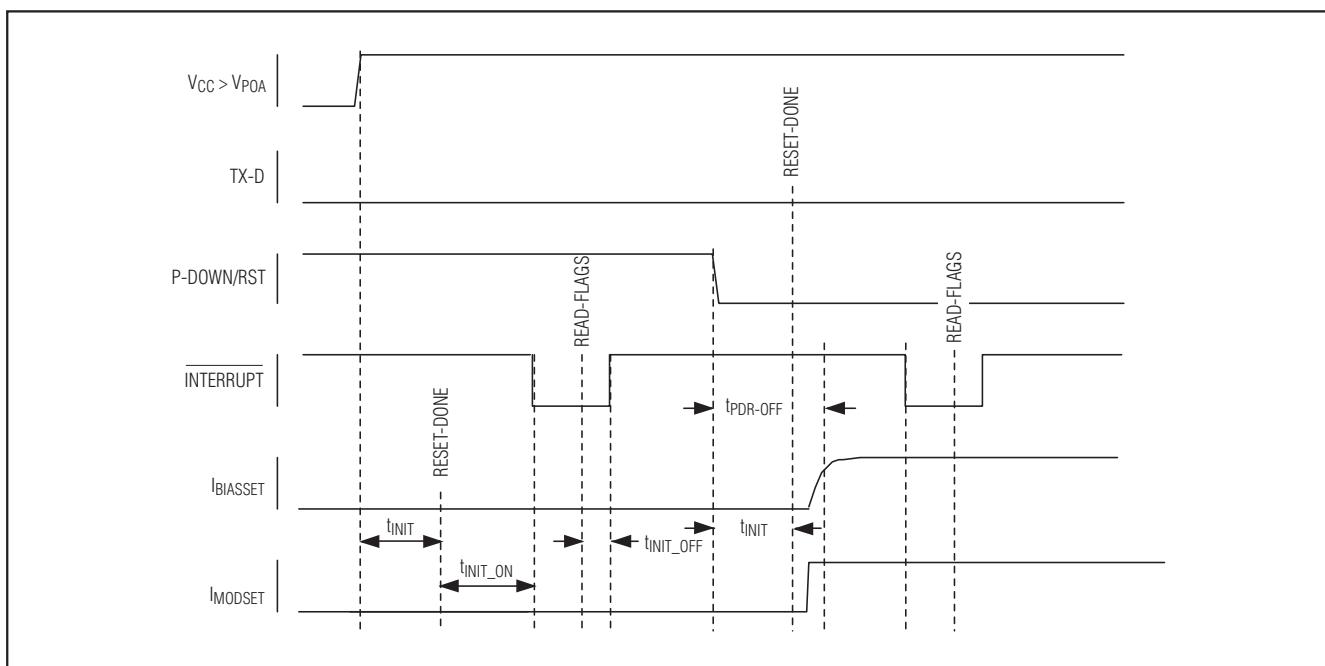

## タイミング図

図1. P-DOWN/RSTがアサート状態でTX-D/SOFT TX-Dが非アサート状態の電源投入時の初期化

図2. P-DOWN/RSTおよびTX-D/SOFT TX-Dが非アサート状態の電源投入時の初期化(通常動作)

# XFPレーザ制御およびデジタル診断IC

DS1862A

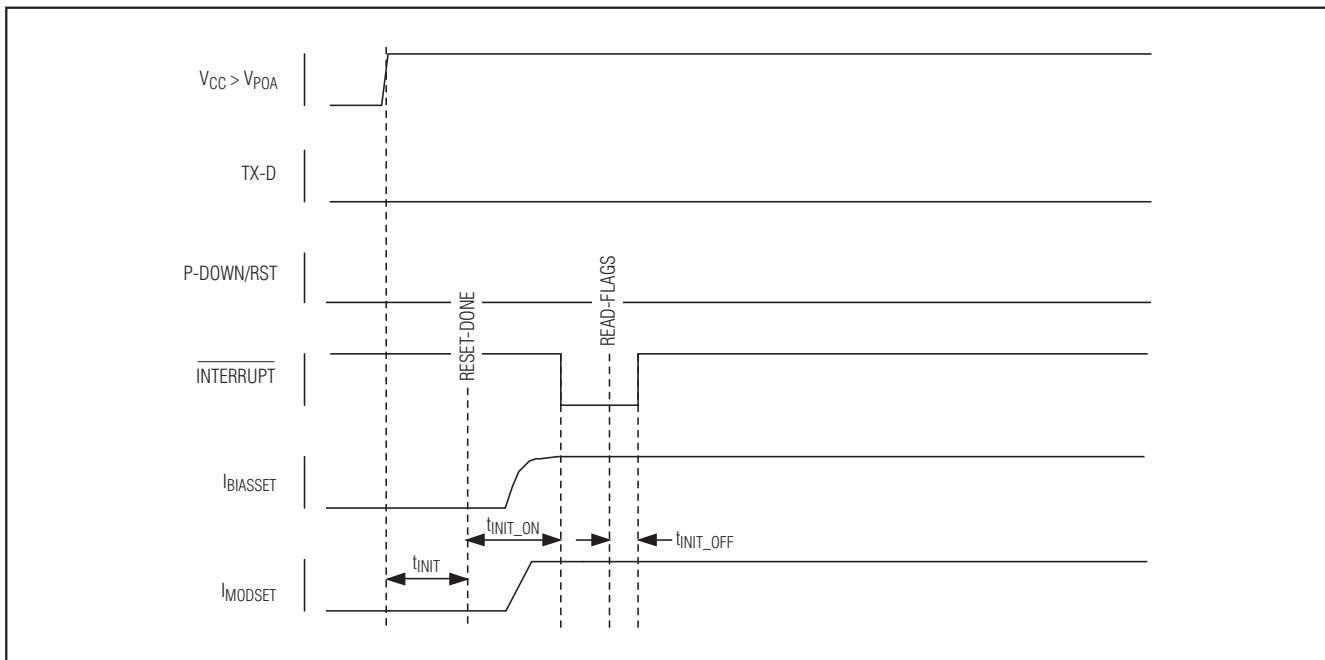

## タイミング図(続き)

図3. 通常動作中のTX-Dのタイミング

図4. 安全フォルト状態の検出

# XFPレーザ制御およびデジタル診断IC

DS1862A

## タイミング図(続き)

図5. P-DOWN/RSTによる過渡安全フォルト状態からの成功した回復

図6. 過渡安全フォルト状態からの失敗した回復

# XFPレーザ制御およびデジタル診断IC

DS1862A

## タイミング図(続き)

図7. モニタチャネルフォルトタイミング

# XFPレーザ制御およびデジタル診断IC

**DS1862A**

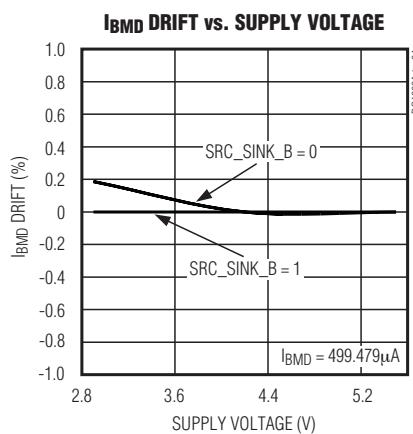

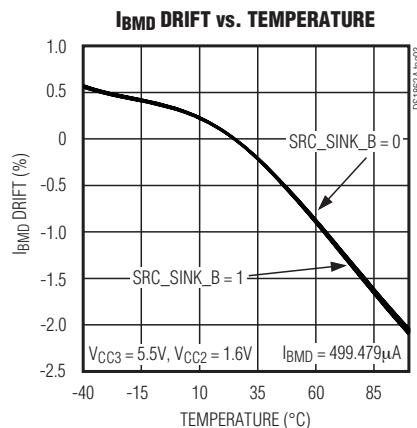

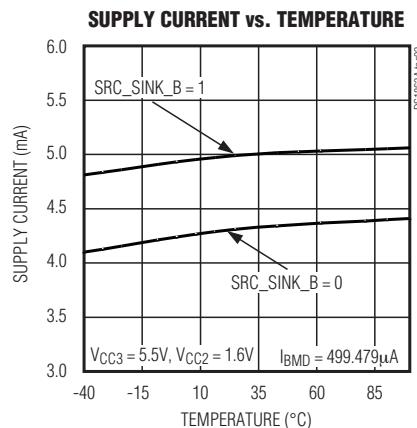

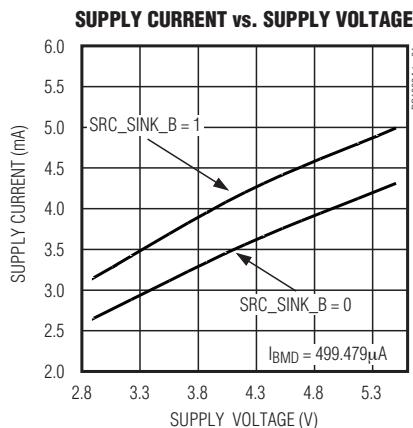

## 標準動作特性

( $T_A = +25^\circ\text{C}$ , unless otherwise noted.)

# XFPレーザ制御およびディジタル診断IC

## 端子説明

DS1862A

| 名称         | 端子 | 機能                                                                                |

|------------|----|-----------------------------------------------------------------------------------|

| P-DOWN/RST | A1 | パワーダウン/リセット入力。この多機能端子は、内部でハイに強制されています。詳細については、「パワーダウン/リセット端子」の項を参照してください。         |

| SC-RX-LOS  | A2 | シグナルコンディショナレシーバの信号喪失入力。この端子は、LVC MOS/LV TTL電圧レベルのアクティブハイ入力です。                     |

| SC-RX-LOL  | A3 | シグナルコンディショナレシーバのロック喪失入力。この端子は、LVC MOS/LV TTL電圧レベルのアクティブハイ入力です。                    |

| THRSET     | A4 | スレッショルド設定出力。この端子は、Rxシグナルコンディショナに使用可能なプログラマブルな電圧源です。                               |

| VCC2       | A5 | 1.8Vの電源入力                                                                         |

| RX-LOS     | B1 | レシーバ信号喪失。このオープンドレイン出力は、光パワーが不十分である場合を示します。                                        |

| SCL        | B2 | I <sup>2</sup> Cシリアルクロック入力                                                        |

| FETG       | B3 | FETゲート出力。この端子は、安全フォルト分離に関する外部FETゲートを駆動することができます。                                  |

| RSSI       | B4 | 受信パワー信号入力                                                                         |

| MODSET     | B5 | 変調電流出力。この端子は、電流のシンクのみが可能です。                                                       |

| TX-D       | C1 | 伝送ディセーブル入力。この端子は、プルアップ抵抗を内蔵しています。                                                 |

| SDA        | C2 | I <sup>2</sup> Cシリアルデータの入力/出力                                                     |

| EN1        | C3 | イネーブル1の出力。シグナルコンディショナの機能制御                                                        |

| EN2        | C4 | イネーブル2の出力。シグナルコンディショナの機能制御                                                        |

| BIASSET    | C5 | バイアス電流の出力。この端子は、電流のシンクのみが可能です。                                                    |

| INTERRUPT  | D1 | 割込み。このオープンドレイン出力端子は、動作フォルトまたは危機的なステータス状態の可能性があることをホストに通知します。                      |

| MOD-NR     | D2 | モジュール動作フォルトの通知。オープンドレイン出力。この端子は、MOD-NRフラグのステータスを通知します。                            |

| AUX1MON    | D3 | 補助1モニタ入力。この端子を使って、電圧量を測定することができます。                                                |

| AUX2MON    | D4 | 補助2モニタ入力。この端子を使って、電圧量または外部温度センサを測定することができます。                                      |

| BMD        | D5 | モニタダイオード電流入力。この端子は、電流のソースまたはシンクが可能です。                                             |

| GND        | E1 | グラウンド                                                                             |

| MOD-DESEL  | E2 | モジュール非選択入力。I <sup>2</sup> C通信をイネーブルするには、この端子をローに強制する必要があります。この端子は、内部でハイに強制されています。 |

| IBIASMON   | E3 | バイアスモニタ入力。この端子を使って、レーザの電圧を監視することができます。                                            |

| SC-TX-LOS  | E4 | シグナルコンディショナトランスマッタの信号喪失。この端子は、LVC MOS/LV TTL電圧レベルのアクティブハイ入力です。                    |

| VCC3       | E5 | 3.3Vまたは5Vの電源入力                                                                    |

# XFPレーザ制御およびデジタル診断IC

**DS1862A**

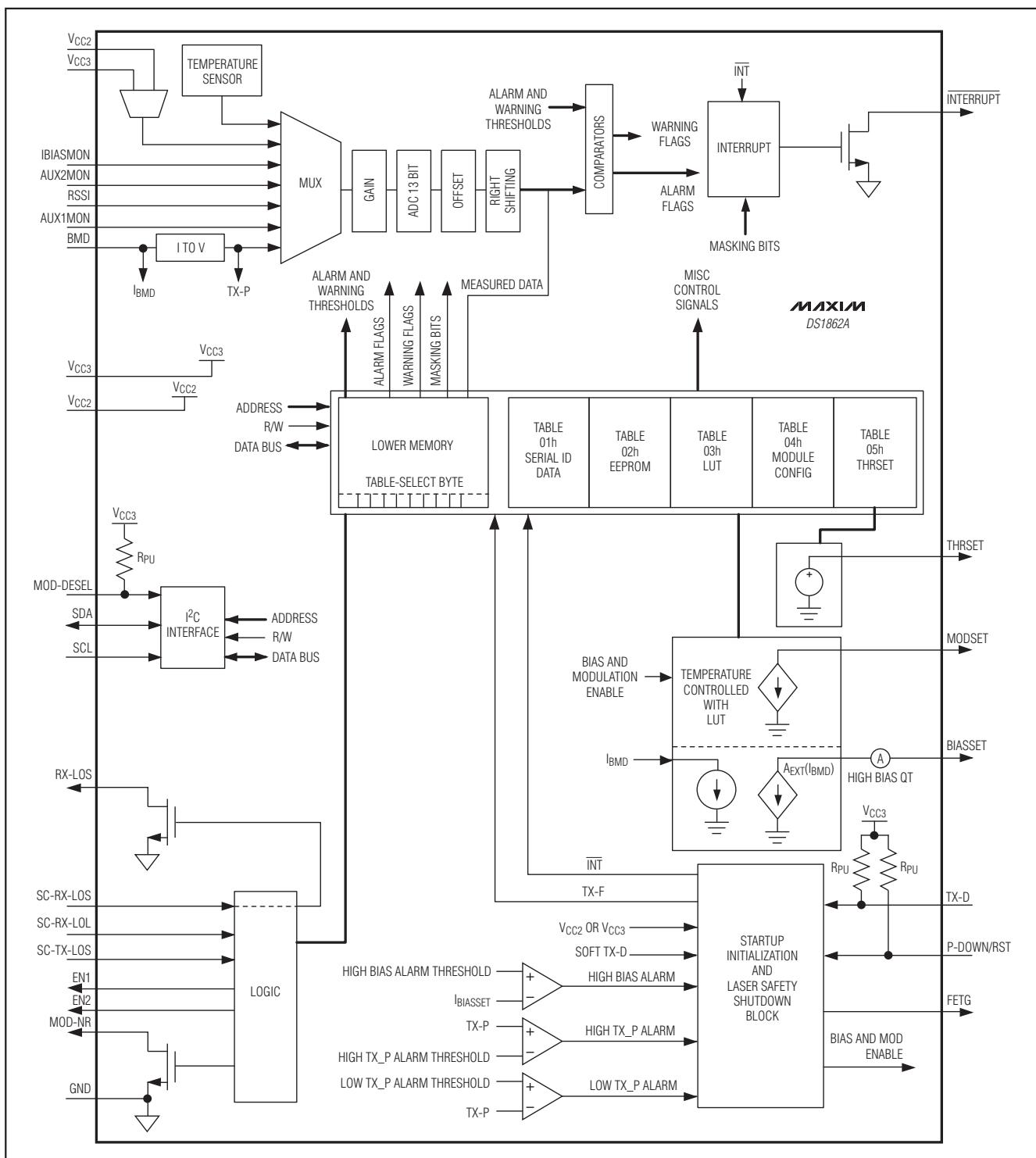

## ブロック図

# XFPレーザ制御およびデジタル診断IC

DS1862A

## 詳細

DS1862Aのブロック図については、以下の各項とメモリマップ/メモリの説明内で詳述します。

### 自動パワー制御(APC)

DS1862AのAPCは、フォトダイオードからのフィードバック電流(BMD)がAPCレジスタで設定された値と一致するまで、バイアス電流(BIASSET)の閉ループ調整によって実行されます。APCレジスタと $I_{BMD}$ の関係は、次式で表されます。

$$I_{BMD} = 5.859\mu A \times APC_C<7:0> + (1.464\mu A \times APC_F<1:0>)$$

ここで、 $APC_C<7:0>$ はBMD電流の粗調整値を制御するテーブル04hのバイト84hの8ビット値であり、 $APC_F<1:0>$ はBMD電流の微調整値を制御する2ビット値です。

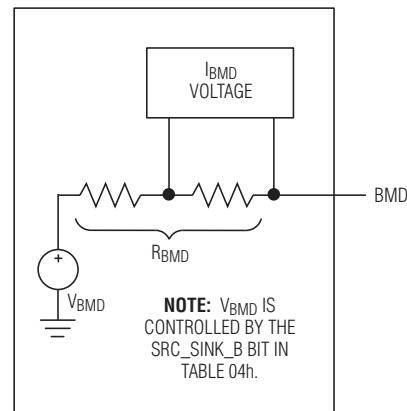

BMD端子は、2個の抵抗と直列の電圧源として表されます。BMD入力端子の全等価抵抗は、図8の図で忠実に近似することができます。外部電流負荷がないと仮定して、BMD端子に現れる電圧は、BMDがシンク電流モード( $SRC\_SINK_B = 0$ )の場合は1.2Vであり、またはBMDがソース電流モード( $SRC\_SINK_B = 1$ )に設定されている場合は2.0Vです。このため、フォトダイオードは $V_{CC3}$ またはGNDを基準することができます。制御ループが定常状態にある場合、BMD電流設定値は、内部抵抗の両端間の $I_{BMD}$ 電圧で測定される電流と一致します。過渡期間に、DS1862Aは、BIASSET端子の駆動電流を調整し、ループを安定状態に移行させます。

DS1862Aは、1/20~10のループ利得を可能とするように設計されています。

パワーアップ時に、BMD電流は、EEPROM APCレジスタ内に事前に保存された電流設定値まで増加します。DS1862Aは動作している間、BMD電流を監視します。BMD電流が所望の(設定された) $I_{BMD}$ 値から偏移し始めると、BIASSET端子の電流は補償のために再び調整されます。

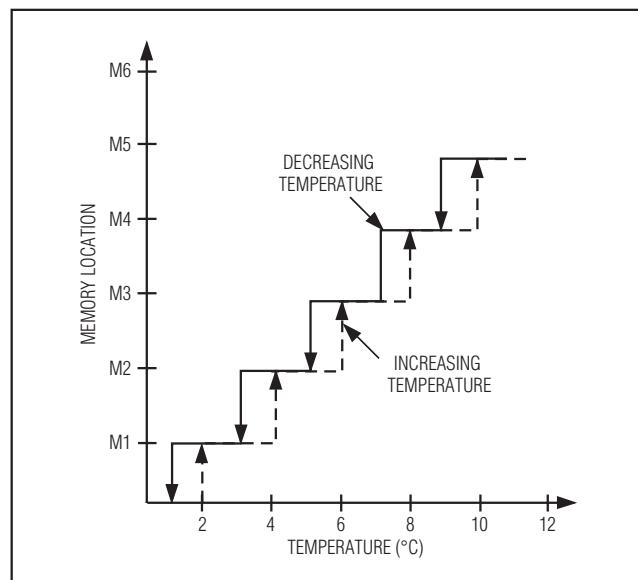

### 消光比制御ルックアップテーブル(LUT)

DS1862Aは、温度指標付きルックアップテーブル(LUT)を使って、消光比を制御します。MODSET端子は、電流を制御している8ビット2進値に基づいて電流をシンクすることができます。また、DS1862Aは、ユーザが設定可能な電流範囲を備え、消光比分解能を向上させます。MODSETに入力する電流を制御するために、5種類の電流範囲(表1を参照)が利用可能です。

表1. MODSETの選択可能な電流範囲

| LUT CURRENT RANGE<br>TABLE 04h, BYTE 86h<2:0> | CURRENT RANGE<br>( $\mu A$ ) |

|-----------------------------------------------|------------------------------|

| 000                                           | 0 to 75                      |

| 001                                           | 0 to 150                     |

| 010                                           | 0 to 300                     |

| 011                                           | 0 to 600                     |

| 100                                           | 0 to 1200                    |

図8. BMD入力の近似モデル

# XFPレーザ制御およびデジタル診断IC

最大の電流範囲が選択された場合は、(LUTからの) FFhの最大値は1200μAのシンク電流に相当します。電流範囲とは関係なく、MODSET値は0ステップを含む256のステップで常に構成されます。

温度ベースのルックアップテーブルまたは他の3種のマニュアル方式によって、IMODSETを自動制御することができます。

温度アドレスによる自動ルックアップは、アドレスポインタを制御する内部または外部温度によって行われます。このポインタは、LUTに保存される127種の事前にロードされた8ビット電流値によって指標付けを行います。127種の温度スロット位置はそれぞれ、-40°C～+102°Cの温度範囲で2°Cのインクリメントに対応しています。これらのポイントを上回るまたは下回るどのような温度によっても、先頭または最後の温度スロットのコードに指標が付けられます。AUX2MONに接続された内部温度センサおよび外部温度センサはともに信号を送出し、指標付きのLUTで消光比を自動制御することができます。表2は、温度とLUT内のメモリ領域の関係を示しています。

**表2. 温度ルックアップテーブル**

| TEMPERATURE (°C) | CORRESPONDING LOOKUP TABLE ADDRESS |

|------------------|------------------------------------|

| < -40            | 80h                                |

| -40              | 80h                                |

| -38              | 81h                                |

| -36              | 82h                                |

| ...              | ...                                |

| +96              | C4h                                |

| +98              | C5h                                |

| +100             | C6h                                |

| +102             | C7h                                |

| > +102           | C7h                                |

MODSETの自動およびマニュアル制御は、テーブル04hのバイトB2hにあるTENとAENの2つのビットで制御されます。デフォルト(出荷時)では、TENとAENはともに設定済みで、完全自動温度ベースのルックアップを起動します。TENまたはAEN、あるいはその両方が変更されると、DS1862Aはマニュアルモードのいずれかに設定されます。表3は、マニュアルモードの機能を示しています。

**表3. TENおよびAENビットの真理値表**

| TEN | AEN | DS1862A LUT FUNCTIONALITY                                                                                                                                                                                                                                                                                                                                   |

|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | 0   | Manual mode that allows users to write a value directly to the LUT VALUE register (Table 04h, Byte B1h) to drive MODSET. While in this mode, the LUT INDEX POINTER register is not being updated, and no longer drives the LUT VALUE register.                                                                                                              |

| 0   | 1   | Manual mode that allows users to write a value directly to the LUT VALUE register (Table 04h, Byte B1h) to drive MODSET. While in this mode, the LUT INDEX POINTER register is still being updated; however, it no longer drives the LUT VALUE register.                                                                                                    |

| 1   | 0   | Manual mode that allows users to write a value to the LUT INDEX POINTER register (Table 04h, Byte B0), then the DS1862A updates the LUT VALUE register (Table 04h, Byte B1h) based on the user's index pointer.                                                                                                                                             |

| 1   | 1   | Automatic mode (factory default). This mode automatically indexes the LUT based on temperature, placing the resulting LUT address in the LUT INDEX POINTER register (Table 04h, Byte B0h). Then the MODSET setting is transferred from that LUT address to the LUT VALUE register (Table 04h, Byte B1h). Lastly, the IMODSET is set to the new MODSET code. |

# XFPレーザ制御およびデジタル診断IC

DS1862A

## モニタチャネル

DS1862Aは、ラウンドロビン方式のマルチプレックスシーケンスでポーリングされる7つの監視対象電圧信号を備え、フレームレートの $t_{\text{FRAME}}$ で更新されます。すべてのチャネルは、16ビット値として読み取られます。しかし、13ビット分解能を備え、温度測定値を除き、すべてのチャネルは無符号の値として保存されます。内部温度を除き、すべての監視対象チャネルの16ビット結果値は、アナログ-デジタル変換結果を内部で8回平均化して、計算されます。内部温度モニタチャネルの結果は、16回平均化されます。内部キャリブレーションの各チャネルの方式の詳細については、「内部キャリブレーション」の項を参照してください。

AUX1MON、AUX2MON、および $V_{\text{CC}2/3}$ モニタチャネルはオプションであり、ディセーブルすることができます。この機能によって、重要なモニタチャネルのフレームレートを短縮することができます。ディセーブル不可のチャネルは、内部温度、BMD、RSSI、およびIBIASMONです。表4には、フルスケール(FS)信号値のテーブル(右シフトしていない出荷時内部キャリブレーションによる)と7つの全チャネルのFSコード結果値が示されています。

## 温度の測定(内部または外部)

DS1862Aは、内部温度センサ、AUX1MON、およびAUX2MONの3種類のモニタチャネルで温度を測定することができます。内部温度およびAUX2MONチャネルのみがLUTを指標付けして、消光比を制御することができます。AUX2MONで外部温度センサを使用するには、テーブル04hのバイト8BhにあるTEMP\_INT/EXTビットを設定する必要があります。AUX2MONが消光比を制御している間、内部温度センサは動作を停止しません。消光比はAUX2MONで制御されますが、温度フラグのステータスを制御し続けるのは、この内部温度信号です。また、TEMP\_INT/EXT = 1の場合は、内部温度は-40°Cおよび+103.9375°Cでクランプされ、TEMP\_INT/EXT = 0の場合は、-120°Cおよび+127.984°Cでクランプされます。ただし、AUX2MONは、許容範囲外の状態を示し、INTERRUPT端子をアサートする固有のフラグを備えています。

表4. モニタチャネルFSおよび LSB の詳細

| SIGNAL             | +FS SIGNAL | +FS (hex) | -FS SIGNAL | -FS (hex) | LSB      |

|--------------------|------------|-----------|------------|-----------|----------|

| Temperature        | 127.984°C  | 7FF8      | -120°C     | 8800      | 0.0625°C |

| $V_{\text{CC}2/3}$ | 6.5528V    | FFF8      | 0V         | 0000      | 100μV    |

| IBIASMON           | 2.4997V    | FFF8      | 0V         | 0000      | 38.147μV |

| RSSI               | 2.4997V    | FFF8      | 0V         | 0000      | 38.147μV |

| AUX1MON            | 6.5528V    | FFF8      | 0V         | 0000      | 38.147μV |

| AUX2MON            | 6.5528V    | FFF8      | 0V         | 0000      | 38.147μV |

| BMD (TX-P)         | 1.5mA      | FFF8      | 0mA        | 0000      | 22.888nA |

AUX1MONおよびAUX2MONはともに、各端子で電圧の関数として温度の測定に使用することができます。表5から0hまたは4hを選択し、これらをイネーブルすることができます。入力電圧を所望の2の補数のデジタルコードに変換するには、内部(または外部)キャリブレーションが必要な場合もあります。このデジタルコードは、下位メモリのバイト6Ah、6Bh、6Ch、6Dhの結果レジスタから読み取り可能です。

## $V_{\text{CC}2/3}$ の測定

DS1862Aには、 $V_{\text{CC}2}$ または $V_{\text{CC}3}$ を内部で測定し、電源電圧を監視するフレキシビリティがあります。 $V_{\text{CC}2}$ または $V_{\text{CC}3}$ は、テーブル01hのバイトDCh内の $V_{\text{CC}2/3\_SEL}$ ビットによってユーザが選択可能です。 $V_{\text{CC}2}$ または $V_{\text{CC}3}$ を監視対象に選択していても、ラウンドロビン方式のモニタ更新方式から $V_{\text{CC}2/3}$ を取り除くために、テーブル04hのバイト8BhのReserve\_ENビットを0にプログラムすることができます。アナログパワーオンリセットフラグのPOAは、 $V_{\text{CC}3}$ 電源のステータスを通知します。POAは $V_{\text{CC}2/3}$ モニタチャネルと同様に動作するように見えますが、POAはまったく別物であり、関係はありません。

| RESERVE_EN | $V_{\text{CC}2/3\_SEL}$ | 結果                                |

|------------|-------------------------|-----------------------------------|

| 0          | 0                       | $V_{\text{CC}2/3}$ の測定はイネーブルされない。 |

| 0          | 1                       | $V_{\text{CC}2/3}$ の測定はイネーブルされない。 |

| 1          | 0                       | $V_{\text{CC}3}$ が測定される。          |

| 1          | 1                       | $V_{\text{CC}2}$ が測定される。          |

## APCおよびレーザパラメータ(BMD、IBIASMON、RSSI)の測定

BMDおよびBIASSETを使って、レーザ機能の制御と監視を行うことができます。APCレジスタに設定されたBMD電流とは関係なく、DS1862AはBMD端子電流を測定し、この値を使ってBIASSET端子の電流を調整するだけでなく、TX-Pを監視することもできます。IBIASMON端子を使って、電圧信号をDS1862Aに入力することができ、これでレーザを通じてバイアス電流を監視することができます。このモニタチャネルは安全フォルト

# XFPレーザ制御およびデジタル診断IC

機能用にHIGH BIAS高速トリップ(QT)警報を駆動せず、BIASSET端子の電流はHIGH BIAS高速トリップ警報を制御するためにDS1862Aによって監視されます。TX-Pと同様に、RSSI端子を使って受信パワー、RX-Pを測定することができます。

## AUX1MONおよびAUX2MONによる電圧量の測定

AUX1MONおよびAUX2MONは、別のパラメータの測定に使用可能な補助モニタ入力です。AUX1/2MONは、測定値の単位(すなわち、電圧、電流、または温度)を決定するユーザが選択可能なレジスタを備えています。表5の4ビットオペコードの幾つかは、単位を示すことに加えて、警報およびフォルト用に内部使用する特別モードにこのデバイスを移行させます。いずれの単位スケールが選択されても、DS1862Aは正の電圧量の測定のみが可能です。このため、2進値を測定量と一致させるには、内部または外部キャリブレーションが必要

**表5. AUX1/2MON機能の選択(単位の選択)**

| VALUE | DESCRIPTION OF AUX1/2MON INTENDED USE<br>(UNITS OF MEASURE)             |

|-------|-------------------------------------------------------------------------|

| 0000b | Auxiliary monitoring not implemented                                    |

| 0001b | APD bias voltage (16-bit value is voltage in units of 10mV)             |

| 0010b | Reserved                                                                |

| 0011b | TEC current (mA) (16-bit value is current in units of 0.1mA)            |

| 0100b | Laser temperature (same encoding as module temperature)                 |

| 0101b | Laser wavelength                                                        |

| 0110b | +5V supply voltage (encoded as primary voltage monitor)                 |

| 0111b | +3.3V supply voltage (encoded as primary voltage monitor)               |

| 1000b | +1.8V supply voltage (encoded as primary voltage monitor) ( $V_{CC2}$ ) |

| 1001b | -5.2V supply voltage (encoded as primary voltage monitor)               |

| 1010b | +5V supply current (16-bit value is current in 0.1mA)                   |

| 1101b | +3.3V supply current (16-bit value is current in 0.1mA)                 |

| 1110b | +1.8V supply current (16-bit value is current in 0.1mA)                 |

| 1111b | -5.2V supply current (16-bit value is current in 0.1mA)                 |

になります。対応可能な単位とそれに対応するユーザプログラマブルの4ビットオペコードの表は、以下に示されています。

## モニタチャネルによる警報/警告フラグ

すべてのモニタチャネルは、ユーザ設定のスレッショルドがモニタチャネル結果と内部で比較されて自動的にアサートする警報および警告フラグを備えています。マスクされていない場合は、フラグが設定されて、このためINTERRUPT端子に割込みが生成されるか、または安全フォルトが生成されます。 $V_{CC2/3}$ 、AUX2MON、AUX1MON、RSSI、および内部温度がそれぞれのスレッショルドトリップポイントを超えると、対応するマスクビットが0の場合は、割込みがINTERRUPT端子に常に生成され、対応する警告または警報フラグが設定されます。同様に、BMDまたはBIASSETがスレッショルドトリップポイントを超えると、安全フォルトが常に発生します。これが発生すると、FETG端子はすぐにアサートし、BIASSETおよびMODSET電流はシャットダウンされます。

## モニタチャネル変換例

表6は、RSSIまたはIBIASMONに関して、出荷時設定キャリブレーションによって16ビットADCコードが実際の測定電圧にどのように対応するかの例を示しています。出荷時デフォルトでは、 LSBは38.147μVに設定されます。

**表6. A/D変換例**

| MSB (BIN) | LSB (BIN) | VOLTAGE (V) |

|-----------|-----------|-------------|

| 11000000  | 00000000  | 1.875       |

| 10000000  | 10000000  | 1.255       |

$V_{CC2}$ 、 $V_{CC3}$ 、AUX1MON、またはAUX2MONを計算するには、無符号の16ビット値を10進数に変換し、100μVを乗算します。

温度(内部)を計算するには、2の補数値の2進数を無符号2進数として取扱い、それを10進数に変換し、256で除算します。その結果が128以上の場合は、その結果から256を減じます。

温度：上位バイト = -128°C ~ +127°C 符号付き、下位バイト = 1/256°C

## 表7. 温度ビットの荷重

| S        | $2^6$    | $2^5$    | $2^4$    | $2^3$    | $2^2$ | $2^1$ | $2^0$ |

|----------|----------|----------|----------|----------|-------|-------|-------|

| $2^{-1}$ | $2^{-2}$ | $2^{-3}$ | $2^{-4}$ | $2^{-5}$ | —     | —     | —     |

表8. 温度変換例

| MSB (BIN) | LSB (BIN) | TEMPERATURE (°C) |

|-----------|-----------|------------------|

| 01000000  | 00000000  | +64              |

| 01000000  | 00001000  | +64.03215        |

| 01011111  | 00000000  | +95              |

| 11110110  | 00000000  | -10              |

| 11011000  | 00000000  | -40              |

## 内部キャリブレーション

DS1862Aは、アナログ入力をデジタル結果にスケーリングする方法を2つ備えています。2個のデバイスは、信号の利得およびオフセットを変更して、キャリブレートされます。内部温度を除き、すべての入力は、テーブル04hに示すオフセットおよび利得用の個別レジスタを備えています。すべてのモニタチャネルに対する右シフトなどの内部キャリブレーション機能の詳細については、下の表を参照してください。

表9. 内部キャリブレーション機能

| SIGNAL             | INTERNAL SCALING | INTERNAL OFFSET | RIGHT-SHIFTING |

|--------------------|------------------|-----------------|----------------|

| Temperature        | —                | x               | —              |

| V <sub>CC2/3</sub> | x                | x               | —              |

| IBIASMON           | x                | x               | x              |

| RSSI (RX-P)        | x                | x               | x              |

| AUX1MON            | x                | x               | x              |

| AUX2MON            | x                | x               | x              |

| BMD (TX-P)         | x                | x               | x              |

個別入力の利得とオフセットをスケーリングするには、アナログ入力と期待するデジタル結果との関係が分かっている必要があります。すべてゼロの対応するデジタル結果を生じる入力はヌル値です(通常、この入力はGNDです)。すべて1の対応するデジタル結果を生じる入力はフルスケール(FS)値から1 LSBを差し引いた値です。また、すべて1のデジタル値に、重み付けされたLSBを乗算すると、FS値が得られます。例えば、デジタル読取り値が16ビット長であり、LSBが $50\mu V$ であることが分かっていると仮定すると、FS値は $2^{16} \times 50\mu V = 3.2768V$ です。

バイナリ検索によって、コンバータの所望のFSを得るために適した利得値を求めることができます。利得値が

求められると、その値を対応するチャネルの利得レジスタにロードすることができます。これには、2つの既知電圧をモニタ入力端子に印加する必要があります。最も良い結果を得るには、印加電圧のいずれか1つをヌル入力にして、他方の印加電圧をFSの90%にする必要があります。デジタル読取りレジスタの最下位バイトのLSBは既知であるため、期待するデジタル結果もヌルおよびFS値入力に対して分かれることになります。図9は、DS1862AのLUT機能に組み込まれたヒステリシスを示しています。

図9. ルックアップテーブルのヒステリシス

電流のソースやシンクが可能なBMDを除き、すべての監視対象チャネルはハイインピーダンスであり、電圧を直接測定することのみが可能です。光、周波数、電力、電流などの他の測定量を所望する場合は、測定量を電圧に変換する必要があります。この場合は、ユーザは監視対象チャネルでの電圧測定ではなく、所望のパラメータの測定に关心があります。間接的な測定量(光、周波数、電力、電流など)と期待するデジタル結果との関係のみを知る必要があります。

推奨するバイナリ検索手順による利得スケーリング例が、次に示す疑似コードとともに示されています。

計算を容易にするために、カウント1とカウント2の2つの整数を定義する必要があります。CNT1 = NULL / LSBとCNT2 = 90%FS / LSBです。CLAMPは、対応可能な最大結果です。

# XFPレーザ制御およびデジタル診断IC

```

/* Assume that the Null input is 0.5V. */

/* In addition, the requirement for LSB is 50µV. */

FS = 65536 * 50e-6;          /* 3.2768 */

CNT1 = 0.5 / 50e-6;          /* 10000 */

CNT2 = 0.90*FS / 50e-6;      /* 58982 */

/* Thus the NULL input of 0.5V and the 90% of FS input

is 2.94912V. */

set the trim-offset-register to zero;

set Right-Shift register to zero (Typically zero.

See the Right-Shifting section);

gain_result = 0h;

CLAMP = FFF8h/2^(Right_Shift_Register);

For n = 15 down to 0

begin

gain_result = gain_result + 2^n;

Force the 90% FS input (2.94912V);

Meas2 = read the digital result from the part;

If Meas2 >= CLAMP then

gain_result = gain_result - 2^n;

Else

Force the NULL input (0.5V);

Meas1 = read the digital result from the part;

if (Meas2 - Meas1) > (CNT2 - CNT1) then

gain_result = gain_result - 2^n;

end;

Set the gain register to gain_result;

```

このように利得レジスタは設定され、変換の分解能は期待するLSBと完全に一致します。次のステップは、DS1862Aのオフセットのキャリブレーションです。正しい利得値を利得レジスタに書き込んで、ヌル入力をモニタ端子に再び入力します。DS1862Aから結果のデジタル値を読み取ります(Meas1)。オフセット値は、Meas1の負の値になります。

$$\text{OFFSET\_REGISTER} = \left[ \frac{(-1)\text{Meas1}}{4} \right]$$

計算されたオフセットがDS1862Aに書き込まれ、利得/オフセットスケーリング手順は完了です。

## 右シフトA/D変換結果 (スケーラブルダイナミックレンジ)

右シフトは、キャリブレーションされたシステムの失われたADC範囲の一部を取り戻すためのデジタル方式です。右シフトがイネーブルされている場合は、非ゼロ値を対応する右シフトレジスタにロードすると、モニタチャネルのレジスタに保存される直前にDS1862Aはキャリブレーションされた結果をシフトします。システムがキャリブレーションされた結果、最大の期待入力が7FFFh (FSの50%)を下回るデジタル出力値になる場合は、右シフト方式を使用する対象になります。

所望の最大デジタル出力が7FFFhを下回る場合は、キャリブレーションされたシステムはADCの範囲の1/2以下を使用しています。同様に、所望の最大デジタル出力が1FFFhを下回る場合は、キャリブレーションされたシステムはADCの範囲の1/8しか使用していません。例えば、印加された最大のアナログ信号が1FFChを下回る最大デジタル出力になる場合は、ADCの範囲の1/8しか使用していません。右シフトによって、内部キャリブレーションの一環として測定信号の分解能が向上します。右シフトがない場合は、ADCの3つのMSビットは使用されません。この例では、右シフトの3という値によってADC範囲は最大になり、変換を最適化するにはより大きな利得設定値をロードする必要があります。これは左揃えされた13ビットコンバータであるため、分解能は失われません。分解能を失わずに、値を3回右シフトすることができます。以下の表は、右シフト方式を効果的に使用可能な場合を示しています。

表10. 右シフトの選択

| OUTPUT RANGE USED WITH ZERO RIGHT-SHIFTS | NUMBER OF RIGHT-SHIFTS NEEDED |

|------------------------------------------|-------------------------------|

| 0h .. FFFFh                              | 0                             |

| 0h .. 7FFFh                              | 1                             |

| 0h .. 3FFFh                              | 2                             |

| 0h .. 1FFFh                              | 3                             |

| 0h .. 0FFFh                              | 4                             |

# XFPレーザ制御およびデジタル診断IC

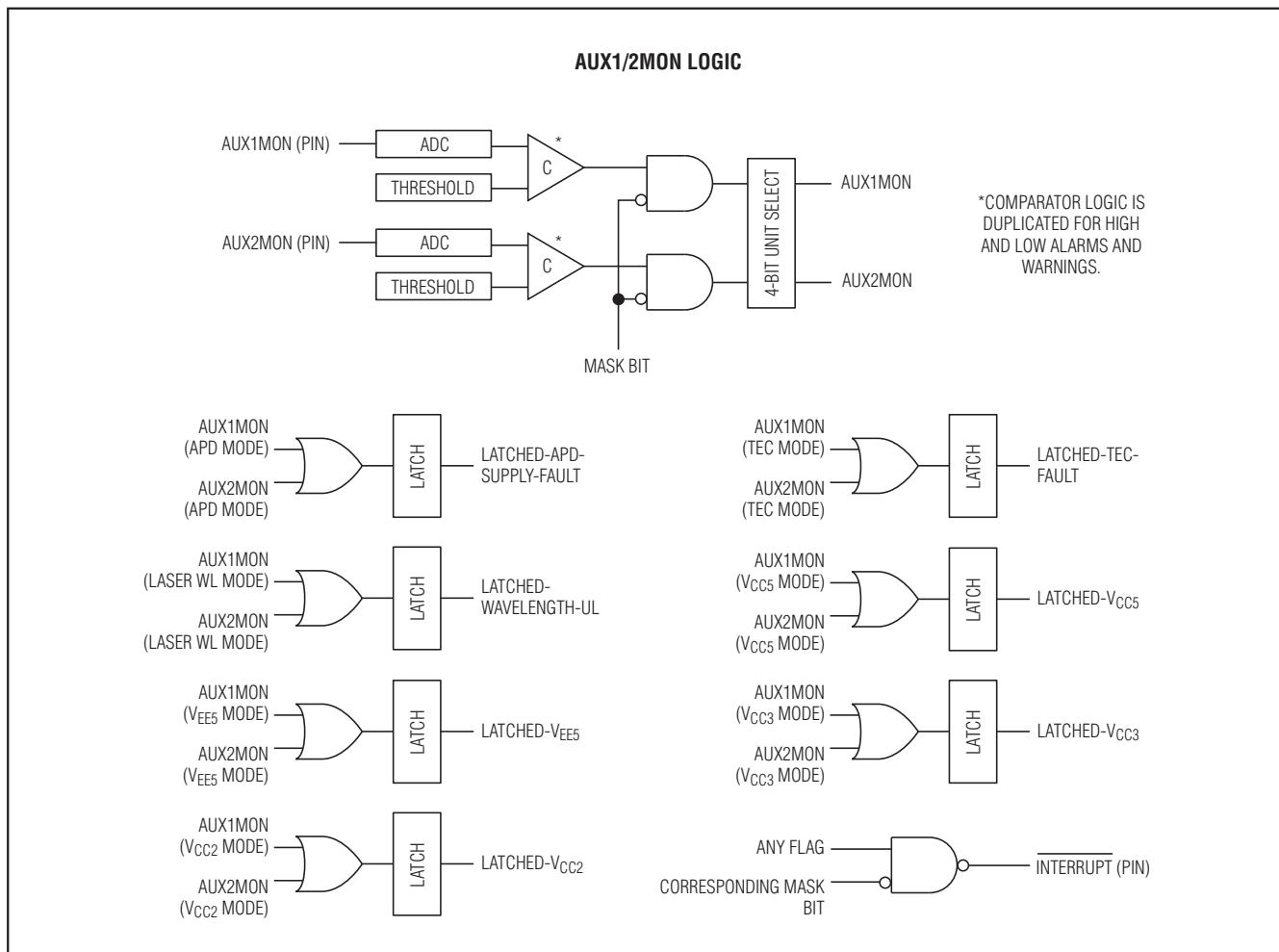

## AUX1/2MON、V<sub>CC2/3</sub>、温度、RX-P、およびIBIASMONによる警告/警報ロジック

DS1862Aは、監視対象のアナログチャネルがユーザ設定の許容値を超えるたびに、警報や警告を生成することができます。温度、バイアス電流(IBIASMONによる)、受信パワー(RSSIによる)、AUX1MON、AUX2MON、およびV<sub>CC2/3</sub>は、ラッチ付きフラグを生成する監視対象チャネルです。AUX1MONおよびAUX2MONに関する

詳細については、以下の図を参照してください。監視対象チャネルが設定した動作ウィンドウから初めて外れると、フラグがハイ状態にラッチされ、各監視対象の信号に対して対応する警報または警告フラグが設定されないように設定可能なマスクビットがあります。フラグが設定されると、そのメモリ位置を読み取るだけでそのフラグはクリアされます。

図10. AUX1/2MONモニタロジック

# XFPレーザ制御およびデジタル診断IC

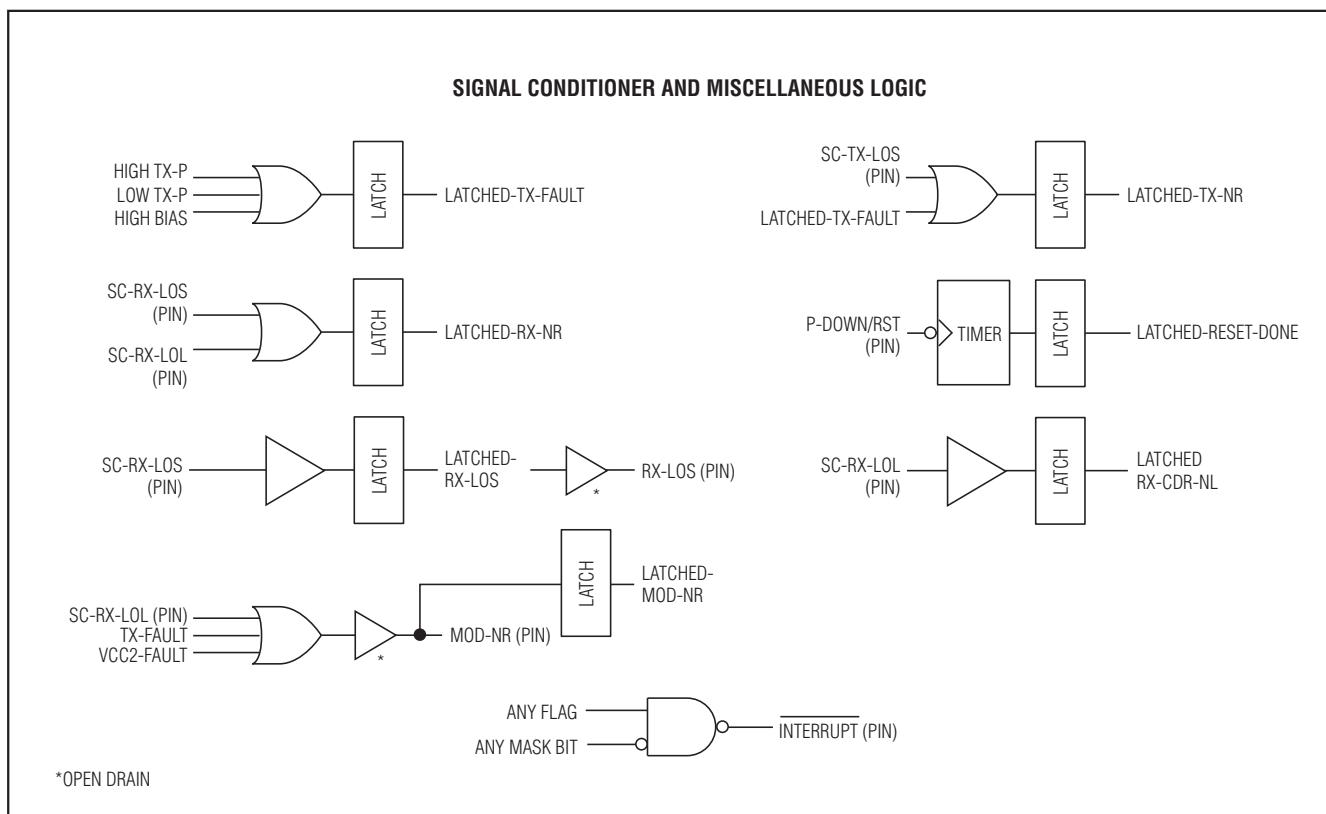

## シグナルコンディショナによる警報/警告ロジック

DS1862Aは、シグナルコンディショナ(SC)端子(SC-RX-LOL、SC-RX-LOS、SC-TX-LOS)の特定のロジック条件で設定されるフラグも備えています。同様に、ラッチされるシグナルコンディショナフラグごとに、警報または警告フラグによってINTERRUPT端子をアサートしないようにすることが可能なマスクビットもあります。この場合も、フラグのメモリアドレスが読み取られるたびに、フラグは自動的にクリアされます。詳細については、図11を参照してください。

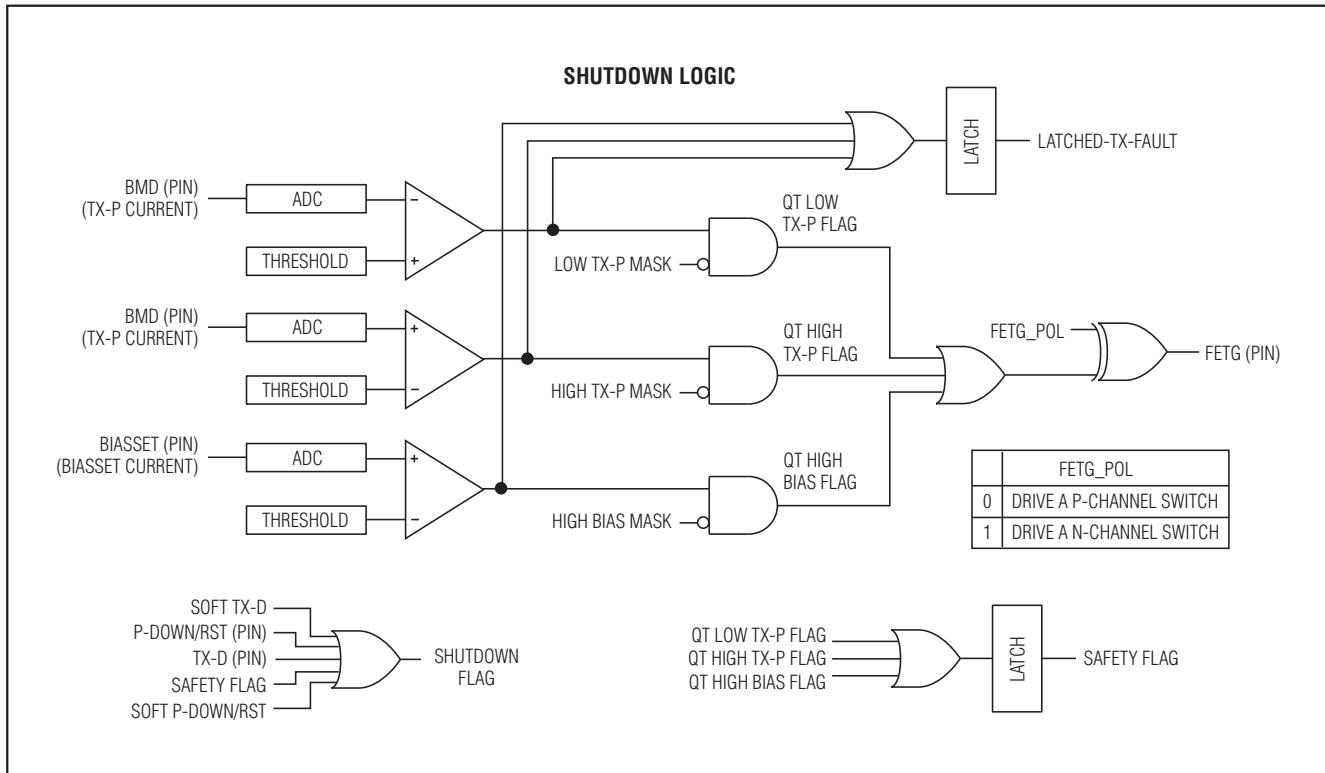

## 高速トリップロジックおよびFETGシャットダウン機能

警報および警告機能のほかに、DS1862Aは、 $I_{MODSET}$ および $I_{BIASSET}$ のシャットダウンとともに、FETG端子でLASERをシャットダウン可能な高速トリップ(QT)機能(高速警報とも呼ばれる)も備えています。 $I_{BMD}$ および

$I_{BIASSET}$ の電流は測定され、高速トリップフラグ(QT LOW TX-P、QT HIGH TX-P、およびQT HIGH BIAS)を設定するユーザ定義のトリップポイントと比較されます。これらのフラグは、許容範囲を超えた状態の検出時にFETGがアサートされないようにマスクすることもできます。TX-D端子、SOFT TX-D、またはP-DOWN/RST端子をハイ状態に設定するとFETGはアサートされませんが、 $I_{MODSET}$ と $I_{BIASSET}$ はシャットダウンされます。詳細については、図12を参照してください。

また、FETG端子の極性を、FETG\_POLビットを設定して、逆にすることもできます。安全フォルトが発生すると、FETG端子とそれに付随するすべてのフラグは、P-DOWN/RST端子をリセット時間 $t_{RESET}$ の間、パルス的にハイにするか、またはバイト6Ehのビット3のSOFT P-DOWN/RSTビットをトグルすることによってのみリセットすることができます。詳細については、「パワーダウン/リセット端子」の項を参照してください。

図11. シグナルコンディショナおよびその他のロジック

図12. 安全フォルトおよびシャットダウンロジック

### パワーダウン/リセット端子

P-DOWN/RST端子は、DS1862Aのリセットやパワーダウンを行う多機能入力端子です。この端子は内部でプルアップされているため、通常は解放状態であり、それはパワーダウンモードに相当します。P-DOWN/RST端子が解放、すなわちハイになると、DS1862AはMODSETおよびBIASSET電流をシャットダウンする応答になります。この端子がローに強制されると、動作が継続します(安全フォルトで阻止されていない場合)。DS1862Aをパワーダウンすること以外に、最短リセット時間 $t_{RESET}$ の間ハイになるパルスをP-DOWN/RST端子に印加することができます。特に、安全シャットダウン状態にあり、安全状態が正常になった後に再起動する必要がある場合に、DS1862Aを再起動するには、この処理が必要です。適切な端子タイミングについては、タイミング図を参照してください。

### パワーダウン機能

パワーダウンモードの間は、 $\text{!BIASSET}$ と $\text{!MODSET}$ は $10\mu\text{A}$ を下回り、レーザを実質的にシャットダウンします。FETGはアサートされず、安全フォルトはこの期間中に発生しません。パワーダウンの間は、I<sup>2</sup>C通信はアクティブのままであるが、シグナルコンディショナ端子のEN1およびEN2は制御不能であり、EN1 = 1およびEN2 = 0の状態に自動的に移行します。シグナルコンディショナ入力による他の内部フラグ/信号は、パワーダウン中にもシグナルコンディショナ端子の状態が引き継ぎ反映されます。たとえば、RX-LOSはSC-RX-LOSのステータスを反映したままであり、MOD-NRはシグナルコンディショナ端子のロジック状態の反映を続けます。同様に、BIASSETおよびMODSET電流がシャットダウンされている場合、FETGをアサートすることができます。ただし、パワーダウンおよびパワーアップ中の短期の $t_{PDR-OFF}$ の間は、TX-Pローフラグは無視され(内部で自動的にマスクアウト)、FETGのロジックに寄与しません。

# XFPレーザ制御およびデジタル診断IC

P-DOWN/RSTのアサート期間(DS1862Aはパワーダウン状態)中に、 $V_{CC3}$ がサイクルされると、DS1862Aはパワーアップ時にパワーダウンモード状態を維持します。パワーダウンモード状態の間は、INTERRUPT端子はアサートしません。 $V_{CC3}$ が復帰すると、リセット完了フラグが割込みアサート遅延 $t_{INIT\_ON}$ の後にアサートします。

## リセット機能

P-DOWN/RST端子は、DS1862Aをパワーダウンするだけでなく、DS1862Aをリセットする機能も果たします。 $t_{RESET}$ のハイになるパルス時間の経過後に、幾つかのイベントがDS1862A内で発生します。最初に、MODSETおよびBIASSET電流がシャットダウンされ、その後元の状態に戻ります。2番目に、リセットパルスの立上りエッジとリセット完了フラグのアサートの間( $t_{INIT}$ )に、ローのTX-Pフラグは無視され、FETGをトリップしません。 $t_{INIT}$ の時間が経過した後、ローのTX-Pフラグの機能が有効になります。また、この時に、リセット完了フラグがアサートされ、割込みが生成されます。 $t_{INIT}$ の前にフォルトがない場合は、割込みはINTERRUPT端子にアサートされません。

P-DOWN/RSTがハイの間に $V_{CC3}$ がパワーアップされると、リセット完了フラグを2回クリアする必要があります。最初のリセット完了フラグは $V_{CC3}$ のパワーアップで生成され、2回目のリセット完了フラグはP-DOWN/RSTの立下りエッジで生成されます。P-DOWN/RSTがローの間に $V_{CC3}$ が連続的に給電されていると、クリアする必要があるのは1つのリセット完了フラグのみです。図による詳細については、タイミング図を参照してください。

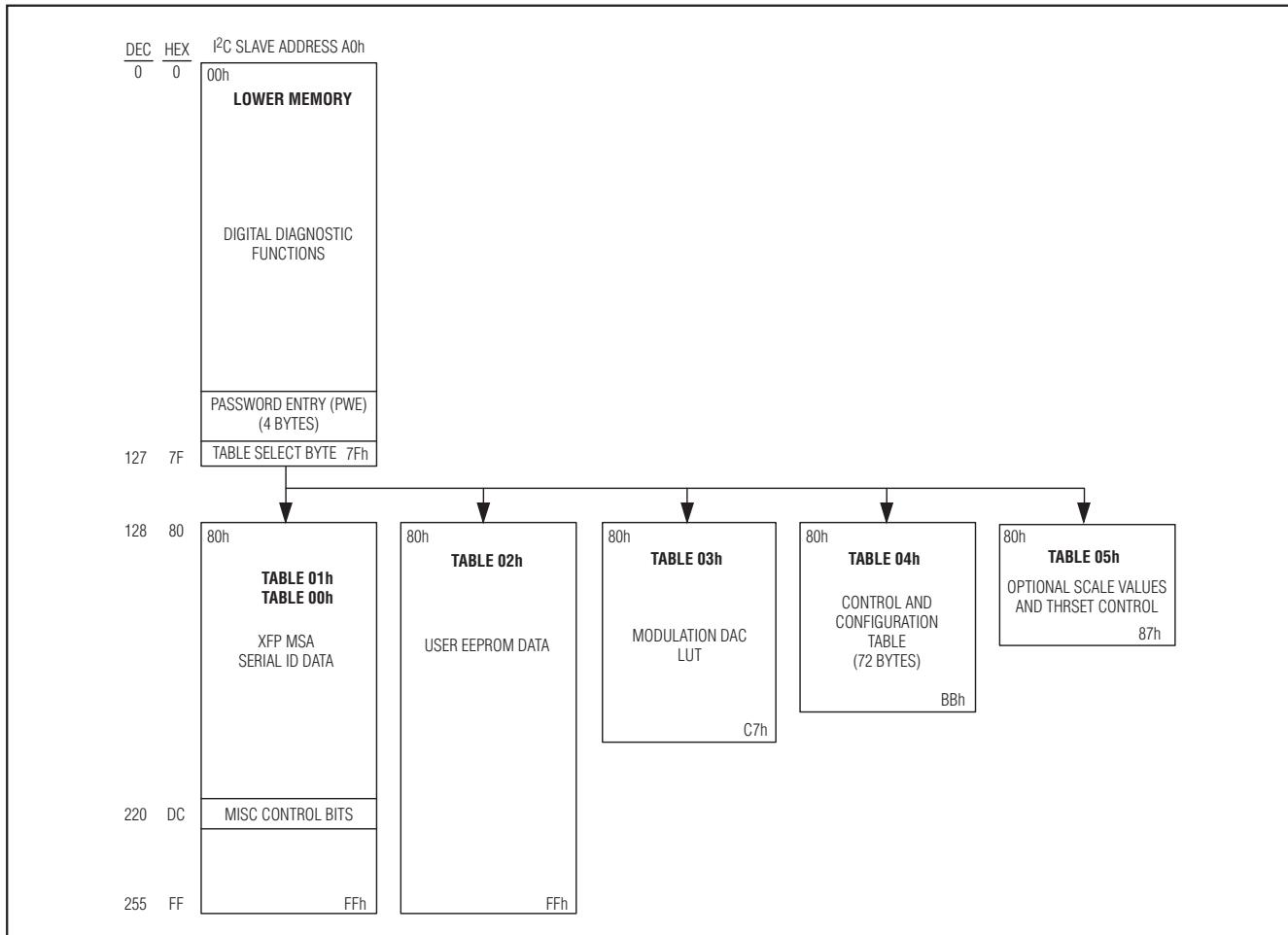

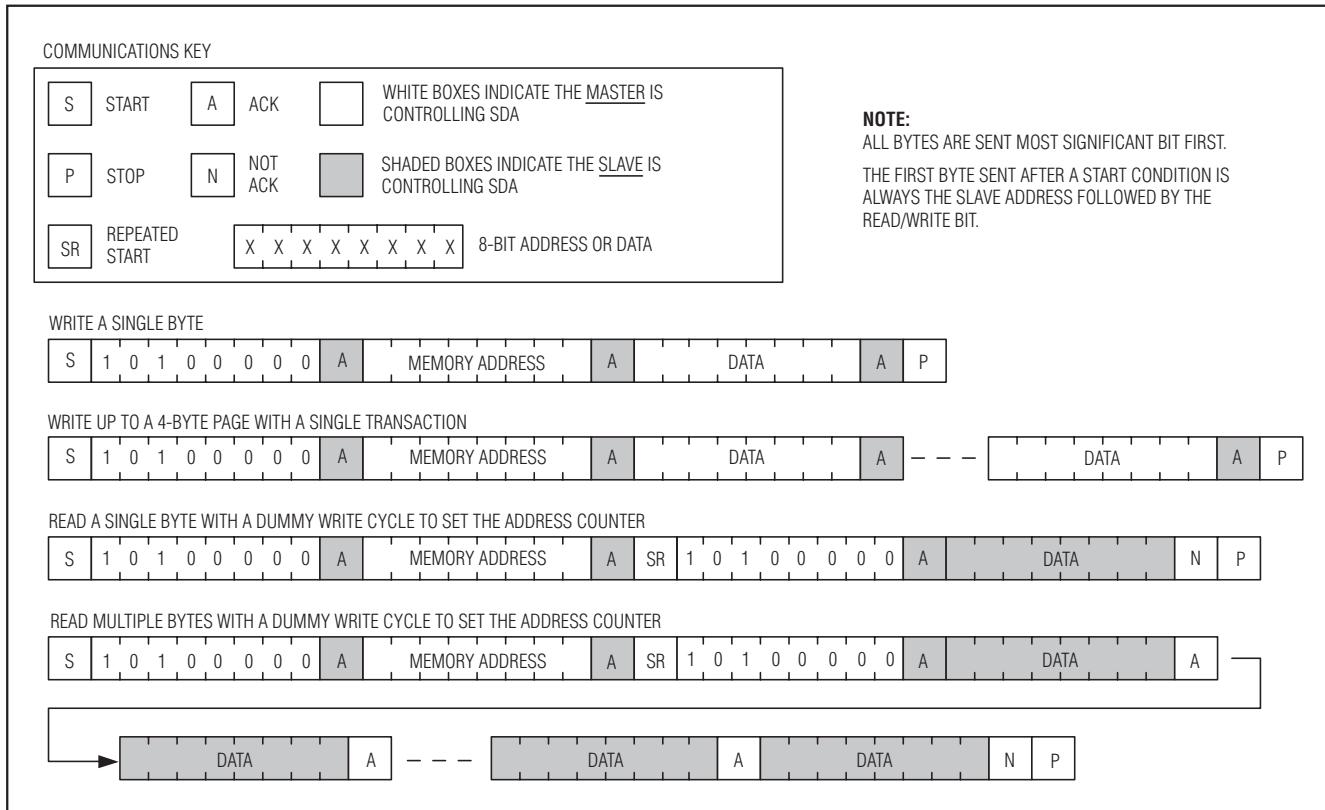

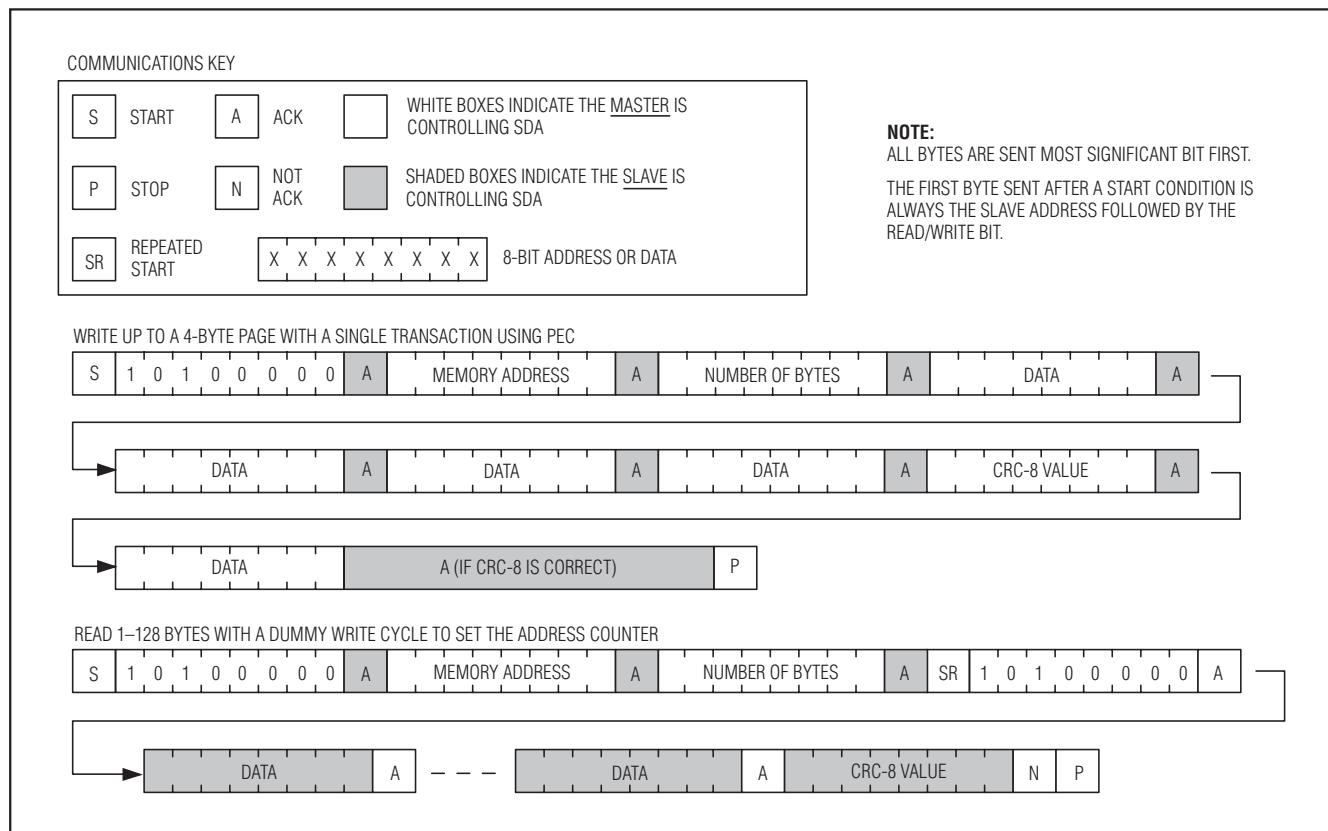

## メモリマップ

### メモリ構成

DS1862Aは、4つのバイト列で内部構成される6つの独立したメモリテーブルを備えています。下位メモリは00hから7Fhまでのアドレスであり、警報/警告スレッ

ショルド、フラグ、マスク、複数の制御レジスタ、パスワード入力領域(PE)、およびテーブル選択バイトを備えています。テーブル01hは、主にユーザEEPROMと各種機能用の複数の制御バイトを備えています。テーブル02hは、ホストのパスワードで保護されるユーザEEPROM専用です。テーブル03hは、LUTによる消光比の制御専用です。テーブル04hは、監視対象チャネルの内部キャリブレーション値、LUTインデックスポインタ、およびその他の制御バイトを内蔵する多機能領域です。テーブル05hは出荷時に設定され、推奨する外部温度センサ用のSCALE値を保存します。また、テーブル05hの1バイトはTHRSET電圧源を制御し、パスワード保護なしで完全アクセスが可能です。各バイトの読み取り/書き込み許可については表11を、また各バイトの機能の詳細については「レジスタ詳細」の項を参照してください。多くの不揮発性メモリ領域は実際にはSRAMシャドウEEPROMであり、テーブル04hのバイトB2h内のSEEBビットで制御されます。

DS1862Aは、多数回の再書き込みが可能な主要メモリアドレス用のSRAMシャドウEEPROMメモリ領域を備えています。デフォルトでは、シャドウEEPROMビットのSEEBは未設定で、これらの領域は通常のEEPROMとして機能します。SEEBを設定すると、これらの領域はSRAMセルのように機能し始め、EEPROMの消耗を懸念せずに無数の書き込みサイクルを可能にします。また、これによって、EEPROMの書き込み期間の $t_{WR}$ が不要になります。SEEBをイネーブルにして行われた変更はEEPROMに作用しないため、これらの変更はパワーサイクルされた場合は保持されません。パワーアップ時の値は、SEEBをディセーブルにして書き込まれた最後の値です。この機能を使って、キャリブレーション中のEEPROM書き込み回数を制限したり、通常動作中のモニタスレッシュホールドを定期的に変更したり、EEPROMに書き込まれる回数を減らすことができます。以下の情報では、シャドウEEPROMがいずれの領域にあるかを示します。

図13. DS1862Aメモリ構成の概要図

### レジスタマップ

表11. 許可テーブル

| PERMISSION | READ                                                                                                                    | WRITE   |

|------------|-------------------------------------------------------------------------------------------------------------------------|---------|

| <0>        | At least one byte in this row is different than the rest of the bytes, so look at each byte separately for permissions. |         |

| <1>        | ALL                                                                                                                     | ALL     |

| <2>        | ALL                                                                                                                     | MODULE  |

| <3>        | ALL                                                                                                                     | HOST    |

| <4>        | MODULE                                                                                                                  | MODULE  |

| <5>        | ALL                                                                                                                     | FACTORY |

| <6>        | NEVER                                                                                                                   | HOST    |

| <7>        | NEVER                                                                                                                   | MODULE  |

# XFPレーザ制御およびデジタル診断IC

DS1862A

| LOWER MEMORY (00h-7Fh) |                             |                             |                            |                            |                     |                            |                             |                            |

|------------------------|-----------------------------|-----------------------------|----------------------------|----------------------------|---------------------|----------------------------|-----------------------------|----------------------------|

| ADDRESS<br>(hex)       | WORD 0                      |                             | WORD 1                     |                            | WORD 2              |                            | WORD 3                      |                            |

|                        | BYTE 0/8                    | BYTE 1/9                    | BYTE 2/A                   | BYTE 3/B                   | BYTE 4/C            | BYTE 5/D                   | BYTE 6/E                    | BYTE 7/F                   |

| 00<0,2>                | USER EE                     | Signal Cond*                | Temp Alarm Hi              |                            | Temp Alarm Lo       |                            | Temp Warn Hi                |                            |

| 08<2>                  | Temp Warn Lo                |                             | VCC3 Alarm Hi**            |                            | VCC3 Alarm Lo**     |                            | VCC3 Warn Hi**              |                            |

| 10<2>                  | VCC3 Warn Lo**              |                             | Bias Alarm Hi              |                            | Bias Alarm Lo       |                            | Bias Warn Hi                |                            |

| 18<2>                  | Bias Warn Lo                |                             | TX-P Alarm Hi              |                            | TX-P Alarm Lo       |                            | TX-P Warn Hi                |                            |

| 20<2>                  | TX-P Warn Lo                |                             | RX-P Alarm Hi              |                            | RX-P Alarm Lo       |                            | RX-P Warn Hi                |                            |

| 28<2>                  | RX-P Warn Lo                |                             | AUX1 Alarm Hi              |                            | AUX1 Alarm Lo       |                            | AUX1 Warn Hi                |                            |

| 30<2>                  | AUX1 Warn Lo                |                             | AUX2 Alarm Hi              |                            | AUX2 Alarm Lo       |                            | AUX2 Warn Hi                |                            |

| 38<0,2>                | AUX2 Warn Lo                |                             | USER EE                    | USER EE                    | Reserved            | Reserved                   | Reserved                    | Reserved                   |

| 40<1>                  | Reserved                    | Reserved                    | Reserved                   | Reserved                   | Reserved            | Reserved                   | USER SRAM                   | USER SRAM                  |

| 48<1>                  | USER SRAM                   | USER SRAM                   | USER SRAM                  | USER SRAM                  | USER SRAM           | USER SRAM                  | USER SRAM                   | USER SRAM                  |

| 50<1>                  | Temp/Res/Bias/<br>TxP Alarm | RxP/AUX1/AUX2/<br>Res Alarm | Temp/Res/Bias/<br>TxP Warn | RxP/AUX1/<br>AUX2/Res Warn | Tx/Rx Misc<br>Flags | Apd/Tec/<br>Wave/Res Flags | VCC5/3/2/Vee<br>Alarm Flags | VCC5/3/2/Vee<br>Warn Flags |

| 58<1>                  | Temp/Res/Bias/<br>TxP Mask  | RxP/AUX1/AUX2/<br>Res Mask  | Temp/Res/Bias/<br>TxP Mask | RxP/AUX1/<br>AUX2/Res Mask | Rx/Rx Misc<br>Mask  | Apd/Tec/Wave/<br>Res Mask  | VCC5/3/2/Vee<br>Alarm Mask  | VCC5/3/2/Vee<br>Warn Mask  |

| 60<1>                  | Temp Value                  |                             | VCC2/3 Value**             |                            | Bias Value          |                            | TX-P Value                  |                            |

| 68<1>                  | RX-P Value                  |                             | AUX1 Value                 |                            | AUX2 Value          |                            | GCS1                        | GCS0                       |

| 70<0,1>                | Reserved                    | Reserved                    | Reserved                   | Reserved                   | POA                 | Reserved                   | PEC_EN                      | Host PW                    |

| 78<0,1>                | Host PW                     | Host PW                     | Host PW                    | PWE (MSB)                  |                     | PWE (LSB)                  |                             | Table Select               |

## EXPANDED BYTES

| BYTE<br>(hex) | BYTE/WORD<br>NAME | Bit7         |              | Bit6*        |              | Bit5         |              | Bit4         |              | Bit3        |      | Bit2 |      | Bit1 |      | Bit0 |      |

|---------------|-------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|-------------|------|------|------|------|------|------|------|

|               |                   | bit15        | bit14        | bit13        | bit12        | bit11        | bit10        | bit9         | bit8         | bit7        | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

| 01            | Signal Cond<1>*   | USER EE      | EN2 Value    | EN1 Value    | Lock-T1-221 |      |      |      |      |      |      |      |

| 50            | <1>               | L-HI-TEMP-AL | L-LO-TEMP-AL | Reserved     | Reserved     | L-HI-BIAS-AL | L-LO-BIAS-AL | L-HI-TX-P-AL | L-LO-TX-P-AL |             |      |      |      |      |      |      |      |

| 51            | <1>               | L-HI-RX-P-AL | L-LO-RX-P-AL | L-HI-AUX1-AL | L-LO-AUX1-AL | L-HI-AUX2-AL | L-LO-AUX2-AL | Reserved     | Reserved     |             |      |      |      |      |      |      |      |

| 52            | <1>               | L-HI-TEMP-W  | L-LO-TEMP-W  | Reserved     | Reserved     | L-HI-BIAS-W  | L-LO-BIAS-W  | L-HI-TX-P-W  | L-LO-TX-P-W  |             |      |      |      |      |      |      |      |

| 53            | <1>               | L-HI-RX-P-W  | L-LO-RX-P-W  | L-HI-AUX1-W  | L-LO-AUX1-W  | L-HI-AUX2-W  | L-LO-AUX2-W  | Reserved     | Reserved     |             |      |      |      |      |      |      |      |

| 54            | <1>               | L-TX-NR      | L-TX-F       | L-TX-CDR-NL  | L-RX-NR      | L-RX-LOS     | L-RX-CDR-NL  | L-MOD-NR     | L-RESET-DONE |             |      |      |      |      |      |      |      |

| 55            | <1>               | L-APD-SUP-F  | L-TEC-F      | L-WAVE-NL    | Reserved     | Reserved     | Reserved     | Reserved     | Reserved     |             |      |      |      |      |      |      |      |

| 56            | <1>               | L-HI-VCC5-AL | L-LO-VCC5-AL | L-HI-VCC3-AL | L-LO-VCC3-AL | L-HI-VCC2-AL | L-LO-VCC2-AL | L-HI-VEE5-AL | L-LO-VEE5-AL |             |      |      |      |      |      |      |      |

\*テーブル01hにあるバイトDDhのビット0が設定されている場合に限り、アドレス01hのビット0に書き込むことができます。

\*\*VCC2/3は予備領域にあります。

# XFPレーザ制御およびディジタル診断IC

**DS1862A**

| BYTE<br>(hex) | BYTE/WORD<br>NAME | EXPANDED BYTES (CONTINUED) |       |                 |       |                 |       |                 |      |                  |      |                 |      |                 |      |                 |

|---------------|-------------------|----------------------------|-------|-----------------|-------|-----------------|-------|-----------------|------|------------------|------|-----------------|------|-----------------|------|-----------------|

|               |                   | Bit7                       |       | Bit6            |       | Bit5            |       | Bit4            |      | Bit3             |      | Bit2            |      | Bit1            |      |                 |

|               |                   | bit15                      | bit14 | bit13           | bit12 | bit11           | bit10 | bit9            | bit8 | bit7             | bit6 | bit5            | bit4 | bit3            | bit2 | bit1            |

| 57            | <1>               | L-HI-VCC5-W                |       | L-LO-VCC5-W     |       | L-HI-VCC3-W     |       | L-LO-VCC3-W     |      | L-HI-VCC2-W      |      | L-LO-VCC2-W     |      | L-HI-VEE5-W     |      | L-LO-VEE5-W     |

| 58            | <1>               | HI-TEMP-AL MASK            |       | LO-TEMP-AL MASK |       | Reserved        |       | Reserved        |      | HI-BIAS-AL MASK  |      | LO-BIAS-AL MASK |      | HI-TX-P-AL MASK |      | LO-TX-P-AL MASK |

| 59            | <1>               | HI-RX-P-AL MASK            |       | LO-RX-P-AL MASK |       | HI-AUX1-AL MASK |       | LO-AUX1-AL MASK |      | HI-AUX2-AL MASK  |      | LO-AUX2-AL MASK |      | Reserved        |      | Reserved        |

| 5A            | <1>               | HI-TEMP-W MASK             |       | LO-TEMP-W MASK  |       | Reserved        |       | Reserved        |      | HI-BIAS-W MASK   |      | LO-BIAS-W MASK  |      | HI-TX-P-W MASK  |      | LO-TX-P-W MASK  |

| 5B            | <1>               | HI-RX-P-W MASK             |       | LO-RX-P-W MASK  |       | HI-AUX1-W MASK  |       | LO-AUX1-W MASK  |      | HI-AUX2-W MASK   |      | LO-AUX2-W MASK  |      | Reserved        |      | Reserved        |

| 5C            | <1>               | TX-NR MASK                 |       | TX-F MASK       |       | TX-CDR-NL MASK  |       | RX-NR MASK      |      | RX-LOL MASK      |      | RX-CDR-NL MASK  |      | MOD-NR MASK     |      | RESET-DONE MASK |

| 5D            | <1>               | APD-SUP-F MASK             |       | TEC-F MASK      |       | WAVE-NL MASK    |       | Reserved        |      | Reserved         |      | Reserved        |      | Reserved        |      | Reserved        |

| 5E            | <1>               | HI-VCC5-AL MASK            |       | LO-VCC5-AL MASK |       | HI-VCC3-AL MASK |       | LO-VCC3-AL MASK |      | HI-VCC2-AL MASK  |      | LO-VCC2-AL MASK |      | HI-VEE5-AL MASK |      | LO-VEE5-AL MASK |

| 5F            | <1>               | HI-VCC5-W MASK             |       | LO-VCC5-W MASK  |       | HI-VCC3-W MASK  |       | LO-VCC3-W MASK  |      | HI-VCC2-W MASK   |      | LO-VCC2-W MASK  |      | HI-VEE5-W MASK  |      | LO-VEE5-W MASK  |

| 6E            | <1>               | TX-D                       |       | SOFT TX-D†      |       | MOD-NR          |       | P-DOWN/RST      |      | SOFT P-DOWN/RST† |      | INTERRUPT       |      | RX-LOS          |      | DATA-NR         |

| 6F            | <1>               | TX-NR                      |       | TX-F            |       | Reserved        |       | RX-NR           |      | RX-CDR-NL        |      | Reserved        |      | Reserved        |      | Reserved        |

| 74            | POA <1>           | POA                        |       | Reserved        |       | Reserved        |       | Reserved        |      | Reserved         |      | Reserved        |      | Reserved        |      | Reserved        |

| 77            | Host PW<6>        | 2 <sup>31</sup>            |       | 2 <sup>30</sup> |       | 2 <sup>29</sup> |       | 2 <sup>28</sup> |      | 2 <sup>27</sup>  |      | 2 <sup>26</sup> |      | 2 <sup>25</sup> |      | 2 <sup>24</sup> |

| 78            | Host PW<6>        | 2 <sup>23</sup>            |       | 2 <sup>22</sup> |       | 2 <sup>21</sup> |       | 2 <sup>20</sup> |      | 2 <sup>19</sup>  |      | 2 <sup>18</sup> |      | 2 <sup>17</sup> |      | 2 <sup>16</sup> |

| 79            | Host PW<6>        | 2 <sup>15</sup>            |       | 2 <sup>14</sup> |       | 2 <sup>13</sup> |       | 2 <sup>12</sup> |      | 2 <sup>11</sup>  |      | 2 <sup>10</sup> |      | 2 <sup>9</sup>  |      | 2 <sup>8</sup>  |

| 7A            | Host PW<6>        | 2 <sup>7</sup>             |       | 2 <sup>6</sup>  |       | 2 <sup>5</sup>  |       | 2 <sup>4</sup>  |      | 2 <sup>3</sup>   |      | 2 <sup>2</sup>  |      | 2 <sup>1</sup>  |      | 2 <sup>0</sup>  |

| 7B            | PWE<6>            | 2 <sup>31</sup>            |       | 2 <sup>30</sup> |       | 2 <sup>29</sup> |       | 2 <sup>28</sup> |      | 2 <sup>27</sup>  |      | 2 <sup>26</sup> |      | 2 <sup>25</sup> |      | 2 <sup>24</sup> |

| 7C            | PWE<6>            | 2 <sup>23</sup>            |       | 2 <sup>22</sup> |       | 2 <sup>21</sup> |       | 2 <sup>20</sup> |      | 2 <sup>19</sup>  |      | 2 <sup>18</sup> |      | 2 <sup>17</sup> |      | 2 <sup>16</sup> |

| 7D            | PWE<6>            | 2 <sup>15</sup>            |       | 2 <sup>14</sup> |       | 2 <sup>13</sup> |       | 2 <sup>12</sup> |      | 2 <sup>11</sup>  |      | 2 <sup>10</sup> |      | 2 <sup>9</sup>  |      | 2 <sup>8</sup>  |

| 7E            | PWE<6>            | 2 <sup>7</sup>             |       | 2 <sup>6</sup>  |       | 2 <sup>5</sup>  |       | 2 <sup>4</sup>  |      | 2 <sup>3</sup>   |      | 2 <sup>2</sup>  |      | 2 <sup>1</sup>  |      | 2 <sup>0</sup>  |

| 7F            | Table Select<1>   | 2 <sup>7</sup>             |       | 2 <sup>6</sup>  |       | 2 <sup>5</sup>  |       | 2 <sup>4</sup>  |      | 2 <sup>3</sup>   |      | 2 <sup>2</sup>  |      | 2 <sup>1</sup>  |      | 2 <sup>0</sup>  |

†バイト6Ehのビット6およびビット3は、それぞれテーブル01hにあるバイトDDhのビット6およびビット5によってマスクされます。

# XFPレーザ制御およびディジタル診断IC

DS1862A

| TABLE 01h (SERIAL ID MEMORY) |                   |                         |                         |                         |                         |                         |                         |                         |                         |                         |                         |                         |                         |                         |                         |                  |                  |

|------------------------------|-------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|------------------|------------------|

| ADDRESS<br>(hex)             | WORD 0            |                         | WORD 1                  |                         | WORD 2                  |                         | WORD 3                  |                         |                         |                         |                         |                         |                         |                         |                         |                  |                  |

|                              | Byte 0/8          | Byte 1/9                | Byte 2/A                | Byte 3/B                | Byte 4/C                | Byte 5/D                | Byte 6/E                | Byte 7/F                |                         |                         |                         |                         |                         |                         |                         |                  |                  |

| 80<2>                        | USER EE           | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 |                         |                         |                         |                         |                         |                         |                         |                  |                  |

| 88<2>                        | USER EE           | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 |                         |                         |                         |                         |                         |                         |                         |                  |                  |

| 90<2>                        | USER EE           | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 |                         |                         |                         |                         |                         |                         |                         |                  |                  |

| 98<2>                        | USER EE           | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 |                         |                         |                         |                         |                         |                         |                         |                  |                  |

| A0<2>                        | USER EE           | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 |                         |                         |                         |                         |                         |                         |                         |                  |                  |

| A8<2>                        | USER EE           | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 |                         |                         |                         |                         |                         |                         |                         |                  |                  |

| B0<2>                        | USER EE           | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 |                         |                         |                         |                         |                         |                         |                         |                  |                  |

| B8<2>                        | USER EE           | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 |                         |                         |                         |                         |                         |                         |                         |                  |                  |

| C0<2>                        | USER EE           | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 |                         |                         |                         |                         |                         |                         |                         |                  |                  |

| C8<2>                        | USER EE           | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 |                         |                         |                         |                         |                         |                         |                         |                  |                  |

| D0<2>                        | USER EE           | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 |                         |                         |                         |                         |                         |                         |                         |                  |                  |

| D8<2>                        | USER EE           | USER EE                 | USER EE                 | USER EE                 | VCC2/3_SEL              | LO MEM 6Eh EN           | AUX1/2 UNIT SEL         | USER EE                 |                         |                         |                         |                         |                         |                         |                         |                  |                  |

| E0<2>                        | USER EE           | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 |                         |                         |                         |                         |                         |                         |                         |                  |                  |

| E8<2>                        | USER EE           | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 |                         |                         |                         |                         |                         |                         |                         |                  |                  |

| F0<2>                        | USER EE           | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 |                         |                         |                         |                         |                         |                         |                         |                  |                  |

| F8<2>                        | USER EE           | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 | USER EE                 |                         |                         |                         |                         |                         |                         |                         |                  |                  |

| EXPANDED BYTES               |                   |                         |                         |                         |                         |                         |                         |                         |                         |                         |                         |                         |                         |                         |                         |                  |                  |