## 特長

高精度 ADC

2 チャンネル同時サンプリングの 16 ビット  $\Sigma$ - $\Delta$  ADC を内蔵

ADC スループットが 1 Hz~8 kHz でプログラマブル

5 ppm/ $^{\circ}$ C のリファレンス電圧を内蔵

電流チャンネル

フル差動のバッファ付き入力

プログラマブル・ゲイン: 1~512

ADC 入力範囲: -200 mV~+300 mV

電流アキュムレータ機能付きのデジタル・コンパレータ

電圧チャンネル

12 V バッテリ入力用のバッファ付き減衰器を内蔵

温度チャンネル

外付けと内蔵の温度センサー・オプション

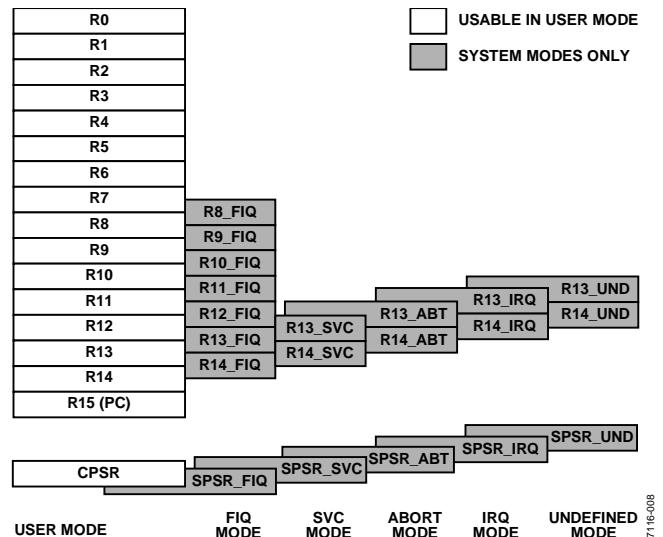

マイクロコントローラ

RISC アーキテクチャの 16/32 ビット ARM7TDMI コアを採用

プログラマブルな分周器付きの 20.48 MHz PLL を内蔵

PLL 入力ソース

内蔵高精度発振器

内蔵低消費電力発振器

外付け(32.768 kHz)時計水晶

JTAG ポートがコードのダウンロードとデバッグをサポート

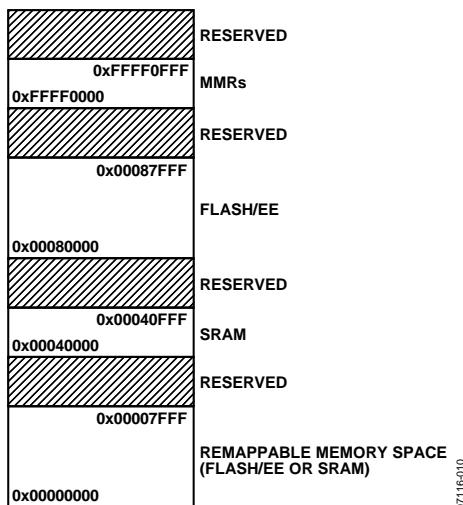

## メモリ

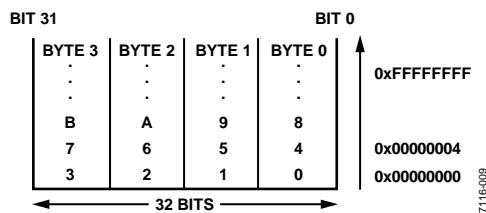

32 kB のフラッシュ/EE メモリ、4 kB の SRAM

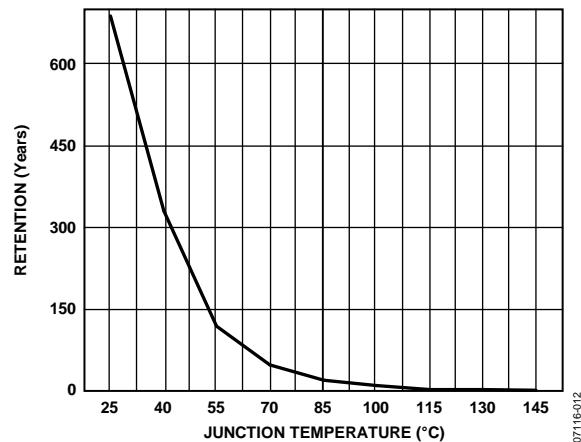

フラッシュ/EE 書き替え回数: 10,000 サイクル、フラッシュ/EE のデータ保持: 20 年

JTAG と LIN によるインサーキット・ダウンロード

内蔵ペリフェラル

ハードウェア同期付き UART により LIN 2.0 互換(スレーブ)をサポート

柔軟なウェイクアップ I/O ピン、マスター/スレーブ SPI シリアル I/O

GPIO ポート: 9 ピン、汎用タイマー × 3

ウェイクアップ・タイマーとウォッチドッグ・タイマー

電源モニター、内蔵パワーオン・リセット

## 電源

直接 12 V バッテリ電源で動作

消費電流

ノーマル・モード: 10 MHz で 10 mA

低消費電力モニター・モード

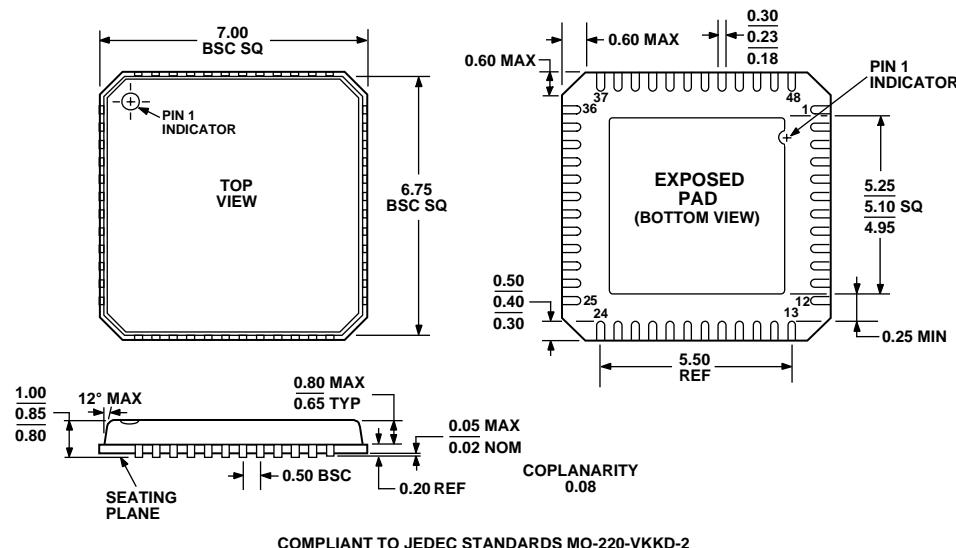

パッケージと温度範囲

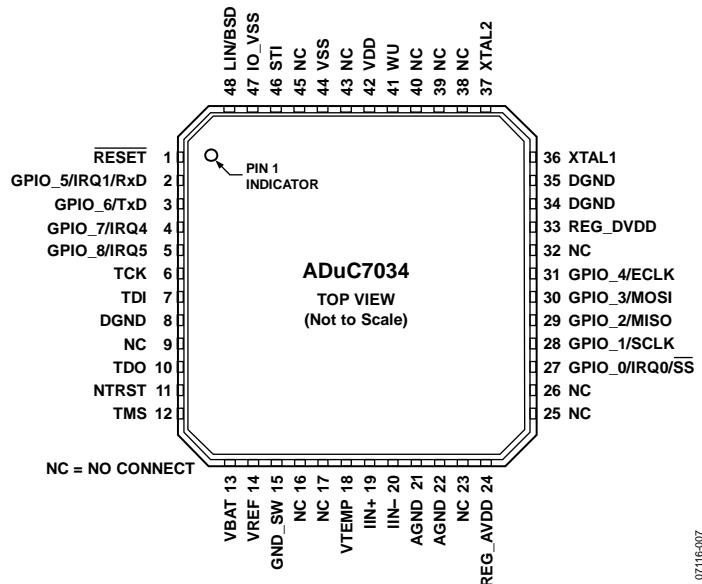

48 ピン 7 mm × 7 mm の LFCSP パッケージを採用

-40 $^{\circ}$ C~+115 $^{\circ}$ C の動作仕様

## アプリケーション

車載システム向けのバッテリ検出/管理

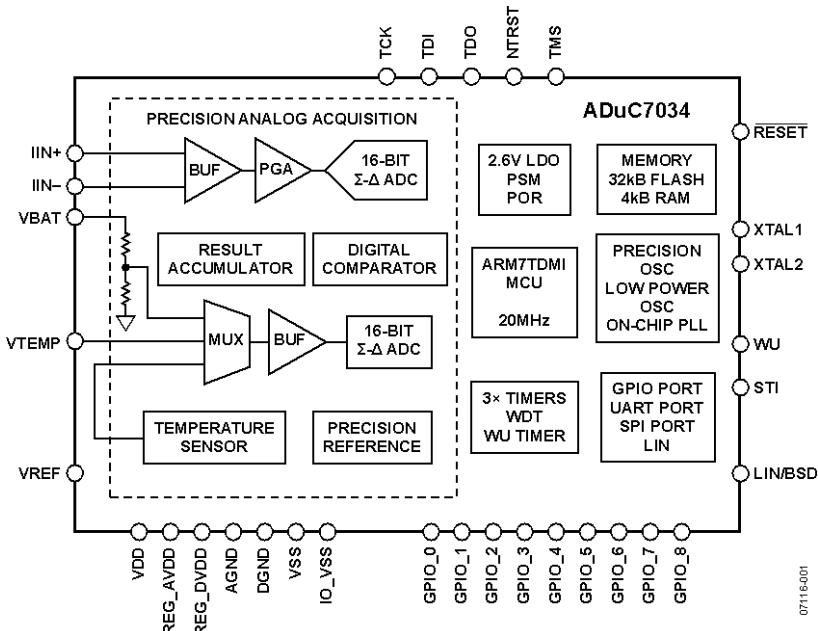

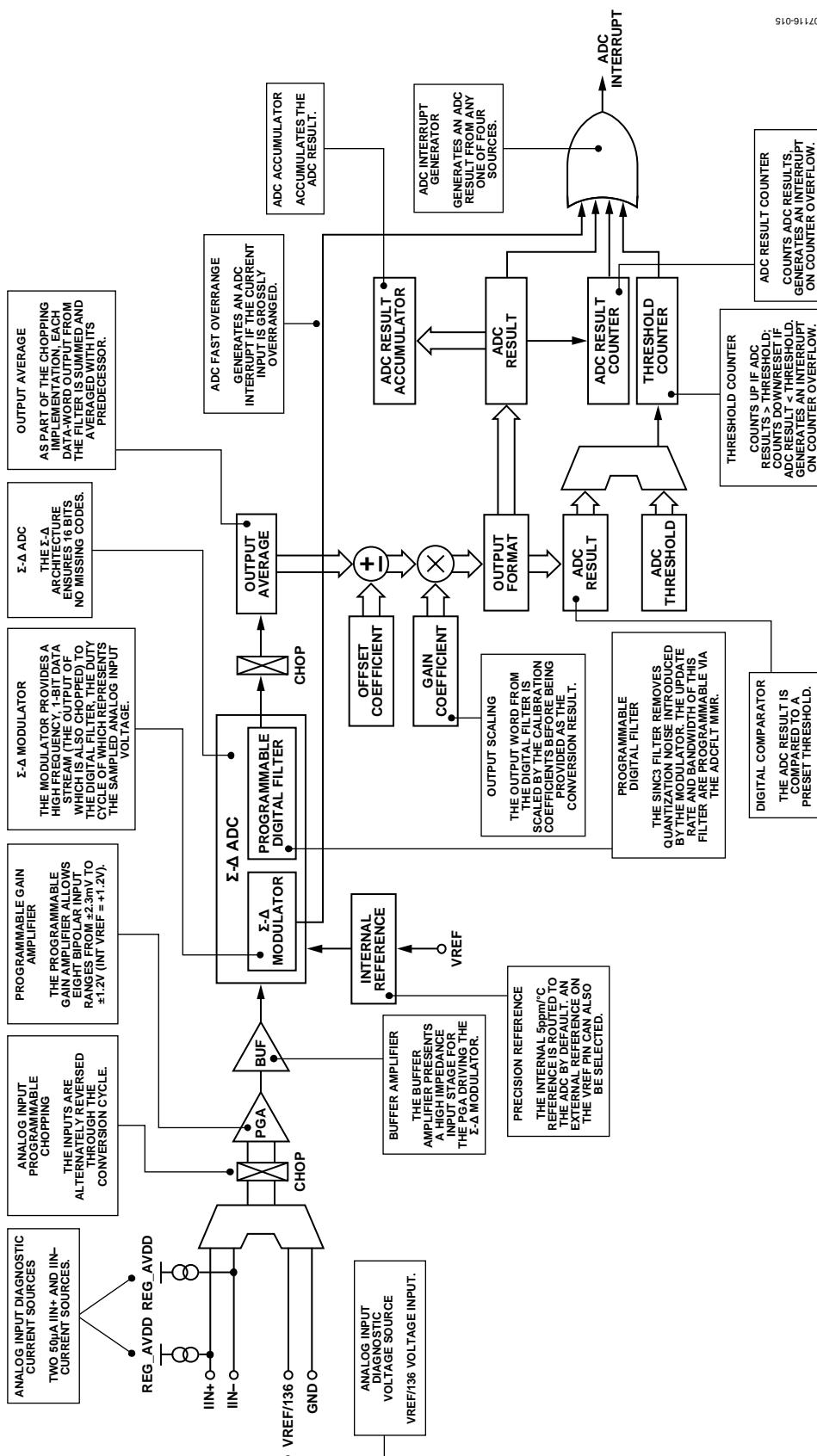

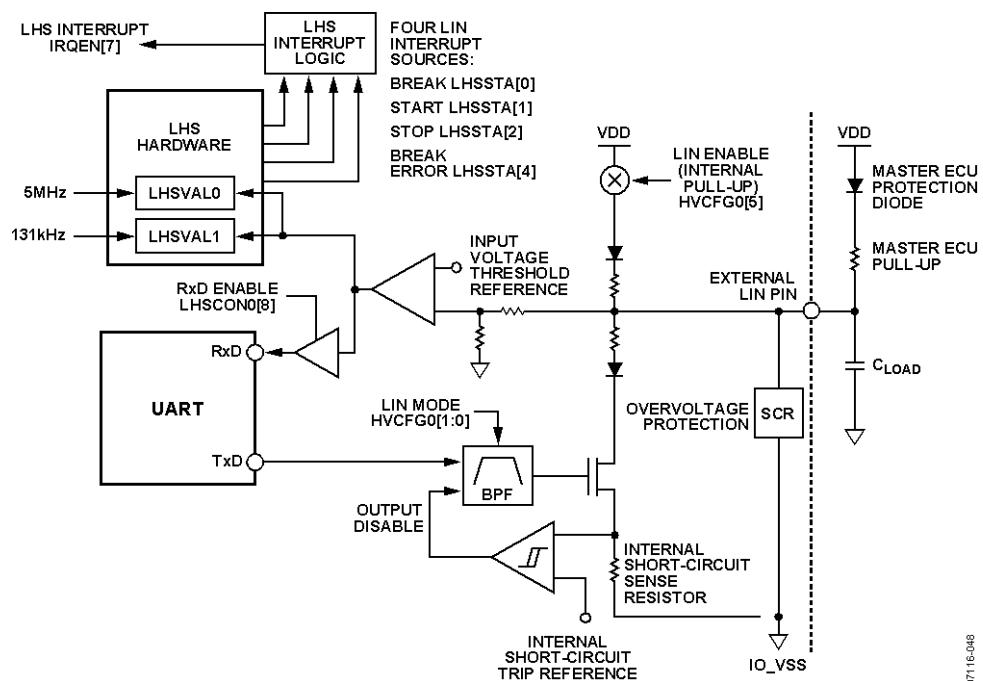

## 機能ブロック図

0716001

図 1.

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。

※日本語データシートは REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

©2008 Analog Devices, Inc. All rights reserved.

# 目次

|                                      |    |

|--------------------------------------|----|

| 特長                                   | 1  |

| アプリケーション                             | 1  |

| 機能プロック図                              | 1  |

| 改訂履歴                                 | 2  |

| 仕様                                   | 3  |

| 電気的仕様                                | 3  |

| タイミング仕様                              | 9  |

| 絶対最大定格                               | 14 |

| ESD の注意                              | 14 |

| ピン配置およびピン機能説明                        | 15 |

| 代表的な性能特性                             | 17 |

| 用語                                   | 18 |

| 動作原理                                 | 19 |

| ARM7TDMI コアの概要                       | 19 |

| メモリ構成                                | 21 |

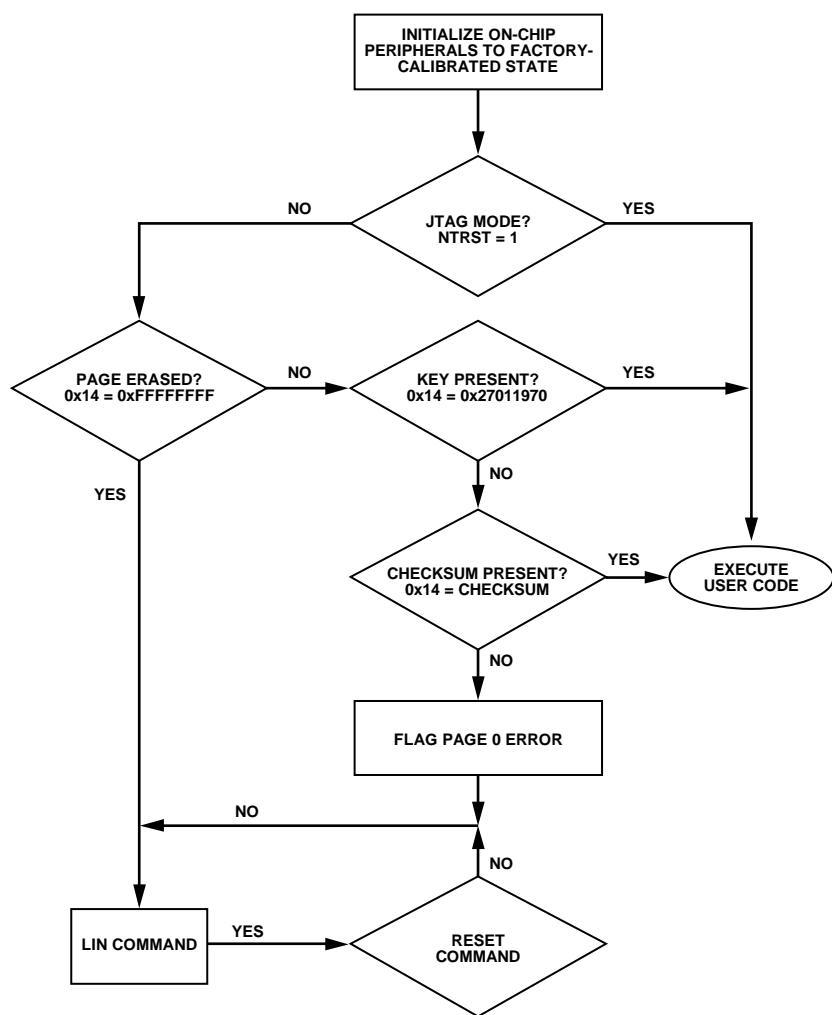

| リセット                                 | 23 |

| フラッシュ/EE メモリ                         | 24 |

| Flash/EE メモリのインサーキット書き込み             | 24 |

| フラッシュ/EE メモリ・コントロール・インターフェース         | 24 |

| フラッシュ/EE メモリのセキュリティ                  | 27 |

| フラッシュ/EE メモリの信頼性                     | 28 |

| SRAM とフラッシュ/EE からのコード実行時間            | 29 |

| ADuC7034 カーネル                        | 30 |

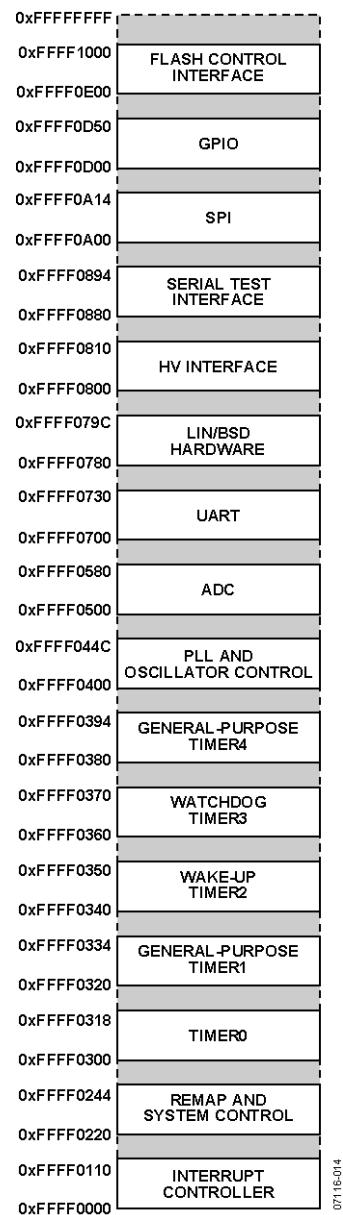

| メモリ・マップド・レジスタ                        | 32 |

| 全 MMR のリスト                           | 33 |

| 16 ビット $\Sigma$ - $\Delta$ A/D コンバータ | 39 |

| 電流チャンネル ADC (I-ADC)                  | 39 |

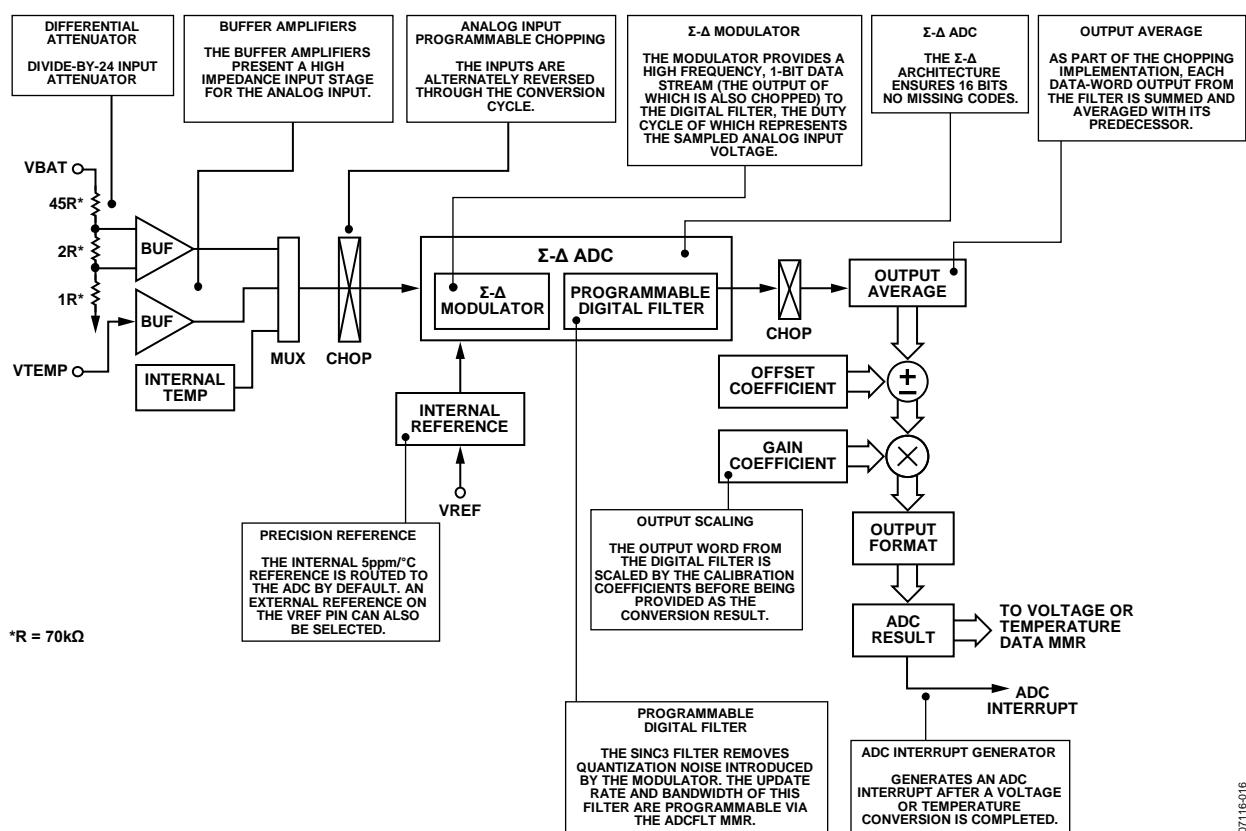

| 電圧/温度チャンネル ADC (V/T-ADC)             | 41 |

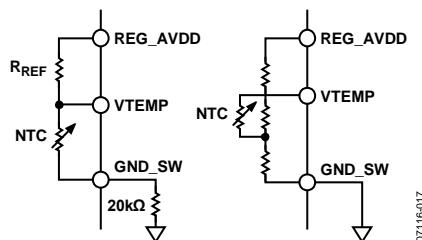

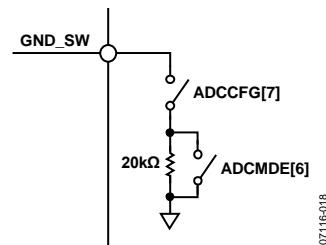

| ADC グラウンド・スイッチ                       | 42 |

| ADC ノイズの性能表                          | 42 |

| ADC MMR インターフェース                     | 43 |

| ADC 低消費電力動作モード                       | 53 |

| ADC コンパレータとアキュムレータ                   | 54 |

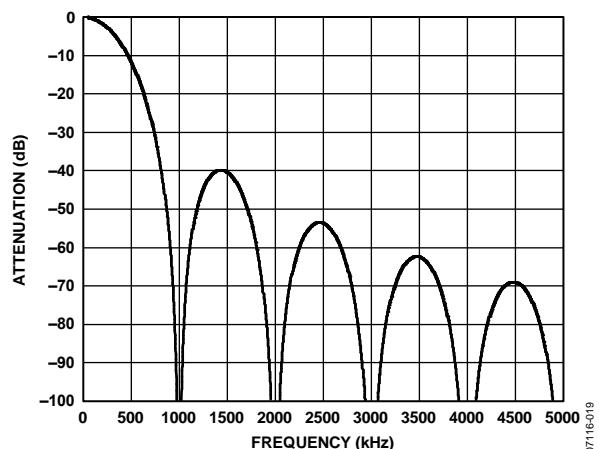

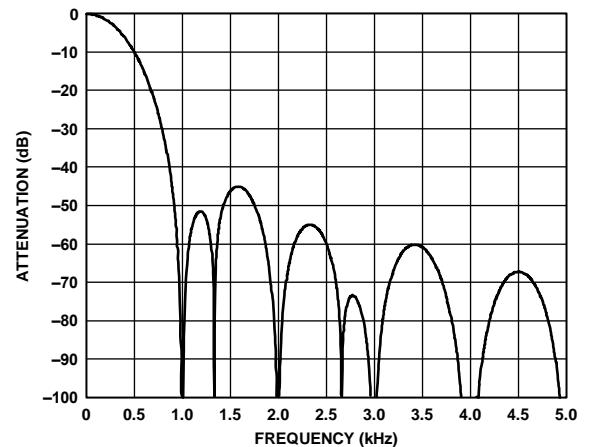

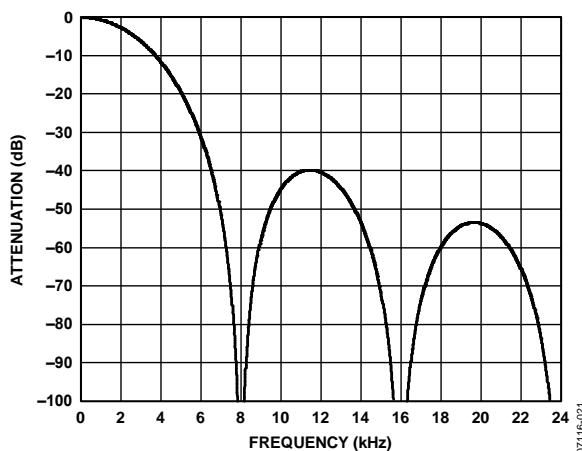

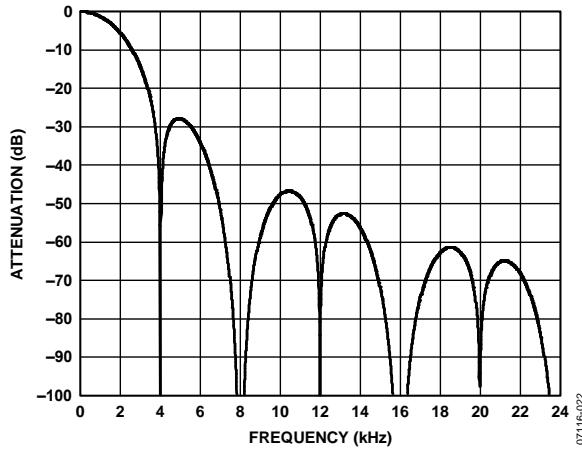

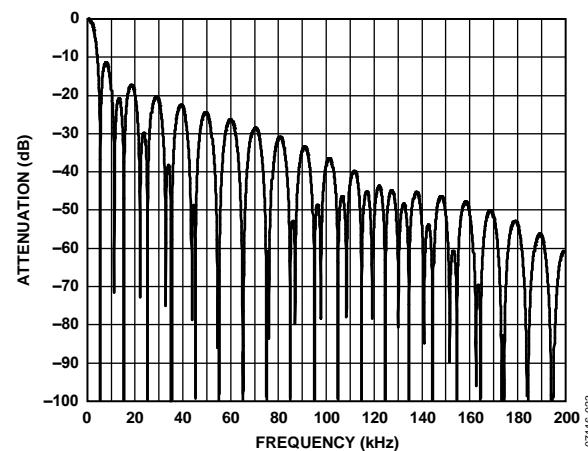

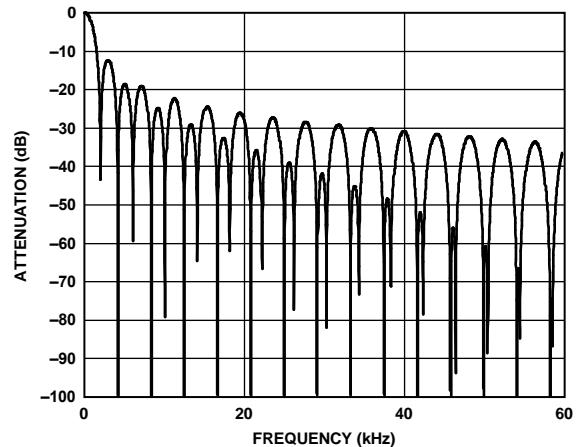

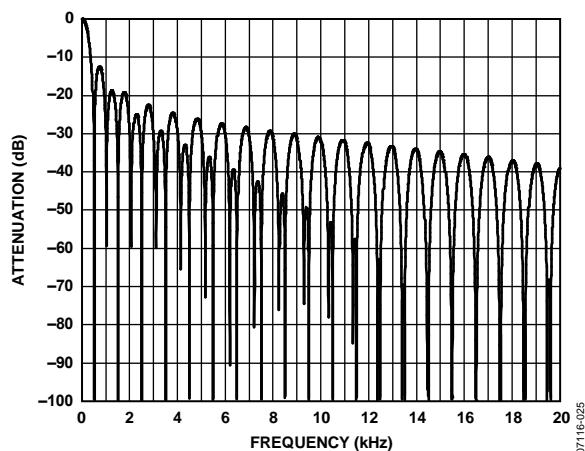

| ADC Sinc3 デジタル・フィルタの応答               | 54 |

| ADC Calibration                      | 57 |

| ADC 診断                               | 58 |

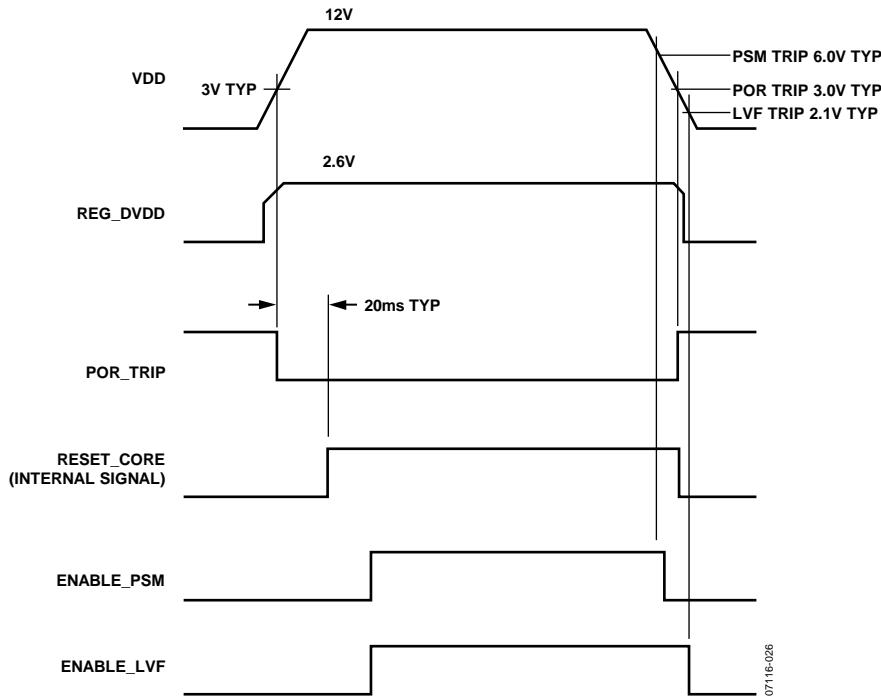

| 電源サポート回路                             | 59 |

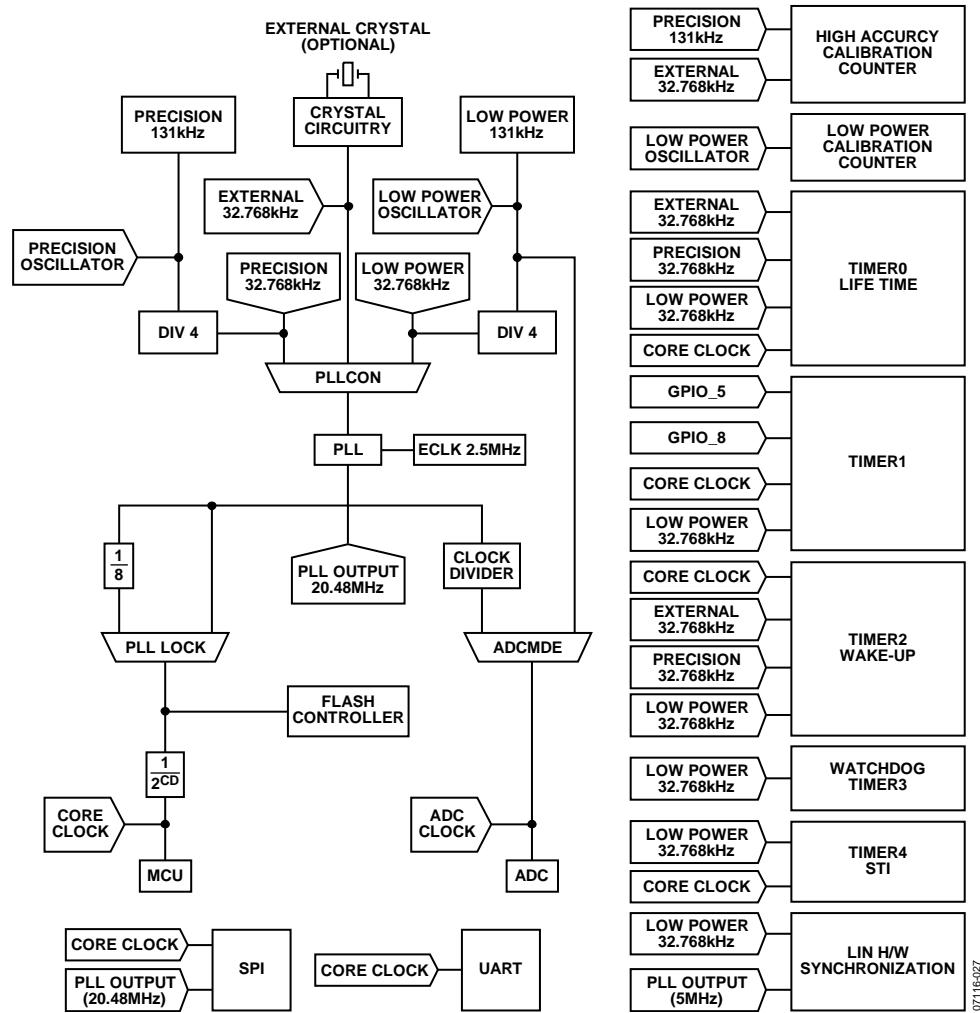

| ADuC7034 のシステム・クロック                  | 60 |

| システム・クロック・レジスタ                       | 61 |

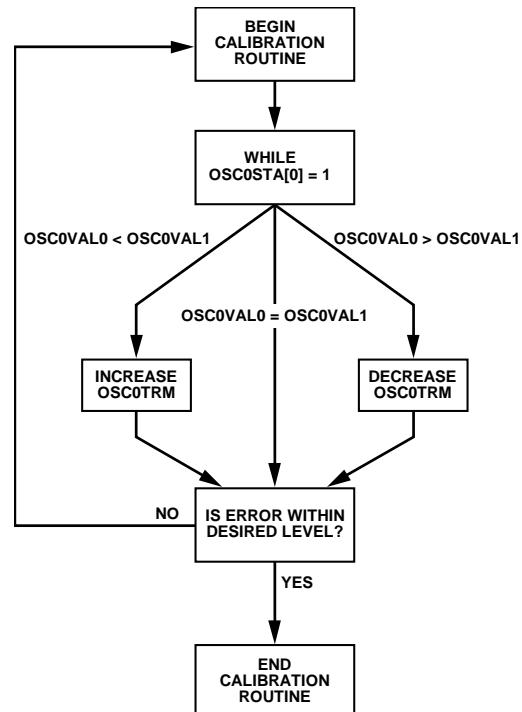

| 低消費電力クロックのキャリブレーション                  | 64 |

| プロセッサ参照ペリフェラル                        | 66 |

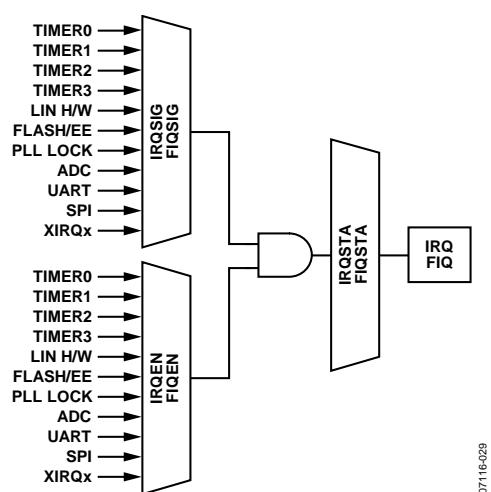

| 割り込みシステム                             | 66 |

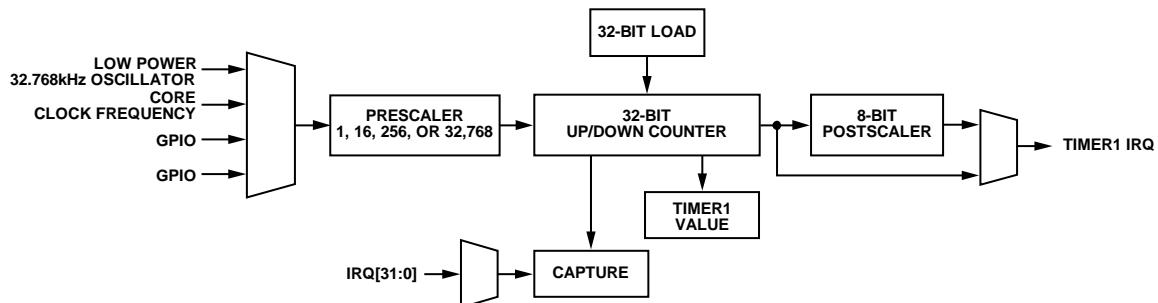

| タイマー                                 | 69 |

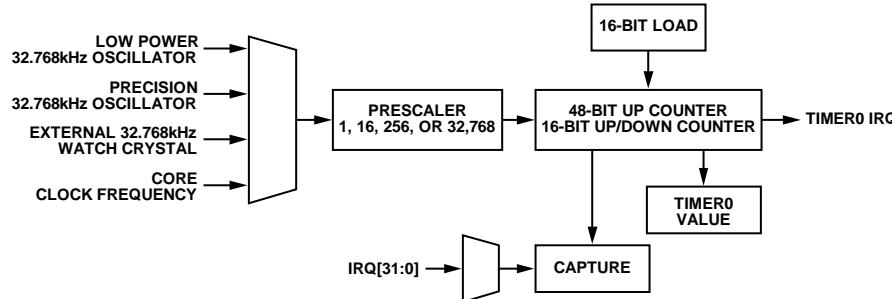

| タイマー0—寿命タイマー                         | 70 |

|                                     |     |

|-------------------------------------|-----|

| タイマー1                               | 72  |

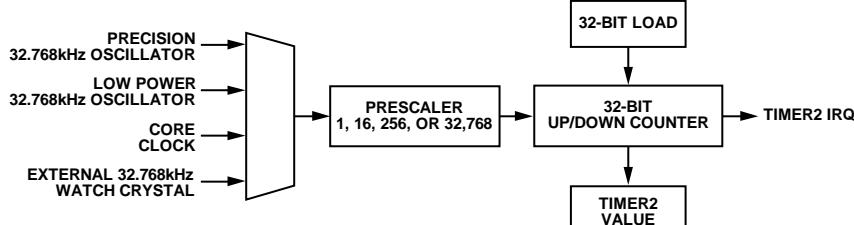

| タイマー2、ウェイクアップ・タイマー                  | 74  |

| タイマー3、ウォッチドッグ・タイマー                  | 76  |

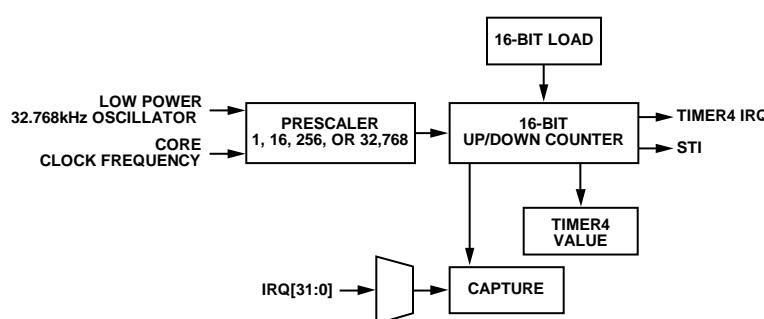

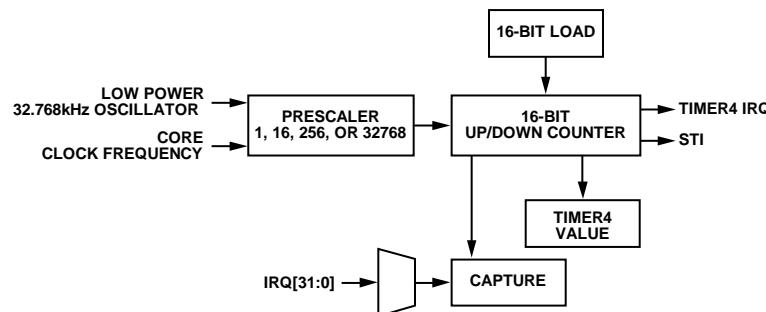

| タイマー4—STI タイマー                      | 78  |

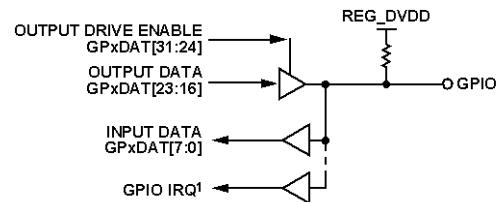

| 汎用 I/O                              | 80  |

| General-Purpose I/O レジスタ            | 82  |

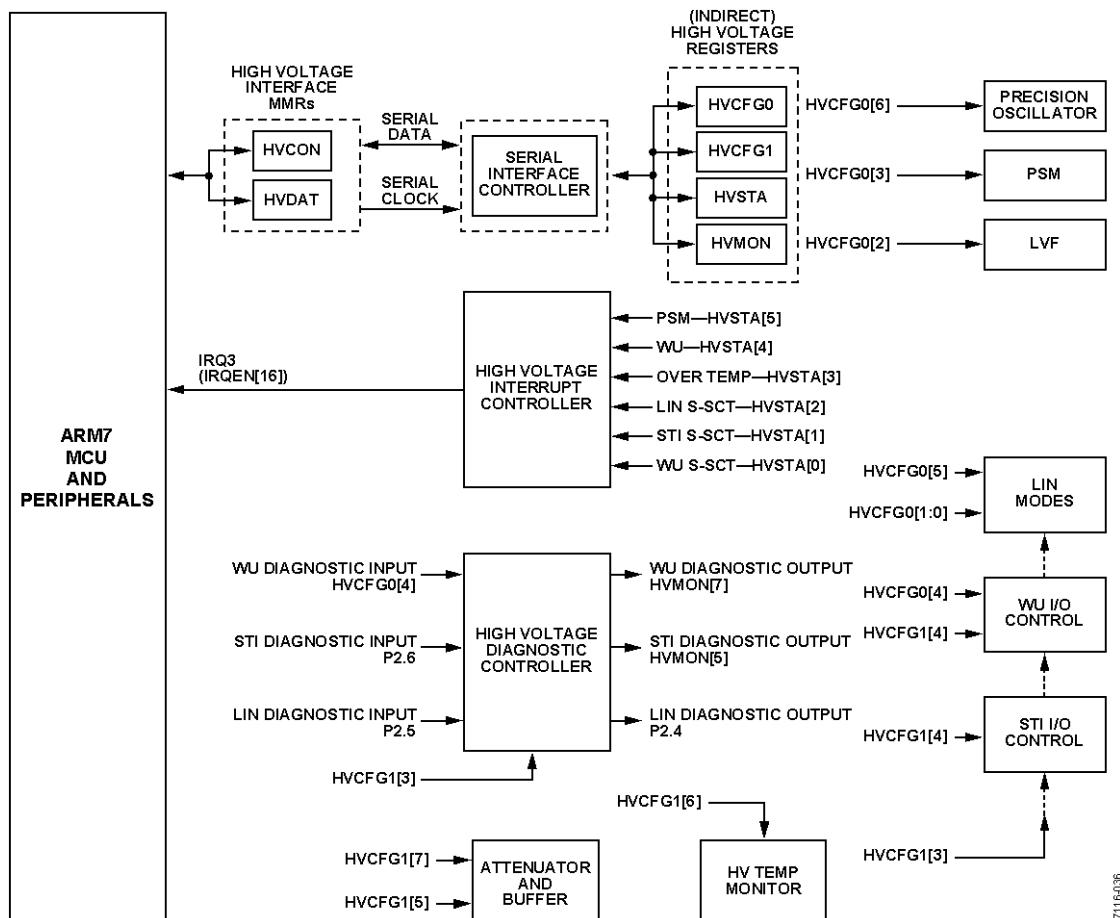

| 高電圧ペリフェラル・コントロール・インターフェース           | 91  |

| 高電圧ペリフェラル・コントロール・インターフェース・レジスタ      | 92  |

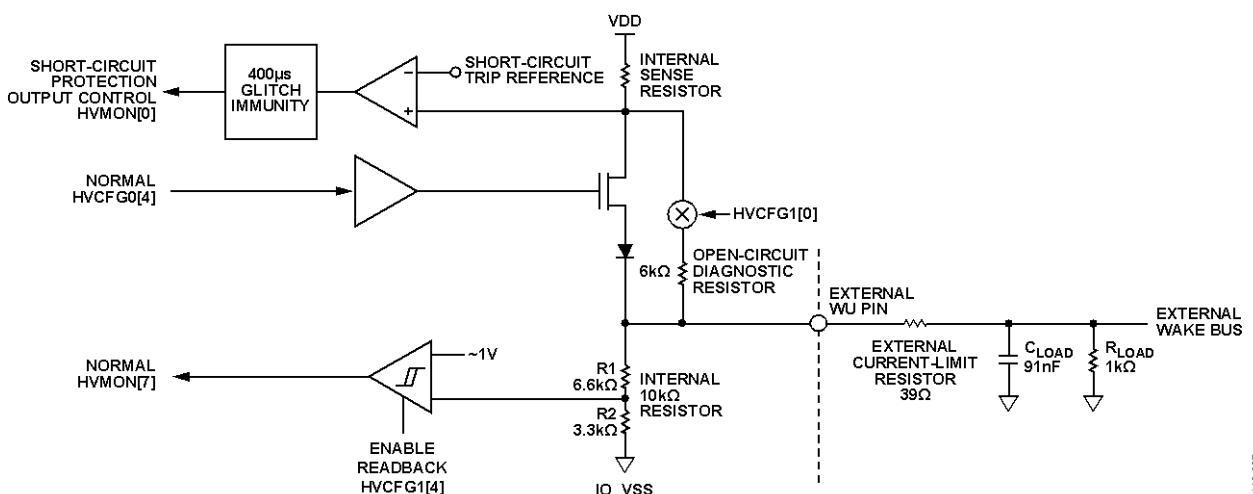

| ウェイクアップ(WU)ピン                       | 98  |

| 高電圧ペリフェラル・コントロール・インターフェースからの割り込みの処理 | 99  |

| 低電圧フラグ(LVF)                         | 99  |

| 高電圧診断                               | 99  |

| UART シリアル・インターフェース                  | 100 |

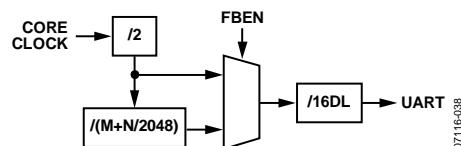

| ポート・レートの発生                          | 100 |

| UART レジスタの定義                        | 101 |

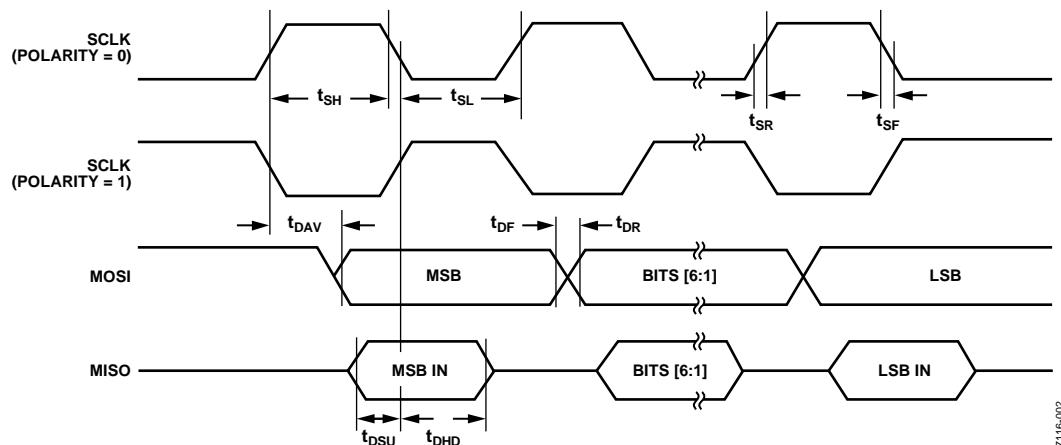

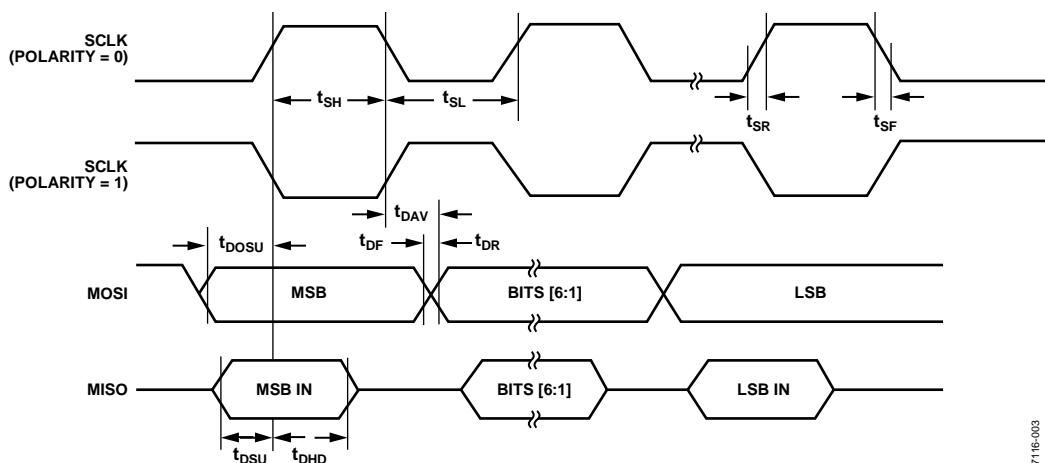

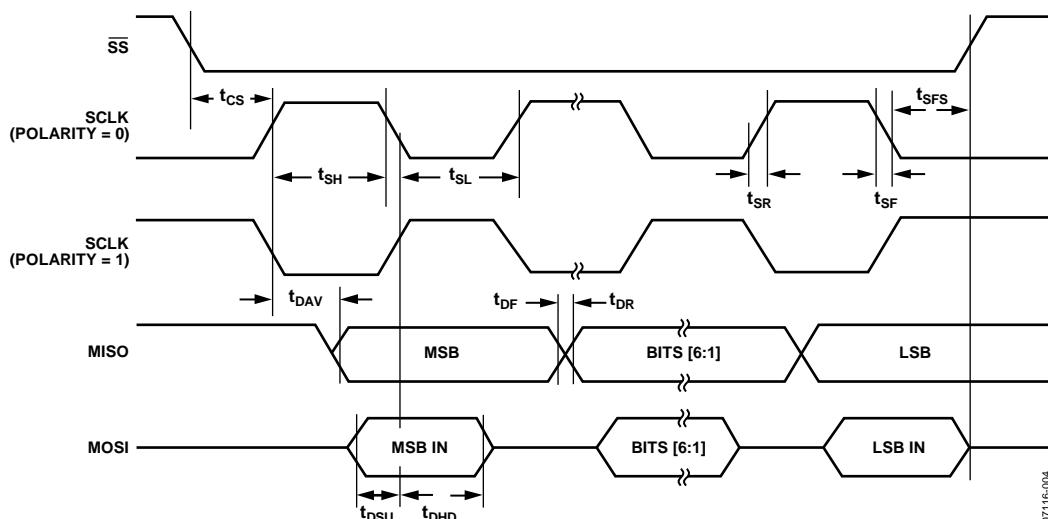

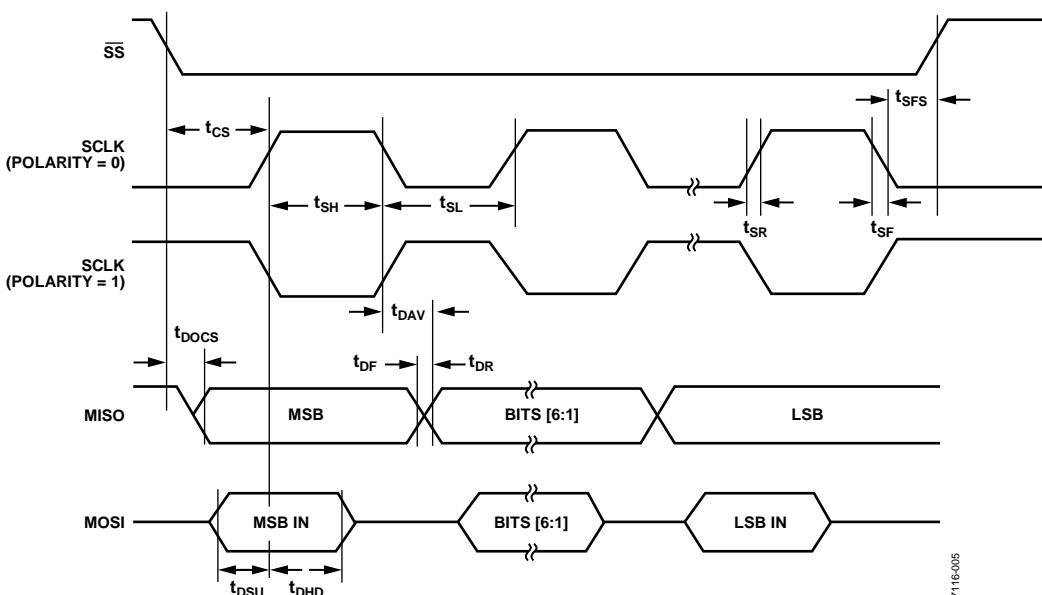

| シリアル・ペリフェラル・インターフェース                | 106 |

| MISO ピン                             | 106 |

| MOSI ピン                             | 106 |

| SCLK ピン                             | 106 |

| SS ピン                               | 106 |

| SPI レジスタの定義                         | 106 |

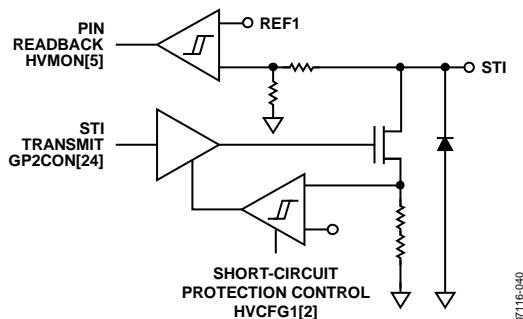

| シリアル・テスト・インターフェース                   | 110 |

| シリアル・テスト・インターフェース・レジスタ              | 110 |

| シリアル・テスト・インターフェースの出力構造              | 112 |

| シリアル・テスト・インターフェースの使用方法              | 112 |

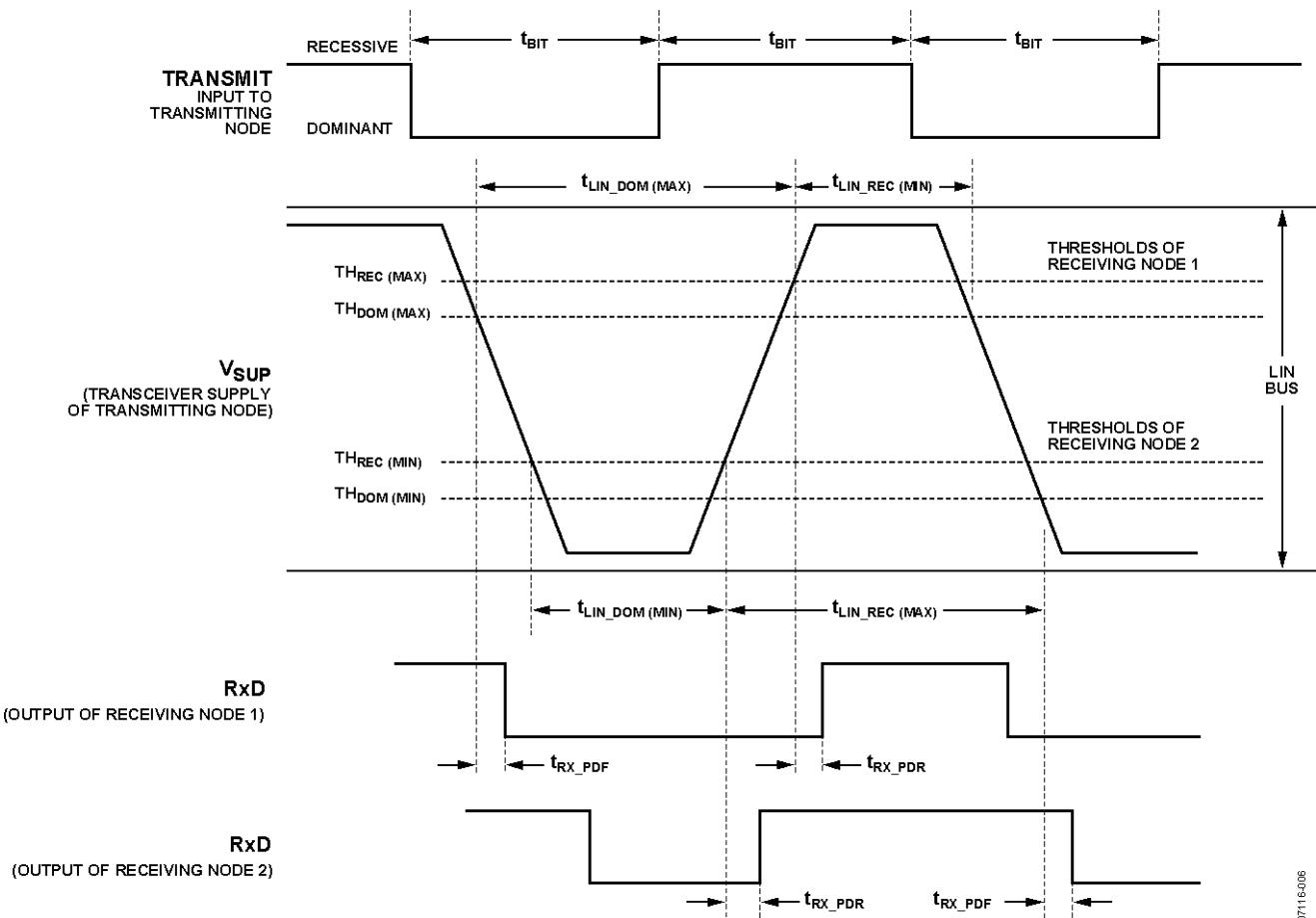

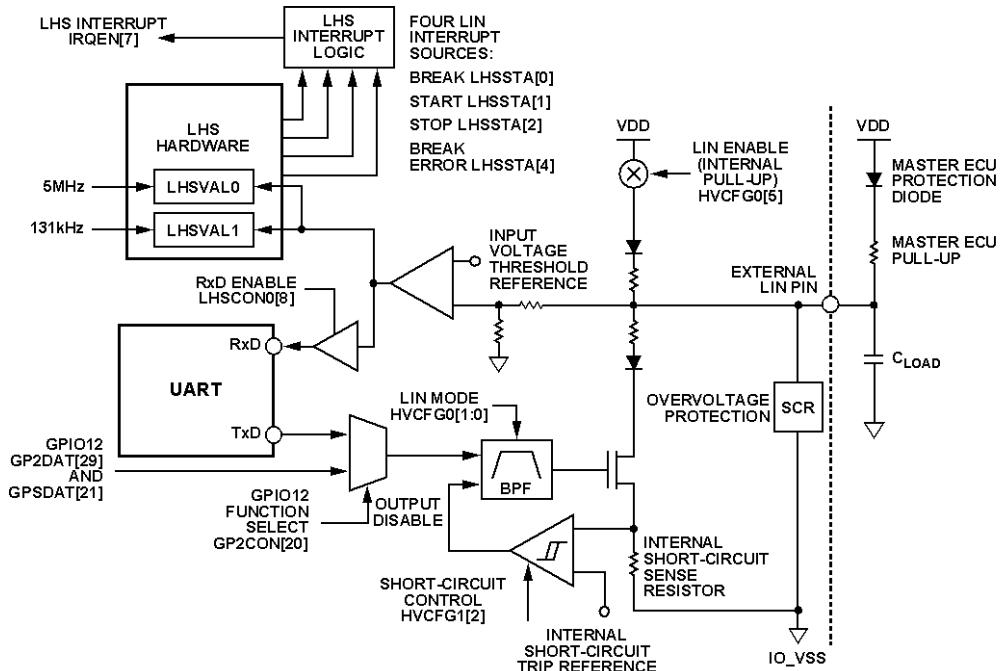

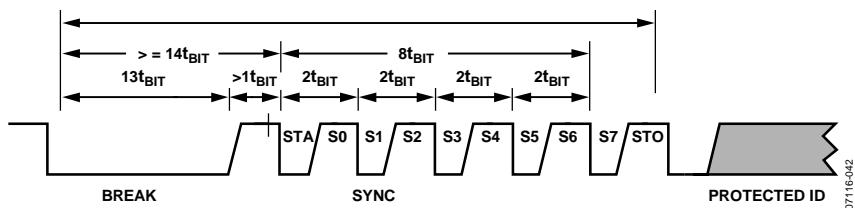

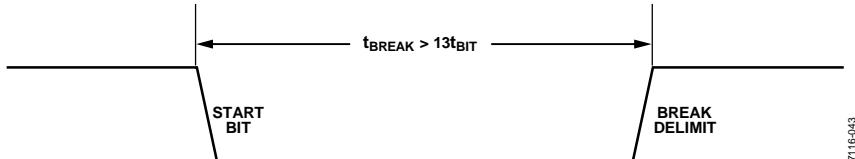

| LIN (ローカル・インターフェース) インターフェース        | 114 |

| LIN MMR の説明                         | 114 |

| LIN ハードウェア・インターフェース                 | 118 |

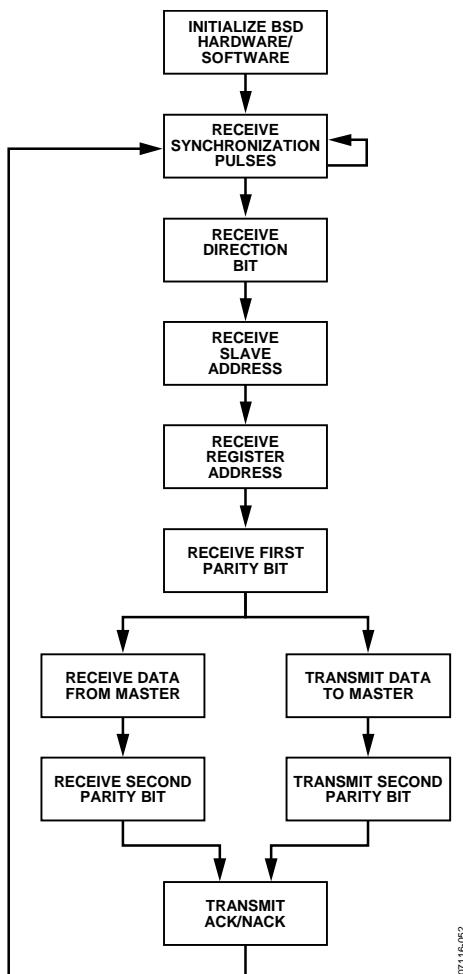

| ビット・シリアル・デバイス(BSD)インターフェース          | 123 |

| BSD 通信のハードウェア・インターフェース              | 123 |

| BSD 関連の MMR                         | 124 |

| BSD 通信フレーム                          | 125 |

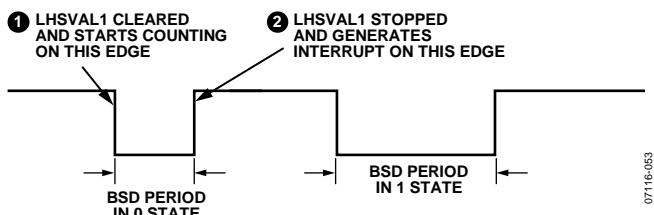

| BSD データの受信                          | 126 |

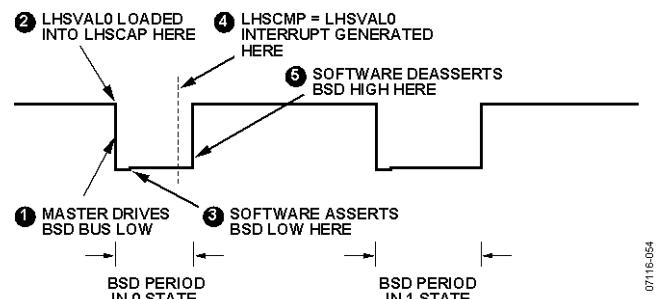

| BSD データの送信                          | 126 |

| BSD インターフェースからのウェイクアップ              | 126 |

| デバイスの識別                             | 127 |

| デバイス識別レジスタ                          | 127 |

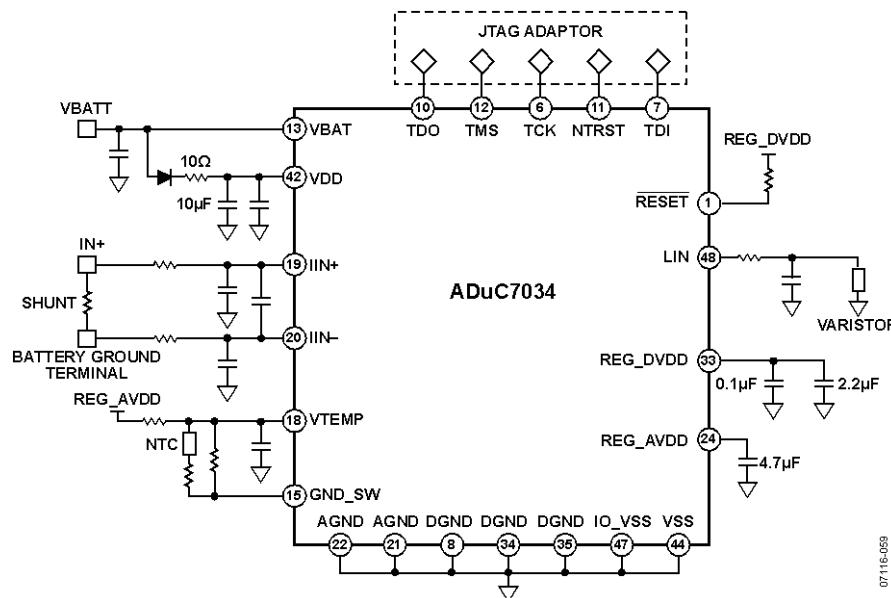

| 回路図                                 | 130 |

| 外形寸法                                | 131 |

| オーダー・ガイド                            | 131 |

## 改訂履歴

4/08—Revision 0: Initial Version

# 仕様

## 電気的仕様

特に指定のない限り、 $V_{DD} = 3.5$  V～18 V、 $V_{REF} = 1.2$  V 内部リファレンス電圧、 $f_{CORE} = 10.24$  MHz (外付け 32.768 kHz の時計水晶または内蔵高精度発振器から駆動)、すべての仕様は  $T_A = -40^\circ\text{C} \sim +115^\circ\text{C}$  で規定。

表 1.

| Parameter                                     | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Min                                                                                                                     | Typ                                                                                                                       | Max                 | Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC SPECIFICATIONS                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                         |                                                                                                                           |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Conversion Rate <sup>1</sup>                  | Chop off, ADC normal operating mode<br>Chop on, ADC normal operating mode<br>Chop on, ADC low power mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4<br>4<br>1                                                                                                             |                                                                                                                           | 8000<br>2600<br>650 | Hz<br>Hz<br>Hz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Current Channel                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                         |                                                                                                                           |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| No Missing Codes <sup>1</sup>                 | Valid for all ADC update rates and ADC modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 16                                                                                                                      |                                                                                                                           |                     | Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Integral Nonlinearity <sup>1, 2</sup>         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                         | ±10                                                                                                                       | ±60                 | ppm of FSR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

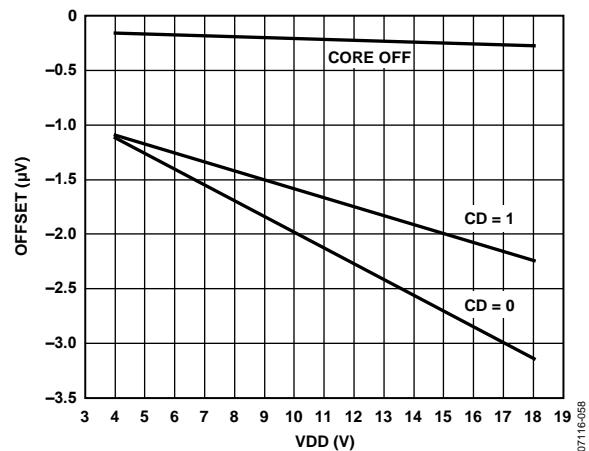

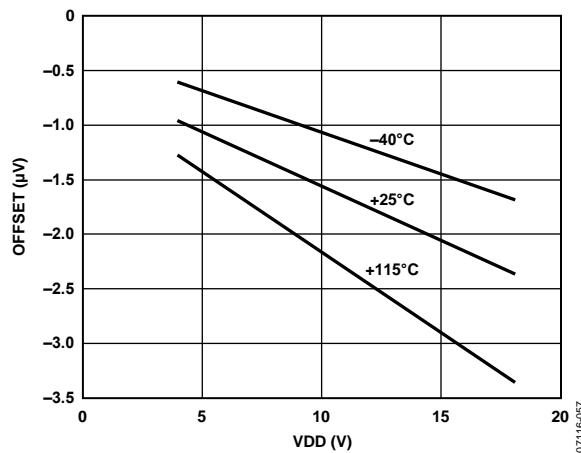

| Offset Error <sup>2, 3, 4, 5</sup>            | Chop off, 1 LSB = 36.6 $\mu\text{V}$ /gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -10                                                                                                                     | ±3                                                                                                                        | +10                 | LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Offset Error <sup>1, 3, 6</sup>               | Chop on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -2                                                                                                                      | ±0.5                                                                                                                      | +2                  | $\mu\text{V}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Offset Error <sup>1, 3</sup>                  | Chop on, low power mode or low power plus mode, MCU powered down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 100                                                                                                                     | -50                                                                                                                       | -300                | nV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Offset Error <sup>1, 3</sup>                  | Chop on, normal mode, CD = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0.5                                                                                                                     | -1.25                                                                                                                     | -3                  | $\mu\text{V}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

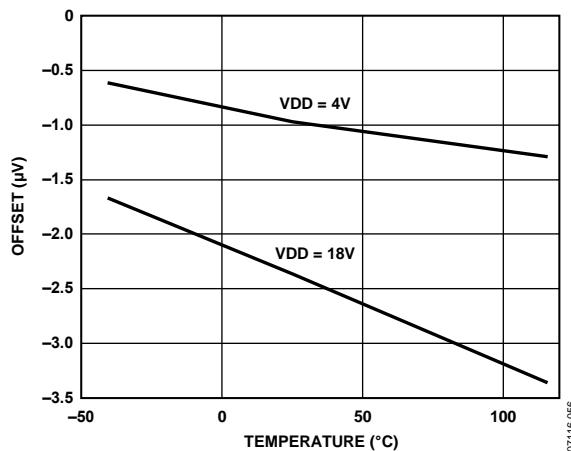

| Offset Error Drift <sup>6</sup>               | Chop off, valid for ADC gains of 4 to 64, normal mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                         | 0.03                                                                                                                      |                     | LSB/°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Offset Error Drift <sup>6</sup>               | Chop off, valid for ADC gains of 128 to 512, normal mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                         | 30                                                                                                                        |                     | nV/°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Offset Error Drift <sup>6</sup>               | Chop on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                         | 10                                                                                                                        |                     | nV/°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Total Gain Error <sup>1, 3, 7, 8, 9, 10</sup> | Normal mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -0.5                                                                                                                    | ±0.1                                                                                                                      | +0.5                | %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Total Gain Error <sup>1, 3, 7, 9</sup>        | Low power mode using ADCREF MMR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -4                                                                                                                      | ±0.2                                                                                                                      | +4                  | %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Total Gain Error <sup>1, 3, 7, 9, 11</sup>    | Low power plus mode, using precision VREF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -1                                                                                                                      | ±0.2                                                                                                                      | +1                  | %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Gain Drift                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                         | 3                                                                                                                         |                     | ppm/°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PGA Gain Mismatch Error                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                         | ±0.1                                                                                                                      |                     | %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Output Noise <sup>1, 12</sup>                 | 4 Hz update rate, gain = 512, ADCFLT = 0xBF1D<br>4 Hz update rate, gain = 512, ADCFLT = 0x3F1D<br>10 Hz update rate, gain = 512, ADCFLT = 0x961F<br>10 Hz update rate, gain = 512, ADCFLT = 0x161F<br>1 kHz update rate, gain $\geq$ 64, ADCFLT = 0x8101<br>1 kHz update rate, gain $\geq$ 64, ADCFLT = 0x0101<br>1 kHz update rate, gain = 512, ADCFLT = 0x0007<br>1 kHz update rate, gain = 32, ADCFLT = 0x0007<br>1 kHz update rate, gain = 8, ADCFLT = 0x8101<br>1 kHz update rate, gain = 8, ADCFLT = 0x0007<br>1 kHz update rate, gain = 8, ADCFLT = 0x0101<br>1 kHz update rate, gain = 4, ADCFLT = 0x0007<br>8 kHz update rate, gain = 32, ADCFLT = 0x0000<br>8 kHz update rate, gain = 4, ADCFLT = 0x0000<br>ADC low power mode, $f_{ADC} = 10$ Hz, gain = 128<br>ADC low power mode, $f_{ADC} = 1$ Hz, gain = 128<br>ADC low power plus mode, $f_{ADC} = 1$ Hz, gain = 512<br>ADC low power plus mode, $f_{ADC} = 250$ Hz, gain = 512, chop enabled | 60<br>75<br>100<br>120<br>0.8<br>1<br>0.6<br>0.8<br>2.1<br>1.6<br>2.6<br>2.0<br>2.5<br>14<br>1.25<br>0.35<br>0.1<br>0.6 | 90<br>115<br>150<br>180<br>1.2<br>1.5<br>0.9<br>1.2<br>4.1<br>2.4<br>3.9<br>2.8<br>3.5<br>21<br>1.9<br>0.5<br>0.15<br>0.9 |                     | nV rms<br>nV rms<br>nV rms<br>nV rms<br>$\mu\text{V}$ rms |

| Voltage Channel <sup>13</sup>                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                         |                                                                                                                           |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| No Missing Codes <sup>1</sup>                 | Valid at all ADC update rates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 16                                                                                                                      |                                                                                                                           |                     | Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Integral Nonlinearity <sup>1</sup>            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                         | ±10                                                                                                                       | ±60                 | ppm of FSR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Offset Error <sup>3, 5</sup>                  | Chop off, 1 LSB = 439.5 $\mu\text{V}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -10                                                                                                                     | ±1                                                                                                                        | +10                 | LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Offset Error <sup>1, 3</sup>                  | Chop on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                         | 0.3                                                                                                                       | 1                   | LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Offset Error Drift                            | Chop off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                         | 0.03                                                                                                                      |                     | LSB/°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Total Gain Error <sup>1, 3, 7, 10, 14</sup>   | Includes resistor mismatch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -0.25                                                                                                                   | ±0.06                                                                                                                     | +0.25               | %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Total Gain Error <sup>1, 3, 7, 10, 14</sup>   | Temperature range = $-25^\circ\text{C}$ to $+65^\circ\text{C}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -0.15                                                                                                                   | ±0.03                                                                                                                     | +0.15               | %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Gain Drift                                    | Includes resistor mismatch drift                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                         | 3                                                                                                                         |                     | ppm/°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Parameter                                      | Test Conditions/Comments                                                                                                                                                                                                        | Min                                   | Typ                                   | Max   | Unit                                                     |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------|-------|----------------------------------------------------------|

| Output Noise <sup>1, 15</sup>                  | 4 Hz update rate, ADCFLT = 0xBF1D<br>10 Hz update rate, ADCFLT = 0x961F<br>1 kHz update rate, ADCFLT = 0x0007<br>1 kHz update rate, ADCFLT = 0x8101<br>1 kHz update rate, ADCFLT = 0x0101<br>8 kHz update rate, ADCFLT = 0x0000 | 60<br>60<br>180<br>240<br>270<br>1600 | 90<br>90<br>270<br>307<br>405<br>2400 |       | µV rms<br>µV rms<br>µV rms<br>µV rms<br>µV rms<br>µV rms |

| Temperature Channel                            |                                                                                                                                                                                                                                 |                                       |                                       |       |                                                          |

| No Missing Codes <sup>1</sup>                  | Valid at all ADC update rates                                                                                                                                                                                                   | 16                                    |                                       |       | Bits                                                     |

| Integral Nonlinearity <sup>1</sup>             |                                                                                                                                                                                                                                 |                                       | ±10                                   | ±60   | ppm of FSR                                               |

| Offset Error <sup>3,4,5, 16</sup>              | Chop off, 1 LSB = 19.84 µV in unipolar mode, tested at gain of 4                                                                                                                                                                | -10                                   | ±3                                    | +10   | LSB                                                      |

| Offset Error <sup>1, 3</sup>                   | Chop on                                                                                                                                                                                                                         | -5                                    | +1                                    | +5    | LSB                                                      |

| Offset Error Drift                             | Chop off                                                                                                                                                                                                                        |                                       | 0.03                                  |       | LSB/°C                                                   |

| Total Gain Error <sup>1, 3, 14</sup>           |                                                                                                                                                                                                                                 | -0.2                                  | ±0.06                                 | +0.2  | %                                                        |

| Gain Drift                                     |                                                                                                                                                                                                                                 |                                       | 3                                     |       | ppm/°C                                                   |

| Output Noise <sup>1</sup>                      | 1 kHz update rate                                                                                                                                                                                                               |                                       | 7.5                                   | 11.25 | µV rms                                                   |

| ADC SPECIFICATIONS ANALOG INPUT                | Internal VREF = 1.2 V                                                                                                                                                                                                           |                                       |                                       |       |                                                          |

| Current Channel                                |                                                                                                                                                                                                                                 |                                       |                                       |       |                                                          |

| Absolute Input Voltage Range                   | Applies to both IIN+ and IIN-                                                                                                                                                                                                   | -200                                  |                                       | +300  | mV                                                       |

| Input Voltage Range <sup>17, 18</sup>          | Gain = 1 <sup>19</sup>                                                                                                                                                                                                          |                                       | ±1.2                                  |       | V                                                        |

|                                                | Gain = 2 <sup>19</sup>                                                                                                                                                                                                          |                                       | ±600                                  |       | mV                                                       |

|                                                | Gain = 4 <sup>19</sup>                                                                                                                                                                                                          |                                       | ±300                                  |       | mV                                                       |

|                                                | Gain = 8                                                                                                                                                                                                                        |                                       | ±150                                  |       | mV                                                       |

|                                                | Gain = 16                                                                                                                                                                                                                       |                                       | ±75                                   |       | mV                                                       |

|                                                | Gain = 32                                                                                                                                                                                                                       |                                       | ±37.5                                 |       | mV                                                       |

|                                                | Gain = 64                                                                                                                                                                                                                       |                                       | ±18.75                                |       | mV                                                       |

|                                                | Gain = 128                                                                                                                                                                                                                      |                                       | ±9.375                                |       | mV                                                       |

|                                                | Gain = 256                                                                                                                                                                                                                      |                                       | ±4.68                                 |       | mV                                                       |

|                                                | Gain = 512                                                                                                                                                                                                                      |                                       | ±2.3                                  |       | mV                                                       |

| Input Leakage Current <sup>1</sup>             |                                                                                                                                                                                                                                 | -3                                    |                                       | +3    | nA                                                       |

| Input Offset Current <sup>1, 20</sup>          |                                                                                                                                                                                                                                 |                                       | 0.5                                   | 1.5   | nA                                                       |

| Voltage Channel                                |                                                                                                                                                                                                                                 |                                       |                                       |       |                                                          |

| Absolute Input Voltage Range                   |                                                                                                                                                                                                                                 | 4                                     |                                       | 18    | V                                                        |

| Input Voltage Range                            |                                                                                                                                                                                                                                 |                                       | 0 to 28.8                             |       | V                                                        |

| VBAT Input Current                             | VBAT = 18 V                                                                                                                                                                                                                     | 3                                     | 5.5                                   | 8     | µA                                                       |

| Temperature Channel                            | Reference selection: REG_AVDD/2 to GND_SW/2                                                                                                                                                                                     |                                       |                                       |       |                                                          |

| Absolute Input Voltage Range                   |                                                                                                                                                                                                                                 | 100                                   |                                       | 1300  | mV                                                       |

| Input Voltage Range                            |                                                                                                                                                                                                                                 |                                       | 0 to VREF                             |       | V                                                        |

| VTEMP Input Current <sup>1</sup>               |                                                                                                                                                                                                                                 |                                       | 2.5                                   | 160   | nA                                                       |

| VOLTAGE REFERENCE                              |                                                                                                                                                                                                                                 |                                       |                                       |       |                                                          |

| ADC Precision Reference                        |                                                                                                                                                                                                                                 |                                       |                                       |       |                                                          |

| Internal VREF                                  |                                                                                                                                                                                                                                 |                                       | 1.2                                   |       | V                                                        |

| Power-Up Time <sup>1</sup>                     |                                                                                                                                                                                                                                 |                                       | 0.5                                   |       | ms                                                       |

| Initial Accuracy <sup>1</sup>                  | Measured at T <sub>A</sub> = 25°C                                                                                                                                                                                               | -0.15                                 |                                       | +0.15 | %                                                        |

| Temperature Coefficient <sup>1, 21</sup>       |                                                                                                                                                                                                                                 | -20                                   | ±5                                    | +20   | ppm/°C                                                   |

| Reference Long-Term Stability <sup>22</sup>    |                                                                                                                                                                                                                                 |                                       | 100                                   |       | ppm/1000 hr                                              |

| External Reference Input Range <sup>23</sup>   |                                                                                                                                                                                                                                 | 0.1                                   |                                       | 1.3   | V                                                        |

| VREF Divide-by-2 Initial Error <sup>1</sup>    |                                                                                                                                                                                                                                 |                                       | 0.1                                   | 0.3   | %                                                        |

| ADC Low Power Reference                        |                                                                                                                                                                                                                                 |                                       |                                       |       |                                                          |

| Internal VREF                                  |                                                                                                                                                                                                                                 |                                       | 1.2                                   |       | V                                                        |

| Initial Accuracy                               | Measured at T <sub>A</sub> = 25°C                                                                                                                                                                                               | -5                                    |                                       | +5    | %                                                        |

| Initial Accuracy <sup>1</sup>                  | Using ADCREF, measured at T <sub>A</sub> = 25°C                                                                                                                                                                                 |                                       | 0.1                                   |       | %                                                        |

| Temperature Coefficient <sup>1, 21</sup>       |                                                                                                                                                                                                                                 | -300                                  | ±150                                  | +300  | ppm/°C                                                   |

| ADC DGNOSTICS                                  |                                                                                                                                                                                                                                 |                                       |                                       |       |                                                          |

| VREF/136 <sup>1</sup>                          | At any gain settings                                                                                                                                                                                                            | 8.5                                   |                                       | 9.4   | mV                                                       |

| Voltage Attenuator Current Source <sup>1</sup> | Differential voltage increase on the attenuator when the                                                                                                                                                                        | 3.1                                   |                                       | 3.8   | V                                                        |

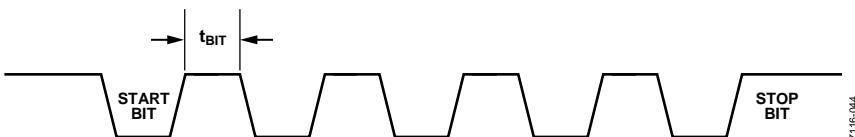

| Parameter                                                                                                                                                                                | Test Conditions/Comments                                                                                                                                             | Min               | Typ                                   | Max                    | Unit                                                                   |