## 特長

74.25MHz、20/30ビットの高解像度入力

SMPTE 274M (1080i)、296M (720p)、240M (1035i) に準拠

6個のNoise Shaped Video (NSV) 方式14ビット・ビデオDACを内蔵

SD用の16倍 (216MHz) DACオーバーサンプリング

ED用の8倍 (216MHz) DACオーバーサンプリング

HD用の4倍 (297MHz) DACオーバーサンプリング

37mA (max) のDAC出力電流

NTSC M、PAL B/D/G/H/I/M/N、PAL 60をサポート

NTSCおよびPALスクエア・ピクセル動作 (24.54/29.5MHz)

マルチフォーマット・ビデオ入力

4:2:2 YCrCb (SD、ED、HD)

4:4:4 YCrCb (EDとHD)

4:4:4 RGB (SD、ED、HD)

マルチフォーマット・ビデオ出力

コンポジット (CVBS) とSビデオ (Y/C)

コンポーネント YPrPb (SD、ED、HD)

コンポーネントRGB (SD、ED、HD)

Macrovision® Rev 7.1.L1 (SD) とRev 1.2 (ED) に準拠

SDとED/HDの同時動作

EIA/CEA-861Bコンプライアンス

## プログラマブル機能

ルミナスおよびクロミナス・フィルタ応答

垂直プランギング期間 (VBI)

サブキャリア周波数 ( $F_{SC}$ ) と位相

ルミナス遅延

コピー・ジェネレーション・マネジメント・システム (CGMS)

クローズド・キャプショニングとワイド・スクリーン・シグナリング (WSS)

外部ビデオ・ソースへのサブキャリア・ロック機能内蔵

完全なビデオ・タイミング・ジェネレータ内蔵

テスト・パターン・ジェネレータ内蔵

リファレンス電圧を内蔵 (オプションの外部入力)

I<sup>2</sup>C®/SPI®デュアル互換のシリアルMPUインターフェース

3.3Vアナログ動作

1.8Vデジタル動作

3.3V I/O動作

温度範囲: -40~+85°C

## アプリケーション

DVDレコーダとプレーヤ

高解像度ブルーレイDVDプレーヤ

HD DVDプレーヤ

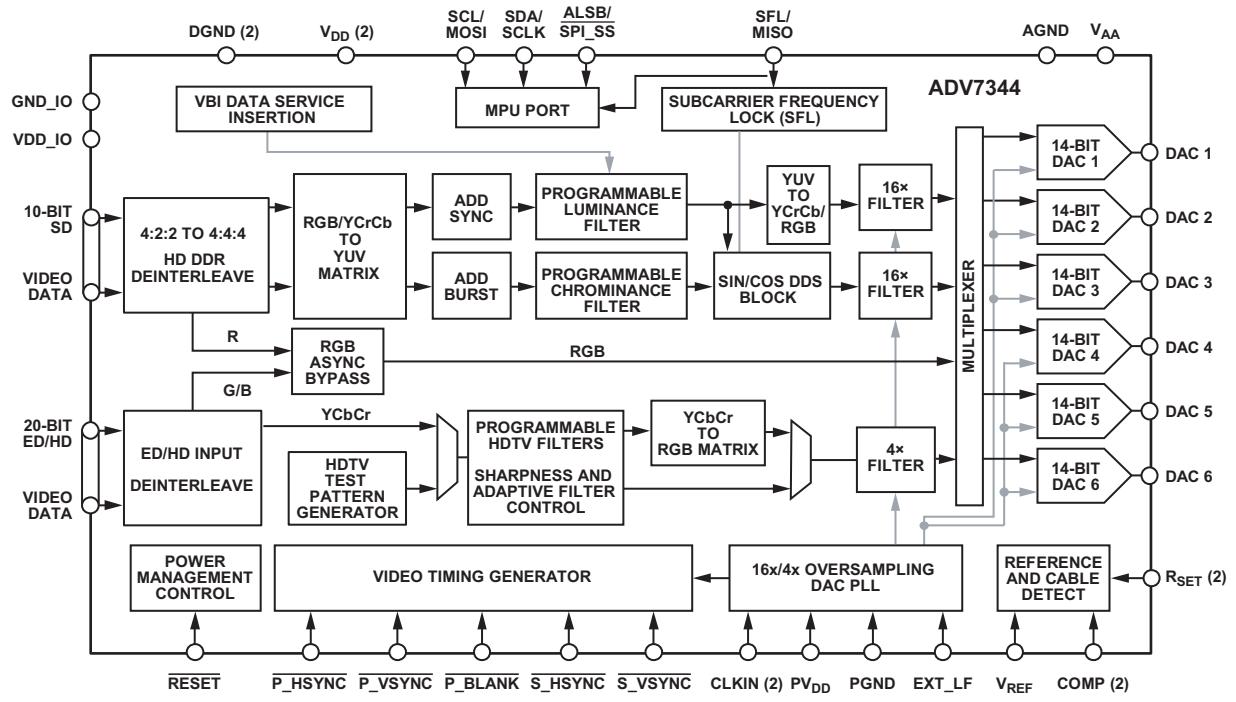

## 機能ブロック図

図1

06409-001

米国特許番号5,343,196と5,442,355、およびその他の知的財産権により保護されています。

米国特許番号4,631,603、4,577,216、4,819,098、およびその他の知的財産権により保護されています。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。

※日本語データシートはREVISIONが古い場合があります。最新の内容については、英語版をご参照ください。

© 2006 Analog Devices, Inc. All rights reserved.

REV. 0

## 目次

|                            |    |                              |    |

|----------------------------|----|------------------------------|----|

| 特長                         | 1  | 色空間変換マトリックス                  | 53 |

| アプリケーション                   | 1  | SDルミナンスとカラー制御                | 54 |

| 機能ブロック図                    | 1  | SD色相調整コントロール                 | 55 |

| 改訂履歴                       | 3  | SDライトネス検出                    | 55 |

| 詳細機能                       | 4  | SDライトネス・コントロール               | 55 |

| 概要                         | 4  | SD入力規格の自動検出                  | 55 |

| 仕様                         | 5  | ダブル・バッファリング                  | 56 |

| 電源仕様と電圧仕様                  | 5  | プログラマブルなDACゲイン制御             | 56 |

| リファレンス電圧仕様                 | 5  | ガンマ補正                        | 56 |

| 入力クロック仕様                   | 5  | ED/HDシャープネス・フィルタとアダプティブ      | 58 |

| アナログ出力仕様                   | 6  | フィルタの制御                      | 58 |

| デジタル入出力仕様                  | 6  | ED/HDシャープネス・フィルタとアダプティブ      | 59 |

| デジタル・タイミング仕様               | 7  | フィルタのアプリケーション例               | 59 |

| MPUポート・タイミング仕様             | 8  | SDデジタル・ノイズ・リダクション            | 60 |

| 電力仕様                       | 8  | SDアクティブ・ビデオ・エッジ制御            | 62 |

| ビデオ性能仕様                    | 9  | 水平／垂直外部同期制御                  | 63 |

| タイミング図                     | 10 | 低消費電力モード                     | 64 |

| 絶対最大定格                     | 17 | ケーブル検出                       | 64 |

| 熱抵抗                        | 17 | DACの自動パワーダウン                 | 64 |

| ESDに関する注意                  | 17 | ピクセルとコントロール・ポートのリードバック       | 64 |

| ピン配置と機能の説明                 | 18 | リセットのメカニズム                   | 64 |

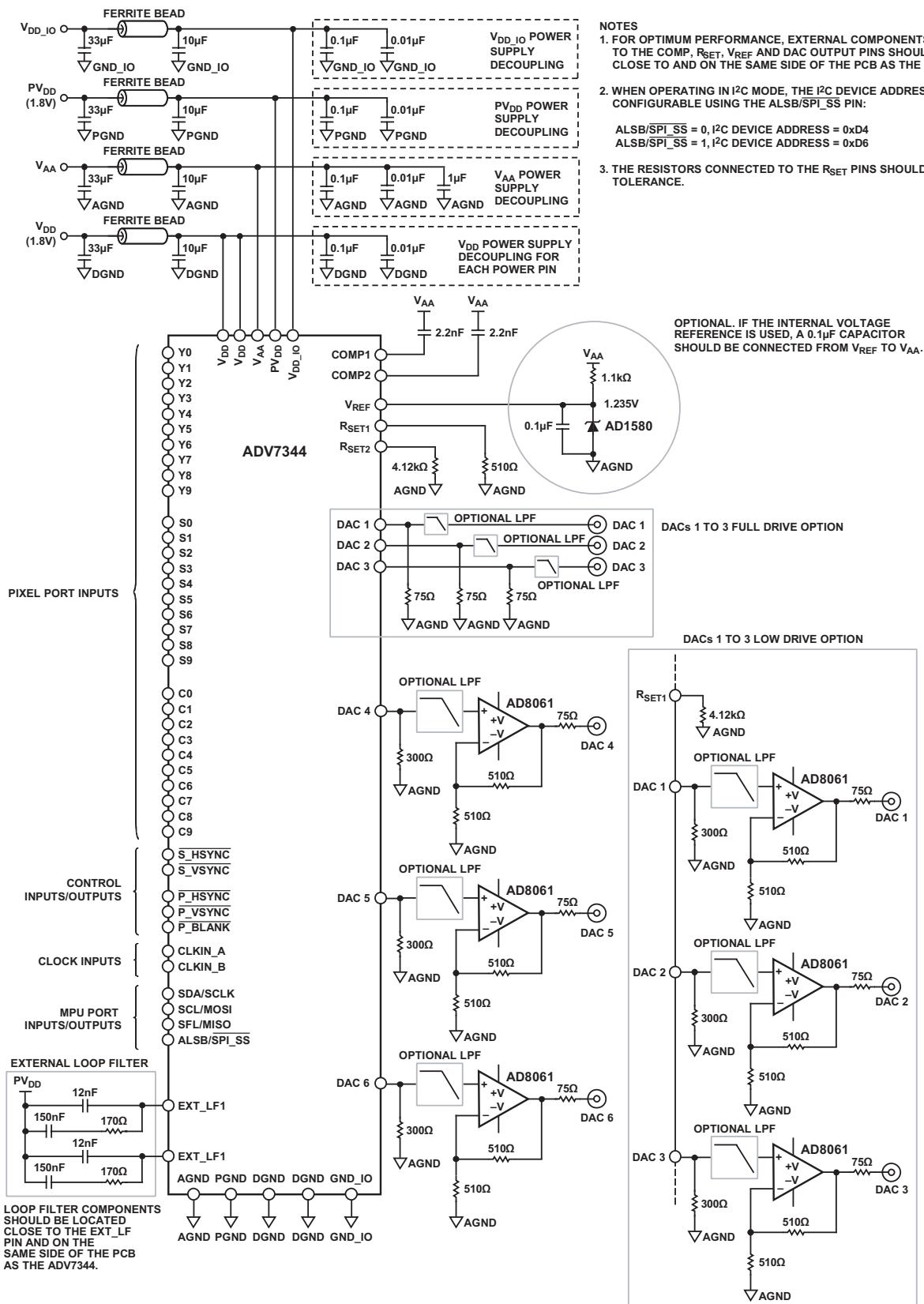

| 代表的な性能特性                   | 20 | プリント回路ボードのレイアウトと設計           | 65 |

| MPUポート説明                   | 25 | DACの設定                       | 65 |

| I <sup>2</sup> C動作         | 25 | リファレンス電圧                     | 65 |

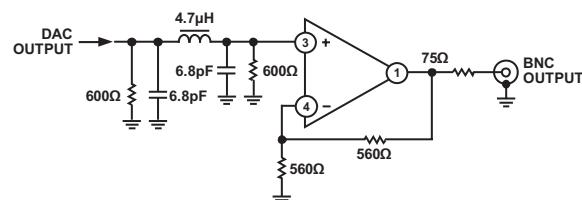

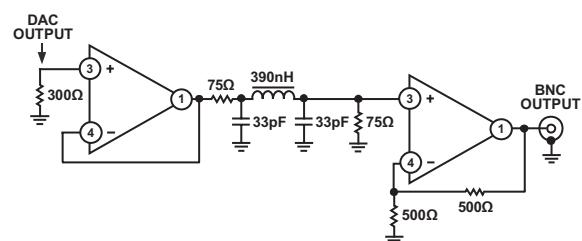

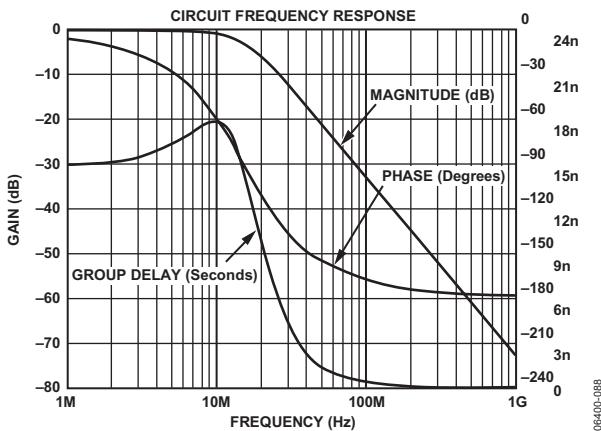

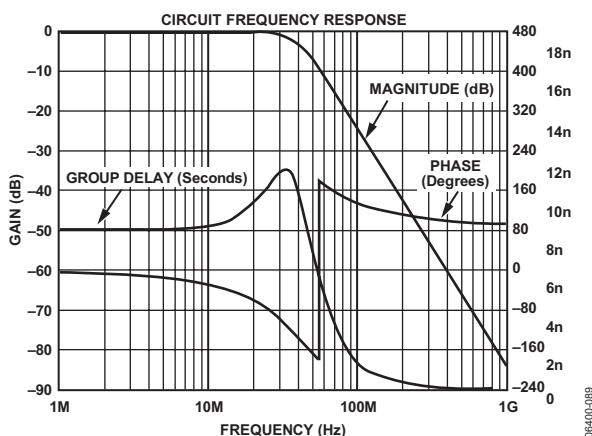

| SPI動作                      | 26 | ビデオ出力バッファとオプションの出力フィルタ       | 65 |

| レジスタ・マップのアクセス              | 27 | プリント回路ボード（PCB）のレイアウト         | 66 |

| レジスタのプログラミング               | 27 | 代表的なアプリケーション回路               | 68 |

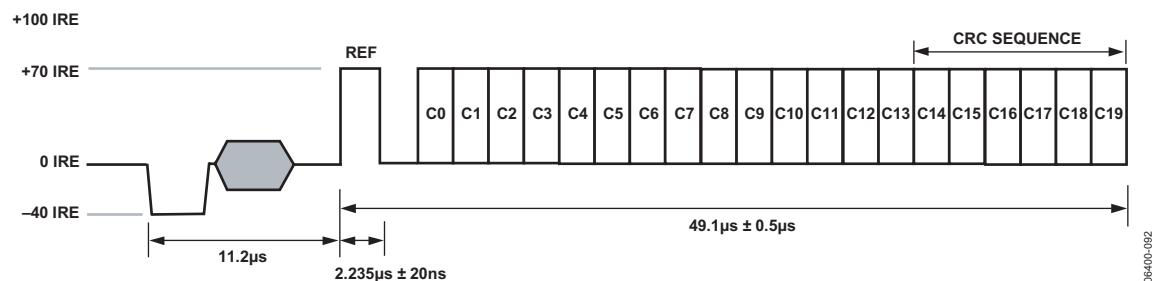

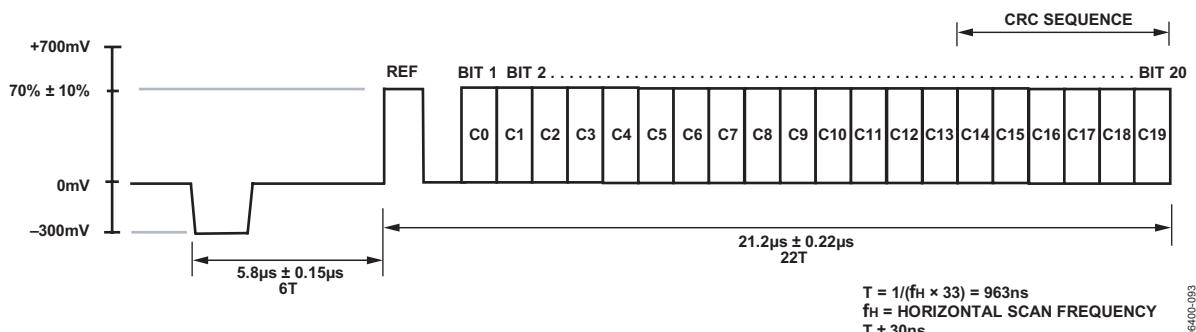

| サブアドレス・レジスタ（SR7～SR0）       | 27 | 付録1—コピー・ジェネレーション・マネジメント・システム | 69 |

| 入力設定                       | 44 | SD CGMS                      | 69 |

| 標準解像度専用                    | 44 | ED CGMS                      | 69 |

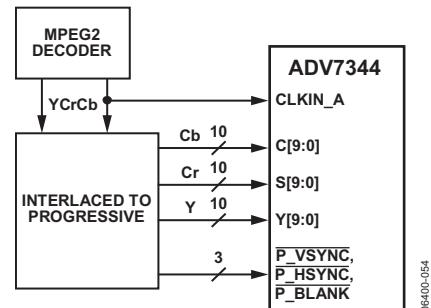

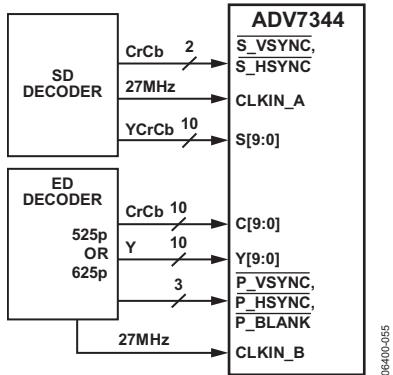

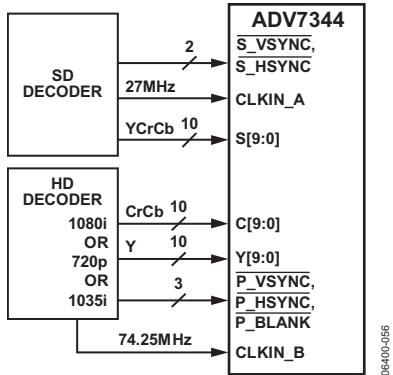

| 拡張解像度／高解像度専用               | 45 | HD CGMS                      | 69 |

| 標準解像度と拡張解像度／高解像度の同時処理      | 45 | CGMS CRC機能                   | 69 |

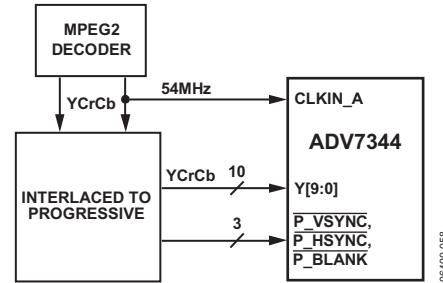

| 拡張解像度専用（54MHz）             | 46 | 付録2—SDワイド・スクリーン・シグナリング       | 72 |

| 出力設定                       | 47 | 付録3—SDクローズド・キャプショニング         | 73 |

| 特長                         | 48 | 付録4—内部テスト・パターン生成             | 74 |

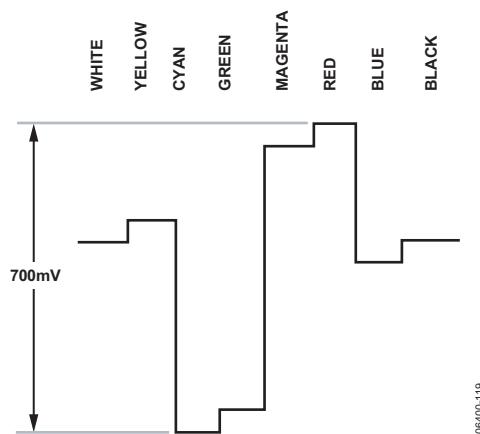

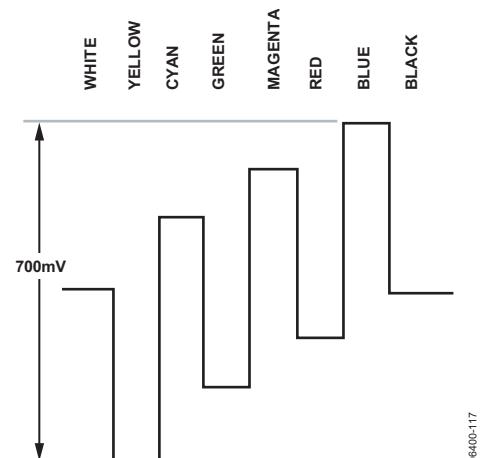

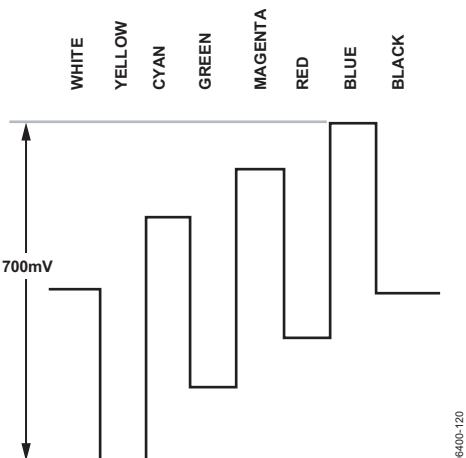

| 出力オーバーサンプリング               | 48 | SDテスト・パターン                   | 74 |

| ED/HD非標準タイミング・モード          | 48 | ED/HDテスト・パターン                | 74 |

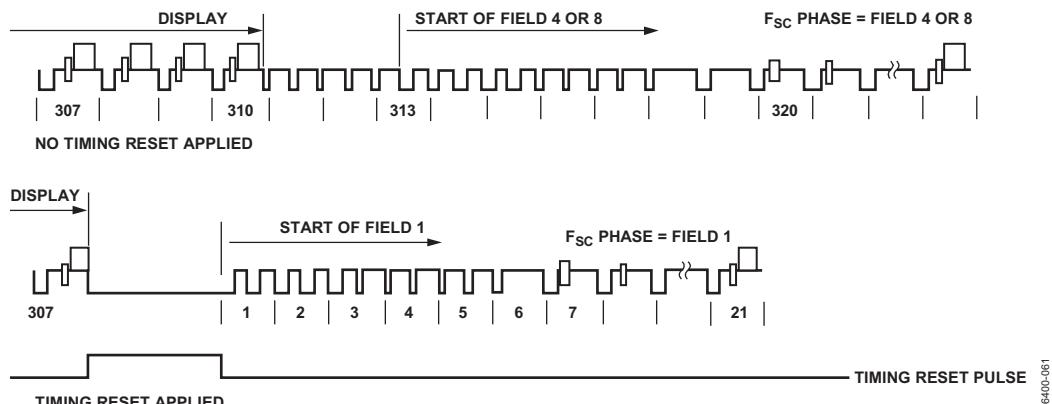

| ED/HDタイミング・リセット            | 49 | 付録5—SDタイミング                  | 75 |

| SDサブキャリア周波数ロック、サブキャリア・フェーズ | 49 | 付録6—HDタイミング                  | 80 |

| リセット、タイミング・リセット            | 49 | 付録7—ビデオ出力レベル                 | 81 |

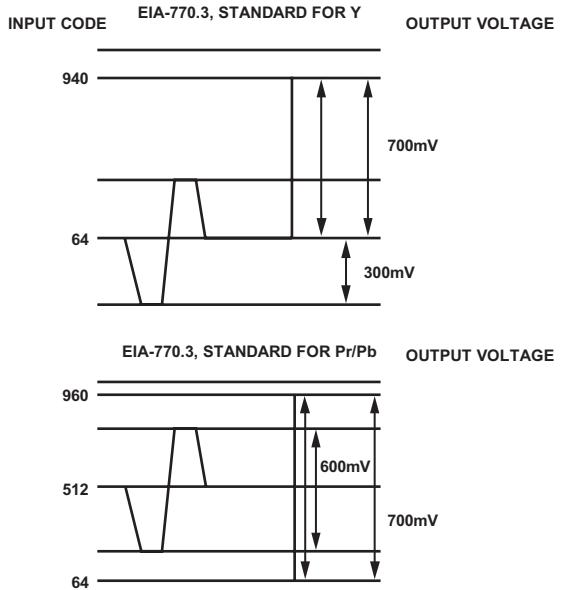

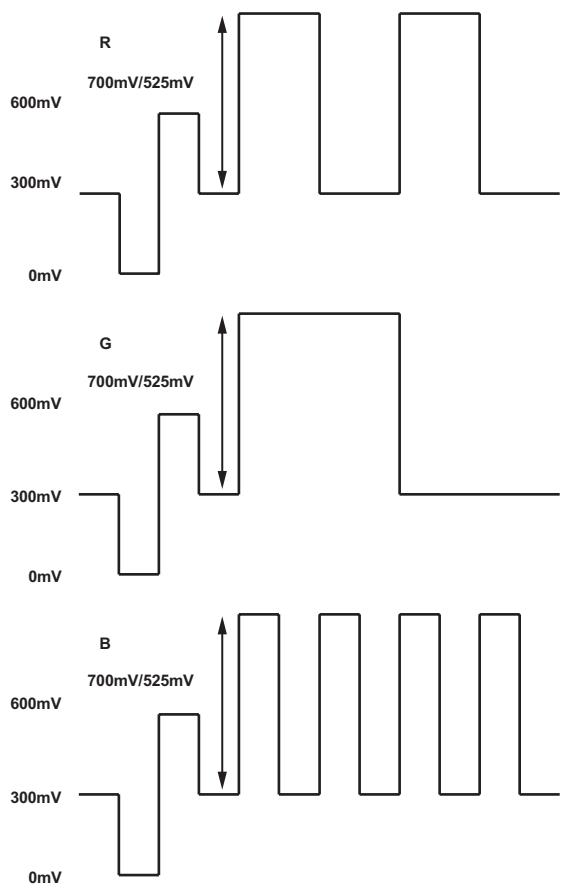

| SD VCR FF/RW同期             | 50 | SD YPrPb出力レベル—SMPTE/EBU N10  | 81 |

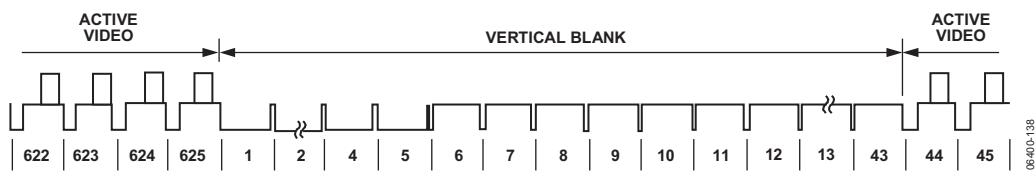

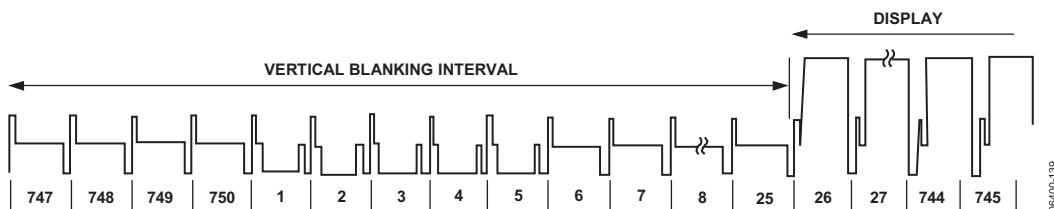

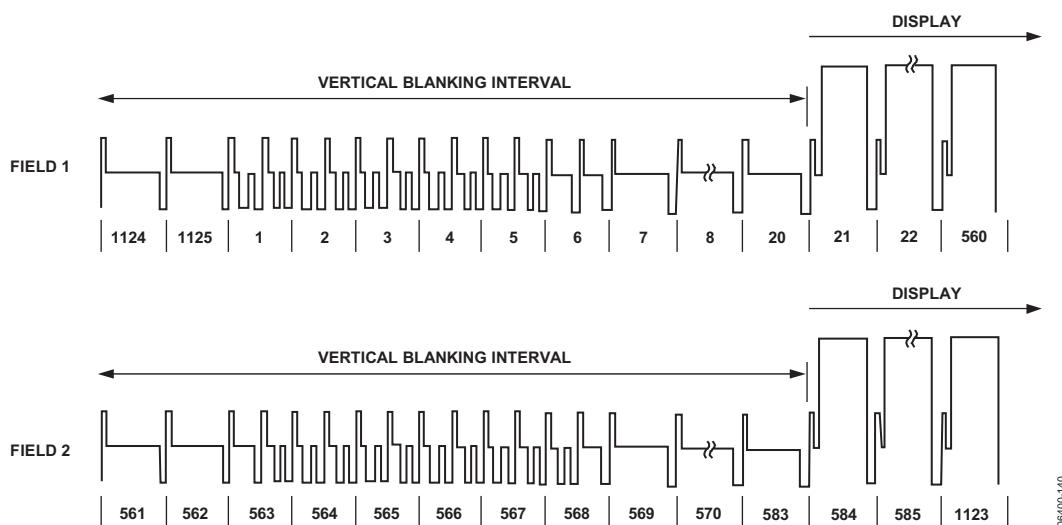

| 垂直ブランкиング期間                | 50 | ED/HD YPrPb出力レベル             | 82 |

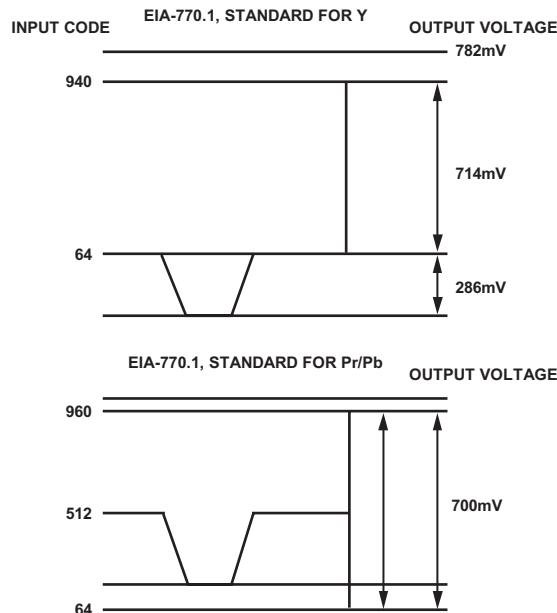

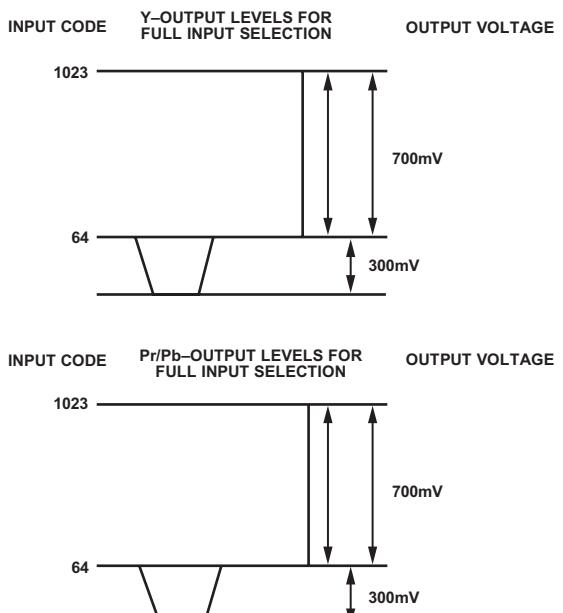

| SDサブキャリア周波数レジスタ            | 50 | SD/ED/HD RGB出力レベル            | 83 |

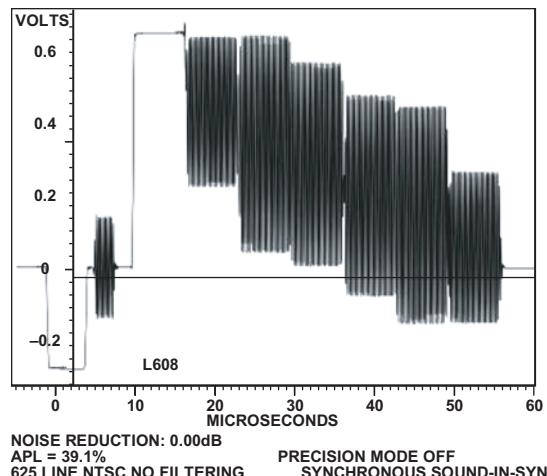

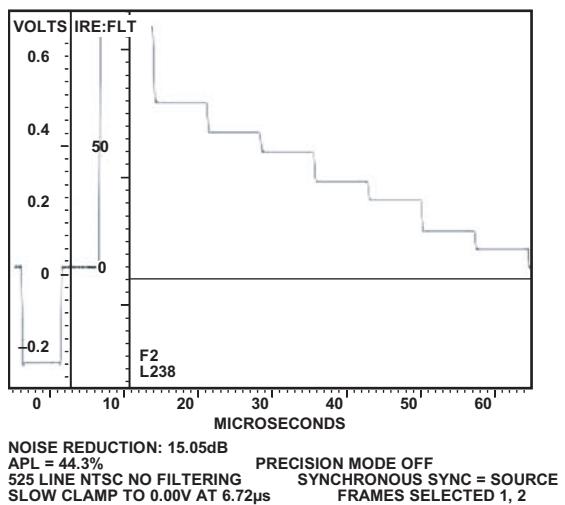

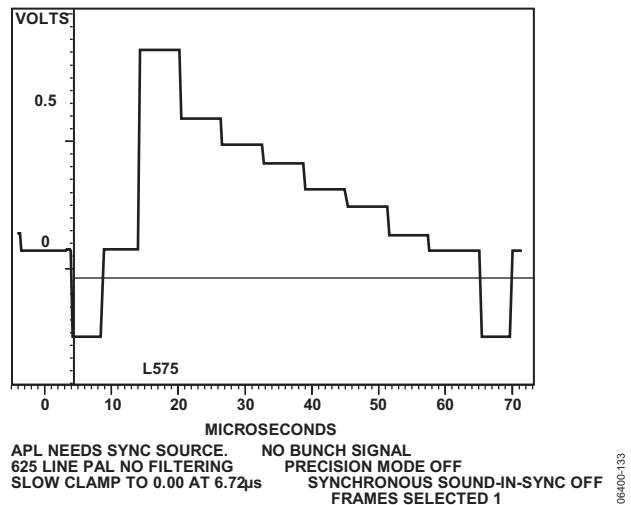

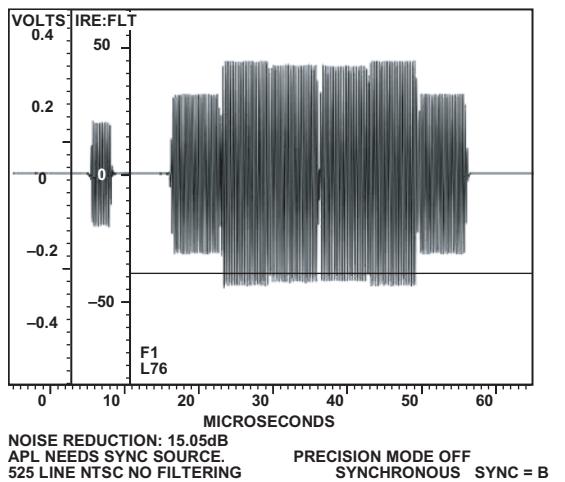

| SDノンインターレース・モード            | 51 | SD出力プロット                     | 84 |

| SDスクエア・ピクセル・モード            | 51 | 付録8—ビデオ規格                    | 85 |

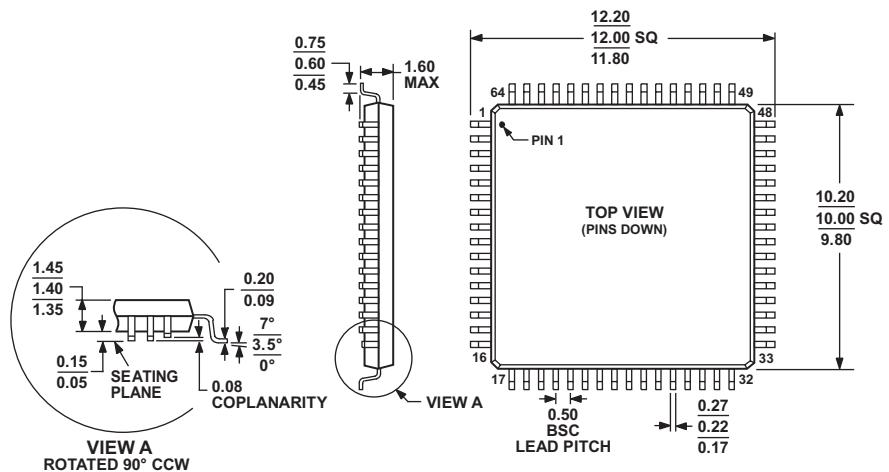

| フィルタ                       | 52 | 外形寸法                         | 87 |

| ED/HDテスト・パターンのカラー制御        | 53 | オーダー・ガイド                     | 87 |

目次（続き）

**改訂履歴**

10/06—Revision 0: Initial Version

# ADV7344

## 詳細機能

高解像度 (HD) プログラマブル機能

(720p/1080i/1035i)

4倍のオーバーサンプリング (297MHz)

内部テスト・パターン・ジェネレータ

カラーおよびブラック・バー、ハッチ、平坦フィールド／フレーム

完全にプログラマブルなYCrCb/RGBマトリックス

ガンマ補正

プログラマブルなアダプティブ・フィルタ制御

プログラマブルなシャープネス・フィルタ制御

CGMS (720p/1080i) およびCGMS Type B (720p/1080i)

デュアル・データレート (DDR) 入力

EIA/CEA-861Bコンプライアンス

拡張解像度 (ED) プログラマブル機能

(525p/625p)

8倍のオーバーサンプリング (216MHz出力)

内部テスト・パターン・ジェネレータ

カラーおよびブラック・バー、ハッチ、平坦フィールド／フレーム

YとPrPb個々の出力遅延

ガンマ補正

プログラマブルなアダプティブ・フィルタ制御

完全にプログラマブルなYCrCb/RGBマトリックス

アンダーシュート・リミッタ

Macrovision Rev 1.2 (525p/625p)

CGMS (525p/625p) およびCGMS Type B (525p)

デュアル・データレート (DDR) 入力

EIA/CEA-861Bコンプライアンス

標準解像度 (SD) プログラマブル機能

16倍のオーバーサンプリング (216MHz)

内部テスト・パターン・ジェネレータ

カラーおよびブラック・バー

Start/End of Active Video用にエッジ・レートを制御

YとPrPb個々の出力遅延

アンダーシュート・リミッタ

ガンマ補正

デジタル・ノイズ・リダクション (DNR)

複数のクロミナンス／ルミナンス・フィルタ

ゲイン／減衰量がプログラマブルなLuma-SSAF™フィルタ

PrPb SSAF™

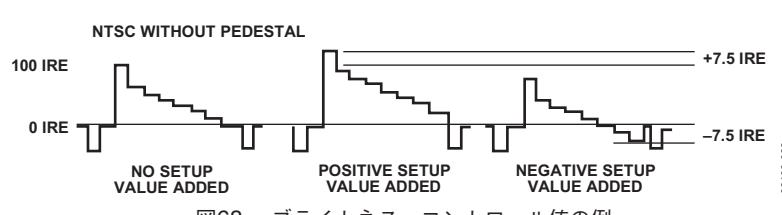

コンポーネントおよびコンポジット／Sビデオ出力での独立したペデスタイル制御

VCR FF/RW同期モード

Macrovision Rev 7.1.L1

コピー・ジェネレーション・マネジメント・システム (CGMS)

ワイド・スクリーン・シグナリング

クローズド・キャプショニング

EIA/CEA-861Bコンプライアンス

## 概要

ADV7344は、64ビンLQFPパッケージを採用した高速D/Aビデオ・エンコーダです。6個の高速、NSV、3.3Vの14ビット・ビデオDACが、標準解像度 (SD)、拡張解像度 (ED)、または高解像度 (HD) のビデオ・フォーマットで、コンポジット (CVBS)、Sビデオ (YC)、およびコンポーネント (YPrPb/RGB) のアナログ出力をサポートします。

ADV7344は、さまざまな方法で設定できる30ビットのピクセル入力ポートを内蔵しています。SDビデオ・フォーマットは、SDRインターフェースを使用してサポートします。ED/HDビデオ・フォーマットは、SDRインターフェースとDDRインターフェースを使用してサポートします。ピクセル・データは、YCrCbまたはRGBの色空間で出力することができます。

ADV7344は、組込みEAV/SAVタイミング・コード、外部ビデオ同期信号、I<sub>C</sub>CとSPIの通信プロトコルもサポートします。

さらに、SDとED/HDの同時入出力もサポートします。216MHz (SDとED) と297MHz (HD) のオーバーサンプリングにより、外部出力フィルタリングは不要です。そしてフルドライブDACにより、外部出力バッファリングは不要です。

ケーブル検出機能とDAC自動パワーダウン機能により、消費電力を最小限に抑えます。

表1に、ADV7344で直接サポートするビデオ規格を示します。

表1. ADV7344で直接サポートする規格<sup>1</sup>

| Resolution  | I/P <sup>2</sup> | Frame Rate (Hz)     | Clock Input (MHz) | Standard          |

|-------------|------------------|---------------------|-------------------|-------------------|

| 720 × 240   | P                | 59.94               | 27                |                   |

| 720 × 288   | P                | 50                  | 27                |                   |

| 720 × 480   | I                | 29.97               | 27                | ITU-R BT.601/656  |

| 720 × 576   | I                | 25                  | 27                | ITU-R BT.601/656  |

| 720 × 480   | I                | 29.97               | 24.54             | NTSC Square Pixel |

| 720 × 576   | I                | 25                  | 29.5              | PAL Square Pixel  |

| 720 × 483   | P                | 59.94               | 27                | SMPTE 293M        |

| 720 × 483   | P                | 59.94               | 27                | BTA T-1004        |

| 720 × 483   | P                | 59.94               | 27                | ITU-R BT.1358     |

| 720 × 576   | P                | 50                  | 27                | ITU-R BT.1358     |

| 720 × 483   | P                | 59.94               | 27                | ITU-R BT.1362     |

| 720 × 576   | P                | 50                  | 27                | ITU-R BT.1362     |

| 1920 × 1035 | I                | 30                  | 74.25             | SMPTE 240M        |

| 1920 × 1035 | I                | 29.97               | 74.1758           | SMPTE 240M        |

| 1280 × 720  | P                | 60, 50, 30, 25, 24  | 74.25             | SMPTE 296M        |

| 1280 × 720  | P                | 23.97, 59.94, 29.97 | 74.1758           | SMPTE 296M        |

| 1920 × 1080 | I                | 30, 25              | 74.25             | SMPTE 274M        |

| 1920 × 1080 | I                | 29.97               | 74.1758           | SMPTE 274M        |

| 1920 × 1080 | P                | 30, 25, 24          | 74.25             | SMPTE 274M        |

| 1920 × 1080 | P                | 23.98, 29.97        | 74.1758           | SMPTE 274M        |

| 1920 × 1080 | P                | 24                  | 74.25             | ITU-R BT.709-5    |

<sup>1</sup> 他の規格は、ED/HDの非標準タイミング・モードでサポートします。

<sup>2</sup> I=インターレース、P=プログレッシブ。

## 仕様

### 電源と電圧の仕様

特に指定のない限り、すべての仕様は $T_{MIN} \sim T_{MAX}$  ( $-40 \sim +85^\circ\text{C}$ ) で規定。

表2

| Parameter                    | Conditions | Min   | Typ | Max   | Unit |

|------------------------------|------------|-------|-----|-------|------|

| SUPPLY VOLTAGES              |            |       |     |       |      |

| $V_{DD}$                     |            | 1.71  | 1.8 | 1.89  | V    |

| $V_{DD\_IO}$                 |            | 2.97  | 3.3 | 3.63  | V    |

| $PV_{DD}$                    |            | 1.71  | 1.8 | 1.89  | V    |

| $V_{AA}$                     |            | 2.6   | 3.3 | 3.465 | V    |

| POWER SUPPLY REJECTION RATIO |            | 0.002 |     |       | %/%  |

### リファレンス電圧仕様

特に指定のない限り、すべての仕様は $T_{MIN} \sim T_{MAX}$  ( $-40 \sim +85^\circ\text{C}$ ) で規定。

表3

| Parameter                               | Conditions | Min   | Typ      | Max  | Unit          |

|-----------------------------------------|------------|-------|----------|------|---------------|

| Internal Reference Range, $V_{REF}$     |            | 1.186 | 1.248    | 1.31 | V             |

| External Reference Range, $V_{REF}$     |            | 1.15  | 1.235    | 1.31 | V             |

| External $V_{REF}$ Current <sup>1</sup> |            |       | $\pm 10$ |      | $\mu\text{A}$ |

<sup>1</sup> 内部 $V_{REF}$ をオーバードライブするときは、外部電流が必要です。

### 入力クロック仕様

$V_{DD} = 1.71 \sim 1.89\text{V}$ 。  $PV_{DD} = 1.71 \sim 1.89\text{V}$ 。  $V_{AA} = 2.6 \sim 3.465\text{V}$ 。  $V_{DD\_IO} = 2.97 \sim 3.63\text{V}$ 。

特に指定のない限り、すべての仕様は $T_{MIN} \sim T_{MAX}$  ( $-40 \sim +85^\circ\text{C}$ ) で規定。

表4

| Parameter                             | Conditions <sup>1</sup> | Min | Typ   | Max | Unit                 |

|---------------------------------------|-------------------------|-----|-------|-----|----------------------|

| $f_{CLKIN\_A}$                        | SD/ED                   |     | 27    |     | MHz                  |

| $f_{CLKIN\_A}$                        | ED (at 54 MHz)          |     | 54    |     | MHz                  |

| $f_{CLKIN\_A}$                        | HD                      |     | 74.25 |     | MHz                  |

| $f_{CLKIN\_B}$                        | ED                      |     | 27    |     | MHz                  |

| $f_{CLKIN\_B}$                        | HD                      |     | 74.25 |     | MHz                  |

| CLKIN_A High Time, $t_9$              |                         | 40  |       |     | % of one clock cycle |

| CLKIN_A Low Time, $t_{10}$            |                         | 40  |       |     | % of one clock cycle |

| CLKIN_B High Time, $t_9$              |                         | 40  |       |     | % of one clock cycle |

| CLKIN_B Low Time, $t_{10}$            |                         | 40  |       |     | % of one clock cycle |

| CLKIN_A Peak-to-Peak Jitter Tolerance |                         |     | 2     |     | $\pm\text{ns}$       |

| CLKIN_B Peak-to-Peak Jitter Tolerance |                         |     | 2     |     | $\pm\text{ns}$       |

<sup>1</sup> SD=標準解像度、ED=拡張解像度 (525p/625p)、HD=高解像度。

# ADV7344

## アナログ出力仕様

$V_{DD} = 1.71 \sim 1.89V$ 。  $PV_{DD} = 1.71 \sim 1.89V$ 。  $V_{AA} = 2.6 \sim 3.465V$ 。  $V_{DD\_IO} = 2.97 \sim 3.63V$ 。  $V_{REF} = 1.235V$  (外部から駆動)。

特に指定のない限り、すべての仕様は  $T_{MIN} \sim T_{MAX}$  ( $-40 \sim +85^\circ C$ ) で規定。

表5

| Parameter                                           | Conditions                                    | Min | Typ  | Max | Unit |

|-----------------------------------------------------|-----------------------------------------------|-----|------|-----|------|

| Full-Drive Output Current (Full-Scale) <sup>1</sup> | $R_{SET} = 510 \Omega$ , $R_L = 37.5 \Omega$  | 33  | 34.6 | 37  | mA   |

| Low Drive Output Current (Full-Scale) <sup>2</sup>  | $R_{SET} = 4.12 k\Omega$ , $R_L = 300 \Omega$ | 4.1 | 4.3  | 4.5 | mA   |

| DAC-to-DAC Matching                                 | DAC 1 to DAC 6                                |     | 1.0  |     | %    |

| Output Compliance, $V_{OC}$                         |                                               | 0   |      | 1.4 | V    |

| Output Capacitance, $C_{OUT}$                       | DAC 1, DAC 2, DAC 3                           |     | 10   |     | pF   |

|                                                     | DAC 4, DAC 5, DAC 6                           |     | 6    |     | pF   |

| Analog Output Delay <sup>3</sup>                    | DAC 1, DAC 2, DAC 3                           |     | 8    |     | ns   |

|                                                     | DAC 4, DAC 5, DAC 6                           |     | 6    |     | ns   |

| DAC Analog Output Skew                              | DAC 1, DAC 2, DAC 3                           |     | 2    |     | ns   |

|                                                     | DAC 4, DAC 5, DAC 6                           |     | 1    |     | ns   |

<sup>1</sup> フルドライブ対応のDAC (DAC 1, DAC 2, DAC 3) にのみ適用可能。

<sup>2</sup> すべてのDACに適用可能。

<sup>3</sup> 入力クロックの立上がりエッジの50%ポイントからDAC出力フルスケール変化の50%ポイントまで測定した出力遅延。

## デジタル入出力仕様

$V_{DD} = 1.71 \sim 1.89V$ 。  $PV_{DD} = 1.71 \sim 1.89V$ 。  $V_{AA} = 2.6 \sim 3.465V$ 。  $V_{DD\_IO} = 2.97 \sim 3.63V$ 。

特に指定のない限り、すべての仕様は  $T_{MIN} \sim T_{MAX}$  ( $-40 \sim +85^\circ C$ ) で規定。

表6

| Parameter                       | Conditions               | Min | Typ | Max       | Unit    |

|---------------------------------|--------------------------|-----|-----|-----------|---------|

| Input High Voltage, $V_{IH}$    |                          | 2.0 |     |           | V       |

| Input Low Voltage, $V_{IL}$     |                          |     | 0.8 |           | V       |

| Input Leakage Current, $I_{IN}$ | $V_{IN} = V_{DD\_IO}$    |     |     | $\pm 10$  | $\mu A$ |

| Input Capacitance, $C_{IN}$     |                          | 4   |     |           | pF      |

| Output High Voltage, $V_{OH}$   | $I_{SOURCE} = 400 \mu A$ | 2.4 |     |           | V       |

| Output Low Voltage, $V_{OL}$    | $I_{SINK} = 3.2 mA$      |     | 0.4 |           | V       |

| Three-State Leakage Current     | $V_{IN} = 0.4 V, 2.4 V$  |     |     | $\pm 1.0$ | $\mu A$ |

| Three-State Output Capacitance  |                          | 4   |     |           | pF      |

## デジタル・タイミング仕様

$V_{DD}=1.71\sim1.89V$ 。  $PV_{DD}=1.71\sim1.89V$ 。  $V_{AA}=2.6\sim3.465V$ 。  $V_{DD\_IO}=2.97\sim3.63V$ 。

特に指定のない限り、すべての仕様は  $T_{MIN}\sim T_{MAX}$  ( $-40\sim+85^{\circ}C$ ) で規定。

表7

| Parameter                                        | Conditions <sup>1</sup>                | Min | Typ | Max | Unit         |

|--------------------------------------------------|----------------------------------------|-----|-----|-----|--------------|

| VIDEO DATA AND VIDEO CONTROL PORT <sup>2,3</sup> |                                        |     |     |     |              |

| Data Setup Time, $t_{11}^4$                      | SD                                     | 2.1 |     |     | ns           |

|                                                  | ED/HD-SDR                              | 2.3 |     |     | ns           |

|                                                  | ED/HD-DDR                              | 2.3 |     |     | ns           |

|                                                  | ED (at 54 MHz)                         | 1.7 |     |     | ns           |

| Data Hold Time, $t_{12}^4$                       | SD                                     | 1.0 |     |     | ns           |

|                                                  | ED/HD-SDR                              | 1.1 |     |     | ns           |

|                                                  | ED/HD-DDR                              | 1.1 |     |     | ns           |

|                                                  | ED (at 54 MHz)                         | 1.0 |     |     | ns           |

| Control Setup Time, $t_{11}^4$                   | SD                                     | 2.1 |     |     | ns           |

|                                                  | ED/HD-SDR or ED/HD-DDR                 | 2.3 |     |     | ns           |

|                                                  | ED (at 54 MHz)                         | 1.7 |     |     | ns           |

| Control Hold Time, $t_{12}^4$                    | SD                                     | 1.0 |     |     | ns           |

|                                                  | ED/HD-SDR or ED/HD-DDR                 | 1.1 |     |     | ns           |

|                                                  | ED (at 54 MHz)                         | 1.0 |     |     | ns           |

| Digital Output Access Time, $t_{13}^4$           | SD                                     |     | 12  |     | ns           |

|                                                  | ED/HD-SDR, ED/HD-DDR or ED (at 54 MHz) |     | 10  |     | ns           |

| Digital Output Hold Time, $t_{14}^4$             | SD                                     | 4.0 |     |     | ns           |

|                                                  | ED/HD-SDR, ED/HD-DDR or ED (at 54 MHz) | 3.5 |     |     | ns           |

| PIPELINE DELAY <sup>5</sup>                      |                                        |     |     |     |              |

| SD <sup>1</sup>                                  |                                        |     |     |     |              |

| CVBS/YC Outputs (2×)                             | SD oversampling disabled               | 68  |     |     | clock cycles |

| CVBS/YC Outputs (16×)                            | SD oversampling enabled                | 67  |     |     | clock cycles |

| Component Outputs (2×)                           | SD oversampling disabled               | 78  |     |     | clock cycles |

| Component Outputs (16×)                          | SD oversampling enabled                | 84  |     |     | clock cycles |

| ED <sup>1</sup>                                  |                                        |     |     |     |              |

| Component Outputs (1×)                           | ED oversampling disabled               | 41  |     |     | clock cycles |

| Component Outputs (8×)                           | ED oversampling enabled                | 46  |     |     | clock cycles |

| HD <sup>1</sup>                                  |                                        |     |     |     |              |

| Component Outputs (1×)                           | HD oversampling disabled               | 40  |     |     | clock cycles |

| Component Outputs (4×)                           | HD oversampling enabled                | 44  |     |     | clock cycles |

<sup>1</sup> SD=標準解像度、ED=拡張解像度 (525p/625p)、HD=高解像度、SDR=シングル・データレート、DDR=デュアル・データレート。

<sup>2</sup> ビデオ・データ: C[9:0]、Y[9:0]、S[9:0]。

<sup>3</sup> ビデオ制御: P\_HSYNC、P\_VSYNC、P\_BLANK、S\_HSYNC、S\_VSYNC。

<sup>4</sup> キャラクタライゼーションにより保証。

<sup>5</sup> 設計により保証。

# ADV7344

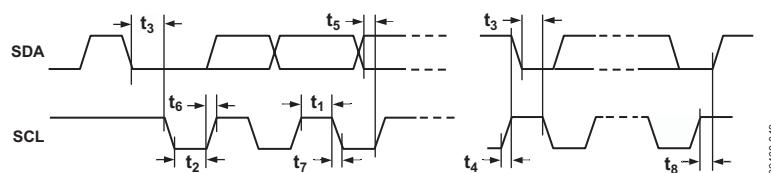

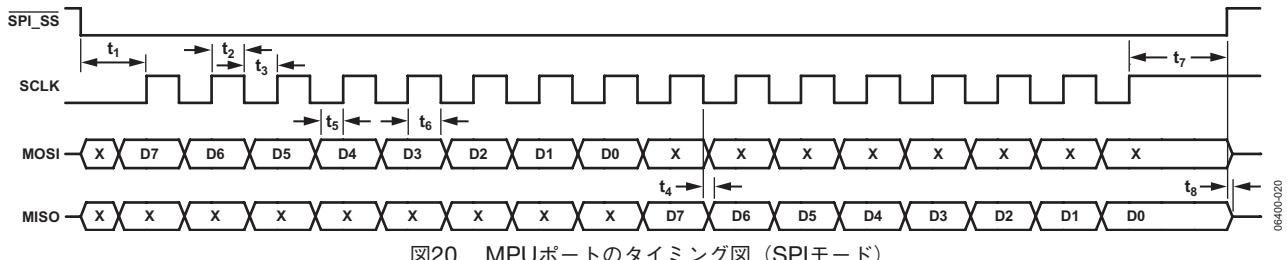

## MPUポート・タイミング仕様

$V_{DD}=1.71\sim1.89V$ 、 $PV_{DD}=1.71\sim1.89V$ 、 $V_{AA}=2.6\sim3.465V$ 、 $V_{DD\_IO}=2.97\sim3.63V$ 。

特に指定のない限り、すべての仕様は $T_{MIN}\sim T_{MAX}$  ( $-40\sim+85^{\circ}C$ ) で規定。

表8

| Parameter                                        | Conditions     | Min | Typ | Max | Unit |

|--------------------------------------------------|----------------|-----|-----|-----|------|

| MPU PORT, I <sup>2</sup> C MODE <sup>1</sup>     | See Figure 19. |     |     |     |      |

| SCL Frequency                                    |                | 0   |     | 400 | kHz  |

| SCL High Pulse Width, $t_1$                      |                | 0.6 |     |     | μs   |

| SCL Low Pulse Width, $t_2$                       |                | 1.3 |     |     | μs   |

| Hold Time (Start Condition), $t_3$               |                | 0.6 |     |     | μs   |

| Setup Time (Start Condition), $t_4$              |                | 0.6 |     |     | μs   |

| Data Setup Time, $t_5$                           |                | 100 |     |     | ns   |

| SDA, SCL Rise Time, $t_6$                        |                |     | 300 |     | ns   |

| SDA, SCL Fall Time, $t_7$                        |                |     | 300 |     | ns   |

| Setup Time (Stop Condition), $t_8$               |                | 0.6 |     |     | μs   |

| MPU PORT, SPI MODE <sup>1</sup>                  | See Figure 20. |     |     |     |      |

| SCLK Frequency                                   |                | 0   |     | 10  | MHz  |

| SPI_SS to SCLK Setup Time, $t_1$                 |                | 20  |     |     | ns   |

| SCLK High Pulse Width, $t_2$                     |                | 50  |     |     | ns   |

| SCLK Low Pulse Width, $t_3$                      |                | 50  |     |     | ns   |

| Data Access Time after SCLK Falling Edge, $t_4$  |                |     | 35  |     | ns   |

| Data Setup Time prior to SCLK Rising Edge, $t_5$ |                | 20  |     |     | ns   |

| Data Hold Time after SCLK Rising Edge, $t_6$     |                | 0   |     |     | ns   |

| SPI_SS to SCLK Hold Time, $t_7$                  |                | 0   |     |     | ns   |

| SPI_SS to MISO High Impedance, $t_8$             |                |     | 40  |     | ns   |

<sup>1</sup> キャラクタライゼーションにより保証。

## 電力仕様

表9

| Parameter                        | Conditions                                                     | Min | Typ | Max | Unit |

|----------------------------------|----------------------------------------------------------------|-----|-----|-----|------|

| NORMAL POWER MODE <sup>1,2</sup> |                                                                |     |     |     |      |

| $I_{DD}^3$                       | SD only (16 $\times$ oversampling)                             | 90  |     |     | mA   |

|                                  | ED only (8 $\times$ oversampling) <sup>4</sup>                 | 65  |     |     | mA   |

|                                  | HD only (4 $\times$ oversampling) <sup>4</sup>                 | 91  |     |     | mA   |

|                                  | SD (16 $\times$ oversampling) and ED (8 $\times$ oversampling) | 95  |     |     | mA   |

|                                  | SD (16 $\times$ oversampling) and HD (4 $\times$ oversampling) | 122 |     |     | mA   |

| $I_{DD\_IO}$                     |                                                                | 1   |     |     | mA   |

| $I_{AA}^5$                       | 3 DACs enabled (ED/HD only)                                    | 124 |     |     | mA   |

|                                  | 6 DACs enabled (SD only and simultaneous modes)                | 140 |     |     | mA   |

| $I_{PLL}$                        | SD only, ED only or HD only modes                              | 5   |     |     | mA   |

|                                  | Simultaneous modes                                             | 10  |     |     | mA   |

| SLEEP MODE                       |                                                                |     |     |     |      |

| $I_{DD}$                         |                                                                | 5   |     |     | μA   |

| $I_{AA}$                         |                                                                | 0.3 |     |     | μA   |

| $I_{DD\_IO}$                     |                                                                | 0.2 |     |     | μA   |

| $I_{PLL}$                        |                                                                | 0.1 |     |     | μA   |

<sup>1</sup>  $R_{SET1}=510\Omega$  (DAC 1、DAC 2、DAC 3はフルドライブ・モードで動作)。 $R_{SET2}=4.12k\Omega$  (DAC 4、DAC 5、DAC 6はロードドライブ・モードで動作)。

<sup>2</sup> ピクセル・データ・ピンに75%のカラー・バー・テスト・パターンを入力。

<sup>3</sup>  $I_{DD}$ は、デジタル・コアの駆動に必要な連続電流です。

<sup>4</sup> シングル・データレート (SDR) とデュアル・データレート (DDR) の両方の入力モードに適用できます。

<sup>5</sup>  $I_{AA}$ は、 $V_{REF}$ 回路を含むすべてのDACへの供給に必要な合計電流です。

## ビデオ性能仕様

表10

| Parameter                                  | Conditions                                             | Min   | Typ | Max | Unit    |

|--------------------------------------------|--------------------------------------------------------|-------|-----|-----|---------|

| STATIC PERFORMANCE                         |                                                        |       |     |     |         |

| Resolution                                 |                                                        | 14    |     |     | Bits    |

| Integral Nonlinearity                      | $R_{SET1} = 510 \text{ k}\Omega, R_{L1} = 37.5 \Omega$ | 3     |     |     | LSBs    |

|                                            | $R_{SET2} = 4.12 \text{ k}\Omega, R_{L2} = 300 \Omega$ | 4     |     |     | LSBs    |

| Differential Nonlinearity <sup>1</sup> +ve | $R_{SET1} = 510 \text{ k}\Omega, R_{L1} = 37.5 \Omega$ | 1     |     |     | LSBs    |

|                                            | $R_{SET2} = 4.12 \text{ k}\Omega, R_{L2} = 300 \Omega$ | 3.2   |     |     | LSBs    |

| Differential Nonlinearity <sup>1</sup> -ve | $R_{SET1} = 510 \text{ k}\Omega, R_{L1} = 37.5 \Omega$ | 1.7   |     |     | LSBs    |

|                                            | $R_{SET2} = 4.12 \text{ k}\Omega, R_{L2} = 300 \Omega$ | 1.4   |     |     | LSBs    |

| STANDARD DEFINITION (SD) MODE              |                                                        |       |     |     |         |

| Luminance Nonlinearity                     |                                                        | 0.2   |     |     | $\pm\%$ |

| Differential Gain                          | NTSC                                                   | 0.2   |     |     | %       |

| Differential Phase                         | NTSC                                                   | 0.3   |     |     | Degrees |

| SNR                                        | Luma ramp                                              | 64.5  |     |     | dB      |

| SNR                                        | Flat field full bandwidth                              | 79.5  |     |     | dB      |

| ENHANCED DEFINITION (ED) MODE              |                                                        |       |     |     |         |

| Luma Bandwidth                             |                                                        | 12.5  |     |     | MHz     |

| Chroma Bandwidth                           |                                                        | 5.8   |     |     | MHz     |

| HIGH DEFINITION (HD) MODE                  |                                                        |       |     |     |         |

| Luma Bandwidth                             |                                                        | 30    |     |     | MHz     |

| Chroma Bandwidth                           |                                                        | 13.75 |     |     | MHz     |

<sup>1</sup> 微分非直線性 (DNL) とは、実際のDAC出力電圧ステップと理想値との偏差です。+ve DNLの場合は、実際のステップ値は理想的なステップ値の上側にあります。-ve DNLの場合は、実際のステップ値は理想的なステップ値の下側にあります。

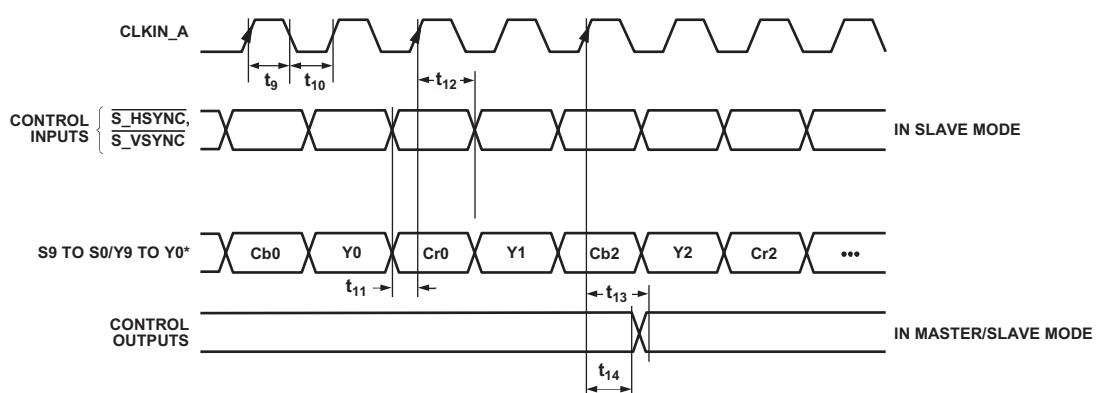

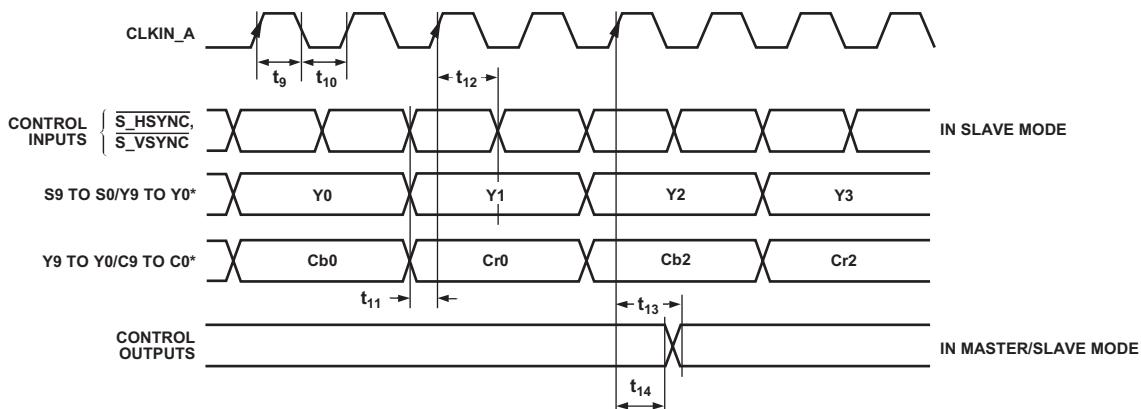

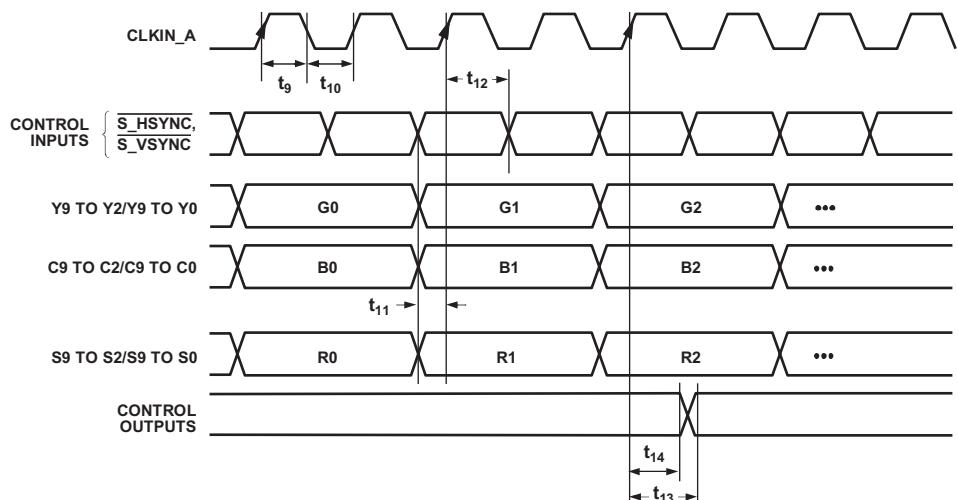

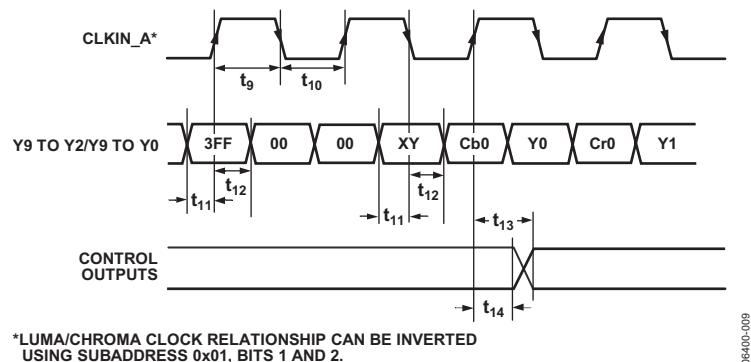

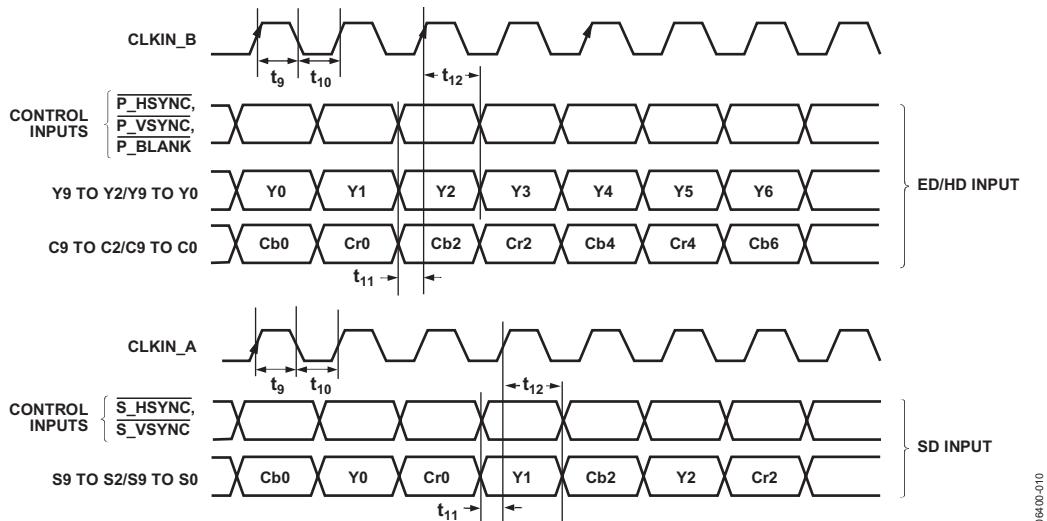

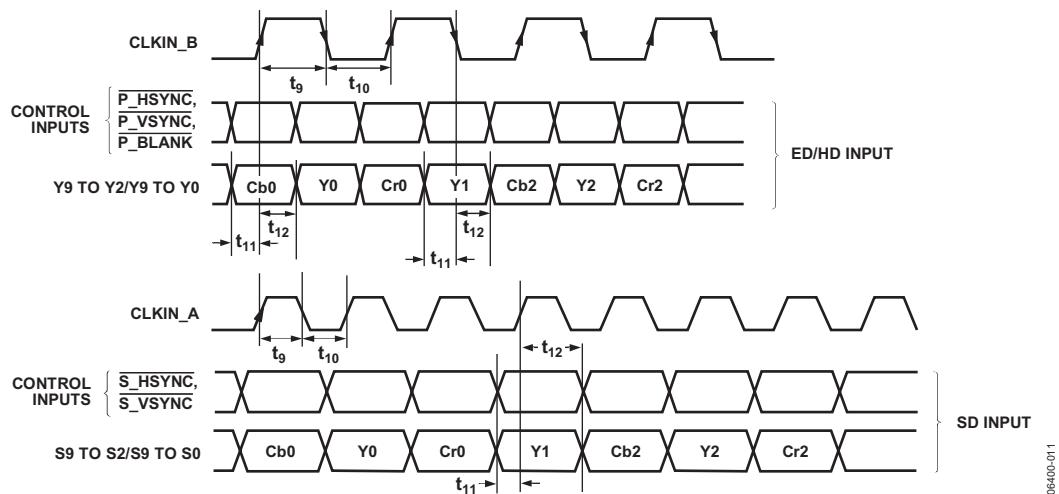

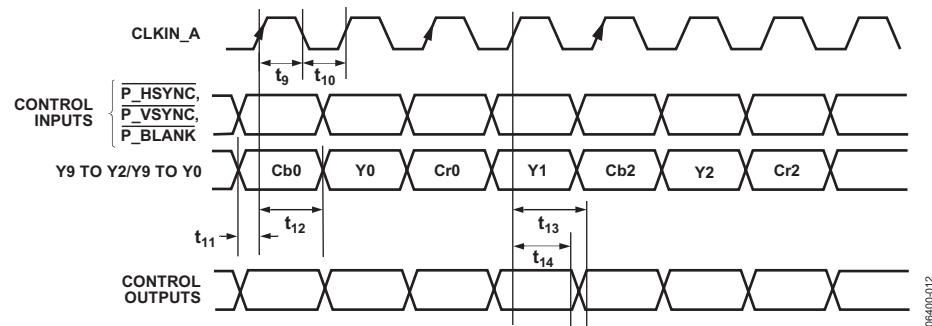

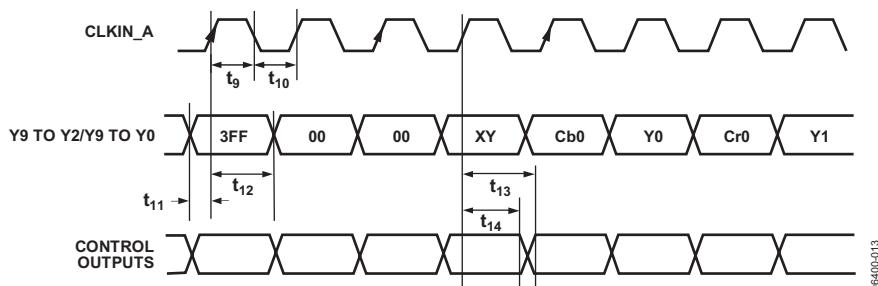

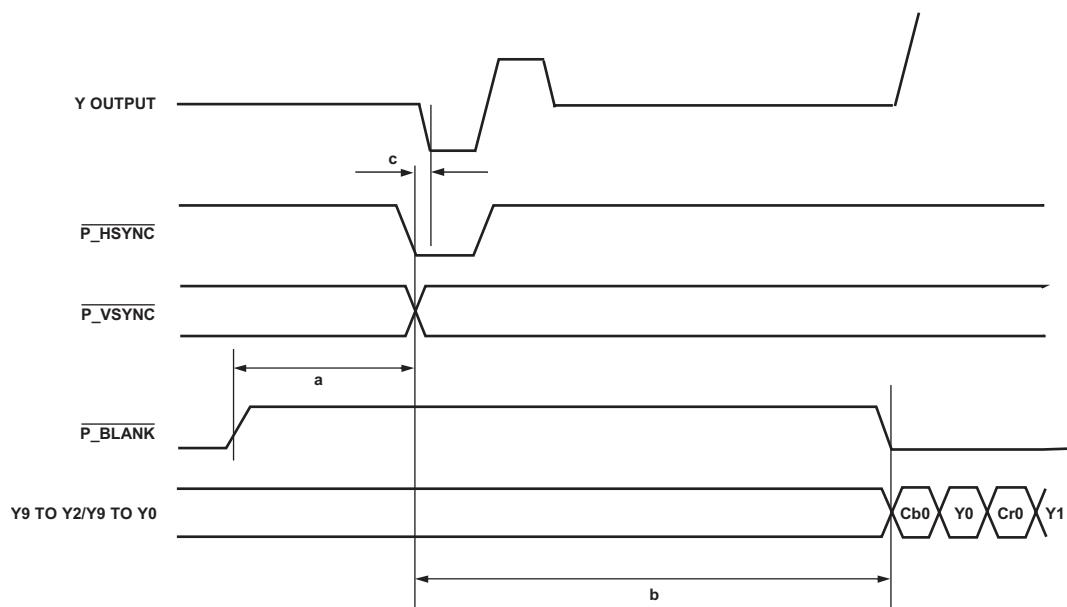

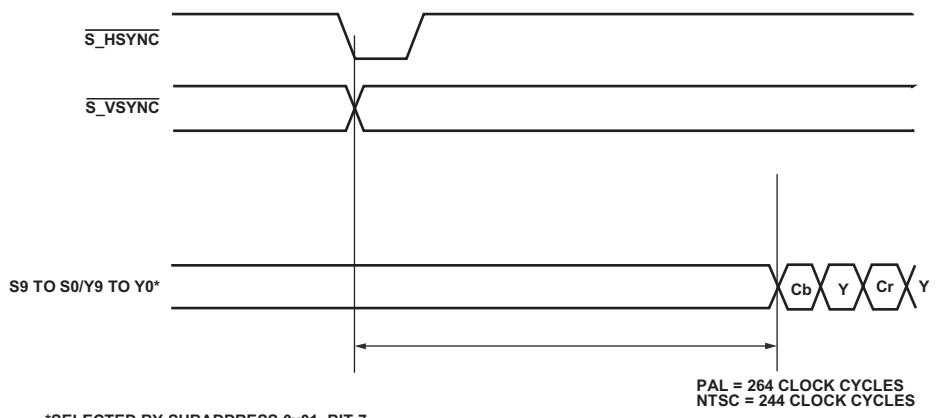

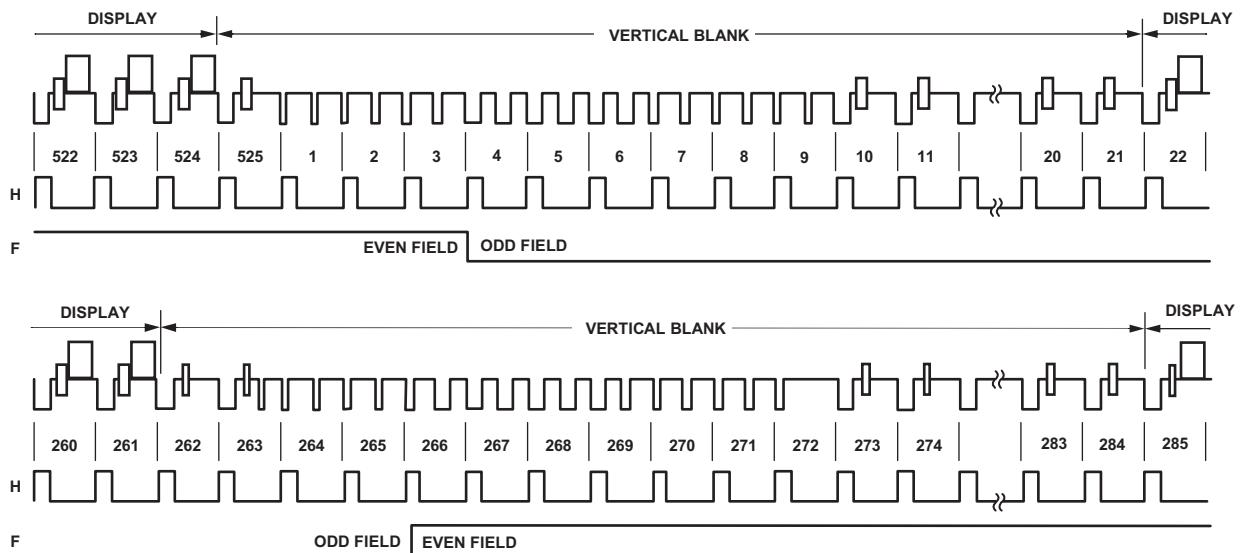

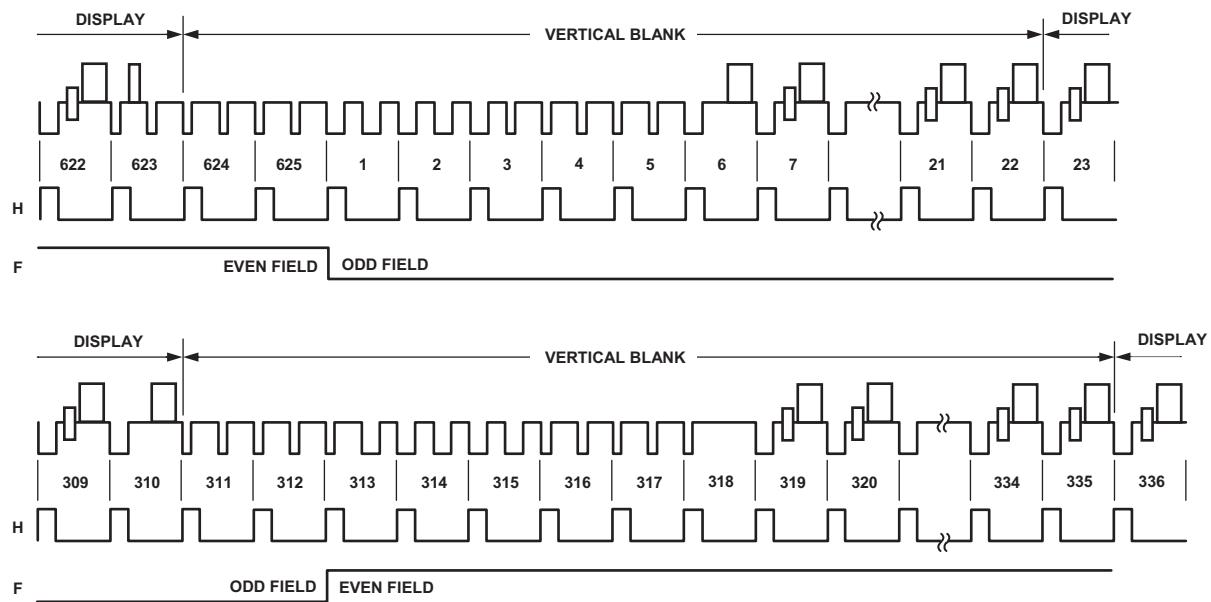

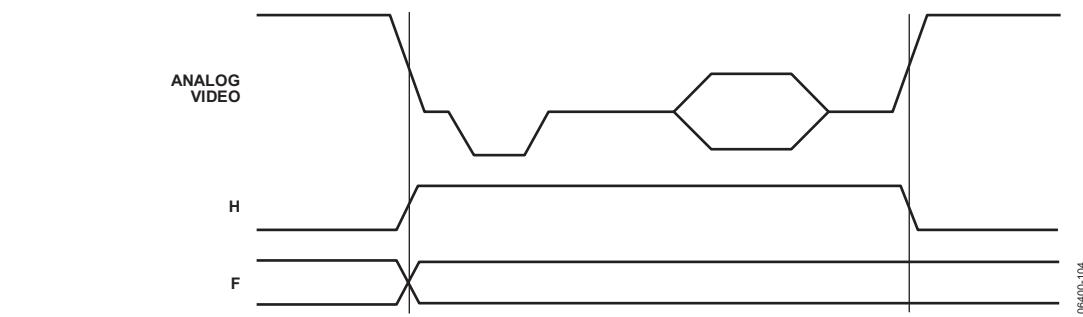

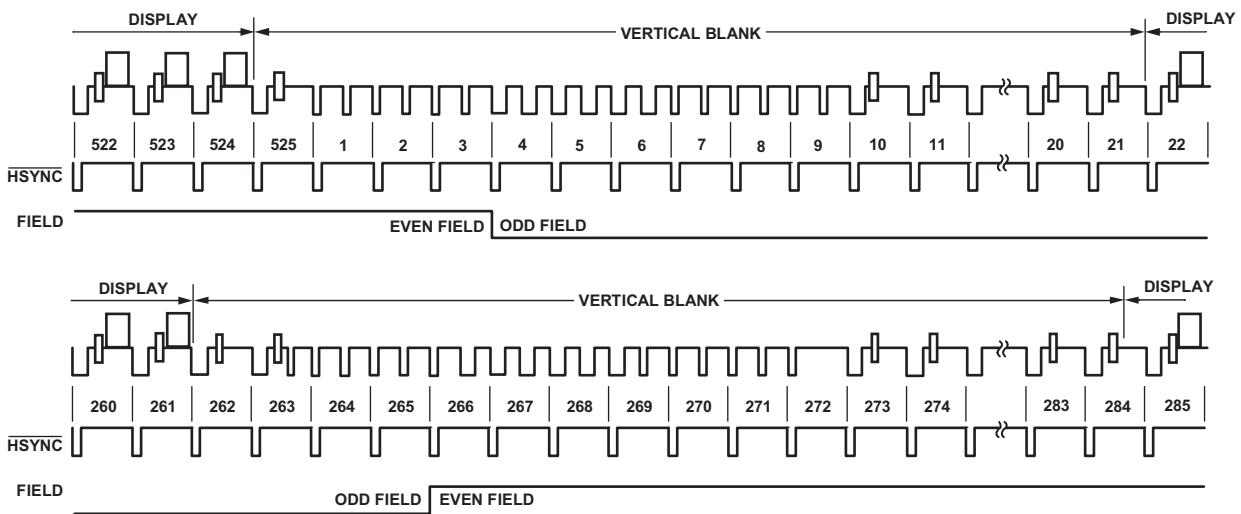

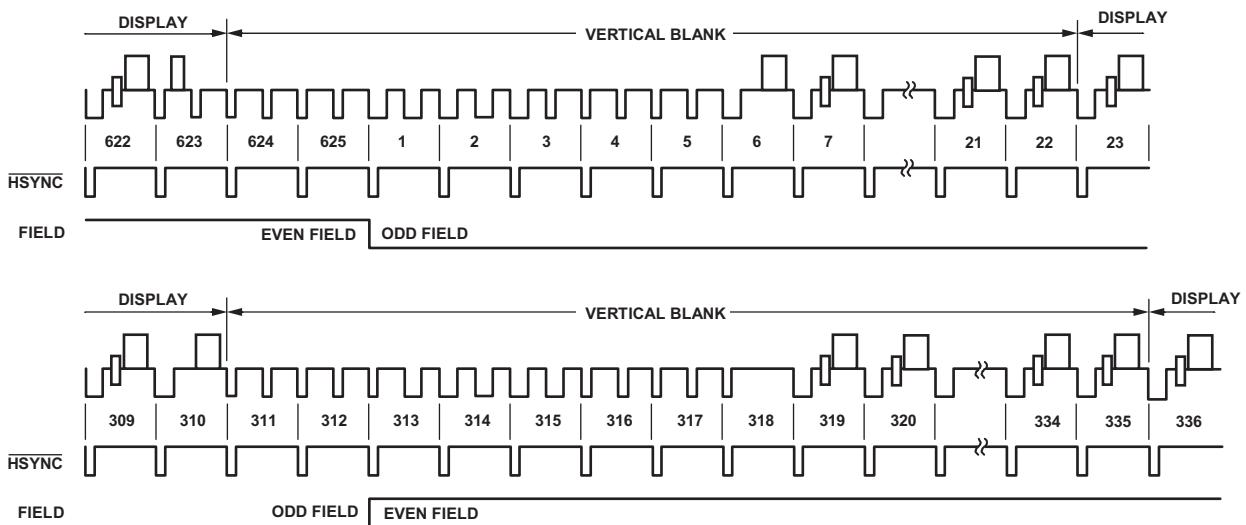

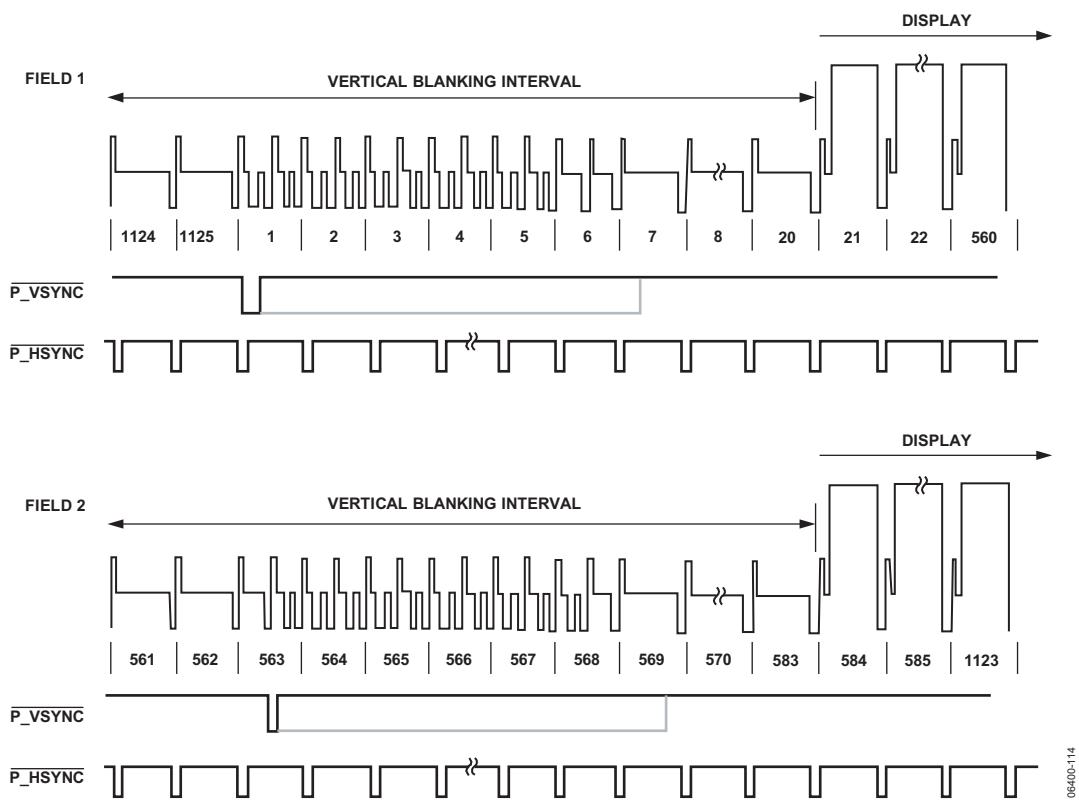

## タイミング図

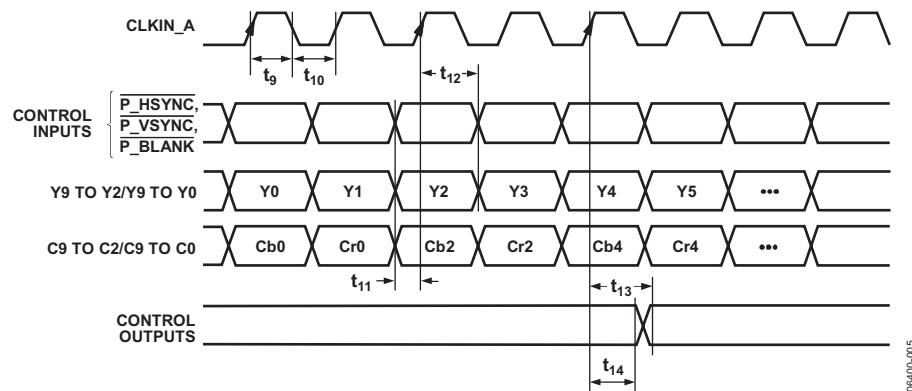

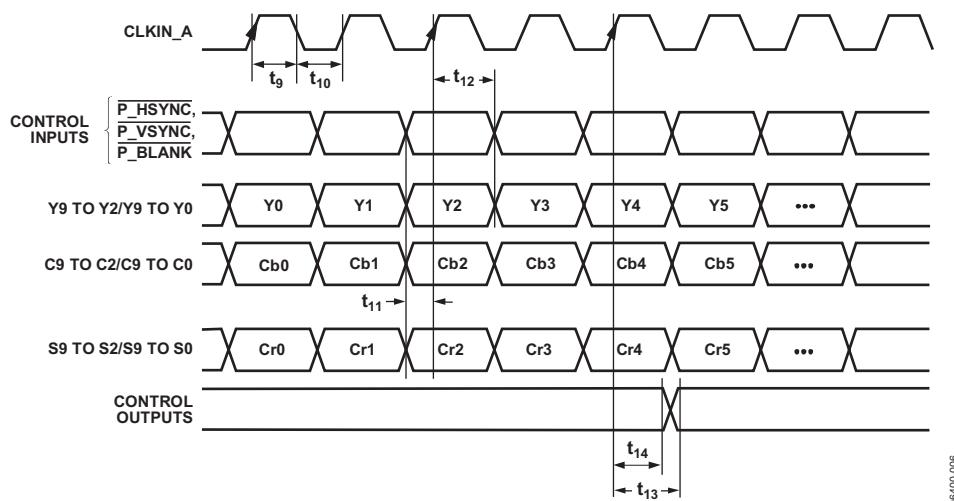

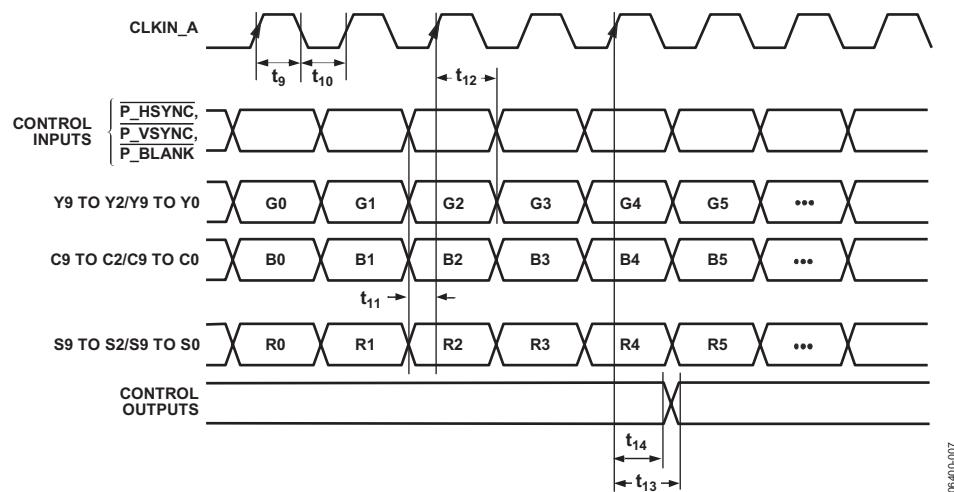

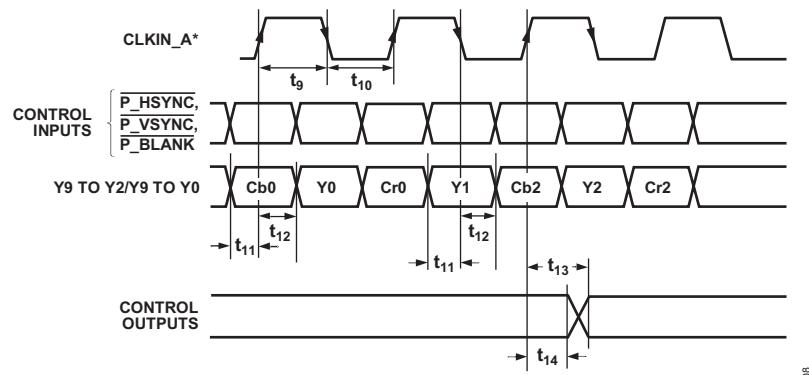

図2~図13では、次の省略形を使用します。

$t_9$ =クロック・ハイレベル時間 $t_{10}$ =クロック・ローレベル時間 $t_{11}$ =データ・セットアップ時間 $t_{12}$ =データ・ホールド時間 $t_{13}$ =制御出力アクセス時間

$t_{14}$ =制御出力ホールド時間

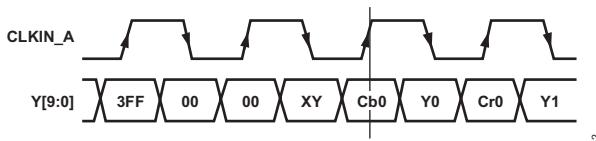

さらに、ADV7344の入力設定については、表31を参照してください。

\*SELECTED BY SUBADDRESS 0x01, BIT 7.

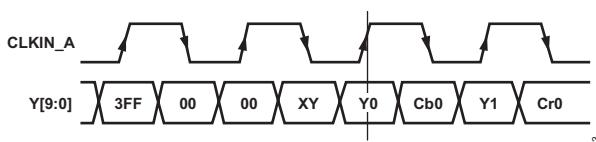

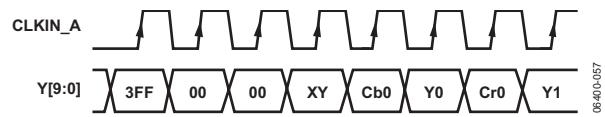

図2. SD専用、8/10ビット、4:2:2 YCrCbピクセル入力モード（入力モード000）

06400-004

\*SELECTED BY SUBADDRESS 0x01, BIT 7.

図3. SD専用、16/20ビット、4:2:2 YCrCbピクセル入力モード（入力モード000）

06400-003

図4. SD専用、24/30ビット、4:4:4 RGBピクセル入力モード（入力モード000）

06400-004

図5. ED/HD-SDR専用、16/20ビット、4:2:2 YCrCbピクセル入力モード（入力モード001）

図6. ED/HD-SDR専用、24/30ビット、4:4:4 YCrCbピクセル入力モード（入力モード001）

図7. ED/HD-SDR専用、24/30ビット、4:4:4 RGBピクセル入力モード（入力モード001）

# ADV7344

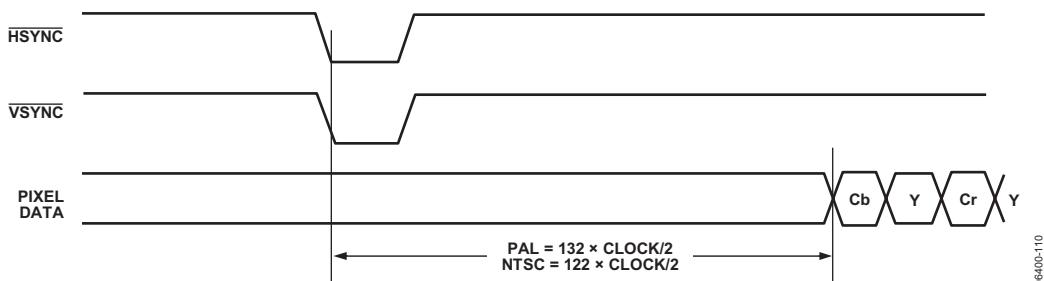

図8. ED/HD-DDR専用、8/10ビット、4:2:2 YCrCb (HSYNC/VSYNC) ピクセル入力モード (入力モード010)

図9. ED/HD-DDR専用、8/10ビット、4:2:2 YCrCb (EAV/SAV) ピクセル入力モード (入力モード010)

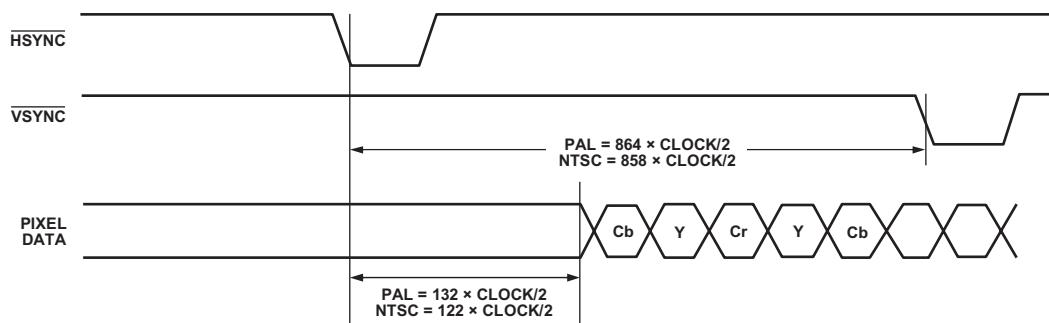

図10. SD、ED/HD-SDR入力モード、16/20ビット、4:2:2 ED/HDと8/10ビット、SDピクセル入力モード (入力モード011)

図11. SD、ED/HD-DDR入力モード、8/10ビット、4:2:2 ED/HDと8/10ビット、SDピクセル入力モード（入力モード100）

図12. ED専用（54MHz）、8/10ビット、4:2:2 YCrCb（HSYNC/SYNC）ピクセル入力モード（入力モード111）

図13. ED専用（54MHz）、8/10ビット、4:2:2 YCrCb（EAV/SAV）ピクセル入力モード（入力モード111）

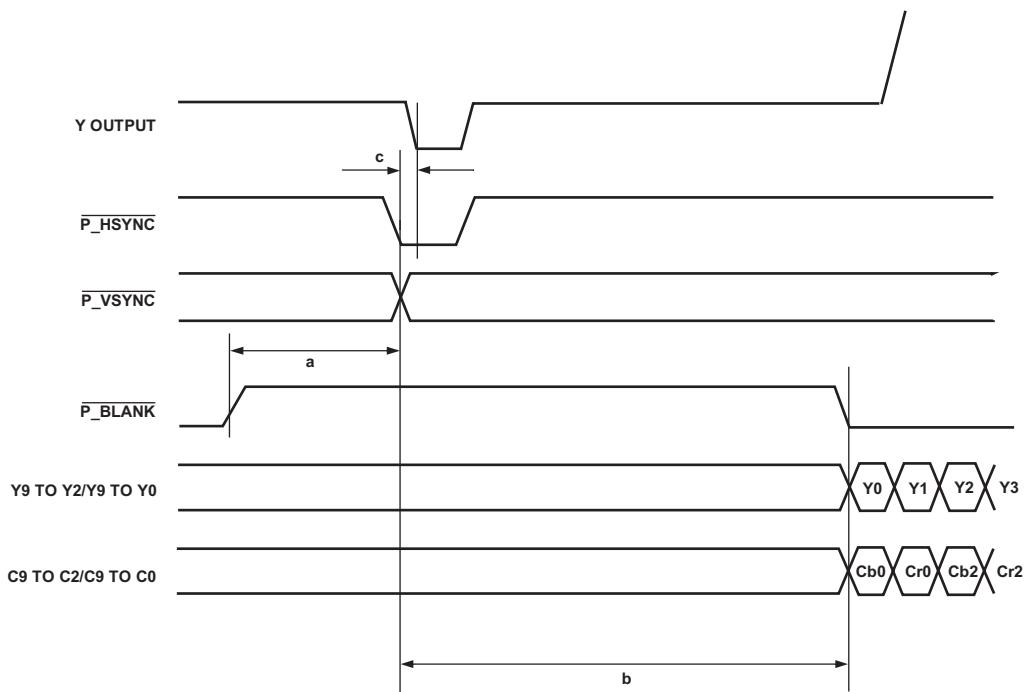

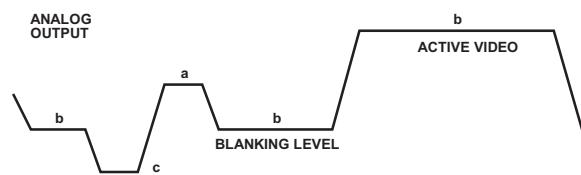

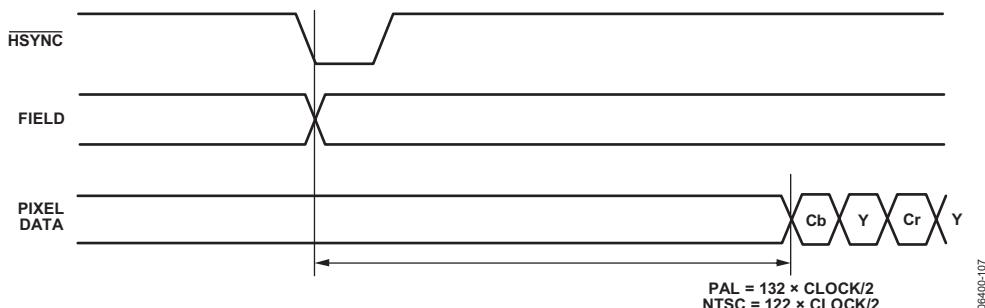

a AND b AS PER RELEVANT STANDARD.

c = PIPELINE DELAY. PLEASE REFER TO RELEVANT PIPELINE DELAY. THIS CAN BE FOUND IN THE DIGITAL TIMING SPECIFICATION SECTION OF THE DATA SHEET.

A FALLING EDGE OF  $\overline{\text{HSYNC}}$  INTO THE ENCODER GENERATES A SYNC FALLING EDGE ON THE OUTPUT AFTER A TIME EQUAL TO THE PIPELINE DELAY.

06400-014

図14. ED-SDR、16/20ビット、4:2:2 YCrCb ( $\overline{\text{HSYNC}}/\overline{\text{VSYNC}}$ ) 入力のタイミング図

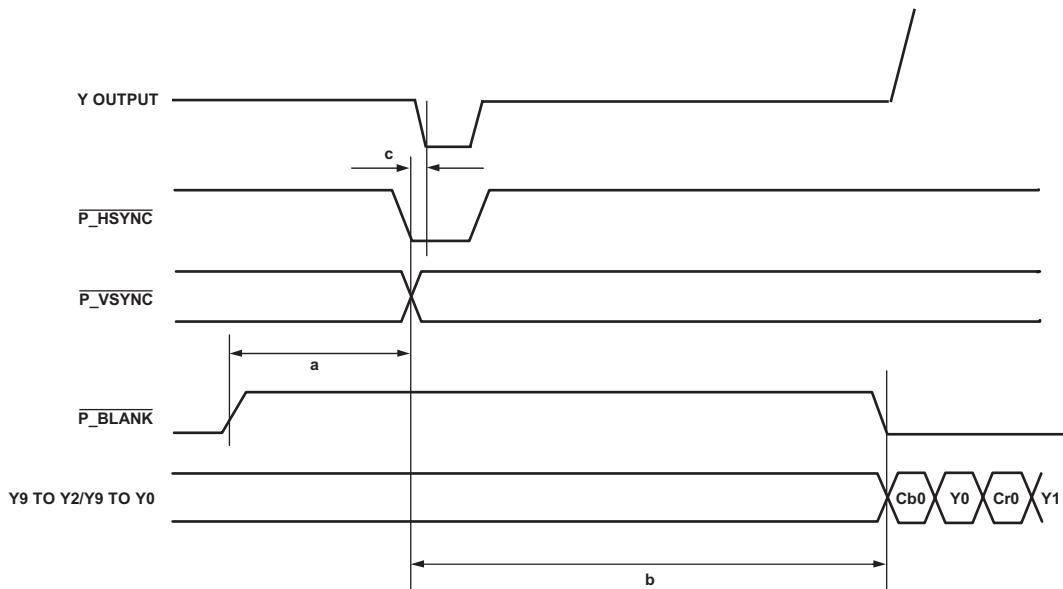

a = 32 CLOCK CYCLES FOR 525p

a = 24 CLOCK CYCLES FOR 625p

AS RECOMMENDED BY STANDARD

b(MIN) = 244 CLOCK CYCLES FOR 525p

b(MIN) = 264 CLOCK CYCLES FOR 625p

c = PIPELINE DELAY. PLEASE REFER TO RELEVANT PIPELINE DELAY. THIS CAN BE FOUND IN THE DIGITAL TIMING SPECIFICATION SECTION OF THE DATA SHEET.

A FALLING EDGE OF  $\overline{\text{HSYNC}}$  INTO THE ENCODER GENERATES A SYNC FALLING EDGE ON THE OUTPUT AFTER A TIME EQUAL TO THE PIPELINE DELAY.

06400-015

図15. ED-DDR、8/10ビット、4:2:2 YCrCb ( $\overline{\text{HSYNC}}/\overline{\text{VSYNC}}$ ) 入力のタイミング図

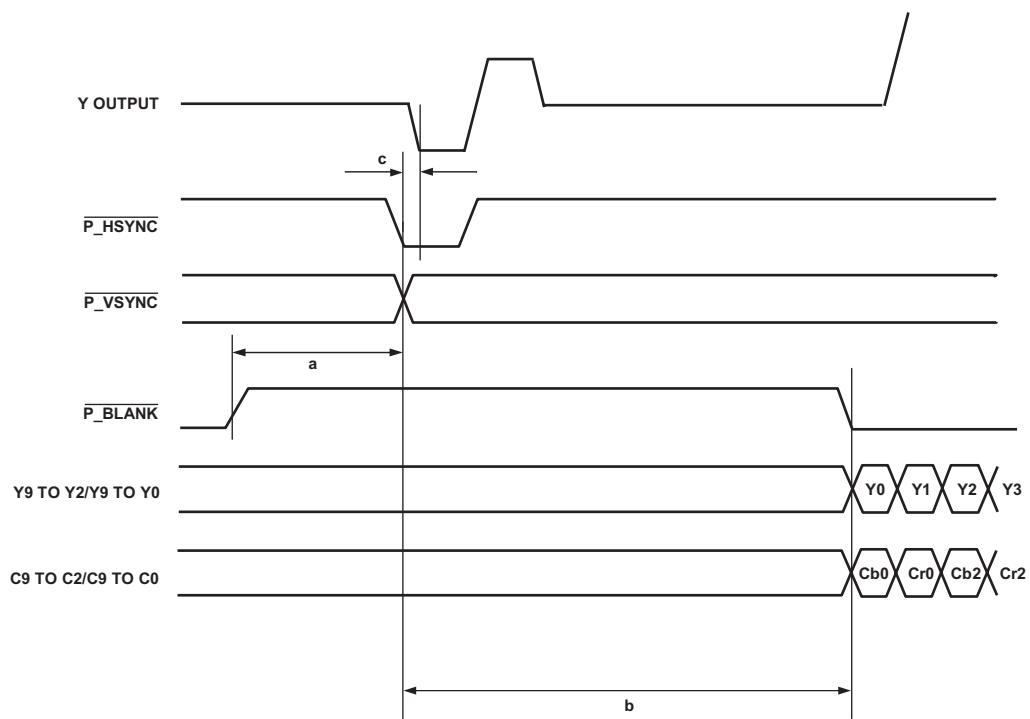

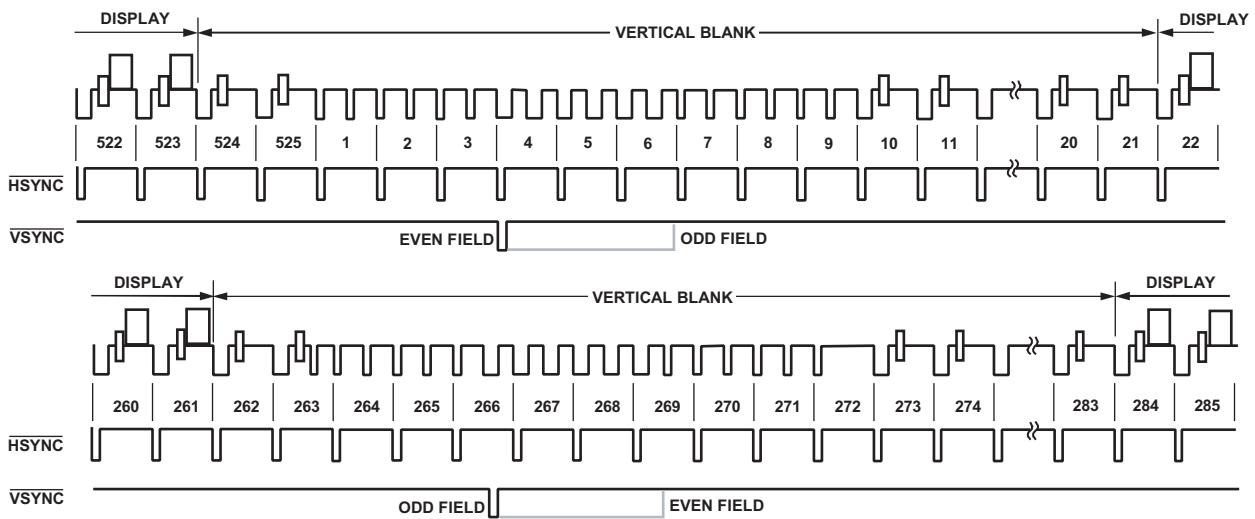

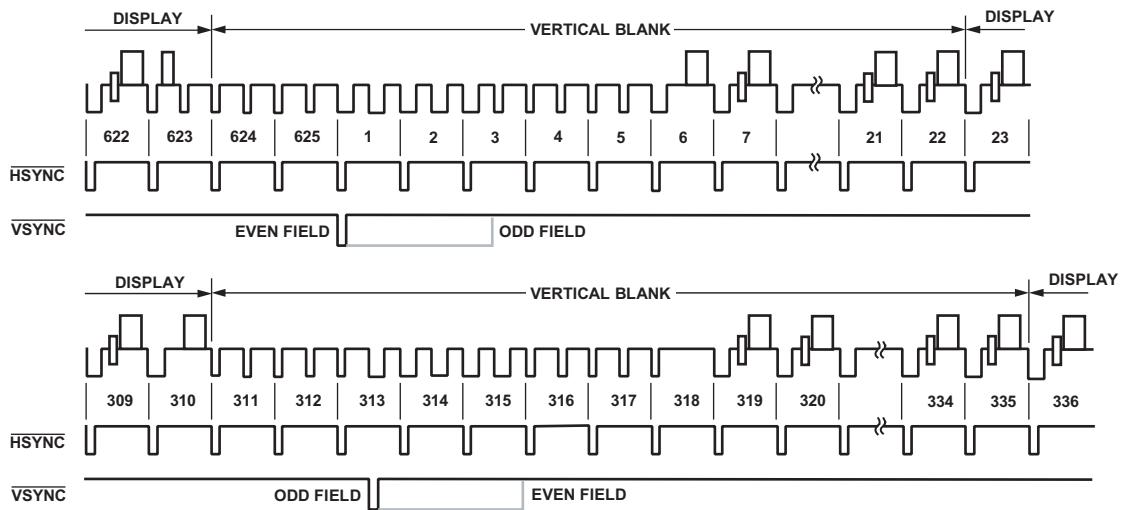

a AND b AS PER RELEVANT STANDARD.

c = PIPELINE DELAY. PLEASE REFER TO RELEVANT PIPELINE DELAY. THIS CAN BE FOUND IN THE DIGITAL TIMING SPECIFICATION SECTION OF THE DATA SHEET.

A FALLING EDGE OF HSYNC INTO THE ENCODER GENERATES A FALLING EDGE OF TRI-LEVEL SYNC ON THE OUTPUT AFTER A TIME EQUAL TO THE PIPELINE DELAY.

06400-016

図16. HD-SDR、16/20ビット、4:2:2 YCrCb (HSYNC/VSYNC) 入力のタイミング図

a AND b AS PER RELEVANT STANDARD.

c = PIPELINE DELAY. PLEASE REFER TO RELEVANT PIPELINE DELAY. THIS CAN BE FOUND IN THE DIGITAL TIMING SPECIFICATION SECTION OF THE DATA SHEET.

A FALLING EDGE OF HSYNC INTO THE ENCODER GENERATES A FALLING EDGE OF TRI-LEVEL SYNC ON THE OUTPUT AFTER A TIME EQUAL TO THE PIPELINE DELAY.

06400-017

図17. HD-DDR、8/10ビット、4:2:2 YCrCb (HSYNC/VSYNC) 入力のタイミング図

# ADV7344

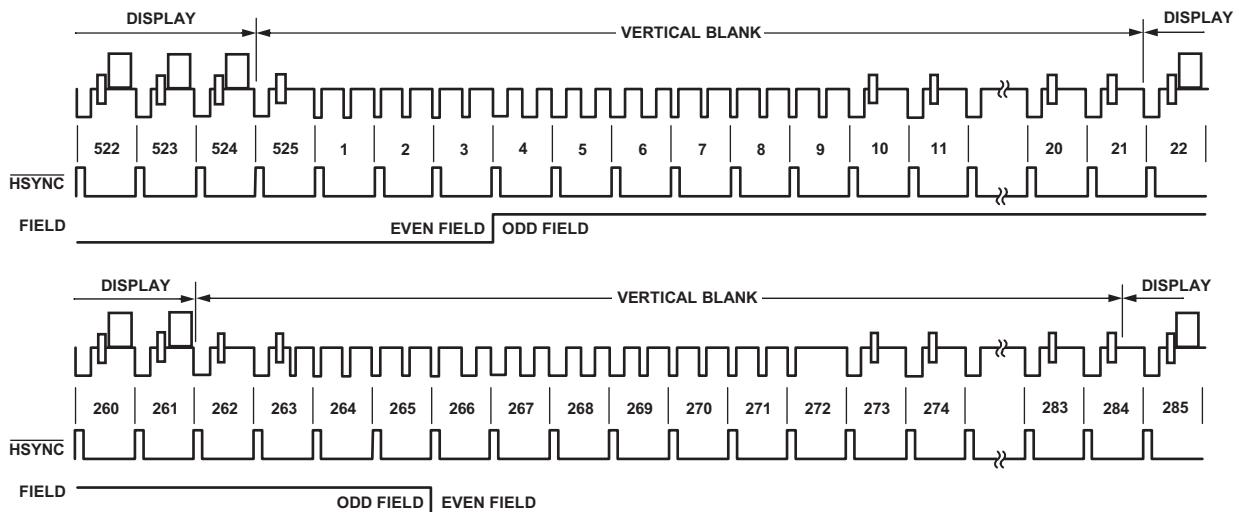

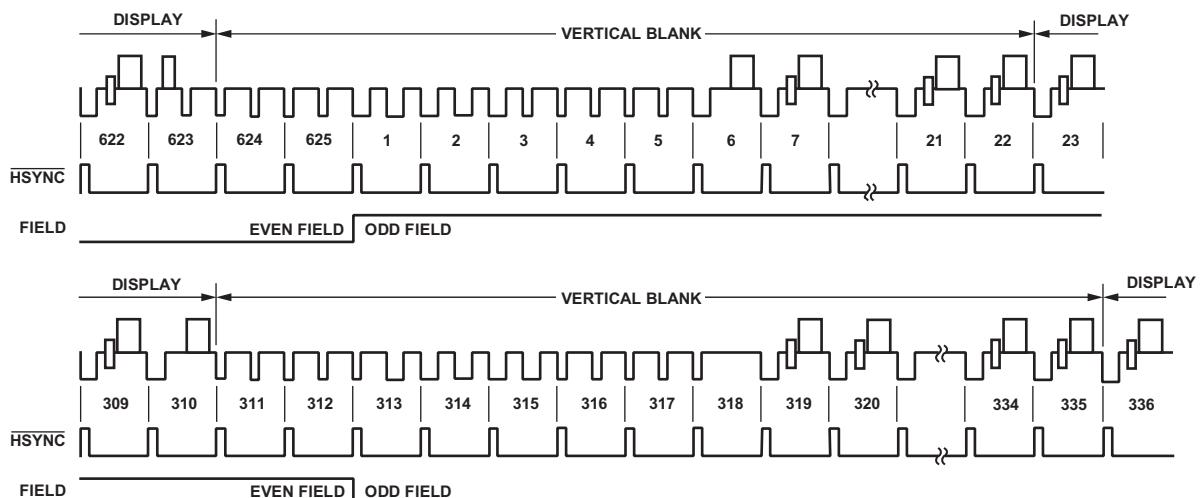

図18. SD入力のタイミング図（タイミング・モード1）

図19. MPUポートのタイミング図（I<sup>2</sup>Cモード）

図20. MPUポートのタイミング図（SPIモード）

## 絶対最大定格

表11

| Parameter <sup>1</sup>                      | Rating                               |

|---------------------------------------------|--------------------------------------|

| V <sub>AA</sub> to AGND                     | -0.3 V to +3.9 V                     |

| V <sub>DD</sub> to DGND                     | -0.3 V to +2.3 V                     |

| PV <sub>DD</sub> to PGND                    | -0.3 V to +2.3 V                     |

| V <sub>DD_IO</sub> to GND_IO                | -0.3 V to +3.9 V                     |

| V <sub>AA</sub> to V <sub>DD</sub>          | -0.3 V to +2.2 V                     |

| V <sub>DD</sub> to PV <sub>DD</sub>         | -0.3 V to +0.3 V                     |

| V <sub>DD_IO</sub> to V <sub>DD</sub>       | -0.3 V to +2.2 V                     |

| AGND to DGND                                | -0.3 V to +0.3 V                     |

| AGND to PGND                                | -0.3 V to +0.3 V                     |

| AGND to GND_IO                              | -0.3 V to +0.3 V                     |

| DGND to PGND                                | -0.3 V to +0.3 V                     |

| DGND to GND_IO                              | -0.3 V to +0.3 V                     |

| PGND to GND_IO                              | -0.3 V to +0.3 V                     |

| Digital Input Voltage to GND_IO             | -0.3 V to V <sub>DD_IO</sub> + 0.3 V |

| Analog Outputs to AGND                      | -0.3 V to V <sub>AA</sub>            |

| Storage Temperature Range (T <sub>S</sub> ) | -65°C to +150°C                      |

| Junction Temperature (T <sub>J</sub> )      | 150°C                                |

| Lead Temperature (Soldering, 10 sec)        | 260°C                                |

<sup>1</sup> 任意の電源またはコモンに対するアナログ出力の短絡時間は、無限とすることができます。

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作セクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

ADV7344は、高性能の集積回路です。ESD定格は1kV未満であるため、ESDの影響を受けやすくなっています。したがって、デバイスの取扱い時や組立て時には、適切な予防措置を講じてください。

### 熱抵抗

$\theta_{JA}$ は、最悪の条件、すなわち回路ボードに表面実装パッケージをハンダ付けした状態で規定しています。

表12. 热抵抗<sup>1</sup>

| Package Type | $\theta_{JA}$ | $\theta_{JC}$ | Unit |

|--------------|---------------|---------------|------|

| 64-Lead LQFP | 47            | 11            | °C/W |

<sup>1</sup> 値は、JEDEC 4層テスト基板を基準にしています。

ADV7344は鉛フリー製品です。リード仕上げは純度100%のSn電気メッキです。デバイスはRoHS準拠であり、255°C (±5°C)までのIRリフロー (JEDEC STD-20) 鉛フリー処理に適しています。

本製品は、従来型のSnPbハンダ処理製品と後方互換性があります。電気メッキされたSnコーティングは、Sn/Pbハンダ・ペーストを用いて従来型リフロー温度220~235°Cでハンダ付けできます。

### ESDに関する注意

ESD (静電放電) の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術であるESD保護回路を内蔵していますが、デバイスで高エネルギーの静電放電が発生した場合、損傷を生じる可能性があります。性能劣化や機能低下を防止するため、ESDに対して適切な予防措置をとることが推奨されます。

# ADV7344

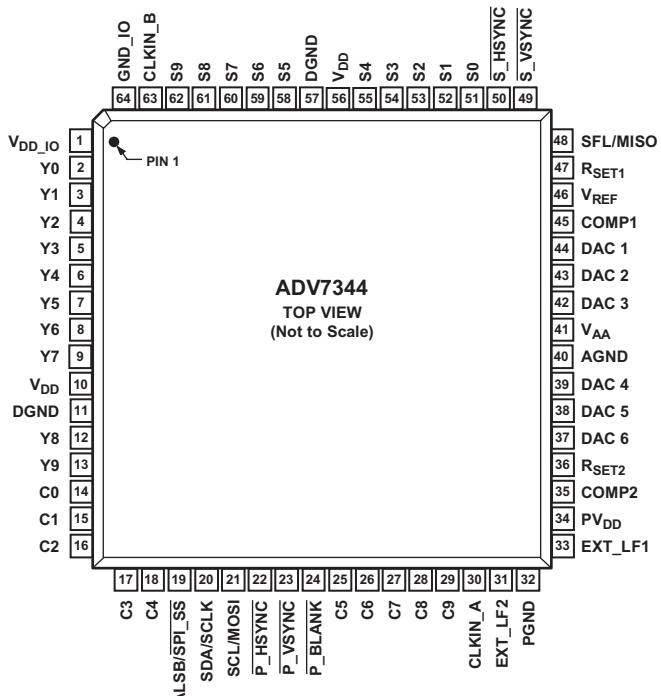

## ピン配置と機能の説明

図21. ピン配置

06000-021

表13. ピン機能の説明

| ピン番号                  | 記号              | 入出力 | 説明                                                                                                                                                                      |

|-----------------------|-----------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13, 12,<br>9 to 2     | Y9 to Y0        | I   | 10ビット・ピクセル・ポート (Y9~Y0)。Y0はLSBです。入力モードについては表31を参照。                                                                                                                       |

| 29 to 25,<br>18 to 14 | C9 to C0        | I   | 10ビット・ピクセル・ポート (C9~C0)。C0はLSBです。入力モードについては表31を参照。                                                                                                                       |

| 62 to 58,<br>55 to 51 | S9 to S0        | I   | 10ビット・ピクセル・ポート (S9~S0)。S0はLSBです。入力モードについては表31を参照。                                                                                                                       |

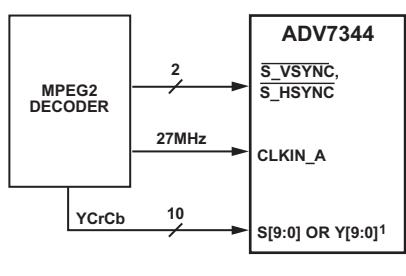

| 30                    | CLKIN_A         | I   | HD専用 (74.25MHz)、ED <sup>1</sup> の場合 (27MHzまたは54MHz)、またはSD専用 (27MHz) のピクセル・クロック入力                                                                                        |

| 63                    | CLKIN_B         | I   | デュアル・モード専用のピクセル・クロック入力。ED動作用の27MHz基準クロック、またはHD動作用の74.25MHz基準クロックを必要とします。                                                                                                |

| 50                    | S_HSYNC         | I/O | SD水平同期信号。このピンは、SD、ED、またはHDの水平同期信号を出力するようにも設定できます。「水平／垂直外部同期制御」を参照。                                                                                                      |

| 49                    | S_VSYNC         | I/O | SD垂直同期信号。このピンは、SD、ED、またはHDの垂直同期信号を出力するようにも設定できます。「水平／垂直外部同期制御」を参照。                                                                                                      |

| 22                    | P_HSYNC         | I   | ED/HD水平同期信号。「水平／垂直外部同期制御」を参照。                                                                                                                                           |

| 23                    | P_VSYNC         | I   | ED/HD垂直同期信号。「水平／垂直外部同期制御」を参照。                                                                                                                                           |

| 24                    | P_BLANK         | I   | ED/HDブランкиング信号。「水平／垂直外部同期制御」を参照。                                                                                                                                        |

| 48                    | SFL/MISO        | I/O | 多機能ピン：サブキャリア周波数ロック (SFL) 入力／SPIデータ出力。SFL入力は、カラー・サブキャリアDDSシステム、タイミング・リセット、またはサブキャリア・リセットの駆動に使用されます。                                                                      |

| 47                    | R_SET1          | I   | このピンは、DAC 1、DAC 2、およびDAC 3出力の振幅制御に使用されます。フルドライブ動作 (たとえば、37.5Ω負荷) の場合は、R_SET1とAGNDの間に510Ω抵抗を接続する必要があります。ロードドライブ動作 (たとえば、300Ω負荷) の場合は、R_SET1とAGNDの間に4.12kΩ抵抗を接続する必要があります。 |

| 36                    | R_SET2          | I   | このピンは、DAC 4、DAC 5、DAC 6出力の振幅の制御に使用されます。R_SET2とAGNDの間に4.12kΩ抵抗を接続する必要があります。                                                                                              |

| 45, 35                | COMP1,<br>COMP2 | O   | 補償ピン。両方のCOMPピンとV_AAの間に2.2nFコンデンサを接続します。                                                                                                                                 |

| ピン番号       | 記号                     | 入出力 | 説明                                                                                   |

|------------|------------------------|-----|--------------------------------------------------------------------------------------|

| 44, 43, 42 | DAC 1, DAC 2,<br>DAC 3 | O   | DAC出力。フルドライブ／ロードライブ対応のDAC。                                                           |

| 39, 38, 37 | DAC 4, DAC 5,<br>DAC 6 | O   | DAC出力。ロードライブのみ対応のDAC。                                                                |

| 21         | SCL/MOSI               | I   | 多機能ピン：I <sup>2</sup> Cクロック入力／SPIデータ入力。                                               |

| 20         | SDA/SCLK               | I/O | 多機能ピン：I <sup>2</sup> Cデータ入出力。また、SPIクロック入力。                                           |

| 19         | ALSB/SPI_SS            | I   | 多機能ピン：この信号はMPU I <sup>2</sup> CアドレスのLSB <sup>2</sup> を設定します。また、SPIスレーブ・セレクト。         |

| 46         | V <sub>REF</sub>       |     | DAC用のオプションの外部リファレンス電圧入力またはリファレンス電圧出力。                                                |

| 41         | V <sub>AA</sub>        | P   | アナログ電源 (3.3V)                                                                        |

| 10, 56     | V <sub>DD</sub>        | P   | デジタル電源 (1.8V)。両電源構成では、V <sub>DD</sub> は、フェライト・ビーズまたは適切なフィルタリングを使用して、他の1.8V電源に接続できます。 |

| 1          | V <sub>DD_IO</sub>     | P   | 入出力デジタル電源 (3.3V)                                                                     |

| 34         | PV <sub>DD</sub>       | P   | PLL電源 (1.8V)。両電源構成では、PV <sub>DD</sub> は、フェライト・ビーズまたは適切なフィルタリングを使用して、他の1.8V電源に接続できます。 |

| 33         | EXT_LF1                | I   | オンチップPLL 1用の外部ループ・フィルタ                                                               |

| 31         | EXT_LF2                | I   | オンチップPLL 2用の外部ループ・フィルタ                                                               |

| 32         | PGND                   | G   | PLLグラウンド・ピン                                                                          |

| 40         | AGND                   | G   | アナログ・グラウンド・ピン                                                                        |

| 11, 57     | DGND                   | G   | デジタル・グラウンド・ピン                                                                        |

| 64         | GND_IO                 | G   | 入出力電源グラウンド・ピン                                                                        |

<sup>1</sup> ED=拡張解像度=525pと625p。<sup>2</sup> LSB=下位ビット。ADV7344では、LSBを0に設定すると、I<sup>2</sup>Cアドレスは0xD4に設定されます。LSBを1に設定すると、I<sup>2</sup>Cアドレスは0xD6に設定されます。

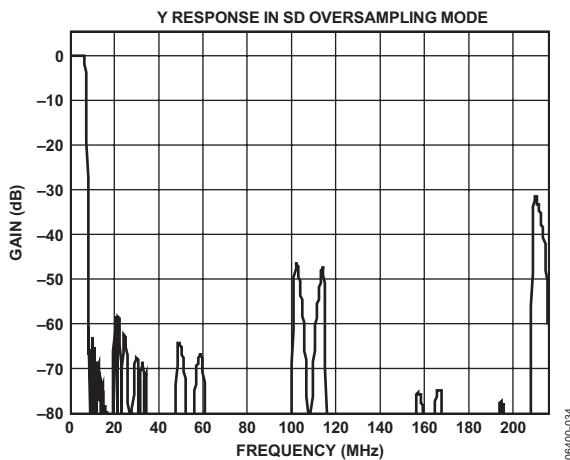

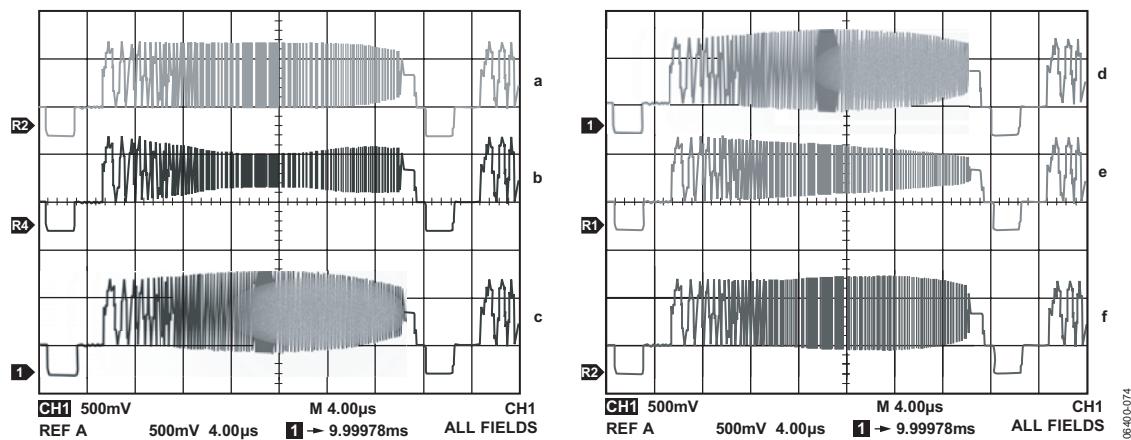

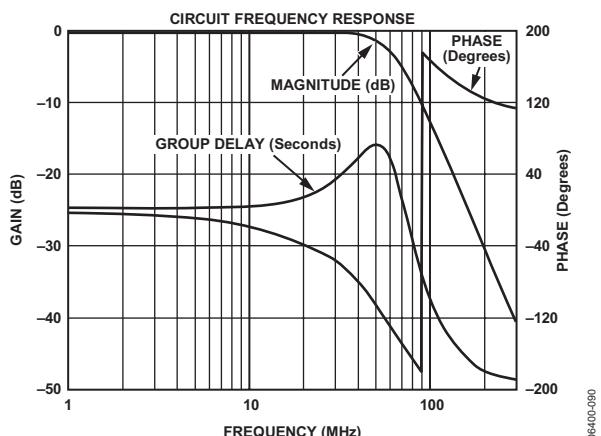

## 代表的な性能特性

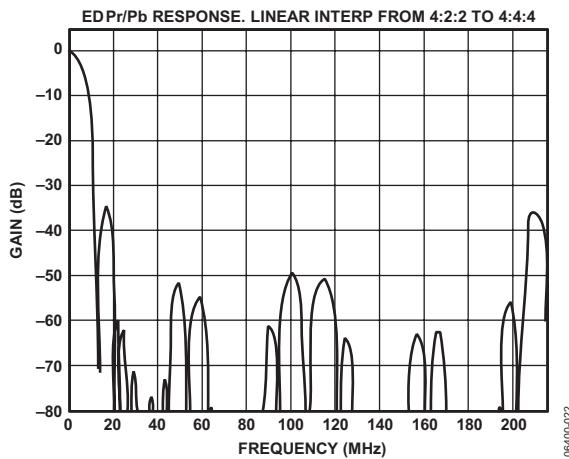

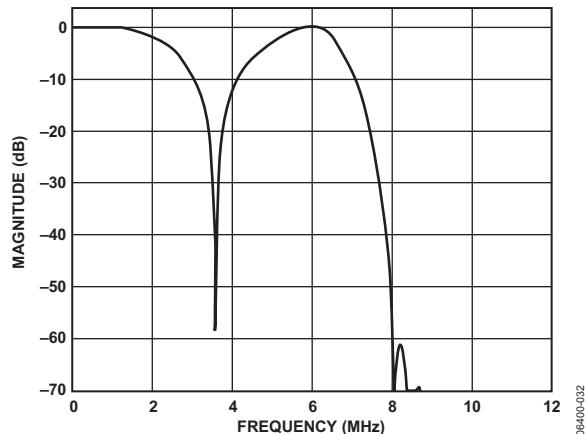

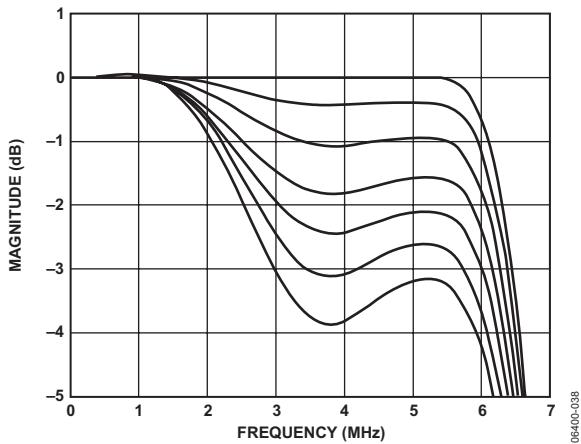

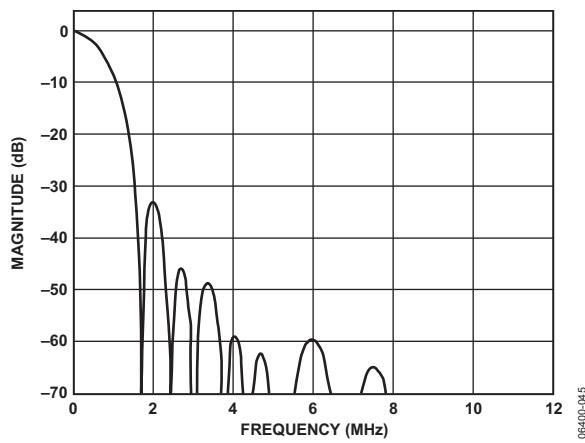

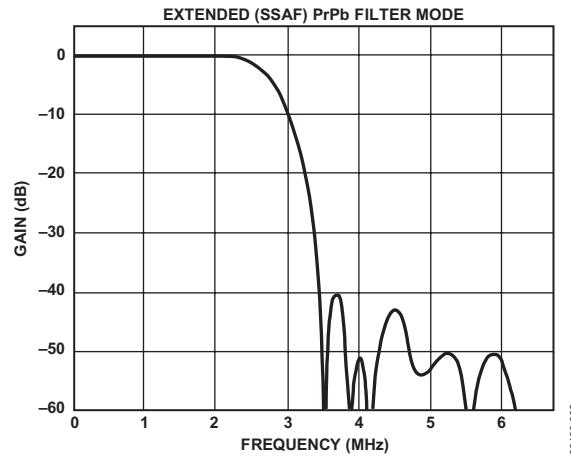

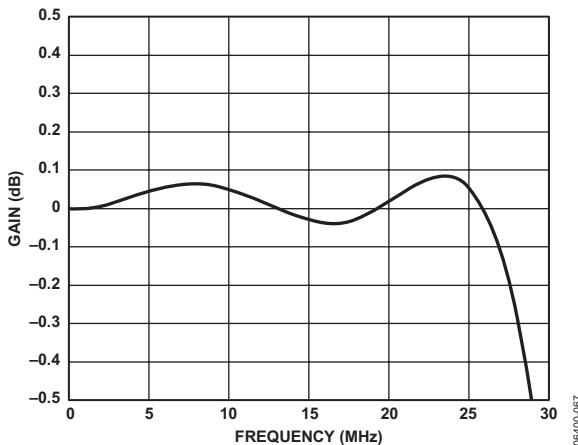

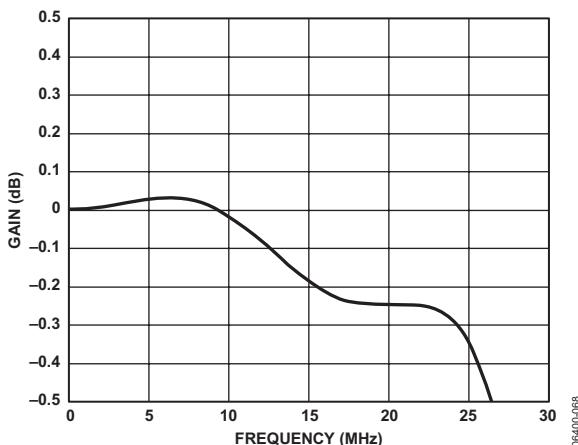

図22. ED 8倍のオーバーサンプリング、PrPb フィルタ（線形）応答

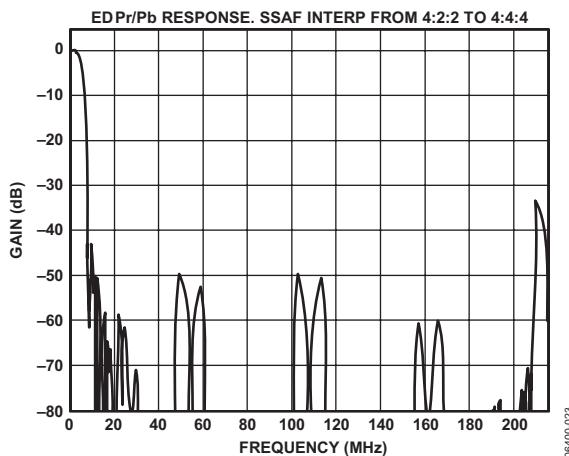

図23. ED 8倍のオーバーサンプリング、PrPb フィルタ（SSAF）応答

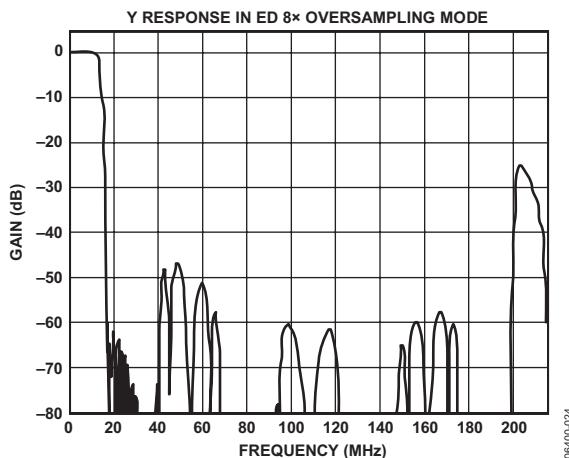

図24. ED 8倍のオーバーサンプリング、Y フィルタ応答

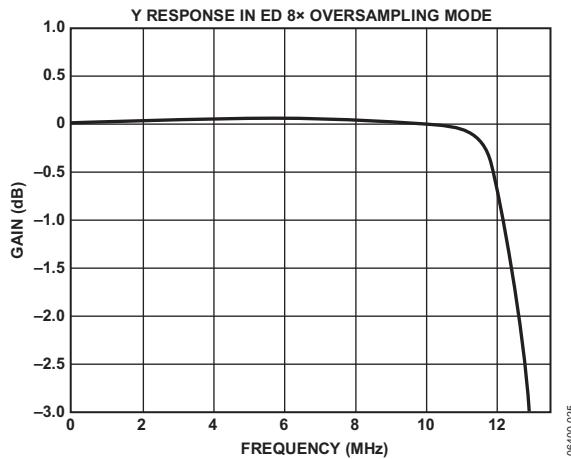

図25. ED 8倍のオーバーサンプリング、Y フィルタ応答（通過帯域に注目）

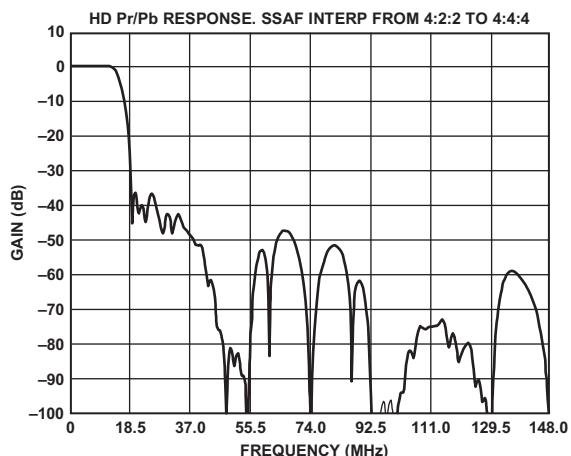

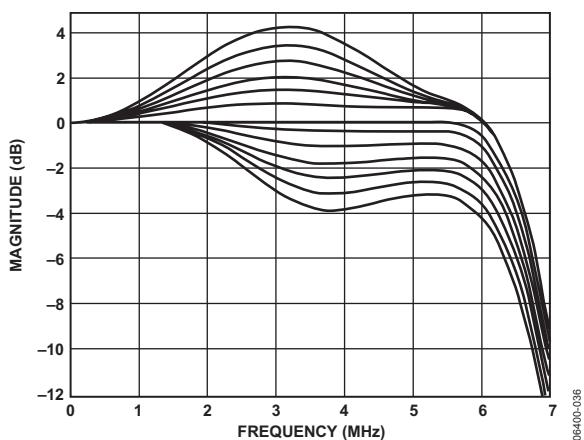

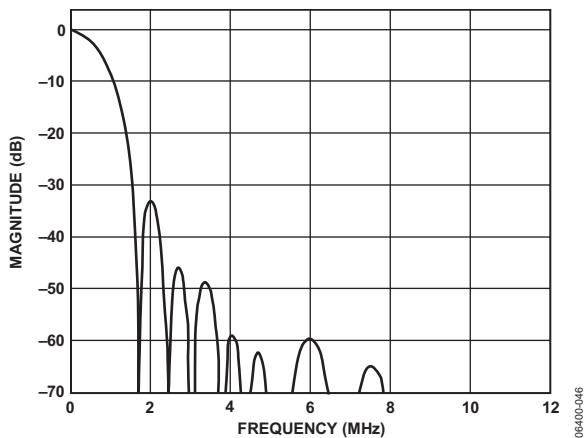

図26. HD 4倍のオーバーサンプリング、PrPb (SSAF) フィルタ応答（4:2:2入力）

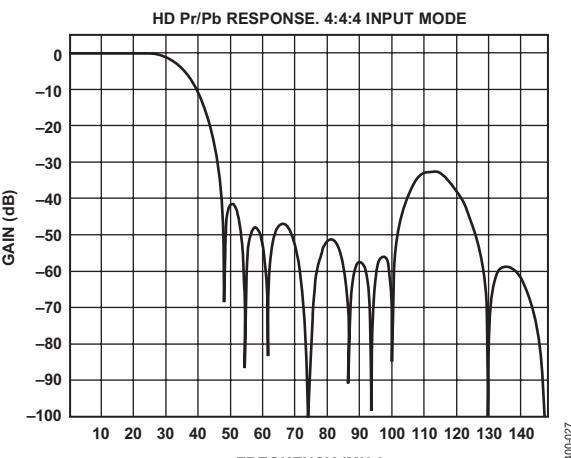

図27. HD 4倍のオーバーサンプリング、PrPb (SSAF) フィルタ応答（4:4:4入力）

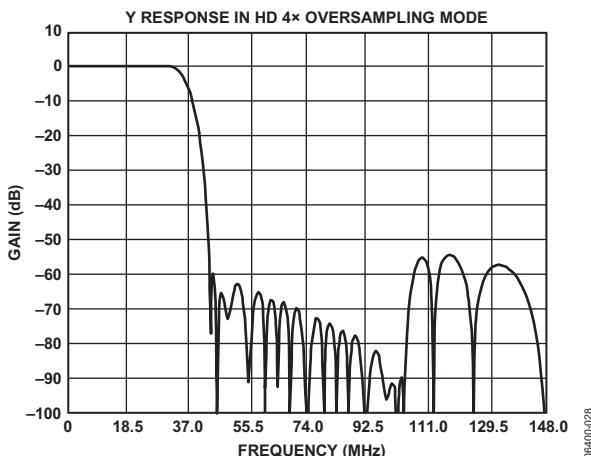

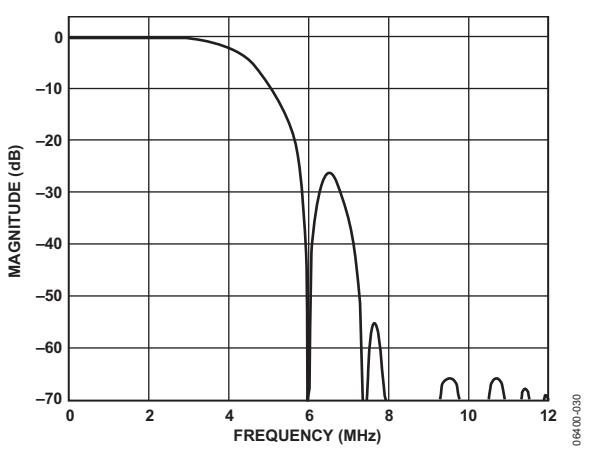

図28. HD 4倍のオーバーサンプリング、Yフィルタ応答

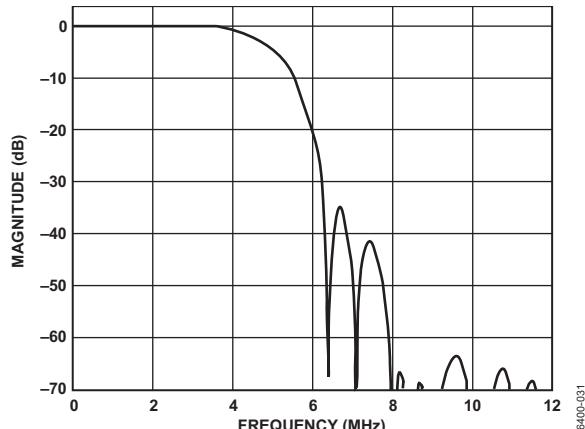

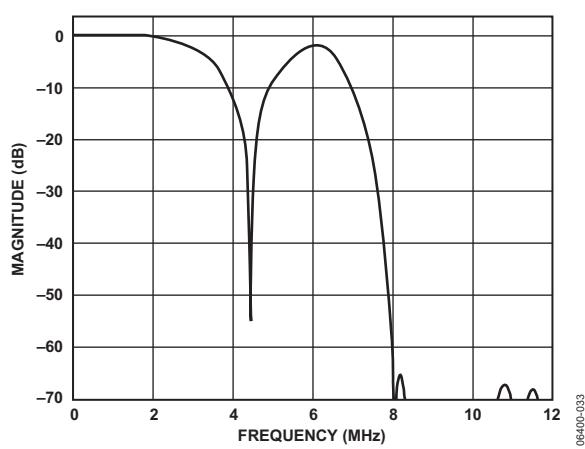

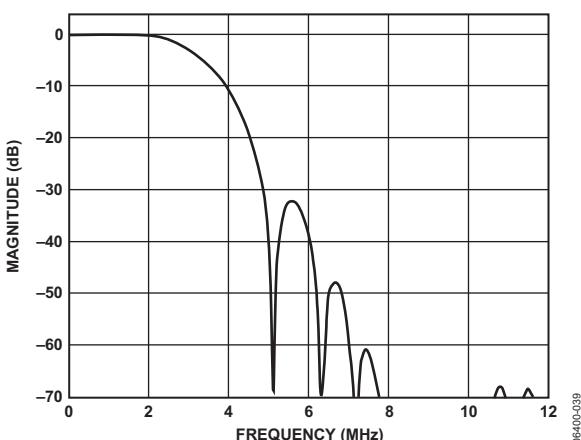

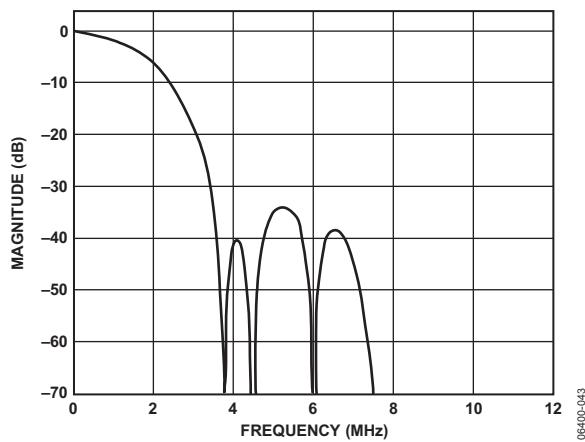

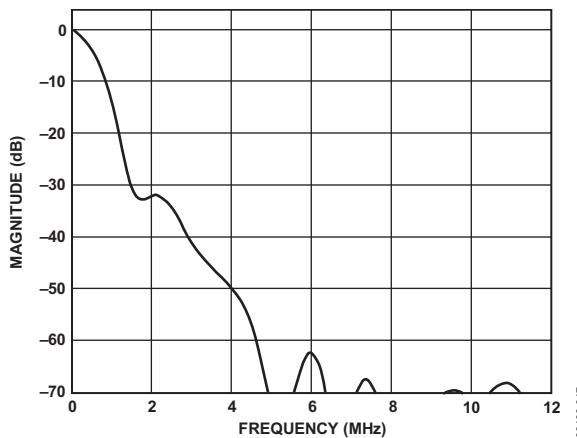

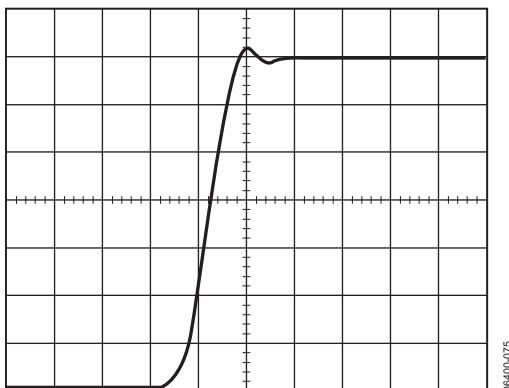

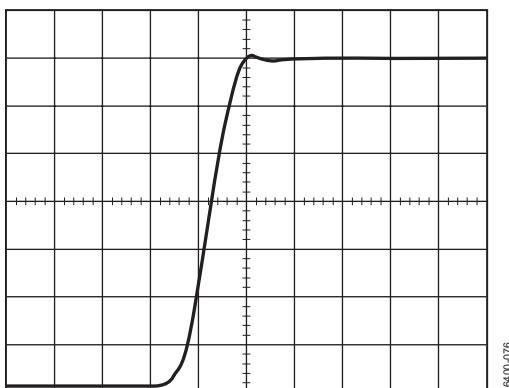

図31. SD PAL、ルミナンス・ローパス・フィルタ応答

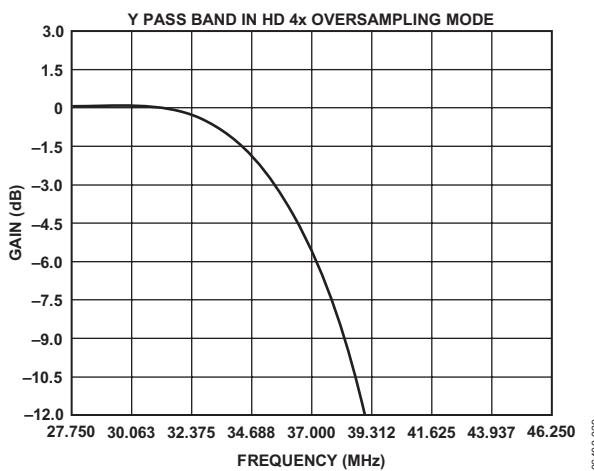

図29. HD 4倍のオーバーサンプリング、Yフィルタ応答

(通過帯域にフォーカス)

図32. SD NTSC、ルミナンス・ノッチ・フィルタ応答

図30. SD NTSC、ルミナンス・ローパス・フィルタ応答

図33. SD PAL、ルミナンス・ノッチ・フィルタ応答

# ADV7344

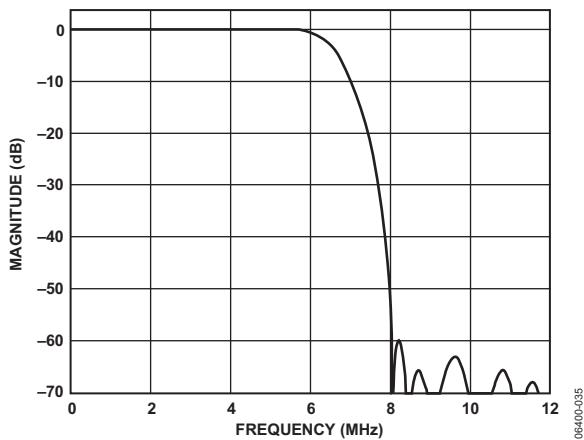

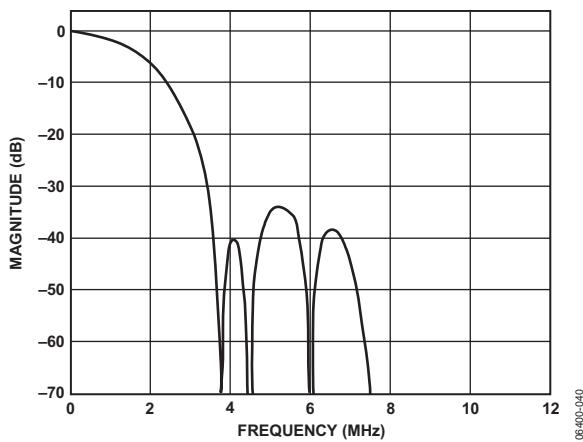

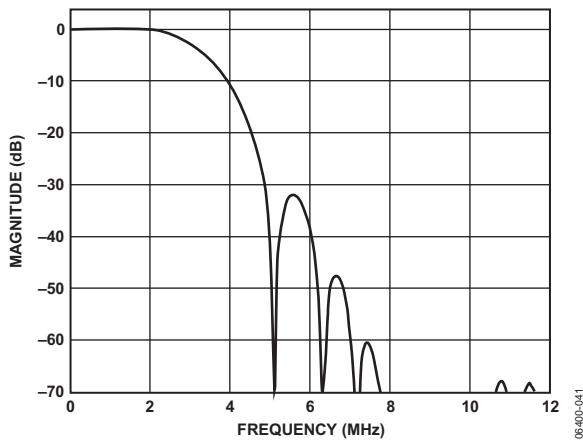

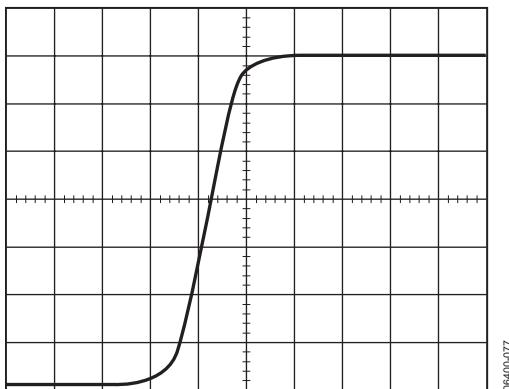

図34. SD、16倍のオーバーサンプリング、Yフィルタ応答

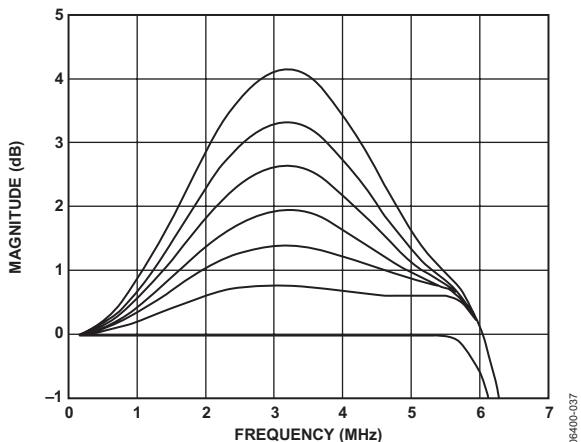

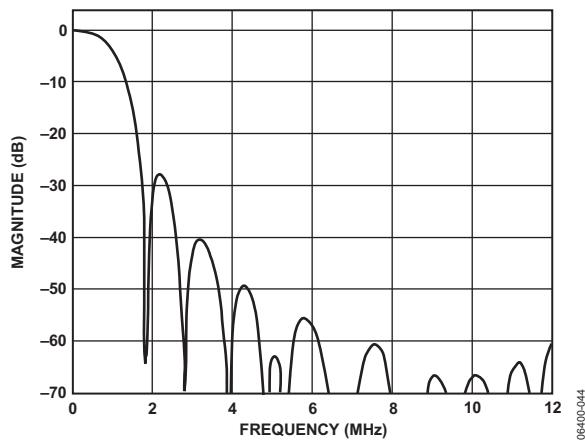

図37. SDルミナンスSSAFフィルタ、プログラマブル・ゲイン

図35. 12MHzまでのSDルミナンスSSAFフィルタ応答

図38. SDルミナンスSSAFフィルタ、プログラマブル減衰

図36. SDルミナンスSSAFフィルタ、プログラマブル応答

図39. SDルミナンスCIFローパス・フィルタ応答

図40. SDルミナンスQCIFローパス・フィルタ応答

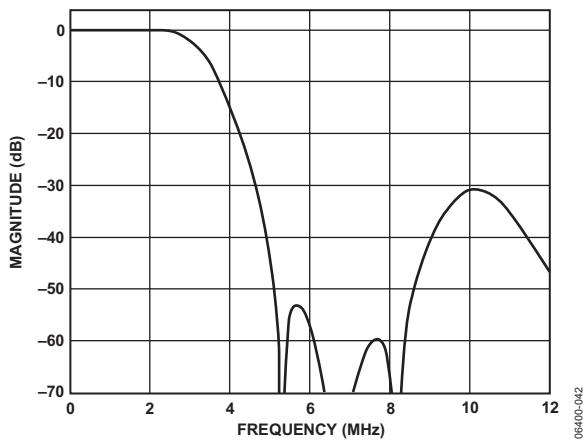

図43. SDクロミナンス1.3MHzローパス・フィルタ応答

図41. SDクロミナンス3.0MHzローパス・フィルタ応答

図44. SDクロミナンス1.0MHzローパス・フィルタ応答

図42. SDクロミナンス2.0MHzローパス・フィルタ応答

図45. SDクロミナンス0.65MHzローパス・フィルタ応答

## ADV7344

図46. SDクロミナンスCIFローパス・フィルタ応答

図47. SDクロミナンスQCIFローパス・フィルタ応答

## MPUポート説明

マイクロプロセッサなどのデバイスは、次のいずれかのプロトコルを使用して、ADV7344と通信できます。

- 2線式シリアル（I<sup>2</sup>C互換）バス

- 4線式シリアル（SPI互換）バス

パワーアップまたはリセット時に、MPUポートはI<sup>2</sup>C動作用に設定されます。SPI動作は、「SPI動作」で説明する手順に従って、いつでも起動することができます。

### I<sup>2</sup>C動作

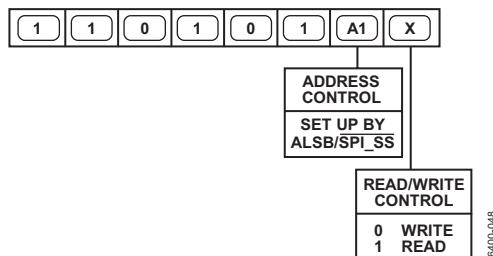

ADV7344は、複数のペリフェラルを駆動する、2線式シリアル（I<sup>2</sup>C互換）マイクロプロセッサ・バスをサポートします。このポートは、オープンドレイン設定で動作します。バスに接続された任意のデバイスとADV7344の間では、シリアル・データ（SDA）とシリアル・クロック（SCL）の2つの入力によって情報が伝送されます。各スレーブ・デバイスは、独自のアドレスによって認識されます。ADV7344では、読み出しと書き込みの動作に対して4つのスレーブ・アドレスを使用できます。これらはデバイスごとの独自のアドレスであり、図48に示します。読み出し／書き込みの動作は、LSBで設定します。ロジック1は読み出し動作に対応し、ロジック0は書き込み動作をサポートします。A1を制御するときは、ADV7344のALSB/SPI\_SSピンをロジック0またはロジック1に設定します。

図48. ADV7344のスレーブ・アドレス=0xD4または0xD6

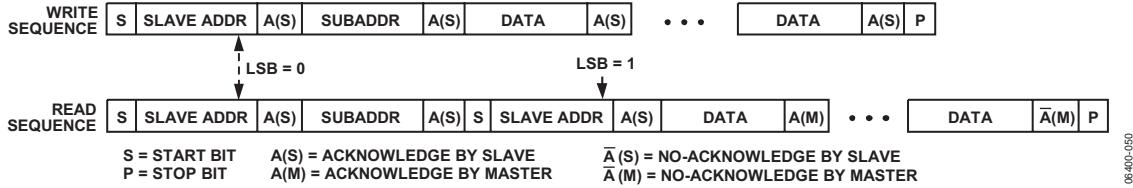

バス上のさまざまなデバイスを制御するときは、次のプロトコルを使用します。マスターは、スタート条件を設定してデータ転送を開始します。スタート条件は、SCLがハイレベルのときに、SDA上でハイレベルからローレベルへの変化として定義されます。これは、アドレス／データ・ストリームが後に続くことを示しています。すべてのペリフェラルは、スタート条件に応答して、次の8ビット（7ビット・アドレス+R/Wビット）をシフトします。各ビットは、MSBからLSBへの順に転送されます。送信されたアドレスに対応するアドレスを持つペリフェラ

ルは、9番目のクロック・パルス区間に中に、データ・ラインをローレベルにして応答します。これはアクノレッジ・ビットと呼ばれています。この時点では、バス上の他のすべてのデバイスが接続を解除して、アイドル状態を維持します。アイドル状態では、各デバイスはSDAラインとSCLラインを監視して、スタート条件と自分のアドレスの受信を待ちます。R/Wビットがデータの転送方向を指定します。データの転送方向を指定します。

先頭バイトのLSBがロジック0のとき、マスターがペリフェラルに情報を書き込むことを意味します。先頭バイトのLSBがロジック1のとき、マスターがペリフェラルから情報を読み込むことを意味します。

ADV7344は、バス上の標準スレーブ・デバイスとして機能します。SDAピン上のデータは8ビット長で、7ビット・アドレスとR/Wビットに対応しています。ADV7344は、先頭バイトをデバイス・アドレスとして、2番目のバイトをサブアドレスの先頭として解釈します。サブアドレスの自動インクリメント機能により、任意の有効なサブアドレスから始まる昇順のサブアドレス・シーケンスで、レジスタとの間でデータの書き込み／読み出しが可能です。データ転送は常にストップ条件によって終了します。すべてのレジスタを更新しなくとも、固有のサブアドレス・レジスタを1個ずつアクセスすることもできます。

ストップ条件とスタート条件は、データ転送の任意のステージで検出できます。通常の読み出し／書き込み動作で、これらの条件が誤った順序でアサートされると、直ちにアイドル状態になります。特定のSCLハイレベル期間中は、1スタート条件、1ストップ条件、または1ストップ条件に続く1スタート条件のみを発生させます。無効なサブアドレスが指定されると、ADV7344はアクノレッジを発生しないでアイドル状態に戻ります。エンコーダのアドレッシングに自動インクリメント方式を使用し、最高サブアドレスを超えた場合は、次の動作が実行されます。

- 読出しモードでは、マスター・デバイスがノー・アクノレッジを発行するまで、最高サブアドレス・レジスタの値が output され続けます。これは読み出しの終了を意味します。ノー・アクノレッジ状態は、9番目のパルスでSDAラインがローレベルにならないときに発生します。

- 書込みモードでは、無効バイトのデータはサブアドレス・レジスタにロードされず、ADV7344からノー・アクノレッジが発行されて、デバイスはアイドル状態に戻ります。

# ADV7344

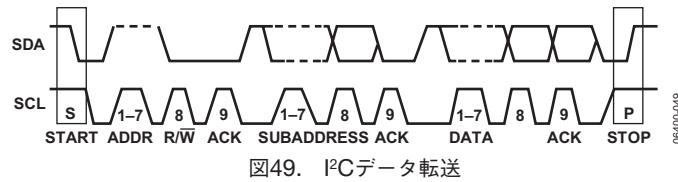

図49に、書き込みシーケンス用のデータ転送例と、スタート／ストップ条件を示します。図50は、バスの書き込み／読み出しシーケンスを示します。

図49. I<sup>2</sup>Cデータ転送

図50. I<sup>2</sup>Cの読み出し／書き込みシーケンス

## SPI動作

ADV7344は、複数のペリフェラルを接続する4線式シリアル(SPI互換)バスをサポートします。バス上のマスターSPIペリフェラルとADV7344との間の情報伝送には、マスター出力／スレーブ入力(MOSI)とシリアル・クロック(SCLK)の2つの入力、ならびにマスター入力／スレーブ出力(MISO)の1つの出力を使用します。バス上の各スレーブ・デバイスのスレーブ・セレクト・ピンは、独自のスレーブ・セレクト・ラインによってマスターSPIペリフェラルに接続します。したがって、スレーブ・デバイスのアドレッシングは必要ありません。

SPI動作を起動するときは、マスターSPIペリフェラル(たとえば、マイクロプロセッサ)は、ADV7344のALSB/SPI\_SSピンに3つのロー・パルスを出力します。エンコーダがALSB/SPI\_SSピン上で3番目の立上がりエッジを検出すると、自動的にSPI通信モードに切り替わります。ADV7344は、リセットまたはパワーダウンが行われるまで、SPI通信モードを維持します。

ADV7344を制御するときは、読み出し／書き込みトランザクションに対して次のプロトコルを使用します。まず、マスターは、ALSB/SPI\_SSピンをローレベルに駆動および保持することで、データ転送を開始します。ALSB/SPI\_SSがローレベルに駆動された後の最初のSCLK立上がりエッジで、0xD4と定義された書き込みコマンドがMOSIラインを経由してADV7344に書き込まれます。MOSIラインに書き込まれた2番目のバイトは、サブアドレスの先頭と解釈されます。MOSIライン上のデータは、MSBファーストで書き込まれ、SCLKの立上がりエッジでクロック駆動されます。

サブアドレスのオートインクリメント機能もあります。これにより、任意の有効なサブアドレスから始まる昇順のサブアドレス・シーケンスで、レジスタとの間でデータの読み込み／書き込みが可能になります。ユーザは、独自のサブアドレス・レジスタに対して、個別にアクセスできます。

書き込みデータ転送では、8ビットのデータバイトが、開始サブアドレス直後のMOSIライン上のADV7344にMSBファーストで書き込まれます。データバイトは、SCLKの立上がりエッジでADV7344に入力されます。すべてのデータバイトが書き込まれると、マスターは、ALSB/SPI\_SSピンをハイレベルに駆動および保持することによって転送を完了します。

読み出しだけ転送では、サブアドレスがMOSIライン上にクロック駆動された後で、ALSB/SPI\_SSピンが駆動され、少なくとも1クロック・サイクルの間はハイレベルに保持されます。その後、ALSB/SPI\_SSピンが駆動され、再びローレベルに保持されます。ALSB/SPI\_SSがローレベルに駆動された後の最初のSCLK立上がりエッジで、0xD5として定義された読み出しコマンドが、MOSIラインを経由してADV7344にMSBファーストで書き込まれます。続いて、8ビットのデータバイトが、ADV7344からMSBファーストでMISOライン上に読み込まれます。データバイトは、SCLKの立下がりエッジでADV7344から出力されます。すべてのデータバイトが読み込まれると、マスターは、ALSB/SPI\_SSピンをハイレベルに駆動および保持することによって転送を完了します。

## レジスタ・マップのアクセス

マイクロプロセッサは、読み出し専用／書き込み専用と規定されているレジスタを除き、ADV7344のすべてのレジスタに対しMPUポートを介して読み出し／書き込みができます。

次の読み出し／書き込み動作の対象となるレジスタは、サブアドレス・レジスタによって指定されます。MPUポートを介するすべての通信は、サブアドレス・レジスタへのアクセスで始まります。続いて、ターゲット・アドレスに対して読み出し／書き込み動作が実行されます。これにより、トランザクションが完了するまで、次のアドレスへのインクリメントが行われます。

### レジスタのプログラミング

表14～28に、各レジスタの機能を説明します。特に指定がない限り、すべてのレジスタに対して読み出し／書き込みができます。

### サブアドレス・レジスタ (SR7～SR0)

サブアドレス・レジスタは、8ビットの書き込み専用レジスタです。MPUポートにアクセスし、読み出し／書き込み動作を選択すると、サブアドレスが設定されます。動作の対象となるレジスタは、サブアドレス・レジスタによって指定されます。

表14. レジスタ0x00

| SR7 to SR0 | Register            | Bit Description                                                                                                                                                                                                          | Bit Number |   |   |   |   |   |   |   | Register Setting | Reset Value |

|------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---|---|---|---|---|---|---|------------------|-------------|

|            |                     |                                                                                                                                                                                                                          | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |                  |             |

| 0x00       | Power Mode Register | Sleep Mode. With this control enabled the current consumption is reduced to $\mu$ A level. All DACs and the internal PLL circuit are disabled. I <sup>2</sup> C registers can be read from and written to in sleep mode. |            |   |   |   |   |   |   | 0 | Sleep mode off.  | 0x12        |

|            |                     | PLL and Oversampling Control. This control allows the internal PLL circuit to be powered down and the oversampling to be switched off.                                                                                   |            |   |   |   |   |   |   | 1 | Sleep mode on.   |             |

|            |                     | DAC 3: Power on/off.                                                                                                                                                                                                     |            |   |   |   |   |   | 0 |   | PLL on.          |             |

|            |                     |                                                                                                                                                                                                                          |            |   |   |   |   |   | 1 |   | PLL off.         |             |

|            |                     | DAC 2: Power on/off.                                                                                                                                                                                                     |            |   |   |   | 0 |   |   |   | DAC 2 off.       |             |

|            |                     |                                                                                                                                                                                                                          |            |   |   | 1 |   |   |   |   | DAC 2 on.        |             |

|            |                     | DAC 1: Power on/off.                                                                                                                                                                                                     |            |   |   | 0 |   |   |   |   | DAC 1 off.       |             |

|            |                     |                                                                                                                                                                                                                          |            |   | 1 |   |   |   |   |   | DAC 1 on.        |             |

|            |                     | DAC 6: Power on/off.                                                                                                                                                                                                     |            |   | 0 |   |   |   |   |   | DAC 6 off.       |             |

|            |                     |                                                                                                                                                                                                                          |            |   | 1 |   |   |   |   |   | DAC 6 on.        |             |

|            |                     | DAC 5: Power on/off.                                                                                                                                                                                                     | 0          |   |   |   |   |   |   |   | DAC 5 off.       |             |

|            |                     |                                                                                                                                                                                                                          | 1          |   |   |   |   |   |   |   | DAC 5 on.        |             |

|            |                     | DAC 4: Power on/off.                                                                                                                                                                                                     | 0          |   |   |   |   |   |   |   | DAC 4 off.       |             |

|            |                     |                                                                                                                                                                                                                          | 1          |   |   |   |   |   |   |   | DAC 4 on.        |             |

# ADV7344

表15. レジスタ0x01~0x09

| SR7 to SR0 | Register             | Bit Description                                                                    | Bit Number |   |   |   |   |   |   |   | Register Setting                                                                     | Reset Value |

|------------|----------------------|------------------------------------------------------------------------------------|------------|---|---|---|---|---|---|---|--------------------------------------------------------------------------------------|-------------|

|            |                      |                                                                                    | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |                                                                                      |             |

| 0x01       | Mode Select Register | Reserved.                                                                          |            |   |   |   |   |   |   | 0 |                                                                                      | 0x00        |

|            |                      | DDR Clock Edge Alignment.<br>Note: Only used for ED <sup>1</sup> and HD DDR modes. |            |   |   |   |   | 0 | 0 |   | Chroma clocked in on rising clock edge; luma clocked in on falling clock edge.       |             |

|            |                      |                                                                                    |            |   |   |   | 0 | 1 |   |   | Reserved.                                                                            |             |

|            |                      |                                                                                    |            |   |   | 1 | 0 |   |   |   | Reserved.                                                                            |             |

|            |                      |                                                                                    |            |   |   | 1 | 1 |   |   |   | Luma clocked in on rising clock edge; chroma clocked in on falling clock edge.       |             |

|            |                      | Reserved.                                                                          |            |   |   |   | 0 |   |   |   |                                                                                      |             |

|            |                      | Input Mode.<br>Note: See Reg. 0x30, Bits[7:3] for ED/HD format selection.          | 0          | 0 | 0 |   |   |   |   |   | SD input only.                                                                       |             |

|            |                      |                                                                                    | 0          | 0 | 1 |   |   |   |   |   | ED/HD-SDR input only.                                                                |             |

| 0x02       | Mode Register 0      | 0                                                                                  | 1          | 0 |   |   |   |   |   |   | ED/HD-DDR input only.                                                                | 0x20        |

|            |                      | 0                                                                                  | 1          | 1 |   |   |   |   |   |   | SD and ED/HD-SDR.                                                                    |             |

|            |                      | 1                                                                                  | 0          | 0 |   |   |   |   |   |   | SD and ED/HD-DDR.                                                                    |             |

|            |                      | 1                                                                                  | 0          | 1 |   |   |   |   |   |   | Reserved.                                                                            |             |

|            |                      | 1                                                                                  | 1          | 0 |   |   |   |   |   |   | Reserved.                                                                            |             |

|            |                      | 1                                                                                  | 1          | 1 |   |   |   |   |   |   | ED only (at 54 MHz).                                                                 |             |

|            |                      | Y/C/S Bus Swap.                                                                    | 0          |   |   |   |   |   |   |   | Allows data to be applied to data ports in various configurations (SD feature only). |             |

|            |                      | 1                                                                                  |            |   |   |   |   |   |   |   |                                                                                      |             |

| 0x03       | ED/HD CSC Matrix 0   |                                                                                    |            |   |   |   |   |   | x | x | LSBs for GY.                                                                         | 0x03        |

| 0x04       | ED/HD CSC Matrix 1   |                                                                                    | x          | x | x | x | x | x | x | x | LSBs for RV.<br>LSBs for BU.<br>LSBs for GV.<br>LSBs for GU.                         | 0xF0        |

| 0x05       | ED/HD CSC Matrix 2   | x                                                                                  | x          | x | x | x | x | x | x | x | Bits[9:2] for GY.                                                                    | 0x4E        |

| 0x06       | ED/HD CSC Matrix 3   | x                                                                                  | x          | x | x | x | x | x | x | x | Bits[9:2] for GU.                                                                    | 0x0E        |

| 0x07       | ED/HD CSC Matrix 4   | x                                                                                  | x          | x | x | x | x | x | x | x | Bits[9:2] for GV.                                                                    | 0x24        |

| 0x08       | ED/HD CSC Matrix 5   | x                                                                                  | x          | x | x | x | x | x | x | x | Bits[9:2] for BU.                                                                    | 0x92        |

| 0x09       | ED/HD CSC Matrix 6   | x                                                                                  | x          | x | x | x | x | x | x | x | Bits[9:2] for RV.                                                                    | 0x7C        |

<sup>1</sup> ED=拡張解像度=525pと625p。

<sup>2</sup> サブアドレス0x31のビット2もイネーブルする必要があります (ED/HD)。サブアドレス0x84のビット6もイネーブルする必要があります (SD)。

表16. レジスタ0x0A~0x10

| SR7 to SR0 | Register                          | Bit Description                      | Bit Number |     |     |     |     |     |     |     | Register Setting            | Reset Value |

|------------|-----------------------------------|--------------------------------------|------------|-----|-----|-----|-----|-----|-----|-----|-----------------------------|-------------|

|            |                                   |                                      | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |                             |             |

| 0x0A       | DAC 4, DAC 5, DAC 6 Output Levels | Positive Gain to DAC Output Voltage. | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0%                          | 0x00        |

|            |                                   |                                      | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 1   | +0.018%                     |             |

|            |                                   |                                      | 0          | 0   | 0   | 0   | 0   | 0   | 1   | 0   | +0.036%                     |             |

|            |                                   |                                      | ...        | ... | ... | ... | ... | ... | ... | ... | ...                         |             |

|            |                                   |                                      | 0          | 0   | 1   | 1   | 1   | 1   | 1   | 1   | +7.382%                     |             |

|            |                                   |                                      | 0          | 1   | 0   | 0   | 0   | 0   | 0   | 0   | +7.5%                       |             |

|            |                                   | Negative Gain to DAC Output Voltage. | 1          | 1   | 0   | 0   | 0   | 0   | 0   | 0   | -7.5%                       | 0x00        |

|            |                                   |                                      | 1          | 1   | 0   | 0   | 0   | 0   | 0   | 1   | -7.382%                     |             |

|            |                                   |                                      | 1          | 0   | 0   | 0   | 0   | 0   | 1   | 0   | -7.364%                     |             |

|            |                                   |                                      | ...        | ... | ... | ... | ... | ... | ... | ... | ...                         |             |

|            |                                   |                                      | 1          | 1   | 1   | 1   | 1   | 1   | 1   | 1   | -0.018%                     |             |

| 0x0B       | DAC 1, DAC 2, DAC 3 Output Levels | Positive Gain to DAC Output Voltage. | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0%                          | 0x00        |

|            |                                   |                                      | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 1   | +0.018%                     |             |

|            |                                   |                                      | 0          | 0   | 0   | 0   | 0   | 0   | 1   | 0   | +0.036%                     |             |

|            |                                   |                                      | ...        | ... | ... | ... | ... | ... | ... | ... | ...                         |             |

|            |                                   |                                      | 0          | 0   | 1   | 1   | 1   | 1   | 1   | 1   | +7.382%                     |             |

|            |                                   |                                      | 0          | 1   | 0   | 0   | 0   | 0   | 0   | 0   | +7.5%                       |             |

|            |                                   | Negative Gain to DAC Output Voltage. | 1          | 1   | 0   | 0   | 0   | 0   | 0   | 0   | -7.5%                       | 0x00        |

|            |                                   |                                      | 1          | 1   | 0   | 0   | 0   | 0   | 0   | 1   | -7.382%                     |             |

|            |                                   |                                      | 1          | 0   | 0   | 0   | 0   | 0   | 1   | 0   | -7.364%                     |             |

|            |                                   |                                      | ...        | ... | ... | ... | ... | ... | ... | ... | ...                         |             |

|            |                                   |                                      | 1          | 1   | 1   | 1   | 1   | 1   | 1   | 1   | -0.018%                     |             |

| 0x0D       | DAC Power Mode                    | DAC 1 Low Power Enable.              |            |     |     |     |     |     |     | 0   | DAC 1 low power disabled    | 0x00        |

|            |                                   |                                      |            |     |     |     |     |     |     | 1   | DAC 1 low power enabled     |             |

|            |                                   | DAC 2 Low Power Enable.              |            |     |     |     |     |     | 0   |     | DAC 2 low power disabled    |             |

|            |                                   |                                      |            |     |     |     |     |     | 1   |     | DAC 2 low power enabled     |             |

|            |                                   | DAC 3 Low Power Enable.              |            |     |     |     |     | 0   |     |     | DAC 3 low power disabled    |             |

|            |                                   | Reserved.                            | 0          | 0   | 0   | 0   | 0   |     |     |     | DAC 3 low power enabled     |             |

| 0x10       | Cable Detection                   | DAC 1 Cable Detect (Read Only).      |            |     |     |     |     |     |     | 0   | Cable detected on DAC 1     | 0x00        |

|            |                                   |                                      |            |     |     |     |     |     |     | 1   | DAC 1 unconnected           |             |

|            |                                   | DAC 2 Cable Detect (Read Only).      |            |     |     |     |     |     | 0   |     | Cable detected on DAC 2     |             |

|            |                                   |                                      |            |     |     |     |     |     | 1   |     | DAC 2 unconnected           |             |

|            |                                   | Reserved.                            |            |     |     |     | 0   | 0   |     |     |                             |             |

|            |                                   | Unconnected DAC Auto Power-Down.     |            |     | 0   |     |     |     |     |     | DAC auto power-down disable |             |

|            |                                   |                                      |            |     | 1   |     |     |     |     |     | DAC auto power-down enable  |             |

|            |                                   | Reserved.                            | 0          | 0   | 0   |     |     |     |     |     |                             |             |

## ADV7344

表17. レジスタ0x12~0x17

| SR7 to<br>SR0 | Register                                      | Bit Description                                                                                                       | Bit Number |   |   |   |   |   |   |   | Register Setting                                                  | Reset<br>Value |

|---------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------|---|---|---|---|---|---|---|-------------------------------------------------------------------|----------------|

|               |                                               |                                                                                                                       | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |                                                                   |                |

| 0x12          | Pixel Port Readback (S Bus MSBs)              | S[9:2] Readback.                                                                                                      | x          | x | x | x | x | x | x | x | Read only                                                         | 0xXX           |

| 0x13          | Pixel Port Readback (Y Bus MSBs)              | Y[9:2] Readback.                                                                                                      | x          | x | x | x | x | x | x | x | Read only                                                         | 0xXX           |

| 0x14          | Pixel Port Readback (C Bus MSBs)              | C[9:2] Readback.                                                                                                      | x          | x | x | x | x | x | x | x | Read only                                                         | 0xXX           |

| 0x15          | Pixel Port Readback<br>(S, Y, and C Bus LSBs) | C[1:0] Readback.<br>Y[1:0] Readback.<br>S[1:0] Readback.<br>Reserved.                                                 | 0          | 0 | x | x | x | x | x | x | Read only                                                         | 0xXX           |

| 0x16          | Control Port Readback                         | <u>P_BLANK.</u><br><u>P_VSYNC.</u><br><u>P_HSYNC.</u><br><u>S_VSYNC.</u><br><u>S_HSYNC.</u><br>SFL/MISO.<br>Reserved. | 0          | 0 | x | x | x | x | x | x | Read only                                                         | 0xXX           |

| 0x17          | Software Reset                                | Reserved.                                                                                                             |            |   |   |   |   |   |   | 0 |                                                                   | 0x00           |

|               |                                               | Software Reset.                                                                                                       |            |   |   |   |   |   | 0 | 1 | Writing a 1 resets the<br>device; this is a self-<br>clearing bit |                |

|               |                                               | Reserved.                                                                                                             | 0          | 0 | 0 | 0 | 0 | 0 | 0 |   |                                                                   |                |

表18. レジスタ0x30

| SR7 to<br>SR0 | Register              | Bit Description                     | Bit Number  |   |   |   |   |   |   |   | Register Setting                                                     | Note            | Reset<br>Value  |

|---------------|-----------------------|-------------------------------------|-------------|---|---|---|---|---|---|---|----------------------------------------------------------------------|-----------------|-----------------|

|               |                       |                                     | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |                                                                      |                 |                 |

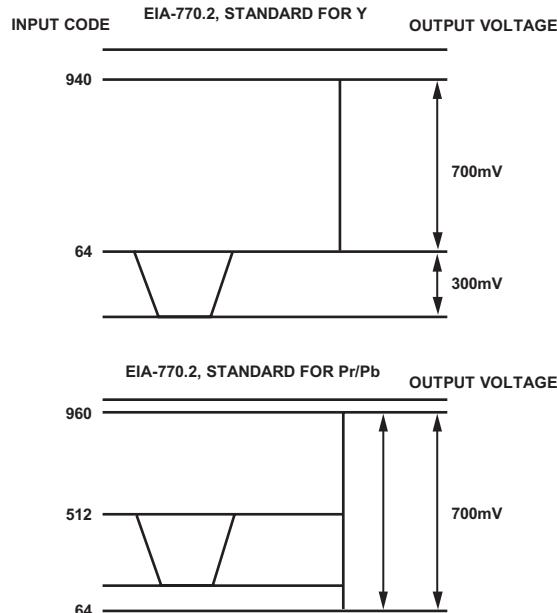

| 0x30          | ED/HD Mode Register 1 | ED/HD Output Standard.              |             |   |   |   |   |   | 0 | 0 | EIA770.2 output.                                                     | ED<br>HD        | 0x00            |

|               |                       |                                     |             |   |   |   |   |   | 0 | 1 | EIA770.3 output.                                                     |                 |                 |

|               |                       |                                     |             |   |   |   |   |   | 1 | 0 | EIA770.1 output.                                                     |                 |                 |

|               |                       |                                     |             |   |   |   |   |   | 1 | 1 | Output levels for full input range.                                  |                 |                 |

|               |                       | ED/HD Input Synchronization Format. |             |   |   |   |   | 0 |   |   | External <u>H</u> SYNC, <u>V</u> SYNC and field inputs. <sup>1</sup> |                 |                 |

|               |                       |                                     |             |   |   |   |   | 1 |   |   | Embedded EAV/SAV codes.                                              |                 |                 |

|               |                       | ED/HD Input Mode.                   | 0           | 0 | 0 | 0 | 0 | 0 |   |   | SMPTE 293M, ITU-BT.1358.                                             | 525p @ 59.94 Hz | 525p @ 59.94 Hz |

|               |                       |                                     | 0           | 0 | 0 | 0 | 0 | 1 |   |   | Nonstandard timing mode.                                             |                 |                 |

|               |                       |                                     | 0           | 0 | 0 | 1 | 0 |   |   |   | BTA-1004, ITU-BT.1362.                                               |                 |                 |

|               |                       |                                     | 0           | 0 | 0 | 1 | 1 |   |   |   | ITU-BT.1358.                                                         |                 |                 |

|               |                       |                                     | 0           | 0 | 1 | 0 | 0 |   |   |   | ITU-BT.1362.                                                         |                 |                 |

|               |                       |                                     | 0           | 0 | 1 | 0 | 1 |   |   |   | SMPTE 296M-1, SMPTE 274M-2.                                          |                 |                 |

|               |                       |                                     | 0           | 0 | 1 | 1 | 0 |   |   |   | SMPTE 296M-3.                                                        |                 |                 |

|               |                       |                                     | 0           | 0 | 1 | 1 | 1 |   |   |   | SMPTE 296M-4, SMPTE 274M-5.                                          |                 |                 |

|               |                       |                                     | 0           | 1 | 0 | 0 | 0 |   |   |   | SMPTE 296M-6.                                                        |                 |                 |

|               |                       |                                     | 0           | 1 | 0 | 0 | 1 |   |   |   | SMPTE 296M-7, SMPTE 296M-8.                                          |                 |                 |

|               |                       |                                     | 0           | 1 | 0 | 1 | 0 |   |   |   | SMPTE 240M.                                                          |                 |                 |

|               |                       |                                     | 0           | 1 | 0 | 1 | 1 |   |   |   | Reserved.                                                            |                 |                 |

|               |                       |                                     | 0           | 1 | 1 | 0 | 0 |   |   |   | Reserved.                                                            |                 |                 |

|               |                       |                                     | 0           | 1 | 1 | 0 | 1 |   |   |   | SMPTE 274M-4, SMPTE 274M-5.                                          |                 |                 |

|               |                       |                                     | 0           | 1 | 1 | 1 | 0 |   |   |   | SMPTE 274M-6.                                                        |                 |                 |

|               |                       |                                     | 0           | 1 | 1 | 1 | 1 |   |   |   | SMPTE 274M-7, SMPTE 274M-8.                                          |                 |                 |

|               |                       |                                     | 1           | 0 | 0 | 0 | 0 |   |   |   | SMPTE 274M-9.                                                        |                 |                 |

|               |                       |                                     | 1           | 0 | 0 | 0 | 1 |   |   |   | SMPTE 274M-10, SMPTE 274M-11.                                        |                 |                 |

|               |                       |                                     | 1           | 0 | 0 | 1 | 0 |   |   |   | ITU-R BT.709-5.                                                      |                 |                 |

|               |                       |                                     | 10011-11111 |   |   |   |   |   |   |   | Reserved.                                                            |                 |                 |

<sup>1</sup> 同期を制御するときは、サブアドレス0x34のビット6に応じて、HSYNC入力とVSYNC入力の組合せ、またはHSYNC入力とフィールド入力の組合せを使用します。

# ADV7344

表19. レジスタ0x31～0x33

| SR7 to<br>SR0 | Register              | Bit Description                                          | Bit Number                           |                       |                       |                       |                       |                       |                       |                       | Register Setting                                                                           | Reset<br>Value |

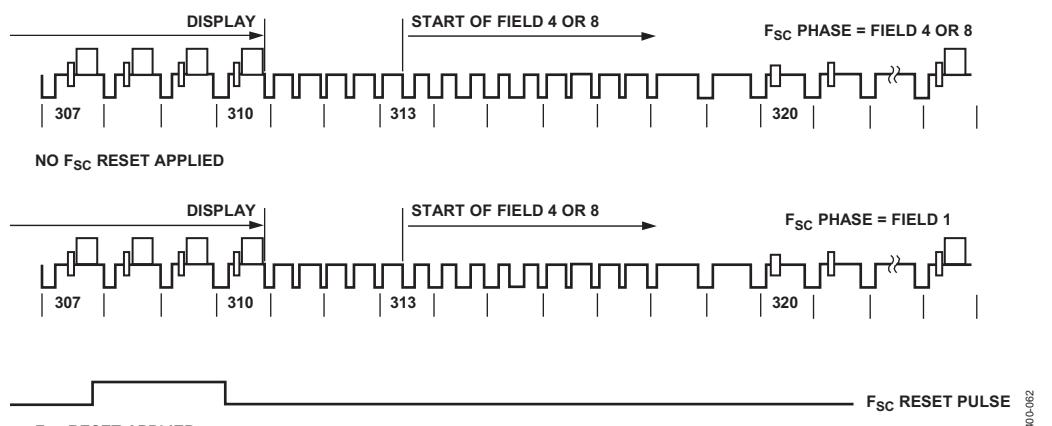

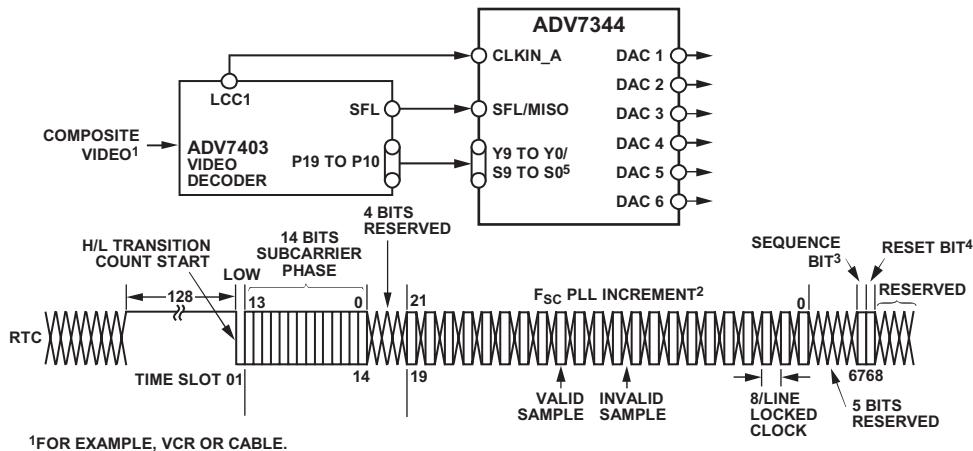

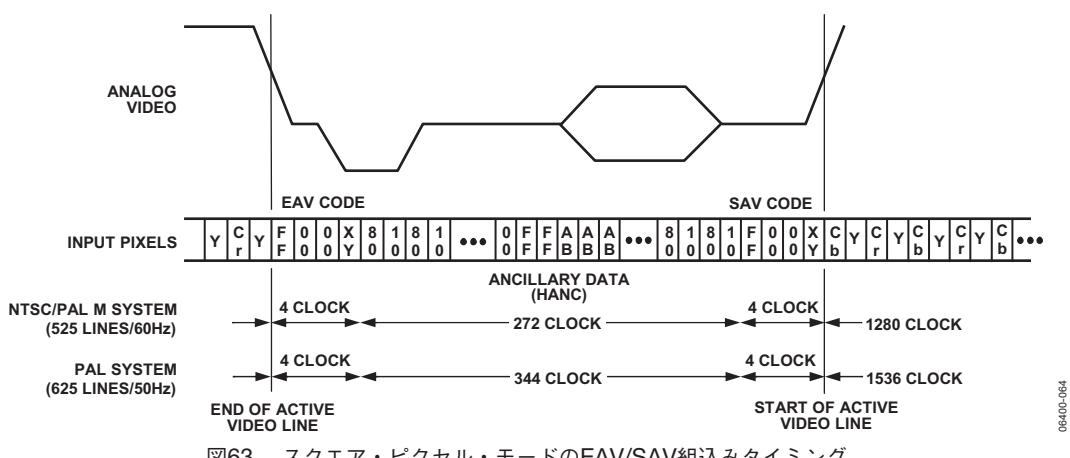

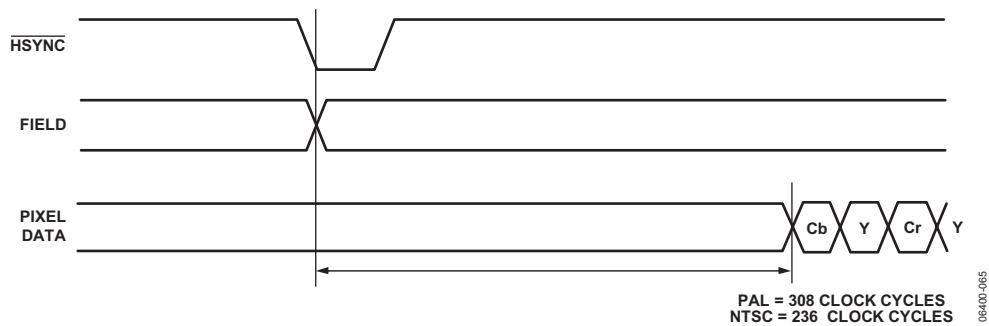

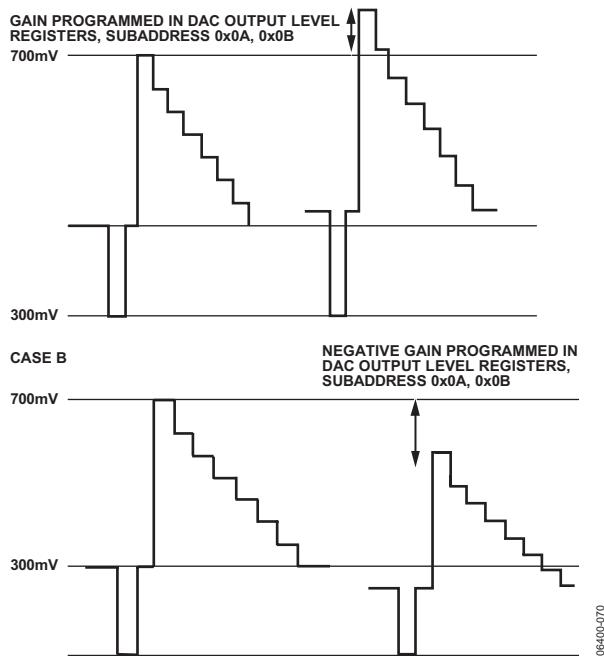

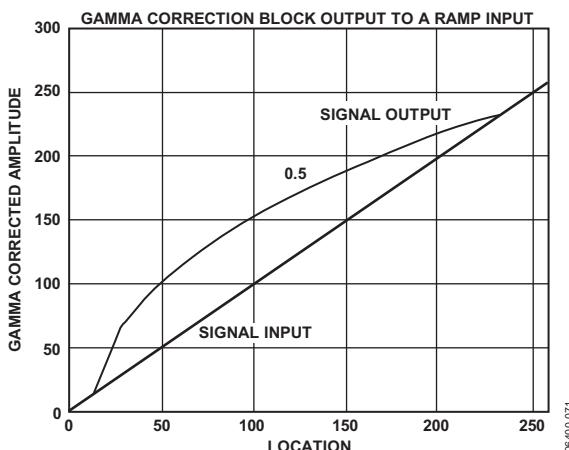

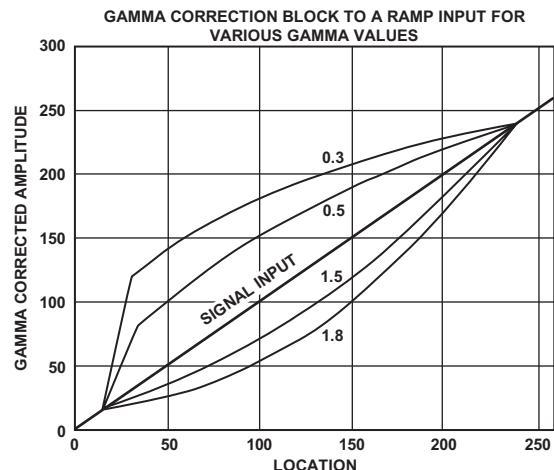

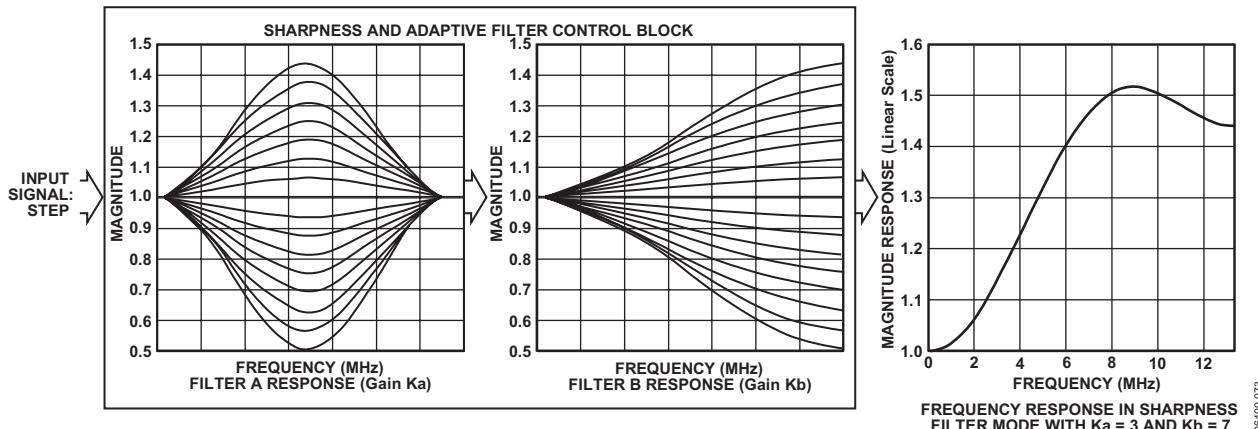

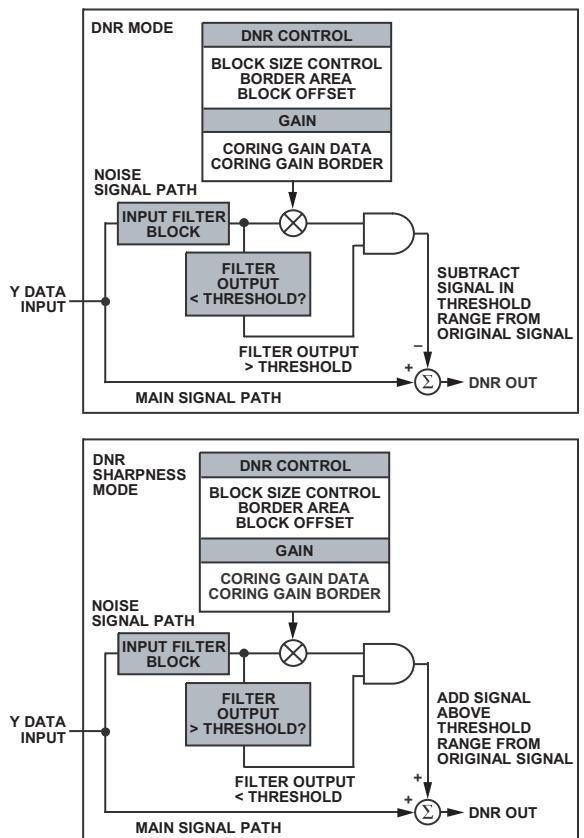

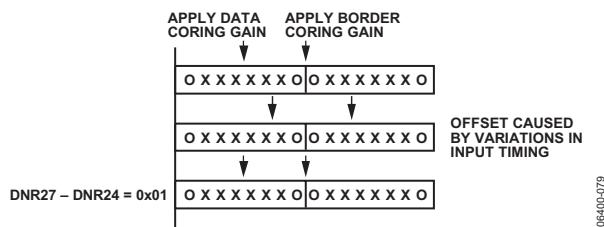

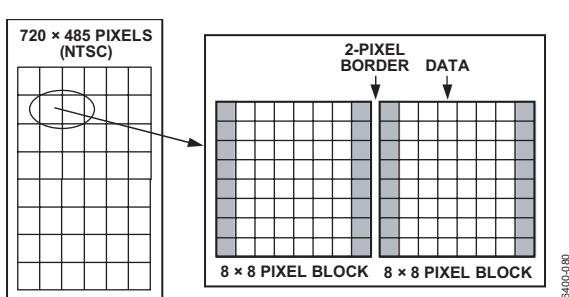

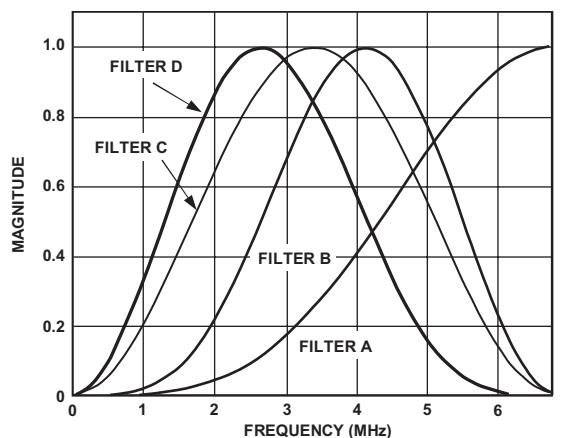

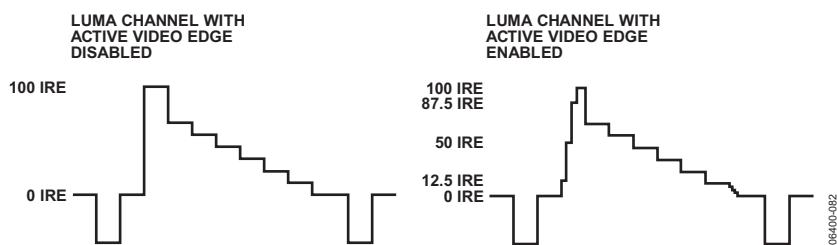

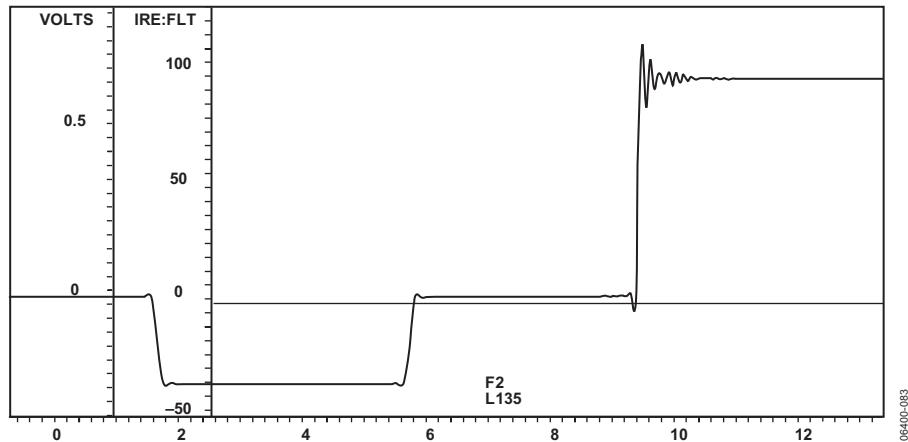

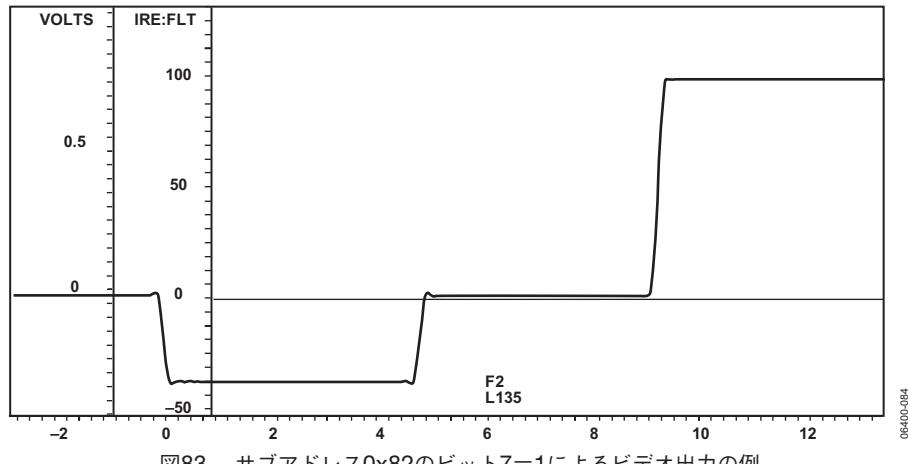

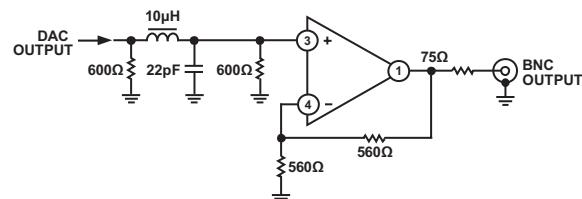

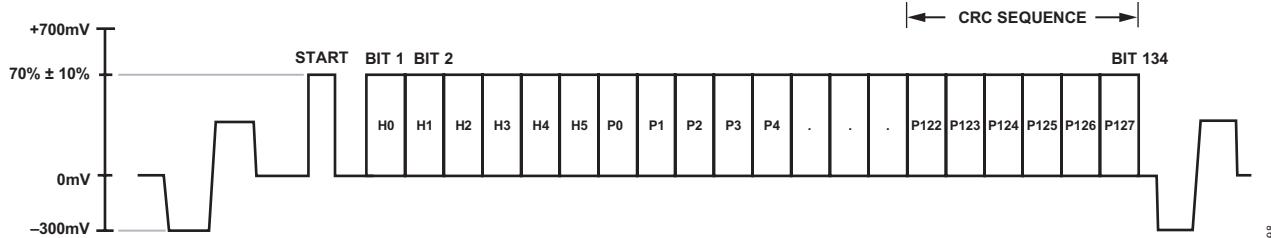

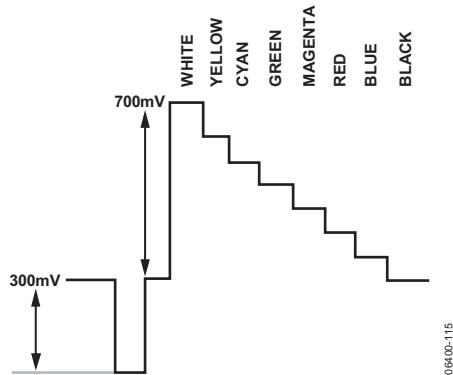

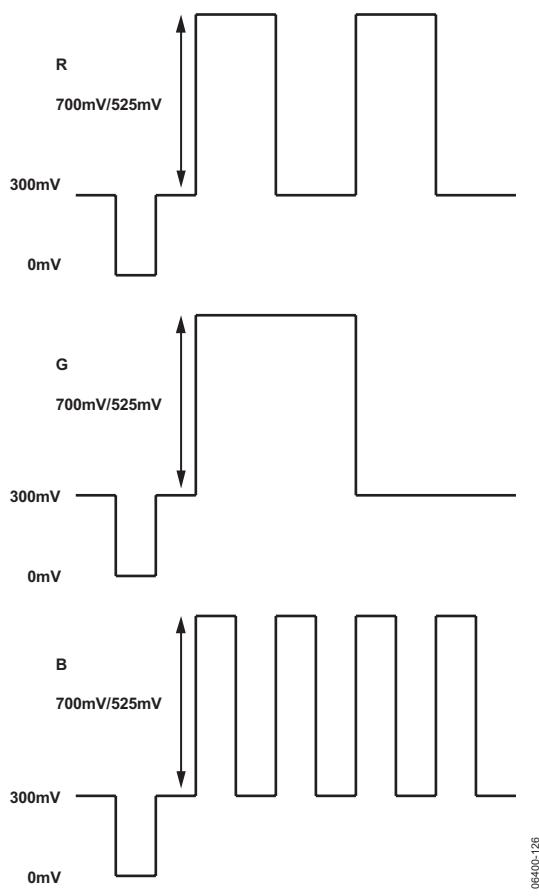

|---------------|-----------------------|----------------------------------------------------------|--------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|--------------------------------------------------------------------------------------------|----------------|