## データシート

# 測光用フロント・エンド

## ADPD105/ADPD107

### 特長

- 多機能の測光用フロント・エンド

- フル統合されたAFE、ADC、LED の各ドライバ、およびタイミング・コア

- フォトダイオードの光学フィルタを必要とせず、クラス最高の周辺光除去の性能を実現

- 8 mA ~ 370 mA の LED ドライバを 3 個搭載

- 2 個の光学入力

- 光学サンプルごとに、柔軟性が高い、複数の短い LED パルスを生成

- 20 ビットのバースト・アキュムレータを使用することで、サンプル期間あたり 20 ビットを実現

- 各サンプルに対応するアキュムレータをオンボード実装し、データ読み出しごとに最大 27 ビットを実現

- 低消費電力の動作

- SPI と I<sup>2</sup>C のどちらかのインターフェイスを採用し、1.8 V で動作するアナログ/デジタル・コア

- 0.122 Hz ~ 3820 Hz の範囲に対応する、柔軟性の高いサンプリング周波数

- FIFO データ処理

### アプリケーション

- ウェアラブル型の健康/フィットネス・モニタ

- SpO<sub>2</sub> のような臨床測定

- 工業用モニタリング

- 背景光の測定

### 概要

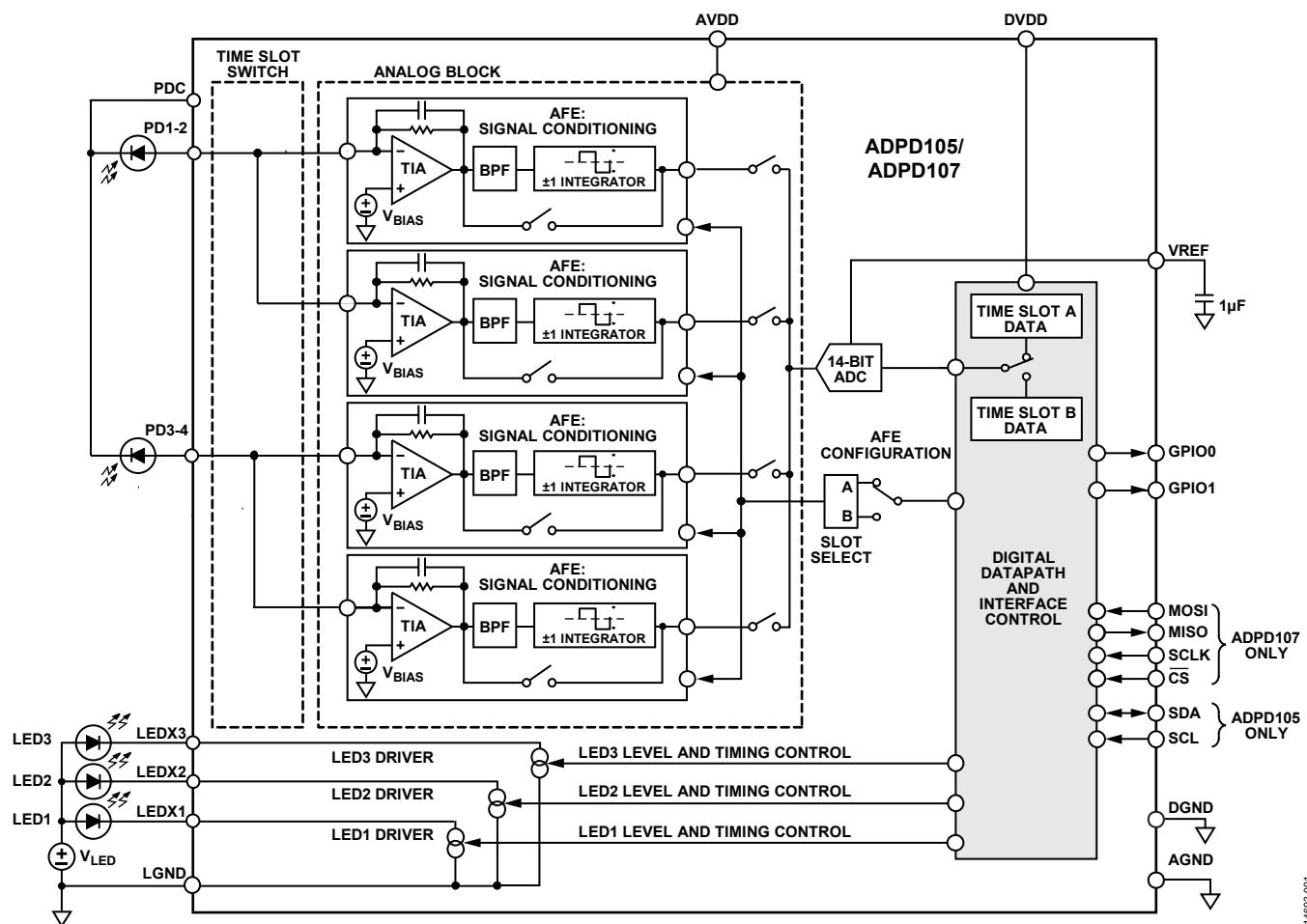

ADPD105/ADPD107 は、高効率の測光用フロント・エンドであり、どちらの製品も 14 ビットの A/D コンバータ (ADC) と 20 ビットのバースト・アキュムレータを内蔵しています。これらの製品は、柔軟性の高い LED (発光ダイオード) ドライバと連携して動作します。また、LED を励起して、対応する光学リターン信号を測定できるように設計されています。データ出力と機能構成は、ADPD105 では 1.8 V の I<sup>2</sup>C インターフェース、ADPD107 では SPI 経由で実施します。制御回路には、フレキシブルな LED 信号制御機能と同期検出機能が搭載されています。

アナログ・フロント・エンド (AFE) は、周辺光によって引き起こされる変調後の干渉に起因する信号のオフセットと劣化を除去する、クラス最高の機能を備えています。

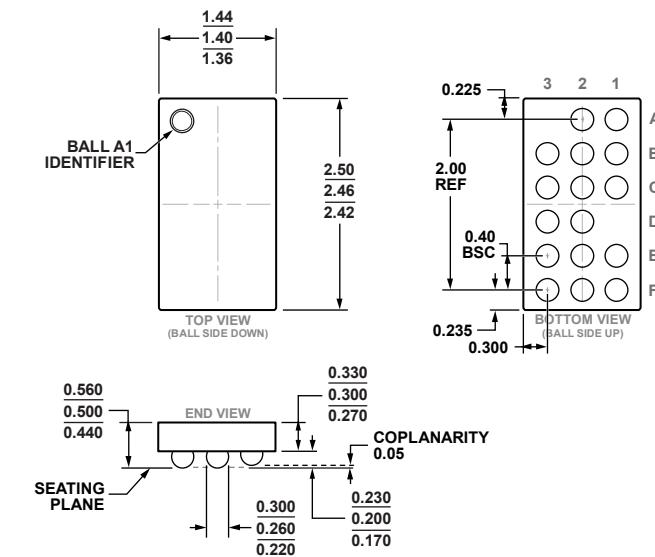

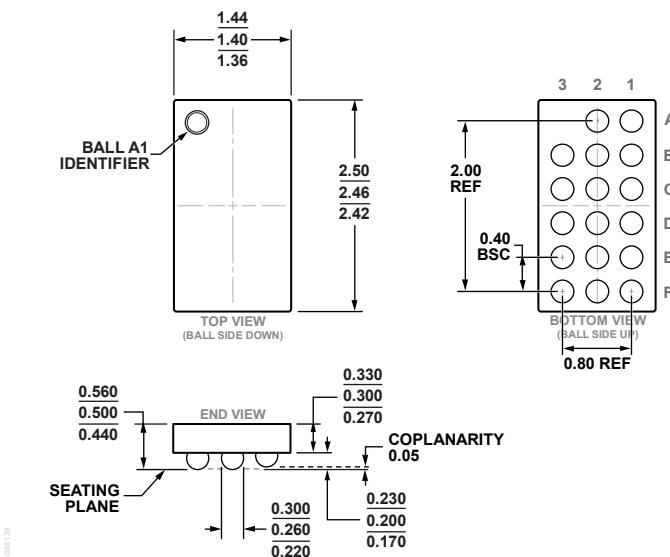

最適な性能を実現できるように、ADPD105/ADPD107 は、100 pF 未満の低静電容量フォトダイオードと結合してください。ADPD105/ADPD107 は、どの LED とでも併用できます。ADPD105 は、2.46 mm × 1.4 mm の WLCSP パッケージを採用しています。SPI 専用バージョンである ADPD107 は、2.46 mm × 1.4 mm の WLCSP パッケージで提供されています。

## 目次

|                                |    |                                   |    |

|--------------------------------|----|-----------------------------------|----|

| 特長                             | 1  | 代表的な接続図                           | 25 |

| アプリケーション                       | 1  | LED ドライバのピンと LED 電源電圧             | 26 |

| 概要                             | 1  | LED ドライバの動作                       | 26 |

| 改訂履歴                           | 2  | 平均電流の決定                           | 26 |

| 機能ブロック図                        | 3  | $C_{VLED}$ の決定                    | 26 |

| 仕様                             | 4  | LED のインダクタンスに関する考慮事項              | 27 |

| 温度と電力の仕様                       | 4  | 推奨されるスタートアップ・シーケンス                | 27 |

| 性能仕様                           | 5  | データの読み出し                          | 27 |

| アナログ仕様                         | 6  | クロックとタイミングの補正                     | 29 |

| デジタル仕様                         | 7  | GPIO0 と GPIO1 で利用できるオプションのタイミング信号 | 30 |

| タイミング仕様                        | 8  | 消費電流の計算                           | 32 |

| 絶対最大定格                         | 10 | ワットあたり SNR の最適化                   | 32 |

| 熱抵抗                            | 10 | 未使用のチャンネルとアンプの無効化による電力の最適化        | 33 |

| 推奨されるハンドル処理プロファイル              | 10 | TIA ADC モード                       | 34 |

| ESD に関する注意                     | 10 | デジタル積分モード                         | 36 |

| ピン配置およびピン機能の説明                 | 11 | パルス接続モード                          | 39 |

| 代表的な性能特性                       | 13 | レジスタの一覧                           | 41 |

| 動作原理                           | 15 | LED 制御レジスタ                        | 45 |

| はじめに                           | 15 | AFE グローバル設定レジスタ                   | 47 |

| デュアル・タイム・スロット動作                | 15 | システム・レジスタ                         | 52 |

| タイム・スロット・スイッチ                  | 16 | ADC レジスタ                          | 56 |

| 調整可能なサンプリング周波数                 | 17 | データ・レジスタ                          | 57 |

| ステート・マシンの動作                    | 18 | 必須のスタートアップ・ロード手順                  | 57 |

| 通常モードの動作とデータ・フロー               | 18 | 外形寸法                              | 58 |

| AFE の動作                        | 20 | オーダー・ガイド                          | 58 |

| AFE 積分オフセットの調整                 | 20 |                                   |    |

| I <sup>2</sup> C シリアル・インターフェース | 22 |                                   |    |

| SPI ポート                        | 23 |                                   |    |

## 改訂履歴

7/2016-Revision 0: Initial Version

## 機能ブロック図

図 1.

14893-001

## 仕様

## 温度と電力の仕様

表 1. 動作条件

| Parameter             | Test Conditions/Comments          | Min | Typ | Max  | Unit |

|-----------------------|-----------------------------------|-----|-----|------|------|

| TEMPERATURE RANGE     |                                   |     |     |      |      |

| Operating Range       |                                   | -40 |     | +85  | °C   |

| Storage Range         |                                   | -65 |     | +150 | °C   |

| POWER SUPPLY VOLTAGES |                                   |     |     |      |      |

| V <sub>DD</sub>       | Applied at the AVDD and DVDD pins | 1.7 | 1.8 | 1.9  | V    |

特に指定のない限り、AVDD = DVDD = 1.8 V、T<sub>A</sub> = 25 °C。

表 2. 消費電流

| Parameter                                                           | Symbol                              | Test Conditions/Comments                                                                  | Min | Typ | Max | Unit |

|---------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------|-----|-----|-----|------|

| POWER SUPPLY (V <sub>DD</sub> ) CURRENT                             |                                     |                                                                                           |     |     |     |      |

| V <sub>DD</sub> Supply Current <sup>1</sup>                         |                                     | SLOTx_LED_OFFSET = 25 μs; LED_PERIOD = 19 μs; LED peak current = 25 mA, 4 channels active |     |     |     |      |

| 1 Pulse                                                             |                                     | 100 Hz data rate; Time Slot A only                                                        | 106 |     |     | μA   |

|                                                                     |                                     | 100 Hz data rate; Time Slot B only                                                        | 94  |     |     | μA   |

|                                                                     |                                     | 100 Hz data rate; both Time Slot A and Time Slot B                                        | 151 |     |     | μA   |

| 10 Pulses                                                           |                                     | 100 Hz data rate; Time Slot A only                                                        | 258 |     |     | μA   |

|                                                                     |                                     | 100 Hz data rate; Time Slot B only                                                        | 246 |     |     | μA   |

|                                                                     |                                     | 100 Hz data rate; both Time Slot A and Time Slot B                                        | 455 |     |     | μA   |

| Peak V <sub>DD</sub> Supply Current (1.8 V)                         | I <sub>V<sub>DD</sub>_PEAK</sub>    |                                                                                           |     |     |     |      |

| 4-Channel Operation                                                 |                                     |                                                                                           | 9.3 |     |     | mA   |

| 1-Channel Operation                                                 |                                     |                                                                                           | 2.3 |     |     | mA   |

| Standby Mode Current                                                | I <sub>V<sub>DD</sub>_STANDBY</sub> |                                                                                           | 0.5 |     |     | μA   |

| V <sub>LEDA</sub> AND V <sub>LEDB</sub> SUPPLY CURRENT <sup>2</sup> |                                     |                                                                                           |     |     |     |      |

| Average Supply Current                                              |                                     |                                                                                           |     |     |     |      |

| V <sub>LEDA</sub> or V <sub>LEDB</sub>                              |                                     | Peak LED current = 100 mA; LED pulse width = 3 μs                                         |     |     |     |      |

| 1 Pulse                                                             |                                     | 50 Hz data rate                                                                           | 15  |     |     | μA   |

|                                                                     |                                     | 100 Hz data rate                                                                          | 30  |     |     | μA   |

|                                                                     |                                     | 200 Hz data rate                                                                          | 60  |     |     | μA   |

| 10 Pulses                                                           |                                     | 50 Hz data rate                                                                           | 150 |     |     | μA   |

|                                                                     |                                     | 100 Hz data rate                                                                          | 300 |     |     | μA   |

|                                                                     |                                     | 200 Hz data rate                                                                          | 600 |     |     | μA   |

<sup>1</sup> V<sub>DD</sub> は AVDD ピンと DVDD ピンに印加される電圧。

<sup>2</sup> LEDA または LEDB は、LED1、LED2、LED3 のいずれか。V<sub>LEDA</sub> または V<sub>LEDB</sub> は、V<sub>LED1</sub>、V<sub>LED2</sub>、V<sub>LED3</sub> のいずれか。

## 性能仕様

特に指定のない限り、AVDD = DVDD = 1.8 V、TA = 全動作温度範囲。

表 3.

| Parameter                            | Test Conditions/Comments                                                                    | Min   | Typ             | Max | Unit  |

|--------------------------------------|---------------------------------------------------------------------------------------------|-------|-----------------|-----|-------|

| DATA ACQUISITION                     |                                                                                             |       |                 |     |       |

| Resolution                           | Single pulse                                                                                |       | 14              |     | Bits  |

| Resolution/Sample                    | 64 to 255 pulses                                                                            |       | 20              |     | Bits  |

| Resolution/Data Read                 | 64 to 255 pulses and sample average = 128                                                   |       | 27              |     | Bits  |

| LED DRIVER                           |                                                                                             |       |                 |     |       |

| LED Current Slew Rate <sup>1</sup>   |                                                                                             |       |                 |     |       |

| Rise                                 | Slew rate control setting = 0; TA = 25°C; I <sub>LED</sub> = 70 mA                          |       | 240             |     | mA/μs |

|                                      | Slew rate control setting = 7; TA = 25°C; I <sub>LED</sub> = 70 mA                          |       | 1400            |     | mA/μs |

| Fall                                 | Slew rate control setting = 0, 1, 2; TA = 25°C; I <sub>LED</sub> = 70 mA                    |       | 3200            |     | mA/μs |

|                                      | Slew rate control setting = 6, 7; TA = 25°C; I <sub>LED</sub> = 70 mA                       |       | 4500            |     | mA/μs |

| LED Peak Current                     | LED pulse enabled                                                                           | 8     | 370             |     | mA    |

| Driver Compliance Voltage            | Voltage above ground required for LED driver operation                                      |       | 0.6             |     | V     |

| LED PERIOD                           |                                                                                             |       |                 |     |       |

| AFE width = 4 μs <sup>2</sup>        |                                                                                             | 19    |                 |     | μs    |

| AFE width = 3 μs                     |                                                                                             | 17    |                 |     | μs    |

| Sampling Frequency <sup>3</sup>      | Time Slot A only; normal mode; 1 pulse; SLOTA_LED_OFFSET = 23 μs; SLOTA_LED_PERIOD = 19 μs  | 0.122 | 3230            |     | Hz    |

|                                      | Time Slot B only; normal mode; 1 pulse; SLOTA_LED_OFFSET = 23 μs; SLOTA_LED_PERIOD = 19 μs  | 0.122 | 3820            |     | Hz    |

|                                      | Both time slots; normal mode; 1 pulse; SLOTA_LED_OFFSET = 23 μs; SLOTA_LED_PERIOD = 19 μs   | 0.122 | 1750            |     | Hz    |

|                                      | Time Slot A only; normal mode; 8 pulses; SLOTA_LED_OFFSET = 23 μs; SLOTA_LED_PERIOD = 19 μs | 0.122 | 2257            |     | Hz    |

|                                      | Time Slot B only; normal mode; 8 pulses; SLOTA_LED_OFFSET = 23 μs; SLOTA_LED_PERIOD = 19 μs | 0.122 | 2531            |     | Hz    |

|                                      | Both time slots; normal mode; 8 pulses; SLOTA_LED_OFFSET = 23 μs; SLOTA_LED_PERIOD = 19 μs  | 0.122 | 1193            |     | Hz    |

| CATHODE PIN (PDC) VOLTAGE            |                                                                                             |       |                 |     |       |

| During All Sampling Periods          | Register 0x54, Bit 7 = 0x0; Register 0x3C, Bit 9 = 1 <sup>4</sup>                           |       | 1.8             |     | V     |

|                                      | Register 0x54, Bit 7 = 0x0; Register 0x3C, Bit 9 = 0                                        |       | 1.3             |     | V     |

| During Slot A Sampling               | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[9:8] = 0x0 <sup>4</sup>                     |       | 1.8             |     | V     |

|                                      | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[9:8] = 0x1                                  |       | 1.3             |     | V     |

|                                      | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[9:8] = 0x2                                  |       | 1.55            |     | V     |

|                                      | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[9:8] = 0x3 <sup>5</sup>                     |       | 0               |     | V     |

| During Slot B Sampling               | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[11:10] = 0x0 <sup>4</sup>                   |       | 1.8             |     | V     |

|                                      | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[11:10] = 0x1                                |       | 1.3             |     | V     |

|                                      | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[11:10] = 0x2                                |       | 1.55            |     | V     |

|                                      | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[11:10] = 0x3 <sup>5</sup>                   |       | 0               |     | V     |

| During Sleep Periods                 | Register 0x54, Bit 7 = 0x0; Register 0x3C, Bit 9 = 1                                        |       | 1.8             |     | V     |

|                                      | Register 0x54, Bit 7 = 0x0; Register 0x3C, Bit 9 = 0                                        |       | 1.3             |     | V     |

|                                      | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[13:12] = 0x0                                |       | 1.8             |     | V     |

|                                      | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[13:12] = 0x1                                |       | 1.3             |     | V     |

|                                      | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[13:12] = 0x2                                |       | 1.55            |     | V     |

|                                      | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[13:12] = 0x3                                |       | 0               |     | V     |

| PHOTODIODE INPUT PINS/ ANODE VOLTAGE |                                                                                             |       |                 |     |       |

| During All Sampling Periods          |                                                                                             |       | 1.3             |     | V     |

| During Sleep Periods                 |                                                                                             |       | Cathode voltage |     | V     |

<sup>1</sup> これらの値に関して、LED のインダクタンスは無視できます。インダクタンスが大きくなると、実効スルーレートは低下します。

<sup>2</sup> 最小 LED 期間 = (2 × AFE 幅) + 5 μs。

<sup>3</sup> この仕様に示す最大値は、通常動作モードにおける ADC の内部サンプリング・レートです。構成によっては、I<sup>2</sup>C の読み出しレートが原因で出力データ・レートが制限を受ける可能性があります。

<sup>4</sup> このモードは、追加のノイズを誘発する可能性があり、絶対に必要な場合以外は推奨できません。1.8 V 設定では、アノード電圧に多くの差動電圧ノイズを含む V<sub>DD</sub> を使用します。アノードとカソード間の差動電圧によって、フォトダイオードの接合両端間を差動電流が流れます。この電流の大きさは C × dV/dt で表せます。

<sup>5</sup> フォトダイオードを使用する場合、この設定は推奨できません。これは、フォトダイオードに 1.3 V の順方向バイアスがかかるためです。

## アナログ仕様

特に指定のない限り、AVDD = DVDD = 1.8 V、TA = 全動作温度範囲。AFE オフセットの補償については、AFE の動作セクションで説明します。

表 4.

| Parameter                                                        | Test Conditions/Comments                                                               | Min   | Typ | Max | Unit    |

|------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------|-----|-----|---------|

| INPUT CAPACITANCE                                                |                                                                                        |       | 100 |     | pF      |

| PULSED SIGNAL CONVERSIONS, 3 $\mu$ s WIDE LED PULSE <sup>1</sup> | 4 $\mu$ s wide AFE integration; normal operation, Register 0x43/Register 0x45 = 0xADA5 |       |     |     |         |

| ADC Resolution <sup>2</sup>                                      | Transimpedance amplifier (TIA) feedback resistor                                       |       |     |     |         |

|                                                                  | 25 k $\Omega$                                                                          | 3.27  |     |     | nA/LSB  |

|                                                                  | 50 k $\Omega$                                                                          | 1.64  |     |     | nA/LSB  |

|                                                                  | 100 k $\Omega$                                                                         | 0.82  |     |     | nA/LSB  |

|                                                                  | 200 k $\Omega$                                                                         | 0.41  |     |     | nA/LSB  |

| ADC Saturation Level                                             | TIA feedback resistor                                                                  |       |     |     |         |

|                                                                  | 25 k $\Omega$                                                                          | 26.8  |     |     | $\mu$ A |

|                                                                  | 50 k $\Omega$                                                                          | 13.4  |     |     | $\mu$ A |

|                                                                  | 100 k $\Omega$                                                                         | 6.7   |     |     | $\mu$ A |

|                                                                  | 200 k $\Omega$                                                                         | 3.35  |     |     | $\mu$ A |

| Ambient Signal Headroom on Pulsed Signal                         | TIA feedback resistor                                                                  |       |     |     |         |

|                                                                  | 25 k $\Omega$                                                                          | 23.6  |     |     | $\mu$ A |

|                                                                  | 50 k $\Omega$                                                                          | 11.8  |     |     | $\mu$ A |

|                                                                  | 100 k $\Omega$                                                                         | 5.9   |     |     | $\mu$ A |

|                                                                  | 200 k $\Omega$                                                                         | 2.95  |     |     | $\mu$ A |

| PULSED SIGNAL CONVERSIONS, 2 $\mu$ s WIDE LED PULSE <sup>1</sup> | 3 $\mu$ s wide AFE integration; normal operation, Register 0x43/Register 0x45 = 0xADA5 |       |     |     |         |

| ADC Resolution <sup>2</sup>                                      | TIA feedback resistor                                                                  |       |     |     |         |

|                                                                  | 25 k $\Omega$                                                                          | 4.62  |     |     | nA/LSB  |

|                                                                  | 50 k $\Omega$                                                                          | 2.31  |     |     | nA/LSB  |

|                                                                  | 100 k $\Omega$                                                                         | 1.15  |     |     | nA/LSB  |

|                                                                  | 200 k $\Omega$                                                                         | 0.58  |     |     | nA/LSB  |

| ADC Saturation Level                                             | TIA feedback resistor                                                                  |       |     |     |         |

|                                                                  | 25 k $\Omega$                                                                          | 37.84 |     |     | $\mu$ A |

|                                                                  | 50 k $\Omega$                                                                          | 18.92 |     |     | $\mu$ A |

|                                                                  | 100 k $\Omega$                                                                         | 9.46  |     |     | $\mu$ A |

|                                                                  | 200 k $\Omega$                                                                         | 4.73  |     |     | $\mu$ A |

| Ambient Signal Headroom on Pulsed Signal                         | TIA feedback resistor                                                                  |       |     |     |         |

|                                                                  | 25 k $\Omega$                                                                          | 12.56 |     |     | $\mu$ A |

|                                                                  | 50 k $\Omega$                                                                          | 6.28  |     |     | $\mu$ A |

|                                                                  | 100 k $\Omega$                                                                         | 3.14  |     |     | $\mu$ A |

|                                                                  | 200 k $\Omega$                                                                         | 1.57  |     |     | $\mu$ A |

| FULL SIGNAL CONVERSIONS <sup>3</sup>                             |                                                                                        |       |     |     |         |

| TIA Saturation Level of Pulsed Signal and Ambient Level          | TIA feedback resistor                                                                  |       |     |     |         |

|                                                                  | 25 k $\Omega$                                                                          | 50.4  |     |     | $\mu$ A |

|                                                                  | 50 k $\Omega$                                                                          | 25.2  |     |     | $\mu$ A |

|                                                                  | 100 k $\Omega$                                                                         | 12.6  |     |     | $\mu$ A |

|                                                                  | 200 k $\Omega$                                                                         | 6.3   |     |     | $\mu$ A |

| Parameter                                 | Test Conditions/Comments                                                                                                 | Min | Typ  | Max | Unit    |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----|------|-----|---------|

| SYSTEM PERFORMANCE                        |                                                                                                                          |     |      |     |         |

| Total Output Noise Floor                  | Normal mode; per pulse; per channel; no LED; photodiode capacitance ( $C_{PD}$ ) = 70 pF<br>25 kΩ; referred to ADC input |     | 1.0  |     | LSB rms |

|                                           | 25 kΩ; referred to peak input signal for 2 μs LED pulse                                                                  |     | 4.6  |     | nA rms  |

|                                           | 25 kΩ; referred to peak input signal for 3 μs LED pulse                                                                  |     | 3.3  |     | nA rms  |

|                                           | 25 kΩ; saturation signal-to-noise ratio (SNR) per pulse per channel <sup>4</sup>                                         |     | 78.3 |     | dB      |

|                                           | 50 kΩ; referred to ADC input                                                                                             |     | 1.2  |     | LSB rms |

|                                           | 50 kΩ; referred to peak input signal for 2 μs LED pulse                                                                  |     | 2.8  |     | nA rms  |

|                                           | 50 kΩ; referred to peak input signal for 3 μs LED pulse                                                                  |     | 2.0  |     | nA rms  |

|                                           | 50 kΩ; saturation SNR per pulse per channel <sup>4</sup>                                                                 |     | 76.6 |     | dB      |

|                                           | 100 kΩ; referred to ADC input                                                                                            |     | 1.7  |     | LSB rms |

|                                           | 100 kΩ; referred to peak input signal for 2 μs LED pulse                                                                 |     | 1.9  |     | nA rms  |

|                                           | 100 kΩ; referred to peak input signal for 3 μs LED pulse                                                                 |     | 1.4  |     | nA rms  |

|                                           | 100 kΩ; saturation SNR per pulse per channel <sup>4</sup>                                                                |     | 73.6 |     | dB      |

|                                           | 200 kΩ; referred to ADC input                                                                                            |     | 2.75 |     | LSB rms |

|                                           | 200 kΩ; referred to peak input signal for 2 μs LED pulse                                                                 |     | 1.6  |     | nA rms  |

|                                           | 200 kΩ; referred to peak input signal for 3 μs LED pulse                                                                 |     | 1.1  |     | nA rms  |

|                                           | 200 kΩ; saturation SNR per pulse per channel <sup>4</sup>                                                                |     | 69.5 |     | dB      |

| DC Power Supply Rejection Ratio (DC PSRR) |                                                                                                                          |     | -37  |     | dB      |

<sup>1</sup> この飽和レベルはADCのみに適用されるので、パルス信号のみが含まれています。パルス以外の信号は、ADC段より前で除去されます。

<sup>2</sup> AFEの動作セクションに従ってAFEオフセットを正しく補正する場合、ADCの分解能はパルスごとに示されます。複数のパルスを使用する場合、パルス数で割ってください。

<sup>3</sup> この飽和レベルは信号バス全体に適用されるので、周辺信号とパルス信号の両方が含まれています。

<sup>4</sup> 飽和SNR値のノイズ項は、受信ノイズのみを表し、光子撮影ノイズやLED信号自体に重畳されるノイズは一切含まれていません。

## デジタル仕様

特に指定のない限り、DVDD = 1.7 V ~ 1.9 V。

表 5.

| Parameter                                                   | Symbol           | Test Conditions/Comments       | Min        | Typ        | Max | Unit |

|-------------------------------------------------------------|------------------|--------------------------------|------------|------------|-----|------|

| LOGIC INPUTS (GPIO <sub>x</sub> , SCL, SDA, SCLK, MOSI, CS) |                  |                                |            |            |     |      |

| Input Voltage Level                                         |                  |                                |            |            |     |      |

| High                                                        | V <sub>IH</sub>  |                                | 0.7 × DVDD | 3.6        |     | V    |

| Low                                                         | V <sub>IL</sub>  |                                |            | 0.3 × DVDD |     | V    |

| Input Current Level                                         |                  |                                |            |            |     |      |

| High                                                        | I <sub>IH</sub>  |                                | -10        |            | +10 | μA   |

| Low                                                         | I <sub>IL</sub>  |                                | -10        |            | +10 | μA   |

| Input Capacitance                                           | C <sub>IN</sub>  |                                |            | 10         |     | pF   |

| LOGIC OUTPUTS                                               |                  |                                |            |            |     |      |

| Output Voltage Level                                        |                  | GPIO <sub>x</sub> , MOSI       |            |            |     |      |

| High                                                        | V <sub>OH</sub>  | 2 mA high level output current | DVDD - 0.5 |            |     | V    |

| Low                                                         | V <sub>OL</sub>  | 2 mA low level output current  |            | 0.5        |     | V    |

| Output Voltage Level                                        |                  | SDA                            |            |            |     |      |

| Low                                                         | V <sub>OL1</sub> | 2 mA low level output current  |            | 0.2 × DVDD |     | V    |

| Output Current Level                                        |                  | SDA                            |            |            |     |      |

| Low                                                         | I <sub>OL</sub>  | V <sub>OL1</sub> = 0.6 V       | 6          |            |     | mA   |

## タイミング仕様

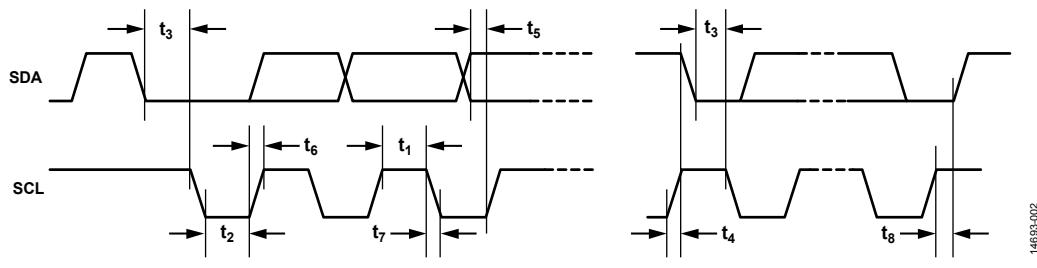

表 6. I<sup>2</sup>C タイミング仕様

| Parameter                          | Symbol         | Test Conditions/Comments | Min  | Typ  | Max | Unit |

|------------------------------------|----------------|--------------------------|------|------|-----|------|

| I <sup>2</sup> C PORT <sup>1</sup> |                | See Figure 2             |      |      |     |      |

| SCL                                |                |                          |      | 400  |     | kHz  |

| Frequency                          |                |                          | 600  |      |     | ns   |

| Minimum Pulse Width                |                |                          | 1300 |      |     | ns   |

| High                               | t <sub>1</sub> |                          |      |      |     |      |

| Low                                | t <sub>2</sub> |                          |      |      |     |      |

| Start Condition                    |                |                          |      |      |     |      |

| Hold Time                          | t <sub>3</sub> |                          | 600  |      |     | ns   |

| Setup Time                         | t <sub>4</sub> |                          | 600  |      |     | ns   |

| SDA Setup Time                     | t <sub>5</sub> |                          | 100  |      |     | ns   |

| SCL and SDA                        |                |                          |      | 1000 |     | ns   |

| Rise Time                          | t <sub>6</sub> |                          |      | 300  |     | ns   |

| Fall Time                          | t <sub>7</sub> |                          |      |      |     |      |

| Stop Condition                     |                |                          | 600  |      |     | ns   |

| Setup Time                         | t <sub>8</sub> |                          |      |      |     |      |

<sup>1</sup> 設計により性能を確保。

図 2. I<sup>2</sup>C タイミング図

14693-002

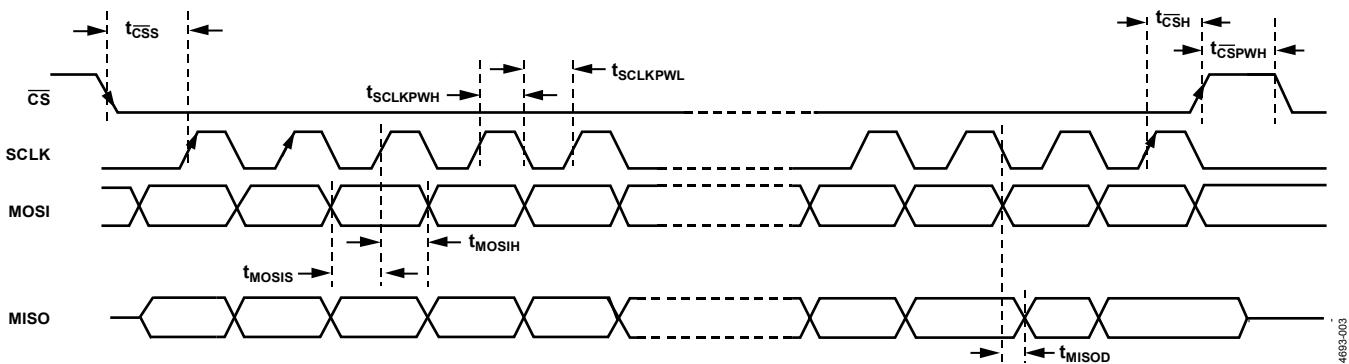

表 7. SPI タイミング仕様

| Parameter           | Symbol        | Test Conditions/Comments                       | Min | Typ | Max | Unit |

|---------------------|---------------|------------------------------------------------|-----|-----|-----|------|

| SPI PORT            |               |                                                |     |     |     |      |

| SCLK                |               |                                                |     |     |     |      |

| Frequency           | $f_{SCLK}$    |                                                |     |     | 10  | MHz  |

| Minimum Pulse Width |               |                                                |     |     |     |      |

| High                | $t_{SCLKPWH}$ |                                                | 20  |     |     | ns   |

| Low                 | $t_{SCLKPWL}$ |                                                | 20  |     |     | ns   |

| CS                  |               |                                                |     |     |     |      |

| Setup Time          | $t_{CSH}$     | CS setup to SCLK rising edge                   | 10  |     |     | ns   |

| Hold Time           | $t_{CSH}$     | CS hold from SCLK rising edge                  | 10  |     |     | ns   |

| Pulse Width High    | $t_{CSPWH}$   | CS pulse width high                            | 10  |     |     | ns   |

| MOSI                |               |                                                |     |     |     |      |

| Setup Time          | $t_{MOSIS}$   | MOSI setup to SCLK rising edge                 | 10  |     |     | ns   |

| Hold Time           | $t_{MOSIH}$   | MOSI hold from SCLK rising edge                | 10  |     |     | ns   |

| MISO Output Delay   | $t_{MISOD}$   | MISO valid output delay from SCLK falling edge |     | 20  |     | ns   |

図 3. SPI タイミング図

14693-003

## 絶対最大定格

表 8.

| Parameter                  | Rating           |

|----------------------------|------------------|

| AVDD to AGND               | -0.3 V to +2.2 V |

| DVDD to DGND               | -0.3 V to +2.2 V |

| GPIO0 to DGND              | -0.3 V to +2.2 V |

| GPIO1 to DGND              | -0.3 V to +2.2 V |

| LEDXx to LGND              | -0.3 V to +3.6 V |

| SCL to DGND                | -0.3 V to +3.9 V |

| SDA to DGND                | -0.3 V to +3.9 V |

| Junction Temperature       | 150°C            |

| ESD                        |                  |

| Human Body Model (HBM)     | 1500 V           |

| Charged Device Model (CDM) | 500 V            |

| Machine Model (MM)         | 100 V            |

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。製品を長時間にわたり絶対最大定格状態に置くと、製品の信頼性に影響を与えることがあります。

## 熱抵抗

熱性能は、プリント回路ボード (PCB) の設計と動作環境に直接関連があります。PCB の熱設計には細心の注意が必要です。

表 9. 热抵抗

| Package Type | $\theta_{JA}$ | Unit |

|--------------|---------------|------|

| CB-16-18     | 60            | °C/W |

| CB-17-1      | 60            | °C/W |

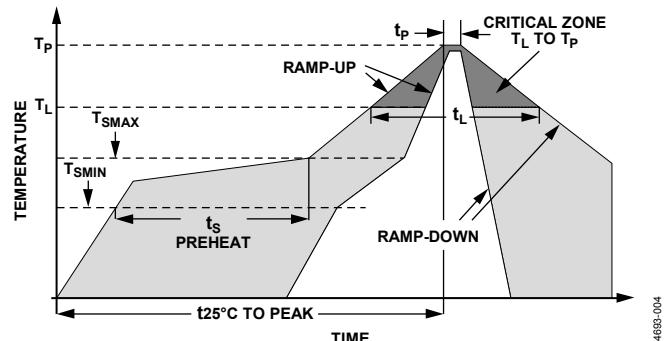

## 推奨されるハンダ処理プロファイル

図 4 と表 10 に、推奨されるハンダ処理プロファイルの詳細を示します。

図 4. 推奨されるハンダ処理プロファイル

表 10. 推奨されるハンダ処理プロファイル

| Profile Feature                                      | Condition (Pb-Free) |

|------------------------------------------------------|---------------------|

| Average Ramp Rate ( $T_L$ to $T_P$ )                 | 3°C/sec max         |

| Preheat                                              |                     |

| Minimum Temperature ( $T_{SMIN}$ )                   | 150°C               |

| Maximum Temperature ( $T_{SMAX}$ )                   | 200°C               |

| Time ( $T_{SMIN}$ to $T_{SMAX}$ ) ( $t_S$ )          | 60 sec to 180 sec   |

| $T_{SMAX}$ to $T_L$ Ramp-Up Rate                     | 3°C/sec maximum     |

| Time Maintained Above Liquidous Temperature          |                     |

| Liquidous Temperature ( $T_L$ )                      | 217°C               |

| Time ( $t_L$ )                                       | 60 sec to 150 sec   |

| Peak Temperature ( $T_P$ )                           | +260 (+0/-5)°C      |

| Time Within 5°C of Actual Peak Temperature ( $t_P$ ) | <30 sec             |

| Ramp-Down Rate                                       | 6°C/sec maximum     |

| Time from 25°C to Peak Temperature                   | 8 minutes maximum   |

## ESDに関する注意

ESD (静電放電) の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

## ピン配置およびピン機能の説明

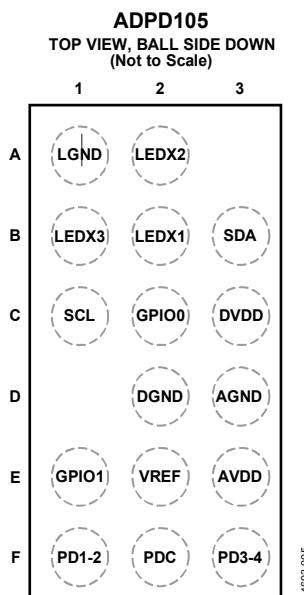

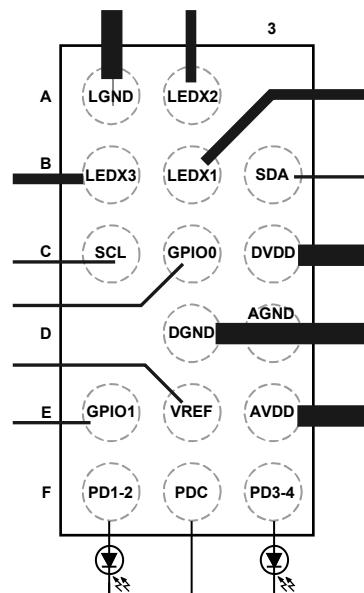

図 5. ADPD105 ピン配置

表 11. ADPD105 ピン機能の説明

| ピン番号 | 記号    | タイプ <sup>1</sup> | 説明                                                                              |

|------|-------|------------------|---------------------------------------------------------------------------------|

| A1   | LGND  | S                | LED ドライバのグラウンド。                                                                 |

| A2   | LEDX2 | AO               | LED ドライバ 2 の電流シンク。使用しない場合、このピンはフロート状態のままにしておきます。                                |

| B1   | LEDX3 | AO               | LED ドライバ 3 の電流シンク。使用しない場合、このピンはフロート状態のままにしておきます。                                |

| B2   | LEDX1 | AO               | LED ドライバ 1 の電流シンク。使用しない場合、このピンはフロート状態のままにしておきます。                                |

| B3   | SDA   | DIO              | I <sup>2</sup> C のデータ入出力 (I/O)。                                                 |

| C1   | SCL   | DI               | I <sup>2</sup> C クロック入力。                                                        |

| C2   | GPIO0 | DIO              | 汎用 I/O。このピンは、割り込みと各種クロック供給オプションに使用します。                                          |

| C3   | DVDD  | S                | 1.8 V デジタル電源。                                                                   |

| D2   | DGND  | S                | デジタル・グラウンド。                                                                     |

| D3   | AGND  | S                | アナログ・グラウンド。                                                                     |

| E1   | GPIO1 | DIO              | 汎用 I/O。このピンは、割り込みと各種クロック供給オプションに使用します。                                          |

| E2   | VREF  | REF              | 内部で生成される ADC 電圧リファレンス。AGND に接続した 1 $\mu$ F のコンデンサを使用して、このピンでバッファを有効にします。        |

| E3   | AVDD  | S                | 1.8 V アナログ電源。                                                                   |

| F1   | PD1-2 | AI               | フォトダイオード 1 (PD1) とフォトダイオード 2 (PD2) の入力で構成される結合電流。使用しない場合、このピンはフロート状態のままにしておきます。 |

| F2   | PDC   | AO               | フォトダイオードのコモン・カソード・バイアス。                                                         |

| F3   | PD3-4 | AI               | フォトダイオード 3 (PD3) とフォトダイオード 4 (PD4) の入力で構成される結合電流。使用しない場合、このピンはフロート状態のままにしておきます。 |

<sup>1</sup> S は電源、AO はアナログ出力、DIO はデジタル入出力、DI はデジタル入力、REF はリファレンス電圧、AI はアナログ入力、AO はアナログ出力を意味します。

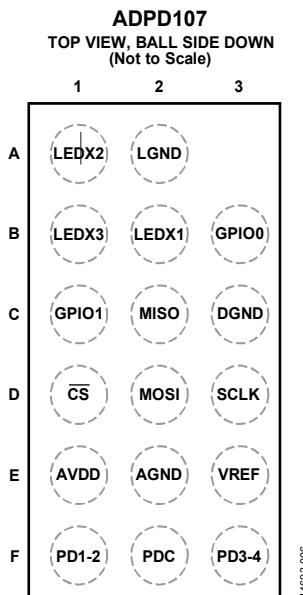

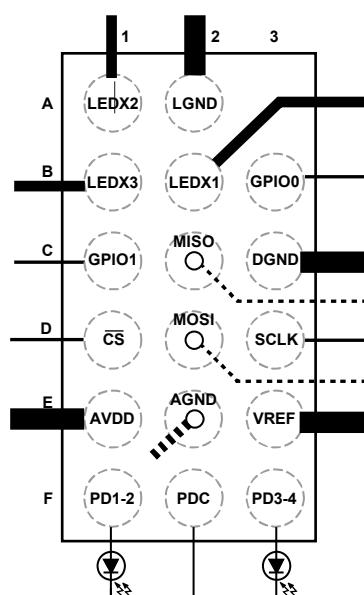

図 6. ADPD107 ピン配置

表 12. ADPD107 ピン機能の説明

| ピン番号 | 記号    | タイプ <sup>1</sup> | 説明                                                                              |

|------|-------|------------------|---------------------------------------------------------------------------------|

| A1   | LEDX2 | AO               | LED ドライバ 2 の電流シンク。使用しない場合、このピンはフロート状態のままにしておきます。                                |

| A2   | LGND  | S                | LED ドライバのグラウンド。                                                                 |

| B1   | LEDX3 | AO               | LED ドライバ 3 の電流シンク。使用しない場合、このピンはフロート状態のままにしておきます。                                |

| B2   | LEDX1 | AO               | LED ドライバ 1 の電流シンク。使用しない場合、このピンはフロート状態のままにしておきます。                                |

| B3   | GPIO0 | DIO              | 汎用 I/O。このピンは、割り込みと各種クロック供給オプションに使用します。                                          |

| C1   | GPIO1 | DIO              | 汎用 I/O。このピンは、割り込みと各種クロック供給オプションに使用します。                                          |

| C2   | MISO  | DO               | マスタ入力、スレーブ出力。                                                                   |

| C3   | DGND  | S                | デジタル・グラウンド。                                                                     |

| D1   | CS    | DI               | SPI チップ・セレクト。アクティブ・ロー。                                                          |

| D2   | MOSI  | DI               | マスタ出力、スレーブ入力。                                                                   |

| D3   | SCLK  | DI               | SPI クロック入力。                                                                     |

| E1   | AVDD  | S                | 1.8 V アナログ電源。                                                                   |

| E2   | AGND  | S                | アナログ・グラウンド。                                                                     |

| E3   | VREF  | REF              | 内部で生成される ADC 電圧リファレンス。AGND に接続した 1 $\mu$ F のコンデンサを使用して、このピンでバッファを有効にします。        |

| F1   | PD1-2 | AI               | フォトダイオード 1 (PD1) とフォトダイオード 2 (PD2) の入力で構成される結合電流。使用しない場合、このピンはフロート状態のままにしておきます。 |

| F2   | PDC   | AO               | フォトダイオードのコモン・カソード・バイアス。                                                         |

| F3   | PD3-4 | AI               | フォトダイオード 1 (PD3) とフォトダイオード 2 (PD4) の入力で構成される結合電流。使用しない場合、このピンはフロート状態のままにしておきます。 |

<sup>1</sup> AO はアナログ出力、S は電源、DIO はデジタル入出力、DO はデジタル出力、DI はデジタル入力、REF はリファレンス電圧、AI はアナログ入力を意味します。

## 代表的な性能特性

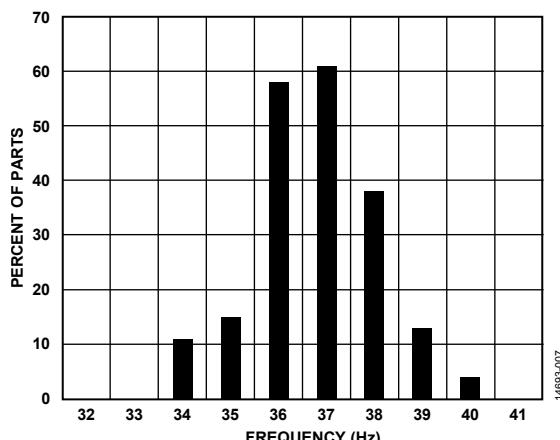

図 7. 32 kHz クロック周波数の分布（デフォルト設定、ユーザーによる補正の前: レジスタ 0x4B = 0x2612）

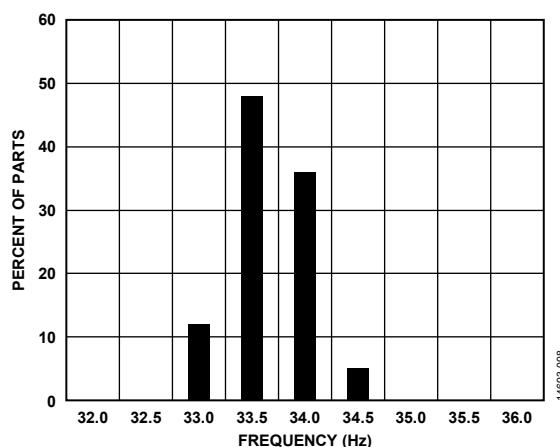

図 8. 32 MHz クロック周波数の分布（デフォルト設定、ユーザーによる補正の前: レジスタ 0x4D = 0x0098）

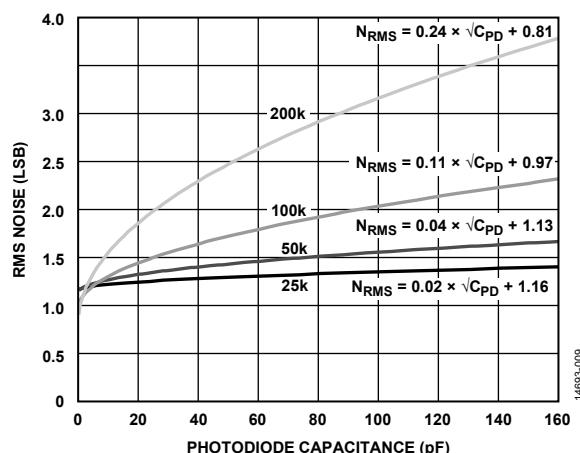

図 9. RMS ノイズとフォトダイオード静電容量の関係

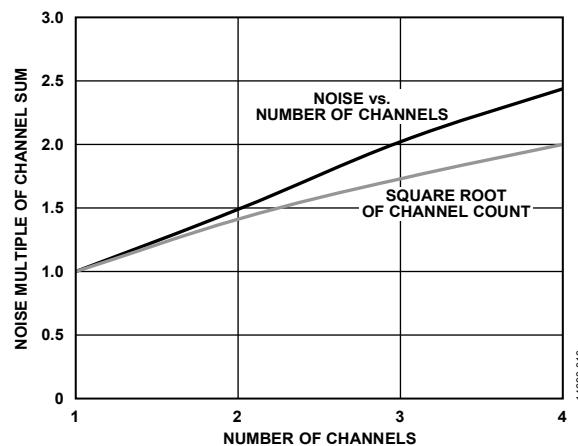

図 10. 複数チャンネルのノイズ合計とチャンネル数の関係

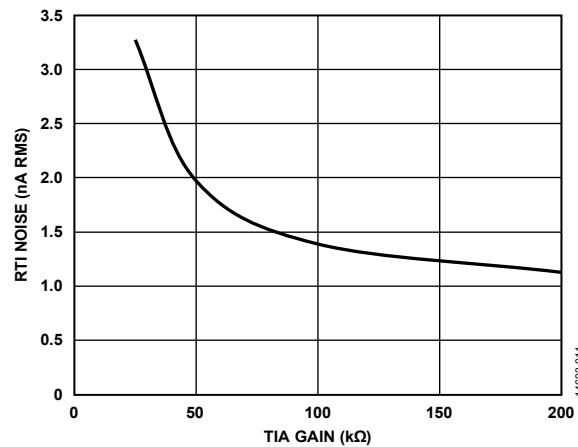

図 11. 入力に対する相対的 (RTI) ノイズと TIA ゲインの関係

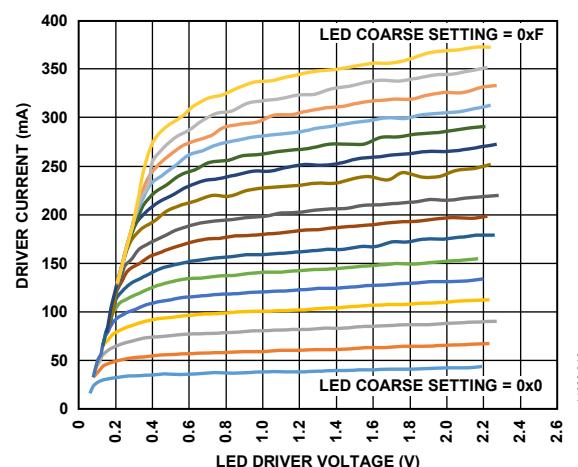

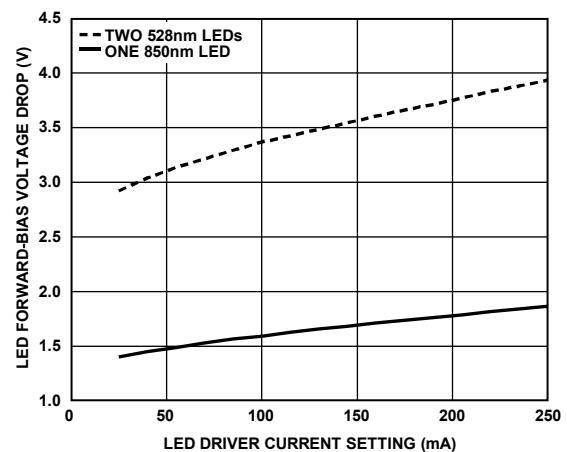

図 12. 各種のおおまかな設定における LED ドライバ電流と LED ドライバ電圧の関係

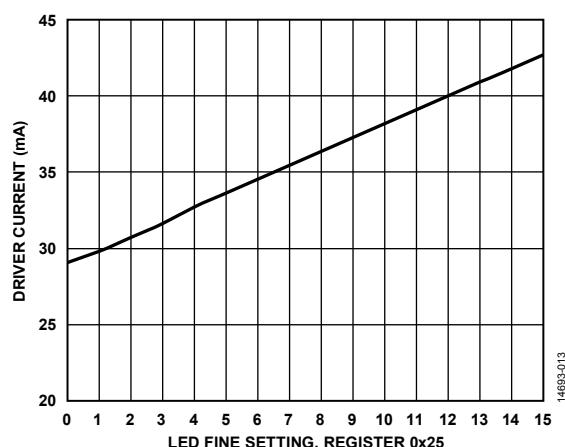

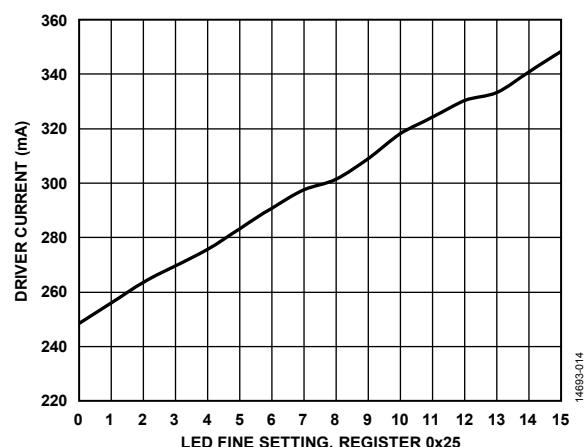

図 13. LED ドライバ電流と LED 微調整の関係

(おおまかな設定 = 0x0)

図 14. LED ドライバ電流と LED 微調整の関係

(おおまかな設定 = 0xF)

## 動作原理

### はじめに

ADPD105/ADPD107はフル機能の光学トランシーバとして動作します。最大3個のLEDを励起して、リターン信号を最大2つの個別の電流入力で測定します。コアを構成しているのは、ADCに結合された測光用フロント・エンド、デジタル・ブロック、および3個の独立したLEDドライバです。コア回路は複数のLEDを励起して、1~8つのフォトダイオード入力を通じてアナログ・ブロックに返された信号を測定し、個別のデータ保管場所に結果を保存します。4個の入力チャンネルを同時に駆動できるように、2個の入力を構成することもできます。レジスタから直接データを読み出すことも、FIFO経由でデータを読み出すこともできます。この高集積システムは、アナログ信号処理ブロック、デジタル信号処理ブロック、ADPD105のI<sup>2</sup>C通信インターフェースまたはADPD107のSPIポートの他、プログラマブルなパルス形式のLED電流源で構成されています。

LEDドライバは電流シンクなので、LED供給電圧やLEDの種類の影響を受けません。フォトダイオード(PD<sub>x</sub>)の入力は、接合容量が100 pF未満であるフォトダイオードに対応します。ADPD105/ADPD107は、比較的に小さなLED電力で高いSNRを達成すると同時に、測定対象の信号に対する周辺光の影響を大幅に低減するように設計されています。

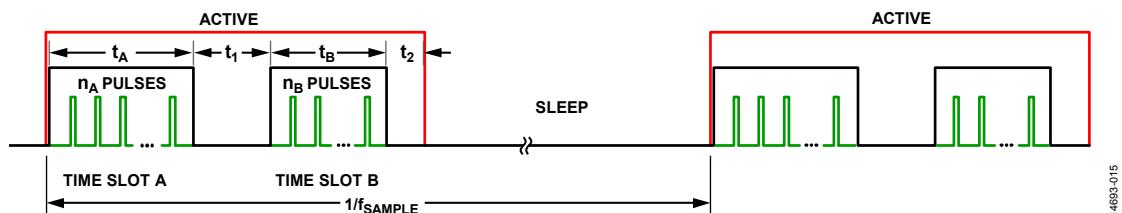

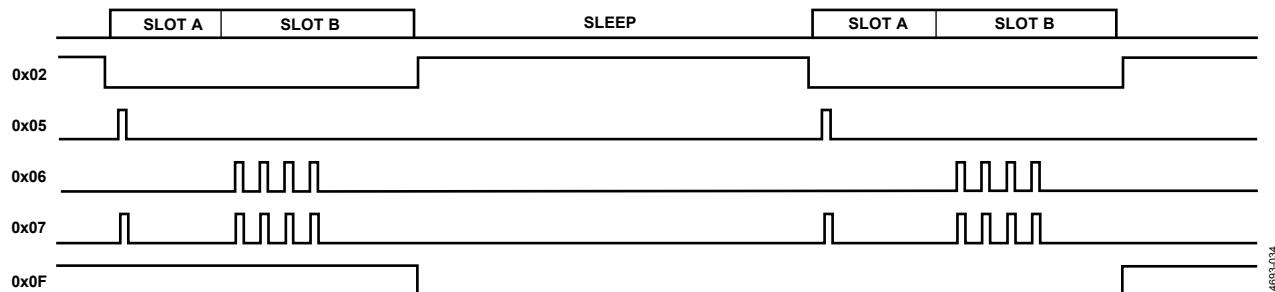

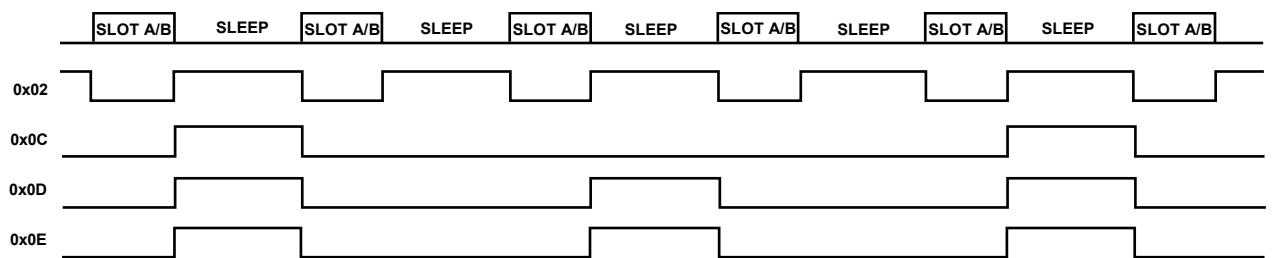

### デュアル・タイム・スロット動作

ADPD105/ADPD107は2つの独立したタイム・スロット(タイム・スロットAとタイム・スロットB)で動作します。これらのスロットは、順番に実行されます。LEDを励起してからデータをキャプチャし、処理を実行するまでの信号パス全体が、各タイム・スロット内で実行されます。各タイム・スロットには個別のデータパスがあります。これらのデータパスは、LEDドライバ、AFEのセットアップ、結果データごとに、独立した設定を使用します。タイム・スロットAとタイム・スロットBは、図15に示すように、サンプリング期間ごとに順番に動作します。

タイミング・パラメータは、次のように定義されます。

$$t_A (\mu s) = \text{SLOT}_A \text{ LED } \text{OFFSET} + n_A \times \text{SLOT}_A \text{ LED } \text{PERIOD}$$

ここで、 $n_A$ はタイム・スロットAに対応するパルス数(レジスタ0x31、ビット[15:8])です。

$$t_B (\mu s) = \text{SLOT}_B \text{ LED } \text{OFFSET} + n_B \times \text{SLOT}_B \text{ LED } \text{PERIOD}$$

ここで、 $n_B$ はタイム・スロットBに対応するパルス数(レジスタ0x36、ビット[15:8])です。

次の数式を使用してLEDの期間を計算します。

$$\text{LED\_PERIOD, minimum} = 2 \times \text{AFE\_WIDTH} + 11$$

$t_1$ と $t_2$ は固定値で、各スロットの計算時間に基づいています。どちらかのスロットが使用されていない場合、そのスロットに対応する時間は全体のアクティブ時間に寄与しません。表13に、これらのLED時間パラメータとサンプリング時間パラメータの値を定義します。

図15. タイム・スロットのタイミング図

表13. LEDタイミング・パラメータとサンプル・タイミング・パラメータ

| Parameter                                  | Register | Bits  | Test Conditions/Comments                                                    | Min | Typ | Max | Unit |

|--------------------------------------------|----------|-------|-----------------------------------------------------------------------------|-----|-----|-----|------|

| SLOT <sub>x</sub> _LED_OFFSET <sup>1</sup> | 0x30     | [7:0] | Delay from power-up to LEDA rising edge                                     | 23  | 63  |     | μs   |

| SLOT <sub>x</sub> _LED_OFFSET <sup>1</sup> | 0x35     | [7:0] | Delay from power-up to LEDB rising edge                                     | 23  | 63  |     | μs   |

| SLOT <sub>x</sub> _LED_PERIOD <sup>2</sup> | 0x31     | [7:0] | Time between LED pulses in Time Slot A; SLOT <sub>x</sub> _AFE_WIDTH = 4 μs | 19  | 63  |     | μs   |

| SLOT <sub>x</sub> _LED_PERIOD <sup>2</sup> | 0x36     | [7:0] | Time between LED pulses in Time Slot B; SLOT <sub>x</sub> _AFE_WIDTH = 4 μs | 19  | 63  |     | μs   |

| $t_1$                                      |          |       | Compute time for Time Slot A                                                |     | 68  |     | μs   |

| $t_2$                                      |          |       | Compute time for Time Slot B                                                |     | 20  |     | μs   |

| $t_{\text{SLEEP}}$                         |          |       | Sleep time between sample periods                                           | 222 |     |     | μs   |

<sup>1</sup> SLOT<sub>x</sub>\_LED\_OFFSETを規定の最小値より小さい値に設定すると、大きいフォトダイオードを使用する場合に、周辺光の除去に失敗する可能性があります。

<sup>2</sup> SLOT<sub>x</sub>\_LED\_PERIODを規定の最小値より小さい値に設定すると、無効なデータ・キャプチャが実行される可能性があります。

## タイム・スロット・スイッチ

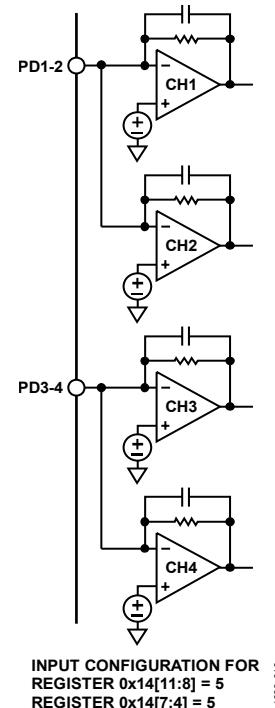

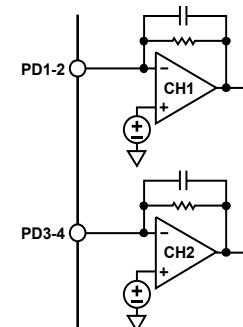

ADPD105/ADPD107 の 4 つのチャンネルに、最大 2 個のフォトダイオードを接続できます。フォトダイオードのアノードは、PD1-2 と PD3-4 の各入力ピンに接続されます。フォトダイオードのカソードは、カソード・ピン PDC に接続されます。レジスタ 0x14 の設定によって、2 つの異なる構成の一方がアノードに割り当てられます (図 16 と図 17 を参照)。

### レジスタ 0x14 による PD1 ~ PD4 の入力構成

図 16 に、PD の各入力を 2 つのチャンネルに接続する構成を示します。この構成は、大電流が流れるフォトダイオードで使用する、高ダイナミック・レンジのモードです。図 17 に、デバイスの各入力を単一のチャンネルに接続する構成を示します。このモードを使用すると、フォトダイオードを流れる電流が小さいと予想される場合に、飽和時の SNR を最大限に高めることができます。

タイム・スロット A とタイム・スロット B の期間中、どちらのフォトダイオード・グループを接続するか設定するには、スイッチを使用します。タイム・スロット・スイッチのレジスタについては、表 14 を参照してください。デバイスが正しく動作するように、未使用的入力はフロート状態のままにしておくことが重要です。フォトダイオードの入力は電流ですが、これらのピンは電圧を出力するともみなされます。これらの入力をいずれかの電圧に接続すると、アナログ・ブロックが飽和する可能性があります。

INPUT CONFIGURATION FOR

REGISTER 0x14[11:8] = 5

REGISTER 0x14[7:4] = 5

14693-016

図 16. PD1 ~ PD4 の接続

INPUT CONFIGURATION FOR

REGISTER 0x14[11:8] = 1

REGISTER 0x14[7:4] = 1

14693-017

図 17. 電流の合計 —2 個のフォトダイオードの出力を合計して、1 つの電流を生成

表 14. タイム・スロット・スイッチ (レジスタ 0x14)

| アドレス | ビット    | 名前           | 説明                                                                                                                                                                                                                                                     |

|------|--------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x14 | [11:8] | SLOTB_PD_SEL | 図 16 と図 17 に示すように、タイム・スロット B に接続するフォトダイオードを選択します。<br>0x0: タイム・スロット B の入力はフロート状態です。<br>0x1: タイム・スロット B の期間中、PD1-2 をチャンネル 1 に接続し、PD3-4 をチャンネル 2 に接続します。<br>0x5: タイム・スロット B の期間中、PD1-2 をチャンネル 1 とチャンネル 2 に接続し、PD3-4 をチャンネル 3 とチャンネル 4 に接続します。<br>その他: 予備。 |

|      | [7:4]  | SLOTA_PD_SEL | 図 16 と図 17 に示すように、タイム・スロット A に接続するフォトダイオードを選択します。<br>0x0: タイム・スロット A の入力はフロート状態です。<br>0x1: タイム・スロット A の期間中、PD1-2 をチャンネル 1 に接続し、PD3-4 をチャンネル 2 に接続します。<br>0x5: タイム・スロット A の期間中、PD1-2 をチャンネル 1 とチャンネル 2 に接続し、PD3-4 をチャンネル 3 とチャンネル 4 に接続します。<br>その他: 予備。 |

## 調整可能なサンプリング周波数

レジスタ 0x12 は、ADPD105/ADPD107 のサンプリング周波数を制御し、レジスタ 0x4B のビット [5:0] は高精度を実現するため、このクロックをさらに調節します。サンプリング周波数を制御するのは、内部の 32 kHz サンプル・レート・クロックです。また、このクロックは内部ステート・マシンの遷移も制御します。一部のサンプリング条件に対する最大サンプリング周波数を表 3 に示します。あらゆる条件に対応する最大サンプリング周波数は、次の式で決定されます。

$$f_{\text{SAMPLE, MAX}} = 1/(t_A + t_I + t_B + t_2 + t_{\text{SLEEP, MIN}})$$

ここで、 $t_{\text{SLEEP, MIN}}$  は、複数のサンプリングの間で必須の最小スリープ時間です。

特定のタイム・スロットを使用しない場合、そのタイム・スロットに属する要素は、計算に寄与しません。例えば、タイム・スロット A を使用しない場合、 $t_A$  と  $t_I$  はサンプリング期間に寄与しません。この場合、新しいサンプリング周波数は次のように計算されます。

$$f_{\text{SAMPLE, MAX}} = 1/(t_B + t_I + t_{\text{SLEEP, MIN}})$$

$t_A$ 、 $t_I$ 、 $t_B$ 、 $t_2$  の各定義については、デュアル・タイム・スロット動作セクションを参照してください。

## サンプリングの外部同期

ADPD105/ADPD107 では、サンプリング期間をトリガする外部同期信号を使用するオプションも利用できます。この外部サンプリング同期信号は、GPIO0 ピンまたは GPIO1 ピンのどちらかに供給できます。この機能を制御するのは、レジスタ 0x4F のビット [3:2] です。この機能を有効にすると、次のサンプリング期間の開始時期は選択した入力の立上がりエッジによって指定されます。トリガされた時点で、1つまたは2つのサンプリング・クロック (32 kHz) 分の遅延が発生した後、通常のスタートアップ・シーケンスが開始されます。このシーケンスは、通常のサンプリング・タイマ期間でトリガを行う場合と同じです。外部同期信号を有効にするには、次の手順を使用します。

1. レジスタ 0x10 に 0x1 を書き込み、プログラム・モードに移行します。

2. レジスタ 0x4F のビット [3:2] に適切な値を書き込み、GPIO0 と GPIO1 のどちらのピンが次のサンプリング・サイクルの開始時期を決定するか選択します。また、適切な入力バッファを有効にするため、GPIO0 ピンにはレジスタ 0x4F のビット 1 を使用し、GPIO1 ピンにはレジスタ 0x4F のビット 5 を使用します。

3. レジスタ 0x38 に 0x4000 を書き込みます。

4. レジスタ 0x10 に 0x2 を書き込み、サンプリング動作を開始します。

5. 選択したピンに対して、希望のレートで外部同期信号を印加します。サンプリングはこのレートで実施されます。通常のサンプリング動作の場合と同様、FIFO またはデータ・レジスタを使用してデータを読み出します。

この場合も、最大周波数に関する制約が適用されます。

## 32 kHz 外部クロックの供給

ADPD105/ADPD107 には、システムを同期するため、または 32 kHz の内部クロックよりも高精度のクロックが必要とされる状況で、32 kHz の外部クロックをデバイスに供給するオプションを利用できます。この 32 kHz の外部クロックは、GPIO1 ピンに供給します。32 kHz の外部クロックを有効にするには、スタートアップ時に次の手順に従います。

1. GPIO1 ピンを入力として使用する前に、GPIO1 を適切なロジック・レベルに設定するか、希望の 32 kHz クロックで駆動します。このピンをフロート状態にしたまま、有効にすることを避けてください。

2. レジスタ 0x4F のビット [6:5] に 01 を書き込み、入力として GPIO1 ピンを有効にします。

3. レジスタ 0x4B のビット [8:7] に 10 を書き込み、32 kHz 外部クロックを使用するようにデバイスを設定します。この設定により、32 kHz 内部クロックは無効になり、32 kHz 外部クロックが有効になります。

4. レジスタ 0x10 に 0x1 を書き込み、プログラム・モードに移行します。

5. デバイスがプログラム・モードにある間、他の制御レジスタに任意の順序で書き込みを行い、必要に応じてデバイスを設定します。

6. レジスタ 0x10 に 0x2 を書き込み、通常のサンプリング動作を開始します。

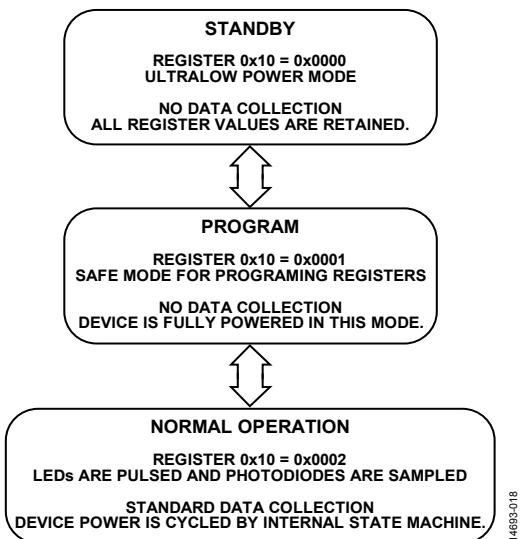

## ステート・マシンの動作

各タイム・スロットの期間内、ADPD105/ADPD107 はステート・マシンに従って動作します。ステート・マシンは、図 18 に示すシーケンスに従って動作します。

図 18. ステート・マシンの動作フローチャート

ADPD105/ADPD107 は、スタンバイ、プログラム、通常サンプリングという 3 つのモードのいずれかで動作します。

スタンバイ・モードは節電モードなので、データ収集は実施されません。このモードでは、すべてのレジスタ値が維持されます。デバイスをスタンバイ・モードに移行するには、レジスタ 0x10 のビット [1:0] に 0x0 を書き込みます。デバイスはパワーアップの時点での、スタンバイ・モードに移行します。

レジスタのプログラム（書き込み）を行う場合は、プログラム・モードを使用します。レジスタへの書き込みやモードの変更を実行す

る場合は、必ずプログラム・モードで ADPD105/ADPD107 の電源オン／オフの切り替えを実行してください。プログラム・モードではパワーサイクルが発生しないので、通常動作時よりもデバイスの消費電流量が大きくなる可能性があります。デバイスをプログラム・モードに移行するには、レジスタ 0x10 のビット [1:0] に 0x1 を書き込みます。

通常動作時、ADPD105/ADPD107 はパルス光を発振し、データを収集します。このモードにおける消費電力は、パルス数とデータ・レートに依存します。デバイスを通常サンプリング・モードに移行するには、レジスタ 0x10 のビット [1:0] に 0x2 を書き込みます。

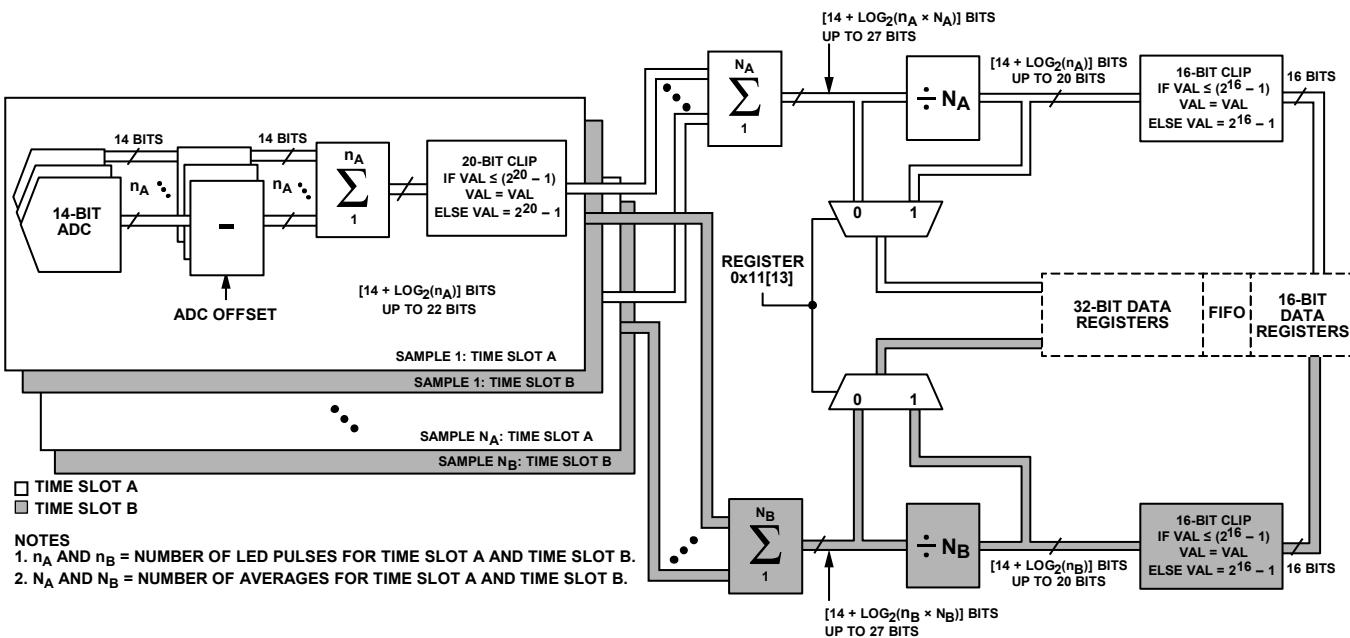

## 通常モードの動作とデータ・フロー

通常動作モードにおいて、ADPD105/ADPD107 は、ステート・マシンによって設定された特定のパターンに従います。図 19 の対応するデータ・フローに、このパターンを示します。このパターンは、次のとおりです。

1. LED パルスとサンプル。ADPD105/ADPD107 は、外部 LED にパルスを出力します。ADPD105/ADPD107 は、反射された光に対する 1 つ以上のフォトダイオードの応答を測定します。各データ・サンプルは、n 個のパルスに対応する結果の合計です。ここで、n は 1 ~ 255 の範囲で設定できます。

2. サンプル間の平均。必要な場合は、2 のべき乗を 2 ~ 128 個の範囲で使用し、ロジックで n 個のサンプルの平均を求めて、出力データとして生成できます。新しい出力データは、N 個のサンプルごとに出力レジスタ内に保存されます。

3. データ読み出し: ホスト・プロセッサは、データ・レジスタまたは FIFO から変換したデータを読み出します。

4. 反復。このシーケンスには、数種類の異なるループが存在しています。このため、異なる種類の平均を使用できるほか、両方のタイム・スロットを時間的に接続した状態に維持することもできます。

図 19. ADPD105/ADPD107 のデータパス

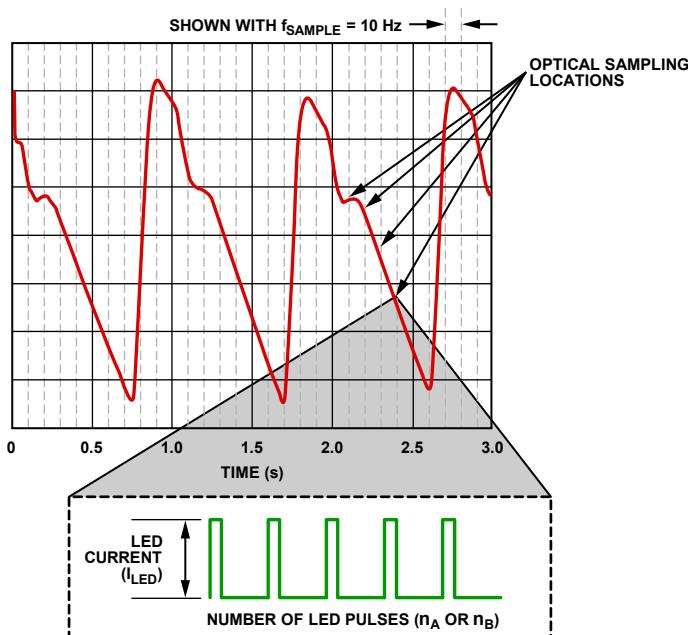

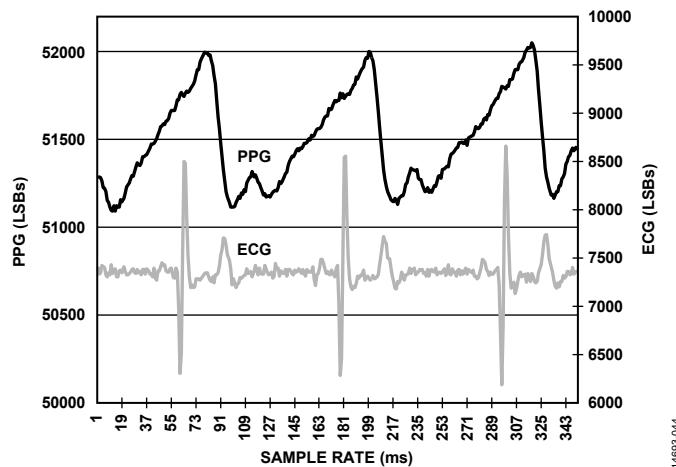

## LED パルスとサンプル

図 20 に示すように、各サンプリング期間に、選択した LED ドライバが一連の LED パルスを駆動します。パルスの振幅、持続期間、個数は、I<sup>2</sup>C インターフェース経由で設定します。各 LED パルスは単一の検出期間と重なるので、検出された値は、対応する LED パルスの応答として収集された総電荷を表します。周辺光など、LED パルスに対応しない電荷は除去されます。

各 LED パルスの後に、パルス形式の LED 信号に関するフォトダイオード出力がサンプリングされ、14 ビットの ADC によってデジタル値に変換されます。サンプリング期間内で実行される後続の各変換は、直前の結果に加算されます。各サンプリング期間内に、ADC から出力された最大 255 個のパルス値の合計を計算できます。サンプリング期間ごとに、20 ビットの最大範囲が存在します。

## 平均化

ADPD105/ADPD107 は、信号の分解能を向上させるため、サンプルの累積と平均化の機能を実行します。

サンプリング期間内に、AFE は最大 256 個の順次パルスの合計を計算できます。図 19 に示すように、AFE によって収集されたサンプルは、AFE の出力側で 20 ビットにクリップされます。複数のサンプリング期間にわたって平均化を実行することで、分解能を最大 27 ビットまで向上できます。N 個のサンプルで構成された累積データは、27 ビットの値として格納され、32 ビット出力レジスタを使用して直接読み出すか、または 32 ビット FIFO 構成を使用して読み出すことができます。

レジスタ 0x15 で設定した平均化機能を使用する場合、後続のパルスは 2 のべき乗単位で平均化されます。ユーザーは平均化に使用するサンプルの個数として、2、4、8 など、最大 128 までの値を選択できます。パルス・データは AFE によって、サンプリング周波数  $f_{\text{SAMPLE}}$  (レジスタ 0x12) で収集されますが、新しいデータ

は N 番目のサンプルごとに、 $f_{\text{SAMPLE}}/N$  のレートでレジスタに書き込まれます。この新しいデータは、以前の N 個のサンプルの合計によって構成されます。32 ビットの合計全体は、32 ビット・レジスタに書き込まれます。ただし、このデータを FIFO に送信する前に、N による除算が実施されます。この除算はビット深度を維持し、FIFO におけるクリッピングを防止します。

複数のサンプル平均化でこの手法を使用すると、ノイズを低減するだけでなく、16 ビットの分解能を維持することができます。パルス数レジスタの値を 8 以下に維持すれば、16 ビット幅を超過することはありません。つまり、レジスタ 0x15 を使用して後続のパルスを平均化する場合、16 ビット幅を超過せずに多くのパルスを累積することができます。この平均化により、ホスト・プロセッサが必要とする FIFO の読み出し回数を減らすことができます。

## データ読出し

ホスト・プロセッサが ADPD105/ADPD107 から出力されたデータを読み出す場合、ADPD105 では I<sup>2</sup>C プロトコルを介して読み出し、ADPD107 では SPI ポートを経由して読み出します。データ・レジスタまたは FIFO を通じてデータが読み出されます。N 個のサンプルごとに、新しいデータを利用できるようになります。ここで、N はユーザーが設定した平均化の係数です。タイム・スロット A とタイム・スロット B に対して、平均化の係数を個別に設定することもできます。これらの係数が等しい場合、両方のタイム・スロットで FIFO にデータを保存するように設定することもできます。2 つの平均化の係数が異なる場合、FIFO にデータを保存できるのはどちらか 1 つのタイム・スロットのみです。もう一方のタイム・スロットから得られたデータは、出力レジスタから読み出すことができます。

データ読出しの動作については、データの読出しセクションで詳細に説明します。

図 20. サンプルあたり 5 個のパルスを使用し、

10 Hz のデータ・レートでフォトプレチスモグラフィ

(PPG、光電式容積脈波記録法) 信号をサンプリングした例

14693-020

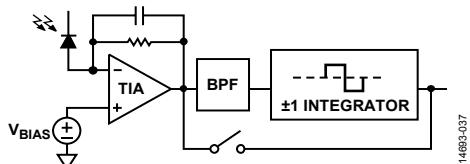

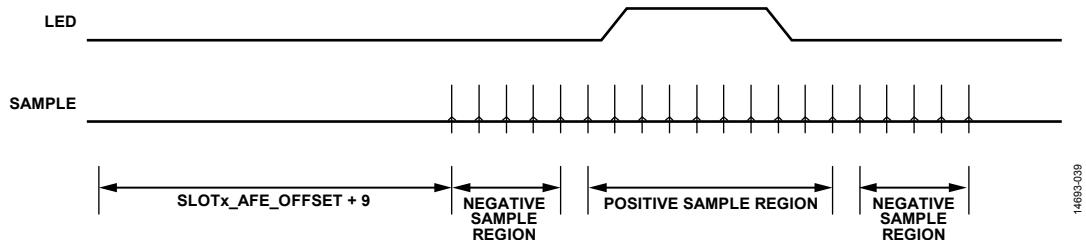

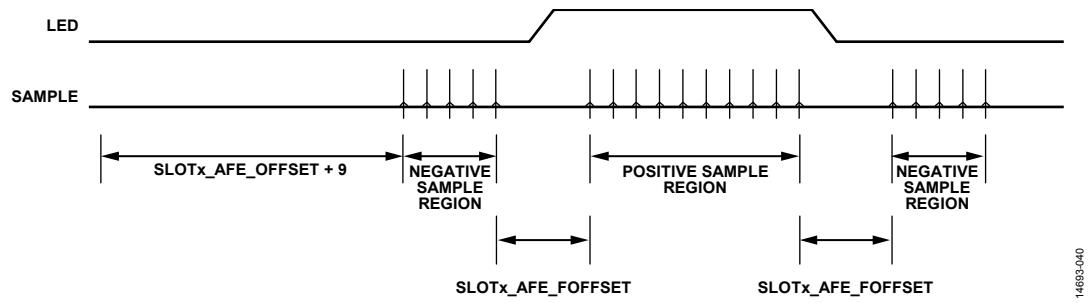

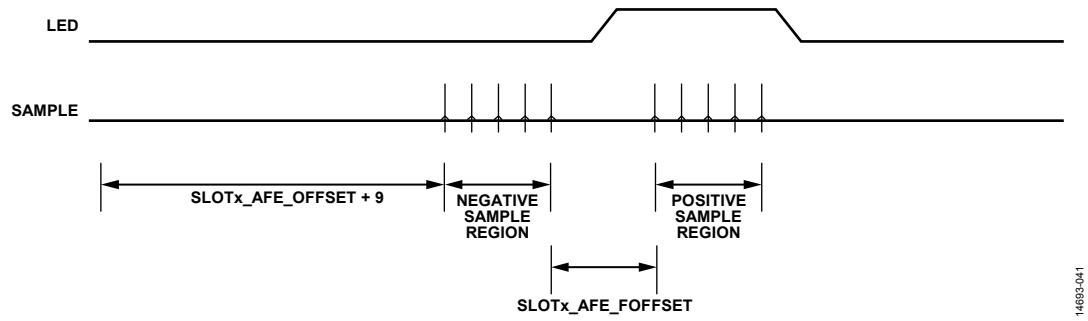

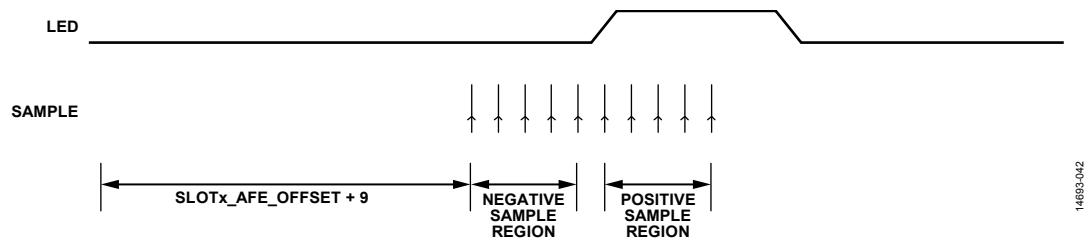

## AFE の動作

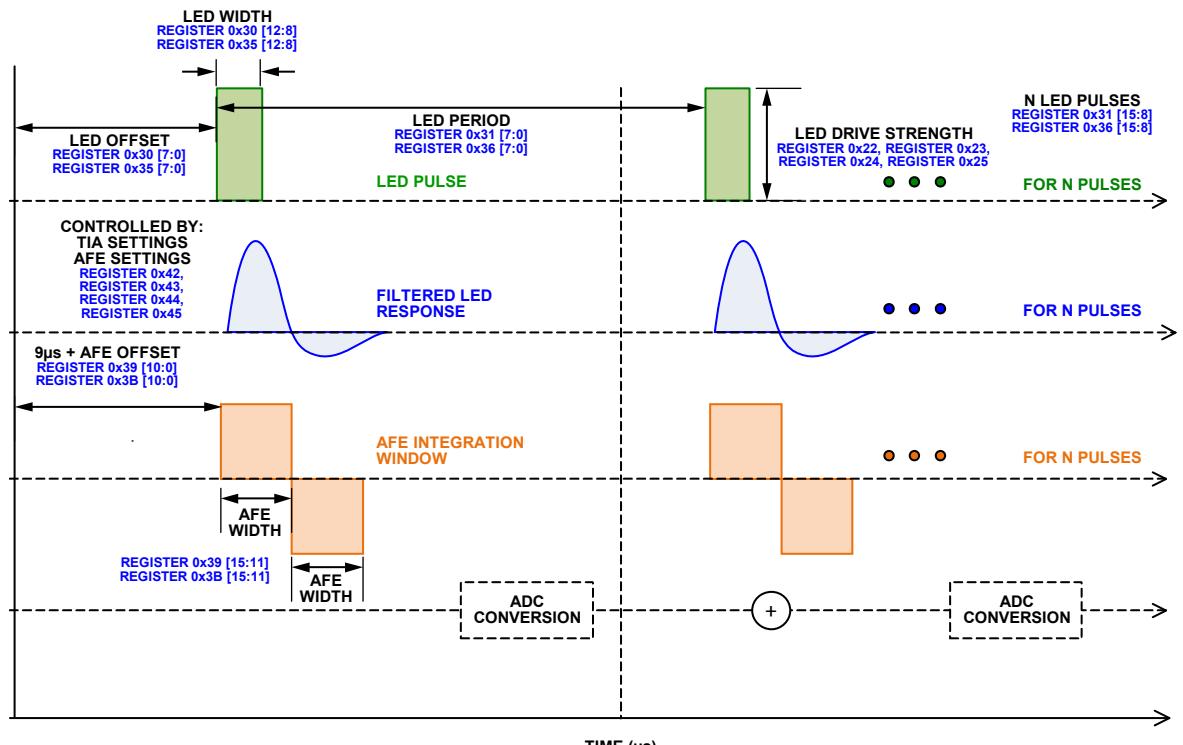

各パルス・バーストのタイミングは、ADPD105/ADPD107 の動作を最適化するうえで重要です。図 21 に、単一のタイム・スロットに対応するタイミング波形を示します。これは、AFE のアナログ・ブロックを介して LED パルス応答を伝搬するときの波形です。緑色で表示している最初のグラフは、LED パルスに対する理想的な出力を示します。青色のグラフに図示されているフィルタ処理後の LED 応答は、アナログ積分器の出力を示します。3番目のグラフに示すオレンジ色のグラフは、最適な場所に配置した積分ウインドウを示します。最適な値が得られるように設定した場合、フィルタ処理後の LED 応答の信号全体を積分できます。次に、バンドパス・フィルタ (BPF) の出力に対して AFE 積分ウインドウを適用し、得られた結果を ADC に送信して、N 個のパルスの合計を計算します。AFE ウィンドウのサイズや位置が正しくない場合、すべての受信信号を正しく報告することや、最適なシステム性能を達成することはできません。したがって、新

しいハードウェア設計を行うたび、または新しい LED パルス幅を設定するたびに、AFE の位置が正しいか検証することが重要です。

## AFE 積分オフセットの調整

AFE 積分幅は、LED パルス幅以上に設定する必要があります。ただし、AFE 積分幅をあまり広くしそると、出力ノイズが増大し、環境に起因する高周波成分を抑制する能力が低下します。このため、AFE 積分幅を小さい値に維持することが望まれます。しかし、AFE 積分幅が狭すぎると、LED 信号が減衰します。ほとんどのハードウェア設定では、AFE 積分幅を LED パルス幅より  $1 \mu\text{s}$  広くすると、最適な SNR を達成できます。LED パルス幅、LED オフセット、AFE 積分幅を設定した後、ADC オフセットを最適化することができます。積分ウインドウの最初のセグメントに出現する立下りエッジが、フィルタ処理後の LED 応答のゼロ交差に一致するように、AFE オフセットを手動で設定する必要があります。

図 21. AFE 動作の図

14693-021

### AFE 積分オフセットの開始ポイント

このオフセットの開始ポイントは、マイクロ秒 ( $\mu$ s) で表現し、積分ウィンドウの立下がりエッジが LED の立下がりエッジに一致するように設定します。

$$LED\_FALLING\_EDGE = SLOTx\_LED\_OFFSET + SLOTx\_LED\_WIDTH$$

および

$$AFE\_INTEGRATION\_FALLING\_EDGE = 9 + SLOTx\_AFE\_OFFSET + SLOTx\_AFE\_WIDTH$$

両方の立下がりエッジが互いに等しくなるように設定した場合、 $SLOTx\_AFE\_OFFSET$  を求めると、次の式が得られます。

$$AFE\_OFFSET\_STARTING\_POINT = SLOTx\_LED\_OFFSET + SLOTx\_LED\_WIDTH - 9 - SLOTx\_AFE\_WIDTH$$

開始ポイントよりも前の時点に AFE オフセットを設定すると、将来に積分を実行するのと同じ結果が得られます。AFE は、まだ発生していない LED パルスに対応する結果を積分することはできません。したがって、 $SLOTx\_AFE\_OFFSET$  の値を  $AFE\_OFFSET\_STARTING\_POINT$  の値よりも小さくするのは、誤った設定と言えます。このような結果は、TIA を流れる電流が想定とは逆方向であることを意味します。つまり、LED パルスを印加すると、TIA に電流が流入するのではなく、TIA から電流が流出することになります。

ほとんどの設定で、 $SLOTx\_AFE\_WIDTH$  が  $SLOTx\_LED\_WIDTH$  よりも 1  $\mu$ s 広いことが原因で、 $AFE\_OFFSET\_STARTING\_POINT$  の値は、 $SLOTx\_LED\_OFFSET$  の値よりも 10  $\mu$ s 小さくなります。この値が  $SLOTx\_LED\_OFFSET - 10$  よりも小さい場合は問題があります。最適な AFE オフセットは、 $AFE\_OFFSET\_STARTING\_POINT$  の値よりも後の時点で発生します。バンド・パス・フィルタへの応答、LED への応答、フォトダイオードへの応答は、いずれもある程度の遅延を加算することになります。一般的に、部品の選択、ボードのレイアウト、 $SLOTx\_LED\_OFFSET$ 、および  $SLOTx\_LED\_WIDTH$  は、 $SLOTx\_AFE\_OFFSET$  の値に変化をもたらす可能性のある変数です。特定の設計を確定した後、 $SLOTx\_AFE\_OFFSET$  の値は固定されるので、さらに最適化を実行する必要はありません。

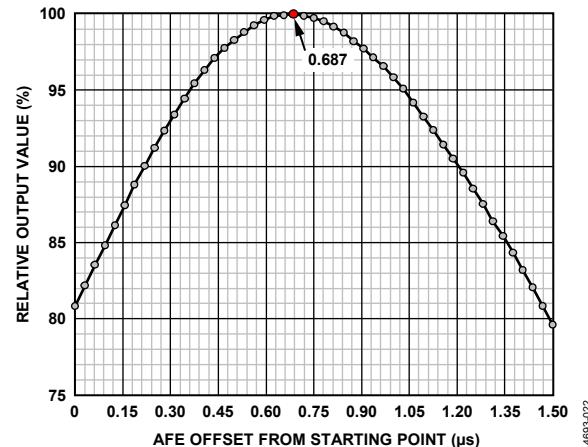

### AFE 位置の掃引

タイム・スロット A とタイム・スロット B の AFE オフセットはそれぞれ、レジスタ 0x39 とレジスタ 0x3B のビット [10:0] で制御します。各 LSB は、32 MHz の 1 サイクル (31.25ns) を表します。これらのレジスタは、31.25 ns ステップの  $2^{11-1}$  倍の長さを

指すと考えることができます。または、レジスタの値をビット単位に分解し、AFE のおおまかな設定値として、ビット [10:5] が約 1  $\mu$ s のステップに相当し、ビット [4:0] が 31.25 ns のステップに相当すると考えることもできます。オフセットを最適化するうえで推奨される方法は、開始ポイントから AFE の位置を掃引し、局所的な最大値を見つけることです。このテストのセットアップ方法を使用すれば、静的な方法でフォトダイオードの範囲内で LED を点灯できます。このテストは通常、固定された距離に反射面を設置して実施します。次に、AFE の位置を掃引すれば、出力レベルの変化を見つけることができます。AFE の位置を調整する場合、31.25 ns のステップを使用して位置を掃引することが重要です。通常、ほとんどのシステムでは、局所的な最大値は開始ポイントから 2  $\mu$ s 以内の時点に存在します。図 22 に、AFE 掃引の一例を示します。ここで、x 軸上の 0 は、すでに定義されている AFE の開始ポイントを表しています。図 22 の各データ・ポイントは、 $SLOTx\_AFE\_OFFSET$  の 31.25 ns ステップに対応します。この例では  $SLOTx\_AFE\_OFFSET$  の最適な位置は、AFE の開始ポイントから 0.687  $\mu$ s 離れた時点になります。

図 22. AFE 掃引の例

表 15 に、最適化を行った後の LED パルス幅と AFE 積分幅の代表的な値を示します。通常、AFE 掃引方法による検証を最初に行わずに、表 15 に示されている  $SLOTx\_AFE\_OFFSET$  の値を使用することは推奨されません。LED パルス幅の新しい値を使用するたび、また ADPD105/ADPD107 を採用した新しいハードウェア・セットを製作するたびに、この手順を繰り返します。最大の精度を達成するには、AFE の掃引より先に、32 MHz クロックの補正を行うことを推奨します。

表 15. AFE ウィンドウの設定

| LED Register 0x30 or Register 0x35 | AFE Register 0x39 or Register 0x3B | Comment                                                        |

|------------------------------------|------------------------------------|----------------------------------------------------------------|

| 0x0219                             | 0x1A08                             | 2 $\mu$ s LED pulse, 3 $\mu$ s AFE width, 25 $\mu$ s LED delay |

| 0x0319                             | 0x21FE                             | 3 $\mu$ s LED pulse, 4 $\mu$ s AFE width, 25 $\mu$ s LED delay |

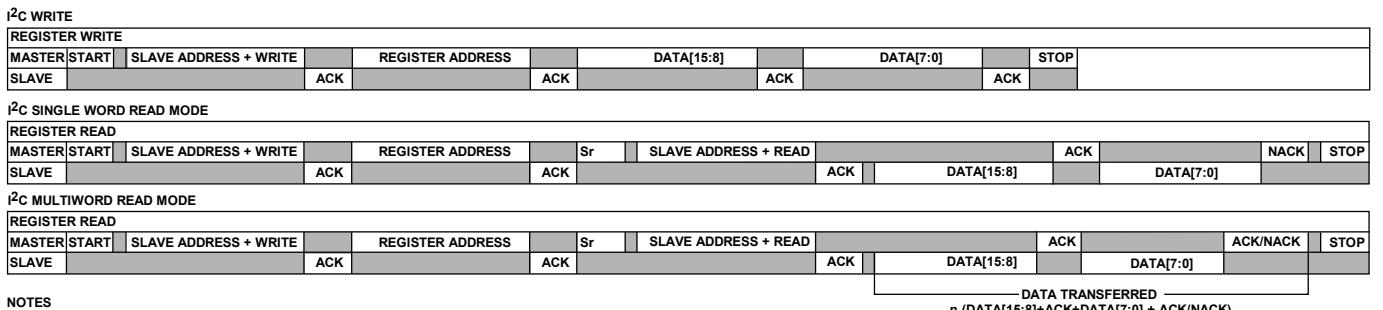

## I<sup>2</sup>C シリアル・インターフェース

ADPD105 は、SDA (データ) ピンと SCL (クロック) ピンを通じて、シリアル・インターフェースをサポートしています。すべての内部レジスタは、この I<sup>2</sup>C インターフェース経由でアクセスします。ADPD105 は I<sup>2</sup>C 専用デバイスであり、SPI をサポートしていません。

ADPD105 は、NXP Semiconductors から出版された *UM10204 I<sup>2</sup>C-Bus Specification and User Manual*、Rev. 05-9 October 2012 に準拠しています。この製品は、高速モード (400 kbps) のデータ転送をサポートしています。レジスタの読み出しと書き込みは、図 23 に示す方法でサポートされています。図 2 に、I<sup>2</sup>C インターフェースのタイミング図を示します。

### スレーブ・アドレス

デバイスに対応する、デフォルトの 7 ビット I<sup>2</sup>C スレーブ・アドレスは 0x64 であり、その後に R/W ビットが続きます。書き込みの場合、デフォルトの I<sup>2</sup>C スレーブ・アドレスは 0xC8 です。読み取りの場合、デフォルトの I<sup>2</sup>C アドレスは 0xC9 です。スレーブ・アドレスは、レジスタ 0x09 のビット [7:1] に書き込む方法で設定できます。複数の ADPD105 デバイスが同じバス・ライン上に存在する場合、GPIO0 ピンと GPIO1 ピンを使用して、アドレスの変更に対してどちらのデバイスが対応するかを選択できます。レジスタ 0x0D を使用すれば、特定のデバイスでアドレスの変更を有効にするためのキーを選択できます。複数の ADPD105 デバイスを同じ I<sup>2</sup>C バス・ラインに接続している状況で、スレーブ・アドレスを変更するには、以下の手順に従ってください。

1. 使用しているキーに応じて、GPIO0 ピンと GPIO1 ピンの一方または両方の入力バッファを有効にするには、レジスタ 0x4F を使用します。。

2. アドレスを変更する必要があると識別されたデバイスで、GPIO0 ピンや GPIO1 ピンをハイまたはローに設定し、使用するキーに一致させることができます。

3. 希望する機能に合わせたレジスタ 0x0D のビット [15:0] を使用して、SLAVE\_ADDRESS\_KEY のビットを書き込みます。許可されるキーを表 29 に示します。

表 16. I<sup>2</sup>C 用語の定義

| Term          | Description                                                                                                  |

|---------------|--------------------------------------------------------------------------------------------------------------|

| SCL           | Serial clock.                                                                                                |

| SDA           | Serial address and data.                                                                                     |

| Master        | The master is the device that initiates a transfer, generates clock signals, and terminates a transfer.      |

| Slave         | The slave is the device addressed by a master. The ADPD105 operates as a slave device.                       |

| Start (S)     | A high to low transition on the SDA line while SCL is high; all transactions begin with a start condition.   |

| Start (Sr)    | Repeated start condition.                                                                                    |

| Stop (P)      | A low to high transition on the SDA line while SCL is high. A stop condition terminates all transactions.    |

| ACK           | During the acknowledge or no acknowledge clock pulse, the SDA line is pulled low and remains low.            |

| NACK          | During the acknowledge or no acknowledge clock pulse, the SDA line remains high.                             |

| Slave Address | After a start (S), a 7-bit slave address is sent, which is followed by a data direction bit (read or write). |

| Read (R)      | A 1 indicates a request for data.                                                                            |

| Write (W)     | A 0 indicates a transmission.                                                                                |

4. レジスタ 0x09 のビット [7:1] を使用して、希望の SLAVE\_ADDRESS ビットを書き込みます。レジスタ 0x09 のビット [7:1] への書き込みを行う際に、レジスタ 0x09 のビット [15:8] に 0xAD を書き込みます。レジスタ 0x0D への書き込みの直後に、レジスタ 0x09 に書き込む必要があります。

5. SLAVE\_ADDRESS を変更する必要のあるすべてのデバイスで、ステップ 1 ~ 4 を繰り返します。

6. 各デバイスで新しい SLAVE\_ADDRESS を使用して通常動作を実行するため、必要に応じて GPIO0 ピンと GPIO1 ピンを設定します。

### I<sup>2</sup>C 読出し動作と書き込み動作

図 23 に、ADPD105 の I<sup>2</sup>C 書込み動作と読み出し動作を示します。シングルワード書き込みとマルチワード読み取りの各動作がサポートされています。単一レジスタの読み出しの場合、2 番目のデータ・バイトを読み出した後、ホストは NACK (ノー・アクノレッジ) を送信します。この場合、アクセスするごとに新しいレジスタ・アドレスが必要です。

マルチワード動作の場合、最後のワードの最終バイトを読み出すまで、各データ・バイト・ペアに続いて、ホストからアクノレッジが送信されます。ホストは、ノー・アクノレッジを送信する方法で、最後のワード読み出しが行われたことを示します。FIFO (レジスタ 0x60) から読み出す場合、データは FIFO 内の次のアドレスへ自動的に進み、すでに読み出したスペース (アドレス) は解放されます。FIFO 以外のアドレスから読み出す場合、レジスタ・アドレスは次のアドレスへ自動的に進みます。ただし、レジスタ 0x5F とレジスタ 0x7F は例外で、アドレスが自動的にインクリメントしません。この自動インクリメントにより、複数のレジスタを順に読み出す場合のオーバーヘッドが低下します。

レジスタ書き込みはいずれもシングルワードのみで、16 ビット (1 ワード) のデータが必要です。

ソフトウェア・リセット (レジスタ 0x0F のビット 0) により、アクノレッジが返されます。その後、デバイスはスタンバイ・モードに戻り、すべてのレジスタがデフォルト状態になります。

図 23. I<sup>2</sup>C 読出し動作と書き込み動作

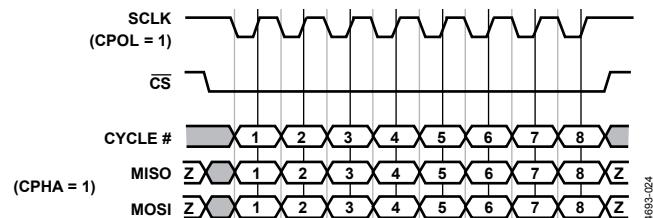

## SPI ポート

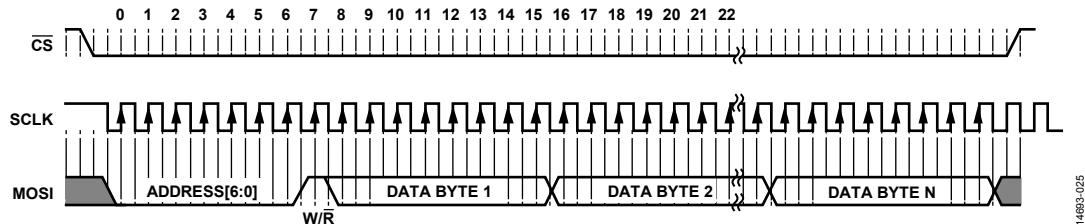

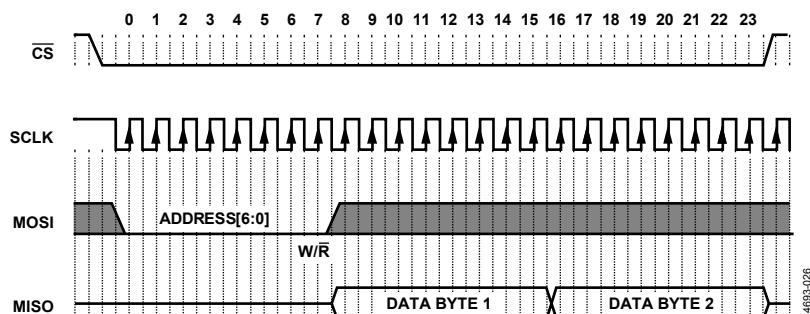

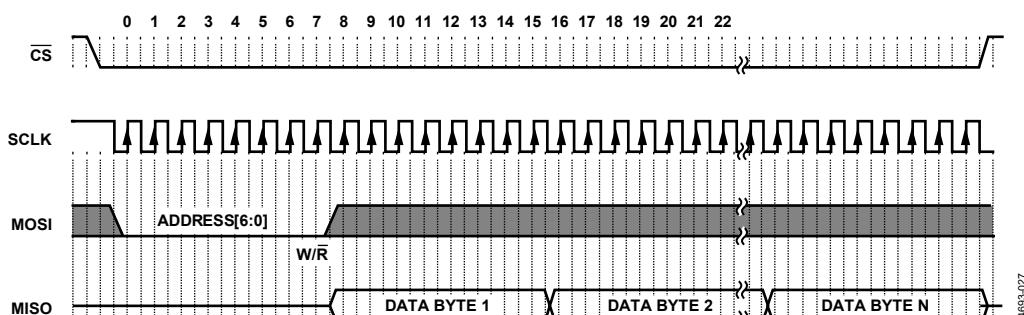

ADPD107 は SPI 専用デバイスです。このデバイスは、I<sup>2</sup>C インターフェースをサポートしていません。SPI ポートは 4 線インターフェースを使用します。このポートは、CS、MOSI、MISO、SCLK の各信号で構成されており、常にスレーブ・ポートとして動作します。CS はトランザクションを開始する際にローになります。トランザクションを終了する際にハイになります。SCLK 信号はローからハイに遷移するときに、MOSI をラッピします。MISO データは SCLK の立下がりエッジでデバイスからシフト出力されます。また、SCLK の立上がりエッジでは、マイクロコントローラのような受信デバイスに対してクロックを供給する必要があります。MOSI 信号はシリアル入力データを伝送し、MISO 信号はシリアル出力データを伝送します。MISO 信号は、読み出し動作が要求されるまでスリー・ステート (Z) を維持します。この結果、他の SPI 互換ペリフェラルが同じ MISO ラインを共有できます。すべての SPI トランザクションは、表 17 に示す共通の基本フォーマットを使用します。タイミング図を図 3 に示します。どのデータも、MSB ファーストで書き込みます。

表 17. 全般的な制御ワード・シーケンス

| Byte 0               | Byte 1     | Byte 2    | Subsequent Bytes      |

|----------------------|------------|-----------|-----------------------|

| Address[6:0],<br>W/R | Data[15:8] | Data[7:0] | Data[15:8], Data[7:0] |

SPI トランザクションで最初に書き込まれるバイトは、7 ビットのアドレスです。これは、アクセスしようとするアドレスの場所を表しており、その後に W/R ビットが続けます。このビットで、通信が書き込み（ロジック・レベル 1）または読み取り（ロジック・レベル 0）のどちらであるかを決定します。この結果を表 18 に示します。

表 18. SPI アドレスと Write/R のバイト・フォーマット

| Bit 0 | Bit 1 | Bit 2 | Bit 3 | Bit 4 | Bit 5 | Bit 6 | Bit 7 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| A6    | A5    | A4    | A3    | A2    | A1    | A0    | W/R   |

一般的に SPI 通信スレーブ・ポートのフォーマットは、SPI モード 3 として知られています。ここでは、クロック極性 (CPOL) = 1、クロック位相 (CPHA) = 1 です（図 24 を参照）。クロックの基本値は 1 です。データはクロックの立上がりエッジでキャプチャされ、立下がりエッジで伝搬されます。

SPI スレーブ・ポートの最大読み出し／書き込み速度は 10 MHz です。

図 24. SPI スレーブ・ポートのクロック極性と位相 (CPOL = 1、CPHA = 1)

単一のレジスタに対するマルチワード SPI 書込み動作のサンプル・タイミング図を図 25 に示します。シングルワード SPI 読出し動作のサンプル・タイミング図を図 26 に示します。MISO ピンは、有効な  $\overline{R}$  ビットを受信した後、3 ステート (Z) から、駆動される状態に遷移します。この例では、バイト 0 はアドレスと W/R ビットで構成されており、それ以降のバイトはデータを伝送します。マルチワード SPI 読出し動作のサンプル・タイミング図を

図 27 に示します。図 25～図 27 では、SCLK の立上がりエッジを上向きの矢印で示し、この立上がりエッジでデータ・ラインがサンプリングされることを表しています。

0x5F、0x60 (FIFO)、0x7F の各アドレスを除き、マルチワードの読み取りまたは書き込みを行う場合、データ・アドレスは後続のトランザクションに備えて、次の連続アドレスへ自動的にインクリメントします。

図 25. SPI スレーブ書き込み用のクロック供給 (バースト書き込みモード、N バイト)

図 26. SPI スレーブ読み出し用のクロック供給 (シングルワード・モード、2 バイト)

図 27. SPI スレーブ読み出し用のクロック供給 (バースト読み出しモード、N バイト)

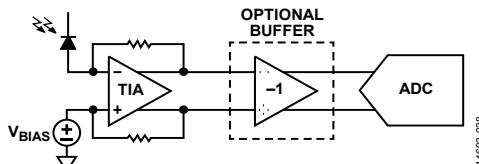

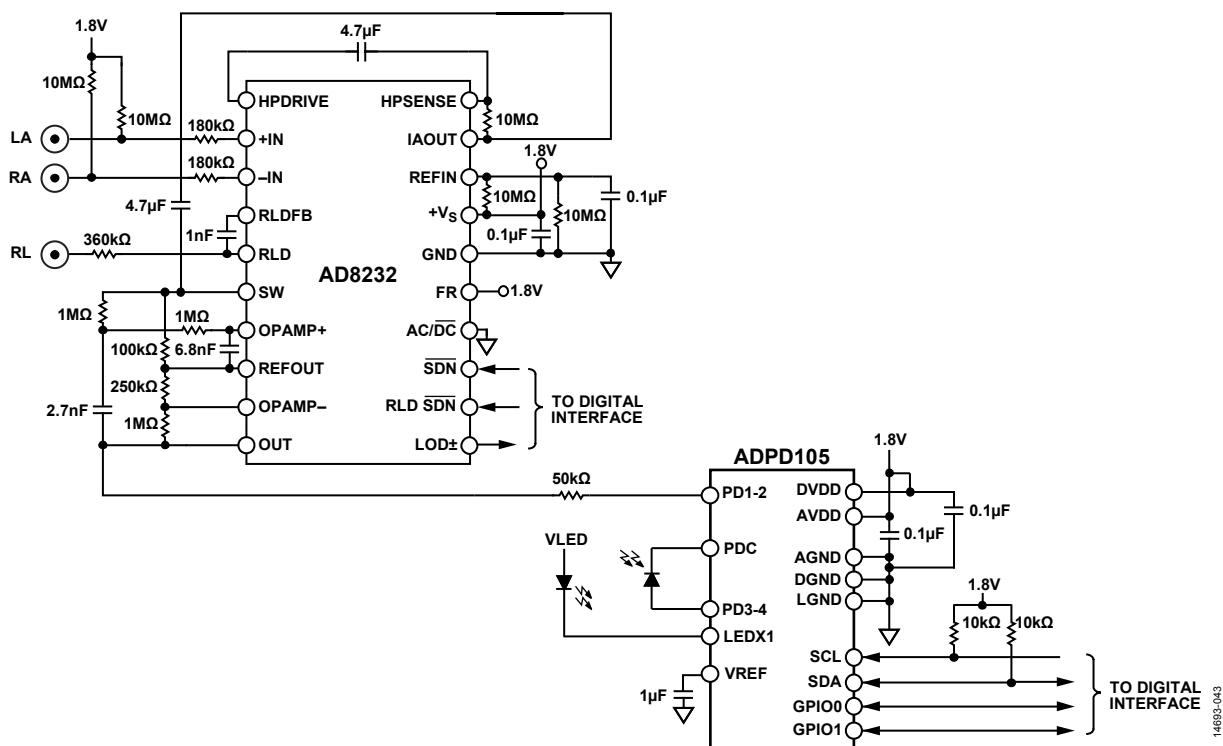

## 代表的な接続図

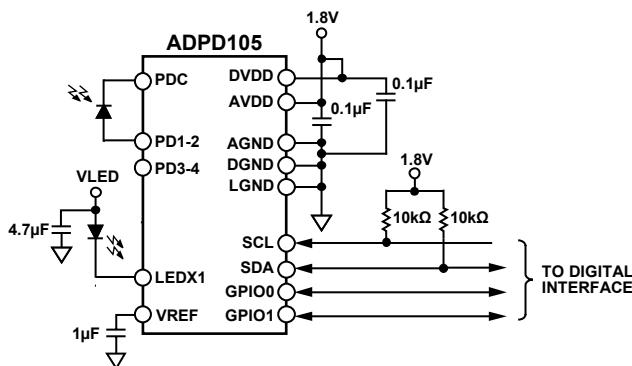

図 28 に、緑の LED と ADPD105 を採用し、手首での心拍測定で使用する代表的な回路を示します。1.8 V I<sup>2</sup>C の通信ラインである SCL と SDA、および GPIO0 と GPIO1 の各ラインは、システムのマイクロプロセッサまたはセンサー・ハブに接続します。I<sup>2</sup>C 信号に対して、1.8 V または 3.3 V の電源に接続したプルアップ抵抗を追加することもできます。GPIO0 と GPIO1 の各信号と互換性があるのは 1.8 V 電源のみであり、これらの信号でレベル変換器が必要になることがあります。図 28 に示す回路は、ADPD107 でも同様に利用できますが、その場合は I<sup>2</sup>C インターフェースを SPI で置き換える必要があります。

1.8 V 電源である  $V_{DD}$  を AVDD と DVDD に供給します。表 3 に規定されており、LED ドライバのピンと LED 電源電圧セクションで計算方法を示すピーク電流要件に従う、標準的なレギュレータ回路を LED 電源として使用します。

最善のノイズ特性を達成するには、AGND、DGND、LGNDのすべてを束ね、グラウンド・プレーン、グラウンド・ポア、太いグラウンド・パターンのように、面積の広い導体面に接続します。

使用するフォトダイオードや LED の数は、アプリケーションだけでなく、必要なダイナミック・レンジと SNR によっても異なります。例えば、単一の大きいフォトダイオードを使用するアプリケーションでは、複数の入力間で電流を分割する方法で、ダイナミック・レンジを広げることができます。電流がデバイスの4個のチャンネルに均等に分割されるように、フォトダイオードのアノードを PD1-2 と PD3-4 の両方のチャンネルに接続すると、単一チャンネルの構成に比べてダイナミック・レンジを実質的に4倍に広げることができます。代わりに、フォトダイオードが小型の場合や、信号が大きく減衰している場合、フォトダイオードを PD1-2 入力のみに接続し、必要とされるダイナミック・レンジの正確な幅に基づいてデバイスを 1 チャンネル・モードまたは 2 チャンネル・モードに設定することで、SNR を最大化できます。フォトダイオードのアノードは常に、PD1-2 と PD3-4 の各入力ピンに接続されます。一方、フォトダイオードのカソードは、PDC ピンに接続されます。どちらか 1 つの入力のみを使用する場合、デバイスが正しく動作するように、未使用の入力をフロート状態のままにしておくことが重要です。

図 29 と図 30 に、ADPD105 と ADPD107 のそれぞれで推奨される接続図とプリント回路基板 (PCB) のレイアウトを示します。サンプリング期間中、電流入力ピンである PD1-2 と PD3-4 には、代表値で 1.3 V の電圧が印加されます。スリープ期間中、これらのピンはカソード・ピンに接続されます。カソードとアノードの各電圧を表 3 に示します。

図 28. 代表的な手首型の HRM (心拍モニタ) 測定

図 29. ADPD105 の接続と PCB レイアウトの図（上面図）

図 30. ADPD107 の接続と PCB レイアウトの図（上面図）、

破線のパターンは外部から見えないビアを経由

## LED ドライバのピンと LED 電源電圧

LEDX1、LEDX2、LEDX3 の各ピンには、3.6 V の絶対最大定格の電圧が印加されています。この定格を超過する電圧を印加した場合でも、デバイス動作の信頼性に影響を与え、特定の状況ではデバイスが正常に動作しなくなる場合があります。LEDx ピンの電圧と LED の供給電圧 ( $V_{LEDx}$ ) を混同しないでください。 $V_{LEDx}$  は外部 LED のアノードに印加される電圧で、LEDX $x$  ピンは内部電流ドライバへの入力です。これらのピンは外部 LED のカソードに接続されます。

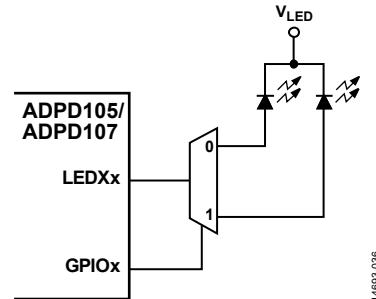

## LED ドライバの動作

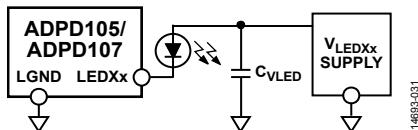

ADPD105/ADPD107 の LED ドライバは、電流シンク型です。設定した LED 電流を維持するうえで、グラウンドを基準としてドライバ・ピンで測定する場合、必要とされるコンプライアンス電圧は、必要な電流の関数で表現されます。図 12 に、さまざまな LED のおおまかな設定値で必要とされるコンプライアンス電圧の代表値を示します。図 31 に、ADPD105/ADPD107 を LED ドライバ経由で LED に接続する場合の基本的な回路図を示します。平均電流の決定と CVLED の決定のセクションで、バイパス・コンデンサ ( $C_{VLED}$ ) と LED の供給電圧 ( $V_{LEDx}$ ) の要件を定義します。

図 31.  $V_{LEDx}$  給電の回路図

## 平均電流の決定

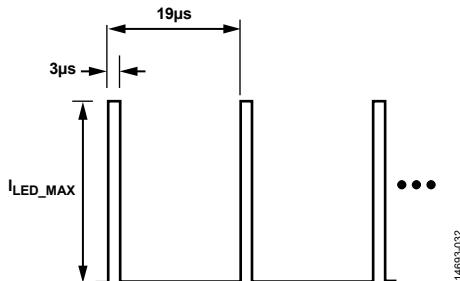

ADPD105/ADPD107 は、短い連続パルスで LED を駆動します。図 32 に、パルス・バースト・シーケンスに関する ADPD105/ADPD107 の代表的な設定を示します。

図 32. LED パルス・バースト・シーケンスの代表的な設定

この例では、LED パルス幅  $t_{LED\_PULSE}$  は 3 μs、LED パルス期間  $t_{LED\_PERIOD}$  は 19 μs です。この LED は緑色の LED で形成されたペアで、250 mA ピークの電流で駆動されます。 $C_{VLED}$  の目的は、個別のパルスの間で LED のバッファとして機能することにあります。ワースト・ケースのシナリオでは、図 32 に示すパルス系列が短いパルスの連続シーケンスとして発生し、 $V_{LEDx}$  電源が平均電流を供給する必要があります。したがって、次のように  $I_{LED\_AVERAGE}$  を計算します。

$$I_{LED\_AVERAGE} = (t_{LED\_PULSE}/t_{LED\_PERIOD}) \times I_{LED\_MAX} \quad (1)$$

ここで

$I_{LED\_AVERAGE}$  は、パルス期間中に  $V_{LEDx}$  電源から供給する必要のある平均電流になります。これは、 $V_{LEDx}$  の定格電源電流でもあります。

$I_{LED\_MAX}$  は、LED を流れるピーク電流の設定値です。

式 1 に示した数値を使用すると、 $I_{LED\_AVERAGE} = 3/19 \times I_{LED\_MAX}$  になります。代表的な LED タイミングでは、 $V_{LEDx}$  の平均電源電流は  $3/19 \times 250 \text{ mA} = 39.4 \text{ mA}$  となり、 $V_{LEDx}$  電源が 40 mA の DC 電流をサポートする必要があることを示しています。

## $C_{VLED}$ の決定

$C_{VLED}$  コンデンサの値を決定するには、LED 動作中の最大順方向バイアス電圧である  $V_{FB\_LED\_MAX}$  を決定する必要があります。図 33 に示すように、LED 電流  $I_{LED\_MAX}$  を  $V_{FB\_LED\_MAX}$  に変換します。この例では、並列接続された緑色の LED 2 個を通過する 250 mA の電流から、 $V_{FB\_LED\_MAX} = 3.95 \text{ V}$  という値が得られます。LED パス内にあるすべての直列抵抗成分も、この電圧計算に含める必要があります。LED パスを設計する際は、LED を流れるピーク電流が非常に大きくなることが原因で、抵抗成分が小さくても電圧降下が大きくなる可能性があることに注意してください。さらに、これらの抵抗成分は、 $V_{LED}$  電源に不要な制約を課す可能性があります。

図 33. ドライバ電流の関数として表現した LED 順方向バイアス電圧降下の平均値の例

$C_{VLED}$  コンデンサのサイズを正しく設定するには、コンデンサの枯渇を避け、LED へのパルス供給を行っている間、コンデンサの電圧が LED の順方向バイアス電圧を下回らないように設定してください。 $V_{LED}$  バイパス・コンデンサの最小値を計算するには、次の式を使用します。

$$C_{VLED} = \frac{t_{LED\_PULSE} \times I_{LED\_MAX}}{V_{LED\_MIN} - (V_{FB\_LED\_MAX} + 0.2)} \quad (2)$$

ここで

$t_{LED\_PULSE}$  は、LED パルス幅。

$I_{LED\_MAX}$  は、デバイスを動作させる際に使用する LED の最大順方向バイアス電流。

$V_{LED\_MIN}$  は、無負荷時に  $V_{LEDx}$  電源から供給される最小電圧。

$V_{FB\_LED\_MAX}$  は、LED が  $I_{LED\_MAX}$  を実現するために必要とされる最小順方向バイアス電圧。

$C_{VLED}$  の式における分子から、バイパス・コンデンサから放電される合計電荷をクーロン単位で表した値が計算されます。この値は設定済みの LED シングル・パルスを最大電流で供給するためには必要となります。分母は、LED で必要とされる電圧と  $V_{LEDx}$  電源の最小電圧の間の差を表します。LED で必要となる電圧とは、LED ドライバの 0.2 V のコンプライアンスや、最大電流で動作する LED の順方向バイアス電圧を実現する、LED のアノード電圧を意味します。ADPD105/ADPD107 の代表的な例では、 $V_{LEDx}$  電源電圧の最小値が 4.4 V であり、2 個の 528 nm LED を並列接続した場合のピーク電流が 250 mA であることを想定しています。 $C_{VLED}$  の最小値は、3  $\mu$ F です。

$$C_{VLED} = (3 \times 10^{-6} \times 0.250) / (4.4 - (3.95 + 0.2)) = 3 \mu\text{F} \quad (3)$$

式 3 に示すように、電源の最小電圧降下は最大アノード電圧に近い値なので、 $C_{VLED}$  に対する要件はより厳しくなり、コンデンサの値がより大きくなる傾向を招きます。式 1、式 2、式 3 に正しい値を挿入することが重要です。例えば、 $V_{LED\_MIN}$  のワースト・ケース値の代わりに  $V_{LED\_MIN}$  の平均値を使用すると、設計に重大な欠陥が生じる可能性があります。その結果、 $C_{VLED}$  の値が過度に小さくなり、アプリケーションで光パワーが不足する可能性があります。したがって、 $C_{VLED}$  の値に十分なマージンを追加することを強く推奨します。また、部品の寿命全体にわたる電圧、バイアス、温度、その他の係数に対するコンデンサ値のディレーティングを考慮し、 $C_{VLED}$  に対するマージンも追加してください。

## LED のインダクタンスに関する考慮事項

ADPD105/ADPD107 の LED ドライバ (LED $Xx$ ) で、スルー・レートを設定できます (レジスタ 0x22 のビット [6:4]、レジスタ 0x23 のビット [6:4]、およびレジスタ 0x24 のビット [6:4])。これらのスルー・レートは、表 3 で定義されています。最小の設定値を使用する場合でも、ボードの設計とレイアウトを注意深く考慮する必要があります。LED のカソードと LED $X$  ピンの間に、長い PCB パターンのような大きい直列インダクタを接続する場合、LED パルスのスルー部分が発生している間に、スイッチングされたインダクタで電圧スパイクが発生し、絶対最大/最小電圧の限界を超える可能性があります。

寄生インダクタンスに起因する電圧スパイクが LED $Xx$  ピンで発生しないことを確認するには、オシロスコープを使用して LED $Xx$  ピンを測定し、通常動作時の電圧をモニタします。3.6 V を上回る正のスパイクは、デバイスの損傷を招く可能性があります。

さらに、-0.3 V を下回る負のスパイクも、デバイスの損傷を招く可能性があります。

## 推奨されるスタートアップ・シーケンス

図 18 に示すように、パワーアップ時にデバイスはスタンバイ・モードになります (レジスタ 0x10 = 0x0)。ADPD105/ADPD107 では、特定のパワーアップ・シーケンスは必要ありません。

スタンバイ・モードから測定を開始するには、次のように ADPD105/ADPD107 を初期化します。

1. CLK32K\_EN ビット (レジスタ 0x4B のビット 7) をセットし、サンプリング・クロック (32 kHz クロック) を開始します。このクロックは、ステート・マシンを制御します。このクロックをオフにすると、ステート・マシンはレジスタ 0x10 の定義に従って遷移できません。

2. レジスタ 0x10 に 0x1 を書き込み、デバイスを強制的にプログラム・モードに移行します。ステップ 1 とステップ 2 を入れ替えることもできますが、両方のステップを実施するまで、実際のステート遷移は発生しません。

3. デバイスがプログラム・モードにある間、他の制御レジスタに対して任意の順序で書き込みを行い、必要に応じてデバイスを設定します。

4. レジスタ 0x10 に 0x2 を書き込み、通常のサンプリング動作を開始します。

通常の動作を終了するには、以下のシーケンスに従って ADPD105/ADPD107 をスタンバイ・モードに移行します。

1. レジスタ 0x10 に 0x1 を書き込み、デバイスを強制的にプログラム・モードに移行します。

2. デバイスがプログラム・モードにある間、任意の順序でレジスタに書き込みを行います。

3. レジスタ 0x00 に 0x00FF を書き込み、すべての割込みをクリアします。必要な場合、レジスタ 0x00 に 0x80FF を書き込む方法で、FIFO もクリアします。

4. レジスタ 0x10 に 0x0 を書き込み、デバイスを強制的にスタンバイ・モードに移行します。

5. 代わりに、CLK32K\_EN ビット (レジスタ 0x4B のビット 7) をリセットして、32 kHz クロックを停止することもできます。デバイスがスタンバイ・モード (レジスタ 0x10 = 0x0) で、実行する必要がある書き込みはレジスタ 0x4B のビット 7=0 のみです。プログラム・モードまたは通常動作モードで、このビットに 0 を書き込むと、スタンバイ・モードを含め、他のどのモードにもデバイスを遷移することができません。これ以降にデバイスに対して書き込みを行い、モードの遷移を実行する場合も、この制限が適用されます。その結果、スタンバイ・モードのように見受けられる状態で、消費電力が大幅に増加します。この理由以外にも、32 kHz クロックが動作している間も電流の引き込み量は非常に小さいため、使いやすさの観点から、32 kHz クロックが有効になった後、このクロックを引き続き動作させることを推奨します。

## データの読出し

サンプル・データにアクセスできるように、ADPD105/ADPD107 には、複数の方法を用意しています。FIFO またはデータ・レジスタを使用してデータにアクセスできるように、各タイム・スロットを個別に設定できます。また、適切な時期に簡単にデータにアクセスできるように、割込み信号を使用する方法も利用できます。FIFO を使用すれば、データ・アクセスに関するシステムのタイミング要件を緩和することもできます。

## FIFO を使用したデータの読出し

ADPD105/ADPD107 は 128 バイトの FIFO メモリ・バッファを搭載しているので、一方または両方のタイム・スロットから取得し

たデータを格納するように、この FIFO を設定することもできます。どの種類のデータを各タイム・スロットから取得して FIFO に書き込むか選択するには、レジスタ 0x11 を使用します。両方のタイム・スロットが FIFO を使用するように設定することもできますが、両者の出力データ・レートが等しい場合のみ、この設定を使用できることに注意してください。

$$\text{出力データ・レート} = f_{\text{SAMPLE}}/N$$

ここで

$f_{\text{SW}}$  は、サンプリング周波数。

$N$  は、各タイム・スロットの平均化の係数 ( $N_A$  はタイム・スロット A、 $N_B$  はタイム・スロット B に対応)。言い換えると、両方のタイム・スロットから取得したデータを FIFO に格納するには、 $N_A = N_B$  が成立している必要があります。

データ・パケットは、出力データ・レートで FIFO に書き込まれます。 FIFO に書き込むデータ・パケットは、有効になっている各タイム・スロットに対応するサンプル全体で形成されています。各フォトダイオード・チャンネルに対応するデータは、16 ビットと 32 ビットのどちらかで格納されます。モードとデータ・フォーマットに応じて、各タイム・スロットはサンプルあたり 2、4、8、16 バイトいずれかのデータを格納できます。データ・パケットが損傷していないことを確認するため、パケット全体を書き込む空き容量が十分にある場合のみ、新しいデータが FIFO に書き込まれます。十分な空き容量がないときに到着したデータは失われます。十分な空き容量が存在する場合、 FIFO はデータの格納を続けます。データ・パケットが損傷していないことを確認するため、必ず完全なパケットを単位として FIFO データの読み出しを行ってください。

FIFO 内に現在格納されているバイト数は、レジスタ 0x00 のビット [15:8] で確認できます。専用の FIFO 割込みを利用することもでき、指定した量のデータが FIFO に書き込まれた時点での自動的に割込みが生成されます。

### 割込みベースの方法

割込みベースの方法を使用して FIFO からデータを読み出すには、次の手順を使用します。

1. プログラム・モードで、必要に応じてタイム・スロットを設定します。

2. レジスタ 0x11 に、各タイム・スロットで希望するデータ・フォーマットを書き込みます。

3. レジスタ 0x06 のビット [13:8] にある FIFO\_THRESH を、割込み閾値に設定します。ここで推奨される値は、データ・パケット内にある 16 ビット・ワードの個数から 1 を引いた値です。この場合、FIFO 内に少なくとも完全なパケットを 1 個格納できる空き容量が存在する時点で、割込みが生成されます。

4. FIFO 割込みを有効にするには、レジスタ 0x01 のビット 8 にある FIFO\_INT\_MASK に 0 を書き込みます。さらに、レジスタ 0x02 内の各ビットに適切な値を書き込む方法で、割込みピン (GPIO0) も設定します。

5. レジスタ 0x10 を 0x2 に設定して、通常の動作モードに移行します。

#### 6. 割込みが発生した場合

- a. 完全なパケットが 1 個以上存在する場合のみ、割込みが生成されるため、FIFO\_SAMPLES ビットを読み出す必要はありません。代わりに、割込みルーチンがこれらのビットを読み出す方法により、利用可能なパケットが複数あるかどうか確認することもできます。

- b. レジスタ 0x60 を使用してマルチワード・アクセスを 1 回以上行う方法で、完全なパケットを読み出します。 FIFO の読み出しを行うと、該当する領域が自動的に解放され、新しいサンプルを格納できるようになります。

FIFO からデータを読み出した直後に FIFO の割込みが自動的にクリアされます。また、 FIFO への書き込みが行われ、 FIFO 内のワード数が閾値に達した時点でのみ、割込みが再び設定されます。

### ポーリングによる方法

ポーリングによる方法を使用して FIFO からデータを読み出すには、次の手順を使用します。

1. プログラム・モードで、必要に応じてタイム・スロットを設定します。

2. レジスタ 0x11 に、各タイム・スロットで希望するデータ・フォーマットを書き込みます。

3. レジスタ 0x10 を 2 に設定して、通常の動作モードに移行します。

次に、ポーリング動作を開始します。

1. ポーリング間隔が経過するまで待ちます。

2. FIFO\_SAMPLES ビット (レジスタ 0x00 のビット [15:8]) を読み出します。

3. FIFO\_SAMPLES ≥ パケット・サイズである場合、次の手順を使用してパケットを読み出します。

- a. レジスタ 0x60 を使用してマルチワード・アクセスを 1 回以上行う方法で、完全なパケットを読み出します。 FIFO の読み出しを行うと、該当する領域が自動的に解放され、新しいサンプルを格納できるようになります。

- b. ステップ 1 を繰り返します。

モード変更が必要な場合や、通常のサンプリングに対して他の中断が必要な場合、 FIFO をクリアする必要があります。ステートをクリアし、 FIFO を空にするには、次の手順に従います。

1. レジスタ 0x10 を 0x1 に設定して、プログラム・モードに移行します。

2. レジスタ 0x00 のビット 15 に 1 を書き込みます。

### 割込みを使用したレジスタからのデータ読み出し

最新のサンプル・データは常にデータ・レジスタで利用でき、各タイム・スロットの終了と同時に更新されます。各フォトダイオード・チャンネルに対応するデータ値は、タイム・スロット A ではレジスタ 0x64 ~ レジスタ 0x67 にある 16 ビット値として利用できます。同様に、タイム・スロット B ではレジスタ 0x68 ~ レジスタ 0x6B にある 16 ビット値として利用できます。最大値に達することが許容される場合、レジスタ 0x64 ~ レジスタ 0x6B のクリップが実施されます。レジスタ 0x64 ~ レジスタ 0x6B が飽和している場合、タイム・スロット A ではレジスタ 0x70 ~ レジスタ 0x77、タイム・スロット B ではレジスタ 0x78 ~ レジスタ 0x7F で、各チャンネルに対応する飽和していない値(最大 27 ビット)を利用できます。レジスタが更新され、読み出しの準備ができた時点で、サンプルの割込みを利用できるようになります。特定のタイム・スロットに対応する割込みを使用するには、次の手順に従います。

1. サンプル割込みを有効にするには、レジスタ 0x01 の適切なビットに 0 を書き込みます。タイム・スロット A での割込みを有効にするには、ビット 5 に 0 を書き込みます。タイム・スロット B での割込みを有効にするには、ビット 6 に 0 を書き込みます。一方または両方の割込みを設定できます。

2. また、レジスタ 0x02 内の各ビットに適切な値を書き込む方法で、割込みピン (GPIO0) を設定します。

3. データ・レジスタが更新された時点で、割込みが生成されます。

4. 割込みハンドラは、次の作業を実行する必要があります。

- a. レジスタ 0x00 を読み取り、ビット 5 またはビット 6 を参照して、どちらの割込みが発生したか確認します。どちらか一方の割込みのみを使用している場合、このステップは不要です。

- b. 次のサンプルの書き込みが可能になる前に、データ・レジスタを読み出します。出力データ・レートに基づき、システム内で適切な割込み遅延を達成し、次のデータ更新が発生する前に応答できるほど十分短いサービス時間を実現する必要があります。

- c. 割込みをクリアするには、レジスタ 0x00 のビット 5 またはビット 6 に 1 を書き込みます。

両方のタイム・スロットを使用している場合、タイム・スロット B の割込みを使用して、すべてのレジスタを読み出す準備ができたときに通知を行うことも可能です。データ・レジスタからデータを転送する目的で、マルチワード読出しを使用することが推奨されます。

#### 割込みを使用しないレジスタからのデータ読み出し

システム割込みの応答が高速でないか十分な予測可能性を確保できないことが原因で、割込みベースの方法を使用できない場合や、割込みピン (GPIOx) を使用していない場合は、データ保持の機構を使用して信頼性の高いデータ・アクセスを実現できます。同じサンプリング時刻に複数のレジスタからデータを読み出すには、現在のデータを読み出している間にサンプルが更新されることを防止する必要があります。割込みのタイミングを使用せずにレジスタ読出しを行う方法は、次のとおりです。

1. アクセスする必要のあるタイム・スロットを対象にして、SLOTA\_DATA\_HOLD または SLOTB\_DATA\_HOLD (それぞれ、レジスタ 0x5F のビット 1 とビット 2) に 1 を書き込みます (両方のタイム・スロットにアクセスすることもできます)。この設定により、サンプルの更新が防止されます。

2. 必要に応じて、レジスタを読み出します。

3. すでにセットした SLOTA\_DATA\_HOLD または SLOTB\_DATA\_HOLD ビット (それぞれ、レジスタ 0x5F のビット 1 とビット 2) に 0 を書き込みます。サンプルの更新が再び許可されます。

読み出しを実施している間に新しいサンプルが到着する可能性があるので、この方法を採用すると、読み出し中のデータの一部が新しいサンプルによって上書きされる問題を防止できます。

#### クロックとタイミングの補正

ADPD105/ADPD107 は 2 つの内部タイム・ベースを使用して動作します。1 つは、サンプリングのタイミングを設定する 32 kHz クロックです。もう 1 つは、LED へのパルス供給やデータ・キャプチャのような内部機能のタイミングを制御する 32 MHz クロックです。どちらのクロックも内部で生成され、デバイス間で約 10 % (typ) の変動を示します。