# 1.2 A、超低ノイズ、高 PSRR RF リニア・レギュレータ

データシート

**ADP7156**

### 特長

入力電圧範囲: 2.3 V ~ 5.5 V

1.2 V ~ 3.3 V の 16 種類の標準電圧が使用可能

最大負荷電流: 1.2 A

低ノイズ

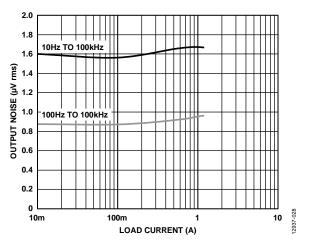

100 Hz ~ 100 kHz で 0.9 μV rms の総合積分ノイズ 10 Hz ~ 100 kHz で 1.6 μV rms の総合積分ノイズ ノイズ・フペクト II 密度: 10 kHz-~1 MHz で 1.7 αV//H

ノイズ・スペクトル密度: 10 kHz~1 MHz で 1.7 nV/√Hz 景酒亦動除主は(DSDD)

電源変動除去比(PSRR)

1 kHz  $\sim$  100 kHz で 80 dB; 1 MHz で 60 dB  $V_{\text{OUT}}$  = 3.3 V,  $V_{\text{IN}}$  = 4.0 V

ドロップアウト電圧: louт = 1.2 A、Vouт = 3.3 V で 120 mV(代表値)

初期精度: ILOAD = 10 mA で ±0.6 %

電源ライン、負荷、温度に対する初期精度: ±1.5 %

静止電流: 無負荷で I<sub>GND</sub> = 4.0 mA、負荷 1.2 A で 7 mA

低シャットダウン電流 :0.2 µA

10 µF セラミック出力コンデンサで安定

10 ピンの 3 mm × 3 mm LFCSP パッケージまたは 8 ピンの

SOIC パッケージを採用

高精度イネーブルを装備

ADIsimPower ツールのサポート

### アプリケーション

ノイズに敏感なアプリケーションでのレギュレーション: 位相ロックループ(PLL)、電圧制御発振器(VCO)、VCO内蔵PLL

通信およびインフラストラクチャ バックホール回線およびマイクロ波回線

### 概要

ADP7156 は  $2.3\,\mathrm{V}\sim5.5\,\mathrm{V}$  で動作するリニア・レギュレータで、最大出力電流  $1.2\,\mathrm{A}$  を供給します。当社独自の最新アーキテクチャを採用して高い電源変動除去比と超低ノイズを実現しており、 $10\,\mu\mathrm{F}$  セラミック出力コンデンサを使うだけで、優れたライン過渡応答と負荷過渡応答を実現します。

ADP7156には 16種類の標準出力電圧があります。  $1.2\,\mathrm{V}$ 、  $1.8\,\mathrm{V}$ 、  $2.0\,\mathrm{V}$ 、  $2.5\,\mathrm{V}$ 、  $2.8\,\mathrm{V}$ 、  $3.0\,\mathrm{V}$ 、  $3.3\,\mathrm{V}$  の電圧の製品を標準在庫品として提供しています。 特別注文により、  $1.3\,\mathrm{V}$ 、  $1.5\,\mathrm{V}$ 、  $1.6\,\mathrm{V}$ 、  $2.2\,\mathrm{V}$ 、  $2.6\,\mathrm{V}$ 、  $2.7\,\mathrm{V}$ 、  $2.9\,\mathrm{V}$ 、  $3.1\,\mathrm{V}$  、  $3.2\,\mathrm{V}$  の電圧の製品も提供しています。

ADP7156 レギュレータの出力ノイズ (代表値) は  $100~\text{Hz}\sim 100~\text{kHz}$ で  $0.9~\mu\text{V}$  rms、ノイズ・スペクトル密度は  $10~\text{kHz}\sim 1~\text{MHz}$ で 1.7~nV/Hz です。ADP7156 は  $10~\text{ピン}~3~\text{mm}\times 3~\text{mm}$  LFCSP パッケージおよび 8~ピン~SOIC パッケージを採用しているため、非常に小型なソリューションであるだけでなく、フットプリントが小さく低プロファイルのパッケージで 1.2~A までの出力電流を必要とするアプリケーションに対して優れた熱性能も提供します。

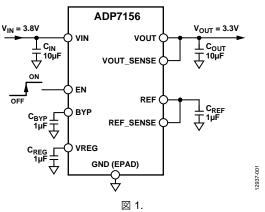

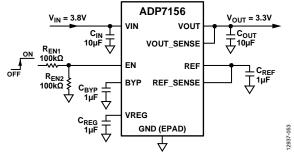

### 代表的なアプリケーション回路

表 1. 関連デバイス

| Model               | Input<br>Voltage  | Output<br>Current | Fixed/<br>Adj <sup>1</sup> | Package                       |

|---------------------|-------------------|-------------------|----------------------------|-------------------------------|

| ADP7158,<br>ADP7159 | 2.3 V to 5.5<br>V | 2 A               | Fixed/<br>Adj              | 10-lead LFCSP/<br>8-lead SOIC |

| ADP7157             | 2.3 V to 5.5<br>V | 1.2 A             | Fixed/<br>Adj              | 10-lead LFCSP/<br>8-lead SOIC |

| ADM7150,<br>ADM7151 | 4.5 V to 16 V     | 800 mA            | Fixed/<br>Adj              | 8-lead LFCSP/<br>8-lead SOIC  |

| ADM7154,<br>ADM7155 | 2.3 V to 5.5<br>V | 600 mA            | Fixed/<br>Adj              | 8-lead LFCSP/<br>8-lead SOIC  |

| ADM7160             | 2.2 V to 5.5<br>V | 200 mA            | Fixed                      | 6-lead LFCSP/<br>5-lead TSOT  |

<sup>&</sup>lt;sup>1</sup>Adj は調節可能を意味します。

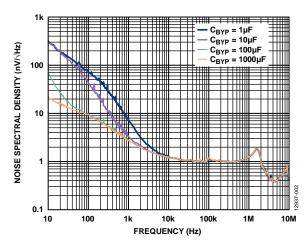

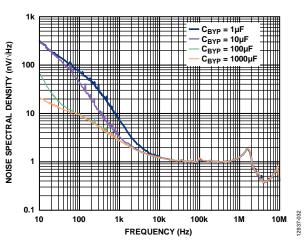

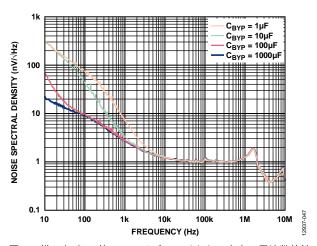

図 2. 様々な C<sub>BYP</sub> 値でのノイズ・スペクトル密度、V<sub>OUT</sub> = 3.3 V

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって 生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示 的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有 者の財産です。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

©2016 Analog Devices, Inc. All rights reserved.

Rev. o

本 社/〒105-6891

東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 電話 03 (5402) 8200

大阪営業所/〒532-0003

大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 電話 06 (6350) 6868

## 目次

| 符長                   | I |

|----------------------|---|

| アプリケーション             | 1 |

| 概要                   |   |

| 代表的なアプリケーション回路       |   |

| 改訂履歴                 |   |

| 仕様                   | 3 |

| 入力コンデンサと出力コンデンサの推奨仕様 |   |

| 絶対最大定格               |   |

| 熱データ                 |   |

| 熱抵抗                  |   |

| ESD に関する注意           |   |

| ピン配置およびピン機能の説明       |   |

| 代表的な性能特性             |   |

| 動作原理                 |   |

|                      |   |

| アプリケーション情報           | 14 |

|----------------------|----|

| ADIsimPower デザイン・ツール | 14 |

| コンデンサの選択             | 14 |

| 低電圧ロックアウト(UVLO)      | 15 |

| プログラマブルな高精度イネーブル     | 16 |

| スタートアップ時間            | 17 |

| REF、BYP、VREG の各ピン    | 17 |

| 電流制限 およびサーマル・シャットダウン | 17 |

| 熱に対する考慮事項            | 17 |

| PCB レイアウトに関する検討事項    | 20 |

| 外形寸法                 | 21 |

| オーダー・ガイド             | 22 |

### 改訂履歴

3/16—Revision 0: Initial Version

Rev. 0 – 2/22 –

## 仕様

特に指定がない限り、 $V_{IN}=V_{OUT}+0.5~V$  または 2.3 V(いずれか大きい方);  $V_{EN}=V_{IN}; I_{LOAD}=10~mA; C_{IN}=C_{OUT}=10~\mu F;$   $C_{REG}=C_{REF}=C_{BYP}=1~\mu F;$  代表値は  $T_A=25~\mathrm{^{\circ}C};$  最大値/最小値は  $T_A=-40~\mathrm{^{\circ}C}\sim+125~\mathrm{^{\circ}C};$

表 2.

| 衣 2.                                 | 1                               |                                                                                                | 1    |      |      |        |

|--------------------------------------|---------------------------------|------------------------------------------------------------------------------------------------|------|------|------|--------|

| Parameter                            | Symbol                          | Test Conditions/Comments                                                                       | Min  | Тур  | Max  | Unit   |

| INPUT VOLTAGE RANGE                  | $V_{\rm IN}$                    |                                                                                                | 2.3  |      | 5.5  | V      |

| LOAD CURRENT                         | $I_{LOAD}$                      |                                                                                                |      |      | 1.2  | A      |

| OPERATING SUPPLY CURRENT             | $I_{GND}$                       | $I_{LOAD} = 0 \mu A$                                                                           |      | 4.0  | 8.0  | mA     |

|                                      |                                 | $I_{LOAD} = 1.2 A$                                                                             |      | 7.0  | 12.0 | mA     |

| SHUTDOWN CURRENT                     | $I_{IN\_SD}$                    | EN = GND                                                                                       |      | 0.2  | 4    | μA     |

| NOISE                                |                                 | $V_{OUT} = 1.2 \text{ V to } 3.3 \text{ V}$                                                    |      |      |      |        |

| Output Noise                         | OUT <sub>NOISE</sub>            | 10 Hz to 100 kHz                                                                               |      | 1.6  |      | μV rms |

| •                                    |                                 | 100 Hz to 100 kHz                                                                              |      | 0.9  |      | μV rms |

| Noise Spectral Density               | OUT <sub>NSD</sub>              | 10 kHz to 1 MHz                                                                                |      | 1.7  |      | nV/√Hz |

| POWER SUPPLY REJECTION               | PSRR                            | 1 kHz to 100 kHz, $V_{IN} = 4.0 \text{ V}$ , $V_{OUT} = 3.3 \text{ V}$ ,                       |      | 80   |      | dB     |

| RATIO                                |                                 | $I_{LOAD} = 1.2 \text{ A}$                                                                     |      |      |      |        |

|                                      |                                 | 1 MHz, $V_{IN} = 4.0 \text{ V}$ , $V_{OUT} = 3.3 \text{ V}$ , $I_{LOAD} = 1.2 \text{ A}$       |      | 60   |      | dB     |

|                                      |                                 | 1 kHz to 100 kHz, $V_{IN} = 2.6 \text{ V}$ , $V_{OUT} = 1.8 \text{ V}$ ,                       |      | 80   |      | dB     |

|                                      |                                 | $I_{LOAD} = 1.2 A$                                                                             |      |      |      |        |

|                                      |                                 | 1 MHz, $V_{IN} = 2.6 \text{ V}$ , $V_{OUT} = 1.8 \text{ V}$ , $I_{LOAD} = 1.2 \text{ A}$       |      | 60   |      | dB     |

| OUTPUT VOLTAGE ACCURACY              |                                 |                                                                                                |      |      |      |        |

| Output Voltage <sup>1</sup>          | $V_{OUT}$                       |                                                                                                | 1.2  |      | 3.3  | V      |

| Initial Accuracy                     |                                 | $I_{LOAD} = 10 \text{ mA}, T_A = 25^{\circ}\text{C}$                                           | -0.6 |      | +0.6 | %      |

|                                      |                                 | $10 \text{ mA} < I_{LOAD} < 1.2 \text{ A}, T_A = 25^{\circ}\text{C}$                           | -1.0 |      | +1.0 | %      |

|                                      |                                 | $10 \text{ mA} < I_{LOAD} < 1.2 \text{ A}, T_A = -40^{\circ}\text{C to} + 125^{\circ}\text{C}$ | -1.5 |      | +1.5 | %      |

| REGULATION                           |                                 |                                                                                                |      |      |      |        |

| Line                                 | $\Delta V_{OUT}/\Delta V_{IN}$  | $V_{IN} = V_{OUT} + 0.5 \text{ V}$ or 2.3 V, whichever is greater to 5.5 V                     | -0.1 |      | +0.1 | %/V    |

| $Load^2$                             | $\Delta V_{OUT}/\Delta I_{OUT}$ | $I_{OUT} = 10 \text{ mA to } 1.2 \text{ A}$                                                    |      |      | 0.3  | %/A    |

| CURRENT-LIMIT THRESHOLD <sup>3</sup> | $I_{LIMIT}$                     |                                                                                                |      |      |      |        |

| REF                                  |                                 |                                                                                                |      | 22   |      | mA     |

| VOUT                                 |                                 |                                                                                                | 1.4  | 1.8  | 2.4  | A      |

| DROPOUT VOLTAGE <sup>4</sup>         | $V_{DROPOUT}$                   | $I_{OUT} = 600 \text{ mA}, V_{OUT} = 3.3 \text{ V}$                                            |      | 60   | 80   | mV     |

|                                      |                                 | $I_{OUT} = 1.2 \text{ A}, V_{OUT} = 3.3 \text{ V}$                                             |      | 120  | 170  | mV     |

| PULL-DOWN RESISTANCE                 |                                 | $EN = 0 \text{ V}, V_{IN} = 5.5 \text{ V}$                                                     |      |      |      |        |

| VOUT                                 | $V_{OUT\_PULL}$                 | $V_{OUT} = 1 V$                                                                                |      | 650  |      | Ω      |

| VREG                                 | $V_{REG\_PULL}$                 | $V_{REG} = 1 V$                                                                                |      | 31   |      | kΩ     |

| REF                                  | V <sub>REF PULL</sub>           | $V_{REF} = 1 V$                                                                                |      | 850  |      | Ω      |

| BYP                                  | V <sub>BYP PULL</sub>           | $V_{BYP} = 1 V$                                                                                |      | 650  |      | Ω      |

| START-UP TIME <sup>5</sup>           |                                 | $V_{OUT} = 3.3 \text{ V}$                                                                      |      |      |      |        |

| VOUT                                 | t <sub>START-UP</sub>           |                                                                                                |      | 1.2  |      | ms     |

| VREG                                 | t <sub>REG START-UP</sub>       |                                                                                                |      | 0.6  |      | ms     |

| REF                                  | t <sub>REF_START-UP</sub>       |                                                                                                | 1    | 0.5  |      | ms     |

| THERMAL SHUTDOWN                     | -KLI_STAKI=UI                   |                                                                                                | 1    |      |      | -      |

| Threshold                            | $\mathrm{TS}_{\mathrm{SD}}$     | T <sub>J</sub> rising                                                                          | 1    | 150  |      | °C     |

| Hysteresis                           | $TS_{SD\_HYS}$                  | -,                                                                                             | 1    | 150  |      | °C     |

| UNDERVOLTAGE THRESHOLDS              | TO2D_HA2                        |                                                                                                | +    | 1.5  |      | + -    |

| Input Voltage                        |                                 |                                                                                                | 1    |      |      |        |

|                                      | UVLO <sub>RISE</sub>            |                                                                                                | 1    | 2.22 | 2.29 | v      |

| Rising                               |                                 |                                                                                                | 1.05 |      | 2.29 |        |

| Falling                              | UVLOFALL                        |                                                                                                | 1.95 | 2.02 |      | V      |

| Hysteresis                           | UVLO <sub>HYS</sub>             |                                                                                                |      | 200  |      | mV     |

Rev. 0 - 3/22 -

| Parameter                         | Symbol                   | Test Conditions/Comments                                   | Min  | Тур  | Max  | Unit |

|-----------------------------------|--------------------------|------------------------------------------------------------|------|------|------|------|

| VREG UVLO THRESHOLDS <sup>6</sup> |                          |                                                            |      |      |      |      |

| Rising                            | VREGUVLO <sub>RISE</sub> |                                                            |      |      | 1.94 | V    |

| Falling                           | VREGUVLOFALL             |                                                            | 1.60 |      |      | V    |

| Hysteresis                        | VREGUVLO <sub>HYS</sub>  |                                                            |      | 185  |      | mV   |

| EN INPUT PRECISION                |                          | $2.3 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}$ |      |      |      |      |

| EN Input                          |                          |                                                            |      |      |      |      |

| Logic High                        | V <sub>EN_HIGH</sub>     |                                                            | 1.13 | 1.22 | 1.31 | V    |

| Logic Low                         | $V_{EN\_LOW}$            |                                                            | 1.05 | 1.13 | 1.22 | V    |

| Logic Hysteresis                  | V <sub>EN_HYS</sub>      |                                                            |      | 90   |      | mV   |

| LEAKAGE CURRENT                   |                          |                                                            |      | •    | •    |      |

| REF_SENSE                         | $I_{REF\_SENSE\_LKG}$    |                                                            |      | 10   |      | nA   |

| EN                                | $I_{EN\_LKG}$            | $EN = V_{IN}$ or $GND$                                     |      | 0.01 | 1    | μΑ   |

$<sup>^1</sup>$  ADP7156 は 1.2 V  $\sim$  3.3 V の範囲で 16 種類の標準電圧 1.2 V、1.3 V、1.5 V、1.6 V、1.8 V、2.0 V、2.2 V、2.5 V、2.6 V、2.7 V、2.8 V、2.9 V、3.0 V、3.1 V、3.2 V、3.3 V を提供しています。

### 入力コンデンサと出力コンデンサの推奨仕様

#### 表 3.

| Parameter                                   | Symbol           | Test Conditions/Comments                             | Min   | Тур | Max | Unit |

|---------------------------------------------|------------------|------------------------------------------------------|-------|-----|-----|------|

| MINIMUM CAPACITANCE                         |                  | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ |       |     |     |      |

| Input <sup>1</sup>                          | $C_{IN}$         |                                                      | 10.0  |     |     | μF   |

| Regulator                                   | $C_{REG}$        |                                                      | 1.0   |     |     | μF   |

| Output <sup>1</sup>                         | $C_{OUT}$        |                                                      | 10.0  |     |     | μF   |

| Bypass                                      | $C_{BYP}$        |                                                      | 1.0   |     |     | μF   |

| Reference                                   | $C_{REF}$        |                                                      | 1.0   |     |     | μF   |

| CAPACITOR EFFECTIVE SERIES RESISTANCE (ESR) |                  | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ |       |     |     |      |

| $C_{OUT}, C_{IN}$                           | $R_{ESR}$        |                                                      | 0.001 |     | 0.1 | Ω    |

| $C_{REG}$ , $C_{REF}$                       | R <sub>ESR</sub> |                                                      | 0.001 |     | 0.2 | Ω    |

| $C_{BYP}$                                   | R <sub>ESR</sub> |                                                      | 0.001 |     | 2.0 | Ω    |

<sup>1</sup> 最小入力容量と最小出力容量は、動作条件の全範囲で 7.0 μF より大きい必要があります。最小容量規定値を確実に満たすようにするため、デバイス選択時にアプリケーションの動作条件の全範囲を考慮する必要があります。 X7R タイプと X5R タイプのコンデンサの使用を推奨します。 Y5V コンデンサと Z5U コンデンサは、すべての低ドロップアウト・レギュレータに推奨しません。

Rev. 0 - 4/22 -

<sup>&</sup>lt;sup>2</sup>10 mA と 1.2 A 負荷を使用した端点計算を使用。

<sup>&</sup>lt;sup>3</sup> 電流制限閾値は、出力電圧が規定代表値の90%に低下する電流値として定義されます。例えば、3.0 V 出力電圧の電流制限値は、出力電圧が3.0 V の90% すなわち2.7 V に低下する電流値として定義されます。

<sup>&</sup>lt;sup>4</sup> ドロップアウト電圧は、入力電圧を公称出力電圧に設定したときの入力電圧—出力電圧間の電圧差として定義されます。ドロップアウト電圧は、2.3 V を超える出力電圧に対してのみ適用されます。

$<sup>^5</sup>$ スタートアップ時間は、 $V_{EN}$ の立上がりエッジから  $V_{OUT}$ 、 $V_{REG}$ または  $V_{REF}$ が公称値の  $90\,\%$  になるまでの時間として定義されます。

<sup>&</sup>lt;sup>6</sup> VREG UVLO 立上がり関値を通過するまで、出力電圧はディスエーブルされます。入力電圧 UVLO 立上がり関値を通過するまで、VREG 出力はディスエーブルされます。

### 絶対最大定格

表 4.

| Parameter                              | Rating                                                      |

|----------------------------------------|-------------------------------------------------------------|

| VIN to Ground                          | -0.3 V to +7 V                                              |

| VREG to Ground                         | -0.3 V to V <sub>IN</sub> , or +4 V<br>(whichever is less)  |

| VOUT to Ground                         | -0.3 V to V <sub>REG</sub> , or +4 V<br>(whichever is less) |

| VOUT_SENSE to Ground                   | -0.3 V to V <sub>REG</sub> , or +4 V<br>(whichever is less) |

| VOUT to VOUT_SENSE                     | ±0.3 V                                                      |

| BYP to VOUT                            | ±0.3 V                                                      |

| EN to Ground                           | -0.3 V to +7 V                                              |

| BYP to Ground                          | -0.3 V to V <sub>REG</sub> , or +4 V<br>(whichever is less) |

| REF to Ground                          | -0.3 V to V <sub>REG</sub> , or +4 V<br>(whichever is less) |

| REF_SENSE to Ground                    | -0.3 V to +4 V                                              |

| Storage Temperature Range              | −65°C to +150°C                                             |

| Operational Junction Temperature Range | -40°C to +125°C                                             |

| Soldering Conditions                   | JEDEC J-STD-020                                             |

上記の絶対最大定格を超えるストレスを加えると、デバイスに 恒久的な損傷を与えることがあります。この規定はストレス定 格のみを指定するものであり、この仕様の動作のセクションに 記載する規定値以上でのデバイス動作を定めたものではありま せん。製品を長時間絶対最大定格状態に置くと、製品の信頼性 に影響を与えることがあります。

### 熱データ

絶対最大定格は組み合わせてではなく、個別に適用されます。 ジャンクション温度を超えると ADP7156 は損傷を受けることが あります。周囲温度をモニタしても、TJが規定温度範囲内にあ るとは保証できません。消費電力が大きくかつ熱抵抗が高いア プリケーションでは、最大周囲温度を下げる必要があります。

中程度の消費電力で、プリント回路ボード(PCB)の熱抵抗が低いアプリケーションでは、ジャンクション温度が規定値内にある限り、最大周囲温度はこの最大値を超えてもかまいません。デバイスのジャンクション温度(T<sub>D</sub>)は、周囲温度(T<sub>A</sub>)、デバイスの消費電力( $P_D$ )、パッケージのジャンクション一周囲間の熱抵抗( $\theta_{JA}$ )に依存します。

最大ジャンクション温度  $(T_I)$  は、次式を使って周囲温度  $(T_A)$  と消費電力  $(P_D)$  から計算します。

$T_J = T_A + (P_D \times \theta_{JA})$

パッケージのジャンクション—周囲間の熱抵抗( $\theta_{IA}$ )は、4 層ボードを使ったモデリングと計算に基いています。ジャンクション—周囲間の熱抵抗は、アプリケーションとボード・レイアウトに強く依存します。最大消費電力が大きいアプリケーションでは、ボードの熱設計に注意が必要です。 $\theta_{IA}$  値は、PCB 材料、レイアウト、環境条件に依存して変化します。 $\theta_{IA}$  の規定値は、4 層の 4 インチ×3 インチ回路ボードに基づいています。ボード構造については JESD51-7 と JESD51-9 を参照してください。

$\Psi_{JB}$ はジャンクション—ボード間のサーマル・キャラクタライゼーション・パラメータで、単位は °C/W です。パッケージの  $\Psi_{JB}$ は、4層ボードを使ったモデリングと計算に基づいています。 JESD51-12 「Guidelines for Reporting and Using Electronic Package Thermal Information」には、サーマル・キャラクタライゼーション・パラメータは熱抵抗と同じではないと記載されています。  $\Psi_{JB}$ は、熱抵抗 ( $\theta_{JB}$ ) の場合のように 1 つのパスではなく、複数のサーマル・パスを通過する電力成分を表します。したがって、 $\Psi_{JB}$ サーマル・パスには、パッケージ上面からの対流やパッケージからの放射(実際のアプリケーションで  $\Psi_{JB}$ を有効にしている要因)が含まれます。最大ジャンクション温度 ( $T_{J}$ ) は、次式を使ってボード温度 ( $T_{B}$ ) と消費電力 ( $T_{B}$ ) から計算します。

$T_J = T_B + (P_D \times \Psi_{JB})$

$\Psi_{JB}$ の詳細については、JESD51-8 と JESD51-12 を参照してください。

### 熱抵抗

θJA、θJC、ΨJB は最悪の条件、すなわち、回路基板に表面実装パッケージをハンダ付けした状態で仕様規定しています。

表 5. 熱抵抗

| Package Type  | $\theta_{JA}$ | $\theta_{JC}$ | $\Psi_{JB}$ | Unit |

|---------------|---------------|---------------|-------------|------|

| 10-Lead LFCSP | 53.8          | 15.6          | 29.1        | °C/W |

| 8-Lead SOIC   | 50.4          | 42.3          | 30.1        | °C/W |

### ESD に関する注意

### ESD(静電放電)の影響を受けやすいデバイスです。

電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

Rev. 0 - 5/22 -

**ADP7156**

## ピン配置およびピン機能の説明

#### NOTES

1. THE EXPOSED PAD IS LOCATED ON THE BOTTOM OF THE PACKAGE. THE EXPOSED PAD ENHANCES THERMAL PERFORMACE, AND IT IS ELECTRICALLY CONNECTED TO GROUND INSIDE THE PACKAGE. CONNECT THE EXPOSED PAD TO THE GROUND PLANE ON THE BOARD TO ENSURE PROPER OPERATION.

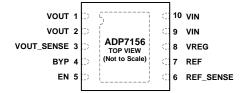

図 3. 10 ピン LFCSP ピン配置

### NOTES

NOTES

1. THE EXPOSED PAD IS LOCATED ON THE BOTTOM OF

THE PACKAGE. THE EXPOSED PAD ENHANCES THERMAL

PERFORMACE, AND IT IS ELECTRICALLY CONNECTED TO

GROUND INSIDE THE PACKAGE. CONNECT THE EXPOSED

PAD TO THE GROUND PLANE ON THE BOARD TO ENSURE

PROPER OPERATION.

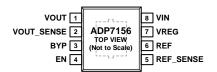

図 4.8 ピン SOIC のピン配置

#### 表 6. ピン機能の説明

| Р     | in No. |            |                                                                                                                                  |

|-------|--------|------------|----------------------------------------------------------------------------------------------------------------------------------|

| LFCSP | SOIC   | Mnemonic   | Description                                                                                                                      |

| 1, 2  | 1      | VOUT       | レギュレーションされた出力電圧。 $10\mu F$ 以上のコンデンサで VOUT をグラウンドへバイパスします。                                                                        |

| 3     | 2      | VOUT_SENSE | 出力検出。VOUT_SENSE は、内部で $10\Omega$ 抵抗を介して VOUT に接続されています。VOUT_SENSE は負荷のできるだけ近くに接続します。                                             |

| 4     | 3      | ВҮР        | 低ノイズ・バイパス・コンデンサ。ノイズを減らすため、BYP ピンとグラウンドの間に 1 μF のコンデンサを接続します。このピンには負荷を接続しないでください。                                                 |

| 5     | 4      | EN         | イネーブル。EN をハイ・レベルにするとレギュレータがオンし、ロー・レベルにするとレギュレータがオフします。自動スタートアップの場合は、EN を VIN に接続します。                                             |

| 6     | 5      | REF_SENSE  | リファレンス検出。REF_SENSE は REF ピンに接続します。REF_SENSE を VOUT または GND へ接<br>続しないでください。                                                      |

| 7     | 6      | REF        | 低ノイズ・リファレンス電圧出力。1 µF 以上のコンデンサで REF をグラウンドへバイパスします。<br>固定出力電圧の場合は、REF_SENSE を REF に短絡します。このピンには負荷を接続しないでください。                     |

| 8     | 7      | VREG       | 低ドロップアウト(LDO)アンプに対する安定化入力電源電圧。1 μF 以上のコンデンサで VREG を グラウンドへバイパスします。                                                               |

| 9, 10 | 8      | VIN        | 安定化入力電源電圧。10 μF 以上のコンデンサで VIN をグラウンドへバイパスします。                                                                                    |

|       |        | EP         | エクスポーズド・パッド。エクスポーズド・パッドはパッケージ底面にあります。エクスポーズド・パッドは熱性能を強化し、パッケージ内部でグラウンドに電気的に接続されています。エクスポーズド・パッドは回路ボードのグラウンド・プレーンへ接続し、正常動作を保証します。 |

-6/22 -Rev. 0

## 代表的な性能特性

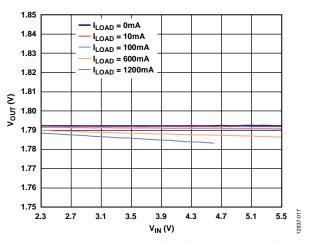

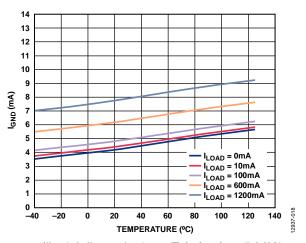

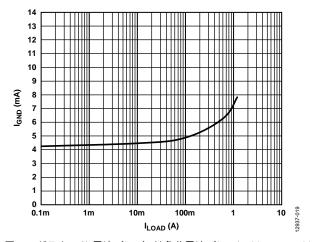

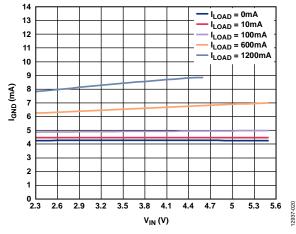

特に指定のない限り、 $V_{IN}$  =  $V_{OUT}$  + 0.5 V または 2.3 V(いずれか大きい方)、 $V_{EN}$  =  $V_{IN}$ ;  $I_{LOAD}$  = 10 mA;  $C_{IN}$  =  $C_{OUT}$  = 10  $\mu$ F;  $C_{REG}$  =  $C_{REF}$  =  $C_{BYP}$  = 1  $\mu$ F;  $T_A$  = 25  $^{\circ}$ C。

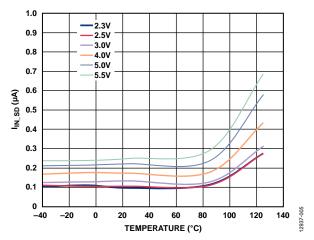

図 5. 様々な入力電圧( $V_{IN}$ )でのシャットダウン電流( $I_{IN\_SD}$ )の 温度特性、 $V_{OUT}$  = 1.8 V

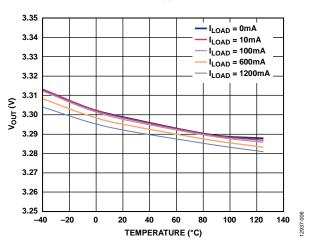

図 6. 様々な負荷での出力電圧 (V<sub>OUT</sub>) の温度特性、V<sub>OUT</sub> = 3.3 V

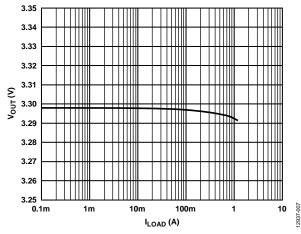

図 7. 出力電圧( $V_{OUT}$ )対負荷電流( $I_{LOAD}$ )、 $V_{OUT}$  = 3.3 V

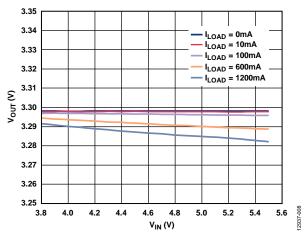

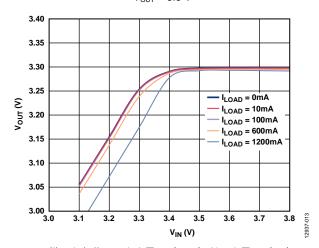

図 8. 様々な負荷での出力電圧( $V_{OUT}$ )対入力電圧( $V_{IN}$ )、  $V_{OUT}=3.3~V$

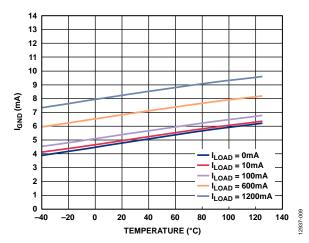

図 9. 様々な負荷でのグラウンド電流( $I_{GND}$ )対温度、  $V_{OUT}=3.3~V$

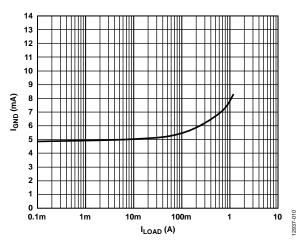

図 10. グラウンド電流( $I_{CND}$ )対負荷電流( $I_{LOAD}$ )、  $V_{OUT}=3.3~V$

Rev. 0 - 7/22 -

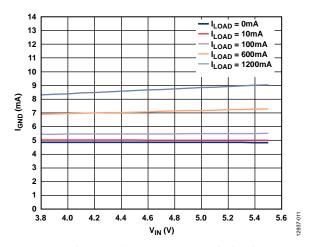

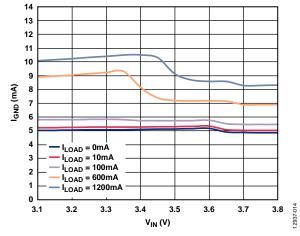

図 11. 様々な負荷でのグラウンド電流( $I_{GND}$ )対 入力電圧( $V_{IN}$ )、 $V_{OUT}$  = 3.3 V

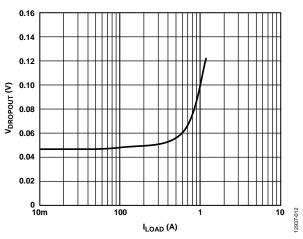

図 12. ドロップアウト電圧( $V_{DROPOUT}$ )対負荷電流( $I_{LOAD}$ )、  $V_{OUT}$  = 3.3 V

図 13. 様々な負荷での出力電圧( $V_{OUT}$ )対入力電圧( $V_{IN}$ )、 ドロップアウト時、 $V_{OUT}=3.3~V$

図 14. 様々な負荷でのグラウンド電流( $I_{GND}$ )対 入力電圧( $V_{IN}$ )、ドロップアウト時、 $V_{OUT}$  =  $3.3\,V$

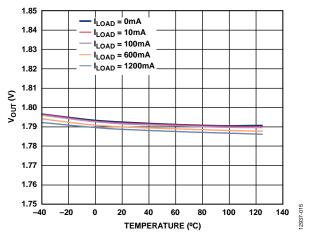

図 15. 様々な負荷での出力電圧( $V_{OUT}$ )の温度特性、  $V_{OUT}$  = 1.8 V

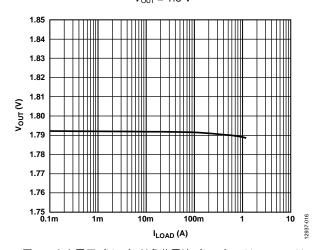

図 16. 出力電圧( $V_{OUT}$ )対負荷電流( $I_{LOAD}$ )、 $V_{OUT}$  = 1.8 V

Rev. 0 - 8/22 -

図 17. 様々な負荷での出力電圧( $V_{OUT}$ )対入力電圧( $V_{IN}$ )、  $V_{OUT}$  = 1.8 V

図 18. 様々な負荷でのグラウンド電流( $I_{GND}$ )の温度特性、  $V_{OUT}$  = 1.8 V

図 19. グラウンド 電流( $I_{GND}$ )対負荷電流( $I_{LOAD}$ )、 $V_{OUT}$  = 1.8 V

図 20. 様々な 負荷でのグラウンド 電流( $I_{GND}$ )対 入力電圧( $V_{IN}$ )、 $V_{OUT}$  = 1.8 V

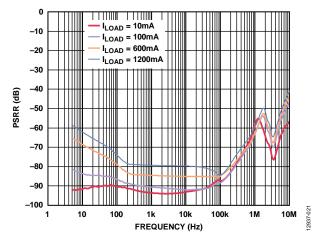

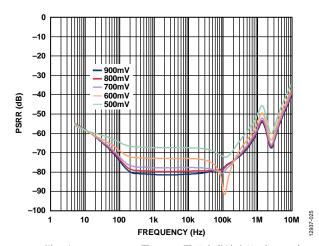

図 21. 様々な負荷での電源変動除去比(PSRR)の周波数特性、  $V_{OUT}=3.3~V$ 、 $V_{IN}=4.0~V$

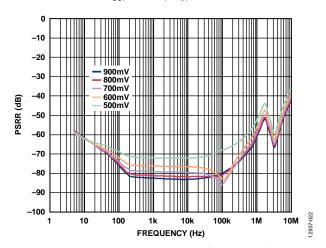

図 22. 様々なヘッドルーム電圧での電源変動除去比(PSRR)の 周波数特性、V<sub>OUT</sub> = 3.3 V、1.2 A 負荷

Rev. 0 - 9/22 -

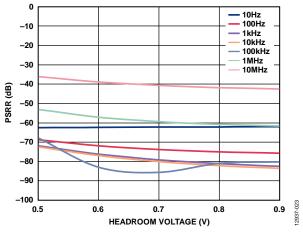

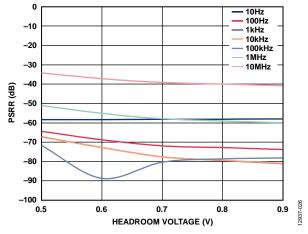

図 23. 様々な周波数での電源変動除去比 (PSRR) 対 ヘッドルーム電圧、V<sub>OUT</sub> = 3.3 V、1.2 A 負荷

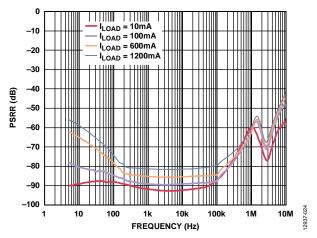

図 24. 様々な負荷での電源変動除去比(PSRR)の周波数特性、  $V_{OUT}$  = 1.8 V、 $V_{IN}$  = 2.6 V

図 25. 様々なヘッドルーム電圧での電源変動除去比(PSRR)の 周波数特性、V<sub>OUT</sub> = 1.8 V、1.2 A 負荷

図 26. 様々な周波数での電源変動除去比 (PSRR) 対 ヘッドルーム電圧、V<sub>OUT</sub> = 1.8 V、1.2 A 負荷

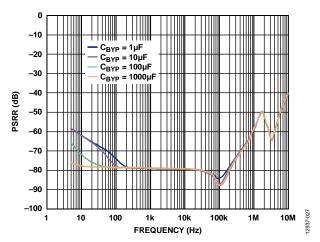

図 27. 様々な  $C_{BYP}$ 値での電源変動除去比(PSRR)の 周波数特性、 $V_{OUT}=3.3~V$ 、 $V_{IN}=4.0~V$ 、1.2 A 負荷

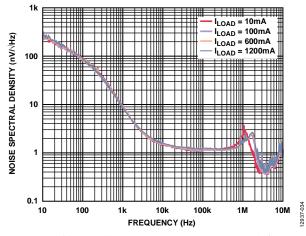

図 28. RMS 出力ノイズ対負荷電流

Rev. 0 - 10/22 -

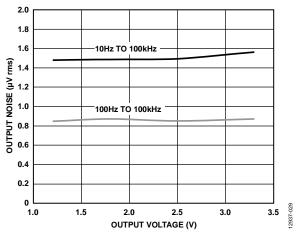

図 29. RMS 出力ノイズ対出力電圧

図 30. 様々な  $C_{BYP}$ 値でのノイズ・スペクトル密度の周波数特性

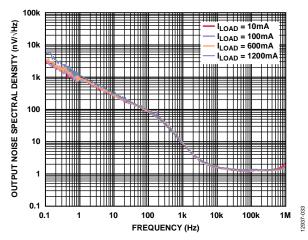

図 31. 様々な負荷での出力ノイズ・スペクトル密度の 周波数特性、0.1 Hz ~ 1 MHz

図 32. 様々な負荷での出力ノイズ・スペクトル密度の 周波数特性、10 Hz ~ 10 MHz

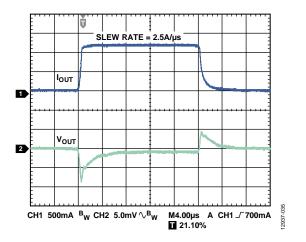

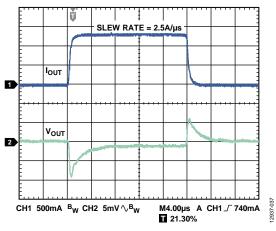

図 33. 負荷過渡応答、 $I_{LOAD}$  = 100 mA  $\sim$  1.2 A、 $V_{OUT}$  = 3.3 V、 $V_{IN}$  = 4.0 V、チャンネル 1 =  $I_{OUT}$ 、チャンネル 2 =  $V_{OUT}$

図 34. 負荷過渡応答、 $I_{LOAD}$  = 100 mA  $\sim$  1.2 A、 $V_{OUT}$  = 3.3 V、 $V_{IN}$  = 4.0 V、 $C_{OUT}$  = 22  $\mu$ F、チャンネル 1 =  $I_{OUT}$ 、チャンネル 2 =  $V_{OUT}$

Rev. 0 - 11/22 -

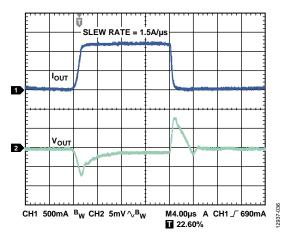

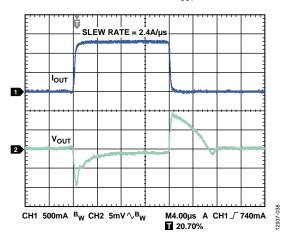

図 35. 負荷過渡応答、 $I_{LOAD}$  = 100 mA  $\sim$  1.2 A、 $V_{OUT}$  = 1.8 V、 $V_{IN}$  = 2.5 V、チャンネル 1 =  $I_{OUT}$ 、チャンネル 2 =  $V_{OUT}$

図 36. 負荷過渡応答、 $I_{LOAD}$  = 100 mA  $\sim$  1.2 A、  $V_{OUT}$  = 1.8 V、 $V_{IN}$  = 2.5 V、 $C_{OUT}$  = 22  $\mu$ F、チャンネル 1 =  $I_{OUT}$ 、チャンネル 2 =  $V_{OUT}$

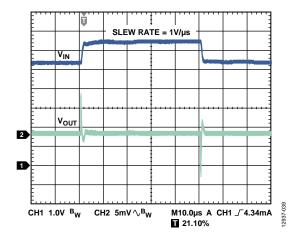

図 37. ライン過渡応答、1 V 入力ステップ、 $I_{\text{LOAD}}$  = 1.2 A、 $V_{\text{OUT}}$  = 3.3 V、 $V_{\text{IN}}$  = 3.8 V、 $\mathcal{F}$  ャンネル 1 =  $V_{\text{IN}}$ 、 $\mathcal{F}$  ャンネル 2 =  $V_{\text{OUT}}$

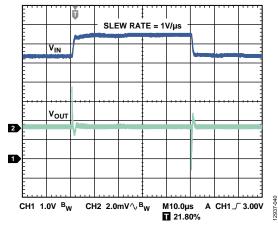

図 38. ライン過渡応答、1 V 入力ステップ、 $I_{LOAD}$  = 1.2 A、 $V_{OUT}$  = 1.8 V、 $V_{IN}$  = 2.5 V、 チャンネル 1 =  $V_{IN}$ 、 チャンネル 2 =  $V_{OUT}$

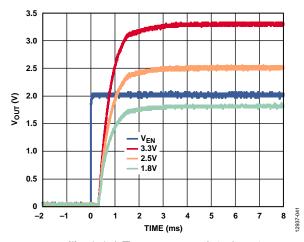

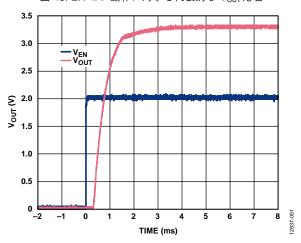

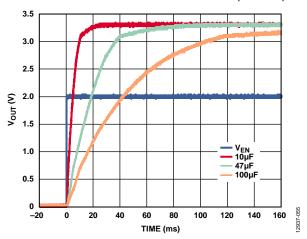

図 39. 様々な出力電圧での、 $V_{EN}$ の立上がりからの  $V_{OUT}$  スタートアップ時間、 $V_{IN}$  = 5 V、 $C_{BYP}$  = 1  $\mu F$

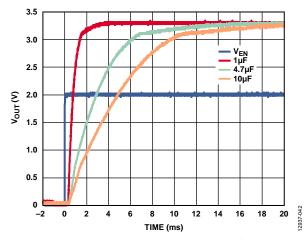

図 40. 様々な  $C_{BYP}$ 値での  $V_{OUT}$  スタートアップ時間動作、  $V_{OUT}$  = 3.3 V

Rev. 0 - 12/22 -

### 動作原理

ADP7156 は、無線周波(RF)アプリケーションを対象とした、超低ノイズで高 PSRR のリニア・レギュレータです。入力電圧範囲は  $2.3~V\sim5.5~V$  で、1.2~A までの負荷電流を供給することができます。シャットダウン消費電流は室温で  $0.2~\mu A$ (代表値)です。

ADP7156 は  $10 \, \mu F$  のセラミック・コンデンサで使用するように 最適化されており、過渡性能が優れています。

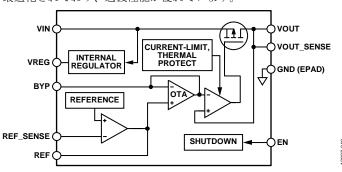

図 41. 簡略化した内部ブロック図

ADP7156はリファレンス電圧、エラーアンプ、P チャンネル MOSFET パス・トランジスタで構成されています。出力電流は、エラーアンプによって制御される PMOS パス・デバイスを経由して供給されます。エラーアンプはリファレンス電圧と出力からの帰還電圧を比較して、その差を増幅します。帰還電圧がリファレンス電圧より低いと、PMOS デバイスのゲート電圧が低くなるので、通過する電流が増え、出力電圧が上昇します。帰還電圧がリファレンス電圧より高いと、PMOS デバイス

のゲート電圧が高くなるので、通過する電流が減り、出力電圧 が低下します。

ADP7156 はリファレンス電圧のフィルタリングを強化することにより、 $10\,\mathrm{kHz}\sim1\,\mathrm{MHz}$  で  $1.7\,\mathrm{nV/Hz}$  (代表値) の出力ノイズ・スペクトル密度を達成できます。エラーアンプは常にユニティ・ゲインであるため、出力ノイズは出力電圧に依存しません。

ADP7156 は EN ピンを使って、通常の動作状態で VOUT ピンをイネーブル/ディスエーブルします。 EN がハイ・レベルのとき VOUT がオンし、EN がロー・レベルのとき VOUT がオフします。自動スタートアップの場合は、EN を VIN へ接続します。

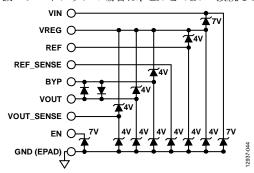

図 42. 簡略化した ESD 保護のブロック図

ESD 保護デバイスは、ブロック図ではツェナー・ダイオードとして示してあります(図 42 参照)。

Rev. 0 – 13/22 –

## アプリケーション情報

### ADISIMPOWER デザイン・ツール

ADP7156には ADIsimPower™ デザイン・ツール・セットを使用できます。ADIsimPower は、特定の設計目標に対して最適化された電源デザインを生成するツールのコレクションです。これらのツールを使用すると、わずか数分で必要なすべての回路図と部品表を作成し、性能を計算することができます。

ADIsimPower は、IC と実際の外付け部品の動作条件や制限事項を考慮しながら、コスト、面積、効率、デバイス数についてデザインを最適化することができます。詳細と ADIsimPower デザイン・ツールの取得については、www.analog.com/ADIsimPower をご覧ください。

#### ADISIIII OWCI をこ見くたらい

コンデンサの選択

積層セラミック・コンデンサ(MLCC)はサイズが小さく、ESRとESLが低く、動作温度範囲が広いので、バイパス・コンデンサに最適です。ただし、欠点はあります。誘電体材料によっては、温度、DCバイアス、AC信号レベルの変化に対して容量が大幅に変化します。そのため、適切なコンデンサを選択すると、最適な回路性能が得られます。

### 出力コンデンサ

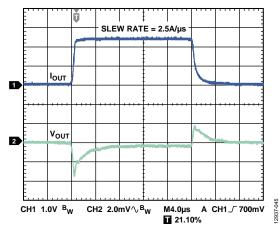

ADP7156 はセラミック・コンデンサで動作するように設計されていますが、ESR 値に注意すれば一般に使用されているほとんどのコンデンサで動作します。出力コンデンサの ESR は、LDO 制御ループの安定性に影響を与えます。ADP7156 の安定性のためには、ESR が  $0.1~\Omega$  以下の最小  $10~\mu F$  のコンデンサの使用を推奨します。出力容量は負荷電流の変化に対する過渡応答にも影響を与えます。大きな値の出力容量を使用すると、負荷電流の大きな変化に対する ADP7156 の過渡応答を改善することができます。 $10~\mu F$  の出力容量に対する過渡応答を図 43 に示します。

図 43. 出力過渡応答 V<sub>OUT</sub> = 3.3 V、C<sub>OUT</sub> = 10 μF、 チャンネル 1 = 負荷電流、チャンネル 2 = V<sub>OUT</sub>

### 入力コンデンサと VREG コンデンサ

VIN ピンとグラウンドの間に 10 μF のコンデンサを接続すると、特に入力パターンが長いかソース・インピーダンスが高い場合、PCB レイアウトに対する回路の感受性を小さくすることができます。

安定性と PSRR 性能をできるだけ高く保つために、VREG とグ ラウンドとの間に 1μF 以上のコンデンサを接続してください。

### REF コンデンサ

REF コンデンサ  $C_{REF}$  は、リファレンス・アンプを安定させるために必要です。REF とグラウンドの間に  $1\,\mu F$  以上の出力コンデンサを接続してください。

### BYP コンデンサ

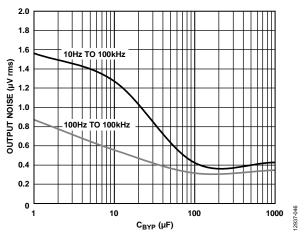

BYP コンデンサ  $C_{BYP}$ は、リファレンス・バッファをフィルタするために必要で、通常、  $1 \mu F$  のコンデンサを BYP とグラウンドの間に接続します。最小  $0.1 \mu F$  のコンデンサを使用できます。ただし、LDO の出力ノイズ電圧が大きくなります。

さらに、BYP コンデンサ値を大きくして、 $1\,\mathrm{kHz}$  以下のノイズを小さくすることができますが、LDO レギュレータのスタートアップ時間が長くなります。 $C_\mathrm{BYP}$ の値を非常に大きくすると、 $10\,\mathrm{Hz}$  以下のノイズが大幅に減少します。固体タンタル・コンデンサはマイクロフォン・ノイズの問題の影響を受けにくいので、約  $33\,\mu\mathrm{F}$  を超えるコンデンサにはタンタル・コンデンサを推奨します。高い周波数で優れたノイズ性能を維持するには、 $1\,\mu\mathrm{F}$  のセラミック・コンデンサを大きなタンタル・コンデンサに並列接続することを推奨します。

図 44. RMS 出力ノイズ対バイパス・コンデンサ( $C_{BYP}$ )

Rev. 0 - 14/22 -

図 45. 様々な  $C_{\text{BYP}}$ 値でのノイズ・スペクトル密度の周波数特性

### コンデンサの特性

最小容量と最大 ESR の条件を満たす限り、任意の高品質セラミック・コンデンサを ADP7156 に使うことができます。セラミック・コンデンサはさまざまな誘電体を使用して作られており、温度や印加電圧に対する動作がそれぞれ異なります。必要な温度範囲と DC バイアス条件に対して最小容量を保証できるような、適切な誘電体が使われているコンデンサを選ぶ必要があります。電圧定格が  $6.3~V\sim50~V$  で、X5R または X7R の誘電体のものを推奨します。Y5V と Z5U の誘電体のものは温度特性と DC バイアス特性が十分でないため推奨しません。

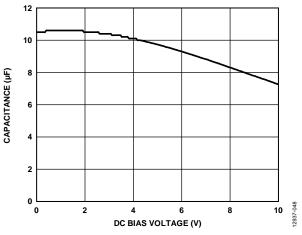

DC 電圧バイアスに対する、1206、10  $\mu$ F、10 V の X5R コンデンサの容量の変化を図 46 に示します。コンデンサの電圧安定性は、コンデンサのサイズと電圧定格の影響を大きく受けます。一般に、コンデンサのパッケージが大きいほど、または電圧定格が大きいほど、優れた安定性を示します。 X5R 誘電体の温度変動は、-40 °C  $\sim$  +85 °C の温度範囲で約 $\pm$ 15 % であり、パッケージ・サイズまたは電圧定格によって変化することはありません。

図 46. 容量対 DC バイアス電圧

温度、部品許容誤差、電圧に対するコンデンサの変動を考慮した、ワーストケース容量を求めるには、式1を使います。

$$C_{EFF} = C_{BIAS} \times (1 - tempco) \times (1 - TOL) \tag{1}$$

ここで、

CEFF はワーストケースの容量、

CBIAS は動作電圧での実効容量、

tempco はワーストケースのコンデンサ温度係数、

TOL はワーストケースの部品許容誤差です。

この例では、-40 °C  $\sim +85$  °C でのワーストケース温度係数 (tempco) を、X5R 誘電体では 15 % と仮定しています。図 46 に示すように、コンデンサの許容誤差 (TOL) は 10 %、かつ 5 V で  $C_{BIAS} = 9.72$   $\mu F$  と仮定しています。

これらの値を式1に代入すると次のようになります。

$$C_{EFF} = 9.72 \ \mu\text{F} \times (1 - 0.15) \times (1 - 0.1) = 7.44 \ \mu\text{F}$$

したがって、この例で選択したコンデンサは、選択した出力電圧で、温度と許容誤差に対する LDO の最小容量条件を満たします。

ADP7156の性能を保証するには、DC バイアス、温度、許容誤差がコンデンサの動作におよぼす影響をアプリケーションごとに評価することが不可欠です。

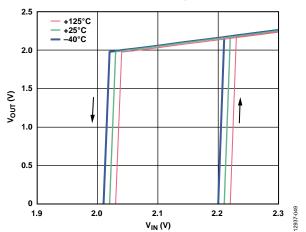

### 低電圧ロックアウト(UVLO)

ADP7156 は入力電圧がレギュレータの最小入力電圧定格を下回るとき出力電圧をディスエーブルする UVLO 回路も内蔵しています。上側と下側の閾値は、200 mV (代表値)のヒステリシスを持つように内部で固定されています。

図 47. 様々な温度での代表的な UVLO 動作、Vout = 3.3 V

UVLO 機能の代表的な動作を図 47 に示します。このヒステリシスは、入力電圧が閾値を通過するときノイズによって発生することがあるオン/オフ発振を防止します。

Rev. 0 – 15/22 –

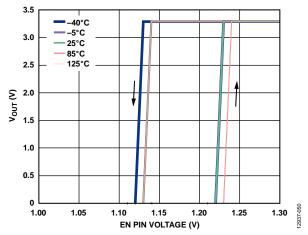

### プログラマブルな高精度イネーブル

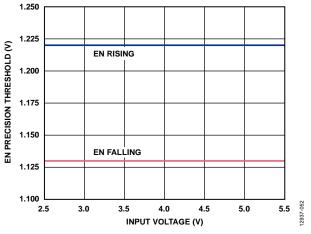

ADP7156 では EN ピンを使って、通常の動作状態で VOUT ピンをイネーブル/ディスエーブルします。図 48 に示すように、EN の電圧が上昇して  $1.22\,\mathrm{V}$  (公称値) の上側閾値を上回ると、 $\mathrm{Vour}$  がオンします。EN の電圧が下降して  $1.13\,\mathrm{V}$  (公称値) の下側閾値を下回ると、 $\mathrm{Vour}$  がオフします。EN 閾値のヒステリシスは  $90\,\mathrm{mV}$  (代表値) です。

ADP7156は、VOUT、VREG、REF、BYPの各ピンに放電抵抗を内蔵しています。デバイスがディスエーブルされると、これらの抵抗がオンし、対応するコンデンサを瞬時に放電するのに役立ちます。

図 48. EN ピン動作に対する代表的な Vour 応答

図 49. EN ピン動作( $V_{EN}$ )に対する代表的な  $V_{OUT}$ 応答、  $V_{OUT}=3.3~V$ 、 $V_{IN}=5~V$ 、 $C_{BYP}=1~\mu F$

図 50. EN 高精度閾値(代表値)対入力電圧(V<sub>IN</sub>)

上側と下側の閾値は、2本の抵抗を使って公称 1.22 V の閾値より高く設定することができます。抵抗値  $R_{EN1}$  と  $R_{EN2}$  は次式によって求めます。

$R_{ENI} = R_{EN2} \times (V_{EN} - 1.22 \text{ V})/1.22 \text{ V}$

ここで、

$R_{EN2}$ の範囲は一般に  $10~{

m k}\Omega\sim 100~{

m k}\Omega$ 。  $V_{EN}$  は所望のオン電圧。

ヒステリシス電圧は次の倍率で大きくなります。

$(R_{EN1} + R_{EN2})/R_{EN1}$

図 51 に示す例では、EN 閾値は 2.44 V で、ヒステリシスは 200 mV です。

図 51. EN ピンの代表的な分圧器

EN ピンの代表的な分圧器構成を図 51 に示します。このヒステリシスは、EN ピンが閾値を通過するときに EN のノイズにより発生するおそれのあるオン/オフ発振を防止します。

Rev. 0 - 16/22 -

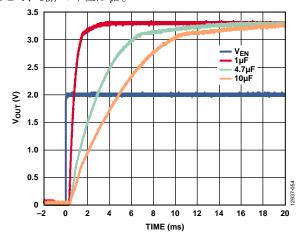

### スタートアップ時間

ADP7156 は内部ソフトスタート機能を使って、出力をイネーブルしたときの突入電流を制限します。3.3 V 出力でのスタートアップ時間は、EN のアクティブ関値を通過してから出力が最終値の90%に達するまでの約1.2 ms です。

出力電圧の秒で表した立上がり時間 (10% から 90%) は、およそ次のようになります。

$0.0012 \times C_{BYP}$

ここで、 $C_{BYP}$  の単位は  $\mu$ F。

図 52. 代表的なスタートアップ動作、 $C_{BYP}$  = 1  $\mu F \sim 10 \mu F$

図 53. 代表的なスタートアップ動作、 $C_{BYP}$  = 10  $\mu F\sim 100~\mu F$

### REF、BYP、VREG の各ピン

REF、BYP、VREG の各ピンには、内部で電圧( $V_{REF}$ 、 $V_{BYP}$ 、 $V_{REG}$ )が生成されます。これらには、正しく動作するために外付けバイパス・コンデンサが必要です。いかなる場合にもこれらのピンに負荷を接続しないでください。接続した場合、

ADP7156 のノイズと PSRR の性能が損われます。 $C_{BYP}$ 、 $C_{REF}$ 、 $C_{REG}$ の値を大きくしてもかまいませんが、スタートアップ時間が長くなります (スタートアップ時間のセクションを参照)。

### 電流制限 およびサーマル・シャットダウン

ADP7156 は過電流保護回路と熱過負荷保護回路により、過大な消費電力による損傷から保護されています。ADP7156 は、出力負荷が 1.8 A (代表値) に達すると電流を制限するように設計されています。出力負荷が 1.8 A を超えると、出力電圧を下げて一定の電流限界値を維持します。

ADP7156 のジャンクション温度が 150 °C を上回ると、サーマル・シャットダウン回路により出力電圧がオフし、出力電流がゼロに減少します。ジャンクション温度が極端に高くなる要因は、大電流動作、回路ボードの設計不備、高い周囲温度などです。 15 °C のヒステリシスが含まれているため、サーマル・シャットダウン後にチップ温度が 135 °C を下回るまで、ADP7156 は通常動作に復帰しません。デバイスがサーマル・シャットダウンから復帰すると、ソフトスタートが開始され、突入電流を小さく抑えます。

電流制限保護とサーマル・シャットダウンは、偶発的な過負荷状態に対してデバイスを保護することを目的としています。例えば、VOUTとグラウンドの間の短絡や、極めて長いソフト・スタート・タイマーは、電流制限とサーマル・シャットダウンの間で熱的発振を引き起こします。

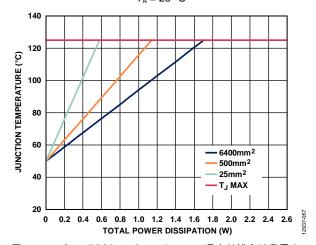

### 熱に対する考慮事項

入力—出力間の電圧差が低いアプリケーションでは、ADP7156 の発熱は大きくなりませんが、周囲温度が高く、入力電圧が高いアプリケーションでは、パッケージの発熱が大きくなって、チップのジャンクション温度が最大ジャンクション温度 125 ℃ を超えることがあります。

チップのジャンクション温度は、式 2 に示すように、周囲温度と電力消費によるパッケージの温度上昇の和です。高信頼性動作を保証するためには、ADP7156 のジャンクション温度が  $125\,^{\circ}$ C を超えてはなりません。ジャンクション温度をこの最大値より低く抑えるには、ジャンクション温度の変化に影響を与えるパラメータを知っておく必要があります。これらのパラメータには周囲温度、パワー・デバイスの消費電力、ジャンクション一周囲間の熱抵抗( $\theta_{JA}$ )があります。 $\theta_{JA}$ 値は、パッケージ組み立て材料とパッケージのエクスポーズド・パッド(グラウンド)を PCB へハンダ付けする部分に使用する銅の量に依存します。

Rev. 0 - 17/22 -

PCB の銅サイズに対する 8 ピン SOIC パッケージと 10 ピン LFCSP パッケージの  $\theta$  JA 値(代表値)を表 7 に示し、8 ピン SOIC パッケージと 10 ピン LFCSP パッケージの  $\Psi$ JB (代表値)を表 8 に示します。

表 7. θ<sub>JA</sub> 値(代表値)

|                                | $\theta_{JA}$ (°C/W) |             |  |  |

|--------------------------------|----------------------|-------------|--|--|

| Copper Size (mm <sup>2</sup> ) | 10-Lead LFCSP        | 8-Lead SOIC |  |  |

| 251                            | 130.2                | 123.8       |  |  |

| 100                            | 93.0                 | 90.4        |  |  |

| 500                            | 65.8                 | 66.0        |  |  |

| 1000                           | 55.6                 | 56.6        |  |  |

| 6400                           | 44.1                 | 45.5        |  |  |

<sup>「</sup>デバイスは最小サイズのピン・パターンにハンダ付け。

### 表 8. Ψ<sub>JB</sub> 値(代表値)

| Package       | Ψ <sub>JB</sub> (°C/W) |

|---------------|------------------------|

| 10-Lead LFCSP | 29.1                   |

| 8-Lead SOIC   | 30.1                   |

次式から ADP7156 のジャンクション温度(T<sub>1</sub>)を計算します。

$$T_J = T_A + (P_D \times \theta_{JA}) \tag{2}$$

ここで、

TA は周囲温度。

PD はチップの消費電力で、次式で与えられます。

$$P_D = ((V_{IN} - V_{OUT}) \times I_{LOAD}) + (V_{IN} \times I_{GND})$$

(3)

ここで、

$V_{IN}$  と  $V_{OUT}$  は、それぞれ入力電圧と出力電圧。

ILOAD は負荷電流。

IGND はグラウンド電流。

グラウンド電流による消費電力は小さいため無視できます。このため、ジャンクション温度の式は次のように簡単になります。

$$T_{J} = T_{A} + (((V_{IN} - V_{OUT}) \times I_{LOAD}) \times \theta_{JA})$$

$$\tag{4}$$

式4に示すように、与えられた周囲温度、入力と出力間の電圧 差、および連続負荷電流に対して、ジャンクション温度が 125 ℃ を超えないようにするため、PCB に対する最小銅サイズ の要件が存在します。

ADP7156のピンとエクスポーズド・パッドがハンダ付けされる場所の銅の量を増やすとパッケージからの放熱を改善することができます。パッケージの下にサーマル・プレーンを追加しても、熱性能が向上します。ただし、表7に示すように、結局は効果の減少点に到達して、それ以上銅面積を増やしてもジャンクション—周囲間の熱抵抗はわずかしか減少しません。

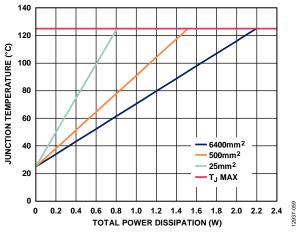

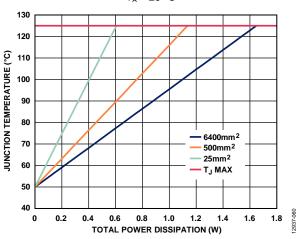

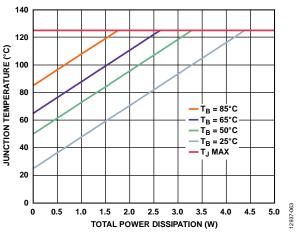

様々な周囲温度、消費電力、PCB の銅面積に対するジャンクション温度の計算結果を図 54 ~ 図 59 に示します。

図 54. 10 ピン LFCSP のジャンクション温度対総合消費電力、  $T_A=25\,^{\circ}\mathrm{C}$

図 55. 10 ピン LFCSP のジャンクション温度対総合消費電力、  $T_A=50$  °C

図 56. 10 ピン LFCSP のジャンクション温度対総合消費電力、  $T_A=85~^{\circ}C$

Rev. 0 — 18/22 —

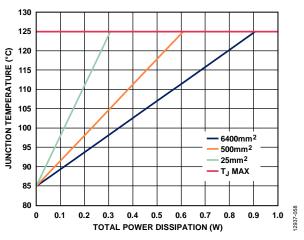

図 57.8 ピン SOIC のジャンクション温度対総合消費電力、  $T_A=25\,^{\circ}\mathrm{C}$

図 58.8 ピン SOIC のジャンクション温度対総合消費電力、  $T_A=50\,^{\circ}\mathrm{C}$

図 59.8 ピン SOIC のジャンクション温度対総合消費電力、 T<sub>A</sub> = 85 °C

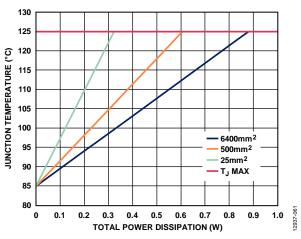

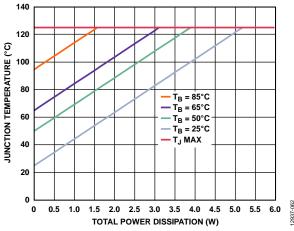

### サーマル・キャラクタライゼーション・パラメータ (Ψ<sub>JB</sub>)

ボード温度が既知の場合、サーマル・キャラクタライゼーション・パラメータ  $\Psi_{IB}$  を使ってジャンクション温度の上昇を推定します(図 60 と図 61 参照)。次式を使って、評価用ボードの温度( $T_B$ )と消費電力( $P_D$ )から最大ジャンクション温度( $T_I$ )を計算します。

$$T_J = T_B + (P_D \times \Psi_{JB}) \tag{5}$$

$\Psi_{JB}$ の代表値は、10 ピン LFCSP パッケージの場合 29.1 °C/W、8 ピン SOIC パッケージの場合 30.1 °C/W です。

図 60. 10 ピン LFCSP のジャンクション温度対総合消費電力

図 61.8 ピン SOIC のジャンクション温度対総合消費電力

Rev. 0 - 19/22 -

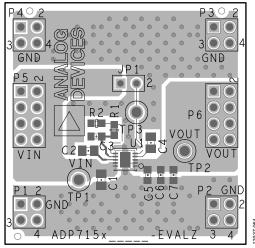

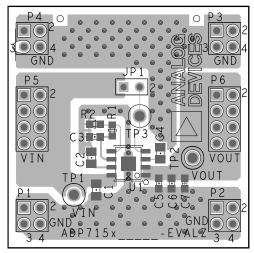

## PCB レイアウトに関する検討事項

入力コンデンサは VIN ピンとグラウンドの間にできるだけ近づけて配置します。出力コンデンサは VOUT ピンとグラウンドの間にできるだけ近づけて配置します。 $V_{REG}$ 、 $V_{REF}$ 、 $V_{BYP}$  のためのバイパス・コンデンサ( $C_{REG}$ 、 $C_{REF}$ 、 $C_{BYP}$ )は、それぞれのピン(VREG、REF、BYP)とグラウンドの近くに配置します。0805、0603、および 0402 のサイズのコンデンサを使うと、面積が制限されているボード上で最小のフットプリントのソリューションを実現できます。エクスポーズド・パッドのグラウンド・メタルの量を最大にし、部品側にできるだけ多くのビアを使って放熱性を良くします。

図 62. 10 ピン LFCSP の PCB レイアウト例

図 63.8 ピン SOIC の PCB レイアウト例

37-065

Rev. 0 — 20/22 —

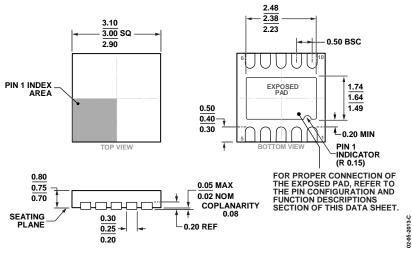

## 外形寸法

図 64. 10 ピン・リードフレーム・チップスケール・パッケージ[LFCSP] 3 mm × 3 mm ボディ、0.75 mm パッケージ高 (CP-10-9) 寸法: mm

COMPLIANT TO JEDEC STANDARDS MS-012-A A

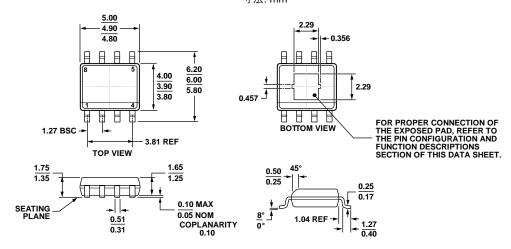

図 65. 8 ピン標準スモール・アウトライン・パッケージ、エクスポーズド・パッド付き [SOIC\_N\_EP] ナロー・ボディ (RD-8-1) 寸法: mm

Rev. 0 — 21/22 —

### オーダー・ガイド

| Model <sup>1, 2</sup> | Temperature Range | Output Voltage (V) | Package Description | Package Option | Branding |

|-----------------------|-------------------|--------------------|---------------------|----------------|----------|

| ADP7156ACPZ-1.2-R7    | −40°C to +125°C   | 1.2                | 10-Lead LFCSP       | CP-10-9        | LST      |

| ADP7156ACPZ-1.8-R7    | −40°C to +125°C   | 1.8                | 10-Lead LFCSP       | CP-10-9        | LSU      |

| ADP7156ACPZ-2.0-R7    | −40°C to +125°C   | 2.0                | 10-Lead LFCSP       | CP-10-9        | LTQ      |

| ADP7156ACPZ-2.5-R7    | −40°C to +125°C   | 2.5                | 10-Lead LFCSP       | CP-10-9        | LSV      |

| ADP7156ACPZ-2.8-R7    | −40°C to +125°C   | 2.8                | 10-Lead LFCSP       | CP-10-9        | LSW      |

| ADP7156ACPZ-3.0-R7    | −40°C to +125°C   | 3.0                | 10-Lead LFCSP       | CP-10-9        | LSY      |

| ADP7156ACPZ-3.3-R7    | −40°C to +125°C   | 3.3                | 10-Lead LFCSP       | CP-10-9        | LSZ      |

| ADP7156ARDZ-1.2-R7    | −40°C to +125°C   | 1.2                | 8-Lead SOIC_N_EP    | RD-8-1         |          |

| ADP7156ARDZ-1.8-R7    | −40°C to +125°C   | 1.8                | 8-Lead SOIC_N_EP    | RD-8-1         |          |

| ADP7156ARDZ-2.0-R7    | −40°C to +125°C   | 2.0                | 8-Lead SOIC_N_EP    | RD-8-1         |          |

| ADP7156ARDZ-2.5-R7    | −40°C to +125°C   | 2.5                | 8-Lead SOIC_N_EP    | RD-8-1         |          |

| ADP7156ARDZ-2.8-R7    | −40°C to +125°C   | 2.8                | 8-Lead SOIC_N_EP    | RD-8-1         |          |

| ADP7156ARDZ-3.0-R7    | −40°C to +125°C   | 3.0                | 8-Lead SOIC_N_EP    | RD-8-1         |          |

| ADP7156ARDZ-3.3-R7    | −40°C to +125°C   | 3.3                | 8-Lead SOIC_N_EP    | RD-8-1         |          |

| ADP7156CP-3.3EVALZ    |                   |                    | Evaluation Board    |                |          |

<sup>&</sup>lt;sup>1</sup>Z=RoHS 準拠製品。

Rev. 0 – 22/22 –

$<sup>^2</sup>$ 電圧オプション 1.3 V、1.5 V、1.6 V、2.2 V、2.6 V、2.7 V、2.9 V、3.1 V、3.2 V のデバイスを注文されるときは、最寄りのアナログ・デバイセズ代理店にご相談ください。