# ADG799A/ADG799G

## 特長

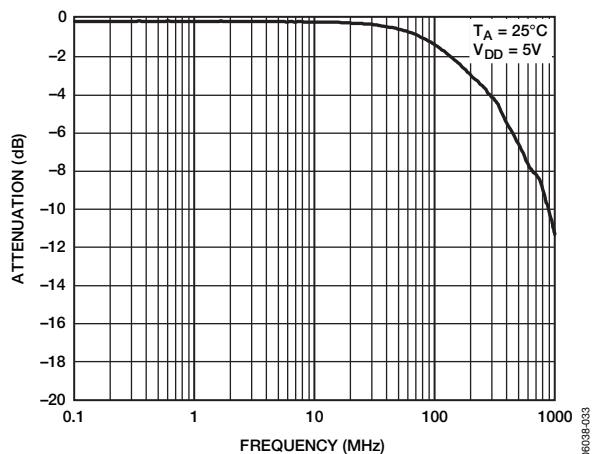

帯域幅：230MHz

低い挿入損失とオン抵抗：2.6Ω (typ)

オン抵抗平坦性：0.3Ω (typ)

3V/5V単電源動作

3.3Vのアナログ信号範囲（5V電源、75Ω負荷）

低い静止電源電流：1nA (typ)

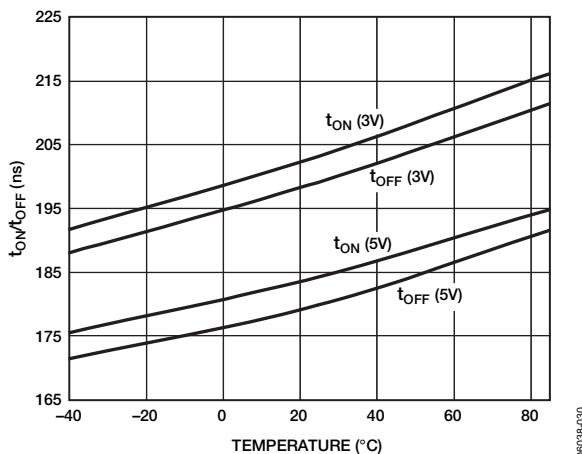

高速なスイッチング時間： $t_{ON}=184\text{ns}$ 、 $t_{OFF}=180\text{ns}$

I<sup>2</sup>C互換のインターフェース

小型の24ピンLFCSP

I<sup>2</sup>Cから制御可能な2つのロジック出力（ADG799Gの場合）

ESD保護

4kV人体モデル

200Vマシン・モデル

1kV電界誘導電荷デバイス・モデル

## アプリケーション

RGB/YPrPbビデオ・スイッチ

HDTV

プロジェクションTV

DVD-R/RW

AVレシーバ

## 概要

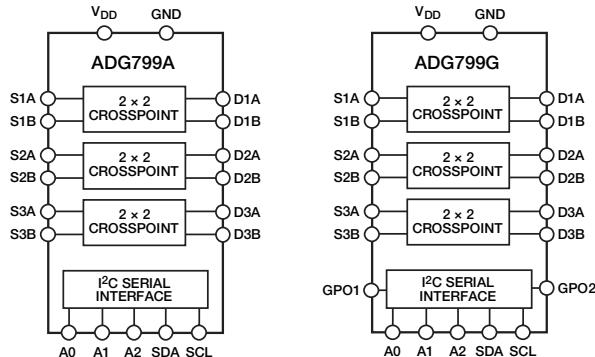

ADG799A/ADG799Gは、標準のI<sup>2</sup>Cシリアル・インターフェースを介して制御可能な3つの2×2クロスポイント・スイッチで構成される、モノリシックCMOSデバイスです。CMOS製造プロセスにより、きわめて小さい消費電力でありながら、高速なスイッチングと低いオン抵抗値を実現しています。

オン抵抗特性は、アナログ入力の全範囲にわたり非常にフラットです。広い帯域幅により、優れた直線性と低歪みを保証します。これらの機能と広い入力信号範囲を組み合わせたADG799A/ADG799Gは、ピクチャ・イン・ピクチャ・アプリケーション向けのRGB/YPrPbビデオ・スイッチなど、広範なTVアプリケーション向けのスイッチング・ソリューションに最適です。

これらのスイッチは、オン時に双方向に等しく導通します。オフ状態では、電源電圧までの信号レベルを阻止します。ADG799A/ADG799Gスイッチは、ブレーク・ビフォア・メークのスイッチング動作を実行します。ADG799Gの2本の汎用ロジック出力ピンは、I<sup>2</sup>Cインターフェースによって制御されます。I<sup>2</sup>Cインターフェースは、ビデオ・フィルタなど、他の非I<sup>2</sup>C互換デバイスの制御にも使用できます。

内蔵I<sup>2</sup>Cインターフェースにより、システムデザインの柔軟性が大幅に向上します。このインターフェースには、ユーザ調整可能な3本のI<sup>2</sup>Cアドレス・ピンがあり、同じバス上で最大8個のデバイスを使用できます。したがって、スイッチング・アレ

## 機能ブロック図

図1. ADG799AおよびADG799G

06038-001

イのサイズを増やすことで、ユーザはデバイスの機能を拡張できます。

ADG799A/ADG799Gは、3Vまたは5Vの単電源で動作し、小型の4mm×4mmボディ、24ピン、鉛フリーのLFCSPパッケージを採用しています。

## 製品のハイライト

- 広帯域幅：230MHz

- 超低消費電力

- 広い入力信号範囲

- I<sup>2</sup>Cシリアル・インターフェースを内蔵

- 小型の4mm×4mm、24ピン、鉛フリーLFCSPパッケージを採用

- ESD保護はESD協会の次の規格に従ってテスト済み

- 4kV HBM (ANSI/ESD STM5.1-2001)

- 200V MM (ANSI/ESD STM5.2-1999)

- 1kV FICDM (ANSI/ESD STM5.3.1-1999)

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。

※日本語データシートはREVISIONが古い場合があります。最新の内容については、英語版をご参照ください。

© 2006 Analog Devices, Inc. All rights reserved.

REV. 0

アナログ・デバイセズ株式会社

本 社／〒105-6891 東京都港区海岸1-16-1 ニューピア竹芝サウスタワービル

電話03(5402)8200

大阪営業所／〒532-0003 大阪府大阪市淀川区宮原3-5-36 新大阪MTビル2号

電話06(6350)6868

# ADG799A/ADG799G

## 目次

|                          |    |                               |    |

|--------------------------|----|-------------------------------|----|

| 特長                       | 1  | 用語集                           | 16 |

| アプリケーション                 | 1  | 動作原理                          | 17 |

| 機能ブロック図                  | 1  | I <sup>2</sup> Cシリアル・インターフェース | 17 |

| 概要                       | 1  | I <sup>2</sup> Cアドレス          | 17 |

| 製品のハイライト                 | 1  | 書き込み動作                        | 17 |

| 改訂履歴                     | 2  | LDSWビット                       | 19 |

| 仕様                       | 3  | パワーオン／ソフトウェア・リセット             | 19 |

| I <sup>2</sup> Cのタイミング仕様 | 7  | 読み出し動作                        | 19 |

| 絶対最大定格                   | 9  | 評価用ボード                        | 20 |

| ESDに関する注意                | 9  | ADG799G評価用ボードの使い方             | 20 |

| ピン配置とピン機能の説明             | 10 | 外形寸法                          | 23 |

| 代表的な性能特性                 | 11 | オーダー・ガイド                      | 23 |

| テスト回路                    | 14 |                               |    |

## 改訂履歴

7/06—Revision 0: Initial Version

## 仕様

特に指定のない限り、 $V_{DD}=5V\pm10\%$ 、GND=0V、 $T_A=-40\sim+85^\circ C$ 。

表1

| Parameter                                                     | Conditions                                                                                                  | Min    | Typ <sup>1</sup> | Max          | Unit     |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------|------------------|--------------|----------|

| ANALOG SWITCH                                                 |                                                                                                             |        |                  |              |          |

| Analog Signal Range <sup>2</sup>                              | $V_S = V_{DD}$ , $R_L = 1 M\Omega$<br>$V_S = V_{DD}$ , $R_L = 75 \Omega$                                    | 0<br>0 | 4<br>3.3         | 4<br>3.3     | V        |

| On Resistance, $R_{ON}$                                       | $V_D = 0 V$ , $I_{DS} = -10 mA$ , see Figure 22<br>$V_D = 0 V$ to $1 V$ , $I_{DS} = -10 mA$ , see Figure 22 |        | 2.6              | 5<br>5.5     | $\Omega$ |

| On Resistance Matching Between Channels, $\Delta R_{ON}$      | $V_D = 0 V$ , $I_{DS} = -10 mA$<br>$V_D = 1 V$ , $I_{DS} = -10 mA$                                          |        | 0.15             | 1.85<br>1.85 | $\Omega$ |

| On Resistance Flatness, $R_{FLAT(ON)}$                        | $V_D = 0 V$ to $1 V$ , $I_{DS} = -10 mA$                                                                    |        | 0.3              | 0.55         | $\Omega$ |

| LEAKAGE CURRENTS                                              |                                                                                                             |        |                  |              |          |

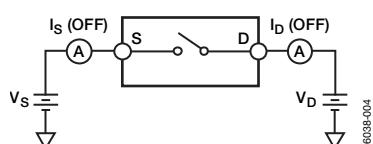

| Source Off Leakage ( $I_{S(OFF)}$ )                           | $V_D = 4 V$ / $1 V$ , $V_S = 1 V$ / $4 V$ , see Figure 23                                                   |        | $\pm 0.25$       |              | nA       |

| Drain Off Leakage ( $I_{D(OFF)}$ )                            | $V_D = 4 V$ / $1 V$ , $V_S = 1 V$ / $4 V$ , see Figure 23                                                   |        | $\pm 0.25$       |              | nA       |

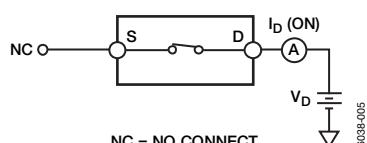

| Channel On Leakage ( $I_{D(ON)}$ , $I_{S(ON)}$ )              | $V_D = V_S = 4 V$ / $1 V$ , see Figure 24                                                                   |        | $\pm 0.25$       |              | nA       |

| DYNAMIC CHARACTERISTICS <sup>3</sup>                          |                                                                                                             |        |                  |              |          |

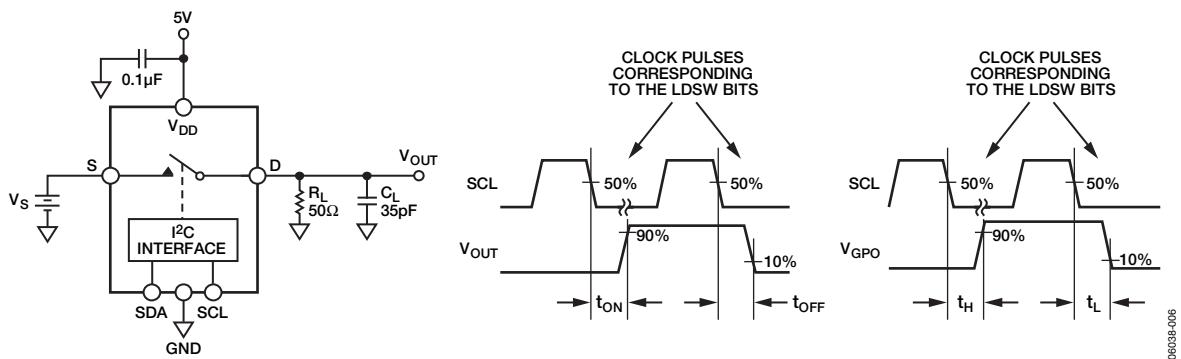

| $t_{ON}$ , $t_{ENABLE}$                                       | $C_L = 35 pF$ , $R_L = 50 \Omega$ , $V_S = 2 V$ , see Figure 28                                             |        | 184              | 240          | ns       |

| $t_{OFF}$ , $t_{DISABLE}$                                     | $C_L = 35 pF$ , $R_L = 50 \Omega$ , $V_S = 2 V$ , see Figure 28                                             |        | 180              | 235          | ns       |

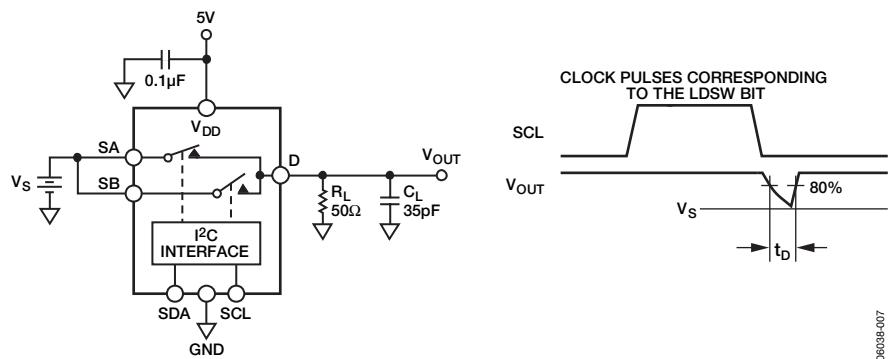

| Break-Before-Make Time Delay, $t_D$                           | $C_L = 35 pF$ , $R_L = 50 \Omega$ , $V_{S1} = V_{S2} = 2 V$ , see Figure 29                                 | 1      | 3                |              | ns       |

| $I^2C$ to GPO Propagation Delay, $t_H$ , $t_L$ (ADG799G only) |                                                                                                             |        |                  | 130          | ns       |

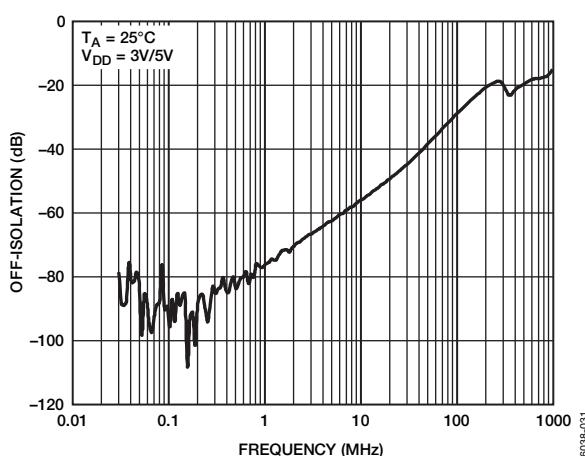

| Off Isolation                                                 | $f = 10 MHz$ , $R_L = 50 \Omega$ , see Figure 26                                                            |        | -60              |              | dB       |

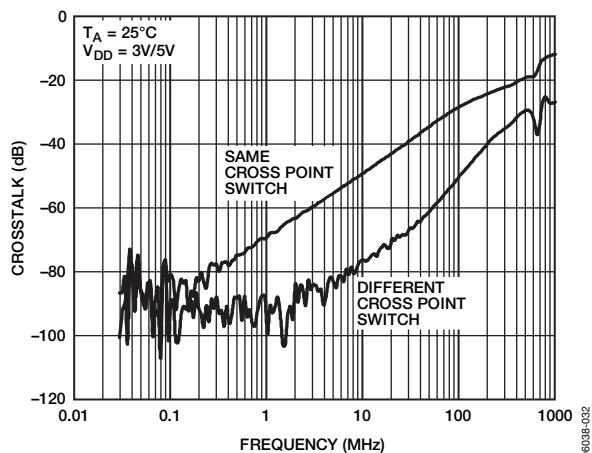

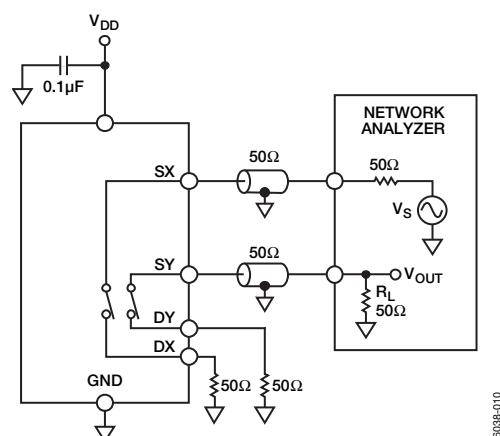

| Channel-to-Channel Crosstalk                                  | $f = 10 MHz$ , $R_L = 50 \Omega$ , see Figure 27                                                            |        |                  |              |          |

| Same Crosspoint Switch                                        |                                                                                                             |        | -50              |              | dB       |

| Different Crosspoint Switch                                   |                                                                                                             |        | -80              |              | dB       |

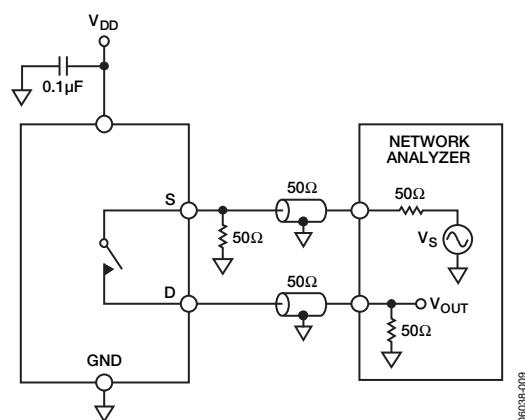

| -3 dB Bandwidth                                               | $R_L = 50 \Omega$ , see Figure 15                                                                           |        | 230              |              | MHz      |

| THD + N                                                       | $R_L = 100 \Omega$                                                                                          |        | 0.14             |              | %        |

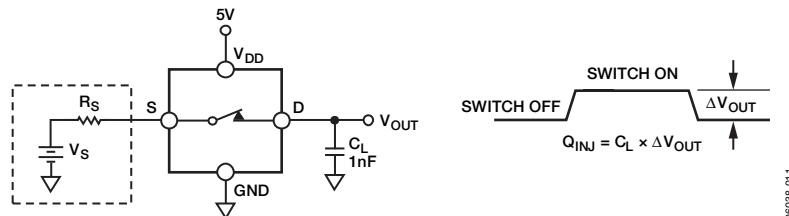

| Charge Injection                                              | $C_L = 1 nF$ , $V_S = 0 V$ , see Figure 30                                                                  |        | 4                |              | pC       |

| $C_{S(OFF)}$                                                  |                                                                                                             |        | 13               |              | pF       |

| $C_{D(OFF)}$                                                  |                                                                                                             |        | 17               |              | pF       |

| $C_{D(ON)}$ , $C_{S(ON)}$                                     |                                                                                                             |        | 35               |              | pF       |

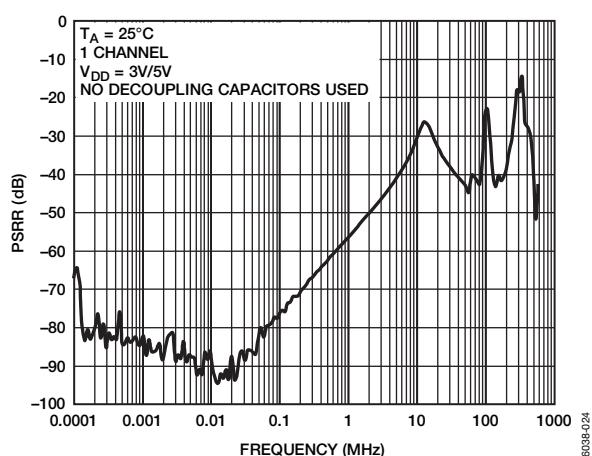

| Power Supply Rejection Ratio, PSRR                            | $f = 20 kHz$                                                                                                |        | 70               |              | dB       |

| Differential Gain Error                                       | CCIR330 test signal                                                                                         |        | 0.56             |              | %        |

| Differential Phase Error                                      | CCIR330 test signal                                                                                         |        | 0.79             |              | Degrees  |

| LOGIC INPUTS <sup>3</sup>                                     |                                                                                                             |        |                  |              |          |

| A0, A1, A2 Pins                                               |                                                                                                             |        |                  |              |          |

| Input High Voltage, $V_{INH}$                                 |                                                                                                             | 2.0    |                  |              | V        |

| Input Low Voltage, $V_{INL}$                                  |                                                                                                             |        | 0.8              |              | V        |

| Input Current, $I_{INL}$ or $I_{INH}$                         | $V_{IN} = 0 V$ to $V_{DD}$                                                                                  |        | 0.005            | $\pm 1$      | $\mu A$  |

| Input Capacitance, $C_{IN}$                                   |                                                                                                             |        | 3                |              | pF       |

## ADG799A/ADG799G

| Parameter                         | Conditions                                                             | Min                 | Typ <sup>1</sup>     | Max                  | Unit          |

|-----------------------------------|------------------------------------------------------------------------|---------------------|----------------------|----------------------|---------------|

| SCL, SDA Pins                     |                                                                        |                     |                      |                      |               |

| Input High Voltage, $V_{INH}$     |                                                                        | $0.7 \times V_{DD}$ |                      | $V_{DD} + 0.3$       | V             |

| Input Low Voltage, $V_{INL}$      |                                                                        | -0.3                |                      | $+0.3 \times V_{DD}$ | V             |

| Input Leakage Current, $I_{IN}$   | $V_{IN} = 0 \text{ V to } V_{DD}$                                      |                     | +0.005               | $\pm 1$              | $\mu\text{A}$ |

| Input Hysteresis                  |                                                                        |                     | $0.05 \times V_{DD}$ |                      | V             |

| Input Capacitance, $C_{IN}$       |                                                                        |                     | 3                    |                      | pF            |

| LOGIC OUTPUTS                     |                                                                        |                     |                      |                      |               |

| SDA Pin <sup>3</sup>              |                                                                        |                     |                      |                      |               |

| Output Low Voltage, $V_{OL}$      | $I_{SINK} = 3 \text{ mA}$                                              |                     | 0.4                  |                      | V             |

|                                   | $I_{SINK} = 6 \text{ mA}$                                              |                     | 0.6                  |                      | V             |

| Floating State Leakage Current    |                                                                        |                     |                      | $\pm 1$              | $\mu\text{A}$ |

| Floating State Output Capacitance |                                                                        |                     |                      | 10                   | pF            |

| GPO1 and GPO2 Pins                |                                                                        |                     |                      |                      |               |

| Output Low Voltage, $V_{OL}$      | $I_{LOAD} = 2 \text{ mA}$                                              |                     | 0.4                  |                      | V             |

| Output High Voltage, $V_{OH}$     | $I_{LOAD} = -2 \text{ mA}$                                             | 2.0                 |                      |                      | V             |

| POWER REQUIREMENTS                |                                                                        |                     |                      |                      |               |

| $I_{DD}$                          | Digital inputs = 0 V or $V_{DD}$ , I <sup>2</sup> C interface inactive |                     | 0.001                | 1                    | $\mu\text{A}$ |

|                                   | I <sup>2</sup> C interface active, $f_{SCL} = 400 \text{ kHz}$         |                     |                      | 0.2                  | mA            |

|                                   | I <sup>2</sup> C interface active, $f_{SCL} = 3.4 \text{ MHz}$         |                     |                      | 0.7                  | mA            |

<sup>1</sup> 特に指定のない限り、typ値は $T_A = +25^\circ\text{C}$ での値。

<sup>2</sup> 仕様については出荷テストを行っていませんが、初期特性評価により保証しています。

<sup>3</sup> 仕様については出荷テストを行っていませんが、デザインにより保証しています。

# ADG799A/ADG799G

特に指定のない限り、 $V_{DD}=3V \pm 10\%$ 、GND=0V、 $T_A=-40 \sim +85^\circ C$ 。

表2

| Parameter                                                     | Conditions                                                                 | Min                 | Typ <sup>1</sup> | Max                  | Unit     |

|---------------------------------------------------------------|----------------------------------------------------------------------------|---------------------|------------------|----------------------|----------|

| ANALOG SWITCH                                                 |                                                                            |                     |                  |                      |          |

| Analog Signal Range <sup>2</sup>                              | $V_S = V_{DD}$ , $R_L = 1 M\Omega$                                         | 0                   | 2.2              |                      | V        |

|                                                               | $V_S = V_{DD}$ , $R_L = 75 \Omega$                                         | 0                   | 1.7              |                      | V        |

| On Resistance, $R_{ON}$                                       | $V_D = 0 V$ , $I_{DS} = -10 mA$ , see Figure 22                            |                     | 3                | 5.5                  | $\Omega$ |

|                                                               | $V_D = 0 V$ to $1 V$ , $I_{DS} = -10 mA$ , see Figure 22                   |                     |                  | 8                    | $\Omega$ |

| On Resistance Matching Between Channels, $\Delta R_{ON}$      | $V_D = 0 V$ , $I_{DS} = -10 mA$                                            |                     | 0.15             | 1.8                  | $\Omega$ |

|                                                               | $V_D = 1 V$ , $I_{DS} = -10 mA$                                            |                     |                  | 2.1                  | $\Omega$ |

| On Resistance Flatness, $R_{FLAT(ON)}$                        | $V_D = 0 V$ to $1 V$ , $I_{DS} = -10 mA$                                   |                     | 0.3              | 2.8                  | $\Omega$ |

| LEAKAGE CURRENTS                                              |                                                                            |                     |                  |                      |          |

| Source Off Leakage ( $I_{S(OFF)}$ )                           | $V_D = 2 V/1 V$ , $V_S = 1 V/2 V$ , see Figure 23                          |                     | $\pm 0.25$       |                      | nA       |

| Drain Off Leakage ( $I_{D(OFF)}$ )                            | $V_D = 2 V/1 V$ , $V_S = 1 V/2 V$ , see Figure 23                          |                     | $\pm 0.25$       |                      | nA       |

| Channel On Leakage ( $I_{D(ON)}$ , $I_{S(ON)}$ )              | $V_D = V_S = 2 V/1 V$ , see Figure 24                                      |                     | $\pm 0.25$       |                      | nA       |

| DYNAMIC CHARACTERISTICS <sup>3</sup>                          |                                                                            |                     |                  |                      |          |

| $t_{ON}$ , $t_{ENABLE}$                                       | $C_L = 35 pF$ , $R_L = 50 \Omega$ , $V_S = 2 V$ , see Figure 28            |                     | 203              | 266                  | ns       |

| $t_{OFF}$ , $t_{DISABLE}$                                     | $C_L = 35 pF$ , $R_L = 50 \Omega$ , $V_S = 2 V$ , see Figure 28            |                     | 200              | 260                  | ns       |

| Break-Before-Make Time Delay, $t_D$                           | $CL = 35 pF$ , $R_L = 50 \Omega$ , $V_{S1} = V_{S2} = 2 V$ , see Figure 29 | 1                   | 3                |                      | ns       |

| $I^2C$ to GPO Propagation Delay, $t_H$ , $t_L$ (ADG799G only) |                                                                            |                     |                  | 121                  | ns       |

| Off Isolation                                                 | $f = 10 MHz$ , $R_L = 50 \Omega$ , see Figure 26                           |                     | -60              |                      | dB       |

| Channel-to-Channel Crosstalk                                  | $f = 10 MHz$ , $R_L = 50 \Omega$ , see Figure 27                           |                     |                  |                      |          |

| Same Crosspoint Switch                                        |                                                                            |                     | -50              |                      | dB       |

| Different Crosspoint Switch                                   |                                                                            |                     | -80              |                      | dB       |

| -3 dB Bandwidth                                               | $R_L = 50 \Omega$ , see Figure 15                                          |                     | 210              |                      | MHz      |

| THD + N                                                       | $R_L = 100 \Omega$                                                         |                     | 0.14             |                      | %        |

| Charge Injection                                              | $C_L = 1 nF$ , $V_S = 0 V$ , see Figure 30                                 |                     | 2                |                      | pC       |

| $C_{S(OFF)}$                                                  |                                                                            |                     | 13               |                      | pF       |

| $C_{D(OFF)}$                                                  |                                                                            |                     | 17               |                      | pF       |

| $C_{D(ON)}$ , $C_{S(ON)}$                                     |                                                                            |                     | 35               |                      | pF       |

| Power Supply Rejection Ratio, PSRR                            | $f = 20 kHz$                                                               |                     | 70               |                      | dB       |

| Differential Gain Error                                       | CCIR330 test signal                                                        |                     | 0.66             |                      | %        |

| Differential Phase Error                                      | CCIR330 test signal                                                        |                     | 1                |                      | Degrees  |

| LOGIC INPUTS                                                  |                                                                            |                     |                  |                      |          |

| A0, A1, A2 Pins <sup>3</sup>                                  |                                                                            |                     |                  |                      |          |

| Input High Voltage, $V_{INH}$                                 |                                                                            | 2.0                 |                  |                      | V        |

| Input Low Voltage, $V_{INL}$                                  |                                                                            |                     | 0.8              |                      | V        |

| Input Current, $I_{INL}$ or $I_{INH}$                         | $V_{IN} = 0 V$ to $V_{DD}$                                                 |                     | +0.005           | $\pm 1$              | $\mu A$  |

| Input Capacitance, $C_{IN}$                                   |                                                                            |                     | 3                |                      | pF       |

| SCL, SDA Pins <sup>3</sup>                                    |                                                                            |                     |                  |                      |          |

| Input High Voltage, $V_{INH}$                                 |                                                                            | $0.7 \times V_{DD}$ |                  | $V_{DD} + 0.3$       | V        |

| Input Low Voltage, $V_{INL}$                                  |                                                                            | -0.3                |                  | $+0.3 \times V_{DD}$ | V        |

| Input Leakage Current, $I_{IN}$                               | $V_{IN} = 0 V$ to $V_{DD}$                                                 |                     | 0.005            | $\pm 1$              | $\mu A$  |

| Input Hysteresis                                              |                                                                            |                     |                  | $0.05 \times V_{DD}$ | V        |

| Input Capacitance, $C_{IN}$                                   |                                                                            |                     |                  | 3                    | pF       |

## ADG799A/ADG799G

| Parameter                         | Conditions                                                                | Min | Typ <sup>1</sup>      | Max                     | Unit          |

|-----------------------------------|---------------------------------------------------------------------------|-----|-----------------------|-------------------------|---------------|

| LOGIC OUTPUTS <sup>3</sup>        |                                                                           |     |                       |                         |               |

| SDA Pin                           |                                                                           |     |                       |                         |               |

| Output Low Voltage, $V_{OL}$      | $I_{SINK} = 3 \text{ mA}$<br>$I_{SINK} = 6 \text{ mA}$                    |     | 0.4<br>0.6<br>$\pm 1$ | V<br>V<br>$\mu\text{A}$ |               |

| Floating State Leakage Current    |                                                                           | 3   |                       |                         |               |

| Floating State Output Capacitance |                                                                           |     |                       |                         | pF            |

| GPO1 and GPO2 Pins                |                                                                           |     |                       |                         |               |

| Output Low Voltage, $V_{OL}$      | $I_{LOAD} = 2 \text{ mA}$                                                 |     | 0.4                   | V                       |               |

| Output High Voltage, $V_{OH}$     | $I_{LOAD} = -2 \text{ mA}$                                                | 2.0 |                       | V                       |               |

| POWER REQUIREMENTS                |                                                                           |     |                       |                         |               |

| $I_{DD}$                          | Digital inputs = 0 V or $V_{DD}$ ,<br>I <sup>2</sup> C interface inactive |     | 0.001                 | 1                       | $\mu\text{A}$ |

|                                   | I <sup>2</sup> C interface active, $f_{SCL} = 400 \text{ kHz}$            |     |                       | 0.1                     | mA            |

|                                   | I <sup>2</sup> C interface active, $f_{SCL} = 3.4 \text{ MHz}$            |     |                       | 0.2                     | mA            |

<sup>1</sup> 特に指定のない限り、typ値は $T_A = +25^\circ\text{C}$ での値。

<sup>2</sup> 仕様については出荷テストを行っていませんが、初期特性評価により保証しています。

<sup>3</sup> 仕様については出荷テストを行っていませんが、デザインにより保証しています。

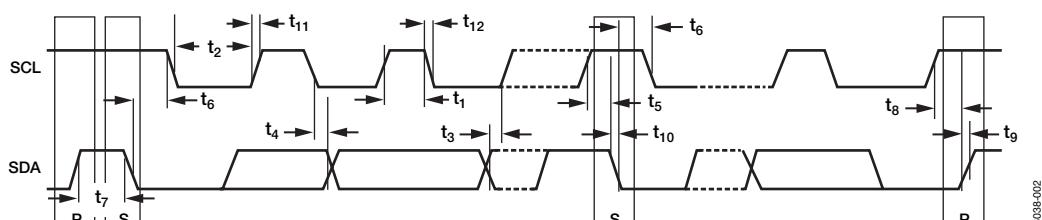

**I<sup>2</sup>Cのタイミング仕様**

特に指定のない限り、V<sub>DD</sub>=2.7~5.5V、GND=0V、T<sub>A</sub>=−40~+85°C（タイミング図については図2を参照）。

表3

| Parameter <sup>1</sup>      | Conditions                  | Min                     | Max  | Unit | Description                                                           |

|-----------------------------|-----------------------------|-------------------------|------|------|-----------------------------------------------------------------------|

| f <sub>SCL</sub>            | Standard mode               |                         | 100  | kHz  | Serial clock frequency                                                |

|                             | Fast mode                   |                         | 400  | kHz  |                                                                       |

|                             | High speed mode             |                         | 3.4  | MHz  |                                                                       |

|                             | C <sub>B</sub> = 100 pF max |                         | 1.7  | MHz  |                                                                       |

|                             | C <sub>B</sub> = 400 pF max |                         |      |      |                                                                       |

| t <sub>1</sub>              | Standard mode               | 4                       |      | μs   | t <sub>HIGH</sub> , SCL high time                                     |

|                             | Fast mode                   | 0.6                     |      | μs   |                                                                       |

|                             | High speed mode             |                         |      |      |                                                                       |

|                             | C <sub>B</sub> = 100 pF max | 60                      |      | ns   |                                                                       |

|                             | C <sub>B</sub> = 400 pF max | 120                     |      | ns   |                                                                       |

| t <sub>2</sub>              | Standard mode               | 4.7                     |      | μs   | t <sub>LOW</sub> , SCL low time                                       |

|                             | Fast mode                   | 1.3                     |      | μs   |                                                                       |

|                             | High speed mode             |                         |      |      |                                                                       |

|                             | C <sub>B</sub> = 100 pF max | 160                     |      | ns   |                                                                       |

|                             | C <sub>B</sub> = 400 pF max | 320                     |      | ns   |                                                                       |

| t <sub>3</sub>              | Standard mode               | 250                     |      | ns   | t <sub>SU:DAT</sub> , data setup time                                 |

|                             | Fast mode                   | 100                     |      | ns   |                                                                       |

|                             | High speed mode             | 10                      |      | ns   |                                                                       |

| t <sub>4</sub> <sup>2</sup> | Standard mode               | 0                       | 3.45 | μs   | t <sub>HD:DAT</sub> , data hold time                                  |

|                             | Fast mode                   | 0                       | 0.9  | μs   |                                                                       |

|                             | High speed mode             |                         |      |      |                                                                       |

|                             | C <sub>B</sub> = 100 pF max | 0                       | 703  | ns   |                                                                       |

|                             | C <sub>B</sub> = 400 pF max | 0                       | 150  | ns   |                                                                       |

| t <sub>5</sub>              | Standard mode               | 4.7                     |      | μs   | t <sub>SU:STA</sub> , setup time for a repeated start condition       |

|                             | Fast mode                   | 0.6                     |      | μs   |                                                                       |

|                             | High speed mode             | 160                     |      | ns   |                                                                       |

| t <sub>6</sub>              | Standard mode               | 4                       |      | μs   | t <sub>HD:STA</sub> , hold time (repeated) start condition            |

|                             | Fast mode                   | 0.6                     |      | μs   |                                                                       |

|                             | High speed mode             | 160                     |      | ns   |                                                                       |

| t <sub>7</sub>              | Standard mode               | 4.7                     |      | μs   | t <sub>BUF</sub> , bus free time between a stop and a start condition |

|                             | Fast mode                   | 1.3                     |      | μs   |                                                                       |

| t <sub>8</sub>              | Standard mode               | 4                       |      | μs   | t <sub>SU:STO</sub> , setup time for stop condition                   |

|                             | Fast mode                   | 0.6                     |      | μs   |                                                                       |

|                             | High speed mode             | 160                     |      | ns   |                                                                       |

| t <sub>9</sub>              | Standard mode               |                         | 1000 | ns   | t <sub>RDA</sub> , rise time of SDA signal                            |

|                             | Fast mode                   | 20 + 0.1 C <sub>B</sub> | 300  | ns   |                                                                       |

|                             | High speed mode             |                         |      |      |                                                                       |

|                             | C <sub>B</sub> = 100 pF max | 10                      | 80   | ns   |                                                                       |

|                             | C <sub>B</sub> = 400 pF max | 20                      | 160  | ns   |                                                                       |

# ADG799A/ADG799G

| Parameter <sup>1</sup> | Conditions                 | Min            | Max  | Unit | Description                                                                                         |

|------------------------|----------------------------|----------------|------|------|-----------------------------------------------------------------------------------------------------|

| $t_{10}$               | Standard mode              |                | 300  | ns   | $t_{FDA}$ , fall time of SDA signal                                                                 |

|                        | Fast mode                  | $20 + 0.1 C_B$ | 300  | ns   |                                                                                                     |

|                        | High speed mode            |                |      |      |                                                                                                     |

|                        | $C_B = 100 \text{ pF max}$ | 10             | 80   | ns   |                                                                                                     |

|                        | $C_B = 400 \text{ pF max}$ | 20             | 160  | ns   |                                                                                                     |

| $t_{11}$               | Standard mode              |                | 1000 | ns   | $t_{RCL}$ , rise time of SCL signal                                                                 |

|                        | Fast mode                  | $20 + 0.1 C_B$ | 300  | ns   |                                                                                                     |

|                        | High speed mode            |                |      |      |                                                                                                     |

|                        | $C_B = 100 \text{ pF max}$ | 10             | 40   | ns   |                                                                                                     |

|                        | $C_B = 400 \text{ pF max}$ | 20             | 80   | ns   |                                                                                                     |

| $t_{11A}$              | Standard mode              |                | 1000 | ns   | $t_{RCL1}$ , rise time of SCL signal after a repeated start condition and after an acknowledge bit. |

|                        | Fast mode                  | $20 + 0.1 C_B$ | 300  | ns   |                                                                                                     |

|                        | High speed mode            |                |      |      |                                                                                                     |

|                        | $C_B = 100 \text{ pF max}$ | 10             | 80   | ns   |                                                                                                     |

|                        | $C_B = 400 \text{ pF max}$ | 20             | 160  | ns   |                                                                                                     |

| $t_{12}$               | Standard mode              |                | 300  | ns   | $t_{FCL}$ , fall time of SCL signal                                                                 |

|                        | Fast mode                  | $20 + 0.1 C_B$ | 300  | ns   |                                                                                                     |

|                        | High speed mode            |                |      |      |                                                                                                     |

|                        | $C_B = 100 \text{ pF max}$ | 10             | 40   | ns   |                                                                                                     |

|                        | $C_B = 400 \text{ pF max}$ | 20             | 80   | ns   |                                                                                                     |

| $t_{SP}$               | Fast mode                  | 0              | 50   | ns   | Pulse width of suppressed spike                                                                     |

|                        | High speed mode            | 0              | 10   | ns   |                                                                                                     |

<sup>1</sup> 初期特性評価によって保証されます。 $C_B$ はバス・ラインの容量負荷を表します。 $t_r$ と $t_f$ は $0.3 V_{DD} \sim 0.7 V_{DD}$ で測定されています。

<sup>2</sup> SCL立下がりエッジの不定領域をブリッジするため、デバイスはSDAに対するデータのホールド時間と確保する必要があります。

## タイミング図

図2. 2線式シリアル・インターフェースのタイミング図

## 絶対最大定格

特に指定のない限り、 $T_A = 25^\circ\text{C}$ 。

表4

| Parameter                             | Rating                                                      |

|---------------------------------------|-------------------------------------------------------------|

| $V_{DD}$ to GND                       | -0.3 V to +6 V                                              |

| Analog, Digital Inputs                | -0.3 V to $V_{DD} + 0.3$ V or 30 mA, whichever occurs first |

| Continuous Current, S or D Pins       | 100 mA                                                      |

| Peak Current, S or D Pins             | 300 mA (pulsed at 1 ms, 10% duty cycle max)                 |

| Operating Temperature Range           |                                                             |

| Industrial (B Version)                | -40°C to +85°C                                              |

| Storage Temperature Range             | -65°C to +150°C                                             |

| Junction Temperature                  | 150°C                                                       |

| $\theta_{JA}$ Thermal Impedance       |                                                             |

| 24-Lead LFCSP                         | 30°C/W                                                      |

| Lead Temperature, Soldering (10 sec)  | 300°C                                                       |

| IR Reflow, Peak Temperature (<20 sec) | 260°C                                                       |

左記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作セクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

1つでもパラメータの絶対最大定格を超えると、デバイスに影響を与える可能性があります。

### 注意

ESD（静電放電）の影響を受けやすいデバイスです。人体や試験機器には4000Vもの高圧の静電気が容易に蓄積され、検知されないまま放電されることがあります。本製品は当社独自のESD保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、回復不能の損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

# ADG799A/ADG799G

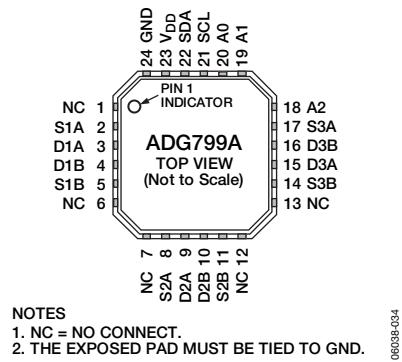

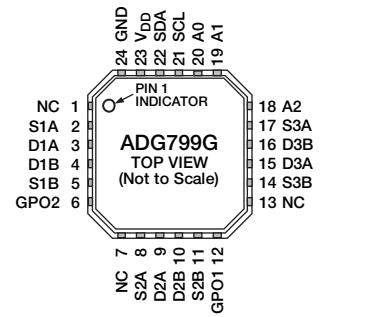

## ピン配置とピン機能の説明

図3. ADG799Aのピン配置

図4. ADG799Gのピン配置

表5. ピン機能の説明

| ピン番号 | 記号              | 機能                                                                                 |

|------|-----------------|------------------------------------------------------------------------------------|

| 1    | NC              | 内部で接続されていません。                                                                      |

| 2    | S1A             | クロスポイント・スイッチ1のA側ソース端子。入力または出力。                                                     |

| 3    | D1A             | クロスポイント・スイッチ1のA側ドレイン端子。入力または出力。                                                    |

| 4    | D1B             | クロスポイント・スイッチ1のB側ドレイン端子。入力または出力。                                                    |

| 5    | S1B             | クロスポイント・スイッチ1のB側ソース端子。入力または出力。                                                     |

| 6    | NC/GPO2         | 内部で接続されていません (ADG799A) / 汎用ロジック出力2 (ADG799G)。                                      |

| 7    | NC              | 内部で接続されていません。                                                                      |

| 8    | S2A             | クロスポイント・スイッチ2のA側ソース端子。入力または出力。                                                     |

| 9    | D2A             | クロスポイント・スイッチ2のA側ドレイン端子。入力または出力。                                                    |

| 10   | D2B             | クロスポイント・スイッチ2のB側ドレイン端子。入力または出力。                                                    |

| 11   | S2B             | クロスポイント・スイッチ2のB側ソース端子。入力または出力。                                                     |

| 12   | NC/GPO1         | 内部で接続されていません (ADG799A) / 汎用ロジック出力1 (ADG799G)。                                      |

| 13   | NC              | 内部で接続されていません。                                                                      |

| 14   | S3B             | クロスポイント・スイッチ3のB側ソース端子。入力または出力。                                                     |

| 15   | D3A             | クロスポイント・スイッチ3のA側ドレイン端子。入力または出力。                                                    |

| 16   | D3B             | クロスポイント・スイッチ3のB側ドレイン端子。入力または出力。                                                    |

| 17   | S3A             | クロスポイント・スイッチ3のA側ソース端子。入力または出力。                                                     |

| 18   | A2              | ロジック入力。7ビット・スレーブ・アドレスの最下位ビットからビットA2を設定。                                            |

| 19   | A1              | ロジック入力。7ビット・スレーブ・アドレスの最下位ビットからビットA1を設定。                                            |

| 20   | A0              | ロジック入力。7ビット・スレーブ・アドレスの最下位ビットからビットA0を設定。                                            |

| 21   | SCL             | デジタル入力、シリアル・クロック・ライン。データをデバイスにクロック入力するためにSDAと組み合わせて使用されるオープン・ドレイン入力。外付けプルアップ抵抗が必要。 |

| 22   | SDA             | デジタル入出力。双方向のオープン・ドレイン・データ・ライン。外付けプルアップ抵抗が必要。                                       |

| 23   | V <sub>DD</sub> | 正電源入力。                                                                             |

| 24   | GND             | グラウンド (0V) リファレンス電圧。                                                               |

## 代表的な性能特性

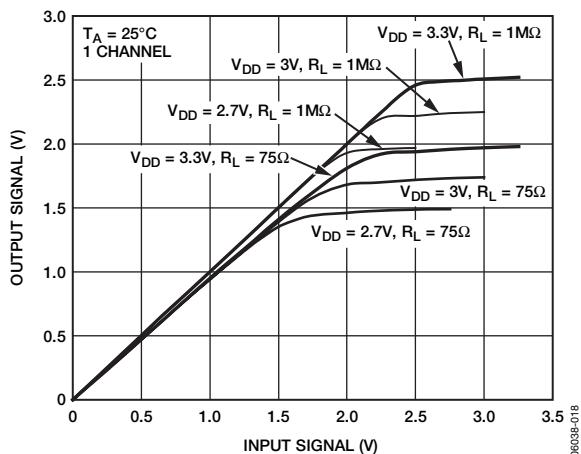

図5. アナログ信号範囲 (3V)

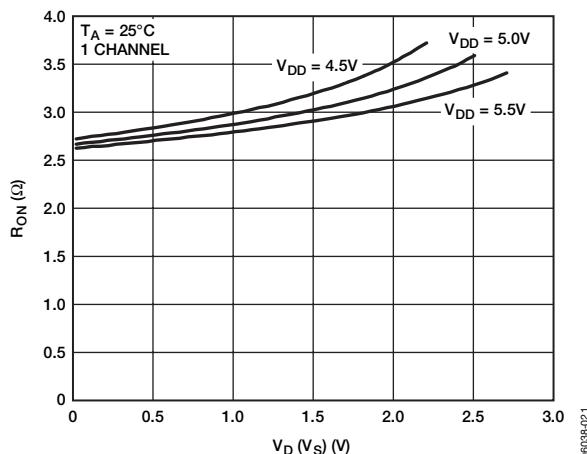

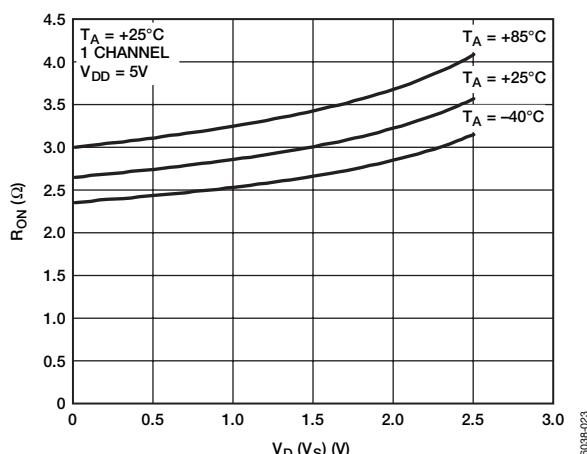

図8.  $V_D$  ( $V_S$ ) 対 オン抵抗 (5V)

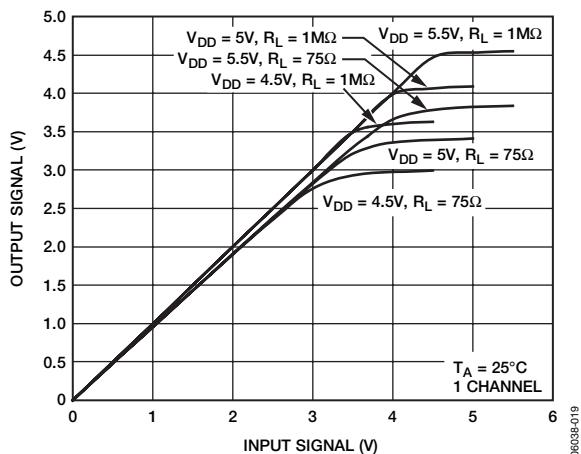

図6. アナログ信号範囲 (5V)

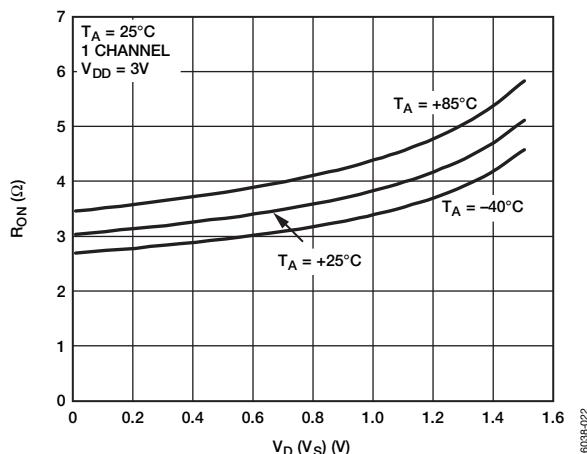

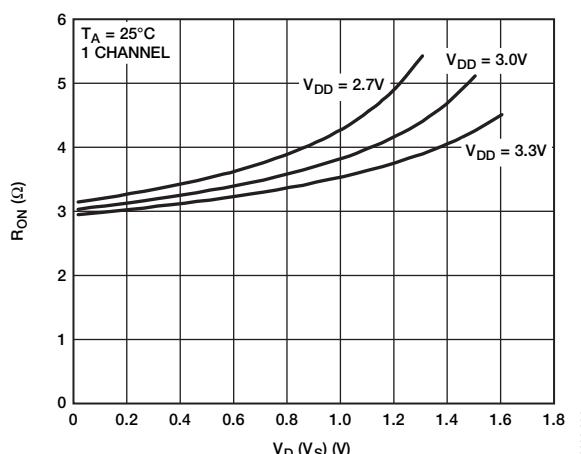

図9.  $V_D$  ( $V_S$ ) 対 さまざまな温度でのオン抵抗 (3V)図7.  $V_D$  ( $V_S$ ) 対 オン抵抗 (3V)図10.  $V_D$  ( $V_S$ ) 対 さまざまあな温度でのオン抵抗 (5V)

# ADG799A/ADG799G

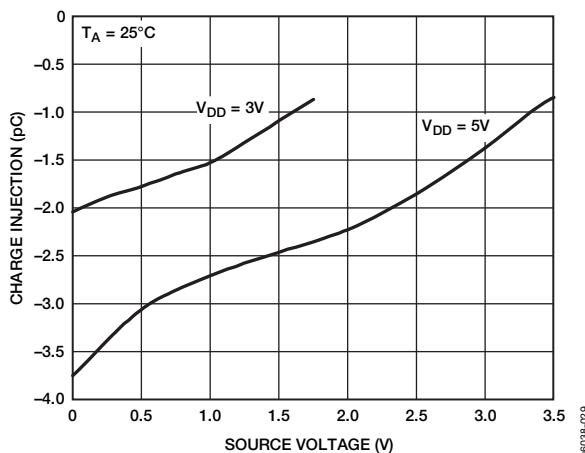

図11. ソース電圧 対 電荷注入

図14. クロストークの周波数特性

図12.  $t_{ON}/t_{OFF}$ の温度特性

図15. 帯域幅

図13. オフ・アイソレーションの周波数特性

図16. PSRRの周波数特性

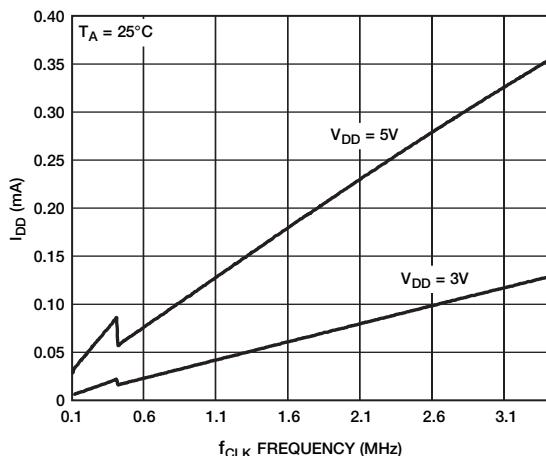

図17.  $f_{CLK}$ 周波数 对  $I_{DD}$

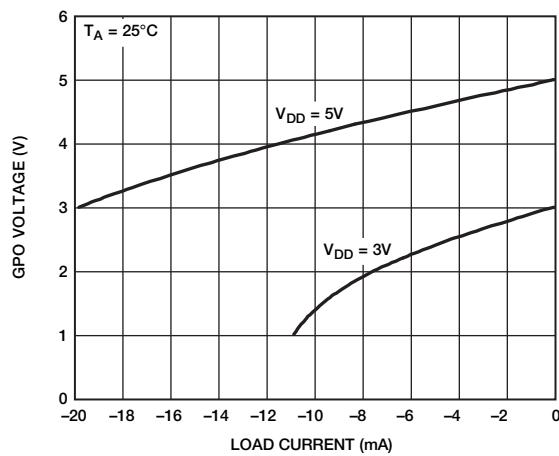

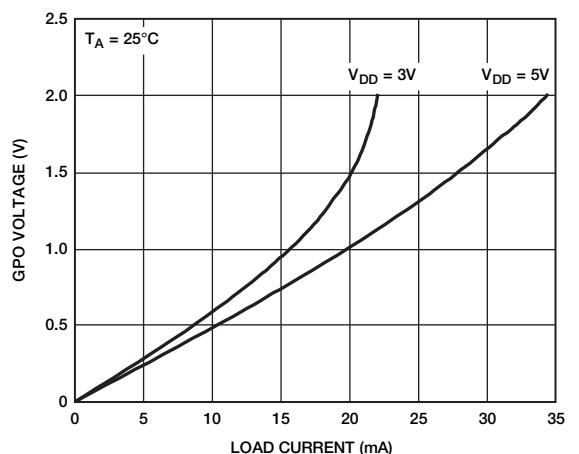

図20. 負荷電流 对 GPO  $V_{OH}$

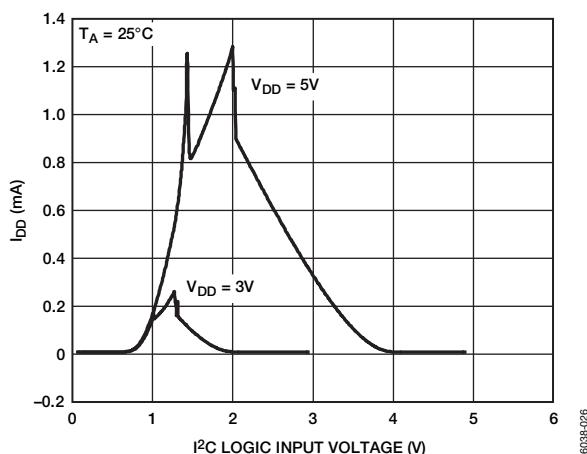

図18.  $I^2C$ ロジック入力電圧 (SDA、SCL) 对  $I_{DD}$

図21. 負荷電流 对 GPO  $V_{OL}$

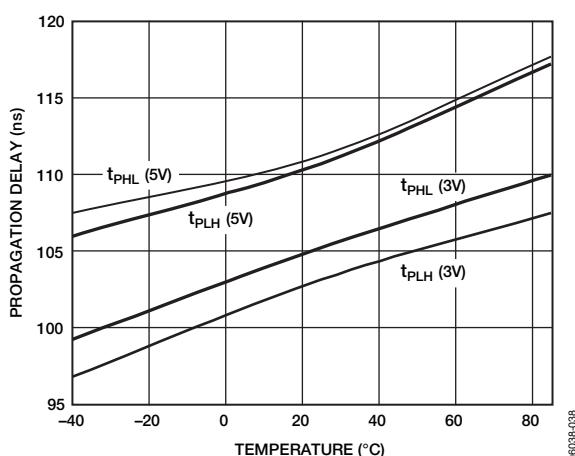

図19.  $I^2C$ からGPOまでの伝搬遅延温度特性

(ADG799Gの場合)

# ADG799A/ADG799G

## テスト回路

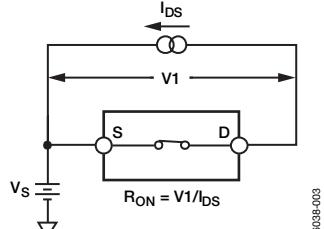

図22. オン抵抗

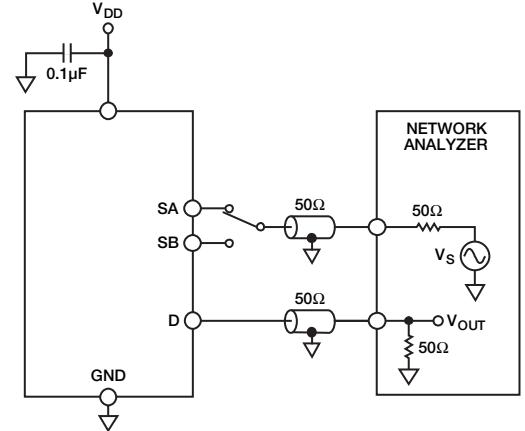

図25. 帯域幅

図23. オフ時リーケ

図26. オフ時アイソレーション

図24. オン時リーケ

図27. チャンネル間クロストーク

# ADG799A/ADG799G

図28. スイッチング時間

図29. ブレーク・ビフォア・メーク遅延時間

図30. 電荷注入

## 用語集

### オン抵抗 ( $R_{ON}$ )

SピンとDピンの間で測定されるオン時直列チャンネル抵抗。

### オン抵抗マッチ ( $\Delta R_{ON}$ )

複数のチャンネルが同じ条件で動作した場合の、チャンネル間のオン抵抗の差。

### オン抵抗平坦性 ( $R_{FLAT(ON)}$ )

一定の負荷電流で規定のアナログ入力電圧変化によって引き起こされる、規定範囲内でのオン抵抗の変動。

### チャンネル・オフ時リーク ( $I_{OFF}$ )

オフ時のチャンネル入力に入出力するリーク電流の合計。

### チャンネル・オン時リーク ( $I_{ON}$ )

オン時のチャンネル抵抗を流れる電流の損失／ゲイン。この電流でデバイスの両端に電圧オフセットが発生します。

### 入力リーク電流 ( $I_{IN}$ 、 $I_{INL}$ 、 $I_{INH}$ )

規定されたローレベルまたはハイレベルの電圧がデジタル入力に入力されたとき、その入力に流れ込む電流。

### 入出力オフ容量 ( $C_{OFF}$ )

スイッチ・チャンネルがオフのときの、アナログ入力とグラウンドとの間の容量。

### 入出力オン容量 ( $C_{ON}$ )

スイッチ・チャンネルがオンのときの、入力または出力とグラウンドとの間の容量。

### デジタル入力容量 ( $C_{IN}$ )

デジタル入力とグラウンドとの間の容量。

### 出力オン時スイッチング時間 ( $t_{ON}$ )

スイッチ・チャンネルを閉じるために必要な時間。LDSWビットの立下がりエッジの50%から、出力が最終値の90%に到達するまでの時間として測定されます。

### 出力オフ時スイッチング時間 ( $t_{OFF}$ )

スイッチを開くために必要な時間。LDSWビットの立下がりエッジの50%から、出力が最終値の10%に到達するまでの時間として測定されます。

### I<sup>2</sup>CからGPOまでの伝搬遅延 ( $t_H$ 、 $t_L$ )

GPOコマンドをロードした後、GPOピンでのロジック値が整定するために必要な時間。LDSWビットの立下がりエッジの50%から、出力が最終値の90%（ハイレベルの場合）または10%（ローレベルの場合）に到達するまでの時間として測定されます。

### 全高調波歪み十ノイズ (THD+N)

信号の高調波振幅+ノイズと基本波との比。

### -3dB帯域幅

出力が3dBだけ減衰する周波数。

### オフ時アイソレーション

オフ状態のスイッチを通過して混入する不要信号の大きさ。

### クロストーク

寄生容量により1つのチャンネルから別のチャンネルに混入される不要信号の大きさ。

### 電荷注入

オン／オフ・スイッチング時にデジタル入力からアナログ出力へ伝達されるグリッチ・インパルスの大きさ。

### 微分ゲイン誤差

輝度レベルが変化したときに発生する色飽和度シフトの大きさ。減衰と増幅の両方が発生するため、任意の2つのレベル間で最大の振幅変化が規定され、%値で表します。

### 微分位相誤差

輝度レベルが変化したときに発生する色相シフトの大きさ。負または正の値となることができ、サブキャリア位相の角度で表します。

### ハイレベル入力電圧 ( $V_{INH}$ )

ロジック1の最小入力電圧。

### ローレベル入力電圧 ( $V_{INL}$ )

ロジック0の最大入力電圧。

### ハイレベル出力電圧 ( $V_{OH}$ )

ロジック1の最小出力電圧。

### ローレベル出力電圧 ( $V_{OL}$ )

ロジック0の最大出力電圧。

### $I_{DD}$

正側電源電流。

## 動作原理

ADG799A/ADG799Gは、標準のI<sup>2</sup>Cシリアル・インターフェースを介して制御可能な3個の2×2クロスポイント・スイッチで構成される、モノリシックCMOSデバイスです。CMOSプロセスにより、きわめて小さい消費電力でありながら、高速なスイッチングと低いオン抵抗値を実現しています。

オン抵抗特性は、アナログ入力の全範囲にわたって非常にフラットです。広い帯域幅により、優れた直線性と低歪みが保証されます。これらの機能と広い入力信号範囲を組み合わせたADG799A/ADG799Gは、広範なTVアプリケーション向けのスイッチング・ソリューションに最適です。

これらのスイッチは、オン時に双方向に等しく良好に導通します。オフの状態では、電源電圧までの信号レベルを阻止します。内蔵のシリアルI<sup>2</sup>Cインターフェースは、クロスポイント・スイッチ（ADG799A/ADG799G）と汎用ロジック・ピン（ADG799G）の動作を制御します。

ADG799A/ADG799Gは、各スイッチを個別に制御する機能や、スイッチの状態を読み出すオプションなど、多くの機能を持っています。ADG799Gには、I<sup>2</sup>Cインターフェースを通じて制御可能な2本の汎用ロジック出力ピンがあります。次のセクションでは、これらの機能を詳しく説明します。

### I<sup>2</sup>Cシリアル・インターフェース

ADG799A/ADG799Gは、I<sup>2</sup>C互換のシリアル・バス・インターフェース（Philips Semiconductor提供の『I<sup>2</sup>Cバス仕様書』を参照）を介して制御されるため、スレーブ・デバイスとして動作することができます（ADG799A/ADG799Gはクロックを発生しません）。I<sup>2</sup>Cマスターとデバイスとの間の通信プロトコルは、次のように動作します。

1. マスターは、スタート条件（SCLがハイレベルのときの、SDAラインでのハイからローへの変化と定義されます）を設定してデータ転送を開始します。これは、アドレス/データ・ストリームが後に続くことを示します。バスに接続されたすべてのスレーブ・デバイスは、スタート条件に応答し、7ビット・アドレス（MSBファースト）とR/Wビットから構成される次の8ビットをシフト・インします。マスターとアドレス指定されたスレーブ・デバイスとの通信時には、このビットによりデータ・フローの方向が決まります。

2. 送信されたアドレスに対応するアドレスを持つスレーブ・デバイスは、9番目のクロック・パルス中にSDAラインをローレベルにすることで応答します。これは、アクノレッジ・ビットと呼ばれます。

この段階では、選択されたデバイスはシリアル・レジスターとの間でデータが読み書きされるのを待ち、バス上の他のすべてのデバイスはアイドル状態を維持します。R/Wビットがハイレベルに設定された場合は、マスターはスレーブ・デバイスから読み出します。R/Wビットがローレベルに設定された場合は、マスターはスレーブ・デバイスへ書き込みます。

3. データは、9個のクロック・パルス（8データ・ビットとそれに続くアクノレッジ・ビット）の連続でシリアル・バスへ送信されます。SDAラインでの変化は、クロック信号SCLのロ一期間中に生じて、SCLのハイ期間中は安定している必要があります。これに対して、クロック信号がハイレベルのときにローからハイに変化すると、トップ・イベントと解釈されてしまい、マスターとアドレス指定されたスレーブ・デバイスとの通信が終了することがあります。

4. すべてのデータバイトを転送した後、マスターはストップ条件（SCLがハイレベルのときの、SDAラインでのローからハイへの変化と定義されます）を設定します。書込みモードでは、マスターは、10番目のクロック・パルス中にSDAラインをハイレベルにしてストップ条件を設定します。読み出しモードでは、マスターは、9番目のクロック・パルスに対してノー・アクノレッジを発行します（SDAラインはハイレベルのままで）。その後マスターは、10番目のクロック・パルスの前にSDAラインをローレベルにし、次に10番目のクロック・パルス中にハイレベルにしてストップ条件を設定します。

### I<sup>2</sup>Cアドレス

各ADG799A/ADG799Gは、7ビットのI<sup>2</sup>Cアドレスを持っています。上位4ビットは内部的に配線接続されていますが、下位3ビット（A0、A1、A2）はユーザが設定できます。これにより、ユーザは、同じバスに最大8個のADG799A/ADG799Gを接続できます。I<sup>2</sup>Cのビット・マップに、7ビット・アドレスの構成を示します。

#### 7ビットI<sup>2</sup>Cアドレスのビット構成

| MSB | LSB |   |   |    |    |    |  |

|-----|-----|---|---|----|----|----|--|

| 1   | 0   | 1 | 0 | A2 | A1 | A0 |  |

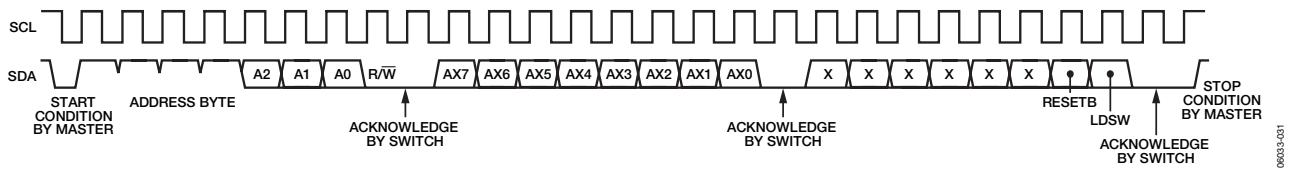

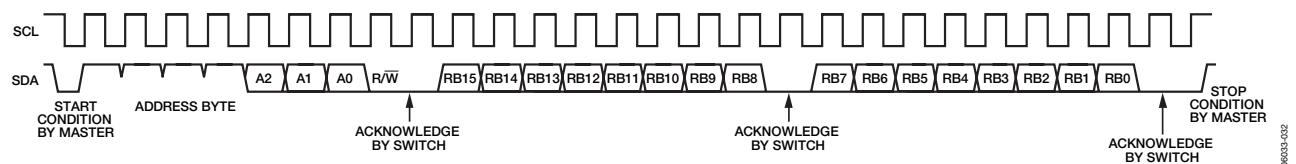

### 書込み動作

ADG799A/ADG799Gへの書込みは、必ずアドレス・バイトとR/Wビットから始めます。次に、スイッチは、SDAをローレベルにしてデータ受信の準備を完了したことを通知します。データは、シリアル・クロック入力SCLの制御のもとで、16ビット・ワードとしてデバイスにロードされます。図31に、ADG799A/ADG799Gに対する書込みシーケンスの全体を示します。最初のデータバイト（AX7~AX0）は、クロスポイント・スイッチとGPOピンの状態を制御します。2番目のバイトのLDSWビットとRESETBビットは、デバイスの動作モードを制御します。表6に、ADG799A/ADG799Gで提供される全コマンドと、書込み動作中にロードする必要のある対応するバイトのリストを示します。

希望する設定を行うため、1つまたは複数のコマンドをデバイスにロードすることができます。表6に示すコマンドの組合せを実行することができますが、次の制約があります。

- 複数のスイッチを参照するコマンドは、前のコマンドを上書きします。

- 一連の連続したコマンドが同じエレメント（すなわち、スイッチやGPOピン）に影響を与える場合には、最後のコマンドだけが実行されます。

# ADG799A/ADG799G

図31. ADG799A/ADG799Gの書き込み動作

表6. ADG799A/ADG799Gのコマンド・リスト

| AX7            | AX6 | AX5 | AX4 | AX3 | AX2 | AX1 | AX0 | Addressed Switch /GPO Pin                                                    |

|----------------|-----|-----|-----|-----|-----|-----|-----|------------------------------------------------------------------------------|

| 0              | 1   | 1   | 0   | 0   | 0   | 0   | 0   | S1A/D1A, S1B/D1B, S2A/D2A, S2B/D2B, S3A/D3A, S3B/D3B off                     |

| 1              | 1   | 1   | 0   | 0   | 0   | 0   | 0   | S1A/D1A, S1B/D1B, S2A/D2A, S2B/D2B, S3A/D3A, S3B/D3B on                      |

| 0              | 1   | 1   | 0   | 0   | 0   | 0   | 1   | S1A/D1B, S1B/D1A, S2A/D2B, S2B/D2A, S3A/D3B, S3B/D3A off                     |

| 1              | 1   | 1   | 0   | 0   | 0   | 0   | 1   | S1A/D1B, S1B/D1A, S2A/D2B, S2B/D2A, S3A/D3B, S3B/D3A on                      |

| 0              | 1   | 1   | 0   | 0   | 0   | 1   | 0   | S1A/D1A and S1A/D1B, S2A/D2A and S2A/D2B, S3A/D3A and S3A/D3B off            |

| 1              | 1   | 1   | 0   | 0   | 0   | 1   | 0   | S1A/D1A and S1A/D1B, S2A/D2A and S2A/D2B, S3A/D3A and S3A/D3B on             |

| 0              | 1   | 1   | 0   | 0   | 0   | 1   | 1   | S1B/D1A and S1B/D1B, S2B/D2A and S2B/D2B, S3B/D3A and S3B/D3B off            |

| 1              | 1   | 1   | 0   | 0   | 0   | 1   | 1   | S1B/D1A and S1B/D1B, S2B/D2A and S2B/D2B, S3B/D3A and S3B/D3B on             |

| 0              | 1   | 1   | 0   | 0   | 1   | 0   | 0   | S1A/D1A and S1B/D1A, S2A/D2A and S2B/D2A, S3A/D3A and S3B/D3A off            |

| 1              | 1   | 1   | 0   | 0   | 1   | 0   | 0   | S1A/D1A and S1B/D1A, S2A/D2A and S2B/D2A, S3A/D3A and S3B/D3A on             |

| 0              | 1   | 1   | 0   | 0   | 1   | 0   | 1   | S1A/D1B and S1B/D1B, S2A/D2B and S2B/D2B, S3A/D3B and S3B/D3B off            |

| 1              | 1   | 1   | 0   | 0   | 1   | 0   | 1   | S1A/D1B and S1B/D1B, S2A/D2B and S2B/D2B, S3A/D3B and S3B/D3B on             |

| 0              | 1   | 1   | 0   | 0   | 1   | 1   | 0   | S1A/D1A off                                                                  |

| 1              | 1   | 1   | 0   | 0   | 1   | 1   | 0   | S1A/D1A on                                                                   |

| 0              | 1   | 1   | 0   | 0   | 1   | 1   | 1   | S1A/D1B off                                                                  |

| 1              | 1   | 1   | 0   | 0   | 1   | 1   | 1   | S1A/D1B on                                                                   |

| 0              | 1   | 1   | 0   | 1   | 0   | 0   | 0   | S1B/D1A off                                                                  |

| 1              | 1   | 1   | 0   | 1   | 0   | 0   | 0   | S1B/D1A on                                                                   |

| 0              | 1   | 1   | 0   | 1   | 0   | 0   | 1   | S1B/D1B off                                                                  |

| 1              | 1   | 1   | 0   | 1   | 0   | 0   | 1   | S1B/D1B on                                                                   |

| 0              | 1   | 1   | 0   | 1   | 0   | 1   | 0   | S2A/D2A off                                                                  |

| 1              | 1   | 1   | 0   | 1   | 0   | 1   | 0   | S2A/D2A on                                                                   |

| 0              | 1   | 1   | 0   | 1   | 0   | 1   | 1   | S2A/D2B off                                                                  |

| 1              | 1   | 1   | 0   | 1   | 0   | 1   | 1   | S2A/D2B on                                                                   |

| 0              | 1   | 1   | 0   | 1   | 1   | 0   | 0   | S2B/D2A off                                                                  |

| 1              | 1   | 1   | 0   | 1   | 1   | 0   | 0   | S2B/D2A on                                                                   |

| 0              | 1   | 1   | 0   | 1   | 1   | 0   | 1   | S2B/D2B off                                                                  |

| 1              | 1   | 1   | 0   | 1   | 1   | 0   | 1   | S2B/D2B on                                                                   |

| 0              | 1   | 1   | 0   | 1   | 1   | 1   | 0   | S3A/D3A off                                                                  |

| 1              | 1   | 1   | 0   | 1   | 1   | 1   | 0   | S3A/D3A on                                                                   |

| 0              | 1   | 1   | 0   | 1   | 1   | 1   | 1   | S3A/D3B off                                                                  |

| 1              | 1   | 1   | 0   | 1   | 1   | 1   | 1   | S3A/D3B on                                                                   |

| 0              | 1   | 1   | 1   | 0   | 0   | 0   | 0   | S3B/D3A off                                                                  |

| 1              | 1   | 1   | 1   | 0   | 0   | 0   | 0   | S3B/D3A on                                                                   |

| 0              | 1   | 1   | 1   | 0   | 0   | 0   | 1   | S3B/D3B off                                                                  |

| 1              | 1   | 1   | 1   | 0   | 0   | 0   | 1   | S3B/D3B on                                                                   |

| X <sup>1</sup> | 1   | 1   | 1   | 0   | 0   | 1   | 0   | Crosspoint Switch 1 disabled (All switches connected to D1A and D1B are off) |

| X <sup>1</sup> | 1   | 1   | 1   | 0   | 0   | 1   | 1   | Crosspoint Switch 2 disabled (All switches connected to D2A and D2B are off) |

| X <sup>1</sup> | 1   | 1   | 1   | 0   | 1   | 0   | 0   | Crosspoint Switch 3 disabled (All switches connected to D3A and D3B are off) |

| 0              | 1   | 1   | 1   | 0   | 1   | 0   | 1   | GPO1 low for ADG799G/Reserved for ADG799A                                    |

| 1              | 1   | 1   | 1   | 0   | 1   | 0   | 1   | GPO1 high for ADG799G/Reserved for ADG799A                                   |

| 0              | 1   | 1   | 1   | 0   | 1   | 1   | 0   | GPO2 low for ADG799G/Reserved for ADG799A                                    |

| 1              | 1   | 1   | 1   | 0   | 1   | 1   | 0   | GPO2 high for ADG799G/Reserved for ADG799A                                   |

| 0              | 1   | 1   | 1   | 0   | 1   | 1   | 1   | GPO1 and GPO2 low for ADG799G/Reserved for ADG799A                           |

| 1              | 1   | 1   | 1   | 0   | 1   | 1   | 1   | GPO1 and GPO2 high for ADG799G/Reserved for ADG799A                          |

| 0              | 1   | 1   | 1   | 1   | 1   | 1   | 1   | All muxes disabled (all switches are off)                                    |

| 1              | 1   | 1   | 1   | 1   | 1   | 1   | 1   | Reserved                                                                     |

<sup>1</sup> X=ロジック状態は関係ありません。

## LDSWビット

LDSWビットを使うと、書き込み動作中にロードされたコマンドの実行方法を制御することができます。ADG799A/ADG799Gは、LDSWビットをハイレベルに設定して実行された2つの連続する書き込み動作の間でロードされたすべてのコマンドを実行します。

すべての書き込みサイクルに対してLDSWをハイレベルに設定すると、LDSWビットがデバイスにロードされた直後にデバイスがコマンドを実行します。1つのコマンドの送信によって希望する設定を実現できるとき、あるいは複数のスイッチまたはGPOピン（あるいはその両方）を同時に更新する必要がないとき、この設定を使用することができます。希望する設定が同時更新と複数のコマンドとを必要とする場合には、コマンドのロード時にLDSWビットをローレベルに設定する必要があります。ただし、最後のコマンドのロード時にはLDSWビットをハイレベルに設定する必要があります。。最後のコマンドがLDSW=ハイレベルでロードされると、デバイスは、前回の更新以降に受信されたすべてのコマンドを同時に実行します。

## パワーオン／ソフトウェア・リセット

ADG799A/ADG799Gには、デバイスに書き込まれた2番目のデータバイトのRESETBビットによって実現される、ソフトウェア・リセット機能があります。クロスポイント・スイッチ・ピンとGPOピンが正常に動作するためには、このビットをハイレベルに設定する必要があります。RESETB=ローレベルのとき、またはパワーアップ後には、すべてのクロスポイント・スイッチ・ピンのスイッチはターン・オフ（オープン）され、GPOピンはローレベルに設定されます。

## 読み出し動作

ADG799A/ADG799Gからデータを読み出すときは、必ずアドレス・バイトとR/Wビットから始めます。次に、スイッチは、SDAをローレベルにしてデータ送信の準備が完了したことを通知します。続いて、ADG799A/ADG799Gは、次のクロック・エッジで2バイトを送信します。これらのバイトはスイッチの状態を含み、各バイトの後にはアクノレッジ・ビットが続きます。ロジック・ハイのビットはオン（クローズ）状態のスイッチを表し、ローのビットはオフ（オープン）状態のスイッチを表します。GPOピンに関しては（ADG799Gの場合）、このビットはピンのロジック値を表します。図32に、読み出しシーケンスの全体を示します。

図32に付随するビットマップに、ADG799AとADG799Gのエレメント（すなわち、スイッチとGPOピン）間の関係と、読み出し動作完了後の状態を表すビットを示します。

### ADG799Aのビットマップ

| RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9     | RB8     | RB7     | RB6     | RB5     | RB4     | RB3 | RB2 | RB1 | RB0 |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|-----|-----|-----|-----|

| S1A/D1A | S1B/D1A | S1A/D1B | S1B/D1B | S2A/D2A | S2B/D2A | S2A/D2B | S2B/D2B | S3A/D3A | S3B/D3A | S3A/D3B | S3B/D3B | -   | -   | -   | -   |

### ADG799Gのビットマップ

| RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9     | RB8     | RB7     | RB6     | RB5     | RB4     | RB3  | RB2  | RB1 | RB0 |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|------|------|-----|-----|

| S1A/D1A | S1B/D1A | S1A/D1B | S1B/D1B | S2A/D2A | S2B/D2A | S2A/D2B | S2B/D2B | S3A/D3A | S3B/D3A | S3A/D3B | S3B/D3B | GPO1 | GPO2 | -   | -   |

図32. ADG799A/ADG799Gの読み出し動作

## ADG799A/ADG799G

### 評価用ボード

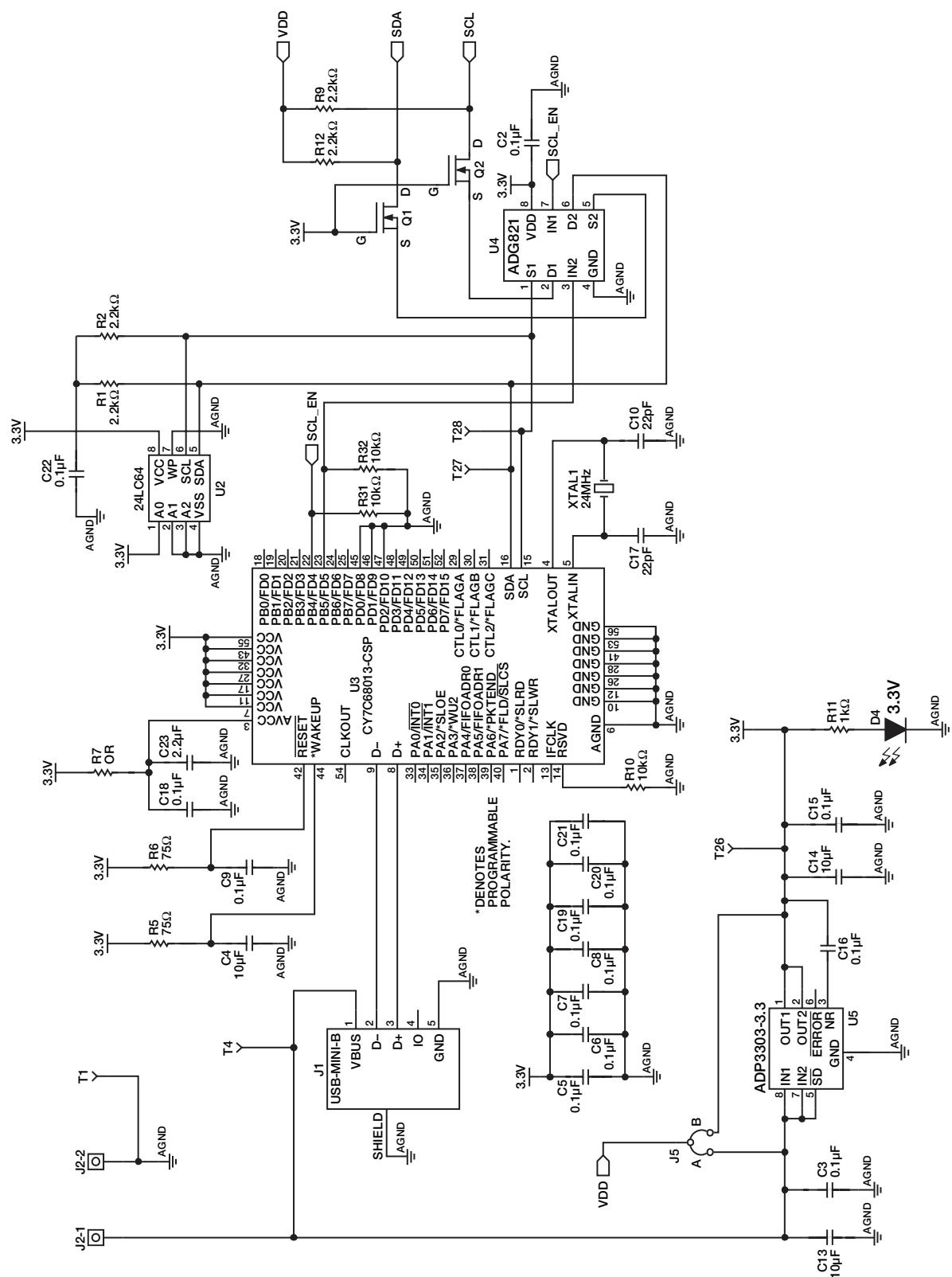

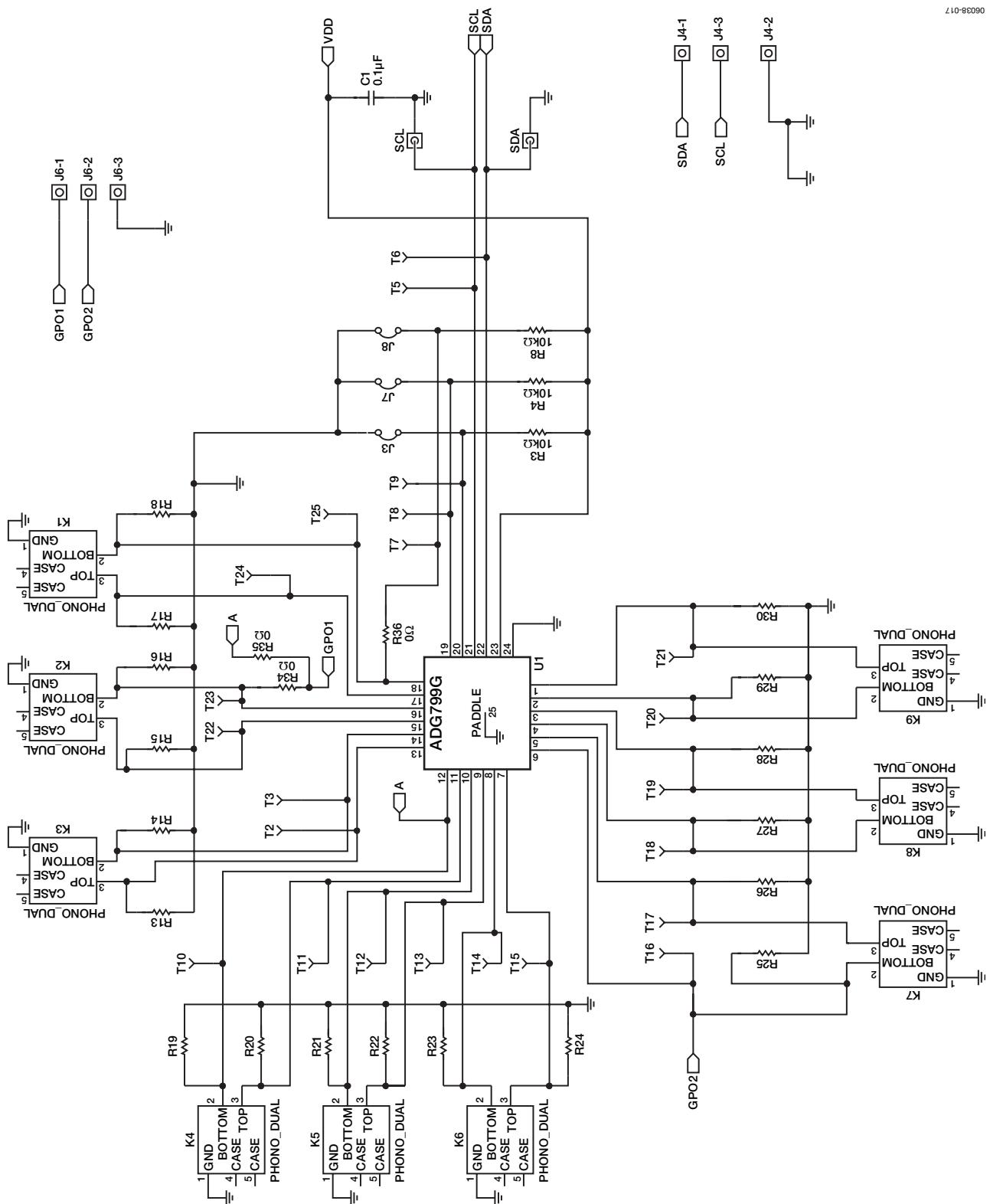

EVAL-ADG799GEBを使うと、デバイスの高性能を最小の努力で評価できます。

評価用キットには、ADG799Gを実装したプリント回路基板が含まれています。評価用ボードを使用すると、ADG799AとADG799Gの性能を評価できます。PCのUSBポートに接続するか、スタンドアロンの評価用ボードとして使用できます。評価用ボード付属のソフトウェアを使用すると、ユーザは、USBポートを通じてADG799Gを容易にプログラムできます。図33と図34に、評価用ボードの回路図を示します。このソフトウェアは、Microsoft® Windows® 2000またはWindows XPと1200×768の最小画面解像度を持ったPCで動作します。

### ADG799G評価用ボードの使い方

ADG799G評価用キットは、デバイスの評価を簡略化するようデザインされたテスト・システムです。このデバイスの各入出力には、オーディオ／ビデオ評価が簡単に行えるよう特に選択されたソケットが付属しています。評価用ボード付属のデータシートには、評価用ボードの動作が詳しく説明されています。

# ADG799A/ADG799G

# ADG799A/ADG799G

06038-017

図34. EVAL-ADG799GEBの回路図、チップ部

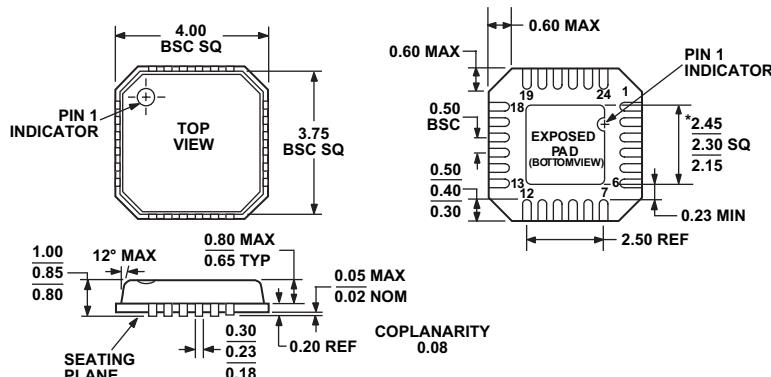

## 外形寸法

図35. 24ピン・リード・フレーム・チップ・スケール・パッケージ [LFCSP\_VQ]

4mm×4mmボディ、極薄クワッド

(CP-24-2)

寸法単位: mm

## オーダー・ガイド

| Model                           | Temperature Range | I <sup>2</sup> C Speed    | Package Description | Package Option |

|---------------------------------|-------------------|---------------------------|---------------------|----------------|

| ADG799ABCPZ-REEL <sup>1</sup>   | -40°C to +85°C    | 100 kHz, 400 kHz          | 24-Lead LFCSP_VQ    | CP-24-2        |

| ADG799ABCPZ-500RL7 <sup>1</sup> | -40°C to +85°C    | 100 kHz, 400 kHz          | 24-Lead LFCSP_VQ    | CP-24-2        |

| ADG799ACCPZ-REEL <sup>1</sup>   | -40°C to +85°C    | 100 kHz, 400 kHz, 3.4 MHz | 24-Lead LFCSP_VQ    | CP-24-2        |

| ADG799ACCPZ-500RL7 <sup>1</sup> | -40°C to +85°C    | 100 kHz, 400 kHz, 3.4 MHz | 24-Lead LFCSP_VQ    | CP-24-2        |

| ADG799GBCPZ-REEL <sup>1</sup>   | -40°C to +85°C    | 100 kHz, 400 kHz          | 24-Lead LFCSP_VQ    | CP-24-2        |

| ADG799GBCPZ-500RL7 <sup>1</sup> | -40°C to +85°C    | 100 kHz, 400 kHz          | 24-Lead LFCSP_VQ    | CP-24-2        |

| ADG799GCCPZ-REEL <sup>1</sup>   | -40°C to +85°C    | 100 kHz, 400 kHz, 3.4 MHz | 24-Lead LFCSP_VQ    | CP-24-2        |

| ADG799GCCPZ-500RL7 <sup>1</sup> | -40°C to +85°C    | 100 kHz, 400 kHz, 3.4 MHz | 24-Lead LFCSP_VQ    | CP-24-2        |

| EVAL-ADG799GEB <sup>2</sup>     |                   |                           | Evaluation Board    |                |

<sup>1</sup> Z=鉛フリー製品

<sup>2</sup> 評価用ボードはRoHSに準拠

アナログ・デバイセズ社またはその二次ライセンスを受けた関連会社からライセンスの対象となるI<sup>2</sup>Cコンポーネントを購入した場合、購入者にはこれらのコンポーネントをI<sup>2</sup>Cシステムで使用するフィリップス社のI<sup>2</sup>Cの特許権に基づくライセンスが許諾されます。ただし、フィリップス社が規定するI<sup>2</sup>C規格仕様に準拠したシステムが必要です。