## ADCMP609

### 特長

$V_{CC} = 2.5 \sim 5.5$  V で完全に仕様が規定されたレール to レール入力

入力同相電圧 :  $-0.2$  V ~  $V_{CC} + 0.2$  V

低グリッチの TTL/CMOS 互換出力段

伝播遅延 : 40 ns

低消費電力 : 2.5 V 時で 1 mW

シャットダウン・ピン付き

プログラマブル・ヒステリシス機能

電源変動除去比 : > 60 dB

動作温度範囲 : -40 ~ +125°C

### アプリケーション

高速計測機器

クロック信号とデータ信号の再生

ロジック・レベルのシフトまたは変換

高速ライン・レシーバ

スレッショールド検出

ピークおよびゼロクロス検出器

高速トリガ回路

パルス幅変調器

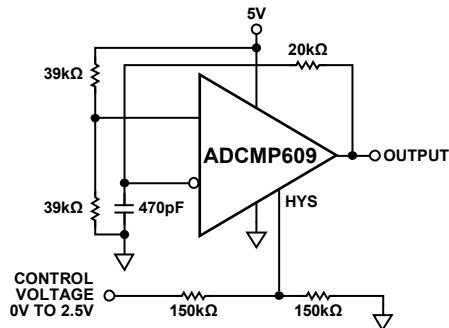

電流／電圧制御発振器

### 概要

ADCMP609 は、アナログ・デバイセズ独自のプロセス技術 XFCB2 で製造された高速コンパレータです。このコンパレータ製品は、豊富な機能を備えた、使いやすいデバイスとなっています。特長としては、 $V_{EE} - 0.2$  V から  $V_{CC} + 0.2$  V までの入力範囲、低ノイズ、TTL/CMOS 互換の出力ドライバ、調整可能なヒステリシス、シャットダウン入力などがあります。

このデバイスは、10mV のオーバードライブで 15pF の負荷を駆動したとき、500μA の動作電流で 40ns の伝播遅延性能を示します。

柔軟性の高い電源設計によって、+2.5 V の単電源で、-0.2 ~ +3.0 V の入力信号範囲で動作し、最大で +5.5 V の正電源、-0.2 ~ +5.7 V の入力信号範囲の動作が可能です。

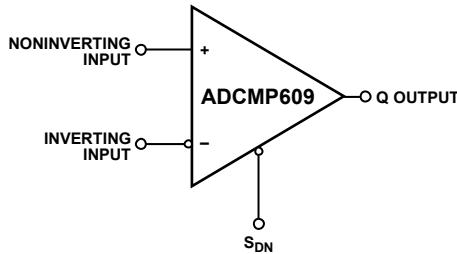

### 機能ブロック図

0691B-001

図 1.

TTL/CMOS 互換の出力段は、規定のタイミング仕様で最大 15 pF の負荷を駆動し、容量が増えるにつれリニアな形で徐々に駆動能力が低下するように設計されています。コンパレータの入力段は大きい入力オーバードライブに対し頑丈に保護されており、有効な入力信号範囲を超えて出力が位相反転することはありません。プログラマブル・ヒステリシス機能も用意されています。

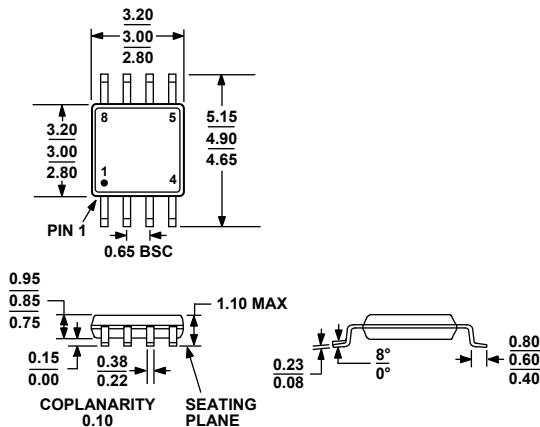

ADCMP609 は 8 ピン MSOP パッケージを採用し、この中にシャットダウン・ピンとヒステリシス・コントロール機能も内蔵しています。

# 目次

|            |   |                       |    |

|------------|---|-----------------------|----|

| 特長         | 1 | アプリケーション情報            | 8  |

| アプリケーション   | 1 | 電源／グラウンドのレイアウトとバイパス処理 | 8  |

| 機能ブロック図    | 1 | TTL/CMOS 互換出力段        | 8  |

| 概要         | 1 | 性能の最適化                | 8  |

| 改訂履歴       | 2 | コンパレータの伝播遅延分散         | 8  |

| 仕様         | 3 | コンパレータのヒステリシス         | 9  |

| 電気的特性      | 3 | クロスオーバー・バイアス・ポイント     | 9  |

| 絶対最大定格     | 4 | 入力スルーレートに関する最低限の条件    | 10 |

| 熱抵抗値       | 4 | 代表的なアプリケーション回路        | 11 |

| ESD に関する注意 | 4 | 外形寸法                  | 12 |

| ピン配置と機能の説明 | 5 | オーダー・ガイド              | 12 |

| 代表的な性能特性   | 6 |                       |    |

## 改訂履歴

### 8/08—Rev. 0 to Rev. A

|                           |    |

|---------------------------|----|

| Changes to Table 4        | 5  |

| Changes to Ordering Guide | 12 |

### 7/07—Revision 0: Initial Version

# 仕様

## 電気的特性

特に指定のない限り、 $V_{CC} = 2.5 \text{ V}$ 、 $T_A = -40 \sim +125^\circ\text{C}$ 、代表値は  $T_A = 25^\circ\text{C}$ 。

表 1.

| Parameter                                            | Symbol     | Conditions                                                                                                                 | Min            | Typ                              | Max                      | Unit          |

|------------------------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------|----------------|----------------------------------|--------------------------|---------------|

| DC INPUT CHARACTERISTICS                             |            |                                                                                                                            |                |                                  |                          |               |

| Voltage Range                                        | $V_P, V_N$ | $V_{CC} = 2.5 \text{ V to } 5.5 \text{ V}$                                                                                 | -0.2           |                                  | $V_{CC} + 0.2 \text{ V}$ | V             |

| Common-Mode Range                                    |            | $V_{CC} = 2.5 \text{ V to } 5.5 \text{ V}$                                                                                 | -0.2           |                                  | $V_{CC} + 0.2 \text{ V}$ | V             |

| Differential Voltage                                 |            | $V_{CC} = 2.5 \text{ V to } 5.5 \text{ V}$                                                                                 |                |                                  | $V_{CC}$                 | V             |

| Offset Voltage                                       | $V_{OS}$   |                                                                                                                            | -5.0           | $\pm 3$                          | +5.0                     | mV            |

| Bias Current                                         | $I_P, I_N$ |                                                                                                                            | -0.4           |                                  | +0.4                     | $\mu\text{A}$ |

| Offset Current                                       |            |                                                                                                                            | -1.0           |                                  | +1.0                     | $\mu\text{A}$ |

| Capacitance                                          | $C_P, C_N$ |                                                                                                                            |                | 1                                |                          | pF            |

| Resistance, Differential Mode                        |            | $-0.5 \text{ V to } V_{CC} + 0.5 \text{ V}$                                                                                | 200            |                                  | 7000                     | k $\Omega$    |

| Resistance, Common Mode                              |            | $-0.5 \text{ V to } V_{CC} + 0.5 \text{ V}$                                                                                | 100            |                                  | 4000                     | k $\Omega$    |

| Active Gain                                          | $A_V$      |                                                                                                                            |                | 80                               |                          | dB            |

| Common-Mode Rejection Ratio                          | $CMRR$     | $V_{CC} = 2.5 \text{ V}$<br>$V_{CM} = -0.2 \text{ V to } +2.7 \text{ V}$<br>$V_{CC} = 5.5 \text{ V}$<br>$R_{HYS} = \infty$ | 50             |                                  |                          | dB            |

| Hysteresis                                           |            |                                                                                                                            |                | 0.1                              |                          | mV            |

| HYSTERESIS MODE AND TIMING                           |            |                                                                                                                            |                |                                  |                          |               |

| Hysteresis Mode Bias Voltage                         |            | Current - 1 $\mu\text{A}$                                                                                                  | 1.145          | 1.25                             | 1.35                     | V             |

| Minimum Resistor Value                               |            | $Hysteresis = 120 \text{ mV}$                                                                                              | 30             |                                  | 120                      | k $\Omega$    |

| SHUTDOWN PIN CHARACTERISTICS <sup>1</sup>            |            |                                                                                                                            |                |                                  |                          |               |

| $V_{IH}$                                             |            | Comparator is operating                                                                                                    | 2.0            |                                  | $V_{CC}$                 | V             |

| $V_{IL}$                                             |            | Shutdown guaranteed                                                                                                        | -0.2           | $+0.4$                           | $+0.4$                   | V             |

| $I_{IH}$                                             |            | $V_{IH} = V_{CC}$                                                                                                          | -6             |                                  | +6                       | $\mu\text{A}$ |

| Sleep Time                                           | $t_{SD}$   | $L_{CC} < 100 \mu\text{A}$                                                                                                 |                | 300                              |                          | ns            |

| Wake-Up Time                                         | $t_H$      | $V_{PP} = 10 \text{ mV}$ , output valid                                                                                    |                | 150                              |                          | ns            |

| DC OUTPUT CHARACTERISTICS                            |            |                                                                                                                            |                |                                  |                          |               |

| Output Voltage High Level                            | $V_{OH}$   | $V_{CC} = 2.5 \text{ V to } 5.5 \text{ V}$                                                                                 |                |                                  |                          | V             |

| Output Voltage Low Level                             | $V_{OL}$   | $I_{OH} = 0.8 \text{ mA}, V_{CC} = 2.5 \text{ V}$<br>$I_{OL} = 0.8 \text{ mA}, V_{CC} = 2.5 \text{ V}$                     | $V_{CC} - 0.4$ |                                  |                          | V             |

| 0.4                                                  |            |                                                                                                                            |                |                                  |                          |               |

| AC PERFORMANCE <sup>2</sup>                          |            |                                                                                                                            |                |                                  |                          |               |

| Rise Time/Fall Time                                  | $t_R/t_F$  | $V_{CC} = 2.5 \text{ V to } 5.5 \text{ V}$<br>10% to 90%, $V_{CC} = 2.5 \text{ V}$<br>10% to 90%, $V_{CC} = 5.5 \text{ V}$ |                | 25 to 50                         |                          | ns            |

| Propagation Delay                                    | $t_{PD}$   | $V_{OD} = 10 \text{ mV}, V_{CC} = 2.5 \text{ V}$<br>$V_{OD} = 50 \text{ mV}, V_{CC} = 5.5 \text{ V}$                       |                | 45 to 75<br>30 to 50<br>35 to 60 |                          | ns            |

| Propagation Delay Skew, Rising to Falling Transition |            | $V_{CC} = 2.5 \text{ V}$<br>$V_{CC} = 5.5 \text{ V}$                                                                       |                | 4.5<br>8                         |                          | ns            |

| Propagation Delay Skew, Q to $\bar{Q}$               |            | $V_{CC} = 2.5 \text{ V}$<br>$V_{CC} = 5.5 \text{ V}$                                                                       |                | 3<br>4                           |                          | ns            |

| Overdrive Dispersion                                 |            | $10 \text{ mV} < V_{OD} < 125 \text{ mV}$                                                                                  |                | 12                               |                          | ns            |

| Common-Mode Dispersion                               |            | $-0.2 \text{ V} < V_{CM} < V_{CC} + 0.2 \text{ V}$                                                                         |                | 1.5                              |                          | ns            |

| POWER SUPPLY                                         |            |                                                                                                                            |                |                                  |                          |               |

| Supply Voltage Range                                 | $V_{CC}$   |                                                                                                                            | 2.5            |                                  | 5.5                      | V             |

| Positive Supply Current                              | $I_{VCC}$  | $V_{CC} = 2.5 \text{ V}$<br>$V_{CC} = 5.5 \text{ V}$                                                                       |                | 550<br>800                       | 650<br>1100              | $\mu\text{A}$ |

| Power Dissipation                                    | $P_D$      | $V_{CC} = 2.5 \text{ V}$<br>$V_{CC} = 5.5 \text{ V}$                                                                       |                | 1.4<br>4.5                       | 1.7<br>7                 | mW            |

| Power Supply Rejection Ratio                         | $PSRR$     | $V_{CC} = 2.5 \text{ V to } 5.5 \text{ V}$                                                                                 | -50            |                                  |                          | dB            |

| Shutdown Current                                     | $I_{SD}$   | $V_{CC} = 2.5 \text{ V to } 5.5 \text{ V}$                                                                                 |                | 150                              | 260                      | $\mu\text{A}$ |

<sup>1</sup> デバイスがシャットダウン・モードのとき、出力はハイ・インピーダンス・モードになりますが、通常のスリーステート出力の場合よりもイネーブル/ディスエーブル時間が大幅に長くなるため、この機能を使用するときは十分に注意してください。

<sup>2</sup> 特に指定のない限り、1 MHz 時に  $V_{IN} = 100 \text{ mV}$  の方形入力、 $V_{CM} = 0 \text{ V}$ 、 $C_L = 15 \text{ pF}$ 、 $V_{CCI} = 2.5 \text{ V}$ 。

## 絶対最大定格

表 2.

| Parameter                                   | Rating                            |

|---------------------------------------------|-----------------------------------|

| Supply Voltages                             |                                   |

| Supply Voltage (V <sub>CC</sub> to Ground)  | -0.5 V to +6.0 V                  |

| Supply Differential                         | -6.0 V to +6.0 V                  |

| Input Voltages                              |                                   |

| Input Voltage                               | -0.5 V to V <sub>CC</sub> + 0.5 V |

| Differential Input Voltage                  | ±(V <sub>CC</sub> + 0.5 V)        |

| Maximum Input/Output Current                | ±50 mA                            |

| Shutdown Pin                                |                                   |

| Applied Voltage (S <sub>DN</sub> to Ground) | -0.5 V to V <sub>CC</sub> + 0.5 V |

| Maximum Input/Output Current                | ±50 mA                            |

| Hysteresis Control Pin                      |                                   |

| Applied Voltage (HYS to Ground)             | -0.5 V to V <sub>CC</sub> + 0.5 V |

| Maximum Input/Output Current                | ±50 mA                            |

| Output Current                              | ±50 mA                            |

| Operating Temperature                       |                                   |

| Ambient Temperature Range                   | -40°C to +125°C                   |

| Junction Temperature                        | 150°C                             |

左記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作セクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

### 熱抵抗値

$\theta_{JA}$  はワーストケース、すなわち回路ボードに表面実装パッケージをハンダ付けした状態で規定しています。

表 3.

| Package Type         | $\theta_{JA}$ <sup>1</sup> | Unit |

|----------------------|----------------------------|------|

| ADCMP609 8-Lead MSOP | 130                        | °C/W |

<sup>1</sup> 自然空冷で測定。

### ESDに関する注意

ESD（静電放電）の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

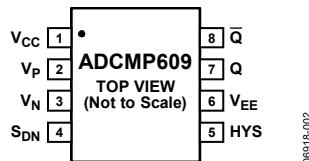

## ピン配置と機能の説明

図 2. ADCMP609 のピン配置

表 4. ADCMP609 のピン機能の説明

| ピン番号 | 記号              | 説明                                                                                                             |

|------|-----------------|----------------------------------------------------------------------------------------------------------------|

| 1    | V <sub>CC</sub> | V <sub>CC</sub> 電源                                                                                             |

| 2    | V <sub>P</sub>  | 非反転アナログ入力                                                                                                      |

| 3    | V <sub>N</sub>  | 反転アナログ入力                                                                                                       |

| 4    | S <sub>DN</sub> | シャットダウン。このピンをローレベルにすると、デバイスがシャットダウンになります。                                                                      |

| 5    | HYS             | ヒステリシス・コントロール。ヒステリシスを付加する際に、抵抗または電流源でバイアスをかけます。                                                                |

| 6    | V <sub>EE</sub> | 負の電源電圧                                                                                                         |

| 7    | Q               | 非反転出力。コンパレータが比較モードの場合、非反転入力 (V <sub>P</sub> ) のアナログ電圧が反転入力 (V <sub>N</sub> ) のアナログ電圧よりも大きいと、Qはロジック・ハイレベルになります。 |

| 8    | Q̄              | 反転出力。コンパレータが比較モードの場合、非反転入力 (V <sub>P</sub> ) のアナログ電圧が反転入力 (V <sub>N</sub> ) のアナログ電圧よりも大きいと、Q̄はロジック・ローレベルになります。 |

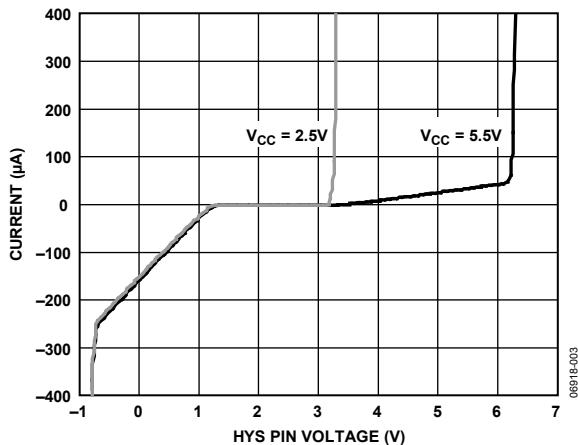

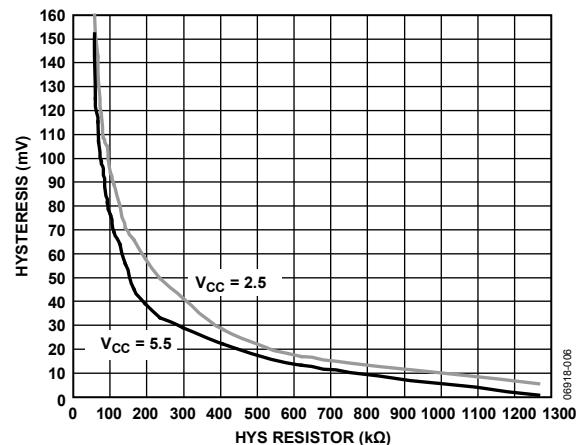

## 代表的な性能特性

特に指定のない限り、 $V_{CC} = 2.5\text{ V}$ 、 $T_A = 25^\circ\text{C}$ 。

図 3. 電圧 (V) 対 HYS ピン電流 (μA)

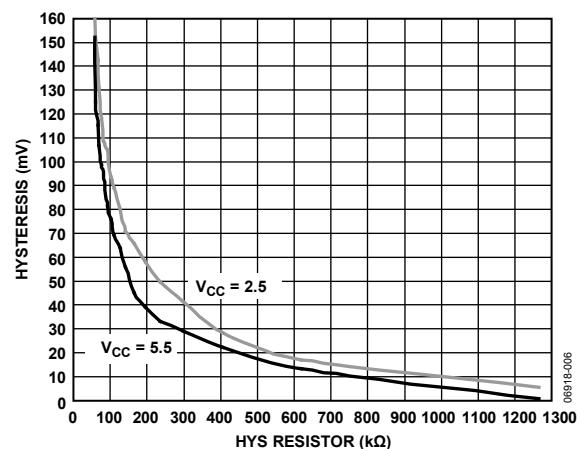

図 6. HYS 抵抗 対 ヒステリシス

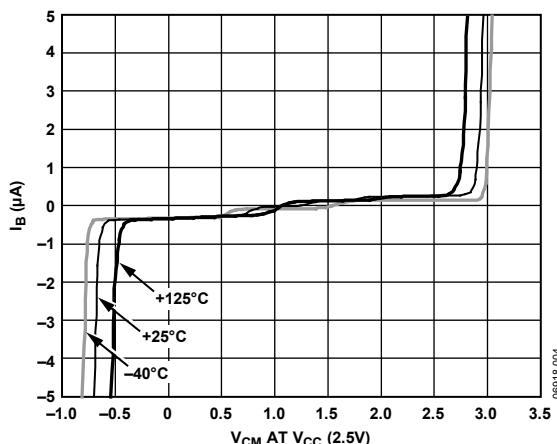

図 4. 入力同相電圧 (V) 対 入力バイアス電流

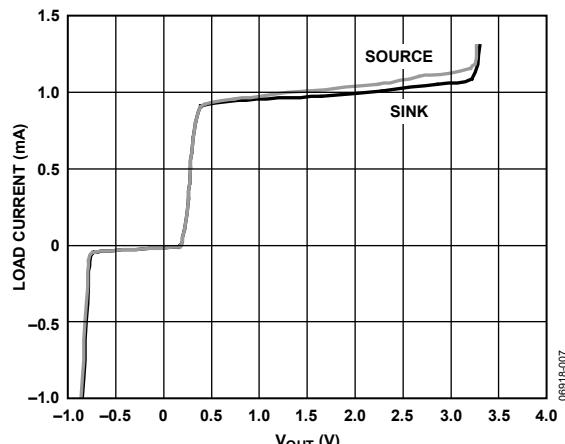

図 7.  $V_{OH}/V_{OL}$  対 負荷電流

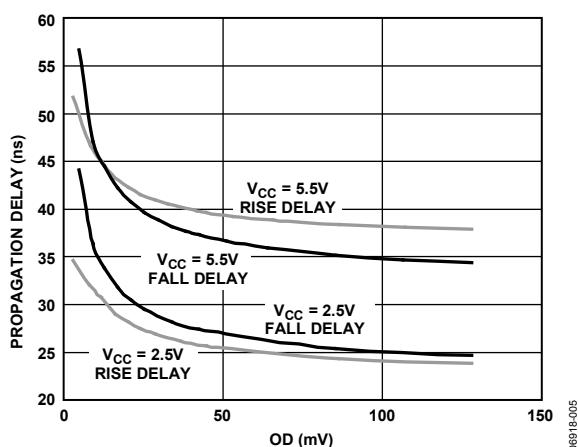

図 5. 入力オーバードライブ 対 伝播遅延

( $V_{CC} = 2.5\text{ V}$  および  $5.5\text{ V}$ )

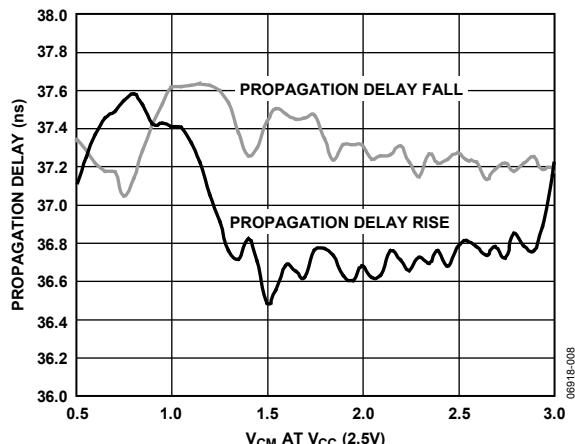

図 8. 入力同相電圧 (V) 対 伝播遅延

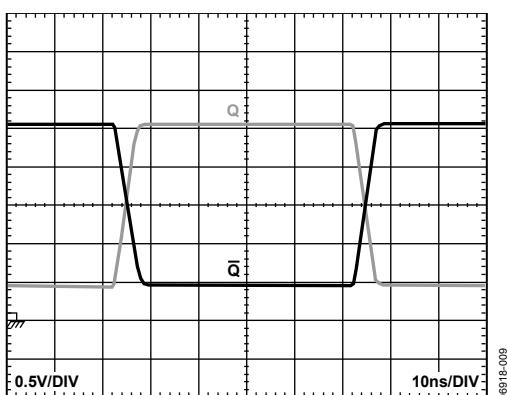

図 9. 1 MHz 出力電圧波形 ( $V_{CC} = 2.5$  V)

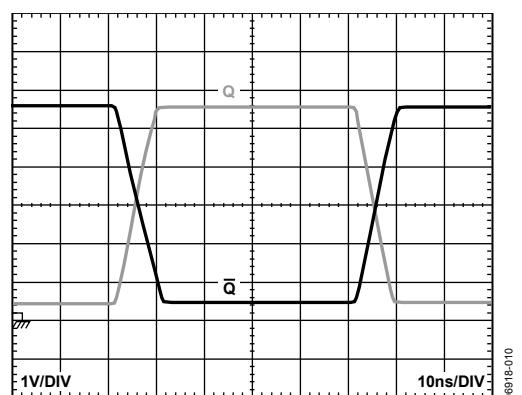

図 10. 1 MHz 出力電圧波形 ( $V_{CC} = 5.5$  V)

## アプリケーション情報

### 電源／グラウンドのレイアウトとバイパス処理

ADCMP609 コンパレータは高速デバイスです。低ノイズの出力段ではありますが、規定の性能を実現するには、正しい高速回路設計方法を使用しなければなりません。コンパレータは補償がないアンプであるため、どのような位相関係の帰還でも発振や望ましくないヒステリシスを発生させる危険性があります。特に重要なのは、低インピーダンスの電源プレーン、なかでも出力電源プレーン ( $V_{CC}$ ) とグラウンド・プレーンを使用することです。多層基板の一部として、別々の電源プレーンを使用することを推奨します。目的とするアプリケーションで最高の性能を実現するには、スイッチングする電流のリターン経路のインダクタンスを最小にすることです。

入力側電源と出力側電源を十分にバイパスすることも大切です。各  $V_{CC}$  電源ピンのできるだけ近くに  $0.1\mu F$  のバイパス・コンデンサを配置してください。冗長ビアを備えたグラウンド・プレーンにコンデンサを接続し、グラウンドから  $V_{CC}$  ピンに帰還する出力電流のために物理的に短いリターン経路ができるようにしてください。インダクタンスと直列実効抵抗値 (ESR) が最小になるように、高周波数バイパス・コンデンサを慎重に選択してください。また、高周波数時のバイパス効果を最大限に高めるために、寄生レイアウト・インダクタンスを十分に管理する必要があります。

### TTL/CMOS互換出力段

規定の伝播遅延性能を実現するために、容量性負荷は規定されている最小値またはそれ以下に保ってください。ADCMP609 の出力は、1 個のショットキーTTL または 3 個の低消費電力ショットキーTTL 負荷（または同等品）を直接駆動できるように設計されています。大きいファンアウト、バス駆動、伝送ラインの場合は、適切なバッファを使用することによって、コンパレータの高い速度と優れた安定性を維持してください。

規定値が  $15\text{ pF}$  の負荷容量の場合、デバイスのトータル伝播遅延の半分以上が出力段のスルーフィルムになります。このため、 $V_{CC}$  が低下すると、それに伴ってトータル伝播遅延が減少します。電源の不安定性は、過度の伝播分散として現われることがあります。

どのような電源を使用する場合も、遅延は 50% ポイントで測定されるため、 $V_{CC}$  電源が  $2.5\text{ V}$  のときに最短の伝播時間が認められます。また、ほかのレベルでスイッチする負荷を駆動するときは、より大きい数値が現れます。

オーバードライブ量による分散と入力スルーレートによる分散は、出力負荷と  $V_{CC}$  の変動によって大きく影響を受けることはありません。

TTL/CMOS 互換出力段を簡略回路図（図 11）に示します。本質的に対称性があり、一般に優れた挙動があるため、この出力段は各種フィルタやその他の一般的ではない負荷を駆動する場合も容易に対応できます。

図 11. TTL/CMOS 互換出力段の簡略回路図

11-018690

### 性能の最適化

どのような高速コンパレータでもそうですが、規定の性能を実現するには、正しい設計とレイアウト方法が欠かせません。浮遊容量、インダクタンス、電源とグラウンドのコモン・インピーダンス、その他のレイアウト上の問題によって性能が大きく制限され、場合によっては発振が生じることもあります。ソース・インピーダンスはできる限り低く抑えてください。高いソース・インピーダンスにコンパレータの寄生入力容量が加わると、入力帯域幅に悪影響があり、応答性全体が低下します。またインピーダンスが高いと、望ましくない結合が生じやすくなります。

### コンパレータの伝播遅延分散

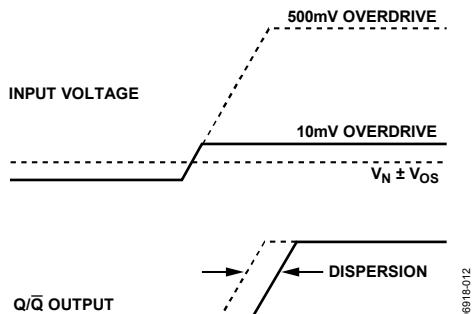

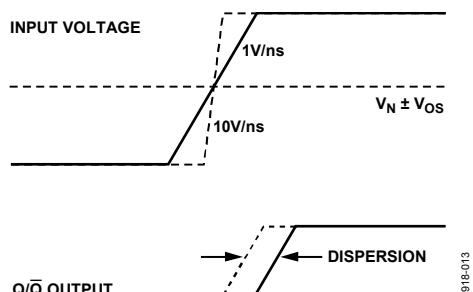

ADCMP609 コンパレータは、 $10\text{ mV}$  から  $V_{CC} - 1\text{ V}$  までの広範な入力オーバードライブ範囲で伝播遅延分散を低減するように設計されています。伝播遅延分散とは、オーバードライブまたはスルーレートのレベル変化が起因して生じる伝播遅延の変動であり、これによって入力信号がどの程度まで、あるいはどの程度早くスイッチング・レッショールドを超えるかがわかります。

伝播遅延分散は、データ通信、自動テストや自動測定、計測機器などのタイミングが重視される高速アプリケーションで重要な仕様です。また、パルス分光法、核計装、医用画像処理などのイベント駆動アプリケーションでも重要です。分散とは、入力オーバードライブ条件の変化に伴う伝播遅延の変動です（図 12 と図 13 を参照）。

オーバードライブが  $10\text{ mV}$  から  $125\text{ mV}$  に変化するときの ADCMP609 の分散は、代表値で  $<12\text{ ns}$  です。このデバイスは正方向と負方向の両方の入力での遅延が高精度にマッチングしており、しかも出力スキーが非常に低いため、この仕様は正と負のどちらの信号にも同じようになります。ただし、繰返し可能な分散の測定では、実際のデバイス・オフセットがオーバードライブに附加されます。

図 12. 伝播遅延：オーバードライブ分散

図 13. 伝播遅延：スルーレート分散

## コンパレータのヒステリシス

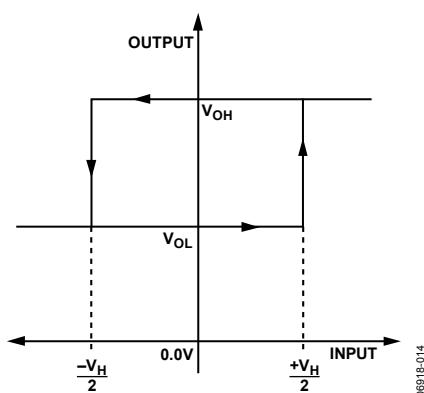

ノイズの多い環境であったり、差動入力振幅が比較的小さいか低速で変化したりする場合は、コンパレータにヒステリシスを追加したほうがよいことがあります。ヒステリシスを追加したコンパレータの伝達関数を図 14 に示します。入力電圧が正方向のスレッショールドよりも低い領域からスレッショールド（図 14 の  $0.0\text{ V}$ ）に上がっていいくときに、入力が $+V_H/2$  に達すると、コンパレータはローからハイにスイッチします。そして新しいスイッチング・スレッショールドは $-V_H/2$  になります。負方向のスレッショールドよりも高い領域から $-V_H/2$  のスレッショールドに達するまで、コンパレータはハイの状態のままでです。このようにすることで、 $\pm V_H/2$  の範囲を超えない限り、 $0.0\text{ V}$  入力を中心とするノイズや帰還出力信号によってコンパレータがその状態を変えることはありません。

図 14. コンパレータ・ヒステリシスの伝達関数

コンパレータにヒステリシスを導入する一般の方法では、出力から入力の方向に正の帰還を使用します。この方法の欠点は、ヒステリシスの量が出力のロジック・レベルに伴って変動するため、スレッショールドを中心とした対称性が失われることです。外付け帰還ネットワークも、高速性能を劣化させる大きな寄生容量を生じさせることができます。場合によっては発振を誘発することさえあります。

ADCMP609 コンパレータは、精度と安定性を大幅に向上させるプログラマブル・ヒステリシス機能を備えています。外部プルダウン抵抗か電流源を HYS ピンとグラウンドの間に接続すると、ヒステリシスの変化が予測可能な安定したものになります。HYS ピンを無接続の状態にするか、ハイレベルに駆動すると、ヒステリシスが除去されます。このピンを使用して適用できる最大のヒステリシス幅は約  $160\text{ mV}$  です。外部抵抗の値の閾値となるヒステリシスを図 15 に示します。

図 15. HYS 抵抗 対 ヒステリシス

HYS ピンは、ヒステリシス・コントロールの全範囲内で  $7\text{ k}\Omega \pm 20\%$  の直列抵抗値を通った  $1.25\text{ V}$  のバイアス電圧と考えられます。このような方法でヒステリシスを適用する利点は、精度と安定性が向上し、使用部品数が低減し、最大限の融通性が得られることです。HYS ピンに外部バイパス・コンデンサを接続するのは、ラッチ機能が損なわれ、場合によってはデバイスのジッタ性能が劣化することがあるため、推奨できません。

このピンをローレベルに駆動すると、ヒステリシス量が大きくなります。このデバイスではその効果は安定ではなく、ラッチ機能として意図したものではありません。

## クロスオーバー・バイアス・ポイント

オペアンプとコンパレータの両方におけるこの種のレール to レール入力は、デュアル・フロントエンド設計になります。 $V_{CC}$  レールの近くでアクティブになるデバイスもあれば、 $V_{EE}$  レールの近くでアクティブになるデバイスもありますが、同相範囲の中の特定のポイントでクロスオーバーが発生します。通常は  $V_{CC}/2$  ですが、このポイントでバイアス電流の方向が反転し、オフセット電圧と電流の測定値が変化します。

ADCMP609 は、この方式をもう少し精巧なものにしており、クロスオーバー・ポイントは約  $0.8\text{ V}$  と約  $1.6\text{ V}$  になっています。

## 入力スルーレートに関する最低限の条件

定格負荷容量と通常の適切なプリント基板の設計方法（「性能の最適化」を参照）に従って、ヒステリシスを適用しなくても任意の入力スルーレートでコンパレータの安定性を保つようしてください。入力段から広帯域ノイズが現れますぐ、ほかの大部分の高速コンパレータで見られるような激しいノイズは発生しま

せん。容量性負荷が加わったり、バイパス処理が不適切であったりすると、発振が発生することがあります。こうした発振は、コンパレータの高いゲイン帯域幅に、パッケージとプリント基板の寄生容量からくる帰還が組み合わさって生じます。多くのアプリケーションでは、チャタリング・ノイズは有害なものではありません。

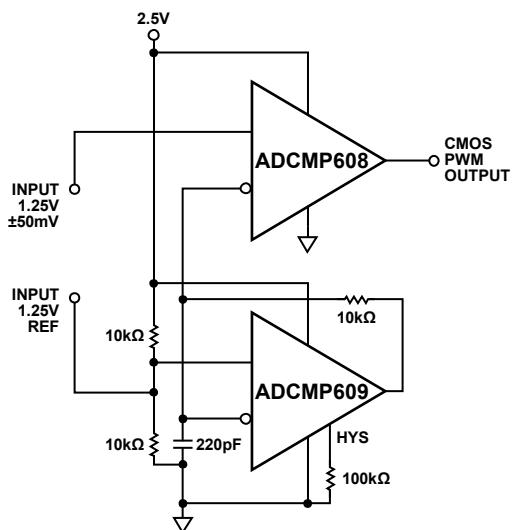

## 代表的なアプリケーション回路

図 16. 電圧制御発振器

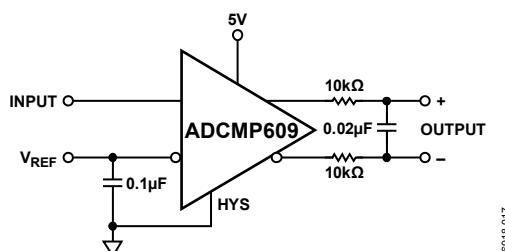

図 17. デューティ・サイクル／差動電圧コンバータ

図 18. 発振器とパルス幅変調器

外形寸法

図 19. 8 ピン・ミニ・スマール・アウトライン・パッケージ [MSOP]

(RM-8)

尺寸単位: mm

オーダー・ガイド

| Model                           | Temperature Range | Package Description                      | Package Option | Branding |

|---------------------------------|-------------------|------------------------------------------|----------------|----------|

| ADCMP609BRMZ <sup>1</sup>       | -40°C to +125°C   | 8-Lead Mini Small Outline Package [MSOP] | RM-8           | GW       |

| ADCMP609BRMZ-REEL <sup>1</sup>  | -40°C to +125°C   | 8-Lead Mini Small Outline Package [MSOP] | RM-8           | GW       |

| ADCMP609BRMZ-REEL7 <sup>1</sup> | -40°C to +125°C   | 8-Lead Mini Small Outline Package [MSOP] | RM-8           | GW       |

| EVAL-ADCMP609BRMZ <sup>1</sup>  |                   | Evaluation Board                         |                |          |

<sup>1</sup> Z = RoHS 準拠製品。