この製品のデータシートに間違いがありましたので、お詫びして訂正いたします。

この正誤表は、2015年6月17日現在、アナログ・デバイセズ株式会社で確認した誤りを記したものです。

なお、英語のデータシート改版時に、これらの誤りが訂正される場合があります。

正誤表作成年月日：2015年6月17日

製品名：ADCMP391/ADCMP392/ADCMP393

対象となるデータシートのリビジョン(Rev)：Rev.C

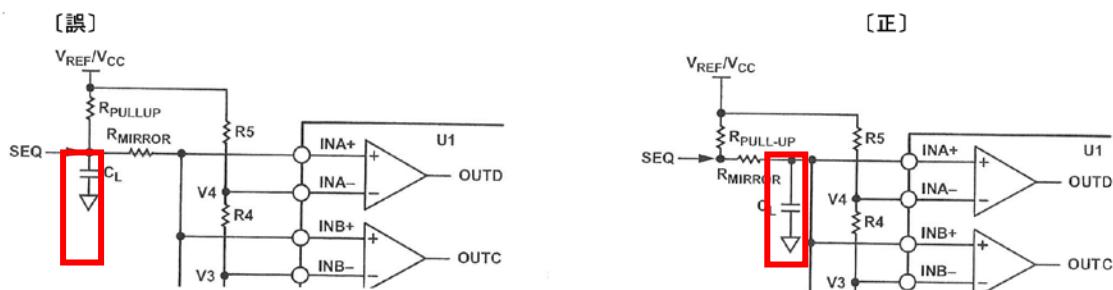

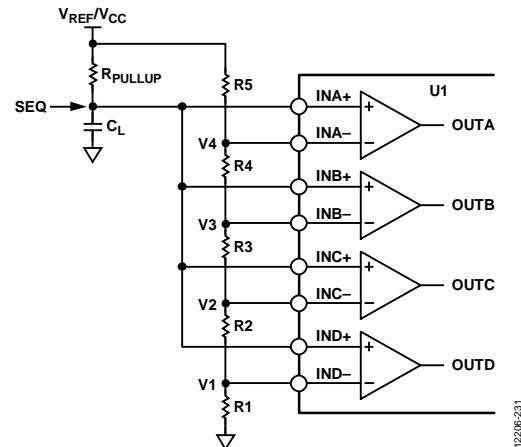

訂正箇所：P.13 図34 ミラー電圧シーケンサの回路構成

図中の左上の回路接続が間違っています。コンデンサ CL の接続位置は、下記の右側の図が正しいものです。

# パワーアップ状態が既知の シングル／デュアル／クワッド・コンパレータ

## データシート

## ADCMP391/ADCMP392/ADCMP393

### 特長

単電源動作: 2.3 V~5.5 V

レール to レールの同相モード入力電圧範囲

$V_{CMR}$  範囲内での低入力オフセット電圧: 1 mV (typ)

$V_{CC} = 0.9 \text{ V}$  から低電圧ロックアウト電圧(UVLO)までのコンパレータ出力ロー・レベルを保証

動作温度範囲: -40°C~+125°C

パッケージ・タイプ:

8 ピン・ナロー・ボディ SOIC (ADCMP391/ADCMP392)

14 ピン・ナロー・ボディ SOIC (ADCMP393)

14 ピン TSSOP (ADCMP393)

### アプリケーション

バッテリの管理/モニタ

電源検出

ウィンドウ・コンパレータ

閾値検出器/弁別器

マイクロプロセッサ・システム

### 概要

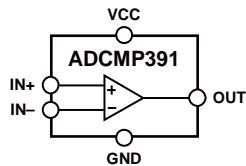

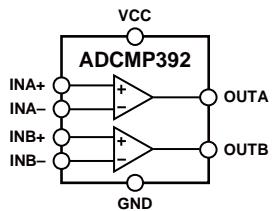

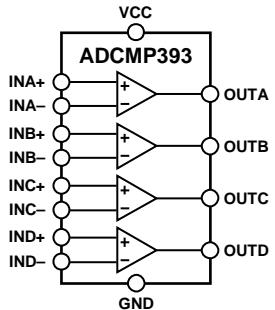

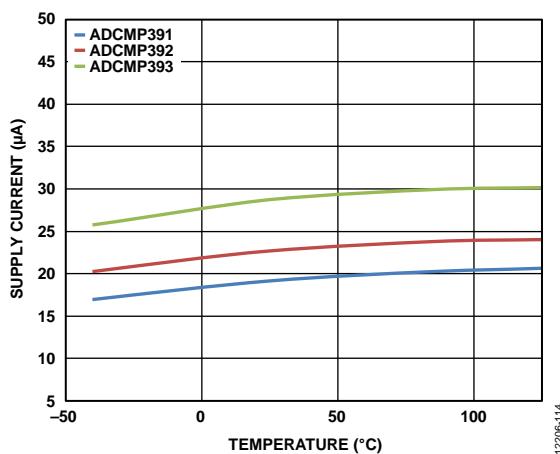

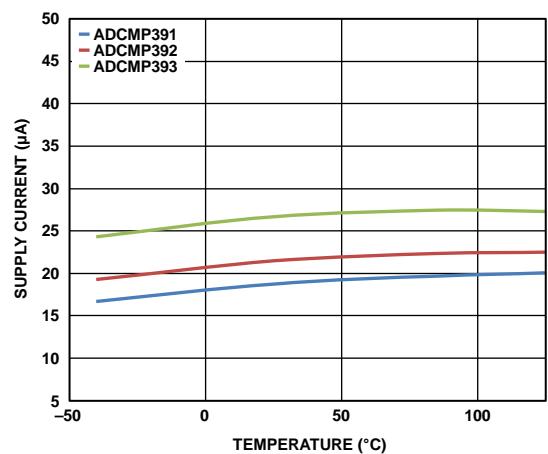

ADCMP391/ADCMP392/ADCMP393 は、それぞれシングル／デュアル／クワッドの汎用アプリケーション向けレール to レール入力低消費電力コンパレータです。これらのコンパレータは 2.3 V~5.5 V の単電源と最小の消費電流で動作します。シングル素子の ADCMP391 の電源電流は僅か 18.6  $\mu\text{A}$  です。デュアル・モデル ADCMP392 とクワッド・モデル ADCMP393 の電源電流はそれぞれ 22.1  $\mu\text{A}$  と 26.8  $\mu\text{A}$  です。これらのデバイスは低電圧かつ低電流動作であるため、バッテリ駆動システムに最適です。

これらのコンパレータは、電源レールを 200 mV 超えることができる同相モード入力電圧範囲と、この全同相モード範囲で 1 mV (typ) のオフセット電圧、UVLO モニタ機能を持っています。さらに、このコンパレータは回路デザインにより、パワーアップ時の出力状態を規定する機能があります。電源電圧が UVLO 閾値を下回っている場合、ロー・レベル出力を発生します。

ADCMP391 と ADCMP392 は 8 ピン・ナロー・ボディ SOIC パッケージを、ADCMP393 は 14 ピン・ナロー・ボディ SOIC パッケージまたは 14 ピン TSSOP パッケージを、それぞれ採用しています。これらのコンパレータの動作は、-40°C~+125°C の拡張温度範囲で規定されています。

### 機能ブロック図

12206-001

図 1.

12206-102

図 2.

12206-103

図 3.

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有者の財産です。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

## 目次

|                   |    |

|-------------------|----|

| 特長                | 1  |

| アプリケーション          | 1  |

| 概要                | 1  |

| 機能ブロック図           | 1  |

| 改訂履歴              | 2  |

| 仕様                | 3  |

| 絶対最大定格            | 4  |

| 熱抵抗               | 4  |

| ESD の注意           | 4  |

| ピン配置およびピン機能説明     | 5  |

| 代表的な性能特性          | 7  |

| 動作原理              | 10 |

| コンパレータの基本動作       | 10 |

| レール to レール入力(RRI) | 10 |

### 改訂履歴

#### 3/15—Rev. B to Rev. C

|                                                                                                   |    |

|---------------------------------------------------------------------------------------------------|----|

| Added ADCMP391/ADCMP392 (Throughout)                                                              | 1  |

| Changes to Equation 4                                                                             | 12 |

| Changes to Equation 13 and 15                                                                     | 13 |

| Changes to Ordering Guide                                                                         | 18 |

| <b>10/14—Rev. A to Rev. B</b>                                                                     |    |

| Added TSSOP Package (Throughout)                                                                  | 1  |

| Changes to Data Sheet Title                                                                       | 1  |

| Added Figure 3; Renumbered Sequentially                                                           | 5  |

| Changes to Open-Drain Output Section                                                              | 9  |

| Changes to Programming Sequencing Control Circuit Section; Added Figure 25; Changes to Figure 26. | 11 |

|                             |    |

|-----------------------------|----|

| オープン・ドレイン出力                 | 10 |

| パワーアップ時の動作                  | 10 |

| クロスオーバー・バイアス・ポイント           | 10 |

| コンパレータのヒステリシス               | 10 |

| 代表的なアプリケーション                | 11 |

| ヒステリシスの付加                   | 11 |

| 正電圧モニタ用のウインドウ・コンパレータ        | 11 |

| 負電圧モニタ用のウ xi ンドウ・コンパレータ     | 12 |

| プログラマブルなシーケンス制御回路           | 12 |

| ミラー電圧シーケンサの例                | 14 |

| 閾値とタイムアウトがプログラマブルな電圧スーパーバイザ | 15 |

| 外形寸法                        | 16 |

| オーダー・ガイド                    | 17 |

Changes to Figure 27 and Figure 28.....12

Changes to Figure 29.....13

Changes to Mirrored Voltage Sequencer Example Section.....13

Changes to Figure 30, and Figure 31.....14

Added Figure 32, Outline Dimensions.....15

Changes to Ordering Guide.....15

#### 6/14—Rev. 0 to Rev. A

|                                                                          |    |

|--------------------------------------------------------------------------|----|

| Changes to Product Title                                                 | 1  |

| Changes to Mirrored Voltage Sequencer Example Section                    | 14 |

| Changes to Threshold and Timeout Programmable Voltage Supervisor Section | 14 |

#### 5/14—Revision 0: Initial Version

## 仕様

特に指定がない限り、 $V_{CC} = 2.3\text{ V} \sim 5.5\text{ V}$ 、 $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ 、 $V_{CMR} = -200\text{ mV} \sim V_{CC} + 200\text{ mV}$ 。Typ 値は  $T_A = 25^\circ\text{C}$  の値。

表 1.

| Parameter                    | Symbol        | Min                      | Typ                  | Max            | Unit          | Test Conditions/Comments <sup>1</sup>                                                                                                                                                                                                                                                  |

|------------------------------|---------------|--------------------------|----------------------|----------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER SUPPLY                 |               |                          |                      |                |               |                                                                                                                                                                                                                                                                                        |

| Supply Voltage               | $V_{CC}$      | 2.3<br>0.9               | 5.5<br>$UVLO_{RISE}$ |                | V             | Guarantees comparator output low                                                                                                                                                                                                                                                       |

| $V_{CC}$ Quiescent Current   | $I_{CC}$      |                          |                      |                |               |                                                                                                                                                                                                                                                                                        |

| ADCMP391                     |               | 18.6                     | 24.7                 |                | $\mu\text{A}$ | All outputs in high-Z state, $V_{OD} = 0.1\text{ V}$                                                                                                                                                                                                                                   |

|                              |               | 18.5                     | 23.8                 |                | $\mu\text{A}$ | All outputs low, $V_{OD} = 0.1\text{ V}$                                                                                                                                                                                                                                               |

| ADCMP392                     |               | 22.1                     | 29.3                 |                | $\mu\text{A}$ | All outputs in high-Z state, $V_{OD} = 0.1\text{ V}$                                                                                                                                                                                                                                   |

|                              |               | 20.7                     | 26.5                 |                | $\mu\text{A}$ | All outputs low, $V_{OD} = 0.1\text{ V}$                                                                                                                                                                                                                                               |

| ADCMP393                     |               | 26.8                     | 36.8                 |                | $\mu\text{A}$ | All outputs in high-Z state, $V_{OD} = 0.1\text{ V}$                                                                                                                                                                                                                                   |

|                              |               | 26.6                     | 34.3                 |                | $\mu\text{A}$ | All outputs low, $V_{OD} = 0.1\text{ V}$                                                                                                                                                                                                                                               |

| UNDERVOLTAGE LOCKOUT         |               |                          |                      |                |               |                                                                                                                                                                                                                                                                                        |

| $V_{CC}$ Rising              | $UVLO_{RISE}$ | 2.062                    | 2.162                | 2.262          | V             |                                                                                                                                                                                                                                                                                        |

| Hysteresis                   | $UVLO_{HYS}$  | 5                        | 25                   | 50             | mV            |                                                                                                                                                                                                                                                                                        |

| COMPARATOR INPUT             |               |                          |                      |                |               |                                                                                                                                                                                                                                                                                        |

| Common-Mode Input Range      | $V_{CMR}$     | -200                     |                      | $V_{CC} + 200$ | mV            |                                                                                                                                                                                                                                                                                        |

| Input Offset Voltage         | $V_{OS}$      | 0.5<br>0.5<br>1<br>1     | 2.5<br>2.5<br>5<br>5 |                | mV            | $INx+ = INx- = 1\text{ V}$<br>$INx+ = INx- = 1\text{ V}, T_A = -40^\circ\text{C} \text{ to } +85^\circ\text{C}$                                                                                                                                                                        |

| Input Offset Current         | $I_{OS}$      |                          |                      | 10             | nA            | $T_A = -40^\circ\text{C} \text{ to } +85^\circ\text{C}$                                                                                                                                                                                                                                |

| Input Bias Current           | $I_{BIAS}$    |                          |                      | $\pm 30$       | nA            | $V_{CMR} = -50\text{ mV} \text{ to } V_{CC} + 50\text{ mV}$                                                                                                                                                                                                                            |

|                              |               |                          |                      | $\pm 80$       | nA            | $INx+ = INx- = 1\text{ V}$                                                                                                                                                                                                                                                             |

|                              |               |                          |                      | $\pm 10$       | nA            | $V_{CMR} = -50\text{ mV} \text{ to } V_{CC} + 50\text{ mV}$                                                                                                                                                                                                                            |

| Input Hysteresis             | $V_{HYS}$     | 3<br>6                   | 4<br>8               |                | mV            | $V_{CMR} = -50\text{ mV} \text{ to } V_{CC} + 50\text{ mV}, T_A = -40^\circ\text{C} \text{ to } +85^\circ\text{C}$                                                                                                                                                                     |

|                              |               |                          |                      |                | mV            | $V_{CM} = 1\text{ V}$                                                                                                                                                                                                                                                                  |

| COMPARATOR OUTPUT            |               |                          |                      |                |               |                                                                                                                                                                                                                                                                                        |

| Output Low Voltage           | $V_{OL}$      | 0.1<br>0.01              | 0.3<br>0.15          |                | V             | $V_{CC} = 2.3\text{ V}, I_{SINK} = 2.5\text{ mA}$                                                                                                                                                                                                                                      |

| Output Leakage Current       | $I_{LEAK}$    |                          |                      | 150            | nA            | $V_{CC} = 0.9\text{ V}, I_{SINK} = 100\text{ }\mu\text{A}$<br>$V_{OUT} = 0\text{ V} \text{ to } 5.5\text{ V}$                                                                                                                                                                          |

| COMPARATOR CHARACTERISTICS   |               |                          |                      |                |               |                                                                                                                                                                                                                                                                                        |

| Power Supply Rejection Ratio | PSRR          | 60                       | 80                   |                | dB            |                                                                                                                                                                                                                                                                                        |

| Common-Mode Rejection Ratio  | CMRR          | 50                       | 74                   |                | dB            |                                                                                                                                                                                                                                                                                        |

| Voltage Gain                 | $A_V$         |                          | 132                  |                | dB            |                                                                                                                                                                                                                                                                                        |

| Rise Time <sup>2</sup>       | $t_R$         |                          | 1.1                  |                | $\mu\text{s}$ | $V_{OUT} = 10\%$ to 90% of $V_{CC}$                                                                                                                                                                                                                                                    |

| Fall Time <sup>2</sup>       | $t_F$         |                          | 0.15                 |                | $\mu\text{s}$ | $V_{OUT} = 90\%$ to 10% of $V_{CC}$                                                                                                                                                                                                                                                    |

| Propagation Delay            |               |                          |                      |                |               |                                                                                                                                                                                                                                                                                        |

| Input Rising <sup>2</sup>    | $t_{PROP\_R}$ | 4.7<br>4.9<br>2.8<br>3.2 |                      |                | $\mu\text{s}$ | $V_{CM} = 1\text{ V}, V_{CC} = 2.3\text{ V}, V_{OD} = 10\text{ mV}$<br>$V_{CM} = 1\text{ V}, V_{CC} = 5\text{ V}, V_{OD} = 10\text{ mV}$<br>$V_{CM} = 1\text{ V}, V_{CC} = 2.3\text{ V}, V_{OD} = 100\text{ mV}$<br>$V_{CM} = 1\text{ V}, V_{CC} = 5\text{ V}, V_{OD} = 100\text{ mV}$ |

| ADCMP392 Channel B           |               | 4.9<br>9.7               |                      |                | $\mu\text{s}$ | $V_{CM} = 1\text{ V}, V_{CC} = 2.3\text{ V}, V_{OD} = 10\text{ mV}$<br>$V_{CM} = 1\text{ V}, V_{CC} = 5\text{ V}, V_{OD} = 10\text{ mV}$                                                                                                                                               |

| Input Falling <sup>2</sup>   | $t_{PROP\_F}$ | 4.5<br>9.5<br>2<br>4.2   |                      |                | $\mu\text{s}$ | $V_{CM} = 1\text{ V}, V_{CC} = 2.3\text{ V}, V_{OD} = 10\text{ mV}$<br>$V_{CM} = 1\text{ V}, V_{CC} = 5\text{ V}, V_{OD} = 10\text{ mV}$<br>$V_{CM} = 1\text{ V}, V_{CC} = 2.3\text{ V}, V_{OD} = 100\text{ mV}$<br>$V_{CM} = 1\text{ V}, V_{CC} = 5\text{ V}, V_{OD} = 100\text{ mV}$ |

| ADCMP392 Channel B           |               | 4.7<br>5                 |                      |                | $\mu\text{s}$ | $V_{CM} = 1\text{ V}, V_{CC} = 2.3\text{ V}, V_{OD} = 10\text{ mV}$<br>$V_{CM} = 1\text{ V}, V_{CC} = 5\text{ V}, V_{OD} = 10\text{ mV}$                                                                                                                                               |

<sup>1</sup>  $V_{OD}$  = オーバードライブ電圧。<sup>2</sup>  $R_{PULLUP} = 10\text{ k}\Omega$ 、 $C_L = 50\text{ pF}$ 。

## 絶対最大定格

表 2.

| Parameter                             | Rating          |

|---------------------------------------|-----------------|

| VCC Pin                               | -0.3 V to +6 V  |

| All INx+ and INx- Pins                | -0.3 V to +6 V  |

| All OUTx Pins                         | -0.3 V to +6 V  |

| OUTx Pins Sink Current ( $I_{SINK}$ ) | 10 mA           |

| Storage Temperature Range             | -65°C to +150°C |

| Operating Temperature Range           | -40°C to +125°C |

| Lead Temperature (10 sec)             | 300°C           |

| Junction Temperature                  | 150°C           |

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作のセクションに記載する規定値以上での製品動作を定めたものではありません。製品を長時間絶対最大定格状態に置くと製品の信頼性に影響を与えます。

### 熱抵抗

表 3. 热抵抗

| Package Type             | $\theta_{JA}$ | Unit |

|--------------------------|---------------|------|

| 8-Lead Narrow-Body SOIC  | 121           | °C/W |

| 14-Lead Narrow-Body SOIC | 80            | °C/W |

| 14-Lead TSSOP            | 125           | °C/W |

### ESD の注意

ESD（静電放電）の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術であるESD保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

## ピン配置およびピン機能説明

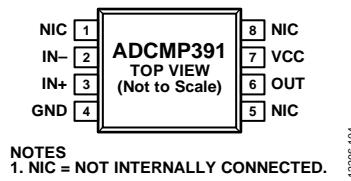

図 4. ADCMP391 のピン配置

表 4. ADCMP391 のピン機能説明

| ピン番号    | 記号  | 説明                 |

|---------|-----|--------------------|

| 1, 5, 8 | NIC | 内部に未接続             |

| 2       | IN- | コンパレータ反転入力         |

| 3       | IN+ | コンパレータ非反転入力        |

| 4       | GND | デバイス・グラウンド         |

| 6       | OUT | コンパレータ出力、オープン・ドレイン |

| 7       | VCC | デバイス電源入力           |

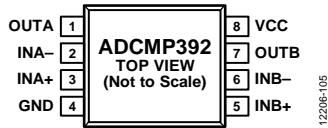

図 5. ADCMP392 のピン配置

表 5. ADCMP392 のピン機能説明

| ピン番号 | 記号   | 説明                    |

|------|------|-----------------------|

| 1    | OUTA | コンパレータ A 出力、オープン・ドレイン |

| 2    | INA- | コンパレータ A 反転入力         |

| 3    | INA+ | コンパレータ A 非反転入力        |

| 4    | GND  | デバイス・グラウンド            |

| 5    | INB+ | コンパレータ B 非反転入力        |

| 6    | INB- | コンパレータ B 反転入力         |

| 7    | OUTB | コンパレータ B 出力、オープン・ドレイン |

| 8    | VCC  | デバイス電源入力              |

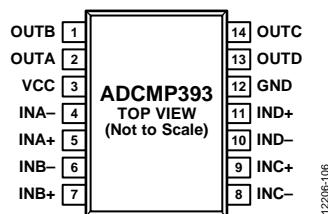

図 6. ADCMP393 SOIC のピン配置

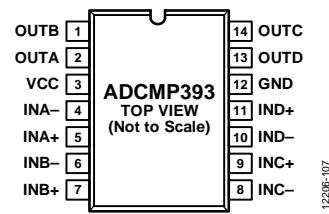

図 7. ADCMP393 TSSOP のピン配置

表 6. ADCMP393 のピン機能説明

| ピン番号 | 記号   | 説明                    |

|------|------|-----------------------|

| 1    | OUTB | コンパレータ B 出力、オープン・ドレイン |

| 2    | OUTA | コンパレータ A 出力、オープン・ドレイン |

| 3    | VCC  | デバイス電源入力              |

| 4    | INA- | コンパレータ A 反転入力         |

| 5    | INA+ | コンパレータ A 非反転入力        |

| 6    | INB- | コンパレータ B 反転入力         |

| 7    | INB+ | コンパレータ B 非反転入力        |

| 8    | INC- | コンパレータ C 反転入力         |

| 9    | INC+ | コンパレータ C 非反転入力        |

| 10   | IND- | コンパレータ D 反転入力         |

| 11   | IND+ | コンパレータ D 非反転入力        |

| 12   | GND  | デバイス・グラウンド            |

| 13   | OUTD | コンパレータ D 出力、オープン・ドレイン |

| 14   | OUTC | コンパレータ C 出力、オープン・ドレイン |

## 代表的な性能特性

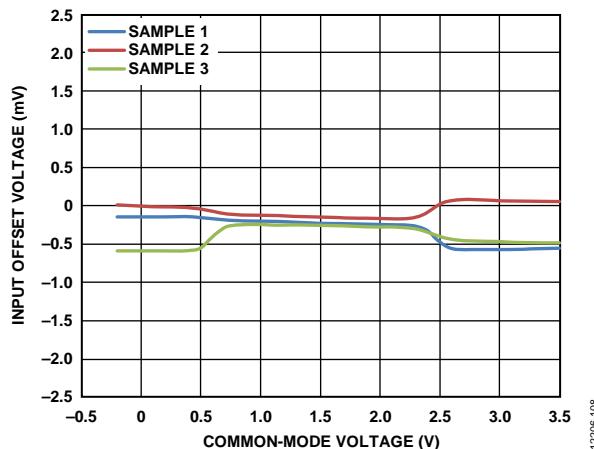

図 8. 入力オフセット電圧 ( $V_{OS}$ )対同相電圧 ( $V_{CM}$ )

$V_{CC} = 3.3\text{ V}$

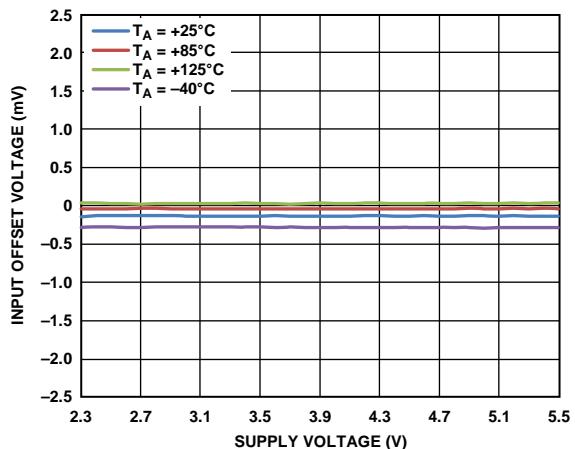

図 11. 様々な温度での電源電圧 ( $V_{CC}$ )対

入力オフセット電圧 ( $V_{OS}$ )、 $V_{CM} = 1\text{ V}$

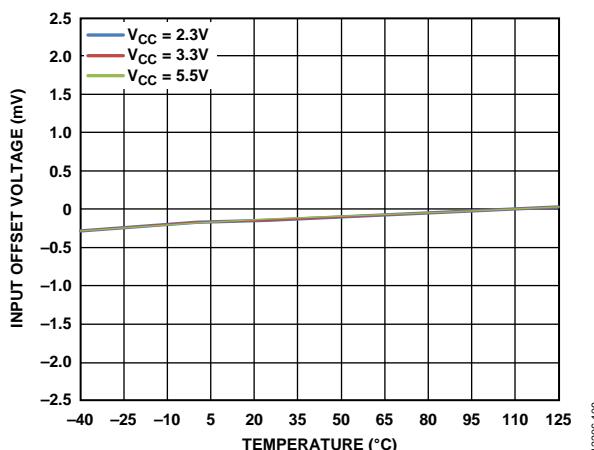

図 9. 様々な電源電圧 ( $V_{CC}$ )での入力オフセット電圧 ( $V_{OS}$ )の温度

特性、 $V_{CM} = 1\text{ V}$

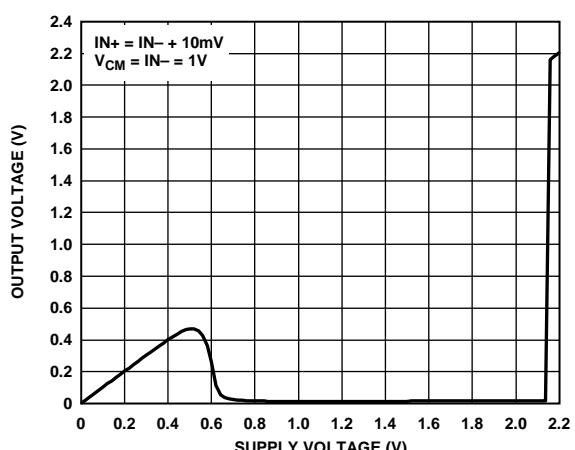

図 12. 定格動作電圧以下の電源電圧 ( $V_{CC}$ )対出力電圧 ( $V_{OUT}$ )

$R_{PULLUP} = 10\text{ k}\Omega$

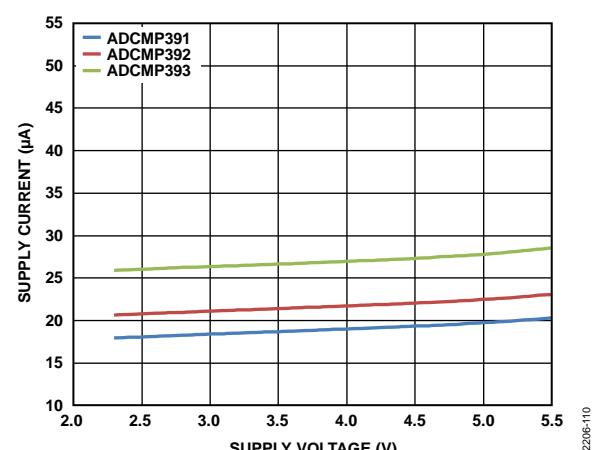

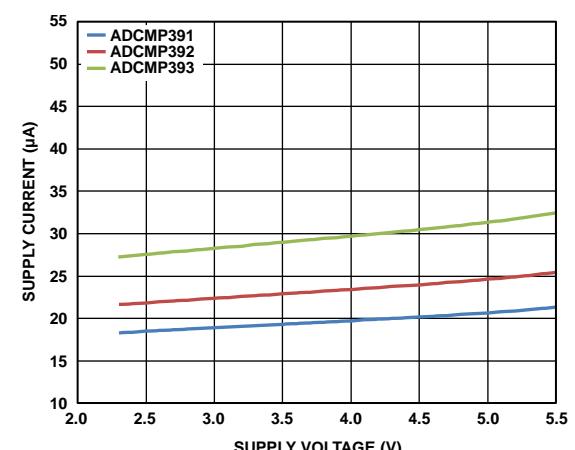

図 10. 様々な温度での電源電圧( $V_{CC}$ )対電源電流、出力ロー電圧

図 13. 様々な温度での電源電圧( $V_{CC}$ )対電源電流、出力ハイ電圧

図 14. 様々な電源電圧 ( $V_{\text{CC}}$ )での電源電流の温度特性

出力ハイ電圧

図 17. 様々な電源電圧 ( $V_{\text{CC}}$ )での電源電流の温度特性

出力ローレベル電圧

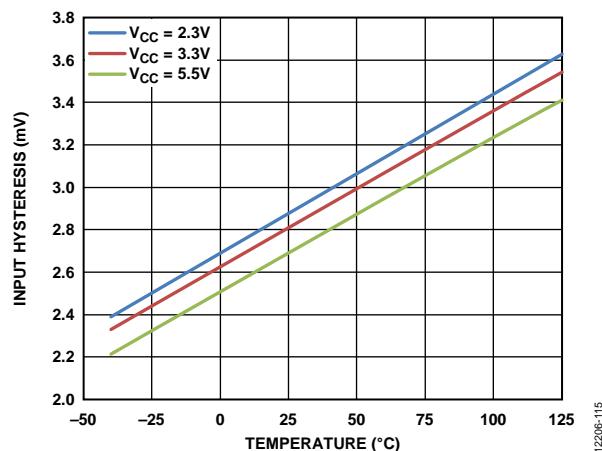

図 15. 様々な電源電圧 ( $V_{\text{CC}}$ )での入力ヒステリシスの温度特性

$V_{\text{CM}} = 1\text{V}$

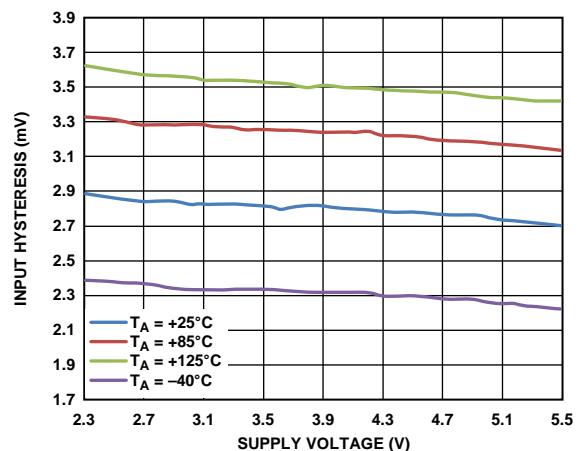

図 18. 様々な温度での電源電圧 ( $V_{\text{CC}}$ )対入力ヒステリシス

$V_{\text{CM}} = 1\text{V}$

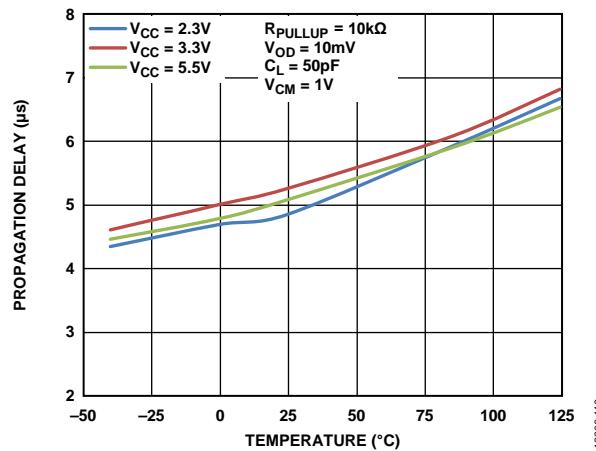

図 16. 伝搬遅延の温度特性

ロード・レベル→ハイ・レベル、 $V_{\text{OD}} = 10\text{ mV}$

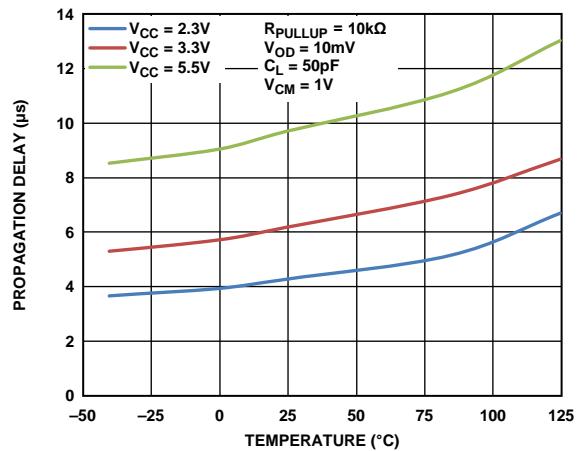

図 19. 伝搬遅延の温度特性

ハイ・レベル→ロード・レベル、 $V_{\text{OD}} = 10\text{ mV}$

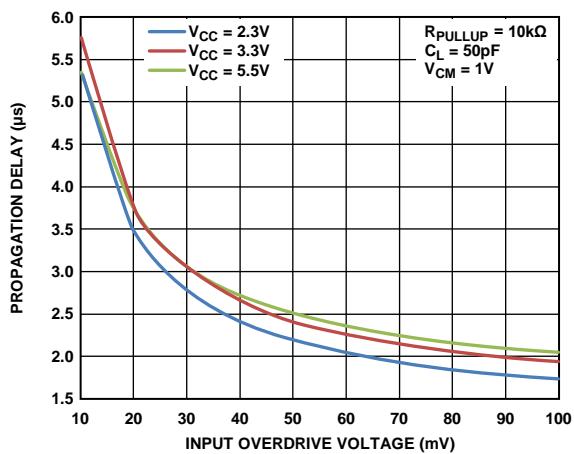

図 20. 入力オーバードライブ電圧対伝搬遅延

ロー・レベル→ハイ・レベル

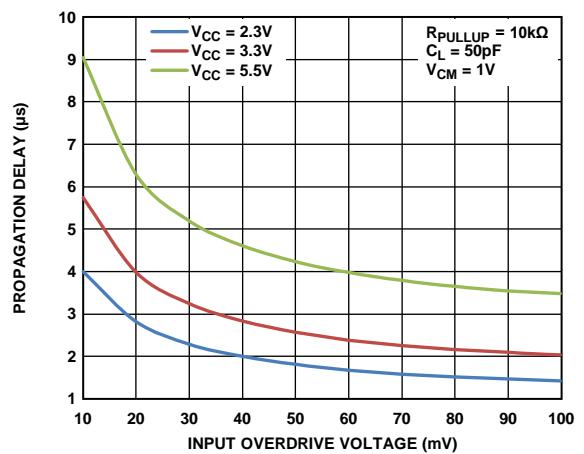

図 23. 入力オーバードライブ電圧対伝搬遅延

ハイ・レベル→ロー・レベル

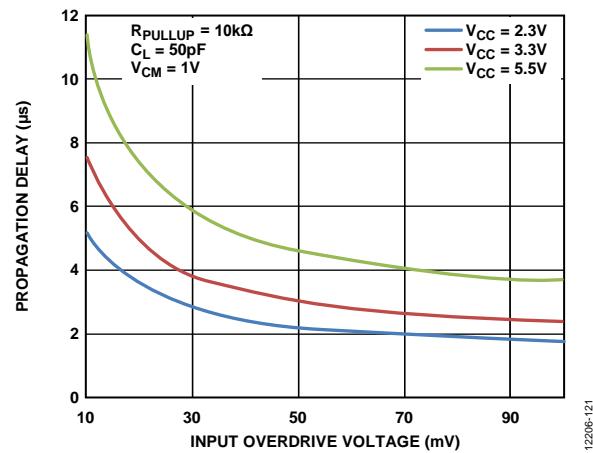

図 21. 入力オーバードライブ電圧対伝搬遅延

ロー・レベル→ハイ・レベル、ADCMP392 チャンネル B

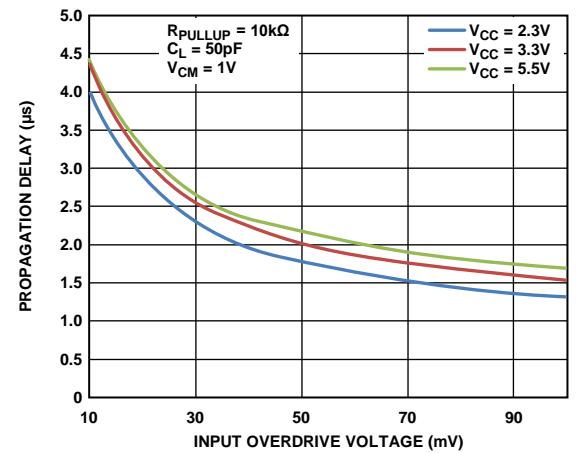

図 24. 入力オーバードライブ電圧対伝搬遅延

ハイ・レベル→ロー・レベル、ADCMP392 チャンネル B

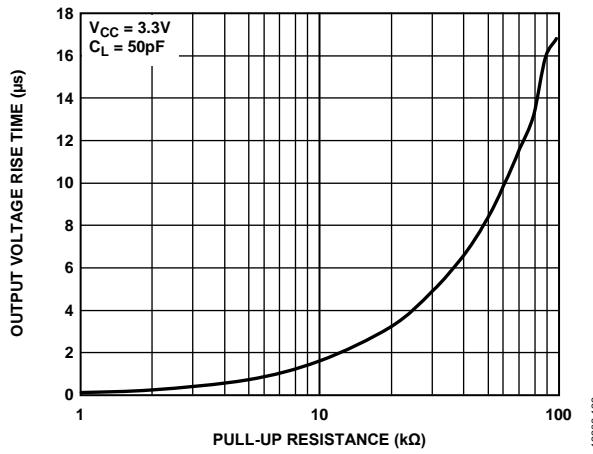

図 22. プルアップ抵抗 ( $R_{PULLUP}$ )対出力電圧立ち上がり時間 ( $t_R$ )

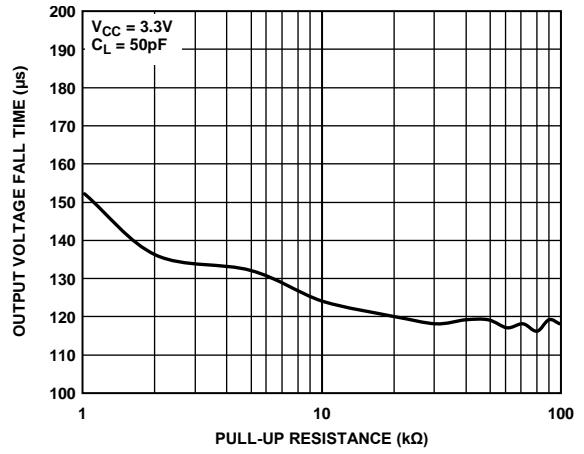

図 25. プルアップ抵抗 ( $R_{PULLUP}$ )対出力電圧立ち下がり時間 ( $t_F$ )

## 動作原理

### コンパレータの基本動作

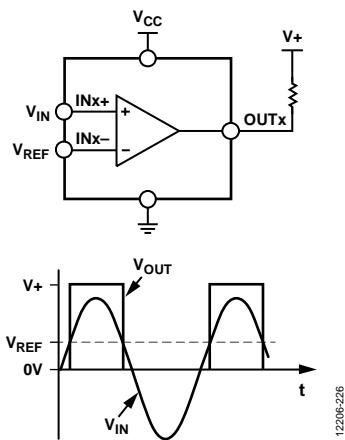

最も基本的な構成では、コンパレータを使ってアナログ入力信号をデジタル出力信号へ変換することができます(図 26 参照)。INx+のアナログ信号を INx-の電圧と比較し、INx+の電位が INx-より高いか否かに応じて、それぞれ OUTx 電圧をハイ・レベルまたはロー・レベルにします。

図 26. 基本コンパレータと入力/出力信号

### レール to レール入力(RRI)

CMOS のレール to レールではない入力ステージ(シングル差動対)を使うと、入力動作電圧が電源ラインから約 1 個分のゲートトーソース間電圧(V<sub>GS</sub>)だけ離れた電圧に制限されてしまいます。通常動作での V<sub>GS</sub> は一般に 1V を超えるため、シングル差動対の入力ステージを使うコンパレータは、大幅に許容入力電圧範囲が制限されます。この制約は、低電圧電源動作でより厳しくなります。この問題を解決するため、レール to レール入力(RRI)ステージを使って入力信号範囲を電源電圧範囲まで広げます。ADCMP391/ADCMP392/ADCMP393 の場合、入力は電源レールの外側 200mV まで正常動作を続けます。

### オープン・ドレン出力

ADCMP391/ADCMP392/ADCMP393 は、出力トランジスタがスイッチ・オフ(オープン H)したときロジック・ハイ電圧レベルへプルアップする外付け抵抗を必要とするオープン・ドレン出力ステージを持っています。プルアップ抵抗は消費電力を小さくするため十分大きくする必要がありますが、コンパレータ出力を他のデジタル回路に接続したときに、ロジック・レベルを迅速に切り替えるためには、逆に十分小さくする必要があります。オープン・ドレン出力の立ち上がり時間は、使用するプルアップ抵抗(R<sub>PULLUP</sub>)と負荷コンデンサ(C<sub>L</sub>)に依存します。立ち上がり時間は次式で計算されます。

$$t_R = 2.2 R_{PULLUP} C_L \quad (10\% - 90\%) \quad (1)$$

### パワー・アップ時の動作

パワー・アップ時、V<sub>CC</sub> が 0.9V に到達すると、ADCMP391/ADCMP392/ADCMP393 はロー・レベルを出力するように保証されています。V<sub>CC</sub> ピンの電圧が UVLO を超えると、コンパレータ入力により出力が制御されます。

### クロスオーバー・バイアス・ポイント

オペアンプとコンパレータのこのタイプのレール to レール入力アーキテクチャは、デュアル・フロントエンド設計を採用しています。PMOS デバイスは V<sub>CC</sub> レールの近くで非アクティブになります。NMOS デバイスは GND の近くで非アクティブになります。したがって同相モード・レンジ内のある既定のポイントで入力素子動作のクロスオーバーが発生します。このポイント(通常 0.8V と V<sub>CC</sub> - 0.8V)で、オフセット電圧の測定値が変化します。

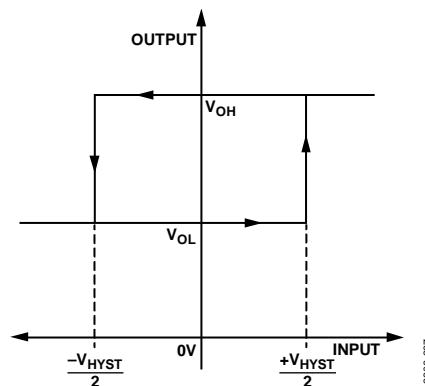

### コンパレータのヒステリシス

ノイズの多い環境、あるいは差動入力振幅が比較的小さいか、または低速の場合は、コンパレータにヒステリシス(V<sub>HYS</sub>)を付加することが望ましくなります。図 27 に、ヒステリシスを持つコンパレータの伝達関数を示します。入力電圧が閾値の下の領域から正の方向へ向かって閾値(図 27 では 0V)に近づき、さらに V<sub>HYS</sub>/2 を横切ると、コンパレータがロー・レベルからハイ・レベルへ変化します。新しいスイッチング閾値は -V<sub>HYS</sub>/2 になります。入力が閾値の下の領域で新しい閾値 -V<sub>HYS</sub>/2 を負方向へ横切るまで、コンパレータはそのハイ・レベル状態を維持します。この方法では、0V 入力を中心とするノイズまたは帰還出力信号が ±V<sub>HYS</sub>/2 で囲まれた領域を超えない限り、コンパレータの状態を変えることはありません。

図 27. コンパレータ・ヒステリシスの伝達関数

## 代表的なアプリケーション

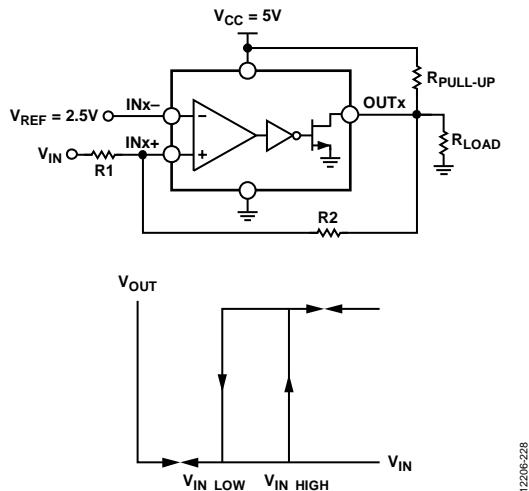

### ヒステリシスの付加

ヒステリシスを付加するときは、図 28 を参照してください。入力信号振幅の増加または減少に応じた異なるスイッチング閾値を、2 本の抵抗を使って発生します。入力電圧が増加する場合は閾値を  $V_{REF}$  より上にし、入力電圧が減少する場合は閾値を  $V_{REF}$  より下にします。

図 28. ヒステリシス付きの非反転コンパレータ構成

上側入力閾値レベルは次式で与えられます。

$$V_{IN\_HI} = \frac{V_{REF}(R1+R2)}{R2} \quad (2)$$

$R_{LOAD} \gg R2$ 、 $R_{PULLUP}$  とすると、

下側入力閾値レベルは次式で与えられます。

$$V_{IN\_LO} = \frac{V_{REF}(R1+R2+R_{PULLUP}) - V_{CC}R1}{R2+R_{PULLUP}} \quad (3)$$

ヒステリシスの幅は、これらの電圧レベル間の差です。

$$V_{HYS} = \frac{V_{REF}(R1)}{R2} - \frac{R1(V_{REF} + V_{CC})}{R2+R_{PULL-UP}} \quad (4)$$

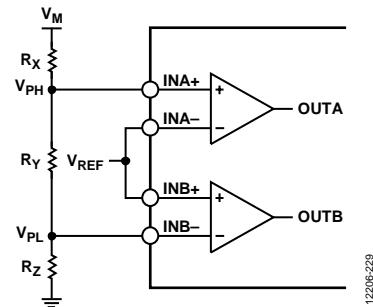

### 正電圧モニタ用のウィンドウ・コンパレータ

正電源レールのモニタリングを説明する場合、モニタリングをする公称動作電圧は  $V_M$  で表し、 $I_M$  は抵抗分圧器の公称電流、 $V_{ov}$  は過電圧トリップ・ポイント、 $V_{uv}$  は低電圧トリップ・ポイントと表します。

図 29. 正電源の低電圧/過電圧モニタリングの構成

図 29 に、正電圧モニタリングの入力接続を示します。3 本の外付け抵抗( $R_X$ 、 $R_Y$ 、 $R_Z$ )により、モニタする正電圧( $V_M$ )を上側電圧( $V_{PH}$ )と下側電圧( $V_{PL}$ )に分割します。上側電圧は  $INA+$  ピンへ、下側電圧は  $INB-$  ピンへ、それぞれ接続します。

過電圧状態は、下側電圧(この場合は  $V_{PL}$ )が  $INB+$  ピンで  $V_{REF}$  閾値を超えたときに発生します。下側電圧  $V_{PL}$  は次式で計算されます。

$$V_{PL} = V_{REF} = V_{OV} \left( \frac{R_Z}{R_X + R_Y + R_Z} \right) \quad (5)$$

さらに、

$$R_X + R_Y + R_Z = V_M / I_M \quad (6)$$

したがって、過電圧モニタのトリップ・ポイントを設定する  $R_Z$  は、次式で計算されます。

$$R_Z = \frac{(V_{REF})(V_M)}{(V_{OV})(I_M)} \quad (7)$$

低電圧状態は、上側電圧  $V_{PH}$  が  $INA-$  ピンで  $V_{REF}$  閾値を下回るときに発生します。上側電圧  $V_{PH}$  は次式で計算されます。

$$V_{PH} = V_{REF} = V_{UV} \left( \frac{R_Y + R_Z}{R_X + R_Y + R_Z} \right) \quad (8)$$

$R_Z$  は既知であるため、 $R_Y$  は次式のように表すことができます。

$$R_Y = \frac{(V_{REF})(V_M)}{(V_{UV})(I_M)} - R_Z \quad (9)$$

$R_Y$  と  $R_Z$  が既知の場合は、 $R_X$  は次式で計算できます。

$$R_X = (V_M / I_M) - R_Y - R_Z \quad (10)$$

$V_M$ 、 $I_M$ 、 $V_{ov}$ 、または  $V_{uv}$  が変る場合、各ステップは再計算する必要があります。

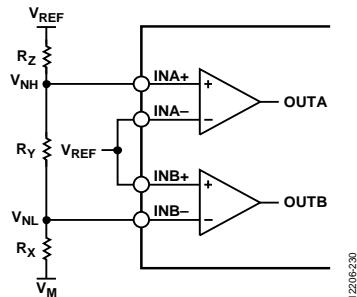

## 負電圧モニタ用のウィンドウ・コンパレータ

図 30 に、負電源電圧モニタリングの回路構成を示します。負電圧をモニタするときは、リファレンス電圧を分圧器回路の終端に(この場合は  $V_{REF}$ )接続する必要があります。

図 30. 負電源の低電圧/過電圧モニタリングの構成

式 7、式 9、式 10 を負電圧モニタリングに適用するときは、これらを少し変更する必要があります。リファレンス電圧  $V_{REF}$  を全体の電圧降下に加算します。このため、 $V_M$ 、 $V_{UV}$ 、 $V_{OV}$  から  $V_{REF}$  を減算した後にこれらを式 7、式 9、式 10 で使用します。

負電圧レベルをモニタするときは、 $V_{REF}$  と負電源電圧との間の電位差を抵抗分圧器により上側電圧  $V_{NH}$  と下側電圧  $V_{NL}$  に分割します。上側電圧  $V_{NH}$  を INC+ に、下側電圧  $V_{NL}$  を IND- に、それぞれ接続します。

過電圧状態が発生するためには、モニタする電圧が公称電圧(振幅)を上回り、かつ INC+ ピンの上側電圧(この場合は  $V_{NH}$ ) がグラウンドを下回る必要があります。上側電圧  $V_{NH}$  は次式で計算されます。

$$V_{NH} = GND = \left[ (V_{REF} - V_{OV}) \left( \frac{R_X + R_Y}{R_X + R_Y + R_Z} \right) \right] + V_{OV} \quad (11)$$

さらに、

$$R_X + R_Y + R_Z = \frac{(V_M - V_{REF})}{I_M} \quad (12)$$

したがって、過電圧モニタのトリップ・ポイントを設定する  $R_Z$  は、次式で計算されます。

$$R_Z = \frac{V_{REF}(V_M - V_{REF})}{I_M(V_{REF} - V_{OV})} \quad (13)$$

低電圧状態は、モニタする電圧が公称電圧(振幅)を下回り、IND- ピンの下側電圧(この場合  $V_{NL}$ ) はグラウンドを上回るときに発生します。下側電圧  $V_{NL}$  は次式で計算されます。

$$V_{NL} = GND = \left[ (V_{REF} - V_{UV}) \left( \frac{R_X}{R_X + R_Y + R_Z} \right) \right] + V_{UV} \quad (14)$$

$R_Z$  は既知であるため、 $R_Y$  は次式のように表すことができます。

$$R_Y = \frac{V_{REF}(V_M - V_{REF})}{I_M(V_{REF} - V_{UV})} - R_Z \quad (15)$$

$R_Y$  と  $R_Z$  が既知の場合は、 $R_X$  は次式で計算されます。

$$R_X = \frac{(V_M - V_{REF})}{I_M} - R_Y - R_Z \quad (16)$$

## プログラマブルなシーケンス制御回路

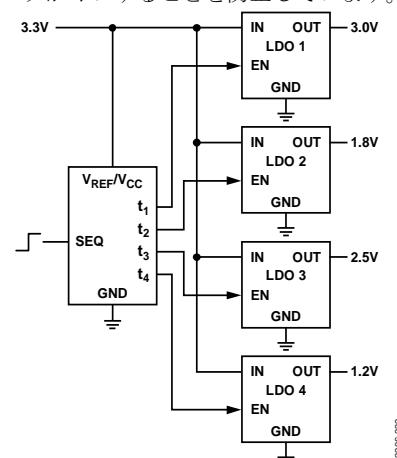

図 31 の回路を使って、電源シーケンスを制御します。遅延は、プルアップ抵抗 ( $R_{PULLUP}$ )、負荷コンデンサ ( $C_L$ )、抵抗分圧器の組み合わせで設定します。

図 31. プログラマブルなシーケンス制御回路

図 32 に、プログラマブルなシーケンス制御回路のシンプルなブロック図を示します。オープン・ドレイン信号 (SEQ) が低インピーダンスから高インピーダンスへ変化するとき、このアプリケーション回路が外部レギュレータ (LDO x) のイネーブル信号 EN を順番に遅延させます。

ADCMP391/ADCMP392/ADCMP393 はスタートアップ時に規定の出力状態を持つため、 $V_{CC}$  が UVLO 閾値を下回っている場合にレギュレータがオンすることを防止しています。

図 32. プログラマブルなシーケンス制御回路の簡略化したブロック図

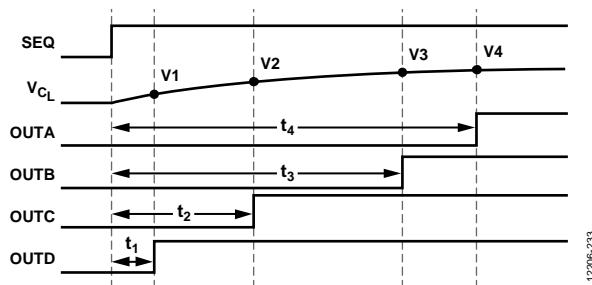

図 33. プログラマブルなシーケンス制御回路のタイミング図

SEQ 信号が低インピーダンスから高インピーダンスへ変化すると、負荷コンデンサ  $C_L$  の電圧が変化し始めます。負荷コンデンサをプルアップ電圧（この場合  $V_{REF}$  または  $V_{CC}$ ）まで充電するためには、この回路内で設定可能な最大遅延になります。ここで使う閾値は、プルアップ電圧の 10%～90% 以内にすることが推奨されます。その際の最大許容遅延は次式で計算されます。

$$t_{MAX} = t_R = 2.2 R_{PULLUP} C_L \quad (17)$$

コンパレータが出力状態を遷移させるときの閾値電圧  $V1 \sim V4$  を変えることにより、各出力の遅延を変えられます。

コンパレータの電圧閾値を計算するときは、次式を使います。

$$V1 = V_{REF} \left( 1 - e^{\frac{-t_1}{R_{PULLUP} C_L}} \right) \quad (18)$$

$$V2 = V_{REF} \left( 1 - e^{\frac{-t_2}{R_{PULLUP} C_L}} \right) \quad (19)$$

$$V3 = V_{REF} \left( 1 - e^{\frac{-t_3}{R_{PULLUP} C_L}} \right) \quad (20)$$

$$V4 = V_{REF} \left( 1 - e^{\frac{-t_4}{R_{PULLUP} C_L}} \right) \quad (21)$$

閾値電圧は、リファレンス電圧または分圧器から得ることができます（図 31 参照）。

まず、抵抗分圧器を流れる許容電流  $I_{DIV}$  を求めます。 $I_{DIV}$  の値を求めた後、次式を使って  $R1, R2, R3, R4, R5$  を計算します。

$$R_{DIV} = \frac{V_{REF}}{I_{DIV}} = R1 + R2 + R3 + R4 + R5 \quad (22)$$

$$R1 = \frac{V1 R_{DIV}}{V_{REF}} \quad (23)$$

$$R2 = \frac{V2 R_{DIV}}{V_{REF}} - R1 \quad (24)$$

$$R3 = \frac{V3 R_{DIV}}{V_{REF}} - R1 - R2 \quad (25)$$

$$R4 = \frac{V4 R_{DIV}}{V_{REF}} - R1 - R2 - R3 \quad (26)$$

$$R5 = R_{DIV} - R1 - R2 - R3 - R4 \quad (27)$$

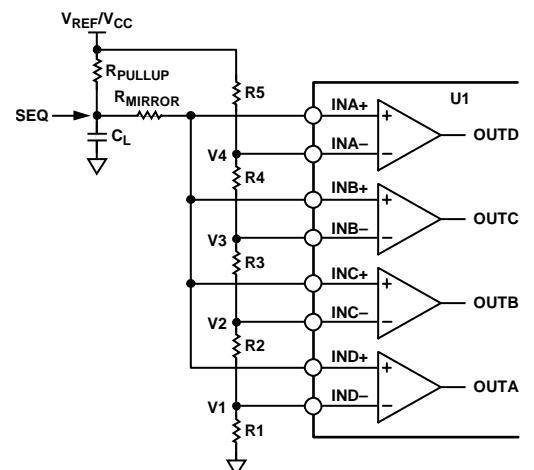

ミラー電圧シーケンス（ON/OFF 対称動作）を発生させるとときは、プルアップ抵抗 ( $R_{PULLUP}$ ) と負荷コンデンサ ( $C_L$ ) との間に抵抗  $R_{MIRROR}$  を追加します（図 34 参照）。

図 34. ミラー電圧シーケンサの回路構成

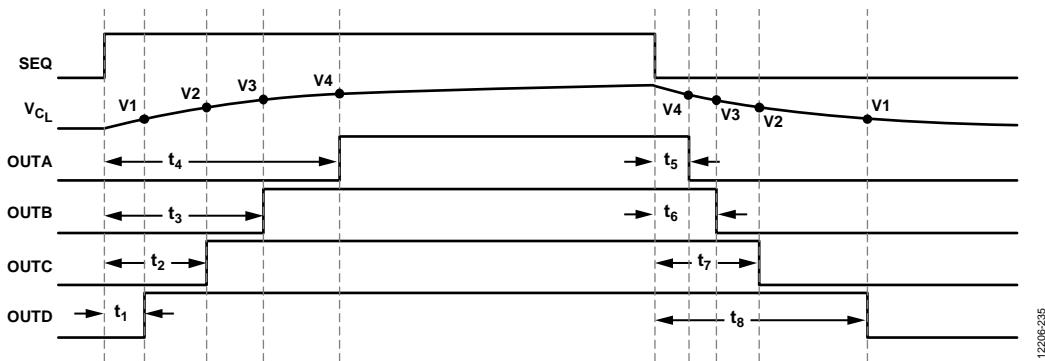

図 34 に、ミラー電圧シーケンサの回路構成を示します。SEQ が低インピーダンスから高インピーダンスへ変化すると、応答は図 33 と同じになります。SEQ が高インピーダンスから低インピーダンスへ変化すると、 $R_{MIRROR}$  で設定されるレートで、負荷コンデンサ ( $C_L$ ) が放電し始めます。各コンパレータの遅延は、 $t_1 \sim t_4$  に対して予め設定された閾値電圧に依存します。この結果が、ミラード・パワーダウン・シーケンスになります。

図 35. ミラー電圧シーケンサのタイミング図

ミラー電圧シーケンサのタイミング図を図 35 に示します。

電圧閾値の計算で、式 18～式 21 では追加抵抗  $R_{MIRROR}$  を考慮する必要があります。これらの新しい閾値を計算するときは、式 28～式 31 を使用してください。

$$V1 = V_{REF} \left( 1 - e^{\frac{-t_1}{(R_{PULLUP} + R_{MIRROR})C_L}} \right) \quad (28)$$

$$V2 = V_{REF} \left( 1 - e^{\frac{-t_2}{(R_{PULLUP} + R_{MIRROR})C_L}} \right) \quad (29)$$

$$V3 = V_{REF} \left( 1 - e^{\frac{-t_3}{(R_{PULLUP} + R_{MIRROR})C_L}} \right) \quad (30)$$

$$V4 = V_{REF} \left( 1 - e^{\frac{-t_4}{(R_{PULLUP} + R_{MIRROR})C_L}} \right) \quad (31)$$

$R_{MIRROR}$  によりコンデンサの放電時間を長くすることにより、ミラー遅延を発生します。ミラー電圧シーケンサでは、式 28～式 31 の同じ閾値を降順に使用しています。ミラー遅延時間の正確な値を計算するときは、式 32～式 35 を使用してください。

$$t_5 = -R_{MIRROR} C_L \ln \left( \frac{V4}{V_{REF}} \right) \quad (32)$$

$$t_6 = -R_{MIRROR} C_L \ln \left( \frac{V3}{V_{REF}} \right) \quad (33)$$

$$t_7 = -R_{MIRROR} C_L \ln \left( \frac{V2}{V_{REF}} \right) \quad (34)$$

$$t_8 = -R_{MIRROR} C_L \ln \left( \frac{V1}{V_{REF}} \right) \quad (35)$$

### ミラー電圧シーケンサの例

ミラー電圧シーケンサの動作については、図 32 を参照してください。これをもとに、 $V_{REF} = 1\text{ V}$  とし、SEQ が低インピーダンスから高インピーダンスへ変化したときに、またはオン時に各レギュレータ間に、50 ms の遅延を必要とするシステムについて検討します。これらの検討条件では、プルアップ抵抗 ( $R_{PULLUP}$ ) と負荷コンデンサ ( $C_L$ ) に対して少なくとも 200 ms の立ち上がり時間が必要です。抵抗  $R_{MIRROR}$  と  $R_{PULLUP}$  の和は、最小所要遅延より長い時間でコンデンサを充電するため、十分大きくする必要があります。対称ミラード・パワーダウン・シーケンスの場合、 $R_{MIRROR}$  の値は、 $R_{PULLUP}$  より十分大きくする必要があります。 $10\text{ k}\Omega$  の  $R_{PULLUP}$  値により、プルダウン電流が  $100\text{ }\mu\text{A}$  に制限されると同時に  $R_{MIRROR}$  に対する適切な値となります。代表的な  $1\text{ }\mu\text{F}$  のコンデンサと  $150\text{ k}\Omega$  の  $R_{MIRROR}$  値により、次の値が得られます。

$$t_{MAX} = 2.2((160 \times 10^3) \times (1 \times 10^{-6})) = 351\text{ ms} \quad (36)$$

各コンパレータに必要とされる閾値電圧は、式 28～式 31 から求められます。例えば、

$$V1 = V_{REF} \left( 1 - e^{\frac{-50 \times 10^{-3}}{(160 \times 10^3 \times 1 \times 10^{-6})}} \right)$$

ここで、 $V1 = 268.38\text{ mV}$ 。

したがって、 $V2 = 464.74\text{ mV}$ 、 $V3 = 608.39\text{ mV}$ 、 $V4 = 713.5\text{ mV}$  となります。

次に、抵抗分圧器を流れる最大電流 ( $I_{DIV}$ ) を  $10\text{ }\mu\text{A}$  とします。この電流から、式 22～式 27 を使って分圧器の全抵抗 ( $R_{DIV}$ ) と個別抵抗値を求めるとき、次のようにになります。

- $R_{DIV} = 100\text{ k}\Omega$

- $R1 = 26.84\text{ k}\Omega \approx 26.7\text{ k}\Omega$

- $R2 = 19.64\text{ k}\Omega \approx 19.6\text{ k}\Omega$

- $R3 = 14.37\text{ k}\Omega \approx 14.3\text{ k}\Omega$

- $R4 = 10.51\text{ k}\Omega \approx 10.5\text{ k}\Omega$

- $R5 = 28.65\text{ k}\Omega \approx 28.7\text{ k}\Omega$

計算した抵抗値は業界の標準値でないため、標準抵抗値を使うと新しい  $R_{DIV}$  値 99.8 kΩ が得られます。抵抗計算値と業界標準値との違いのため、各コンパレータの閾値も変化します。シンプルな分圧器の式を使って新しい閾値値を計算します。

$$VI = V_{REF}R1/R_{DIV} \quad (37)$$

ここで、  $V1 = \frac{1V(26.7\text{ k}\Omega)}{99.8\text{ k}\Omega} = 267.54\text{ mV}$ 。

したがって、  $V2 = 463.93\text{ mV}$ 、  $V3 = 607.21\text{ mV}$ 、  $V4 = 712.42\text{ mV}$  となります。

各コンパレータの閾値が変化したため、各コンパレータの出力変化タイミングも変化します。各コンパレータの新しい遅延値を、次式を使って計算します。

$$t_1 = -C_L(R_{PULLUP} + R_{MIRROR}) \ln \left( 1 - \frac{V1}{V_{REF}} \right) \quad (38)$$

ここで、  $t_1 = -1\text{ }\mu\text{F}(10\text{ k}\Omega + 150\text{ k}\Omega) \ln \left( 1 - \frac{267.54\text{ mV}}{1} \right) = 49.81\text{ ms}$ 。

したがって、  $t_2 = 99.78\text{ ms}$ 、  $t_3 = 149.52\text{ ms}$ 、  $t_4 = 199.4\text{ ms}$  となります。

式 32～式 35 を使って  $t_5$ ～ $t_8$  を計算します。

$$t_5 = -R_{MIRROR}C_L \ln \left( \frac{V4}{V_{REF}} \right)$$

ここで、  $t_5 = -150\text{ k}\Omega \times 1\text{ }\mu\text{F} \times \ln \left( \frac{712.42\text{ mV}}{1} \right) = 50.86\text{ ms}$ 。

したがって、  $t_6 = 74.83\text{ ms}$ 、  $t_7 = 115.2\text{ ms}$ 、  $t_8 = 197.78\text{ ms}$  となります。

## 閾値とタイムアウトがプログラマブルな電圧スーパーバイザ（電圧監視とリセット・トリガー）

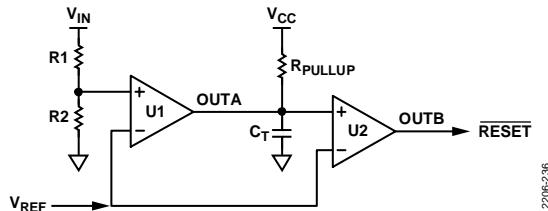

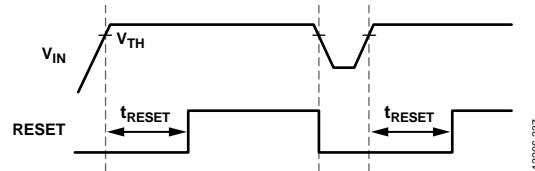

図 36 に、プログラマブルな閾値とタイムアウト回路の回路構成を示します。タイムアウト  $t_{RESET}$  は、  $V_{IN}$  が不安定なときにデバイスが誤動作するのを防止するため、  $\overline{RESET}$  信号をトグルする閾値電圧より入力電圧 ( $V_{IN}$ ) を高く維持する必要がある時間です。  $V_{IN}$  が閾値電圧を下回ると、  $RESET$  信号が迅速にトグルします。

図 36. プログラマブル閾値およびタイムアウト回路

図 37. 閾値とタイムアウトがプログラマブルな電圧スーパーバイザのタイミング図

スタートアップ時、ADCMP391/ADCMP392/ADCMP393 は  $V_{CC}$  が UVLO 閾値を下回っても、ロー・レベル出力状態を保証し、電圧監視回路が不要なトグルをするのを防止します。

$V_{IN}$  が抵抗分圧器 ( $R1$  と  $R2$ ) および  $V_{REF}$  で設定された閾値に到達すると、OUT1 がロー・レベルからハイ・レベルへ変化し、タイムアウト・コンデンサ ( $C_T$ ) の充電を開始します。  $V_{IN}$  を閾値電圧より高く維持し、かつ  $C_T$  の電圧が  $V_{REF}$  に到達すると、OUT2 がトグルされます。 $C_T$  の充電中に、 $V_{IN}$  が閾値電圧を下回ると、タイムアウト・コンデンサが迅速に放電して、 $V_{IN}$  が不安定の間に OUT2 がトグルされるのを防止します。

$V_{IN}$  が  $V_{CC}$  に接続されている場合には、 $V_{CC}$  が最小動作電圧を超えると、回路が動作します。

閾値電圧 ( $V_{TH}$ ) は、抵抗分圧器または  $V_{REF}$  を変化させて設定します。閾値電圧は次式で計算します。

$$V_{TH} = V_{REF} \left( 1 + \frac{R1}{R2} \right) \quad (39)$$

タイムアウトは、プルアップ抵抗値またはタイムアウト・コンデンサを変えて調整します。タイムアウト値を設定するときは、 $R_{PULLUP}$  を流れる許容電流と  $I_{PULLUP}$  を求めます。 $I_{PULLUP}$  が既知の場合、 $R_{PULLUP}$  と  $C_T$  を次式で計算します。

$$R_{PULLUP} = V_{CC}/I_{PULLUP} \quad (40)$$

$$C_T = \frac{-t_{RESET}}{R_{PULLUP} \ln \left( 1 - \frac{V_{REF}}{V_{CC}} \right)} \quad (41)$$

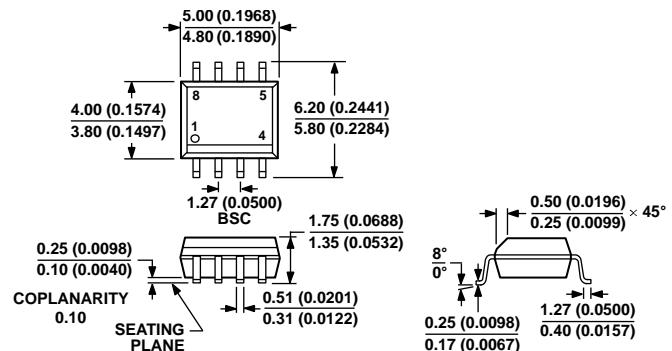

## 外形寸法

COMPLIANT TO JEDEC STANDARDS MS-012-AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

01247-A

図 38. 8 ピン標準スモール・アウトライン・パッケージ[SOIC\_N]

ナロー・ボディ

(R-8)

寸法: mm (インチ)

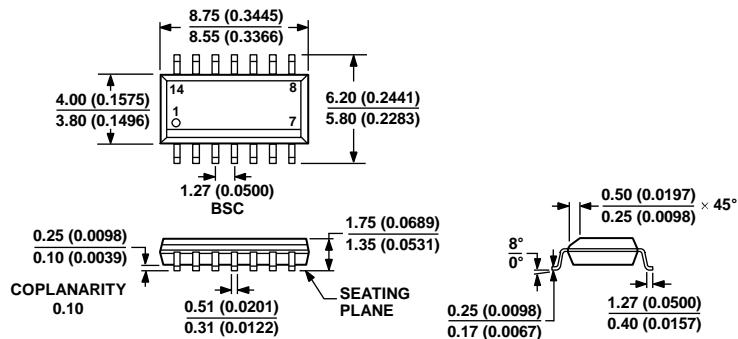

COMPLIANT TO JEDEC STANDARDS MS-012-AB

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

060606-A

図 39. 14 ピン標準スモール・アウトライン・パッケージ[SOIC\_N]

ナロー・ボディ

(R-14)

寸法: mm (インチ)

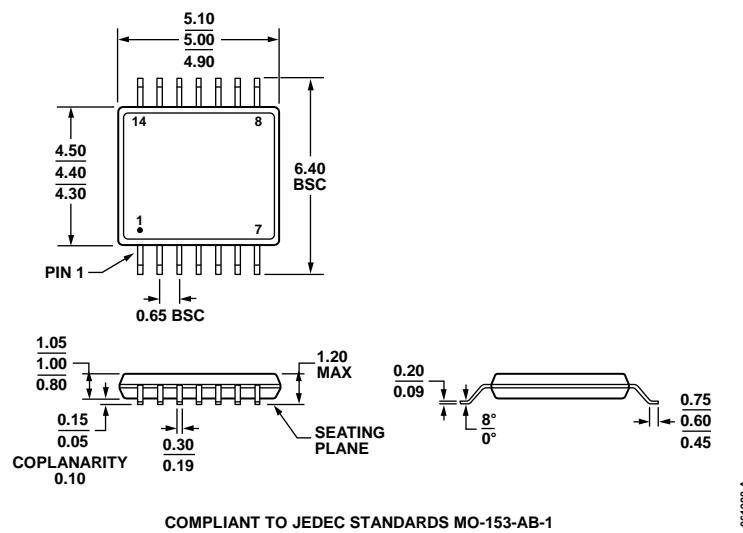

図 40. 14 ピン薄型シュリンク・スモール・アウトライン・パッケージ[TSSOP]

(RU-14)

寸法: mm

## オーダー・ガイド

| Model <sup>1</sup> | Temperature Range | Package Description                               | Package Option |

|--------------------|-------------------|---------------------------------------------------|----------------|

| ADCMP391ARZ        | -40°C to +125°C   | 8-Lead Standard Small Outline Package [SOIC_N]    | R-8            |

| ADCMP391ARZ-RL7    | -40°C to +125°C   | 8-Lead Standard Small Outline Package [SOIC_N]    | R-8            |

| ADCMP392ARZ        | -40°C to +125°C   | 8-Lead Standard Small Outline Package [SOIC_N]    | R-8            |

| ADCMP392ARZ-RL7    | -40°C to +125°C   | 8-Lead Standard Small Outline Package [SOIC_N]    | R-8            |

| ADCMP393ARZ        | -40°C to +125°C   | 14-Lead Standard Small Outline Package [SOIC_N]   | R-14           |

| ADCMP393ARZ-RL7    | -40°C to +125°C   | 14-Lead Standard Small Outline Package [SOIC_N]   | R-14           |

| ADCMP393ARUZ       | -40°C to +125°C   | 14-Lead Thin Shrink Small Outline Package [TSSOP] | RU-14          |

| ADCMP393ARUZ-RL7   | -40°C to +125°C   | 14-Lead Thin Shrink Small Outline Package [TSSOP] | RU-14          |

<sup>1</sup> Z = RoHS 準拠製品。