# 2 ADC、1 DACのオーディオDSP付き 低消費電力コーデック

## データシート

## ADAU1788

### 特長

プログラマブルな FastDSP オーディオ処理エンジン

最大 768kHz のサンプル・レート

バイクワッド・フィルタ、リミッタ、ボリューム制御、

ミキシング

28 ビット SigmaDSP オーディオ処理コア

SigmaStudio を利用して GUI 画面でプログラム可能

最大 50MIPS の性能

低遅延の 24 ビット ADC および DAC

96dB の S/N 比 (PGA および ADC を通した信号に A 加重

フィルタを適用した場合)

105dB の合計 S/N 比 (DAC およびヘッドフォンを通した

信号に A 加重フィルタを適用した場合)

シリアルポートの  $f_{SYNC}$  周波数 : 8~768kHz

5μs の群遅延 ( $f_s = 768\text{kHz}$ ) 、アナログ入力からアナログ

出力まで

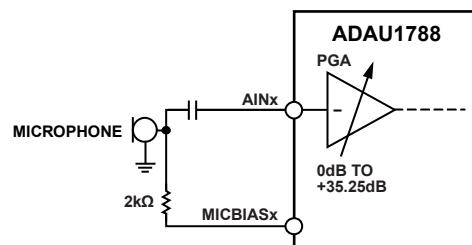

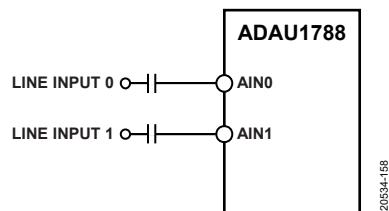

2 つのシングルエンド・アナログ入力 : マイクロフォン入力

またはライン入力として設定可能

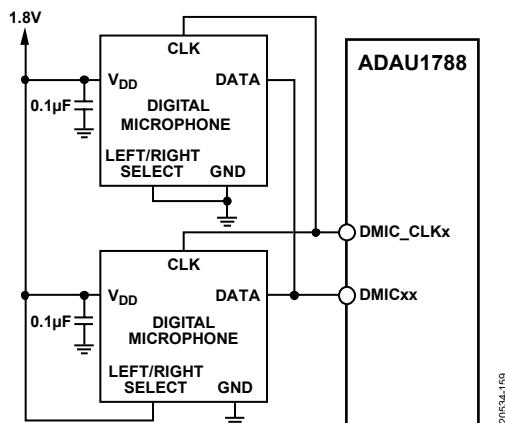

4 つのデジタル・マイクロフォン入力

1 つのアナログ差動オーディオ出力 : ライン出力または

ヘッドフォン・ドライバとして設定可能

PLL は 30kHz~27MHz の任意の入力クロック・レートに

対応

全二重、4 チャンネル非同期サンプル・レート・コンバータ

(ASRC)

16 チャンネル・シリアル・オーディオ・ポートは I<sup>2</sup>S、

左揃え、TDM16 までの TDM に対応

柔軟なルーティングが可能な 8 つのインターポレータと

8 つのデシメータ

電源

アナログ AVDD : 1.8V (代表値)

デジタル I/O IOVDD : 1.1~1.98V

デジタル DVDD : 0.9V (代表値)

低消費電力 (標準的な消費電力は 8.030mW)

I<sup>2</sup>C インターフェースおよび SPI 制御インターフェース

柔軟な GPIO

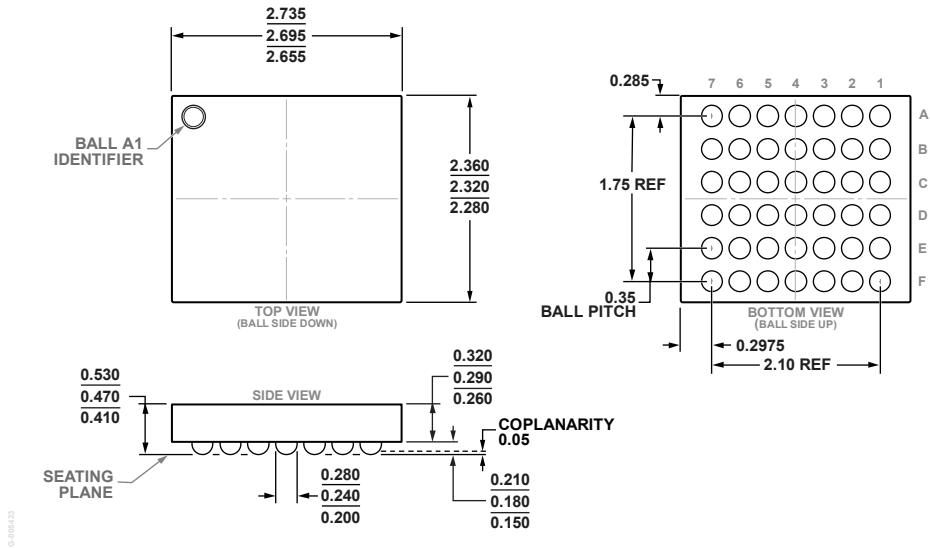

42 ポール、0.35mm ピッチ、2.695mm × 2.320mm WLCSP

### アプリケーション

ノイズ・キャンセリング機能搭載のハンドセット、ヘッド

セット、ヘッドフォン

BlueTooth ANC 機能搭載のハンドセット、ヘッドセット、

ヘッドフォン

個人向けナビゲーション機器

デジタル・カメラおよびビデオ・カメラ

楽器用のエフェクト・プロセッサ

マルチメディア・スピーカ・システム

スマートフォン

### 概要

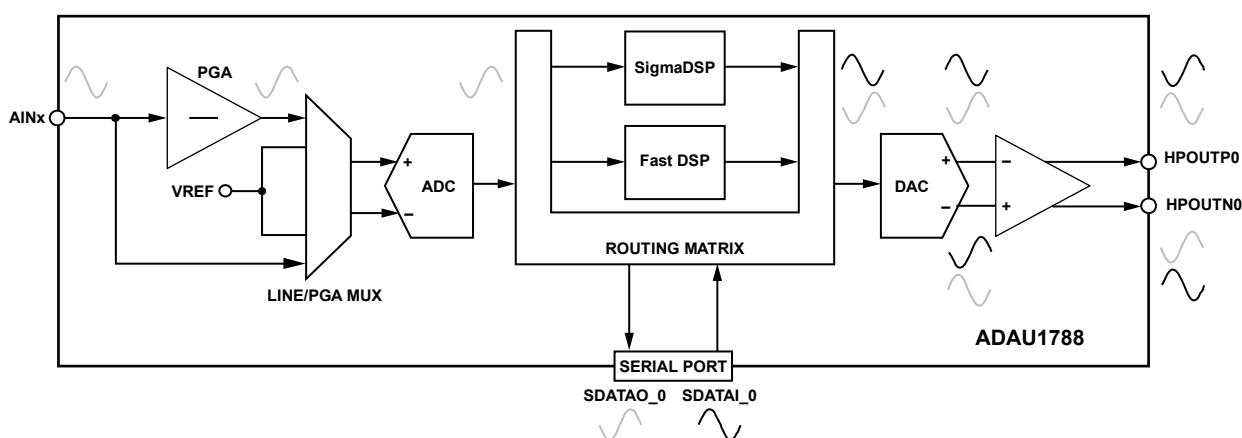

ADAU1788 は、2 つのデジタル・シグナル・プロセッサ

(DSP) を搭載する 2 入力、1 出力のコーデックです。アナ

ログ入力から DSP コアを経由してアナログ出力に至る経路

は、低遅延になるように最適化されており、ノイズ・キャン

セリング・ヘッドセットに最適です。少数の受動部品を追加

するだけで、ADAU1788 はノイズ・キャンセリング・ヘッ

ドフォン・ソリューションを提供します。

このデータシートでは、BCLK\_0/MP1 などの多機能ピンに

ついてはすべてのピン名を表記しますが、特定の機能のみが

該当するような説明箇所では、BCLK\_0 のように 1 つのピ

ン機能だけを表記しています。

## 目次

|                               |    |                                    |    |

|-------------------------------|----|------------------------------------|----|

| 特長                            | 1  | フラグと条件付き実行                         | 41 |

| アプリケーション                      | 1  | 入力ソース                              | 41 |

| 概要                            | 1  | 電源と実行の制御                           | 42 |

| 改訂履歴                          | 5  | データ・メモリ                            | 42 |

| 機能ブロック図                       | 6  | パラメータ                              | 42 |

| 仕様                            | 7  | パラメータ・バンクの切替え                      | 42 |

| アナログ性能仕様                      | 7  | パラメータ・バンクのコピー                      | 42 |

| 水晶発振器アンプの仕様                   | 9  | パラメータ・メモリの読み書き                     | 43 |

| デジタル入出力の仕様                    | 9  | FastDSP パラメータのセーフロード               | 43 |

| 電源の仕様                         | 10 | SigmaDSP コア                        | 44 |

| パワーダウン電流                      | 10 | 信号処理の詳細                            | 44 |

| 消費電力                          | 11 | 読み出し/書き込みデータ・フォーマット                | 45 |

| デジタル・フィルタ                     | 12 | ソフトウェア・セーフロード                      | 46 |

| デジタル・タイミング仕様                  | 13 | FastDSP のセーフロード                    | 46 |

| 絶対最大定格                        | 17 | プログラム RAM、パラメータ RAM、およびデータ RAM     | 47 |

| 熱抵抗                           | 17 | プログラム RAM                          | 47 |

| ESD に関する注意                    | 17 | パラメータ RAM                          | 47 |

| ピン配置およびピン機能の説明                | 18 | データ RAM                            | 47 |

| 代表的な性能特性                      | 21 | 低消費電力オプション                         | 48 |

| システムのブロック図                    | 28 | ADC バイアス電流制御                       | 48 |

| 動作原理                          | 29 | DAC バイアス電流制御                       | 48 |

| システムのクロッキングとパワーアップ            | 30 | DAC 低消費電力モード                       | 48 |

| パワーダウン動作およびオプション              | 30 | PLL バイパス                           | 48 |

| ADC から DAC へのパワーアップ例          | 31 | SigmaDSP のクロック周波数制御                | 49 |

| DVDD LDO レギュレータ               | 31 | 非同期サンプル・レート・コンバータ (ASRC) の低消費電力モード | 49 |

| クロックの初期化                      | 31 | 制御ポート                              | 50 |

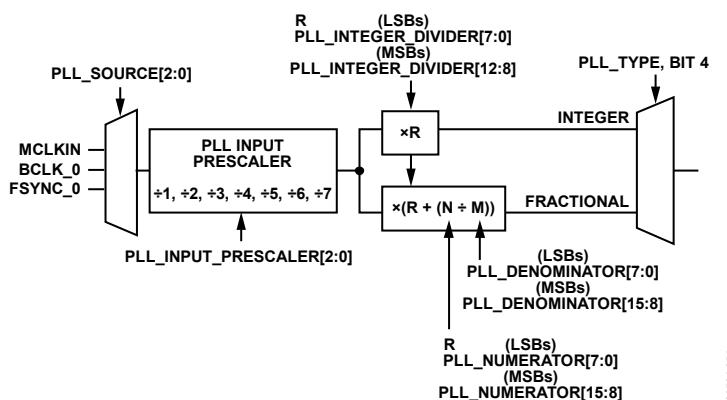

| PLL                           | 32 | バースト・モード通信                         | 50 |

| マルチチップ位相同期                    | 33 | メモリの読み出しと書き込み                      | 51 |

| クロック出力                        | 33 | I <sup>2</sup> C ポート               | 51 |

| 電源シーケンス                       | 33 | SPI ポート                            | 54 |

| 信号ルーティング                      | 34 | 多目的ピン                              | 55 |

| 入力信号経路                        | 35 | シリアル・データ・ポート                       | 56 |

| アナログ入力                        | 35 | アプリケーション情報                         | 58 |

| デジタル・マイクロフォン入力                | 36 | 電源バイパス・コンデンサ                       | 58 |

| ADC                           | 37 | レイアウト                              | 58 |

| 出力信号経路                        | 38 | グラウンド接続                            | 58 |

| アナログ出力                        | 38 | PCB の積層                            | 58 |

| DAC                           | 38 | レジスタの一覧                            | 59 |

| PDM 出力                        | 39 | レジスタの詳細                            | 66 |

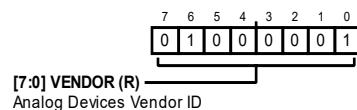

| ASRC                          | 39 | アナログ・デバイセズ・ベンダ ID レジスタ             | 66 |

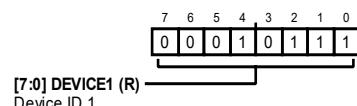

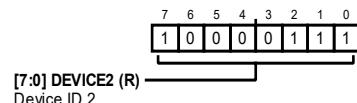

| インターポレーション・ブロックと デシメーション・ブロック | 40 | デバイス ID レジスタ                       | 66 |

| 信号レベル                         | 40 | リビジョン・コード・レジスタ                     | 66 |

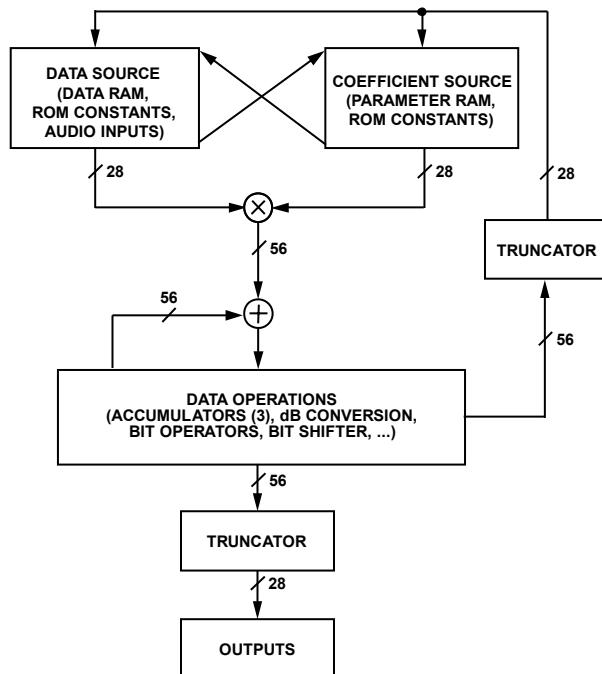

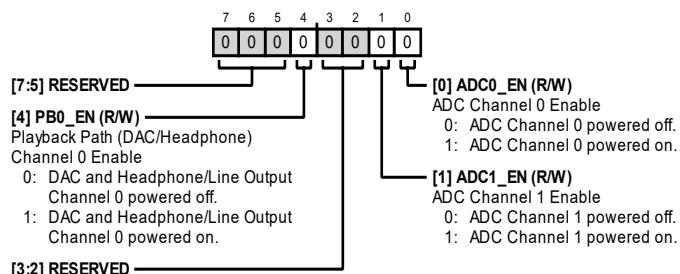

| FastDSP コア                    | 41 | ADC、DAC、およびヘッドフォン・パワー・コントロール・レジスタ  | 67 |

| 命令                            | 41 |                                    |    |

| フィルタ精度                        | 41 |                                    |    |

|                                                             |    |

|-------------------------------------------------------------|----|

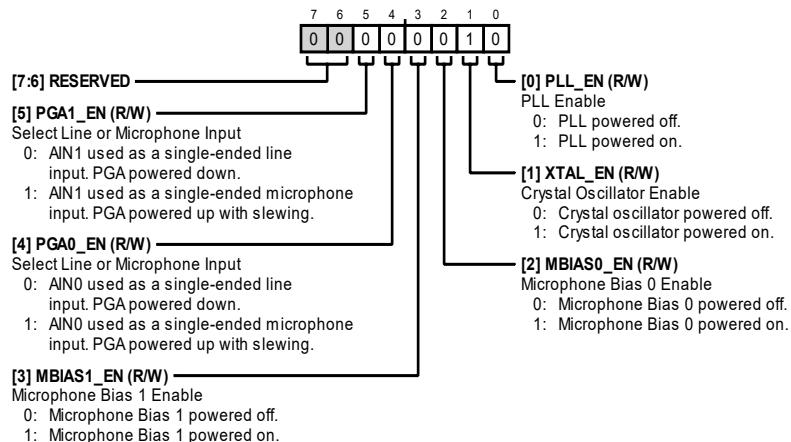

| PLL、マイクロフォン・バイアス、およびPGAパワー・コントロール・レジスタ                      | 67 |

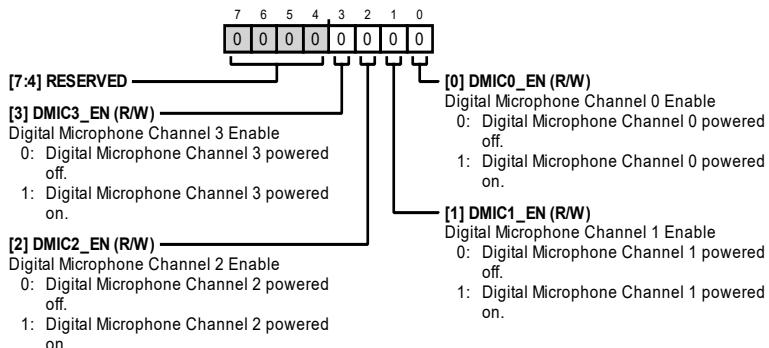

| デジタル・マイクロフォン・パワー・コントロール・レジスタ                                | 68 |

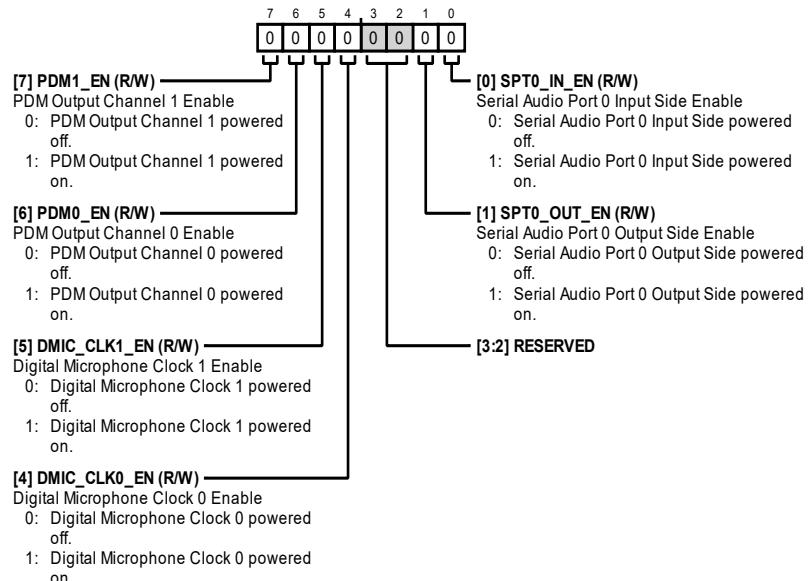

| シリアル・ポート、PDM出力、およびデジタル・マイクロフォン・クロック・パワー・コントロール・レジスタ         | 69 |

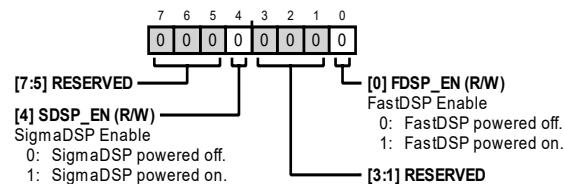

| DSPパワー・コントロール・レジスタ                                          | 70 |

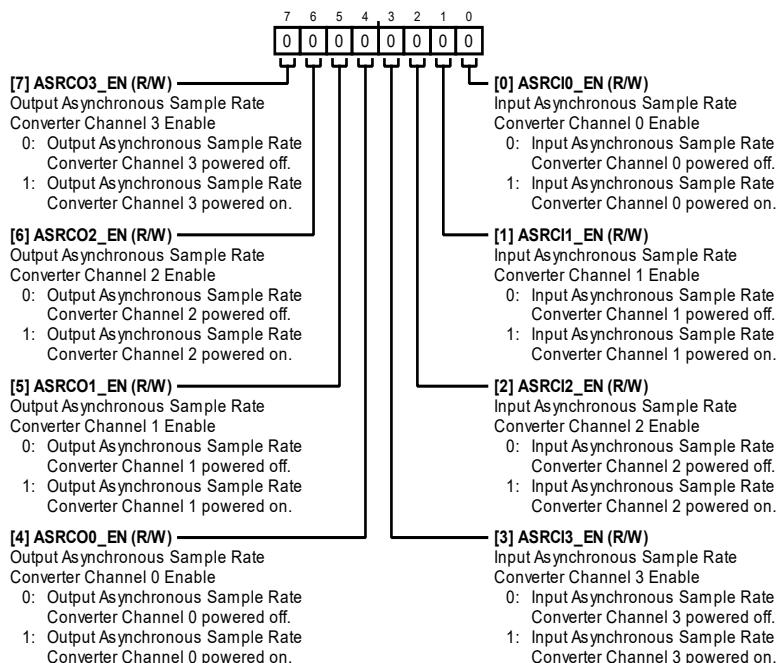

| ASRCパワー・コントロール・レジスタ                                         | 70 |

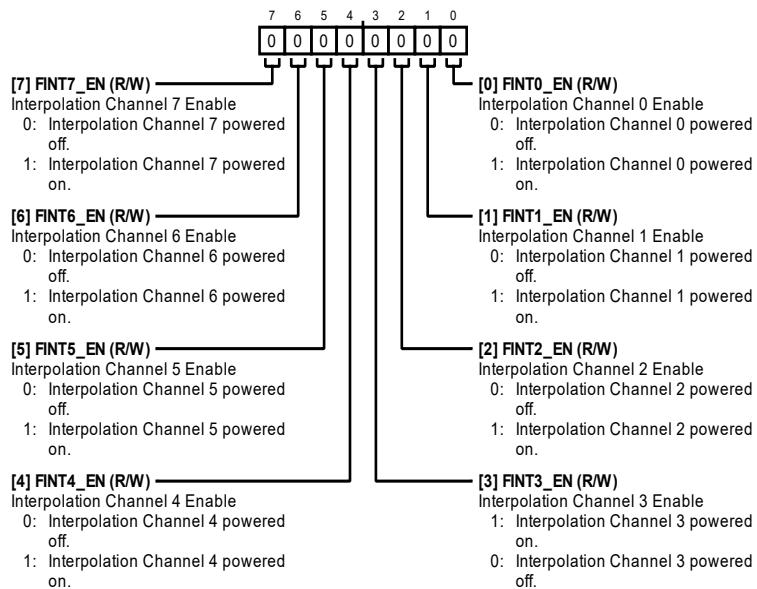

| インターポレータ・パワー・コントロール・レジスタ                                    | 72 |

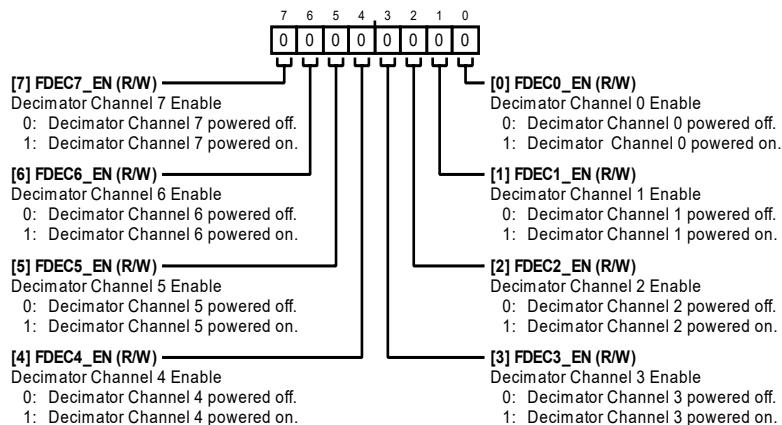

| デシメータ・パワー・コントロール・レジスタ                                       | 73 |

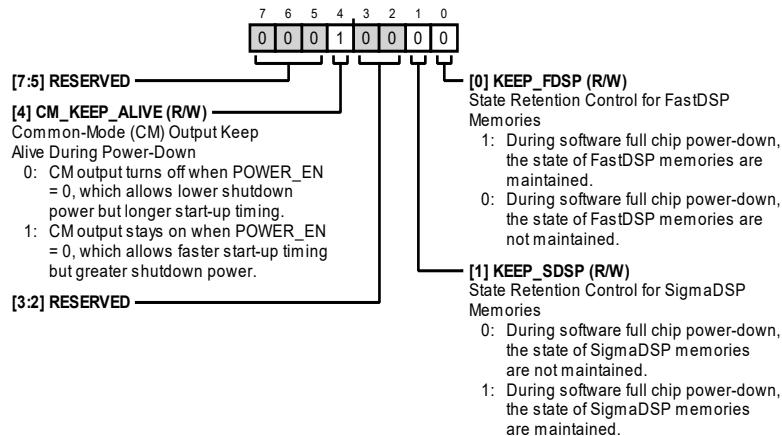

| ステート保持期間コントロール・レジスタ                                         | 74 |

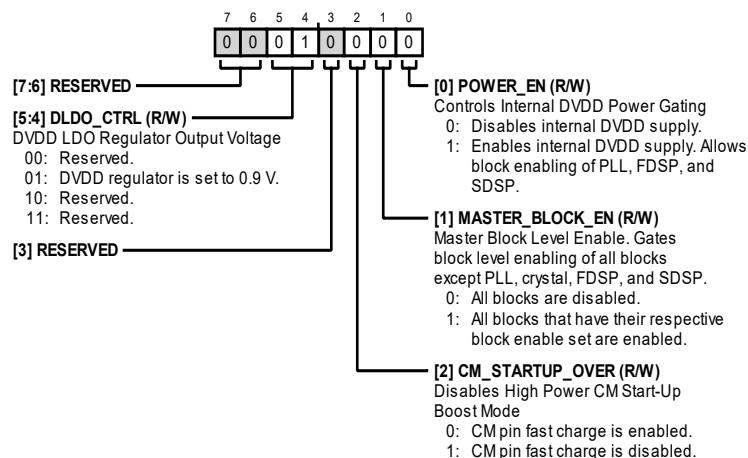

| チップ・パワー・コントロール・レジスタ                                         | 75 |

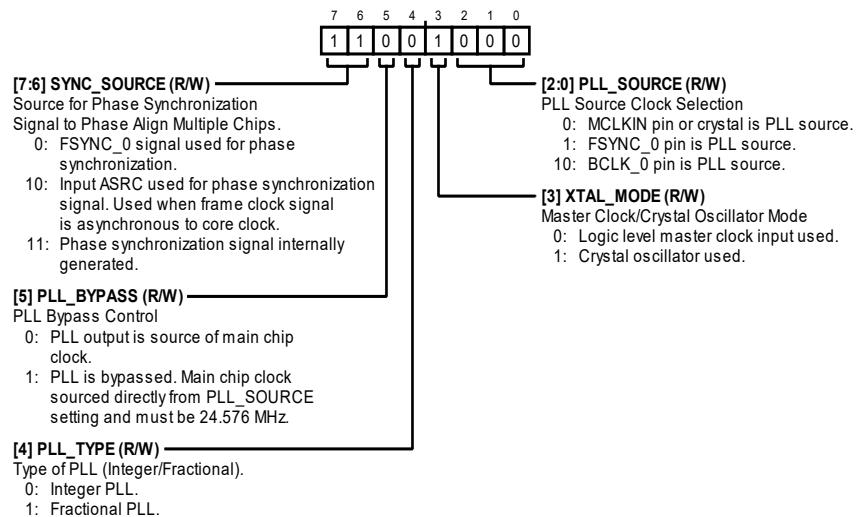

| クロック・コントロール・レジスタ                                            | 76 |

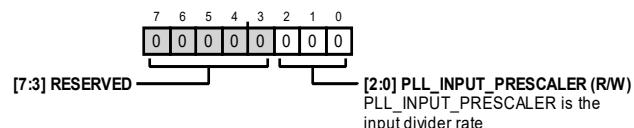

| PLL入力分周器レジスタ                                                | 76 |

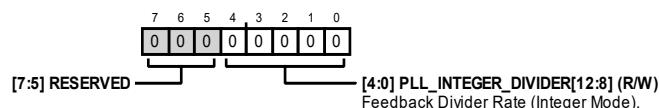

| PLL整数帰還分周器(MSB)レジスタ                                         | 77 |

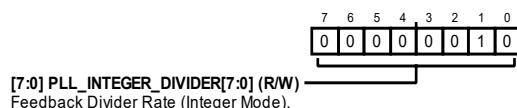

| PLL整数帰還分周器 LSB)レジスタ                                         | 77 |

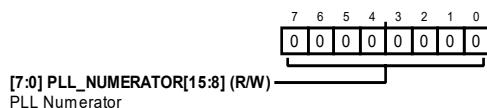

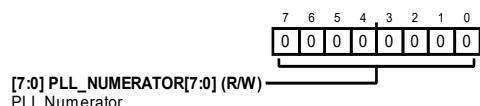

| PLL分数分子(MSB)レジスタ                                            | 77 |

| PLL分数分子 LSB)レジスタ                                            | 77 |

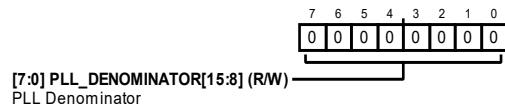

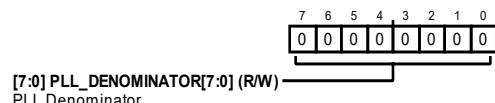

| PLL分数分母(MSB)レジスタ                                            | 78 |

| PLL分数分母 LSB)レジスタ                                            | 78 |

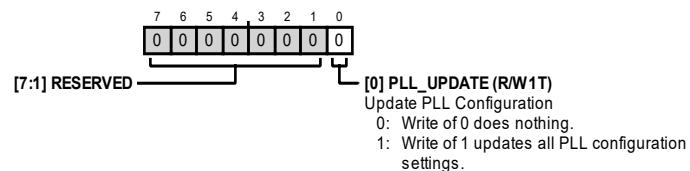

| PLL更新レジスタ                                                   | 78 |

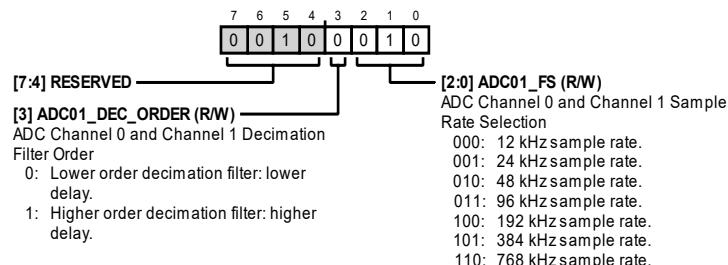

| ADCサンプル・レート・コントロール・レジスタ                                     | 79 |

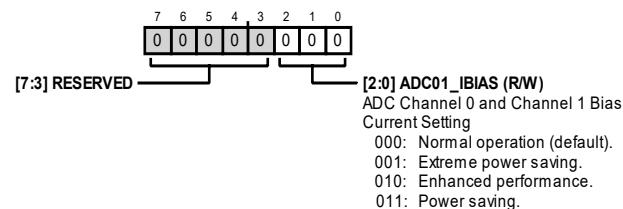

| ADC <sub>IBIAS</sub> コントロール・レジスタ                            | 79 |

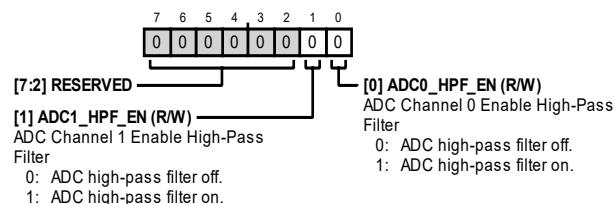

| ADCハイパス・フィルタ・コントロール・レジスタ                                    | 80 |

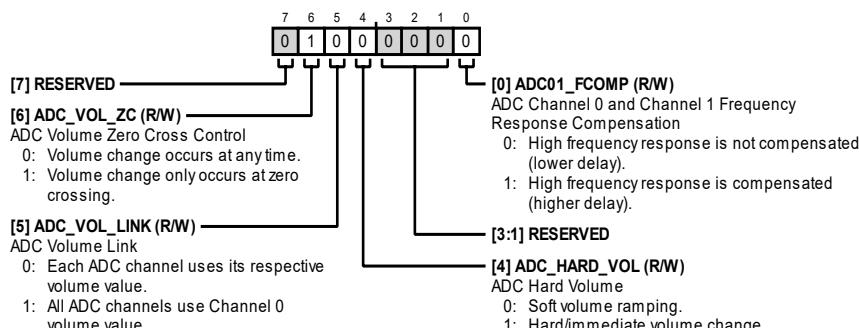

| ADCミュートおよび補償コントロール・レジスタ                                     | 80 |

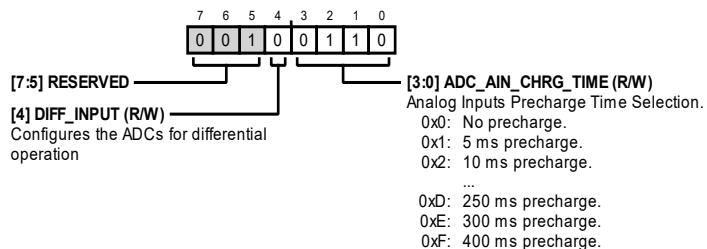

| アナログ入力プリチャージ時間レジスタ                                          | 81 |

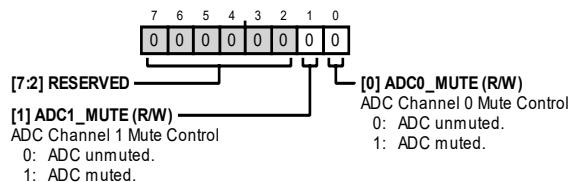

| ADCチャンネル・ミュート・レジスタ                                          | 82 |

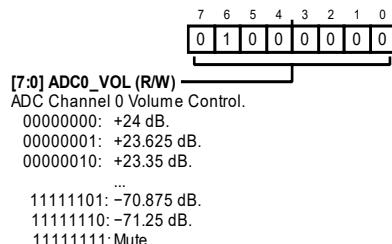

| ADCチャンネル0ボリューム制御レジスタ                                        | 82 |

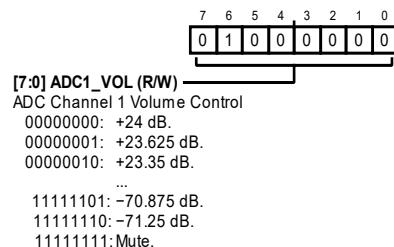

| ADCチャンネル1ボリューム制御レジスタ                                        | 83 |

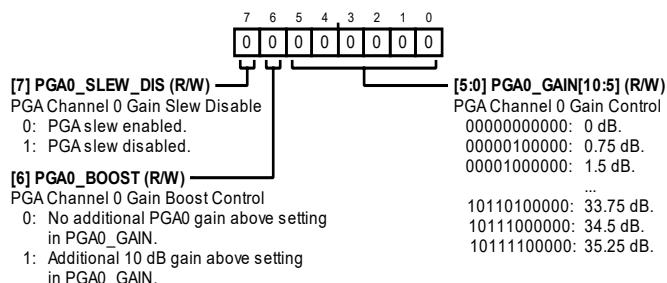

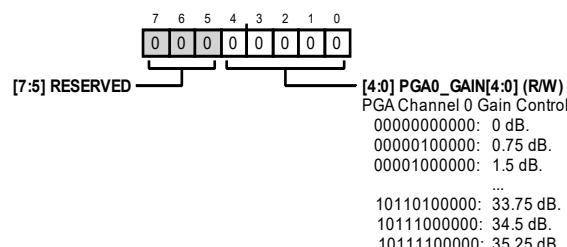

| PGAチャンネル0ゲイン・コントロールMSB、ミュート、ブースト、およびスルーレジスタ                 | 84 |

| PGAチャンネル0ゲイン・コントロール LSB)レジスタ                                | 84 |

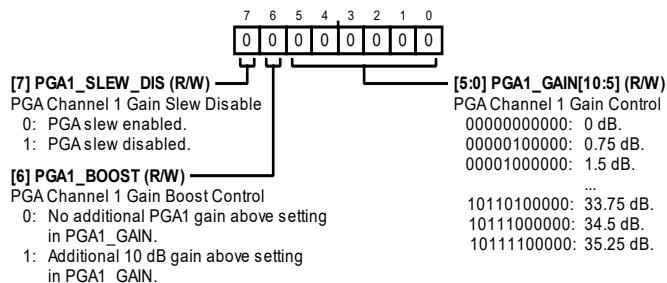

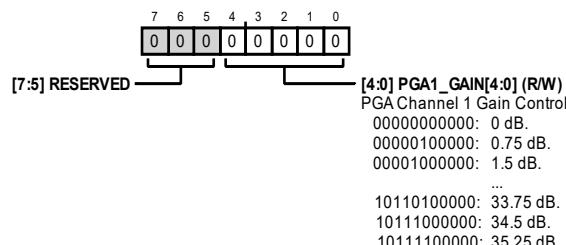

| PGAチャンネル1ゲイン・コントロールMSB、ミュート、ブースト、およびスルーレジスタ                 | 85 |

| PGAチャンネル1ゲイン・コントロール LSB)レジスタ                                | 85 |

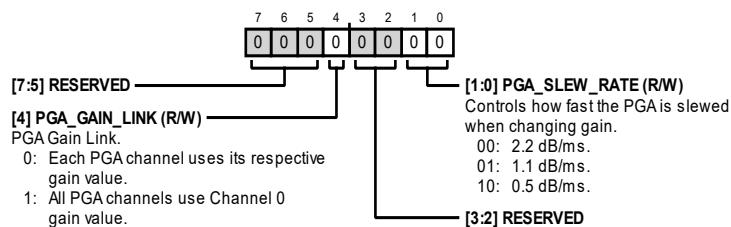

| PGAスルーレートおよびゲイン・リンク・レジスタ                                    | 86 |

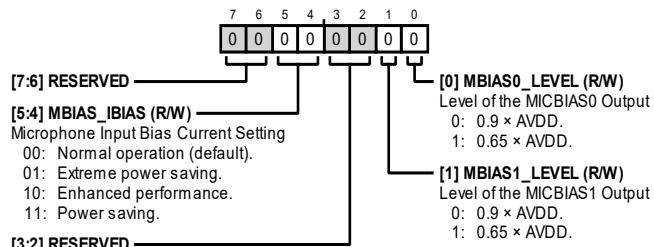

| マイクロフォン・バイアス・レベルおよび電流レジスタ                                   | 86 |

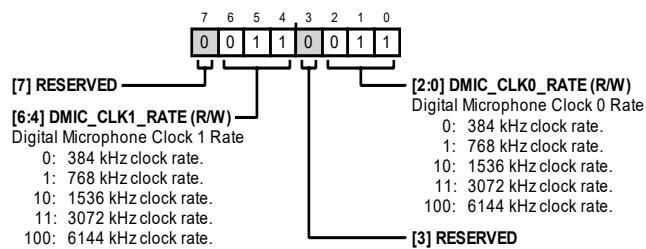

| DMICクロック・レート・コントロール・レジスタ                                    | 87 |

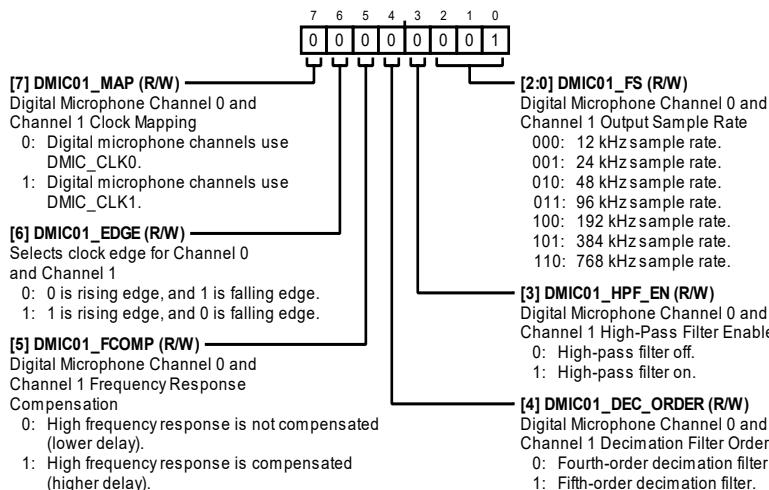

| デジタル・マイクロフォン・チャンネル0およびチャンネル1レート、次数、マッピング、およびエッジ・コントロール・レジスタ | 88 |

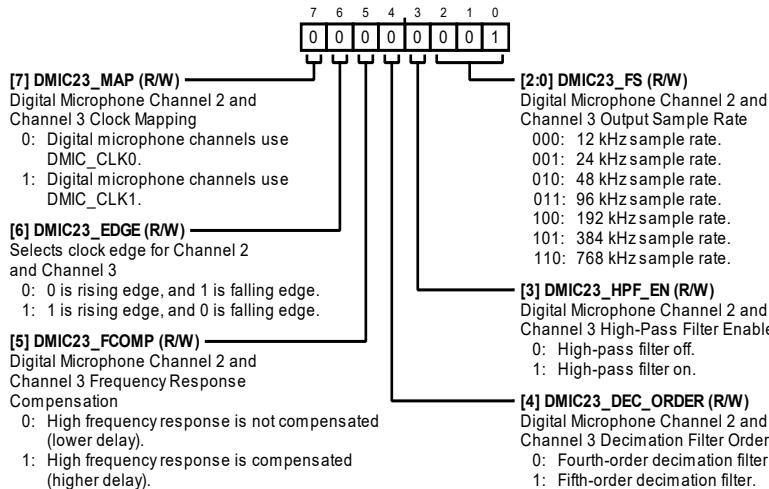

| デジタル・マイクロフォン・チャンネル2およびチャンネル3レート、次数、マッピング、およびエッジ・コントロール・レジスタ | 89 |

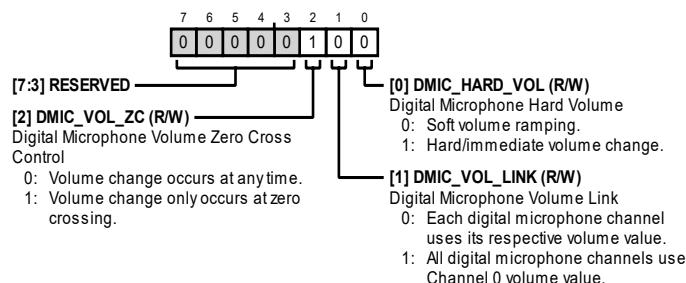

| DMICボリューム・オプション・レジスタ                                        | 90 |

|                                             |     |

|---------------------------------------------|-----|

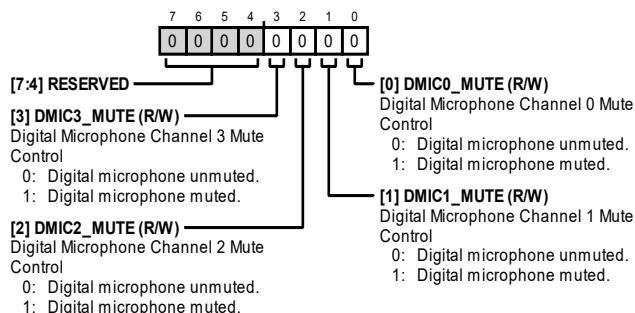

| デジタル・マイクロフォン・チャンネル・ミュート・コントロール・レジスタ         | 90  |

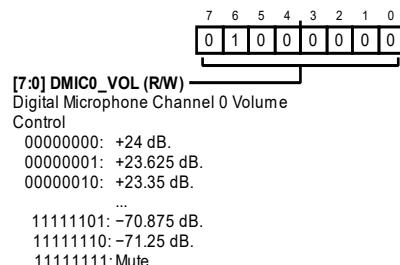

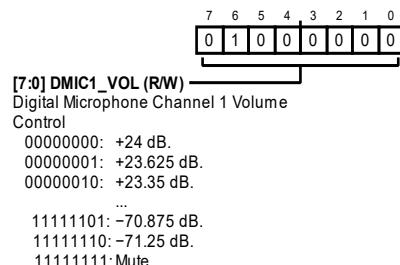

| デジタル・マイクロフォン・チャンネル0ボリューム制御レジスタ              | 91  |

| デジタル・マイクロフォン・チャンネル1ボリューム制御レジスタ              | 92  |

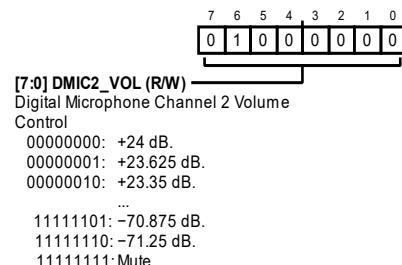

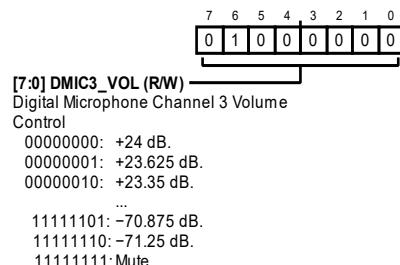

| デジタル・マイクロフォン・チャンネル2ボリューム制御レジスタ              | 93  |

| デジタル・マイクロフォン・チャンネル3ボリューム制御レジスタ              | 94  |

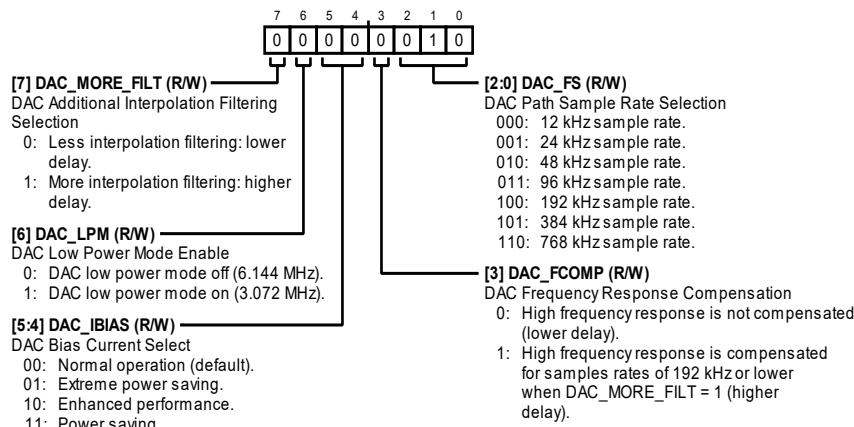

| DACサンプル・レート、フィルタリング、およびパワー・コントロール・レジスタ      | 95  |

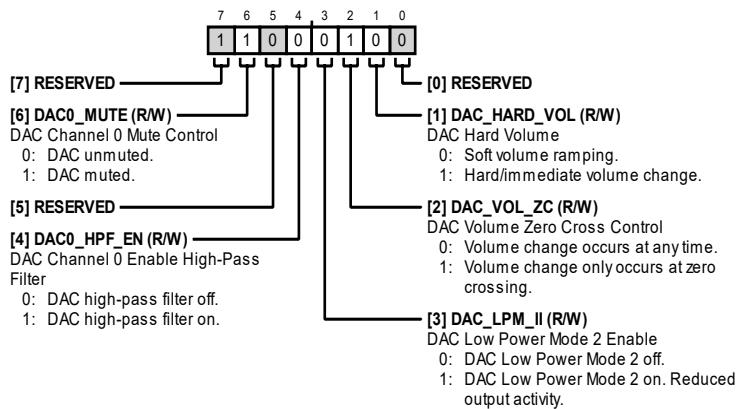

| DACボリューム・リンク、ハイパス・フィルタ、およびミュート・コントロール・レジスタ  | 96  |

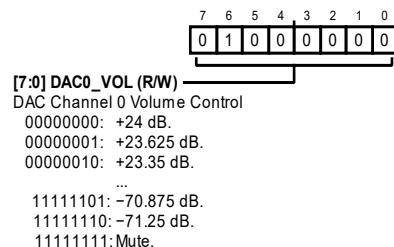

| DACチャンネル0ボリューム・レジスタ                         | 97  |

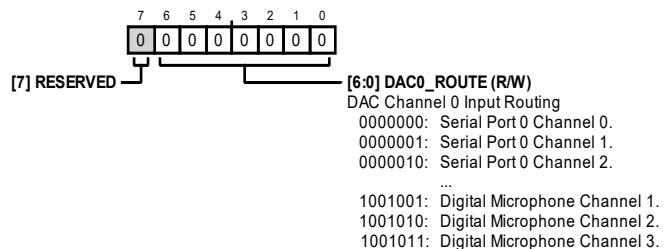

| DACチャンネル0ルーティング・レジスタ                        | 98  |

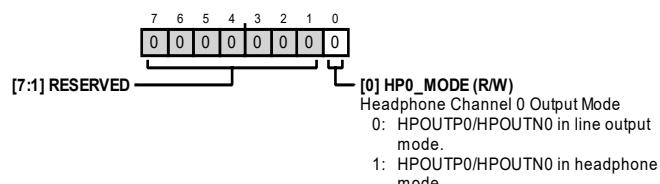

| ヘッドフォン・コントロール・レジスタ                          | 99  |

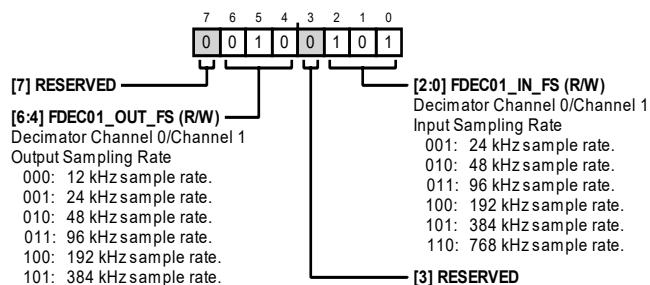

| 高速から低速へのデシメータ・サンプル・レート・チャンネル0およびチャンネル1レジスタ  | 100 |

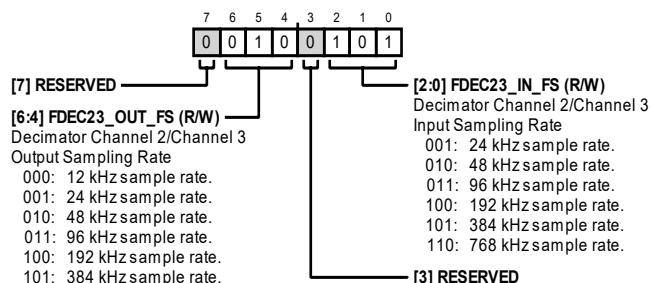

| 高速から低速へのデシメータ・サンプル・レート・チャンネル2およびチャンネル3レジスタ  | 101 |

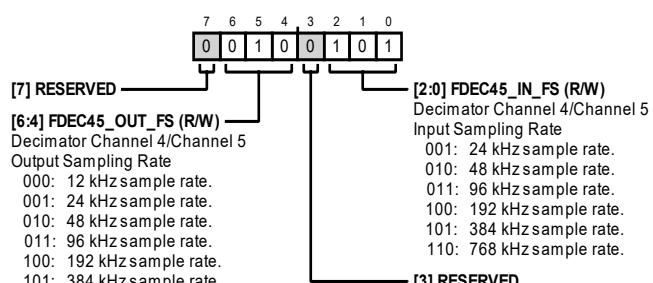

| 高速から低速へのデシメータ・サンプル・レート・チャンネル4およびチャンネル5レジスタ  | 101 |

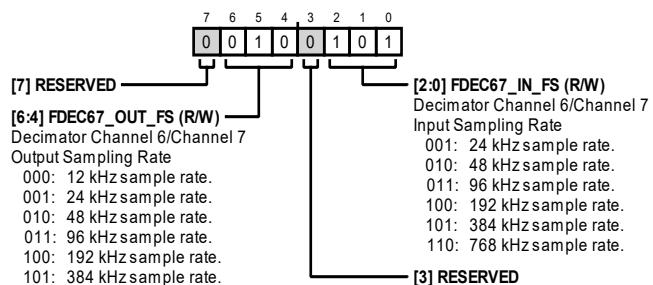

| 高速から低速へのデシメータ・サンプル・レート・チャンネル6およびチャンネル7レジスタ  | 102 |

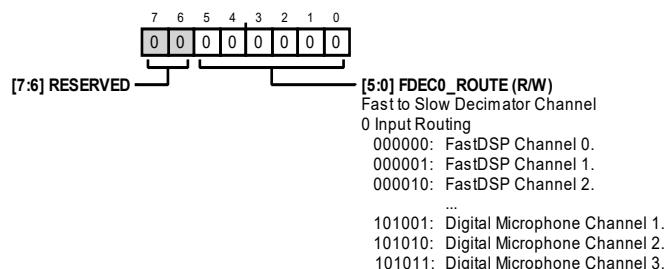

| 高速から低速へのデシメータ・チャンネル0入力ルーティング・レジスタ           | 103 |

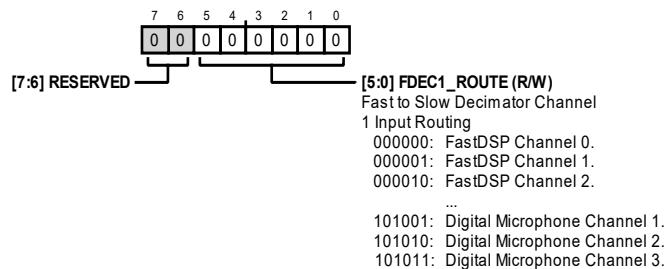

| 高速から低速へのデシメータ・チャンネル1入力ルーティング・レジスタ           | 104 |

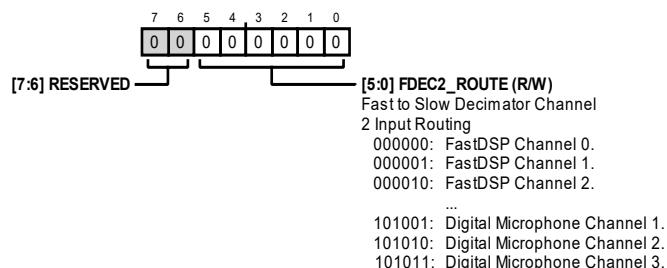

| 高速から低速へのデシメータ・チャンネル2入力ルーティング・レジスタ           | 105 |

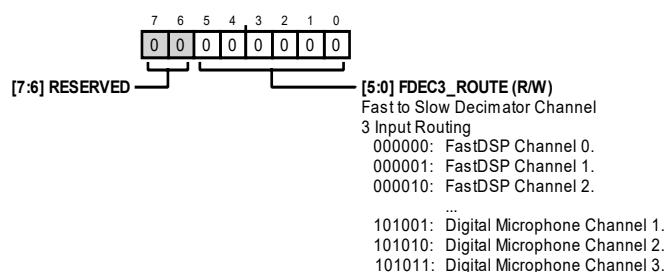

| 高速から低速へのデシメータ・チャンネル3入力ルーティング・レジスタ           | 106 |

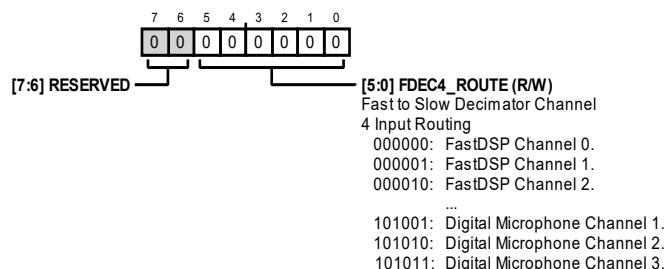

| 高速から低速へのデシメータ・チャンネル4入力ルーティング・レジスタ           | 108 |

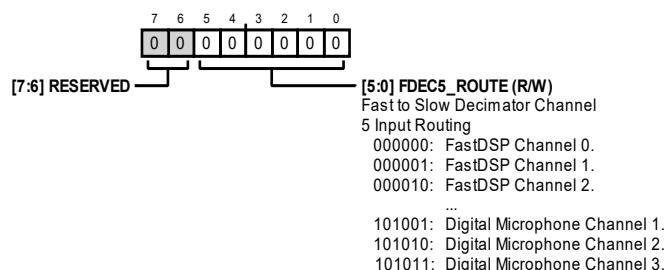

| 高速から低速へのデシメータ・チャンネル5入力ルーティング・レジスタ           | 109 |

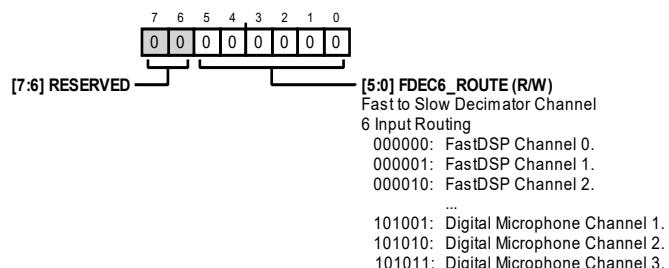

| 高速から低速へのデシメータ・チャンネル6入力ルーティング・レジスタ           | 110 |

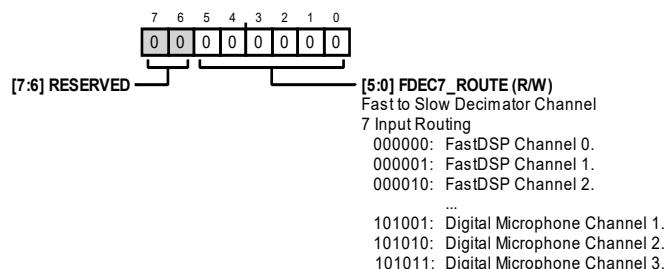

| 高速から低速へのデシメータ・チャンネル7入力ルーティング・レジスタ           | 112 |

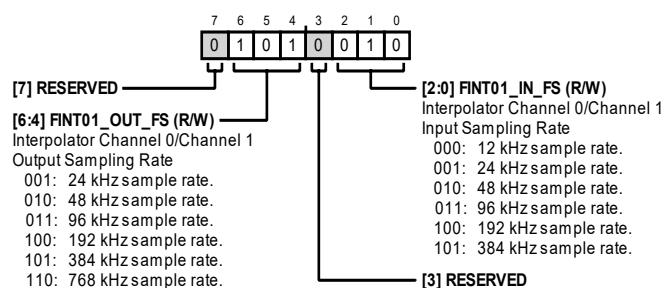

| 低速から高速へのインターポレータ・サンプル・レート・チャンネル0/チャンネル1レジスタ | 113 |

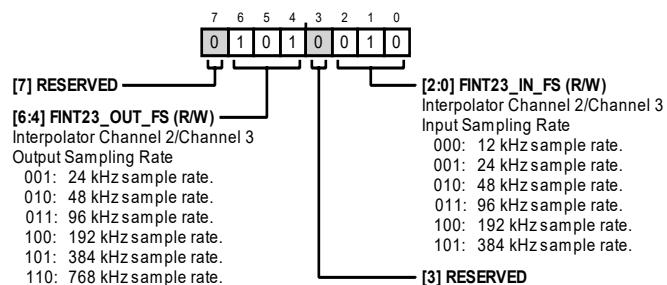

| 低速から高速へのインターポレータ・サンプル・レート・チャンネル2/チャンネル3レジスタ | 114 |

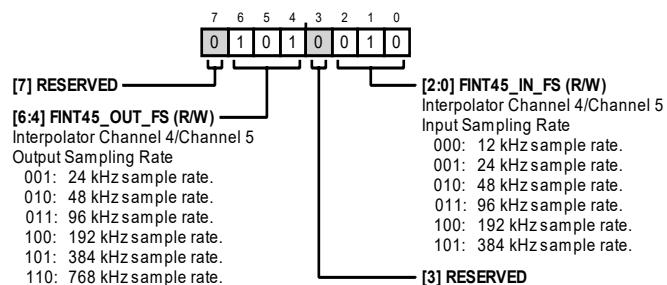

| 低速から高速へのインターポレータ・サンプル・レート・チャンネル4/チャンネル5レジスタ | 115 |

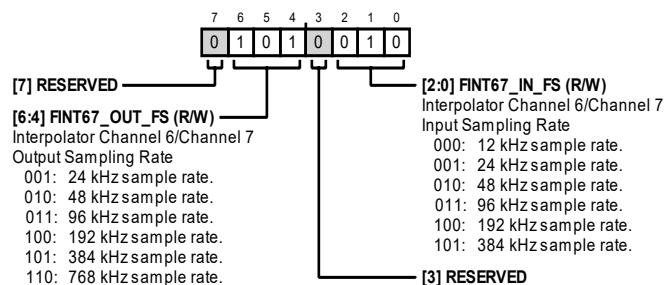

| 低速から高速へのインターポレータ・サンプル・レート・チャンネル6/チャンネル7レジスタ | 116 |

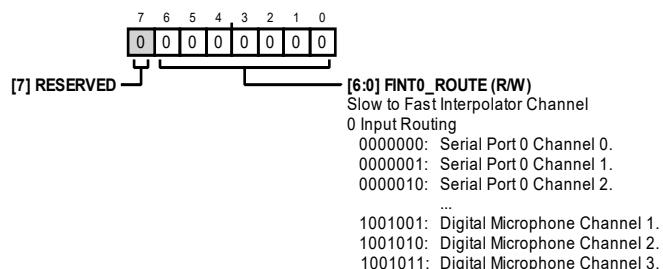

| 低速から高速へのインターポレータ・チャンネル0入力ルーティング・レジスタ        | 117 |

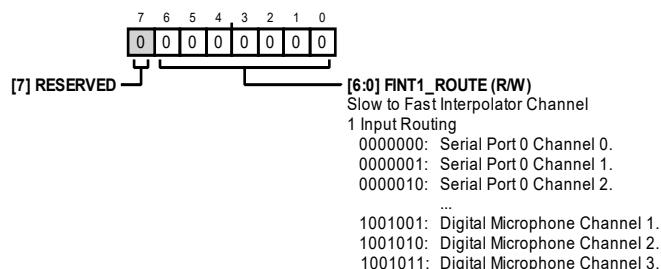

| 低速から高速へのインターポレータ・チャンネル1入                    |     |

|                                       |     |

|---------------------------------------|-----|

| カルーティング・レジスタ                          | 119 |

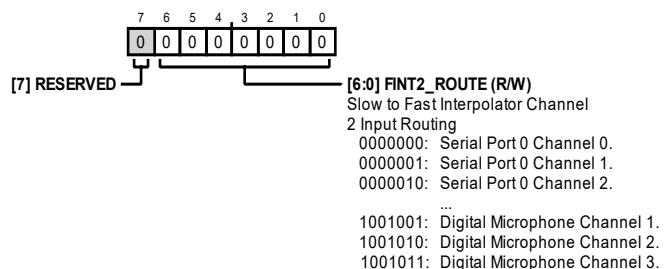

| 低速から高速へのインターポレータ・チャンネル2入力             |     |

| カルーティング・レジスタ                          | 120 |

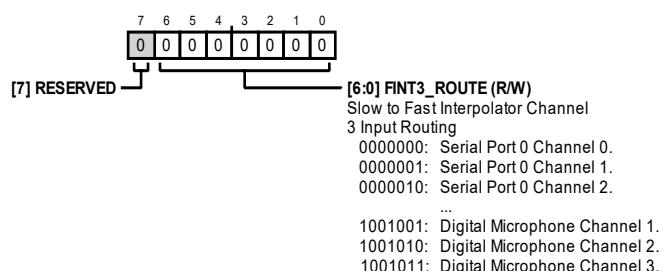

| 低速から高速へのインターポレータ・チャンネル3入力             |     |

| カルーティング・レジスタ                          | 122 |

| 低速から高速へのインターポレータ・チャンネル4入力             |     |

| カルーティング・レジスタ                          | 124 |

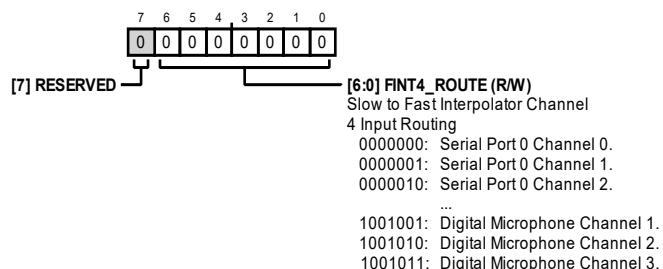

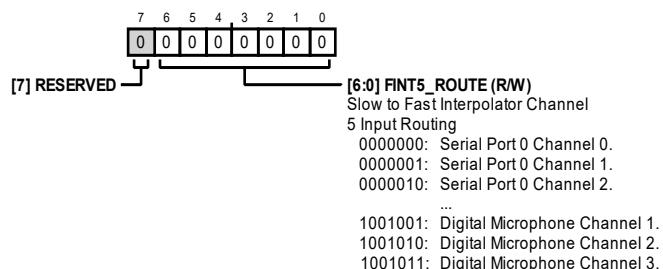

| 低速から高速へのインターポレータ・チャンネル5入力             |     |

| カルーティング・レジスタ                          | 126 |

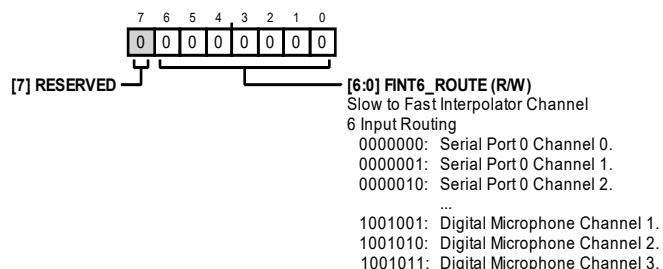

| 低速から高速へのインターポレータ・チャンネル6入力             |     |

| カルーティング・レジスタ                          | 128 |

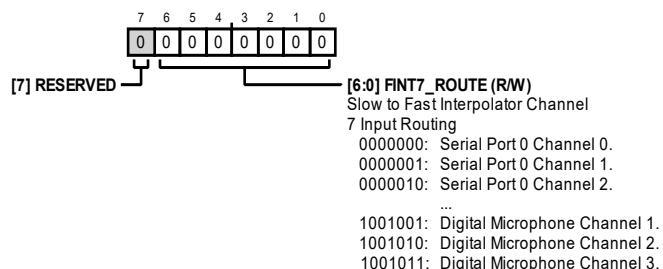

| 低速から高速へのインターポレータ・チャンネル7入力             |     |

| カルーティング・レジスタ                          | 130 |

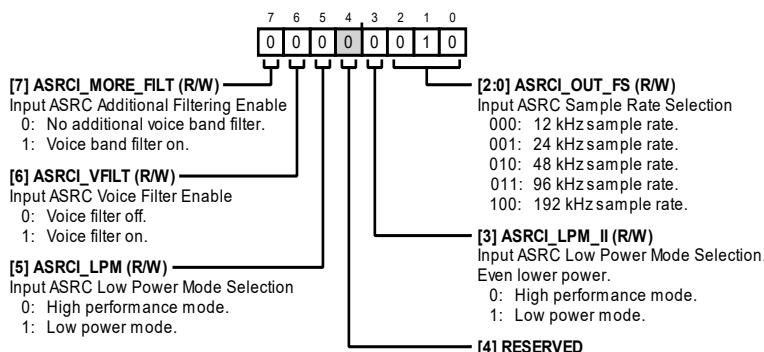

| 入力 ASRC コントロール、ソース、およびレート選択レジスタ       | 132 |

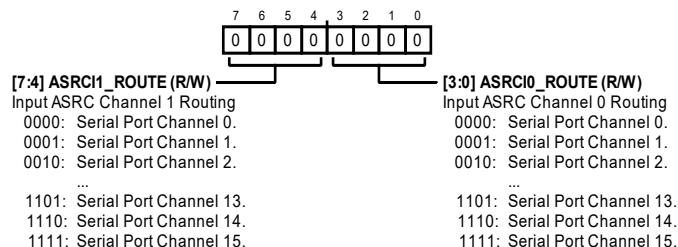

| 入力 ASRC チャンネル0およびチャンネル1入力カルーティング・レジスタ | 133 |

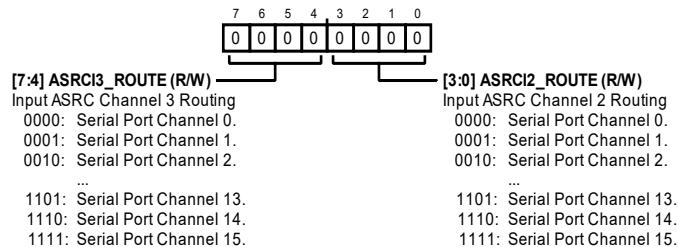

| 入力 ASRC チャンネル2およびチャンネル3入力カルーティング・レジスタ | 134 |

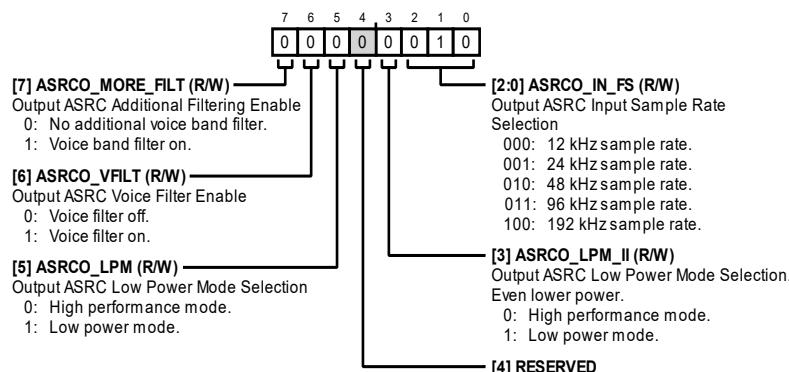

| 出力 ASRC コントロール・レジスタ                   | 135 |

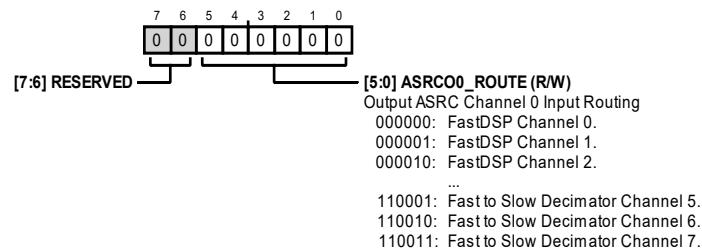

| 出力 ASRC チャンネル0入力カルーティング・レジスタ          | 136 |

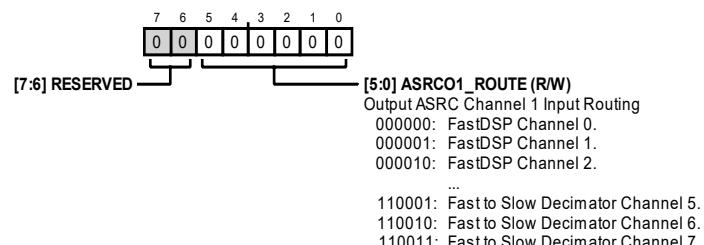

| 出力 ASRC チャンネル1入力カルーティング・レジスタ          | 137 |

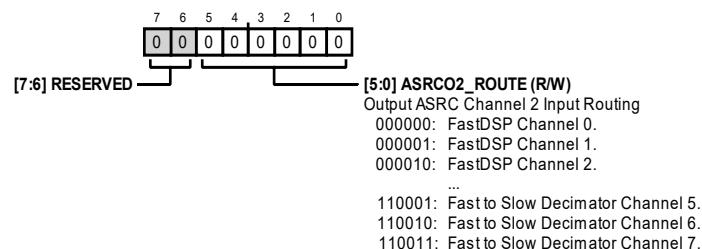

| 出力 ASRC チャンネル2入力カルーティング・レジスタ          | 139 |

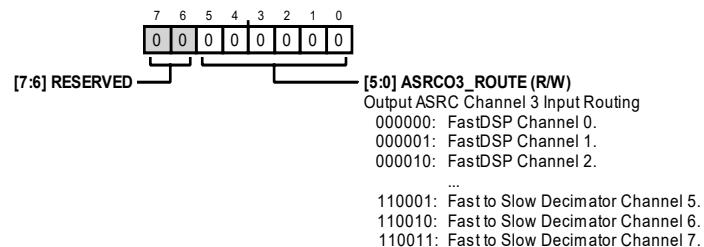

| 出力 ASRC チャンネル3入力カルーティング・レジスタ          | 140 |

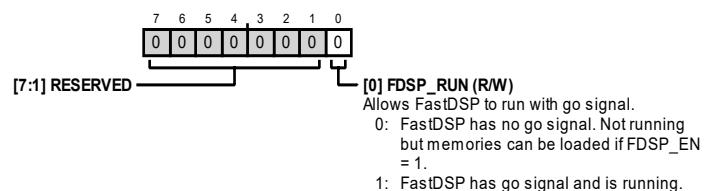

| FastDSP 実行レジスタ                        | 141 |

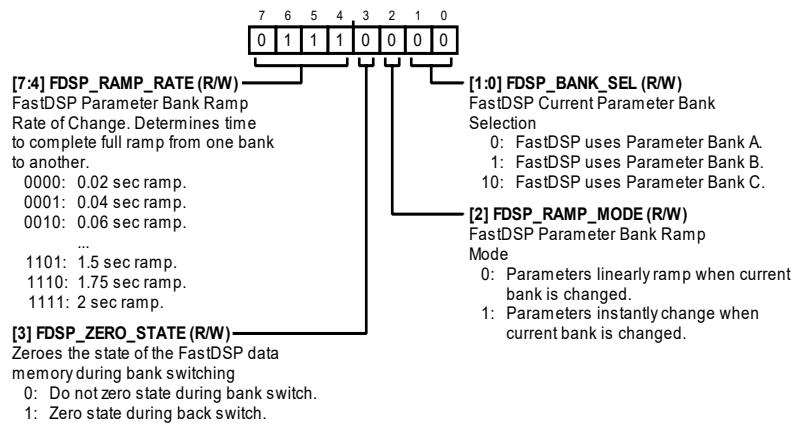

| FastDSP 電流バンクおよびバンク・ランピング・コントロール・レジスタ | 142 |

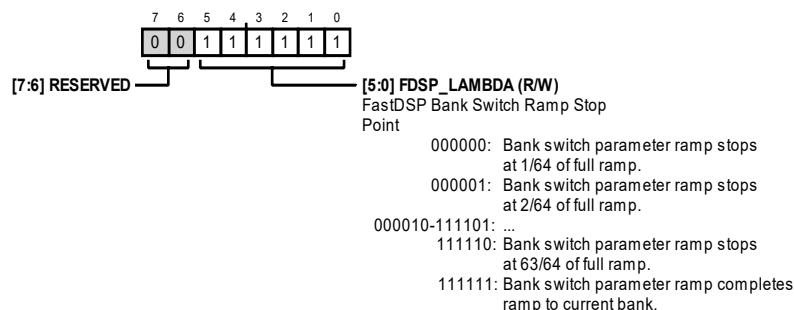

| FastDSP バンク・ランプ停止ポイント・レジスタ            | 143 |

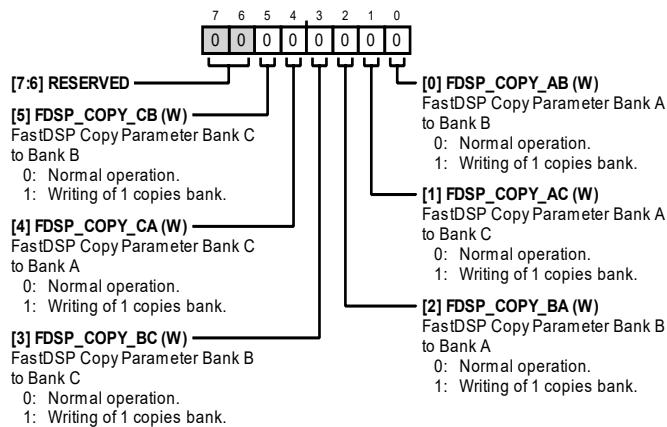

| FastDSP バンク・コピー・レジスタ                  | 144 |

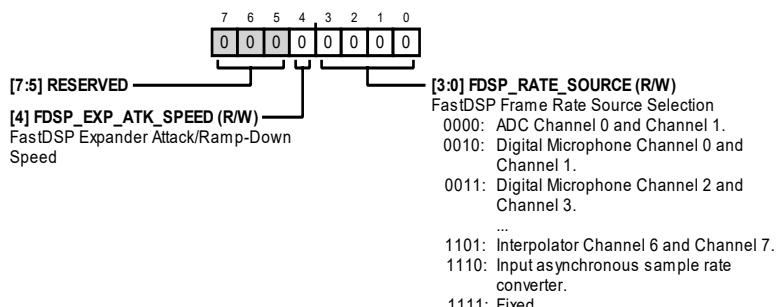

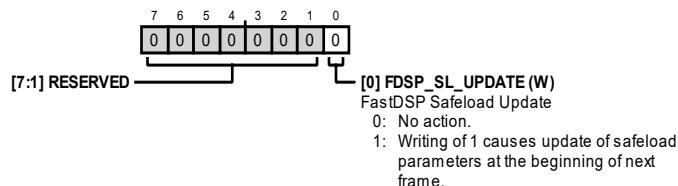

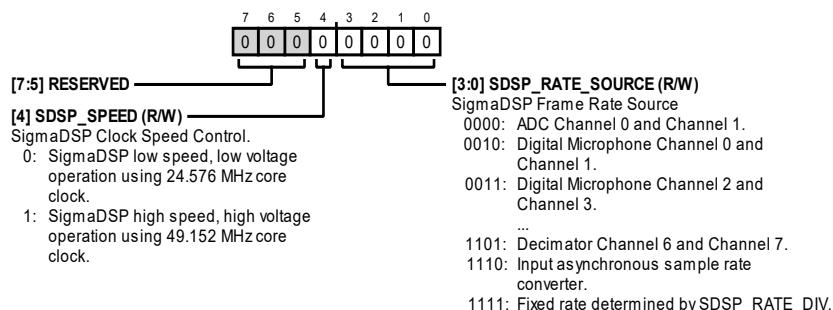

| FastDSP フレーム・レート・ソース・レジスタ             | 145 |

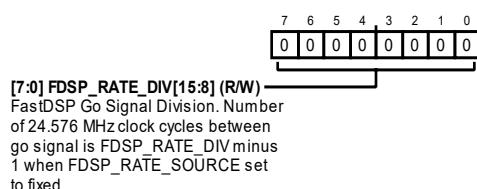

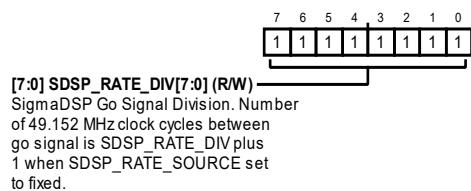

| FastDSP 固定レート分周 MSB レジスタ              | 145 |

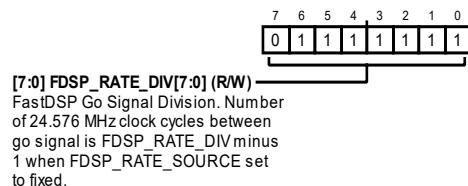

| FastDSP 固定レート分周 LSB レジスタ              | 146 |

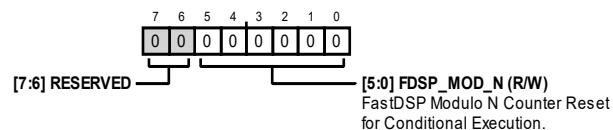

| FastDSP 低レート条件付き実行用モジュロNカウタ・レジスタ      | 146 |

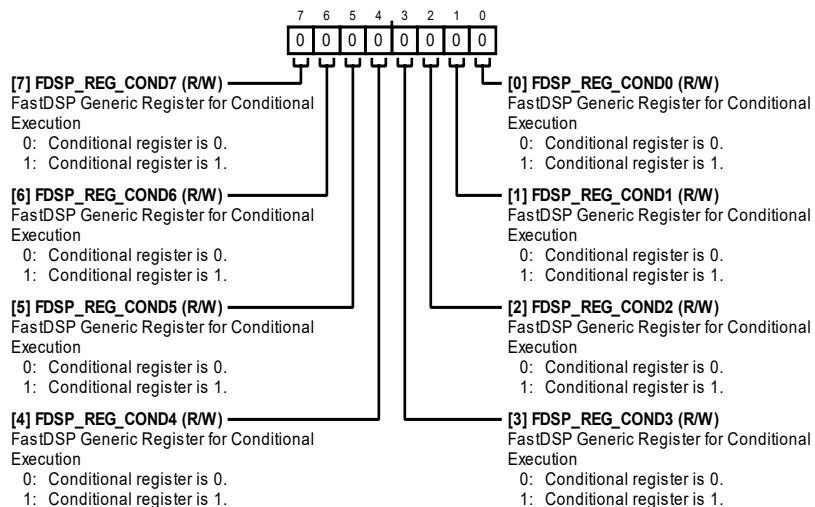

| FastDSP 汎用条件付き実行レジスタ                  | 147 |

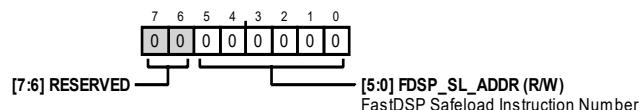

| FastDSP セーフロード・アドレス・レジスタ              | 148 |

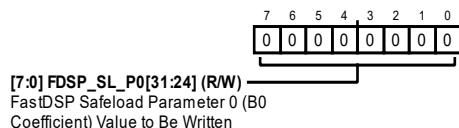

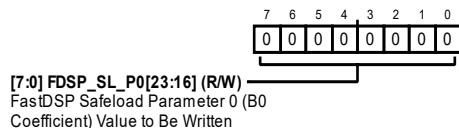

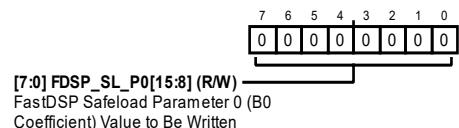

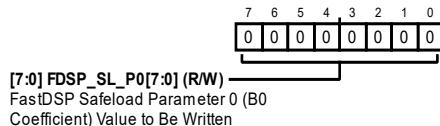

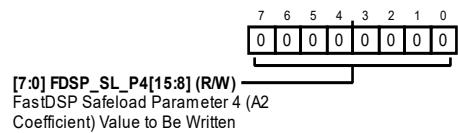

| FastDSP セーフロード・パラメータ0値レジスタ            | 148 |

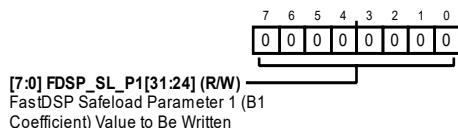

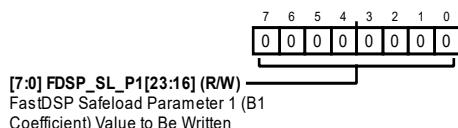

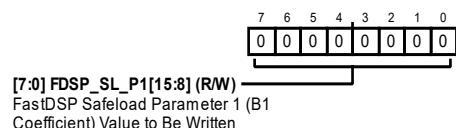

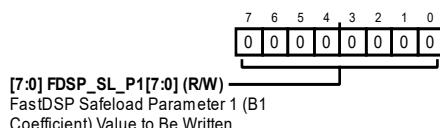

| FastDSP セーフロード・パラメータ1値レジスタ            | 149 |

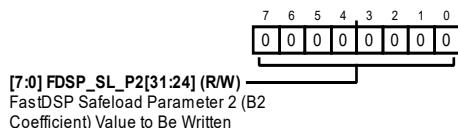

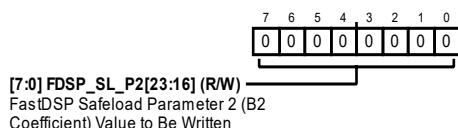

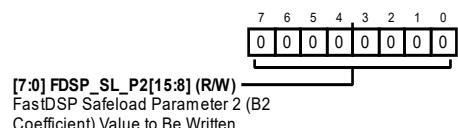

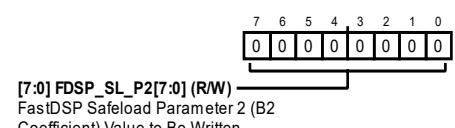

| FastDSP セーフロード・パラメータ2値レジスタ            | 150 |

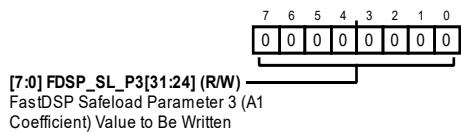

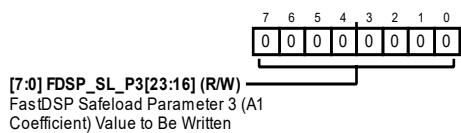

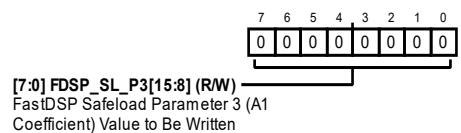

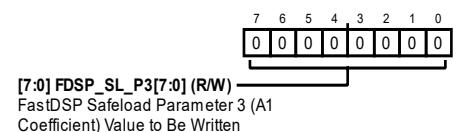

| FastDSP セーフロード・パラメータ3値レジスタ            | 151 |

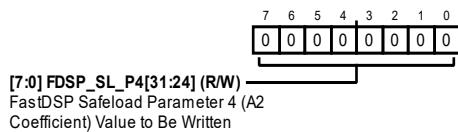

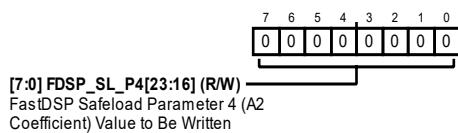

| FastDSP セーフロード・パラメータ4値レジスタ            | 152 |

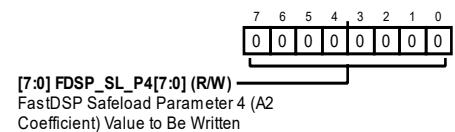

| FastDSP セーフロード更新レジスタ                  | 153 |

| SigmaDSP フレーム・レート・ソース選択レジスタ           | 153 |

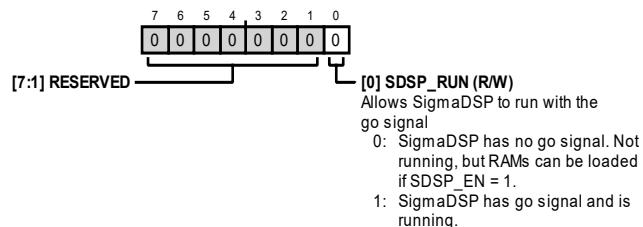

| SigmaDSP 実行レジスタ                       | 154 |

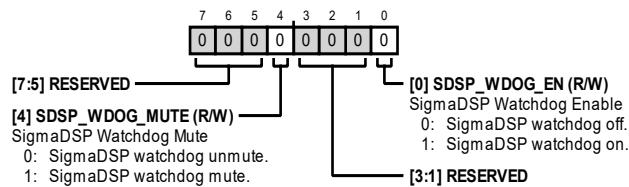

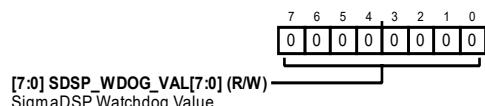

| SigmaDSP ウオッチドッグ・コントロール・レジスタ          | 154 |

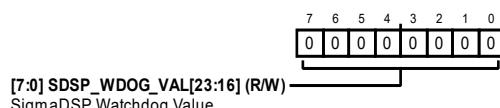

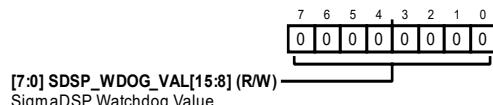

| SigmaDSP ウオッチドッグ値レジスタ                 | 154 |

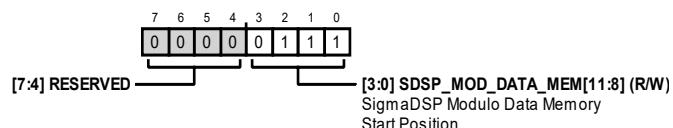

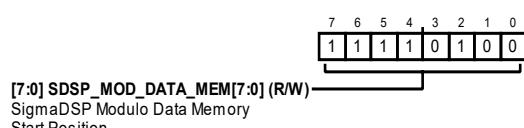

| SigmaDSP モジュロ・データ・メモリ開始位置レジスタ         | 155 |

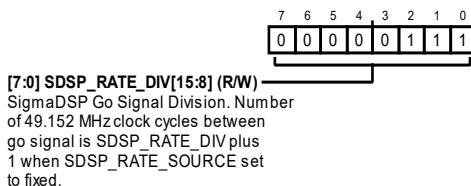

| SigmaDSP 固定フレーム・レート分周レジスタ             | 156 |

|                                    |     |

|------------------------------------|-----|

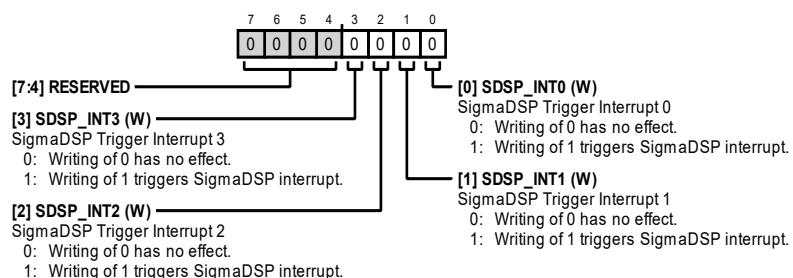

| SigmaDSP 割り込み設定レジスタ                | 156 |

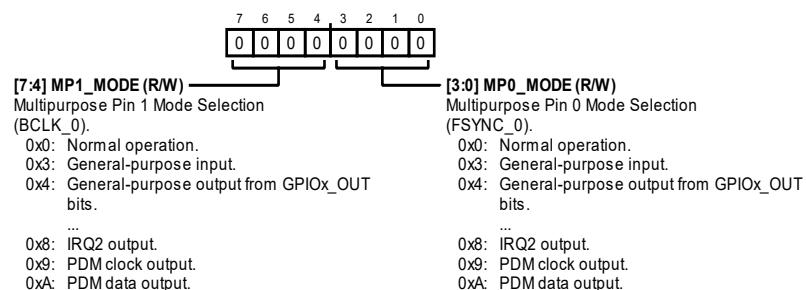

| 多目的ピン0/ピン1モード選択レジスタ                | 157 |

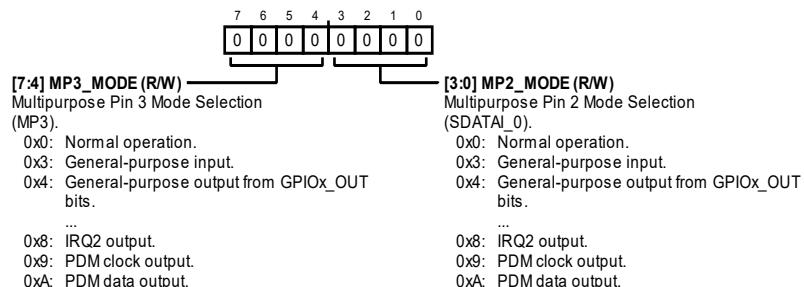

| 多目的ピン2/ピン3モード選択レジスタ                | 158 |

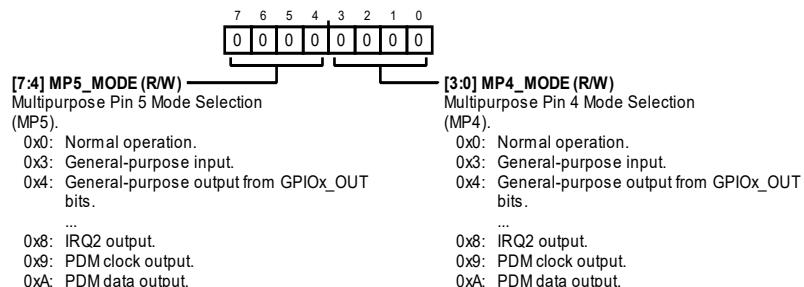

| 多目的ピン4/ピン5モード選択レジスタ                | 159 |

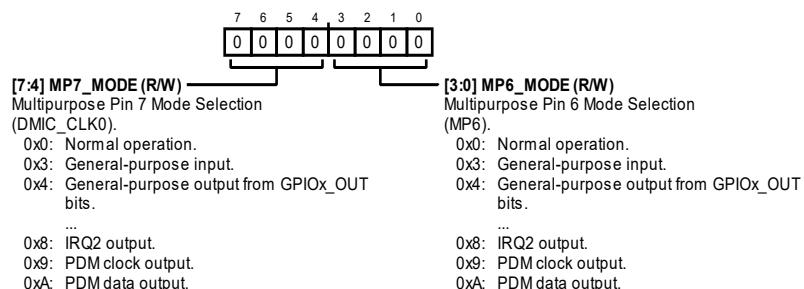

| 多目的ピン6/ピン7モード選択レジスタ                | 160 |

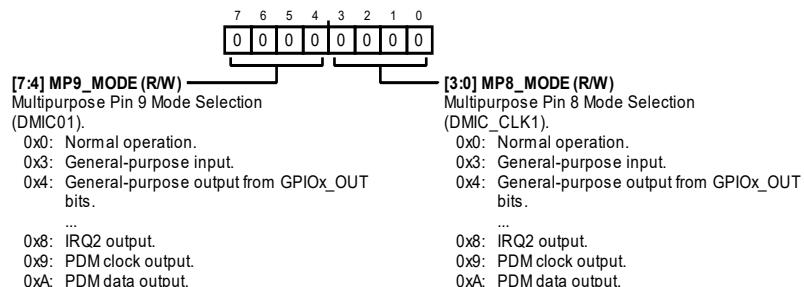

| 多目的ピン8/ピン9モード選択レジスタ                | 161 |

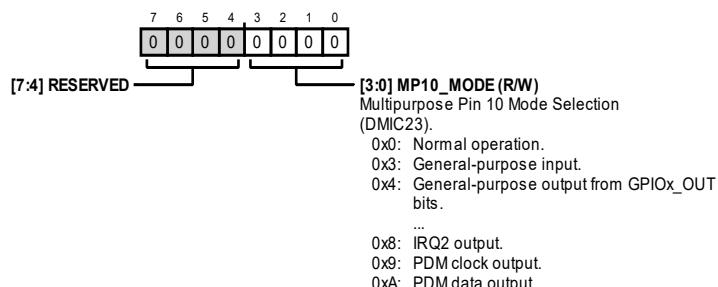

| 多目的ピン10モード選択レジスタ                   | 162 |

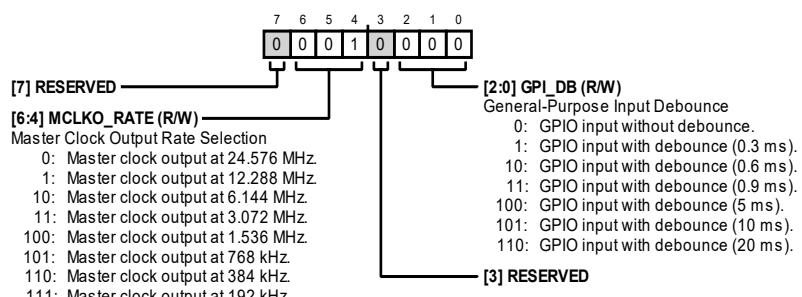

| 汎用入力バウンス防止制御およびマスタ・クロック出力レート選択レジスタ | 162 |

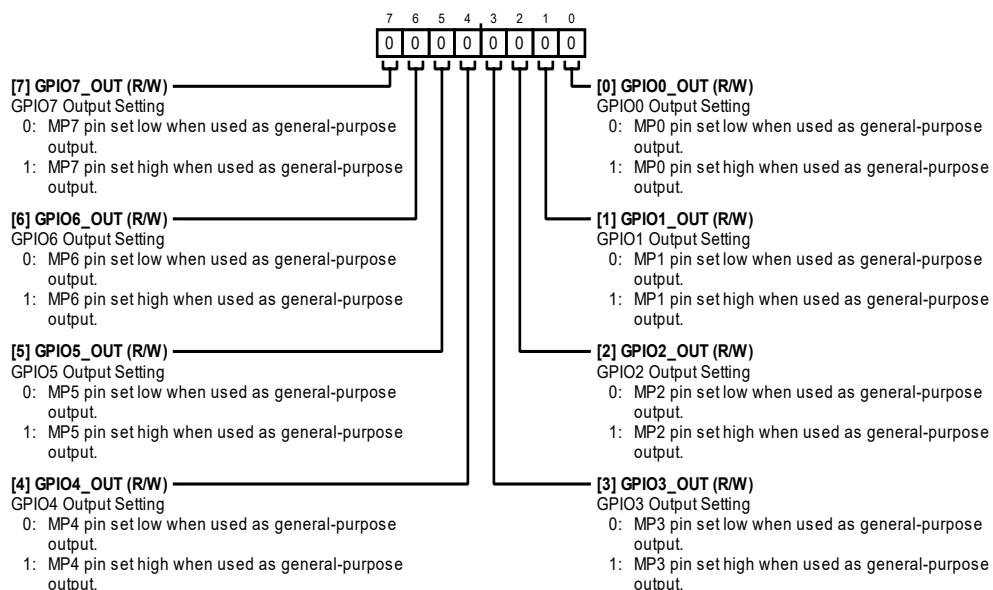

| 汎用出力ピン0～ピン7コントロール・レジスタ             | 163 |

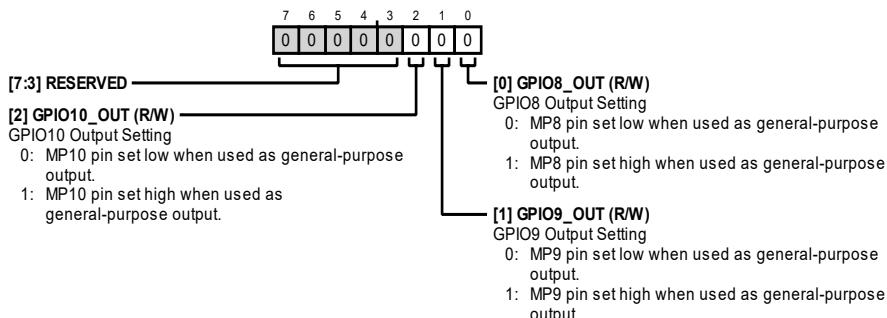

| 汎用出力ピン8～ピン10コントロール・レジスタ            | 164 |

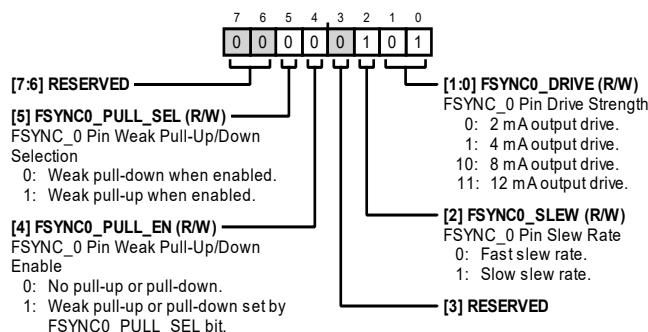

| FSYNC_0ピン・コントロール・レジスタ              | 165 |

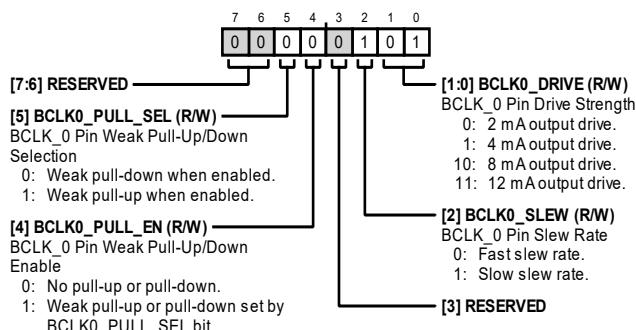

| BCLK_0ピン・コントロール・レジスタ               | 166 |

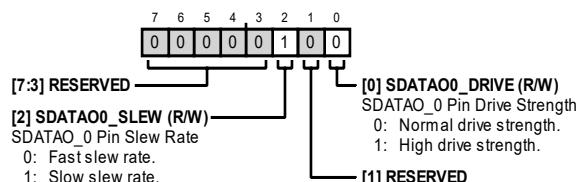

| SDATAO_0ピン・コントロール・レジスタ             | 166 |

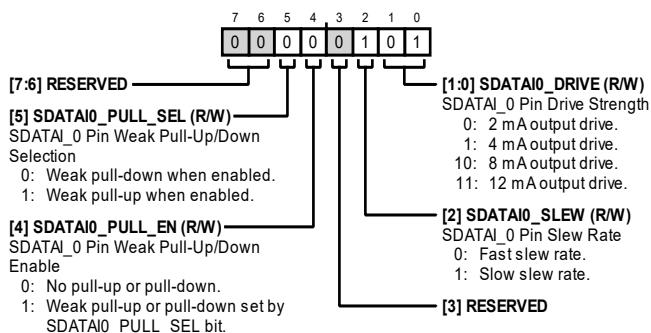

| SDATAI_0ピン・コントロール・レジスタ             | 167 |

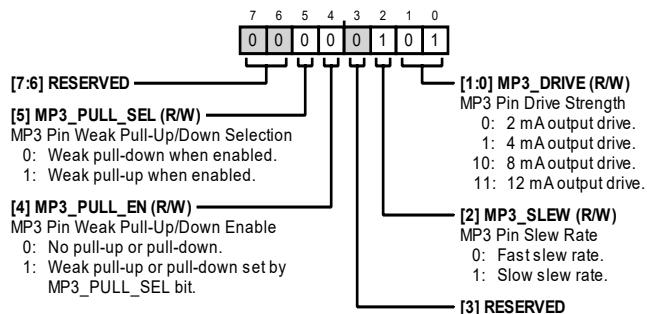

| MP3ピン・コントロール・レジスタ                  | 168 |

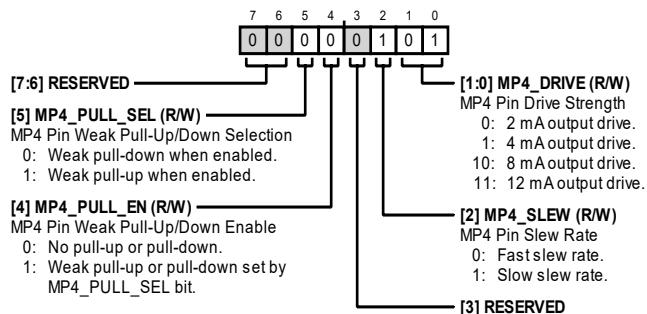

| MP4ピン・コントロール・レジスタ                  | 169 |

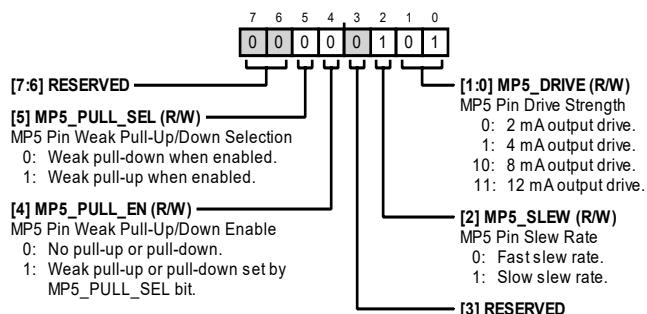

| MP5ピン・コントロール・レジスタ                  | 170 |

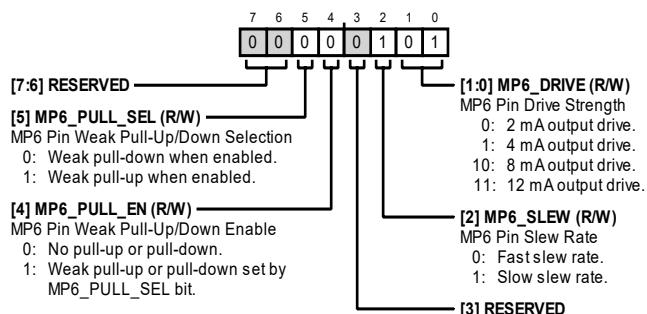

| MP6ピン・コントロール・レジスタ                  | 171 |

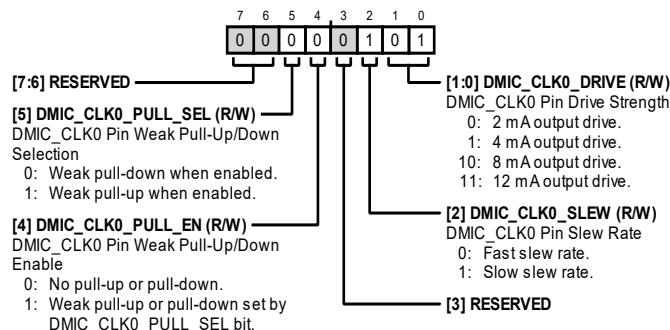

| DMIC_CLK0ピン・コントロール・レジスタ            | 172 |

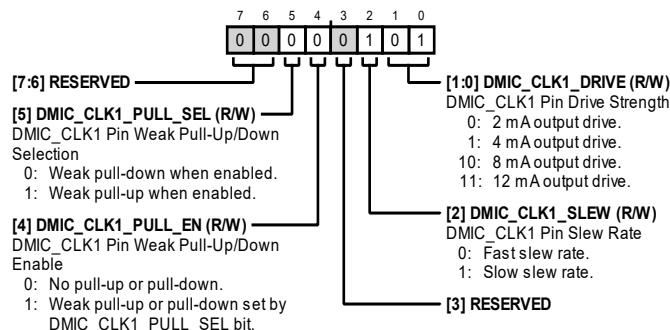

| DMIC_CLK1ピン・コントロール・レジスタ            | 173 |

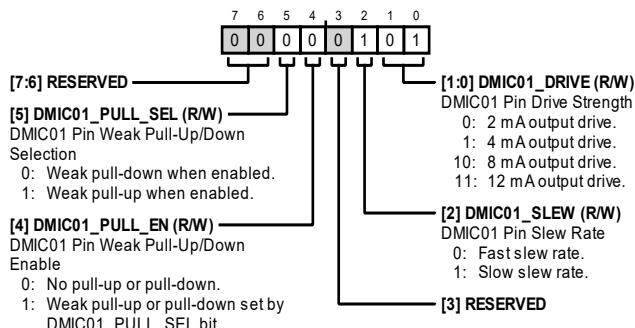

| DMIC01ピン・コントロール・レジスタ               | 174 |

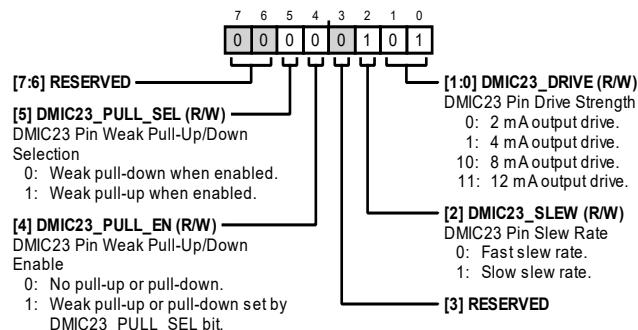

| DMIC23ピン・コントロール・レジスタ               | 175 |

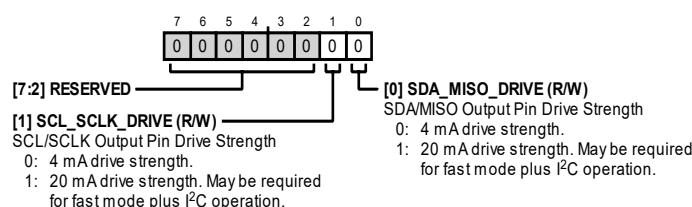

| SDA/MISOピン・コントロール・レジスタ             | 175 |

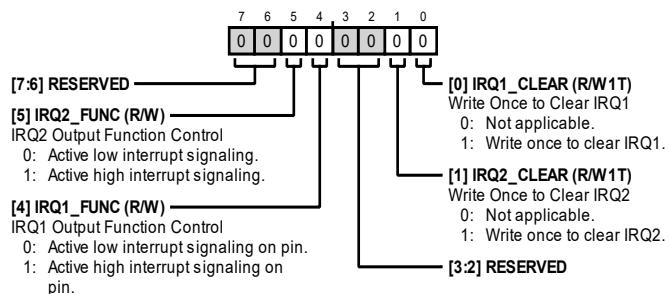

| IRQシグナルおよびクリア・レジスタ                 | 176 |

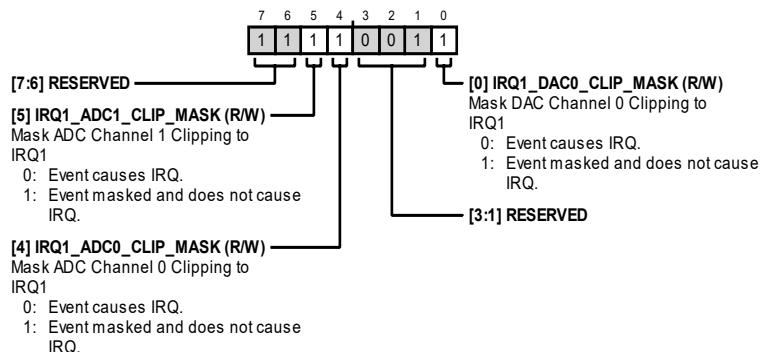

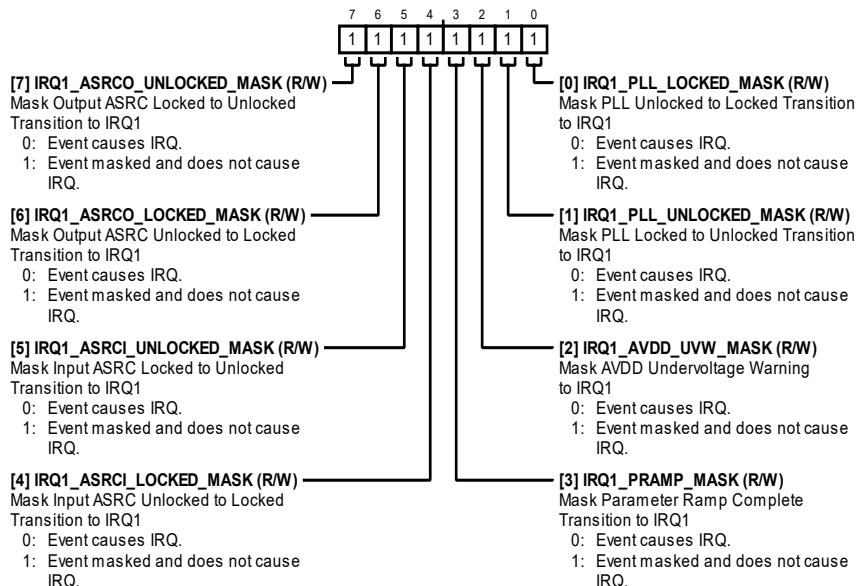

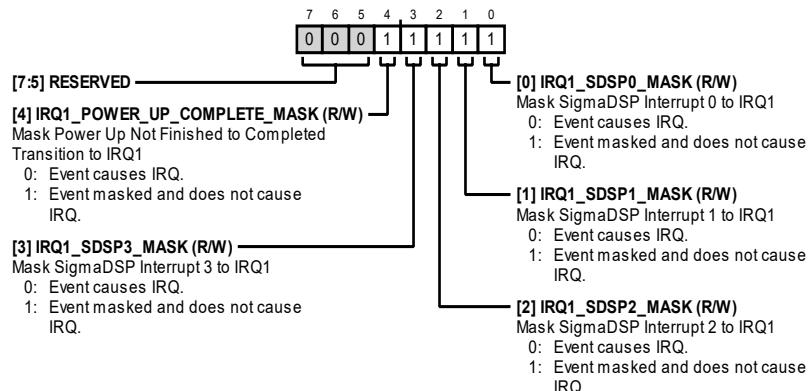

| IRQ1マスク・レジスタ                       | 177 |

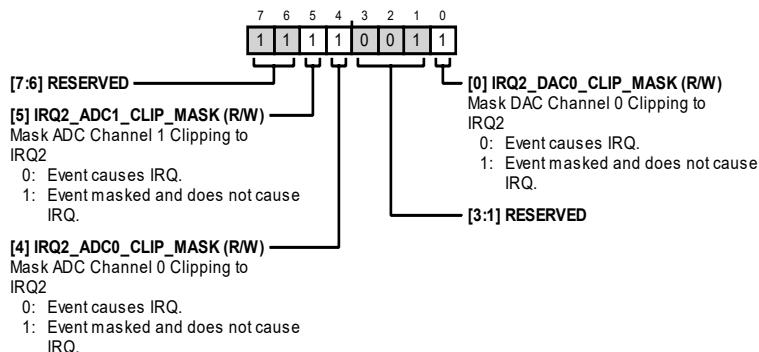

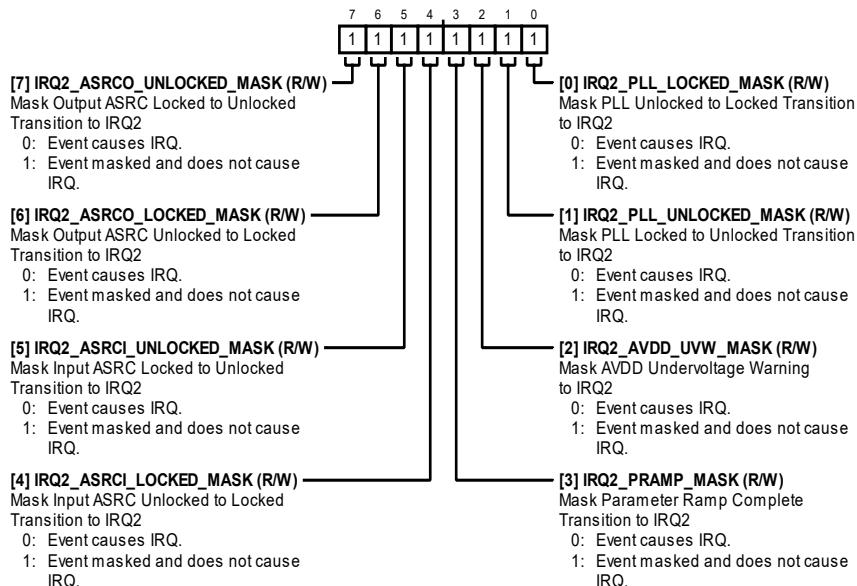

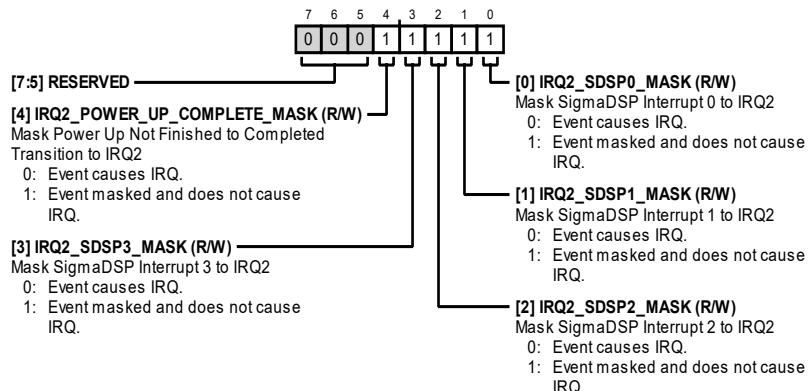

| IRQ2マスク・レジスタ                       | 180 |

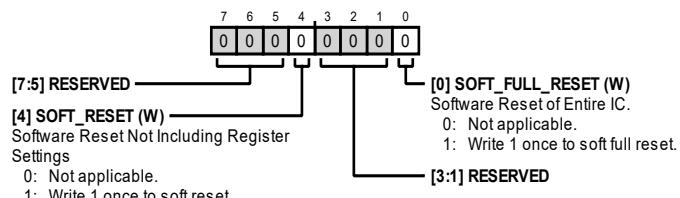

| チップ・リセット・レジスタ                      | 182 |

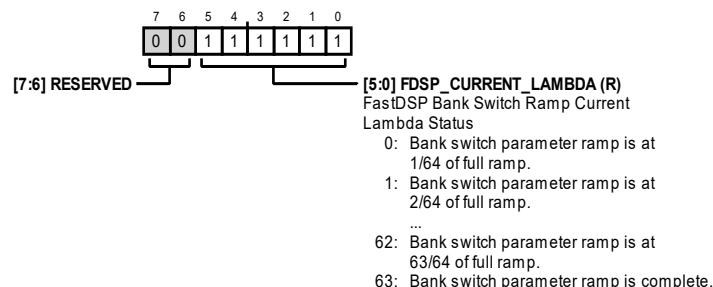

| FastDSP 電流ラムダ・レジスタ                 | 183 |

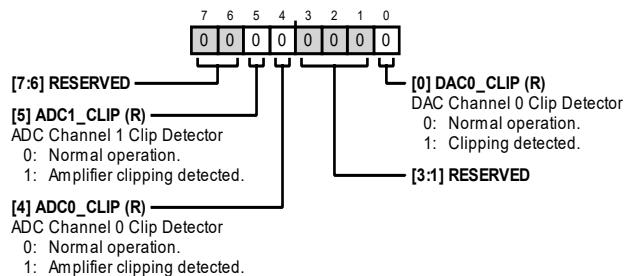

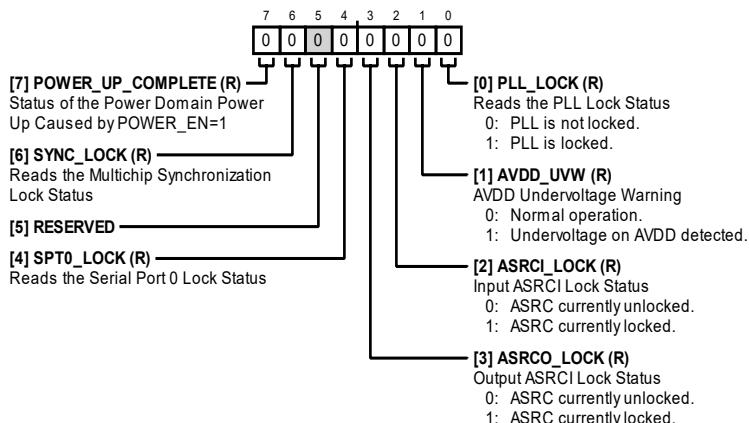

| チップ・ステータス1レジスタ                     | 184 |

| チップ・ステータス2レジスタ                     | 184 |

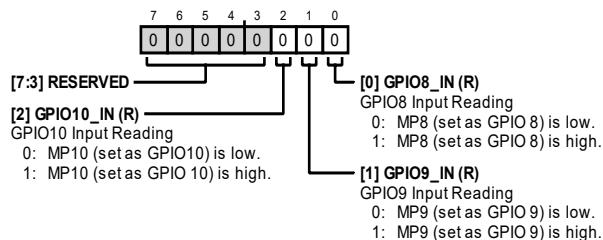

| 汎用入力読出し0～入力読出し7レジスタ                | 185 |

| 汎用入力読出し8～入力読出し10レジスタ               | 186 |

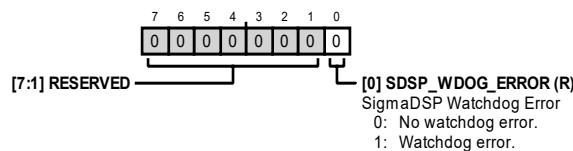

| DSPステータス・レジスタ                      | 186 |

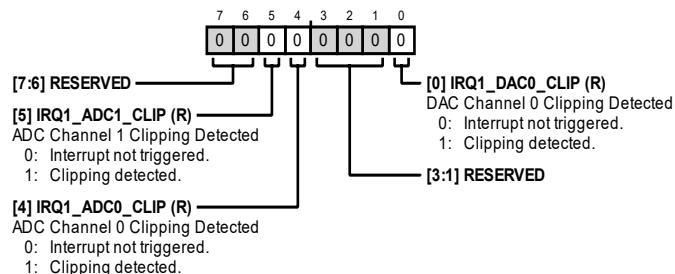

| IRQ1ステータス1レジスタ                     | 187 |

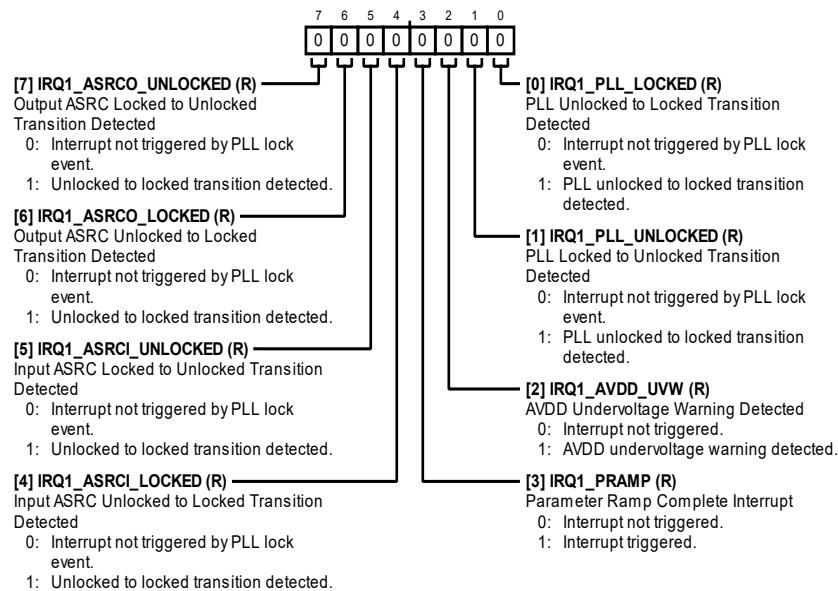

| IRQ1ステータス2レジスタ                     | 188 |

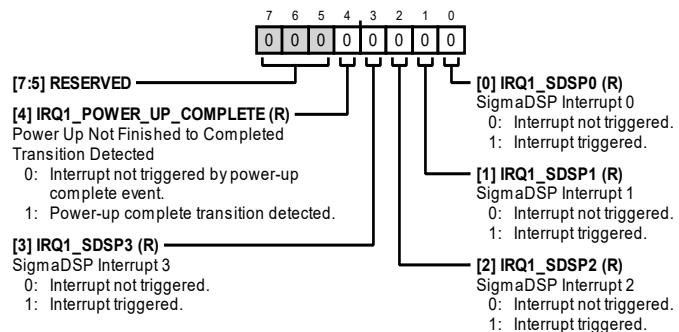

| IRQ1ステータス3レジスタ                     | 189 |

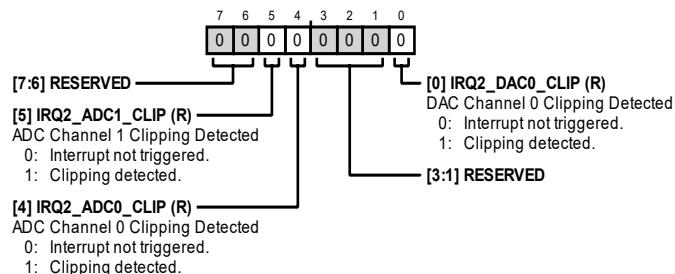

| IRQ2ステータス1レジスタ                     | 190 |

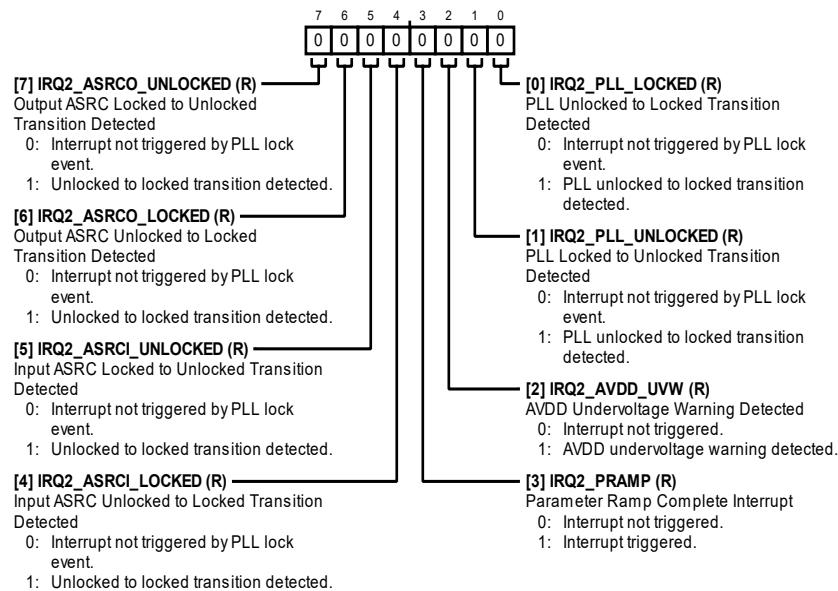

| IRQ2ステータス2レジスタ                     | 191 |

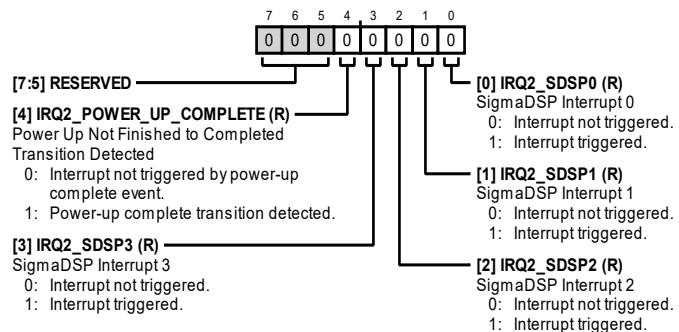

| IRQ2ステータス3レジスタ                     | 192 |

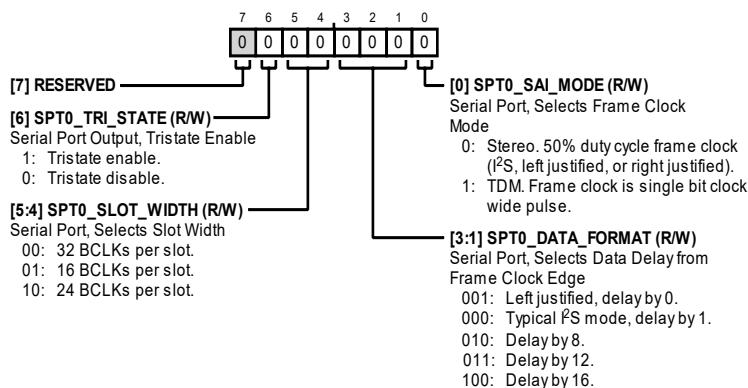

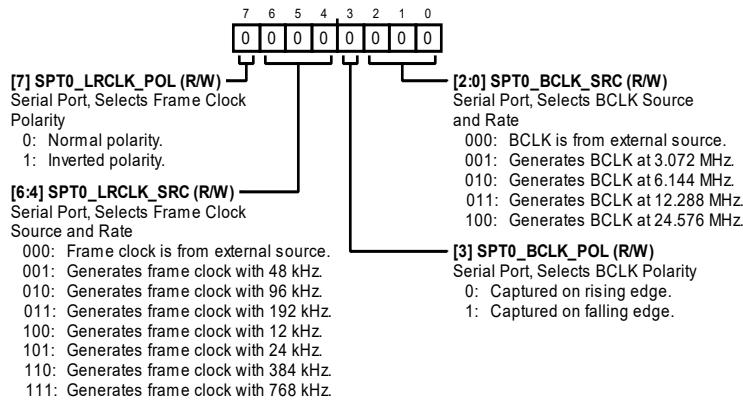

| シリアル・ポート0制御1レジスタ                   | 193 |

| シリアル・ポート0制御2レジスタ                   | 194 |

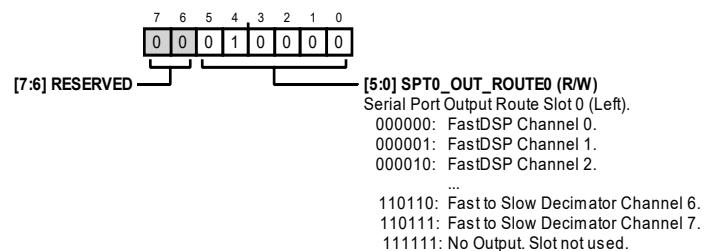

| シリアル・ポート0出力カルーティング・スロット0(左)レジスタ    | 195 |

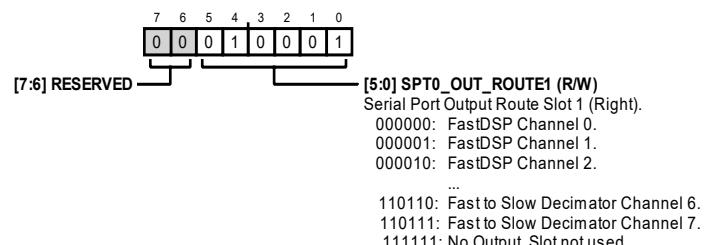

| シリアル・ポート0出力カルーティング・スロット1(右)レジスタ    | 196 |

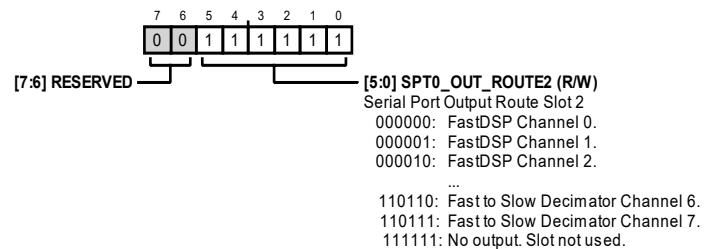

| シリアル・ポート0出力カルーティング・スロット2レジスタ       | 198 |

|                                  |     |

|----------------------------------|-----|

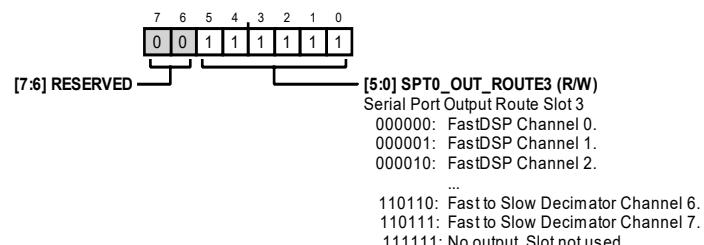

| シリアル・ポート 0 出力ルーティング・スロット 3 レジスタ  | 199 |

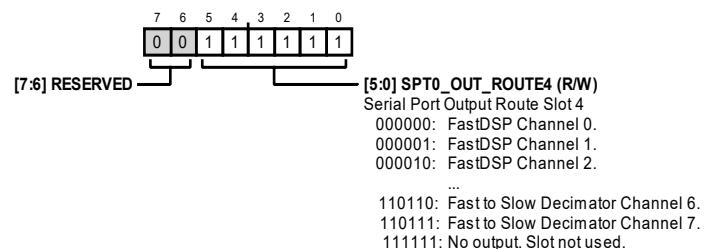

| シリアル・ポート 0 出力ルーティング・スロット 4 レジスタ  | 201 |

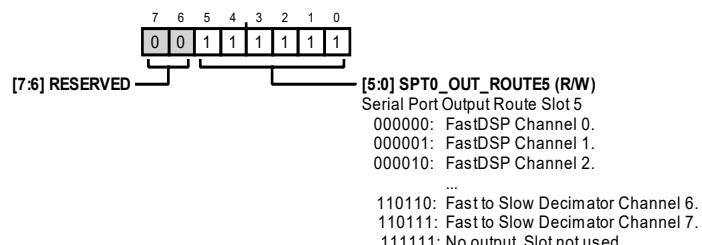

| シリアル・ポート 0 出力ルーティング・スロット 5 レジスタ  | 202 |

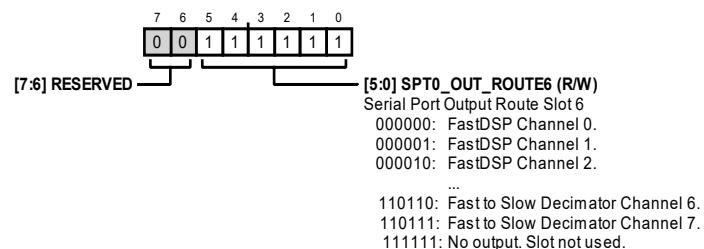

| シリアル・ポート 0 出力ルーティング・スロット 6 レジスタ  | 204 |

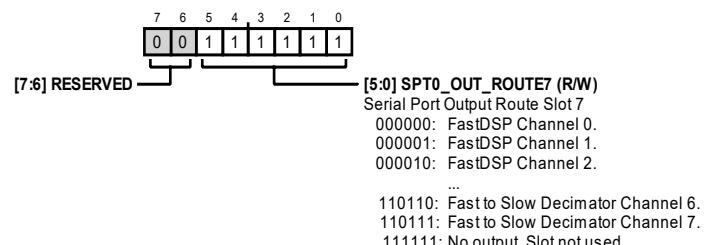

| シリアル・ポート 0 出力ルーティング・スロット 7 レジスタ  | 205 |

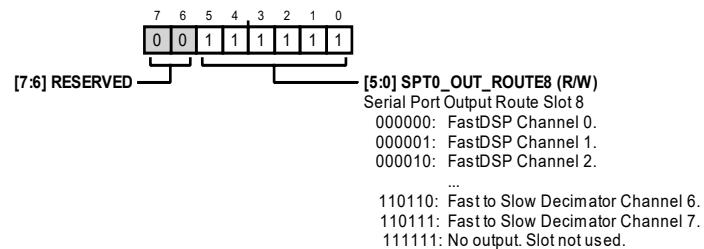

| シリアル・ポート 0 出力ルーティング・スロット 8 レジスタ  | 207 |

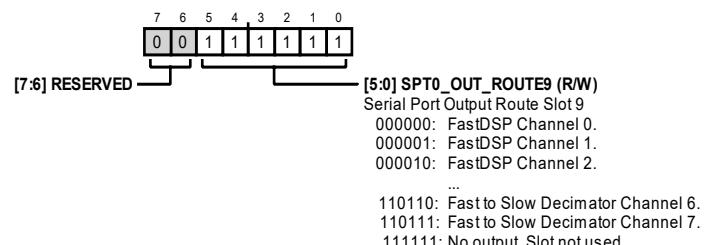

| シリアル・ポート 0 出力ルーティング・スロット 9 レジスタ  | 208 |

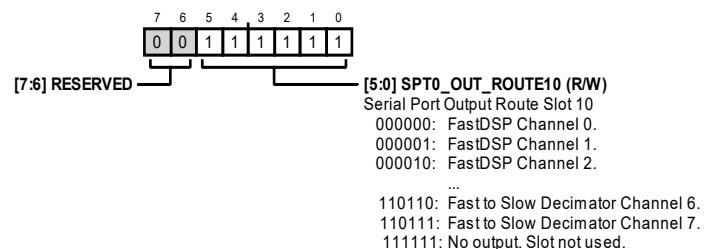

| シリアル・ポート 0 出力ルーティング・スロット 10 レジスタ | 210 |

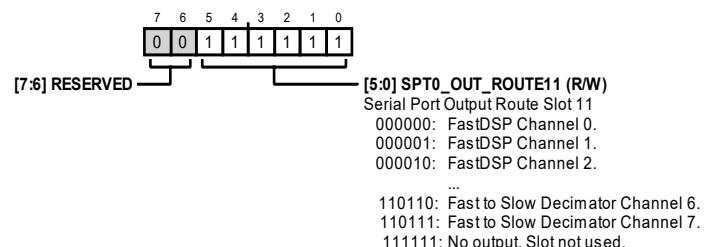

| シリアル・ポート 0 出力ルーティング・スロット 11 レジスタ | 211 |

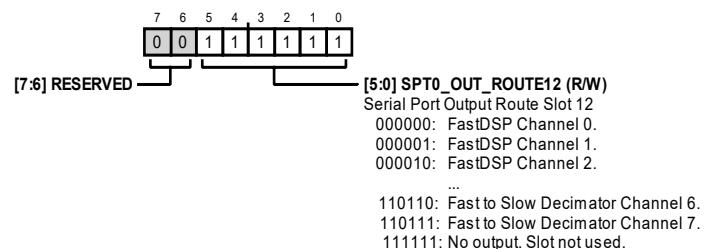

| シリアル・ポート 0 出力ルーティング・スロット 12 レジスタ | 213 |

|                                    |     |

|------------------------------------|-----|

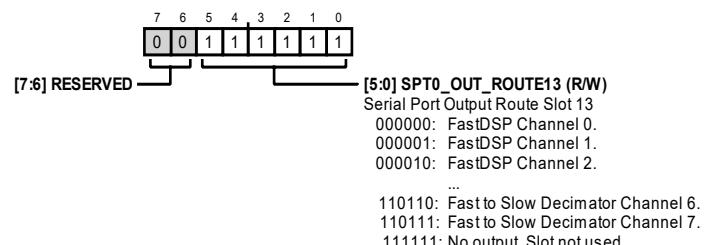

| シリアル・ポート 0 出力ルーティング・スロット 13 レジスタ   | 214 |

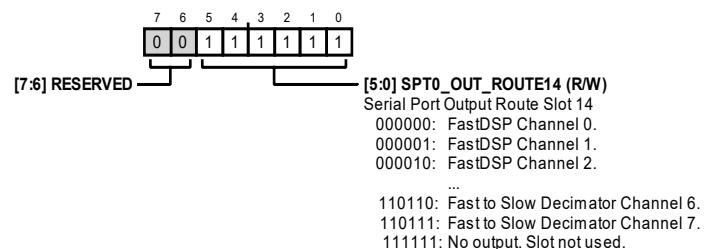

| シリアル・ポート 0 出力ルーティング・スロット 14 レジスタ   | 216 |

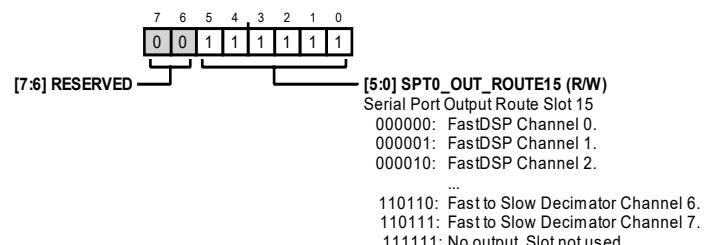

| シリアル・ポート 0 出力ルーティング・スロット 15 レジスタ   | 217 |

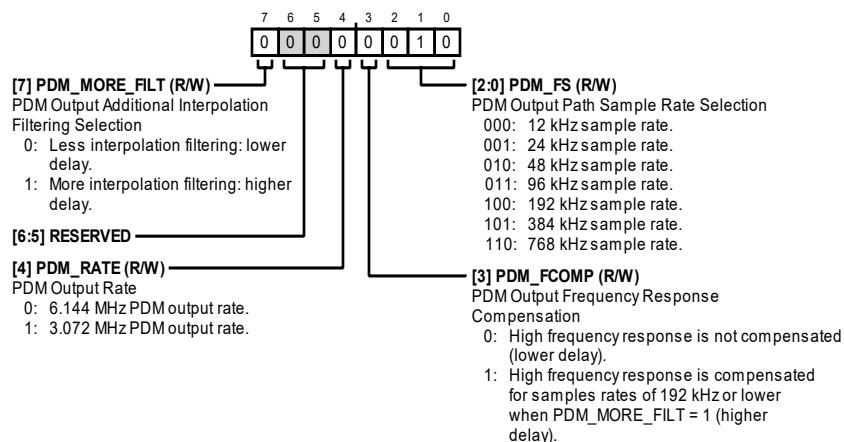

| PDM サンプル・レートおよびフィルタリング・コントロール・レジスタ | 219 |

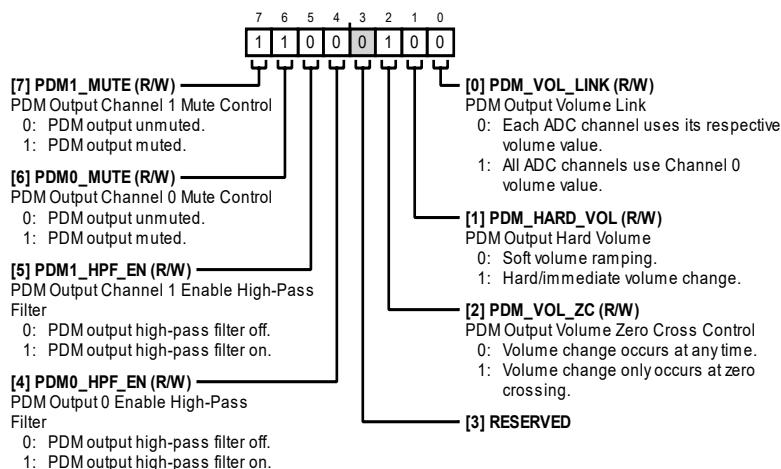

| PDM ミュート、ハイパス、およびボリューム・オプション・レジスタ  | 220 |

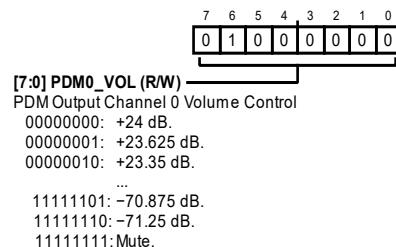

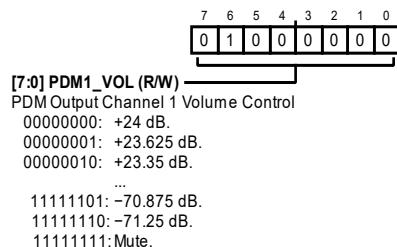

| PDM 出力チャンネル 0 ボリューム・レジスタ           | 221 |

| PDM 出力チャンネル 1 ボリューム・レジスタ           | 222 |

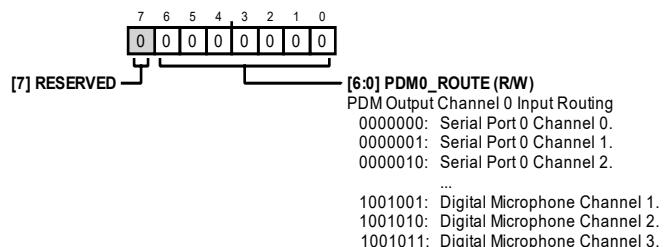

| PDM 出力チャンネル 0 ルーティング・レジスタ          | 222 |

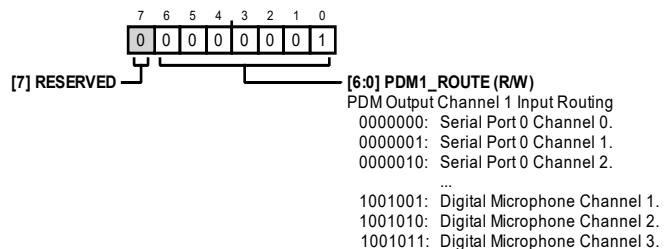

| PDM 出力チャンネル 1 ルーティング・レジスタ          | 224 |

| 外形寸法                               | 226 |

| オーダー・ガイド                           | 226 |

## 改訂履歴

8/2019-Revision 0: 初版

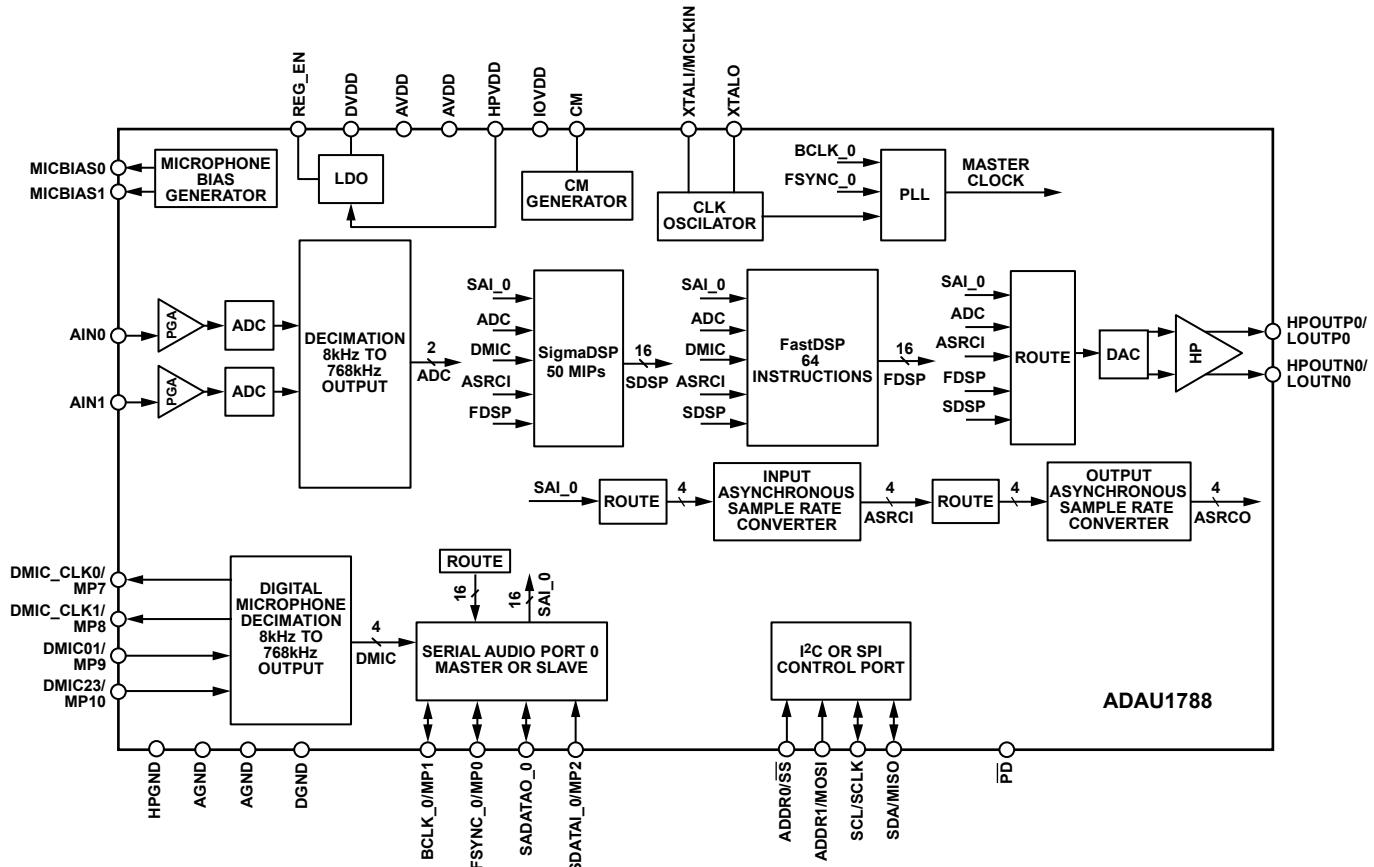

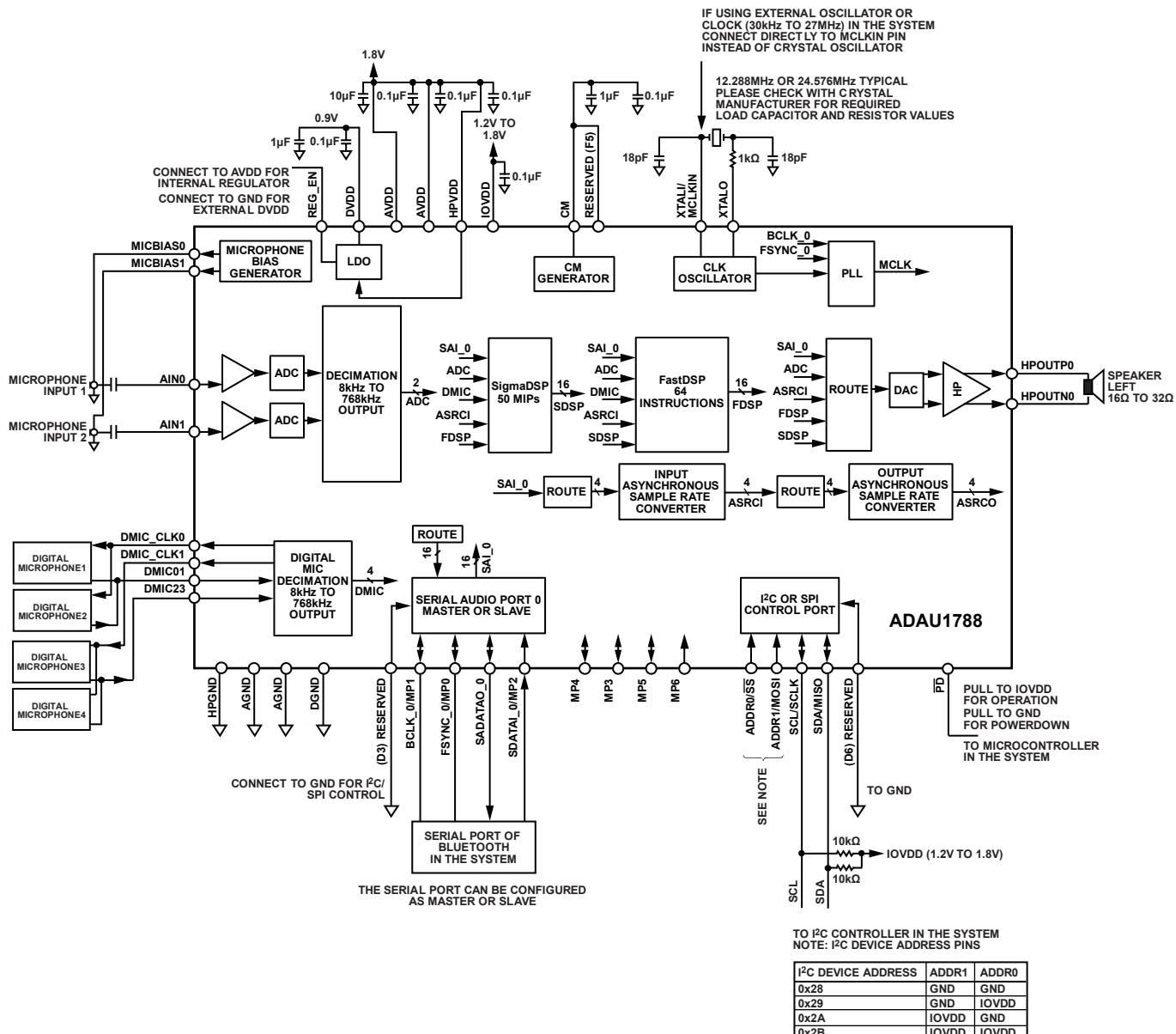

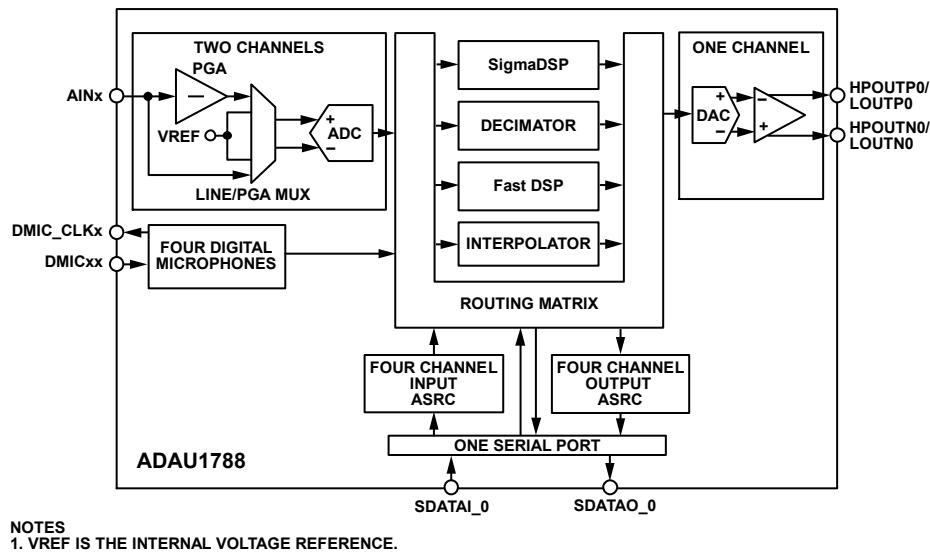

## 機能ブロック図

## NOTES

1. SAI\_0 IS THE SERIAL AUDIO INTERFACE 0.

2. DMIC IS THE DIGITAL MICROPHONE.

3. ASRCI IS THE INPUT ASYNCHRONOUS SAMPLE RATE CONVERTER.

4. ASRCO IS THE OUTPUT ASYNCHRONOUS SAMPLE RATE CONVERTER.

5. FDSP IS FastDSP.

6. SDSP IS SigmaDSP.

20534-001

図 1.

## 仕様

特に指定のない限り、マスター・クロック入力 = 24.576MHz、シリアル入力サンプル・レート = 48kHz、測定帯域幅 = 20Hz~20kHz、ワード幅 = 24 ビット、周囲温度 (TA) = 25°C、ライン出力負荷 = 10kΩ。

## アナログ性能仕様

特に指定のない限り、電源電圧 AVDD = IOVDD = 1.8V および DVDD = 0.9V。

表 1.

| Parameter                                         | Test Conditions/Comments                       | Min | Typ   | Max | Unit  |

|---------------------------------------------------|------------------------------------------------|-----|-------|-----|-------|

| ANALOG-TO-DIGITAL CONVERTERS (ADCs)               |                                                |     |       |     |       |

| ADC Resolution                                    | All ADCs                                       |     | 24    |     | Bits  |

| Digital Gain Step                                 |                                                |     | 0.375 |     | dB    |

| Digital Gain Range                                |                                                | -71 |       | +24 | dB    |

| INPUT RESISTANCE                                  |                                                |     |       |     |       |

| Single-Ended Line Input                           |                                                |     | 14.3  |     | kΩ    |

| Programmable Gain Amplifier (PGA) Inputs          | 0 dB gain                                      |     | 20.26 |     | kΩ    |

|                                                   | 32 dB gain                                     |     | 0.97  |     | kΩ    |

| SINGLE-ENDED LINE INPUT                           | PGAx_EN = 0, PGAx_BOOST = 0, PGAx_SLEW_DIS = 1 |     |       |     |       |

| Full-Scale Input Voltage                          | 0 dBFS                                         |     | 0.49  |     | V rms |

|                                                   | 0 dBFS                                         |     | 1.38  |     | V p-p |

| Dynamic Range <sup>1</sup>                        | 20 Hz to 20 kHz, -60 dB input                  |     |       |     |       |

| With A-Weighted Filter (RMS)                      |                                                |     | 97    |     | dB    |

| With Flat 20 Hz to 20 kHz Filter                  |                                                |     | 94    |     | dB    |

| Signal-to-Noise Ratio (SNR) <sup>2</sup>          |                                                |     |       |     |       |

| With A-Weighted Filter (RMS)                      |                                                |     | 98    |     | dB    |

| With Flat 20 Hz to 20 kHz Filter                  |                                                |     | 96    |     | dB    |

| Interchannel Gain Mismatch                        |                                                |     | 40    |     | mdB   |

| Total Harmonic Distortion + Noise (THD + N) Level | 20 Hz to 20 kHz, -1 dB full-scale output       |     |       |     |       |

| Offset Error                                      |                                                |     | -90   |     | dBFS  |

| Gain Error                                        |                                                |     | ±0.1  |     | mV    |

| Interchannel Isolation                            | CM capacitor = 10 μF                           |     | ±0.2  |     | dB    |

| Power Supply Rejection Ratio (PSRR)               | CM capacitor = 10 μF                           |     | 100   |     | dB    |

|                                                   | 100 mV p-p at 1 kHz                            |     |       |     |       |

|                                                   | 100 mV p-p at 10 kHz                           |     | 60    |     | dB    |

|                                                   |                                                |     | 40    |     | dB    |

| SINGLE-ENDED PGA INPUT                            | PGAx_EN = 1, PGA_x_BOOST = 0                   |     |       |     |       |

| Full-Scale Input Voltage                          |                                                |     | 0.49  |     | V rms |

|                                                   | 0 dBFS                                         |     | 1.38  |     | V p-p |

| Dynamic Range <sup>1</sup>                        | 20 Hz to 20 kHz, -60 dB input                  |     |       |     |       |

| With A-Weighted Filter (RMS)                      |                                                |     | 96    |     | dB    |

| With Flat 20 Hz to 20 kHz Filter                  |                                                |     | 94    |     | dB    |

| THD + N Level                                     | 20 Hz to 20 kHz, -1 dBFS output                |     | -88   |     | dBFS  |

| SNR <sup>2</sup>                                  |                                                |     |       |     |       |

| With A-Weighted Filter (RMS)                      |                                                |     | 96    |     | dB    |

| With Flat 20 Hz to 20 kHz Filter                  |                                                |     | 94    |     | dB    |

| PGA Gain Variation                                | Standard deviation                             |     |       |     |       |

| With 0 dB Setting                                 |                                                |     | 0.05  |     | dB    |

| With 35.25 dB Setting                             |                                                |     | 0.15  |     | dB    |

| Parameter                        | Test Conditions/Comments                                              | Min   | Typ | Max | Unit     |

|----------------------------------|-----------------------------------------------------------------------|-------|-----|-----|----------|

| PGA Boost                        | PGA_x_BOOST                                                           | 10    |     |     | dB       |

| Interchannel Gain Mismatch       |                                                                       | 0.005 |     |     | dB       |

| Offset Error                     |                                                                       | 0     |     |     | mV       |

| Gain Error                       |                                                                       | ±0.2  |     |     | dB       |

| Interchannel Isolation           |                                                                       | 83    |     |     | dB       |

| PSRR                             | CM capacitor = 10 $\mu$ F, 100 mV p-p at 1 kHz<br>100 mV p-p at 1 kHz | 70    |     |     | dB       |

|                                  |                                                                       | 49    |     |     | dB       |

| MICROPHONE BIAS                  | MBIASx_EN = 1, 1 $\mu$ F load                                         |       |     |     |          |

| Bias Voltage                     | MBIASx_LEVEL = 1                                                      | 1.18  |     |     | V        |

|                                  | MBIASx_LEVEL = 0                                                      | 1.63  |     |     | V        |

| Bias Current Source              |                                                                       |       | 2   |     | mA       |

| Output Impedance                 |                                                                       | 1     |     |     | $\Omega$ |

| MICBIASx Isolation               | MBIASx_LEVEL = 0                                                      | 95    |     |     | dB       |

|                                  | MBIASx_LEVEL = 1                                                      | 99    |     |     | dB       |

| Noise <sup>3</sup>               | AVDD = 1.8 V, 20 Hz to 20 kHz, A-weighted                             |       |     |     |          |

|                                  | MBIASx_LEVEL = 0                                                      | 3.5   |     |     | $\mu$ V  |

|                                  | MBIASx_LEVEL = 1                                                      | 3.5   |     |     | $\mu$ V  |

| CONVERTERS DIGITAL               |                                                                       |       |     |     |          |

| Internal Converter Resolution    | All digital-to-analog converters (DAC)/ADCs                           | 24    |     |     | Bits     |

| Digital Gain                     |                                                                       |       |     |     |          |

| Step                             |                                                                       | 0.375 |     |     | dB       |

| Range                            |                                                                       | -71   | +24 |     | dB       |

| Ramp Rate                        |                                                                       | 4.5   |     |     | dB/ms    |

| DAC DIFFERENTIAL OUTPUT          | Differential operation                                                |       |     |     |          |

| Full-Scale Output Voltage        | 0 dBFS to DAC                                                         | 1.0   |     |     | V rms    |

| Dynamic Range <sup>1</sup>       | Line output mode, 20 Hz to 20 kHz, -60 dB input                       |       |     |     |          |

|                                  |                                                                       | 105   |     |     | dB       |

| With A-Weighted Filter (RMS)     |                                                                       | 102   |     |     | dB       |

| With Flat 20 Hz to 20 kHz Filter |                                                                       |       |     |     |          |

| SNR <sup>2</sup>                 | Line output mode, 20 Hz to 20 kHz                                     |       |     |     |          |

| With A-Weighted Filter (RMS)     |                                                                       | 105   |     |     | dB       |

| With Flat 20 Hz to 20 kHz Filter |                                                                       | 102   |     |     | dB       |

| THD + N Level                    | Line output mode, 20 Hz to 20 kHz, -1 dBFS                            | -93   |     |     | dBV      |

| Gain Error                       | Line output mode                                                      | ±1.5  |     |     | %        |

| Dynamic Range <sup>1</sup>       | Headphone mode, 20 Hz to 20 kHz, -60 dB input                         |       |     |     |          |

| With A-Weighted Filter (RMS)     |                                                                       | 105   |     |     | dB       |

| With Flat 20 Hz to 20 kHz Filter |                                                                       | 101   |     |     | dB       |

| SNR <sup>2</sup>                 | Headphone mode, 20 Hz to 20 kHz                                       |       |     |     |          |

| With A-Weighted Filter (RMS)     |                                                                       | 105   |     |     | dB       |

| With Flat 20 Hz to 20 kHz Filter |                                                                       | 101   |     |     | dB       |

| THD + N Level                    | Headphone mode                                                        |       |     |     |          |

| 32 $\Omega$ Load                 | -1 dBFS, output power (P <sub>OUT</sub> ) = 27 mW                     | -75   |     |     | dBV      |

|                                  | P <sub>OUT</sub> = 1 mW                                               | -82   |     |     | dBV      |

| 24 $\Omega$ Load                 | -2 dBFS, P <sub>OUT</sub> = 28 mW                                     | -75   |     |     | dBV      |

| 16 $\Omega$ Load                 | -3 dBFS, P <sub>OUT</sub> = 33 mW                                     | -75   |     |     | dBV      |

| Headphone Output Power           |                                                                       |       |     |     |          |

| 32 $\Omega$ Load                 | AVDD = 1.8 V, <0.1% THD + N                                           | 30    |     |     | mW       |

| 24 $\Omega$ Load                 | AVDD = 1.8 V, <0.1% THD + N                                           | 40    |     |     | mW       |

| 16 $\Omega$ Load                 | AVDD = 1.8 V, <0.1% THD + N                                           | 50    |     |     | mW       |

| Parameter                    | Test Conditions/Comments                                                 | Min  | Typ             | Max      | Unit          |

|------------------------------|--------------------------------------------------------------------------|------|-----------------|----------|---------------|

| Gain Error                   | Headphone mode                                                           |      | ±2.5            |          | %             |

| DC Offset                    |                                                                          |      | ±0.2            |          | mV            |

| PSRR                         | CM capacitor = 10 $\mu$ F<br>100 mV p-p at 1 kHz<br>100 mV p-p at 10 kHz |      | 70<br>70<br>1.5 | 70<br>70 | dB<br>dB<br>V |

| AVDD Undervoltage Trip Point |                                                                          |      |                 |          |               |

| CM REFERENCE                 | CM pin                                                                   |      | 0.85            |          | V             |

| Output                       |                                                                          |      | 5               |          | k $\Omega$    |

| Source Impedance             |                                                                          |      |                 |          |               |

| PHASED-LOCKED LOOP (PLL)     |                                                                          |      |                 |          |               |

| Input Frequency              | After input prescale                                                     | 0.03 |                 | 27       | MHz           |

| Output Frequency             |                                                                          | 32   | 49.152          | 50       | MHz           |

| Fractional Limits            | Fractional mode, fraction part (N/M), see the PLL section                | 0.1  |                 | 0.9      |               |

| Integer Limits               | Fractional mode, integer part                                            | 2    |                 | 1536     |               |

| Lock Time                    | 48 kHz input<br>24.576 MHz input                                         |      | 2.03<br>0.46    | 0.55     | ms<br>ms      |

| REGULATOR                    |                                                                          |      | 1               |          | mV/V          |

| Line Regulation              |                                                                          |      | 0.5             |          | mV/mA         |

| Load Regulation              |                                                                          |      |                 |          |               |

<sup>1</sup> ダイナミック・レンジは、-60dBFS の信号を印加した状態でのフルスケール電力レベルに対する測定対象帯域のノイズ電力と高調波電力の合計の比率（デシベル単位）です。

<sup>2</sup> S/N 比は、信号を印加しない状態でのフルスケール電力レベルに対する測定対象帯域の全てのノイズ電力の合計の比率（デシベル単位）です。

<sup>3</sup> これらの仕様は、このピンに 4.7 $\mu$ F のデカップリング・コンデンサと 5.0k $\Omega$  の負荷を使用した場合の値です。

## 水晶発振器アンプの仕様

特に指定のない限り、電源電圧 AVDD = IOVDD = 1.8V および DVDD = 0.9V。

表 2.

| Parameter        | Test Conditions/Comments | Min | Typ | Max | Unit |

|------------------|--------------------------|-----|-----|-----|------|

| JITTER           |                          |     | 270 | 500 | ps   |

| FREQUENCY RANGE  |                          | 1   |     | 27  | MHz  |

| LOAD CAPACITANCE |                          |     |     | 20  | pF   |

## デジタル入出力の仕様

特に指定のない限り、-40°C < TA < +85°C、IOVDD = 1.1V~1.98V。

表 3.

| Parameter           | Symbols         | Test Conditions/Comments                                                                                                                            | Min                          | Typ                          | Max | Unit         |

|---------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------|-----|--------------|

| INPUT VOLTAGE       |                 |                                                                                                                                                     |                              |                              |     |              |

| High                | V <sub>IH</sub> |                                                                                                                                                     | 0.7 × IOVDD                  |                              |     | V            |

| Low                 | V <sub>IL</sub> | IOVDD = 1.8 V, input high current (I <sub>IH</sub> ) at V <sub>IH</sub> = 1.1 V<br>Input low current (I <sub>IL</sub> ) at V <sub>IL</sub> = 0.45 V |                              | 0.3 × IOVDD<br>10            | 10  | V<br>$\mu$ A |

| OUTPUT VOLTAGE HIGH | V <sub>OH</sub> |                                                                                                                                                     |                              |                              |     |              |

| Drive Strength      |                 | Output high current (I <sub>OH</sub> ) = 1 mA<br>I <sub>OH</sub> = 3 mA                                                                             | 0.71 × IOVDD<br>0.71 × IOVDD | 0.83 × IOVDD<br>0.83 × IOVDD |     | V<br>V       |

| Low                 |                 |                                                                                                                                                     |                              |                              |     |              |

| High                |                 |                                                                                                                                                     |                              |                              |     |              |

| Parameter                                      | Symbols         | Test Conditions/Comments               | Min         | Typ            | Max            | Unit |

|------------------------------------------------|-----------------|----------------------------------------|-------------|----------------|----------------|------|

| OUTPUT VOLTAGE<br>LOW<br>Drive Strength<br>Low | V <sub>OL</sub> | Output low current ( $I_{OL}$ ) = 1 mA | 0.1 × IOVDD | 0.3 ×<br>IOVDD | 0.3 ×<br>IOVDD | V    |

| High                                           |                 | $I_{OL}$ = 3 mA                        |             |                |                |      |

| INPUT CAPACITANCE                              |                 |                                        |             | 5              | pF             |      |

## 電源の仕様

特に指定のない限り、電源電圧  $AVDD = IOVDD = 1.8V$  および  $DVDD = 0.9V$ 。PLL ディスエーブル、マスタ・クロックを直接供給。デジタル入出力 (I/O) ラインに 25pF の負荷を使用。

表 4.

| Parameter                                 | Test Conditions/Comments                                                                          | Min   | Typ   | Max   | Unit |

|-------------------------------------------|---------------------------------------------------------------------------------------------------|-------|-------|-------|------|

| SUPPLIES                                  |                                                                                                   |       |       |       |      |

| AVDD Voltage                              |                                                                                                   | 1.7   | 1.8   | 1.98  | V    |

| DVDD Voltage                              |                                                                                                   | 0.85  | 0.9   | 0.99  | V    |

| IOVDD Voltage                             |                                                                                                   | 1.1   | 1.8   | 1.98  | V    |

| Digital I/O Current with IOVDD = 1.8 V    | Crystal oscillator (24.576 MHz) enabled, IOVDD = 1.8 V                                            |       |       |       |      |

| Slave Mode, Serial Audio Port 0 (SPT0) On | Sampling frequency ( $f_s$ ) = 48 kHz, BCLK_0 = 3.072 MHz<br>$f_s$ = 192 kHz, BCLK_0 = 12.288 MHz | 0.271 |       |       | mA   |

| Master Mode, SPT0 On                      | $f_s$ = 48 kHz, BCLK_0 = 3.072 MHz<br>$f_s$ = 192 kHz, BCLK_0 = 12.288 MHz                        | 0.280 | 0.477 | 1.077 | mA   |

## パワーダウン電流

電源電圧  $AVDD = IOVDD = 1.8V$  および  $DVDD = 0.9V$  (外部電源)。PLL および水晶発振器ディスエーブル。

表 5.

| Parameter                                      | AVDD Current<br>Min Typ Max | DVDD Current<br>Min Typ Max | IOVDD Current<br>Min Typ Max | Unit |

|------------------------------------------------|-----------------------------|-----------------------------|------------------------------|------|

|                                                |                             |                             |                              |      |

| PD PIN LOW (HARDWARE POWER-DOWN)               | 0.52                        | 11                          | 0.69                         | µA   |

| POWER_EN = 0                                   |                             |                             |                              |      |

| No Keep Alives                                 | 0.52                        | 11                          | 0.69                         | µA   |

| CM_KEEP_ALIVE = 1, KEEP_FDSP and KEEP_SDSP = 0 | 62                          | 11                          | 6.0                          | µA   |

| CM_KEEP_ALIVE = 1, KEEP_FDSP and KEEP_SDSP = 1 | 64                          | 11                          | 6.0                          | µA   |

## 消費電力

マスタ・クロック = 24.576MHz (水晶発振器イネーブル) で PLL イネーブル。DVDD = 0.9V、および AVDD = IOVDD = 1.8V (外部電源)。必要に応じて、ADC0 および ADC1 は 384kHz で動作。FastDSP™は 384kHz で動作 (精度 27 ビットのバイクワッド・フィルタ)、SigmaDSP®は 48kHz で動作。SDSP\_SPEED = 0 では 24MIPS の測定値、SDSP\_SPEED = 1 では 50MIPS の測定値。DAC0 は 384kHz で動作、DAC\_LPM = 1。1 つのシリアル・ポート入出力 (スレーブとして設定)、32Ω のヘッドフォン負荷を使用。静止電流 (信号なし)。

表 6.

| ADC Channel | DAC Channel | ASRCI/ASRCO Channel <sup>1</sup> | SigmaDSP MIPS | FastDSP Instruction | Digital Microphone Channels | Interpolator/Decimator Channel | DVDD Current (mA) | AVDD Current (mA) | IOVDD Current (mA) |

|-------------|-------------|----------------------------------|---------------|---------------------|-----------------------------|--------------------------------|-------------------|-------------------|--------------------|

| 0           | 1           | 0                                | 0             | 0                   | 0                           | 0                              | 0.395             | 1.188             | 0.283              |

| 2           | 0           | 0                                | 24            | 0                   | 0                           | 0                              | 1.213             | 1.652             | 0.293              |

| 2           | 0           | 0                                | 50            | 0                   | 0                           | 0                              | 2.081             | 1.652             | 0.293              |

| 2           | 0           | 0                                | 0             | 32                  | 0                           | 0                              | 1.876             | 1.652             | 0.293              |

| 2           | 0           | 0                                | 0             | 64                  | 0                           | 0                              | 3.289             | 1.652             | 0.293              |

| 2           | 1           | 2/2                              | 24            | 32                  | 0                           | 0                              | 3.020             | 2.531             | 0.293              |

| 2           | 1           | 2/2                              | 24            | 32                  | 0                           | 2/2                            | 3.060             | 2.531             | 0.293              |

| 2           | 1           | 2/2                              | 24            | 32                  | 4                           | 2/2                            | 3.131             | 2.531             | 0.415              |

| 2           | 1           | 2/2                              | 50            | 64                  | 4                           | 4/4                            | 5.477             | 2.531             | 0.415              |

<sup>1</sup> ASRCI は入力非同期サンプル・レート・コンバータで、ASRCO は出力非同期サンプル・レート・コンバータです。

標準的なアクティブ・ノイズ・キャンセリング (ANC) 設定。マスタ・クロック = 24.576MHz (水晶発振器ディスエーブル、PLL をバイパス)。DVDD = 0.9V、および AVDD = IOVDD = 1.8V (外部電源)。2 つの ADC (PGA イネーブル)。DAC を差動ヘッドフォン動作に設定。DAC 出力に 32Ω の負荷を使用し、DAC\_LPM = 1。1 つのシリアル・ポート入出力 (スレーブとして設定)。2 つの入出力非同期サンプル・レート・コンバータ (ASRC)。2 つの低速から高速へのインターポレータをイネーブル。MICBIAS0 と MICBIAS1 の両方を 0.9 × AVDD でイネーブル。FastDSP は 32 個の命令 (精度 27 ビットのバイクワッド・フィルタ) を 384kHz で実行。SigmaDSP は 24MIPS を 48kHz で実行。静止電流 (信号なし)。

表 7.

| Operating Voltage    | Power Management Setting | Typical Current (mA) |       |       | Total Power Consumption (mW) | Typical ADC THD + N (dB) | Typical High Power Output THD + N (dB) |

|----------------------|--------------------------|----------------------|-------|-------|------------------------------|--------------------------|----------------------------------------|

|                      |                          | AVDD                 | DVDD  | IOVDD |                              |                          |                                        |

| AVDD = IOVDD = 1.8 V | Normal (default)         | 2.828                | 3.216 | 0.025 | 8.030                        | -89.5                    | -78 at 24 mW output                    |

| DVDD = 0.9 V         | Power saving             | 2.453                | 3.215 | 0.025 | 7.354                        | -80.5                    | -78 at 24 mW output                    |

|                      | Extreme power saving     | 2.306                | 3.213 | 0.025 | 7.088                        | -78                      | -77.5 at 24 mW output                  |

## デジタル・フィルタ

表 8.

| Parameter                               | Test Conditions/Comments                                                                                              | Min  | Typ                  | Max                                                              | Unit                          |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------|----------------------|------------------------------------------------------------------|-------------------------------|

| ADC INPUT TO DAC OUTPUT PATH            |                                                                                                                       |      |                      |                                                                  |                               |

| Pass-Band Ripple                        | DC to 20 kHz, $f_S = 192$ kHz<br>(ADC01_FCOMP = 1, DAC_FCOMP = 1)                                                     |      |                      | $\pm 0.02$                                                       | dB                            |

| Group Delay <sup>1</sup>                | $f_S = 192$ kHz<br>$f_S = 384$ kHz<br>$f_S = 768$ kHz                                                                 |      | 12.9<br>7.5<br>5     |                                                                  | $\mu$ s<br>$\mu$ s<br>$\mu$ s |

| SAMPLE RATE CONVERTER                   |                                                                                                                       |      |                      |                                                                  |                               |

| Pass Band                               | LRCLK < 63 kHz<br>63 kHz < LRCLK < 112 kHz<br>LRCLK > 112 kHz                                                         |      |                      | $0.475 \times f_S$<br>$0.4286 \times f_S$<br>$0.4286 \times f_S$ | kHz                           |

| Audio Band Ripple                       | 20 Hz to 20 kHz                                                                                                       | -0.1 |                      | +0.1                                                             | dB                            |

| Input and Output Sample Frequency Range |                                                                                                                       | 7    |                      | 224                                                              | kHz                           |

| Dynamic Range                           | $x_{LPM} = 0$<br>$x_{LPM} = 1$<br>$x_{LPM\_II} = 1$                                                                   |      | 130<br>130<br>130    |                                                                  | dB<br>dB<br>dB                |

| THD + Noise                             | 20 Hz to 20 kHz, input: typical at 1 kHz and maximum at 20 kHz<br>$x_{LPM} = 0$<br>$x_{LPM} = 1$<br>$x_{LPM\_II} = 1$ |      | -130<br>-120<br>-115 | -120<br>-110<br>-90                                              | dBFS<br>dBFS<br>dBFS          |

| Startup Time to Lock                    |                                                                                                                       |      |                      | 25                                                               | ms                            |

| PULSE DENSITY MODULATION (PDM) OUTPUTS  |                                                                                                                       |      |                      |                                                                  |                               |

| Dynamic Range                           | 20 Hz to 20 kHz, with A-weighted filter                                                                               |      | 126                  |                                                                  | dBFS                          |

| THD + N                                 | 20 Hz to 20 kHz, -6 dBFS input                                                                                        |      | -125                 |                                                                  | dBFS                          |

| Group Delay from ADC                    | $f_S = 384$ kHz<br>$f_S = 768$ kHz                                                                                    |      | 7.5<br>4.9           |                                                                  | $\mu$ s<br>$\mu$ s            |

<sup>1</sup> 群遅延は、ゼロ命令を使用して高速デジタル・シグナル・プロセッサ (FDSP) で測定しています。

## デジタル・タイミング仕様

特に指定のない限り、 $-40^{\circ}\text{C} < T_A < +85^{\circ}\text{C}$ 、 $\text{IOVDD} = 1.1\text{V} \sim 1.8\text{V}$ 、および  $\text{DVDD} = 0.9\text{V} \sim 0.99\text{V}$ 。

表 9.

| パラメータ                                  | 限界値   |       | 単位            | 説明                                                                  |

|----------------------------------------|-------|-------|---------------|---------------------------------------------------------------------|

|                                        | 最小値   | 最大値   |               |                                                                     |

| MASTER CLOCK                           |       |       |               | MCLKIN の周期                                                          |

| $t_{\text{MPI}}$                       | 0.037 | 33.3  | $\mu\text{s}$ | 30kHz～27MHz の入力クロック (PLL をインテジャー・モードで使用)                            |

| $t_{\text{MPF}}$                       | 0.037 | 1.0   | $\mu\text{s}$ | 30kHz～27MHz の入力クロック (PLL をフラクショナル・モードで使用)                           |

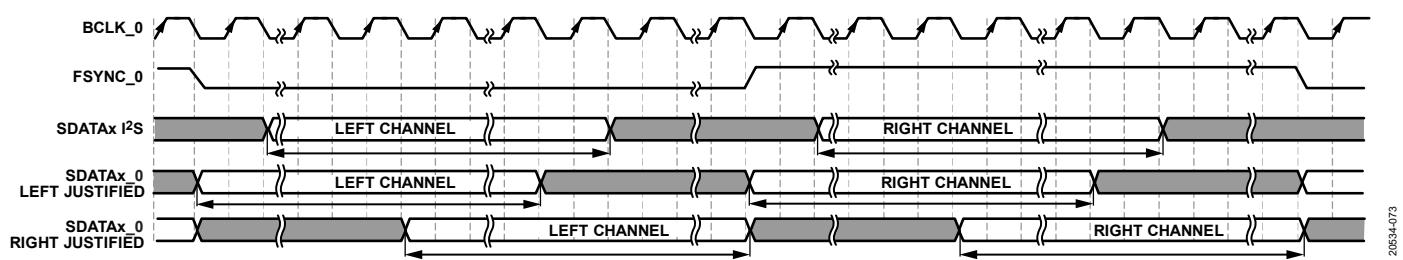

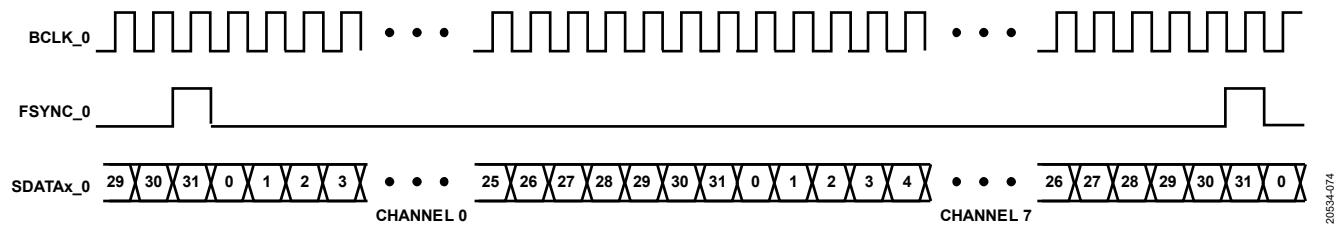

| SERIAL PORT                            |       |       |               |                                                                     |

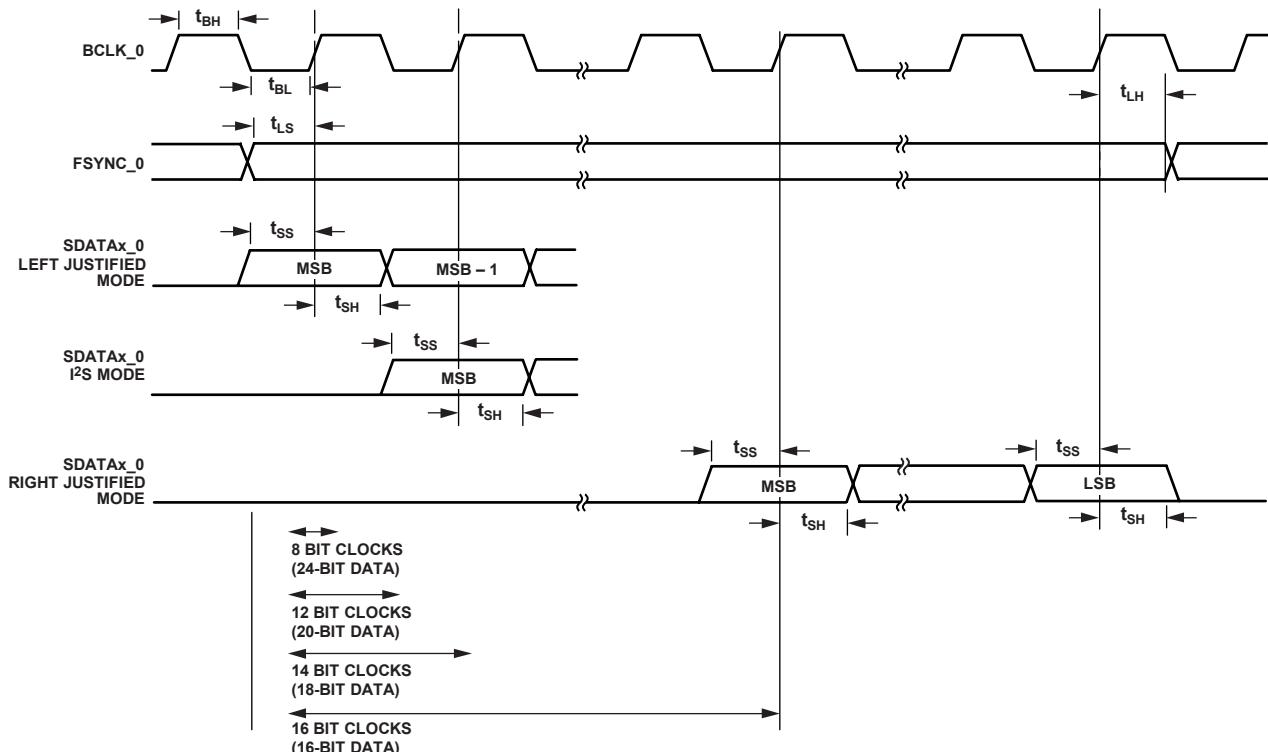

| $t_{\text{BL}}$                        | 18    |       | ns            | BCLK_0 のロー・パルス幅 (マスタ・モードおよびスレーブ・モード)                                |

| $t_{\text{BH}}$                        | 18    |       | ns            | BCLK_0 のハイ・パルス幅 (マスタ・モードおよびスレーブ・モード)                                |

| $f_{\text{BCLK}}$                      | 0.512 | 24.57 | MHz           | BCLK_0 の周波数                                                         |

| $t_{\text{LS}}$                        | 3     |       | ns            | BCLK_0 の立上がりまでの FSYNC_0 のセットアップ時間 (スレーブ・モード)                        |

| $t_{\text{LH}}$                        | 5     |       | ns            | BCLK_0 の立上がりからの FSYNC_0 のホールド時間 (スレーブ・モード)                          |

| $f_{\text{SYNC}}$                      | 8     | 768   | kHz           | FSYNC_0 の周波数                                                        |

| $t_{\text{SS}}$                        | 3     |       | ns            | BCLK_0 の立上がりまでの SDATAI_0 のセットアップ時間 (マスタ・モードおよびスレーブ・モード)             |

| $t_{\text{SH}}$                        | 10    |       | ns            | BCLK_0 の立上がりからの SDATAI_0 のホールド時間 (マスタ・モードおよびスレーブ・モード)               |

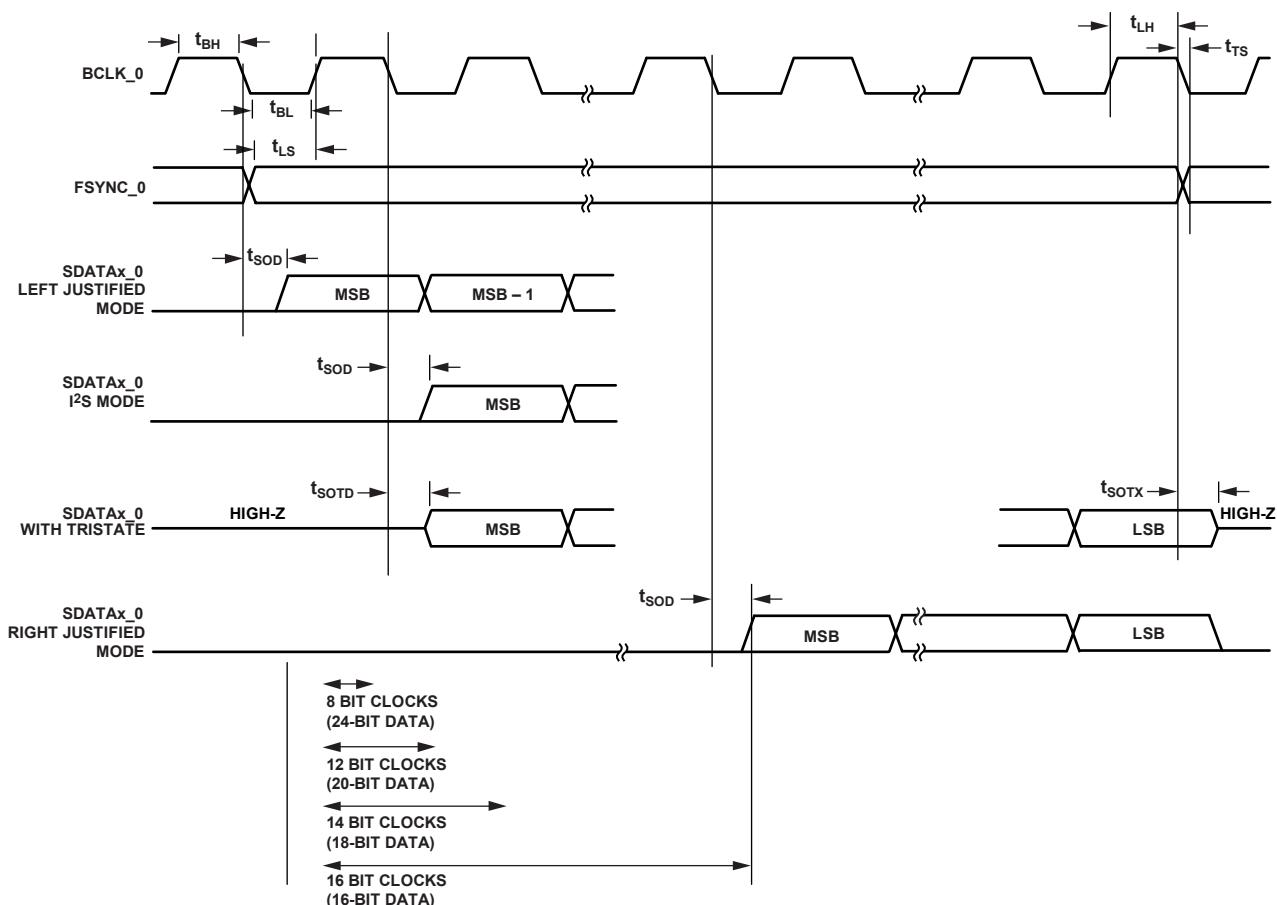

| $t_{\text{TS}}$                        |       | 6     | ns            | BCLK_0 の立下がりから FSYNC_0 へのタイミング・スキー (マスタ・モード)                        |

| $t_{\text{SOD}}$                       | 0     | 16    | ns            | BCLK_0 の立下がりからの SDATAO_0 の遅延時間 (マスタ・モードおよびスレーブ・モード)、IOVDD は最小 1.62V |

|                                        | 0     | 32    | ns            | BCLK_0 の立下がりからの SDATAO_0 の遅延時間 (マスタ・モードおよびスレーブ・モード)、IOVDD は最小 1.1V  |

| $t_{\text{SOTD}}$                      | 0     | 16    | ns            | BCLK_0 の立下がりから SDATAO_0 がトライステート・モードで駆動されるまでの時間                     |

| $t_{\text{SOTX}}$                      | 0     | 16    | ns            | BCLK_0 の立下がりから SDATAO_0 がトライステート・モードでトライステートになるまでの時間                |

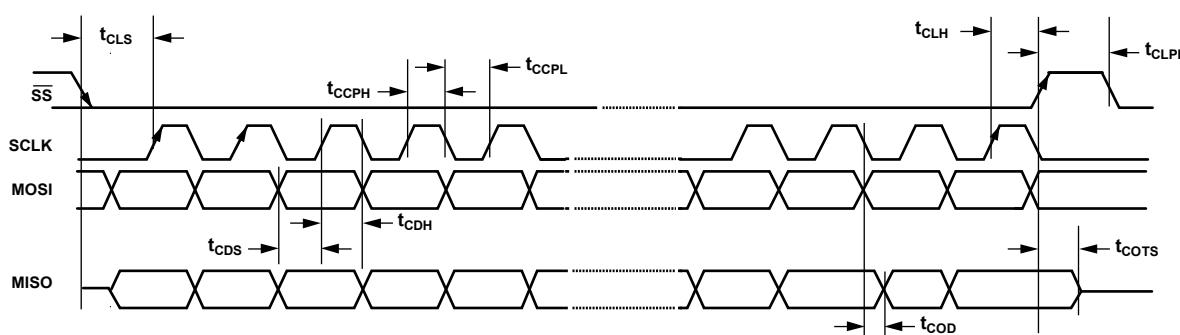

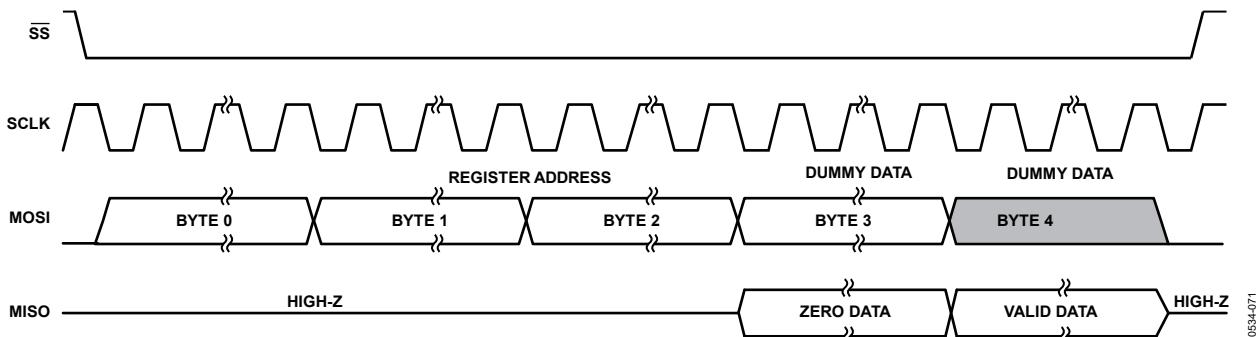

| SERIAL PERIPHERAL INTERFACE (SPI) PORT |       |       |               |                                                                     |

| $f_{\text{SCLK}}$                      |       | 10    | MHz           | SCLK の周波数                                                           |

| $t_{\text{CCPL}}$                      | 35    |       | ns            | SCLK のパルス幅ロー                                                        |

| $t_{\text{CCPH}}$                      | 35    |       | ns            | SCLK のパルス幅ハイ                                                        |

| $t_{\text{CLS}}$                       | 5     |       | ns            | SCLK の立上がりまでの $\overline{\text{SS}}$ のセットアップ時間                      |

| $t_{\text{CLH}}$                       | 40    |       | ns            | SCLK の立上がりからの $\overline{\text{SS}}$ のホールド時間                        |

| $t_{\text{CLPH}}$                      | 10    |       | ns            | $\overline{\text{SS}}$ のパルス幅ハイ                                      |

| $t_{\text{CDS}}$                       | 10    |       | ns            | SCLK の立上がりまでの MOSI のセットアップ時間                                        |

| $t_{\text{CDH}}$                       | 10    |       | ns            | SCLK の立上がりからの MOSI のホールド時間                                          |

| $t_{\text{COD}}$                       |       | 30    | ns            | SCLK の立下がりからの MISO の遅延時間                                            |

| $t_{\text{COTS}}$                      |       | 30    | ns            | $\overline{\text{SS}}$ の立上がりからの MISO の高インピーダンス時間                    |

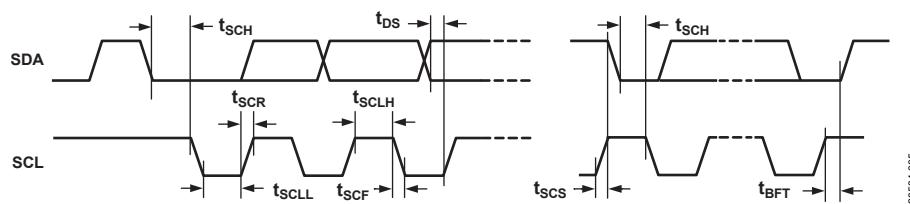

| I <sup>2</sup> C PORT                  |       |       |               |                                                                     |

| $f_{\text{SCL}}$                       |       | 1     | MHz           | SCL の周波数                                                            |

| $t_{\text{SCLH}}$                      | 0.26  |       | $\mu\text{s}$ | SCL ハイ                                                              |

| $t_{\text{SCLL}}$                      | 0.5   |       | $\mu\text{s}$ | SCL ロー                                                              |

| $t_{\text{SCS}}$                       | 0.26  |       | $\mu\text{s}$ | (SDA の立下がりまでの) SCL の立上がりセットアップ時間、反復開始条件に関連                          |

| $t_{\text{SCR}}$                       |       | 120   | ns            | SCL と SDA の立上がり時間、 $C_{\text{LOAD}} = 400\text{pF}$                 |

| $t_{\text{SCH}}$                       | 0.26  |       | $\mu\text{s}$ | (SDA の立下がりからの) SCL の立下がりホールド時間、開始条件に関連                              |

| $t_{\text{DS}}$                        | 50    |       | ns            | (SCL の立上がりまでの) SDA のセットアップ時間                                        |

| $t_{\text{SCF}}$                       |       | 120   | ns            | SCL と SDA の立下がり時間、 $C_{\text{LOAD}} = 400\text{pF}$                 |

| $t_{\text{BFT}}$                       | 0.5   |       | $\mu\text{s}$ | (SDA の立上がりまでの) SCL の立上がりセットアップ時間、停止条件に関連                            |

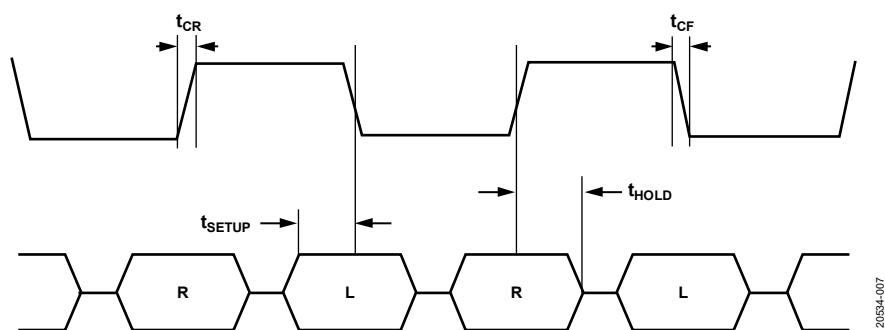

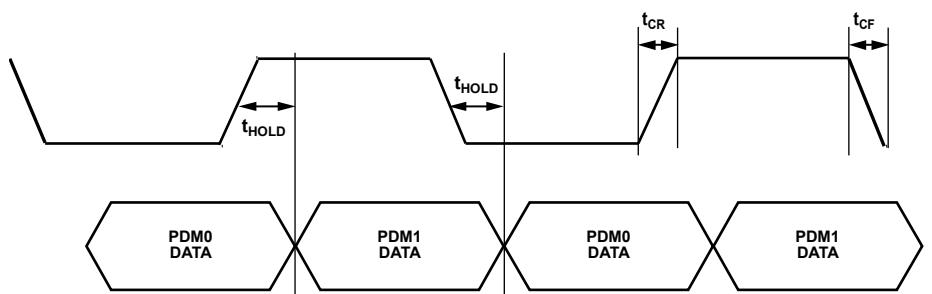

| パラメータ                                    | 限界値 |                    |     |                                        |

|------------------------------------------|-----|--------------------|-----|----------------------------------------|

|                                          | 最小値 | 最大値                | 単位  | 説明                                     |

| GENERAL-PURPOSE INPUT/OUTPUT (GPIO) PINS |     |                    |     |                                        |

| $t_{GIL}$                                |     | $1.5 \times 1/f_S$ | μs  | コアがハイまたはローの値を読み出すまでの MPx の入力遅延時間       |

| $t_{RLPW}$                               | 20  |                    | ns  | $\overline{PD}$ のロー・パルス幅               |

| DIGITAL MICROPHONE                       |     |                    |     |                                        |

| $t_{CF^1}$                               |     | 12                 | ns  | デジタル・マイクロフォン・クロックの立下がり時間               |

| $t_{CR^1}$                               |     | 14                 | ns  | デジタル・マイクロフォン・クロックの立上がり時間               |

| $t_{SETUP}$                              | 10  |                    | ns  | デジタル・マイクロフォン・データのセットアップ時間              |

| $t_{HOLD}$                               | 3   |                    | ns  | デジタル・マイクロフォン・データのホールド時間                |

| PDM OUTPUT                               |     |                    |     |                                        |

| $f_{PDM\_CLK}$                           |     | 3.072<br>6.144     | MHz | PDM のクロック周波数<br>3MHz の設定値<br>6MHz の設定値 |

| $t_{CF^1}$                               | 12  | ns                 |     | デジタル PDM クロック出力の立下がり時間                 |

| $t_{CR^1}$                               | 14  | ns                 |     | デジタル PDM クロック出力の立上がり時間                 |

| $t_{HOLD}$                               | 35  | 46                 | ns  | PDM データのホールド時間                         |

<sup>1</sup> デジタル・マイクロフォン・クロックの立上がり時間と立下がり時間は、25pF の負荷と 2mA のドライブ強度で測定されます。

## デジタル・タイミング図

20534-02

図 2. シリアル入力ポートのタイミング図

図3. シリアル出力ポートのタイミング図

20534-003

図 4. SPI ポートのタイミング図

0534-004

図 5. I<sup>2</sup>C ポートのタイミング図

20E31 00E

図 6. デジタル・マイクロフォンのタイミング図

20534-007

図 7. PDM 出力のタイミング図

20534-008

## 絶対最大定格

表 10.

| Parameter                           | Rating                 |

|-------------------------------------|------------------------|

| Power Supply (AVDD, IOVDD)          | -0.3 V to +1.98 V      |

| Digital Supply (DVDD)               | -0.3 V to +1.21 V      |

| Input Current (Except Supply Pins)  | ±20 mA                 |

| Analog Input Voltage (Signal Pins)  | -0.3 V to AVDD + 0.3 V |

| Digital Input Voltage (Signal Pins) | -0.3 to IOVDD + 0.3 V  |

| Operating Temperature Range (Case)  | -40°C to +85°C         |

| Storage Temperature Range           | -65°C to +150°C        |

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間にわたり絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

### 熱抵抗

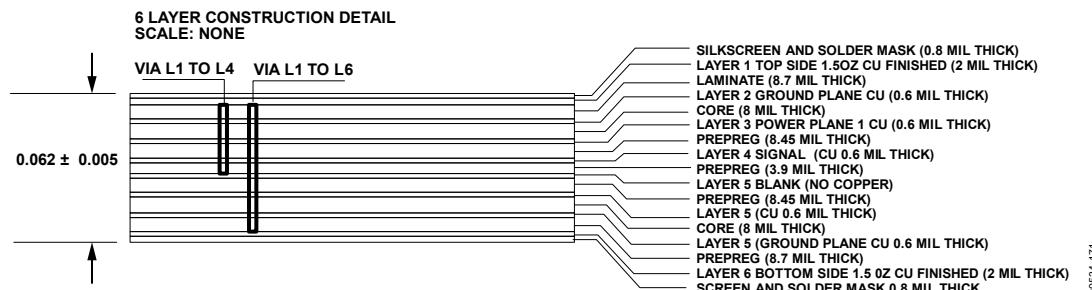

熱性能は、プリント回路基板 (PCB) の設計と動作環境に直接関連しています。PCB の熱設計には細心の注意を払う必要があります。

$\theta_{JA}$  および  $\theta_{JC}$  は、自然対流冷却下にある 4 層 PCB に関する JESD51-9 に従って決定されます。

表 11. 热抵抗

| Package Type | $\theta_{JA}^1$ | $\theta_{JC}^1$ | Unit |

|--------------|-----------------|-----------------|------|

| CB-42-2      | 46.7            | 0.3             | °C/W |

<sup>1</sup> 热抵抗のシミュレーション値は、2 つのサーマル・ピアを備えた JEDEC 2S2P サーマル・テスト・ボードに基づいています。JEDEC JESD-51 参照。

### ESD に関する注意

ESD (静電放電) の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

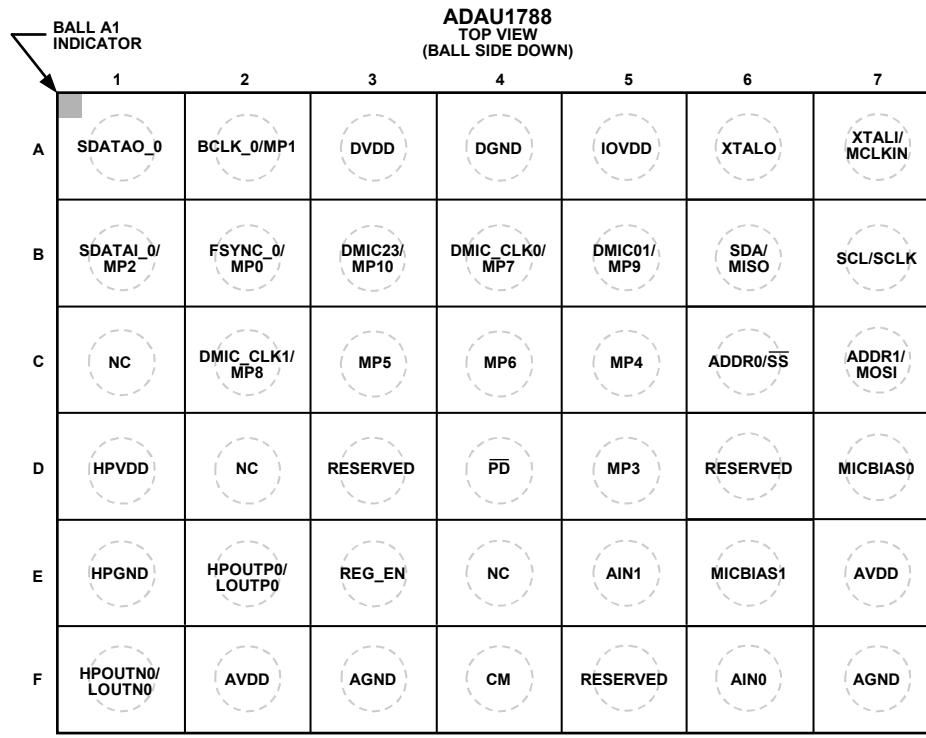

## ピン配置およびピン機能の説明

2054-009

図 8. ボール構成（上面図）

表 12. ボール機能の説明

| ボール番号 | 記号           | タイプ <sup>1</sup> | 説明                                                                                                                                                              |

|-------|--------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1    | SDATAO_0     | D_IO             | シリアル・オーディオ・ポート 0 の出力データ。                                                                                                                                        |

| A2    | BCLK_0/MP1   | D_IO             | シリアル・オーディオ・ポート 0 のビット・クロック (BCLK_0)。<br>多目的入出力 1 (MP1)。                                                                                                         |

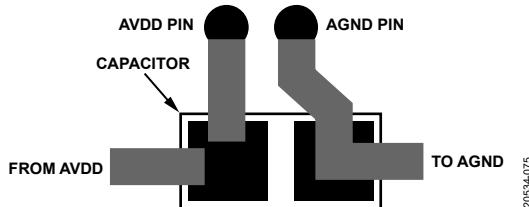

| A3    | DVDD         | PWR              | デジタル・コア電源。デジタル電源は内蔵レギュレータから生成するか、外部電源から直接供給することができます。いずれの場合も、1μF および 0.1μF のコンデンサを使用して DVDD を DGND にデカッピングします。                                                  |

| A4    | DGND         | PWR              | デジタル・グラウンド。AGND ピンと DGND ピンは、共通グラウンド・プレーン内で直接一緒に接続できます。                                                                                                         |

| A5    | IOVDD        | PWR              | デジタル入出力ピン用の電源。デジタル出力ピンは IOVDD から電力を供給されます。このピンはデジタル入力ピンにかかる最高入力電圧を設定します。このピンに流れる電流は可変です。これはこの電流はデジタル出力の負荷によって異なるためです。0.1μF のコンデンサを使用して、IOVDD を DGND にデカッピングします。 |

| A6    | XTALO        | A_OUT            | 水晶発振器クロック出力。このピンは水晶発振器アンプの出力です。このピンを使用してシステム内の他の IC にクロックを供給しないでください。                                                                                           |

| A7    | XTALI/MCLKIN | D_IN             | 水晶発振器クロック入力 (XTALI)。<br>マスター・クロック入力 (MCLKIN)。                                                                                                                   |

| ボール番号 | 記号             | タイプ <sup>1</sup> | 説明                                                                                                                                                                                                                                                              |

|-------|----------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B1    | SDATAI_0/MP2   | D_IO             | シリアル・オーディオ・ポート 0 の入力データ (SDATAI_0)。<br>多目的入出力 2 (MP2)。                                                                                                                                                                                                          |

| B2    | FSYNC_0/MP0    | D_IO             | シリアル・オーディオ・ポート 0 のフレーム同期／左右クロック (FSYNC_0)。<br>多目的入出力 0 (MP0)。                                                                                                                                                                                                   |

| B3    | DMIC23/MP10    | D_IO             | デジタル・マイクロフォンのステレオ入力 2 およびデジタル・マイクロフォンのステレオ入力 3 (DMIC23)。<br>多目的入出力 10 (MP10)。                                                                                                                                                                                   |

| B4    | DMIC_CLK0/MP7  | D_IO             | デジタル・マイクロフォン・クロック出力 0 (DMIC_CLK0)。<br>多目的入出力 7 (MP7)。                                                                                                                                                                                                           |

| B5    | DMIC01/MP9     | D_IO             | デジタル・マイクロフォンのステレオ入力 0 およびデジタル・マイクロフォンのステレオ入力 1 (DMIC01)。<br>多目的入出力 9 (MP9)。                                                                                                                                                                                     |

| B6    | SDA/MISO       | D_IO             | I <sup>2</sup> C データ (SDA)。このピンは双方オープンコレクタ入力です。このピンに接続されるラインには、2.0kΩ のプルアップ抵抗が必要です。<br>SPI データ出力 (MISO)。この SPI データ出力はレジスタとメモリ・ロケーションのリードバックに使用されます。SPI 読出しがアクティブでない場合、このピンはトライステートになります。                                                                        |

| B7    | SCL/SCLK       | D_IN             | I <sup>2</sup> C クロック (SCL)。デバイスが I <sup>2</sup> C 制御モードの場合、このピンは常にオープンコレクタ入力です。デバイスがセルフブート・モードの場合、このピンはオープンコレクタ出力 (I <sup>2</sup> C マスタ) です。このピンに接続されるラインには、2.0kΩ のプルアップ抵抗が必要です。<br>SPI クロック (SCLK)。このピンは連続的に動作させることも、SPI トランザクションと SPI トランザクションの間遮断することもできます。 |

| C1    | NC             | NC               | 接続なし。このピンは開放状態のままにします。                                                                                                                                                                                                                                          |

| C2    | DMIC_CLK1/MP8  | D_IO             | デジタル・マイクロフォン・クロック出力 1 (DMIC_CLK1)。<br>多目的入出力 8 (MP8)。                                                                                                                                                                                                           |

| C3    | MP5            | D_IO             | 多目的入出力 5 (MP5)。このピンを使用しない場合は DGND に接続します。                                                                                                                                                                                                                       |

| C4    | MP6            | D_IO             | 多目的入出力 6 (MP6)。このピンを使用しない場合は DGND に接続します。                                                                                                                                                                                                                       |

| C5    | MP4            | D_IO             | 多目的入出力 4 (MP4)。このピンを使用しない場合は DGND に接続します。                                                                                                                                                                                                                       |

| C6    | ADDR0/SS       | D_IN             | I <sup>2</sup> C アドレス 0 (ADDR0)。<br>SPI ラッチ信号(SS)。このピンは SPI トランザクションの開始時にローになり、トランザクションの終了時にハイになる必要があります。各 SPI トランザクションの完了までの SCLK サイクル数は、SPI トランザクションの開始時に送信されるアドレスと読出し／書込みビットによって異なります。                                                                       |

| C7    | ADDR1/MOSI     | D_IN             | I <sup>2</sup> C アドレス 1 (ADDR1)。<br>SPI データ入力 (MOSI)。                                                                                                                                                                                                           |

| D1    | HPVDD          | PWR              | ヘッドフォン・アンプの電源 (1.8V アナログ電源)。0.1μF のコンデンサを使用して、このピンを HPGND にデカッピングします。ヘッドフォン出力の駆動に必要な大きな電流を供給するには、このピンへの PCB パターンを広くする必要があります。                                                                                                                                   |

| D2    | NC             | NC               | 接続なし。このピンは開放状態のままにします。                                                                                                                                                                                                                                          |

| D3    | RESERVED       | D_IN             | 内部使用に限定。このピンは DGND に接続します。                                                                                                                                                                                                                                      |

| D4    | PD             | D_IN             | アクティブ・ローのパワーダウン。全てのデジタル回路とアナログ回路がパワーダウンします。このピンには内部ブルダウン抵抗が接続されています。したがって、電源ピンに電力が印加されている間に入力信号がフロート状態になると、ADAU1788 はパワーダウン・モードに保たれます。                                                                                                                          |

| D5    | MP3            | D_IO             | 多目的入出力 3。このピンを使用しない場合は DGND に接続します。                                                                                                                                                                                                                             |

| D6    | RESERVED       | D_IN             | 内部使用に限定。このピンは DGND に接続します。                                                                                                                                                                                                                                      |

| D7    | MICBIAS0       | A_OUT            | エレクトレット・マイクロフォン 0 のバイアス電圧。このピンは 1μF のコンデンサを使用してデカッピングします。                                                                                                                                                                                                       |

| E1    | HPGND          | PWR              | ヘッドフォン・アンプのグラウンド。                                                                                                                                                                                                                                               |

| E2    | HPOUTP0/LOUTP0 | A_OUT            | ヘッドフォン出力非反転チャンネル 0 (HPOUTP0)。<br>ライン出力非反転チャンネル 0 (LOUTP0)。                                                                                                                                                                                                      |

| E3    | REG_EN         | A_IN             | レギュレータ・イネーブル。このピンを AVDD に接続するとレギュレータはイネーブルになり、このピンをグランドに接続するとレギュレータはディスエーブルになります。                                                                                                                                                                               |

| E4    | NC             |                  | 接続なし。このピンは開放状態のままにします。                                                                                                                                                                                                                                          |

| E5    | AIN1           | A_IN             | ADC1 の入力。                                                                                                                                                                                                                                                       |

| E6    | MICBIAS1       | A_OUT            | エレクトレット・マイクロフォン 1 のバイアス電圧。このピンは 1μF のコンデンサを使用してデカッピングします。                                                                                                                                                                                                       |

| ボール番号 | 記号             | タイプ <sup>1</sup> | 説明                                                                                                                                                                                                                |

|-------|----------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E7    | AVDD           | PWR              | 1.8V アナログ電源。0.1 $\mu$ F のコンデンサを使用して、このピンを AGND にデカップリングします。                                                                                                                                                       |

| F1    | HPOUTN0/LOUTN0 | A_OUT            | ヘッドフォン出力非反転チャンネル 0 (HPOUTP0)。<br>ライン出力非反転チャンネル 0 (LOUTP0)。                                                                                                                                                        |

| F2    | AVDD           | PWR              | 1.8V アナログ電源。0.1 $\mu$ F のコンデンサを使用して、AVDD を AGND にデカップリングします。                                                                                                                                                      |

| F3    | AGND           | PWR              | アナログ・グラウンド。AGND ピンと DGND ピンは、共通グラウンド・プレーン内で直接一緒に接続できます。                                                                                                                                                           |

| F4    | CM             | A_OUT            | コモンモード・リファレンス（公称値 0.85V に固定）。このピンと AGND の間に 10 $\mu$ F と 0.1 $\mu$ F のデカップリング・コンデンサを接続して、ADC と DAC の間のクロストークを低減できます。コンデンサの材料は重要ではありません。外部アナログ回路に CM からの電流が流れていません（例えば、オペアンプの非反転入力）、このピンはその外部アナログ回路をバイアスすることができます。 |

| F5    | RESERVED       | A_IN             | 内部使用に限定。このピンは CM に接続します。                                                                                                                                                                                          |

| F6    | AIN0           | A_IN             | ADC0 の入力。                                                                                                                                                                                                         |

| F7    | AGND           | PWR              | アナログ・グラウンド。                                                                                                                                                                                                       |

<sup>1</sup> D\_IO はデジタル入出力、PWR は電源、A\_OUT はアナログ出力、D\_IN はデジタル入力、NC は接続なし、A\_IN はアナログ入力を意味します。

## 代表的な性能特性

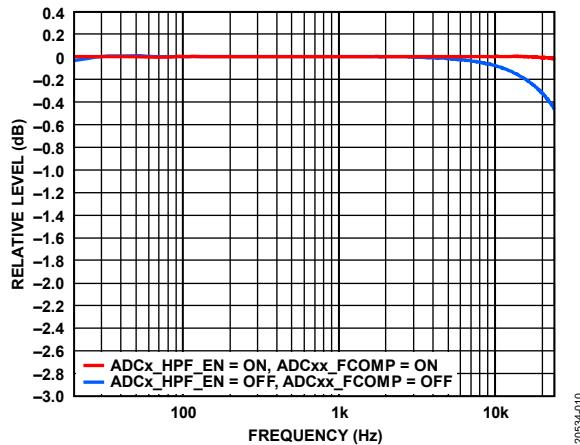

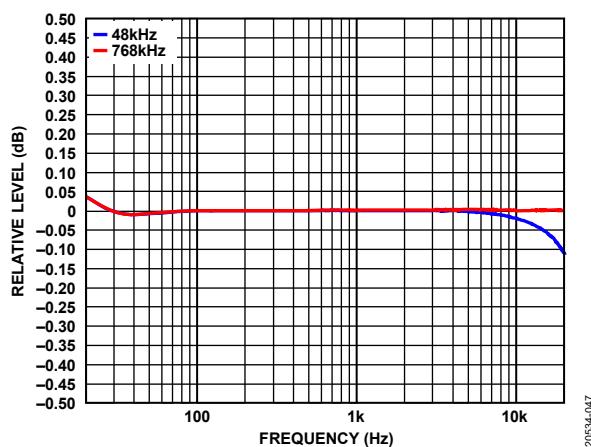

図 9. 周波数応答、 $f_s = 48\text{kHz}$ 、 $-20\text{dBV}$  入力、

信号経路 =  $\text{AINx} \sim \text{SDATAO}_0$ 、PGA なし

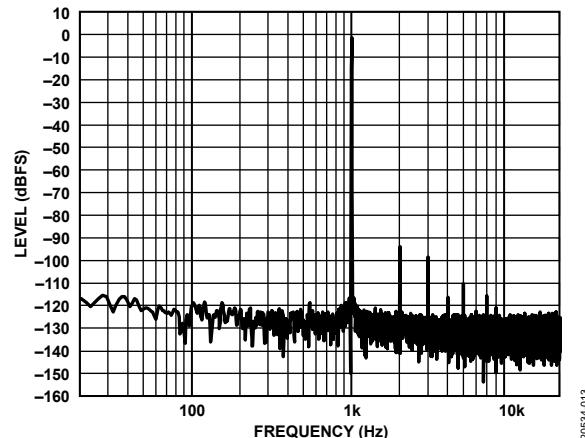

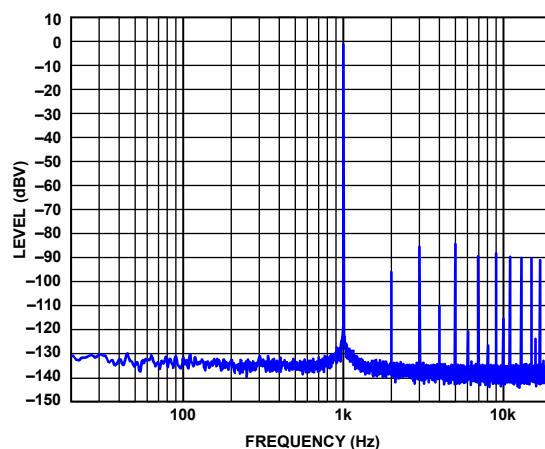

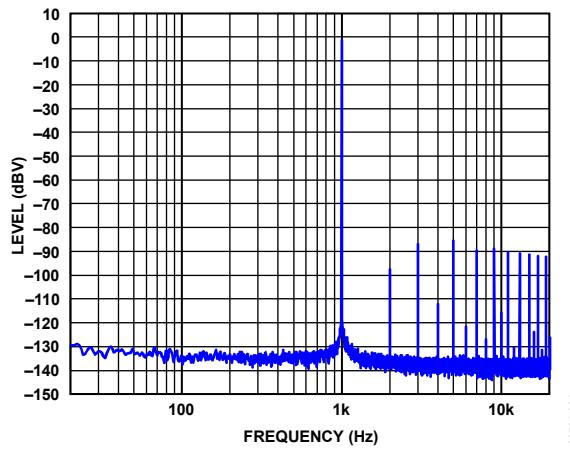

図 12. 高速フーリエ変換(FFT)、 $-7\text{dBV}$  入力、 $-1\text{dBFS}$  出力、

$f_s = 48\text{kHz}$ 、信号経路 =  $\text{AINx} \sim \text{SDATAO}_0$ 、PGA なし

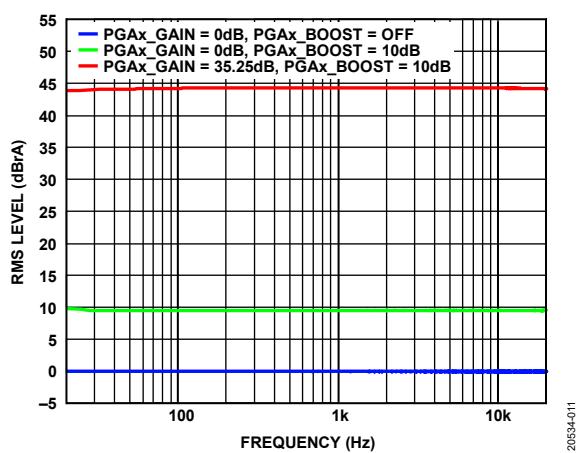

図 10. 周波数応答、 $f_s = 48\text{kHz}$ 、信号経路 =  $\text{AINx} \sim \text{SDATAO}_0$ 、

出力は PGA ゲイン設定値を基準とする

(0dB/10dB/35.25dB + 10dB ブースト)

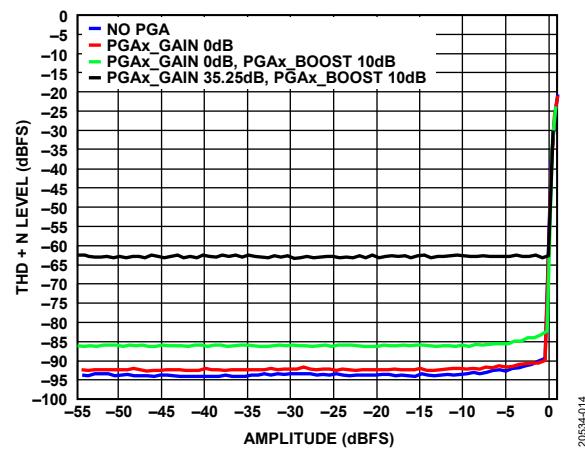

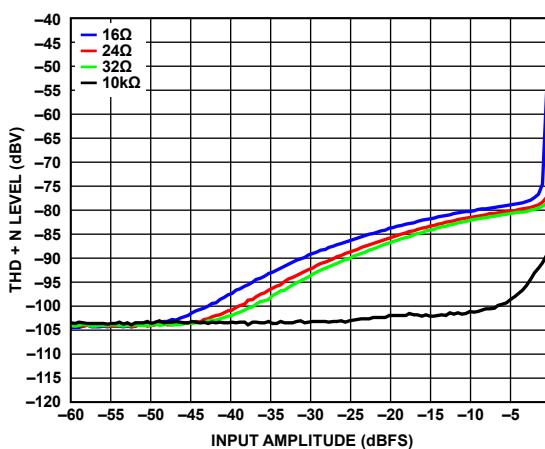

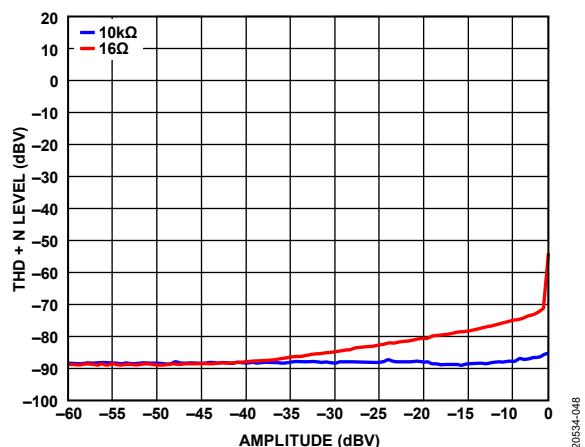

図 13. THD + N レベルと振幅の関係、 $f_s = 48\text{kHz}$ 、

信号経路 =  $\text{AINx} \sim \text{SDATAO}_0$

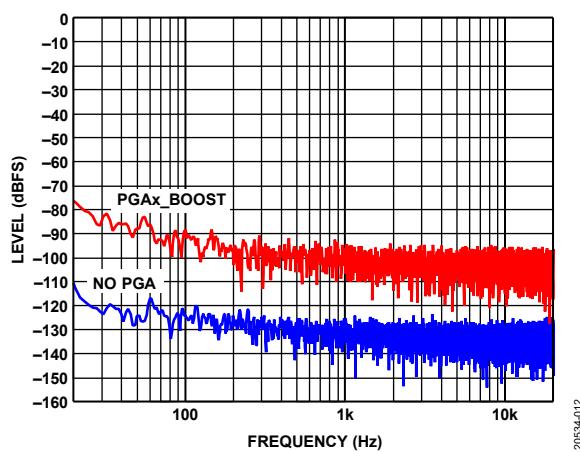

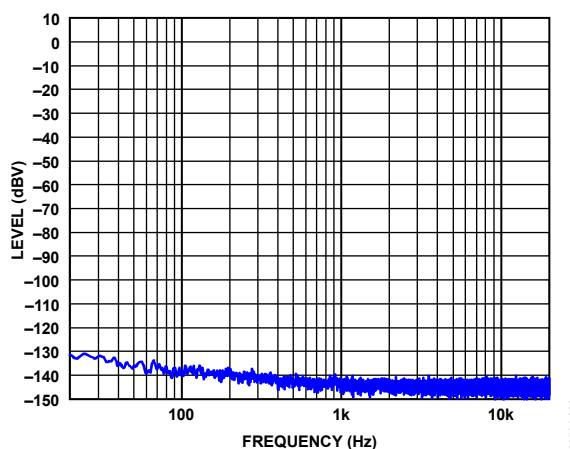

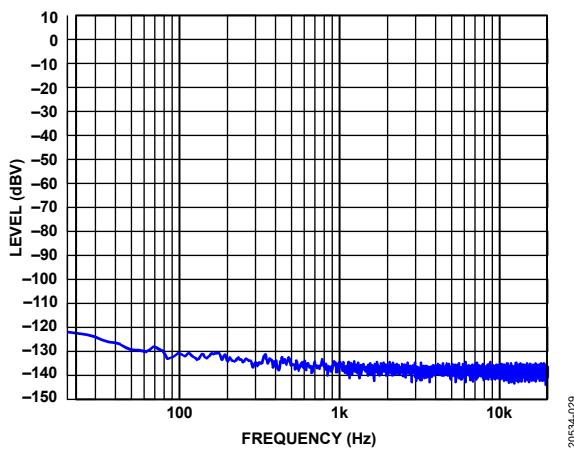

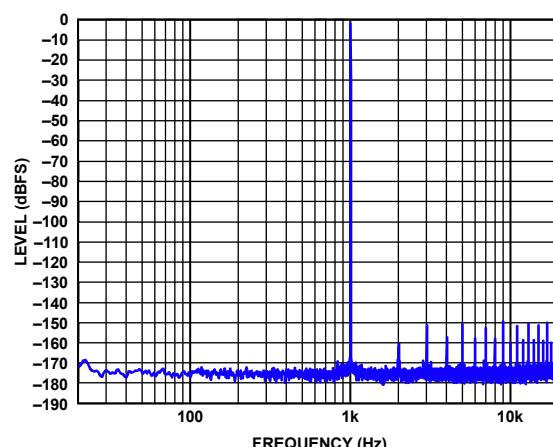

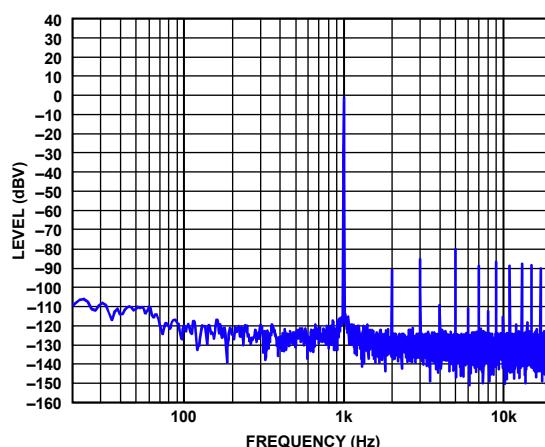

図 11. FFT、信号なし、 $f_s = 48\text{kHz}$ 、

信号経路 =  $\text{AINx} \sim \text{SDATAO}_0$ 、PGA なしおよび

35.25dB PGAx\_GAIN + 10dB PGAx\_BOOST

図 14. 周波数応答、 $f_s = 48\text{kHz}$ 、信号経路 =  $\text{SDATAI}_0 \sim \text{PDM}$  出力

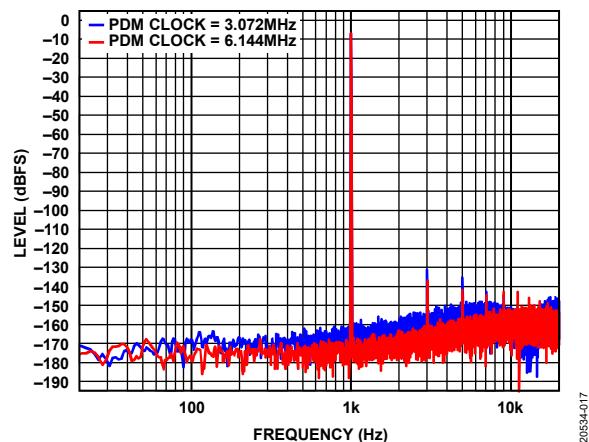

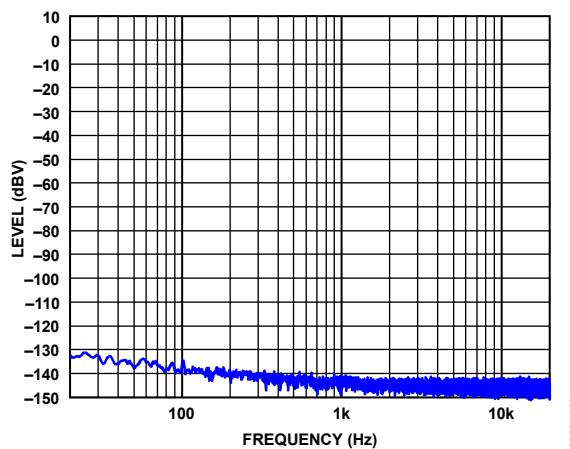

図 15. FFT、信号なし、 $f_s = 48\text{kHz}$ （全体を通して）、

信号経路 = SDATAI\_0～FastDSP～PDM 出力

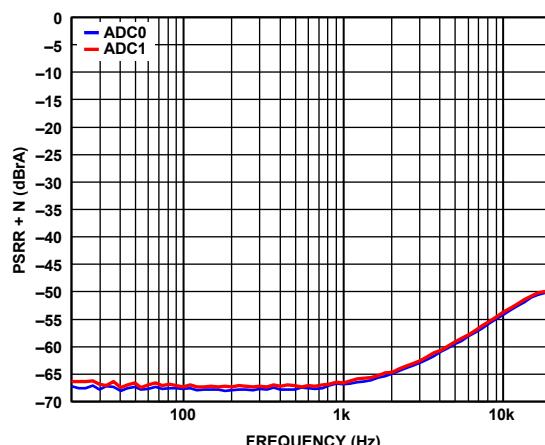

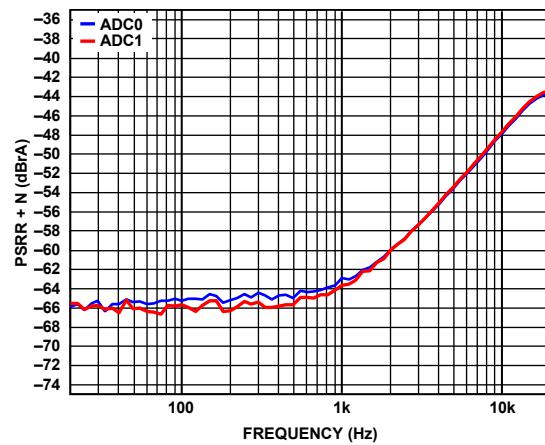

図 18. PSRR + N、信号経路 = AINx～SDATAO\_0、 $f_s = 48\text{kHz}$ 、

AVDD に 100mVp-p のリップル入力、

PGA = 0dB (0dBra = -23.3dBFS)

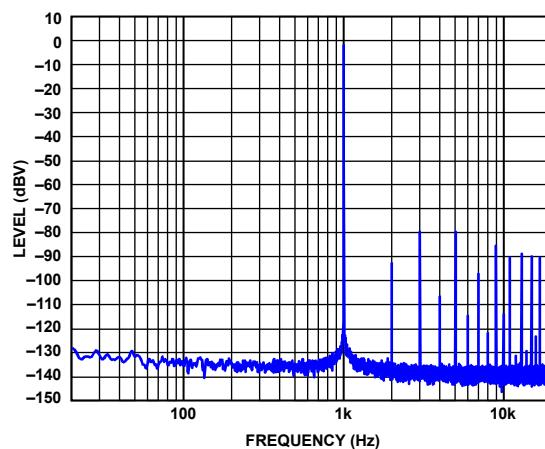

図 16. FFT、-7dBFS、 $f_s = 48\text{kHz}$ （全体を通して）、

信号経路 = SDATAI\_0～FastDSP～PDM 出力

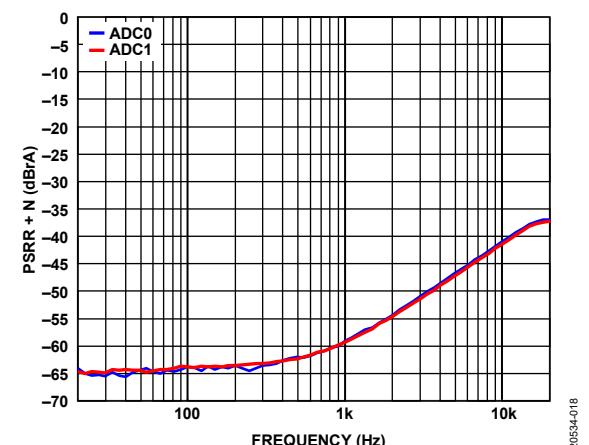

図 19. PSRR + N、信号経路 = AINx～SDATAO\_0、 $f_s = 48\text{kHz}$ 、

AVDD に 100mVp-p のリップル入力、

PGA = 10dB (0dBra = -23.3dBFS)

図 17. PSRR + N、信号経路 = AINx～SDATAO\_0、 $f_s = 48\text{kHz}$ 、

AVDD に 100mVp-p のリップル入力、

PGA なし (0dBra = -23.3dBFS)

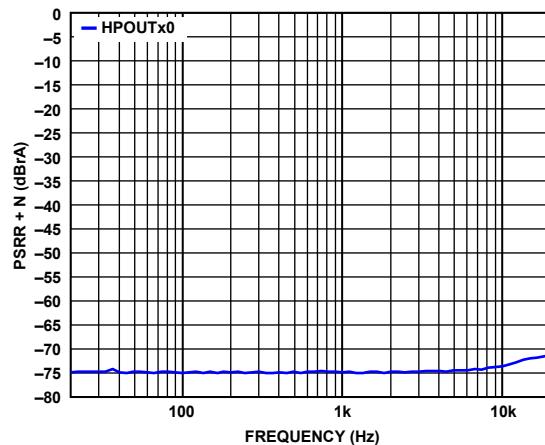

図 20. PSRR + N、信号経路 = SDATAI\_0～HPOUTx0、

$f_s = 48\text{kHz}$ 、AVDD に 100mVp-p のリップル入力

(0dBra = -29dBV)

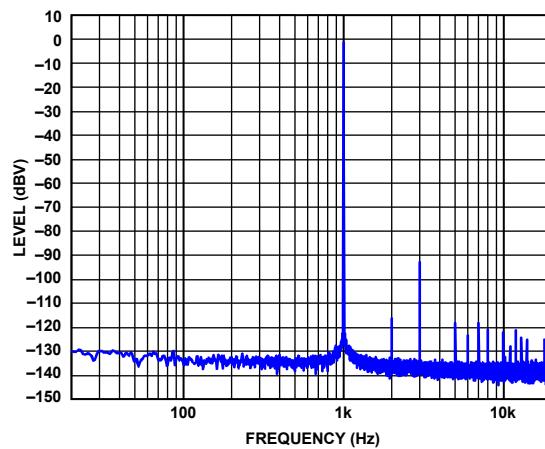

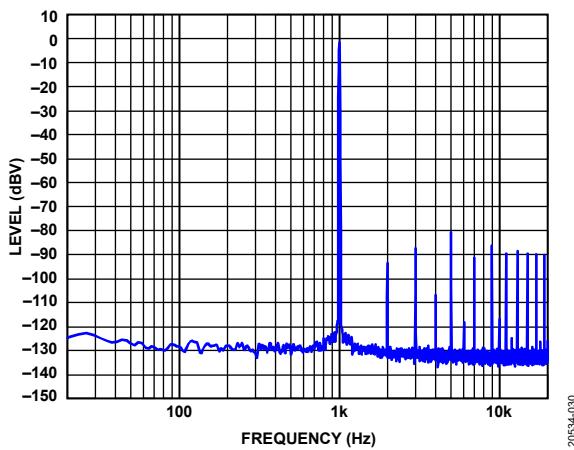

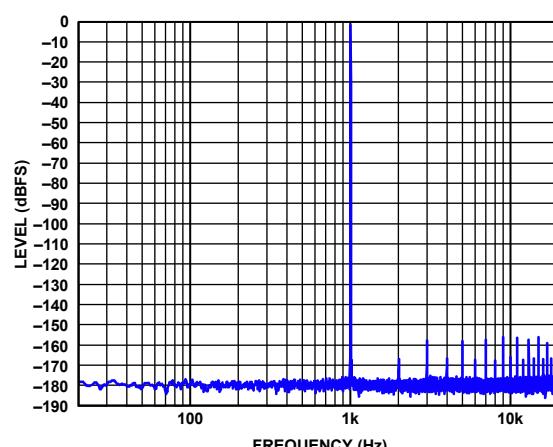

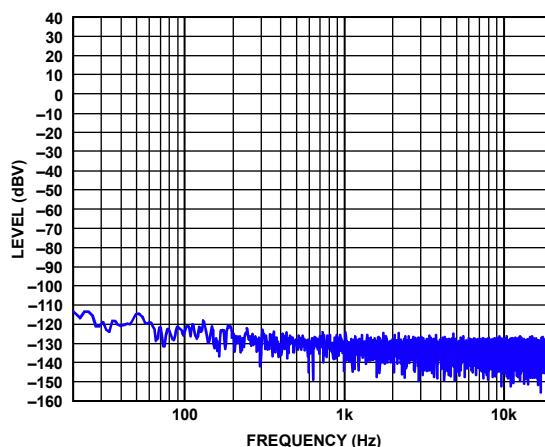

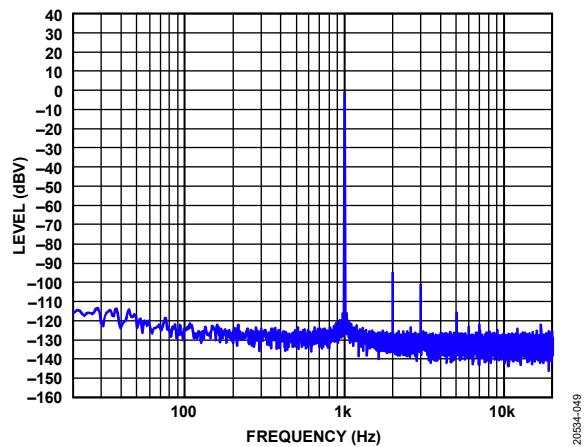

図 21. FFT、信号なし、 $f_s = 48\text{kHz}$ 、信号経路 = SDATAI\_0～HPOUTx0、ヘッドフォン・モード、負荷 =  $16\Omega$

図 24. FFT、-1dBFS、 $f_s = 48\text{kHz}$ 、信号経路 = SDATAI\_0～HPOUTx0、ヘッドフォン・モード、負荷 =  $24\Omega$

図 22. FFT、信号なし、 $f_s = 48\text{kHz}$ 、信号経路 = SDATAI\_0～LOUTx0、ライン出力モード、負荷 =  $10\text{k}\Omega$

図 25. FFT、-1dBFS、 $f_s = 48\text{kHz}$ 、信号経路 = SDATAI\_0～HPOUTx0、ヘッドフォン・モード、負荷 =  $16\Omega$

図 23. FFT、-1dBFS、 $f_s = 48\text{kHz}$ 、信号経路 = SDATAI\_0～HPOUTx0、ヘッドフォン・モード、負荷 =  $32\Omega$

図 26. FFT、-1dBFS、 $f_s = 48\text{kHz}$ 、信号経路 = SDATAI\_0～LOUTx0、ライン出力モード、負荷 =  $10\text{k}\Omega$

図 27. FFT、信号なし、 $f_s = 768\text{kHz}$ 、信号経路 = SDATAI\_0～インターポレータ～FastDSP～HPOUTx0、ヘッドフォン・モード、負荷 =  $16\Omega$

図 30. FFT、-1dBFS、 $f_s = 768\text{kHz}$ 、信号経路 = SDATAI\_0～インターポレータ～FastDSP～LOUTx0、ライン出力モード、負荷 =  $10\text{k}\Omega$

図 28. FFT、信号なし、 $f_s = 768\text{kHz}$ 、信号経路 = SDATAI\_0～インターポレータ～FastDSP～LOUTx0、ライン出力モード、負荷 =  $10\text{k}\Omega$

図 31. THD + N レベルと入力振幅の関係、 $f_s = 48\text{kHz}$ 、 $16\Omega$ 、 $24\Omega$ 、 $32\Omega$ 、または  $10\text{k}\Omega$ 、信号経路 = SDATAI\_0～HPOUTx0/LOUTx0

図 29. FFT、-1dBFS、 $f_s = 768\text{kHz}$ 、信号経路 = SDATAI\_0～インターポレータ～FastDSP～HPOUTx0、ヘッドフォン・モード、負荷 =  $16\Omega$

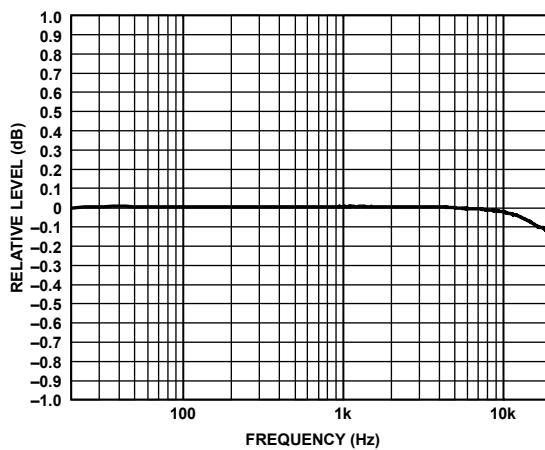

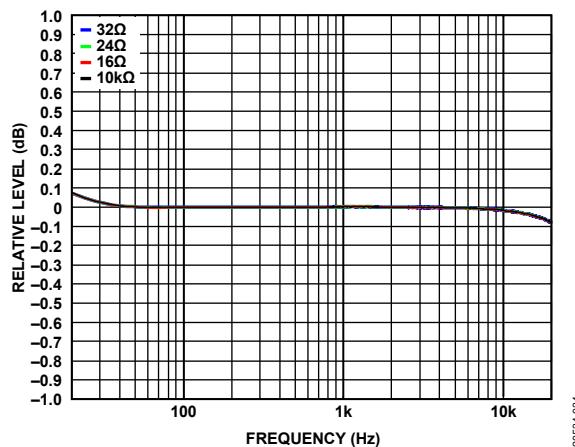

図 32. 相対レベルと周波数の関係、 $f_s = 48\text{kHz}$ 、信号経路 = SDATAI\_0～HPOUTx0/LOUTx0、 $16\Omega$  または  $10\text{k}\Omega$

図 33. 相対レベルと周波数の関係、 $f_s = 768\text{kHz}$ 、信号経路 = SDATAI\_0～インターポレータ～FastDSP～HPOUTx0/LOUTx0、 $16\Omega \sim 10k\Omega$

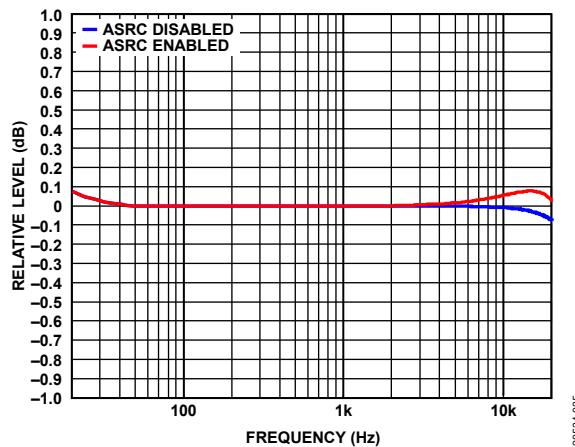

図 34. 相対レベルと周波数の関係、 $f_s = 48\text{kHz}$ （全体を通して、FastDSP = 768kHz を除く）、信号経路 = SDATAI\_0～ASRCI～SigmaDSP～インターポレータ～FastDSP～デシメータ～ASRCO～SDATAO\_0

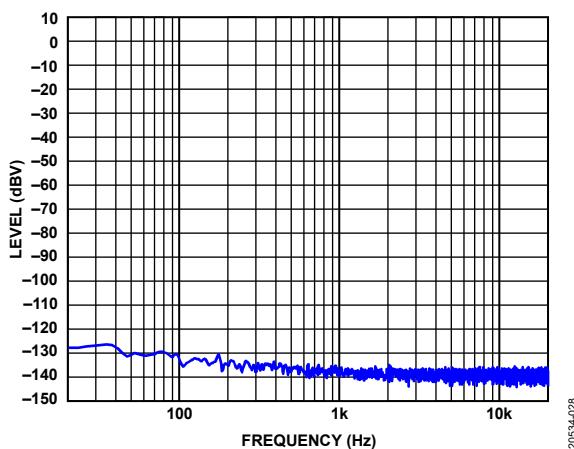

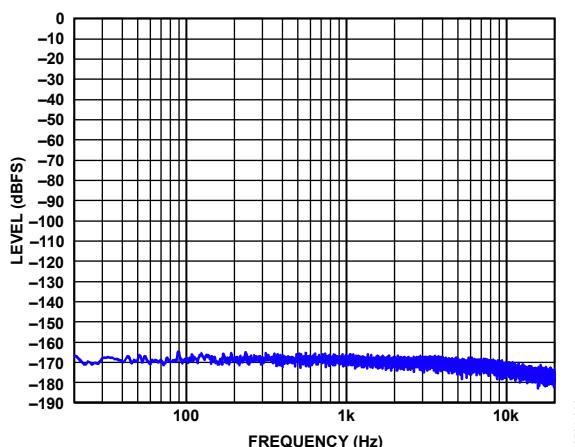

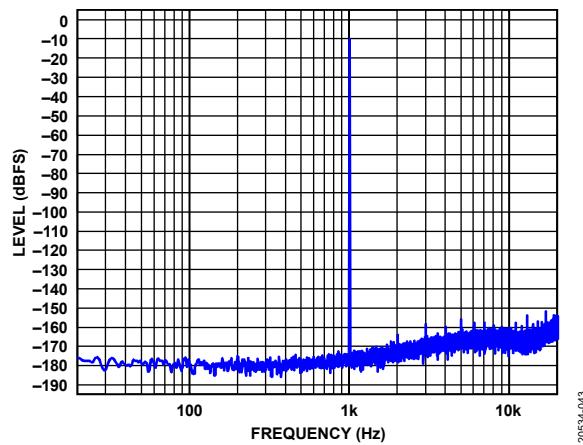

図 35. FFT、信号なし、 $f_s = 48\text{kHz}$ （全体を通して、FastDSP = 768kHz を除く）、信号経路 = SDATAI\_0～ASRCI～SigmaDSP～インターポレータ～FastDSP～デシメータ～ASRCO～SDATAO\_0

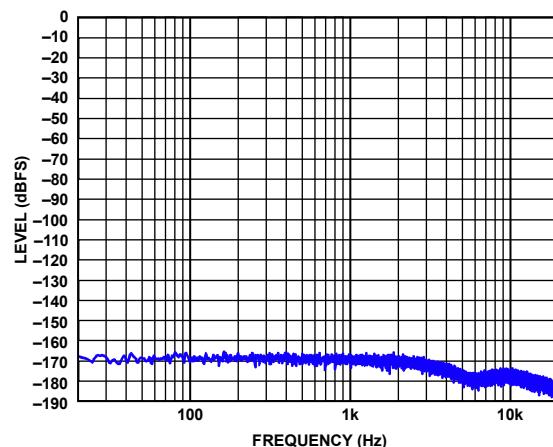

図 36. FFT、信号なし、 $f_s = 48\text{kHz}$ （全体を通して、FastDSP = 768kHz を除く）、信号経路 = SDATAI\_0～SigmaDSP～インターポレータ～FastDSP～デシメータ～SDATAO\_0

図 37. FFT、-1dBFS、 $f_s = 48\text{kHz}$ （全体を通して、FastDSP = 768kHz を除く）、信号経路 = SDATAI\_0～ASRCI～SigmaDSP～インターポレータ～FastDSP～デシメータ～ASRCO～SDATAO\_0

図 38. FFT、-1dBFS、 $f_s = 48\text{kHz}$ （全体を通して、FastDSP = 768kHz を除く）、信号経路 = SDATAI\_0～SigmaDSP～インターポレータ～FastDSP～デシメータ～SDATAO\_0

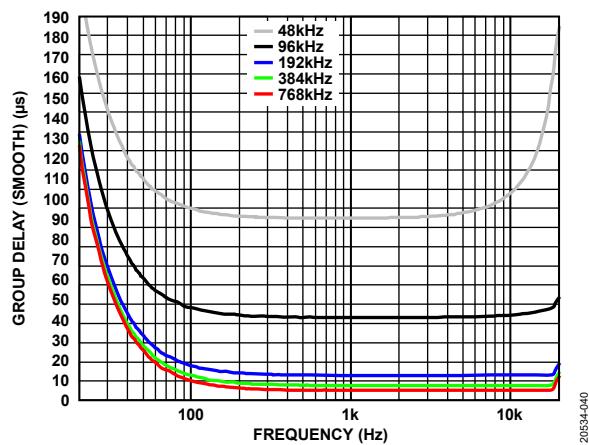

図 39. 群遅延（スムージング）と周波数の関係、 $f_s = 192\text{kHz} \sim 768\text{kHz}$ 、信号経路 = AINx～FastDSP～HPOUTx0/LOUTx0

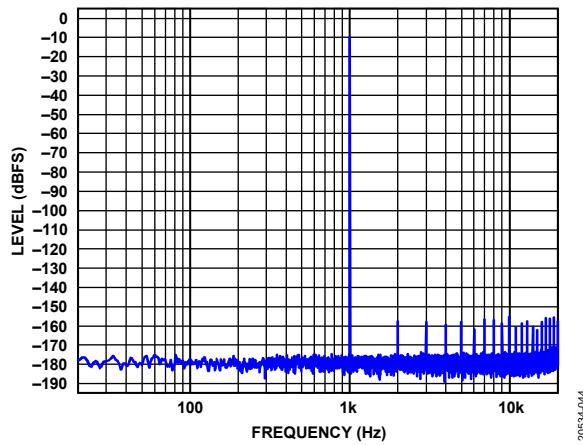

図 42. FFT、-10dBFS、DMIC\_CLKx\_RATE = 3.072MHz、信号経路 = DMICxx～SDATAO\_0

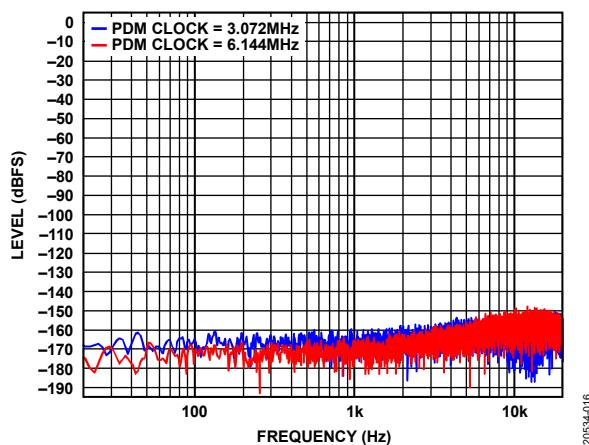

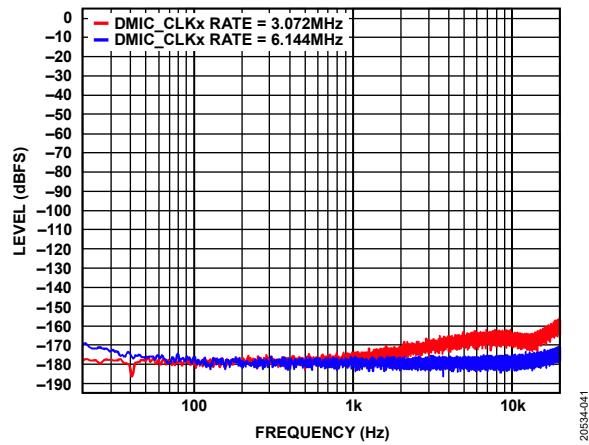

図 40. FFT、信号なし、DMIC\_CLKx\_RATE = 3.072MHz～6.144MHz、信号経路 = DMICxx～SDATAO\_0

図 43. FFT、-10dBFS、DMIC\_CLKx\_RATE = 3.072MHz、信号経路 = DMICxx～SDATAO\_0

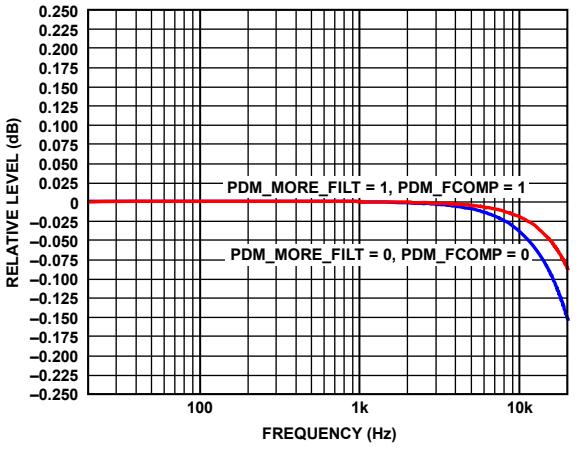

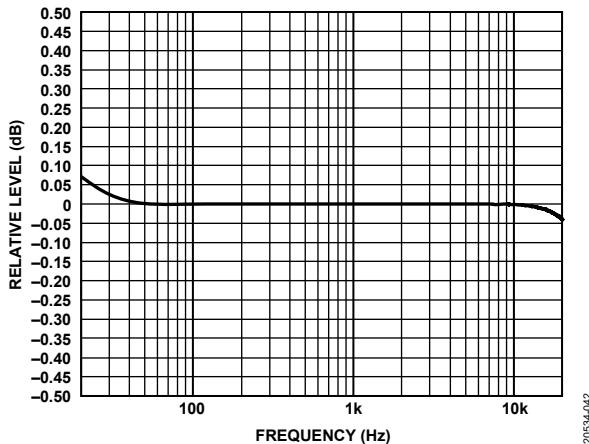

図 41. 相対レベルと周波数の関係、DMIC\_CLKx\_RATE = 3.072MHz～6.144MHz、信号経路 = DMICxx～SDATAO\_0

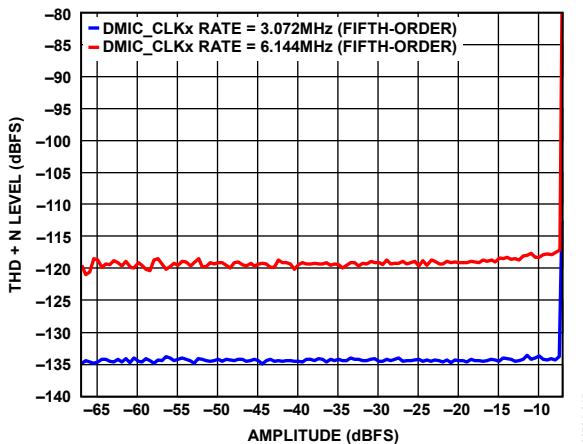

図 44. THD + N レベルと振幅の関係、-10dBFS、DMIC\_CLKx\_RATE = 3.072MHz～6.144MHz、信号経路 = DMICxx～SDATAO\_0

図 45. 相対レベルと周波数の関係、ヘッドフォン／ライン出力モード、負荷 =  $16\Omega$ ～ $10k\Omega$ 、 $f_s = 48\text{kHz}$  および  $768\text{kHz}$ 、信号経路 = AIN0～DAC0

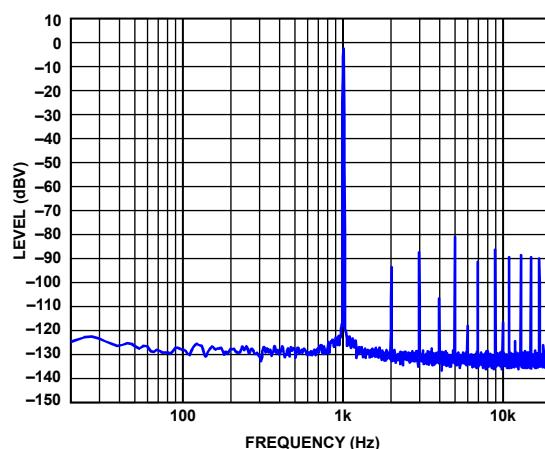

図 48. FFT、 $-1\text{dBV}$ 、ヘッドフォン・モード、負荷 =  $16\Omega$ 、 $f_s = 48\text{kHz}$ ～ $768\text{kHz}$ 、信号経路 = AINx～HPOUTx0

図 46. THD + N レベルと振幅の関係、 $f_s = 48\text{kHz}$ ～ $768\text{kHz}$ 、負荷 =  $10k\Omega$  および  $16\Omega$ 、信号経路 = AINx～HPOUTx0/LOUTx0

図 49. FFT、信号なし、負荷 =  $16\Omega$ ～ $10k\Omega$ 、 $f_s = 48\text{kHz}$ ～ $768\text{kHz}$ 、信号経路 = AINx～HPOUTx0/LOUTx0

図 47. FFT、 $-1\text{dBV}$ 、ライン出力モード、負荷 =  $10k\Omega$ 、 $f_s = 48\text{kHz}$ ～ $768\text{kHz}$ 、信号経路 = AIN0～LOUTx0

## システムのブロック図

図 50. アナログ・マイクロフォンを搭載した ADAU1788 システムのブロック図（セルフブート・モード）

## 動作原理

ADAU1788 は、最適化されたオーディオ処理コアを搭載した低消費電力のオーディオ・コーデックであり、高品質オーディオ、低消費電力、小さいサイズ、低遅延を必要とするノイズ・キャンセリング・アプリケーションに最適です。このデバイスの ADC 2 チャンネルと DAC 1 チャンネルは、それぞれ S/N 比が 96dB 以上、THD + N レベルが-88dB 以上です。シリアル・オーディオ・ポートは、I<sup>2</sup>S、左揃え、右揃え、および TDM の各モードと互換性があり、デジタル・オーディオ・データとのインターフェース用にトライステートにすることができます。動作電圧は 1.8V で、デジタル電源電圧を発生する内蔵レギュレータを使用します。必要に応じてこのレギュレータをパワーダウンし、外部から電圧を供給できます。

入力信号経路は柔軟な構成が可能であり、シングルエンドのアナログ・マイクロフォン入力と最大 8 つのデジタル・マイクロフォン入力を受け入れます。2 本のマイクロフォン・バイアス・ピンにより、エレクトレット・マイクロフォンとのシームレスなインターフェースが可能です。各入力信号にはボリューム調整用の PGA があります。

ADC と DAC は、12kHz～768kHz の範囲で選択可能なサンプリング・レートで動作する、高品質 24 ビット Σ-Δ コンバータです。ADC と DAC では、オプションのハイパス・フィルタを使用して、1Hz のカットオフ周波数と細かいステップのデジタル・ソフト・ボリューム制御が得られます。モノ DAC 出力は、インピーダンスが 16Ω 以上のヘッドフォン・イヤピース・スピーカを差動駆動できます。出力の負荷が軽い場合は、オプションによりライン出力モードに変更できます。

SigmaDSP コアは低消費電力オーディオ処理に最適化されています。このコアは、アナログ・デバイセズの SigmaStudio® ソフトウェアを使用して GUI 画面でプログラムできます。このソフトウェアには、フィルタ、ダイナミ

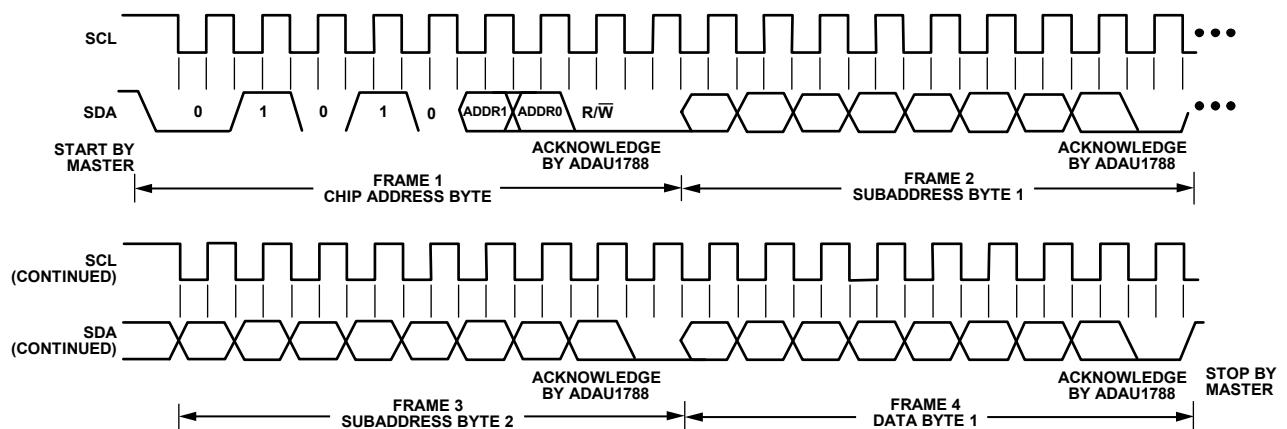

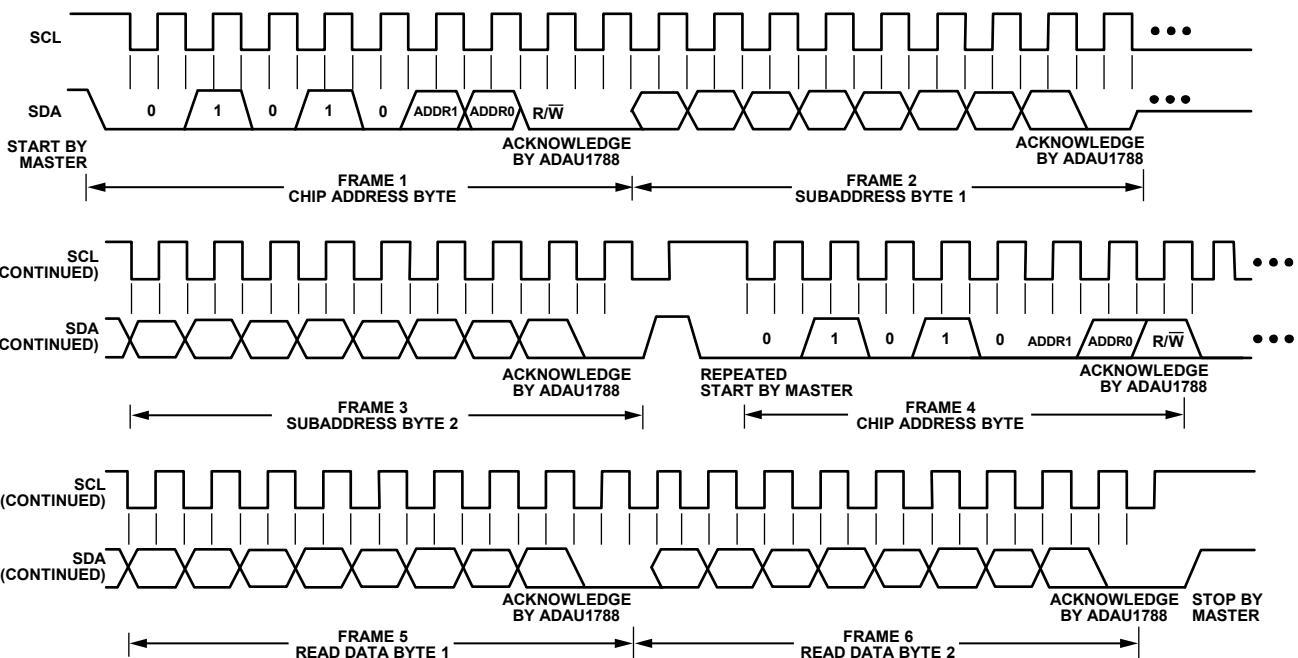

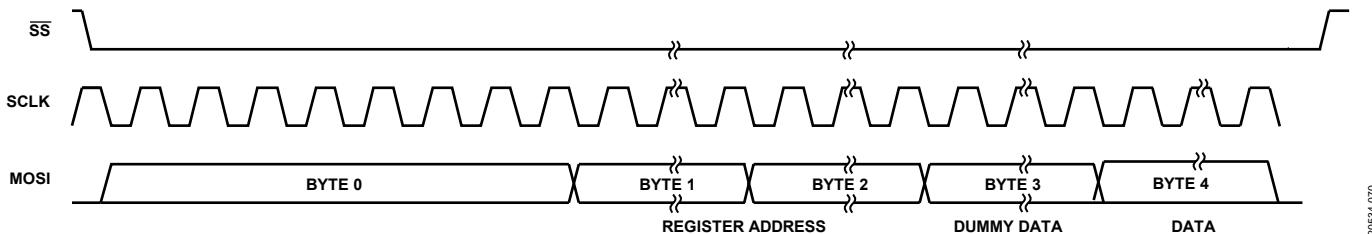

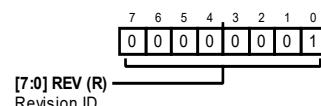

クス・プロセッサ、ミキサー、低レベル DSP 機能などのオーディオ処理ブロックのライブラリが含まれており、カスタム信号フローを GUI 画面で迅速に開発できます。