## 特長

内部クロック速度：400MSPS

14ビットDAC内蔵

プログラマブルな位相／振幅ディザリング

32ビット同調ワード

1kHzオフセット（DAC出力）で位相ノイズ $\leq -120$ dBc/Hz

優れた動的性能

160MHz（ $\pm 100$ kHzオフセット）A<sub>OUT</sub>で $>80$ dB SFDR

シリアルI/O制御

超高速アナログ・コンパレータ

自動リニア／ノンリニア周波数掃引機能

4つの周波数／位相オフセット・プロファイル

電源：1.8V

ソフトウェア／ハードウェア制御のパワーダウン

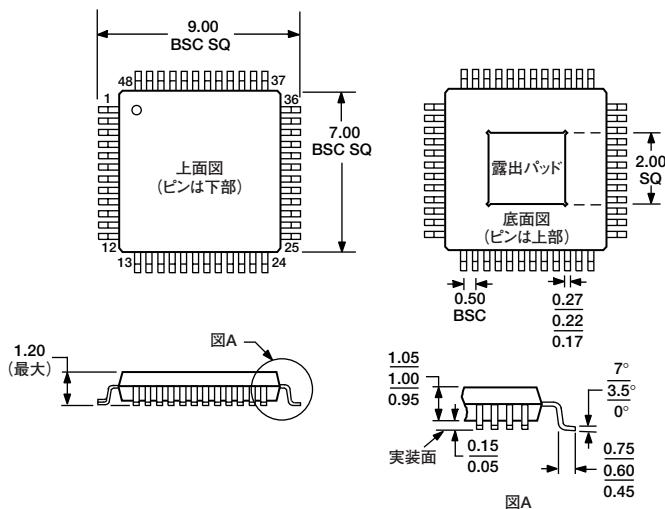

48ピンTQFP/EPパッケージ

1024ワード×32ビットRAM内蔵

多くのデジタル入力で5V入力レベルに対応

PLL REFCLK乗算器（4X～20X）

内部発振器（単一水晶発振器で駆動可能）

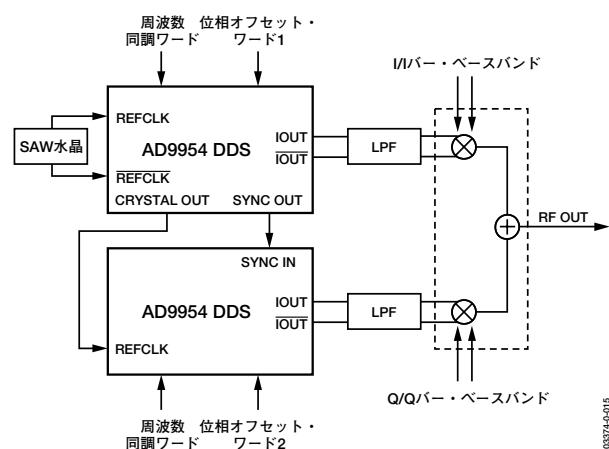

位相変調機能

マルチチップ同期

## アプリケーション

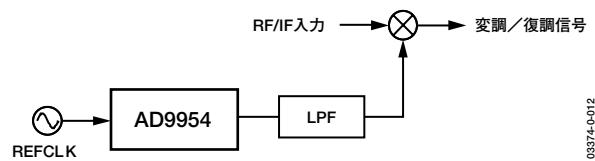

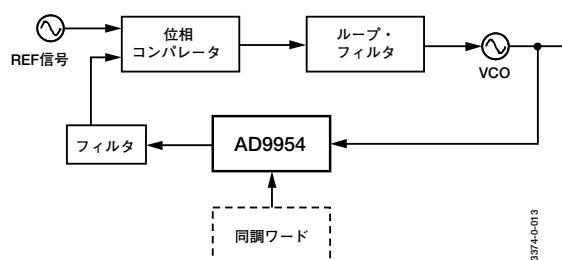

即応LO周波数合成

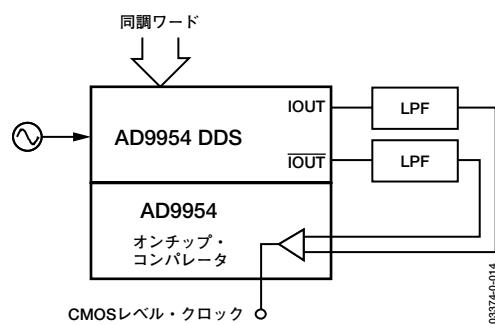

プログラマブルなクロック発振器

レーダー／スキャン・システム向けのFMチャーブ源

車載用レーダー<sup>1</sup>

テスト／測定機器

音響・光学デバイス・ドライバ

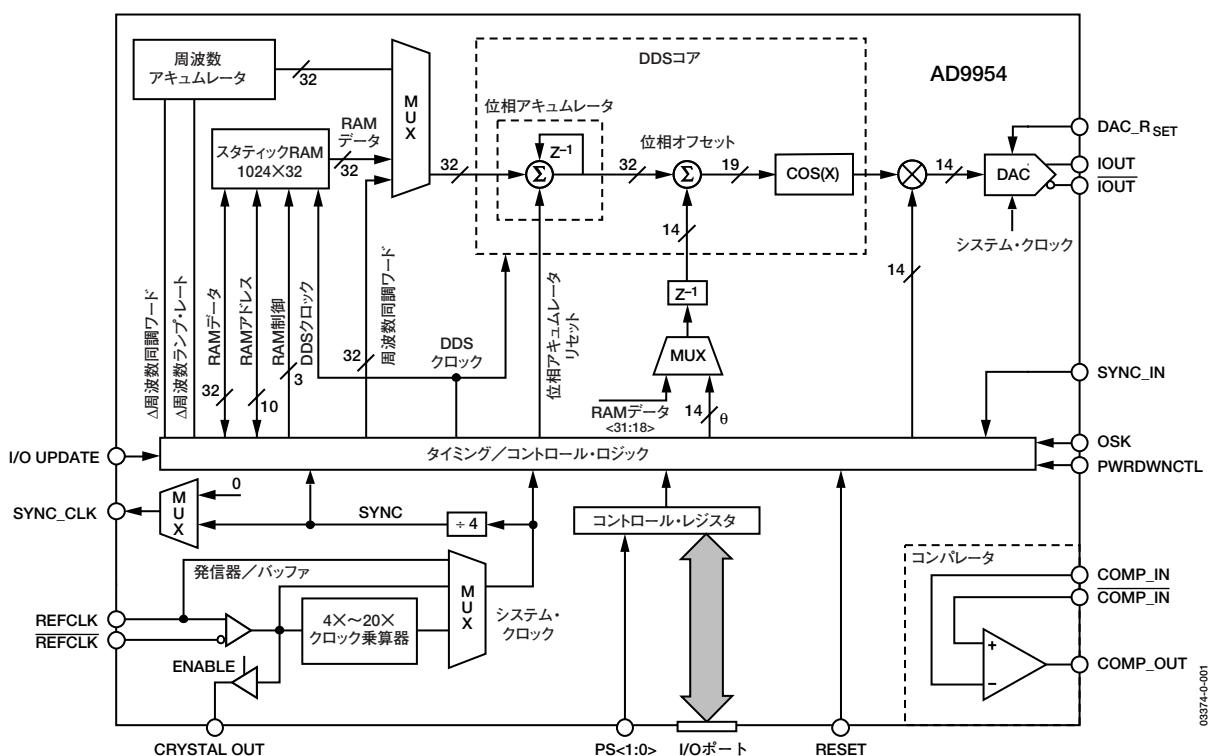

## 機能ブロック図

図1. 48ピンTQFP/EP

03374-0-001

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。本紙記載の商標および登録商標は、各社の所有に属します。

※日本語データシートはREVISIONが古い場合があります。最新の内容については、英語版をご参照ください。

© 2003 Analog Devices, Inc. All rights reserved.

REV. 0

# AD9954

## 目次

---

|                         |    |

|-------------------------|----|

| 概要                      | 3  |

| AD9954 — 電気的仕様          | 4  |

| 絶対最大定格                  | 7  |

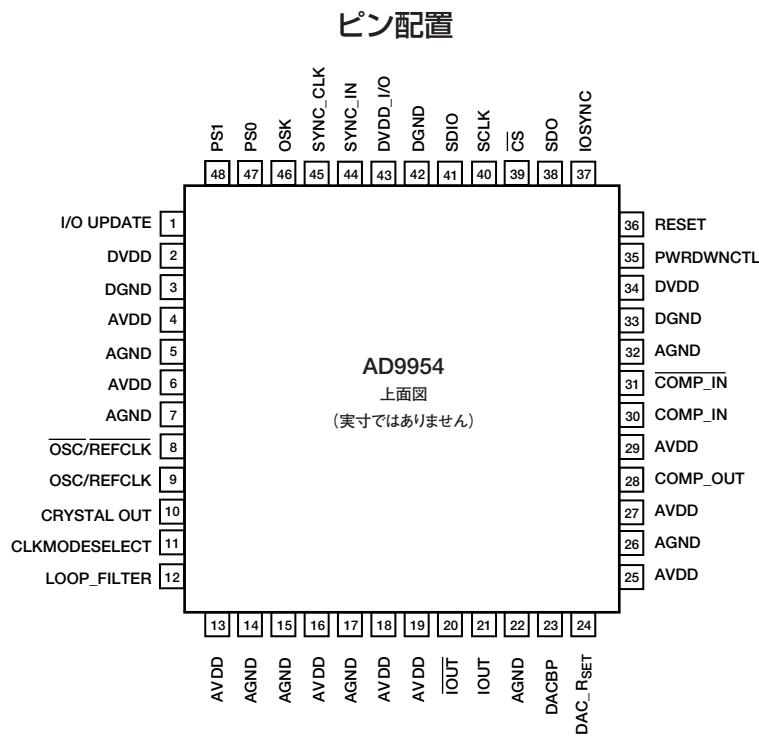

| ピン配置                    | 8  |

| ピン機能の説明                 | 9  |

| 代表的な性能特性                | 10 |

| 動作原理                    | 13 |

| コンポーネント・ブロック            | 13 |

| 動作モード                   | 22 |

| シリアル・ポート動作              | 30 |

| 命令バイト                   | 32 |

| シリアル・インターフェース・ポート・ピンの説明 | 32 |

| MSB/LSB転送               | 32 |

| シリアル・ポートによるRAM I/O      | 32 |

| 推奨アプリケーション回路            | 35 |

| 外形寸法                    | 36 |

| ESDに関する注意               | 36 |

| オーダー・ガイド                | 36 |

## 改訂履歴

リビジョン0：初版

## 概要

AD9954は、最高400MSPSで動作する14ビットDACを備えたDDS（ダイレクト・デジタル・シンセサイザ）です。高性能な高速内蔵DACと組み合わせた高度なDDS技術によって、デジタル設定可能なフル機能の高周波シンセサイザを形成し、周波数即応性に優れたアナログ出力サイン波形を最高200MHzで生成します。AD9954は、高速の周波数ホッピングと微細な同調分解能（32ビット周波数同調ワード）が得られるよう設計されています。周波数同調ワードと制御ワードは、シリアルI/Oポートからロードします。一部のモードで柔軟な周波数掃引機

能を提供するために、1024×32のスタティックRAMを内蔵しています。ユーザー定義の直線掃引動作モードにも対応します。また、方形波出力を必要とするアプリケーション用に高速コンバーティも内蔵しています。

AD9954は−40～+105°Cの拡張工業用温度範囲（2）で動作するように仕様規定されています。

# AD9954

## AD9954 — 電気的仕様

表1. 特に指定のない限り、AVDD、DVDD=1.8V±5%、DVDD\_I/O=3.3V±5%、R<sub>SET</sub>=3.92kΩ、外部リファレンス・クロック周波数=20MHz (20×でREFCLK乗算器をイネーブル)。DAC出力は、AGNDではなく、AVDDを基準にする必要があります。

| パラメータ                                           | 温度   | テスト・レベル | Min      | Typ  | Max      | 単位     |

|-------------------------------------------------|------|---------|----------|------|----------|--------|

| <b>REFクロック入力特性</b>                              |      |         |          |      |          |        |

| 周波数範囲                                           |      |         |          |      |          |        |

| REFCLK乗算器をディスエーブル                               | 全範囲  | VI      | 1        |      | 400      | MHz    |

| REFCLK乗算器を4×でイネーブル                              | 全範囲  | VI      | 20       |      | 100      | MHz    |

| REFCLK乗算器を20×でイネーブル                             | 全範囲  | VI      | 4        |      | 20       | MHz    |

| 入力容量                                            | 25°C | V       |          | 3    |          | pF     |

| 入力インピーダンス                                       | 25°C | V       |          | 1.5  |          | kΩ     |

| デューティ・サイクル                                      | 25°C | V       |          | 50   |          | %      |

| デューティ・サイクル<br>(REFCLK乗算器をイネーブル)                 | 25°C | V       | 35       |      | 65       | %      |

| REFCLK入力電力 <sup>1</sup>                         | 全範囲  | IV      | -15      | 0    | +3       | dBm    |

| <b>DAC出力特性</b>                                  |      |         |          |      |          |        |

| 分解能                                             |      |         |          | 14   |          | ビット    |

| フルスケール出力電流                                      | 25°C |         | 5        | 10   | 15       | mA     |

| ゲイン誤差                                           | 25°C | I       | -10      |      | +10      | %FS    |

| 出力オフセット                                         | 25°C | I       |          |      | 0.6      | μA     |

| 微分非直線性                                          | 25°C | V       |          | 1    |          | LSB    |

| 積分非直線性                                          | 25°C | V       |          | 2    |          | LSB    |

| 出力容量                                            | 25°C | V       |          | 5    |          | pF     |

| 残留位相ノイズ<br>(@1kHzオフセット、40MHz A <sub>OUT</sub> ) |      |         |          |      |          |        |

| REFCLK乗算器を20×でイネーブル                             | 25°C | V       |          | -105 |          | dBc/Hz |

| REFCLK乗算器を4×でイネーブル                              | 25°C | V       |          | -115 |          | dBc/Hz |

| REFCLK乗算器をディスエーブル                               | 25°C | V       |          | -132 |          | dBc/Hz |

| 電圧コンプライアンス・レンジ                                  | 25°C | I       | AVDD-0.5 |      | AVDD+0.5 | V      |

| <b>広帯域SFDR</b>                                  |      |         |          |      |          |        |

| 1~10MHzのアナログ出力                                  | 25°C | V       |          | 73   |          | dBc    |

| 10~40MHzのアナログ出力                                 | 25°C | V       |          | 67   |          | dBc    |

| 40~80MHzのアナログ出力                                 | 25°C | V       |          | 62   |          | dBc    |

| 80~120MHzのアナログ出力                                | 25°C | V       |          | 58   |          | dBc    |

| 120~160MHzのアナログ出力                               | 25°C | V       |          | 52   |          | dBc    |

| <b>狭帯域SFDR</b>                                  |      |         |          |      |          |        |

| 40MHzのアナログ出力 (±1MHz)                            | 25°C | V       |          | 87   |          | dBc    |

| 40MHzのアナログ出力 (±250kHz)                          | 25°C | V       |          | 89   |          | dBc    |

| 40MHzのアナログ出力 (±50kHz)                           | 25°C | V       |          | 91   |          | dBc    |

| 40MHzのアナログ出力 (±10kHz)                           | 25°C | V       |          | 93   |          | dBc    |

| 80MHzのアナログ出力 (±1MHz)                            | 25°C | V       |          | 85   |          | dBc    |

| 80MHzのアナログ出力 (±250kHz)                          | 25°C | V       |          | 87   |          | dBc    |

| 80MHzのアナログ出力 (±50kHz)                           | 25°C | V       |          | 89   |          | dBc    |

| 80MHzのアナログ出力 (±10kHz)                           | 25°C | V       |          | 91   |          | dBc    |

| 120MHzのアナログ出力 (±1MHz)                           | 25°C | V       |          | 83   |          | dBc    |

| 120MHzのアナログ出力 (±250kHz)                         | 25°C | V       |          | 85   |          | dBc    |

| 120MHzのアナログ出力 (±50kHz)                          | 25°C | V       |          | 87   |          | dBc    |

| 120MHzのアナログ出力 (±10kHz)                          | 25°C | V       |          | 89   |          | dBc    |

| 160MHzのアナログ出力 (±1MHz)                           | 25°C | V       |          | 81   |          | dBc    |

| 160MHzのアナログ出力 (±250kHz)                         | 25°C | V       |          | 83   |          | dBc    |

| 160MHzのアナログ出力 (±50kHz)                          | 25°C | V       |          | 85   |          | dBc    |

| 160MHzのアナログ出力 (±10kHz)                          | 25°C | V       |          | 87   |          | dBc    |

| パラメータ                     | 温度   | テスト・レベル | Min | Typ | Max | 単位     |

|---------------------------|------|---------|-----|-----|-----|--------|

| コンパレータ入力特性                |      |         |     |     |     |        |

| 入力容量                      | 25°C | V       |     | 3   |     | pF     |

| 入力抵抗                      | 25°C | IV      |     | 500 |     | kΩ     |

| 入力電流                      | 25°C | I       |     | ±12 |     | μA     |

| ヒステリシス                    | 25°C | IV      | 30  |     | 45  | mV     |

| コンパレータ出力特性                |      |         |     |     |     |        |

| ロジック1電圧、高インピーダンス負荷        | 全範囲  | VI      | 1.6 |     |     | V      |

| ロジック0電圧、高インピーダンス負荷        | 全範囲  | VI      |     | 0.4 |     | V      |

| 伝搬遅延                      | 25°C | IV      |     | 3   |     | ns     |

| 出力デューティ・サイクル誤差            | 25°C | IV      |     | ±5  |     | %      |

| 立ち上がり／立ち下がり時間、5pF負荷       | 25°C | IV      |     |     | 1   | ns     |

| トグル・レート、高インピーダンス負荷        | 25°C | IV      | 200 |     |     | MHz    |

| 出力ジッタ <sup>2</sup>        | 25°C | IV      |     |     | 1   | ps RMS |

| コンパレータ狭帯域SFDR             |      |         |     |     |     |        |

| 10MHz (1MHz)              | 25°C | V       |     | 80  |     | dBc    |

| 10MHz (250kHz)            | 25°C | V       |     | 85  |     | dBc    |

| 10MHz (50kHz)             | 25°C | V       |     | 90  |     | dBc    |

| 10MHz (10kHz)             | 25°C | V       |     | 95  |     | dBc    |

| 70MHz (1MHz)              | 25°C | V       |     | 80  |     | dBc    |

| 70MHz (250kHz)            | 25°C | V       |     | 85  |     | dBc    |

| 70MHz (50kHz)             | 25°C | V       |     | 90  |     | dBc    |

| 70MHz (10kHz)             | 25°C | V       |     | 95  |     | dBc    |

| 110MHz (1MHz)             | 25°C | V       |     | 80  |     | dBc    |

| 110MHz (250kHz)           | 25°C | V       |     | 85  |     | dBc    |

| 110MHz (50kHz)            | 25°C | V       |     | 90  |     | dBc    |

| 110MHz (10kHz)            | 25°C | V       |     | 95  |     | dBc    |

| 140MHz (1MHz)             | 25°C | V       |     | 80  |     | dBc    |

| 140MHz (250kHz)           | 25°C | V       |     | 85  |     | dBc    |

| 140MHz (50kHz)            | 25°C | V       |     | 90  |     | dBc    |

| 140MHz (10kHz)            | 25°C | V       |     | 95  |     | dBc    |

| 160MHz (1MHz)             | 25°C | V       |     | 80  |     | dBc    |

| 160MHz (250kHz)           | 25°C | V       |     | 85  |     | dBc    |

| 160MHz (50kHz)            | 25°C | V       |     | 90  |     | dBc    |

| 160MHz (10kHz)            | 25°C | V       |     | 95  |     | dBc    |

| クロック発振器出力ジッタ <sup>3</sup> |      |         |     |     |     |        |

| 5MHz A <sub>OUT</sub>     | 25°C | V       |     | 100 |     | ps RMS |

| 10MHz A <sub>OUT</sub>    | 25°C | V       |     | 60  |     | ps RMS |

| 40MHz A <sub>OUT</sub>    | 25°C | V       |     | 50  |     | ps RMS |

| 80MHz A <sub>OUT</sub>    | 25°C | V       |     | 50  |     | ps RMS |

| 120MHz A <sub>OUT</sub>   | 25°C | V       |     | 50  |     | ps RMS |

| 140MHz A <sub>OUT</sub>   | 25°C | V       |     | 50  |     | ps RMS |

| 160MHz A <sub>OUT</sub>   | 25°C | V       |     | 50  |     | ps RMS |

| タイミング特性                   |      |         |     |     |     |        |

| シリアル制御バス                  | 全範囲  | IV      |     |     |     |        |

| 最大周波数                     | 全範囲  | IV      |     | 25  |     | Mbps   |

| 最小クロック・パルス幅ローレベル          | 全範囲  | IV      | 7   |     |     | ns     |

| 最小クロック・パルス幅ハイレベル          | 全範囲  | IV      | 7   |     |     | ns     |

| 最大クロック立ち上がり／立ち下がり時間       | 全範囲  | IV      |     | 2   |     | ns     |

| 最小データ・セットアップ・タイム          | 全範囲  | IV      | 3   |     |     | ns     |

| DVDD_I/O=3.3V             | 全範囲  | IV      |     | 5   |     | ns     |

| 最小データ・セットアップ・タイム          | 全範囲  | IV      |     | 0   |     | ns     |

| DVDD_I/O=1.8V             | 全範囲  | IV      |     |     |     |        |

| 最小データ・ホールド・タイム            | 全範囲  | IV      |     |     |     |        |

# AD9954

| パラメータ                            | 温度   | テスト・レベル | Min | Typ  | Max | 単位                      |

|----------------------------------|------|---------|-----|------|-----|-------------------------|

| 最大データ有効時間                        | 全範囲  | IV      |     | 25   |     | ns                      |

| ウェイクアップ時間 <sup>4</sup>           | 全範囲  | IV      |     | 1    |     | ms                      |

| 最小リセット・パルス幅ハイレベル                 | 全範囲  | IV      | 5   |      |     | SYSCLKサイクル <sup>5</sup> |

| I/O UPDATE、PS0、PS1～SYNCCLK       | 全範囲  | I       | 4   |      |     | ns                      |

| セットアップ・タイムDVDD_I/O=3.3V          |      |         |     |      |     |                         |

| I/O UPDATE、PS0、PS1～SYNCCLK       | 全範囲  | I       | 6   |      |     | ns                      |

| セットアップ・タイムDVDD_I/O=3.3V          |      |         |     |      |     |                         |

| I/O UPDATE、PS0、PS1～SYNCCLK       | 全範囲  | I       | 0   |      |     | ns                      |

| ホールド・タイム                         |      |         |     |      |     |                         |

| レイテンシ                            |      |         |     |      |     |                         |

| I/O UPDATE～周波数変更の伝搬遅延            | 25°C | IV      | 24  |      |     | SYSCLKサイクル              |

| I/O UPDATE～位相オフセット変更の伝搬遅延        | 25°C | IV      | 24  |      |     | SYSCLKサイクル              |

| I/O UPDATE～振幅変更の伝搬遅延             | 25°C | IV      | 16  |      |     | SYSCLKサイクル              |

| PS0、PS1～RAM駆動周波数変更の伝搬遅延          | 25°C | IV      | 28  |      |     | SYSCLKサイクル              |

| PS0、PS1～RAM駆動位相変更の伝搬遅延           | 25°C | IV      | 28  |      |     | SYSCLKサイクル              |

| PS0～リニア周波数掃引の伝搬遅延                | 25°C | IV      | 28  |      |     | SYSCLKサイクル              |

| CMOSロジック入力                       |      |         |     |      |     |                         |

| ロジック1電圧 @DVDD_I/O (ピン43) =1.8V   | 25°C | I       |     | 1.25 |     | V                       |

| ロジック0電圧 @DVDD_I/O (ピン43) =1.8V   | 25°C | I       |     |      | 0.6 | V                       |

| ロジック1電圧 @DVDD_I/O (ピン43) =3.3V   | 25°C | I       |     | 2.2  |     | V                       |

| ロジック0電圧 @DVDD_I/O (ピン43) =3.3V   | 25°C | I       |     |      | 0.8 | V                       |

| ロジック1電流                          | 25°C | V       |     | 3    | 12  | μA                      |

| ロジック0電流                          | 25°C |         |     |      | 12  | μA                      |

| 入力容量                             | 25°C |         |     |      | 2   | pF                      |

| CMOSロジック出力 (1mA負荷) DVDD_I/O=1.8V |      |         |     |      |     |                         |

| ロジック1電圧                          | 25°C | I       |     | 1.35 |     | V                       |

| ロジック0電圧                          | 25°C | I       |     |      | 0.4 | V                       |

| CMOSロジック出力 (1mA負荷) DVDD_I/O=3.3V |      |         |     |      |     |                         |

| ロジック1電圧                          | 25°C | I       |     | 2.8  |     | V                       |

| ロジック0電圧                          | 25°C | I       |     |      | 0.4 | V                       |

| 電力消費量 (AVDD=DVDD=1.8V)           |      |         |     |      |     |                         |

| シングル・トーン・モード (コンパレータはオフ)         | 25°C | I       |     | 162  | 171 | mW                      |

| RAMまたは直線掃引をイネーブル                 | 25°C | I       |     | 175  | 190 | mW                      |

| コンパレータをイネーブル                     | 25°C | I       |     | 180  | 190 | mW                      |

| RAMとコンパレータをイネーブル                 | 25°C | I       |     | 198  | 220 | mW                      |

| 高速パワーダウン・モード                     | 25°C | I       |     | 150  | 160 | mW                      |

| フルスリープ・モード                       | 25°C | I       |     | 20   | 27  | mW                      |

| 同期機能 <sup>6</sup>                |      |         |     |      |     |                         |

| 最大SYNCクロック・レート (DVDD_I/O=1.8V)   | 25°C | VI      |     | 62.5 |     | MHz                     |

| 最大SYNCクロック・レート (DVDD_I/O=3.3V)   | 25°C | VI      |     | 100  |     | MHz                     |

| SYNC_CLKアライメント分解能 <sup>7</sup>   | 25°C | V       |     |      | ±1  | SYSCLKサイクル              |

<sup>1</sup> 位相ノイズを最善にするために、可能なかぎり大きい振幅クロックを使用します。クロック入力振幅を減らすと、デバイスの位相ノイズ性能も低下します。

<sup>2</sup> コンパレータのみからのサイクル間残留ジッターです。

<sup>3</sup> コンパレータを駆動するDDSコアからのサイクル間残留ジッターです。

<sup>4</sup> ウェイクアップ時間は、アナログ・パワーダウン・モードから復帰する時間です (パワーダウン動作モードのセクションを参照)。必要な最長時間は、リファレンス・クロック乗算器PLLがリファレンスに再固定する時間です。ウェイクアップ時間は、DAC\_BPにコンデンサがなく、推奨のPLLループ・フィルタ値を使用していることを前提にしています。

<sup>5</sup> SYSCLKサイクルは、DDSがオンチップ使用する実際のクロック周波数です。外部リファレンス・クロック周波数を通信するためにリファレンス・クロック乗算器を使用する場合、SYSCLK周波数は、外部周波数×リファレンス・クロックの増倍率になります。リファレンス・クロック乗算器を使用しない場合は、SYSCLK周波数は外部リファレンス・クロック周波数と同じです。

<sup>6</sup> SYNC\_CLK=1/4 SYSCLKレート。SYNC\_CLKレート $\geq$ 50MHzの場合、高速SYNCイネーブル・ビットCFR2<11>をセットしてください。

<sup>7</sup> このパラメータは、デジタル同期機能がシステム・クロック立ち上がりエッジ間の位相遅延 (タイミング・スキュー) を克服できないことを示しています。システム・クロック・エッジが整列している場合は、同期機能は2つのエッジ間のスキューを増大しません。

## 絶対最大定格

表2.

|                                |             |

|--------------------------------|-------------|

| 最大ジャンクション温度 .....              | 150°C       |

| DVDD_I/O (ピン43) .....          | 4V          |

| AVDD、DVDD .....                | 2V          |

| デジタル入力電圧 (DVDD_I/O=3.3V) ..... | -0.7~+5.25V |

| デジタル入力電圧 (DVDD_I/O=1.8V) ..... | -0.7~+2.2V  |

| デジタル出力電流 .....                 | 5mA         |

| 保存温度 .....                     | -65~+150°C  |

| 動作温度 .....                     | -40~+105°C  |

| リード温度 (10秒のハンダ処理) .....        | 300°C       |

| $\theta_{JA}$ .....            | 38°C/W      |

| $\theta_{JC}$ .....            | 15°C/W      |

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作に関するセクションに記載されている規定値以上でのデバイス動作を定めたものではありません。長時間デバイスを絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

表3. テスト・レベルの説明

|     |                                                               |

|-----|---------------------------------------------------------------|

| I   | 100%の出荷テストを実施。                                                |

| II  | 25°Cで100%の出荷テストを実施し、規定の温度でサンプル・テストを実施。                        |

| III | サンプル・テストのみを実施。                                                |

| IV  | パラメータは、設計と特性テストにより保証されています。                                   |

| V   | パラメータはtyp値のみ。                                                 |

| VI  | デバイスは、25°Cで100%の出荷テストを実施し、設計および特性テストにより工業用動作温度範囲に対して保証されています。 |

03074-0-032

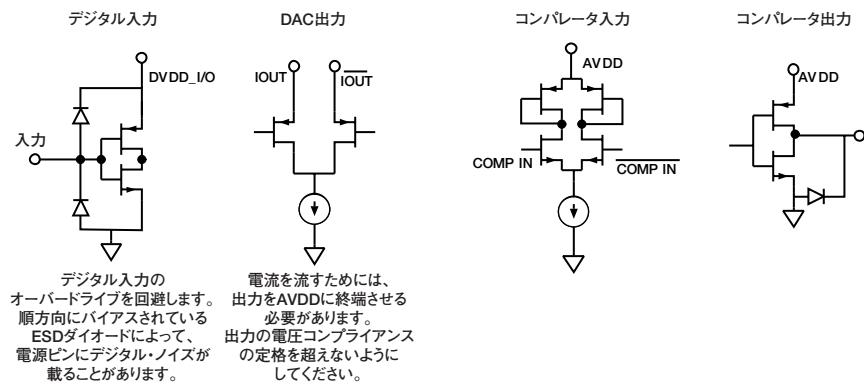

図2. 入／出力の等価回路

# AD9954

図3. 48ピンEP\_TQFP

注：パッケージの底面にある露出パドルはDACへの電気的接続になるため、アナログ・グラウンドに接続する必要があります。また、ピン43のDVDD\_I/Oは1.8Vまたは3.3Vに接続できます。DVDDピン（ピン2とピン34）は1.8Vにしか接続できません。

## ピン機能の説明

表4. ピン機能の説明 — 48ピンTQFP/EP

| ピン番号                             | 記号                   | I/O | 説明                                                                                                                                       |

|----------------------------------|----------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------|

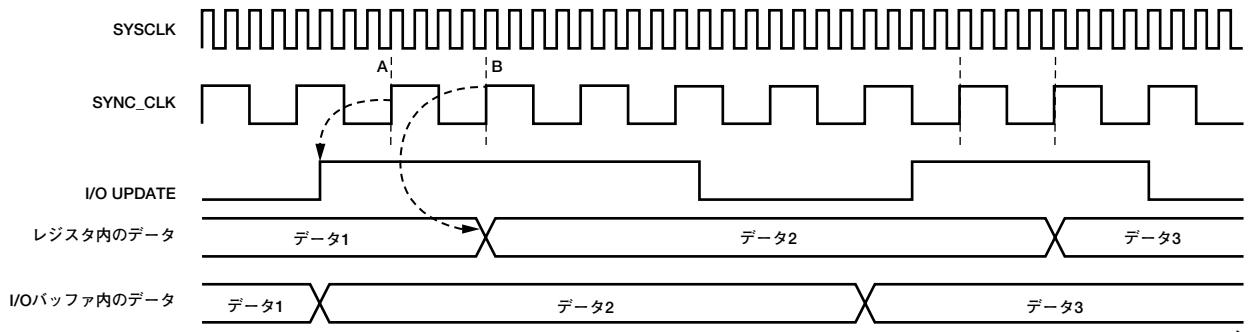

| 1                                | I/O UPDATE           | I   | 立ち上がりエッジで、内部バッファ・メモリの内容をI/Oレジスタに転送します。このピンは、SYNC_CLK出力信号をベースにしてセットアップし、保持する必要があります。                                                      |

| 2, 34                            | DVDD                 | I   | デジタル電源ピン (1.8V)                                                                                                                          |

| 3, 33, 42                        | DGND                 | I   | デジタル電源グラウンド・ピン                                                                                                                           |

| 4, 6, 13, 16, 18, 19, 25, 27, 29 | AVDD                 | I   | アナログ電源ピン (1.8V)                                                                                                                          |

| 5, 7, 14, 15, 17, 22, 26, 32     | AGND                 | I   | アナログ電源グラウンド・ピン                                                                                                                           |

| 8                                | OSC/REFCLK           | I   | コンプリメンタリー・リファレンス・クロック／発振器入力。REFCLKポートをシングルエンド・モードで動作するとき、REFCLKBを0.1μFコンデンサでAVDDに対してデカッピングしてください。                                        |

| 9                                | OSC/REFCLK           | I   | リファレンス・クロック／発振器入力。発振器／REFCLK動作の詳細については、クロック入力のセクションを参照してください。                                                                            |

| 10                               | CRYSTAL OUT          | O   | 発振器部の出力                                                                                                                                  |

| 11                               | CLKMODESELECT        | I   | 発振器部の制御ピン。ハイレベルのとき発振器部をイネーブルにし、ローレベルのとき発振器部をバイパスします。                                                                                     |

| 12                               | LOOP_FILTER          | I   | このピンによって、REFCLK乗算器のPLLループ・フィルタの外付けゼロ補償ネットワークに接続します。ネットワークは、AVDDに接続する0.1μFコンデンサと1kΩ抵抗との直列接続で構成されます。                                       |

| 20                               | IOUT                 | O   | コンプリメンタリーDAC出力。AGNDではなく、AVDDへの抵抗によってバイアスをかけてください。                                                                                        |

| 21                               | IOUT                 | O   | DAC出力。AGNDではなく、AVDDへの抵抗によってバイアスをかけてください。                                                                                                 |

| 23                               | DACBP                | I   | DACバイアスライン・デカッピング・ピン                                                                                                                     |

| 24                               | DAC_R <sub>SET</sub> | I   | AGNDとDAC_R <sub>SET</sub> を接続する抵抗 (公称3.92kΩ) により、DACのリファレンス電流が決まります。                                                                     |

| 28                               | COMP_OUT             | O   | コンパレータ出力                                                                                                                                 |

| 30                               | COMP_IN              | I   | コンパレータ入力                                                                                                                                 |

| 31                               | COMP_IN              | I   | コンパレータ・コンプリメンタリー入力                                                                                                                       |

| 35                               | PWRDNCTL             | I   | 外部パワーダウン制御として使用する入力ピン (詳細については表13を参照)。                                                                                                   |

| 36                               | RESET                | I   | アクティブ・ハイのハードウェア・リセット・ピン。I/Oポート・レジスタ・マップに示すように、RESETピンのアサートによってAD9954は初期状態になります。                                                          |

| 37                               | IOSYNC               | I   | シリアル・ポート・コントローラの非同期アクティブ・ハイ・リセット。ハイレベルのとき、現在のI/O動作が直ちに終了し、IOSYNCがローレベルに戻ると新しいI/O動作を開始できるようになります。このピンを使用しない場合は、接地します。フローティング状態にはしないでください。 |

| 38                               | SDO                  | O   | I/Oポートを3線式シリアル・ポートとして動作させるとき、このピンがシリアル・データ出力になります。2線式シリアル・ポートにするとき、このピンは未使用で、未接続のままにすることができます。                                           |

| 39                               | CS                   | I   | このピンはアクティブ・ロー・チップ・セレクトとして機能し、これによって複数のデバイスによるI/Oバスの共有ができます。                                                                              |

| 40                               | SCLK                 | I   | このピンは、I/O動作用のシリアル・データ・クロックとして機能します。                                                                                                      |

| 41                               | SDIO                 | I/O | I/Oポートを3線式シリアル・ポートとして動作させるとき、このピンがシリアル・データ入力になります。2線式シリアル・ポートにするときは、双方向シリアル・データ・ピンになります。                                                 |

| 43                               | DVDD_I/O             | I   | デジタル電源 (I/Oセルの場合のみ、3.3V)                                                                                                                 |

| 44                               | SYNC_IN              | I   | 複数のAD9954の同期をとるための入力信号。この入力はマスターAD9954のSYNC_CLK出力に接続します。                                                                                 |

| 45                               | SYNC_CLK             | O   | 外付けハードウェアのシンクロナイザとなるクロック出力ピン                                                                                                             |

| 46                               | OSK                  | I   | 動作用にプログラムする場合、整形ON/OFFキーイング機能の方向を制御する入力ピン。OSKはSYNC_CLKピンに同期します。OSKをプログラムしない場合は、DGNDに接続してください。                                            |

| 47, 48                           | PS0, PS1             | I   | 4つの内部プロファイルから1つを選択するための入力ピン。プロファイル<1:0>は、SYNC_CLKピンに同期します。これらの入力に変化があると、内部バッファ・メモリの内容がI/Oレジスタに転送されます (内部I/O UPDATEを送信)。                  |

| <49>                             | AGND                 | I   | パッケージの底面にある露出パドルはDAC用のグラウンド接続であり、どんなボード・レイアウトでもAGNDに接続する必要があります。                                                                         |

# AD9954

## 代表的な性能特性

図4.  $F_{out}=1\text{MHz}$   $F_{CLK}=400\text{MSPS}$ 、

WBSFDR

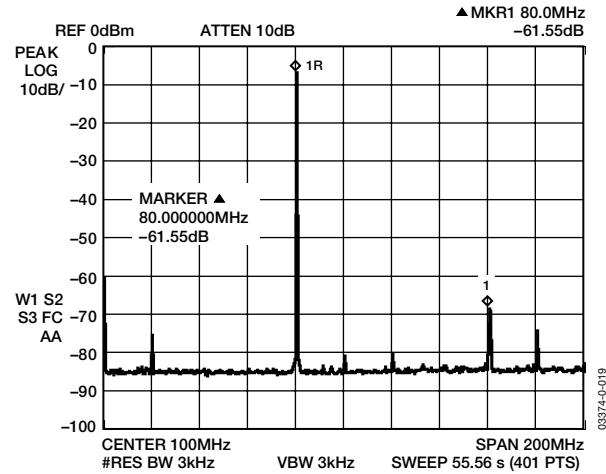

図7.  $F_{out}=80\text{MHz}$   $F_{CLK}=400\text{MSPS}$ 、

WBSFDR

図5.  $F_{out}=10\text{MHz}$ ,  $F_{CLK}=400\text{MSPS}$ 、

WBSFDR

図8.  $F_{out}=120\text{MHz}$ ,  $F_{CLK}=400\text{MSPS}$ 、

WBSFDR

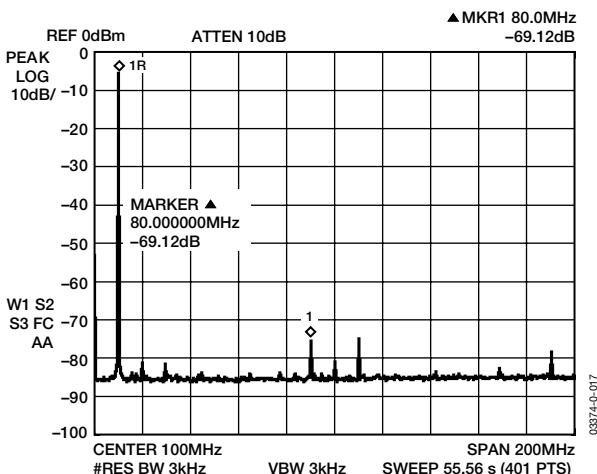

図6.  $F_{out}=40\text{MHz}$ ,  $F_{CLK}=400\text{MSPS}$ 、

WBSFDR

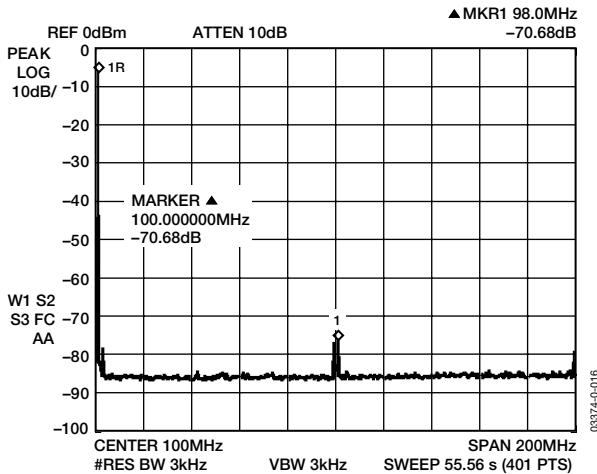

図9.  $F_{out}=160\text{MHz}$ ,  $F_{CLK}=400\text{MSPS}$ 、

WBSFDR

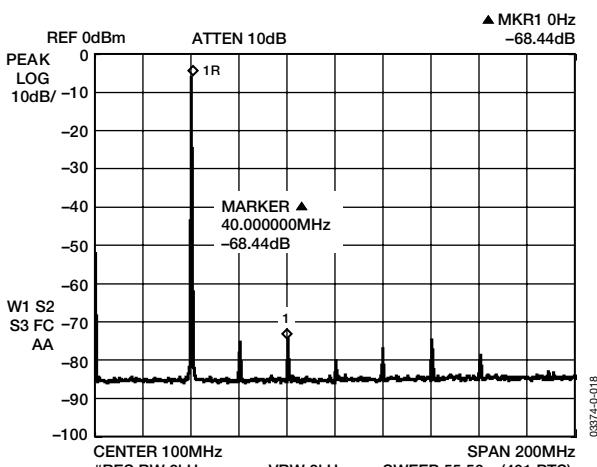

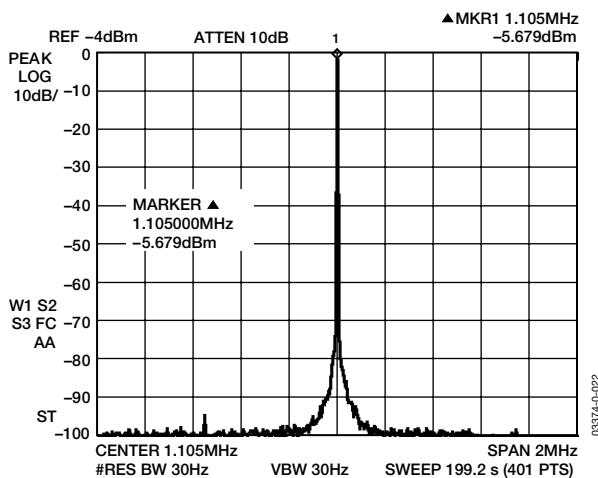

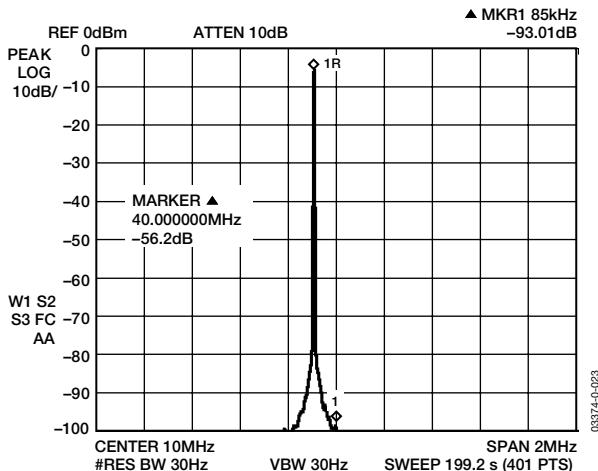

図10.  $F_{\text{OUT}}=1.1\text{MHz}$ 、 $\text{FCLK}=400\text{MSPS}$ 、NBSFDR、 $\pm 1\text{MHz}$

図13.  $F_{\text{OUT}}=80.3\text{MHz}$ 、 $\text{FCLK}=400\text{MSPS}$ 、NBSFDR、 $\pm 1\text{MHz}$

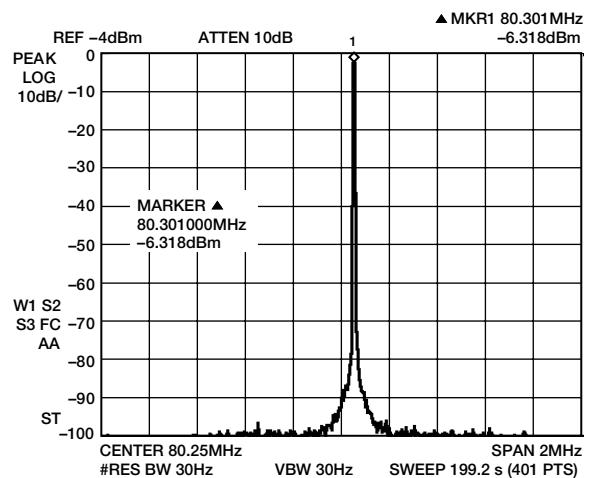

図11.  $F_{\text{OUT}}=10\text{MHz}$ 、 $\text{FCLK}=400\text{MSPS}$ 、NBSFDR、 $\pm 1\text{MHz}$

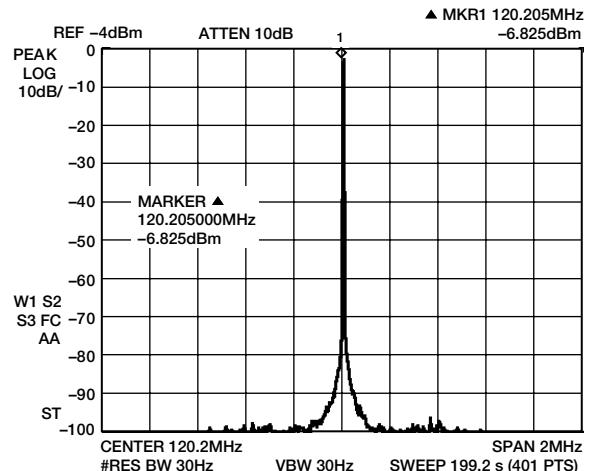

図14.  $F_{\text{OUT}}=120.2\text{MHz}$ 、 $\text{FCLK}=400\text{MSPS}$ 、NBSFDR、 $\pm 1\text{MHz}$

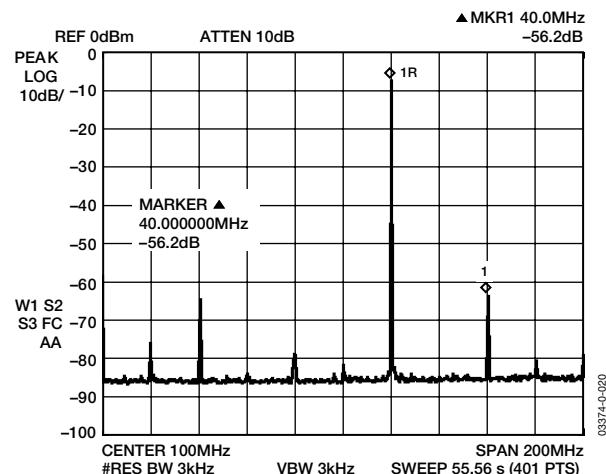

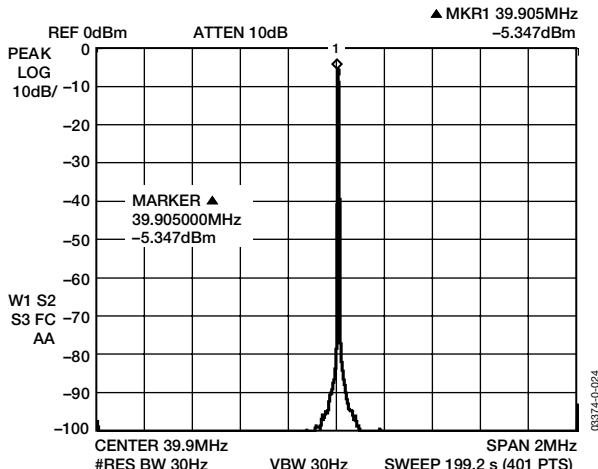

図12.  $F_{\text{OUT}}=39.9\text{MHz}$ 、 $\text{FCLK}=400\text{MSPS}$ 、NBSFDR、 $\pm 1\text{MHz}$

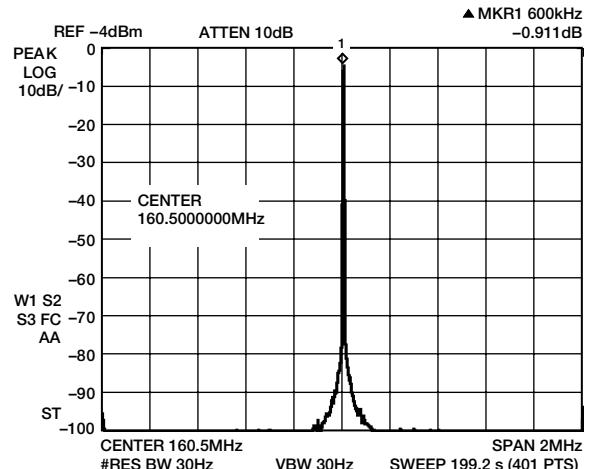

図15.  $F_{\text{OUT}}=160\text{MHz}$ 、 $\text{FCLK}=400\text{MSPS}$ 、NBSFDR、 $\pm 1\text{MHz}$

# AD9954

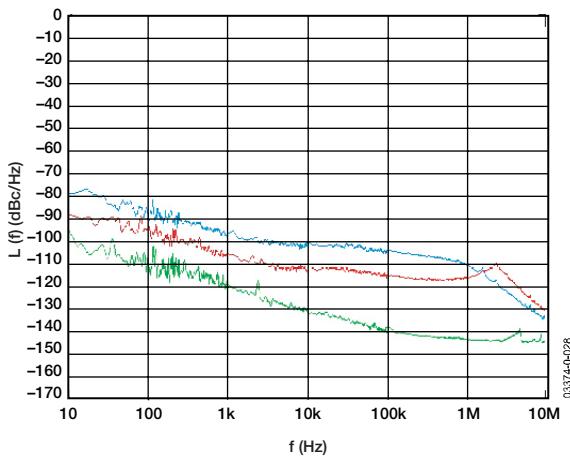

図16. 残留位相ノイズ： $F_{OUT}=159.5\text{MHz}$ 、

$F_{CLK}=400\text{MSPS}$ （緑）、 $4\times100\text{MSPS}$

（赤）、 $20\times20\text{ MSPS}$ （青）

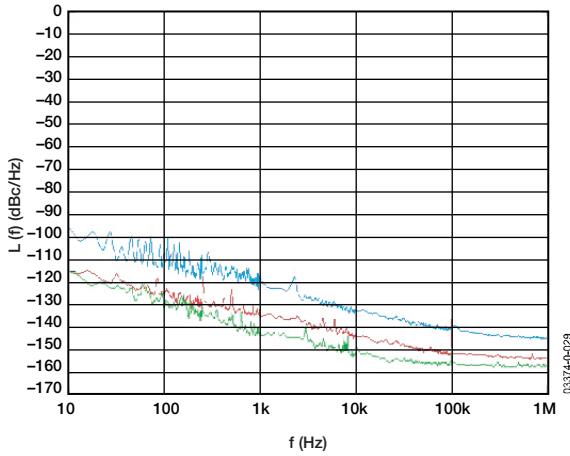

図17. 残留位相ノイズ： $F_{OUT}=9.5\text{MHz}$ 、

$F_{CLK}=400\text{MSPS}$ （緑）、 $4\times100\text{MSPS}$

（赤）、 $20\times20\text{ MSPS}$ （青）

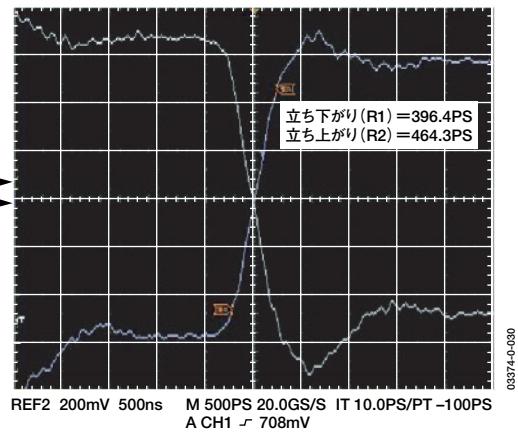

図18. コンパレータの立ち上がり／立ち下がり

時間、 $160\text{MHz}$

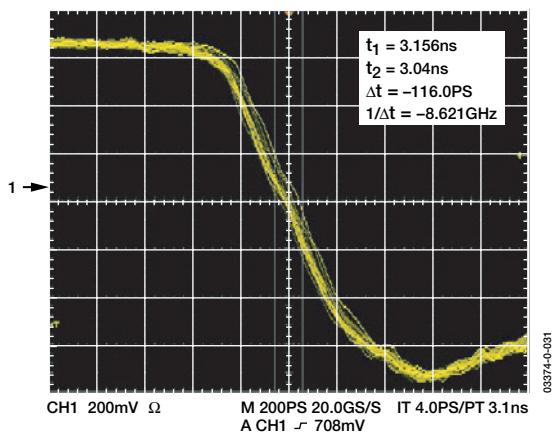

図19.  $160\text{MHz}$ でのDDSとコンパレータの同時

動作時の残留ピークtoピーク・ジッタ

## 動作原理

### コンポーネント・ブロック

#### DDSコア

DDSの出力周波数 ( $f_o$ ) は、システム・クロック (SYSCLK) の周波数、周波数同調ワード (FTW) の値、アキュムレータの容量 (この場合は $2^{32}$ ) の関数です。正確には、次式で表される関係になります。ここで、 $f_s$ はSYSCLKの周波数です。

$$f_o = (FTW) (f_s) / 2^{32} \quad 0 \leq FTW \leq 2^{31}$$

$$f_o = f_s \times (1 - (FTW / 2^{32})) \quad 2^{31} < FTW < 2^{32} - 1$$

位相アキュムレータの出力の値は、COS (x) 機能ブロックによって振幅値に変換され、DACに転送されます。

アプリケーションによっては、出力信号をゼロ位相に強制することが望れます。ただしFTWを0に設定するだけでは不十分で、これではDDSコアが現在の位相値を保持することにしかなりません。このため、制御ビットによって、位相アキュムレータ出力をゼロに強制する必要があります。

パワーアップ時に、クリア位相アキュムレータ・ビットがロジック1に設定されますが、このビットのバッファ・メモリはクリアされます (ロジック0)。したがって、パワーアップ時には、最初のI/O UPDATEが実行されるまで、位相アキュムレータはクリア状態のままでです。

#### 位相ロック・ループ (PLL)

PLLによって、REFCLK周波数の乗算が可能になります。PLLの制御には、制御機能レジスタNo.2の5ビットREFCLK乗算器部分であるビット $<7:3>$ をプログラムします。

0x04~0x14の範囲の値 (10進4~10進20) を得るようにプログラムすると、PLLはREFCLK入力周波数に対応する10進値をかけて乗算します。ただし、PLLの最大出力周波数は400MHzに制限されています。PLL値が変更されるたびに、PLLがロックするための時間 (約1ms) をとるよう注意する必要があります。

PLLをバイパスするときは、4~20 (10進) の範囲外の値をプログラムします。バイパスする場合、電力の節約のためにPLLはシャットダウンします。

表5. クロック入力の動作モード

| CFR1<4> | CLKMODESELECT | CFR2<7:3>            | 発振器はイネーブル？ | システム・クロック                    | 周波数範囲 (MHz)          |

|---------|---------------|----------------------|------------|------------------------------|----------------------|

| ローレベル   | ハイレベル         | $3 < M < 21$         | はい         | $F_{CLK} = F_{OSC} \times M$ | $80 < F_{CLK} < 400$ |

| ローレベル   | ハイレベル         | $M < 4$ または $M > 20$ | はい         | $F_{CLK} = F_{OSC}$          | $20 < F_{CLK} < 30$  |

| ローレベル   | ローレベル         | $3 < M < 21$         | いいえ        | $F_{CLK} = F_{OSC} \times M$ | $80 < F_{CLK} < 400$ |

| ローレベル   | ローレベル         | $M < 4$ または $M > 20$ | いいえ        | $F_{CLK} = F_{OSC}$          | $10 < F_{CLK} < 10$  |

| ハイレベル   | X             | X                    | いいえ        | $F_{CLK} = 0$                | 該当せず                 |

#### クロック入力

AD9954は、さまざまなクロック手法に対応します。ユーザー・プログラマブルなビットで、差動／シングルエンド入力クロック、オンチップ発振器のイネーブル、位相ロック・ループ (PLL) 乗算器のサポートのすべてを制御します。6つの動作モードのうちの1つを設定してシステム・クロックを生成することができます。これらのモードは、CLKMODESELECTピンのCFR1<4>とCFR2<7:3>を使用して設定します。外部ピン CLKMODESELECTをロジック・ハイに接続すると、オンチップ水晶発振器回路がイネーブルになります。オンチップ発振器がイネーブルになっているとき、AD9954のユーザーは、外付け水晶をREFCLK入力とREFCLKB入力に接続して、20~30MHzの範囲で低周波のリファレンス・クロックを生成します。発振器が生成した信号は、バッファリングされてから、残りのチップに配信されます。このバッファリングされた信号は、CRYSTAL OUTピンから得られます。ビットCFR1<4>を使用すれば、バッファをイネーブル／ディスエーブルにしてシステム・クロックのオン／オフ切り替えができます。水晶発振器をオンにする場合、始動時間が長くなりますが、これを回避するために発振器そのものはパワーダウンしません。CFR2<9>をロジック・ハイに設定すると、水晶発振器出力バッファがイネーブルになります。CFR2<9>がロジック・ローの場合、発振器出力バッファはディスエーブルになります。

CLKMODESELECTをロジック・ローに接続すると、オンチップ発振器と発振器出力バッファがディスエーブルになります。発振器がディスエーブルになると、外付け発振器からREFCLK信号やREFCLKB信号を供給する必要があります。差動動作の場合、コンプリメンタリー信号でこれらのピンを駆動します。シングルエンド動作の場合は、未使用ピンとアナログ電源の間に $0.1\mu F$ コンデンサを接続してください。コンデンサがあると、クロック入力ピンのバイアス電圧は1.35Vになります。さらに、PLLを使用すれば、リファレンス周波数を4~20の範囲の整数値で倍倍することができます。クロック動作モードを表5にまとめて示します。なお、PLL乗算器はCFR1<4>ビットとは無関係に、CFR2<7:3>ビットで制御します。

# AD9954

## DAC出力

AD9954には14ビットの電流出力DACが内蔵されています。多くのDACと異なり、この出力はAGNDではなくAVDDを基準にしています。

2つのコンプリメンタリー出力から、1つに結合されたフルスケール出力電流 ( $I_{OUT}$ ) が得られます。差動出力はDAC出力のコモン・モード・ノイズの量を減らすため、S/N比が高くなるという利点があります。DAC\_R<sub>SET</sub>ピンとDACグラウンド (AGND\_DAC) の間に接続した外付け抵抗 (R<sub>SET</sub>) によって、フルスケール電流を制御します。次に示すように、フルスケール電流は抵抗値に比例します。

$$R_{SET} = 39.19 / I_{OUT}$$

結合されたDAC出力の最大フルスケール出力電流は15mAですが、出力を10mAまでに制限すると最善のスプリアスフリー・ダイナミック・レンジ (SFDR) 性能が得られます。DAC出力のコンプライアンス・レンジはAVDD+0.5V～AVDD−0.5Vです。このレンジを超える電圧が発生すると、DAC歪みが大きくなりすぎて、DAC出力回路を損傷する可能性があります。出力電圧をこのコンプライアンス・レンジ内に保持するには、負荷終端に適切な配慮をする必要があります。

## コンパレータ

多くのアプリケーションでは、サイン波よりも方形波信号が要求されます。たとえば、多くのクロック・アプリケーションでは、スルーレートを高くすると、位相ノイズとジッターが低くなります。これらのアプリケーションをサポートするため、AD9954にはオンチップ・コンパレータが組み込まれています。このコンパレータは、200MHzを超える帯域幅と1.3～1.8Vのコモン・モード入力レンジを備えています。コンパレータのパワーダウン・ビットCFR1<6>を設定すれば、コンパレータをオフにして消費電力を節約できます。

## リニア（線形）掃引ブロック

リニア掃引という動作モードでは、開始周波数 (F0) から終端周波数 (F1) への変化が瞬間的ではなく、掃引またはランプといった方法で行われます。周波数ランプでは、リニア／ノンリニアとは無関係に、主要なF0/F1周波数のほかに、F0とF1の間にある中間周波数も多数出力することになります。

リニア掃引ブロックは、立ち下がり／立ち上がり△周波数同調ワード、立ち下がり／立ち上がり△周波数ランプ・レート、周波数アキュムレータで構成されています。リニア掃引イネーブル・ビットCFR1<21>でリニア掃引ブロックをイネーブルにします。さらに、リニア掃引ノードウェル・ビットで、掃引中に終端周波数に達したときのリニア掃引ブロックの動作を制御します。周波数掃引の実際のプログラミングの方法については、動作モードのセクションで説明します。

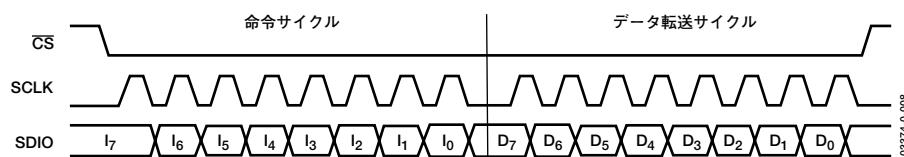

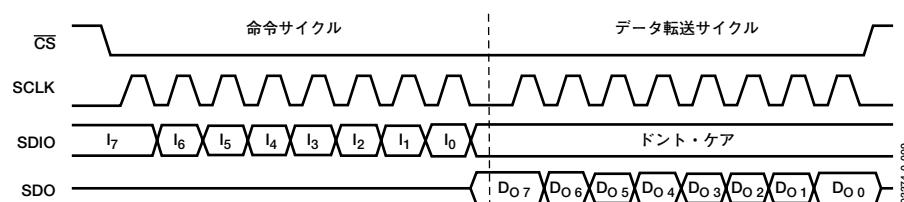

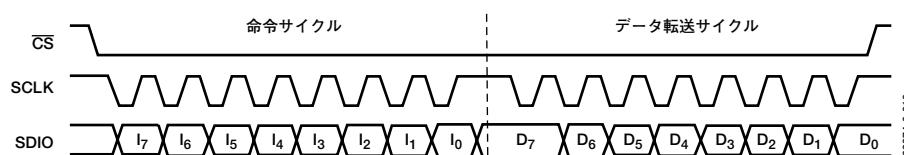

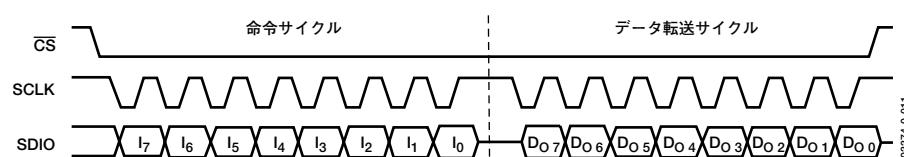

## シリアルI/Oポート

AD9954のシリアル・ポートは柔軟な同期シリアル通信ポートで、業界標準の多くのマイクロコントローラやマイクロプロセッサと簡単にインターフェースできます。このシリアルI/Oポートは、Motorola 6905/11 SPIやIntel 8051 SSRのプロトコルなど、ほとんどの同期転送フォーマットと互換性があります。

インターフェースによって、AD9954を構成するすべてのレジスタへの読み出し／書き込みアクセスが可能になります。MSBファーストまたはLSBファーストの転送フォーマットに対応します。また、AD9954のシリアル・インターフェース・ポートを1ピンのI/O (SDIO) として設定すれば2線式インターフェースになり、in/out用の2本の単方向ピン (SDIO/SDO) にすれば3線式インターフェースになります。IOSYNCとCSのオプション・ピン2本によって、AD9954のシステム設計がきわめて柔軟になります。

## レジスタ・マップと説明

レジスタ・マップを表7と表8に示します。デバイスの動作モードによって再マップされるレジスタがあるため、リニア掃引イネーブル・ビットの状態によって適切なレジスタ・マップが異なります。特に、リニア掃引イネーブル・ビットが偽の場合、レジスタ0x07、0x08、0x09、0x0Aは、各RAMプロファイル・スライスのRAMセグメント制御ワードとして機能します。リニア掃引イネーブル・ビットが真の場合、0x07が偽のリニア掃引制御ワードになり、0x08は正のリニア掃引制御ワードになります。リニア掃引モードでは、レジスタ0x09と0x0Aを使用しません。RAM動作よりもリニア掃引動作が優先されるため、電力節減のためリニア掃引イネーブル・ビットCFR1<21>が真の場合は、RAMイネーブル・ビットCFR1<31>をゼロに設定することを推奨します。各レジスタに関連付けられたシリアル・アドレス番号は、16進フォーマットで示されます。角括弧<>は、特定のビットまたはビット範囲を参照するために使用しています。たとえば、<3>はビット3、<7:3>は7から3までのビット範囲 (7と3を含む) を表します。

表6. リニア掃引イネーブル・ビットと対応するレジスタ・マッピング

| リニア掃引イネーブル・ビット | レジスタ・マップ            |

|----------------|---------------------|

| 偽 (CFR1<21>=0) | RAMセグメント制御ワード・アクティブ |

| 真 (CFR1<21>=1) | リニア掃引制御ワード・アクティブ    |

表7. レジスタ・マップ—リニア掃引イネーブル・ビットが偽の場合 (CFR1&lt;21&gt;=0)

注: RAMイネーブル・ビットCFR1&lt;31&gt;は、RAMセグメント制御ワードではなくRAMそのものをアクティブにするだけです。

| レジスタ名<br>(シリアル・<br>アドレス)          | ビット範囲   | (MSB)<br>ビット7                                                         | ビット6                       | ビット5                    | ビット4             | ビット3                   | ビット2                    | ビット1                       | (LSB)<br>ビット0  | デフォルト値<br>または<br>プロファイル |  |  |  |  |  |  |  |  |

|-----------------------------------|---------|-----------------------------------------------------------------------|----------------------------|-------------------------|------------------|------------------------|-------------------------|----------------------------|----------------|-------------------------|--|--|--|--|--|--|--|--|

| 制御機能レジスタ<br>No.1 (CFR1)<br>(0x00) | <7:0>   | デジタル・<br>パワーダウン                                                       | Comp<br>パワーダウン             | DAC<br>パワーダウン           | クロック入力<br>パワーダウン | 外部パワー<br>ダウノード         | 直線掃引<br>ノードウェル          | SYNC_CLK<br>出力ディス<br>エーブル  | 未使用            | 0x00                    |  |  |  |  |  |  |  |  |

|                                   | <15:8>  | I/O UDで<br>SRRをロード                                                    | 周波数<br>アキュムレータ<br>を自動クリア   | 位相<br>アキュムレータ<br>を自動クリア | SINE出力を<br>イネーブル | 周波数<br>アキュムレータ<br>をクリア | 位相<br>アキュムレータ<br>をクリア   | SDIO入力のみ                   | LSB<br>ファースト   | 0x00                    |  |  |  |  |  |  |  |  |

|                                   | <23:16> | 自動SYNC<br>イネーブル                                                       | ソフトウェア<br>手動同期             | リニア掃引<br>イネーブル          | 未使用              | 未使用                    | 未使用                     | 未使用                        | 未使用            | 0x00                    |  |  |  |  |  |  |  |  |

|                                   | <31:24> | RAM<br>イネーブル                                                          | RAMデステイ<br>ネーションは<br>位相ワード | 内部プロファイル制御<2:0>         |                  |                        | I/O UDで<br>ARRをロード      | OSK<br>イネーブル               | 自動OSK<br>キーイング | 0x00                    |  |  |  |  |  |  |  |  |

| 制御機能レジスタ<br>No.2 (CFR2)<br>(0x01) | <7:0>   | REFCLK乗算器<br>0x00または0x01、または0x02または0x03:バイパス乗算器<br>0x04~0x14:4×~20×倍増 |                            |                         |                  |                        | VCO範囲                   | チャージ・ポンプ電流<1:0>            |                |                         |  |  |  |  |  |  |  |  |

|                                   | <15:8>  | 未使用                                                                   |                            |                         |                  | 高速同期<br>イネーブル          | ハードウェア<br>手動同期<br>イネーブル | CRYSTAL<br>OUTピン・<br>アクティブ | 未使用            | 0x00                    |  |  |  |  |  |  |  |  |

|                                   | <23:16> | 未使用                                                                   |                            |                         |                  |                        |                         |                            |                |                         |  |  |  |  |  |  |  |  |

| 振幅スケール係数<br>(ASF)<br>(0x02)       | <7:0>   | 振幅スケール係数レジスタ<7:0>                                                     |                            |                         |                  |                        |                         |                            |                |                         |  |  |  |  |  |  |  |  |

|                                   | <15:8>  | 自動ランプ・<br>レート速度制御<1:0>                                                | 振幅スケール係数レジスタ<13:8>         |                         |                  |                        |                         |                            |                |                         |  |  |  |  |  |  |  |  |

| 振幅ランプ・<br>レート(ARR)<br>(0x03)      | <7:0>   | 振幅ランプ・レート・レジスタ<7:0>                                                   |                            |                         |                  |                        |                         |                            |                |                         |  |  |  |  |  |  |  |  |

| 周波数同調<br>ワード (FTW0)<br>(0x04)     | <7:0>   | 周波数同調ワードNo.0 <7:0>                                                    |                            |                         |                  |                        |                         |                            |                |                         |  |  |  |  |  |  |  |  |

|                                   | <15:8>  | 周波数同調ワードNo.0 <15:8>                                                   |                            |                         |                  |                        |                         |                            |                |                         |  |  |  |  |  |  |  |  |

|                                   | <23:16> | 周波数同調ワードNo.0 <23:16>                                                  |                            |                         |                  |                        |                         |                            |                |                         |  |  |  |  |  |  |  |  |

|                                   | <31:24> | 周波数同調ワードNo.0 <31:24>                                                  |                            |                         |                  |                        |                         |                            |                |                         |  |  |  |  |  |  |  |  |

| 位相オフセット・<br>ワード (POW0)<br>(0x05)  | <7:0>   | 位相オフセット・ワードNo.0 <7:0>                                                 |                            |                         |                  |                        |                         |                            |                |                         |  |  |  |  |  |  |  |  |

|                                   | <15:8>  | 未使用<1:0>                                                              | 位相オフセット・ワードNo.0 <13:8>     |                         |                  |                        |                         |                            |                |                         |  |  |  |  |  |  |  |  |

| 周波数同調ワード<br>(FTW1)<br>(0x06)      | <7:0>   | 周波数同調ワードNo.1 <7:0>                                                    |                            |                         |                  |                        |                         |                            |                |                         |  |  |  |  |  |  |  |  |

|                                   | <15:8>  | 周波数同調ワードNo.1 <15:8>                                                   |                            |                         |                  |                        |                         |                            |                |                         |  |  |  |  |  |  |  |  |

|                                   | <23:16> | 周波数同調ワードNo.1 <23:16>                                                  |                            |                         |                  |                        |                         |                            |                |                         |  |  |  |  |  |  |  |  |

|                                   | <31:24> | 周波数同調ワードNo.1 <31:24>                                                  |                            |                         |                  |                        |                         |                            |                |                         |  |  |  |  |  |  |  |  |

# AD9954

| レジスタ名<br>(シリアル・<br>アドレス)                   | ビット範囲   | (MSB)<br>ビット7                                     | ビット6              | ビット5                 | ビット4 | ビット3                 | ビット2 | ビット1           | (LSB)<br>ビット0 | デフォルト値<br>または<br>プロファイル |

|--------------------------------------------|---------|---------------------------------------------------|-------------------|----------------------|------|----------------------|------|----------------|---------------|-------------------------|

| RAMセグメント<br>制御ワードNo.0<br>(RSCW0)<br>(0x07) | <7:0>   | RAMセグメント0モード制御<2:0>                               | ノー・ドウェル<br>・アクティブ | RAMセグメント0開始アドレス<9:6> |      |                      |      | PS0=0<br>PS1=0 |               |                         |

|                                            | <15:8>  | RAMセグメント0開始アドレス<5:0>                              |                   |                      |      | RAMセグメント0最終アドレス<9:8> |      |                |               | PS0=0<br>PS1=0          |

|                                            | <23:16> | RAMセグメント0最終アドレス<7:0>                              |                   |                      |      |                      |      |                |               | PS0=0<br>PS1=0          |

|                                            | <31:24> | RAMセグメント0アドレス・ランプ・レート<15:8>                       |                   |                      |      |                      |      |                |               | PS0=0<br>PS1=0          |

|                                            | <39:32> | RAMセグメント0アドレス・ランプ・レート<7:0>                        |                   |                      |      |                      |      |                |               | PS0=0<br>PS1=0          |

| RAMセグメント<br>制御ワードNo.1<br>(RSCW1)<br>(0x08) | <7:0>   | RAMセグメント1モード制御<2:0>                               | ノー・ドウェル<br>・アクティブ | RAMセグメント1開始アドレス<9:6> |      |                      |      | PS0=0<br>PS1=1 |               |                         |

|                                            | <15:8>  | RAMセグメント1開始アドレス<5:0>                              |                   |                      |      | RAMセグメント1最終アドレス<9:8> |      |                |               | PS0=0<br>PS1=1          |

|                                            | <23:16> | RAMセグメント1最終アドレス<7:0>                              |                   |                      |      |                      |      |                |               | PS0=0<br>PS1=1          |

|                                            | <31:24> | RAMセグメント1アドレス・ランプ・レート<15:8>                       |                   |                      |      |                      |      |                |               | PS0=0<br>PS1=1          |

|                                            | <39:32> | RAMセグメント1アドレス・ランプ・レート<7:0>                        |                   |                      |      |                      |      |                |               | PS0=0<br>PS1=1          |

| RAMセグメント<br>制御ワードNo.2<br>(RSCW2)<br>(0x09) | <7:0>   | RAMセグメント2モード制御<2:0>                               | ノー・ドウェル・アクティブ     | RAMセグメント2開始アドレス<9:6> |      |                      |      | PS0=1<br>PS1=0 |               |                         |

|                                            | <15:8>  | RAMセグメント2開始アドレス<5:0>                              |                   |                      |      | RAMセグメント2最終アドレス<9:8> |      |                |               | PS0=1<br>PS1=0          |

|                                            | <23:16> | RAMセグメント2最終アドレス<7:0>                              |                   |                      |      |                      |      |                |               | PS0=1<br>PS1=0          |

|                                            | <31:24> | RAMセグメント2アドレス・ランプ・レート<15:8>                       |                   |                      |      |                      |      |                |               | PS0=1<br>PS1=0          |

|                                            | <39:32> | RAMセグメント2アドレス・ランプ・レート<7:0>                        |                   |                      |      |                      |      |                |               | PS0=1<br>PS1=0          |

| RAMセグメント<br>制御ワードNo.3<br>(RSCW3)<br>(0x0A) | <7:0>   | RAMセグメント3モード制御<2:0>                               | ノー・ドウェル・アクティブ     | RAMセグメント3開始アドレス<9:6> |      |                      |      | PS0=1<br>PS1=1 |               |                         |

|                                            | <15:8>  | RAMセグメント3開始アドレス<5:0>                              |                   |                      |      | RAMセグメント3最終アドレス<9:8> |      |                |               | PS0=1<br>PS1=1          |

|                                            | <23:16> | RAMセグメント3最終アドレス<7:0>                              |                   |                      |      |                      |      |                |               | PS0=1<br>PS1=1          |

|                                            | <31:24> | RAMセグメント3アドレス・ランプ・レート<15:8>                       |                   |                      |      |                      |      |                |               | PS0=1<br>PS1=1          |

|                                            | <39:32> | RAMセグメント3アドレス・ランプ・レート<7:0>                        |                   |                      |      |                      |      |                |               | PS0=1<br>PS1=1          |

| RAM (0x0B)                                 |         | RAM [1023:0] <31:0> (読み出し命令書き込みRAMシグネチャ・レジスタ・データ) |                   |                      |      |                      |      |                |               |                         |

表8. レジスタ・マップ—リニア掃引イネーブル・ビットが真の場合 (CFR1&lt;21&gt;=1)

注: RAMイネーブル・ビットCFR1&lt;31&gt;は、RAMセグメント制御ワードではなくRAMそのものをアクティブにするだけです。

| レジスタ名<br>(シリアル・<br>アドレス)              | ビット範囲           | (MSB)<br>ビット7                                                         | ビット6                       | ビット5                    | ビット4             | ビット3                    | ビット2                       | ビット1                      | (LSB)<br>ビット0   | デフォルト値<br>または<br>プロファイル |  |  |  |  |  |  |  |

|---------------------------------------|-----------------|-----------------------------------------------------------------------|----------------------------|-------------------------|------------------|-------------------------|----------------------------|---------------------------|-----------------|-------------------------|--|--|--|--|--|--|--|

| 制御機能<br>レジスタNo.1<br>(CFR1)<br>(0x00)  | <7:0>           | デジタル・<br>パワーダウン                                                       | Comp<br>パワーダウン             | DAC<br>パワーダウン           | クロック入力<br>パワーダウン | 外部パワー<br>ダウン・モード        | CRYSTAL<br>OUTビン・<br>アクティブ | SYNC_CLK<br>出力ディス<br>エーブル | 未使用             | 0x00                    |  |  |  |  |  |  |  |

|                                       | <15:8>          | I/O UDで<br>SRRをロード                                                    | 周波数<br>アキュムレータ<br>を自動クリア   | 位相<br>アキュムレータ<br>を自動クリア | SINE出力を<br>イネーブル | 周波数<br>アキュムレータ<br>をクリア  | 位相<br>アキュムレータ<br>をクリア      | SDIO入力のみ                  | LSB<br>ファースト    | 0x00                    |  |  |  |  |  |  |  |

|                                       | <23:16>         | 自動SYNC<br>イネーブル                                                       | ソフトウェア<br>手動同期             | リニア掃引<br>イネーブル          | 未使用              | 未使用                     | 未使用                        | 未使用                       | 未使用             | 0x00                    |  |  |  |  |  |  |  |

|                                       | <31:24>         | RAM<br>イネーブル                                                          | RAMデステイ<br>ネーションは<br>位相ワード | 内部プロファイル制御<2:0>         |                  |                         | I/O UDで<br>ARRをロード         | 出力整形<br>キーイング・<br>イネーブル   | 自動出力整形<br>キーイング | 0x00                    |  |  |  |  |  |  |  |

| 制御機能レジスタ<br>No.2 (CFR2)<br>(0x01)     | <7:0>           | REFCLK乗算器<br>0x00または0x01、または0x02または0x03：バイパス乗算器<br>0x04~0x14：4×~20×倍倍 |                            |                         |                  | VCO範囲                   | チャージ・ポンプ電流<1:0>            |                           |                 | 0x00                    |  |  |  |  |  |  |  |

|                                       | <15:8>          | 未使用                                                                   |                            |                         | 高速同期<br>イネーブル    | ハードウェア<br>手動同期<br>イネーブル | CRYSTAL<br>OUTビン・<br>アクティブ | 未使用                       | 未使用             | 0x00                    |  |  |  |  |  |  |  |

|                                       | <23:16>         | 未使用                                                                   |                            |                         |                  |                         |                            |                           | 未使用             | 0x00                    |  |  |  |  |  |  |  |

| 振幅スケール係数<br>(ASF)<br>(0x02)           | <7:0><br>(0x07) | 振幅スケール係数レジスタ<7:0>                                                     |                            |                         |                  |                         |                            |                           |                 |                         |  |  |  |  |  |  |  |

|                                       | <15:8>          | 自動ランプ・<br>レート速度制御<1:0>                                                |                            | 振幅スケール係数レジスタ<13:8>      |                  |                         |                            |                           |                 |                         |  |  |  |  |  |  |  |

| 振幅ランプ・<br>レート(ARR)<br>(0x03)          | <7:0>           | 振幅ランプ・レート・レジスタ<7:0>                                                   |                            |                         |                  |                         |                            |                           |                 |                         |  |  |  |  |  |  |  |

| 周波数同調<br>ワード (FTW0)<br>(0x04)         | <7:0>           | 周波数同調ワードNo.0 <7:0>                                                    |                            |                         |                  |                         |                            |                           |                 |                         |  |  |  |  |  |  |  |

|                                       | <15:8>          | 周波数同調ワードNo.0 <15:8>                                                   |                            |                         |                  |                         |                            |                           |                 |                         |  |  |  |  |  |  |  |

|                                       | <23:16>         | 周波数同調ワードNo.0 <23:16>                                                  |                            |                         |                  |                         |                            |                           |                 |                         |  |  |  |  |  |  |  |

|                                       | <31:24>         | 周波数同調ワードNo.0 <31:24>                                                  |                            |                         |                  |                         |                            |                           |                 |                         |  |  |  |  |  |  |  |

| 位相オフセット・<br>ワード (POW0)<br>(0x05)      | <7:0>           | 位相オフセット・ワードNo.0 <7:0>                                                 |                            |                         |                  |                         |                            |                           |                 |                         |  |  |  |  |  |  |  |

|                                       | <15:8>          | オープン<1:0>                                                             |                            | 位相オフセット・ワードNo.0 <13:8>  |                  |                         |                            |                           |                 |                         |  |  |  |  |  |  |  |

| 周波数同調ワード<br>(FTW1)<br>(0x06)          | <7:0>           | 周波数同調ワードNo.1 <7:0>                                                    |                            |                         |                  |                         |                            |                           |                 |                         |  |  |  |  |  |  |  |

|                                       | <15:8>          | 周波数同調ワードNo.1 <15:8>                                                   |                            |                         |                  |                         |                            |                           |                 |                         |  |  |  |  |  |  |  |

|                                       | <23:16>         | 周波数同調ワードNo.1 <23:16>                                                  |                            |                         |                  |                         |                            |                           |                 |                         |  |  |  |  |  |  |  |

|                                       | <31:24>         | 周波数同調ワードNo.1 <31:24>                                                  |                            |                         |                  |                         |                            |                           |                 |                         |  |  |  |  |  |  |  |

| 負のリニア掃引<br>制御ワード<br>(NLSCW)<br>(0x07) | <7:0>           | 立ち下がり△周波数同調ワード<7:0>                                                   |                            |                         |                  |                         |                            |                           |                 |                         |  |  |  |  |  |  |  |

|                                       | <15:8>          | 立ち下がり△周波数同調ワード<15:8>                                                  |                            |                         |                  |                         |                            |                           |                 |                         |  |  |  |  |  |  |  |

|                                       | <23:16>         | 立ち下がり△周波数同調ワード<23:16>                                                 |                            |                         |                  |                         |                            |                           |                 |                         |  |  |  |  |  |  |  |

|                                       | <31:24>         | 立ち下がり△周波数同調ワード<31:24>                                                 |                            |                         |                  |                         |                            |                           |                 |                         |  |  |  |  |  |  |  |

|                                       | <39:32>         | 立ち下がり掃引ランプ・レート・ワード<7:0>                                               |                            |                         |                  |                         |                            |                           |                 |                         |  |  |  |  |  |  |  |

# AD9954

| レジスタ名<br>(シリアル・<br>アドレス)              | ビット範囲   | (MSB)<br>ビット7 | ビット6 | ビット5 | ビット4 | ビット3 | ビット2 | ビット1 | (LSB)<br>ビット0           | デフォルト値<br>または<br>プロファイル |

|---------------------------------------|---------|---------------|------|------|------|------|------|------|-------------------------|-------------------------|

| 正のリニア掃引<br>制御ワード<br>(PLSCW)<br>(0x08) | <7:0>   |               |      |      |      |      |      |      | 立ち上がり△周波数同調ワード<7:0>     | PS0=1                   |

|                                       | <15:8>  |               |      |      |      |      |      |      | 立ち上がり△周波数同調ワード<15:8>    | PS0=1                   |

|                                       | <23:16> |               |      |      |      |      |      |      | 立ち上がり△周波数同調ワード<23:16>   | PS0=1                   |

|                                       | <31:24> |               |      |      |      |      |      |      | 立ち上がり△周波数同調ワード<31:24>   | PS0=1                   |

|                                       | <39:32> |               |      |      |      |      |      |      | 立ち上がり掃引ランプ・レート・ワード<7:0> | PS0=1                   |

## コントロール・レジスタ・ビットの説明

### 制御機能レジスタNo.1 (CFR1)

CFR1を使用して、AD9954のさまざまな機能、特長、モードを制御します。各ビットの機能について以下に説明します。

#### CFR1<31> : RAMイネーブル・ビット

CFR1<31>=0 (デフォルト)。CFR1<31>が非アクティブの場合、RAMの動作をディスエーブルにし、シングルトーン動作モードまたはリニア掃引動作モードをイネーブルにします。

CFR1<31>=1。CFR1<31>がアクティブの場合、RAMの動作をイネーブルにします。現在のプロファイルのRSCWのモード制御ビットによって、通常動作のアクセス制御を制御します。

#### CFR1<30> : RAMデスティネーション・ビット

CFR1<30>=0 (デフォルト)。CFR1<31>がアクティブの場合、RAMデスティネーション・ビットをロジック0 (CFR1<30>=0) にすると、RAM出力によって位相アキュムレータを駆動する (つまり、周波数同調ワード) 構成になります。CFR1<31>が非アクティブの場合、CFR1<30>はドント・ケアです。

CFR1<30>=1。CFR1<31>がアクティブの場合、RAMデスティネーション・ビットをロジック1 (CFR1<30>=1) にすると、RAM出力によって位相オフセット加算器を駆動する (つまり、DDSコアの位相オフセットを設定する) 構成になります。

#### CFR1<29:27> : 内部プロファイル制御ビット

これらのビットによって、RAMの使用時にプロファイル・ビットが無視され、AD9954が自動プロファイル・ループ・シーケンスに入ります。これによりユーザーは、外部入力なしで動作する周波数/位相の複合掃引ができるようになります。詳細については、内部プロファイル制御のセクションを参照してください。

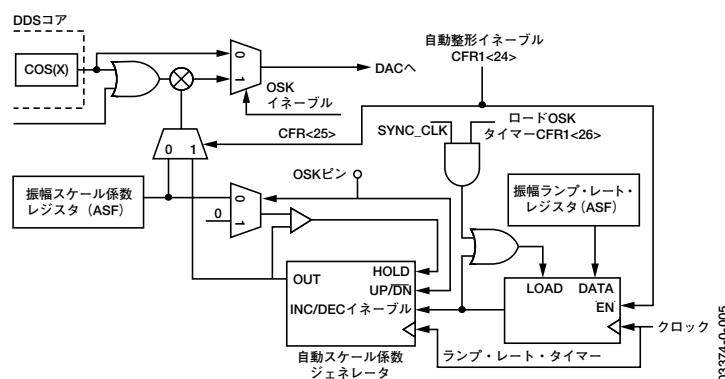

#### CFR1<26> : 振幅ランプ・レート負荷制御ビット

CFR1<26>=0 (デフォルト)。振幅ランプ・レート・タイマーは、タイムアウト時 (timer == 1) にのみロードされ、I/O UPDATE入力信号ではロードされません。

CFR1<26>=1。振幅ランプ・レート・タイマーは、タイムアウト時 (timer == 1) かI/O UPDATE入力信号があるときにロードされます。

CFR1<25> : 整形オン/オフ・キーイング・イネーブル・ビット

CFR1<25>=0 (デフォルト)。整形オン/オフ・キーイングをバイパスします。

CFR1<25>=1。整形オン/オフ・キーイングをイネーブルにします。イネーブルになると、CFR1<24>がこの機能の動作モードを制御します。

CFR1<24> : 自動整形オン/オフ・キーイング・イネーブル・ビット (CFR1<25>がアクティブ・ハイの場合のみ有効)

CFR1<24>=0 (デフォルト)。CFR1<25>がアクティブの場合、CFR1<24>をロジック0にして、手動の整形オン/オフ・キーイング動作をイネーブルにします。DACに送信された各振幅サンプルに振幅スケール係数をかけて乗算します。詳細については、整形オン/オフ・キーイングのセクションを参照してください。

CFR1<24>=1。CFR1<25>がアクティブの場合、CFR1<24>をロジック1にして、自動の整形オン/オフ・キーイング動作をイネーブルにします。OSKピンをハイレベルにトグルすると、出力スケーラは、振幅ランプ・レートによって決まるレートでゼロ・スケールから振幅スケール係数まで増加します。OSKピンをローレベルにトグルすると、振幅ランプ・レートで振幅スケール係数からゼロ・スケールまで出力が減少します。詳細については、整形オン/オフ・キーイングのセクションを参照してください。

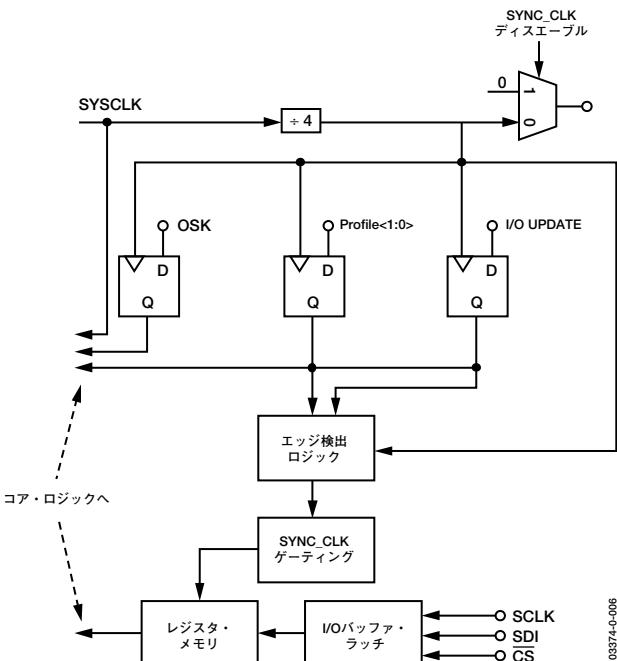

#### CFR1<23> : 自動同期イネーブル・ビット

CFR1<23>=0 (デフォルト)。複数のAD9954の自動同期機能が非アクティブです。

CFR1<23>=1。複数のAD9954の自動同期機能がアクティブです。デバイスは、内部同期クロック (SYNC\_CLK) の同期をとってsync-in入力に存在する信号に合わせます。詳細については、複数のAD9954の同期化のセクションを参照してください。

#### CFR1<22> : 複数のAD9954のソフトウェア手動同期

CFR1<22>=0 (デフォルト)。手動同期機能は非アクティブです。

*CFR1<22>*=1。ソフトウェア制御の手動同期機能を実行します。SYNC\_CLK立ち上がりエッジを1 SYNC\_CLKサイクルだけ進めて、このビットをクリアします。立ち上がりエッジを何回も進めるには、そのつどこのビットをセットする必要があります。詳細については、複数のAD9954の同期化のセクションを参照してください。

*CFR1<21>*：リニア周波数掃引|イネーブル

*CFR1<21>*=0（デフォルト）。AD9954のリニア周波数掃引機能は非アクティブです。

*CFR1<21>*=1。AD9954のリニア周波数掃引機能をイネーブルにします。イネーブルになると、立ち上がりまたは立ち下がりの△周波数同調ワードがプログラムされたランプ・レートで周波数アキュムレータに入り、Profile 0入力の制御によって出力周波数が増減します。詳細については、リニア掃引モードのセクションを参照してください。

*CFR1<20:16>*：未使用

*CFR1<15>*：リニア掃引ランプ・レート・ロード制御ビット

*CFR1<15>*=0（デフォルト）。リニア掃引ランプ・レート・タイマーは、タイムアウト時（timer == 1）にのみロードされ、I/O UPDATE入力信号ではロードされません。

*CFR1<15>*=1。リニア掃引ランプ・レート・タイマーは、タイムアウト時（timer == 1）かI/O UPDATE入力信号があるときにロードされます。

*CFR1<14>*：周波数アキュムレータ・ビットの自動クリア

*CFR1<14>*=0（デフォルト）。△周波数ワードが変更された場合、周波数アキュムレータの現在の状態は変化しません。

*CFR1<14>*=1。I/O UPDATE信号を受信すると、このビットが1サイクルの間、周波数アキュムレータを自動的に同期クリア（0をロード）します。

*CFR1<13>*：位相アキュムレータ・ビットの自動クリア

*CFR1<13>*=0（デフォルト）。周波数同調ワードが適用された場合、位相アキュムレータの現在の状態は変化しません。

*CFR1<13>*=1。I/O UPDATE信号を受信すると、このビットが1サイクルの間、位相アキュムレータを自動的に同期クリア（0をロード）します。

*CFR1<12>*：サイン／コサイン選択ビット

*CFR1<12>*=0（デフォルト）。角度から振幅への変換ロジックにコサイン関数を使用します。

*CFR1<12>*=1。角度から振幅への変換ロジックにサイン関数を使用します。

*CFR1<11>*：周波数アキュムレータのクリア

*CFR1<11>*=0（デフォルト）。周波数アキュムレータが通常に機能します。

*CFR1<11>*=1。周波数アキュムレータのメモリ素子がクリアされ、このビットがクリアされるまでクリア状態のままになります。

*CFR1<10>*：位相アキュムレータのクリア

*CFR1<10>*=0（デフォルト）。位相アキュムレータが通常に機能します。

*CFR1<10>*=1。位相アキュムレータのメモリ素子がクリアされ、このビットがクリアされるまでクリア状態のままになります。

*CFR1<9>*：SDIO入力のみ

*CFR1<9>*=0（デフォルト）。SDIOピンが双方向動作になります（2線式シリアル・プログラミング・モード）。

*CFR1<9>*=1。シリアル・データI/Oピン（SDIO）が入力専用ピンになります（3線式シリアル・プログラミング・モード）。

*CFR1<8>*： LSBファースト

*CFR1<8>*=0（デフォルト）。MSBファースト・フォーマットがアクティブです。

*CFR1<8>*=1。シリアル・インターフェースが、LSBファースト・フォーマットでシリアル・データを受け付けます。

*CFR1<7>*：デジタル・パワーダウン・ビット

*CFR1<7>*=0（デフォルト）。すべてのデジタル機能とクロックがアクティブです。

*CFR1<7>*=1。すべての非I/Oデジタル機能を停止させ、消費電力を大幅に低減します。

*CFR1<6>*：コンバレータ・パワーダウン・ビット

*CFR1<6>*=0（デフォルト）。コンバレータの動作をイネーブルにします。

*CFR1<6>*=1。コンバレータをディスエーブルにし、消費電力を最低の状態にします。

*CFR1<5>*：DACパワーダウン・ビット

*CFR1<5>*=0（デフォルト）。DACの動作をイネーブルにします。

*CFR1<5>*=1。DACをディスエーブルにし、消費電力を最低の状態にします。

*CFR1<4>*：クロック入力パワーダウン・ビット

*CFR1<4>*=0（デフォルト）。クロック入力回路の動作をイネーブルにします。

*CFR1<4>*=1。クロック入力回路をディスエーブルにし、デバイスの消費電力を最低の状態にします。

# AD9954

**CFR1<3>** : 外部パワーダウン・モード

CFR1<3>=0 (デフォルト)。選択された外部パワーダウン・モードは、高速回復パワーダウン・モードです。このモードでは、PWRDWNCTL入力ピンがハイレベルになると、デジタル・ロジックとDACデジタル・ロジックがパワーダウンします。DACバイアス回路、コンバレータ、PLL、発振器、クロック入力回路はパワーダウンしません。

CFR1<3>=1。選択された外部パワーダウン・モードは、フル・パワーダウン・モードです。このモードでは、PWRDWNCTL入力ピンがハイレベルになると、すべての機能がパワーダウンします。これには、パワーアップに時間がかかるDACとPLLも含まれます。

**CFR1<2>** : リニア掃引ノードウェル・ビット

CFR1<2>=0 (デフォルト)。リニア掃引ノードウェル機能は非アクティブです。

CFR1<2>=1。リニア掃引ノードウェル機能がアクティブです。リニア掃引イネーブル・ビットCFR1<21>がアクティブで、CFR1<2>もアクティブの場合には、リニア掃引ノードウェル機能がアクティブになります。詳細については、リニア掃引モードのセクションを参照してください。CFR1<21>がクリアされている場合、このビットはドント・ケアです。

**CFR1<1>** : SYNC\_CLKディスエーブル・ビット

CFR1<1>=0 (デフォルト)。SYNC\_CLKピンはアクティブです。

CFR1<1>=1。SYNC\_CLKピンが静的ロジック0状態になることで、デジタル回路から生じるノイズが最小になります。同期回路が内部的にアクティブのままであるため、通常のデバイス・タイミングが維持されます。

**CFR1<0>** : 未使用。0のままにしておく。

**制御機能レジスタNo.2 (CFR2)**

CFR2を使用して、主にチップのアナログ部に関するAD9954のさまざまな機能、特長、モードを制御します。

**CFR2<15:12>** : 未使用

**CFR2<11>** : 高速同期イネーブル・ビット

CFR2<11>=0 (デフォルト)。高速同期エンハンスマント機能はオフです。

CFR2<11>=1。高速同期エンハンスマント機能はオンです。50MHzを超えてSYNC\_CLK入力 (200MSPS SYSCLK) の自動同期機能を使用するときは、このビットをセットしてください。詳細については、複数のAD9954の同期化のセクションを参照してください。

**CFR2<10>** : ハードウェア手動同期イネーブル・ビット

CFR2<10>=0 (デフォルト)。ハードウェア手動同期機能はオフです。

CFR2<10>=1。ハードウェア手動同期機能をイネーブルにします。このビットがセットされている間、SYNC\_INピンの立ち上がりエッジで、デバイスはSYNC\_CLK立ち上がりエッジを1 REFCLKサイクルだけ進めます。ソフトウェア手動同期イネーブル・ビットと異なり、このビットはセルフクリアしません。ハードウェア手動同期モードがイネーブルになっていると、このビットがクリアされるまでイネーブル状態のままになります。詳細については、複数のAD9954の同期化のセクションを参照してください。

**CFR2<9>** : CRYSTAL OUTイネーブル・ビット

CFR2<9>=0 (デフォルト)。CRYSTAL OUTピンは非アクティブです。

CFR2<9>=1。CRYSTAL OUTピンはアクティブです。アクティブの場合、水晶発振器回路の出力がCRYSTAL OUTピンを駆動します。さらに、このピンを他のデバイスに接続して、リファレンス周波数を生成することができます。発振器は、20~30MHzの範囲で水晶発振子に応答します。

**CFR2<8>** : 未使用

**CFR2<7:3>** : リファレンス・クロック乗算器制御ビット

この5ビット・ワードで、クロック乗算器 (PLL) ブロックから出る乗算値を制御します。有効値は、10進の4~20 (0x04~0x14) です。この範囲外の値を入力すると、クロック乗算器をバイパスします。詳細については、位相ロック・ループ (PLL) のセクションを参照してください。

**CFR2<2>** : VCO範囲制御ビット

このビットを使用して、VCOの範囲設定を制御します。CFR2<2>==0 (デフォルト) のとき、VCOは100~250MHzの範囲で動作します。CFR2<2>==1のときは、250~400MHzの範囲で動作します。

**CFR2<1:0>** : チャージ・ポンプの電流制御ビット

これらのビットを使用して、チャージ・ポンプの電流設定を制御します。デフォルト設定のCFR2<1:0>で、チャージ・ポンプ電流を75μAのデフォルト値に設定します。ビット (01, 10, 11) が1つずつ増えるたびに、チャージ・ポンプ電流に25μAの電流が加算されます (100μA, 125μA, 150μA)。

**その他のレジスタについて**

**振幅スケール係数 (ASF)**

ASFレジスタは、出力整形キーイング (OSK) 動作で使用する14ビットの振幅スケール係数と2ビットの自動ランプ・レート速度値を格納します。自動OSK動作では、ASF<15:14>によって、インクリメント/デクリメントごとの振幅ステップ数をOSKブロックに指示します。ASF<13:0>は、OSK内部乗算器で得られる最大値を設定します。手動OSKモードでは、ASF<15:14>は無効です。ASF<13:0>は、出力スケール係数を直接提供します。OSKイネーブル・ビットがクリアされている場合 (CFR1<25>=0)、このレジスタはデバイス動作に影響を与えません。

### 振幅ランプ・レート (ARR)

ARRレジスタは、自動OSKモードで使用する8ビットの振幅ランプ・レートを格納します。このレジスタで、振幅スケール係数カウンタがインクリメント／デクリメントするレートをプログラミします。OSKを手動モードに設定している場合、またはOSKイネーブルをクリアしている場合は、このレジスタはデバイスの動作に影響を与えません。

### 周波数同調ワード0 (FTW0)

周波数同調ワードは、DDSコアの位相アキュムレータでアキュムレーション・レートを制御する32ビット・レジスタです。その機能はデバイスの動作モードによって異なります。

### 位相オフセット・ワード (POW)

位相オフセット・ワードは、位相オフセット値を格納する14ビット・レジスタです。このオフセット値を位相アキュムレータの出力に加算し、出力信号の電流位相をオフセットします。位相オフセットの正確な値は、次式から得られます。

$$\Phi = \left( \frac{POW}{2^{14}} \right) \times 360^\circ$$

RAMイネーブル・ビットをセットし (CFR1<31>=1)、RAMデスティネーションがクリアされていると (CFR1<30>=0)、RAMが位相オフセット・ワードを提供するため、このレジスタはデバイスの動作に影響を与えません。

### 周波数同調ワード1 (FTW1)

周波数同調ワードは、リニア掃引動作で上位周波数を設定する32ビット・レジスタです。

### 負と正のリニア掃引制御ワード (NLSCW、PLSCW)

レジスタ0x07と0x08は多機能レジスタです。リニア掃引ビットCFR1<21>をイネーブルにすると、レジスタ0x07が負のリニア掃引制御ワード (NLSCW) として機能し、レジスタ0x08は正のリニア掃引制御ワード (PLSCW) として機能します。各リニア掃引制御ワードには、32ビットの△周波数同調ワード (FDFTW、RDFTW) と8ビットの掃引ランプ・レート・ワード (FSRRW、RSRRW) が入っています。△周波数同調ワードによって、得られた同調ワードを周波数アキュムレータがインクリメント／デクリメントする量が決まります。掃引ランプ・レート・ワードは、アキュムレータがインクリメント／デクリメントするレートを同期クロック・サイクルの数で決めます。

### RAMセグメント制御ワード (RSCW0、RSCW1、RSCW2、RSCW3)

リニア掃引イネーブル・ビットCFR1<21>がクリアされると、レジスタ0x07、0x08、0x09、0x0Aは、各RAMセグメントのRAMセグメント制御ワードとして機能します。各RAMセグメント制御ワードは、RAMセグメント・アドレス・ランプ・レート、最終アドレス値、開始アドレス値、RAMセグメント・モード制御、ノー・ドウェル・ビットで構成されています。

### RAMセグメント・アドレス・ランプ・レート、RSCW<39:24>

ランピングなど、アドレス値を1つずつ実行するRAMモードの場合、この16ビット・ワードによって、RAMコントローラが各アドレスで一時停止するSYNC\_CLKサイクルの数を定めます。値0は無効です。1~65535の値を使用できます。

### RAMセグメント最終アドレスRSCW<9:8>、RSCW<23:16>

この不連続な10ビット・シーケンスによって、RAMセグメントの最終アドレス値を規定します。ビットが記載される順序は、書き込むときに求められる順序と同じです。RSCW<23>は、書き込み動作時にはRSCW<9>よりも上位にありますが、最終アドレス値の3番目のMSBに過ぎません。RSCW<9>は、RSCWではRSCW<23>よりも後にきますが、最終アドレス値のMSBです。

### RAMセグメント開始アドレスRSCW<3:0>、<15:10>

この不連続な10ビット・シーケンスによって、RAMセグメントの最終アドレス値を規定します。ビットが記載される順序は、書き込むときに求められる順序と同じです。RSCW<15>は、書き込み動作時にはRSCW<3>よりも上位にありますが、最終アドレス値の5番目のMSBに過ぎません。RSCW<3>は、RSCWではRSCW<15>よりも後にきますが、最終アドレス値のMSBです。

### RAMセグメント・モード制御RSCW<7:5>

この3ビット・シーケンスによって、RAMセグメントの動作モードを決めます。可能なRAMモードは5つだけであるため、値0~5だけが有効です。さまざまなRAMモードのビットの組み合わせを決めるには、表9を参照してください。

### RAMセグメント・ノー・ドウェル・ビットRSCW<4>

このビットで、掃引プロファイルのノー・ドウェル機能を設定します。規定された先頭から規定された最終まで掃引するプロファイルでは、次のプロファイルが選択されるまでRAMコントローラが最終アドレスで一時停止します。このビットがセットされている場合は、開始アドレスに戻って、次のプロファイルが選択されるまでそこで一時停止します。

### RAM

AD9954には、1024×32ブロックのSRAMが組み込まれています。RAMは双方向のシングルポートです。RAMとの間では読み出し／書き込みの動作が有効ですが、2つの動作を同時にすることはできません。シリアルI/Oポートからの書き込み動作が優先されます。読み出し動作中にRAMへの書き込みが行われると、読み出し動作が停止します。RAMはさまざまな方法で制御できます。制御機能レジスタのデータによって制御したり、RAMセグメント制御ワード<7:5>で説明した動作モードで規定することもできます。RAMの読み出し／書き込み制御については、サポートするそれぞれのモードごとに説明します。

RAMイネーブル・ビット (CFR1<31>) をセットすると、RAMデスティネーション・ビット (CFR1<30>) の状態に応じて、RAM出力からの入力で位相アキュムレータを駆動するか、あるいは位相オフセット加算器を駆動するかを選択できます。CFR1<30>がロジック1の場合、RAM出力は位相オフセット加算器に接続され、デバイスに位相オフセット制御ワードを提供します。CFR1<30>がロジック0 (デフォルト条件) の場合、RAM出力は位相アキュムレータの入力に接続され、デバイスの周波数同調ワードを提供します。RAM出力が位相アキュムレータを駆動する場合、位相オフセット・ワード (POW、アドレス0x05) が位相オフセット加算器を駆動します。同様に、RAM出力が位相オフセット加算器を駆動する場合、周波数同調ワード (FTW、アドレス0x04) が位相アキュムレータを駆動します。CFR1<31>がロジック0のとき、シリアル・ポートから書き込まれない限り、RAMは非アクティブです。AD9954のパワーアップ状態はシングルトーン・モードで、このときRAMイネーブル・ビットは非アクティブです。RAMは、Profile<1:0>入力ピンによって制御される4つの重複しないスライスに分割されます。

# AD9954

特に規定されていない限り、Profile<1:0>入力ピンとそれぞれのRAMセグメント制御ワードによって、すべてのRAM書き込み／読み出しが制御されます。通常動作時はRAMに書き込みができますが、RAMに書き込みの命令を与えるI/O動作によってRAMからの読み出し動作が直ちに停止するため、現在の動作モードが機能しなくなります。ただし、RAMからの読み出しを行わないシングルトーン・モードは例外です。

RAMへの書き込みは次のように行われます。希望するRAMセグメント制御ワードを設定した後、プロファイル・セレクト・ピンPS<1:0>によって、そのRAMセグメントを選択します。命令バイトの処理中に、RAMのアドレス0x0Bを書き込みます。シリアル・ポートとRAMコントローラが連携してプロファイルの幅を決定し、シリアル・ポートは、開始アドレスから終了アドレスまで、規定された数の32ビット・ワードを連続的に受け付けます。次の例を参考にしてください。

- RAMセグメント制御ワード1が、RAMの開始アドレスを256に記載し、終了アドレスを511に記載します。

- PS0=1およびPS1=0

- 命令バイトは10001001です。

RAMコントローラが、256の32ビット・ワードを受けるようにシリアル・ポートを設定します。最初の32ビットがワードとして構文解析され、RAMアドレス256に送信され、次の32ビットがまた構文解析されて257に送信され、以下同様に256ワードが送信されるまでこれを繰り返します（この動作では、総計8192のデータ・ビットになります）。

## 動作モード

### シングルトーン・モード

シングルトーン・モードでは、DDSコアが1つの同調ワードを使用します。FTW0にどんな値が格納されても、すべて位相アキュムレータに供給されます。この値は手動によってのみ変更できます。変更する場合は、FTW0に新しい値を書き込み、I/O UPDATEを実行します。位相オフセット・レジスタによって位相調整ができます。

### RAM制御動作モード

#### ダイレクト・スイッチ・モード

ダイレクト・スイッチ・モードによって、FSKまたはPSKの変調が可能になります。AD9954をダイレクト・スイッチ・モードにプログラムするには、RAMイネーブル・ビットを真に設定し、希望する各プロファイルのRAMセグメント・モード制御ビットをロジック000 (b) に設定します。このモードでは、現在のプロファイルについてRAMセグメント開始アドレスからRAMの内容を読み出すだけです。ダイレクト・スイッチ・モードでは、アドレス・ランピングはイネーブルになりません。

4トーンFSKを実行するには、ユーザーは、各RAMセグメント制御ワードをダイレクト・スイッチ・モードに設定し、一意の開始アドレス値をプログラムします。さらに、RAMイネーブル・ビットを真に設定してRAMをイネーブルにし、RAMデステイニエーション・ビットを偽に設定してRAM出力を周波数同調ワードに設定します。Profile<1:0>の入力は、4トーンFSKデータ入力です。プロファイルが変更されると、新しいプロファイルに格納された周波数同調ワードを位相アキュムレータにロードし、これを使用して位相連続方式で現在格納されている値をインクリメントします。位相オフセット・ワードが、位相オフセット加算器を駆動します。2トーンFSKを実行するときは、データに対して1つのプロファイル・ピンだけを使用します。

AD9954をPSK変調用に設定する方法は、FSKの場合と似ていますが、RAMデステイニエーション・ビットをロジック1に設定する点だけは違います。これによって、RAM出力が位相オフセット加算器を駆動できるようになります。FTW0が位相アキュムレータへの入力を駆動します。プロファイル・ピンをトグルすると、電流位相値が変更（変調）されます。RAMの上位14ビットが位相加算器を駆動します(<31:18>)。RAMデステイニエーション・ビットをセットしているときは、RAM出力のビット<17:0>は使用しません。ダイレクト・スイッチ・モードでは、ノー・ドウェル・ビットはドント・ケアです。

#### ランプアップ・モード

ランプアップ・モードでは、セグメント化されたRAM機能と組み合わせて、最大4つの異なる「掃引プロファイル」をAD9954にプログラムできます。AD9954をランプアップ・モードにプログラムするには、RAMイネーブル・ビットを真にし、使用する各プロファイルのRAMモード制御ビットをロジック001 (b) にプログラムします。メモリをイネーブルにするどのモードでもそうですが、RAMデステイニエーション・ビットによって、RAM出力が位相アキュムレータを駆動するか、位相オフセット加算器を駆動するかを制御します。

掃引を開始すると（I/O UPDATEまたはプロファイル・ビットの変更を使用）、RAMアドレス・ジェネレータが、現在のRSCWのRAMセグメント開始アドレス・ビットをロードして、このアドレスからRAM出力を駆動します。また、ランプ・レート・タイマーがRAMセグメント・アドレス・ランプ・レート・ビットをロードします。ランプ・レート・タイマーが1サイクルを完了すると、RAMアドレス・ジェネレータが次のアドレスにインクリメントし、タイマーがランプ・レート・ビットを再ロードして、新しいカウントダウン・サイクルを開始します。このシーケンスは、RAMアドレス・ジェネレータが現在のRSCWのRAMセグメント最終アドレス・ビットに等しいアドレスにインクリメントするまで続きます。

RAMアドレス・ジェネレータが最終アドレスに等しくなったときにノー・ドウェル・ビットがクリアされている場合は、終端周波数に達したため、ジェネレータがインクリメントを停止します。掃引は完了しており、前述のように、開始から最終RAMアドレスまで別の掃引をイネーブルにするI/O UPDATEまたはプロファイルの変更が検出されるまで再開しません。

RAMアドレス・ジェネレータが最終アドレスに等しくなったときにノー・ドウェル・ビットがセットされている場合は、次のランプ・レート・タイマー・サイクルの後で位相アキュムレータがクリアされます。位相アキュムレータは、I/O UPDATE入力またはプロファイルの変更によって別の掃引が開始されるまでクリアされたままでです。

ランプアップ・モードのもう1つのアプリケーションは非対称FSK変調です。RAMを2つのセグメントに設定し、Profile<0>ビットをデータ入力に使用すると、非対称なランプ型FSKになります。

#### 双方向ランプ・モード

双方向ランプ・モードでは、Profile<0>信号を制御入力として使用し、2つの周波数間で対称的な掃引を実行します。AD9954を双方向ランプ・モードにプログラムするには、RAMイネーブル・ビットを真にし、RSCW0のRAMモード制御ビットをロジック010 (b) に設定します。双方向ランプ・モードでは、Profile<1>入力は無視され、Profile<0>入力がランプ方向インジケータになります。このモードでは、メモリはセグメント化されず、単一の開始および最終アドレスだけを使用します。RAMの制御に影響を与えるアドレス・レジスタは、Profile 0に関連付けられたRSCWの中にあります。

このモードに入ると (I/O UPDATEやProfile<0>の変更を使用)、RAMアドレス・ジェネレータがRSCW0のRAMセグメント開始アドレス・ビットをロードし、ランプ・レート・タイマーがRAMセグメント・アドレス・ランプ・レート・ビットをロードします。RAMは開始アドレスからデータを駆動し、ランプ・レート・タイマーが1までのカウント・ダウンを開始します。このモードで動作している間は、Profile<0>ピンをトグルしても、デバイスが内部I/O UPDATEを生成することはできません。Profile<0>ピンがランプ方向インジケータとして機能しているときに、I/Oバッファから内部レジスタへのデータ転送を開始するには、I/O UPDATEピンの立ち上がりエッジを使用しなければなりません。

現在、RAMアドレス制御はProfile<0>入力の関数です。Profile<0>ビットがロジック1のとき、RAMアドレス・ジェネレータは、ランプ・レート・タイマーが1サイクル完了する(次いでタイマー再開のために再ロードする)と次のアドレスへインクリメントします。ランプアップ・モードのように、Profile<0>入力がハイレベルになっている限り、RAMアドレス・ジェネレータが最終アドレスにインクリメントするまでこのシーケンスが続けます。Profile<0>入力がローレベルになると、RAMアドレス・ジェネレータは直ちにデクリメントし、ランプ・レート・タイマーが再ロードされます。Profile<0>入力がローレベルになっている限り、RAMアドレスが開始アドレスに等しくなるまで、RAMアドレス・ジェネレータはランプ・レート周期でデクリメントを続けます。

デバイスがこのモードにプログラムされている限り、Profile<0>入力信号によってランプアップ／ダウンのシーケンスを制御します。このモードでは、ノー・ドウェル・ビットも、Profile 1、2、3に関連付けられたRAMセグメント制御ワード内のすべてのデータもドント・ケアです。双方向ランプ・モードでのRAMの制御には、Profile 0のRAMセグメント制御ワード内の情報だけを使用します。

#### 連続双方向ランプ・モード

連続双方向ランプ・モードを使用すると、2つの周波数間で自動対称掃引ができます。AD9954を連続双方向ランプ・モードにプログラムするには、RAMイネーブル・ビットを真にし、使用する各プロファイルのRAMモード制御ビットをロジック011 (b) に設定します。

このモードに入ると (I/O UPDATEやProfile<1:0>の変更を使用)、RAMアドレス・ジェネレータが現在のRSCWのRAMセグメント開始アドレス・ビットをロードし、ランプ・レート・タイマーがRAMセグメント・アドレス・ランプ・レート・ビットをロードします。RAMは開始アドレスからデータを駆動し、ランプ・レート・タイマーは1までのカウント・ダウンを開始します。ランプ・レート・タイマーが1サイクルを完了すると、RAMアドレス・ジェネレータが次のアドレスまでインクリメントし、タイマーはランプ・レート・ビットを再ロードしてカウント・ダウンを継続します。RAMアドレス・ジェネレータが現在のRSCWのRAMセグメント最終アドレス・ビットに等しいアドレスにインクリメントするまで、このシーケンスが続けます。終端アドレスに達すると、RAMアドレス・ジェネレータは、RAMセグメント開始アドレスになるまでランプ・レートの値をデクリメントします。開始アドレスに至ると、このシーケンス全体が繰り返されます。

デバイスがこのモードにプログラムされている限り、このシーケンス全体が繰り返されます。このモードでは、ノー・ドウェル・ビットはドント・ケアです。一般にこのモードの制御は双方向ランプ・モードの場合と同じですが、異なる点はランプのアップ／ダウンが自動で(Profile<0>入力による外部制御なし)、スイッチング・プロファイルが有効であることです。このモードになると、アドレス・ジェネレータは開始アドレスから最終アドレスまでランプしてから、ランプ・レート・レジスタにプログラムされたレートで開始アドレスまで戻ります。このモードによって、自動のこぎり波掃引特性が得られます。

#### 連続再循環モード

連続再循環モードでは、2つの周波数間で自動的な連続单方向掃引ができます。AD9954を連続再循環モードにプログラムするには、RAMイネーブル・ビットを真にし、使用する各プロファイルのRAMモード制御ビットをロジック100 (b) に設定します。

このモードに入ると (I/O UPDATEやProfile<1:0>の変更を使用)、RAMアドレス・ジェネレータが現在のRSCWのRAMセグメント開始アドレス・ビットをロードし、ランプ・レート・タイマーがRAMセグメント・アドレス・ランプ・レート・ビットをロードします。RAMは開始アドレスからデータを駆動し、ランプ・レート・タイマーは1までのカウント・ダウンを開始します。ランプ・レート・タイマーが1サイクルを完了すると、RAMアドレス・ジェネレータが次のアドレスまでインクリメントし、タイマーはランプ・レート・ビットを再ロードしてカウント・ダウンを継続します。RAMアドレス・ジェネレータが現在のRSCWのRAMセグメント最終アドレス・ビットと等しいアドレスにインクリメントするまで、このシーケンスが続けます。終端アドレスに達すると、RAMアドレス・ジェネレータがRAMセグメント開始アドレス・ビットを再ロードし、シーケンスが繰り返されます。

デバイスがこのモードにプログラムされている限り、指定のRAMアドレスを循環するシーケンスが繰り返されます。このモードでは、ノー・ドウェル・ビットはドント・ケアです。

# AD9954

RAM制御動作モードに関する注意事項とまとめ

注：

- 1) ユーザーは、開始アドレスを最終アドレスより必ず低くするようにしてください。

- 2) プロファイルの変更やI/O UPDATEの実行によって、現在の掃引が自動的に終了して次の掃引を開始します。

- 3) RAMデスティネーション・ビットを真に設定して、RAM出力が位相オフセット加算器を駆動するようにすることもできます。上の説明は周波数掃引を対象にしていますが、位相掃引動作も可能です。

AD9954には、5つのRAM制御動作モードがあります（表9を参照）。

表9. RAM動作モード

| RSCW<7:5><br>(バイナリ) | モード        | 注                              |

|---------------------|------------|--------------------------------|

| 000                 | ダイレクト・スイッチ | 掃引なし、プロファイル有効、ノードウェル無効         |

| 001                 | ランプアップ     | 掃引、プロファイル有効、ノードウェル有効           |

| 010                 | 双方向ランプ     | 掃引、Profile<0>は方向制御ビット、ノードウェル無効 |

| 011                 | 連続双方向ランプ   | 掃引、プロファイル有効、ノードウェル無効           |

| 100                 | 連続再循環      | 掃引、プロファイル有効、ノードウェル無効           |

| 101、110、111         | オープン       | 無効モード—ダイレクト・スイッチへのデフォルト        |

## 内部プロファイル制御

AD9954には、複合周波数掃引を構成できるモードがあります。このモードでは、タイミング・コントロールをソフトウェアで設定できます。内部プロファイル制御機能で、Profile<1:0>ピンを切り離し、AD9954がプロファイル間の切り替えを制御できるようにします。プロファイル選択ビットの3つの組み合わせに対して、連続またはシングル・バーストのプロファイル切り替えを可能にするモードが定義されています。これらを表10に示します。CFR1<29:27>ビットのいずれかがアクティブの場合、内部プロファイル制御モードが使用されています。内部プロファイル制御は、デバイスがRAMモードで動作しているときにのみ有効です。リニア掃引動作には、内部プロファイル制御はありません。

内部プロファイル制御モードを使用しているとき、RAMセグメント・モード制御ビットはドント・ケアであり、これらのモード制御ビットがランプアップ・モードにプログラムされているかのようにデバイスはすべてのプロファイルを動作させます。RAMアドレス・ジェネレータが現在のプロファイルのメモリ内容を使い果たすと、別のプロファイルに切り替わります。

表10. 内部プロファイル制御

| CFR1<29:27><br>(バイナリ) | モードの内容                                              |

|-----------------------|-----------------------------------------------------|

| 000                   | 内部制御非アクティブ                                          |

| 001                   | 内部制御アクティブ、シングル・バースト、Profile 0、1の順にアクティブにしてから停止      |

| 010                   | 内部制御アクティブ、シングル・バースト、Profile 0、1、2の順にアクティブにしてから停止    |

| 011                   | 内部制御アクティブ、シングル・バースト、Profile 0、1、2、3の順にアクティブにしてから停止  |

| 100                   | 内部制御アクティブ、連続、Profile 0、1の順にアクティブにしてから、0からループを開始     |

| 101                   | 内部制御アクティブ、連続、Profile 0、1、2の順にアクティブにしてから、0からループを開始   |

| 110                   | 内部制御アクティブ、連続、Profile 0、1、2、3の順にアクティブにしてから、0からループを開始 |

| 111                   | 無効                                                  |

シングル・バースト・モードでは、複合掃引を1回実行します。たとえば、デバイスがランプアップ・モードにプログラムされ、CFR1<29:27>ビットがロジック010 (b) に設定されている場合、I/O UPDATEを受け付けると、内部コントロール・ロジックがProfile 0のランプアップ・モード・シーケンスを実行するようデバイスに通知します。Profile 0のRAMセグメント最終アドレス値に到達すると、デバイスは、Profile 1に自動的に切り替え、そのランプアップ・シーケンスの実行を始めます。Profile 1のRAMセグメント最終アドレス値に到達すると、デバイスはProfile 2に自動的に切り替え、そのランプアップ・シーケンスの実行を始めます。Profile 2のRAMセグメント最終アドレス値に到達すると、このシーケンスが終了し、複合掃引が完了します。新しいI/O UPDATEが実行されると、バースト・プロセスを再開します。

連続内部プロファイル制御モードでは、デバイスがこのモードにプログラムされている限り、複合掃引を連続的に実行します。上の例で今度はCFR1<29:27>ビットをロジック101 (b) に設定すると、Profile 2のRAMセグメント最終アドレス値に到達するまで、同じ動作が行われます。ここでシーケンスを停止しないで、Profile 0からシーケンスを繰り返します。

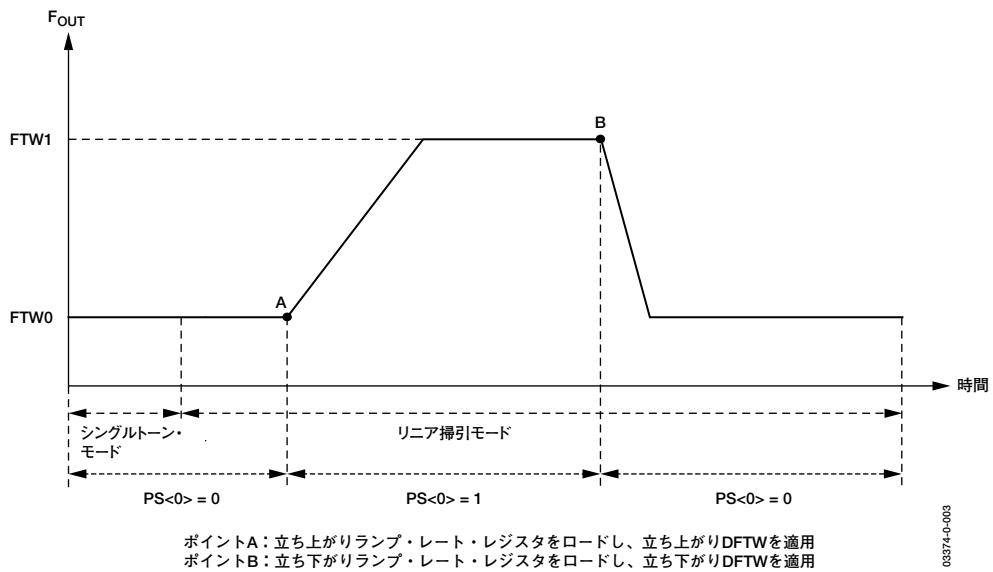

### リニア掃引モード

リニア掃引イネーブル・ビットCR1<21>をセットすると、AD9954はリニア掃引モードになります。リニア掃引モードでは、AD9954の出力周波数は、FTW0によってプログラムされた開始周波数から最終周波数FTW1まで増加するか、FTW1からFTW0まで低下します。このランピング・レートは、△周波数同調ワードとランプ・レート・ワードによって決まります。終端周波数に到達したときのデバイスの動作は、リニア掃引ノー・ドウェル・ビットCFR1<2>が制御します。FTW0からFTW1まで増加するとき、32ビットの立ち上がり△周波数同調ワード(RDFTW)が周波数アキュムレータをインクリメントします。周波数アキュムレータがインクリメントするレートは、8ビットの立ち上がり掃引ランプ・レート・ワード(RSRRW)が制御します。FTW1からFTW0まで低下するとき、32ビットの立ち下がり△周波数同調ワード(FDFTW)はアキュムレータをデクリメントします。アキュムレータがデクリメントするレートは、8ビットの立ち下がり掃引ランプ・レート・ワード(FSRRW)によって決まります。

掃引の方向(FTW1への立ち上がりまたはFTW0への立ち下がり)は、PS<0>ピンが制御します。目的周波数に到達すると、リニア掃引ノー・ドウェル・ビットCFR1<02>の状態によって、PS<0>ピンの状態が変化するまで目的周波数を保持するか、直ちに初期周波数FTW0に復帰します。リニア掃引モードで動作している間、Profile<0>ピンをトグルしても、デバイスは内部I/O UPDATEを生成しません。PS<0>ピンが掃引方向インジケータとして機能しているとき、I/Oバッファから内部レジスタへのデータ転送は、I/O UPDATEピンの立ち上がりエッジを使用しなければ開始できません。

AD9954のリニア掃引機能では、最低周波数をFTW0レジスタにロードし、最高周波数をFTW1レジスタにロードしなければなりません。区別的なノンリニア周波数遷移では、希望する応答を変化させるために周波数遷移が行われている最中にレジスタを再プログラムする必要があります。図20に、代表的な周波数ランプ動作を示します。リセット後、デバイスは最初シングルトーン・モードになります。リニア掃引モードで動作するためのプログラミング手順は、次のとおりです。

- 0) 00でのプロファイル入力。

- 1) リニア掃引イネーブル・ビット(CFR1<21>=1)をセットし、必要に応じてリニア掃引ノー・ドウェル・ビット(CFR1<2>={0,1})をセットまたはクリアします。

- 2) 立ち上がり／立ち下がりの△周波数同調ワードとランプ・レート値をプログラムします。

- 3) 低い出力周波数をレジスタFTW0に、高い出力周波数をレジスタFTW1にプログラムします。

- 4) I/O UPDATEを使って、このデータをレジスタに移動します(出力周波数はFTW0になります)。

- 5) 最低／最高周波数間での掃引の方向を切り換えるために、必要に応じてPS<0>入力を変更します。

図20に、デバイスが最初にシングルトーン・モードでパワーアップすることを示します。プロファイル入力はローレベルで、FTW0入力を位相アキュムレータに設定します。次にユーザーは、シリアル・ポート(図20のポイントA)から、立ち上がり／立ち下がりの△周波数同調ワード、ランプ・レート、リニア掃引イネーブル・ビットを設定して、デバイスを適宜設定します。この例では、リニア掃引ノー・ドウェル・ビットはクリアされます(CFR1<2>=0)。

### リニア掃引機能の一般的な動作

リニア掃引モードでは、PS<1>ピンをロジック0に接続する必要があります。リニア掃引モードをアクティブにして、PS<0>ピンがローレベルからハイレベルに遷移すると、周波数アキュムレータの入力にRDFTWが適用され、掃引レート・タイマーにRSRRレジスタがロードされます。掃引レート・タイマーは初期値から1までカウント・ダウンし、ここで周波数アキュムレータが入力をアキュムレートします。RDFTWのアキュムレーションは、ランプ・レート(RSRR)によって指定されたレートで行われ、周波数加算器の出力がFTW1レジスタ値と等しくなるまで継続します。ここでアキュムレーションが停止し、AD9954は、FTW1によって指定された周波数を出力します。この出力は、PS<0>ピンがロジック1にとどまる限り、FTW1のままでです。

PS<0>ピンがハイレベルからローレベルに遷移すると、周波数アキュムレータの入力にネゲートされたFDFTWが適用され、掃引レート・タイマーにFSRRレジスタがロードされます。タイマーが1までカウント・ダウンするたびに、周波数アキュムレータが入力をアキュムレートします。ランプ・レート(FSRR)で指定されたレートでの、ネゲートされたFDFTWのアキュムレーションは、周波数加算器の出力がFTW0レジスタ値と等しくなるまで継続します。ここでアキュムレーションが停止し、AD9954は、FTW0によって指定された周波数を出力します。この出力は、PS<0>ピンがロジック0にとどまる限り、FTW0のままでです。

# AD9954

図20. リニア掃引周波数プラン

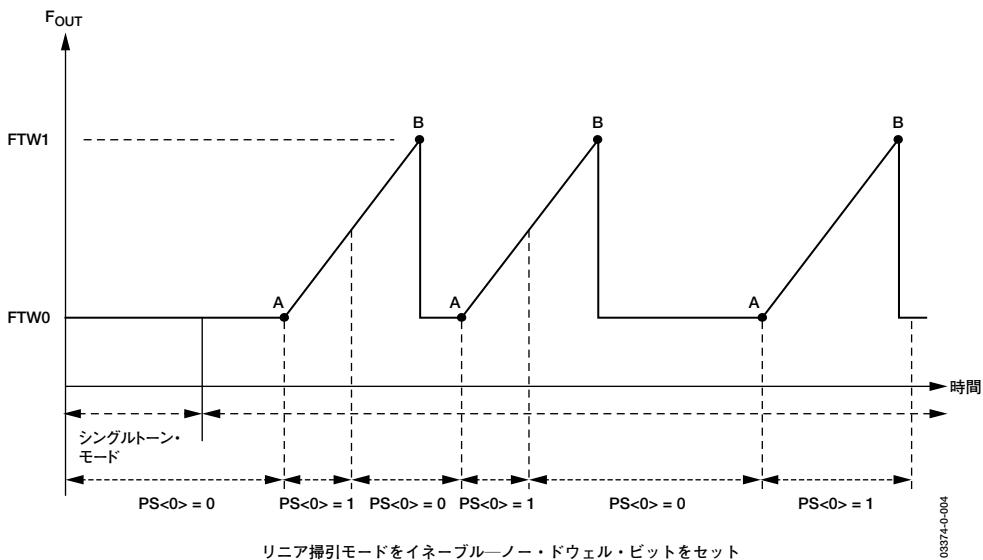

図21. ノー・ドウェル周波数プランを使用したリニア掃引

## リニア掃引のノー・ドウェル機能

リニア掃引機能は、ノー・ドウェル機能で動作できます。リニア掃引ノー・ドウェル・ビットがセットされている(CFR1<2>=1)場合、立ち上がり掃引は、非ノー・ドウェル・リニア掃引モードの場合と同じ方法で開始します。PS<0>入力ピンでの立ち上がりエッジを検出すると、立ち上がり掃引アクションを開始します。周波数が終端周波数に到達するまで、立ち上がり掃引ランプ・レートで設定されたレートと、立ち上がり $\Delta$ 周波数同調ワードで設定された分解能で、掃引を続けます。終端周波数に到達すると、出力周波数はすぐに開始周波数に復帰し、デバイスがPS<0>ピンにそれ以降の立ち上がりエッジを検出するまで、その開始周波数にとどまります。図21に、リニア掃引ノー・ドウェル・ビットをセットしている場合のリニア掃引モード動作の例を示します。Aと記されたポイントはPS0に立ち上がりエッジが検出される場所で、Bと記されたポイントは $F_{OUT}$ が終端周波数に到達したとAD9954が判断し、自動的に開始周波数に復帰する場所です。このモードでは、各掃引でProfile<0>ピンの立ち上がりエッジがそれぞれ必要です。

ノー・ドウェル・ビットを使用するリニア掃引を $FTW0$ から $FTW1$ に掃引するには、正のリニア掃引制御ワードを使用してください。 $PS<0>$ を1から0にトグルしても、ノー・ドウェル・ビットがセットされていれば立ち下がり掃引は開始されず、すでに始まっている正の掃引が中断されることもありません。

## ランプ・レート・タイマーのプログラミング